#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# DYNAMIC SIMULATOR OF A FLIGHT MANAGEMENT SYSTEM FOR COMMERCIAL JETLINER – DEVELOPMENT, INTEGRATION AND APPLICATION

Ming He Liu

A Thesis

In

The Department

Of

Mechanical and Industrial Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

October 2002

©Ming He Liu, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our life Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-77701-4

# **ABSTRACT**

Dynamic Simulator of a Flight Management System

for Commercial Jetliner -

Development, Integration and Application

#### Ming He Liu

Flight management of modern civil aircraft is realized by a system of sophisticated computerized devices and commands, which provides the pilot with navigation, aircraft status and other dynamic flight information enabling him to perform his task correctly. However, rigorous testing of the flight management system (FMS) is needed to discover and remedy any flaw in the hardware or software components so as to ensure proper running of the system, as well as to reveal potential for further improvement. A joint project between the CMC Electronics Canada Inc., world leader in civil aircraft FMS, and the Concordia University was initiated to develop a dynamic test bed (DTB) for achieving this aim, culminating in an application-level testing tool that could meet specified requirements yet remain within affordable range. This paper describes achievements gained in phase 1 and 2 of the project, focussing on the A429-PC hardware setup and fabrication of a breakout box with its circuit board on the hardware side, as well as the real-time architecture design, an executive program, a device driver for A429 and a client-server Ethernet network on the software side. Accessory tools created such as an ARINC switch graphic user interface (GUI), ARINC label GUI and discrete signal

GUI are also described. Also given is a rather comprehensive overview of the principles relevant to the project together with suggestions for future improvement of the DTB.

# **ACKNOWLEDGEMENTS**

The author wishes to pay special tribute to his supervisors Dr. H. Hong and Dr. J. V. Svoboda, for their guidance in completing this thesis.

To Mr. Gilles Huard the author is greatly appreciative for his assistance concerning the custom electronic hardware.

The author is especially indebted to his father and wife for providing the help and encouragement to undertake this interesting task.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                          | 13         |

|------------------------------------------|------------|

| LIST OF TABLES                           | XI         |

| NOMENCLATURE                             | XII        |

| CHAPTER 1                                | 1          |

| 1.1 BACKGROUND OF NAVIGATION TECHNOLOGY  |            |

| 1.1.1 Flight Instruments                 | 3          |

| 1.1.2 Navigation Systems                 | 3          |

| 1.1.2.1 Airborne Navigation Systems      | 3          |

| 1.1.2.2 Ground-based Navigation Systems  | 5          |

| 1.2 FLIGHT MANAGEMENT SYSTEM             | 10         |

| 1.3 Test Bed Review                      | 13         |

| 1.4 Thesis Objectives                    | 14         |

| CHAPTER 2                                | 16         |

| 2.1 Purpose of the Dynamic Test Bed      | 16         |

| 2.2 HARDWARE COMPONENTS                  |            |

| 2.3 SOFTWARE ARCHITECTURE                |            |

| 2.3.1 Simulation Software                |            |

| 2.3.2 Interface PC Software              | 21         |

| 2.3.2.1 Synchronization Mechanism        | 21         |

| 2.3.2.2 DTBExecutive Workspace           |            |

| 2.3.3 Communication Tool                 | 24         |

| 2.3.4 Graphic User Interface (GUI)       | 25         |

| CHAPTER 3                                | <b>2</b> 7 |

| 3.1 ARINC 429-PC16 INTERFACE             | 27         |

| 3.1.1 ARINC Standards                    |            |

| 3.1.2 A429-PC16 Design Review            | 29         |

| 3.1.3 ARINC 429 Physical Aspects         | 30         |

| 3.1.3.1 Transmission Media               |            |

| 3.1.3.2 Wiring Topology                  | 31         |

| 3.1.4 ARINC 429 Architecture Overview    | 32         |

| 3.1.5 Address Map                        |            |

| 3.1.6 Transmit Management                |            |

| 3.1.6.1 Transmit Control Block Structure |            |

| 3.1.6.2 Transmit Command Block Structure |            |

| 3.1.7 Receive Management                 |            |

| 3.1.7.1 Receive Control Block Structure  | 45         |

| 3.1.7.2 Receive Firmware Operation       |            |

| 3.1.8 Transmitter Set-up                   |    |

|--------------------------------------------|----|

| 3.1.9 ARINC Word & Conversions             | 55 |

| 3.1.9.1 Label                              | 56 |

| 3.1.9.2 SDI                                | 56 |

| 3.1.9.3 Data Area                          | 57 |

| 3.1.9.4 Sign/Status Matrix                 |    |

| 3.1.9.5 Parity Field                       |    |

| 3.1.10 ARINC I/O Driver Derived            |    |

| 3.1.10.1 Installing the ARINC429 IO Card   |    |

| 3.1.10.2Installing the software            |    |

| 3.1.10.3 Installing the SBS Driver Library |    |

| 3.1.10.4Configuration Files                |    |

| 3.2 PCI-6025E INTERFACE                    |    |

| 3.2.1 Analog Input                         |    |

| 3.2.1.1 Overview                           |    |

| 3.2.1.2 RSE Configuration                  |    |

| 3.2.2 Analog Output                        |    |

| 3.2.3 Discrete I/O                         |    |

| 3.2.4 Discrete I/O Power-up State          | 75 |

| 3.3 CMA-900                                |    |

| 3.3.1 Features                             | 78 |

| 3.3.2 Waypoint Navigation                  | 78 |

| 3.3.3 Departures                           | 80 |

| 3.3.4 GPS Navigation                       | 81 |

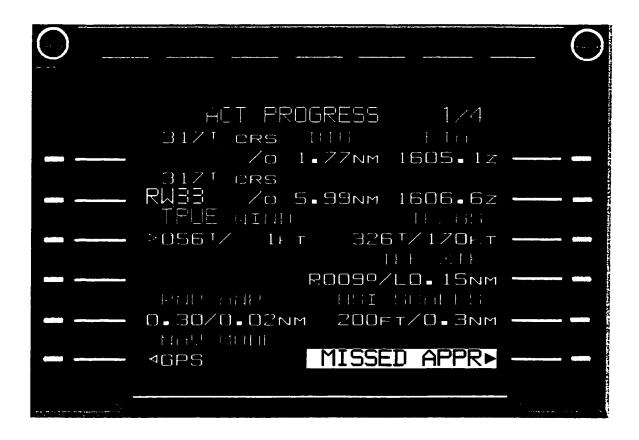

| 3.3.5 GPS Instrument Approaches            | 82 |

| 3.3.6 Required Navigation Performance      | 85 |

| 3.4 CONTROL DISPLAY UNIT (CDU)             | 86 |

| 3.5 Breakout Box Design                    | 88 |

| 3.5.1 Dimension Design                     | 88 |

| 3.5.2 Breakout-box Components              | 91 |

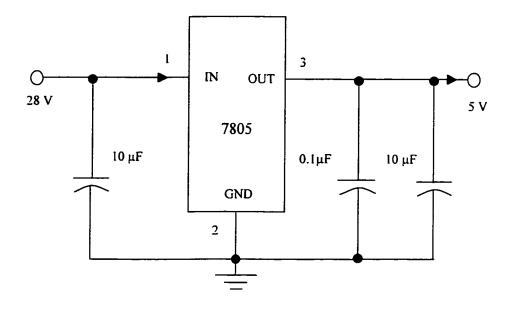

| 3.5.2.1 Power Supply                       |    |

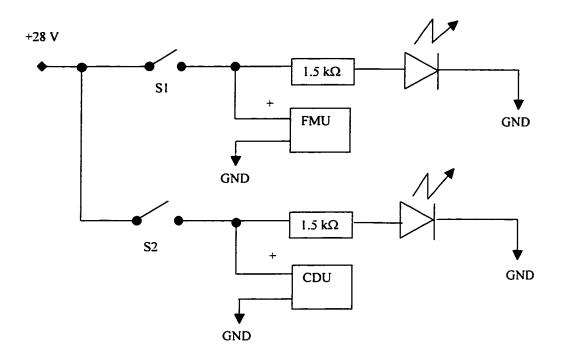

| 3.5.2.2 LED Display Circuit                | 91 |

| 3.5.2.3 Discrete Input Switches            | 92 |

| 3.5.2.4 Internal Circuit Board             | 93 |

| 3.5.2.5 Connectors                         |    |

| 3.5.2.6 Cables                             | 97 |

| CHAPTER 4                                  | 98 |

| 4.1 Software Requirements                  | QQ |

| 4.2 DTB REALIZATION                        |    |

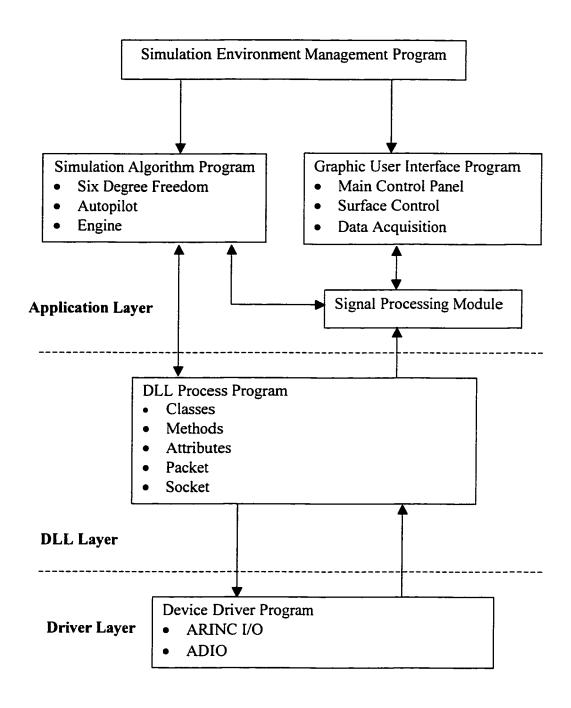

| 4.2.1 Device Driver Layer                  |    |

| 4.2.2 Dynamical Link Library Layer         |    |

| 4.2.3 Application Layer                    |    |

| 4.2.3.1 Signal Process Module              |    |

| 4.2.3.2 GUI Module                         |    |

| 4.2.3.3 Simulation Algorithm Module        |    |

| 4.3 SOFTWARE DEVELOPMENT EXAMPLES          |    |

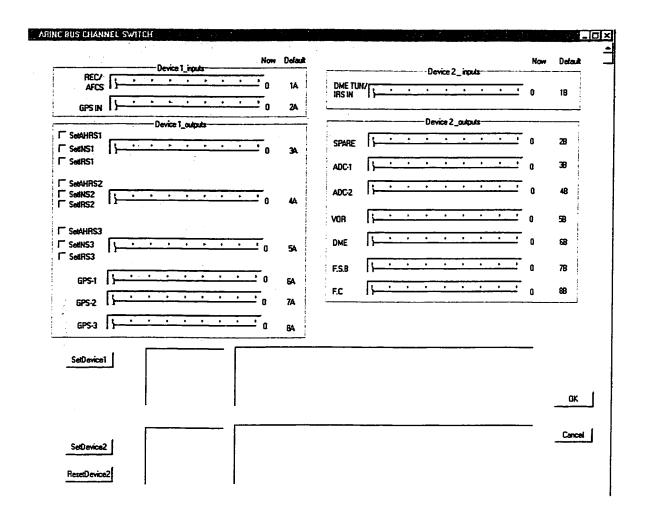

| 4.3.1 ARINC Channel Switch GUI                 | 103 |

|------------------------------------------------|-----|

| 4.3.1.1 Introduction                           | 103 |

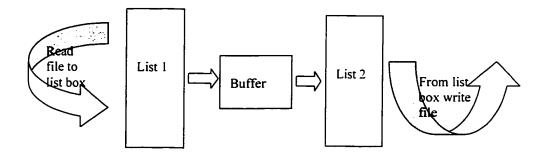

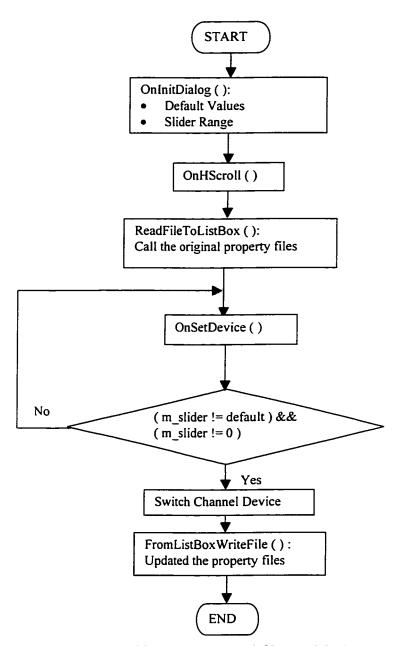

| 4.3.1.2 Software Architecture                  | 104 |

| 4.3.1.3 Software Components                    | 106 |

| 4.3.2 ARINC I/O Configuration Management       | 108 |

| 4.3.2.1 Class Arinc429Channel                  | 109 |

| 4.3.2.2 Class Arinc429Device                   | 110 |

| 4.3.2.3 Class Arinc429TCB                      | 110 |

| 4.3.2.4 Class Arinc429RCB                      | 111 |

| 4.3.2.5 Class DTBProperties                    | 112 |

| 4.3.2.6 Class DTBArincIOThread                 | 112 |

| CHAPTER 5                                      | 114 |

| 5.1 FIRST STAGE: LOOP-BACK TEST                | 114 |

| 5.2 SECOND STAGE: LNAV TEST                    | 115 |

| 5.3 THIRD STAGE: VNAV TEST                     | 120 |

| CHAPTER 6                                      | 124 |

| 6.1 BACKGROUND REVIEW                          | 124 |

| 6.2 HARDWARE SUMMARY & DISCUSSION              | 125 |

| 6.3 SOFTWARE SUMMARY & DISCUSSION              | 125 |

| 6.4 Future Work                                | 127 |

| 6.4.1 Breakout box Modification                | 127 |

| 6.4.2 Software Development                     | 127 |

| 6.4.3 Testing Aspects                          | 128 |

| 6.5 CONCLUDING REMARKS                         | 128 |

| REFERENCES                                     | 131 |

| APPENDIX                                       | 135 |

| A. "SBS_DEV.CFG" FILE                          | 135 |

| B. "SBSA429.INI" FILE                          |     |

| C. ARINC LABEL PROPERTY FILE                   |     |

| D. Breakout Box Wiring Table                   |     |

| E. ARINC OUTPUT WORDS                          |     |

| F. DETAILED ARINC WORD (LABEL 001) DESCRIPTION |     |

| G. GPS WITH RAIM                               |     |

| H. NAVIGATION TERMINOLOGY DEFINITIONS          |     |

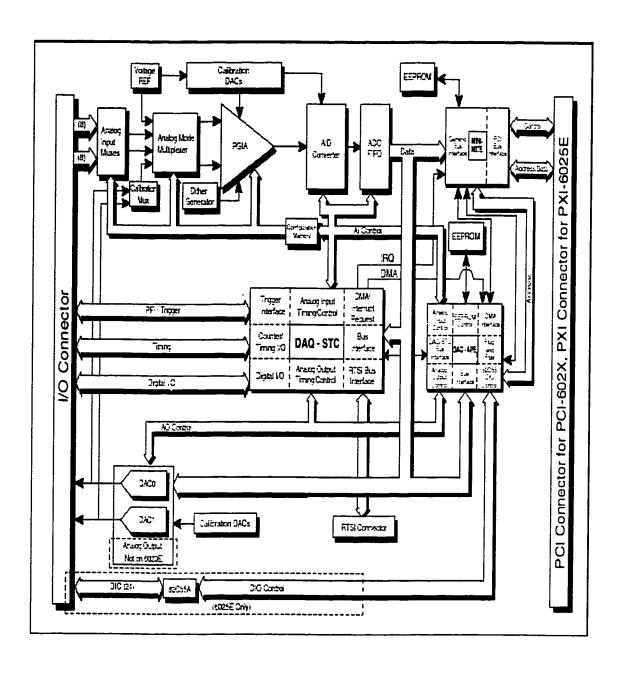

| I. PCI- 6025E BLOCK DIAGRAM                    |     |

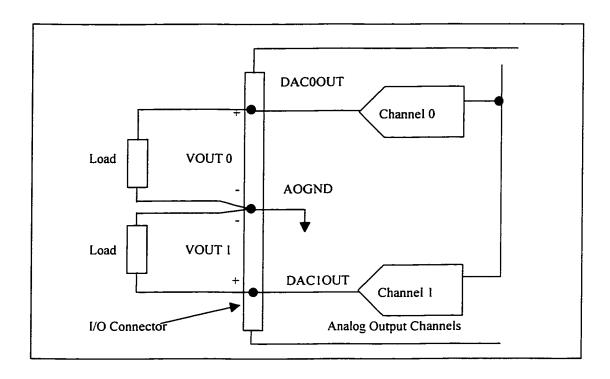

| FIGURE 23: ANALOG OUTPUT CONNECTORS                         | 72  |

|-------------------------------------------------------------|-----|

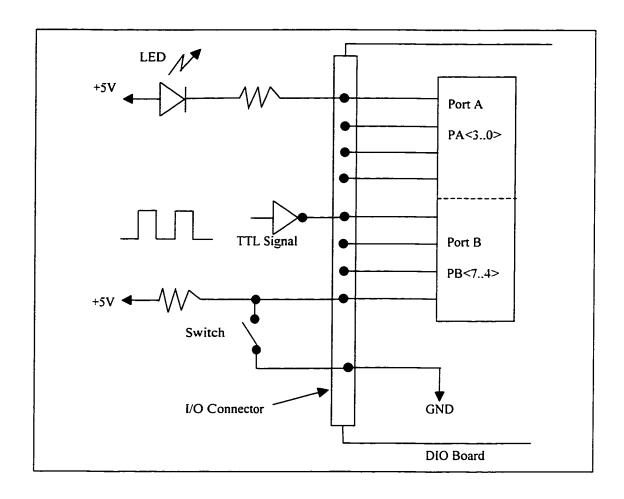

| FIGURE 24: DISCRETE I/O CONNECTIONS BLOCK DIAGRAM           | 74  |

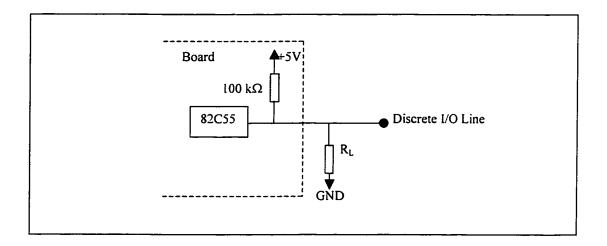

| FIGURE 25: DIO LINE CONFIGURED FOR HIGH DIO POWER-UP STATE  | 75  |

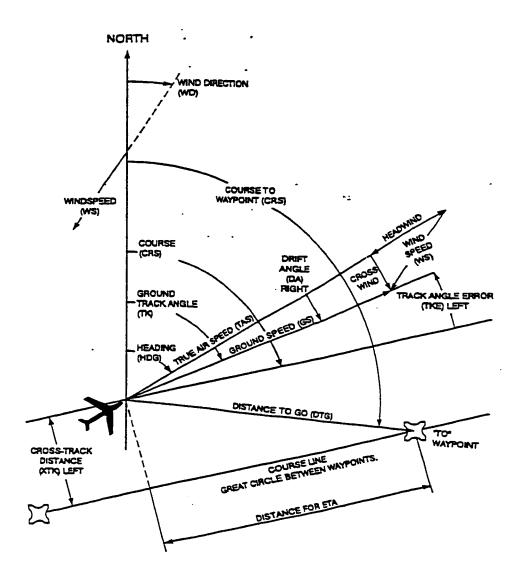

| FIGURE 26: NAVIGATION RELATIONSHIPS                         | 79  |

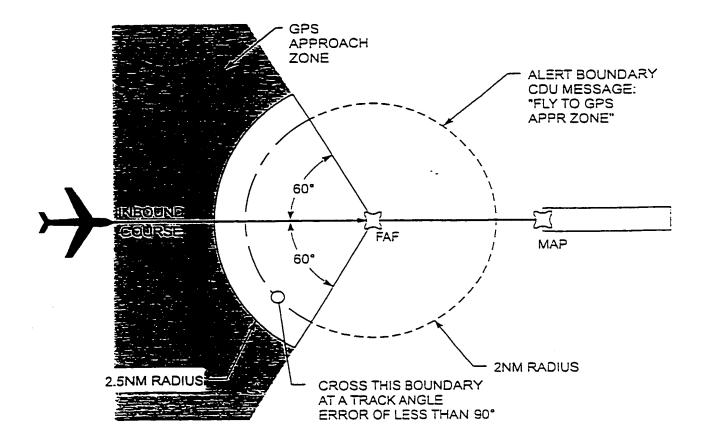

| FIGURE 27: GPS APPROACH                                     | 84  |

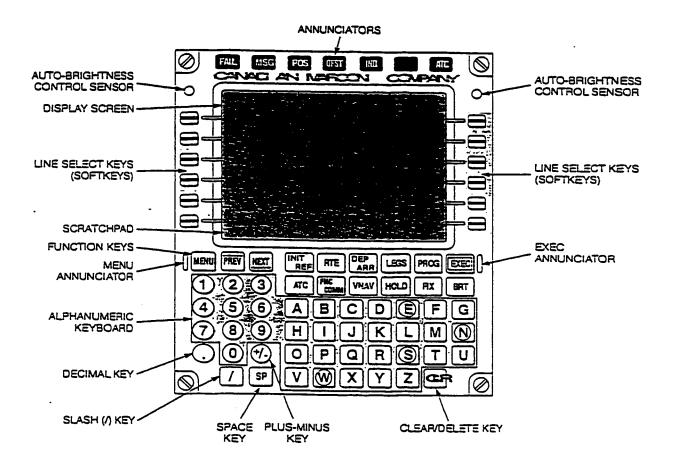

| FIGURE 28: CDU FRONT PANEL                                  | 87  |

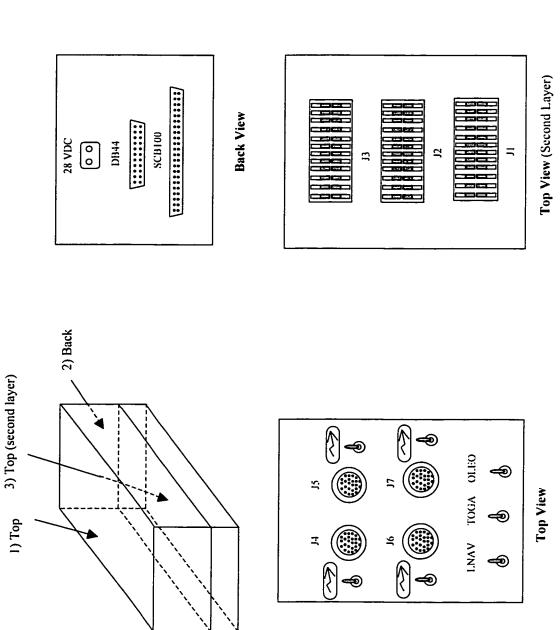

| FIGURE 29: Breakout-box Overview                            | 89  |

| FIGURE 30: LED DISPLAY CIRCUIT                              | 92  |

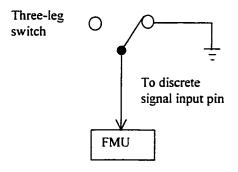

| FIGURE 31: DISCRETE INPUT SWITCH                            | 93  |

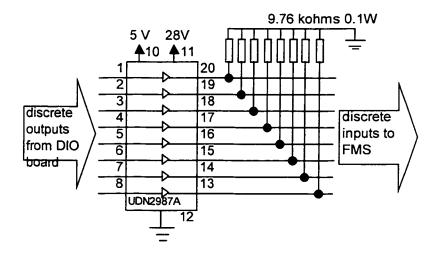

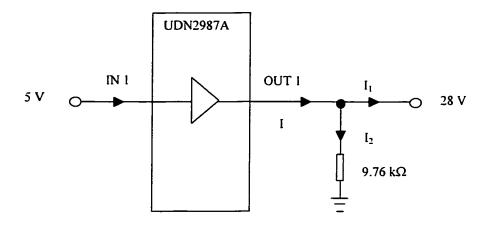

| FIGURE 32: LOGIC CONVERSION (5 V TO 28 V)                   | 93  |

| FIGURE 33: SIMPLIFIED LOGIC CONVERSION CIRCUIT              | 94  |

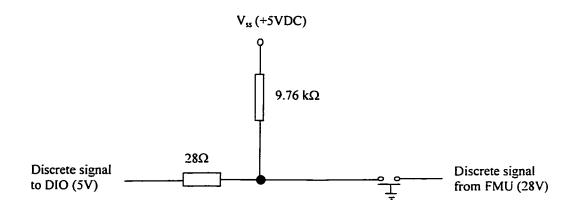

| Figure 34: Logic Conversion (28V to 5V)                     | 95  |

| FIGURE 35: VOLTAGE REGULATOR                                | 96  |

| FIGURE 36: BLOCK DIAGRAM OF DTB SOFTWARE INTEGRATION        | 100 |

| FIGURE 37: LAYOUT OF THE ARINC CHANNEL BUS SWITCH GUI       | 105 |

| FIGURE 38: LIST BOX CONTROL BLOCK DIAGRAM                   | 105 |

| FIGURE 39: FLOW CHART OF CHANNEL SWITCH                     | 106 |

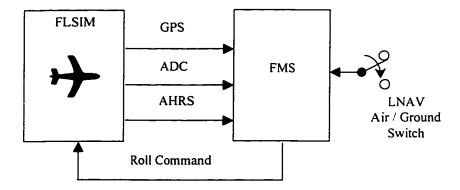

| FIGURE 40: LNAV TEST BLOCK DIAGRAM                          | 115 |

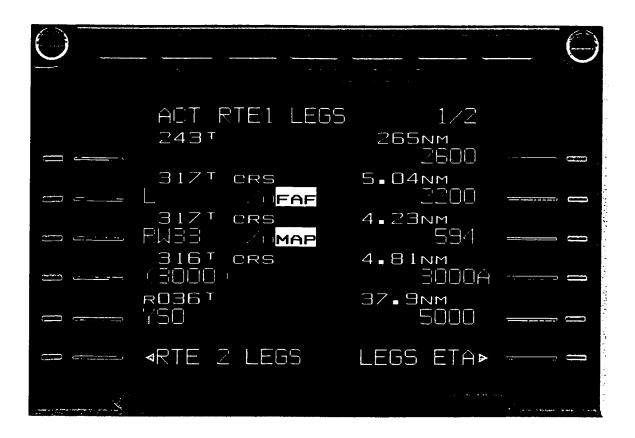

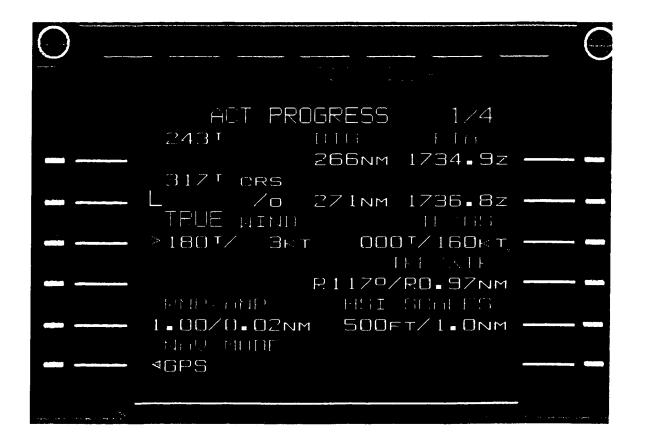

| FIGURE 41: FLIGHT PLAN ALONG LEGS (WAYPOINTS)               | 116 |

| FIGURE 42: LNAV OFF STATUS                                  | 117 |

| Figure 43: LNAV ON Status                                   | 118 |

| FIGURE 44: LNAV COMPLETED                                   | 119 |

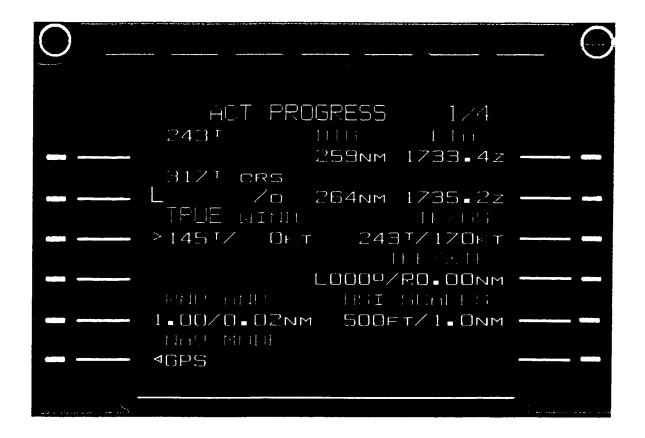

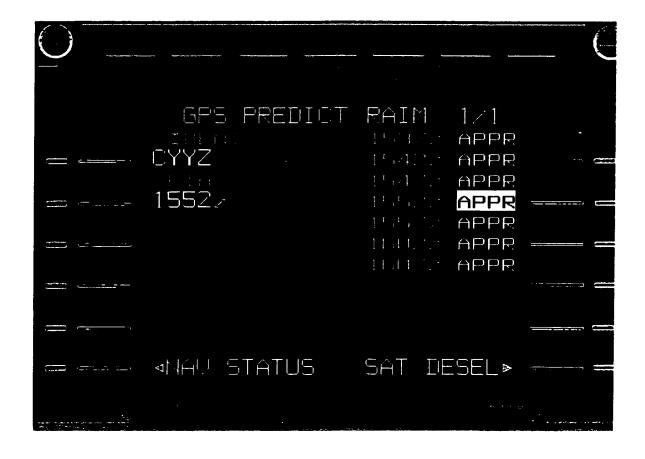

| FIGURE 45: COMPONENTS OF APPROACH/LANDING PHASE (SIDE VIEW) | 120 |

# **LIST OF FIGURES**

| FIGURE 1: BLOCK DIAGRAM OF VOR RECEIVER                           | 6  |

|-------------------------------------------------------------------|----|

| FIGURE 2: DME OPERATION                                           | 7  |

| FIGURE 3: FLIGHT MANAGEMENT SYSTEM                                | 11 |

| FIGURE 4: CONTROL DISPLAY UNIT (CDU)                              | 12 |

| FIGURE 5: HARDWARE COMPONENTS OF DTB                              | 17 |

| FIGURE 6: HARDWARE BLOCK DIAGRAM OF DTB                           | 18 |

| FIGURE 7: SIMULATOR REAL TIME SOFTWARE OVERVIEW                   | 19 |

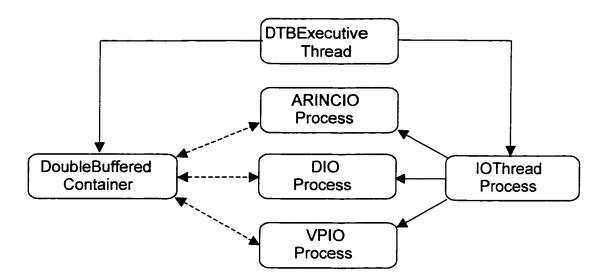

| FIGURE 8: DTBEXECUTIVE COMPONENTS                                 | 22 |

| FIGURE 9: SIMULATION CONTROL GUI                                  | 26 |

| FIGURE 10: A429-PC BLOCK DIAGRAM                                  | 29 |

| FIGURE 11: STAR TOPOLOGY FOR LRU WIRING                           | 31 |

| FIGURE 12: BUS DROP TOPOLOGY FOR LRU WIRING                       | 31 |

| FIGURE 13: A429-PC16 MEMORY MAP (DEVICE 1)                        | 34 |

| FIGURE 14: SOFTWARE CONTROL REGISTERS                             | 35 |

| FIGURE 15: TRANSMIT CONTROL BLOCK STRUCTURE                       | 36 |

| FIGURE 16: TRANSMIT COMMAND BLOCK DATA STRUCTURE                  | 41 |

| FIGURE 17: RECEIVE CONTROL BLOCK STRUCTURE                        | 46 |

| FIGURE 18: PARAMETERS RELATIONSHIP OF A TRANSMITTER               | 52 |

| Figure 19: 32-bit ARINC Word                                      | 55 |

| FIGURE 20: BASE I/O ADDRESS 390H, TOP VIEW OF PC16 AS INSTALLED   | 63 |

| FIGURE 21: I/O CONNECTOR PIN ASSIGNMENT FOR THE PCI-6025E         | 69 |

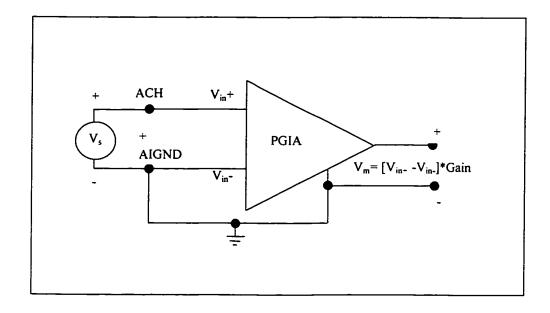

| FIGURE 22: PGIA WITH RSE CONFIGURATION FOR FLOATING SIGNAL SOURCE | 71 |

| FIGURE 46: GPS WITH RAIM              | 122 |

|---------------------------------------|-----|

| FIGURE 47: ENTERING GPS APPROACH ZONE | 123 |

# LIST OF TABLES

| TABLE 1: TYPE CODES                                                    |

|------------------------------------------------------------------------|

| TABLE 2: DATA STORAGE STRUCTURE                                        |

| TABLE 3: DEFINITION OF TRANSMITTER PARAMETERS                          |

| Table 4: Label Conversion                                              |

| TABLE 5: GENERALIZED BNR WORD FORMAT                                   |

| TABLE 6: CONVERTING AN ENGINEERING VALUE TO ARINC WORD (BNR FORMAT) 61 |

| TABLE 7: GENERALIZED BCD WORD FORMAT                                   |

| TABLE 8: CONVERTING AN ENGINEERING VALUE TO ARINC WORD (BCD FORMAT) 61 |

| TABLE 9: REQUIRED .CPP FILES                                           |

| Table 10: Required .h Files                                            |

| Table 11: Required Functions for Initializing                          |

| Table 12: PCI-6025E Analog Input Modes                                 |

| TABLE 13: PCI-6025E MEASUREMENT PRECISION                              |

| Table 14: Required Navigation Performance                              |

| TABLE 15: FUNCTIONS IN CLASS GUI1DLG                                   |

| Table 16: Functions of Class Arinc429Channel 109                       |

| TABLE 17: FUNCTIONS OF CLASS ARINC429DEVICE                            |

| TABLE 18: FUNCTIONS OF CLASS ARINC429TCB                               |

| TABLE 19: FUNCTIONS OF CLASS ARINC429RCB                               |

| TABLE 20: FUNCTIONS OF CLASS DTBPROPERTIES                             |

| Table 21: Functions of Class DTBArincIOThread                          |

# **NOMENCLATURE**

ACT - Approach/Terminal Control

ADC - Air Data Computer

ADF - Automatic Direction Finder

AGL - Above Ground Level

AEEC - Airlines Electronic Engineering Committee

AHRS - Attitude Horizon Reference System

AIGND - Analog Input Ground

AISENSE - Analog Input Sense

ANP - Actual Navigation Performance

ARINC - Aeronautical Radio Incorporation

ATC - Air Traffic Control

ATM - Air Traffic Management

CDU - Control Display Unit

CIC - Center for Industrial Control of Concordia University

CMA - Canadian Marconi Avionics

CMC - CMC Electronics Canada Inc.

CRS - Course to Waypoint

DA - Drift Angle

DIO - Discrete Input / Output

DLL - Dynamic Link Library

DME - Distance-measuring Equipment

D/R - Dead Reckoning

DSP - Digital Signal Processor

DTB - Dynamic Test Bed

DTG - Distance to Go

EPU - Estimate of Position Uncertainty

ETA - Estimated Time of Arrival

FAF - Final Approach Fix

FLSIM - Flight Simulator

FMC - Flight Management Computer

FMS - Flight Management System

FMU - Flight Management Unit

FOM - Figure of Merit

GIAL - GPS Integrity Alarm Limit

GPS - Global Positioning System

GS - Ground Speed

GUI - Graphic User Interface

HDG - Heading

HDOP - Horizontal Dilution of Precision

HIL - Horizontal Integrity Limit

HOL - Higher Order Language

HSI - Horizontal Situation Indicator

IAS - Indicated Air Speed

ICAO - International Civil Aviation Organization

ILS - Instrument Landing System

INS - Inertial Navigation System

IRS - Inertial Reference Sensor

LNAV - Lateral Navigation

LRU - Line Replace Unit

MAP - Missed Approach Point

MCP - Mode Control Panel

MFC - Microsoft Foundation Classes

NM / nm - Nautical Mile, 1 nm = 1.853 km

NRSE - Non-referenced Single-ended

OOP - Object-oriented Programming Language

OS - Operating System

PGIA - Programmable Gain Instrumentation Amplifier

PPI - Programmable Peripheral Interface

RAIM - Receiver Autonomous Integrity Monitoring

RNP - Required Navigation Performance

RSE - Referenced Single-ended

RTA - Required Time of Arrival

SDI - Source / Destination Identifier

SID - Standard Instrument Departure

SPDT - Single-pole Single-throw

SSM - Sign / Status Matrix

STAR - Standard Terminal Arrival Routes

TAS - True Air Speed

TCP/IP - Transmission Control Protocol / Internet Protocol

TK - Ground Track Angle

TKE - Track Angle Error

TOGA - Take off Go Around

VHF - Very High Frequency

VNAV - Vertical Navigation

VOR - VHF Omni-directional Range System

VPI - Virtual Prototypes Incorporation

WD - Wind Direction

WS - Wind Speed

XTK - Cross-track Distance

ZIF - Zero Insertion Force

# CHAPTER 1

# **INTRODUCTION**

# 1.1 Background of Navigation Technology

Navigation is the determination of following a predetermined path of a moving vehicle. The three components of position and the three components of velocity make up a six-component state vector that fully describes the translational motion of the vehicle. Navigation data are usually sent to other onboard sub-systems, for example, to the flight control, flight management, engine control, communication control and crews displays computers. Navigation sensors may be located in the vehicle, in another vehicle, on the ground, or in air space. When the state vector is measured and calculated onboard of a moving vehicle, the process is called navigation process.

Essentially, aircraft instruments are extensions of a pilot's senses, refinements of his/her vision and other sensory perceptions that supply the information he or she needs to feel at home in the sky at all times. Avionics (shorthand for aviation electronics) and instrumentation are commonly used terms describing those systems, equipment, and instruments that enable the pilot to control and monitor the performance of the aircraft and that provide vital information to the ground-based air traffic control system. Today's advancing technology, with its increase in automation and function integration, suggests that these terms might have become obsolete. Further, future aircraft development, directed toward even greater integration of the aircraft's systems, will fundamentally change the role of the pilot within this environment [1].

In the past, much emphasis was placed on acquiring and displaying to the pilot an ever-increasing amount of information required during a flight. For example, during takeoff and landing, the pilot reviews his checklist, constantly scans his instruments, especially noting the attitude of the aircraft, rate of climb (rate of descent when landing), airspeed, and engine functions, maintains direction, looks outside to avoid collisions, maintains communication with the Approach/Terminal Control (ACT) when necessary, and monitors a host of other parameters. All these necessary actions result in increased workload by forcing the pilot to evaluate highly complex sets of input data, decide upon courses of action, and then implement these actions in minimal times. Such situations are seen as undesirable since they increase the pilot's chances of making errors, consequently reducing the intelligent, computer-aided decision-making system of the modern aircraft, which works cooperatively with the pilot in order to ensure the safety of the aircraft and its crew and passengers.

The role of the pilot may now and in the future be viewed as that of a flight manager, one who monitors the aircraft's performance but maintains override control of all automated and/or integrated functions associated with the aircraft. A more appropriate and perhaps more descriptive term for this broad area of concern is "flight management."

A flight management system, in the context of this definition, comprises the sensors, displays, and associated subsystems used to process and record flight information. The flight information includes data for status, control, communications, navigation, propulsion, landing, alerting, self-protection, armament support systems (in military aircraft), and other flight parameters involved in the air and on the ground. The

flight management system, working as a synergistic unit, processes and records the data as well as integrates them, working in consonance with the pilot's knowledge, experience, and judgment.

#### 1.1.1 Flight Instruments

By the early 1930s, the developing aviation community considered as being essential three general groups of: 1) flight instruments (such as the pitot-static tube) to indicate the aircraft's attitude, 2) navigation instruments (such as compass and autopilot) to inform the pilot of his position in air space, and 3) engine and airframe instruments (such as fuel flow meter and tachometer) to indicate how the aircraft is operating.

Even though some systems are no longer representative of modern technology, a brief description of the systems will be presented here due to two reasons. First, a belief that by knowing the line of development from past to present, it would be far easier to comprehend that from present to future. Second, airport systems are built to extremely high standards and are consequently very expensive. Some old equipment is still in operation, meeting the original specifications and still performing an excellent job.

#### 1.1.2 Navigation Systems

Navigation systems can be grouped into three branches termed airborne navigation system, ground-based navigation system and space-based navigation system.

#### 1.1.2.1 Airborne Navigation Systems [27]

A typical application of the airborne navigation system is the Inertial Navigation System (INS). The early INS generally included a computer and a stable platform

composed of gyroscopes and accelerometers suspended in a gimbal arrangement. The gyros, together with the computer, generated signals to maintain the platform's accelerometers in a level position with relation to the earth's surface. In this way, they accurately measured aircraft accelerations, which were then converted to velocities. These velocities, when modified by the computer with appropriate corrections, provided extremely accurate navigational information. In addition, the inertial platform provided attitude outputs of roll, pitch, and platform heading as analog signals, which could be used by other systems in the aircraft.

The conventional inertial navigation system, after an injection of initial position information, is now capable of continuously and accurately updating displays of position, ground speed, attitude, and heading. In addition, it provides guidance or steering data for the autopilot and other flight instruments. However, the accuracy of the inertial navigation system will degrade over a period of time in flight, and therefore the system must be periodically updated.

The accelerometer is the basic measuring instrument of the inertial navigation system. Accelerometers mounted at right angles to one another within the gimbal system of a vertical gyro can measure the acceleration of the aircraft horizontally and vertically. While acceleration by itself is of little importance, its integration with time results in a measure of aircraft velocity. A second integration provides distance form the aircraft's take-off point. The accelerometer is basically a pendulum device that swings from its null position when the aircraft accelerates. A signal-pickoff device determines how far the pendulum has moved, and the resultant signal is sent to an amplifier. The signal from the amplifier activates a torquer in the accelerometer that restores the pendulum to the

null position. The amount of signal (electrical current) sent to the torquer is a function of the aircraft's acceleration.

## 1.1.2.2 Ground-based Navigation Systems [28]

Typical applications of ground-based navigation systems are the VHF Omnidirectional Range System (VOR) and Distance-measuring Equipment (DME).

VOR is the currently International Civil Aviation Organization (ICAO)-approved short-distance navigation system. It may be visualized as a huge wheel, the spokes of which are courses extending from the hub out to line-of-sight distance around the station. Ideally, an infinite number of these spokes are available to the pilot for his selection [2]. The courses are perfectly straight and pass through a central point at the hub, with each course in the form of a vertical plane.

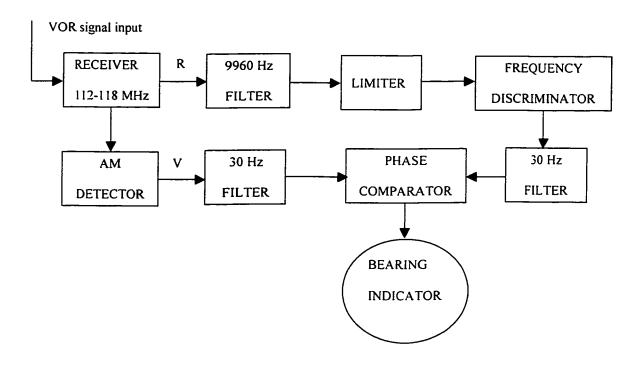

Operation of the VOR is based on comparing the phase difference between two 30 Hz signals transmitted from a ground station in the 112-118 MHz frequency band and received on a VHF receiver in the aircraft. One transmitted signal R (the reference-phase signal) has a constant phase regardless of the position of the aircraft. The phase of the second transmitted signal V (the variable-phase signal) is a function of the bearing of the aircraft from the transmitting station. The two signals are in phase when the receiving position is due north (magnetic) from the facility. For any other bearing, the phase difference between the two signals is equal to the bearing of the aircraft from the ground station.

Basically, the VOR ground transmitter facility has two antenna systems. One, the "carrier antenna," radiates a radio-frequency signal with an omni-directional pattern (in the horizontal plane), amplitude-modulated (AM) with a 9,960 Hz subcarrier, which is in turn frequency-modulated (FM) at 30 Hz (the reference-phase signal). This carrier is also

simultaneously modulated, either with the tone identification from the facility, or by voice for communication purposes. The second antenna system, the "sideband antenna," when combined with the first, produces a space modulation rotation at 30 Hz, the variable-phase signal. A monitoring system checks the station output continuously and automatically and, in the event of transmitter trouble, actuates warning alarms.

In the aircraft, the composite signal is received on a conventional VHF receiver. After demodulation, the two audio signals are separated by suitable filters (30 Hz and 9,960 Hz), and the 9,960 Hz subcarrier is passed through a discriminator to recover the 30 Hz reference signal. The phase difference between the two 30 Hz signals is then measured to determine the bearing of the receiving point from the facility. The principle of VOR receiver can also be represented in Figure 1.

Figure 1: Block Diagram of VOR Receiver

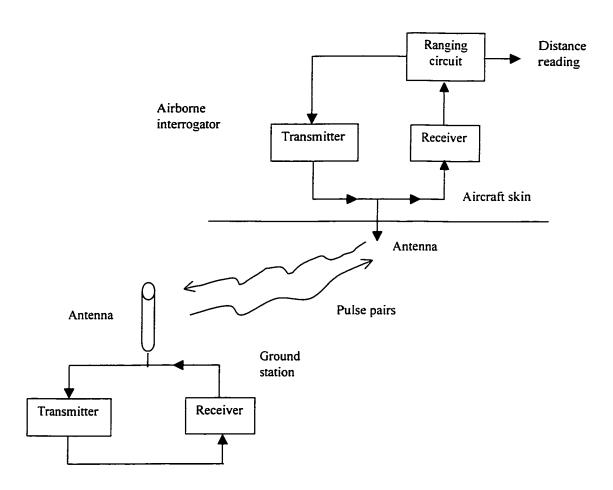

Distance-measuring Equipment (DME) [5] is a system combining ground-based and airborne equipment to measure the distance of the aircraft from the ground facility. DME is used primarily for fixing an aircraft's position, approaching an airport, avoiding protected air or ground space, holding at a given position, or figuring ground speed. The DME ground station is usually co-located with other navigation or distance-measuring systems. DME operating principle is shown in Figure 2.

Figure 2: DME Operation

The airborne DME consists of a transmitter-receiver, a control unit, a distance indicator, and an antenna. The ground-based portion of the DME system consists of a transmitter-receiver and an antenna, but operates only on a single frequency.

The transmitter section of the airborne equipment contains the circuits to generate. amplify, and transmit interrogating pulse pairs. The receiver section contains the circuits required to receive, amplify, and decode the received reply pulses. Computation circuits then determine the validity of the reply pulses and calculate the distance by comparing the elapsed time between transmission and reception.

#### 1.1.2.2.1 Space-based Navigation Systems [29]

Global Positioning System (GPS) has been a worldwide navigational aid with an accuracy of a few meters. The basic principle is that a number of satellites in orbit each radiate a series of precisely timed radio signals. The user notes the time at which the signals are received and from the delay of each due to transmit time and knowledge of the position of the satellite at the moment of transmission, calculates the distance from each and thus the position.

GPS can achieve position accuracy of 16 meters in three dimensions, the correct time within one-millionth of a second, and the user's velocity to the nearest one-tenth of a meter per second. GPS employs a network of 21 satellites (plus 3 operational spares) in six orbital planes, each broadcasting precise time and location information. The satellites operated in circular 20,200 km orbits at an inclination angle of 55 degrees, and with a 12 hour period. They are precisely arranged so that a minimum of 5 satellites is in view at all times at any single location in the world.

GPS consists of three segments: the Space Segment, a constellation of satellites circling the earth; the Control Segment, a series of ground stations that monitor the

satellites and transmit corrected position and time data to the satellites; and the User Segment, all sea, land, and air equipment that receive the satellite signals and calculate user position, time, and velocity. Each satellite transmits two l-band signals (1,575.42 and 1,227.6 MHz). Both signals contain data that include satellite locations; thus, the range to the satellite can be determined with the user's receiver by comparing the time delay between satellites. The precise latitude, longitude, altitude, velocity, and time can therefore be determined for an unlimited number of users.

When the GPS is turned on, the pilot enters an estimate of his present position, velocity, and time. The GPS equipment then begins to search for and track satellites. The data from the satellite signals identifies the satellite number, locates the satellite in space, and establishes system time. The GPS receiver then calculates the range to the satellite by measuring the time of receipt of the signal and multiplying that time by the speed of propagation of a radio signal. This calculation locates the user on a sphere of radius R1, whose center is the transmitting satellite. With the range of one satellite known, a range measurement is made to a second satellite to define a second sphere of range R2. In a like manner, R3 is then determined by measuring the range to a third satellite. Using the three range measurements and elementary geometry, the GPS receiver determines the user's precise position in terms of latitude, longitude, and altitude. Range to a fourth satellite is required to determine the time-offset from the user's crystal clock with respect to the GPS atomic time standard. The velocity measurement is determined by counting the Doppler shift from the GPS center frequency.

The effects of GPS on future generations of air traffic management systems and on civil and military users of airspace, both domestic and international, will undoubtedly be quite substantial.

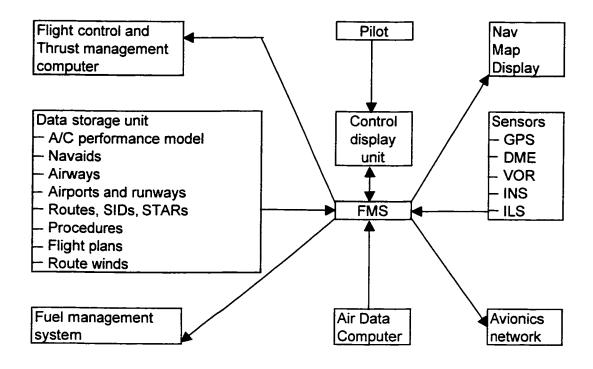

## 1.2 Flight Management System

Flight management system (FMS) has three specific capabilities relevant to Air Traffic Management (ATM) [3]. It can guide the aircraft accurately along a predetermined path defined by a sequence of two-dimensional (latitude and longitude) or three-dimensional (adding altitude) waypoints. The FMS also can minimize the cost of the flight by selecting optimum speeds and/or altitudes along the predetermined path. The optimization is based on a pilot-selected cost index that weighs fuel cost relative to flight time cost. When the cost of flight time is weighted heavily, the FMS will complete the trip more quickly, burning more fuel in the process. Finally, the FMS has a required time of arrival (or 4D navigation) capability that assures the aircraft will arrive at selected waypoints within small time windows (e.g., within ten seconds of the prescribed times).

Extensive data bases are resident in the FMS, as well as the current flight plan and the wind velocities and air temperatures expected along the route of flight. The FMS provides pitch, steering, and autothrottle commands to the aircraft guidance systems, as well as essential flight data, including estimated times of arrival at waypoints, fuel remaining and fuel flow, current position and speed, and current winds. The FMS integrates the various avionic subsystems, including the navigation sensors (Figure 3). It will automatically tune VOR/DME receivers according to the position of the aircraft and the navigation aid frequencies stored in the database.

Figure 3: Flight management system [3]

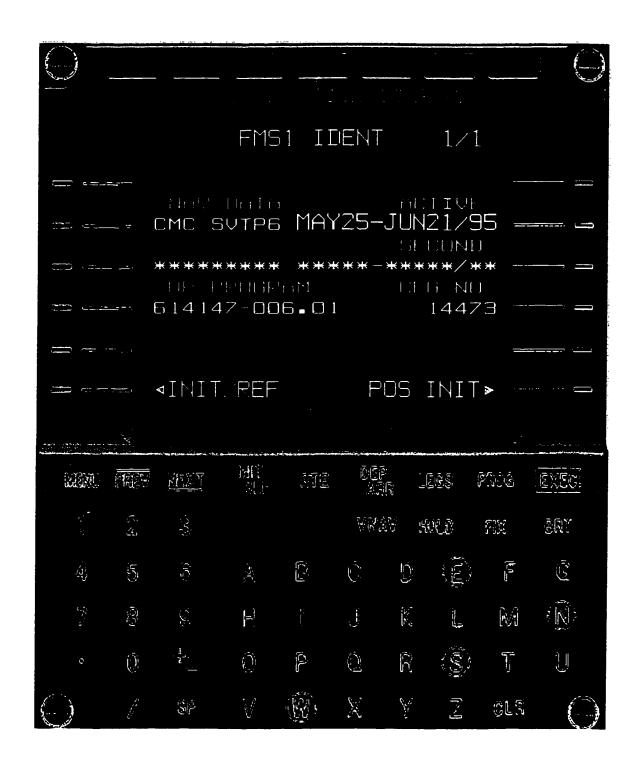

Modern civil transport airplanes are often equipped with a Flight Management Computer (FMC), typically part of the Flight Management System (FMS), which optimizes the performance and/or flight path of the aircraft in terms of some parameter such as flight time or the plane fuel cost. The most common interface between the crew and the FMC is a Control Display Unit (CDU) shown in Figure 4. In addition to the alphanumeric keyboard, there are special-purpose keys that support the flight-planning and management processes. There are typically three CDUs in the aisle stand of the cockpit, one each for the captain and first officer in the front of the aisle stand, and one at the rear of the aisle stand intended primarily for use by maintenance personnel to operate the on-board maintenance system. The third CDU also is a backup for the other two.

Figure 4: Control display unit (CDU) [30]

#### 1.3 Test Bed Review

Over the last 10 years, hundreds of hours of flight simulation have been expended in the US, Canada and Europe in efforts to revise the handling quality requirements for flight management systems. In the same time, very few flight simulation experiments addressing handling qualities at FMS dynamic interface have been reported. There has been no significant use of flight simulation of the dynamic interface in test and evaluation programs [21]. A NASA Dryden Flight Research Center program explored a practical application of real-time adaptive configuration optimization for enhanced transport performance on an L-1011 (Lockheed Corporation, Burbank, California) aircraft in 1998. This adaptive configuration optimization system is better than benefits available with a preprogrammed flight management system [31]. However, the testing was very expensive since they were all performed in actual aircraft.

Most of dynamic interfaces are software-based. As an example, the mobile spaceplane simulation facility being developed for Phillips Laboratory by Boeing provides a test bed for assessing operations before prototype vehicles and their support systems are built [22]. Also, Boeing reported the project "Open Control Platform for Uninhabited Air Vehicles" in 2001. The Open Control Platform (OCP) will be integrated with popular and useful hybrid system control design tools such as Matlab/Simulink, and Ptolemy II to enable the rapid design, simulation, and the test of reliable embedded software for unmanned air vehicles [32]. This will lower cost and reduce effort as operations-related problems are uncovered and resolved through simulation before hardware prototypes are built. However, this design process is not an "end-to-end" process since there is no integration of the avionics hardware.

CMC Electronics Canada Incorporation, as the world leader of FMS design, was promoting a project of dynamic test bed (DTB) to reach new stage in order to get more credibility and replicate the real world. This DTB will have the capability to interface and communicate between the high-fidelity six-degree-of-freedom flight simulator and the CMA-900 flight management system of real time. DTB as one of the important steps in FMS development is its testing in the dynamic environment of the specific aircraft type. While such testing is mostly performed in the actual aircraft, a more economical approach would be carry out the bulk of the testing using a laboratory-based simulated environment or test bed, for which the basis is a reconfigurable, real-time flight dynamic model. This distributed approach to the development of FMS is based on a modular concept; simulator modules are allocated to individuals PCs, which communicate via Ethernet packets transmitted at a certain rate. Similar approach is reported by a few research organizations throughout the world including the engineering simulator in Cranfield University, College of Aeronautics, UK [33].

## 1.4 Thesis Objectives

This thesis is written for the navigation engineer, whether user or designer, who is concerned with the practical application of newly developed FMS. It is also the intention of the author to provide enough information for future students to carry on similar task in this field.

This thesis will focus on the author's contribution to the joint project sponsored by the CMC Electronics Canada Inc.(CMC) and the Center for Industrial Control (CIC) of Concordia University – Dynamic Test Bed for Flight Management System, including

the description of the real-time software architecture design, system software implementation and breakout box design. The author will describe not only procedures followed in carrying out the project, but also provide salient insight for each component of the test bench, particularly from the hardware point of view.

The first chapter presents a historical overview of navigation technology relative to the DTB and its mission for civil and military aircraft. Chapter 2 gives the whole picture for the DTB by means of purpose of DTB, hardware components and software architecture for the system. Chapter 3 continues to explore the detailed explanation of the hardware components by means of ARINC 429-PC16 card interfacing, PCI-6025E card interfacing, breakout box design, and the general principles and application of the FMS. Chapter 4 discusses some software assistant tools to monitor flight simulation parameters in real run time performance. Chapter 5 covers all stages for verifying the system by means of loop-back, Lateral Navigation (LNAV) and Vertical Navigation (VNAV). The last chapter summarizes all work along the DTB and provides some recommendation for the future work of the coming phase.

# **CHAPTER 2**

# **DYNAMIC TEST BED OVERVIEW**

#### 2.1 Purpose of the Dynamic Test Bed

The primary function of DTB is to evaluate and test the dynamic performance of the CMA-900 Flight Management System (FMS). The DTB has as core software (VPI FLSIM version 7) of a flight simulator (B737-200) model to simulate with all interfaces of the FMS, including a flight model, environment model, Air Data Computers (ADC) model, GPS model, etc. DTB is in effect a simplified aircraft simulator, which recreates the flight simulation signals for FMS. The FMS will act as if it is in an aircraft. "Dynamic" means all signals changing simultaneously as they do in a real aircraft. Therefore, DTB gives testing of the FMS in a real-time environment and provides a useful tool to develop the new VNAV capabilities on CMA-900 FMS for CMC.

In order to complete the tasks, DTB provides the following functions:

- a) Evaluation of the CMA-900 Lateral (LNAV) and Vertical Navigation (VNAV) accuracy requirements.

- b) Closed loop testing of the FMS for the development, verification and demonstration of LNAV and VNAV requirements.

- c) Crew interface evaluation in a dynamic simulation mode.

- d) Gradual introduction of DTB as a certificate tool for Transport Canada requirements.

# 2.2 Hardware Components

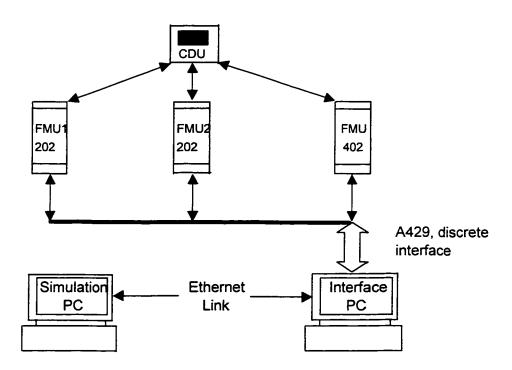

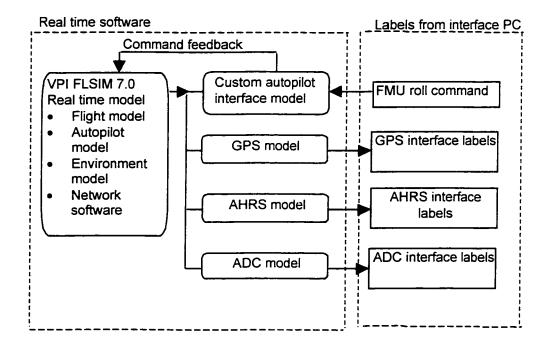

The DTB consists of two PC computers: the Simulation PC and the Interface PC. The Simulation PC holds the simulation software (FLSIM 7.0) which is provided by Visual Prototypes Inc. (VPI). The Interface PC holds the two interface cards A429-PC16 and PCI-6025E, that takes the flight information generated by the simulation PC and sends it to the FMS in the ARINC and discrete protocol, respectively. The general layout of hardware components is shown in Figure 5.

Figure 5: Hardware components of DTB

Figure 5 shows that the DTB has the flexibility for interfacing two kinds of CMA-900 FMS. Model 202, which was originally donated by CMC, has no VNAV functionality and is used for initial testing at the Concordia Aerospace lab; model 402, still under VNAV development but presently possesses Glide Slope functionality mode.

Hardware block diagram is shown in Figure 6, which offers more detailed information about the hardware set-up. The DTB hardware includes two computers, one A429-PC16 card, one PCI6025-E card, one breakout box and the cables to connect these to each other and the FMS being simulated. The Simulation PC, with a network card installed, performs most of the simulation and display tasks during execution of the simulation. The Interface PC also has a network card to communicate with the Simulation PC during the simulation, and it holds one ARINC429 card and one discrete I/O card. The interface PC runs all interface software.

Figure 6: Hardware block diagram of DTB

J1, J2, J4, J5, J6 and J7 are connectors providing the interconnect points for all wiring between the FMS and the DTB. The wiring within is semi-permanent, thus making changes possible. Another connector J3 inside the breakout box simply provides common joint (node) for all avionics.

### 2.3 Software Architecture

## 2.3.1 Simulation Software

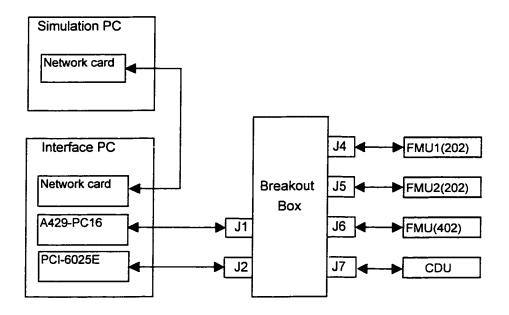

The simulation software includes real time software, the operating system being Windows NT 4 (work station) and the compiler is Microsoft Visual C++ (version 6.0). The simulator software overview is shown in Figure 7.

Figure 7: Simulator real time software overview

The real time software contains the core simulation software (VPI FLSIM model) which includes the flight model, autopilot model, environment model and network software. The network software bundles all interface labels, which contain all flight performance information such as Heading and True Air Speed in ARINC words format, and transfers them to and from the interface computer. The ARINC words format will be presented in Section 3.1.8 in this thesis.

The custom autopilot interface model will act on commands from a Mode Control Panel (MCP). Unlike an autopilot in a real aircraft, DTB has the following custom autopilot modes:

- Speed hold mode (selectable speed)

- Heading hold mode (selectable heading)

- Altitude hold (selectable altitude)

- Vertical speed mode (selectable vertical speed)

- LNAV mode (roll command from a FMU)

- VNAV mode (vertical deviation from a FMU)

The GPS model takes basic aircraft position information and maps it into A429 words that are transmitted by the GPS.

The AHRS model receives information from the flight model and sends the True Heading and Magnetic Heading to the FMU via A429 words.

The ADC model takes information from the flight model, the environment model and the altimeter barometric settings and transmits A429 words in standard ADC format.

### 2.3.2 Interface PC Software

### 2.3.2.1 Synchronization Mechanism

For the system to implement synchronization, the basic concept of multithreaded programming is introduced. A process is a running program that has its own memory, file handles, and other system resources while a thread is an individual process that contains independent execution paths. Threads are execution streams and form the basis of multitasking [10]. That is to say, each program that runs in Windows has its own main thread to launch the program, and which may also start additional threads. Each new thread has its own procedures and executes the code in that procedures at the same time that other threads are working. Threads are managed by the operating system, each thread having its own stack. In other word, many threads can access the same global variables, even a single function.

There are two kinds of threads in Windows, user interface threads and worker threads. A user interface thread has windows and its own message loop which sends and receives messages for user's application. A worker thread has no windows, and therefore it is relatively easier to achieve the synchronization between the FMS performance and flight simulator reaction in DTB since all worker threads have the same characteristics.

In the system referred to in Figure 8, the main function defines an instance of the DTBExecutiveThread first, all other working threads beginning in the order DTBVPIIOThread, DTBArincIOThread, DTBVADIOThread and passing data to the double buffered container. After performing their functions, they will stop until being woken up at every 30 Hz period which is predefined from the flight simulator. At the beginning of each cycle, the DTBExecutiveThread first copies everything from the

writable layer into the readable layer of the double buffered container, then it will wake up the threads in a fixed order. The *flags* (logic TRUE or FALSE) in each thread are used to synchronize all of the working threads in the double buffered container when updated by the *DTBExecutiveThread*.

### 2.3.2.2 DTBExecutive Workspace

The Interface PC software takes all flight simulation information from the Simulation PC via a network packet and transfers it to the interface cards smoothly in real-time. This module controls the ARINC-429 and discrete information, the software being put under the workspace of "DTBExecutive". The design is described at the Class/Object level and the architecture is Object Oriented. The software architecture consists the executive workspace which runs on the Interface PC housing the IO cards, and the VPI link & interface running on the Simulation PC along with the VPI flight simulator. The "DTBExecutive" software structure can be seen in Figure 8. The solid line format represents control signals; the dash line format is used to show data signals.

Figure 8: DTBExecutive Components

The main *DTBExecutiveThread* object is used to execute the rest of the objects in the workspace of "*DTBExecutive*". It runs periodically (at 30 Hz), and in each cycle of execution, it invokes operations in the other objects of this component.

The *IOThreadProcess* object is a generalized interface that encapsulates the general functionality that must be provided by every one of the IO card processes including performing the IO, waiting to be awaken by the executive thread, and updating the double buffered container data.

The ARINCIOProcess object implements all the operations needed to control, transmit, and receive data to and from the ARINC 429 cards. The thread associated with this object is triggered periodically to continue its execution by the Executive Thread object. When it is triggered, the ARINCIOPProcess object performs the necessary checking for available data in the ARINC buffers to be read, reads available data into the double buffered container, and transmits data from the double buffered container to the FMS via the ARINC channels.

The *DIOProcess* object implements all the operations needed to control. read, and write digital and analog data from/to the National Instruments IO card. The thread associated with this object is triggered periodically to continue its execution by the Executive Thread object. On being triggered, the *DIOProcess* object performs digital/analog read/write operations with the National Instrument card and updates the corresponding fields in the double buffered container.

The *VPIOProcess* object is a TCP/IP client-server for communication with the other component running on the VPI Simulation PC. The thread associated with this object is triggered periodically to continue its execution by the Executive Thread object.

When it is triggered, the *VPIOProcess* object sends data from the double buffered container to the VPI simulator and receives the data sent by the VPI simulator into the double buffered container.

The *DoubleBufferedContainer* object implements a double-buffered system bus. Double buffering enables access synchronization between the various threads in the software architecture. The first buffering layer in this container is available at any time for any thread to read data from while the second buffering layer is available for the other threads to perform synchronized write operations into it [11]. The Executive Thread periodically locks the two buffering layers and copies the second one into the first before releasing the mutual exclusion lock. The purpose of double buffering is to cancel the effect of the sequence of execution of the threads on the performance of the whole system and to provide a standard synchronization mechanism according to a validated real-time software design pattern.

#### 2.3.3 Communication Tool

Visual C++ Transmission Control Protocol / Internet Protocol (TCP/IP) client-server two—way communication module was designed for transferring data between the Simulation PC and the interface PC. This is a 32-bit synchronous Winsock application and thus supports multithreaded programming.

There are three classes in this module- the main class *CblockingSocket*, two helper classes *CsockAddr* and *ChlockingSocketException*. The *CblockingSocket* was designed for synchronous use in a worker thread, and embodies the major functionality of the module. The *CsockAddr* achieves conversion between network byte order (big

endian) and host byte order (little endian). The *CblockingSocketException* handles the exceptions on errors that occur and time-outs thrown by the *CblockingSocket* when sending or receiving data [9] [46].

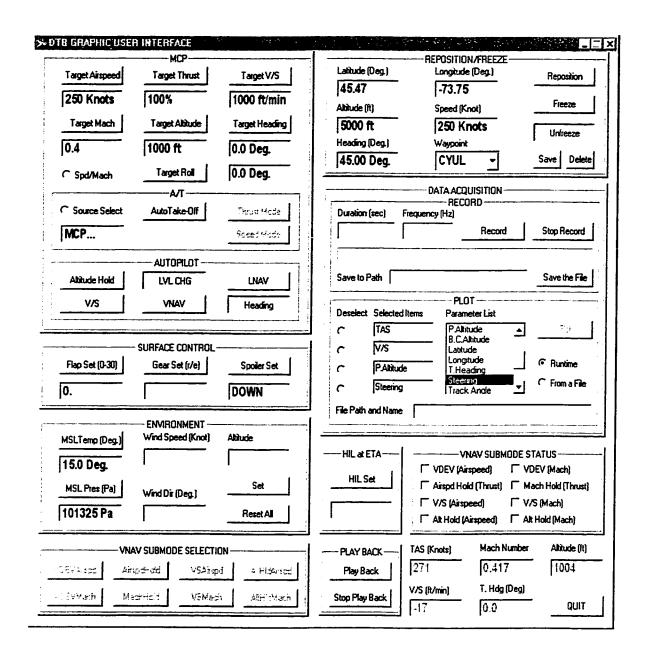

## 2.3.4 Graphic User Interface (GUI)

There are four major GUIs developed in the DTB, namely Simulation control, ARINC labels, DIO and Channel Switch. The Simulation control GUI contains all simulation control features such as reposition, freeze, recording and graphing, aircraft flight controls settings and Automatic Flight Control systems. The feature of the MCP GUI is presented in Figure 9. ARINC labels GUI is used to trace down the real time performance of the simulation parameters in standard ARINC format and their engineering values. DIO GUI is used to check up the status of the simulation discrete signals. Channel Switch GUI is used to provide the flexibility of changing different channel setting for the existing ARINC property file in the specific A429-PC 16 card.

The author has contributed to the development of the last three GUIs in the DTB and the detailed description will be given in Chapter 4.

Figure 9: Simulation Control GUI

# **CHAPTER 3**

# HARDWARE INTEGRATION

The technologies that dominate systems design shift with hardware miniaturization and concomitant architectural integration strategies. Years ago, systems engineers relied upon functional encapsulation in dedicated hardware units (subsystems) and standard communication channels, especially ARINC 429. Specialized computer hardware teams designed subsystems and software engineers often formulated requirements after hardware design. Now and in the future, highly integrated systems designs blur the distinction between system and subsystem. Therefore, the systems engineer should have background not only in software technology area, but also in data buses and processors.

### 3.1 ARINC 429-PC16 Interface

#### 3.1.1 ARINC Standards

Advances in microelectronics, information processing, and displays, and the integration of those technologies into the modern flight management system, are reaching the stage when almost any operational demand can be met. While technically and economically beneficial, the integration philosophy can also make life difficult for some airline buyers who may want to make their own choice of equipment, for example, to maintain commonality with systems already in use or to protect their national industry. National and international standards, such as those recommended by Aeronautical Radio, Inc.(ARINC) and other organizations, all contribute to interface definitions, interference

management, safety, materials use, tests, and other fields and define the operational, dimensional and signal interface characteristics to ensure interchangeability between equipment of different manufacturers and compatibility with other equipment [4].

The ARINC organization is the technical, publishing and administrative support arm for the Airlines Electronic Engineering Committee (AEEC) group. The purpose of the standards published by this organization is to meet the operational and technical requirements of individual airline users, while establishing the most general solution so that a market force may develop. ARINC standards are currently used in military avionics primarily for special mission and transport category military aircraft. However, as ARINC standards begin to address integrated avionics, they are likely to have impact on fighter / attack avionics. This relationship is also dual track, as military hardware and software technologies find their way into transport avionics [8]. ARINC Specification 429 is a serial data bus used for point to point communication. Multicast operation is also possible with a line for each receiver, but two-way communications (full duplex) is not possible in this manner. In other words, transmission of information occurs from a port on the Line Replace Unit (LRU) that is designated for transmission only. Similarly, receive ports are used for receive only, and information cannot flow into a port designated for transmission. This is the basic definition of a simplex bus.

Data transfers are clocked at either 100,000 bits per second or 12,000-14.500 bits per second with a tolerance of 1%. This data bus functions most commonly for transmitting navigation information. An attachment to ARINC 429 contains a digital interface standard that provides data word formats for radio navigation information such as frequencies for Very High Frequency Omni-Range (VOR), Instrument Landing

System (ILS), Automatic Direction Finder (ADF), and transponder, as well as Distance Measuring Equipment (DME).

## 3.1.2 A429-PC16 Design Review

The design of the A429 incorporates an open systems philosophy. The A429 is a generic processing engine that can be configured through various application programs. Processing for each of sixteen channels is performed independently through host-defined Transmit, Receive, and Monitoring data structures.

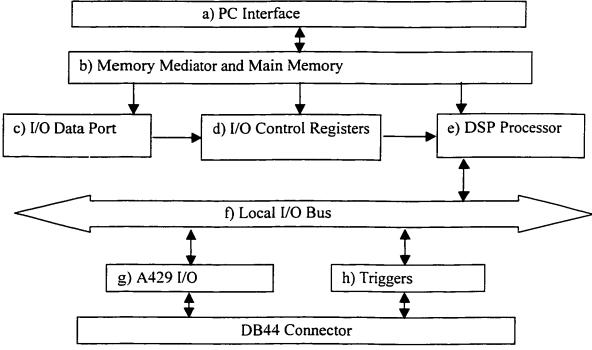

The A429-PC16 appears as two independent 8-channel devices, namely Device 1 and Device 2. Device 1 contains Channel 1 through 8; Device 2 contains Channel 9 through 16. Each channel can be configured either as transmitter or receiver, and all the receiver channels being always assigned to the lower channel numbers. Each device has 256K of internal RAM. Figure 10 shows the basic block diagram of the A429 module.

Figure 10: A429-PC Block Diagram

From top to bottom, block (a) shows the host interface where the circuit block contains the 16 data slave interface and the interrupt logic. Block (b) provides a main device memory of 256k byte SRAM and a high-speed bus mediator for memory access between the device and the host. Block (c) provides the organism with access to the device RAM. Block (d) gives the elementary control functions of the A429-PC, which includes firmware start/stop, PC interrupt control, memory base address, memory window control, and memory access control. Block (e) is a general-purpose digital signal processor that executes the firmware code to afford the low level ARINC functionality running under Windows NT operating system. Block (f) is a general local bus, which offers the correspondence for A429 channels, hardware clock, and LED logic. Block (g) provides the transmitter or receiver function for the actual A429 buses. Block (h) provides a coupled latching 48-bit, and a 1-µsec timer, the latching of a 48-bit time stamp being controlled by the Digital Signal Processor (DSP) through discrete logic and ensuring accurate and consistent time marks for each ARINC 429 message.

### 3.1.3 ARINC 429 Physical Aspects

It is often easier to understand the system if the physical aspects of ARINC 429 are described first. These include transmission media, wiring topology and transmission characteristics.

#### 3.1.3.1 Transmission Media

The transmission media for the ARINC bus is a 78  $\Omega$  twisted-shielded pair. Each bus has only one source, but a maximum number of 20 sinks can be connected. A source can handle a maximum load of 400  $\Omega$ . A receiver sink must have minimum effective

input impedance of 8 k $\Omega$ . The bus length in the most applications is designed for less than 175 feet.

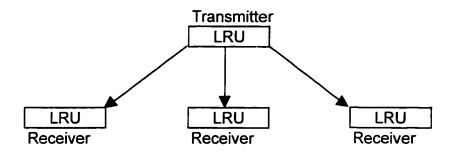

## 3.1.3.2 Wiring Topology

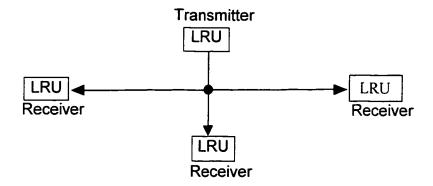

There are two topologies - Star and Bus Drop, which are shown in Figure 11 and Figure 12 respectively.

Figure 11: Star Topology for LRU Wiring

Figure 12: Bus Drop Topology for LRU Wiring

The choice of wiring topology depends on the distance of the sinks to the source.

Safety is the advantage of Star topology since each LRU has its own connection to the

source, and any break along bus length results in loss of only one listener. However, the Star topology requires much more wire, thus adding more weight. On the other hand, although the Bus Drop topology uses the same number of connections, there is significant reduction in weight.

### 3.1.3.2.1 Transmission Characteristics

ARINC 429 has two speeds of operation – 12.5 kHz and 100 kHz. Transmission of sequential words is separated by at least 4 bit times of NULL (zero voltage). This eliminates the need for a separate clock signal wire. That's why this signal is known as a self-clocking signal. Most ARINC 429 transmitters are designed using RC circuit to control the rise time and this implementation is preferred in order to minimize overshoot ringing.

#### 3.1.4 ARINC 429 Architecture Overview

The multi-channel ARINC 429 card (A429) provides simultaneous interface of multiple transmit channels, receive channels, bus monitoring, advanced interrupt services, and high speed host operations. The A429 architecture uses a DSP processor to transmit or receive A429 messages and store them on the monitoring data buses. Low–level processes control all A429 messages within the monitoring buses for protocol verification. High-level processing is responsible for moving A429 packets in real-time to and from the defined data buffers. The general A429 architecture can be specified as Control Registers. Device Management, Transmit Management, Receive Management and Bus Monitoring.

The Control Registers allow the host application program to control hardware and data structures for A429 processing. They include the host command set syntax and key software control registers for managing A429 processing and the hardware registers that are directly accessible from the PC. Device Management includes the processes for setting up and general operation of A429 transmitters and receivers. Transmit Management includes the data structures associated with all A429 messages. Receive Management provides a sophisticated data structure for real-time bus monitoring of A429 traffic. Bus Monitoring gives information on how to receive, and it is useful when the host system has tight processing constraints (relative to ARINC 429 traffic), but must still receive every ARINC 429 message word.

Since the DTB is mainly involved in transmitting and receiving firmware, those two architectures will be described in detail in the following sections.

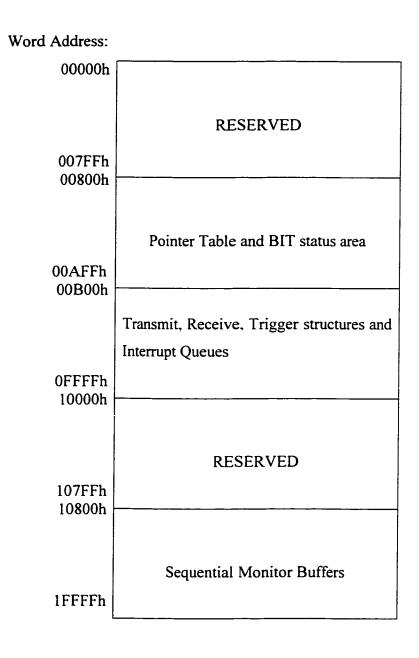

# 3.1.5 Address Map

Before going into the detailed description on transmit/receive management, the memory address map is described for the A429 memory RAM. As mentioned previously, each device has 256k bytes RAM. The detailed address map is shown on Figure 13. It is noted that the internal addresses between 00000h and 007FFh and 10000h and 107FFh are reserved and should not be accessed. There are 128k word addresses between 00000h and 1FFFFh, and each 16-bit word has two bytes. Hence, the memory size for each A429 device is 256k bytes.

Figure 13: A429-PC16 Memory Map (Device 1)

The bit 0 of the 16-bit I/O Control/Status Register (CSR) selects the lower or upper 128k bytes. In the PC16, CSR1 (word address 0000h) bit 0 can be used to access the full 256k bytes of Device 1 memory and CSR2 (word address 0004h) bit 0 can be used to access the full 256k bytes of Device 2. Software control registers are compound with General Control Registers, System Clock Registers. Interrupt Registers, Trigger Registers, Sequential Monitor Registers, Transmit/Receive Operation Registers and Command Block Pointer Registers. The detailed software control registers address map is shown on Figure 14.

| Address       | Name                                 |  |

|---------------|--------------------------------------|--|

| 880h – 886h   | General Control Registers            |  |

| 896h – 899h   | System Clock Registers               |  |

| 89Bh – 8A0h   | Interrupt Registers                  |  |

| 8A3h – 8A6h   | Trigger Registers                    |  |

| 8A9h – 8ADh   | Sequential Monitor Registers         |  |

| 900h – A00h   | Transmit/Receive Operation Registers |  |

| 0B00h - FFFFh | Command Block Pointer Registers      |  |

Figure 14: Software Control Registers

It is noted that the address range (900h – A00h) applies for both transmit and receive operation. Each channel control table has a length of 1Fh, in other words, there are 32 words for each channel transmit/receive control block. And those location used for transmitter or receiver is determined by the first word from control block structure – Channel Type. Also, it should be clear that the locations which are not included in Figure 14 are reserved as A429 internal use. Accessing these locations will produce unpredictable results.

## 3.1.6 Transmit Management

This section explains the definition and management of transmit command blocks and their associated data buffers. Command blocks are linked to allow for flexible and accurate A429 messages transmission.

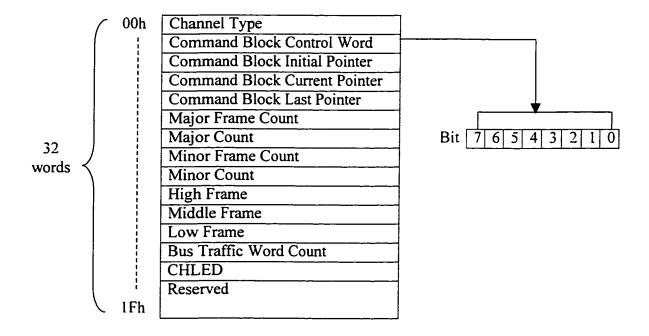

#### 3.1.6.1 Transmit Control Block Structure

A control block of each transmitter contains 32 words that govern command block processing. Note that, the "words" here have different bit number definitions with standard ARINC format that will be described in section 3.1.9. Figure 15 illustrates the major data structure for a control block. Each cell represents a word.

Figure 15: Transmit Control Block Structure

Channel Type This 16-bit word defines the type of channel, it contains FFFFh if it has been predetermined as a transmit-channel and 0000h if it has been designated as a receive-channel.

Command Block Control Word This word governs transmit and command block operations for the channel through the following bits:

- Bit 0 is the Halt bit, which is used to halt processing for the associated command structure when it is set to "1". The firmware completes processing the current command block, halts processing, and then clears this bit.

- Bit 1 is used to present the transmit-speed. For fast transmission (100 kHz). this bit is set to "1"; for slow transmission (12.5 kHz), this bit is set to "0".

- Bit 3 is Channel Wrap bit. The purpose of the channel wrap feature is to allow an operator to receive data on a channel and immediately transmit the same data out on a selected transmit channel. To enable Channel Wrap processing, this bit is set to "1"; for normal operation, as in the case of the DTB, it is set to "0".

- Bit 4 is used to enable or disable Channel Wrap Error Injection globally with "1" or "0" respectively. When masking data, the possible errors come from the word parity, adding a bit and subtracting a bit.

Command Block Initial Pointer (CBIPTR) This pointer location is constantly monitored by the A429's firmware. When CBIPTR is at non-zero, the firmware sets this pointer to zero and executes a chain of command blocks beginning at the offset defined in

CBIPTR. The interface between this pointer and the command block will be described in the next sub-section 3.1.6.2.

Command Block Current Pointer This pointer points to the current location in the command block structure. This pointer is at zero until processing of a command block structure starts. The interface between this pointer and the command block will be described in the next sub-section 3.1.6.2 as well.

Command Block Last Pointer This location is updated when a halt occurs, and indicates the last command block that was executed before the halt occurred.

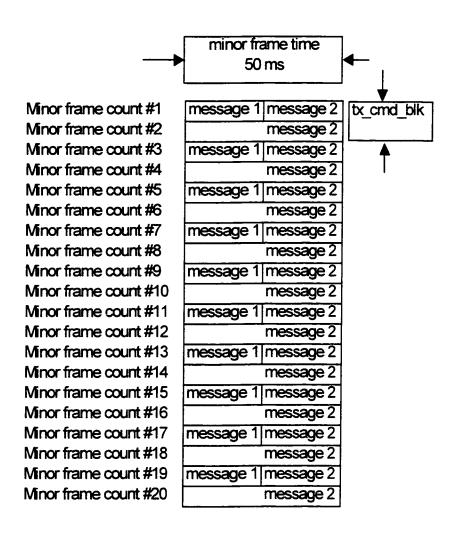

Major Frame Count This value determines the number of major frames to execute before halting command block processing. For continuous operation, in the case of the DTB, it is set to "0". In time-division multiplexing, a frame is defined as one complete commutator revolution that includes a single synchronizing signal or code. Major Frame is the time period, during which all data of a multiplex are sampled at least once, including one or more Minor Frames. Major frame length is determined as (N)(Z) words, where N is the number of words and Z is the number of words in the longest submultiple frame. For more detail about the relationship between major frame and minor frame, see section 3.1.8 with actual example.

Major Count This value indicates the current major frame being processed, and it is updated by the A429 firmware.

Minor Frame Count This value determines the number of minor frames to execute for each major frame.

Minor Count This value indicates the current minor frame being processed, and it is updated by the A429 firmware.

High Frame This register contains the most significant 16 bits of the 48-bit time at which the last minor frame type command was processed, this value being used by the A429 firmware to keep track of minor frame times.

Middle Frame This register contains the middle 16 bits of the 48-bit time at which the last minor frame type command was processed, this value being used by the A429 firmware to keep track of minor frame times.

Low Frame This register contains the least significant 16 bits of the 48-bit time at which the last minor frame type command was processed, this value being used by the A429 firmware to keep track of minor frame times.

Bus Traffic Word Count In this value is the increment for each word transmitted.

A word count is provided for each channel.

CHLED, Channel Activity Indicator This value is used by A429 firmware to indicate bus activity. It contains 0000h if there is no bus activity, 00FFh if the channel is active, and FF00h if the channel is transmitting errors.

The rest of the total 32 words are reserved and used for further application under ARINC development.

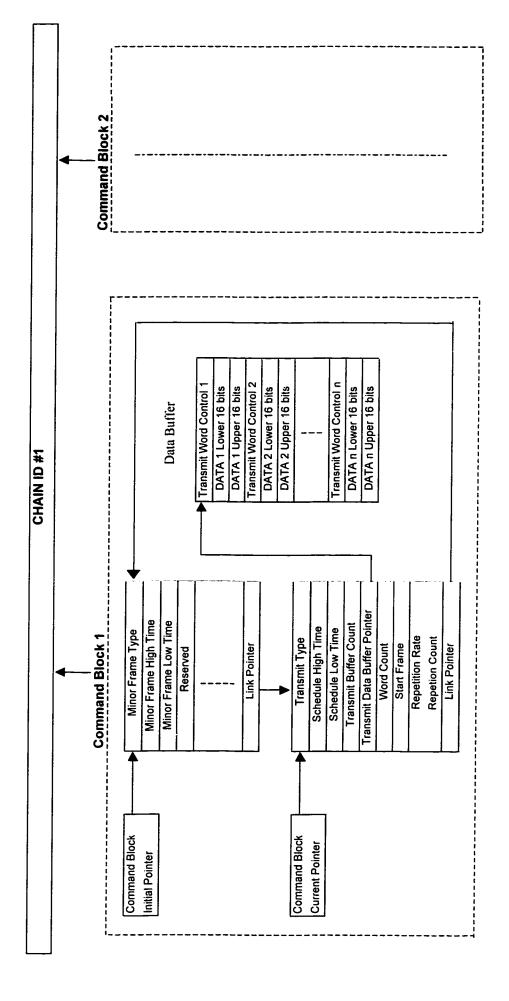

### 3.1.6.2 Transmit Command Block Structure

After setting up the control block, A429 transmission commands have to be specified in a series of linked-list command blocks. The length of the command block linked-list is limited only by the available internal 256k bytes of A429 device memory (SRAM). Each byte here has 8 bits according to the internal A429 address range (00000h-1FFFFh). Separate control areas for each of the eight channels allow the A429 device to perform each channel simultaneously. The transmit-register for a channel is pointed at offsets from the base address of that channel's control table. Channel control

tables begin at 00900h and have a length of 1Fh. Hence, the control table for channel 1 occupies 00900h to 0091Fh, the control table for channel 2 occupies 00920h to 0093Fh, and so forth.

Figure 16 illustrates the data structure for one command block linked-list chain. Each transmit-channel has one Chain ID Number, and there could be many command blocks linked to this Chain. Separating different command block depends on the label characteristics, and labels having the same transmitting speed should be grouped into the same command block. To program transmit operations on the A429, a linked-list data structure of command blocks has to be constructed and loaded into A429 memory first, then the 16-bit Command Block Initial Pointer (CBIPTR) has to be programmed with the address of the first word the first command block. When the firmware detects a nonzero value in CBIPTR, it uses this value as a pointer to the first command block of the linked list. It then sets CBIPTR to "0" and begins processing the command block.

Figure 16: Transmit Command Block Data Structure

Minor Frame Type/Transmit Type This place defines a code for the type of operation and the way of performance. The accessible codes are shown in Table 1.

**Table 1: Type Codes**

| Operation   | Control<br>(Bit 15) | Control<br>(Bit 14)         | Transmit<br>Block (Bit 13) | Control<br>(Bit 12) | Type Code<br>(Bit 0) |

|-------------|---------------------|-----------------------------|----------------------------|---------------------|----------------------|

| Minor Frame | NO-OP               | Interrupt at end of command | N/A                        | N/A                 | 0                    |

| Transmit    | NO-OP               | Interrupt at end of command | l = Single<br>0 = Block    | N/A                 | I                    |

- Bit 15 is set to "1" to skip the command or is set to "0" to process the command.

- Bit 14 is set to "1" to make an interrupt when the command is ended or is set to "0" to produce no interrupts upon end of the command.

- Bit 13 is set to "1" to transmit a single word each time the command block is

processed when the next data word in the transmit-buffer is sent. To transmit

the whole data buffer each time the command block is processed, set this bit

to "0".

- Bits 1 11 are reserved as A429 device internal use.

Minor Frame High Time This register is associated with the minor frame type command and contains the upper 16 bits of the time, in microseconds, allotted for a minor frame.

Minor Frame Low Time This register is associated with the minor frame type command and contains the lower 16 bits of the time, in microseconds, allotted for a

minor frame. When the firmware encounters another minor frame, it checks both minor frame high and low times to determine when to start processing the next minor frame.

Schedule High Time This register is associated with the transmit type command and contains the lower 16 bits of the time, in microseconds, that must expire before the transmit command block is processed. The time is referenced from the last minor frame type command.

Schedule Low Time This register is associated with the transmit type command and contains the upper 16 bits of the time, in microseconds, that must expire before the transmit command block is processed. The time is also referenced from the last minor frame type command.

Transmit Buffer Count (TBCNT) This register is associated with the transmit type command and indicates the number of data words to transmit for the associated command block. Each value to be transmitted requires three 16-bit words in Hex. The first word is the control word, followed by the lower 16 bits of the ARINC data word, then by upper 16 bits of the ARINC data word, i.e., the Transmit Buffer Length is equal to 3 times that of TBCNT.

Transmit Data Buffer Pointer This value is associated with the transmit type command and points to the base of the transmit buffer for the associated command block.

Word Count This register is associated with the transmit type command and points to the current location in the transmit data buffer.

Start Frame This register is associated with the transmit type command and indicates which minor frame a transmit type command block will begin executing.

Repetition Rate (REPRTE) This register is associated with the transmit type command and indicates how often to process a transmit type command block after the START condition is met. If the REPRTE is equal to 2, processing of the command block will occur every other time that the associated command block is accessed.

Repetition Count The A429 firmware uses this value to control the Repetition Rate word transmission.

Link Pointer This value points to the next command block in the chain.

Transmit Word Control This is the first word of a three-word block which defines a transmit word.

### 3.1.6.2.1 Transmit Firmware Operation

During transmit operations, the firmware decodes each block of the linked-list program and takes the suitable action. If a minor frame type is used, the minor frame times are checked and the structure is set up for minor frame operation. If a transmit-type is indicated and schedule times, start, and repetition rates are met, the transmit-buffer is transmitted. The command block structure is continued until a halt condition happens which can be generated in one of these three ways:

- By setting bit 0 of Command Block Control Word in the control block structure to "1".

- By setting the Link Pointer of the command block data structure to "0".

- By completing the specified number of major frames.

## 3.1.7 Receive Management

In order to access the receiver operation from all sixteen channels of the board, the parameters and data storage structures must be defined first. Table 2 defines the data storage structure required for A429 PC16.

**Table 2: Data Storage Structure**

| Data Storage Structures    | Description                                            |  |

|----------------------------|--------------------------------------------------------|--|

| Current Value Buffer       | Contains the latest received data words for a specific |  |

|                            | channel. They are arranged by label or both SDI and    |  |

|                            | label.                                                 |  |

| Current Time Buffer        | A time stamp buffer can be set up to provide a current |  |

|                            | time stamp for each received word.                     |  |

| Channel Sequential Monitor | Stores data received on a specific channel.            |  |

| Global Sequential Monitor  | Stores data from all receive-channels.                 |  |

It should be noted that either the Channel or Global Sequential could be selected. Even though the DTB deals with Current Value Buffer and Channel Sequential Monitor only, it would still be a good idea to go briefly through all components starting with the receive data structure.

#### 3.1.7.1 Receive Control Block Structure

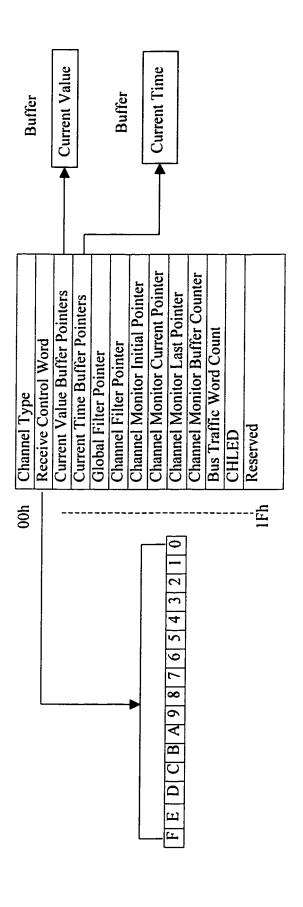

The receive control block structure is comprised of 32 words. They are mainly the channel type word, the receive control word, the current value buffer pointer, the current time buffer pointers, the filter pointers, bus traffic word count, and channel activity indicator. Figure 17 illustrates the receive control block structure.

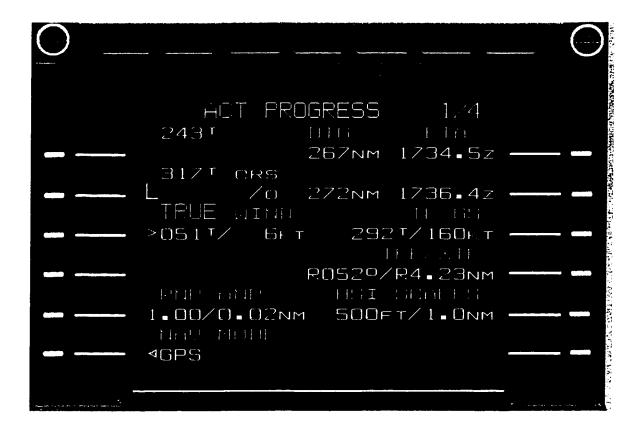

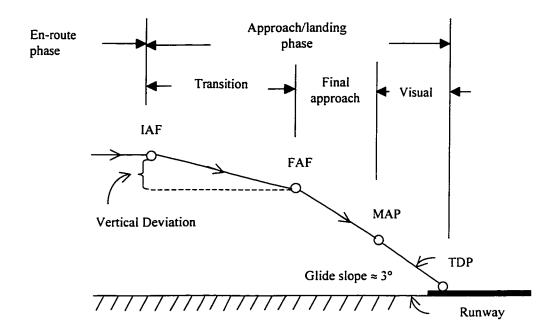

Figure 17: Receive Control Block Structure