#### AN EBD APPROACH TO EMBEDDED PRODUCT DESIGN

Jun Zhang

#### A Thesis

in

#### The Department

of

Concordia Institute for Information Systems Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Quality System Engineering) at

Concordia University

Montreal, Quebec, Canada

Quality Systems Engineering

November 2011

© Jun Zhang, 2011

#### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

By:

ZHANG, JUN

Entitled: AN EBD APPROACH TO EMBEDDED PRODUCT DESIGN

and submitted in partial fulfillment of the requirements for the degree of

Master of Applied Science (Quality System Engineering)

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|             | Dr. Simon Li                                                                   | _Chair      |  |

|-------------|--------------------------------------------------------------------------------|-------------|--|

|             | Dr. Youmin Zhang                                                               | Examiner    |  |

|             | Dr. Chun Wang                                                                  | Examiner    |  |

|             | Dr. Yong Zeng                                                                  | _Supervisor |  |

| Approved by | Dr. Mourad Debbabi, Director                                                   |             |  |

|             | Concordia Institute for Information System Engineering<br>Dr. Robin Drew, Dean |             |  |

|             | Faculty of Engineering and Computer Science                                    | ce          |  |

| Date        | 11/30/2011                                                                     |             |  |

#### ABSTRACT

#### AN EBD APPROACH TO EMBEDDED PRODUCT DESIGN

#### Jun Zhang

In contrast to general-purpose computers, an embedded system has a special function for a special purpose. Nowadays, embedded products play an important role in daily life, and they are widely used almost everywhere, such as in GPS, mobile phones, digital TV, transportation systems, computer systems in aircraft, computer systems in vehicles.

Despite its popularity, the development process for embedded products is usually very complicated and thus very often results in over time (development time), or in overbudget (cost) or a lack of expected product specifications. Therefore, it is necessary to use an appropriate prescriptive method or design methodology to guide a designer in the design process.

The objective of the present thesis is to introduce a new approach to embedded system engineering to implement a new embedded product design. A rich working experience in industry suggests that there is a need for such work. Compared to the traditional approach, which uses product-based or process-based design analysis, the proposed approach uses environment-based design (EBD) methodology for the whole embedded system development life cycle, which may be a systematic procedure aimed to help designers during embedded product development. To better illustrate the application of the proposed design approach to embedded system engineering, an original example of an embedded ARM Linux system is used as a case study in the present thesis.

#### ACKNOWLEDGMENTS

I would like to thank Professor Yong Zeng for constructive and insightful suggestions and guidance during my graduate career in his Design Lab. I thank him for helpful suggestions and his constant encouragement.

I want to thank all the members in the Design Lab, especially Suo Tan and Thanh An Nguyen.

Finally, I also take this opportunity to thank my family. Without their support, I would not have gone so far.

## **Table of Contents**

| List of Figures                                                     | viii |

|---------------------------------------------------------------------|------|

| List of Tables                                                      | X    |

| Chapter 1 INTRODUCTION                                              | 1    |

| 1.1 Background                                                      | 1    |

| 1.2 Copyright statement about case studies                          | 2    |

| 1.3 Motivation                                                      | 3    |

| 1.4 Contributions                                                   | 4    |

| 1.5 Thesis organization                                             | 5    |

| Chapter 2 EMBEDDED SYSTEM DESIGN                                    | 7    |

| 2.1 Embedded systems                                                | 7    |

| 2.1.1 Introduction of embedded Linux system: terminology            | 8    |

| 2.1.2 Embedded product structure                                    | 13   |

| 2.1.3 Embedded system design flow                                   | 14   |

| 2.1.4 Recommendation of a good design in an embedded product design | 16   |

| 2.2 Criteria of an effective design methodology                     | 16   |

| 2.3 Embedded system design methodology: related work                | 17   |

| 2.4 Motivation of the EBD in embedded system design                 | 23   |

| Chapter 3 APPLICATION OF EBD TO EMBEDDED PRODUCT DESIGN             | 24   |

| 3.1 Case study introduction                                         | 25   |

| 3.2 Overview: why EBD in an embedded system development                  | 26              |

|--------------------------------------------------------------------------|-----------------|

| 3.3 Understanding design problems: embedded product life cycle environi  | ment analysis30 |

| 3.4 Analyzing design problems: conflict identification in embedded produ | ct life cycle43 |

| 3.5 Solving design problems: solution generation                         | 48              |

| Chapter 4 VALIDATION OF EBD: EMBEDDED PRODUCT DEVELOPM                   | MENT - A        |

| CASE STUDY                                                               | 50              |

| 4.1 Introduction                                                         | 51              |

| 4.1.1 Additional case review                                             |                 |

| 4.1.2 Must-do task list for a detailed product development               |                 |

| 4.1.3 Example of a hidden problem                                        |                 |

| 4.2 Development process without EBD methodology                          | 56              |

| 4.2.1 Product development process                                        |                 |

| 4.2.2 Quality of development process                                     |                 |

| 4.3 Analyzing and diagnosing the development process using EBD           | 65              |

| 4.3.1 Adjustment of the development process using EBD                    |                 |

| 4.3.2 Design state                                                       |                 |

| 4.3.3 Distrusted variables life time                                     |                 |

| 4.3.4 EBD approach to the development process: examples                  |                 |

| 4.3.5 Result of EBD approach                                             |                 |

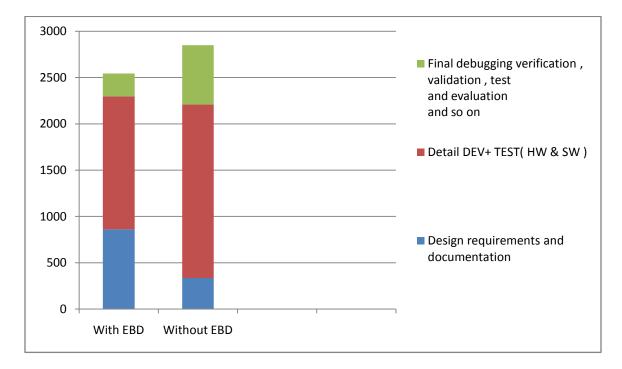

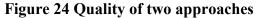

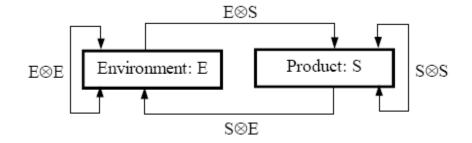

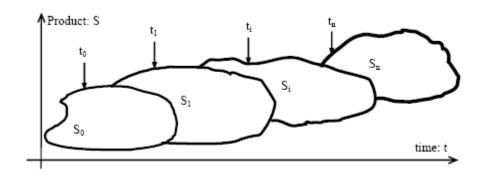

| 4.4 Quality of two approaches                                            | 97              |

| Chapter 5 CONCLUSIONS AND FUTURE WORK                      |     |

|------------------------------------------------------------|-----|

| 5.1 Conclusion: why use an EBD in embedded system design   | 98  |

| 5.2 Future work                                            | 100 |

| APPENDIX                                                   |     |

| 1.1 Overview of environment-based design                   | 101 |

| 1.2 Recursive object model                                 | 101 |

| 1.2.1 Mathematical foundation                              | 102 |

| 1.2.2 ROM: graphical representation of natural language    | 103 |

| 1.2.3 ROMA: translation of natural language to ROM diagram | 105 |

| 1.3 Formulization of design requirements                   |     |

| 1.4 Environment analysis                                   |     |

| 1.5 Conflict identification                                | 112 |

| 1.6 Solution generation                                    | 113 |

| 1.7 Relationships between the three activities of EBD      | 114 |

| Bibliography                                               |     |

## List of Figures

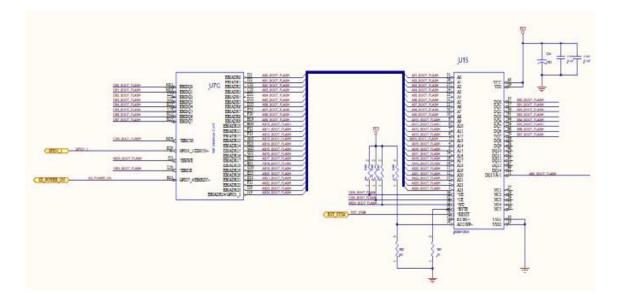

| Figure 1 Embedded system schematic example: memory interface                     | 9  |

|----------------------------------------------------------------------------------|----|

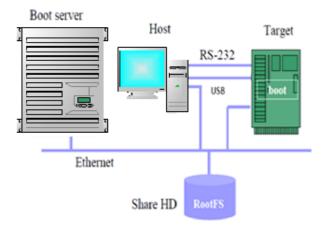

| Figure 2 An embedded system PCB example                                          | 10 |

| Figure 3 Crossing development environment - An example: a distributed system     |    |

| development                                                                      | 12 |

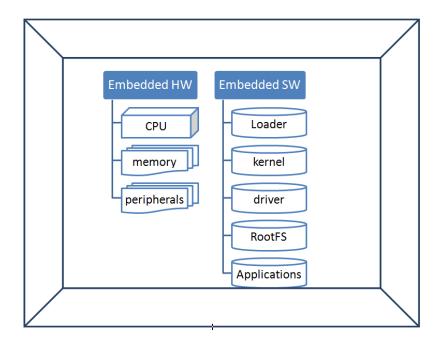

| Figure 4 An example of an embedded system                                        | 13 |

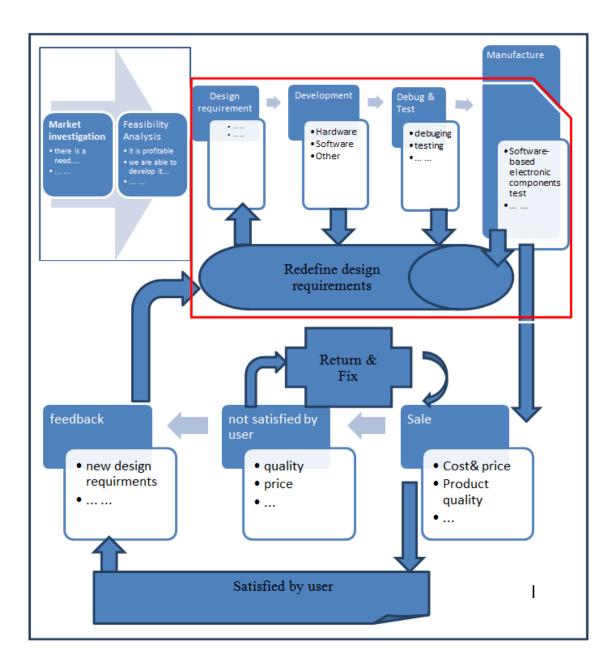

| Figure 5 Scope of the development/design in the present thesis                   | 15 |

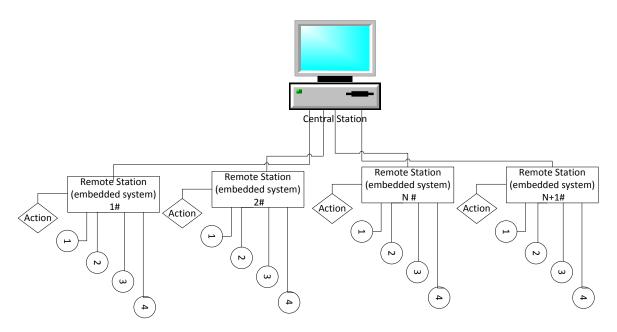

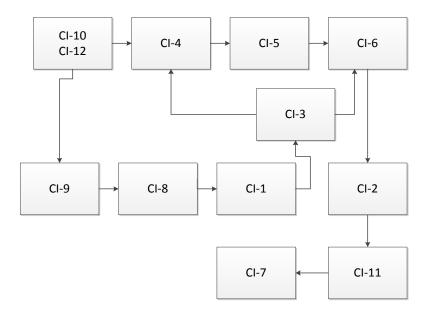

| Figure 6 The system                                                              | 25 |

| Figure 7 Three major product environments [36]                                   | 27 |

| Figure 8 Seven events & eight levels for design requirements [37]                | 28 |

| Figure 9 EBD process model [36]                                                  | 28 |

| Figure 10 Illustration of problems existing in software product development [38] | 29 |

| Figure 11 Created first ROM diagram                                              | 32 |

| Figure 12 Created first updated ROM diagram                                      | 33 |

| Figure 13 Seven events & eight levels of requirements-AB[19]                     | 38 |

| Figure 14 Conflict relationships analysis: an example                            | 47 |

| Figure 15 The best roadmap for solving the conflicts                             | 49 |

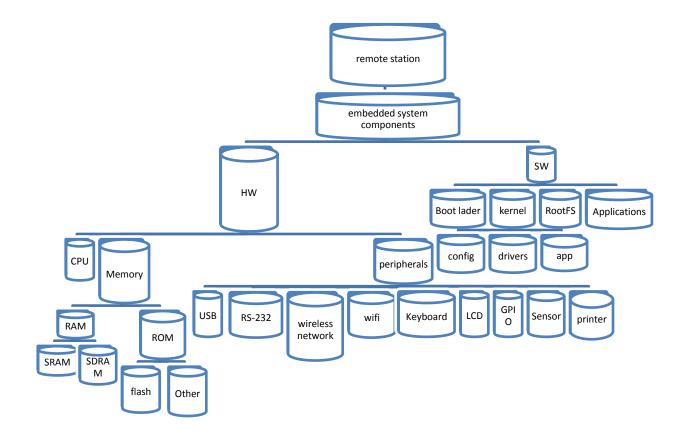

| Figure 16 The remote station system components                                   | 53 |

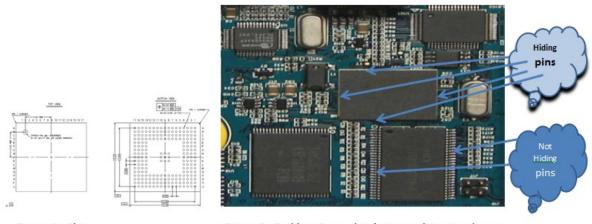

| Figure 17 An example of SDRAM mounting – hidden problems                         | 55 |

| Figure 18 An example of results from SDRAM pins problems- effect from a hidden   |    |

| problem                                                                          | 56 |

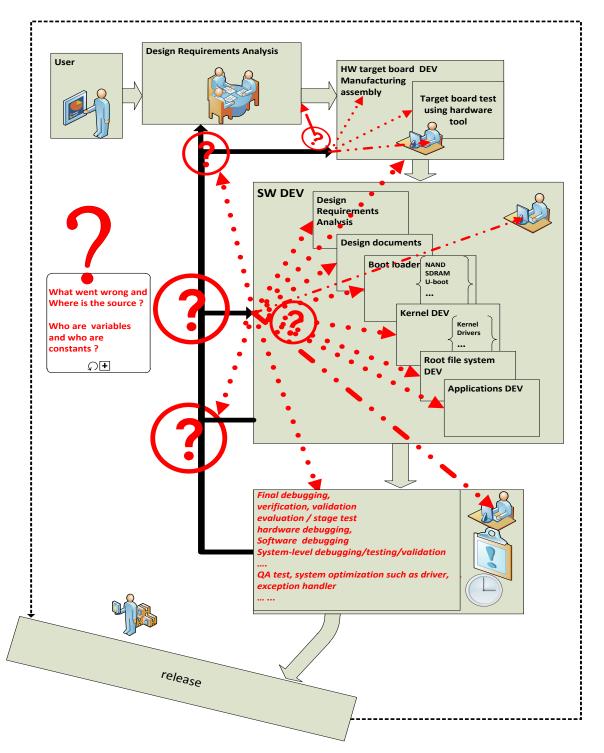

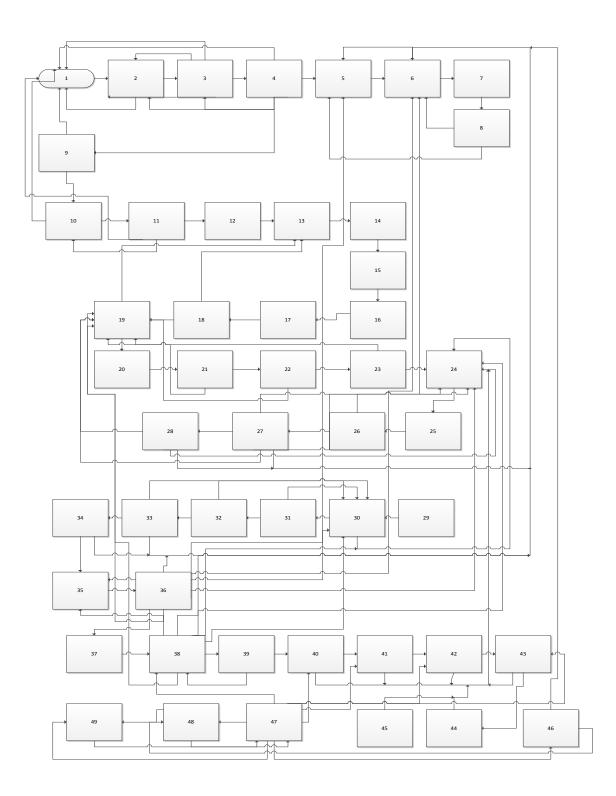

| Figure 19 Detailed development process without using EBD                         | 63 |

| Figure 20 | Detailed development process with EBD application       | 74 |

|-----------|---------------------------------------------------------|----|

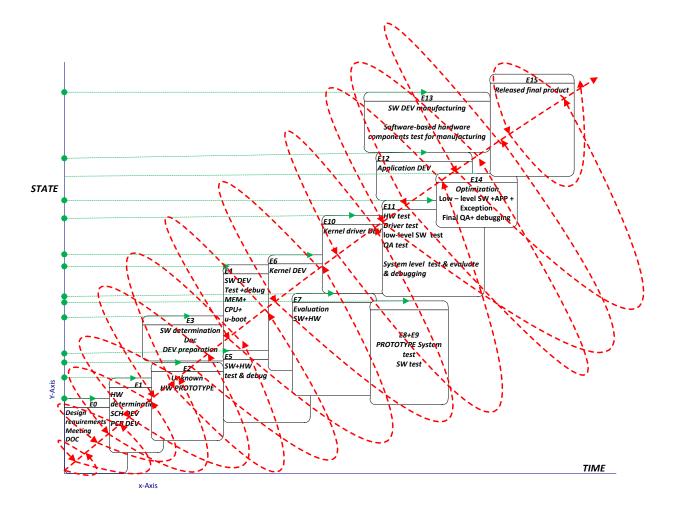

| Figure 21 | Design state & development time                         | 75 |

| Figure 22 | Variables in each design environment & development time | 93 |

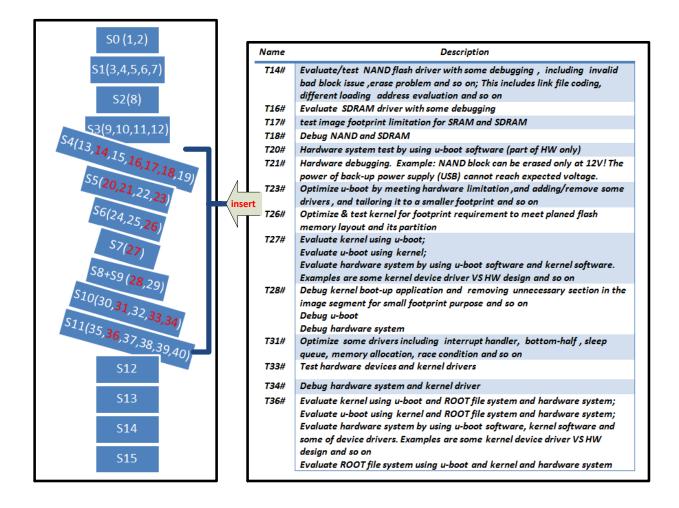

| Figure 23 | EBD approach to the development process                 | 95 |

| Figure 24 | Quality of two approaches                               | 97 |

### **List of Tables**

| Table 1 Rules for generic questions[39]                                            | . 34 |

|------------------------------------------------------------------------------------|------|

| Table 2 Generic domain questions and answers                                       | . 35 |

| Table 3 Specific domain questions and answers example using ROM                    | . 38 |

| Table 4 Lifecycle analysis of the embedded product design problem- specific domain |      |

| questions                                                                          | . 42 |

| Table 5 Conflict identification                                                    | . 44 |

| Table 6 Root conflicts analysis                                                    | . 48 |

| Table 7 Technical to-do list for the development                                   | . 54 |

| Table 8 Detailed system development process and its duration                       | . 57 |

| Table 9 Result without EBD                                                         | . 64 |

| Table 10 EBD analysis for phase one                                                | . 66 |

| Table 11 EBD diagnose for phase two                                                | . 69 |

| Table 12 EBD analysis and diagnose for phase three                                 | . 72 |

| Table 13 X variable & C constant: two examples                                     | . 94 |

| Table 14 Result with EBD                                                           | 96   |

## Chapter 1 INTRODUCTION

#### **1.1 Background**

In contrast to general-purpose computers which are designed to meet the needs of many different end-users, an embedded system has a special function for special purpose [1]. In other words, an embedded system is designed to perform a special function. The earlier development of modern embedded systems can be dated back to the 1960's. Apollo Guidance Computer, developed at the MIT Instrumentation Laboratory in the 1960's, is one of the early recognizably modern embedded systems. Since then, embedded systems have gone through a dramatic evolution. The price of embedded systems has significantly decreased whereas the processing power and functionality has dramatically increased. This leads to the significantly increased popularity of embedded systems in a wide range of devices.

In the past half century, embedded systems have undergone a dramatic evolution which has resulted in a significantly decreased cost and increased functionality. This, in turn, leads to the greatly increased demand for embedded products. Nowadays, embedded products play an important role in everyday life and are widely used in daily life, such as global positioning systems (GPS), mobile phones, digital television (TV), transportation systems, computer systems in aircraft, and computer systems in vehicles. The development process for embedded products is very complicated and thus fails very often. Therefore, it is important to use an appropriate design methodology to control design quality. For example, the author has found that some embedded system development projects fail without even starting to write a single code due to a misunderstanding of design requirements. Therefore, it is important to use an appropriate design quality.

The present thesis illustrates how to apply EBD to embedded product designs.

#### **1.2 Copyright statement about case studies**

The author of the present thesis has worked on the design of embedded systems in different scales. Due to the copyright from the confidential agreement that the author has signed with different organizations, the author has no written permit from a company to use real projects as the case study and therefore those industrial case studies cannot be used in the present thesis. Instead, the author created the original case study for the present thesis research.

This is to state that the case study is not associated with any real industrial project or company. In regard to the case study, two things can be stated with confidence because

of the author's rich working experience in industry:

- ✓ For the purposes of showing EBD approach to embedded system design, there is no difference between the embedded system example used here and that of a real project used in a company;

- ✓ The example chosen is comparable to a project from the real world. Consequently, this thesis does not break any confidential agreement that the author has signed with any organization.

#### **1.3 Motivation**

Many IT companies do not have final sellable products even if they have great ideas in the beginning. In order to have sellable products to release and to allow entry into the market as soon as possible, designers often suffer some kind of stress due to budget, the expected development duration of the product, and product quality requirement. These conditions may affect the designers' creation during the process of developing new products. It is very common for expert designers to appear to be "ill-behaved" problem solvers, especially in terms of the development duration and product cost. Therefore, it is very important to develop a new design methodology that can help designers in the process of product design and lead to the improvement of design efficiency, as well as product quality. The objective of the present thesis is to show how to apply EBD to embedded product development to improve design quality. It is hoped that by applying EBD to embedded product development, product quality will be improved and that many IT companies will benefit. In other words, the results of the proposed research will satisfy the needs of many IT companies, particularly those of companies that have to develop more competitive products and take some market share away from their competitors.

#### **1.4 Contributions**

In the present thesis, the description of EBD is attached in the appendix. In the present thesis, a brief review of embedded systems is first given, as well as the design methodology for embedded system development. This is followed by the illustration of how to apply EBD to embedded system development. In addition, the validation of EBD will be discussed. The main contributions of this thesis include the following:

(1) A new approach to embedded system design, conceptual design model EBD, is proposed to guide embedded developers in the design process. This is a new model in embedded system engineering.

The first stage of EBD (environment analysis) benefits both managers in development engineering and developers. The second stage of EBD (conflict

identification) and the third stage of EBD (solution generation) are beneficial mainly to developers. However, that concept also works for managers.

- (2) The application of EBD to an embedded product design is illustrated by the general concept.

- (3) To illustrate the application of the proposed model and the quantitative approach, the case of an embedded ARM Linux product, a real-world example, is adopted studied as a case study.

#### **1.5 Thesis organization**

The rest of the present thesis is organized as follows:

- Chapter 1 INTRODUCTION: introduction of the background, motivation and contributions;

- (2) Chapter 2 EMBEDDED PRODUCT DESIGN: introduction of the embedded system terminology, the embedded product structure, the embedded system design flow, and the recommendation of a good design in an embedded product design;

- (3) Chapter 3 APPLICATION OF EBD TO EMBEDDED PRODUCT DESIGN: explanation of why EBD can be used to embedded system development, and from general point of view, explanation of how to apply EBD to an embedded product design step by step: understanding design problems, analyzing design problems, and then solving design problems. An example (no confidential data from a real

company are used) is used to show how to apply the EBD for practiced application.

- (4) Chapter 4 VALIDATION OF EBD: EMBEDDED DEVELOPMENT CASE STUDY: review of the case including an additional introduction, and then description of detailed development process. This is followed by the validation of the result with two different design procedures – by using EBD and by not using EBD.

- (5) Chapter 5 CONCLUSIONS AND FUTURE WORK: concluding remarks about why an EBD in embedded system design and future work.

In the present thesis, the description of EBD is attached in the appendix. If you want to know what EBD is , please go to Appendix.

### **Chapter 2**

### **EMBEDDED SYSTEM DESIGN**

In Chapter 1, the background of the embedded system design is introduced. Then some basic terminology used in embedded systems is explained, and the recommendation of a good embedded design is explained. Finally, in Chapter 4, EBD is validated whether or not EBD design methodology can help an embedded designer to reach a high level of embedded design.

The objective of the present thesis is to bring a new design methodology to embedded product design engineering, thereby enhancing the quality of design. To achieve this objective, this literature review covers the following areas:

- (1) Introduction of the embedded system : terminology

- (2) Embedded system design methodology: related work

#### 2.1 Embedded systems

Embedded products are widely used in daily life, such as GPS, mobile phones, digital TV, transportation systems, aircraft computer systems, vehicles. The development process is complicated and thus fails very often.

It is difficult to define or to describe embedded systems precisely. There have been many different definitions for embedded systems because the field is a wide and varied. The following are some examples of possible definitions:

- ✓ An embedded system is a special function for special purpose computer system with a combination of hardware and software[1].

- ✓ An embedded computer system (or simply an embedded system) is "a digital system which uses a microprocessor running software to implement some or all of its functions" [2].

For the different operating system (OS), we have the embedded Linux system, the embedded Windows CE, embedded VXWORKS, the embedded android system and so forth. According to the CPU, there are embedded ARM system, embedded PPC system, embedded Intel system, etc.

#### 2.1.1 Introduction of embedded Linux system: terminology

A brief overview of some terminologies used for embedded systems is given below:

#### (1) Embedded hardware (embedded HW):

a) Schematic( SCH ) : in an embedded system design, a schematic diagram is a diagram showing the logic of the hardware – used for the product and also often reflects the pre-

design of the printed circuit board (PCB) [3].

An example of a SCH is shown in the following Figure 1:

Figure 1 Embedded system schematic example: memory interface

b) PCB: A printed circuit board (PCB) is designed for manufacturing or fixing a target board. It mechanically supports Chips on the board. This kind of system is called a System on Board (SOB). System on Chip (SOC) is not the topic in the thesis. In addition, a PCB electrically connects electronic components through conductive pathways, VIAs, tracks or signal traces. It is etched from copper sheets laminated onto a non-conductive substrate [4-6].

An example of a PCB is shown below in the following Figure 2:

| Altium Designer Winter 09 - G:\HW\board jun\junInterfaceV3_4-7.                    | PcbDoc * - Free Documents. Licensed to jmj. Not signed in.                         | -                          |                             | _ 0 X                               |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------|-----------------------------|-------------------------------------|

| DXP Eile Edit View Project Place Design Tools Auto                                 | Route <u>Reports</u> <u>Window</u> <u>H</u> elp                                    | G:\HW\board jun\junInterfa | ○・○・骨 🔟 • 🗟 • 🛝 •           | 는 • 🖻 • 🏢 •                         |

| D ≌ 🖩 🖨 Q 🗶 🕸 🕸 🕸 🖓 🖓 🖓 🖓 🖓 🖓 🖓                                                    | 🤊 🗠 🎾 🛍 (Not Saved) 🔹 📝 🏗 🗗 🥥 🗣 🔿 🖬 🛋 🗛 🌐                                          |                            | • • (All)                   | • 🖓 🗙                               |

| Files 🗸 🖉 🖉 junInterfaceV3_4-7.PcbD                                                | oc *                                                                               |                            |                             | Favo                                |

| Open a document 😵                                                                  |                                                                                    |                            |                             | vrites                              |

| Open a project 😵                                                                   |                                                                                    |                            |                             | ••• •                               |

| New ×                                                                              |                                                                                    |                            |                             | board                               |

|                                                                                    |                                                                                    |                            |                             |                                     |

| New from existing file 🛛 😵                                                         |                                                                                    |                            |                             | rarie                               |

| New from template                                                                  |                                                                                    |                            | <b>9</b>                    |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    | <b>Q</b>                   |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    | unzhm@hotmail.com                                                                  |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

|                                                                                    |                                                                                    |                            |                             |                                     |

| <b>.</b> ا                                                                         |                                                                                    |                            |                             | • • • • • • • • •                   |

| <ul> <li>Files / Projects / Navigator / PCB / PCB   S \ TopLayer   Bott</li> </ul> |                                                                                    |                            |                             | Mask Level Clear                    |

| X1.905mm Y-47.9806mm Grid:0.0254mm (Electrical Grid) Track                         | 0.00001mm,-79.49999mm)(0.00001mm,0.00001mm) KeepOut Net: Width:0.127mm Length:79.5 | imm System                 | Design Compiler Help Instru |                                     |

| 🚯 🙆 📜 🖸 🌸 🛃 🚺                                                                      |                                                                                    | 111.15                     | en 😢 🕈 🔺 🔐 🕎 🕯              | <sup>3)</sup> 2:41 AM<br>10/25/2011 |

Figure 2 An embedded system PCB example

#### (2) Embedded software (embedded SW)

#### a) Boot loader

A CPU can only execute program code found from ROM or RAM. And operating systems and applications images are stored on nonvolatile date storage such as NAND flash, NOR flash or NFS server. When an embedded system is first powered on, it usually does not have an operating system in ROM or RAM. The computer system has to execute a minimum image from ROM. This image is the boot loader image [7].

The job of the Boot Loader is to initialize minimum hardware components from an unknown state to a known state, to load the kernel from the loading memory to the running memory and

so on. Examples of boot loaders are the following: bootstrap loader, LILO, GRUB, ROLO, Loadin, Etherboot, LinuxBIOS, Compaq's bootldr, blob, PMON, sh-boot, u-boot, 2nd boot loader. Multiple-stage boot loaders are used according to the platform. Their design constraints are that they often need to have a small footprint due to one-time use.

#### b) Kernel

A kernel is a bridge between user applications and the hardware. The job of kernel is to process date and to manage the system resources and the hardware system. The kernel is the main part of computer operating systems [8].

#### c) Device driver

In an embedded system, usually, the hardware connects to the communications subsystem or the computer bus. Therefore, device driver software is to allow the higher-level computer programs to interact with a hardware device. For example, when a program calls up routines in the device driver, then the driver sends commands to the hardware device. Applications talk to hardware devices through the device driver [9].

#### d) Root file system

Applications would be able to access any data by file name or directory with a file system. A file system's job is mainly to organize data, manage the available space on the device(s), provide mechanisms to control access to the data and metadata, and update data in the same file at nearly the same time. Some file systems, such as procfs, may be virtual distinguishable

from a directory service and registry[10].

#### e) Application

An application, often called "app", helps the user to perform specific functions such as calling on media players software, GUI functions, Microsoft Office, android applications for education. Apps may be separated from the kernel in some operating systems such as Linux. In some operating systems such as VXWORKS, they are not separated. The system software serves the application in terms of user [11].

#### (3) Crossing development environment

A crossing development environment is shown in Figure 3 below.

- a) **Target** board is the PROTOTYPE of the product.

- b) Host is the computer for embedded developers to develop images.

- c) **Server** is the computer that manages the sharing of resources. The source control software is often used such as perforce or SVN.

## Figure 3 Crossing development environment - An example: a distributed system development

#### 2.1.2 Embedded product structure

To sum up, in general, an embedded system structure may resemble the structure shown

in the following Figure 4:

Figure 4 An example of an embedded system

The peripherals of an embedded system may be different due to different product. For example, the core of embedded systems talks with the outside world via peripherals. Examples are the following: Serial Communication Interfaces (SCI), Multi Media Cards (SD Cards, Compact Flash etc.),Networks( Ethernet, Lon Works, etc.), Discrete IO(General Purpose Input/output ), Analog to Digital/Digital to Analog, Debugging( JTAG, ISP, ICSP, BDM Port, BITP, and DP9 ports) , GPS. For example, if you are developing a digital camera, you may have the following peripherals: LCD for display, flash memory for storage, RAM for running images, a keyboard for the user to input, a speaker to play sounds, a USB to connect to a printer or a PC.

If an embedded system is too simple, the loader, kernel, ROOTFS, drivers, applications may be optional. SW may not have a kernel (operating system) such as the MCS-51 based embedded system used many years ago, or it may not need to develop drivers...

#### 2.1.3 Embedded system design flow

A new embedded product life cycle may be different. The scope of the development/design would therefore be different.

**Figure 5** shows a general embedded product life cycle. The topic in the present thesis would include only the development process shown in the rectangle with the red shape: design requirements, design, debug/test, software-based electronic components test in a manufacturing process, and redefined design requirements.

Figure 5 Scope of the development/design in the present thesis

This **Figure 5** also shows an example of the development process in an embedded product life cycle.

# 2.1.4 Recommendation of a good design in an embedded product design

A recommendation for a good embedded product design/development would be as follows:

- Product features (final design) meet with most design requirements. In other words, a good embedded product design should give customers satisfaction;

- ✓ Development time is short ;

- ✓ Cost is low ;

- ✓ It is easy to update HW/SW; it is possible to update HW/SW; and the updating cost is not too high.

A quality process in embedded product development should at least include points 1, 2, and 3 given above. In industry, experienced engineers should pay more attention to the 4th point above.

#### 2.2 Criteria of an effective design methodology

An effective design methodology should:

- (1) Be able to help the designer have a "good design" in terms of shorter development time and cost, as mentioned in the last section.

- (2) Be able to guide a designer to jump out of a recursive loop[12]

- (3) Be able to improve design process[13] [2].

## 2.3 Embedded system design methodology: related work

The first conference on design methodology was held in London in 1962 [14]. Since then, many conferences on this topic have been held due to the increased realization of the importance of design methodology. In terms of the development of engineering design methodology, there was significant improvement of it in the 1980s[15]. Although many design methodologies have been proposed in this area so far, due to the complexity of embedded systems, it is very hard to find one approach that fits all.

In this section, there is a brief review of some related existing major embedded system design methodologies and their advantages and disadvantages. Some of the representative major embedded system design methodologies are summarized as follows:

#### (1) The test-driven development of embedded systems

This method is based largely on test-driven development using existing software test infrastructures (such as Extreme Programming) with both custom hardware and custom software. They use Extreme Programming trying to detect the problems caused by changing earlier requirements. For example, a developer first writes failing test cases for the necessary functionality, and then writes code, debugs the system, and then refractors as necessary until 100% of the test cases pass[16].

The advantage of this method is that it tries to detect problems earlier under changing requirements. However, the main disadvantage of this method is that it uses existing software to test infrastructures. Three questions must be asked:

- ✓ Can the hardware be trusted in an embedded product design based on an earlier process?

- Can the software be trusted in an embedded product design based on an earlier process?

- ✓ Where is the existing trusted software in an embedded product design based on an earlier process?

We cannot use a distrusted hardware or software to test other hardware or software. We can use trusted hardware or software to test other hardware or software.

#### (2) Platform-Based Design methodology for embedded systems

Platform-Based Design methodology reduces time-to-market in terms of development time[17]. Examples are the TI OMAP platform for cellular phones, the Nexperia platforms for consumer electronics, the Intel Centrino platform for laptops. However, Business Week reported that Intel CEO Ottellini called those kind of companies are a "platform company" [18]. Many companies approach platform development simply as ABC(ad hoc, Bottom-up, and Core-centric) [17]. Alberto Sangiovanni-Vincentelli and Grant Martin (the authors) believe that Platform-Based Design is "top-down", "Bottom-up" and "meet-in-the- middle" [19]. Alberto Sangiovanni-Vincentelli and Grant Martin also believe that the embedded system design involves two essential components: a rigorous methodology for embedded software development and platform-based design[19]. Motorola's Silver and Green Oak, "develop a family of similar chips that differ in one or more components but are based on the same microprocessor" [19]. Such a chip family is also a platform[19].

The advantage of this method is that the time-to-market may be shorter because of using the platform. Also , because the system platforms may already be defined, what the designers need to do is just apply it[20]. However, one of the biggest disadvantages of this approach is that a platform gives the designer only limited choices [21]. This is because a different products have different functions different constraints. So, different architecture platforms may need to be applied. This is not difficult to understand.

#### (3) Hardware/Software Co-design

Traditional embedded system design develops hardware and software separately[22]. Many researchers are trying to develop and improve this Co-design approach[22] .This approach is to find out what the well-understood design problems are, and also what the unsolved design problems are, as well as the relationship between hardware and software in the early stages of embedded system design [23], because SW and HW shares resources in the embedded product [20].

However, to make a good design tradeoffs, the designer has to be knowledgeable in both hardware and software domains [23].

In other words, hardware/software co-design types to develop HW and SW of the embedded product dependently because of the dependence and interaction between hardware and software [24-27]. This is important because embedded products are becoming more and more complicated. Hardware and software rely more and more on each other [24-27].

Co-design may be good in some cases such as in the middle stage of the development process. However, it is important to ask:

- ✓ In the earlier stages of modern new embedded product design, no SW such as the boot loader is running, so where is the trusted software to co-design or test the HW?

- And, because it is co-designed, it has to start from the system-level specification.

However, system-level specification is often a variable and may be changed in the later design stage.

#### (4) Interface-Based Design

The central idea of Interface-Based Design is that different components can be connected only if their interfaces match. In other words, the other side of the interface does not have to know the details of the internals [28]. This approach requests that the output of one component be "compatible" with the input of the other component [28].

Similar to Interface-Based Design, Thomas and Luca de Alfaro purposed *component-based design*, they wanted each component to function in its environment and they wanted the designer to pay attention to the relations between those components by asking the following questions [29]:

- $\checkmark$  What does it do?

- ✓ And how can it be used [29] ?

#### (5) Model-based design

Model-based design methodology gives a designer a faster and more cost-effective design methodology for embedded system design [30] [31]. Due to the complicated development process for embedded system, it is helpful to develop a good model.

Model-Based Design allows you to improve efficiency by automatically generating embedded software code such as using C++ UML. However, it cannot guide a designer to solve all the design problems in terms of conflicts. And, it does not fit all your needs due to your different the design requirements.

Since embedded system started in the 1960's, embedded system design methodology [32] has summarized by Daniel D. Gajski, Samar Abdi, Andreas Gerstlauer and Gunar Schirner as follows:

(1) Capture-and-Simulate methodology (1960s to 1980s) [32]

At that time, hardware and software was separately developed and there was a gap between them[32]. Software designers tested some requirements and then gave those specifications to hardware designers [33]. It took many years for designers to realize that the specifications can be always updated from their implementation. This is called capture-and-simulate because the designer captures the design description often at the end of the design. And it is for simulation purposes only [32].

- (2) Describe-and-Synthesize methodology (the late 1980s to the late 1990s) [32]In the 1980s, because some development tools for logical synthesis were developed, both the behavior and the structure of designs could be captured [32].

- Therefore, in this methodology, behavior and function come first and then the structure or implementation follow [32, 33]. This methodology improved Capture-and-Simulate methodology [32]. However, today's embedded system designs[34] are sometimes too large for this methodology [32, 35]. Later, in the 1990s, Register-Transfer-Level (RTL) was introduced to embedded system engineering; however, the gap is still there because there was no relation between RTL and the higher system level [32].

- (3) Specify, Explore-and-Refine methodology (the early 2000s to 2010) [32] In order to close the gap between higher system level and RTL including HW and SW, Specify, Explore-and-Refine methodology was developed [32]. This methodology can be described as consisting of a sequence of models[22] in which each model is the refinement of previous ones [32].

# 2.4 Motivation of the EBD in embedded system design

We have discussed a good design in Section 2.1.4 as well as the criteria of an effective design methodology in 2.3, including advantages and disadvantages. We have found that all of those embedded system design methodologies are not for general purpose. With this objective, EBD is carried out for the application of embedded system design.

### **Chapter 3**

## APPLICATION OF EBD TO EMBEDDED PRODUCT DESIGN

With the background introduced in Chapter 1, the knowledge of embedded systems and a recommendation (or so-called definition) of a good design in Chapter 2, now in Chapter 3, will introduce:

- $\checkmark$  Why EBD is recommended to embedded system design

- $\checkmark$  How to apply EBD into an embedded system design.

Due to diversify of embedded systems from very simple to a complex embedded system, an example is used to show how to use EBD from general point of view. The example is an embedded ARM Linux system for natural rainfall and water levels control.

The detailed development is shown in the next chapter. In this Chapter the concept design is shown. The advantage of applying EBD will be shown in the next chapter by giving the detailed development.

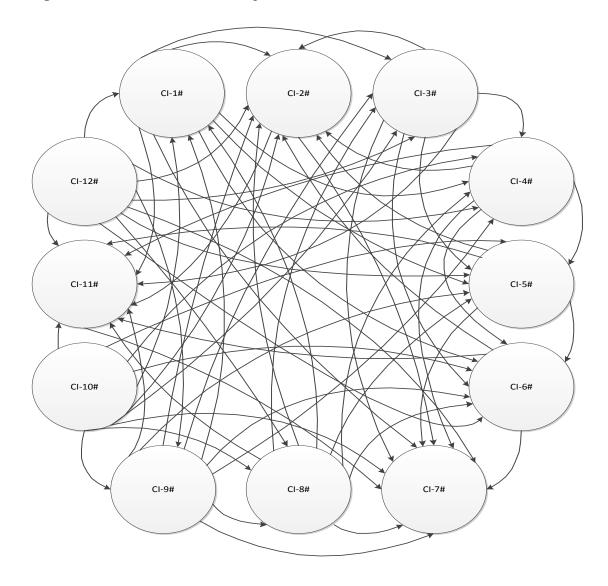

#### 3.1 Case study introduction

All of the whole systems shown in **Figure 6** are to track natural rainfall and water levels in local and nearby reservoirs (or rivers, or lakes). The purpose for the tracking is to avoid drought and flood disaster to local residents because of an excess of rain or a scarcity of rain. The function of the remote station (embedded system) shown in **Figure 6** from 1# to N+1 # below is to collect the data of rainfall and the level of water. After being dealt with by the system, the signals are sent by the network to the central station server shown in **Figure 6**.

Figure 6 The system

Where,

- ✓ Input of remote station are 1#, 2#, 3# and 4#

- $\checkmark$  Output of remote station is "Action" release water or/and send data to server

- ✓ Data process unit is the remote station (embedded system)

- ✓ Input 1 is rainfall

- ✓ Input 2 is water level

- ✓ Input 3 is water level back-up

- ✓ Input 4 is level of battery power

That remote station (embedded system) shown in **Figure 6** above is the one designed in the case study not only for this chapter for concept design as an application of EBD but also for the next chapter for the detailed development as a validation of EBD.

# **3.2 Overview: why EBD in an embedded system development**

Some embedded system developers, just like the author years ago, may think this way: do not talk about methodologies, just do the development. The author also thought this way years ago; however, debugging, testing, redesigning, verification and validation would take longer than expected.

To get started naturally, first understand why EBD can be applied to an embedded system development process.

First, an embedded product is a computing system for special purposes for special functions with a combination of HW and SW. It is an artificial system created by human beings with some constraints and it serves people. It has to exist in working nature following a life cycle. Therefore, the product cannot come into conflict with its working

environments going from nature to the built and human environments. For example, an aerospace sensor system (embedded system) works at a very low natural temperature and in a natural environment with a specific humidity, an environment which is different from the environments in which it was developed. So when developing it, these parameters have to be considered. When an embedded product targets the North American market, a 120V should be used whereas a 220V should be used if it is targeting the Chinese market.

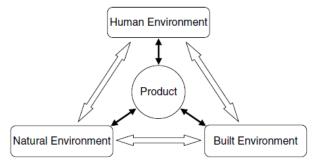

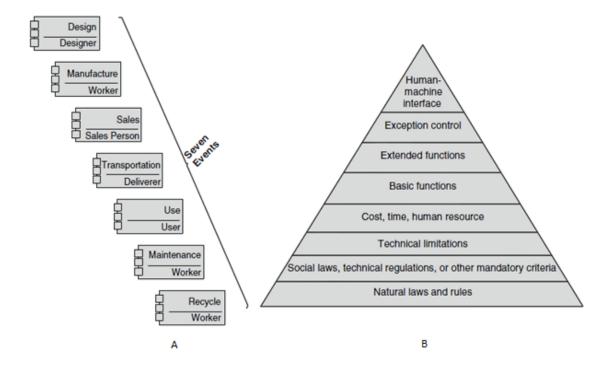

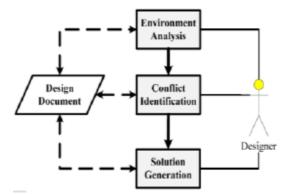

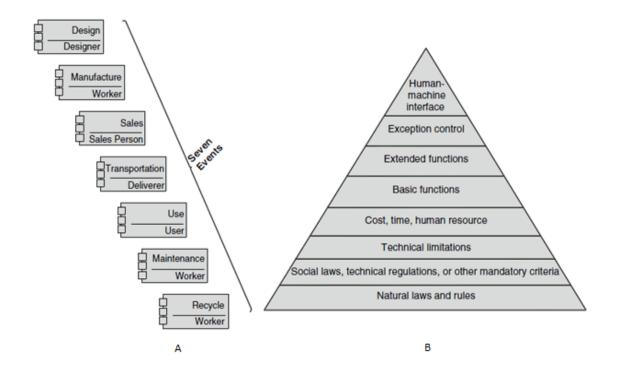

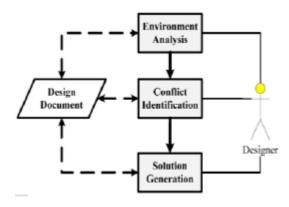

Then next, let us see what EBD states :1) there are three major product environments shown in **Figure 7** below [36]; 2) the classifications for the product environment can be divided into natural, built and human as shown in A of **Figure 8** below [37] or is based on the product life cycle shown in B of **Figure 8** below [37]; 3) the EBD process is composed of environment analysis, conflict identification and solution generation as shown in Figure 9 below [36].

Figure 7 Three major product environments [36]

Figure 8 Seven events & eight levels for design requirements [37]

Figure 9 EBD process model [36]

Now finally, let us come back to see how people usually solve a problem (embedded system development process):

- (1) Understand embedded system design problems

- (2) Analyzing embedded system design problems

- (3) Solving embedded system design problems

However, people often fail at the first step: understanding the design problems. Figure 10 shows how important it is to understand design requirements correctly.

a) How the customer explained it

b) How the project leader understood it c) How the analyst analyzed it

d) How the programmer wrote it e) What the customer really needed

## Figure 10 Illustration of problems existing in software product development [38]

According to Standish Group statistical data, only 16.2% of software projects are completed on time and within the budget. The website It-cortex concludes that only 1 out 5 IT projects is likely to bring full satisfaction and only 16.2% of software projects that are completed on-time and on-budget bring full satisfaction [38].

In the following section, a step-by-step guide is presented to show how to apply EBD to an embedded product design.

# 3.3 Understanding design problems: embedded product life cycle environment analysis

No matter whether you apply EBD to embedded system design or not, without doubt, *to understand what to do* is the first thing for a developer dealing with an embedded system design. According to EBD, the purpose of environment analysis is to understand design problems. In other words, the purpose is to understand design requirements early and in a right way by analyzing the product working environment in its life cycle from nature, to the built, human environment.

In embedded system engineering, design requirements or specifications are often verbally received from other design engineers or users. No matter what other design requirements are, they should finally be changed into technical design requirements. The developer will often then create code that handles the specifications. The author has learned from experience that development time is very often longer than expected because of testing, validating, debugging, redesigning, and redefining the design requirements.

Let us start with a simple embedded system design example to understand it. We start with a simple word to describe the objective of the expected embedded product according to the understanding of the concept.

## Objective:

*Objective 0: develop a machine to do something (verbally received embedded system design requirements).*

Very often, the objective for the design is given by someone who may know very little about computer systems or the real meaning of an embedded system. Or he/she does not have any knowledge of embedded system design. He/she just expresses this objective to professionals, asking generic questions.

### *Objective 1(transferred into technical design requirements):*

- (1) Develop embedded hardware;

- (2) and develop embedded software

- to initialize hardware components;

- to load binary images to target the board;

- to load images from a loading address to a running address;

- to manage electronic components;

- to boot up a system;

- to provide a service to the user;

- to provide distributed individual online updating features for some images.

This is a general development objective description for the remote station (the embedded system), shown in **Figure 6** above. To better understand design problems including hidden problems, the following general questions would be recommended in the next

section, namely Step 2.

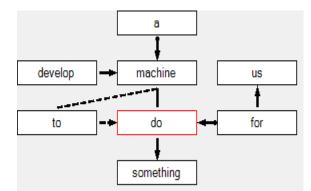

### Step 1: Create a ROM diagram from the initialized design/development objective.

Figure 11 Created first ROM diagram

This first ROM diagram shown above in **Figure 11** was created for the initialized design problem: verbally received embedded system design requirements.

We recommend generating a ROM from your answer rather than your questions because the purpose of generating a ROM is the following:

- ✓ To get what a user really needs by asking the right questions and collecting the right answers.

- $\checkmark$  To find the key components.

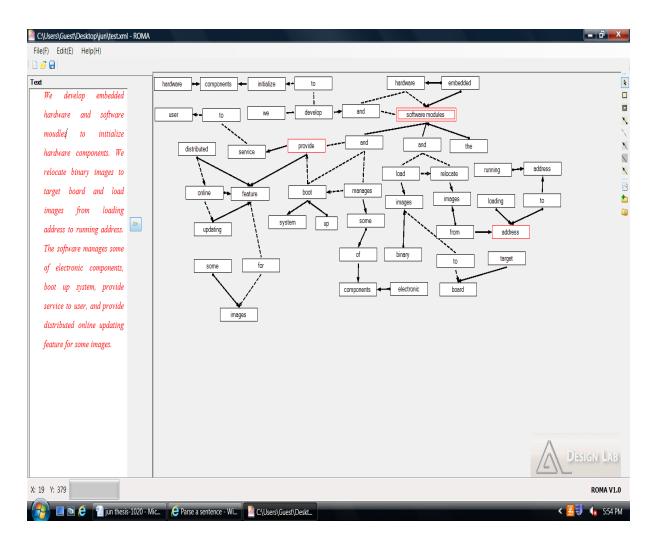

Having transferred the technical design requirements shown above from a natural language, we now create it in an updated ROM diagram (Figure 12).

Figure 12 Created first updated ROM diagram

**Figure 12** above was created first as an updated ROM diagram to initialize the design problem: having changed it into technical design requirements.

According to EBD (*rules for objects analysis*), for example, from ROM **Figure 11** above, we already know the key environment components - machine and something. The reason is that - for "machine", there is one constraint relationship and one predicate relation; for "something" there is one predicate relation and one connection relation. Similarly, in **Figure 12** ROM above, using Rules for object analysis according to EBD, you may have key environment components: an embedded system, hardware components, binary images, and images from a loading address to a running address, some electronic components, and the system, service and distributed online updating feature for each image.

Then taking the following steps, we ask the right generic questions and the specific questions. Professionals may ask better but fewer questions than non-professionals. However, non-professionals are still able to ask concept and preliminary design questions. For a detailed development, non-professionals may not be able to give the right answers in some cases.

# Step 2: Ask generic questions and collect answers and then repeat until no more generic questions can be asked.

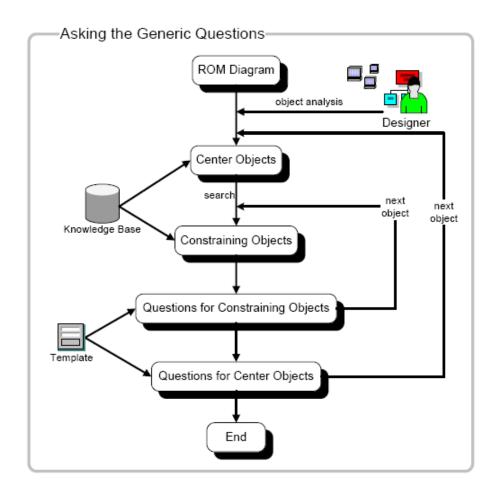

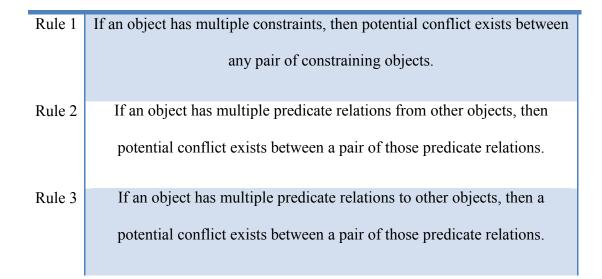

According to EBD, rules for generic questions shown in APPENDIX, as follows:

### Table 1 Rules for generic questions[39]

Rule 1

Before an object can be further defined, the objects constraining them should be defined.

**Rule 2** An object with the most undefined constraints should be taken care of

first.

From the ROM, we already know that the key or critical environment component is an embedded product (machine). This is not hard to understand: we should have a working computer system first and then do the rest. Therefore, the expected product should be a computer system first. Following the EBD (*Rules for objects analysis*), the following questions and answers for general embedded product generic questions are collected.

|             | Generic questions asking                                       |                           |

|-------------|----------------------------------------------------------------|---------------------------|

|             | Questions & Answers                                            | Stopping asking questions |

| develop     | Q1: Who develops it?                                           | Stop for now              |

|             | A1: professionals                                              |                           |

| (Who/how/   |                                                                |                           |

| what to +   | Q3: How to develop it?                                         |                           |

| object      | A3: ask professional embedded engineers.                       | Stop for now              |

| constrainin | They know how to parallel implement the system                 |                           |

| g N1)       | including its HW components and SW components                  |                           |

| A machine   | Q: What kind of machine?                                       |                           |

| (What +     | A: a computer system                                           | Stop for now:             |

| N1)         | Q: What kind of <b>computer system?</b>                        | because it is             |

|             | A: An embedded system                                          | clear that we             |

|             | Q: What kind of embedded system?                               | design an                 |

|             | A: an embedded product-a computer system with                  | embedded                  |

|             | specific function that it <b>does something</b> for humans. it | system.                   |

|             | is a combination of HW and SW.                                 |                           |

| Do          | Q6: Who <b>does</b> something?                                 | Stop for now:             |

|             | A6:This artificial embedded computer system does               | because Low-              |

| (           | something intelligently                                        | Level                     |

| Who/How     | Q17: What does the <b>artificial</b> mean?                     | embedded SW               |

| + object    | A15: It means it is made by humans and has                     | design                    |

| constrainin | constraints and is not perfect                                 | requirements              |

| g N2)       | Q7: What to <b>do</b> ?                                        | would be clear            |

|             | A7: the embedded product does <b>something</b>                 | from the A16              |

|             | Q8: How to <b>do</b> something?                                | sequence                  |

|             | A8: the embedded product <b>intelligently knows how</b>        |                           |

Table 2 Generic domain questions and answers

|                            | to do something and what to do.<br>(Once powered up, it can do what human products can<br>do for humans)<br>Q18: How to do it intelligently?<br>A16: developers design a number of SW modules<br>telling it what to do by following a certain sequence :<br>Power up<br><i>Example of an additional question: how to power up</i><br><i>the system? How to code it?</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                            | Run Boot loader<br>Example of additional questions: how/where to run<br>boot loader?<br>Load kernel to running address<br>Example of additional question: how/where to load?<br>Run kernel<br>Example of an additional question: how/where to run?<br>Find ROOTFS and then run applications<br>Example of additional question: how/where to find                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

| Something<br>(What<br>+N2) | <i>and run it?</i><br>Q9: What is the <b>something</b> ?<br>A9: something means <b>the specific function of the</b><br><b>system</b><br>Something means this product is a computer system<br>with specific functions instead of a computer system<br>with a general function, and it knows what /how to do.<br>In another words, humans wanted the artificial<br>embedded computer system to perform <b>something</b> for<br>humans <b>intelligently</b> . From the technical point of<br>view, it is the job of the <b>applications</b> to perform this.<br><b>What specific function</b> ?<br>A14: <b>special function</b> means it executea a specific<br>code and is able to do <b>this</b> and/or <b>that</b> as the <b>user</b><br><b>requires</b> .This and that in here is what you want this<br>product to do. | Stop for now:<br>because what<br>high level<br>applications<br>needed would<br>be clear for now |

With answers collected by asking the generic domain questions, in order to ask more right question after this stage, you should update a ROM diagram from the generic domain answers. At this point, do not update this ROM because the goal in the present paper is just to show the concept of applying EBD to an embedded system design.

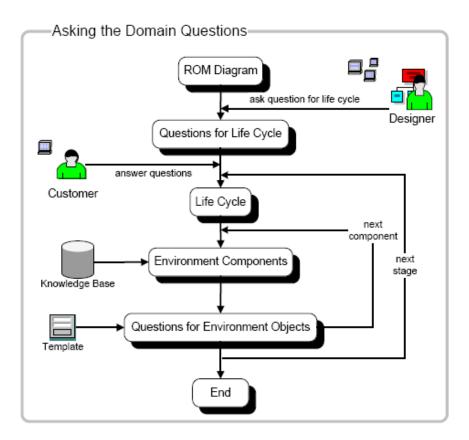

# Step 3: Ask specific domain questions and collect answers and then repeat until no more generic questions can be asked.

This stage is to get the detailed design requirements. According to EBD (Rules for asking domain specific questions[39], as discussed in the last section, to get detailed design requirements, we should understand that:

1. The product design requirements should be analyzed at each event in its life cycle[37]

In a different embedded product design such as different devices design, its life cycle may encounter different events. For example, you may divide your product life=cycle events into design /development, test and debug, software=based HW components testing for manufacturing, manufacturing, sale, transportation, use, maintenance and recycling. **Figure 13**, which follows, is just an example.

Figure 13 Seven events & eight levels of requirements-AB[19]

2. The priority of consideration from high to low is: nature, built to human [19]

Due to the large variety of embedded systems, there is also a large variety of specific design requirements in terms of specific domain questions and answers. It is not possible to provide the detailed conflicts for all the embedded systems in general. However, the following questions are recommended at this stage:

| specific questions asking                                       |                 |

|-----------------------------------------------------------------|-----------------|

| recommend questions                                             | example Answers |

| 1, what system components do you need in terms of HW and SW?    | System          |

| 1.1 What HW components?                                         | components(HW   |

| 1.1.1: What CPU? Why this CPU? What is CPU chip cost including  | components and  |

| other related HW components such as peripherals? Why MMU/why no | SW components)  |

| MMU?                                                            | determination   |

|                                                                 | would be clear  |

| CPU- The expected answer may be one from PowerPC, ARM, Intel,   |                 |

Table 3 Specific domain questions and answers example using ROM

| 1.4 Do we need to develop a ROOTFS or can we use open source?<br>Ex: Why yes?<br>Why not?                                                                                                                                                                                                                                                                                                                   | design<br>requirements<br>would be clear for          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| <ul> <li>1.3 Develop Boot Loader or use existing open source?</li> <li>Ex: Why develop it u-boot?</li> <li>1.3.1 If the OS may be updated into another OS in the future, can your loader be applied?</li> <li>1.3.2 Development cost?</li> <li>1.3.3 Open source cost for Boot Loader?</li> <li>1.3.4 What perimeter to transfer to kernel if using u-boot?</li> <li>1.3.5 What size limitation?</li> </ul> | design<br>requirements<br>would be clear for<br>now   |

| Mostly we use OS but some outdated simple systems do not. You may<br>have more questions like: Why do we need an OS and why not?                                                                                                                                                                                                                                                                            |                                                       |

| <ul><li>1.2.3What modules do we need to develop?</li><li>1.2.4 What interface do we have or need?</li><li>1.2.5 What drivers do we need?</li><li>1.2.6 Do we need a real time operating system (RTOS)?</li><li>1.2.7 Do we really need operating system OS or no OS?</li></ul>                                                                                                                              |                                                       |

| 1.2.2 What version?<br>Possible answers are Linux 2.4, 2.6 and so on.                                                                                                                                                                                                                                                                                                                                       |                                                       |

| 1.2.1The cost of the OS in terms of the related SW module including drivers and so on?                                                                                                                                                                                                                                                                                                                      |                                                       |

| The expected answer may be Linux, Windows CE, VXWORKS, and android and so on.                                                                                                                                                                                                                                                                                                                               | system and drivers<br>needed would be<br>use is clear |

| 1.2 What operating system do we need?                                                                                                                                                                                                                                                                                                                                                                       | What operating                                        |

| <ul> <li>1.2 What SW components?</li> <li>1.2.1 What SW images? Elf or Bin?</li> <li>1.2.2 What Boot Loader image? U-boot? Grub?</li> <li>1.2.3 What kernel image? BZIMAGE or other?</li> <li>1.2.4 What ROOTFS image? CRAMFS, ext2?</li> <li>1.2.5 What applications? Video player or what?</li> <li>1.2.6 What restrictions on the SW and so on?</li> </ul>                                               |                                                       |

| 1.1.3 What peripherals? What network? Blue tooth? GPS? What drivers?                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 1.1.2: What memory? What size? SRAM size and expected images footprint? SDRAM size and expected images footprint? What flash? No flash? NAND flash? SD card? EEPROM? Why this flash? What type? Size? Or flash with XIP?                                                                                                                                                                                    |                                                       |

| AMD, MIPS, M68k, COLDFIRE, AVR, M32C, PIC, RL78, SHARC, SPARC, ST6, MCS-51 etc.                                                                                                                                                                                                                                                                                                                             |                                                       |

|                                                                        | now                |

|------------------------------------------------------------------------|--------------------|

| 1.5 What applications do we need?                                      | design             |

|                                                                        | requirements       |

|                                                                        | would be clear for |

|                                                                        | now                |

| 1.6 How to boot up the system?                                         | Boot up app would  |

| 1.6.1 How to power up the system?                                      | be clear           |

| 1.6.2 Push a button or not?                                            |                    |

| 1.6.3 Execute specific code from CPU specific offset?                  |                    |

| 1.6.4 How to run boot loader?                                          |                    |

| 1.6.5 Which memory location will execute which specific program?       |                    |

| 1.6.6 How to load kernel to running address?                           |                    |

| 1.6.7 Where is the running address for xx image?                       |                    |

| 1.6.8 Where is loading address for xxx image?                          |                    |

| 1.6.9 If bad block in loading address of flash, what to do?            |                    |

| 1.6.10 How to run kernel?                                              |                    |

| 1.6.11 How to run applications?                                        |                    |

| 1.7What is the life cycle of the embedded product?                     | Design             |

|                                                                        | requirements       |

|                                                                        | would be from life |

|                                                                        | cycle of the       |

|                                                                        | product            |

| 1.8What are constraints for each event of the product life cycle?      |                    |

| 1.9What constraints for the system?                                    | What constraints   |

|                                                                        | would be clear     |

| Example: Will a radiation environment affect the system's functioning? |                    |

| other constraints                                                      |                    |

|                                                                        |                    |

We stop to ask questions once the design requirements are clear. We do not give a detailed answer because of the large variety of embedded systems. For example, in embedded product development, it may not be possible to use open source and therefore the boot loader will have to be customized. Then you will have your own answer. There would be more detailed questions asked in the specific questions stage according to your product. At this point, it is enough to just show a general process of how to apply an EBD to the embedded product design process. So far, by asking specific domain questions, the HW components should be determined to use, including CPU and memory, for the remote station system. We also have embedded remote station system SW components determination including OS, file system, loaders, and applications and so on. In addition, we have low level embedded remote station system SW design requirements. Next, it is time to do the HW development and the SW coding. At this point, you should also have an updated ROM from your answers. We do not refer to an updated ROM for asking specific domain questions because of the large variety of embedded systems.

According to EBD, the following **Table 4** is recommended to determine the design requirements including hidden design requirements in the product life cycle (from Event #1# to Event #n#), for example, in the following **Table 4**, conflicts and constraints.

| Table 4 Lifecycle analysis of the embedded product design problem- specific domain | n |  |  |  |

|------------------------------------------------------------------------------------|---|--|--|--|

| questions                                                                          |   |  |  |  |

| Events<br>in life<br>cycle of<br>embedde<br>d<br>product | embedded<br>product<br>nature<br>environme<br>nt in life<br>cycle | Your<br>embedded product<br>built environment<br>in life cycle          |                                  |                                         |                        | embed<br>human                | Your<br>ded produ<br>environm<br>life cycle |                               |

|----------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|-----------------------------------------|------------------------|-------------------------------|---------------------------------------------|-------------------------------|

|                                                          | Nature<br>law and<br>rules                                        | Social<br>law,<br>technical<br>regulatio<br>ns, or<br>other<br>criteria | Technic<br>al<br>limitatio<br>ns | Cost,<br>time,<br>human<br>resourc<br>e | Basic<br>functio<br>ns | Exten<br>ded<br>functi<br>ons | Except<br>ion<br>control                    | Human<br>machine<br>interface |

| Event 1#                                                 | E1N1<br>Constraint<br>s 1N1                                       | E1B1<br>Constraints 1B1                                                 |                                  |                                         |                        |                               | E1H1<br>traints 1H                          | I                             |