# MINICOMPUTER BASED MICROPROCESSOR DEVELOPMENT SYSTEMS

Richard Moses

A Thesis

in

The Department

of

Electrical Engineering

Presented in Partial Fulfillment of the Requirements for the degree of Master of Engineering at Concordia University Montreal, Quebec, Canada

August, 1979

© Richard Moses, 1979

### **ABSTRACT**

# MINICOMPUTER BASED MICROPROCESSOR DEVELOPMENT SYSTEMS

### Richard Moses

Tailoring ones own development system for microprocessor applications provides an alternative to purchasing an existing system. With the aid of a minicomputer, a system may be configured to the requirments

of the user while staying in the cost boundaries of

what would be required for investing in an off-theshelf system. The main feature is that the system is

adaptable to any microprocessor family and may be upgraded as technology advances.

Such a system has been developed at the microprocessor applications laboratory as part of the Department of Electrical Engineering at Concordia University. Configured around a DEC PDP 11/45 minicomputer the system has been applied to the RCA CDP1802 microprocessor.

The 1802 microprocessor along with 1Kbytes of

memory is incorporated into a single board microcomputer module. During prototype development the microcomputer module is linked through an extender cable to the microprocessor development system via a custom designed hardware interface. Using RT-11 software, system and application programs written in RCA microprocessor assembly language are editted, assembled linked and executed by the PDP 11/45 minicomputer.

### **ACKNOWLEDGEMENTS**

The author acknowledges his indebtedness to J.Kishon and R.Beyar for their kindness in offering their opinions and technical assistance throughout the research development. In addition, acknowlegement is due to to S.A.Gracovetsky whose influence as an educator and a leader will always be remembered, as well as V.Ramachandran who contributed time and ideas for the generation of the thesis. The research described here was supported in part by the National Research Council of Canada under contract number 1560. Finally credit is also due to AES Data. Ltd for supplying the facilities and materials for the preparation of the manuscript.

## CONTENTS

|                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                    |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| ABSTRACT                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii                                     |

| ACKNOWLEDGEMENTS                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                                       |

| LIST OF FIGURES                                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ×                                       |

| LIST OF TABLES                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xii                                     |

| SYMBOLS AND ABREVIATIONS                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xiii                                    |

| CHAPTER 1                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | * · · · · · · · · · · · · · · · · · · · |

| THE NEED FOR MICROPROCESSOR DEVELOPMENT TOOLS    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |

| 1.1 Introduction 1.2 Present Microprocessor      | , and the second | 3                                       |

| Development Aids  1.3 Microprocessor Development |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| Systems                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ¥                                       |

|                                       | ~              | ,   | Page        |

|---------------------------------------|----------------|-----|-------------|

| CHAPTER 2                             |                |     | į           |

| AN ALTERNATIVE APPROACH TO THE DESIGN | OF             | •   | . ,4        |

| A, MICROPROCESSOR DEVELOPMENT SYSTEM  | · ·            |     | τ,          |

| 2.1 Using Minicomputers for           | ,              | •   | 12          |

| Microprocessor System                 | ,              |     | •           |

| Development                           |                |     |             |

| 2.2 Scope of Thesis                   |                |     | 18          |

|                                       |                | 1   |             |

|                                       | ή <sub>ε</sub> | ·   |             |

| CHAPTER 3.                            |                | •   |             |

| THE HARDWARE                          | •              |     | ,           |

| 3.1 Introduction                      | • .            | . 1 | 22          |

| 3.2 The DR-11C                        |                | •   | 24          |

| 3.3 The Controller                    | •              |     | 26          |

| 3.4 The RCA CDP 1802 Microprocessor   |                | • . | 31          |

| 3.5 CPU Module                        |                | •   | 36.         |

| 3.6 Monitor Module                    | ,              | •   | 49          |

| 3.7 Summary                           |                |     | <b>65</b> ` |

|                         | . !        |      | Page |

|-------------------------|------------|------|------|

| CHAPTER 4               |            |      |      |

| SOFTWARE DESCRIPTION    | •          | ·    | •    |

| 4.1 Introduction        |            |      | 66   |

| 4.2 DR-11C Parallel I/  | 'o · `     |      | 67   |

| 4.3 Dat Address Multi   | plexing.   | •    | 69   |

| 4.4 8255 Initializatio  | on .       |      | 70   |

| 4.5 Microprocessor Mod  | le Control | · Fr | 71   |

| 4.6 Program Loading     | .          |      | . 72 |

| 4.7 Single Stepping     | i          |      | 75   |

| 4.8 Input Ports         | •          | •    | 76   |

| 4.9 Summary             | ļ          |      | 78   |

| CHAPTER 5               |            |      | •    |

| SYSTEM · IMPLEMENTATION |            | , .  | •    |

| 5.1 Introduction        | •          |      | 79   |

| 5.2 Design Target       |            | ,    | 80   |

| 5.3 Development System  | Software   | · ·  | . 81 |

| 5.4 Summary             |            |      | 87   |

|             |          | •   |   |          | ,          |     | Page |

|-------------|----------|-----|---|----------|------------|-----|------|

| CHAPTER 6   | *        |     |   |          | <b>o</b> , |     | •    |

| CONCLUSIONS |          |     |   |          |            | ' , | 88   |

| REFERENCES  | /        | -   | , |          | •          |     | 90   |

| /           | <i>.</i> |     |   | <b>₽</b> | ,          |     |      |

| APPENDIX /  |          | • ' |   | •        | •          |     | 93   |

### LIST OF FIGURES

| 'Figure | Title                           | , P | age |

|---------|---------------------------------|-----|-----|

| 1.1     | Spectrum of microprocessor      | ۶   | 4   |

|         | development aids.               |     |     |

| 1.2     | Parallel hardware and soft-     | •   | 10  |

| •       | ware development.               | . 1 |     |

|         |                                 |     |     |

| 2.1     | System configuration            |     | 20  |

|         |                                 | 1   |     |

| 3.1     | The DR-11C general purpopse     | ,   | 24  |

|         | interface.                      | •   |     |

|         |                                 |     |     |

| 3.2     | Controller address byte format. | _   | 28  |

| 3.3     | Range of processor chips and    | ,   | .32 |

| *       | application domains.            |     |     |

| •       |                                 |     |     |

| 3.4     | RCA 1802 microprocessor         |     | 35  |

| a :     | architecture.                   | . • |     |

| Figure       | . Title                       | Page         |

|--------------|-------------------------------|--------------|

| ;<br>2       |                               | 3<br>16<br>8 |

| 3.5 -        | CPU module block diagram.     | 37           |

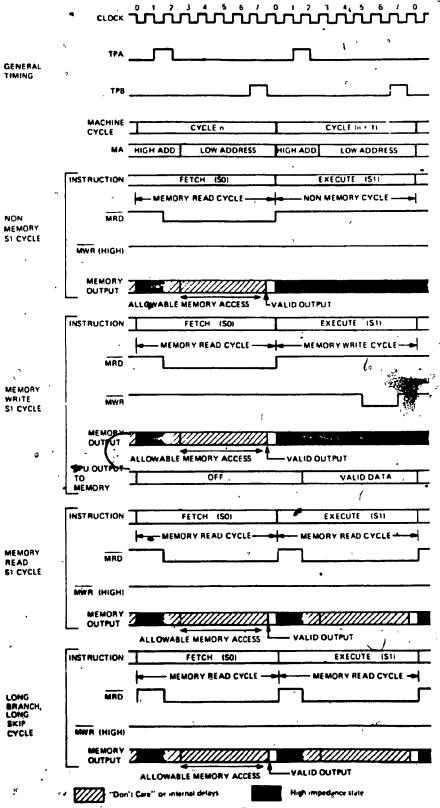

| 3.6          | 1802 timing waveforms.        | 39           |

|              | \n' \                         |              |

| 3.7          | 1802 signal descriptions.     | 4.7°         |

| 3.8          | Softwarte controlled transfer | , 50         |

| <b>4</b>     | of data and control via       |              |

| ,            | Monitor module.               | ¢            |

| •            |                               |              |

| 3.9          | 8255 mode configuration.      | 52           |

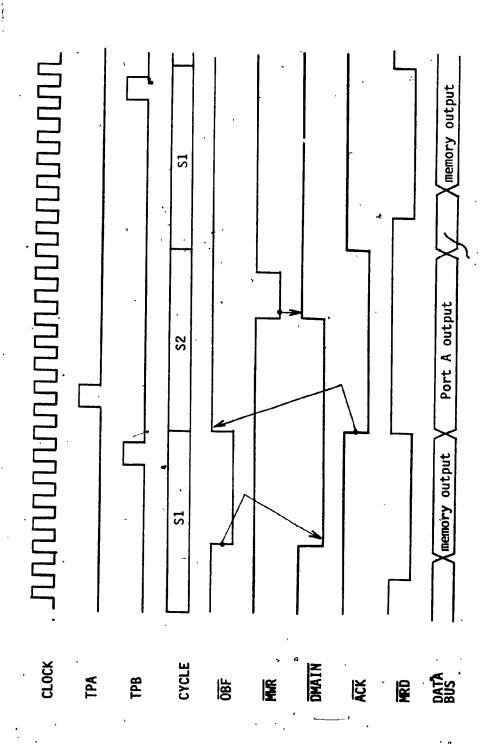

| 3.10         | Program loading timing        | 61           |

| ,            | waveforms.                    | `            |

| ,            |                               | •            |

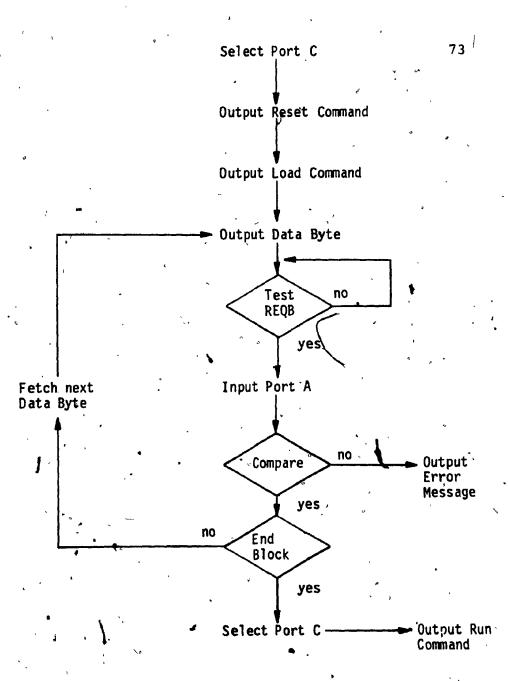

| 4.1          | Program loading flow chart.   | 73           |

|              | <b>9</b>                      |              |

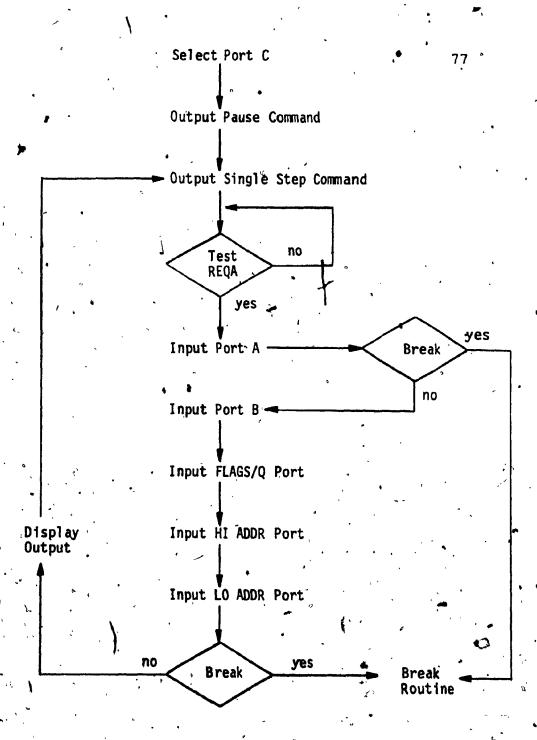

| <b>4.2</b> 0 | Single stepping, break point. | 77           |

|              | search flow chart.            |              |

### LIST OF TABLES

| Table, T | Title                      | Pag |

|----------|----------------------------|-----|

| 2.1      | Approximate minimal system | 1   |

| * <      | price lists.               |     |

| 3.1      | CSRO CSR1 truth table.     | 3(  |

| 3.2      | Monitor module address man | 5,5 |

### SYMBOLS AND ABREVEATIONS.

In Circuit Emulation ICE Programable Read Only Memory PROM Random Access Memory RAM Digital Equipment Corporation DEC 1/0 Input/Output Printed Circuit PC . Central Processing Unit CPÙ Vofts Amps cmos Complementary Metal Oxide Semiconductor Integrated Circuit IC Silicon On .Saphire sos • MHz Megahertz Kbytes 1024 bytes microseconds us nanoseconds ns Read/Write R°/W Most Significant Bit MSB

Direct Memory Access . DMA Transistor Transistor Logic -TTĻ no-op no opération Large Scale Integration LSI Programable Peripheral · PPI Interface CRT Cathode Ray Tube A/D Analog to Digital D/A-Digital to Analog

### CHAPTER 1

### THE NEED FOR MICROPROCESSOR DEVELOPMENT TOOLS

### 1.1 INTRODUCTION

The complexity of systems have dictated the use of digital computers for computational and decision making processes in a real time environment. In this respect the advent of the minicomputer offered designers an extensive range of hardware and software capabilities to a wide range of engineering applications. With advancing technology the minicomputer had become more efficient in terms of operation and costs to the point where they gained a relevant popularity in all engineering disciplines.

The evolution of microprocessor technology from an applications point of view came as an extension of the minicomputer to a wider and less costly area of implementation, thus the adaptation to microcomputers from minicomputers is natural. Furthermore the coalition of the two systems, both having similar foundations may be advantageous; such as distributed processing and microprocessor development systems.

Microprocessors are displaying performance capabilities previously matched by TTL and minicomputer dėsigns. The results have been a wave of product realizations with greater cost effectiveness and complexity. Future generations of microprocessors, single component microcomputers, memories and per- . ipherals will ultimately push performance and lower components costs. However the key problem that will remain in configuring microprocessor systems will be the generation of software and in particular its integration with the system hardware. First genteration designs were commonly plagued by lengthly development times and insufficient testing capabilities. Albeit a radical transition from traditional TTL designs, new development tools become a neccessity for any microprocessor based application. The effectiveness of producing a viable product will depend on the efficiency of development as well as manufacture and service.

### 1.2 PRESENT MICROPROCESSOR DEVELOPMENT AIDS

The intent of any microprocessor development aid is for the simplification of a particular segment of the software and hardware design. Various aids are offered by several manufacturers so that microprocessors would be more accessable and usable by a prospective user. Available in several packages these items range in complexity; they include parts families, single board computers, hardware development aides, in circuit emulators and full development systems.

In choosing one of these packages for designing a specific microprocessor application the user need consider the following; the complexity of the design in terms of hardware and software, the amount of hardware and software interaction, the amount of testing required and the flexibility of the package for future use. A brief look at the contemporary spectrum of devices might give some insight to the requirements of a general purpose development system. A detailed description of these devices may be found in (3).

A generalized range of development tools presently offered is depicted in Figure 1.1. Due to the interactive hardware and software nature of microprocessor

# SPECTRUM OF MICROPROCESSOR DEVELOPMENT AIDS

| e                                                                            | ANALIZEKS IN CIKCUII EMULATORS  |

|------------------------------------------------------------------------------|---------------------------------|

| ŠĻ                                                                           | isplay single step              |

| break points<br>register and<br>memory display<br>alter register<br>contents | . register memory di .alter reg |

Figure 1.1

SOFTWARE

HARDWARE

A wide range of microprocessor development aids are currently available, Due to the interactive nature of the hardware and software, these aids vary from circuit testing instruments to time sharing computer programs. systems, it is not surprising that the scope of aids range from time-sharing and minicomputer systems to hardware sequential devices. The extreme left of the spectrum represents hardware support for pulse tracing and static state testing. This equipment such as various oscilloscopes and logic testers which normally would be present in most research labs, are particularly useful for debugging specific logic functions once a problem has been pin-pointed. However for the tracing of software flow in conjuction with monitoring line activity, the use of these instruments is unpractical.

As an extension of the oscilloscope, logic state analyzers allowing multichannel synchronous observation of bus lines, have been aimed for use with microprocessor systems. Multiple display formats (binary, hex,octal, voltage levels) and storage capabilities, allow the user to follow a particular segment of program flow and line activity in real time. These instruments are rather sophisticated and are only useful for testing and debugging logical functions and program segments. Although these devices are adaptable to any microprocessor or logic system they are nevertheless

expensive.

Development tools intended for the use for a particular CPU include a range of microprocessor analyzers and In-Circuit-Emulators(ICE). Resh systems allow the monitoring of program flow, displaying instructions, addresses, and logical states for handshake lines or other external logic. Extra features may include observation and alteration of memory and register contents, setting of break points, and system capabilites for more than one make of micrprocessor.A desirable characteristic of these systems is that they provide the user an easy to use push button instrument, allowing the designer to concentrate on the applica-The main drawback, howtion software and hardware. ever is that the devices are unpractical for developing complicated software, and adaptability to a certain microprocessor family is dependant on the "personality modules" offered by the instrument manufacturer.

At the extreme software end of the spectrum are the time-sharing systems run on a host computer. Using cross assemblers, software development for a specific microprocessor is backed by the full software support of the host computer, i.e. editors, assemblers, link-

ers, high level languages such as FORTRAN, etc. In some cases time-sharing may be advantageous in that it may support several programmers working in parallel. However, the use of time-sharing systems is particularly useful for developing static software-i.e., program variables are time independant. Debugging of real time functions may be achieved through the use of of software simulators, however their performance only seconds real time execution and monitoring. Furthermore the need for simulators is unneccessary if ICE capabilities are existant.

The requirements for a general purpose user orientated development system falls towards the middle of the spectrum which is highlighted by the microcomputer/ICE systems. Their area of application is aimed at hardware and software devlopment and test.

### 1.3 MICROPROCESSOR DEVELOPMENT SYSTEMS

The microprocessor development system has evolved to be a valuable tool in the design of any microprocessor based application. Microcomputer system designers have witnessed the growth of available systems over the last several years, when Intel introduced the first microcomputer development system for its 8080 family. Indeed development systems now exist for all established microcomputer families supplied both by the major manufacturers of these lines and by independent instrument manufacturers. Naming a few, development systems are available in various formats from Intel, Zilog, Motorola, RCA, TI, Rockwell, Signetics and Tektronix.

There exist two basic modes in which these development systems may be utilized. The first method entails using the development system for software development. Once the software has been been developed and optimized the neccessary hardware design is implemented into the final realization. The second method involves the simultaneous development of both software and hardware requirements using the develop-

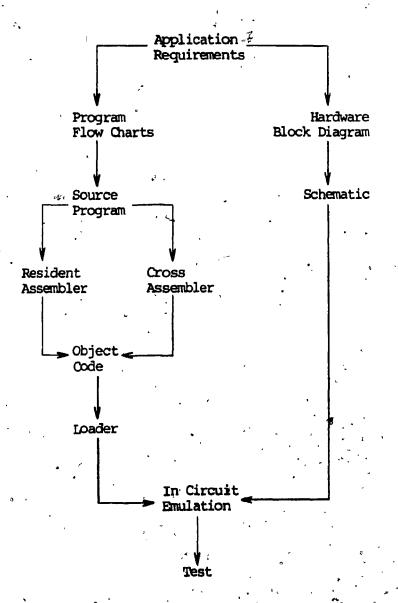

ment system for diagnosis and control. For applications characterized by smaller or less sophisticated systems where there is not a considerable amount of interaction between the software and hardware, the first method is adequate. However, for more complicated designs the user is apt to conform to the second method requiring an interactive develpment system. A emeralized format for implementing such a system for ( specific application is depicted in Figure 1:2. Once the functional requirements of the design have been defined, software and hardware development (including some intermediate testing) máy proceed in parallel. Program development incorporates the system's software support which would normally include a resident assembler, editor, and a reasonable amount of RAM with perhaps a floppy disc operating system. An overview may be found in (2). In circuit emulation [ (ICE) is particularily useful for debugging software and testing software and hardware interactions.

At the present stage of development, various firms offer their own respective family of devices so that no two microprocessors are completely compatible with each other. Although such versatility in architecture and languages offers the user a wide range of

Figure 1.2 Parallel hardware and software development for a specific application. Not indicated is the feedback process for discovering errors at the different stages.

devices to best suit the need, it poses problems to those who wish to configure systems around more than one brand of microprocessor. Thus with the aquirement of a dedicated development system, the designer is committed to a particular make of microprocessor. In terms of financial resources, resorting to numerous development systems for several microprocessors is highly unpractical.

Manufacturers have been aware of this problem and their response signifies the labest trend, which offers optional personality modules for use with various processors. These personality modules usually take the form of hardware interfaces and cross assemblers for adapting the sytem to a number of microprocessor devices. A good example of such a system is that offered by Tektronix which has the capability of supporting the 8080, 8085, 2-80 and 6800 microprocessors. Although these systems are an improvement over dedicated systems they are nevertheless quite expensive, usually in the \$15,000-\$20,000 bracket.

### CHAPTER 2

# AN ALTERNATIVE APPROACH TO THE DESIGN OF A MICROPROCESSOR DEVELOPMENT SYSTEM

# 2.1 USING MINICOMPUTERS FOR MICROPROCESSORS SYSTEM DEVELOPMENT

If the aids provided for a specific system are unsatisfactory the alternative remains to design ones own personal system. The procurment of a development system around a minicomputer entails the design of hardware interfaces and the writing of the development system software. The initial design time before the system becomes operable, is an important factor to be considered when adopting the building rather than buying approach. The choice will depend to some extent on the availability and experience of the personel required for the project. The minimum requirement would probably include a reasonable amount of knowledge interogramming and Mardware logical design.

The initial cost outlay for a minicomputer and additional hardware falls within the ball park range of what would be expected for investment into an ex-

isting system. Recently, minicomputer manufacturers have offered systems for lower end applications at lower costs yet maintain system compatability with the family line. As an example the acquisition of a PDP 11/03 system carries the full software support of the 11 family of minicomputers as well as a host of peripherals. All told a suitable system, as indicated in Table 1 could be purchased for approximately \$15,000.

. Considerable cost savings could be achieved if an existing minicomputer is already available, as is the case with many groups entering the field of micrprocessor design. The concept of developing microprocessor software on a host computer has existed now for a number of years and is well documented in the literature(1,4,5,6,12). Using the minicomputer software capabilities (e.g. MACRO 11 Assembler) such development should pose no real problem to designer who has some experience in assembler programming. implementing the hecessary hardware, microprocessor manufacturers usually provide a generous amount of information on the device operation, interfacing as well as applications. .. Furthermore, the interfacing of the device into the overall development system provides the designer with experience that is useful

| ITEM                 | PRICE    |

|----------------------|----------|

| "naked" Minicomputer | \$3,000  |

| . Cartridge Disk     | \$8,000  |

| CRT terminal         | .\$1,000 |

| Line Printer         | \$1,000  |

| Interfaces           | \$2,000  |

|                      | ۹        |

| TOTAL                | \$15,000 |

Table 2.1 Approximate minimal system price list

later on when an actual application is in mind.

In summary, although the approach to such a design involves the extra effort until the development system becomes on-line, the solution for a flexible and efficient system pays off in the long run. The intent of the design goes beyond the notion of simply building and running an operational system but also keeps the following objectives in mind.

FLEXIBILITY—the flexibility of the system configuration makes it adaptable to any current microprocessor device; thus the system is upgradable as technology produces enhanced devices. Functional modules could further be annexed such as PROM programmers and a monitor memory for use in real time in circuit monitoring, as demonstrated in (11). The master-slave concept may be extended for multiprocessor development (i.e. each microprocessor defined by its own hardware and software modules) as well as time sharing capabilities. These ideas are important considerations for implementing the system in an educational environment as proposed in (10).

SOFTWARE SUPPORT-the extent of the minicomputer software support exceeds that of present day development systems. Granted existing systems have been aimed at a specific application, but on a per dollar basis the minicomputer operating system offers a more flexible and proficient software package.

The operating system is incorporated for the development of system and application programming. Higher level languages may find their use in the construction of handlers, monitors etc. Editors and assemblers are manipulated for application software development. The file management system offers complete storage and referencing capabilities for all files. The extension of the software support allows various functions such as a foreground/background monitor for time-sharing and multiprocessor applications. Naturally the minicomputer could be incorporated in numerous other domains as well, so that the system is not tied down only to microprocessor development.

SPEED—the interactive nature of the minicomputer CPU and disk controller allows for fast assembly of the source application program. During software development, modifications to the microprocessor source program is achieved through editting and reassembly. The inherent speed of the system thus avoids the programmer being subjected to lengthy assembly times and

probable frustrations.

EASE OF OPERATION—the complete sytems serves as a valuable tool for microprocessor applications. The prospective user need not be concerned with the operation of the system but on how to manipulate it for a given application. Eventually the user would require a minimal knowledge of the system editor as well as basic protocol for assembly loading and monitoring. Complete activity may be channelled via standard CRT terminal offering visual push button interaction between the user and system.

### 2.2 SCOPE OF THESIS

The thesis presented herein concerns itself with one possible implementation of a minicomputer based microprocessor development system. Specifically our discussion will revolve around a PDP 11/45 minicomputer and the RCA 1802 microprocessor. By delving into the global operation and detailed hardware and software aspects of the design, an overall appreciation of the system organization as well as a funtional description of the various elements are supplied.

Presently the laboratory at Concordia incorporates a PDP 11/45 minicomputer with refresh graphics terminial, Decwriter, two RK05 disk drives, and line printer. For a number of years the computing system had been involved in several analytical as well as real time applications. Considering the advantages of using a minicomputer as a microprocessor development tool, the incorporation of the 11/45 was for us at least the most direct and economical approach. However, since the 11 family is software compatible down the line, the system is adaptable to any member of the PDP 11 family.

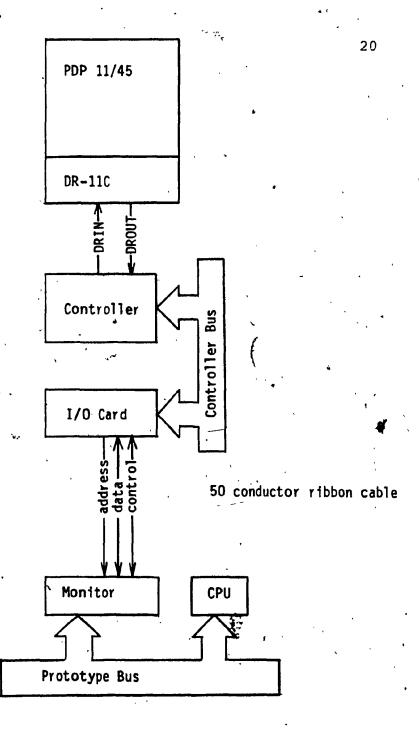

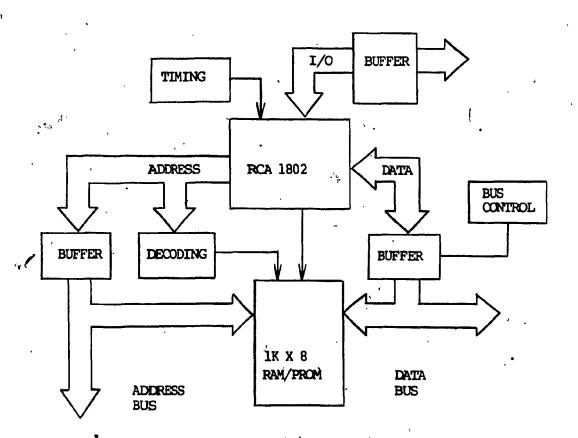

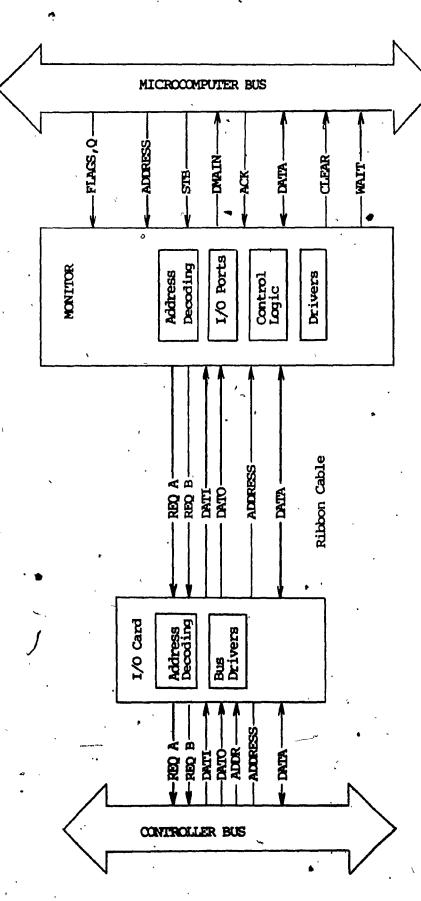

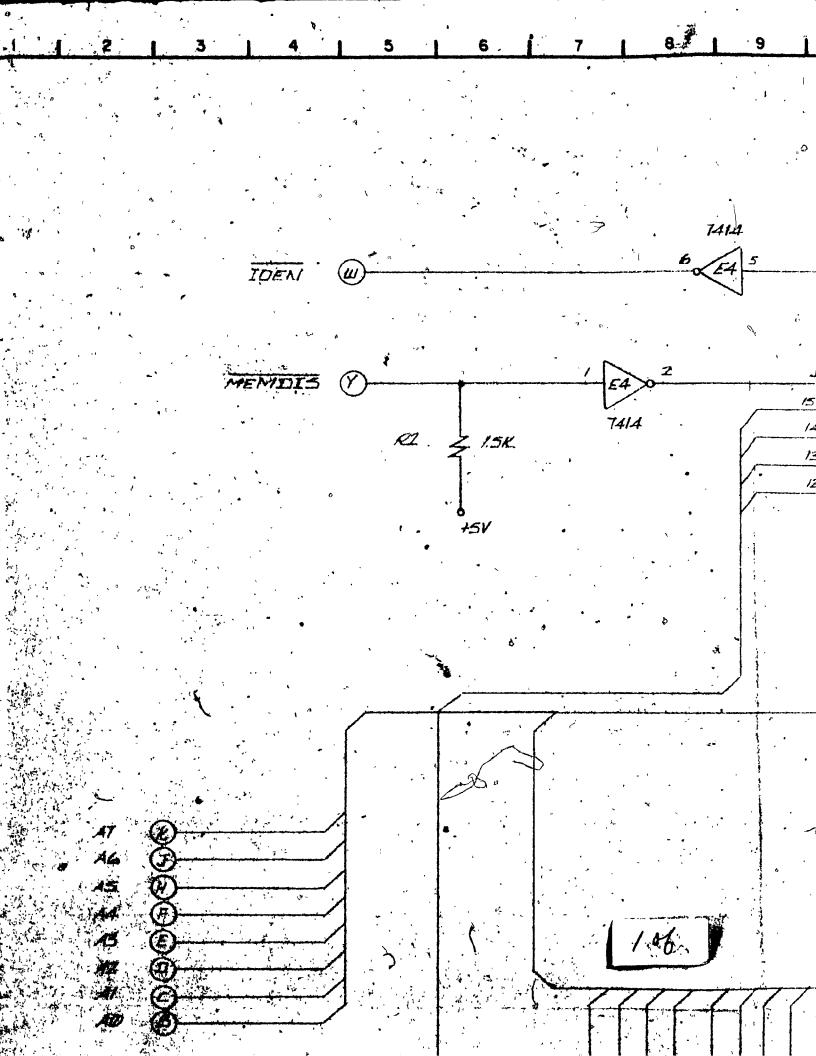

The generalized system configuration is illustrated in Figure 2.1. Transfer and control of parallel data to and from the PDP is handled by the DR-11C general purpose interface. The module which is purchased from DEC for approximately \$800 can easily be configured for a wide range of I/O use. Via the Controller the input and output buffer registers of the DR-11C (DRIN, DROUT) are channelled onto a single 16 bit bidirectional bus. Bus control may be requisitioned to any of 1 of 8 peripherals I/O cards and retains control until deselected. As an extension of the DR11C, selection and transfer of data to the peripheral I/O cards is under complete software control.

In the case of the microprocessor development system one of the I/O cards will be represented by a particular microprocessor Monitor module. Its primary function is for the control, loading and monitoring of the microprocessor. Associated with each microprocessor Monitor card will be its appropriate software module. Thus several micro processors whether identical or not will run with their own Monitor interfaces, software modules and card addresses on the Controller bus either singularily or simultaneously

Figure 2.1 System configuration. By linking the minicomputer and prototype, application programs are loaded, monitored and run.

multi-user environment).

The development system is built around a modular basis, i.e. CPU and Monitor printed circuit cards are designed for prototype integration. Additional plug in modules for various support functions and I/O may be developed and retained for future applications. The same principle holds for commonly used software routines and macros which are linked into the final application routine. During development the monitor module is part of the prototype system and is useful for loading programs, in-circuit-emulation and debugging. Once the hardware and software have been developed and optimized the monitor is removed and is retained for future applications or maintenance checks on the product.

### CHAPTER 3

### THE HARDWARE

### 3.1 INTRODUCTION

The hardware requirements for the development system may be subdivided into three basic groups; these include 1) I/O from the master, 2) target machine, and 3) link with the prototype system.

I/O from the masters defines how status, control and data are transmitted from the master minicomputer. The target machine defines the structure of the microprocessor or microcomputer under development. Finally linkage specifies how information is passed between the master I/O and the target machine.

In our application the I/O from the master is handled by the Controller and the specialized DR-11C interface to the minicomputer. Our target machine is represented by the RCA CDP 1802 microprocessor, integrated into the CPU module. Linkage is accomplished via the Monitor module. A complete description of the various hardware elements are given in the following sections.

### 3.2 THE DR-11C

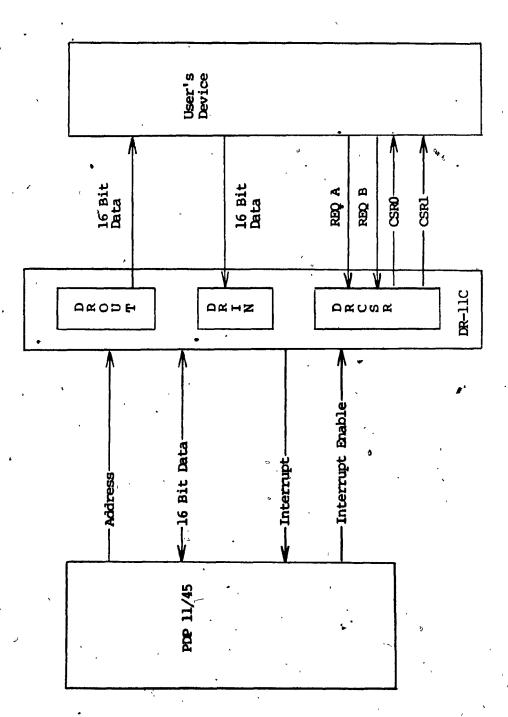

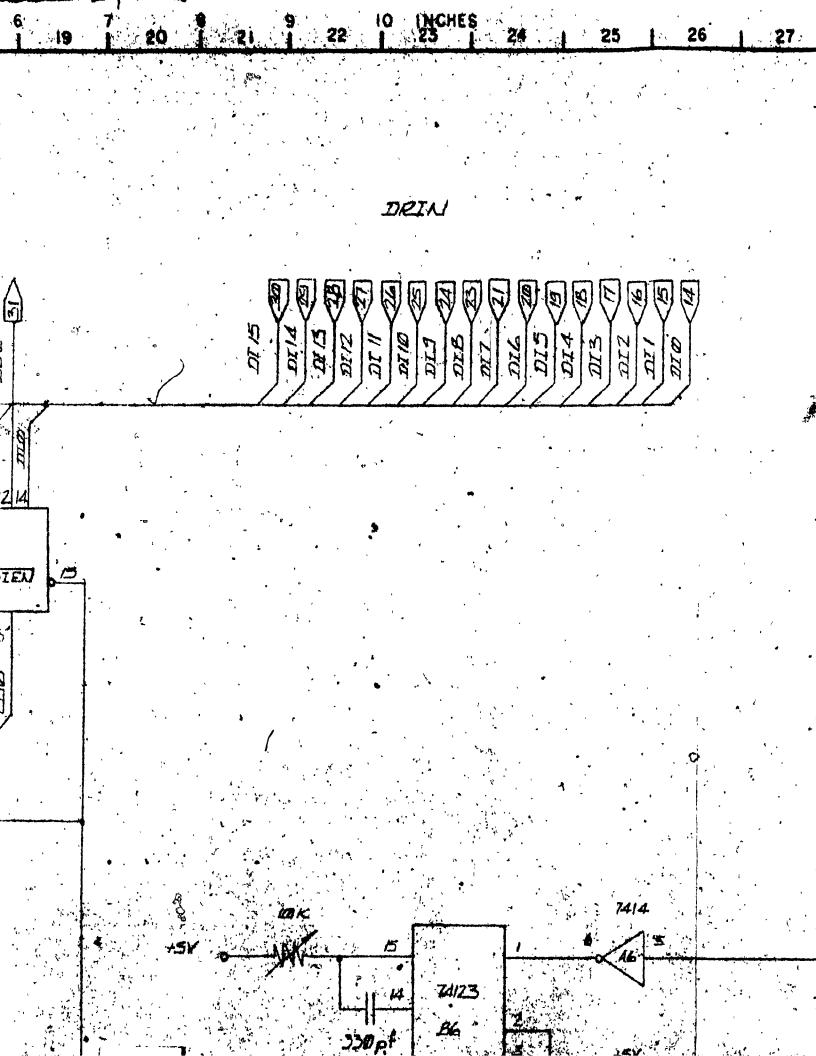

The DR-11C (Figure 3.1) is a general purpose interface between the PDP-11 bus and a user's device. The interface provides buffer/registers for input and output program controlled parallel data transfer, as well as for status and control functions. The status lines may be controlled by either the program or external device for command, monitoring and interrupt functions. The interface consists of three registers; control and status (DRCSR), input buffer (DRIN) and output buffer/ register (DROUT). Operation is initial-` ized under program control by addressing the DR-11C to specify the register and type of operation to be performed . In order to synchronize timing of data transfers to and from the interface, two control signals New Data Ready (NDR) and Data Transmitted (DTR) are available to the user.

Upon software transfer of data to the DROUT the NDR pulse is strobed indicating the user's device that data has been loaded. When an input from the DRIN has been executed the DTR line is strobed indicating that data has been read by the 11/45 CPU. The six bits of

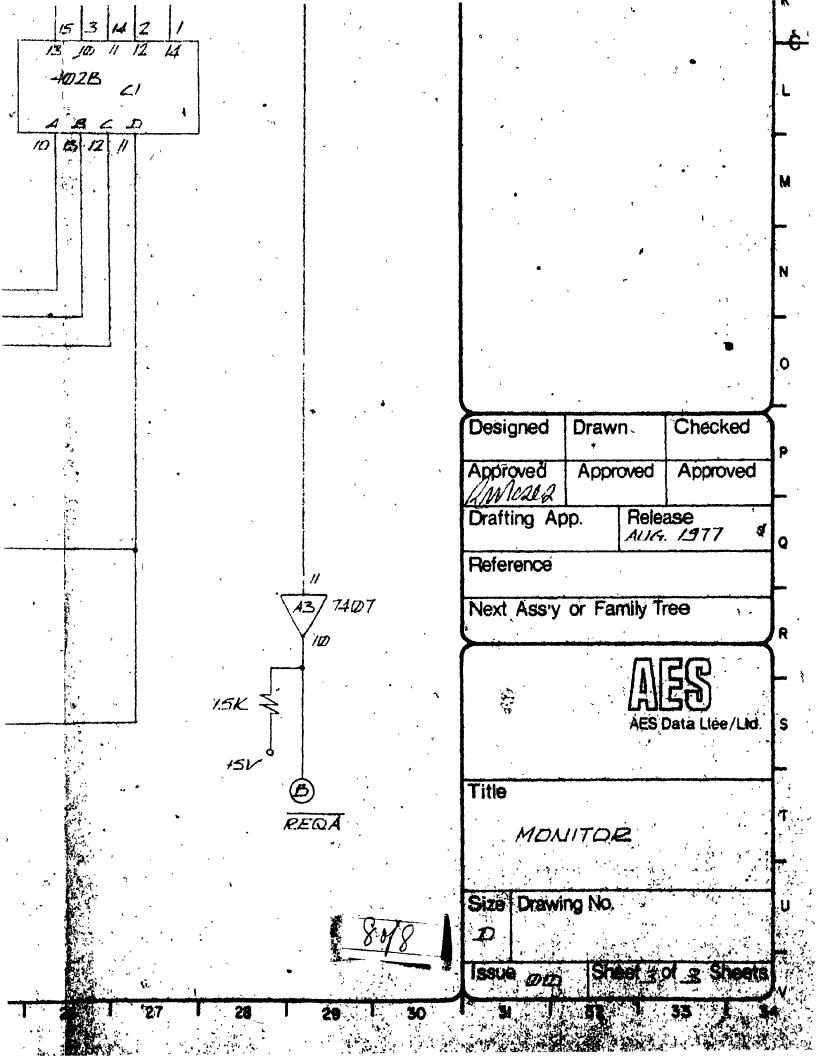

Figure 3.1 The DR-11C is a general purpose interface between the PDP 11/45 minicomputer UNIBUS and a user's peripheral.

the DRCSR are used for control and monitoring functions of the device. The two request lines REQ A and REQ B, which can only be read by the program, are manipulated either to initiate interrupts (depending whether INT A and/or INT B are set)or to provide flags that may be monitored by the program. The bits CSRO and CSRI are set under program control to provide commands to the external device. A complete description of the DR-IIC may be found in (8).

# 3.3 THE CONTROLLER®

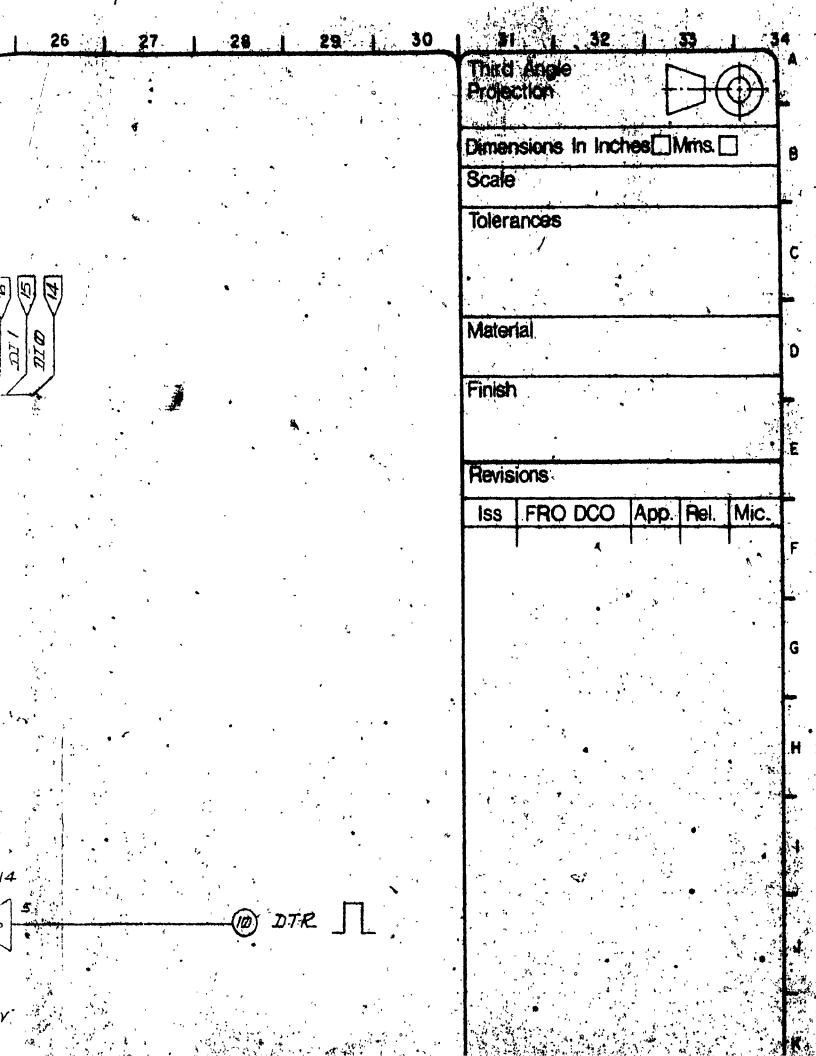

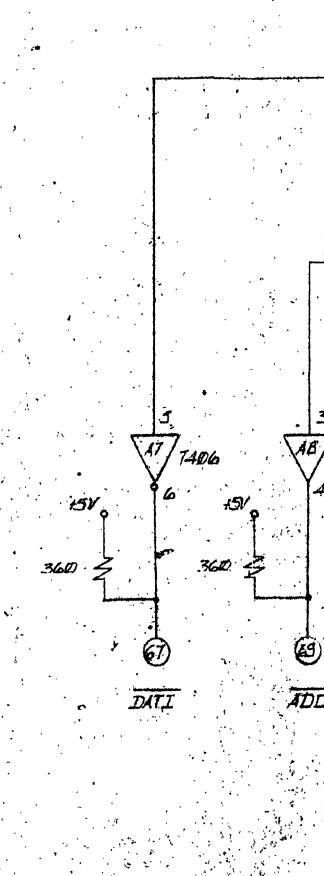

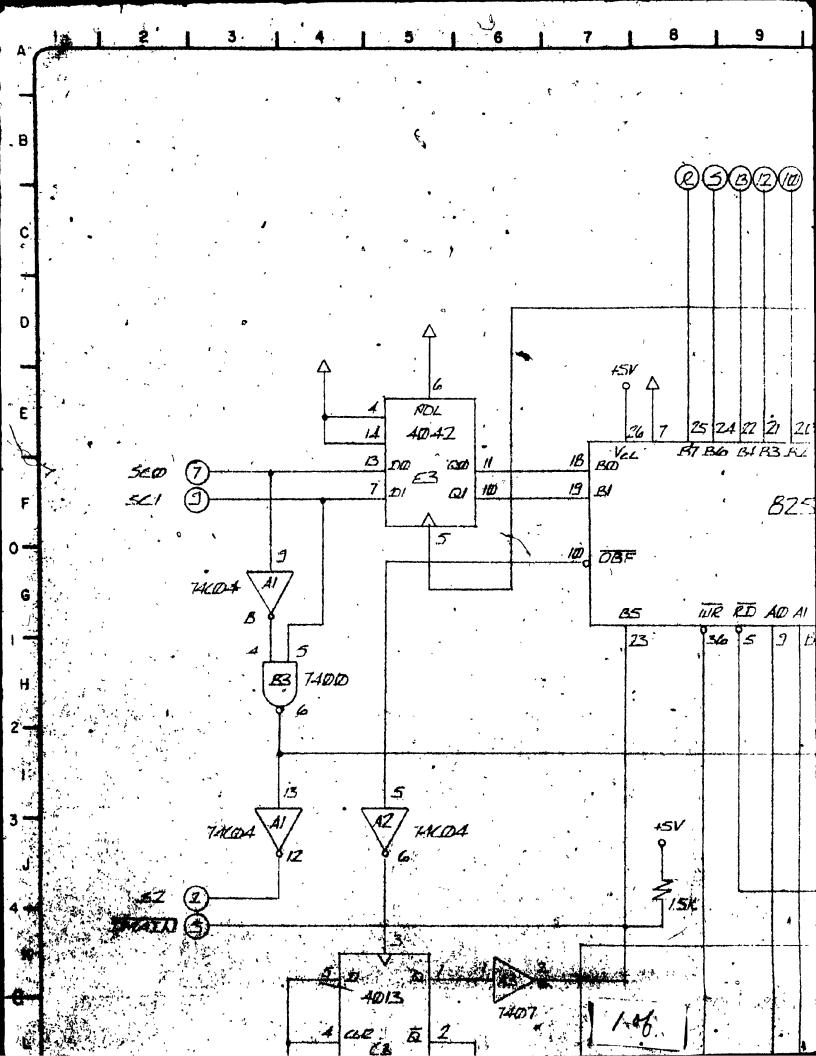

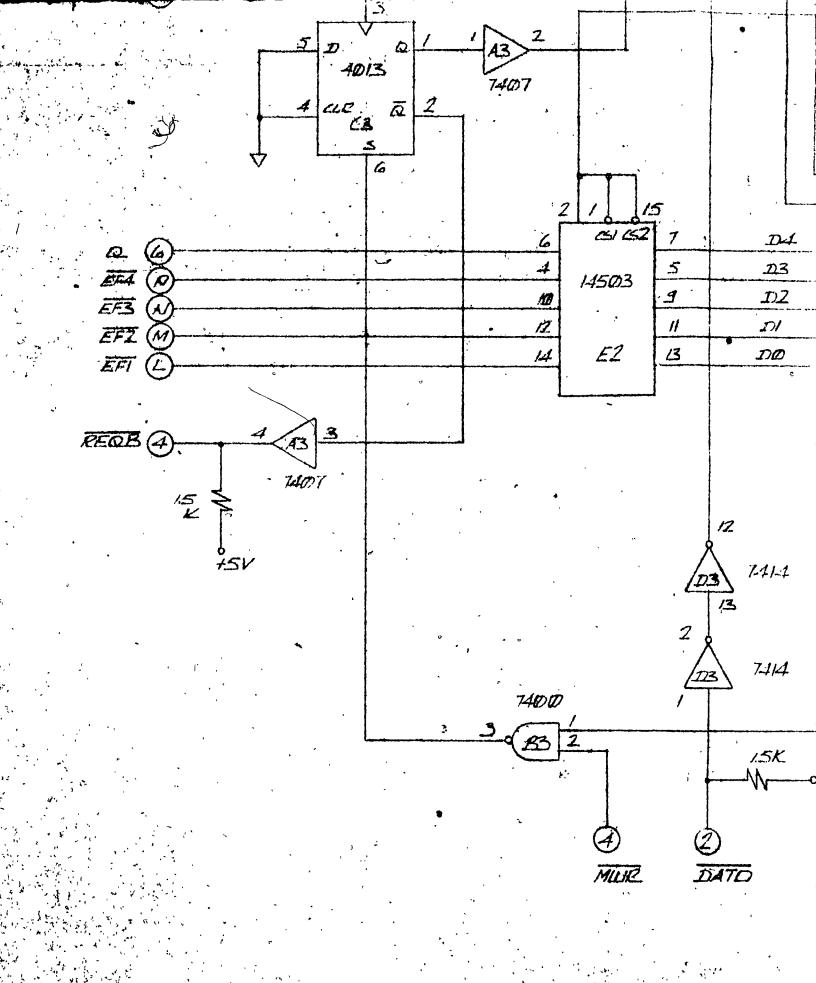

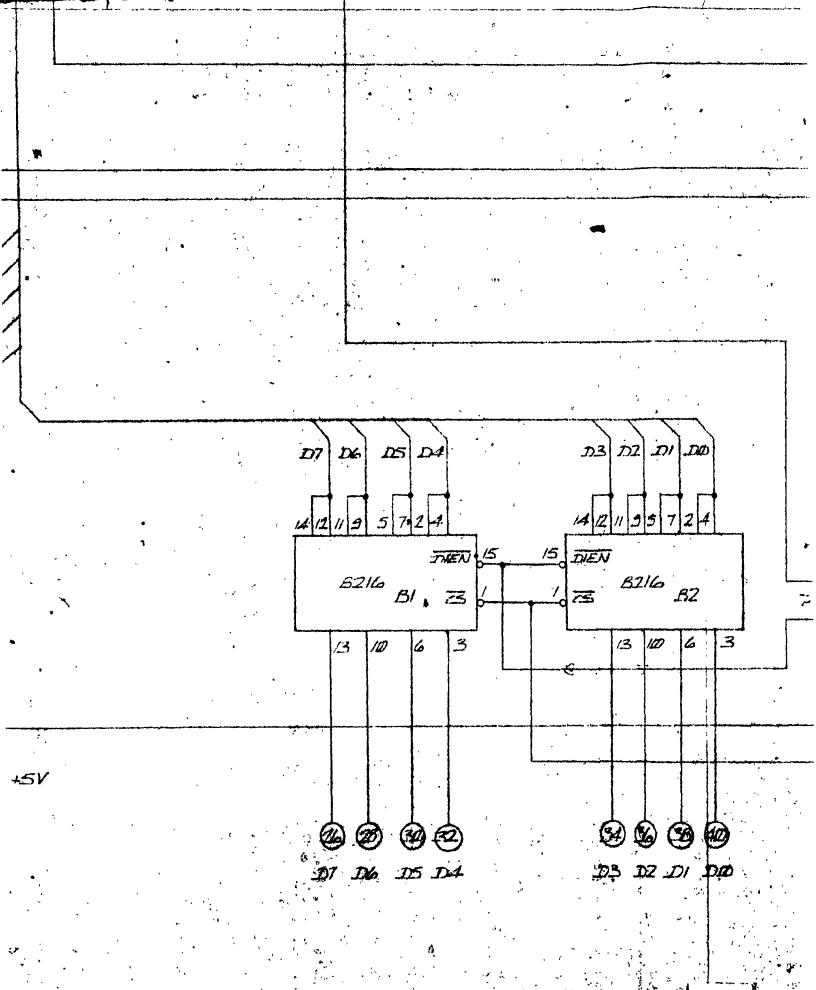

The transformation from a separate I/O structure of the DR-11C to a more compatible bidirectional bus structure is achieved by the Controller. Housed in the minicomputer mainframe, the Controller channels the I/O and status registers of the DR-11C (DRIN, DROUT, DRCSR) onto the bidirectional bus of the Controller chassis. The detailed schematic of the Controller is given in the appendix.

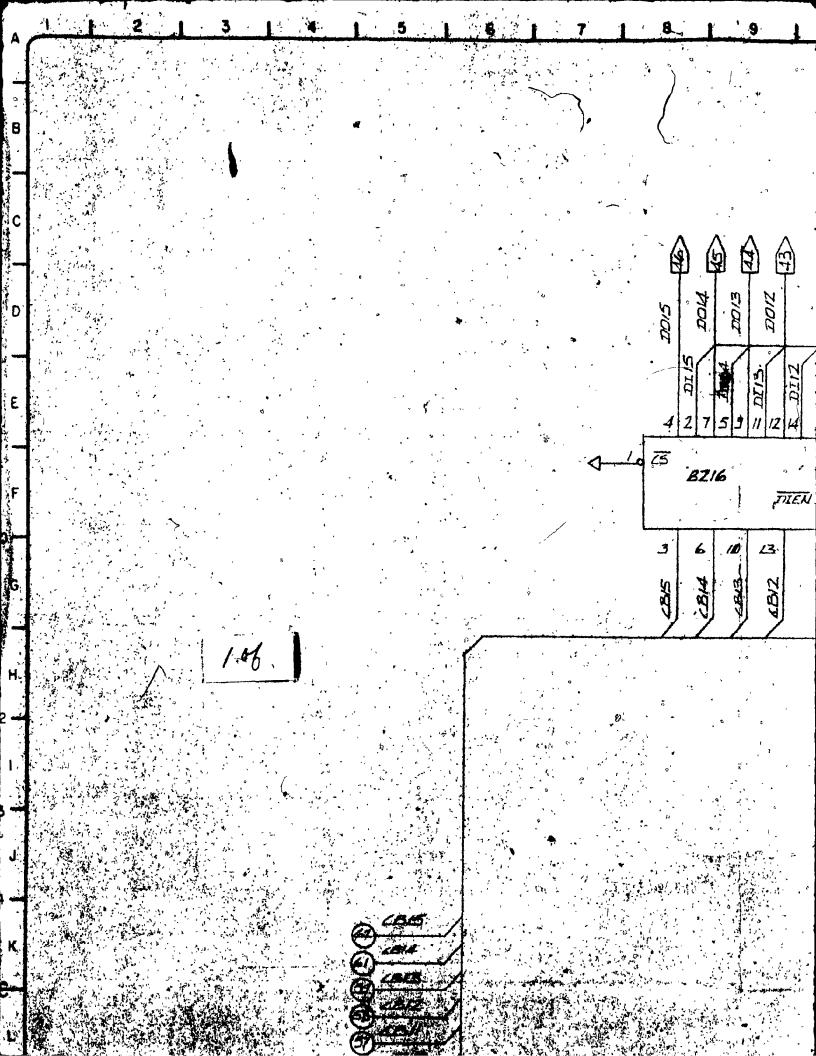

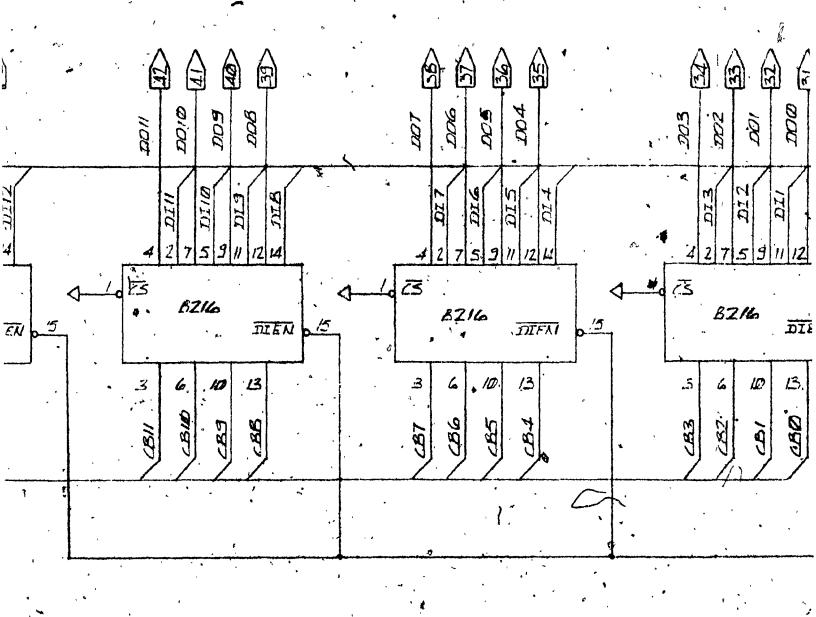

Bidirectional traffic control as well as bus driving capabilities are handled by the 8216 drivers. Normally the direction of the drivers are in the output mode with respect to the DR-11C, i.e. the DIEN input is low and the Controller bus is hooked to the DROUT. Upon a program Data. In sequence the DTR line is strobed. On the rising edge of the strobe two events occur; 1) the DRIN buffers are enabled, 2) direction of the 8216 drivers is switched so that the Controller bus is channelled into the DRIN buffers. At the same time a stretched and inverted version of DATI is issued to the Controller bus.

The Controller has the option of supporting up to

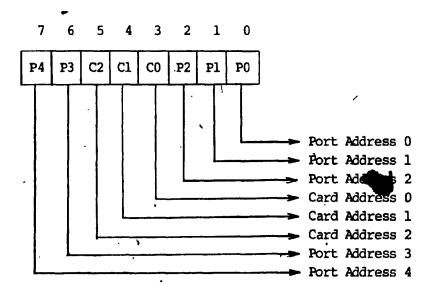

8 I/O peripherals. Selection of a peripheral or I/O Card requires the appropriate decoding of a three bit address. The format of the address word is shown in Figure 3.2.

The address byte is organized around 8 bits of which bits 3-5 are decoded for I/O Card selection. The remaining 5 bits may be used for control functions or for selecting one of 32 ports on the selected I/O card. Address bytes are transmitted on the Controlller bus to each card for decoding. Only one of the cards will match the 3 bit card address and consequently gain control of the bus or perform some function depending on the setting of the remaining address bits. Data (up to 16 bits) and address (8bits) words are Multiplexed on the Controller bus in accordance with the appropriate pulsing of the DATO and ADDR strobe To differentiate between an address or data word being transmitted the CSRO and CSRI bits of the DRCSR are used. Thus during a Data Out program sequence, depending on how these two bits have been set will determine whether to issue a DATO or ADDR strobe. This is accomplished by decoding the two CSR bits

Figure 3.2 Controller address byte format

with the NDR signal by means of the 7242 decoder. The remaining bit combinations of the CSR bits allow for two more functions. The first, INIT, will generate a strobe which may be used for the initialization or resetting of a device or operation. The second, DATA HOLD, will reverse the normal direction of the Controller bus drivers i.e. place the 8216 drivers on the input mode with respect to the DR-11C. This particular function is useful for observing the Controller's bus lines under static conditions. A summary of the CSR functions are given in Table 3.1.

Lastly the Controller buffers and inverts the REQ A and REQ B lines before feeding them into the DRCSR. Linkage between the Controller chassis and the DR-11C Berg connector is accomplished via a 40 connector ribbon cable. The Controller has the capabilities of supporting 8 (8"X 10",40 pin) plug-in modules, and maintains its own 5V, 15V@lA power supply.

| CSR0 | CSR1 | Function               |  |  |

|------|------|------------------------|--|--|

| . 0  | 0    | DROUT contains address |  |  |

| 0    | 1    | DROUT contains data    |  |  |

| 1    | 0    | INIT strobe            |  |  |

| 1    | 1    | IN mode                |  |  |

<u>Table 3.1</u> CSR0 CSR1 truth table.

# 3.4 THE RCA CDP 1802 MICROPROCESSOR

The first step in any microcomputer system design is to develop a set of criteria for microprocessor selection. Some of these criteria include;

- -flexibility

- -performance

- -cost

- -peripheral compatability

- -reliability

While the development system is adaptable to any device, our intention was to carry the basic philosophy of flexibility one step further by choosing a microprocessor that would be compatible to a wide spectrum of applications. In considering various devices the RCA CDP1802 8 bit CMOS microprocessor was chosen as central control and processing unit.

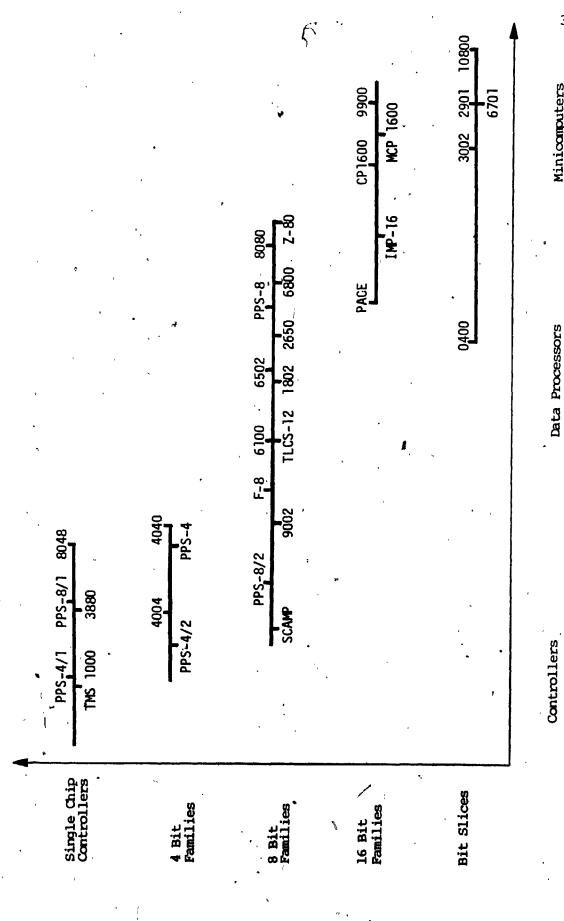

The range of microprocessor families and their immediate application domains is shown in Figure 3.3. In contrast to the 4 bit and 16 bit devices, system architecture around 8 bit machines appear to cover the most ground. Nevertheless, enhanced 8 bit devices can

Minicomputers

Figure 3.3 Range of processor chips and their application domains.

handle 16 bit data, making it possible for the user to upgrade his system .

In the applications spectrum the Intel 8080 and Motorola 6800 are very popular processors. Both are similarily organized with bus configurations typical of 8 bit systems. Such bus organization allows interface and peripheral IC's to use these lines, ensuring the user a well formulated method of designing his basic system.

Our decision was to proceed with the 1802 microprocessor manufactured by the RCA Solid State Division. The device possesses many of the advantages of

the older established families as well as several of

its own useful characteristics. In brief RCA 1802

features include:

- -single chip CPU

- -single 5V supply required

- -65K memory access

- -CMOS technology

- -2.5 microsecond instruction cycle

- -16 scratchpad registers(may point to either address or data)

- -91 instruction set

- -on board DMA facility

- -interrupt and programmed IO capabilities.

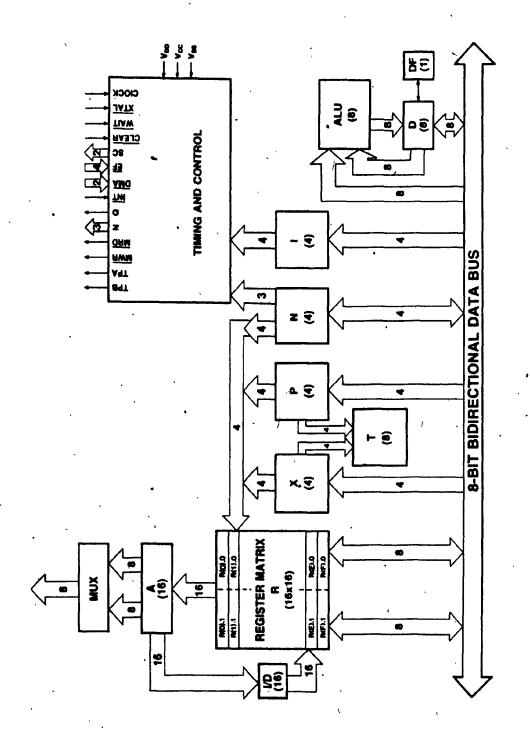

The block diagram of the 1802 architecture is shown in Figure 3.4. Furthermore the device will be pin to pin compatible to an enhanced SOS (Silicon On Saphire) version to be released by RCA at some later date. The SOS device promises to push speed through-put by a factor of two. Complete performance specifications and functional description of the 1802 microprocessor is given in (9).

Figure 3.4 RCA 1802 microprocessor architecture.

# 3.5 CPU MODULE

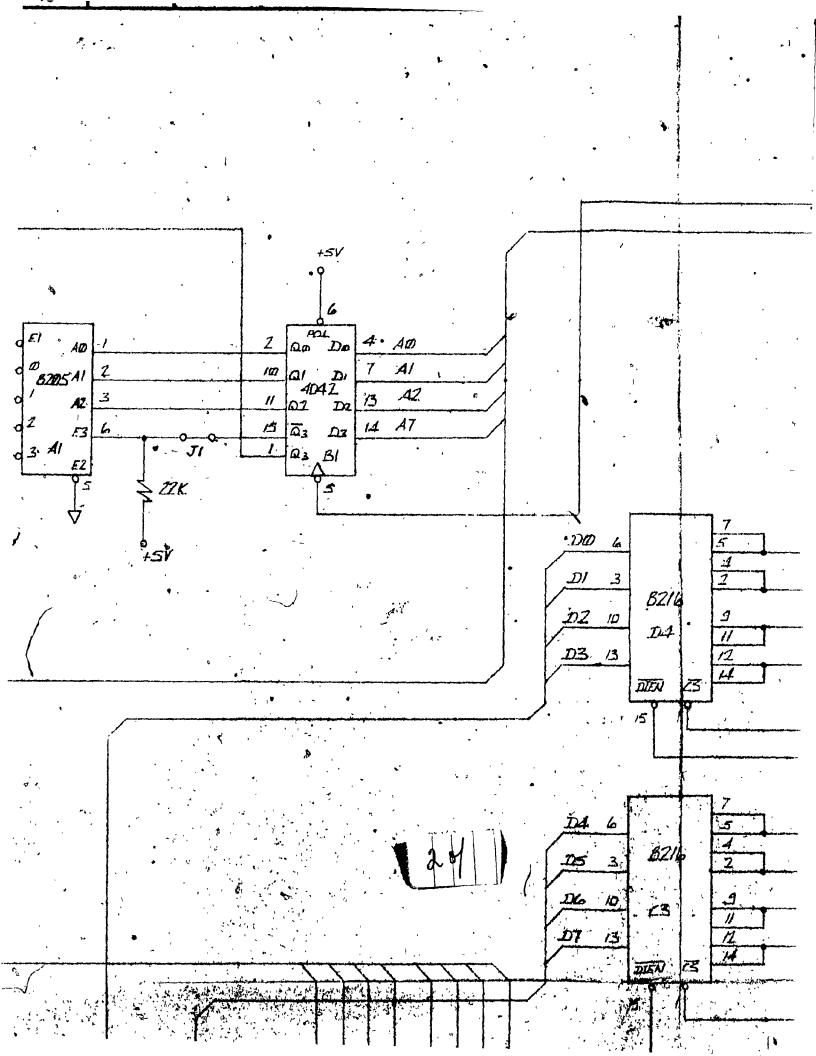

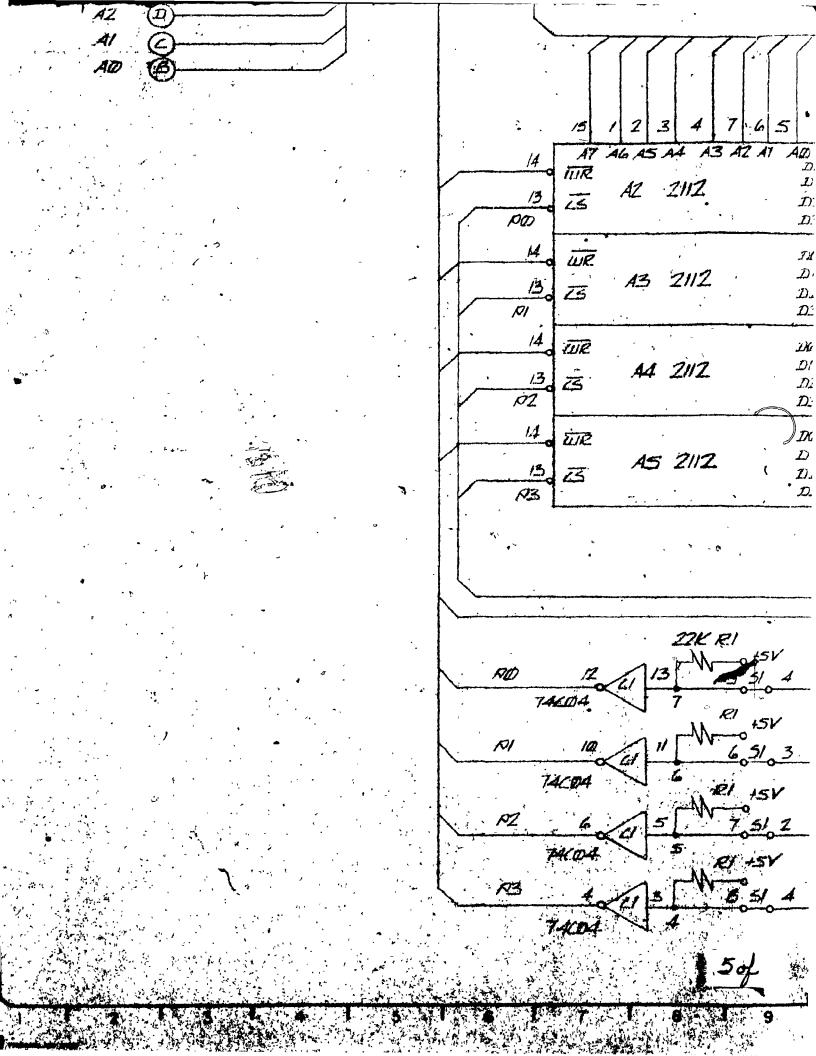

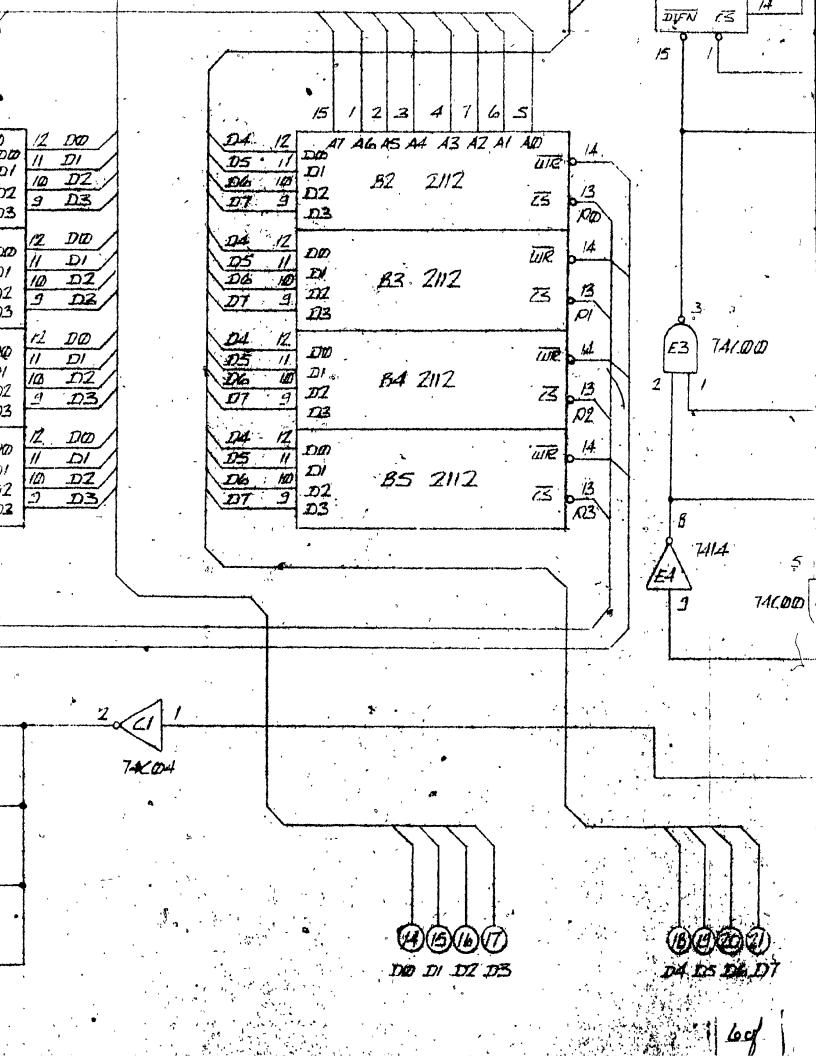

The 1802 microprocessor is incorporated into the CPU module. The module also contains lKbytes of on board memory which may be configured as either RAM and/or PROM. The CPU module block diagram is illustrated in Figure 3.5. For initial development, RAM may be used and upon final prototype development the required software may be permanently loaded into PROM. The module is packaged on a standard size PC board and comprises the fundamental unit for the application development and final product. The schematic for the CPU module is given in the appendix. Maximum component density was considered in the initial design. - The result is a high density single board microcomputer. Although the 1802 contains an on chip clock oscillator (requiring and external crystal), an external clock may also be provided. The latter course was taken in the design (using the 74123) the intent being that the user may set and adjust the operating clock frequency (via an adjustable trim-pot) for optimum performance; 1802 specs allow for a maximum 6.4 MHz clock frequency (operating at a 10V supply). All data and control

Figure 3.5 CPU module block diagram. Based on the 1802 microprocessor and 1K memory (RAM and/or PROM) the module serves as common denominator for all applications.

outputs are buffered. Control inputs (flags, interrupts, DMA requests, mode control) are pulled up to 5V through pull up resistor networks.

On board memory is configured around 256 X 4bit static devices. Eight components are incorporated to yeild lKbytes of memory. The Intel 2112 RAM and 3641 PROM are used. Pin compatability of two devices allows for interchangability and offers various combinations of RAM and /or PROM configurations.

The 1802 provides 8 memory address lines, supplying a 16 bit address word in the form of two successive address bytes. The high order byte (Al)appears on the address lines first followed by the low order address byte (A2). Two timing signals TBA and TBB are supplied by the microprocessor each machine cycle for synchronizing external events to internal 1802 events. The relationship between TPA, TPB and the memory address lines are shown in Figure 3.9.

The CMOS 4042 latch is used to record the most significant as well as lower 3 bits of the high address byte (clocking occurring on the falling edge of TPA). Decoding of the lower three bits of Al is accomplished by the 8205 selection switch to choose the

Figure 3.6 1802 timing waveforms.

appropriate memory page(1 page equals 256 bytes). Although up to 2Kbyte of memory may be accessed only 1Kbyte of on board memory is actually available. Bit 7 of the high address byte, if set deactivates the 8205 decoder and drives the IOEN line active low.

The memory data output (see Figue 3.9) is latched into the CPU on the falling edge of TPB. For a 3.2 MHz clock frequency (max at 5V) the allowable memory access time is in the order of 1.4us which is suitable for the maximum access time of lus of the 2112 static RAM device (the 3621 PROM will have a faster access time of approximately 60 ns).

Setting of S1 switch accordingly for each page determines whether RAM or PROM configuration is being used. For the PROM configuration S1 for the specific page is set in the OPEN condition and chip selects the device. Page selection via chip selects is derived from the 8205 decoder. For the RAM configuration S1 for the specific page is set in the CLOSED position. Consequently the MWR line is fed to the R/W line of of the 2112; when low indicates a Memory Write operation. Note from Figure 3.6 that data from the CPU is stable on the bus prior to activation of the MWR line. Norm-

ally the 2112 is in the READ state i.e. the R/W line is maintained high. Once again page selection is accomplished through the chip select derived from the 8205 decoder. Data may be loaded from the CPU to an external device in the same manner as it is loaded into memory. An I/O device may be characterized by a specific address or address block and programmed data transfers to these loactions will transmit data to the device. Presently, the most significant address bit '(bit 7 of Al) is used to determine whether an address is referencing memory or an I/O device. The MSB of the 16 bit address is latched at TPA time which in turn enables the IOEN line (active low) and deselects the on board lK of memory.

The 64K (65,535) memory referencing capability of the 1802 is sectored in the following memory mapping scheme. Full memory is divided via bit 16 into 32K for memory and 32K for I/O.Should the full memory address space be required the IOEN option may be disabled through jumper J1.

Memory is organized around pages 256 bytes long. Eight pages are integrated into a memory bank (2K). Memory extension cards are organized around memory

banks, and possess the appropriate decoding for page selection. Recall the address bits 8-10 of the address word are used to select the proper page. The remaining address bits 11-14 will choose 1 out of the 16 possible memory banks.

" The on board 1K memory on the CPU card represents one half the capacity of a possible memory bank. The full memory bank may be completed by stationing the remainig 1K elsewhere. An added input line to the module is supplied, MEMDIS which when activated deselects the on board memory. Presently the 1802 will address the first 1K of memory directly to the on board memory; however through the use of the MEMDIS line this lK may be relocated elsewhere. In situations where external memory (banks) are being utilized an external decoding circuitry will define the relative locations of the various memory banks. Thus each memory bank module may possess a similar MEMDIS input. and depending on the state of the line decides if the given bank is selected.

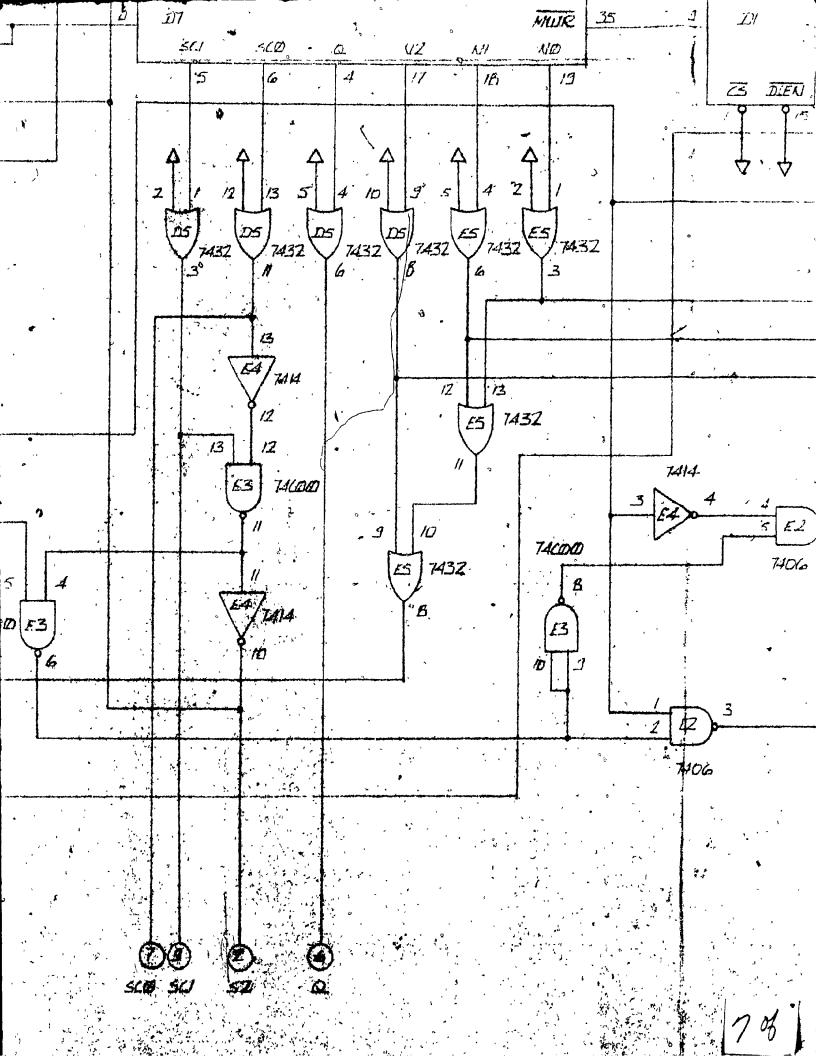

Under normal operation the 1802 may be in one of any four machine states. Each machine state designated \$\frac{1}{2}\$. S4,lasts the duration of 8 clock cycles, comprising

one machine cycle. Two state code lines SCO, SCl are available to the user and indicates that the CPU is; l)fetching an instruction, or 2)executing an instruction, or 3)processing a DMA request, or 4) ackowledging an interrupt request. The State Code truth table is shown in the 1802 signal description chart in Figure 3.7.

SCO, SC1, Q and N lines are buffered via the 7432 The Q line is a software generated output signal and the N lines are activated by COSMAC I/O instructions. The 8 data lines of the 1802 are configured in the bidirectional mode. Data output is channelled through the 8216 bidirectional bus drivers. 'Although outputs from the 1802 device can interface directly to a single TTL load, the 50ma driving capabilities of the 8216 drivers are well suited for bus driving. The direction of the data traffic is dependant of the type of instruction being executed. general when the MRD line is active data is being read from memory or an I/O device. Under such conditions the 8216 transceivers are in the input mode with respect with the CPU. An exeption to the rule is the INPUT instruction which loads memory and an internal CPU register (simultaneously from the data bus. In such a situation MRD is high, however the 8216 must be in the input mode (i.e. the bus lines must be connected to the 1802 data bus). Extra logic has been provided to switch bus directions for the IN N instructions.

During DMA (S2) cycles data is channelled directly to and from memory via the data bus. The source or destination of the data is from to or from some external peripheral, however the 1802 yeilds the corresponding memory addresses and monitors the transactions. Once a DMA cycle has been ascertained the microprocessor data lines are disabled from the card data bus via the CS line on the 8216 bus drivers. State decoding logic is activated during an S2 cycle to disable the D4 and C3 drivers. Furthermore S2 cycles are indicated by the S2 active output line.

In order to inform any external device the present direction of data flow on the CPU data bus. The DATIN ouput is provided. Direction of the bus will be instruction and/or state dependant.

Nine input lines allow for I/O controllers to transfer status or commands to the central processor.

All inputs are pulled up to 5V via resistor networks.

Active low inputs to these lines may be derived from one or more devices through the use of open collector drivers.

Four input flags enable a device to transfer status information to the microprocessor. The flags are internally sampled at the beginning of each S1 cycle and may be tested by conditional branch instructions.

Activation of the INTE interrupt line causes the machine to enter the S3 state. During this cycle the present program counter is stored and replaced with the starting address of the interrupt routine. Interrupt requests may be enabled or disabled by an internal flip-flop set or reset through the software. As soon as the microprocesor enters an the interrupt state the interrupt enable flip-flop is enabled to inhibit any further interrupts.

Direct memory transfer signals DMAIN and DMAOUT are user generated signals that may be ascerted at any time. Data is transferred directly via memory data bus, and address locations are stored and incremented automatically by an internal register (RO). The DMA as well as the INTE lines may request service inde-

pendant of the microprocessor internal events, however the CPU will first complete its present S1 execution cycle before going into either an S2 or S3 state.

The remaining two inputs CLEAR and WAIT are decoded by the 1802 to place the CPU in one of any four operational modes. The four modes of operation; LOAD, RESET, PAUSE, and RUN and corresponding CLEAR and WAIT truth table are listed in Figure 3.7

In the LOAD mode a program may be loaded directly into memory. The process is similar to a DMAIN operation with the exception that the intervals between transfers are filled with IDLE (no-op) operations.

RESET resets the internal registers, TPA and TPB are suppressed and the the CPU is placed in the Sl state.

PAUSE stops the internal CPU timing generator on the falling edge of the clock (of the upcomming full clock period). Although the clock may be left running, the CPU is frozen in the state at which time the PAUSE occured. Resumption of operation occurs when the PAUSE condition is removed.

RUN places the machine in its running state. When initiated from RESET, RUN will begin program execution

# Signal Descriptions

## BUS 0-7

8-bit bidirectional data bus for CPU - memory - I/O transfers.

#### No:

I/O selection lines. The 3 lowest-order bits of the N register appear on these lines when an input or output instruction is executed. They are used to uniquely select the desired I/O port. Different I/O instructions generate different signals on the N- lines (op codes 61-67 are outputs, 69-6F are inputs).

#### C

Bit-serial output line that can be set or reset under program control via two dedicated instructions (7B, 7A).

### INTERRUPT

Input to the CPU that initiates execution of the user's interrupt service program.

# DMA IN

# DMA OUT

Direct Memory Access request lines. Initiates DMA data transfer action within the SCP1802

# EF14

Four External Flag lines Conditionally tested by branch instructions to convey external information to the CPU, priortize multiple interrupts, etc.

#### SCo. SC

The State Code lines output the SCP1802's current machine state.

| ST         | ATE                 | SC | SC |   |

|------------|---------------------|----|----|---|

| SO         | Instruction Fetch   | 0  |    | 0 |

| S1         | Instruction Execute | ٥0 |    | 1 |

| S2         | DMA Transfer        | 1  | ĺ  | 0 |

| <b>S</b> 3 | Interrupt           | 1  |    | 1 |

#### MAD

Memory Read signal. Can be used to control 3-state outputs from addressed memory if it has a common data in/out bus. Also used to indicate direction of data transfer during an I/O instruction.

#### CLOCK

Input for external one phase clock signal.

#### YTAI

A crystal is connected between XTAL and CLOCK (typically with a 10 megohm resistor) when the on-chip oscillator is used.

## WAIT

## CLEAR

Control lines to determine the SCP1802's mode:

| MODE  | CLEAR | WAIT |

|-------|-------|------|

| Run   | 1     | 1    |

| Pause | 1     | 0    |

| Reset | 0     | 1    |

| Load  | 0     | 0    |

Run: Normal CPU instruction

execution.

Pause: Stops CPU operation at the next high-to-low clock input; only the oscillator continues to

operate.

Reset: I, N, Q, X, P, R (0), BUS ♦0 IE ♦1 (interrupts enabled)

Load: Allows an I/O device to load memory from location 0000 without a "bootstrap loader".

### VDD. VCC. VSS

The I/O voltage supply level  $V_{CC}$  is isolated from the internal CPU voltage level  $V_{DD}$  This allows for simple interfacing bewteen the SCL1802 and TTL, NMOS, etc.  $V_{SS}$  is ground,

#### TPA

Timing Pulse for strobing high order memory address byte into external latch or ROM.

#### TPB

Timing Pulse used by external I/O devices to time interaction with CPU.

## MA<sub>0.7</sub>

8-bit Memory Address bus carries the multiplexed 16-bit memory address, high-order byte first followed by the low-order byte.

#### MWR

Memory Write. A pulse appearing after the memory address lines have stabilized. starting at location 0.

のから、 いるのでする まるじょど 皮を含みて Linux のでは

The CPU module is integrated on a 4.5" X 8" double sided printed circuit board. Maximum density is achieved through the use LSI components as well as resistor networks. Power and ground busses are well distributed and decoupled so as to maintain a relatively noise free environment. CMOS components have been used extensively so as to reduce power requirements and increase noise immunity.

Operating at 5V the module consumes in the order of 80ma. The module may be produced in small quantities for under \$100.00.

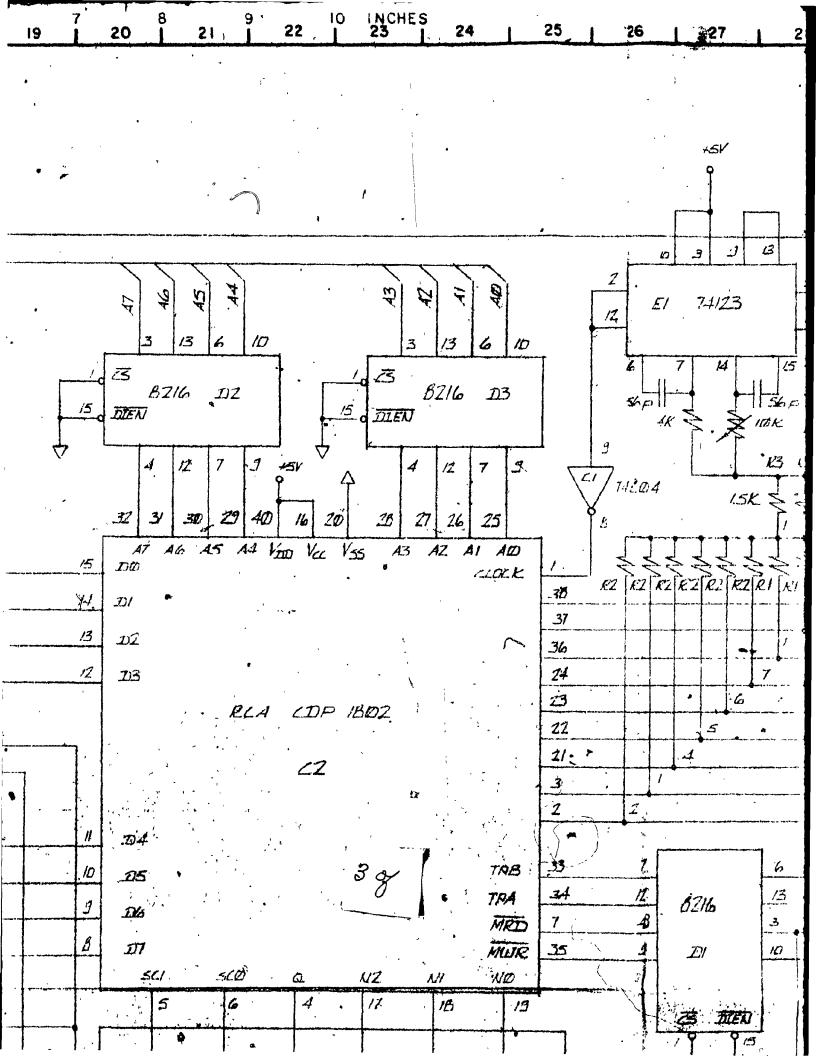

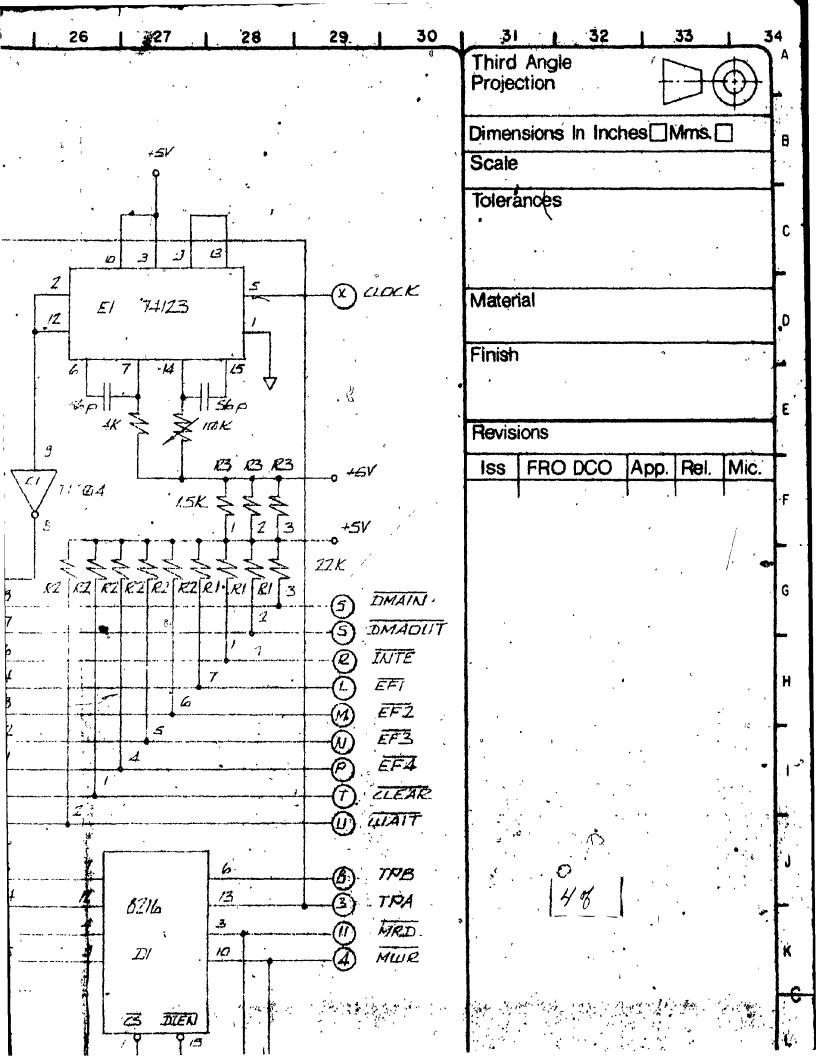

# 3.6 MONITOR MODULE

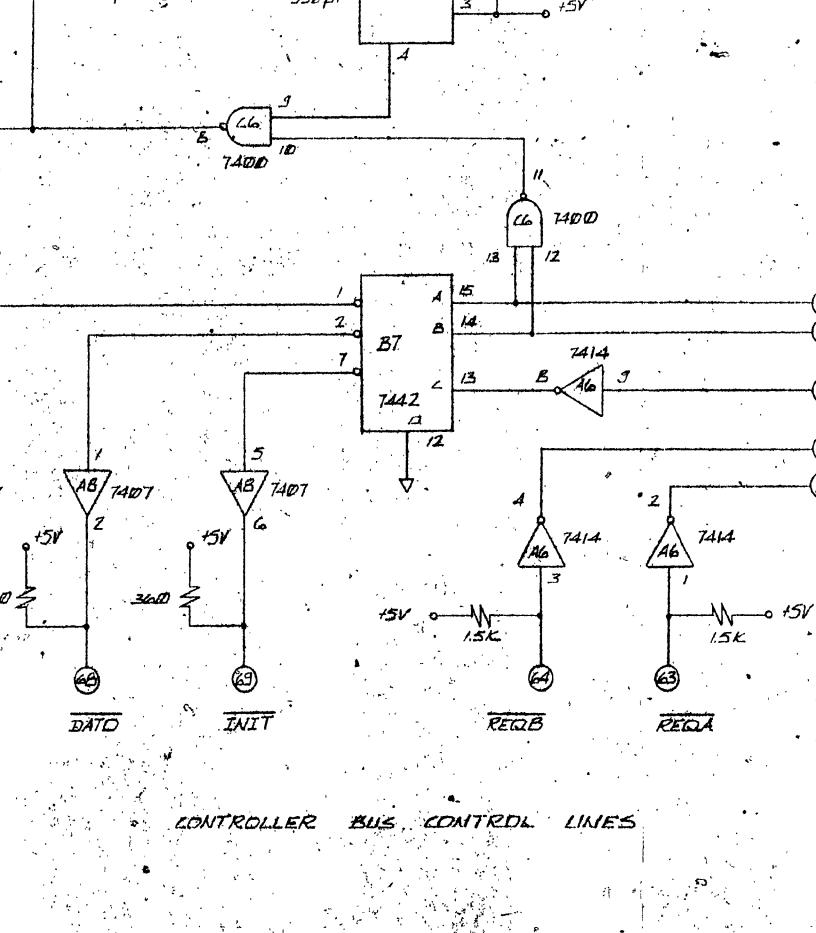

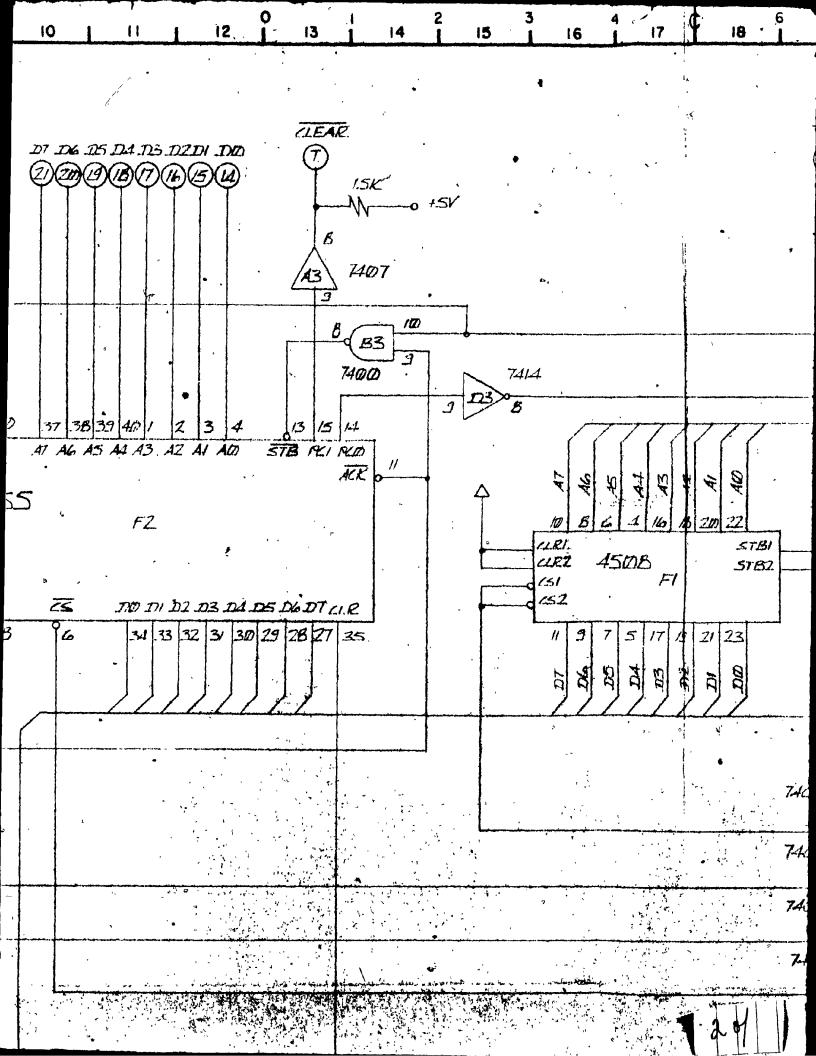

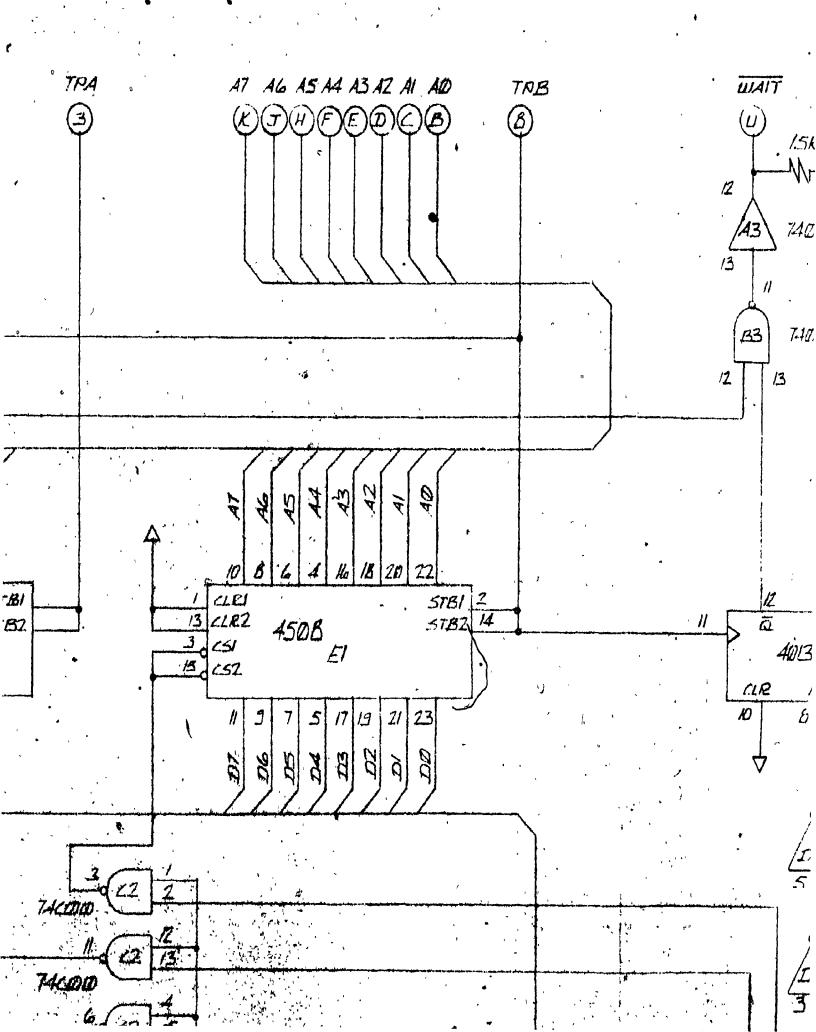

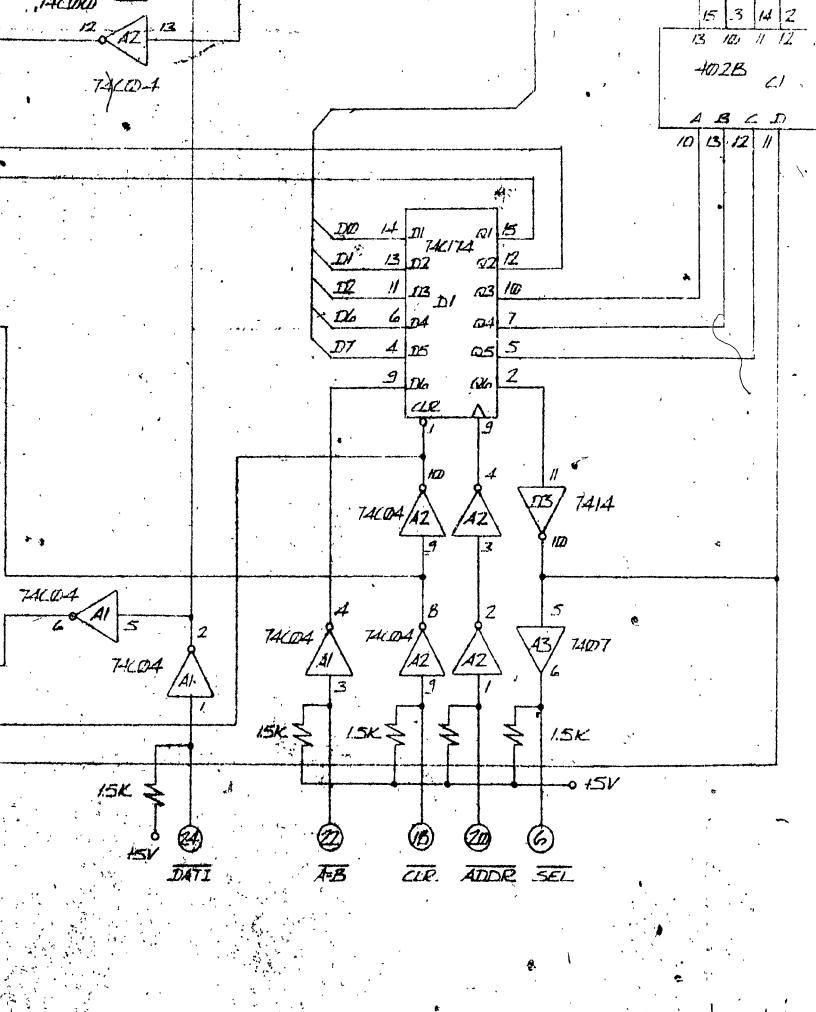

The CPU module is interfaced to the I/O Controller via the Monitor module. The Monitor is responsible for the transfer of data and commands to the microprocessor as well as for monitoring the status, address and control lines of the microprocessor. The module is linked by a 40 line ribbon cable to its associated card on the I/O Controller chasis. The generalized configuration is illustrated in Figure 3.8.

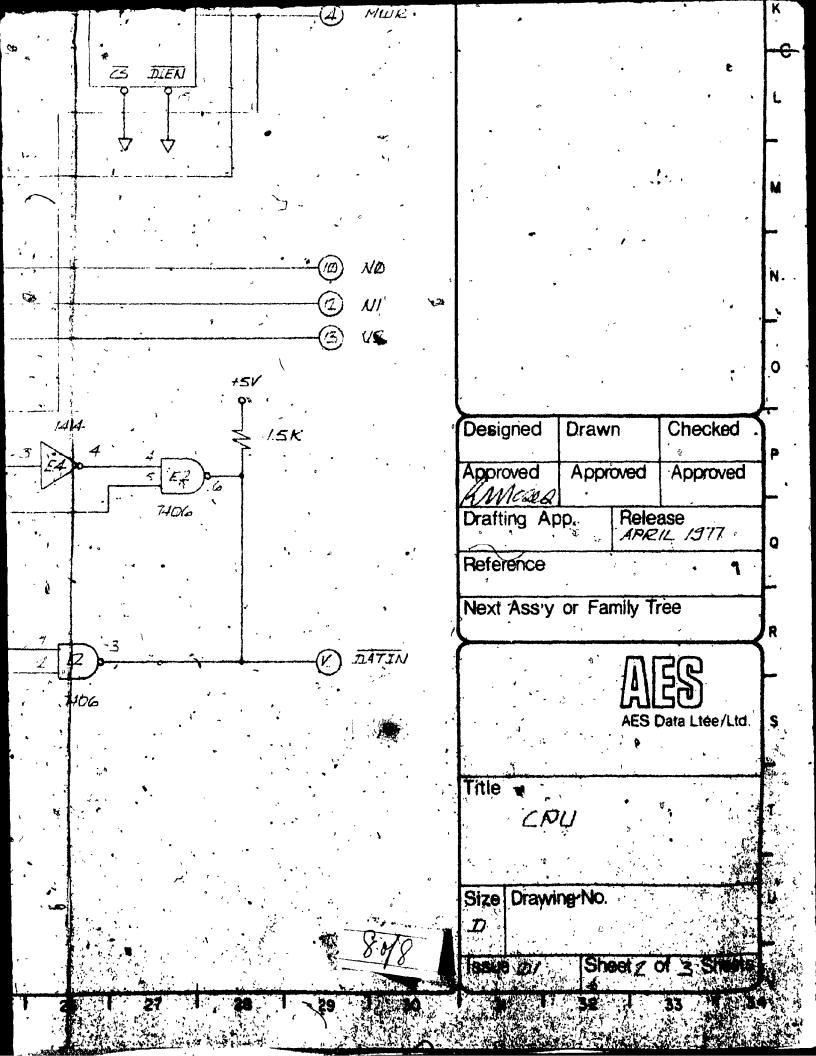

The I/O card is a simplified version of the address selection logic. Basically it contains a comparator for address matching as well as line drivers for the cable to the Monitor module. The schematic for the monitor is given in the appendix.

Upon card selection the 8216 3-state drivers are enabled thereby hooking the monitor onto the Controller bus, the remaining bits of the address word are latched and finally the individual ports on the Monitor are enabled. Note the 8216's are in the input mode by default and change direction only on the issuance of the DATI strobe.

The Intel 8255 PPI(programmable peripheral int-

Figure 3.8 Software controlled transfer of data and control between the microcomputer and Controller is acheived via the Monitor module.

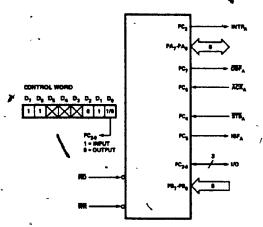

erface) is used extensively for tramsfer of I/O. The 40 pin package may be configured in several ways depending on the application in mind.

Bits 7 and 6 of the address byte are used for selecting one of the three ports of the 8255 via the Al and AO inputs. The lower three bits of the address byte are decoded through the 4028 to choose one of five functions. Four are used in conjunction with the DATI strobe to read one of four input ports. The fifth is incorporated for single stepping the microprocessor through consecutive machine cycles.

Essentially the 8255 multiplexes the Monitor bidirectional data bus to one of three ports (A,B,C). Selection and configuration of the ports is done via a software command word. For our application the PPI is configured in Mode 2 and Mode 0 (Figure 3.9). Port A is used as a bidirectional port for data transfer to and from the the CPU module data bus.PC4-PC7 lines from Port C are used for handshaking of data transmission.Port B is used as a input read only port, monitoring the status of the microprocessor DMA, INTE, N, and state code (SC1,SC0) lines. The remaining three output Port C lines (PC0-PC2) are used in conjunction

MODE 2 AND MODE ( (INPUT)

Figure 3.9 8255 mode configuration. Port A (mode 2) is a bidirectional 8 bit bus using five lines from Port C for handshaking. Port B (mode 0) is set as an input 8 bit port.

with the microprocessor WAIT and CLEAR lines. Writing data from the Controller bus into the PPI occurs during the DATO strobe. All incoming control signals are buffered.

The destination of the incoming data is determined by the port selection bits Al and AO. An incoming byte may either be data (which will be directed to one of the ports) or a control word. The control word is used for initializing the 8255 into its configuration and for setting or resetting 8255 internal flip-flops.

Selection of the 8255 itself as well as any of its internal ports is accomplished using the address byte format (Figure 3.2). P0-P2 set to 0 will select the 8255 via the 4028 decoder. C2-C0 is the actual card address and is strap selectable on the various cards. For our purposes the Monitor module has been assigned the address 1.

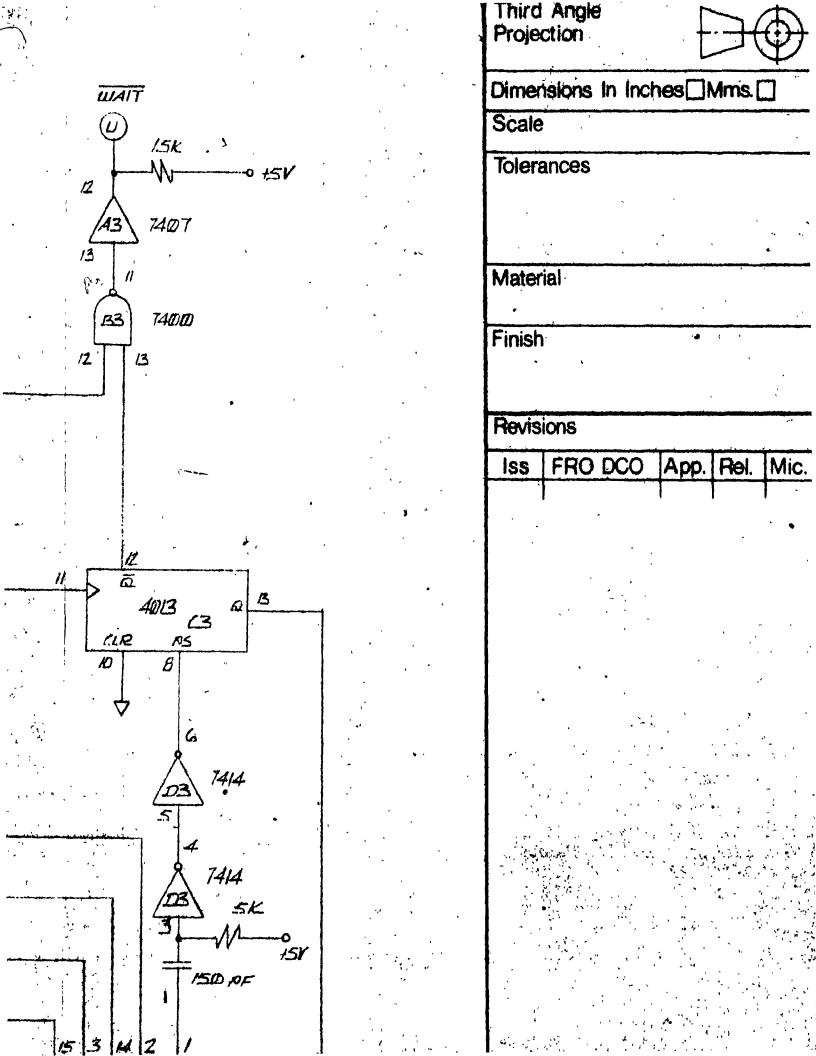

The microprocessor operational mode, set by the WAIT and CLEAR lines are set by writting the appropriate bit code to PCO and PCl of Port C. PCl is wired, through a buffer to the CLEAR line. The WAIT line is tapped from two sources; one is PCO on the 8255 and

secondly the single stepping circuitry via a NAND gate. Normally single stepping is disabled and the 1802 operational mode is derived from PCO and and PCl of Port C.

Single stepping is accomplished by placing the CPU in the RUN mode for a single machine cycle and then halting it ( placed in the PAUSE mode) until another single step is requested. Referring to Figure 3.7 we note that the RUN and PAUSE states may alternately be achieved by flipping the WAIT line between high and low states.