### Yield-Aware Leakage Power Reduction of On-Chip SRAMs

Afshin Nourivand

A Thesis In the Department of Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements For the Degree of Doctor of Philosophy (Electrical and Computer Engineering) at Concordia Uuniversity Montréal, Québec, Canada

October 2010

©Afshin Nourivand, 2010

### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Afshin Nourivand

Entitled: Yield-Aware Leakage Power Reduction of On-Chip SRAMs

and submitted in partial fulfilment of the requirements for the degree of

**Doctor of Philosophy** (Electrical and Computer Engineering)

complies with the regulations of the university and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|                      | Chair                     |

|----------------------|---------------------------|

| Dr. M. Paraschivoiu  |                           |

|                      | External Examiner         |

| Dr. M. Sachdev       |                           |

|                      | External to Program       |

| Dr. T. Radhakrishnan |                           |

|                      | Examiner                  |

| Dr. G. Cowan         |                           |

|                      | Examiner                  |

| Dr. M. Z. Kabir      |                           |

|                      | Thesis Co-Supervisor      |

| Dr. A. J. Al-Khalili |                           |

| Dr. V. Carrain       | Thesis Co-Supervisor      |

| Dr. Y. Savaria       |                           |

|                      |                           |

| wed by               |                           |

| Dr. M. Kahrizi,      | Graduate Program Director |

September 29, 2010

Dr. Robin A. L. Drew, Dean Faculty of Engineering and Computer Science

#### Abstract

#### Yield-Aware Leakage Power Reduction of On-Chip SRAMs

#### Afshin Nourivand, Ph.D. Concordia University, 2010

Leakage power dissipation of on-chip static random access memories (SRAMs) constitutes a significant fraction of the total chip power consumption in state-of-the-art microprocessors and system-on-chips (SoCs). Scaling the supply voltage of SRAMs during idle periods is a simple yet effective technique to reduce their leakage power consumption. However, supply voltage scaling also results in the degradation of the cells' robustness, and thus reduces their capability to retain data reliably. This is particularly resulting in the failure of an increasing number of cells that are already weakened by excessive process parameters variations and/or manufacturing imperfections in nano-meter technologies. Thus, with technology scaling, it is becoming increasingly challenging to maintain the yield while attempting to reduce the leakage power of SRAMs. This research focuses on characterizing the yield-leakage tradeoffs and developing novel techniques for a yield-aware leakage power reduction of SRAMs.

We first demonstrate that new fault behaviors emerge with the introduction of a low-leakage standby mode to SRAMs. In particular, it is shown that there are some types of defects in SRAM cells that start to cause failures only when the drowsy mode is activated. These defects are not sensitized in the active operating mode, and thus escape the traditional March tests. Fault models for these newly observed fault behaviors are developed and described in this thesis. Then, a new low-complexity test algorithm, called March RAD, is proposed that is capable of detecting all the drowsy faults as well as the simple traditional faults.

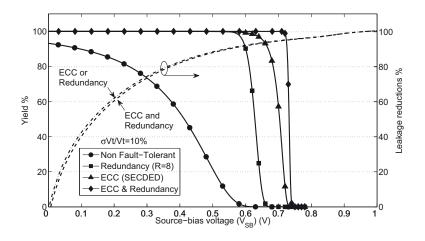

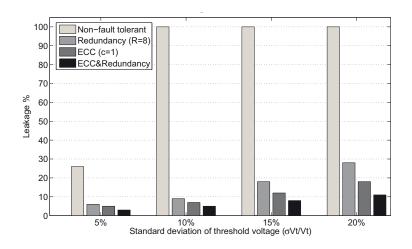

Extreme process parameters variations can also result in SRAM cells with very weak data-retention capability. The probability of such cells may be very rare in small memory arrays, however, in large arrays, their probability is magnified by the huge number of bit-cells integrated on a single chip. Hence, it is critical also to account for such extremal events while attempting to scale the supply voltage of SRAMs. To estimate the statistics of such rare events within a reasonable computational time, we have employed concepts from extreme value theory (EVT). This has enabled us to accurately model the tail of the cell failure probability distribution versus the supply voltage. Analytical models are then developed to characterize the yield-leakage tradeoffs in large modern SRAMs. It is shown that even a moderate scaling of the supply voltage of large SRAMs can potentially result in significant yield losses, especially in processes with highly fluctuating parameters. Thus, we have investigated the application of fault-tolerance techniques for a more efficient leakage reduction of SRAMs. These techniques allow for a more aggressive voltage scaling by providing tolerance to the failures that might occur during the sleep mode. The results show that in a 45-nm technology, assuming 10% variation in transistors threshold voltage, repairing a 64KB memory using only 8 redundant rows or incorporating single error correcting codes (ECCs) allows for  $\sim$  90% leakage reduction while incurring only  $\sim 1\%$  yield loss. The combination of redundancy and ECC, however, allows to reach the practical limits of leakage reduction in the analyzed benchmark, i.e.,  $\sim 95\%$ .

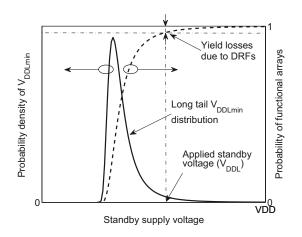

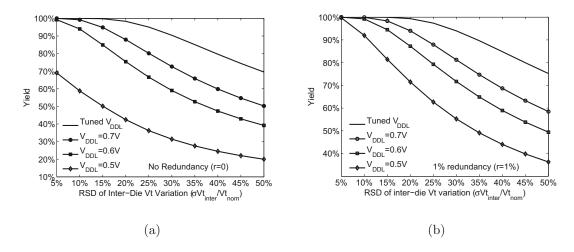

Applying an identical standby voltage to all dies, regardless of their specific process parameters variations, can result in too many cell failures in some dies with heavily skewed process parameters, so that they may no longer be salvageable by the employed fault-tolerance techniques. To compensate for the inter-die variations, we have proposed to tune the standby voltage of each individual die to its corresponding minimum level, after manufacturing. A test algorithm is presented that can be used to identify the minimum applicable standby voltage to each individual memory die. A possible implementation of the proposed tuning technique is also demonstrated. Simulation results in a 45-nm predictive technology show that tuning standby voltage of SRAMs can enhance data-retention yield by an additional 10% - 50%, depending on the severity of the variations.

#### Acknowledgements

I would like to express my sincere gratitude and appreciation to my academic supervisors, Professor Asim J. Al-Khalili and Professor Yvon Savaria, for their insightful guidance and generous support throughout this research. They both have been instrumental in the success of this research. Professor Al-Khalili was always there to give me the moral support and encouragement during tough times. His sound vision, knowledge, and experience helped me improve both professionally and personally. I am also deeply indebted and hold great respect for my co-supervisor, Professor Savaria, whom without his guidance and support this work would not have been possible. His expertise and critical suggestions have shaped the character of this research. I continue to be amazed by the breadth of his knowledge, his innovative ideas, and his endless energy for research. Indeed, I feel truly privileged for having this unique experience of working under the supervision of such great professors.

I want to thank my thesis defense committee members: Dr. Manoj Sachdev, Dr. Glenn Cowan, Dr. Zahangir Kabir, and Dr. Thiruvengadam Radhakrishnan for their helpful comments and suggestions. My very special thanks go to my external examiner, Dr. Manoj Sachdev, for the time he took to carefully read and comment on my dissertation. His insightful comments and suggestions helped me enhance this work significantly.

I would also like to thank those people in the ECE department who provided a positive environment that encouraged me to aim at high-quality research. Namely, I am grateful to Dr. Omair Ahmad for his support during the first 2 years of my studies. I also thank Dr. Otmane Ait Mohamed for being on my qualification exam committee. I would also like to thank Ted Obuchowicz for keeping the CAD tools running. My special thanks also go to Pamela Fox, the Ph.D. program coordinator, and Kimberly Adams, the TA coordinator. I also want to thank all former and current members of the VLSI group for the cheerful moments that we shared in the lab.

Last but surely not least, I am truly grateful and indebted to my parents, for their endless sacrifices and for teaching me the fundamental principles of uprightness, honesty, compassion and hard work. To my beloved parents.

# Contents

| C             | onten                 | $\mathbf{ts}$ |                                                                                                                                             | viii |  |

|---------------|-----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| $\mathbf{Li}$ | st of                 | Figure        | 25                                                                                                                                          | xii  |  |

| Li            | st of                 | Tables        | 3                                                                                                                                           | xv   |  |

| A             | Acronyms xvi          |               |                                                                                                                                             |      |  |

| 1             | $\operatorname{Intr}$ | oducti        | on                                                                                                                                          | 1    |  |

|               | 1.1                   | Motiva        | $tion \ldots \ldots$ | 5    |  |

|               | 1.2                   | Contri        | butions and Proposed Solutions                                                                                                              | 6    |  |

|               |                       | 1.2.1         | New Fault Behaviors and Their Impact on Low-Leakage SRAMs                                                                                   | 6    |  |

|               |                       | 1.2.2         | Modeling the Yield-Leakage Tradeoff in Large SRAM Arrays<br>Considering Extreme Failure Events                                              | 7    |  |

|               |                       | 1.2.3         | Aggressive Leakage Reduction of SRAMs Using Fault-Tolerance      Techniques                                                                 | 8    |  |

|               |                       | 1.2.4         | Post-Silicon Tuning of Standby Supply Voltage for Reduction of Parametric Yield Losses Due to Data-retention Failures                       | 8    |  |

|               | 1.3                   | Organi        | ization of the Dissertation                                                                                                                 | 9    |  |

| <b>2</b>      | Bac                   | kgroun        | ıd                                                                                                                                          | 11   |  |

|               | 2.1                   | SRAM          | s Organization and Operation                                                                                                                | 11   |  |

|               |                       | 2.1.1         | SRAMs Organization                                                                                                                          | 11   |  |

|               |                       | 2.1.2         | SRAM Cells                                                                                                                                  | 13   |  |

|               | 2.2                   | Leakag        | ge Power Dissipation in SRAMs                                                                                                               | 14   |  |

|               |                       | 2.2.1         | Subthreshold Current                                                                                                                        | 15   |  |

|               |                       | 2.2.2         | Gate-Tunneling Current                                                                                                                      | 15   |  |

|               | 2.3                   | SRAM          | Leakage Reduction Techniques                                                                                                                | 16   |  |

|               |                       | 2.3.1         | Supply Voltage Scaling                                                                                                                      | 16   |  |

|   |     | 2.3.2        | Source Biasing                                                                     | 18      |

|---|-----|--------------|------------------------------------------------------------------------------------|---------|

|   |     | 2.3.3        | Architectural Level Leakage Reduction Techniques                                   | 19      |

|   | 2.4 | Yield        | Losses Due to the Introduction of a Drowsy Mode to SRAMs .                         | 24      |

|   |     | 2.4.1        | Impact of Process Variations on Drowsy SRAMs                                       | 26      |

|   |     | 2.4.2        | Impact of Defects on Drowsy SRAMs                                                  | 29      |

|   |     | 2.4.3        | Importance of Extremal Events in Large SRAMs $\ .$                                 | 31      |

|   |     | 2.4.4        | Yield-Leakage Tradeoff in SRAMs                                                    | 32      |

|   | 2.5 | Summ         | nary                                                                               | 32      |

| 3 |     | v Fau<br>AMs | lt Models and Their Impact on Low Leakage Drowsy                                   | 34      |

|   | 3.1 | Impac        | et of Defects on Drowsy SRAMs                                                      | 35      |

|   |     | 3.1.1        | Data Retention Voltage (DRV) of Defective Cells                                    | 36      |

|   |     | 3.1.2        | Wake-up Time                                                                       | 38      |

|   | 3.2 | Simul        | ation Methodology                                                                  | 39      |

|   | 3.3 | Fault        | Modeling and Notation                                                              | 41      |

|   |     | 3.3.1        | Open Defects in SRAM Cells                                                         | 42      |

|   |     | 3.3.2        | Functional Fault Models                                                            | 43      |

|   |     | 3.3.3        | Fault Notation                                                                     | 44      |

|   | 3.4 | SRAN         | I Drowsy Faults Due to Resistive-Open Defects                                      | 45      |

|   |     | 3.4.1        | Static Drowsy Faults (SDF)                                                         | 47      |

|   |     | 3.4.2        | Dynamic Drowsy Faults (DDF)                                                        | 50      |

|   | 3.5 | Testin       | ng for Drowsy Faults                                                               | 54      |

|   |     | 3.5.1        | March RAD                                                                          | 55      |

|   |     | 3.5.2        | Test Implications of Drowsy Cache Architectures                                    | 57      |

|   |     | 3.5.3        | Sensitivity to Process Parameters Variations                                       | 58      |

|   | 3.6 | Summ         | nary                                                                               | 60      |

| 4 | 00  | -            | e Leakage Reduction of SRAMs Using Fault-Tolerance<br>es: The Yield-Power Tradeoff | e<br>61 |

|   | 4.1 | Maxir        | num Applicable Source-Bias Voltage to a Memory                                     | 62      |

|   | 4.2 | Mode         | ling the Tail of the $V_{SBmax}$ Distribution                                      | 64      |

|   |     | 4.2.1        | Simulation Setup and Process Variation Model                                       | 66      |

|   |     | 4.2.2        | Tail Modeling Procedure                                                            | 67      |

|   | 4.3 | Comp    | uting Array Yield at Elevated $V_{SB}$                                    | 68  |

|---|-----|---------|---------------------------------------------------------------------------|-----|

|   |     | 4.3.1   | Cell Failure Probability at Elevated $V_{SB}$                             | 69  |

|   |     | 4.3.2   | Array Failure Probability at Elevated $V_{SB}$                            | 70  |

|   | 4.4 | Estim   | ating Net Power Savings                                                   | 74  |

|   |     | 4.4.1   | Overhead Power Associated with Fault-Tolerance Techniques .               | 74  |

|   |     | 4.4.2   | Estimating Leakage Power Considering Process Variations $\ .$ .           | 75  |

|   | 4.5 | Simula  | ation Results and Discussion                                              | 75  |

|   |     | 4.5.1   | Yield Degradations due to Source-Biasing                                  | 76  |

|   |     | 4.5.2   | Yield-Leakage Tradeoff Using Different Fault-Tolerance Tech-<br>niques    | 79  |

|   | 4.6 | Summ    | lary                                                                      | 82  |

| 5 |     |         | on Tuning of Standby Supply Voltage in SRAMs to Reduce                    |     |

| 0 |     |         | ic Data-Retention Failures                                                | 83  |

|   | 5.1 | Inter-1 | Die Distribution of $V_{DDLmin}$                                          | 84  |

|   | 5.2 | Minim   | num Applicable Standby Voltage to a Memory Die $(V_{DDLmin})$ .           | 85  |

|   |     | 5.2.1   | Joint Impact of Inter- and Intra-Die Variations on $V_{DDLmin}$ of SRAMs  | 87  |

|   |     | 5.2.2   | Impact of the Size of Memory on its $V_{DDLmin}$                          | 87  |

|   |     | 5.2.3   | Impact of Adding Redundancy on $V_{DDLmin}$ of SRAMs                      | 87  |

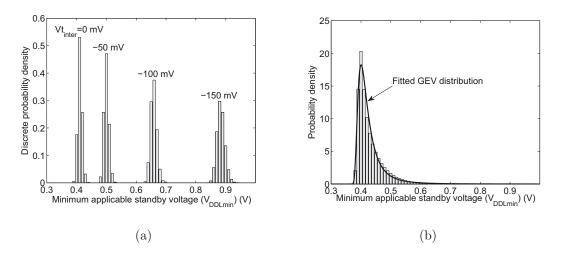

|   |     | 5.2.4   | Mathematical Model of Inter-Die $V_{DDLmin}$ Distribution                 | 88  |

|   |     | 5.2.5   | Tradeoff between Leakage Reduction and Yield of SRAMs $$ .                | 89  |

|   | 5.3 |         | ating Data-Retention Failure Probability as a Function of Supply ge       | 90  |

|   |     | 5.3.1   | Estimation of Rare Failure Events                                         | 90  |

|   |     | 5.3.2   | Simulation Methodology                                                    | 91  |

|   | 5.4 | Comp    | uting Array Yield from Cell Failure Probability                           | 97  |

|   |     | 5.4.1   | Yield of a Memory Without Redundancy                                      | 97  |

|   |     | 5.4.2   | Yield of a Memory With Redundancy                                         | 98  |

|   |     | 5.4.3   | Poisson Yield Model                                                       | 99  |

|   | 5.5 | Apply   | ing an Identical Standby Voltage to All Dies                              | 100 |

|   |     | 5.5.1   | Impact of Inter-die Variations on Data-Retention Failure Prob-<br>ability | 101 |

|   |     | 5.5.2   | Impact of Inter-die Variations on Array Failure Probability               | 103 |

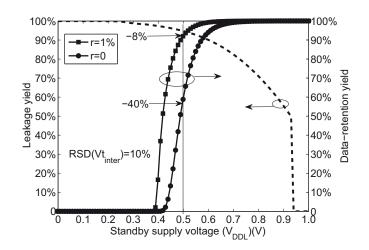

|    |       | 5.5.3   | Impact of Inter-die Variations on Data-Retention Yield $\ldots$                               | 104 |

|----|-------|---------|-----------------------------------------------------------------------------------------------|-----|

|    |       | 5.5.4   | Impact of Process Parameters Variations on Leakage Yield                                      | 106 |

|    |       | 5.5.5   | Tradeoff Between Data-Retention and Leakage Yield $\ . \ . \ .$                               | 107 |

|    | 5.6   | Yield I | Enhancement by Standby Supply Voltage Tuning                                                  | 108 |

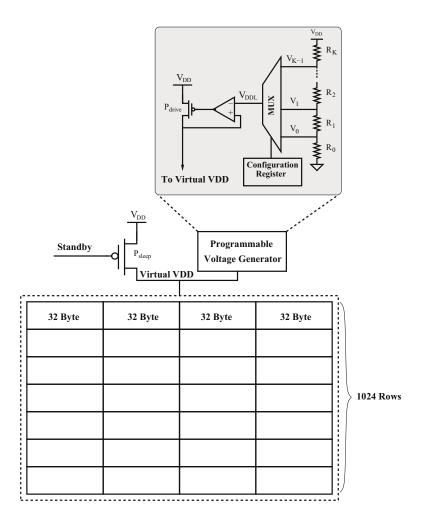

|    |       | 5.6.1   | Post-Silicon Standby Voltage Tuning                                                           | 108 |

|    |       | 5.6.2   | Overhead of the Tuning Technique                                                              | 112 |

|    | 5.7   | Simula  | ation Results for Yield Enhancements and Discussions                                          | 113 |

|    |       | 5.7.1   | $V_{DDLmin}$ Distribution                                                                     | 114 |

|    |       | 5.7.2   | Yield Enhancements by Standby Voltage Tuning                                                  | 115 |

|    |       | 5.7.3   | Yield Losses Due to Dies With Excess Leakage in Case of Volt-                                 |     |

|    |       |         | age Tuning                                                                                    | 117 |

|    |       | 5.7.4   | Uncorrelated Inter-Die Shift for NMOS and PMOS $\ . \ . \ .$ .                                | 117 |

|    | 5.8   | Summ    | ary                                                                                           | 118 |

| 6  | Con   | clusio  | ns and Future Work                                                                            | 119 |

|    | 6.1   | Contri  | butions and Main Results                                                                      | 120 |

|    | 6.2   | Future  | e Work                                                                                        | 122 |

|    |       | 6.2.1   | More Efficient Tests for Detection of Drowsy Faults $\ . \ . \ .$ .                           | 122 |

|    |       | 6.2.2   | A Built-In Technique for Self-Tuning of Standby Supply Voltage<br>Against Run-Time Variations | 123 |

|    |       | 6.2.3   | Compensating for Systematic Intra-Die Variations                                              | 124 |

| Re | efere | nces    |                                                                                               | 125 |

# List of Figures

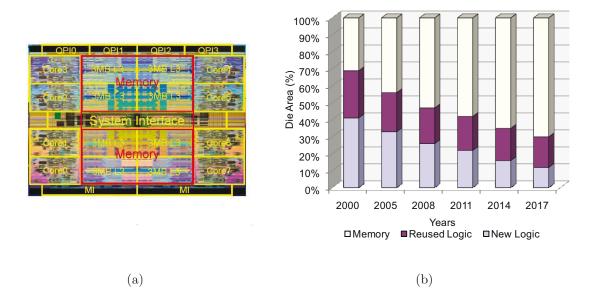

| 1.1 | (a) 24MB of on-chip L3 cache in Intel's 8-core Xeon processor. Adapted from [4] (Copyright 2010 IEEE) and (b) projections of logic/memory composition of low-power SOC designs [5].                              | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

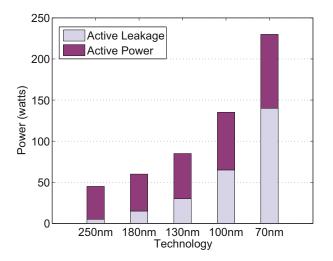

| 1.2 | Increasing leakage power fraction of total processor power consumption<br>with technology scaling [6]                                                                                                            | 3  |

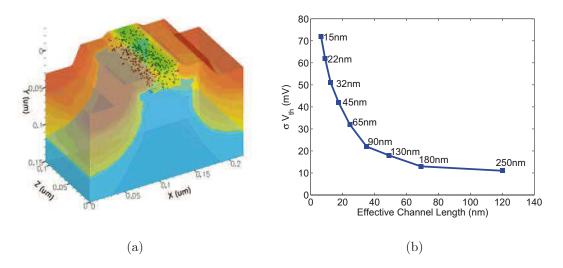

| 1.3 | (a) Random dopant fluctuations, adapted from [7] (Copyright 2008 Intel) and (b) scaling trend of threshold voltage variation $[8, 9, 5]$ .                                                                       | 4  |

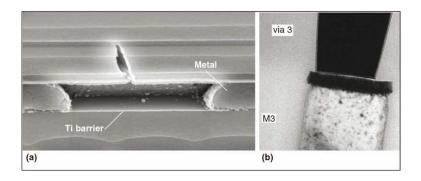

| 1.4 | Examples of weak open defects: (a) cross section of a metal open line, the metal cavity and formation of a weak open due to the Ti barrier, and (b) a resistive via. Adapted from [11] (Copyright 2002 IEEE)     | 5  |

| 2.1 | A typical SRAM organization.                                                                                                                                                                                     | 12 |

| 2.2 | Conventional 6T SRAM cell                                                                                                                                                                                        | 13 |

| 2.3 | SRAM cell leakage currents during standby mode. The leaking tran-<br>sistors are shown in dotted lines                                                                                                           | 15 |

| 2.4 | (a) SRAM cell leakage currents at reduced supply voltage and (b) circuit simulation results for leakage currents at reduced supply voltages for an SRAM cell in a 45-nm technology at $T = 27^{\circ}C$ .        | 17 |

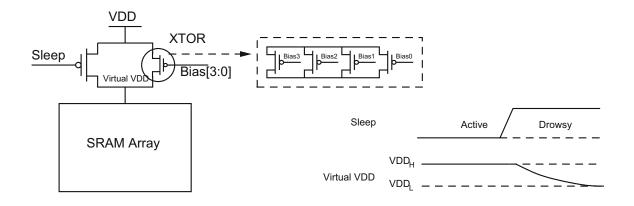

| 2.5 | SRAM supply scaling by power gating. The programmable bias tran-<br>sistors enable controlling of the virtual VDD                                                                                                | 18 |

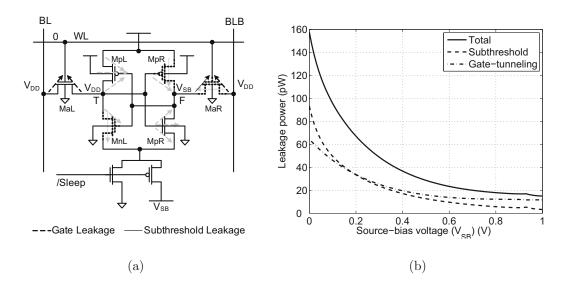

| 2.6 | (a) SRAM cell leakage currents at raised source-line voltage and (b) circuit simulation results for leakage currents at raised source-line voltages for an SRAM cell in a 45-nm technology at $T = 27^{\circ}C.$ | 19 |

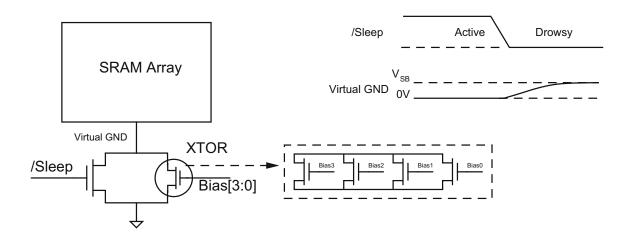

| 2.7 | SRAM ground gating. The programmable bias transistors enable to control the virtual GND                                                                                                                          | 20 |

| 2.8 | DRG-Cache.                                                                                                                                                                                                       | 21 |

| 2.9 | Leakage reduction technique using periodic sleep policy                                                                                                                                                          | 22 |

| 2.10 | Leakage reduction with wake-up counters                                                                                                                                                                                                                                                                | 23 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

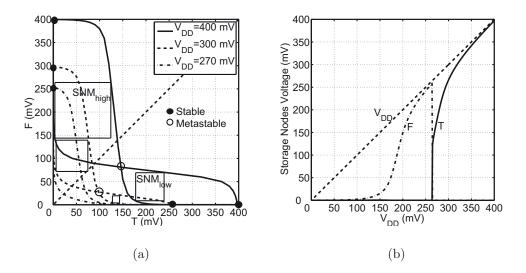

| 2.11 | (a) Butterfly curve of a balanced cell at different supply voltages. SNM of the cell is reduced to zero at $V_{DD} = 200mV$ , and (b) Waveforms for the voltage of storage nodes, i.e., $T$ and $F$ , of a balanced cell as the supply voltage is reduced down to zero.                                | 25 |

| 2.12 | Inter and intra die variation modeling                                                                                                                                                                                                                                                                 | 27 |

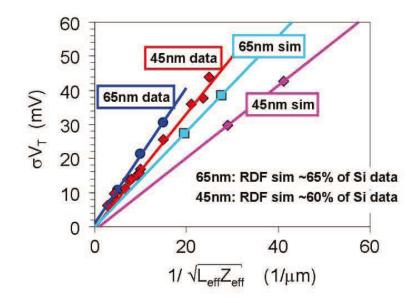

| 2.13 | Random within-die variations in threshold voltage in 65-nm and 45-nm technologies. Adapted from [7] (Copyright 2008 Intel).                                                                                                                                                                            | 28 |

| 2.14 | (a) Butterfly curves of an imbalanced cell at different supply voltages.<br>$SNM_{low}$ is reduced to zero before $SNM_{high}$ at $V_{DD} = 270mV$ . and<br>(b) waveforms for the voltage of storage nodes, i.e., $T$ and $F$ , of an<br>imbalanced cell as the supply voltage is reduced down to zero | 29 |

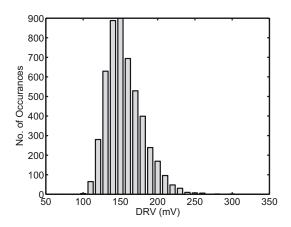

| 2.15 | Histogram of the DRV from a 5000 point Monte Carlo simulation of SRAM cells in a 45-nm predictive technology node                                                                                                                                                                                      | 30 |

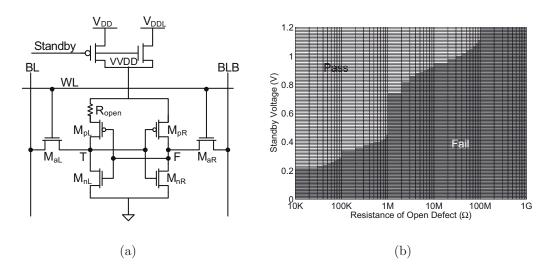

| 2.16 | (a) A resistive open defect in pull-up path of a 6T SRAM cell, (b) simulation results showing the reduction of DRV in defective SRAM cells.                                                                                                                                                            | 31 |

| 3.1  | (a) A resistive open defect in pull-up path of a 6T SRAM cell, (b)<br>Shmoo plot showing pass/fail status of an SRAM cell for two parame-<br>ters: i) resistance of open defect and ii) standby voltage                                                                                                | 37 |

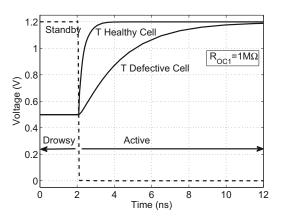

| 3.2  | Simulation results showing the difference in wake-up time of a healthy cell and a defective cell.                                                                                                                                                                                                      | 39 |

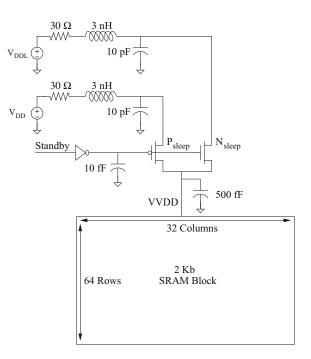

| 3.3  | Simulation setup.                                                                                                                                                                                                                                                                                      | 41 |

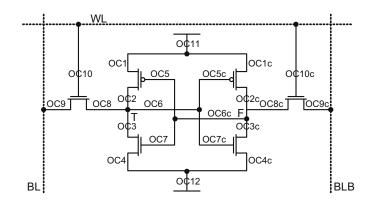

| 3.4  | All possible open defects in a 6T SRAM cell                                                                                                                                                                                                                                                            | 43 |

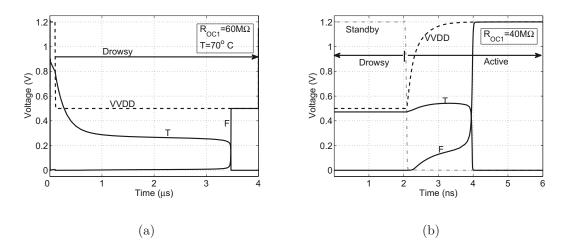

| 3.5  | HSPICE simulation results of a defective cell exhibiting (a) a drowsy data-retention fault (DDRF) and (b) a drowsy transition fault (DTF).                                                                                                                                                             | 48 |

| 3.6  | (a) Simulation results of a defective cell exhibiting (a) a drowsy read-destructive fault (DRDF) and (b) a drowsy incorrect read fault (DIRF).                                                                                                                                                         | 51 |

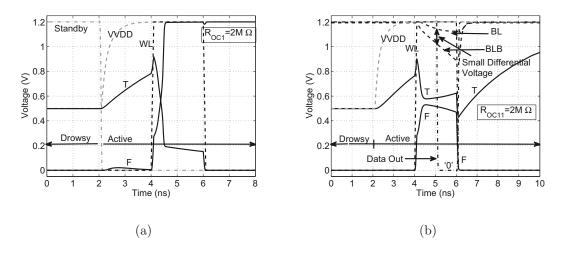

| 3.7  | (a) Monte Carlo simulation results of (a) a healthy cell and (b) a defective cell with $R_{OC1} = 40M\Omega$ , when the March RAD test is performed on them.                                                                                                                                           | 59 |

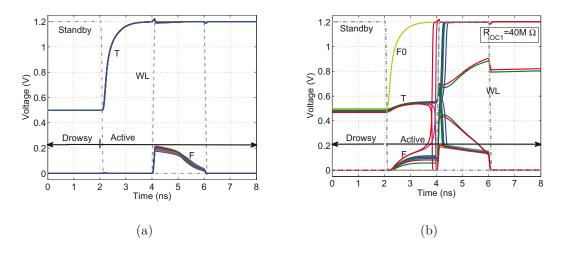

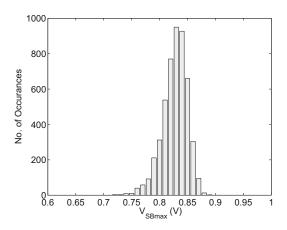

| 4.1  | Histogram of maximum applicable source-bias voltage to SRAM cells $(V_{SBmax})$ obtained by 5000 Monte Carlo simulations                                                                                                                                                                               | 63 |

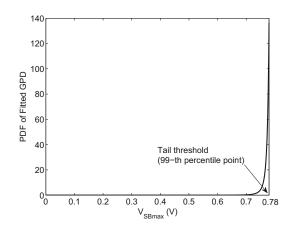

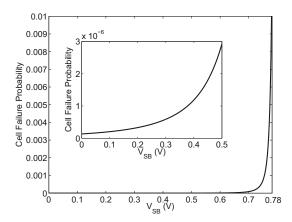

| 4.2  | Fitted GPD to the tail of $V_{SBmax}$ distribution ( $\sigma Vt/Vt = 10\%$ )                                                                                                                                                                                                                           | 69 |

| 4.3  | Cell failure probability at elevated source-bias voltages up to the first percentile point. $(\sigma V t/V t = 10\%)$ .                                                                                                                                                                                | 70 |

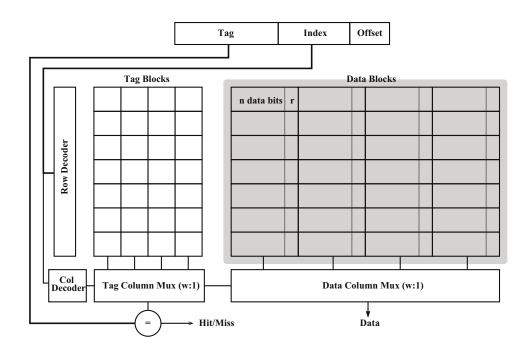

| 4.4  | Organization of a typical on-chip cache. Leakage reduction is applied only to the data array.                                                                                                                                                                                                                                                                    | 71  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

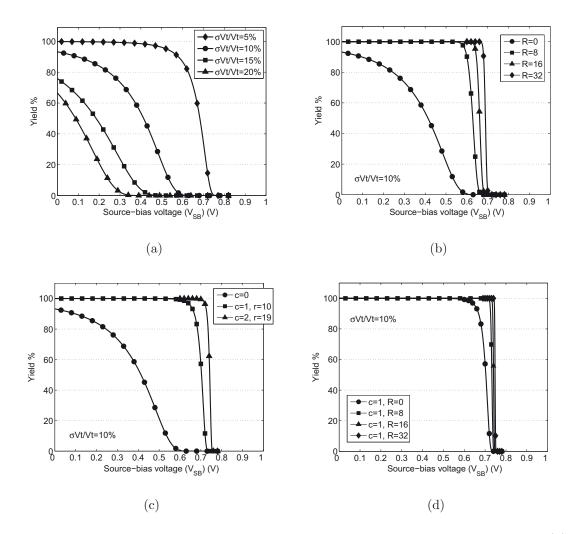

| 4.5  | Yield of the 64KB SRAM as a function of the source-bias voltage (a) at different levels of process variations when no fault-tolerance technique is present, (b) when $R = 8$ , $R = 16$ , or $R = 32$ redundant rows are added, (c) when SEC-DED or DEC-TED codes are employed, (d) when $R = 8$ redundant rows in combination with a SEC-DED code are employed. | 77  |

| 4.6  | The yield-leakage tradeoff in SRAMs: the leakage reductions and yield losses in a 64KB memory as the source-bias voltage is raised                                                                                                                                                                                                                               | 80  |

| 4.7  | Feasible reduced leakage of a 64KB memory using various fault-<br>tolerance techniques subject to a 99% target yield. (100% leakage<br>means no reduction is possible.)                                                                                                                                                                                          | 81  |

| 5.1  | A conceptual illustration of the long tail $V_{DDLmin}$ distribution and probability of functional array versus standby supply voltage                                                                                                                                                                                                                           | 84  |

| 5.2  | Histogram of the DRV from a 5000 point Monte Carlo simulation of SRAM cells in a 45-nm predictive technology node                                                                                                                                                                                                                                                | 86  |

| 5.3  | Inter and intra-die variation modeling                                                                                                                                                                                                                                                                                                                           | 93  |

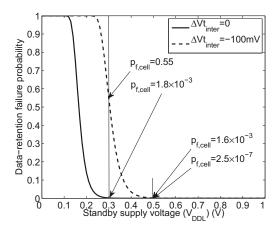

| 5.4  | (a) Probability of DRFs versus standby voltage at two different inter-<br>die corners.                                                                                                                                                                                                                                                                           | 101 |

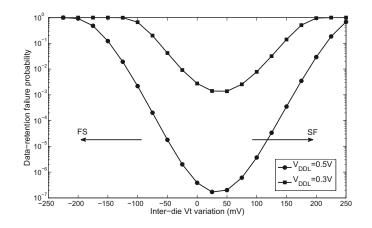

| 5.5  | Probability of DRFs at various inter-die corners for $V_{DDL} = 0.5V$ and $V_{DDL} = 0.3V$                                                                                                                                                                                                                                                                       | 102 |

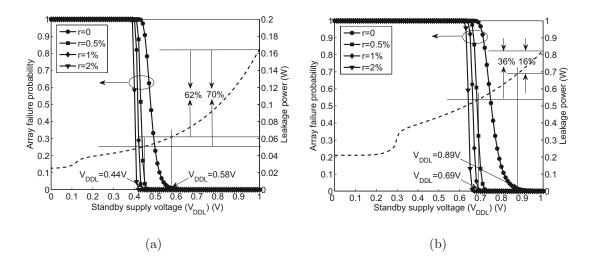

| 5.6  | Array failure probability of a 1Mb memory versus standby voltage with different levels of available redundancy $(r = R/M)$ at (a) nominal-Vt corner, and (b) $\Delta V t_{inter} = -100mV$ .                                                                                                                                                                     | 104 |

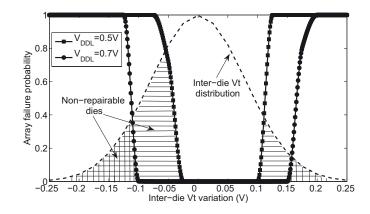

| 5.7  | Dies at some skewed process points become non-repairable by the available redundancy $(r = 1\%)$ , when an identical standby voltage is applied to all dies.                                                                                                                                                                                                     | 105 |

| 5.8  | Data-retention and leakage yield versus standby voltage.                                                                                                                                                                                                                                                                                                         | 105 |

|      |                                                                                                                                                                                                                                                                                                                                                                  |     |

| 5.9  | Standby supply voltage tuning scheme.                                                                                                                                                                                                                                                                                                                            | 111 |

| 5.10 | (a) Distribution of $V_{DDLmin}$ at various inter-die corners, and (b) Distribution of $V_{DDLmin}$ for memory dies in a process with $\sigma_{Vt_{inter}} = 10\%$ .                                                                                                                                                                                             | 114 |

| 5.11 | (a) Yield of a 1Mb memory versus relative standard deviation (RSD) of inter-die Vt variation at fixed and tuned standby voltages with no redundancy, and (b) with 1% redundancy ratio                                                                                                                                                                            | 115 |

# List of Tables

| 3.1 | Single-Cell Static and Dynamic Faults In Drowsy SRAM Due To PODs. | 46 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | March RAD Test                                                    | 55 |

| 3.3 | March RAD Fault Coverage                                          | 57 |

| 4.1 | The organization of the simulated memory array.                   | 76 |

# Acronyms

| BIST    | Built-In Self Test                             |

|---------|------------------------------------------------|

| CDF     | Cumulative Distribution Function               |

| CMOS    | Complementary Metal-Oxide-Semiconductor        |

| DDRDF   | Drowsy Deceptive Read Destructive Fault        |

| DDRF    | Drowsy Data-Retention Fault                    |

| DEC-TED | Double Error Correcting-Triple Error Detecting |

| DIRF    | Drowsy Incorrect Read Fault                    |

| DPM     | Defects Per Million                            |

| DRDF    | Drowsy Read Destructive Fault                  |

| DRF     | Data-Retention Fault                           |

| DRV     | Data-Retention Voltage                         |

| DTF     | Drowsy Transition Fault                        |

| DUSF    | Drowsy Undefined State Fault                   |

ECC Error Correcting Code

- EVT Extreme Value Theory

- FFM Functional Fault Model

- FP Fault Primitive

- GEV Generalized Extreme Value

- GPD Generalized Pareto Distribution

- IS Importance Sampling

- ITRS International Technology Roadmap for Semiconductors

- MC Monte Carlo

- MLE Maximum Likelihood Estimation

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- MPSoC Multi-Processor System-on-a-Cchip

- MTTF Mean Time To Failure

- NMOS N-channel MOSFET

- OSBV Optimum Source-Bias Voltage

- PDF Probability Density Function

- PMOS P-channel MOSFET

- POD PMOS Open Defect

- PTM Predictive Technology Model

- PWM Probability Weighted Moments

- RDF Random Dopant Fluctuation

- RSD Relative Standard Deviation

- SD Spot Defect

- SDRF Standby Data Retention Fault

- SEC-DED Single Error Correcting-Double Error Detecting

- sF strong Fault

- SNM Static Noise Margin

- SoC System-on-a-Chip

- SRAM Static Random Access Memory

- wF weak Fault

## Chapter 1

# Introduction

Aggressive scaling of CMOS devices in the last four decades has enabled the semiconductor industry to meet its ever-increasing demand for higher performance and higher integration densities. However, this trend is encountering several major challenges in the nano-meter era, due to the high integration levels as well as the physical limitations of semiconductor devices. High power consumption is one of the major challenges of integrated circuit design in nano-scale technologies [1]. For high-performance applications, large power dissipations within a small die area are resulting in alarming temperatures, posing serious reliability concerns. For battery operated devices, on the other hand, increased power consumption is drastically limiting the battery lifetime.

Embedding memory into the dies is proven to be a very effective way to improve the performance of systems while reducing their overall power consumption [1, 2, 3]. On-chip cache memory plays a major role in the enhancement of the performance of microprocessors by providing a higher bandwidth and lower latency, while consuming much less power compared to logic. As a result, increasingly larger fractions of chip area are being dedicated to on-chip memories in state-of-the-art microprocessors and

Figure 1.1. (a) 24MB of on-chip L3 cache in Intel's 8-core Xeon processor. Adapted from [4] (Copyright 2010 IEEE) and (b) projections of logic/memory composition of low-power SOC designs [5].

system-on-chips (SoCs). For example, the latest 8-core Xeon® processor from Intel® contains 24MB of on-chip L3 (level 3) cache [4], that occupies the majority of the die area (see Figure 1.1(a)). It is predicted that this trend will continue in the future technologies as shown in Figure 1.1(b), where in 2017, more than 70% of the die area will be occupied by memory [5].

Being the largest block on the chip, a low power robust memory design is crucial for the overall reliability, yield and power of the SoCs. There are various design options to realize embedded memories [2]. Currently, static random access memory (SRAM) is the most popular choice for high performance designs, mainly due to its fast access time and compatibility with the mainstream CMOS bulk technology [1, 2]. With scaling to sub-100nm regime, satisfying the multi-dimensional requirements of low power, high yield and reliability of SRAMs has become increasingly difficult, due to the generally conflicting nature of these requirements [3]. Some of the major challenges of SRAM design are as follows:

Figure 1.2. Increasing leakage power fraction of total processor power consumption with technology scaling [6].

Leakage power: With technology scaling, transistors exhibit larger leakage currents [1], and as a result, the leakage power consumption in microprocessors and SoCs has started to dominate the total chip power consumption (see Figure 1.2) [6]. A significant fraction of the chips' leakage power is dissipated by SRAMs, as they must remain powered on all the time to retain their data, while their large number of transistors constantly draw leakage power [1]. A low leakage operation of SRAMs is particularly critical for portable devices, as they spend most of their battery lifetime in standby mode.

Process parameters variations: As process geometries continue to shrink, controlling the variations in device parameters during fabrication is becoming increasingly difficult [10, 7]. Random variations, e.g., random dopant fluctuations (RDF) (see Figure 1.3(a)), are particularly troublesome as they are unpredictable, and thus, despite the systematic variations, they cannot be minimized by design-time techniques. The intrinsic random variations are inversely proportional to the gate area, and thus their impact on device parameters, e.g., threshold voltage, are significantly increasing with technology scaling [8, 9] (see Figure 1.3(b)). SRAMs, in particular, are profoundly

Figure 1.3. (a) Random dopant fluctuations, adapted from [7] (Copyright 2008 Intel) and (b) scaling trend of threshold voltage variation [8, 9, 5].

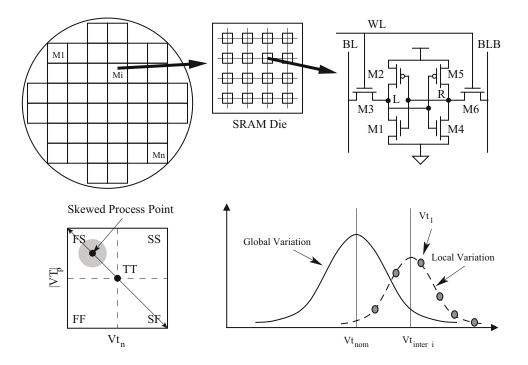

impacted by random variations as they use minimum-size transistors to obtain higher integration densities [1, 3]. The process parameters variations translate into fluctuations in SRAM metrics such as minimum operating voltage, access time, etc. Modern embedded SRAMs contain millions of transistors, thus some cells will necessarily exhibit behavior far out in the tail of the metrics distribution (as far as 6-7 $\sigma$ ) [1]. Such extreme cases can easily fall out of the design specifications and cause failures. Thus, to maintain a sufficient yield in scaled technologies, it is imperative to effectively deal with the process variation issues in SRAMs.

Manufacturing defects: Due to manufacturing inaccuracies, spots of extra, missing or undesired material can cause undesired shorts or opens in circuits. With the increasing complexity of processes and the large number of interconnect layers, the probability of these defects is increasing with technology scaling. Traditionally, fault models have been developed to describe the behavior of SRAMs, in the presence of such defects, during normal operating modes. However, new operating modes, e.g., sleep mode, are being introduced to SRAMs in modern integrated circuits. The introduction of these new operating modes to SRAMs can cause new faulty behaviors to

Figure 1.4. Examples of weak open defects: (a) cross section of a metal open line, the metal cavity and formation of a weak open due to the Ti barrier, and (b) a resistive via. Adapted from [11] (Copyright 2002 IEEE).

emerge. Therefore, there can be defects in SRAM cells that while not causing a malfunction during the normal operating mode, start to do so when memory is switched to other operating modes. Examples of such defects can be weak opens or shorts that connect nodes weakly by having a finite parasitic resistance (see Figure 1.4) [11]. Such weak defects can deteriorate various metrics of SRAM cells without causing a hard failure in normal operating conditions. However, they can turn into a strong fault at deteriorated or low power operating conditions such as the reduced supply voltage during a sleep mode. Thus, it is crucial to test memories in all operating modes, in order to minimize the number of defective parts.

### 1.1 Motivation

As mentioned above, due to the dedication of a significant fraction of the chip area to SRAMs in modern microprocessors and SoCs, their low power dissipation, high yield and high reliability are crucial for the overall success of the designs. Unfortunately, fulfilling the joint requirements of low power dissipation and high yield/reliability of SRAMs poses a "design paradox". Turning the circuits knobs to reduce the leakage power consumption of SRAMs also results in the reduction of the cells robustness, making them vulnerable to parametric data-retention failures (DRF)s. The failure rates are accentuated in new technologies due to the everincreasing process parameters variations and manufacturing imperfections. Moreover, due to the sheer number of data cells in contemporary on-chip memories, even a very small failure probability can translate to significant yield losses. Thus, it is crucial to maintain the correct operation across the entire array, while trying to reduce the power dissipation of SRAMs. In this thesis, we have made an attempt to address the contradictory design requirements of joint low-power dissipation and high yield in SRAMs, and propose solutions for their yield-aware leakage power reduction.

### **1.2** Contributions and Proposed Solutions

## 1.2.1 New Fault Behaviors and Their Impact on Low-Leakage SRAMs

We have demonstrated that there are faults, not sensitized in normal operation, that appear when an SRAM is switched to a low-leakage drowsy operating mode. Fault models for these newly observed fault behaviors are developed and described in this thesis. Based on the derived fault models, a new low-complexity test algorithm, called March RAD, is proposed, that is capable of detecting all the drowsy faults as well as the traditional simple faults.

It is also shown that as the supply voltage is reduced to cut down leakage, a larger number of defects are sensitized, resulting in more failing cells within a memory array. This establishes a tradeoff between leakage reduction and yield of SRAMs.

Details of this part of our work are described in Chapter 3 of this thesis. The following submitted paper reports the results of this study:

A. Nourivand, A. J. Al-Khalili, and Y. Savaria, "Analysis of resistive open defects in drowsy SRAM cells," submitted to the *Journal of Electronic Testing: Theory* and Applications (JETTA).

## 1.2.2 Modeling the Yield-Leakage Tradeoff in Large SRAM Arrays Considering Extreme Failure Events

A main contribution of this thesis is the modeling of the yield-leakage tradeoff in SRAM arrays. This analysis is essential for a design-time determination of the supply voltage to be applied to an SRAM subject to a target yield and leakage budget. Unlike the existing models, we have considered the impact of rare failure events, due to the extreme process parameters variations, on the yield-leakage tradeoff. We have employed concepts from extreme value theory (EVT) to model the rare failure events in SRAMs at scaled supply voltages. The results show that even a moderate scaling of the standby supply voltage results in significant yield losses in large non-fault-tolerant SRAMs, due to the failure of cells with extremely skewed process parameters. The yield losses grow with the size of memory and the aggravating process parameters variations.

The modeling methodology and the results of the yield-leakage tradeoff analysis are described in Chapter 4 of this thesis. The following paper summarizes the results of this part of our work:

A. Nourivand, A. J. Al-Khalili, and Y. Savaria, "Aggressive Leakage Reduction of SRAMs Using Fault-Tolerance Techniques: The Yield-Power Tradeoff," submitted to the *IEEE Transactions on Circuits and Systems I*.

### 1.2.3 Aggressive Leakage Reduction of SRAMs Using Fault-Tolerance Techniques

We investigated the aggressive leakage reduction of SRAMs using fault-tolerance techniques. Using the proposed model for yield-leakage tradeoff, it was shown that employing fault-tolerance techniques allows for efficient leakage reduction of SRAMs by providing tolerance to data-retention failures during the sleep mode. The results showed that repairing a memory by adding a small number of redundant resources or incorporating simple error correcting codes (ECC) allows for significant leakage reductions while incurring negligible yield losses. The combination of redundancy and ECC, however, allowed us to reach the bounds of the leakage reduction. In particular, the latter approach was shown to be viable when variations are large and the activity factor of memory is small.

The details of this investigation are reported in Chapter 4 of this thesis. The results of this part of our work are reported in the above-mentioned paper (i.e., paper No. 2).

# 1.2.4 Post-Silicon Tuning of Standby Supply Voltage for Reduction of Parametric Yield Losses Due to Dataretention Failures

We proposed a post-silicon standby supply voltage tuning technique for SRAMs to compensate for the die-to-die process parameters variations, and thereby decrease yield losses due to the parametric data-retention failures during the sleep mode. It was shown that applying an identical standby voltage to all dies, regardless of their specific process parameters variations, results in the failure of some dies, due to the data-retention failures, and thus it entails significant yield losses. To avoid yield losses, we proposed to tune the standby voltage of each individual die to its corresponding minimum level. A test algorithm was presented to identify the minimum applicable standby voltage to each individual memory die after manufacturing. The effects of adding redundant resources on the minimum applicable standby voltage to a memory die was also investigated. Simulation results showed that yield can be enhanced significantly by the combined effect of repairing and standby voltage tuning, even when heavy process variations are present.

The details of this study are elaborated in Chapter 5 of this thesis. The following paper is submitted based on the results from this part of our research:

3. A. Nourivand, A. J. Al-Khalili, and Y. Savaria, "Post-silicon tuning of standby supply voltage in SRAMs to reduce yield losses due to parametric data-retention failures," accepted for publication in the *IEEE Transactions on Very Large Scale Integration (VLSI) Systems.*

### **1.3** Organization of the Dissertation

The organization of this dissertation is as follows:

In Chapter 2, we provide the background on SRAM organization and operation, and we discuss the challenges of SRAM design in nanoscale technologies. The design paradox of low power and high yield is explained in this chapter.

In Chapter 3, results of fault injection and simulation of drowsy SRAMs are presented, and the newly observed single-cell static and dynamic drowsy faults are described. Then, a March test for detection of all drowsy faults as well as the simple traditional faults is proposed.

Chapter 4 investigates the aggressive leakage reduction of SRAMs using different

fault-tolerance techniques. A simulation methodology is presented for modeling the tail distribution of cell failures at scaled voltages. Then, mathematical relations are developed to compute the yield of a complete memory array from the failure probability of a single cell at scaled rail-to-rail voltages. Finally, the simulation results for a 64KB memory are presented, and the effectiveness of various fault-tolerance techniques for leakage reduction of SRAMs with minimal yield loss is analyzed.

In Chapter 5, a post-silicon standby supply voltage tuning scheme for SRAMs is presented to decrease yield losses due to the parametric data-retention failures during the standby mode, while reducing the leakage currents effectively. An implementation of the proposed tuning technique is demonstrated. The simulation results for the inter-die distribution of minimum applicable standby voltage of memory dies, and the corresponding yield enhancements by the proposed technique are presented.

Chapter 6 summarizes the contributions of this research and draws the main conclusions.

## Chapter 2

# Background

In order to study the design for the low power and high yield dilemma in SRAMs, an understanding of their organization and operation is required. Hence, in this chapter, we first provide a brief description of SRAMs architecture and operation. Then, the sources of power dissipation in SRAMs are discussed and the existing leakage reduction techniques are reviewed. The impact of these techniques on the stability of SRAM cells and the corresponding yield losses are evaluated.

### 2.1 SRAMs Organization and Operation

In the following, we briefly describe the organization and operation of SRAMs.

#### 2.1.1 SRAMs Organization

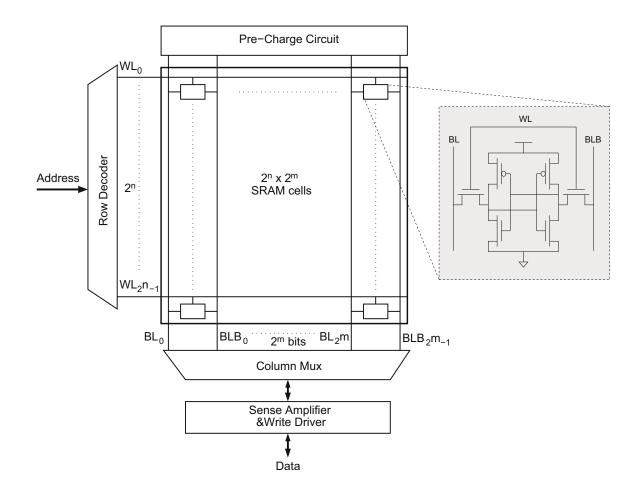

An SRAM consists of an array of memory cells along with peripheral circuits that enable reading from and writing into the array. The basic organization of an SRAM array is shown in Figure 2.1. The memory array consists of  $2^n$  rows and  $2^m$  columns of cells. During a memory access, the supplied address is decoded by the row decoder

Figure 2.1. A typical SRAM organization.

to select one of the rows by activating its corresponding wordline (WL). To obtain a proper aspect ratio (length:width), multiple data words are usually placed in one row [12]. Thus, a column multiplexer (MUX) is used to select only the target data word. Data words are usually a group of 16, 32, or 64 bits. For example, in a memory with a 32-bit data width and  $2^m = 256$  bits per row, each row contains 8 data words.

During a read operation, the bitlines (BL and BLB) are first charged to VDD by the pre-charge circuit (see Figure 2.1). Then, the wordline of the accessed row is activated and the BLs (BLBs) starts to discharge if their corresponding cell contains data '0' ('1'). Sense amplifiers are used to detect a very low differential voltage between BL and BLB of each column, speeding up the read cycle. A timing control

Figure 2.2. Conventional 6T SRAM cell.

unit usually triggers the sense amplifiers at the right time, so they capture and send the correct data to the I/O drivers. For a write operation, the write drivers charge or discharge the bitlines according to the input data and then the corresponding wordline is activated to write the data into the cells.

### 2.1.2 SRAM Cells

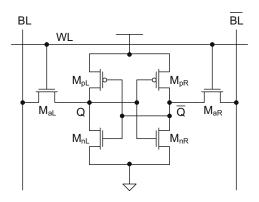

SRAM cells have a latch type structure that enables them to retain their data as long as the power supply is maintained. Different SRAM cells have been proposed in the literature, e.g., 4-transistor (4T) [12], 6T [12], 8T [13, 14], 10T cells [15]. However, the 6T cell is still the most popular option for embedded memory design at the present time due to its small area and stable operation.

A schematic of the conventional 6T SRAM cell is shown in Figure 2.2. The two pull-down transistors (MnR, MnL) and the two pull-up transistors (MpR, MpL) comprise a pair of cross-coupled inverters which operates as a static latch to store one bit of data [12]. Access to the storage nodes, T and F, for reading and writing is enabled by wordline WL which controls the two access transistors MaR and MaL. The two bitlines, BL and BLB, transfer both the stored data and its inverse in and out of the cell.

The size of the cell should be as small as possible to achieve high memory density and high yield. However, reliable operation of the cell imposes some sizing constraints. In particular, a careful sizing of the transistors is necessary to avoid a destructive read. The read operation can be destructive because the access and the pull-down transistors are in conflict during the read time and the voltage of the low storage node rises to a voltage higher than ground. The cell ratio, defined as  $r = W_{pull-down}/W_{access}$ , controls the voltage rise and it must be large enough to prevent the voltage of node '0' from rising above the driver transistor's threshold voltage [12]. A reliable write operation, on the other hand, is ensured if the access transistor can overcome the pull-up transistor and pull down the voltage of storage node '1' to a voltage lower than the threshold voltage of the pull-down transistor. The cell pull-up ratio, defined as  $q = W_{pull-up}/W_{access}$ , must be small enough to ensure that the storage node voltage is pulled below the driver transistor threshold voltage, allowing the cell to flip [12].

### 2.2 Leakage Power Dissipation in SRAMs

Power is dissipated as leakage and active switching in SRAMs. Due to a low switching factor in SRAMs, leakage power tends to be the dominant part of the power consumption [1, 6]. The subthreshold leakage current, gate-tunneling current, and the reverse-biased junction current are known to be the major components of the leakage consumption in sub-100nm technologies [16]. The results in this work are based on simulations using an industrial 90-nm technology and a predictive 45-nm technology (PTM) [17]. Our simulations show that the junction current is negligible compared to the other two leakage mechanisms in these technologies. Therefore, we

Figure 2.3. SRAM cell leakage currents during standby mode. The leaking transistors are shown in dotted lines.

will consider only the subthreshold and gate leakage currents in this work. Figure 2.3 shows the main leakage contributors in a 6T SRAM cell.

#### 2.2.1 Subthreshold Current

The subthreshold current in MOSFETs is the off-state leakage current from drain to source of the device. As supply voltage scales down with technology, the transistor threshold voltage is scaled down as well in order to maintain performance. Due to the exponential dependence of subthreshold leakage current on the threshold voltage [12], it is exponentially growing with technology scaling [6].

### 2.2.2 Gate-Tunneling Current

The gate-oxide thickness,  $t_{ox}$ , is rapidly decreasing with each technology node to achieve higher speeds [6]. A thin gate-oxide layer of less than 2-3 nm can cause a dramatic increase in gate-tunneling currents. However, the introduction of new gatedielectric materials with high dielectric constant (high-k) beyond 45nm technologies has reduced the gate-tunneling currents significantly [18].

### 2.3 SRAM Leakage Reduction Techniques

SRAM leakage reduction techniques can be broadly categorized into statepreserving and non-state preserving. State-preserving techniques do not alter the contents of the memory, while in non-state-preserving techniques the data is lost. Non-state-preserving techniques generally save more leakage by completely removing the power from SRAMs. The latter techniques are only applicable if a copy of the data is retained in some other place, e.g., a higher level memory. Therefore, they can be applied to write-through caches, for example. However, shutting off the memory can incur a significant dynamic power overhead due to the induced misses that require accesses to higher level memories. Therefore, state-preserving techniques are preferred for caches despite their lower leakage reduction capabilities [19, 20]. These techniques have been widely applied to instruction and data caches at all hierarchy levels, i.e., L1, L2, and L3 [19, 20, 21, 22].

Various techniques, e.g., voltage scaling [19], source biasing [23], and body biasing [24] have been proposed in the literature to reduce leakage power of SRAMs by switching the cells into a state-preserving low-leakage mode during the idle periods [25, 26]. Scaling the rail-to-rail voltage of SRAMs, by voltage scaling or source biasing, is a more attractive technique due to its lower cost and higher leakage savings [27]. Thus, in this work, we focus on the leakage reduction of SRAMs using the dynamic voltage scaling and source biasing techniques.

#### 2.3.1 Supply Voltage Scaling

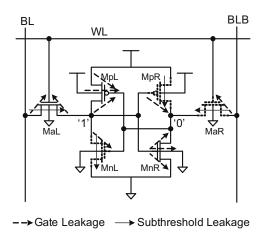

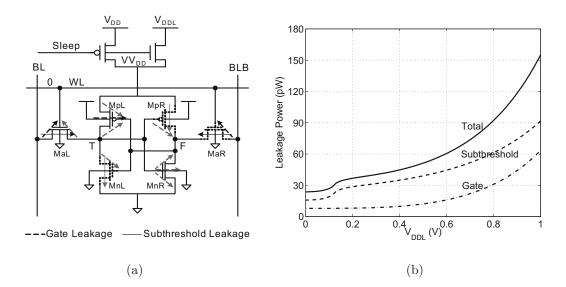

Figure 2.4(a) shows the supply voltage scaling technique for a typical SRAM cell. When the cell is in the active mode, i.e., Sleep = 0, the nominal supply voltage  $(V_{DD})$  is applied to the cell. However, when cells are idle, they are placed in a *drowsy mode*

Figure 2.4. (a) SRAM cell leakage currents at reduced supply voltage and (b) circuit simulation results for leakage currents at reduced supply voltages for an SRAM cell in a 45-nm technology at  $T = 27^{\circ}C$ .

by activating *Sleep* signal, where a low standby voltage  $(V_{DDL})$  is applied to the cell. The leakage power is significantly reduced in the drowsy mode due to the decreases in both subthreshold and gate leakage currents. The reduced leakage currents are shown in gray in Figure 2.4(a). The leakage current versus supply voltage of a typical SRAM cell in a 45-nm technology is shown in Figure 2.4(b). As can be seen, the leakage currents reduce sub-linearly with the standby voltage.

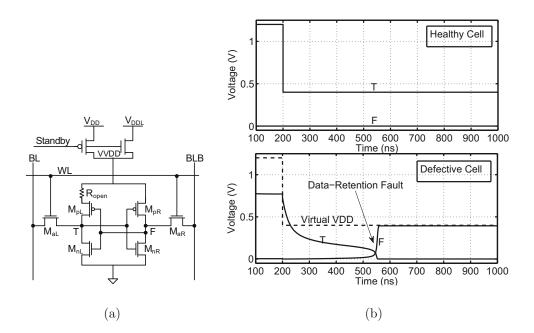

Scaling of the supply voltage during the drowsy mode can be alternatively realized by power gating the cells using a large sleep transistor as shown in Figure 2.5 [18]. This removes the need for an additional on-chip supply voltage, i.e.,  $V_{DDL}$  During the drowsy mode, the large sleep transistor is turned off, and thus the virtual VDD node starts to discharge due to the SRAM leakage currents. To stabilize the voltage of virtual VDD node at a pre-defined level ( $V_{DDL}$ ), small bias transistor(s) are placed in parallel with the sleep transistor (see Figure 2.5). To allow for post-silicon compensation of process variations impact, the bias transistors are made programmable, e.g., through fuses [18].

Figure 2.5. SRAM supply scaling by power gating. The programmable bias transistors enable controlling of the virtual VDD.

#### 2.3.2 Source Biasing

The rail-to-rail voltage of SRAM cells can be alternatively scaled by raising the voltage of their source line. Figure 2.6(a) shows a typical SRAM cell with the sourcebiasing technique. During the active mode the /*Sleep* signal is high and thus the virtual GND node is tied to ground. To switch the SRAM to the drowsy mode, the /*Sleep* signal is set low and a higher supply voltage ( $V_{SB}$ ) is applied to the source-line of cells. Both the subthreshold and gate leakage currents are affected by source-biasing. The reduced leakage currents are shown in gray in Figure 2.6(a). The leakage current versus source biasing voltage ( $V_{SB}$ ) of a typical SRAM cell in a 45-nm technology is shown in Figure 2.6(b). As can be seen, the leakage currents reduce efficiently with the raising of the source-bias voltage.

Similar to the power gating, the SRAM cells can be ground gated to raise the virtual ground voltage of cells. Figure 2.7 shows the ground gating technique, where a sleep transistor is used to cut off the ground node of an SRAM array during the sleep mode. As a result, the virtual ground node is charged to a predefined level ( $V_{SB}$ ) by the leakage currents of the SRAMs, eliminating the need for an extra supply voltage. The bias transistors are used to tune the upper limit of the source-bias voltage. To

Figure 2.6. (a) SRAM cell leakage currents at raised source-line voltage and (b) circuit simulation results for leakage currents at raised source-line voltages for an SRAM cell in a 45-nm technology at  $T = 27^{\circ}C$ .

compensate for the process variations effect on the virtual ground node voltage, bias transistors are made programmable [18, 28].

#### 2.3.3 Architectural Level Leakage Reduction Techniques

Architectural level leakage reduction techniques work together with the circuit level techniques, presented in the previous section, to reduce the leakage power dissipation. Voltage scaling and source-biasing techniques are equally applicable to SRAM cells in all memory structures.

In general, cache leakage reduction techniques can be divided into two categories [27]: i) passive leakage reduction and ii) active leakage reduction techniques. In passive leakage reduction techniques, the whole memory is switched to the sleep mode during the idle periods of the system. Whereas, in active leakage reductions, only portions of the memory are dynamically switched between active and drowsy (sleep) modes during the system run-time. At any time window, the accesses to memory are usually concentrated only on a small subset of the active lines, and all the other lines

Figure 2.7. SRAM ground gating. The programmable bias transistors enable to control the virtual GND.

are idle, dissipating leakage power. Thus, active leakage reduction techniques achieve a higher leakage reduction efficiency compared to the static techniques [29].

In active leakage reduction techniques, blocks of memory, at different granularity, are dynamically activated and deactivated based on a mode management policy. Coarse-grained techniques reduce the hardware overhead by employing policies that apply to large blocks of cache, while fine-grained techniques suppress leakage at small blocks of cache at the cost of extra overhead. In order to obtain the best power saving results with the minimal performance penalty, the access profile of a memory structure needs to be considered when determining the following parameters:

- Sleep granularity: the size of the smallest block of cells which can be switched to the sleep mode independently, e.g., row-by-row, bank-by-bank.

- Mode management policy: the policy that manages the switching of memory blocks between the active and sleep operating modes.

The cache management policies can be categorized as: 1) per-access wake-up, 2) periodic sleep, and 3) wake-up counter. The above techniques are described below.

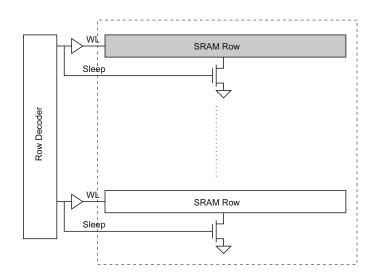

Figure 2.8. DRG-Cache.

#### 2.3.3.1 Per-access wake-up

With this policy, only the row (bank) that is going to be accessed is awakened, and then it is put back in the sleep mode immediately after the access. This policy is implemented in the data-retention gated-ground cache (DRG-Cache) [21] as shown in Figure 2.8. In this scheme, all the cells in a row share a common sleep transistor that is activated by the row's wordline. Hence, the cells are turned on only during the access times. Another leakage reduction architecture called segmented virtual grounding (SVGND) [30] implements this policy by ground gating columns of cells. This policy is the simplest, however it can incur large power overheads due to the frequent switchings between active and sleep modes. For L2 caches, a row-by-row drowsy scheme using the per-access wake-up policy is proposed in [21]. However, power saving is reported to be only about 50% due to the large dynamic power overhead of frequent switching between active and drowsy modes.

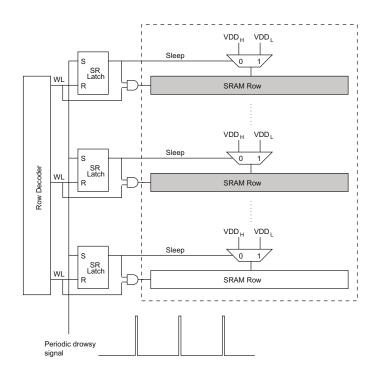

Figure 2.9. Leakage reduction technique using periodic sleep policy.

#### 2.3.3.2 Periodic sleep

Due to the temporal locality of reference in caches, an accessed data line will most probably be accessed again after a short period of time. Thus, it is more efficient to keep an accessed line alive for a period of time after its first access. Periodic sleep exploits this property in caches to reduce the power overhead by removing the unnecessary switchings between the active and sleep modes. In this policy, when a line (bank) is about to be accessed it is awakened and is kept in the active mode. However, the whole memory is periodically put into the sleep mode by a global periodic signal. The period of this signal is determined so that the optimum energy efficiency is obtained [19]. This policy is implemented for a data cache in [19], and supply voltage scaling is employed as the leakage reduction technique. The architecture of this technique is shown in Figure 2.9. To store the state of each row, an SR latch is used, which is reset when a row is accessed for the first time, applying  $VDD_H$  to the row. All the latches are set every 2000 clock cycles, to switch the whole memory array to

Figure 2.10. Leakage reduction with wake-up counters.

the drowsy mode, by applying a lower supply voltage  $(VDD_L)$ . For L1 data caches, authors in [19] reported that a fine-grained, i.e. row-by-row, drowsy scheme with periodic sleep policy, achieves 60% - 75% leakage power reduction across SPEC2000 benchmarks [19].

#### 2.3.3.3 Wake-up counter

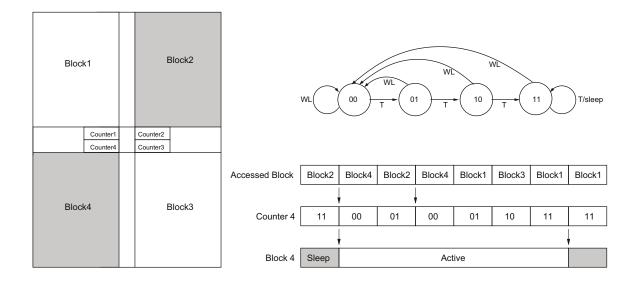

Another technique to reduce the power overhead due to unnecessary switching between active/sleep modes is to use a wake-up counter. Here, a counter is associated with each bank (row) of the memory that switches it to the sleep mode if a certain time interval elapses from its last access. This interval is determined as the break-even point between leakage power and switching power overhead. Figure 2.10 shows the operation of this technique on a block-based memory. The wake-up interval is assumed to be 4 clock cycles in this example. The counter associated with a bank is reset if an access is issued to a data in that bank, otherwise, the counter is incremented. When counter counts up to 4, it activates the sleep signal of the bank, placing it in the sleep mode. The counter and the operating mode of *Block4* are shown in Figure 2.10 for a sample access scenario. At the first access to *Block4*, its counter is reset and thus it is awakened. At the second access to *Block4*, the counter is reset and thus the block is still kept in the active mode. Eventually, as there is no access to *Block4* for the next 4 cycles, it is automatically placed in the sleep mode. The sub-array based drowsy scheme proposed for L3 caches [22] reported as about 95% leakage reduction using 16 clock cycle wake-up intervals.

# 2.4 Yield Losses Due to the Introduction of a Drowsy Mode to SRAMs

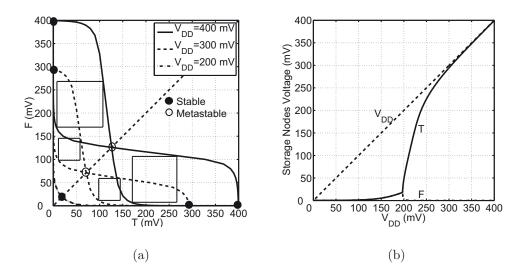

To maximize the leakage reductions in SRAMs, it is desirable to reduce the railto-rail voltage of cells as low as possible during the standby mode [31]. However, this also causes the SRAM cells to become less stable and thus fail to retain their data reliably. Indeed, an SRAM cell is capable of retaining data as long as its static noise margin (SNM) is positive. SNM of an SRAM cell is an accepted measure of the stability, and is defined as the minimum dc noise voltage necessary to flip the state of a cell. A graphical representation of SNM is presented by drawing the transfer characteristic of a cell's left inverter and the mirror transfer characteristic of its right inverter and finding the side of the maximum square nested between these two curves [32] as shown in Figure 2.11(a).

Switching memory cells to a drowsy mode, e.g., by lowering the supply voltage, reduces their noise margin [33, 19], as shown in Figure 2.11(a). As can be seen, as long as the SNM is larger than zero, the cell has two stable states, thus it retains its data. At  $V_{DD} = 200mV$ , SNM becomes zero and the regenerative effect of cross-coupled inverters of an SRAM cell is disabled. At this supply voltage, the voltage of both

Figure 2.11. (a) Butterfly curve of a balanced cell at different supply voltages. SNM of the cell is reduced to zero at  $V_{DD} = 200mV$ , and (b) Waveforms for the voltage of storage nodes, i.e., T and F, of a balanced cell as the supply voltage is reduced down to zero.

storage nodes converge to a common stable point. The behavior of the storage nodes of a perfectly balanced cell as the supply voltage is reduced down to zero is shown in Figure 2.11(b), assuming that the initial state of the cell is '1', i.e., T = 1.2V and F = 0V (see Figure 2.2). As  $V_{DD}$  is reduced, the true node (T) follows it and the false node (F) remains at zero. However, below 300mV, T starts to deviate from  $V_{DD}$ , and eventually at  $V_{DD} = 200mV$ , both nodes converge to a certain voltage and the state of the cell is lost. The supply voltage at which the SNM of a cell shrinks to zero is called its data-retention voltage (DRV).

Excessive process parameters variations and manufacturing imperfections in nanoscale technologies are increasingly resulting in "weak cells" with a severely degraded stability [34, 35, 36]. Switching cells to a drowsy mode reduces the cells stability, however, weak cells, which are inherently less stable, can be severely affected. Introduction of a drowsy mode to SRAMs can result in failure of the weak cells, and thereby degrade yield drastically. In the following, we explain the impact of these two factors on the failure probability of SRAM cells.

#### 2.4.1 Impact of Process Variations on Drowsy SRAMs

As process geometries continue to shrink, controlling the variation in device parameters during fabrication is becoming increasingly difficult [10, 7]. The variations in device features can be either due to systematic or random variations in the fabrication process. Systematic variations are classified as across-field and layout-dependent variations [37]. Across-field systematic variations are caused by lithographic and etching sources such as dose, focus and exposure variations etc. [37]. These variations exhibit a strong spatial correlation and thus cause discrepancies in the behavior of identical devices at different locations on a photo-mask reticle. The layout-dependent systematic variations, on the other hand, can cause two layouts of the same device to have different characteristics even when they are located close to each other. Systematic variations are predictable and can be modeled based on factors such as layout structure and the surrounding topological environment [37]. Random variations, on the other hand, are unpredictable and are caused by random uncertainties in the fabrication process such as microscopic fluctuations in the number and location of dopant atoms in the channel region, gate line-edge and line-width roughness, (LER) and (LWR) respectively, [37]. Random variations can cause significant mismatch among two identical devices placed next to each other. These random variations are intrinsic to devices as they cannot be eliminated by external control of manufacturing processes or layout techniques [37].

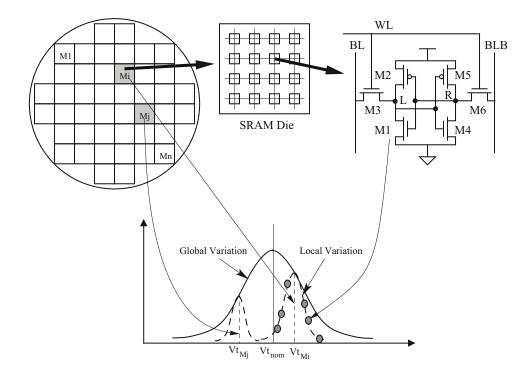

Depending on the scale of variations, they are classified as inter-die (die-to-die) and intra-die (within-die) variations. Inter-die variations are caused due to systematic variations from lot-to-lot, wafer-to-wafer, and within-wafer variations, and affect every element on a chip equally (see Figure 2.12). However, intra-die variations are caused by both the systematic and random variations and result in discrepancies among properties of identical devices on the same chip as shown in Figure 2.12.

Figure 2.12. Inter and intra die variation modeling.

Traditionally, the inter-die fluctuations have been the main concern in CMOS digital circuit designs, and the intra-die fluctuations have been neglected [38]. However, in new technologies the intra-die variations have exceeded the inter-die fluctuations [38]. The intra-die variations contain both the systematic and the random components of the process parameters variations. Random variations are more concerning as the systematic variations can be minimized by layout techniques [37]. The random variations effect the current drive capability of transistors by causing variations in the threshold voltage and channel dimensions of the device. Threshold voltage variation due to RDFs in the channel area is the most dominant source of variation in current technologies [7]. Variation in the threshold voltage (Vt) of transistors is inversely proportional to the square root of the channel area [39] (see Figure 2.13). With technology scaling, the random variations are becoming the dominant part of intra-die variations. For example,  $\sigma Vt$  as large as 45mV is reported for the Intel's 45-nm technology as shown in Figure 2.13. As minimum-size transistors are used in

Figure 2.13. Random within-die variations in threshold voltage in 65-nm and 45-nm technologies. Adapted from [7] (Copyright 2008 Intel).