# Amplifier-Based Tuneable RF Predistortion for Radio-over-Fibre Systems

Jingfang Liu

A Thesis

In the Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering) at

Concordia University

Montréal, Québec, Canada

March 2011

© Jingfang Liu, 2011

## CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

| This is to cer | ify that the thesis prepared                          |                          |                                      |

|----------------|-------------------------------------------------------|--------------------------|--------------------------------------|

| By:            | Jingfang Liu                                          |                          |                                      |

| Entitled:      | "Amplifier-based Tuneable R<br>Systems"               | F Predistortion for Rad  | io-over-Fiber                        |

| and submitted  | d in partial fulfillment of the red                   | quirements for the degre | ee of                                |

|                | Master of A <sub>l</sub>                              | oplied Science           |                                      |

| -              | h the regulations of this Univerginality and quality. | rsity and meets the acce | pted standards with                  |

| Signed by the  | e final examining committee:                          |                          |                                      |

|                | Dr. D. Qiu                                            |                          | Chair                                |

|                | Dr. A. Ben Hamza, CIISE                               |                          | Examiner, External<br>To the Program |

|                | Dr. P. Valizadeh                                      |                          | Examiner                             |

|                | Dr. G. Cowan                                          |                          | Supervisor                           |

|                | Dr. X. Zhang                                          |                          | Supervisor                           |

| Approved by    | Dr. W. E. Lynch Department of Electrical and          |                          | _<br>g                               |

|                | _20                                                   | Dr. Robin                | A. L. Drew                           |

Dr. Robin A. L. Drew

Dean, Faculty of Engineering and

Computer Science

#### **ABSTRACT**

#### **Amplifier-Based Tuneable RF Predistortion for Radio-over-Fibre Systems**

#### Jingfang Liu

Semiconductor laser diodes (LDs) have been extensively employed for directly transporting wideband multicarrier signals in radio-over-fibre (RoF) systems. However, an inherent characteristic of LDs, the nonlinearity, always has been a fundamental problem in fibre-optic systems. When optical subcarrier modulation (SCM) is used, nonlinear characteristics will induce harmonic and intermodulation distortion (IMD) products that degrade the system's performance significantly. Therefore, it is essential to improve the linearity of RoF systems.

An amplifier-based tuneable radio frequency (RF) predistortion circuit for RoF systems is proposed to linearize the distributed feedback laser diode (DFB-LD) in the range of  $0.7 \sim 2.5$  GHz. Instead of conventional insertion loss linearization techniques, in this work, a high gain amplifier-based tuneable predistortion circuit was designed. The designed amplifier-based predistortion circuit consists of an impedance matching network and a distortion generation block. To match the distortion generator to the  $50\,\Omega$  characteristic impedance of an RF source, a capacitively cross-coupled common gate (CCC-CG) broadband matching network is designed. The tuneability of the predistortion circuit is achieved by adjusting the bias current of the triplet-core circuit in the predistortion generation block. The predistortion integrated circuit (IC) is designed with TSMC90nm technology. Performance of the investigated predistortion is simulated with Cadence Virtuoso Hspice/Spectre circuit simulator. Compared with free running LDs.

this predistortion circuit achieves more than  $10 \, dB$  third-order IMD (IMD3) suppression over the operating frequency range. The proposed scheme is suitable for broadband RF optical transmission applications.

Theoretical analysis of the nonlinear transfer function of the predistortion circuit and DFB-LD has been performed. The nonlinearity of transistors under different configurations is analyzed.

#### Acknowledgements

I would like to thank many people who made my life at Concordia memorable and enjoyable. First and foremost, I wish to acknowledge my advisors Dr. X. Zhang and Dr. G. Cowan-they are great research mentors who gave me strong motivation in my research. I really appreciate the opportunity they provided and their considerate guidance, patient advice and support for me to finish this work.

I want to thank Dr. B. Hraimel for performing the measurement, PhD candidate Frank Bernardo and VLSI/CAD Specialist Ted Obuchowicz for their help with CAD tools. Thanks to my friends in photonics lab and VLSI lab for their helpful discussions with optical components, CAD tools and friendship.

Also I have sincere appreciation to the Le Fonds québécois de la recherche sur la nature et les technologies (FQRNT), Quebec, Canada for supporting this research project.

Finally, I must reserve my special thanks for my significant others. I would like to thank my parents, my sister, brother and my husband Luo Ma for their unconditional love and support throughout my life.

## **Table of Contents**

| ABSTRACTiii                                                                           |

|---------------------------------------------------------------------------------------|

| Acknowledgementsv                                                                     |

| Table of Contentsvi                                                                   |

| List of Figuresix                                                                     |

| List of Tablesxii                                                                     |

| List of Acronymsxiii                                                                  |

| List of Principal Symbolsxvi                                                          |

| Chapter 1 Introduction1                                                               |

| 1.1 Introduction1                                                                     |

| 1.2 Motivation and Review of Technologies                                             |

| 1.3 Objective8                                                                        |

| 1.4 Thesis Scope and Contributions9                                                   |

| 1.5 Thesis Outline                                                                    |

| Chapter 2 The Principle of Predistortion12                                            |

| 2.1 Introduction to Distributed Feedback Laser Diode12                                |

| 2.2 Mathematical Analysis of Predistortion                                            |

| 2.2.1 Modeling of Nonlinear Transmission Characteristics of a DFB-LD in RoF Systems14 |

| 2.2.2 Mathematical Analysis of Predistortion                                          |

| 2.3 Triplet-Core Circuit                                                              |

| 2.3.1 Nonlinear Transconductance of a Single Transistor and Differential Circuits21   |

| 2.3.2 Introduction of Gilbert Cell and the <i>Multi-tanh</i> Principle                |

| 2.3.3 Proposed Triplet-Core Circuit                                                   |

| 2.4 Conclusion                                                                | 33    |

|-------------------------------------------------------------------------------|-------|

| Chapter 3 Input Impedance Matching Network Design of The Proposed Trip        | olet- |

| core Circuit                                                                  | 34    |

| 3.1 Introduction                                                              | 34    |

| 3.2 Capacitively Cross-coupled Common Gate LNA                                | 35    |

| 3.2.1 Noise Analysis of the CCC-CG LNA                                        | 40    |

| 3.2.2 S-parameter Test Setup of Fully Differential Circuit                    | 41    |

| 3.2.3 Design and Simulation Results                                           | 42    |

| 3.3 Nonlinearity Analysis of the CG LNA and CCC-CG LNA                        | 45    |

| 3.5 Conclusion                                                                | 47    |

| Chapter 4 Design of the Amplifier-based Tuneable RF Predistortion             | 48    |

| 4.1 Introduction                                                              | 48    |

| 4.2 Design Guidelines of the Amplfier-Based Tuneable RF Predistortion Circuit | 48    |

| 4.2.1 System Architecture Consideration                                       | 49    |

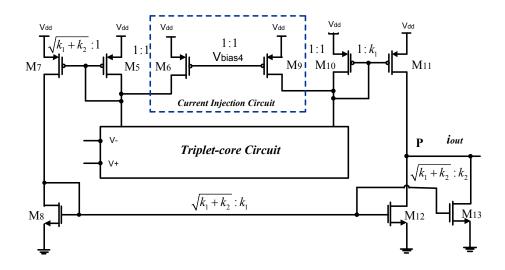

| 4.2.2 Current Mirror Design                                                   | 51    |

| 4.2.2.1 Basic Current Mirror                                                  | 52    |

| 4.2.2.2 Cascode Current Mirror                                                | 53    |

| 4.2.2.3 Active Current Mirror                                                 | 55    |

| 4.2.3 Current Injection Technique                                             | 57    |

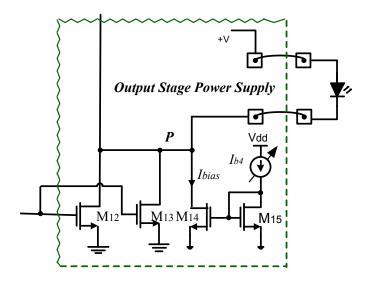

| 4.2.4 Laser Bias Circuit and Output Stage Power Supply                        | 58    |

| 4.3 Circuit Performance Evaluation                                            | 59    |

| 4.3.1 Two-Tone Signal Simulation                                              | 59    |

| 4.3.2 Tuneability Evaluation                                                  | 65    |

| 4.4 Comparison of This Work with Previous Predistortion                       | 67    |

| 4.5 Conclusion       | 68 |

|----------------------|----|

| Chapter 5 Conclusion | 70 |

| 5.1 Conclusion       | 70 |

| 5.2 Future Work      | 71 |

| References           | 73 |

## **List of Figures**

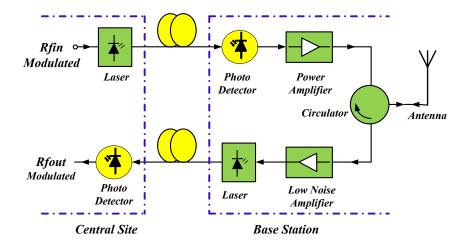

| Figure 1.1 Radio-over-fibre system [1]                                                    | 2  |

|-------------------------------------------------------------------------------------------|----|

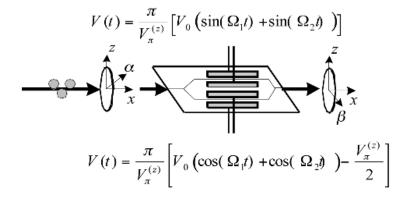

| Figure 1.2 Mixed polarization linearization of MZM for OSSB modulation [4].               | 4  |

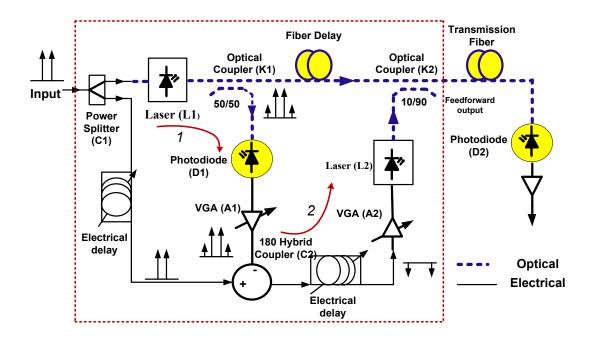

| Figure 1.3 Diagram of a feedforward system [6].                                           | 5  |

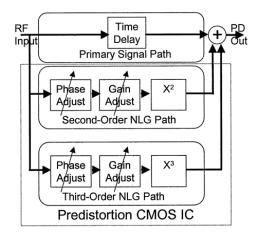

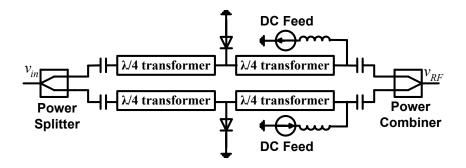

| Figure 1.4 Predistortion block diagram [7].                                               | 7  |

| Figure 1.5 Schematic diagram of anti-parallel diodes predistortion [11].                  | 8  |

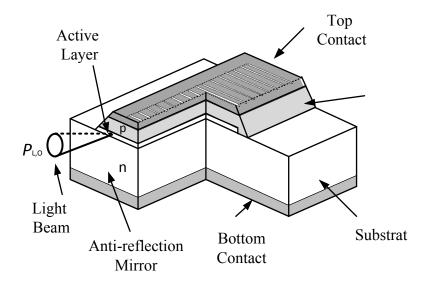

| Figure 2.1 Diagram of a DFB-LD with Bragg grating on the top [12].                        | 13 |

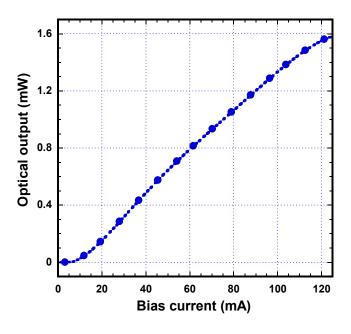

| Figure 2.2 Measured nonlinear characteristics of a DFB-LD.                                | 14 |

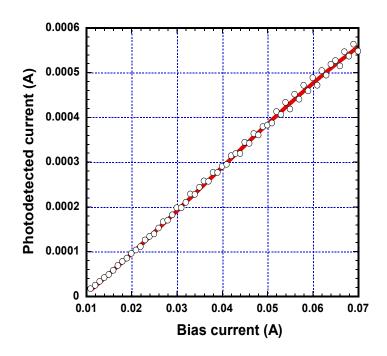

| Figure 2.3 Measured nonlinear characteristics of the DFB-LD.                              | 16 |

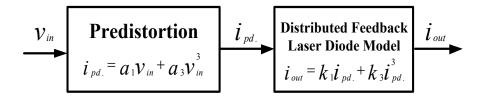

| Figure 2.4 Block diagram of predistortion circuit and DFB-LD.                             | 17 |

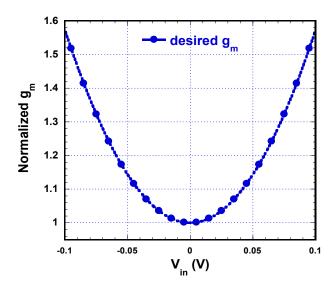

| Figure 2.5 Desired $g_m$ curve of the predistortion circuit.                              | 19 |

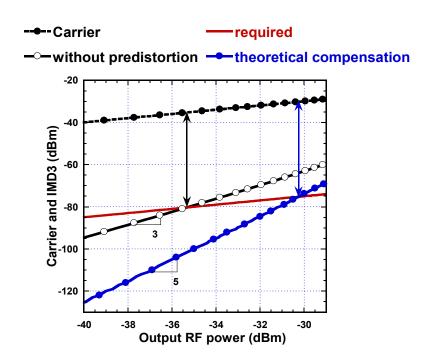

| Figure 2.6 Nonlinear characteristic of DFB-LD with theoretical predistortion cancellation | 20 |

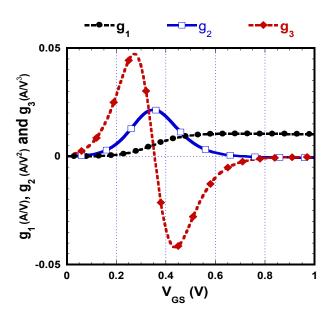

| Figure 2.7 Simulated DC characteristics of a W/L (10 µm/100 nm) NMOSFET.                  | 22 |

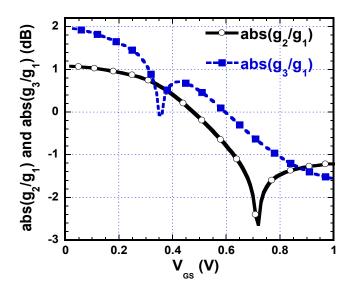

| Figure 2.8 Simulated $g_2/g_1$ and $g_3/g_1$ ratio of a W/L (10 $\mu$ m/100 nm) NMOSFET.  | 22 |

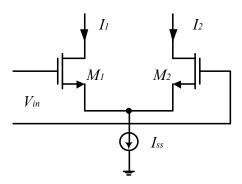

| Figure 2.9 Basic differential pair.                                                       | 23 |

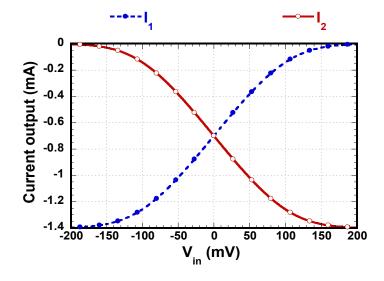

| Figure 2.10 Voltage-current (V-I) characteristic of the differential pair.                | 25 |

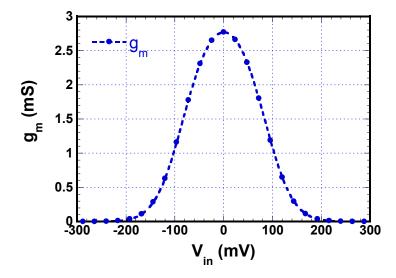

| Figure 2.11 $g_m$ of transistor $M_1$ .                                                   | 25 |

| Figure 2.12 Basic Multi-tanh doublet [21]                                                 | 27 |

| Figure 2.13 Dual $g_m$ components for the doublet.                                        | 28 |

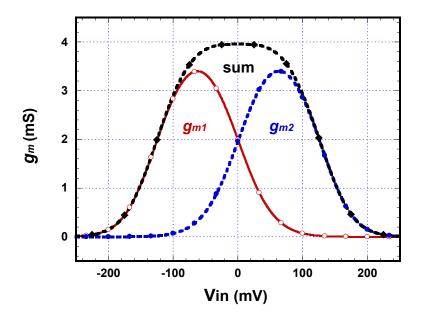

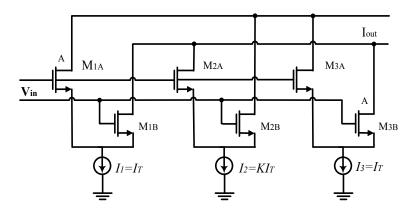

| Figure 2.14 Transconductance of the proposed doublet circuit.                             | 29 |

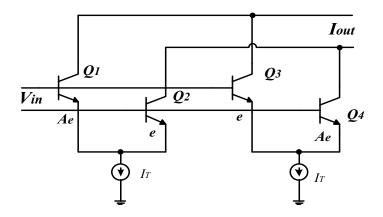

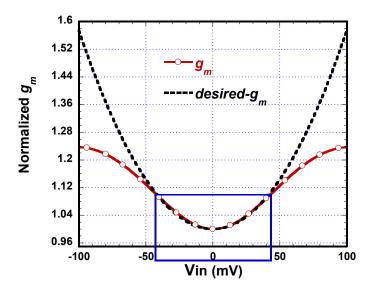

| Figure 2.15 Schematic diagram of the proposed triplet-core circuit.                       | 30 |

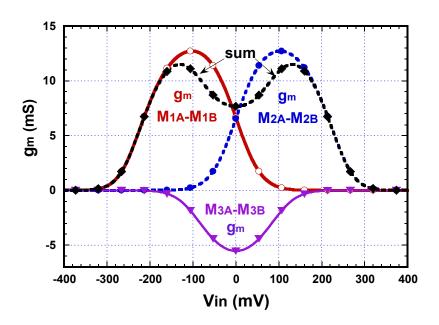

| Figure 2.16 $g_m$ curves of proposed triplet-core circuit.                                | 31 |

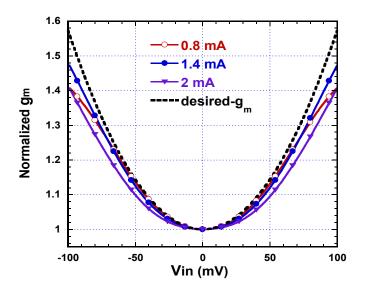

| Figure 2.17 Overall $g_m$ curves by tuning $I_I$ and $I_3$ .                              | 32 |

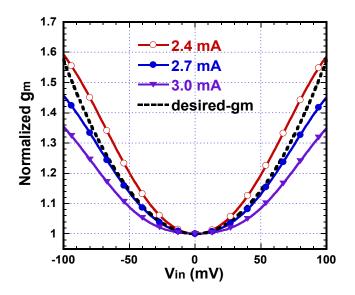

| Figure 2.18 Overall $g_m$ curves by tuning $I_2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

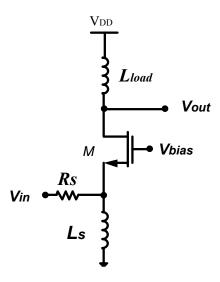

| Figure 3.1 Basic CG LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36     |

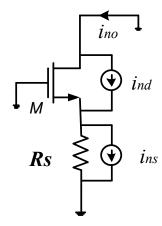

| Figure 3.2 Dominant noise sources in the basic CG LNA [29].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37     |

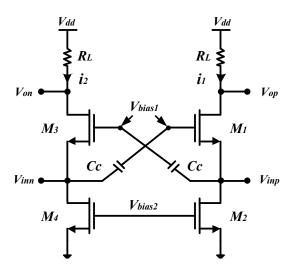

| Figure 3.3 Proposed fully differential CCC-CG LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38     |

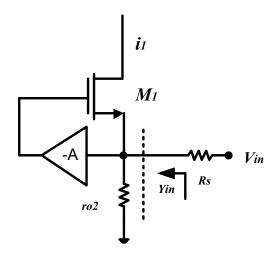

| Figure 3.4 CG stage with $g_m$ -boosting feedback [28].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39     |

| Figure 3.5 A normal CG LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39     |

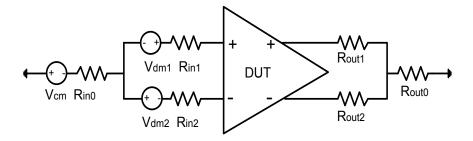

| Figure 3.6 Traditional test setup for simulating a differential amplifier [30].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41     |

| Figure 3.7 Improved test setup of designed circuit [31].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42     |

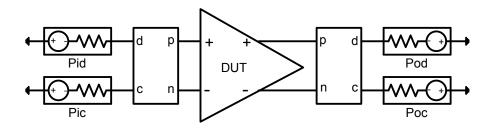

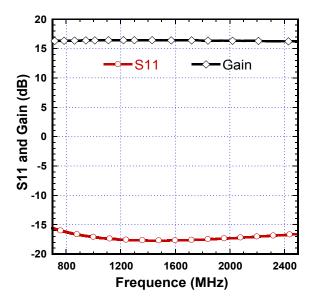

| Figure 3.8 Simulated gain and S11from 0.7 to 2.5 <i>GHz</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43     |

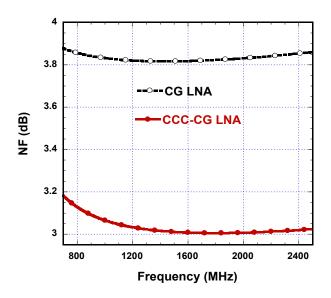

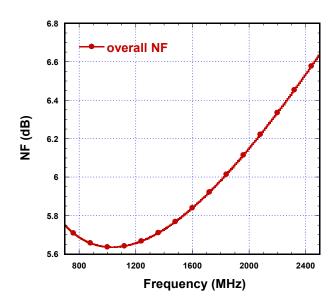

| Figure 3.9 Simulated NF from 0.7 to 2.5 <i>GHz</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44     |

| Figure 3.10 Simulated NF of the predistortion circuit from 0.7 to 2.5 <i>GHz</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44     |

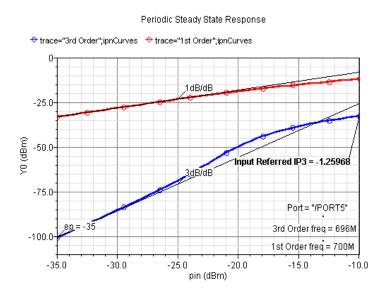

| Figure 3.11 Third-order input intercept point of the CG LNA when $f_0$ =0.7 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45     |

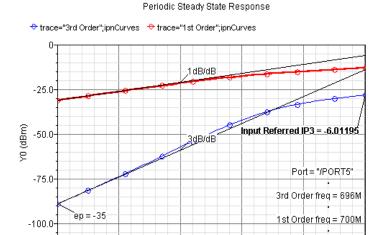

| Figure 3.12 Third-order input intercept point of the CCC-CG LNA when $f_0 = 0.7$ GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46     |

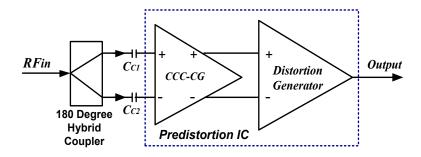

| Figure 4.1 Block diagram of the system architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49     |

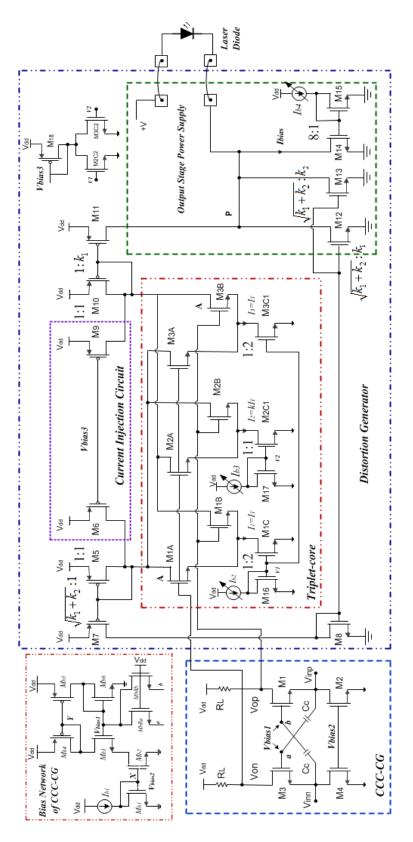

| Figure 4.2 Chip architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50     |

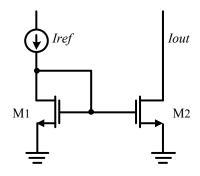

| Figure 4.3 A basic current mirror.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52     |

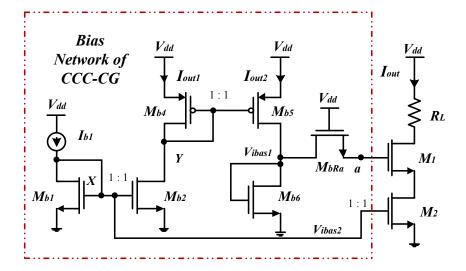

| Figure 4.4 Current bias network the CCC-CG matching network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54     |

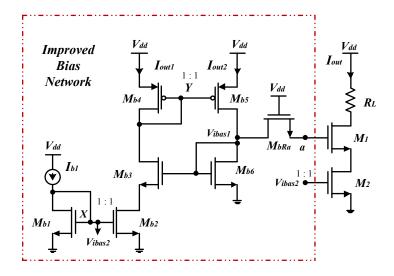

| Figure 4.5 An improved bias network of the CCC-CG stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55     |

| Figure 4.6 Proposed active current amplification stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56     |

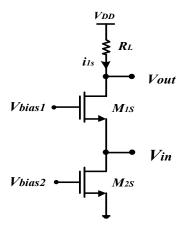

| Figure 4.7 Laser diode power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59     |

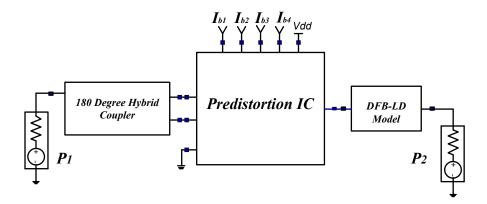

| Figure 4.8 Harmonic balance simulation setup of the DFB-LD with predistortion circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60     |

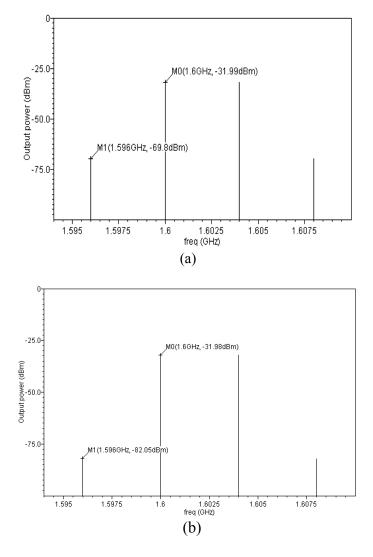

| Figure 4.9 Simulated spectra at the output of the DFB-LD, (a) without and (b) with predistoral predictions of the DFB-LD, (b) with predictions of the DFB-LD, (c) without and (d) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) without and (e) with predictions of the DFB-LD, (e) with predictions | ortion |

| (matched) circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61     |

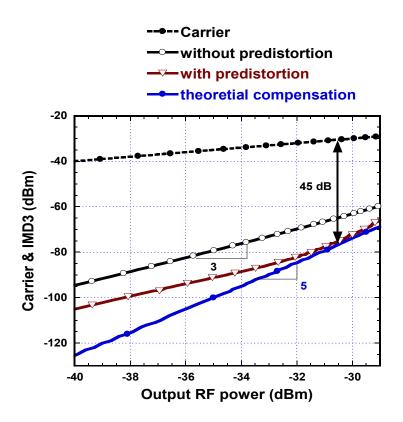

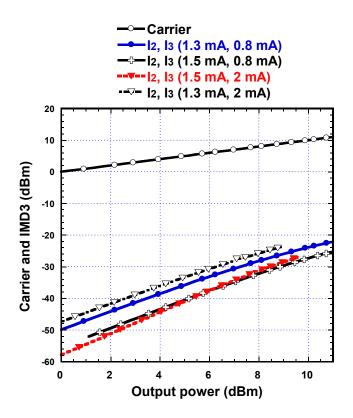

| Figure 4.10 Simulated carrier and IMD3 of DFB-LD, with and without predistortion (match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | hed)   |

| circuit at 1600 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62.    |

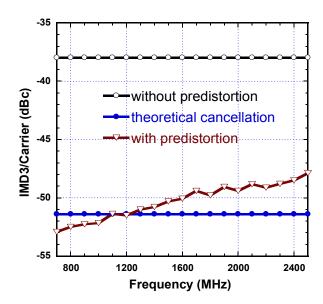

| Figure 4.11 Simulated IMD3/C of DFB-LD, theoretical analysis, with and without predistortic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | on  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| (matched) from 0.7 to 2.5 GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64  |

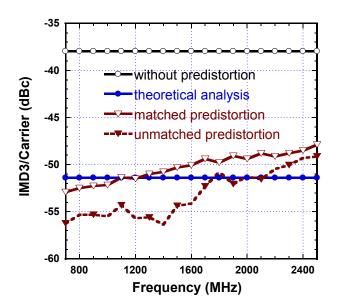

| Figure 4.12 Simulated IMD3/C with matched and unmatched predistortion circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65  |

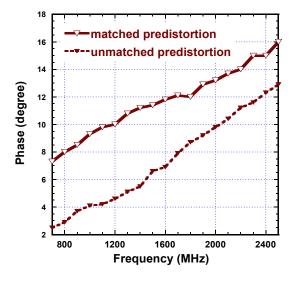

| Figure 4.13 Simulated phase difference between signal carrier and IMD3 with matched and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| unmatched predistortion circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65  |

| Figure 4.14 Simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for different bias currents $I_{b2}$ and $I_{b2}$ are simulated output power of the predistortion circuit for the predistortion | ınd |