# On the FPGA Implementation and Performance Analysis of a Digital Carrier Synchronizer

Sayed Hafizur Rahman

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Masters of Applied Science at

Concordia University

Montréal, Québec, Canada

November 2006

© Sayed Hafizur Rahman, 2006

Library and Archives Canada

Branch

Published Heritage Direction du

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington

Patrimoine de l'édition

Ottawa ON K1A 0N4 Canada

Bibliothèque et

Archives Canada

Your file Votre référence ISBN: 978-0-494-28925-9 Our file Notre référence ISBN: 978-0-494-28925-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **Abstract**

## On the FPGA Implementation and Performance Analysis of a Digital Carrier Synchronizer

Sayed Hafizur Rahman, M.A.Sc Concordia University, 2006

The evolutionary growth of digital communication has an acute impact on the digital integrated circuit (IC) design industry. Nowadays instead of ASICs (Application Specific Integrated Circuits), Field programmable gate arrays (FPGAs) are often employed to implement digital communication systems due to the speed, performance, reliability and flexibility. Digital communication systems such as modulation-demodulation and M-PSK require the use of carrier synchronization in phase and frequency. This work addresses the FPGA implementation and analysis of a Digital Carrier Synchronizer (DCS), which is a phase-locked loop (PLL), realized using digital circuits. This novel methodology highlights implementation promises towards some of the critical issues associated with the design of its analog counterpart, usually known as PLL. The principle function of this DCS is heavily dependent on the Numerically Controlled Oscillator (NCO) and the Loop Filter (LF). There are various methods to

implement NCOs and LFs that are used in the architectural model of DCS. This research work examines the performance of two different NCOs and LFs realization in DCS for modem (modulator-demodulator) application using FPGA based design solutions. The methods presented are Look up Table (LUT) and Xilinx ROM based NCO in one hand, and 1<sup>st</sup> order and 2<sup>nd</sup> order based LF in the other hand. Each has its own merits and de-merits. A DCS mathematical model has been developed in order to analyze the stability of the design. Furthermore, the performance of this two implementations based on three performance metrics i.e. stability, locking-time and tracking range has been studied. From the analysis, Xilinx ROM based NCO with 2<sup>nd</sup> order LF performs better and are more suited for modem's DCS.

#### **Acknowledgements**

First and foremost, my wholehearted thanks and admire are due to the Holy One, Allah, Who has always been with me through out my entire struggle in life wiping out all my fears, for oblation His countless blessings.

I would like to express my sincere gratitude and appreciation to my supervisor Dr. Otmane Ait Mohamed for providing me the opportunity to work in this challenging but exciting field and to be part of his research group, for his expert guidance, and for his support and encouragement throughout my research and thesis process.

I would like to specially thank Asif Iqbal Ahmed of Hardware Verification Group, Concordia University, for his invaluable guidance. Without his insight and steering, needless to say, this project would have never got completed. Also, I would like to curiously thank Dr. Youcef Fouzar, Zarlink Semiconductor, Ottawa, Canada, for valuable discussion of my project.

To all my fellow researchers in Hardware Verification Group (HVG) at Concordia University, thank you for encouragement, thoughtful discussion, and productive feedback. I wish to express my sincere and heartfelt thanks to Kamran Hussain, Amer Samara, Abu Nasser Mohammed Abdullah and Haja Moinudeen who have helped me during the course of my research work. I would specially like to thank to my eldest brother, Mujibur Rahman in Texas Instrument, USA, who helped me out whenever I was in difficulties.

Last but not least I would like to thank my eldest brothers, father and the rest of my family members in Bangladesh for their constant moral support and encouragement which were invaluable in completing this thesis.

То

## My Father, Sayed Mostafizur Rahman

And

My Mother, **Late – Firoza Begum**

## **TABLE of CONTENETS**

| List of Figures                                                                | xi          |

|--------------------------------------------------------------------------------|-------------|

| List of Tables                                                                 | xiii        |

| List of Acronyms                                                               | xiv         |

| Chapter 1 Introduction                                                         | 1           |

| 1.1 Thesis Contributions                                                       | 4           |

| 1.2 Thesis organization                                                        | 6           |

| Chapter 2 Related Work and Preliminaries                                       | 7           |

| 2.1 Related Work                                                               | 7           |

| 2.2 Preliminaries                                                              | 9           |

| 2.2.1 Synthesis Process                                                        | 9           |

| 2.2.1.1 Synthesizable vs. Non-Synthesizable RTL                                | 11          |

| 2.2.1.2 Synthesis for FPGA                                                     | 13          |

| 2.2.1.3 Xilinx Integrated Software Environment (ISE)                           | 13          |

| 2.2.2 Functional Verification Using Simulation                                 | 16          |

| 2.2.2.1 What is Functional Verification?                                       | 16          |

| 2.2.2.2 The Importance of verification                                         | 17          |

| 2.2.2.3 What is testbench?                                                     | 19          |

| 2.3 Summary                                                                    | 20          |

| Chapter 3 Conventional Analog Phase Locked (APLL)                              | 21          |

| 3.1 Introduction                                                               | 21          |

| 3.2 Phase Detector (PD)                                                        | 22          |

| 3.3 Loop Filter (LF)                                                           | 24          |

| 3.4 Voltage Controlled Oscillator (VCO)                                        | 26          |

| 3.5 Summary                                                                    | 30          |

| Chapter 4 Mathematical Model of a Digital Carrier Synchronizer (DCS) in the Di | screte Time |

| Domain (Z-Domain)                                                              | 31          |

| 4.1 Introduction                                                               | 31          |

|   | 4.    | 1.1  | Mapping the Poles of a second-order system from S-domain to Z domain     | 32         |

|---|-------|------|--------------------------------------------------------------------------|------------|

|   | 4.2   | N    | fathematical model of DCS Architecture                                   | 33         |

|   | 4.3   | Α    | nalysis of the DCS                                                       | . 34       |

|   | 4.    | 3.1  | Transfer function of Loop Filter in the Z-domain                         | 34         |

|   | 4.    | 3.2  | Transfer function of NCO in the Z-domain                                 | 36         |

|   | 4.    | 3.3  | Phase Error Response of the DCS                                          | 39         |

|   | 4.    | 3.4  | Stability analysis of the DCS                                            | 41         |

|   | 4.    | 3.5  | Tracking Range of the DCS                                                | 43         |

|   | 4.4   | S    | rummary                                                                  | <b>4</b> 3 |

| C | hapte | er 5 | Design and Datapath Implementation of Digital Carrier Synchronizer (DCS) | . 44       |

|   | 5.1   | Ir   | ntroduction                                                              | . 44       |

|   | 5.2   | P    | hase Detector                                                            | 45         |

|   | 5.    | 2.1  | Data path of the Phase Detector                                          | 46         |

|   | 5.3   | F    | irst Order Digital Loop Filter (LF)                                      | . 48       |

|   | 5.    | 3.1  | Data path of the Loop Filter                                             | 49         |

|   | 5.4   | ٨    | lumerically Controlled Oscillator (NCO)                                  | . 50       |

|   | 5.    | 4.1  | Datapath of LooK Up Table (LUT) Based NCO                                | 51         |

|   | 5.5   | D    | igital Loop Filter                                                       | . 53       |

|   | 5.    | 5.1  | Designing a IIR Low pass Filter                                          | 54         |

|   | 5.    | 5.2  | Designing a FIR Low pass filter                                          | 55         |

|   | 5.6   | Х    | ilinx System Generator                                                   | . 57       |

|   | 5.    | 6.1  | Strategy                                                                 | 58         |

|   |       | 5.6. | 1.1 Selecting an FPGA Board                                              | 58         |

|   |       | 5.6. | 1.2 Selecting a Digital Filter Design Method                             | 58         |

|   |       | 5.6. | 1.3 Kaiser Window Method                                                 | 59         |

|   | 5.7   | C    | CORDIC Based NCO                                                         | 62         |

|   | 5.8   | X    | ilinx ROM Based NCO                                                      | . 65       |

|   | 5.9   | s    | tummary                                                                  | 67         |

| Chapter 6 S        | Synthesis and Emulation                                        | 68  |

|--------------------|----------------------------------------------------------------|-----|

| 6.1 S <sub>l</sub> | pace Exploration via Synthesis Process                         | 68  |

| 6.1.1              | Comparison of Different NCOs                                   | 68  |

| 6.1.2              | DCS Synthesis Using Various Configuration of NCO and LF        | 71  |

| 6.2 E              | mulation                                                       | 71  |

| 6.2.1              | Introduction                                                   | 71  |

| 6.2.2              | The Emulation Process                                          | 73  |

| 6.2.3              | Synthesized Emulation Environment setup                        | 73  |

| 6.2.4              | Design Implementation                                          | 75  |

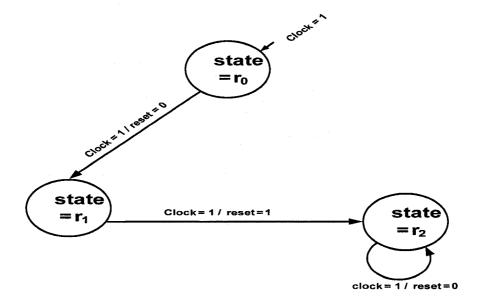

| 6.2.4              | 4.1 Internal Reset Generator through an FSM                    | 76  |

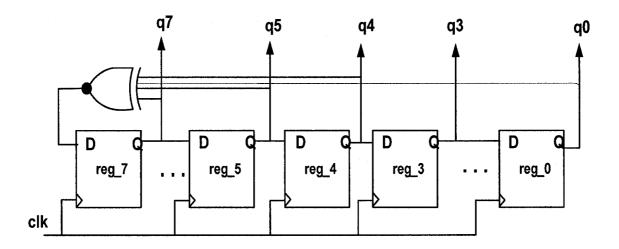

| 6.2.4              | 4.2 Linear Feedback Shift Register (LFSR)                      | 77  |

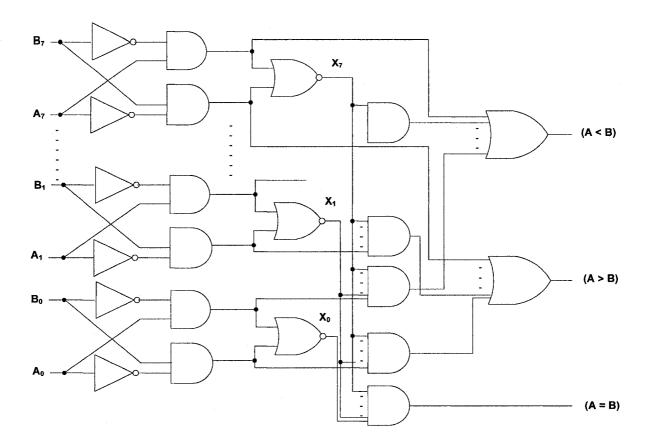

| 6.2.4              | 4.3 Digital Magnitude Comparator                               | 78  |

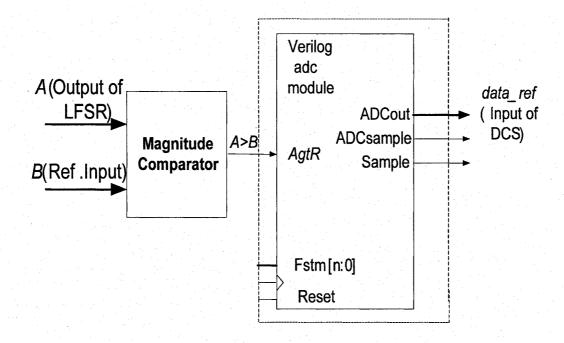

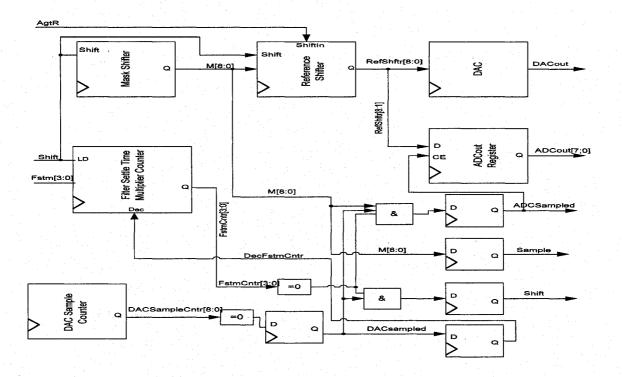

| 6.2.4              | 4.4 ADC (Analog to Digital Converter)                          | 81  |

| 6.2.4              | 4.5 Clock Divider (clk_div)                                    | 82  |

| 6.2.4              | , ,                                                            |     |

| 6.3 S              | ummary                                                         | 83  |

| Chapter 7 S        | Simulation Results and Performance Evaluation of Different DCS |     |

| Implement          | ations                                                         | 84  |

| 7.1 In             | troduction                                                     | 84  |

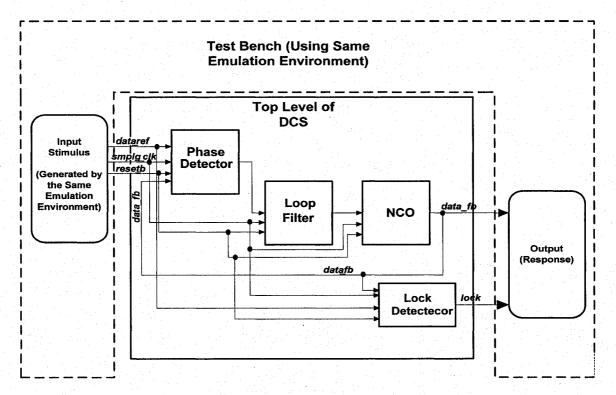

| 7.2 S              | imulation Environment for DCS                                  | 85  |

| 7.2.1              | Instantiations                                                 | 86  |

| 7.2.2              | Initial and Always Blocks                                      | 87  |

| 7.2.3              | Printing Using \$display During Simulation                     | 88  |

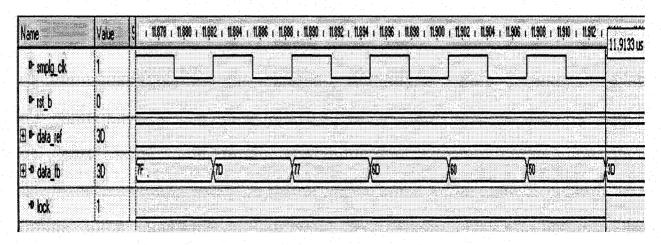

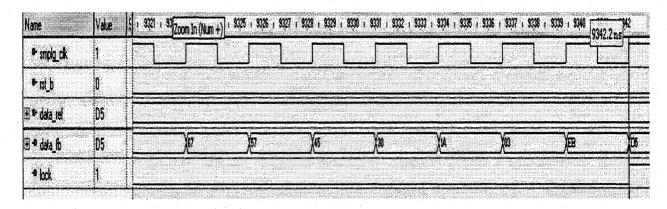

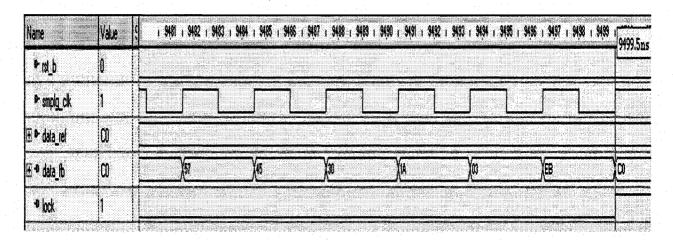

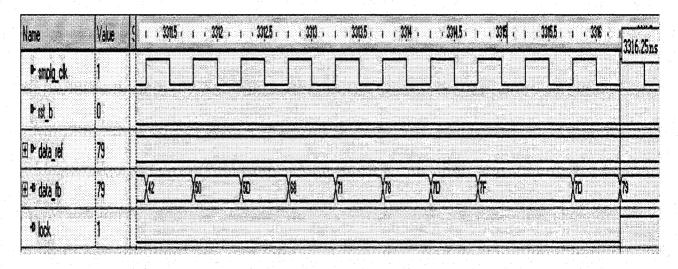

| 7.3 S              | imulation Results and Discussion                               | 89  |

| 7.4 T              | racking Range and Locking Time Analysis                        | 93  |

| 7.5 S              | ummary                                                         | 97  |

| Chapter 8 (        | Conclusion and Future Work                                     | 98  |

| References         |                                                                | 101 |

## List of Figures

| Figure 1. Digital Carrier Synchronization (DCS) path                           | 2  |

|--------------------------------------------------------------------------------|----|

| Figure 2. Logic Synthesis Flow from RTL to Gates                               | 10 |

| Figure 3. Screen shot of Xilinx Project Navigator, from the ISE Software Suite | 14 |

| Figure 4. A Functional Verification Path                                       | 16 |

| Figure 5. Verification Dominates Design                                        | 18 |

| Figure 6. Block Diagram of a Testbench                                         | 20 |

| Figure 7. Analog Phase Locked Loop                                             | 21 |

| Figure 8. Phase Detector as a Multiplier                                       | 23 |

| Figure 9. Filtering the Phase Detector Output signal to remove                 | 25 |

| Figure 10. The Circuit Implementation of the first order passive Loop Filter   | 25 |

| Figure 11. Block Diagram of Voltage Controlled Oscillator                      | 27 |

| Figure 12. Mathematical model of DCS in discrete time domain (Z-domain)        | 34 |

| Figure 13. Block diagram of Loop Filter in Z-domain                            | 35 |

| Figure 14. Block diagram of NCO in Z-domain                                    | 36 |

| Figure 15. Pole-Zero Plot for a stable DCS                                     | 42 |

| Figure 16. Digital Carrier Synchronization Path on the FPGA platform           | 44 |

| Figure 17. Datapath of the Digital Carrier Synchronization                     | 45 |

| Figure 18. Datapath of Phase Detector                                          | 46 |

| Figure 19. Phase Detection State machine                                       |    |

| Figure 20. Datapath of 1 <sup>st</sup> Order Loop Filter                       | 49 |

| Figure 21. Look Up Table (LUT) Based NCO                                       | 51 |

| Figure 22. Second Order Low Pass IIR Filter                                    | 54 |

| Figure 23. Second Order Low Pass FIR Filter                                    | 56 |

| Figure 24. CORDIC Based NCO                                                    | 62 |

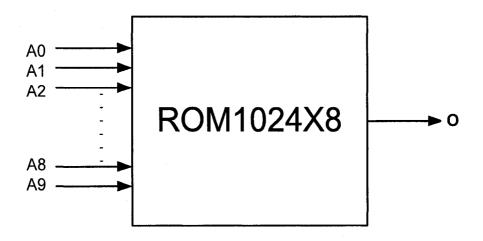

| Figure 25. Xilinx ROM 1024X1                                                      |

|-----------------------------------------------------------------------------------|

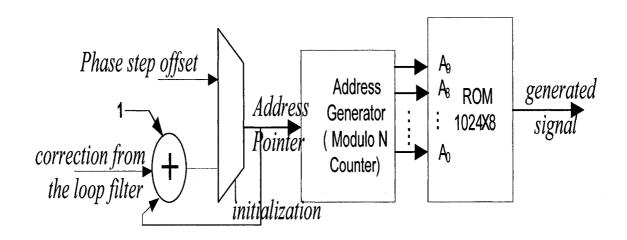

| Figure 26. Xilinx ROM Based NCO with Modulo N Counter                             |

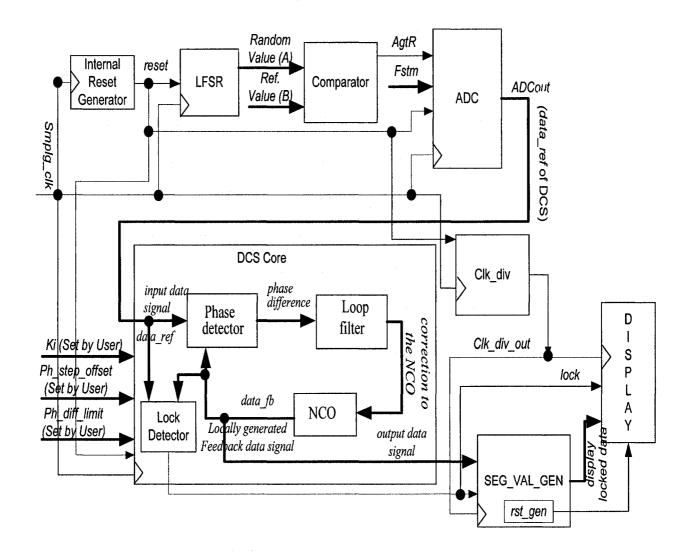

| Figure 27. Emulation Environment for DCS                                          |

| Figure 28. FSM for internal Reset signal generator                                |

| Figure 29. An 8-bit Pseudo Random Generator                                       |

| Figure 30. 8-Bit Digital Magnitude Comparator                                     |

| Figure 31. ADC with a Magnitude Comparator                                        |

| Figure 32. Datapath of Analog to Digital Converter                                |

| Figure 33. Simulation Environment for DCS                                         |

| Figure 34. Stimulus Module Instantiation                                          |

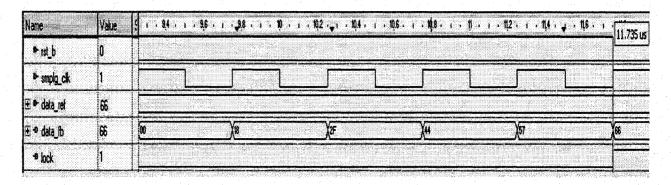

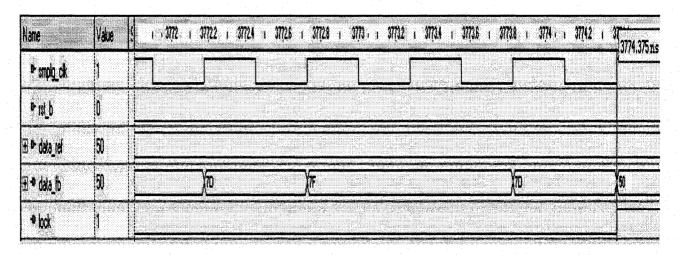

| Figure 35. DCS Using LUT based NCO and 1st Order LF (When Fs = 72 MHz) 89         |

| Figure 36. DCS Using LUT based NCO and 1st Order LF (When Fs = 75MHz) 89          |

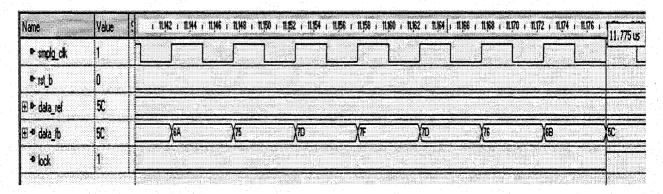

| Figure 37. DCS Using Xilinx ROM based NCO and 1st Order LF (When Fs = 73 MHz) 90  |

| Figure 38. DCS Using Xilinx ROM based NCO and 1st Order LF (When Fs =77MHz) 90    |

| Figure 39. DCS Using LUT based NCO and 2nd Order LF (When Fs =85 MHz) 91          |

| Figure 40. DCS Using LUT based NCO and 2nd Order LF (When Fs = 88 MHz) 92         |

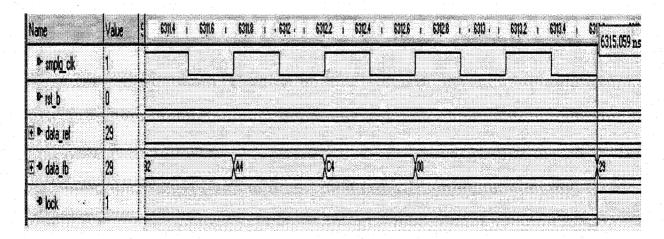

| Figure 41. DCS Using Xilinx ROM based NCO and 2nd Order LF(When Fs = 95 MHz) 92   |

| Figure 42. DCS Using Xilinx ROM based NCO and 2nd Order LF(when Fs = 105 MHz)93   |

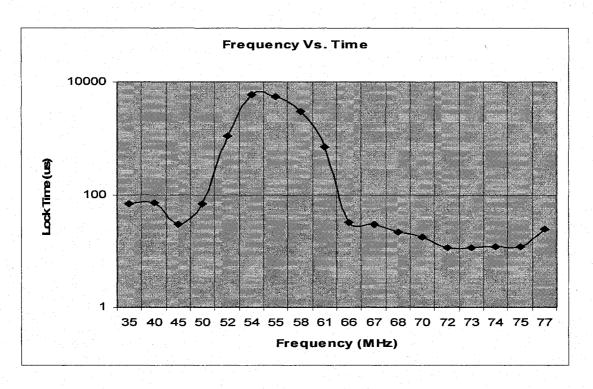

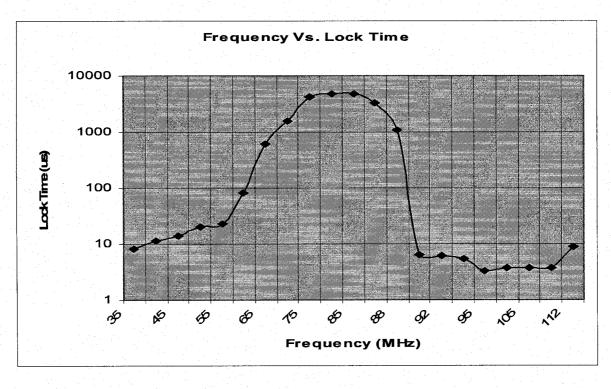

| Figure 43. Tracking Frequency vs. Lock Time of DCS using LUT Based NCO and 1st    |

| Order LF                                                                          |

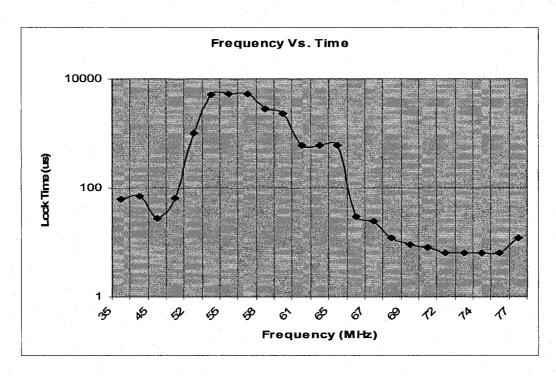

| Figure 44. Tracking Frequency vs. Lock Time of DCS using Xilinx ROM based NCO and |

| 1st Order LF95                                                                    |

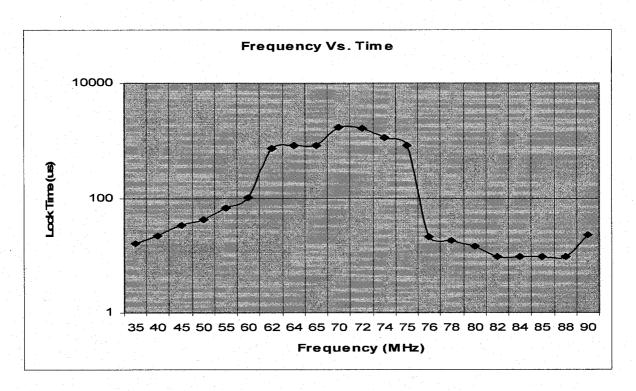

| Figure 45. Tracking Vs. Lock Time of DCS using LUT based NCO and 2nd Order LF 96  |

| Figure 46. Tracking Frequency Vs. Lock Time of DCS using Xilinx ROM based NCO and |

| 2nd Order   F                                                                     |

## List of Tables

| Table 1. Physical resources Occupation on FPGA board for FIR and IIR Filter | 59 |

|-----------------------------------------------------------------------------|----|

| Table 2. Angle Value & Shift Sequences of CORDIC Based NCO                  | 64 |

| Table 3. Xilinx ROM1024X8 Initialization (When Fs = 50 MHz)                 | 66 |

| Table 4. Performance Evaluation Using Xilinx                                | 69 |

| Table 5. Performance Evaluation Using Synopsys                              | 69 |

| Table 6. Synthesis Report of Different DCS Implementations                  | 71 |

| Table 7. Summarized Emulation Results of Different DCS Implementations      | 83 |

| Table 8. Summarized Analysis of Different DCS Implementations               | 97 |

### List of Acronyms

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

APLL Analog Phase Locked Loop

CORDIC Coodinate Rotation Digital Computer

DAC Digital to Analog Converter

DCS Digital Carrier Synchronizer

DPLL Digital Phase Locked Loop

FPGA Filed Programmable Gate Array

FIR Finite Impulse Response

FSM Finite State Machine

IIR Infinite Impulse Response

LUT Look Up Table

LF Loop Filter

LPF Low Pass Filter

NCO Numerically Controlled Oscillator

PD Phase Detector

PM Phase Modulation

SOC System-On-Chip

UCF User Constraint File

VCO Voltage Controlled Oscillator

## **Chapter 1**

## Introduction

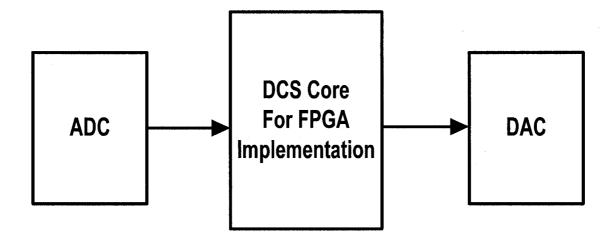

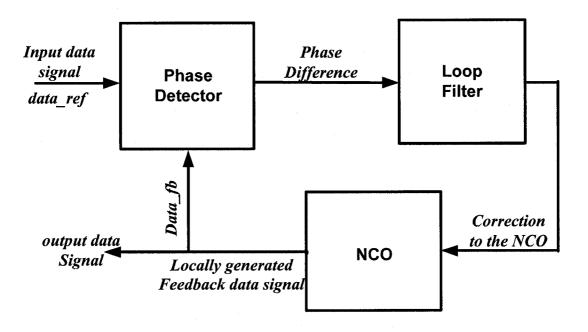

The continuous progress in modern digital communication systems, such as wireless, telecom, and datacom require a stable periodic signal to offer timing solutions. This stability provides the basis for synchronizing, aligning the sampling clock, restraining the clock skew or synthesizing frequencies. Phase locking, studied for more than half a century, is the principal technique to provide timing solutions. A list of tasks recognized by phase-locked loops (PLL) includes carrier synchronization, carrier recovery, clock recovery, phase modulation, phase/frequency demodulation, frequency synthesis, duty cycle correction, and jitter reduction [1]. Carrier Synchronization is an important part in coherent communication systems, especially for those employing a high bandwidth efficiency modulation schemes such as modem. Conventionally, a feedback loop called the phase-locked loop (PLL) is used to implement the carrier synchronization [2]. Digital carrier synchronizers (DCS) (Shown in Fig. 1) follow the analog phase locked loop techniques to synchronize any given signal [3]. The input signal of the DCS is sampled by the analog to digital converter (ADC) [4], which is not synchronous with the signal of the receiver's digital to analog converter (DAC) [3] [5]. There is a frequency or phase offset that exists between

the transmitter (ADC) and the receiver (DAC). In order to remove this offset a digital carrier synchronizer (DCS) is required.

Figure 1. Digital Carrier Synchronization (DCS) path

In this research work, the carrier synchronization is considered in digital domain in the context of digital modulation application, i.e. modem, which are designed mainly using a digital approach, because of the flexibility and high performance of digital systems. The carrier synchronization in digital modems is achieved by phase-locked loops, and as the DPLL is purely digital, it can be used in these systems. In modem applications, the locking time and tracking frequency are of extreme importance. Whenever the phase-locked loop loses lock in a modem, it means that hundreds of bits of data will be lost before the modem can regain synchronization [6]. The carrier frequency of our target application, modem, is 2.048 MHz. In this research work, two distinct realizations of DCS are investigated. The first one is the LUT based NCO with 1<sup>st</sup> and 2<sup>nd</sup> order LF and the second one is the Xilinx ROM based NCO with 1<sup>st</sup> and 2<sup>nd</sup> order LF. For each design we try to obtain the optimal locking time, and a wider tracking frequency

range, when changing the frequencies from 35 MHz to 110 MHz. Furthermore, the stability of our design was analyzed using MATLAB and showed that it's stable under certain constraints, which become then our design requirements. Our implementation targets a Field Programmable Gate Arrays (FPGAs).

As the technology of a multi-million gate in new devices is advancing very fast, both FPGAs and Application Specific Integrated Circuits (ASICs) are competitively demonstrating their capabilities in very large and high-speed applications. Consecutively, choosing the right technology to implement a given design is becoming the key question for several applications. In one hand, with ASICs one can implement multi-million gates in a small area of silicon using a library of reusable hardware and software blocks as Intellectual Property (IP) cores [7]. On the other hand, FPGAs have also satisfied wonderfully the requirements of fulfilment large complex designs in their today's multi-million gate ranges. Large variety of high performance IP cores (Microprocessors, Microcontrollers, Intellectual functional logics etc.) as well as high speed memories are much more accessible in today's FPGAs [8]. These features facilitate the implementation of a large complex system designs in FPGAs. Since the FPGAs are programmable, this indeed lowers the cost of any required changes or modifications in the design for future, and considering the importance of shorter Time To Market (TTM) in industry, which is a great benefit. For our DCS implementation we chose Xilinx Virtex-II Pro FPGA family which is based on IP cores and customized modules. It has multi-gigabit transceivers and PowerPC CPU blocks. It empowers complete solutions for telecommunication, wireless, networking, video, and DSP applications. Virtex-II Pro architectures are optimized for high performance designs in a wide range of densities. Combining a wide variety of flexible features and IP cores, the Virtex-II Pro family enhances programmable logic design capabilities and it is a powerful alternative to mask-programmed gate arrays [9]. Virtex-II Pro has some highly advanced features which include high performance Digital Clock Manager (DCM), and large storage.

#### 1.1 Thesis Contributions

The main contributions of the thesis are as follows:

- A mathematical model of our DCS implementation was developed in order to verify the stability of the model. The mathematical model was derived by the z-transform techniques. Initially the transfer functions of each component of the DCS model (i.e. phase detector, loop filter and NCO) were derived in the Z-domain. Subsequently the transfer function of our full DCS model was developed using negative feedback loop criteria. Finally the pole-zero condition was investigated using MatLab in order to verify the stable condition of our DCS architecture. The pole-zero plots also presented which are depicting the location of the poles and zeroes in the unit circle. Details about this development are provided in Chapter 4.

- Our initial focus was started of on the improvement of the NCO. Provided that

a precomposed datapath was consisted of an NCO implemented in Look Up

Table based method. The NCO using CORDIC based method was

reimplemented and afterwards used Xilinx ROM based method. Details about this development are presented in Chapter 5.

- After that our goal was to enhance the loop filter configuration as it played a major role in the feed forward gain of DCS along with NCO. Originally different NCOs were integrated with first order loop filter and checked the performance. Although synthesis wise it was the perfect candidate our goal lied to implement an NCO for faster locking time and wider tracking range. Therefore a second order loop filter was opted in order to accomplish the tracking range and locking criteria. A detail explanation is described in Chapter 5.

- Our developed emulation environment was portable and was two fold: First

we wanted to validate the sanity of DCS core and second, we wanted to

reuse the same emulation environment for different DCS configurations.

- our initial examination was involved with the locking time and tracking frequency range of DCS model using first order loop filter and LUT based NCO. Subsequently, a LUT based NCO was replaced with the Xilinx ROM based NCO and observed the locking time and tracking frequency range. At last, the first order loop filter was substituted with the second order loop in the DCS datapath in order to examine the locking time and tracking frequency range.

#### 1.2 Thesis organization

This thesis work illustrates the different DCS implementations using different order of loop filters and various NCOs. The highlight of our research work is to present a novel idea of DCS using Xilinx ROM based NCO in order to carry out the better performance metrics in the context of locking time and tracking frequency range for modern applications. The rest of this thesis is organized as follows: Chapter 2 provides a detailed explanation of the synthesis procedure and the functional verification using simulation. Chapter 3 gives a brief overview of the conventional analog phase locked loop. Chapter 4 explains a mathematical model of DCS architecture with some analysis. Chapter 5 discusses the detail datapath design and implementation of different DCSs with some modifications. Chapter 6 elaborates the emulation environment for FPGAs and Chapter 7 is devoted to simulation results and discussions. Finally Chapter 8 concludes this research work.

## **Chapter 2**

## **Related Work and Preliminaries**

#### 2.1 Related Work

An assortment of NCO implementation schemes, using both LUT and CORDIC algorithms, can be found in Kadam *et al.* [10]. The work revealed that CORDIC based NCO requires less space (hardware) than the LUT based implementation. Our work leads to that Xilinx ROM based NCO uses less hardware than others NCO. However, the major difference is rooted in the performance of NCO block in the framework of DCS in our research. However, the major difference is rooted in the performance of NCO block in the framework of DCS implementation in our research while in Kadam *et al.* [10]; their investigation tackles single modular implementation of NCO.

Ray et al. [11] is another noteworthy research that studied the use of CORDIC architecture in implementing commonly used functions into specific FPGAs. They mainly focused on applicable Digital Signal Processing applications. Once again, the difference with our research to the mentioned work is in the context of DCS.

Liang Yi & others [12] analyzed a direct digital frequency synthesizer (DDS) which is also called NCO. Their work focused only on the size of ROM lookup table and the precision of sine wave. In our work, we focus on the different performance metrics of NCO for speeding up the DCS.

A notable work to mention is the research performed by Khalid et al. [13]. They mainly focused on designing the emulator for quantum algorithms. Their work did not mention about the emulation environment nor did they mention about the complexity of the emulation environment. The principal contribution of our research to the above mentioned work is in the context of designing an emulation environment for DCS architecture. Our emulation environment provides the flexibility of integrating any data synchronizer. With a Xilinx soft IP (e.g. ADC) core, an internal reset signal generator, LFSR, Comparator and a clock divider, ours was truly a well fitting emulation environment.

Kyung-soo Oh et al. [14] as well developed an emulator environment for functional verification of a multi-media processor. They needed customized board control functions to control the specific FPGA board but on the contrary our environment can target on any Xilinx family of FPGA without any control circuitry. Last but not least we would like to cite the work done by P. Civera et al. [15]. Their work presented FPGA based circuit emulation for performing fault-injection. The key difference between this research to theirs is the application area. Our work focused more on verification of DCS circuits used on MODEMS, whereas their prescribed work completed the flow for Design-For-Testability (DFT).

In the following sections some preliminaries will be discussed which are required for our research work.

#### 2.2 Preliminaries

#### 2.2.1 Synthesis Process

Synthesis is a process, which enables the conversion of a behavioral-level model, in the form of RTL coding, to a gate-level model. It is important to note that the synthesis process will not always implement the same section of code in the same manner, since the tools employed for the task are powerful and have the capacity to optimize the design; attempting to provide an optimal solution in terms of timing, area, and power. In order for a design to be optimized, a compromise must be reached between the minimization of area, power, and timing requirements. The best compromise for a particular design depends on the requirements of the system that the design is to be used in. In order for the synthesis engineer to have some control over the optimization process, constraints can be set to define the maximum acceptable area and power, and to define the operating frequency of the module. The synthesis tool will work, iteratively, to meet these requirements; however, if they are too optimistic then timing violations may result, requiring the design of the module to be addressed, or the constraints relaxed.

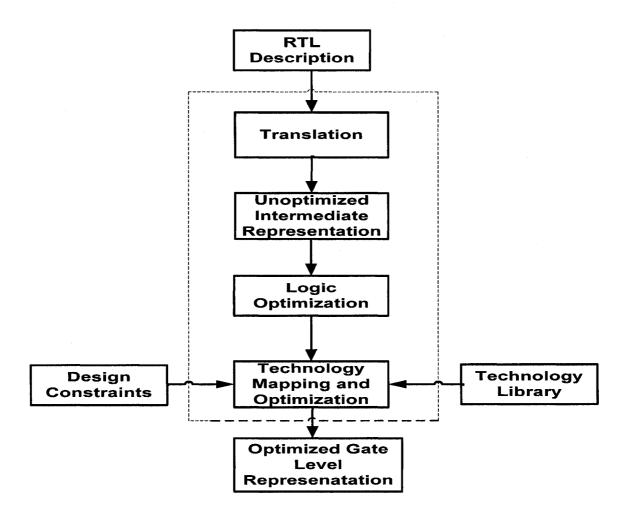

Figure 2. Logic Synthesis Flow from RTL to Gates [16]

Managing a complex datapath requires that the synthesis possess a high degree of automation. The synthesis procedure can be automated so that it is only necessary to run a single script (i.e.  $dc\_shell$ ); nevertheless, it is useful to have a good understanding of this process throughout the development of the design. Although a variety of synthesis tools are available, to address our research need we have employed *Xilinx ISE* and *Synopsys Design Compiler* [9]. The main characteristics of these tools are they work on similar principles and involve similar stages during synthesis. Figure 2, extracted from [16], provides a good

illustration of the key stages of the synthesis process. In Figure 2, RTL Description represents behavioral-level Verilog coding which describing the functionality of the design. Translation is a process, which converts the RTL coding at the input into a representation more convenient for the tool; 'unnecessary' code such as comments will be removed at this stage. Unoptimized Intermediate Representation converts the output of the Translation process to a form based on the structure of the design, which is incomprehensible to the user. Logic Optimization employs various techniques to remove redundant logic, providing an optimized representation of the initial RTL Description, a very significant stage before the physical information and constraints are considered. Technology Mapping and Optimization maps cells in the gate-level representation to cells from a specified **Technology Library** and then iteratively optimizes the design in an attempt to meet the specified Constraints. An Optimized Gate-Level Representation of the design is the output from the synthesis process, along with reports on timing, area, and power of the design. A number of alterations are required in the synthesis scripts in order to define design characteristics, such as the interface, the clock periods, the top-level module name and the *Technology Library*.

#### 2.2.1.1 Synthesizable vs. Non-Synthesizable RTL

There are three levels of abstraction that may be used to represent the design;

Behavioral, RTL (Register Transfer Level) and Structural. The behavioral code is

at a higher level of abstraction. It is used primarily for translating the architectural

specification, to a code that can be simulated. Behavioral coding is initially

performed to explore the authenticity and feasibility of the chosen implementation for the design. Conversely, the RTL coding actually describes and infers the structural components and their connections. This type of coding is used to describe the functionality of the design and synthesizable to produce the structural netlist, which uses the leaf cells of a library [17].

If the modules in a design contain only synthesizable statements, software can be used to transform or synthesize the design into a netlist that describes the basic components and connections to be implemented in hardware. The netlist may then be transformed into, for example, a form describing the standard cells of an integrated circuit (e.g. an ASIC) or a bitstream for a programmable logic device (e.g. FPGA). For example the following snapshot of the multiplexer code is synthesizable:

```

module mux (a, b, sel, y)

input a, b, sel;

output y;

assign y = sel? a: b;

endmodule

```

The following code signifies that when sel = true, y will get the value of a, otherwise b. This characterizes the behavior of a multiplexer. On the contrary, there is also non-synthesizable verilog RTL coding style exist. For instance, let's examine the following lines of code,

initial begin // beginning of the simulation

```

clock = 0;

clear_n = 1;

cycle_count = 0;

end

always # 100 clock = ~clock; // clock period of 100 time unit

```

The above code segment is generally adopted to generate the clock in the testbench but in reality the synthesis tool will not allow to synthesize the code segment. The main reason for this is in real digital circuit we can not assume an initial value without a reset.

#### 2.2.1.2 Synthesis for FPGA

The *Synthesis for FPGA* phase of the project includes similar stages to those involved in standard synthesis procedure, but has additional stages to convert the design to a format, which can be successfully programmed onto the FPGA.

The following section considers the use of the Xilinx Integrated Software Environment (ISE) employed in the synthesis for FPGA of the different NCOs, LFs and Digital Carrier Synchronization (DCS). Issues specific to the synthesis of the module are also addressed.

#### 2.2.1.3 Xilinx Integrated Software Environment (ISE)

The Xilinx Integrated Software Environment (ISE) is a tool suite developed for the synthesis and conversion process. Project Navigator is a tool from this suite

which enables a design flow to be set up to automate the control of the other software tools in the suite [18].

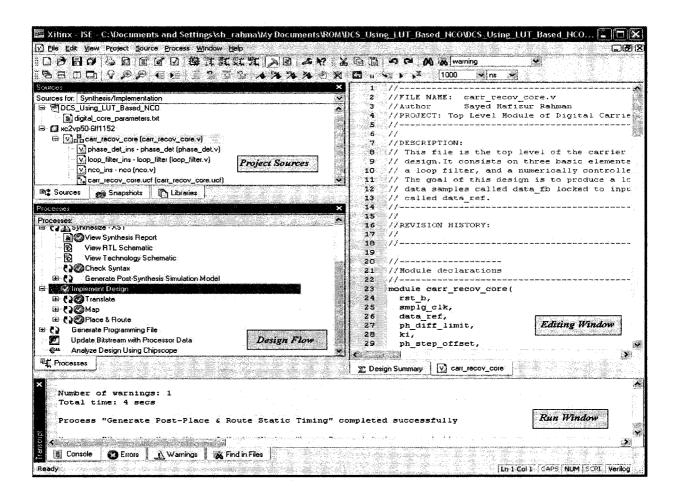

Figure 3. Screen shot of Xilinx Project Navigator, from the ISE Software Suite.

The user has control over how the design progresses through the flow, and can easily view reports from different stages of the synthesis flow. Figure 3 shows a labelled screen shot from Project Navigator. The **Project Sources** area includes links to the Verilog coding and instantiated modules, which are required at the input to the synthesis procedure, and also allows the assignment of constraint files to any of the listed Verilog files. The **Design Flow** area shows the complete

flow, user constraints and also provides indication as to the design's progress through this flow. The **Editing Window** allows for the modification of any input file, while the **Run Window** shows the report for either: the stage which is currently running or the last stage to be run.

In the Design Flow window (see Fig. 3) the options to setup the user constraint files for the design should be specified. The constraint files are:

- Create Timing Constraints: This constraint file enables us to setup the clock period on the FPGA global clock pin.

- Assign Package Pins: Assign package pins were used when we downloaded into our target device.

- Create Area Constraints: Since no area constraints are not specified in our design, so we didn't use this constraint for our implementation.

There are three main stages in the Synthesis for FPGA flow shown in the *Project Navigator* **Design Flow** window in Figure 3. The *Synthesis* stage of the flow is essentially the same as standard synthesis processes, converting behavioural Verilog RTL to a gate-level equivalent. The XST (Xilinx Synthesis Technology) synthesis tool is employed in the design flow for the Digital Carrier Synchronization Module. The *Implement Design* phase employs NGDBuild software to *translate* the netlist, which is output from the *Synthesis* stage, along with design constraint information, to an intermediate format. The design is then *mapped* to pins of the Xilinx FPGA in use; this is specified in *Project Navigator*.

The design then undergoes the *place and route* operation, which provides output to the bit-stream generator. The *Generate Programming File* phase is entered largely on the iMPACT tool, which is capable of generating various file formats, depending on how the download to FPGA is to be conducted. Project Navigator also enables the incorporation of the Xilinx ChipScope<sup>TM</sup> Pro Integrated Logic Analyser into the flow.

#### 2.2.2 Functional Verification Using Simulation

#### 2.2.2.1 What is Functional Verification?

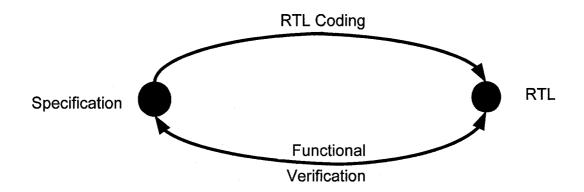

The main purpose of functional verification is to ensure that a design implements intended functionality. A functional verification path is shown in Figure 4. Functional verification reconciles a design with its specification. Without functional verification, one must trust that the transformation of a specification document into RTL code was performed correctly, without misinterpretation of the specification's intent [19]. It is important to note that, unless a specification is written in a formal language with precise semantics, it is impossible to prove that a design meets the intent of

Figure 4. A Functional Verification Path [19]

its specification. Functional verification, as a process, can show that a design meets the intent of its specification [19]. Functional verification can be realized using three complementary approaches: Black-box, White-box, and Grey-box verification.

In our DCS project, we follow the simulation-based verification, which is also called Black-box verification. In a Simulation-Based Verification, the test environment has the following features:

- The testbench consisted of HDL procedures that provided stimulus data to the DUT or read data from it.

- The tests (testcases), which called the testbench procedures in sequence to apply selected input stimuli (random or directed) to the DUT and check the results, were directed towards specific features of the design.

#### 2.2.2.2 The Importance of verification

Today, in the epoch of multimillion gates of ASICs, reusable Intellectual Property (IP), and System-on-a-Chip (SoC) designs, verification consumes about 70% of the design effort. The number of verification engineers is usually twice the number of RTL designers. When design projects are completed, the code that implements the testbenches makes up to 80% of the total code volume.

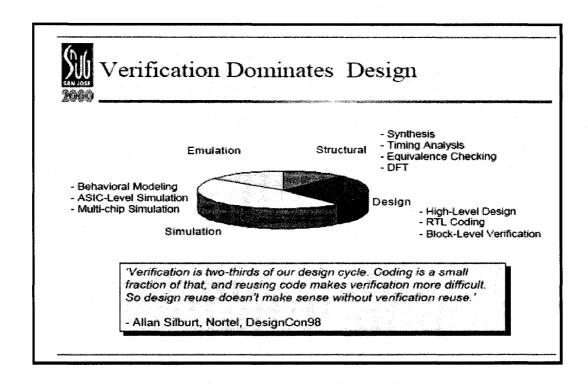

Figure 5. Verification Dominates Design [20]

Most of the case studies have shown that functional verification consumes more than 50 percent of the design-cycle time (Fig. 5) [20].

With functional verification involving such a dominant portion of the chip development process, SoC teams look for any opportunity for leverage. Some of the best leverage comes from the designers who wrote the RTL code that must be verified. Designers can no longer pass their code "over the wall" to the Verification team; they need to be involved in the verification process in order to ensure that the SoC works as intended. Therefore, the process of SoC verification is becoming a necessity for large, complex chip projects. This process encompasses a broad range of concepts, including verification friendly RTL coding standards for the designers, cross-participation in design and

Verification plan reviews, and clean, consistent interfaces at multiple levels of design abstraction.

#### 2.2.2.3 What is testbench?

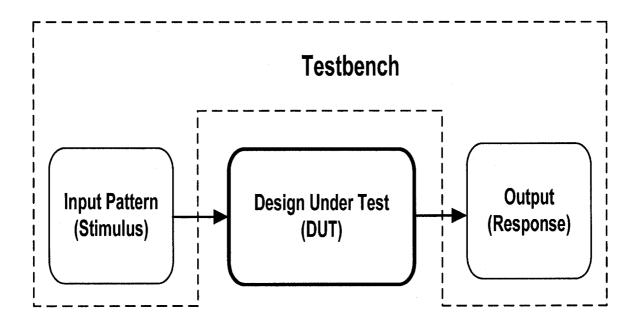

To simulate a design, an external apparatus called a test bench is often required to mimic the environment in which the design will reside. Among other functionality, the main purpose of a test bench, written in HDL, is to supply input waveforms to the design under test (DUT) and to monitor the response using waveform viewer such as Simvision whether the DUT produces the expected outputs.

Figure 6 shows a simple block diagram of a testbench that surrounds the DUT. A test bench is not manufactured as the design; it has far fewer coding style restrictions. Together with the perception that test benches are discarded once the design is verified, the structures of a test bench are often at the mercy of verification engineers [21]. Consequently, test benches frequently generate wrong stimuli, compare with wrong results, or miss corner cases, eventually diverting valuable engineering time to debugging the test benches instead of the design.

Figure 6. Block Diagram of a Testbench [19]

Furthermore, without well-organized guidelines, test benches can be a nightmare to maintain and hence are not reusable. Therefore, to have easily maintainable and reliable test benches, it is important to understand organizations and designs of test benches [21].

#### 2.3 Summary

In this chapter, related works and also some preliminaries such as synthesis, testbench and simulation which are related to our research work are presented. In the following chapter, the analog phase locked loop (APLL) techniques and the operations of its key components will be discussed.

## **Chapter 3**

## Conventional Analog Phase Locked (APLL)

#### 3.1 Introduction

This chapter focuses on the most common analog phase locked loop technique which enables us the thinking about the digital carrier synchronization.

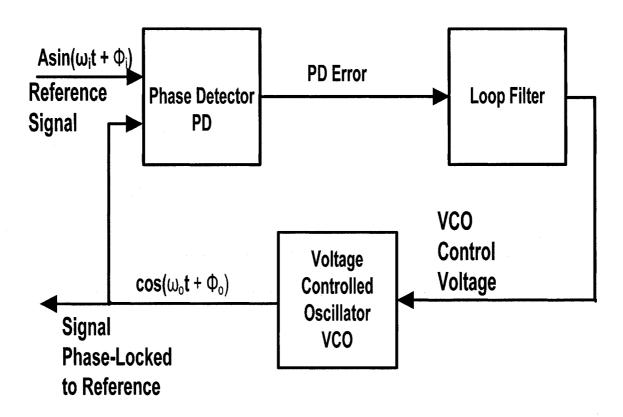

Figure 7. Analog Phase Locked Loop

An APLL is a circuit shown in Figure 7 synchronizing an output signal generated by an Oscillator, with a reference or input signal in frequency as well as in phase [22]. The synchronized Oscillator in analog PLL is a Voltage controlled Oscillator (VCO). If a phase error builds up, a control mechanism acts on the Oscillator in such a way that the phase error is again reduced to a minimum. In such a control system the phase of the output signal is actually locked to the phase of the reference signal.

In a feedback-system PLL regulates the phase  $\varphi_o$  of its periodic output signal, with the frequency  $\omega_o$ , in a constant relationship to the phase  $\varphi_{in}$  of a periodic input signal, with the input frequency  $\omega_{in}$ , by a feedback process [23]. The basic functional blocks of a classical analog PLL are phase detector (PD), loop filter (LF) and voltage controlled oscillator (VCO). In analog PLL all the functional blocks are in analog. In the following section we will introduce about the different components of Analog PLL.

### 3.2 Phase Detector (PD)

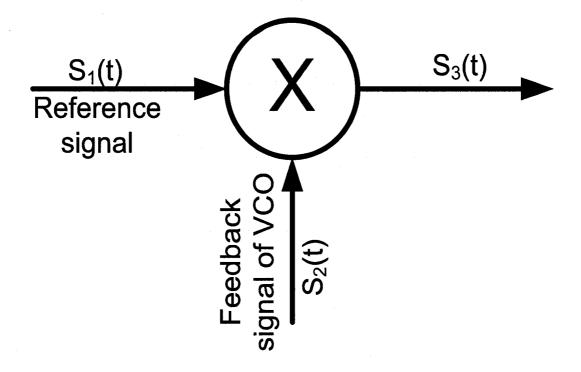

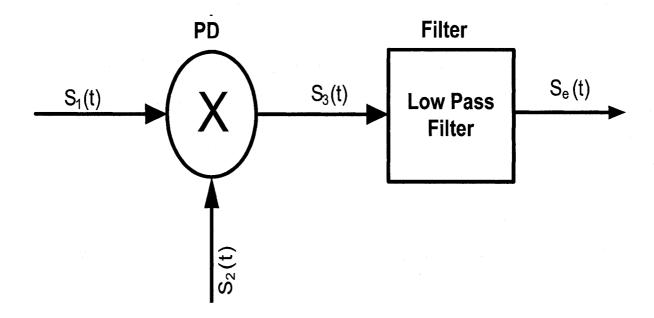

A phase detector (PD) is a circuit capable of delivering an output signal that is proportional to the phase difference between its two input signals S<sub>1</sub> (t) and S<sub>2</sub> (t). In analog PLLs, different types of phase detectors are used. In this analog PLL, we are considering an ideal multiplier phase detector shown in Figure 8 which is the first phase detector in the history of the PLL.

Figure 8. Phase Detector as a Multiplier

The multiplier phase detector (Figure 8) is completely used in analog PLL. Here we are considering with two sinusoid signals  $S_1$  (t), which is the reference signal and  $S_2$  (t), which is the feedback signal of the VCO. Both signals have same frequency but the phases are  $90^{\circ}$  out of phase. We have set the phase of these signals as a variable. Note that  $S_2$  (t) is a cosine hence is  $90^{\circ}$  shifted from  $S_1$  (t).

Multiplier Output, S<sub>3</sub> (t) = Reference Signal (t) \* Feedback Signal of VCO

$$S_3(t)=S_1(t)*S_2(t)$$

$$S_1(t)=A_1\sin[\omega t+\varphi_1(t)]$$

Where,

$$S_2(t)=A_2\cos[\omega t+\varphi_2(t)]$$

The output of the multiplier is

$$S_3(t) = K_d A_1 A_2 \sin[\omega t + \varphi_1(t)] \cos[\omega t + \varphi_2(t)]$$

Where  $K_{d}$  is the gain of the multiplier. Now manipulating the above equation, we can get

$$S_{3}(t) = \underbrace{\frac{K_{d} A_{1} A_{2}}{2} \sin[\varphi_{1}(t) - \varphi_{2}(t)]}_{First \ Part} + \underbrace{\frac{K_{d} A_{1} A_{2}}{2} \sin[2\omega t + \varphi_{1}(t) + \varphi_{2}(t)]}_{Second \ Part}$$

(1.1)

In the equation (1.1), we can see that the multiplier signal consists of two parts, the first one is the function of only the phase difference of two signals  $S_1(t)$  &  $S_2(t)$  and the second term is at a frequency which is twice the signal frequency (the  $2\omega t \ term$ ) plus the sum of the two phases [24].

We can use the equation (1.1) to develop the PLL by recognizing that the output signal of the multiplier is a function of the phase difference of the two input signals. We can use this useful information to synchronize the two signals. The higher frequency terms in the second part of equation (1.1) (twice the frequency) can be eliminated by filtering it out.

#### 3.3 Loop Filter (LF)

We need a filter from getting rid of the unwanted higher frequency term which is in the second part of equation (1.1).

Figure 9. Filtering the Phase Detector Output signal to remove

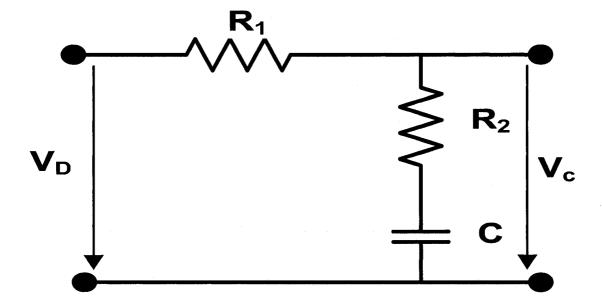

Now we can add a loop filter shown in Figure 9, which acts as a low pass filter, at the output of the PD. In this APLL, we consider a passive first order loop filter.

Figure 10. The Circuit Implementation of the first order passive Loop Filter

The circuit representation of the passive first order loop filter is shown in Figure 10. The output of the low pass filter (LPF) in Figure 9, as the phase difference is varied. It is called LPF because it only passes the lower frequency term and eliminates the higher frequency term. When there is a phase difference, then the signal out of the LPF is just the first part of Equation (1.1). We call this part the error signal which is also called the control signal.

$$S_e(t) = \frac{K_d A_1 A_2}{2} \sin[\varphi_1(t) - \varphi_2(t)]$$

(1.2)

If phase difference is 0 degrees then we would expect the signal  $S_e$  (t) to be zero, which is the desired and the locked-state of the PLL. If the phase between the two signals ( $S_1$  and  $S_2$ ) varies from that, then, we would expect the filtered  $S_3$  signal to change [24]. If the phase difference is not zero, i.e.  $S_e$  (t) is not zero; we need to oscillate the signal. For oscillating the signal, i.e. for making the  $S_e$  (t) signal is zero, we need an oscillator. In order for that we are using the Voltage Controlled Oscillator (VCO).

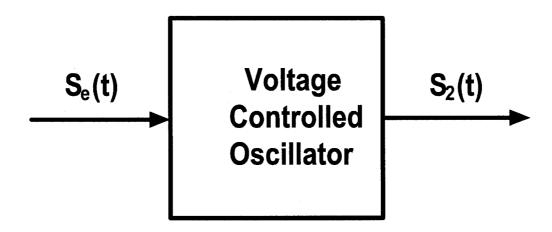

#### 3.4 Voltage Controlled Oscillator (VCO)

Oscillators are a natural and expected part of the electronic scene. They occur in many applications and make possible circuits and subsystems that perform very useful functions. A voltage-controlled oscillator (VCO) (in Fig. 11) is an oscillator where the principle variable is a voltage. The VCO is an integral part of every phase locked loop circuit. It is an electronic oscillator, which is specially designed

to be controlled in oscillation frequency by a voltage input. The frequency of oscillation, or rate of repetition, is varied with an applied DC voltage, while modulating signals may be fed into the VCO to generate frequency modulation (FM) or phase modulation (PM).

Figure 11. Block Diagram of Voltage Controlled Oscillator

The error signal provides an indication of what is happening to the input phase. We need an error signal to have zero amplitude and we can do that only by changing the phase of the signal S2 to match the phase of signal S1. VCO which produce the signal allows us to do that.

VCO in Figure 11 produces a periodic signal, the frequency of which changes based on a control signal applied externally. If the error signal is zero then, the VCO produces just its quiescent (center frequency). But if the error signal is something other than zero, then it responds by changing its operating frequency [24].

A constant of  $k_0$  represents the sensitivity of the VCO. It represents the change in the instantaneous frequency of the VCO as a function of the error signal amplitude such that  $K_0 = \frac{d\omega_0}{dv}$ . The signal out of the VCO is given by,  $S_2(t) = A_2 \cos(\omega_C t + \phi_2(t))$ . The units of  $K_0$  are Hertz per volts. For a given certain input voltage, it will produce a change in the output signal frequency by the following relationship.

$$\omega_{out} = \omega_c + k_0 v(t)$$

Where,  $\omega_c$  is its center or operating frequency. So, if K =5000Hz/volt, then an input of 0.1 volt would produce a new output frequency of  $\omega_c$  + 500 Hz.

For a periodic signal p (t), if its frequency in Hz is equal to the rate of change of phase in  $2\pi$  segment, or  $f(t) = \frac{1}{2\pi} \frac{d\varphi_i(t)}{dt}$  and conversely, phase is the integral part of frequency over certain period of time,  $\varphi_i(t) = 2\pi \int_0^t f_i(t) dt$  (1.3)

This relationship applies to all periodic signals, even those that are non-sinusoidal.

Now we can write the phase of the feed-back signal as,

$$\varphi_{2}(t) = 2\pi K_{0} \int_{0}^{t} S_{e}(t) dt$$

$$= 2\pi K_{0} S_{e}(t) t$$

(1.4)

So as long as the error signal has non-zero amplitude, the phase of the VCO signal will keep on increasing until such time as it is decreased to zero. By substituting the equation (1.4) into equation (1.2) we get,

$$S_e(t) = \frac{K_m A_1 A_2}{2} \sin[\varphi_1(t) - \varphi_2(t)]$$

$$S_{e}(t) = \frac{K_{m} A_{1} A_{2}}{2} \sin[\varphi_{1}(t) - 2\pi K_{0} \int_{0}^{t} S_{e}(t) dt]$$

(1.5)

The equation of S<sub>e</sub> can be linearized by making the following assumption,

$$\sin(\varphi) \approx \varphi \text{ for small } \varphi$$

$\sin[\varphi_1(t) - \varphi_2(t)] \approx [\varphi_1(t) - \varphi_2(t)]$

Now we can rewrite equation (1.5) by removing the sine function.

$$S_{e}(t) = \frac{K_{m} A_{1} A_{2}}{2} [\varphi_{1}(t) - \varphi_{2}(t)]$$

$$S_{e}(t) = \frac{K_{m} A_{1} A_{2}}{2} [\varphi_{1}(t) - 2\pi K_{0} \int_{0}^{t} S_{e}(t)]$$

$$= \frac{K_{m} A_{1} A_{2}}{2} [\varphi_{1}(t) - 2\pi K_{0} S_{e}t]$$

(1.6)

In the equation (1.6),  $S_e$  is the amplitude of  $S_e$  (t) at time t.

For example, if the input signal changes by 10 degrees, this causes that the error signal to slowly increase in amplitude from 0 to 0.1. At time t, the frequency of the

signal produced by the VCO increases by  $K_0S_e$ , where  $S_e$  is the instantaneous amplitude of the error signal and time T is the sampling time.

As long as error signal is present, the phase keeps changing linearly. However, as the phase of the signal out of the VCO changes, the new difference in phase increases and the error signal amplitude decreases at the next go-around. This decreases the phase change further until the error signal amplitude has gone to zero. This is how an analog PLL works.

#### 3.5 Summary

In this chapter, the conventional analog phase locked loop techniques and its important components are introduced. In the following chapter, the mathematical model of digital carrier synchronization (DCS) which is the digital version of analog phase locked loop will be introduced. Some important analysis of our DCS implementation will also be discussed.

## Chapter 4

# Mathematical Model of a Digital Carrier Synchronizer (DCS) in the Discrete Time Domain (Z-Domain)

#### 4.1 Introduction

Before analyzing the mathematical model of a DCS system in the discrete time domain (Z-domain), we have to analyze the corresponding model in the continuous time domain (S -domain). In automatic control system theory, the transfer function of the second-order system in the S-domain (e.g. continuous time domain) can be written as,

$$H_{s}(S) = \frac{\omega_{n}^{2}}{S^{2} + 2\xi\omega_{n}S + \omega_{n}^{2}}$$

(4.1)

Where  $\omega_n$  is defined as natural undamped frequency, and  $\xi$  is defined as damping ratio. This system is called a standard prototype second-order system. Based on the transfer function of a second-order prototype system, a characteristic equation of the system is defined as

$$\Delta(S) = S^2 + 2\xi \omega_n S + \omega_n^2 \tag{4.2}$$

By solving the roots of the characteristic equation, two poles of the system,  $S_0$  and  $S_1$ , can be derived.

$$S_0 = -\xi \omega_n + j\omega_n \sqrt{(1 - \xi^2)}$$

(4.3)

$$S_{l} = -\xi \omega_{n} - j\omega_{n} \sqrt{(1 - \xi^{2})}$$

(4.4)

# 4.1.1 Mapping the Poles of a second-order system from S-domain to Z domain

The transfer function of a second-order system in the Z-domain can be written in a general format as

$$H(Z) = \frac{N(Z)}{(Z - Z_1)(Z - Z_0)}$$

(4.5)

Where  $Z_0$  and  $Z_1$  are two poles of the system in Z-domain. Corresponding to S-domain analysis, a characteristic equation of a discrete-time system is defined as

$$\Delta(Z) = (Z - Z_1)(Z - Z_0) = Z^2 - (Z_1 + Z_0)Z + Z_1Z_0$$

(4.6)

C<sub>1</sub> and C<sub>0</sub> are defined as coefficients of the characteristic equation:

$$C_{I} = -(Z_{I} + Z_{0})$$

$$C_{0} = Z_{I}Z_{0}$$

(4.7)

Then the characteristic equation can be written in the simplified format

$$\Delta(Z) = Z^{2} + C_{1}Z + C_{0} \tag{4.8}$$

By the definition of a discrete-time transformation [25], two poles of this system in the Z-domain can be mapped from the poles in S-domain as

$$Z_{0} = e^{s_{0}T_{s}}$$

$$\therefore Z_{0} = e^{(-\xi \omega nT_{s} + j\omega nT_{s}\sqrt{(1-\xi^{2})}}$$

and

$$Z_{1} = e^{s_{1}T_{s}}$$

$$\therefore Z_{1} = e^{(-\xi \omega_{n}T_{s} - j\omega_{n}T_{s}\sqrt{(1-\xi^{2})}}$$

$$(4.9)$$

Where, Ts is the sampling period of the discrete system.

With the poles mapped in the Z-domain and Equation (4.7), coefficients  $C_0$  and  $C_1$  of the characteristic equation (Equation 4.8) described by the parameters  $\xi$  and  $\omega_n$ :

$$C_{0} = e^{-2 \xi \omega_{n} T_{s}}$$

$$C_{1} = -2 e^{-\xi \omega_{n} T_{s}} \cos(\omega_{n} T_{s} \sqrt{(1 - \xi^{2})})$$

(4.10)

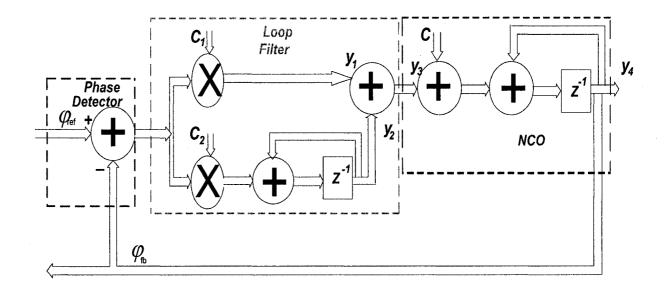

#### 4.2 Mathematical model of DCS Architecture

The mathematical model of DCS in discrete time domain (*Z-domain*) is shown in Figure 12. This DCS consists of three most important functional units:

- (a) phase detector

- (b) loop filter

- (c) numerically controlled oscillator (NCO)

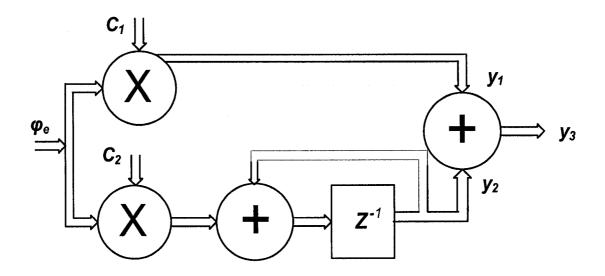

Figure 12. Mathematical model of DCS in discrete time domain (Z-domain)

Initially phase detector (PD) computes the phase error ( $\varphi_e$ ) depending on the phase ( $\varphi_{ref}$ ) of the reference signal,  $data\_ref$  and the phase ( $\varphi_{fb}$ ) of the feedback signal,  $data\_fb$ . Then this phase error is filtered and finally, it is used to control the instantaneous output phase of the NCO ( $\varphi_{fb}$ ). In figure 4.1, the coefficients  $C_1$  and  $C_2$  are used as a parameter of the digital loop filter, where  $C_1 = 1$  and  $C_2 = 0$ , +1 or -1. In NCO, the parameter C is fixed for a constant value of 1.

The transfer functions of each component in the DCS are in the Z-transform format and analysis shown in the next section.

#### 4.3 Analysis of the DCS

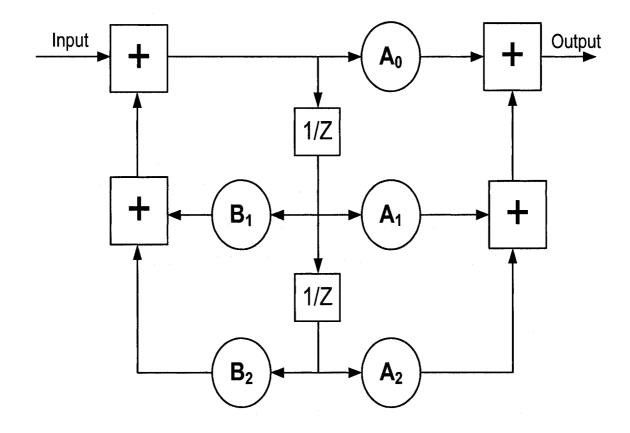

#### 4.3.1 Transfer function of Loop Filter in the Z-domain

Figure 13 shows the loop filter in the discrete time (Z-domain) domain. The loop filter takes the phase error ( $\varphi_e$ ) as an input and outputs  $y_3$  depending on the

value of the coefficients  $C_1$  and  $C_2$ . The transfer function of the loop filter is as follows:

$$y_{2} = C_{2}\varphi_{e} + y_{2}Z^{-1}$$

$$\Rightarrow Zy_{2} - y_{2} = C_{2}Z\varphi_{e}$$

$$\Rightarrow y_{2} = \frac{C_{2}Z\varphi_{e}}{(Z - 1)}$$

$$(4.11)$$

and  $y_i = C_i \varphi_e$  (4.12)

Figure 13. Block diagram of Loop Filter in Z-domain

Now adding the equation (4.11) and (4.12), we can get

$$y_{3} = y_{2} + y_{1}$$

$$\Rightarrow y_{3} = \frac{C_{2}Z\varphi_{e}}{(Z-1)} + C_{1}\varphi_{e}$$

$$\Rightarrow y_{3} = \frac{C_{2}Z\varphi_{e} + C_{1}(Z-1)\varphi_{e}}{(Z-1)}$$

$$\Rightarrow y_{3} = H_{1}(Z) = \frac{\varphi_{e}[C_{2}Z + C_{1}(Z-1)]}{(Z-1)}$$

$$(4.13)$$

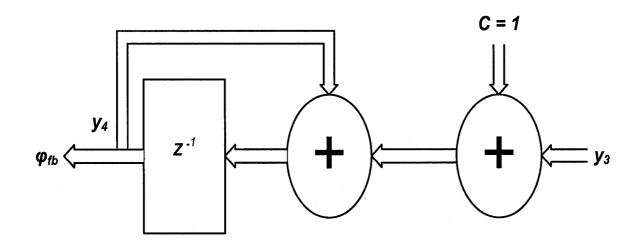

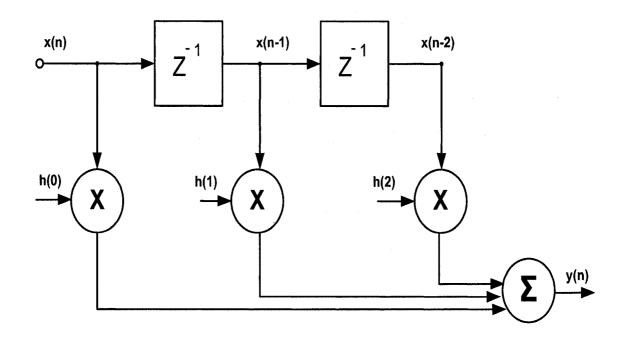

#### 4.3.2 Transfer function of NCO in the Z-domain

The NCO in the discrete time (Z-domain) domain is shown in Figure 14. This NCO takes  $y_3$  as an input which controls the instantaneous output phase of the NCO ( $\varphi_{fb}$ ).

Figure 14. Block diagram of NCO in Z-domain

The transfer function of NCO in the discrete time domain is as follows:

$$y_{4} = (y_{4})Z^{-1} + (y_{3})Z^{-1}$$

$$\Rightarrow y_{4}Z = y_{3} + y_{4}$$

$$\Rightarrow y_{4} = \frac{y_{3}}{(Z - 1)}$$

(4.14)

Now combining the equation (4.13) and (4.14), we can get

$$y_{4} = \frac{1}{(Z-1)} * \frac{\varphi_{e}[C_{2}Z + C_{1}(Z-1)]}{(Z-1)}$$

$$\Rightarrow y_{4} = \frac{1}{(Z-1)^{2}} * \varphi_{e}[C_{2}Z + C_{1}(Z-1)]$$

So,

$$\varphi_{fb}(Z) = \frac{\varphi_e[C_2Z + C_1(Z - 1)]}{(Z - 1)^2}$$

$$\Rightarrow \varphi_{fb}(Z) = H_2(Z) = \frac{\varphi_e[(C_1 + C_2)Z - C_1]}{(Z - 1)^2}$$

(4.15)

We know that,

$$H(Z) = \frac{\varphi_{fb}(Z)}{\varphi_{ref}(Z)} \tag{4.16}$$

Then the closed-loop transfer function of our DCS model, H (Z), would be

$$H(Z) = \frac{\varphi_{\beta}(Z)}{\varphi_{M}(Z)} = \frac{A}{1 + \beta A} = \frac{H_{1}(Z)H_{2}(Z)}{1 + H_{1}(Z)H_{2}(Z)\beta}$$

$$\therefore H(Z) = \frac{H_{1}(Z)H_{2}(Z)}{1 + H_{1}(Z)H_{2}(Z)}$$

Since, the data from the NCO goes directly back to the phase detector, this DCS has unity feedback. Therefore, we set  $\beta = 1$ .

The expanded format of the transfer function of H(Z) can be derived as follows,

$$\therefore \varphi_{e}(Z) = \varphi_{ref}(Z) + (-\varphi_{fb})(Z)

\Rightarrow \varphi_{e}(Z) = \varphi_{ref}(Z) - \frac{\varphi_{e}[(C_{1} + C_{2})Z - C_{1}]}{(Z - 1)^{2}}

\Rightarrow \varphi_{e}(Z) = \varphi_{ref}(Z)[(Z - 1)^{2}] * \frac{1}{(Z - 1)^{2} + [(C_{1} + C_{2})Z - C_{1}]}

\Rightarrow \varphi_{e}(Z) = \frac{(Z - 1)^{2}}{(Z - 1)^{2} + [(C_{1} + C_{2})Z - C_{1}]} * \varphi_{ref}(Z)$$

(4.17)

Substituting Equation (4.17) into Equation (4.15) produces

$$\varphi_{fb}(Z) = \frac{[(C_1 + C_2)Z - C_1]}{(Z - 1)^2} * \frac{(Z - 1)^2}{(Z - 1)^2 + [(C_1 + C_2)Z - C_1]} * \varphi_{ref}(Z)$$

$$\Rightarrow \varphi_{fb}(Z) = \frac{(C_1 + C_2)Z - C_1}{(Z - 1)^2 + [(C_1 + C_2)Z - C_1]} * \varphi_{ref}(Z)$$

$$\Rightarrow \frac{\varphi_{fb}(Z)}{\varphi_{ref}(Z)} = \frac{(C_1 + C_2)Z - C_1}{(Z - 1)^2 + [(C_1 + C_2)Z - C_1]}$$

$$H(Z) = \frac{\varphi_{fb}(Z)}{\varphi_{ref}(Z)} = \frac{(C_1 + C_2)Z - C_1}{(Z - 1)^2 + [(C_1 + C_2)Z - C_1]}$$

(4.18)

$$\therefore H(Z) = \frac{(C_1 + C_2)Z - C_1}{Z^2 - 2Z - 1 + C_1 Z + C_2 Z - C_1}$$

$$= \frac{(C_1 + C_2)Z - C_1}{Z^2 + (C_1 + C_2 - 2)Z + (1 - C_1)}$$

$$H(Z) = \frac{(g_1 + 2)Z - (1 - g_0)}{(Z^2 + g_1 Z + g_0)}$$

(4.19)

where,

$$C_1 + C_2 - 2 = g_1$$

and  $1 - C_1 = g_0$  (4.20)

The coefficients C<sub>1</sub> and C<sub>2</sub> can be resolved based on Equations 4.20 and 4.10:

$$C_{1} = 1 - e^{-2\xi\omega_{n}T_{s}}$$

$$C_{2} = 1 + e^{-2\xi\omega_{n}T_{s}} - 2e^{-\xi\omega_{n}T_{s}} \cos(\omega_{n}T_{s}\sqrt{(1-\xi^{2})})$$

#### 4.3.3 Phase Error Response of the DCS

Due to the reference phase  $(arphi_{ ext{\tiny ref}})$  i.e. input phase, the phase error response  $(arphi_{ ext{\tiny e}})$  is

$$\varphi_{e}(Z) = \frac{(Z-1)^{2}}{(Z-1)^{2} + [(C_{1} + C_{2})Z - C_{1}]} * \varphi_{ref}(Z)$$

Assume that the phase of the input signal, i.e. reference signal has a step change. In the time domain, step changing of the phase of the reference signal can be described by the step function

$$\varphi_{ref}(t) = \Delta \varphi * u(t) \tag{4.21}$$

Where, u(t) is the unit step function and  $\Delta \varphi$  is the constant phase value of the reference signal by which the input signal phase jump. Now applying the Z-transform to the equation (4.21) yields

$$\varphi_{ref}(Z) = \frac{\Delta \varphi * Z}{(Z-1)} \tag{4.22}$$

The output-response function of the DCS for a phase-step input can be written as

$$\varphi_{fb}(Z) = H(Z)^* \varphi_{ref}(Z)$$

$$\Rightarrow \varphi_{fb}(Z) = \frac{\Delta \varphi * Z}{(Z-1)} * \frac{(g_1 + 2)Z - (1 - g_0)}{(Z^2 + g_1 Z + g_0)}$$

(4.23)

Based on the Equation (4.22), a numerical analysis can be carried out by using an existing software tool such as MATLAB. By this way, the steady-state error of an implemented DCS system can be observed.

By the definition of phase error, a phase error  $(\mathit{Err}(Z))$  function can be written as

$$Err (Z) = \varphi_{ref} (Z) - \varphi_{fb} (Z)$$

(4.24)

Substituting Equation (4.16) into Equation (4.23) produces

$$Err(Z) = [1 - H(Z)] \varphi_{ref}(Z)$$

(4.25)

Now substituting Equations (4.18) and (4.22) into Equation (4.25), the phaseerror function can be written as

$$Err(Z) = \frac{\Delta \varphi Z(Z-1)}{(Z^2 + g_1 Z + g_0)}$$

(4.26)

According to the Final-Value Theorem,

$$\lim_{K \to \infty} e(KT) = \lim_{Z \to 1} (1 - Z^{-1}) Err(Z)$$

(4.27)

The steady-state error, which is the final value of e (KT) in the time-domain, can be derived by using this Final-Value Theorem [26]. The condition for using the Final-Value Theorem is that the function (1-  $Z^{-1}$ ) Err (Z) has no poles on or outside the unit circle |Z|=1 in the Z-plane.

Substituting Equation (4.18) into Equation (4.21) yields

$$\lim_{K \to \infty} e(KT) = \lim_{Z \to 1} \frac{\Delta \varphi Z(Z-1)}{(Z^2 + g_1 Z + g_2)} = 0$$

It shows that the steady-state phase error is zero for the phase step input ( $\Delta \varphi$ ).

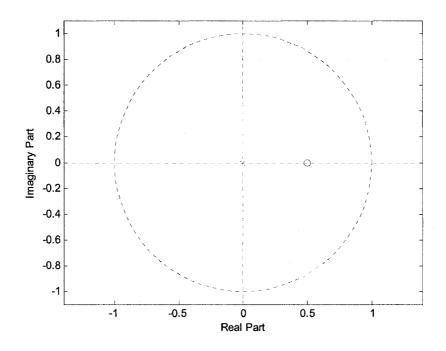

#### 4.3.4 Stability analysis of the DCS

One mandatory requirement for designing DCSs is that the DCS system must be stable. Basically, the stable condition of a discrete-time system occurs when the roots of the characteristic equation are inside the unit circle |Z| = 1 in the Z-plane (Shown in Fig. 15). Normally, after a system is implemented, numerical coefficients can be substituted into the characteristic equation. By solving the characteristic equation numerically, the positions of the poles can be found to determine if the system is stable.

One of the most efficient methods for testing the stability of a discrete-time system is Jury's stability criterion [27]. This method can guide the designs of a DCS to converge to an optimized stable system quickly, without a large amount of numerical calculation and simulation.

Figure 15. Pole-Zero Plot for a stable DCS

It can be applied directly to the DCS model (Shown in Fig. 12) to determine the stable condition. According to this criterion, the necessary and sufficient conditions are that the characteristic equation of DCS,

$$\Delta(Z) = a_{2}Z^{2} + a_{1}Z + a_{0} = 0$$

Should meet the following conditions in order to have no roots on or outside the unit circle:

$$\Delta(1) > 0,$$

$\Delta(-1) > 0, and |a_0| < a_2$

Applying these conditions to the denominator of Equation (2.11), the stable condition ranges of this DCS model can be derived as

$$0 < C_{_{1}} < 2$$

$$0 < C_2 < 4$$

#### 4.3.5 Tracking Range of the DCS

In the previous section we showed that the  $2^{nd}$  order DCS is stable. Now it will be shown that this loop can also track a step input. To study the tracking, we examine the phase error  $(\varphi_e)$  that results from a simplified reference or input  $(\varphi_{ref})$ . A small phase error is usually desired and is considered to be the criterion of good tracking performance. If the error should become so large that the NCO skips cycles, the loop is considered to have lost lock, even if momentarily [28].

As the tracking range of DCS is proportional to the loop DC gain [29], we can expect a very wide tracking range. The tracking range is only limited by the half of the sampling frequency, which is  $f_s/2$ . The loop DC gain is given by

$$K_{v} = \lim_{Z \to I} \left[ \frac{C_{2}(Z - I) + C_{I}}{(Z - I)^{2}} \right] \to \infty$$

$$(4.28)$$

#### 4.4 Summary

In this chapter, a mathematical model of DCS architecture was derived, through which an in-depth understanding of DCS is attained. Some important parameters and stability of the DCS model are also analyzed. In the next chapter, the methodology and datapath implementation of DCS and the analysis of its important components will be presented.

## **Chapter 5**

# Design and Datapath Implementation of Digital Carrier Synchronizer (DCS)

#### 5.1 Introduction

An important task for a digital communications receiver is to remove any frequency or phase offsets that might exist between the transmitter and receiver oscillators. A carrier-recovery loop is designed and implemented in order to remove this offset. A key component of a carrier-recovery loop is a phase-locked loop (PLL).

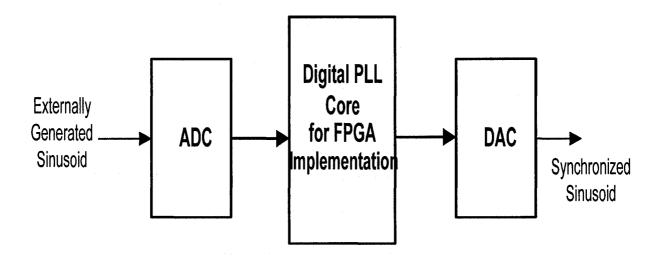

Figure 16. Digital Carrier Synchronization Path on the FPGA platform

The use of a PLL enables the receiver to adaptively track and remove frequency or phase offsets [30]. Figure 16 shows the digital carrier synchronization path.

An analog to digital carrier (ADC) receives the externally generated sinusoid signal and outputs the sample data as input to the digital PLL which is implemented in the FPGA, and a digital to analog converter (DAC) receives the locally generated data and outputs the synchronized sinusoid signal.

The goal of this digital carrier synchronization (DCS) is to produce a locally generated data samples called data\_fb which is synchronized to input data samples called data\_ref. Three major functional units of DCS shown in Figure 17 are A. Phase Detector (PD), B. Loop Filter (LF), and C. Numerically Controlled Oscillator (NCO).

#### 5.2 Phase Detector

A PLL is driven by the phase error, in analog PD it was S<sub>3</sub> (t), signal which is

Figure 17. Datapath of the Digital Carrier Synchronization

generated by the phase detector. The phase detector generates the phase difference value on the input signal and the oscillated signal, i.e.  $data\_ref$  (in analog it was  $S_1$  (t) and  $data\_fb$  (in analog it was  $S_2$  (t)), with respects to their rising edges.

#### 5.2.1 Data path of the Phase Detector

The datapath of the phase detector is shown in Figure 18. The *data\_ref* signal is driven by the sampling clock, which is the system clock. In order to achieve the higher detection accuracy, a higher frequency for the detection clock may be used.

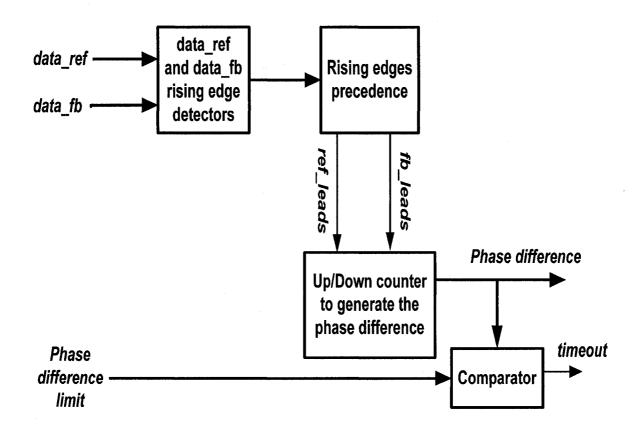

Figure 18. Datapath of Phase Detector

In Figure 18, the edge detector block detects the edges of the *data\_ref* and *data fb* signals with respect to the rising edge of the clock.

- if (data\_ref(n-1) < 0 and data\_ref(n) ≥ 0), posedge\_ref = 1</li>

- if (data\_fb(n-1) < 0 and data\_fb(n) ≥ 0), posedge\_fb = 1</li>

Where, posedge\_ref indicates the rising edge of the data\_ref and posedge\_fb shows the rising edge of the data\_fb signal. The rising edge of the data\_ref and the rising edge of the data fb are determined in one clock cycle.

The rising edges precedence block provides the precedence of the data\_ref or the data\_fb rising edges, which are indicated by ref\_leads and fb\_leads (in Fig. 18) respectively.

- if (posedge ref =1 and data fb < 0), ref leads = 1

- if (posedge\_fb =1 and data\_ref < 0), fb\_leads = 1

Where, ref\_leads =1 shows that the posedge\_ref comes before the posedge\_fb signal, i.e. the reference signal comes before the feedback signal, and fb\_leads =1 indicates that the posedge fb occurs before the posedge ref.

And an up/down counter accumulates the phase steps between the two edges to output the phase difference. If ref\_leads = 1, the up/down counter (in Fig. 18) will increment, and if fb\_leads = 1, the counter will decrement. In this way the counter provides the phase difference value at the output of the phase detector.

Finally, the timeout signal indicates that the phase difference between the two input signals data\_ref and data\_fb are larger than the phase limit, which is set by

the user. For reducing phase difference value (phase error), we need to filter the signal.

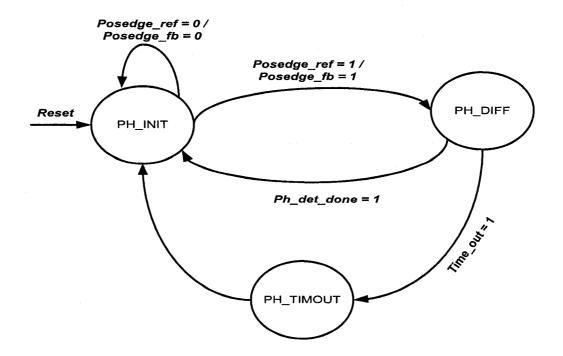

Figure 19. Phase Detection State machine

A phase detect state machine is shown in Figure 19. It has three states phase initialization, phase difference, and phase detects state.

#### 5.3 First Order Digital Loop Filter (LF)

A first order digital Loop Filter is used to filter the phase difference or phase error  $(\varphi_e)$  signal, which is generated by the phase detector in order to supply the required correction to the NCO.

#### 5.3.1 Data path of the Loop Filter

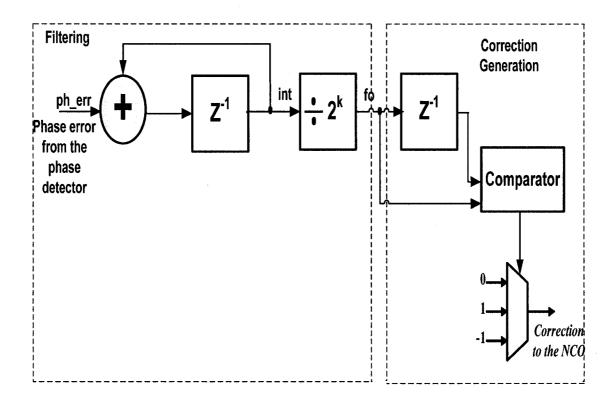

Figure 20 shows the datapath of the first order loop filter. It has two parts: the

Figure 20. Datapath of 1st Order Loop Filter

filtering part and the correction generation part. The filtering part, firstly, it integrates the phase error (*ph\_err*) signal, which is obtained from the output of the phase detector. Secondly, it accumulates the value and finally, it shifts the accumulated value to set the required bandwidth for the filter. If the output of the filtering part, which is the integrator value, provides the most significant bit (MSB), the filter will pass the lowest phase error frequencies. And if the output of the integrator is least significant bits, it will pass the highest phase error

frequencies. For this implementation, the filter passes the LSBs as the integrator (int in Fig. 20) is divided by the  $2^k$ .

The expression of the integrator is,

$$int(n) = ph \quad err(n) + ph \quad err(n-1) \tag{5.1}$$

If we compare the equation (5.1) with the equation (4) of analog loop filter, we can see the same relationship. In the correction generation part, it compares the previous value of the output of the filtering part with the old value of the filtering part. This gives the trend of the phase error. The expression for the correction generation part is:

Correction to the NCO =

$$\begin{cases} -1, & \text{if } fo(n) < fo(n-1) \\ 0, & \text{if } fo(n) = fo(n-1) \\ +1, & \text{if } fo(n) > fo(n-1) \end{cases}$$

Where, fo determines the output of the filter. In order to ensure that the output of NCO changes smoothly, the absolute correction value doesn't go over 1. Last but not the least; we also use the 2<sup>nd</sup> order loop filter in order to examine the overall performance of our DCS.

#### **5.4 Numerically Controlled Oscillator (NCO)**

Numerically Controlled Oscillator (NCO) is one of the key components of digital carrier synchronizer (DCS). In DCS, NCO allows to perform the precise

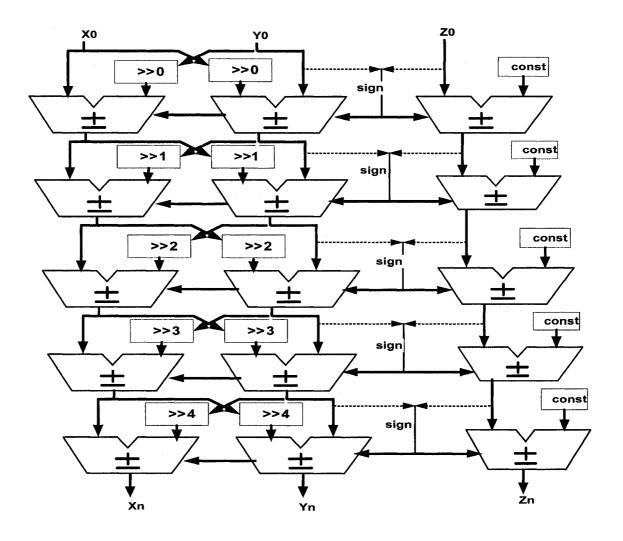

adjustment of the carrier frequency based on the output of the phase-detecting circuit. The NCO is controlled by the numerical value or the sampling index (discussed later). For generating periodic-like signal, NCO is an established method. In this research, we investigate three different types of NCO, which are used in DCS. The first one is the Look Up Table (LUT) based NCO, the second is CORDIC based NCO, and the finally Xilinx ROM based NCO.

#### 5.4.1 Datapath of Look Up Table (LUT) Based NCO

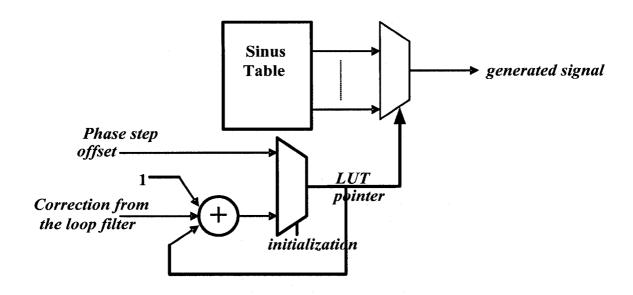

A Lookup Table (LUT) based NCO implementation is shown in Figure 21. It is

Figure 21. Look Up Table (LUT) Based NCO

one of the popular schemes to implement numerically controlled oscillator based on table-look-up. A lookup table method stores the samples of the sinusoidal signal depending on the carrier frequency, the sampling frequency and the carrier amplitude. Afterwards those samples are being read out of the lookup table to produce the sinusoidal signal in an order determined by the total number of samples or sampling index. According to our design specification [30], the given parameters are, carrier frequency, Fc = 2.048 MHZ, the sampling frequency, Fs = 50 MHz. Since our data bus has one sign bit [MSB] and seven data bits, the carrier amplitude, A is equal to  $2^7 - 1 = 127$ . Hence, the maximum value of the sample index n, is equal to, (Fs / Fc), 24. Bearing this in mind, we can state that the data\_fb, which is generated by the NCO block, is a function of n and can be represented by Equation (5.1).

$$data \quad fb(n) = A\sin(2pi * (Fc/Fs) * n) \tag{5.1}$$

The above equation signifies the output value of  $data\_fb$  in terms of the sampling index n, carrier Frequency  $F_c$ , sampling frequency  $F_s$  and the amplitude A. Note that the number of sampling clock periods in one carrier period cannot exceed the value of  $F_s/F_c$  and the smallest angle value is  $2*pi/(F_s/F_c)$ . It is easily visible to the readers that the sample index n is the LUT pointer value which is shown in Figure 21. If the  $LUT\_Pointer$  exceeds the value of  $F_s/F_c$ , the previous value of  $data\_fb$  is retained with the Flip-Flop.

In the following sections, we will explain the datatapath modification of different DCS implementations that means modification of Loop Filter and NCO. The first order digital loop filter and NCO with look up table were explained in section 5.3 and 5.4 respectively. Now we will first discuss the implementation and analysis of

the second order digital loop filter with its different parameters. Then we will explain the implementation of CORDIC based and Xilinx ROM based NCO.

#### 5.5 Digital Loop Filter

Digital filters are preferably used in the place of analog filters as they eliminate a number of problems associated with their classical analog counterparts. Digital filters belong to the class of discrete-time LTI (linear time invariant) systems, which are characterized by the properties of causality, recursibility, and stability [25]. They can be characterized in the time domain by their unit-impulse response and in the frequency domain by their transfer function. The unit-impulse response sequence of a causal LTI system can be of either finite or infinite duration, which determines whether they are classified as Finite Impulse Response (FIR) or Infinite Impulse Response (IIR) systems. FIR filters include low-pass, high-pass, band-pass, and band-stop filters [25].