# Verification and Validation Techniques in Systems Engineering: Application to State-Chart Diagrams

Payam Kafashe Panjeh Shahi

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

December 2006

© Payam Kafashe Panjeh Shahi, 2006

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-28918-1 Our file Notre référence ISBN: 978-0-494-28918-1

### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **ABSTRACT**

Verification and Validation Techniques in Systems Engineering: Application to State-Chart Diagrams

### Payam Kafashe Panjeh Shahi

Verification and validation have become very important steps in systems engineering. This is due to the increasing complexity of nowadays systems. Verification and validation aims at detecting flaws early in the design process and/or to verify/validate design models of systems. The state of the art techniques in this field are mainly based on simulation and extensive testing. In this thesis, we propose a new paradigm for verification and validation in systems engineering. It is based on an established synergy between program analysis, software engineering techniques and automatic verification. To illustrate this paradigm, we present a technique for the verification/validation of state-chart diagrams in UML/SysML modeling languages.

To my dear family:

Javad,

Heshmat

and Raham.

And also I would like to appreciate Mr. Mohammed Rostami Safa, The president of Saveh Rolling and Profile Mills Company, for his generosity and gentleness. Without his aid, this thesis could not have been written.

### **ACKNOWLEDGEMENTS**

I have been very fortunate to have Dr. Mourad Debbabi as my supervisor. I am deeply grateful for his strong support and encouragement throughout my master studies. His expertise and judicious advice have shaped the execution of my research.

I also wish to express my gratitude to the examination committee members for reviewing my thesis and giving me valuable feedback.

During my studies in Concordia University many people have encouraged me. I have enjoyed doing research and working with my colleagues. I thank all of them for their support and the nice time we have spent together.

I would like to reserve my deepest appreciations to my family for their perpetual love and encouragements. I can never thank them enough.

# TABLE OF CONTENTS

| LI | ST O                                                              | F FIGU                                         | JRES                                    | xi |  |

|----|-------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----|--|

| 1  | Intr                                                              | Introduction                                   |                                         |    |  |

|    | 1.1                                                               | Backg                                          | round and Motivations                   | 1  |  |

|    | 1.2                                                               | Objec                                          | tives                                   | 2  |  |

|    | 1.3                                                               | Contri                                         | ibutions                                | 3  |  |

|    | 1.4                                                               | Struct                                         | ure                                     | 3  |  |

| 2  | Systems Engineering, Definition and Standards                     |                                                |                                         |    |  |

|    | 2.1                                                               | Objec                                          | t Management Group                      | 6  |  |

|    |                                                                   | 2.1.1                                          | Model Driven Architecture               | 6  |  |

|    |                                                                   | 2.1.2                                          | Meta Object Facility                    | 8  |  |

|    |                                                                   | 2.1.3                                          | XML Metadata Interchange Format         | g  |  |

|    | 2.2                                                               | INtern                                         | national COuncil on Systems Engineering | 12 |  |

|    | 2.3                                                               | International Organization for Standardization |                                         |    |  |

|    | 2.4 Unified Modeling Language                                     |                                                |                                         | 13 |  |

|    |                                                                   | 2.4.1                                          | History                                 | 13 |  |

|    |                                                                   | 2.4.2                                          | Infrastructure and Superstructure       | 16 |  |

|    |                                                                   | 2.4.3                                          | Profiles                                | 19 |  |

|    | 2.5                                                               | Syster                                         | m Modeling Language                     | 23 |  |

|    |                                                                   | 2.5.1                                          | History                                 | 24 |  |

|    |                                                                   | 2.5.2                                          | Diagrams                                | 25 |  |

| 3  | Verification, Validation and Accreditation in Systems Engineering |                                                |                                         |    |  |

|    | 3.1                                                               | Introduction                                   |                                         |    |  |

|    | 2.9                                                               | Forms                                          | 1 Varification                          | 90 |  |

|   | 3.3                                                                   | Progra                                  | ım Analysis                                               | 32 |  |  |

|---|-----------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------|----|--|--|

|   | 3.4                                                                   | Softwa                                  | are Engineering Techniques                                | 33 |  |  |

|   | 3.5                                                                   | Projects on Verification and Validation |                                                           | 39 |  |  |

|   |                                                                       | 3.5.1                                   | Validation and Verification of Object Technology          | 40 |  |  |

|   |                                                                       | 3.5.2                                   | Model-Based Verification and Validation of Properties     | 42 |  |  |

|   |                                                                       | 3.5.3                                   | vUML                                                      | 42 |  |  |

|   |                                                                       | 3.5.4                                   | OMEGA                                                     | 43 |  |  |

|   |                                                                       | 3.5.5                                   | Socle                                                     | 43 |  |  |

|   |                                                                       | 3.5.6                                   | Verification and Validation of UML Dynamic Specifications | 44 |  |  |

|   |                                                                       | 3.5.7                                   | Hugo/RT                                                   | 44 |  |  |

| 4 | A New Paradigm for Verification and Validation of Systems Engineering |                                         |                                                           |    |  |  |

|   | 4.1                                                                   | Appro                                   | ach                                                       | 46 |  |  |

|   | 4.2                                                                   | Systen                                  | n Aspects and System Properties                           | 47 |  |  |

|   | 4.3                                                                   | Verific                                 | ation and Validation Framework                            | 50 |  |  |

| 5 | Ver                                                                   | ificatio                                | on and Validation of State-Chart Diagram                  | 52 |  |  |

|   | 5.1                                                                   | 5.1 State-Chart Description             |                                                           |    |  |  |

|   |                                                                       | 5.1.1                                   | State                                                     | 54 |  |  |

|   |                                                                       | 5.1.2                                   | Top State                                                 | 55 |  |  |

|   |                                                                       | 5.1.3                                   | Composite State                                           | 55 |  |  |

|   |                                                                       | 5.1.4                                   | Composite Concurrent State                                | 56 |  |  |

|   |                                                                       | 5.1.5                                   | Simple/Basic State                                        | 56 |  |  |

|   |                                                                       | 5.1.6                                   | Pseudo-state                                              | 56 |  |  |

|   |                                                                       | 5.1.7                                   | Submachine-state                                          | 58 |  |  |

|   |                                                                       | 5.1.8                                   | Stub-state                                                | 59 |  |  |

|   |                                                                       | 5.1.9                                   | Synch-state                                               | 59 |  |  |

|   |                                                                       | 5.1.10                                  | Hierarchical State Decomposition                          | 59 |  |  |

| 7 Conclusion |     |         | n                                                                 | 113 |

|--------------|-----|---------|-------------------------------------------------------------------|-----|

| 6            | Cas | se Stud | у                                                                 | 109 |

|              |     | 5.3.11  | Promela Code Generation Algorithm                                 | 101 |

|              |     | 5.3.10  | Translation of UML State-Charts to Extended Hierarchical Automata | 99  |

|              |     | 5.3.9   | Rules                                                             | 97  |

|              |     | 5.3.8   | Automated State and Transition Verification                       | 96  |

|              |     |         | tomata                                                            | 88  |

|              |     | 5.3.7   | Implementing State-Charts in SPIN using Extended Hierarchical Au- |     |

|              |     | 5.3.6   | LTL Model Checking using SPIN                                     | 84  |

|              |     | 5.3.5   | Linear-Time Temporal Logic Properties                             | 82  |

|              |     | 5.3.4   | Model Checking of State-Charts by Translating to SPIN             | 82  |

|              |     | 5.3.3   | Translation of UML State-Charts to Extended Hierarchical Automata | 79  |

|              |     | 5.3.2   | Procedure                                                         | 78  |

|              |     | 5.3.1   | Objectives                                                        | 78  |

|              | 5.3 | State-0 | Chart Verification and Validation                                 | 78  |

|              |     | 5.2.8   | State Transitions                                                 | 76  |

|              |     | 5.2.7   | UML State-Charts and Extended Hierarchical Automata               | 74  |

|              |     | 5.2.6   | State Machine                                                     | 69  |

|              |     | 5.2.5   | Transition Execution Sequence                                     | 68  |

|              |     | 5.2.4   | Guards                                                            | 68  |

|              |     | 5.2.3   | Transitions                                                       | 65  |

|              |     | 5.2.2   | Events                                                            | 65  |

|              |     | 5.2.1   | States                                                            | 61  |

|              | 5.2 | State-0 | Chart Semantics                                                   | 61  |

|              |     | 5.1.12  | Transitions                                                       | 60  |

|              |     | 5.1.11  | Events and Guards                                                 | 59  |

6

Bibliography 115

# LIST OF FIGURES

| 2.1  | MDA Layers                                 | 7  |

|------|--------------------------------------------|----|

| 2.2  | OMG 4-Layer Architecture                   | 8  |

| 2.3  | XMI File Example                           | 11 |

| 2.4  | XMI Diagram                                | 11 |

| 2.5  | History of UML                             | 14 |

| 2.6  | Example of a Constraint                    | 19 |

| 2.7  | Example of a Stereotype and a Tagged Value | 20 |

| 2.8  | UML 2.0 Taxonomy                           | 21 |

| 2.9  | Example of a State Machine Diagram         | 22 |

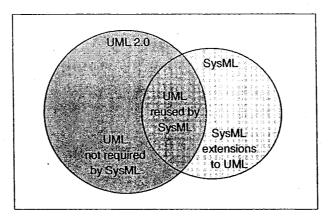

| 2.10 | UML and SysML Compliance                   | 24 |

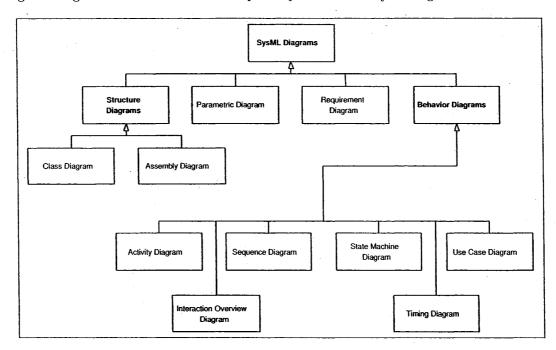

| 2.11 | SysML Diagrams Taxonomy                    | 25 |

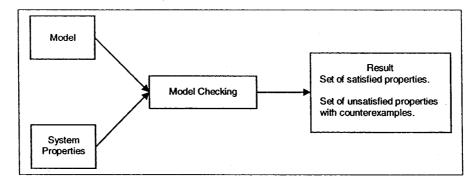

| 3.1  | Formal Verification by Model-Checking      | 30 |

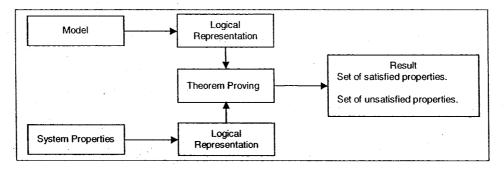

| 3.2  | Theorem Proving Formal Verification        | 32 |

| 3.3  | Data Coupling                              | 34 |

| 3.4  | Stamp Coupling                             | 34 |

| 3.5  | Control Coupling                           | 35 |

| 3.6  | External Coupling                          | 35 |

| 3.7  | Common Coupling                            | 35 |

| 3.8  | Functional Cohesion                        | 36 |

| 3.9  | Sequential Cohesion                        | 37 |

| 3.10 | Communicational Cohesion                   | 37 |

| 3.11 | Procedural Cohesion                        | 38 |

| 3.12 | Logical Cohesion                           | 38 |

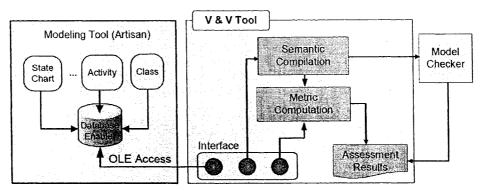

| 4.1 | Architecture of the Framework              | 50  |

|-----|--------------------------------------------|-----|

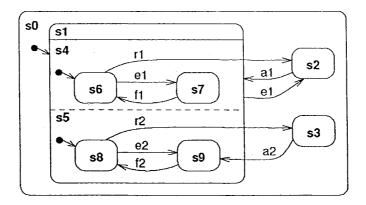

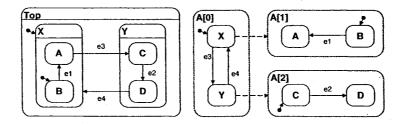

| 5.1 | Example of State-Chart                     | 75  |

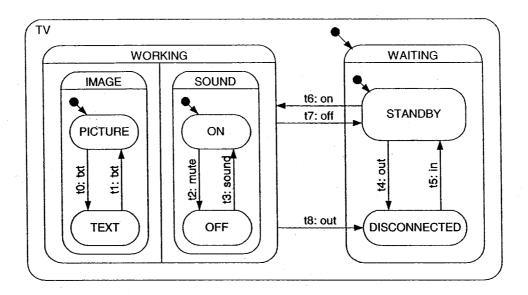

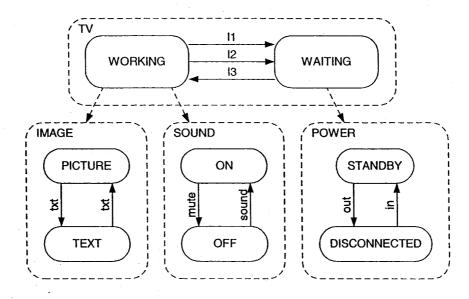

| 5.2 | State-Chart Example Modeling a TV          | 90  |

| 5.3 | EHA Equivalent of the State-Chart TV Model | 90  |

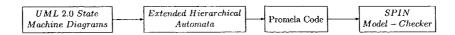

| 5.4 | Model Transformation                       | 99  |

| 6.1 | LCA Example                                | 109 |

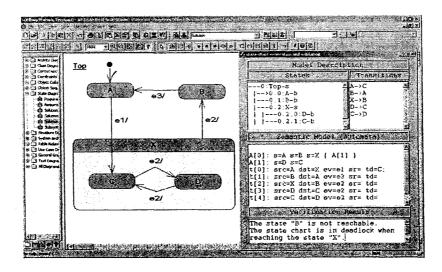

| 6.2 | Verification Tool Snapshot                 | 111 |

# Chapter 1

# Introduction

# 1.1 Background and Motivations

As the size and the complexity of systems continue to increase, verification and validation will become even more essential in the systems development life cycle. Determining whether a system meets its predefined requirements and performs as it is required, have tremendous advantages, such as reduced cost of development, increased efficiency, and enhanced reliability. Exhaustive methods for testing and assuring good quality systems design have become more and more less practical because of the increasing size of and complexity of systems. Both competitiveness and time-to-market requirements mandate that verification and validation be completed within a reasonable period of time and cost. Moreover, as safety becomes a critical concern in many systems, more rigorous methods to verify and validate quality attributes become necessary. Currently, traditional verification and validation methods, such as simulation and semi-formal methods are used to perform the verification and validation tasks. However, these methods are neither rigorous nor exhaustive. Verification and validation are highly recommended, particularly for the development of high safe/secure systems, which require the establishment of their partial or total correctness. The development of these systems under such requirements means that a new paradigm

for verification and validation is needed. This paradigm should cater for automation and rigour. To this end, we propose, in this thesis, a new approach to verification and validation systems engineering. This approach is based on an established synergy between program analysis, software engineering techniques and automatic verification. The advantages of the proposed approach include automation, formality, rigour and cost effectiveness. By automation, we mean the execution of the verification and validation by automatic procedures. This is achieved by using formal automatic verification such as model checking together with program analysis techniques. The proposed approach rests on formal methods that are based on well-defined (syntax and semantics) specification languages and proving techniques (sound semantic based verification algorithms). Rigour comes as a downstream result of formality. The proposed approach is cost effective since it automates verification and validation tasks and abstracts away the underlying complexity in well-defined and automated techniques.

## 1.2 Objectives

The primary objectives of this thesis are:

- To report and present the main standardization bodies, initiatives and languages in the area of systems engineering.

- To compile and compare the state of the art in terms of verification and validation and systems engineering.

- To prepare a new approach to do verification and validation in systems engineering that will achieve more automation, rigour and formality.

- To illustrate in detail the proposed approach on state-chart diagrams in UML/SysML modeling languages.

### 1.3 Contributions

The main contributions of this thesis are:

- Study of the most prominent standardization bodies, initiatives and languages in systems engineering.

- Study of the state of the art techniques in the area of the systems engineering.

- Elaboration of a new approach for verification and validation for systems engineering that is based on an established synergy between program analysis, software engineering techniques and automatic verification.

- Elaboration of verification techniques for state-chart diagrams for UML/SysML modeling languages.

- Illustration of the verification techniques on a case study.

- Design and implementation of a verification and validation software framework that prototypes the proposed approach.

### 1.4 Structure

Here is the way the rest of the thesis is organized. Chapter 2 is dedicated to a presentation of the relevant standardization bodies, standards and initiatives in the area of systems engineering. Chapter 3 is devoted to a presentation of some techniques that are relevant to verification and validation in systems engineering. Control flow analysis, data flow analysis and slicing are briefly introduced. Moreover, a presentation of the state of the arts techniques for the verification and validation in systems engineering is given. Chapter 4 lays down the detail of the new proposed approach for verification and validation in systems engineering.

Chapter 5 illustrates the proposed techniques on state-chart diagrams in UML/SysML languages. Chapter 6 provides a case study while Chapter 7 contains some conclusions on this research together with a discussion of future work.

# Chapter 2

# Systems Engineering, Definition and Standards

System engineering is a discipline that develops and exploits structured, efficient approaches to analyze and solve complex engineering problems. It covers the entire life cycle of an engineering system in order to ensure that the customer's requirements are satisfied. Currently, systems engineers are using different documentation approaches to express the system requirements. They are also using many modeling techniques to give a complete design of a system. This diversity of techniques and approaches limits the communication and the exchange of information among system engineers. Thus, international standards are needed to produce an effective and synergic collaboration among system engineers. It will facilitate worldwide system engineering technologies compatibility and interoperability. Many organizations have been working on providing standard frameworks and modeling languages for system engineering. This section provides background information about some of these Standard Organizations such as Object Management Group (OMG), International Council On System Engineering (INCOSE) and the International Standard Organization (ISO). Also it will present some initiatives and modeling languages related to system engineering developed by these organizations.

# 2.1 Object Management Group

OMG [14] is an international association founded in 1989. OMG [14] provides standards for object-oriented applications to help reduce complexity, lower costs, and hasten the introduction of new software applications. The OMG [14] is accomplishing these goals through the introduction of a suite of specifications that will lead the industry towards interoperable, reusable, portable software components and data models. OMG [14] has established numerous widely used standards such as MDA and MOF to name a few significant ones related to system engineering. The following sections present these standards.

### 2.1.1 Model Driven Architecture

The Model-Driven Architecture (MDA) starts with the well-known idea of separating the specification of the operation of a system from the details of the way that system uses the capabilities of its platform. It is an approach to using models in software development, including the writing of specifications and the actual developing of applications, which allow the functionality and behavior of the system to be separated from implementation details. This enables the application to be easily ported from one environment to another by first creating one or more Platform Independent Models (PIM) that are later translated into one or more Platform Specific Models (PSM). MDA is being developed to include a broad range of concepts (such as the separation of the model from the implementation) so that it can be applied to all types of software development projects including electronic commerce, financial services, health care, aerospace and transportation. MDA provides an approach, and enables tools, to:

- Specify a system independent of the platform that supports it.

- Specify platforms.

- Choose a particular platform for the system.

• Transform the system specification into one for a particular platform.

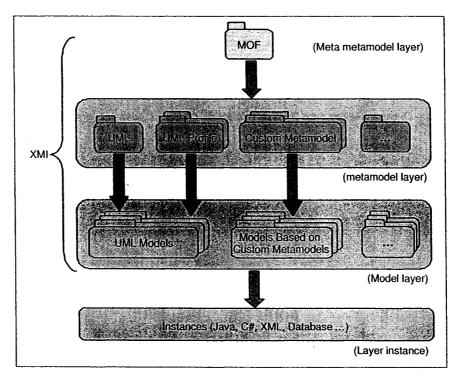

The three primary goals of MDA are portability, interoperability, and reusability through architectural separation of concerns. MDA is based on the four-layer [15] meta modeling architecture, and several OMG's complementary standards as shown in Figure 2.1. These standards are Meta-Object Facility (MOF), Unified Modeling Language (UML) and (XMI). The layers are (1) meta-meta model layer, (2) meta model layer, (3) model layer, and (4) instance layer.

Figure 2.1: MDA Layers

The main objective of having four layers with a common meta-meta model architecture is to support multiple meta models and models, and to enable their extensibility and integration.

### 2.1.2 Meta Object Facility

The Meta Object Facility (MOF) [13] defines an abstract language and framework for specifying, constructing and managing technology neutral meta models. The MOF specification is intended to provide information on modeling capability. It is the OMG's standard for defining modeling languages and their interoperability. In this context, the MOF Model is referred to as a meta-meta model because it is being used to define meta models such as UML. The MOF provides a formal and clear semantics for each element of the UML meta model.

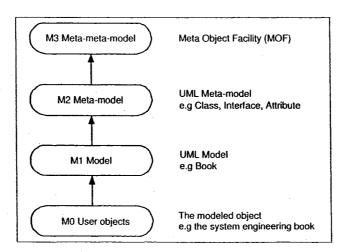

The UML and MOF are based on a conceptual layered meta model architecture, Figure 2.2, where elements in a given conceptual layer describe elements in the next layer down. For example:

- The MOF meta-meta model is the language used to define the UML meta model.

- The UML meta model is the language used to define UML models.

- A UML model is a language that defines aspects of a library system.

Figure 2.2: OMG 4-Layer Architecture

However, the UML modeling language was released before the MOF. Therefore, MOF and UML are very similar. Actually MOF is defined by a subset of the elements used in the UML core. In a nutshell, the four main modeling concepts are:

- Classes, which model MOF meta objects.

- Associations, which model binary relationships between meta objects.

- Data Types, which model other data (e.g., primitive types, external types, etc.).

- Packages, which modularize the models.

The MOF standard has also contributed to provide a solid foundation to the MDA architecture. The MOF formal meta models are used to define the concepts of Platform Independent Models (PIM) that can be mapped to Platform Specific Models (PSM). These two models are used to achieve the main goals of the MDA.

## 2.1.3 XML Metadata Interchange Format

The XML Metadata Interchange Format (XMI) [19] was proposed in response to an OMG Request For Proposal (RFP) on 1997-12-03 relating to a Stream-based Model Interchange. The RFP solicited proposals "for a transfer format specification for file export/import of models, and a transfer format specification for unique identification of the version of the MOF meta-meta model and any meta models referenced." Three initial submissions relative to the RFP were received, from: 1) Daimler-Benz Research and Technology and Recerca Informtica 2) Fujitsu/Softeam; and 3) a larger industry group led by DSTC, IBM, Oracle, Platinum Technology, and Unisys. The XMI proposal came as an initial submission from the third group. The first two submissions address the role of XML, but in neither case does XML constitute a central feature as in the XMI proposal.

In its initial proposal, the XMI specifies an open information interchange model that is intended to give developers working with object technology the ability to exchange programming data over the Internet in a standardized way, thus bringing consistency and compatibility to applications created in collaborative environments. By establishing an industry standard for storing and sharing object-programming information, development teams using various tools from multiple vendors can still collaborate on applications. The proposed standard will allow developers to leverage the web to exchange data between tools, applications, and repositories to create secure, distributed applications built in a team development environment. The XMI standard would combine the benefits of the web-based XML standard for defining, validating, and sharing document formats on the web with the benefits of the object-oriented Unified Modeling Language (UML). This is a specification of the OMG that provides application developers a common language for specifying, visualizing, constructing, and documenting distributed objects and business models. The main purpose of XMI is to enable easy interchange of meta data between modeling tools (based on the OMG UML) and between tools and meta data repositories (OMG MOF based) in distributed heterogeneous environments. XMI defines many of the important aspects involved in describing objects in XML:

- The representation of objects in terms of XML elements and attributes is the foundation of XMI.

- Since objects are typically interconnected, XMI includes standard mechanisms to link objects within the same file or across files.

- Object identity allows objects to be referenced from other objects with their IDs.

- The versioning of objects and their definitions is handled by XMI.

- XMI documents are validated using DTDs and Schemas.

Figure 2.3 illustrates an example of a XMI file.

```

<xsd:attribute name="position" type="xsd:string" use="optional"/>

<xsd:attribute name="addition" type="xsd:IDREFS" use="optional"/>

</xsd:extension>

</xsd:complexContent>

</xsd:complexType>

<xsd:element name="Add" type="Add"/>

<xsd:complexType name="Replace">

<xsd:complexContent>

<xsd:extension base="Difference">

<xsd:attribute name="position" type="xsd:string" use="optional"/>

<xsd:attribute name="replacement" type="xsd:IDREFS" use="optional"/>

</xsd:extension>

</xsd:complexContent>

</xsd:complexType>

<xsd:element name="Replace" type="Replace"/>

<xsd:complexType name="Delete">

<xsd:complexContent>

<xsd:extension base="Difference"/>

</xsd:complexContent>

</xsd:complexType>

<xsd:element name="Delete" type="Delete"/>

```

Figure 2.3: XMI File Example

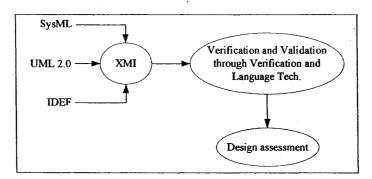

We have used XMI as an input for creating semantic models. Therefore, every modeling design in different platforms that can be exported to XMI can be converted to the semantic model, and verification and validation can then be performed on these models. Figure 2.4 shows an XMI example.

Figure 2.4: XMI Diagram

# 2.2 INternational Council on Systems Engineering

The INternational COuncil on Systems Engineering (INCOSE) [34] is an international professional society for systems engineers whose mission is to foster the definition, understanding, and practice of world class systems engineering in industry, academia, and government. INCOSE was formed in 1992 to develop, and enhance the interdisciplinary approach to enable the realization of successful systems. SysML initiative can be traced to a decision to pursue an extension of UML for systems engineering at the Model Driven Systems Design workgroup meeting at the International Council on Systems Engineering (INCOSE) in January 2001. This resulted in a collaborative effort between INCOSE and OMG.

The decision was made by the OMG to pursue UML for systems engineering. In March 2003, OMG issued a Request for Proposal (RFP) for a customized version of UML suitable for Systems Engineering. There was only one technology submission to the RFP, which was by the SysML group, proposing a Systems Modeling Language (SysML). The latter defines a general-purpose modeling language for systems engineering applications. It supports the specification, analysis, design, verification and validation of a broad range of complex systems that may include hardware, software, data, personnel, procedures, and facilities.

# 2.3 International Organization for Standardization

International Organization for Standardization (ISO) [35] is the world's largest developer of standards. Their standards are useful to industrial and business organizations of all types, to governments and other regulatory bodies, to conformity assessment professionals, to people in general in their roles as consumers and end users. ISO 10303 is one of the standards related to product data representation and exchange which is implemented by XML.

# 2.4 Unified Modeling Language

The Unified Modeling Language (UML) [37, 39] is a language that enables system developers to specify, visualize, and document models. These models are used to abstract the implementation details of software or systems. This abstraction enables developers to prepare the implementation of a system carefully before actually implementing it.

UML is the simplifying and the merging of three major notations. They are Grady Booch's methodology for describing a set of objects and their relationships, James Rumbaugh's Object-Modeling Technique (OMT), and Ivar Jacobson's approach, which includes a "use case" methodology. They were working to unify their methods at Rational Software and this work resulted in their first proposal in 1995.

OMG is a non-profit consortium that develops and maintains computer industry specifications. In 1996, they issued a request for proposal for a standard approach to object-oriented modeling. Booch, Rumbaugh, and Jacobson began working together with other developers and companies to create such a proposal for the OMG. In September 1997, they submitted their proposal, which was adopted unanimously two months later by the consortium. The OMG assumed responsibility for the maintenance of UML.

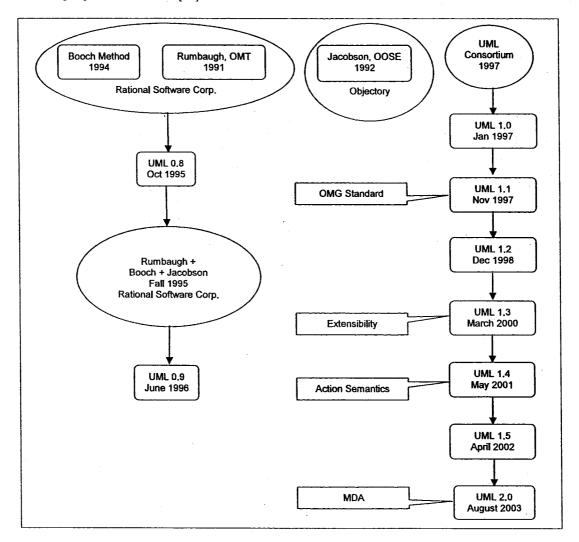

### 2.4.1 History

This section describes the history of the Unified Modeling Language. A summary of the history of UML is shown in Figure 2.5. Identifiable object-oriented modeling languages began to appear between the mid-1970s and the late 1980s. Their number increased from less than ten to more than fifty during the period between 1989 and 1994. However, none of these languages satisfied the oriented-object designers completely. The development of UML began in late 1994 when Grady Booch of Rational Software Corporation started his work on unifying the Booch and Object Modeling Technique (OMT) methods [23]. OMT, developed by Jim Rumbaugh, focused on the analysis of business and data intensive systems.

The Booch method, developed by Grady Booch, had particular strengths in design and implementation. These two methods were merged in the fall of 1995 and referred to the new language as the Unified Modeling Language version 0.8. At that time, Ivar Jacobson and his Objectory company joined Rational and this unification effort started by merging the Object-Oriented Software Engineering (OOSE) method with UML. OOSE is based around the use case concept that proved itself by achieving high levels of reuse by facilitating communication between projects and users [37].

Figure 2.5: History of UML

Grady Booch, Jim Rumbaugh, and Ivar Jacobson were motivated to create a unified modeling language for three reasons. First, these methods were already evolving towards each other independently. Second, they brought a mature modeling language and some stability to the object-oriented marketplace by unifying the semantics and notation. Third, they expected that their collaboration would yield improvements in all three earlier methods, helping them to capture lessons learned and to address problems that none of their methods previously handled well. Grady Booch, Jim Rumbaugh, and Ivar Jacobson established four goals:

- Enable the modeling of systems (and not just software) using object-oriented concepts.

- Establish an explicit coupling to conceptual as well as executable artifacts.

- Address the issues of scale that is inherent to complex and mission-critical systems.

- Create a modeling language usable by both humans and machines.

The result of this collaboration led to the release of the UML 0.9 and 0.91 documents in June and October 1996. As the UML designers observed that additional focused attention was still required, they invited and received feedback from the general community. They tried to achieve the broader goal of an industry standard modeling language. In early 1995, Ivar Jacobson and Richard Soley decided to push harder to achieve standardization in the methods marketplace. During 1996, a Request for Proposal (RFP) issued by the OMG provided the catalyst for some organizations to join forces around producing a joint RFP response. Rational established the UML Partners consortium with several organizations willing to dedicate resources to work toward a strong UML 1.0 definition. Those contributing most to the UML 1.0 definition included: Digital Equipment Corp., HP, i-Logix, IntelliCorp, IBM, ICON Computing, MCI Systemhouse, Microsoft, Oracle, Rational Software, TI, and Unisys. This collaboration was submitted to the OMG in January 1997 as an initial RFP response.

In January 1997, IBM, ObjecTime, Platinum Technology, Ptech, Taskon, Reich Technologies, and Softeam also submitted separate RFP responses to the OMG. These companies joined the UML partners to contribute their ideas. Together, the partners produced the revised UML 1.1 response. The focus of the UML 1.1 release was to improve the clarity of the UML 1.0 semantics and to incorporate contributions from the new partners. It was submitted to the OMG for their consideration and adopted in the fall of 1997 [37]. Then The standard has progressed through version 1.3 and on to version 1.4. The most recently adopted specification is version 1.4.1 in September 2002, which added Action Semantics. Although UML 1.x has enjoyed widespread acceptance, it has some shortcomings such as the lack of support for diagram interchange. Also, it is considered as being too complex and having an inadequate semantics definition. Finally, UML 1.x is not fully aligned with MOF. Thus, a major revision is required to address these problems [29]. For that reason, a formal RFP requirements has been issued that contains the following points:

- UML internals must have a more precise conceptual base for better MDA support.

- The user-level features must have new capabilities for large-scale software systems and consolidate the existing features.

- UML must support a constraint language.

- UML must have support for a standard for exchanging graphic information.

A new version of UML (UML 2.0) [29] has been specified to correct the shortcomings of UML 1.x.

### 2.4.2 Infrastructure and Superstructure

The UML infrastructure [15] refers to language's metamodel, which defines the semantics for how elements of a model get instantiated in another model. The core metamodel is used to define MOF [13], UML, Common Warehouse Metamodel (CWM) [12], and profiles. The

infrastructure is the top metamodel of the languages so they all derive from it. By deriving from the infrastructure, the languages are architecturally aligned. This permits the transfer of models from one to another. The infrastructure of UML is defined by the infrastructure library, which is a set of packages that satisfy the following requirements:

- It defines the core of a metalanguage that is to be reused to define a variety of metamodels, such as UML, MOF and CWM.

- It aligns the architectures of UML, MOF, and XMI so that model interchange is fully supported.

- It allows the customization of UML through profiles and the creation of new languages based on the same core as UML.

The infrastructure library is composed of the core package and the profiles package. The UML core package contains the complete metamodel particularly designed for high reusability. This allows other metamodels to benefit from the abstract syntax and semantics that have already been defined. Other metamodels at the same metalevel (e.g. UML) either import or specialize the specified metaclasses. The modeling languages UML, CWM, and MOF each depend on the common core. The idea is to allow UML and other MDA metamodels to reuse parts of the core package so that they can benefit from the abstract syntax and semantics that have already been defined.

To make the reuse easier, the core package is subdivided into four sub-packages:

- Primitive Types: Includes a few predefined primitive types (e.g. integer, boolean, and string) that are commonly used in metamodeling. They are designed specifically for UML and MOF. They define a small set of data types that are used to sepcify the core metamodel.

- Abstractions: Defines the common concepts (e.g. classifiers, behavioral elements, and generalizations) needed to build modeling elements and contains abstract metaclasses

that are intended to be further specialized or commonly reused by other metamodels. These metaclasses define the fundamental concepts that are common to most modeling languages.

- Basic package: Defines the common characterics of classifiers, classes, data types, and packages and refines the contents of the abstractions.

- Constructs: Contains concrete metaclasses (metaclasses that are not abstract) that lend themselves primarily to object-oriented modeling.

The UML metamodel is defined as one of the layers of a four-layer metamodeling architecture [15]. The first layer of the hierarchy is the meta-metamodeling layer. The purpose of this layer is to define the language for specifying a metamodel. It is more compact than the metamodel that it describes and can normally be reused to define several metamodels. The second layer is the metamodeling layer, which is an instance of the metamodel. This means that every element of the metamodel is an instance of an element in the meta-metamodel. The primary purpose of the metamodel layer is to define a language for specifying models. They are more elaborate than the meta-metamodels of the first layer. Examples of metamodels in that layer include UML and CWM. The third layer is the model layer, which is an instance of the metamodel layer. The primary purpose is to allow users to model a wide variety of different types of systems, such as software or engineering systems. The fourth layer contains the run times instances of the model elements defined above.

One of the goals of UML 2.0 was to standardize and align the language with MDA. Creating the infrastructure was part of this goal. By making the infrastructure the top metamodel, other languages would also derive from it making it possible to create a language structure that facilitates reuse. Finally, the UML superstructure [17] defines the user level constructs required for UML 2.0. It is used to extend and customize the UML infrastructure to define the UML metamodel. The elements that make up the modeling notations of UML are defined in the superstructure. These are designed by adding or extending elements

defined in the infrastructure.

### 2.4.3 Profiles

The profile in UML allows the customizing of UML for a specific domain. The profiles in UML are in a package that contains mechanisms, which allow metaclasses from existing metamodels to be extended to adapt them for different purposes.

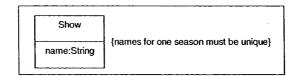

UML is defined using a metamodel, which is a model of a modeling language. The metamodel cannot be changed because it is too complicated. It would also be dangerous to modify the metamodel because that could make some of the UML applications, which rely on this metamodel, useless. Therefore, the profile is used to permit limited changes to the language. These changes do not affect the UML metamodel. UML includes three main extensibility mechanisms, constraints, stereotypes, and tagged values. Constraints are shown in Figure 2.6. They are textual statements expressed either in a formal language or in natural language. They are used to specify more details about components represented in the UML models. These details normally restrict how a component will be used. Constraints are normally written next to the UML element that is being restricted.

Figure 2.6: Example of a Constraint

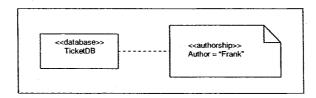

The stereotype in UML is essentially a metaclass, which is a class whose instances are classes. These are the classes that are used to create metamodels. They are used to represent a variation of an existing model element (e.g. a different use) with the same form but a different intent. In the UML models, stereotypes are shown in between the "<<>>" symbols. Stereotypes extend the semantics but not the structure of the metamodel classes. Tagged values are a named piece of information attached to a component in models created

in UML. They represent additional modeling information beyond that information defined in the metamodel. Tagged values along with stereotypes are shown in Figure 2.7.

These three constructs permit many kinds of extensions to the UML metamodel without imposing modifications on it. Together, the constraints, stereotypes, and tagged values are refrered to as the profile

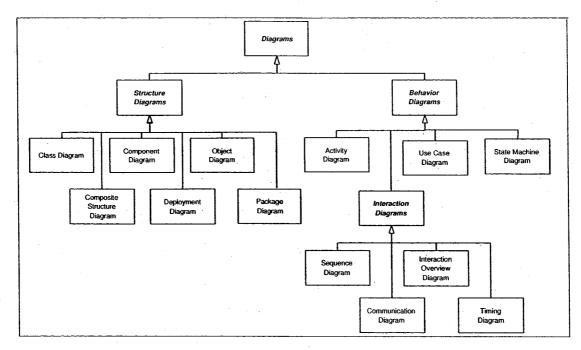

The classification of the UML 2.0 diagrams can be seen in Figure 2.8 that shows the taxonomy of the diagrams. The diagrams are divided into three categories, the structure diagrams, the behavior diagrams, and the interaction diagrams. The structure diagrams contain the class, component, composite structure, deployment, object, and package diagrams. The behavior diagrams contain the activity, use case, and state machine diagrams as well as all the interaction diagrams, which contain the communication, interaction overview, sequence, and timing diagrams.

There are a few changes in the UML 2.0 taxonomy compared with the previous versions. Some diagrams are new. They are the composite structure, the interaction overview, and the timing diagrams. Other diagrams have been modified from the previous versions. They are the activity, state machine, sequence, and communication diagrams.

Figure 2.7: Example of a Stereotype and a Tagged Value

The structural diagrams show the static features of a model. Static features include classes and associations, objects and links, and collaborations. These static features provide the skeleton in which the dynamic elements of the model are executed.

The behavioral diagrams show the interactions among resources modeled in the structural diagrams and how they execute their capabilities. The interaction diagrams are a subset of the behavior diagrams. They emphasize on the interactions between objects.

Figure 2.8: UML 2.0 Taxonomy

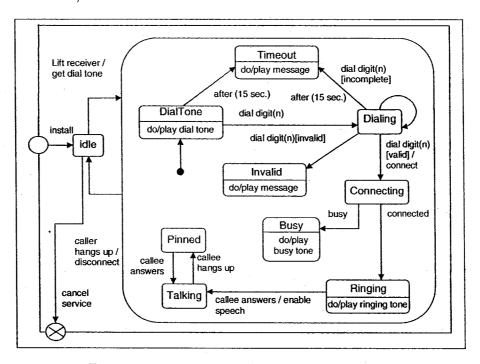

A state machine diagram shows the behavior of an entity. The state machines describe the significant states (conditions) that an entity can be in as a result of environmental stimuli or events that cause the entity to change. They describe the behavior of the entity and show the transitions between discrete states (conditions) the entity can exist in. Transitions can show the events that cause the changes. Guards determine if the state can change and the actions that occur. There may be a number of state machine diagrams that are needed to describe the entity and each diagram could focus on a different aspect of the entities' behavior. The purpose of the state machine diagram is to:

- Depict the various states that an object may be in.

- Show the transitions between the states of the objects.

The syntax and semantics of the state machine diagram contain a number of states. They also contain state transitions, which are events that cause objects to change into other states. A state machine diagram contains an initial state node and a final state node, which show the beginning and the end of the execution of the diagram.

Figure 2.9 shows an example of state machine diagram. The example shows a complex state machine representing a phone system. The state machine is the part inside the inner rectangle. The rest of the diagram is the rest of the system, which starts at the empty circle and ends at the circle with an X inside. Once the system enters the state machine, it starts its execution at the small filled black circle and executes all the operations of the machine by following the arrows. This is similar to the activity diagram but in this case, the execution has some constraints. For example, if, after playing the dial tone for 15 seconds, the system is still at that state, it will advance to the timeout state.

Figure 2.9: Example of a State Machine Diagram

# 2.5 System Modeling Language

The System Modeling Language (SysML) is a general-purpose system modeling language that supports the specification, analysis, design, verification, and validation of a broad range of complex systems. These systems may include hardware, software, data, personnel, procedures, and facilities.

At the moment, the SysML specification is not complete; Therefore, some elements in this section are not yet definitive.

SysML is a joint effort between the INCOSE and OMG. Companies that are involved in the partnership are: American Systems Corporation, ARTISAN Software Tools, BAE SYSTEMS, The Boeing Company, Ceira Technologies, Deere & Company, EADS Astrium GmbH, Eurostep Group AB, Gentleware AG, I-Logix, International Business Machines, International Council on Systems Engineering, Israel Aircraft Industries, Lockheed Martin Corporation, Motorola, National Aeronautics and Space Administration, National Institute of Standards and Technology, Northrop Grumman, oose de Dienstleistungen fur innovative Informatik GmbH, PivotPoint Technology Corporation, Popkin Software, Project Technology, Raytheon Company, Structured Software Systems Limited, Telelogic AB, THALES, and Vitech Corporation.

The goal of designing SysML is to satisfy basic requirements of the systems engineering community as defined in the UML for systems engineers RFP [18]. Some constructs and diagrams are added to this UML subset as necessary to address other systems engineer's requirements to make SysML easier to learn, implement, and apply. SysML reuses UML (Figure 2.10) when it is required and when it is practical in a manner that minimizes changes to the underlying language. Therefore it would be easy to implement SysML tools for vendors who already support UML.

SysML is aligned with the ISO AP233 data interchange standard to support interopertability among engineering tools. Since it is a customization from UML, it also inherits

the XMI interchange from its predecessor.

Figure 2.10: UML and SysML Compliance

### 2.5.1 History

Since 1997, UML has been widely used among the software engineering community. It is also being used in many other disciplines such as business processes and human resources. Many systems engineers use UML to model various kinds of systems such as real-time systems and hardware components. Some system engineers did not adopt UML and they decided to develop some alternatives to this modeling language. A common approach was to model additional systems engineering concepts in other modeling tools. This made it difficult to integrate the different viewpoints and achieve traceability. Therefore, OMG made the decision to pursue UML for systems engineering.

In March 2003, OMG issued a Request for Proposal (RFP) for a customized version of UML suitable for systems engineering [18]. The customization of UML for systems engineering is intended to support the modeling of a broad range of systems, which may include hardware, software, data, personnel, procedures, and facilities. There was only one technology submission to the RFP, which was made by the SysML group, proposing the Systems Modeling Language, SysML.

SysML reuses UML 2.0 diagrams to express system design models and some of the UML 2.0 diagrams were discarded such as the communication diagram and deployment diagram. Two new diagrams were also added. They are the parametric diagram and the requirement diagram. Figure 2.11 illustrates the complete SysML taxonomy of diagrams.

Figure 2.11: SysML Diagrams Taxonomy

#### 2.5.2 Diagrams

The SysML partners have introduced two new diagrams to make systems modeling easier and more efficient. These are the parametric diagram and the requirement diagram. Four diagrams were modified: activity, assembly, class, and state machine. There are also four diagrams that have not been modified from UML 2.0: Interaction overview, sequence, use case, and timing.

#### Parametric Diagram

The parameter is a measurable factor, such as temperature or pressure, that defines a system and determines its behavior and varies in an experiment. This is why the SysML partners plan on adding the parametric diagram to their standard.

The parametric diagram was added to SysML to bring more compliance with other system modeling tools. It can be used to do simulations on models by modifying some values and observing changes to the whole system. The parametric diagram can also be used to perform various types of analysis. Changing a value in a parametric diagram and observing the consequences on the whole system, can identify potential problems. It shows what conditions could make the system unreliable.

The motivation and purpose of the parametric diagram is that many systems engineering tools offer ways to express mathematical relations among properties but UML 2.0 does not offer any way to express these relations. The parametric diagram defines a set of quantifiable characteristics and relations between them. These relations state how any verification on a value of one property impacts the value of other properties. This modeling of relations among properties is extremely valuable for analysis purposes. The result of the analysis on this diagram can be included in a verification or validation process to help assess performances and reliability.

Parametric syntax can be used in a parametric diagram but it can also be used in other diagrams. Assembly diagrams can easily be enhanced with parametric relations. Parametric Diagrams rely on other mathematical languages, such as MathML, to express equations relating to different properties.

#### Requirement Diagram

The requirement is a feature, a property, or a behavior that a system has to provide. Listing requirements is the very first step in the process of designing a system. It allows the designer to state explicitly what is expected from the future system. Requirements are also useful

in the verification and validation phase of the development because it is possible to verify if the system that has been built fulfills the requirements that were specified.

This new diagram produces a way to depict requirements and to relate them to other specification, design, or verification models. The requirements can be represented in graphical, table, or tree format. Requirements can be expressed and stored in different ways. A very common way to keep track of requirements is the usage of requirement management tools. While these tools are very powerful and can store a lot of information, they are also harder to integrate with other model elements. This is the strength of the requirement diagram; it allows to easily understand relations between requirements and their environment.

# Chapter 3

# Verification, Validation and Accreditation in Systems Engineering

## 3.1 Introduction

This chapter describes verification and validation techniques which are used in the thesis. We have described the modeling languages that we will use and the properties that can be verified and validated on the systems modeled by these languages. Now, we describe the methods that we will use to perform the verification and validation of those properties on the models. There are three main types of techniques that we introduce in this chapter. They are formal verification, program analysis, and software engineering. Formal verification includes methods such as model-checking and theorem proving. Program analysis includes flow analysis, type-based analysis as well as abstract interpretation. The software engineering techniques enable the verification and validation of coupling, cohesion, and object oriented metrics.

#### 3.2 Formal Verification

Formal verification refers to the variety of scientific and engineering techniques for verifying and validating the correctness of systems. These techniques are often based on mathematical logic and can be used to perform verification and validation on a number of UML and SysML diagrams. For each technique that we discuss here, we describe what it is, how it operates, and we address the underlying advantages and disadvantages.

One of the goals of formal verification is to examine all the possible behaviors of a system to determine if it satisfies some properties or not. They can reveal inconsistencies, ambiguities, incompleteness as well as several other shortcomings in a system. Previous methods such as simulation and testing only permit the verification of some behaviors of systems. Those behaviors that have been tested or simulated may satisfy a property but those that have not been simulated and tested may not. Formal verification allows to verify properties by exhaustively checking all of the system states.

In this section, we concentrate on two formal verification techniques: Model-checking and theorem proving. Model-checking stands for the verification of a model by brute force enumeration. The model is usually expressed as a directed graph. Each node in the graph represents a state of the system and contains a set of properties. Model-checking verifies that each state of the graph satisfies the properties associated with the state. Theorem proving is a technique where both the system and its desired properties are expressed as formulas in a mathematical logic. This logic is given in a formal system, which defines a set of axioms and a set of inference rules. Theorem proving is the process of deriving a proof of a property from the axioms of the system. Proving properties is done in a series of derivations that involve instantiations of axioms and inference rules.

#### Model-checking

Model-checking [38] is a method for formally verifying finite-state (and sometimes even infinite-state) systems. Given a system model and some desired system properties,

model-checking explores all the states of the model to check whether the given system properties are satisfied by the model. Model-checking either proves that the properties are satisfied or generates counter examples that show that those properties are not satisfied.

The advantages of model-checking include automation and the generation of counter examples for those properties that are not satisfied. Automation means that performing model-checking is something that can be done automatically. Accordingly, the inner workings of the model-checking procedures are transparent to the system verified. Another advantage is that if the model-checking finds that a property is not satisfied then it can generate a counter example to show how and where the problem occurs. This might be of a great help to analyze the system design to meet the desired property in question.

The main disadvantage of model-checking is the state explosion problem. Since model-checking explores all the possible behaviors of the system, there can be many states to explore. If the number of possibilities become too large, model-checking might take too long to perform the verification. Many techniques have been developed to help alleviate the temporal and spatial needs of verification.

Figure 3.1: Formal Verification by Model-Checking

As shown in Figure 3.1, model-checking takes as input a model together with a set

of properties to be verified. Model-checking will produce as output two sets: the set of satisfied properties and the set of unsatisfied properties with counter examples. With the counter examples, it is possible to fix the model and then re-run again the model-checking procedure.

#### • Theorem proving

Theorem proving [27] is a method for performing verification on formal specifications of system models. To use theorem proving, one applies a set of rules of inference to a specification in order to derive new properties of interest. Tools used for theorem proving consist of a collection of inference steps that can be used to reduce a proof's goal to simpler subgoals that can be discharged automatically by the primitive proofs of the tool. For theorem proving, a property and a model are used. The goal is to verify the given property. The theorem prover is either able to verify the property by completing the proof or find subgoals that give scenarios in which the property is violated. Theorem proving usually requires considerable technical expertise and understanding of the specification. It gives developers a lot of flexibility and control in doing the proof. An advantage of theorem proving is that it is not limited by the size of the model. Large systems that cannot be verified using model-checking, can still be verified by theorem proving since state space explosion is not anymore an issue. A disadvantage of theorem proving is that if one fails to complete the proof of a property, it does not mean that the property cannot be proved. It may just mean that the prover is not provided with enough information to complete the proof.

Theorem proving works by using the proof inference technique. A developer validates the design of a system by proving a conjecture that describes how the system should work by using axioms that describe the system itself. As shown in Figure 3.2, the properties that the developed system must have are converted into a logical representation. The system (or the model of the system) is also converted into that particular

Figure 3.2: Theorem Proving Formal Verification

form. The results of the converted system are then used to show that the properties that the system must have are true or false. If the prover shows that the properties are true then the system has been validated.

## 3.3 Program Analysis

Program analysis [10] is the usage of automated techniques to explore program properties. Statically by analyzing a program, its behavior can be predicted without having to execute it. It allows the optimization of compilation, security analysis, and automated verification. There are different techniques for program analysis such as control flow analysis and data flow analysis. Control flow analysis aims at tracking the flow of execution within a given program. Control flow analysis is done by identifying "basic blocks" in the program execution. With these blocks, we can compute the execution flow and analyze it. Control flow analysis could be applied for verification and validation of behavioral design models to find portions of the system that are never used or that are repetitive. Data-flow analysis is a technique of automatically gathering information about the values calculated in a procedural computer program by applying rules to its control flow graph. The information gathered is often useful in optimizing the program. A simple way to perform data flow analysis of programs is to set up data flow equations for each node of the control flow graph and solve them by repeatedly calculating the output from the input locally at each node until the whole system stabilizes.

Data flow analysis techniques can be applied to behavioral diagrams to examine the use of resources. If some resource is declared in a structural diagram but never used in a behavioral diagram, this can denote as a problem.

## 3.4 Software Engineering Techniques

When designing a software system, different software engineering techniques play a big role in the process. A good software system offers components that are more robust, more maintainable, and more reusable. These components should be highly cohesive and loosely coupled. Different software metrics were developed to measure object oriented concepts [2] such as inheritance and encapsulation. In the following, we will cover coupling and cohesion. After that, we will talk about a metrics suite for object oriented systems.

• Coupling [8] is a measure of the interdependence among modules. Highly coupled modules interact in ways that make their separate modification difficult. Module coupling decreases the reusability of the coupled objects. It increases the chances of system corruption when changes are made to one or more of the coupled objects. Undesirable high levels of coupling occur when abstractions are poor and encapsulation inadequate. Good systems tend to have a low degree of coupling among objects. The minimum degree of coupling is obtained by making modules as independent as possible.

Six levels of coupling were defined to measure the interdependence among the system modules. These levels were ordered according to their effects on system understandability, maintainability and reusability of the coupled modules. High level of coupling is considered when two modules are coupled in more than one way. No coupling occurs when modules are not dependent on others; this level of coupling is highly preferable. In the following we define the different levels of coupling from best to worst as follows:

- Independent Coupling: No coupling exists between modules.

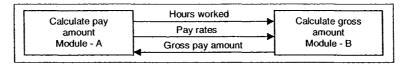

Data Coupling: Two modules are data coupled if they pass data through scalar or array parameters. This type of coupling is depicted in Figure 3.3.

Figure 3.3: Data Coupling

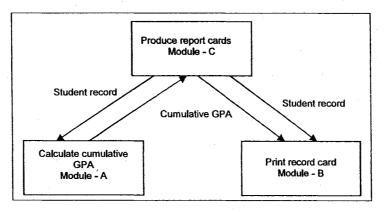

- Stamp Coupling: Two modules are stamp coupled if they pass data through a parameter that is a record. Stamp coupling is perceived as worse than data coupling because any change to the record will affect all of the modules that refer to that record, even those modules that do not refer to the fields that are changed. Two modules are stamp coupled if they communicate via a passed data structure, which contains more information than necessary for the modules to perform their functions. Stamp coupling is illustrated in Figure 3.4.

Figure 3.4: Stamp Coupling

Here we assume the "student record" contains a name, address, SIN, and information in addition to academic performance information.

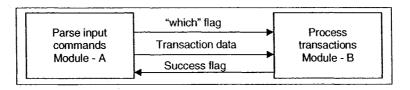

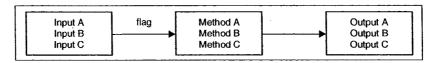

- Control Coupling: Two modules are control coupled if one passes a flag value that is used to control the internal logic of the other. Control coupling is shown in Figure 3.5.

Figure 3.5: Control Coupling

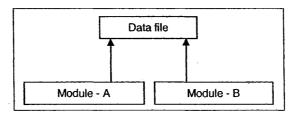

External Coupling: Two modules are externally coupled if they communicate through an external medium such as a file. Figure 3.6 shows external coupling.

Figure 3.6: External Coupling

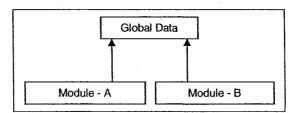

Common Coupling: Two modules are common coupled if they refer to the same global data. Figure 3.7 shows common coupling.

Figure 3.7: Common Coupling

- Content Coupling: Two modules are content coupled if they access and change

each other's internal data state or procedural state. This type of coupling is

considered the worst and is avoided in design.

- Cohesion [8] is a measure of the degree of how well the elements of an object work to

achieve the same purpose. It measures how well-defined the purpose of an object is,

and whether each part of the object contributes directly to achieve that purpose. High

cohesion means that an object has one well-defined purpose and every element in the object contributes directly to that purpose. On the contrary, low cohesion means that either the purpose is obscure or some of the elements do not contribute to the purpose. Low cohesion can occur due to the two mentioned reasons.

A module may exhibit any of seven levels of cohesion depending on how the activities within the module are related. Functional cohesion is the most desirable type of cohesion. Coincidental cohesion is the worst type and is always avoided. In the following, the seven types of cohesion are ordered from best to worst.

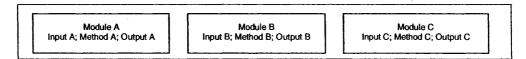

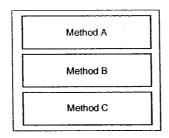

- Functional Cohesion: A functionally cohesive module contains elements that all contribute to the execution of one and only one problem-related task. A module is functionally cohesive if it can be described as a single coherent function. The goal of design is to achieve this type of cohesion. Modules of this type will be reusable. Figure 3.8 shows that each module has only one method.

Figure 3.8: Functional Cohesion

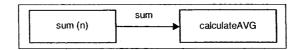

- Sequential Cohesion: A sequentially cohesive module is one whose elements are involved in activities such that output data from one activity serves as input data to the next activity. A sequentially cohesive module is easily maintained. Indeed, it is almost as maintainable as a functionally cohesive module. The only real disadvantage of a sequentially cohesive module is that it is not so readily reusable in the same system, or in other systems, as is a functionally cohesive module. The reason is that it contains activities that will not in general be useful together. Sequential cohesion is shown in Figure 3.9.

- Communicational Cohesion: A communicational cohesive module is one whose

Figure 3.9: Sequential Cohesion

elements contribute to activities that use the same input or output data. Communicational cohesion occurs when a module performs operations related to a sequence of steps performed in the program. All the actions performed by the module are performed on the same data. Communicational cohesion is an improvement on procedural cohesion because all the operations are performed on the same data. Figure 3.10 shows communicational cohesion.

Figure 3.10: Communicational Cohesion

- Procedural Cohesion: As shown in Figure 3.11, a procedurally cohesive module is one whose elements are involved in different and possibly unrelated activities in which control flows from each activity to the next without sharing any data. As in sequential cohesion, tasks occur in sequence but they do not share data. Procedurally cohesive modules seem quite natural in their context. However, taken in isolation, they are extremely difficult to understand and seem incoherent. In order to understand such a module, the software engineer must know something about the program from which the module was taken. Such modules are rarely reusable.

- Temporal Cohesion: A temporally cohesive module is one whose elements are involved in activities that are related in time. A temporally cohesive module is

Figure 3.11: Procedural Cohesion

one which performs several sequential functions, which have a weak relationship (or no relationship) to one another but all of which must be performed in a short period of time.

An example of a temporally cohesive object is an "Initialization" object. Temporal cohesion can be removed by insuring that each function within the temporally cohesive object is reassigned to the proper object.

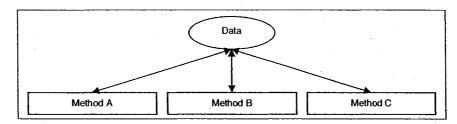

- Logical Cohesion: A logically cohesive module is one whose elements contribute to activities of the same general category in which the activity or activities to be executed are selected from outside the module by a flag for example. Figure 3.12 shows an example of logical cohesion.

Figure 3.12: Logical Cohesion

- Coincidental Cohesion: A module is said to exhibit coincidental cohesion if there is little or no constructive relationship among the elements of the module. This could also be called a random module. It occurs when modules are not partitioned to represent a single abstraction, but are partitioned for some reason such as the number of lines of code. Coincidental cohesion can also show up in modules that do not represent a single, object oriented concept such as a math object. In

a multiple inheritance scheme, a "class" has been defined that only represents a collection of commonly occurring code rather than a single object oriented concept. There is no simple way to remove a coincidently cohesive module from a system. Some redesign has to be performed.

• Object oriented metrics can be used to measure the quality of the product before it is produced. This is important since the cost of reducing the risk of a flaw within a program before it is developed is much lower than the cost of fixing a returned product. Different metrics [36] suites were developed in the software engineering discipline. Metrics measure software qualities such as reusability and maintainability. Many of these metrics are proposed in 1994 by Chidamber and Kemerer [3]. This metric suite consists of six metrics that are crucial for object oriented development. The six metrics of this suite are:

- Weighted Methods per Class (WMC)

- Response For a Class (RFC)

- Lack of Cohesion of Methods (LCOM)

- Coupling Between Object Classes (CBO)

- Depth of Inheritance Tree (DIT)

- Number of Children (NOC)

## 3.5 Projects on Verification and Validation

In this section, we give the state of art on the work being done on design verification and validation of systems engineering models. For this purpose, we go through some examples of research efforts being conducted on design verification and validation. For each work, we will give its main objective, the used methods and the targeted diagrams of the modeling language.

The increasing demand on having well designed systems emphasizes the interest on design verification and validation methods and tools. Applying verification and validation from the design phase of a system could help detecting and resolving problems earlier. This significantly reduces the subsequent cost of design, development, and testing. These systems could be designed using different modeling languages such as UML and SysML. Although verification and validation is an essential task, we still observe a lack of application of verification and validation on systems engineering.

It is worthy to say that, as much as we are aware, most of the projects on design verification and validation target only software engineering models and do not address systems engineering ones. On the other hand, the majority of these efforts addresses only UML [28] designed software systems and they do not cover all of the diagrams of this modeling language. Moreover, the projects that we reviewed are using formal verification and validation techniques such as model checking [31] and theorem proving [40]. None of these efforts tried to apply program analysis [20] (e.g. inter-procedural analysis) and software engineering (e.g. the use of cohesion and coupling algorithms) techniques. Finally, previous work does not provide precise feedback after verification and analysis; design assessments are generally ad hoc and do not present any analytical results to detail the problems of the design.

Several research institutions and industries are working on methods and tools for verification and validation of design models. Herein, we will briefly describe some of these projects.

#### 3.5.1 Validation and Verification of Object Technology

This project, Validation and Verification of Object Technology [44], is being developed by the Information Security and Object Technology (ISOT) Research Group at the University of Victoria. It started in November 2001 and aims to use UML as a graphical Object-Oriented notation and the Prototype Verification System-Specification Language (PVS-SL) [25], a specification language integrated with support tools and theorem prover, as a formal

notation.

The main objective of the VVOT project is to define a framework and associated tools for the development of object-oriented software systems using formal methods. The VVOT project is divided into a mainstream project and a number of derived sub projects designated for specific aspects of object technology. The main project formalizes a subset of UML models such as state-chart diagram.

The resulting formal model works as an input for the sub projects for specific activities, applications, or architectures including security, testing, verification, and validation.