#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# Modeling and Formal Verification of a Telecom System Block Using MDGs

Md Hasan Zobair

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montréal, Québec, Canada

April 2001

© Hasan Zobair, 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-59312-6

#### **Abstract**

# Modeling and Formal Verification of a Telecom System Block Using MDGs

#### Md Hasan Zobair

Simulation-based verification cannot uncover all errors in an implementation because only a small fraction of all possible cases can be considered. Formal verification is a different technique that can alleviate this problem. Because the correctness of a formally verified design implicitly involves all cases regardless of the input values.

This thesis demonstrates the effectiveness of Multiway Decision Graphs (MDG) to carry out the formal verification of an industrial Telecom hardware which is commercialized by PMC-Sierra Inc. To handle the complexity of the design, we adopted a hierarchical proof methodology as well as a number of model abstraction and reduction techniques. Based on the hierarchy of the design, we followed a hierarchical approach for the equivalence checking of the TSB. We first verified that the RTL implementation of each module complies with the specification of its behavioral model. We also succeeded to verify the full RTL implementation of the TSB against its top level specification. Besides equivalence checking, we furthermore applied model checking to ascertain that both the specification and the implementation of the TSB satisfy some specific characteristics of the system. To measure the performance of the MDG verification, we also conducted the verification of the same TSB with Cadence FormalCheck. The experimental results show that in some cases, the MDG based modeling with abstract state variables allows more efficient verification than that of the boolean modeling in FormalCheck.

## Acknowledgments

The contributions of others to the completion of this thesis have been substantial and varied. I will here acknowledge those whose names most immediately comes to mind and apologize those names I have omitted inadvertently.

I would like to express my indebtness to my supervisor Dr. Sofiène Tahar. His guidance, assistance and encouragement were an asset during the thesis work in particular and in my stay at Concordia, in general. Professor Tahar also read and criticized many versions of this thesis. The final version owes much to him, the mistakes are my own.

I would like to thank Mr. Jean Lamarche, Manager, PMC-Sierra Inc. for providing the RASE telecom system block design as a research case study. Without his cooperation this research work would not be possible. In particular, for his valuable time to explain us the functionalities of the design.

I would like to thank the examination committee members, Dr. A. Al-Khalili, Dr. P. Sinha, Dr. O. Ait-Mohamed for serving in my thesis defence. Their comments and feedback were of great value in improving earlier versions of this thesis.

To all my friends and colleagues in the Hardware Verification Group (HVG) at Concordia, thank you for your encouragement, thoughtful discussions, and help. I wish to express my sincere and heartfelt thanks to my friends Syed Asif Iqbal and Mohammed Wahidul Islam who have helped me to proofread my thesis drafts many times.

Last but not least I would like to thank my wife, my parents and the rest of my family members in Bangladesh for their constant moral support and encouragement which were invaluable in completing this thesis.

## **Table of Contents**

| List o | f Figures                                                     | vii |

|--------|---------------------------------------------------------------|-----|

| List o | f Tables                                                      | ix  |

| List o | f Acronyms                                                    | X   |

| Chap   | ter 1 Introduction                                            | 1   |

| 1.1    | Motivation and Goal                                           | 1   |

| 1.2    | Background and Related Work                                   | 2   |

|        | 1.2.1 Formal Verification                                     |     |

|        | 1.2.2 Formal Verification Techniques                          | 5   |

|        | 1.2.3 Related Work                                            | 9   |

| 1.3    | Scope of the Thesis                                           | 13  |

| Chapt  | ter 2 Multiway Decision Graphs                                | 16  |

| 2.1    | Multiway Decision Graphs                                      | 16  |

|        | Hardware Modeling with MDGs                                   |     |

| 2.3    | MDG-based Verification Techniques                             | 20  |

| Chapt  | ter 3 Modeling and Verification Methodology                   | 25  |

| 3.1    | Hierarchical Proof Methodology                                | 24  |

| 3.2    | Abstraction and Reduction Techniques                          | 28  |

|        | 3.2.1 Behavioral Abstraction                                  | 29  |

|        | 3.2.2 Structural Abstraction                                  |     |

|        | 3.2.3 Data Abstraction                                        |     |

|        | 3.2.4 Temporal Abstraction                                    |     |

|        | 3.2.5 Model Reduction                                         | 34  |

| Chapt  | ter 4 Modeling and Formal Verification of a TSB: A Case Study | 37  |

|        | The RASE Telecom System Block                                 |     |

| 4.2    | Behavioral Modeling of the TSB                                |     |

|        | 4.2.1 Transport Overhead Extraction Module                    | 40  |

|        | 4.2.2 Automatic Protection Switch Control Module              |     |

|        | 4.2.3 Synchronization Status Filtering Module                 |     |

|        | 4.2.4 Interrupt Server                                        |     |

|        | 4.2.5 Bit Error Rate Monitoring (BERM) Module                 |     |

| 4.3    |                                                               |     |

| 4.4    | Hierarchical Verification of the RASE TSB                     |     |

|        | 4.4.1 Equivalence Checking                                    |     |

|        | 4.4.2 Validation by Property Checking                         |     |

|        | 4.4.3 Comparison between FormalCheck and MDG tools            | 67  |

| Chapter 5    | Conclusion and Future Work            | 75 |

|--------------|---------------------------------------|----|

| Bibliography | ,                                     | 78 |

| Appendix A   | Properties of the RASE in MDG         | 86 |

| Appendix B   | Properties of the RASE in FormalCheck | 91 |

|              |                                       |    |

## **List of Figures**

| Figure 1.1:  | Flow of hierarchical design and verification                | 3  |

|--------------|-------------------------------------------------------------|----|

| Figure 2.1:  | The MDG for an OR gate                                      | 14 |

| Figure 2.2:  | The MDG for a comparator                                    | 15 |

| Figure 2.3:  | The MDG for an ASM                                          | 15 |

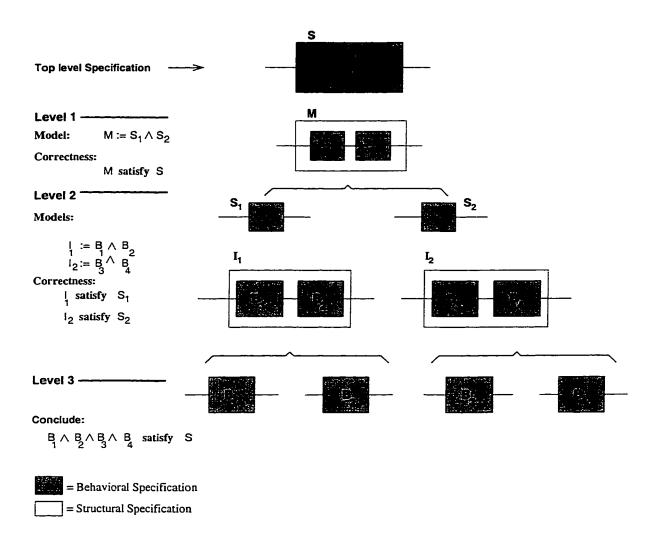

| Figure 3.1:  | An example of hierarchical proof                            | 25 |

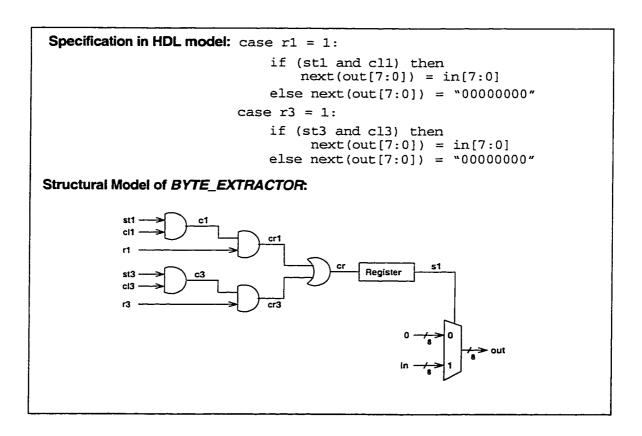

| Figure 3.2:  | An example of structural abstraction                        | 26 |

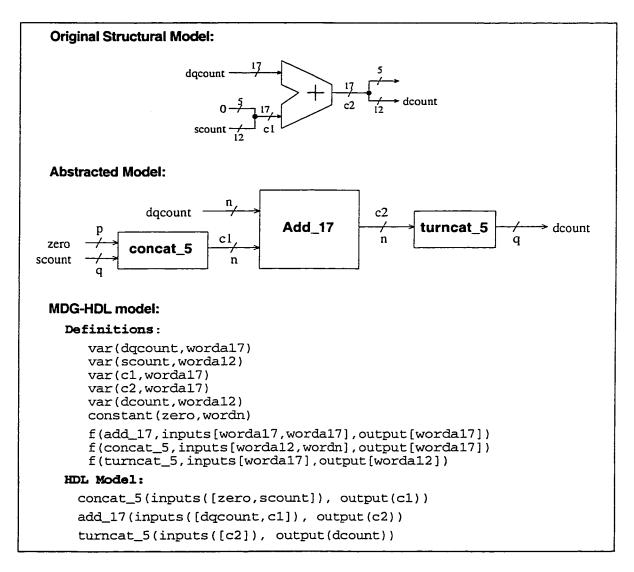

| Figure 3.3:  | An example of data abstraction                              | 26 |

| Figure 4.1:  | The STS-1 SONET frame structure                             | 35 |

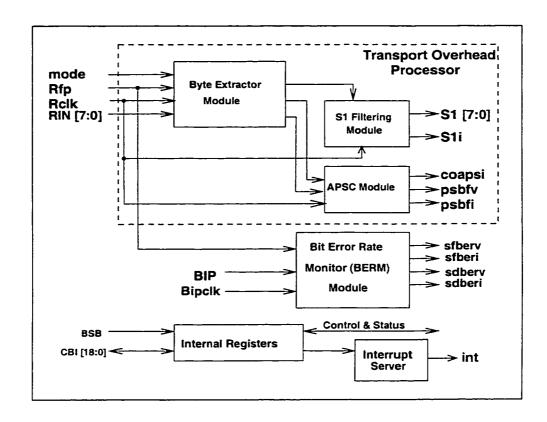

| Figure 4.2:  | The RASE telecom system block                               | 37 |

| Figure 4.3:  | The hierarchy tree of the TSB                               | 38 |

| Figure 4.4:  | The column counting ASM                                     | 43 |

| Figure 4.5:  | The row counting ASM                                        | 45 |

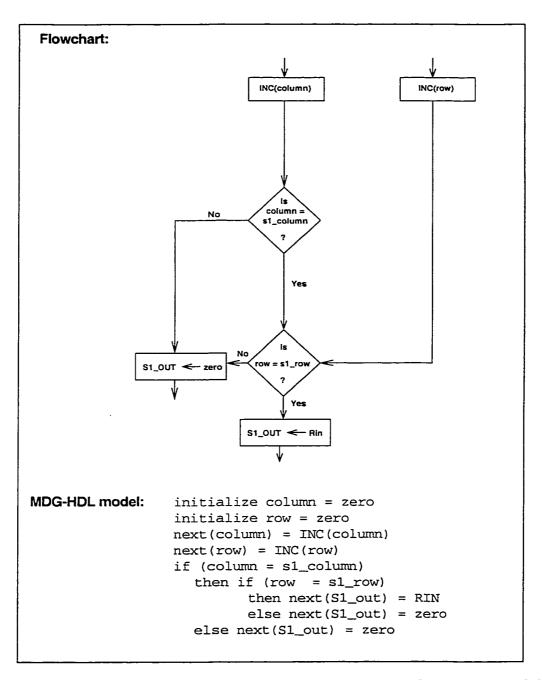

| Figure 4.6:  | Flowchart specification of byte extractor and its MDG model | 47 |

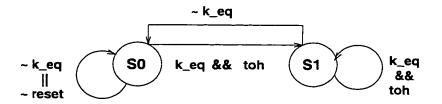

| Figure 4.7:  | Filtering ASM for K1 and K2 bytes                           | 47 |

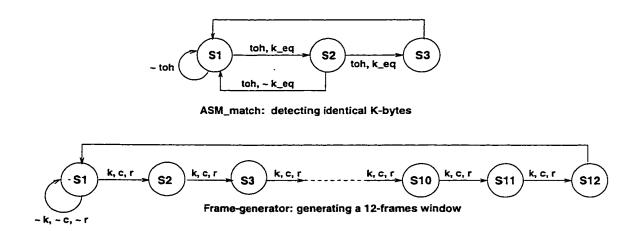

| Figure 4.8:  | Set of ASMs to declare the APS failure alarm                | 47 |

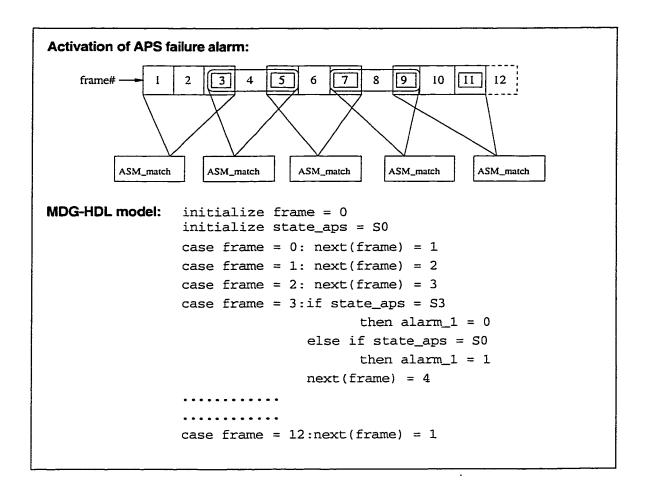

| Figure 4.9:  | Example to model APS failure alarm                          | 47 |

| Figure 4.10: | Abstract state machine to filter the S1 bytes               | 47 |

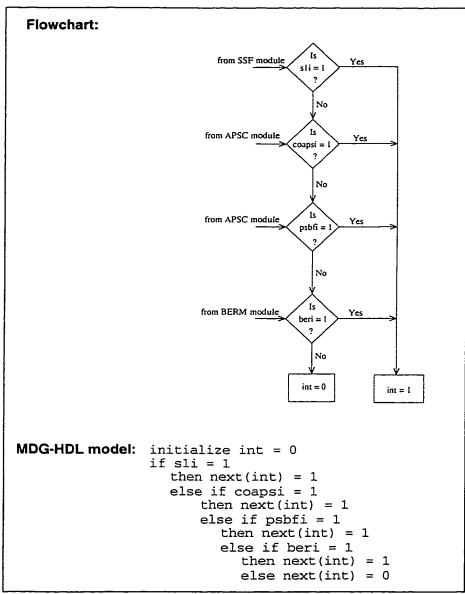

| Figure 4.11: | Flowchart specification of int. server and its MDG model    | 47 |

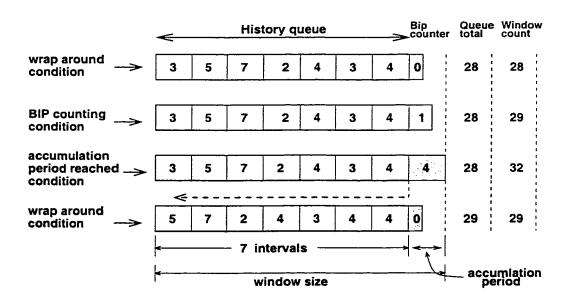

| Figure 4.12: | BERM sliding window algorithm                               | 47 |

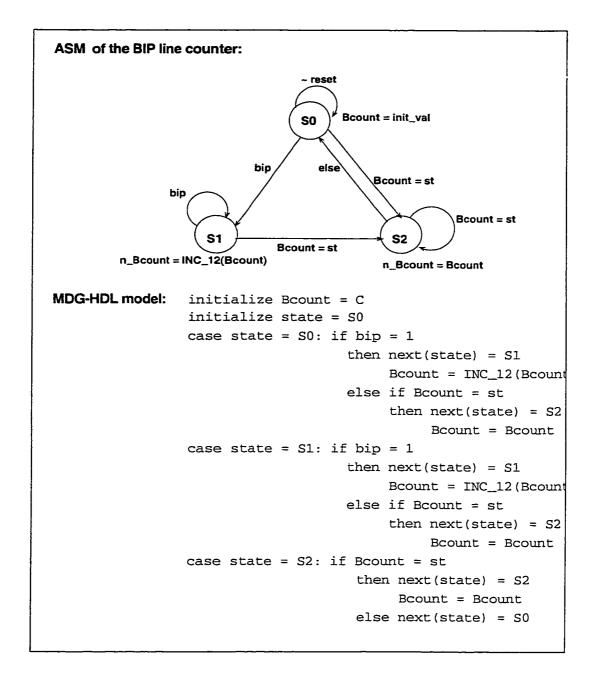

| Figure 4.13: | An ASM to count the BIP line and its MDG-HDL model          | 47 |

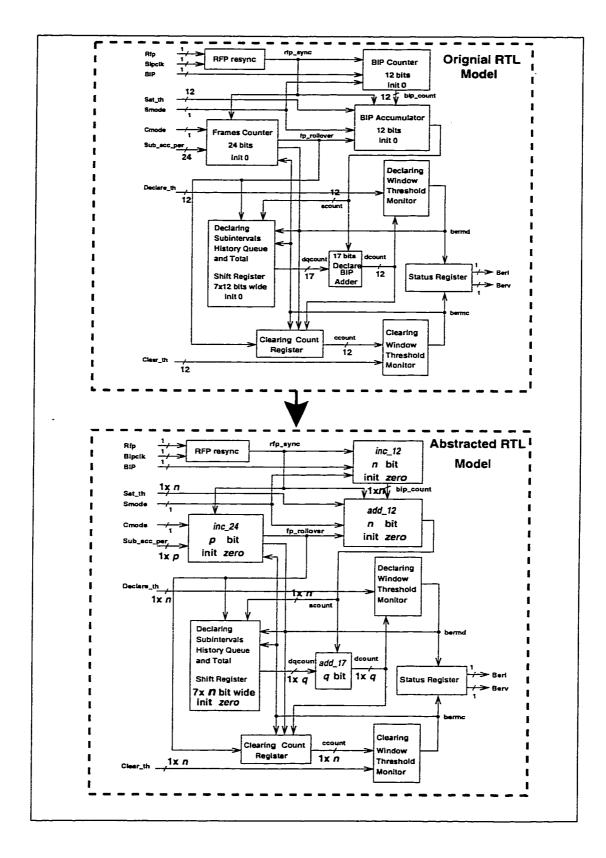

| Figure 4.14: | Module abstraction of the BERM block                        | 47 |

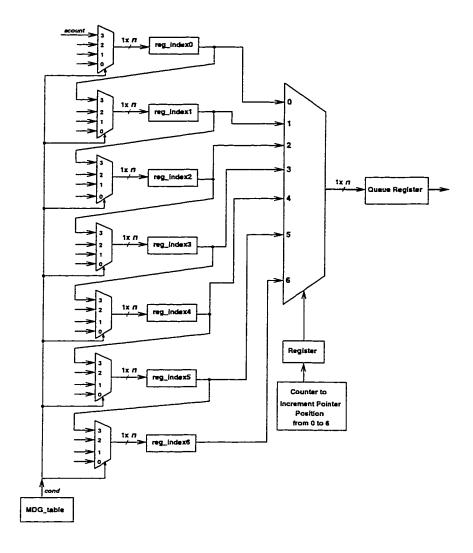

| Figure 4.15: | The implementation of a multi-dimensional array             | 47 |

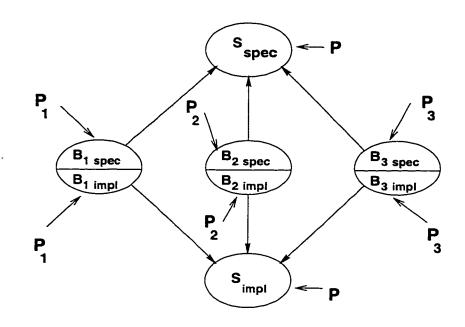

| Figure 4.16: | Hierarchical proof methodology                              | 47 |

## **List of Tables**

| Table 4.1: Experimental results for equivalence checking                                | 58 |

|-----------------------------------------------------------------------------------------|----|

| Table 4.2: Properties and their corresponding modules of RASE TSB                       | 60 |

| Table 4.3: Experimental results of property checking on the specification               | 64 |

| Table 4.4: Experimental results of property checking on the implementation              | 65 |

| Table 4.5: Property checking on the top level implementation using FormalCheck and MDGs | 69 |

## **List of Acronyms**

- ACTL: Abstract Computational Tree Logic

- ATM: Asynchronous Transfer Mode

- APSC: Automatic Protection Switching Control

- BDD: Binary Decision Diagram

- ROBDD: Reduced Ordered BDD

- EOBDD: Extended Ordered BDD

- BMD: Binary Moment Diagram

- HDD: Hybrid Decision Diagram

- MTBDD: Multi Terminal BDD

- MDG: Multiway Decision Graph

- CTL: Computational Tree Logic

- TSB: Telecom System Block

- RASE: Receive Automatic Protection Switch Control, Synchronization Status Extraction and Bit Error Rate Monitor, a commercial product of PMC-Sierra Inc.

- SONET: Synchronous Transport Optical Network

- SSF: Synchronization Status Filtering, S1 byte filtering of SONET frame

- BER: Bit Error Rate

- BIP: Bit Interleaved Parity

- BERM: Bit Error Rate Monitoring on B2 bytes of a SONET frame

- SPE: Synchronous Payload Envelope of a SONET frame

- STS-1: Synchronous Transport Signal, basic electrical signal of a SONET frame.

- STS-3: Synchronous Transport Signal, multiplexed from STS-1 signal

- TOH: Transport Overhead section of a SONET frame

- SOH: Section Overhead

- LOH: Line Overhead

- POH: Path Overhead

- UTOPIA: Universal Test and Operations PHY Interface for ATM

- TMRS: Transmit Master/Receive Slave, a commercial product of PMC-Sierra Inc.

- RTL: Register Transfer Level

- RIN: Receive Input data stream

- FSM: Finite State Machine

- PHY: Physical Layer

- VIS: Verification Interacting with Synthesis

- SMV: Symbolic Model Verifier

## Chapter 1

### Introduction

#### 1.1 Motivation

Design errors in digital designs are destructive. The devices are manufactured in vast quantities and errors cannot be remedied in the field by patching. Recently discovered errors in several industrial designs demonstrate that these concerns are not academic. In addition to economic considerations, the degree of design correctness is necessary to the use of digital systems in critical applications. As IC chips grew from tens of thousands of gates in the eighties to more than 10 millions today, designers and verifiers of these massive new circuits face a pair of conflicting goals. They must find ways to contain the expansion of verification time, effort, and cost. They also must increase verification coverage and quality to ensure single-pass success [34].

Simulation-based method is currently used by the industrial community for system-level verification, since it can handle the entire design at a time. When a simulation trace exposes a design error, a verifier analyzes the trace and rectifies the design. However, the rectification might be inadequate because the trace shows only one specific behavior of the system and one cannot confirm that no other trace exposes the error. This handicap is the motivation for the need of new methods to achieve economical and reliable verification of

digital systems. Formal verification technique had paved a path, showing the utility of finding bugs early in the design cycle. It now affords some promising new methods for the validation of digital designs. Some automatic formal verification techniques are gradually finding their place in the verification process as complement to logic simulation. FSM-based automatic verification techniques have proven to be successful formal verification technique that can be applied to real industrial design. However, since it requires the design to be described at the boolean level, they often fail to verify a large-scale design because of the *state space explosion* problem caused by the large datapath. On the other hand while scalable to large designs, theorem proving based interactive verification techniques require a great expertise by the verifier.

Thus, the motivation behind this work was to investigate Multiway Decision Graphs (MDGs) in verifying a large-scale industrial design, and proposes a hierarchical approach for organizing the verification of the investigated design using MDGs. We also provide a comparative evaluation of the experimental results from the model checking of the proposed design using Cadence FromalCheck and the MDG tools.

#### 1.2 Background and Related Work

A cornerstone of many of the Asic CAD suites is the ability to design hierarchically. Complex designs need a mechanism to reduce their complexity for both the designer and verifier. It is difficult to understand a design with hundreds of components; it is easier to understand the same design with only a few components. Using hierarchies to handle complexities is an old methods. It does not mean that the design becomes less complex (sometimes it becomes more complex instead), but it becomes easier to understand for both the designer and verifier. To accelerate the design flow and assure the correctness of

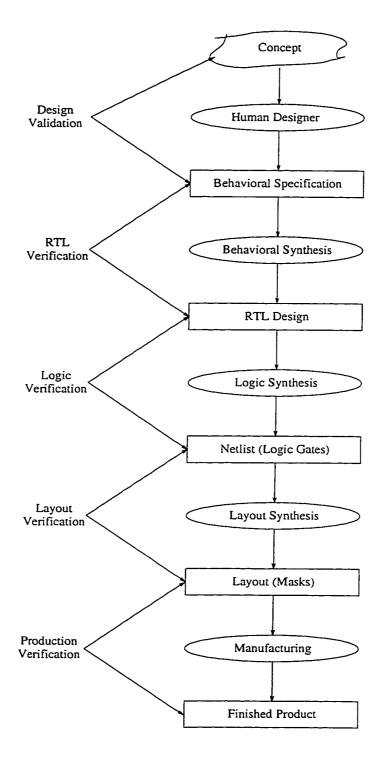

complex digital systems, a hierarchical design approach is usually adopted by the industrial community (see Figure 1.1) [29].

Figure 1.1: Flow of hierarchical design and verification

The system architect first manually derives the requirements of the system as the system behavioral specification. This specification is then refined manually or using CAD tools (e.g., Synopsys) into more detailed descriptions such as register-transfer (RT), logic and mask level descriptions. As the late detection of design errors is largely responsible for unexpected delays in realizing the hardware design, it is extremely important to ensure correctness in each design step. With correct-by-construction design style, automatic tools, such as behavioral and logic synthesis techniques can be used to ensure behavioral and gate level design correctness. However, the refinement process from high-level specification to synthesizable design usually requires manual fine tuning to achieve high performance. More progress is needed to automate the design process at higher levels in order to produce designs of the same quality as is achievable by hand. It is thus essential that the specification (or behavior) and the intermediate design stages be verified for consistency and correctness with respect to some user-specified properties or a previous level of the specification, thus making post-design verification essential. Formal verification techniques are useful in verifying designs between different levels of hierarchy. Such as using sequential equivalence checking, we can verify that whether the RTL model of the design satisfies its specification or not. We can also apply formal verification techniques to verify the gate level netlists of the design. Currently combinational equivalence checking is used in post synthesis design verification where often manual design changes focus on speed, power or testability considerations. In order for a combinational equivalence checker to work, the designs must have a one-to-one mapping of registers/flip-flops. Model checking can be applied to prove temporal properties, i.e., specification, on a design model under all possible and allowable conditions. Here the design under verification can be an

RTL model or a behavioral model. Formal verification techniques, however, cannot be applied to detect a fabrication fault resulting from layout defects during the fabrication process, which may lead to an incorrect behavior of the design.

#### 1.2.1 Formal Verification

Formal verification technique is the mathematical demonstration of consistency between specification and implementation of a design. The ability of formal verification is to check "corner-cases", which are difficult or infeasible to test through simulation. These include especially complex scenarios unanticipated by the designers. Decreased time to market comes from the ability to apply formal verification earlier in the design cycles and thus find bugs sooner than is possible with simulation. Verifiers who adopted formal verification methods cut the time required to verify a complex design's implementation from months to weeks or days. Because formal verification techniques consider all cases implicitly, a verifier does not need to generate test cases to verify a design which takes much of the verification time during traditional simulation phase. Due to the above reasons formal verification is growing as a powerful complementary approach to simulation in the industrial community [39].

#### **1.2.2 Formal Verification Techniques**

In general, formal verification consists of mathematically establishing that an implementation satisfies its specification. The implementation refers to the system design which is to be verified. This entity can represent a design description at any level of the system abstraction hierarchy. The specification usually refers to the property with respect to

which correctness is to be determined. It can be expressed in a variety of ways, such as behavioral description, an abstract structural description, a timing diagram which reflects the behavior of the system at different time points, a temporal logic formula, etc.

Formal verification techniques naturally group themselves into theorem proving methods and automated FSM state enumeration based methods [31, 37].

#### 1.2.2.1 Theorem Proving

Theorem proving is the most general verification technique, in which a specification and its implementation are usually expressed as first-order or higher-order logic formulae. Their relationship, equivalence or implication, is regarded as a theorem to be proven within the proof system using a set of axioms and inference rules. Theorem proving have had their greatest successes in verifying datapath dominated circuits as it supports the verification of parameterized datapath dominated circuits [51]. It has high abstraction and powerful logic expressiveness capabilities. Using theorem proving, designs can thus be represented at different abstraction levels rather than only at the boolean level [35]. Therefore, it allows a hierarchical verification methodology which can effectively deal with the overall functionality of designs having complex datapaths. However, in contrast to more automated formal verification methods, such as model checking or equivalence checking, it is currently a memory and time consuming methods. This is specially so when a real industrial design is to be considered. Users need expertise to verify any design using theorem proving which is the major difficulty for applying the method on industrial designs. Some of the widely used theorem prover in the hardware verification community are HOL (Higher-Order Logic) [30], PVS (Prototype Verification System) [46], Nqthm (a BoyerMoore theorem prover) [8], ACL2 (Industrial strength version of the Boyer-Moore theorem prover) [36].

#### 1.2.2.2 FSM-based Techniques

Automated finite state based methods can also be classified into the following categories [31]:

- Model Checking: The specification is in the form of a logic formula, the truth of which is determined with respect to a semantic model provided by an implementation.

- Equivalence Checking: The equivalence of a specification and an implementation is checked, e.g., equivalence of functions, equivalence of finite-state automata, etc.

Model checking [17, 18] is an automatic technique for verifying finite state concurrent systems. It has a number of advantages over traditional approaches to the problems that are based on simulation and deductive reasoning. The method has been used successfully in practice to verify complex sequential circuit designs and communication protocols. In model checking, ideally the verification is completely automatic. There are two main approaches within model checking — logic based and automa-based [37]. The logic paradigm is based on temporal logics [10, 27]. On the other hand, the automata paradigm is based on language containment [38]. These two are not at all fundamentally same and each can be described in terms of the other.

A Model checker provides means for checking that a model of the design satisfies a given specification, but it is impossible to determine whether the given specification covers all the properties that the system should satisfy. The main challenge in model checking

is dealing with the state space explosion problem [13]. This problem occurs in systems with many components that can interact with each other or systems that have data structures that can assume many different values, e.g., the datapath of a design. In such cases the number of global states can be enormous. One successful technique which attempts to reduce the state space explosion problem is known as symbolic model checking [22, 23]. In this technique, the transition and output functions as well as the sets of states generated during the reachability analysis are encoded by Bryant's Reduced and Ordered Binary Decision Diagrams (ROBDDs) [11]. A number of ROBDD-based verification tools have been developed which are used by the hardware verification community are VIS (Verification Interacting with Synthesis) [9], SMV (Symbolic Model Verifier) [44]. Both of these tools are based on CTL [8]. However, the ROBDD-based methods are not capable to verify designs having non-trivial datapaths [23, 16]. Other tools like, FormalCheck [7] perform model checking based on ω-automata [33] which is commercialized by Cadence design systems. It has some built-in localization reduction algorithm that can handle large size industrial design [7, 14].

Equivalence checking [37] is used to proof the functional equivalence of two design representations modeled at the same or different levels of abstraction. It can be divided into two categories: one is combinational equivalence checking, and the other is sequential equivalence checking. Equivalence checking verifies for all input sequences that an implementation has the same outputs as the specification.

In combinational equivalence checking, the function of the two descriptions are converted into canonical forms which are then structurally compared. The major advantage of BDDs is their efficiency for a wide variety of practically relevant combinational circuits.

Two combinational designs functionally modeled by the Boolean functions are proven equivalent by compairing their normal forms. If ROBDDs are used which have the canonical form property, it is sufficient to test both graphs for isomorphism. Subject to a reduction criterion and for a fixed variable ordering, BDDs are a canonical representation for Boolean functions, in the sense that the BDDs for two functions  $f_1$  and  $f_2$  are isomorphic iff  $f_1 = f_2$ . Current designs which are clock-driven synchronized designs, need to be separated into small portions. The tool then maps each register of one model into another and compares their combinational circuits between every two consecutive registers.

Sequential equivalence checking is used to verify the equivalence between two sequential designs at each state. Sequential equivalence checking considers just the behavior of two designs while ignoring their implementation details such as register mapping. It can verify the equivalence between RTL and netlist or RTL and behavioral model which is very important in design verification. To verify the equivalence of these models, we need efficient representation for the manipulation of next-state and output functions and the set of states. Two models are considered equivalent iff for each input sequence, both machines generate the same output sequence. The problem of showing that two machines are equivalent can be reduced to the problem of finding the reachable state set of a product machine. The reachable state set of sequential circuit can be computed using a fixpoint calculation, where the next-state relation derived from the next-state function and current inputs to the circuit. The number of iterations required to compute the reachable state set can be linear in the number of states for the circuits that have "long" cycles of states. The disadvantage of sequential equivalence checking is that it cannot handle a large design because it encounters state space explosion problem very fast.

Recently, a number of ROBDD extensions such as BMDs [12], HDDs [19] and K\*BMDs [26] have been developed to represent arithmetic functions more compactly than ROBDDs to accelerate the verification of complex arithmetic circuits. EOBDDs (can be improved by labelling the leaf nodes with terms containing abstract sorts. MDGs (Multiway Decision Diagrams) [20], successor of EOBDDs (Extended Ordered Binary Decision Diagrams) [42], include the labelling of edges to be first order terms and non-terminal nodes to be abstract variables. ROBDDs, a special cases of MDGs, can be turned into MDGs by transforming them from graphs representing functions into graphs representing relations. In this thesis, we will use MDG-based verification. Details on MDG are described in Chapter 2.

#### 1.2.3 Related Work

In this section, we review several existing related works on the formal verification of different moderate sized digital systems using FSM-based methods. Some of these case studies are used to illustrate the limitations of current formal verification technique in verifying industrial like designs. Among these limitations, state space explosion is the well-known problem faced by the FSM-based methods when verifying designs with a substantial datapath. Researchers of these works had presented different reduction and abstraction techniques to cope with this limitation.

Chen et al. at Fujitsu Digital Technology Ltd. [16] identified a design error in an ATM (Asynchronous Transfer Mode) [32] circuit using the SMV tool [44] by verifying some properties expressed in CTL [8]. When the circuit was manufactured it showed an abnormal behavior under certain circumstances. Identifying the specific error during simulation,

they established an abstracted model to cope with the state space explosion and verified the abstracted model by SMV. The design error was detected during the model checking. However, the ATM model was reduced and abstracted a lot from the original design according to the specific error, and the same ATM model may not be used to verify other properties of the original design.

Garcez [28] has also verified some properties on the implementation of the Fairisle ATM switch fabric [41] using HSIS [3] model checking tool. The author described the netlist implementation of the ATM switch fabric using a subset of Verilog, and checked properties on submodules of the fabric using model checking. During the model checking, he did not consider the whole switch fabric to avoid state space explosion. Moreover, he changed the implementation of the fabric to ease the verification process.

Lu and Tahar [42, 41] verified a the Fairisle ATM switch fabric [41] using VIS [9]. Since they did not succeed in using the original switch fabric to verify relevant liveness and safety properties (due to *state space explosion*) they abstracted the model by datapath reduction technique. After this reduction in the model, they successfully verified several properties, but the verification time of each property was unreasonably long. To reduce the verification time, they applied *property division* and *latch reduction* techniques. They also conducted equivalence checking between the behavioral and structural specifications of the submodules written in Verilog HDL. The VIS tool failed to complete the equivalence checking of even a very reduced model of the whole switch fabric due to state space explosion.

Hong and Tahar [49] used an ATM Bit Error Rate Monitor (BERMON) design to illustrate their methodology for the compositional verification of IP-block based designs using

VIS tool. In this work, they focused on the reasoning of the compositional verification of the IP based design and on the issue of how interface behavior should be provided with an IP block to make the verification feasible.

Rajan *et al.* [50] used a combination of theorem proving, model checking and simulation to verify a high-level ATM model. They used model checking to verify some control components in the design, and applied exhaustive simulation to verify some operational components. Theorem prover was applied to verify the whole ATM model. They discovered bugs in the high-level ATM model which was assumed correct during simulation.

Barakatain and Tahar [5] applied model checking techniques for the formal verification of a SCI-PHY Level 2 protocol (a super set of UTOPIA Level 2 protocol [2]) Engine. They used Cadence FormalCheck [14] to formally verify the RTL implementation of the Receive Slave SCI-PHY mode of the Transmit Master/Receive Slave (TMRS) design [48]. The TMRS is an existing industrial design of PMC-Sierra Inc., with a 7500 equivalent gate-count. During the verification process, they used several model abstraction and reduction techniques within FormalCheck to avoid state space explosion, and then verified a number of relevant liveness and safety properties on the TMRS. They succeeded the discovery of a number of mismatches between the TMRS RTL design, document specification and UTOPIA Level 2 protocol description.

Xu et al. [53] verified a Frame Multiplexer/Demultiplexer (FMD) chip from Nortel Semiconductors using Cadence FormalCheck [14]. The FMD chip is part of a system used in multiplexing/demultiplexing framed data between various channels and a SONET line. The authors constructed a non deterministic model to simulate the normal operating environment. Tool guided model reduction was used to build an abstracted model which in

turn reduced the state space of the original design. During the verification process, they detected two errors in the implementation of the FMD model.

Tahar et al. [52] verified the Fairisle ATM switch fabric [41] in an automatic fashion using MDGs by property and equivalence checking. The original design was modeled in Qudos HDL, containing 4200 equivalent gate-count. They used model abstraction techniques to reduce the state space of the gate level netlist. Using the abstract sort and uninterpreted functions within MDG, they were able to verified the whole switch fabric without having any state space explosion problem.

Zobair et al. [60] used the Fairisle ATM switch fabric [41] to investigate the impact of design changes on formal verification using the MDG tools [59]. In this work, they showed that design for *verifiability* can have significant effect on the speed of verification using automated decision diagram based technique. The same result was obtained by Curzon et al. [25], using interactive proof with the HOL theorem prover [30] for the same design verification. The difference in nature of these two verification methodologies suggests design for *verifiability* can be widely applicable as design for *testability*.

Z. Zhou et. al [58] demonstrated the MDG-based formal verification technique on the example of the Island Tunnel Controller (ITC) design. In this work, they studied in detail the non-termination problem of abstract state enumeration and presented a heuristic state generalization technique to solve this problem. They also provided comparative experimental results for the verification of a number of safety properties using two well-known ROBDD-based verification tools SMV [44] and VIS [9].

Balakrishnan and Tahar [4] verified an Embedded System of a Mouse Controller named PIC 16C71 from Microchip Technology Inc. using MDGs [20]. They modeled the

system at different levels of design hierarchy, i.e., the microcontroller RT level, the microcontroller Instruction Set Architecture (ISA), the embedded software assembly code level and the embedded software flowchart specification. The verification was conducted using equivalence checking and property checking. They detected inconsistencies in the assembly code with respect to the specification during the verification phase.

#### 1.3 Scope of the Thesis

In this thesis, we present a methodology for the formal verification of a real industrial design using Multiway Decision Graphs (MDGs) [20]. The design we considered is a Telecom System Block (TSB) — Receive APS Control, Synchronization Status Extraction and Bit Error Rate Monitor Telecom System Block (RASE TSB) which is a commercial product of PMC-Sierra Inc. [47]. The main aspect of this work is to illustrate the ability of the Multiway Decision Graphs (MDG) tools to carry out a verification process of a large industrial design. Equivalence checking and model checking have been carried for the verification process. The RASE TSB processes a portion of the SONET [6] line overhead of a received SONET data stream. It processes the first STS-1 of an STS-N data stream which can be configured to be received in byte serial format at 6.48 Mbps (STS-1) or 19.44 Mbps (STS-N).

As observed from the examples described in the related work section, the Fairisle ATM switch fabric (with its 4200 equivalent gates) is the largest design to be modeled and verified by the MDG tools. In contrast, the RASE TSB design contains 11400 equivalent gates which is much larger than any other design verified by the MDG tools.

The outline of this thesis is as follows: Chapter 2 gives a brief introduction to Multiway Decision Graphs and its related verification techniques. Chapter 3 illustrates, through simple examples, the hierarchical proof and abstraction methodologies for the modeling and verification of a Telecom System Block (TSB) using MDGs. Chapter 4 describes the functionality of the RASE TSB and applies the proposed modeling and verification approaches on the target TSB. In Chapter 4, we also present a comparison of experimental results obtained using MDG and Cadence FormalCheck. Conclusions and ideas on future work are presented in Chapter 5.

## Chapter 2

### **Multiway Decision Graphs**

Multiway Decision Graphs (MDGs), a new class of decision graphs, have been proposed [20] as a solution to the state space explosion problem of ROBDD based verification tools. These decision graphs subsume the class of Bryant's reduced ordered binary decision diagrams (ROBDD) [11], while accommodating abstract sorts and uninterpreted function symbols. MDGs are thus much more compact than ROBDDs which enhances its capability to verify a broader range of circuits [52].

#### 2.1 Multiway Decision Graphs

The underlying formal system of MDGs is a subset of many-sorted first-order logic augmented with a distinction between abstract sorts and concrete sort. Concrete sorts have finite enumerations, while abstract sorts do not. The enumeration of a concrete sort  $\alpha$  is a set of distinct constants of sort  $\alpha$ . The constants occurring in enumerations are referred to as individual constants, and the other constants as generic constants and could be viewed as 0-ary function symbols. The distinction between abstract and concrete sorts leads to a distinction between three kinds of function symbols. Let f be a function symbol of type  $\alpha_1 \times \alpha_2 \times ... \times \alpha_n \to \alpha_{n+1}$ . If  $\alpha_{n+1}$  is an abstract sort, then f is an abstract function symbol. If all the  $\alpha_1... \alpha_{n+1}$  are concrete, then f is a concrete function symbol. If  $\alpha_{n+1}$  is

concrete while at least one of the  $\alpha_1$ ...  $\alpha_n$  is abstract, then f is referred to as a *cross-operator*. Concrete function symbols must have explicit definition; they can be eliminated and do not appear in MDGs. Abstract function symbols and cross-operators are *uninterpreted*. An MDG is finite, directed acyclic graph (DAG). An internal node of an MDG can be a variable of concrete sort with its edge labels being the individual constants in the enumeration of the sort; or it can be a cross-term (whose function symbol is a cross-operator). An MDG may only have one leaf node denoted as T, which means all paths in the MDG are true formulae. Thus MDGs essentially represent relations rather than functions. In MDG, a data value can be represented by a single variable of abstract type rather than by concrete (e.g., 32 bits) boolean variables. Variables of concrete sorts are used for representing control signals. Using MDGs, a data operation is represented by an uninterpreted function symbol. As a special case of uninterpreted functions, *cross-operators* are useful for modeling feedback from the datapath to the control circuitry.

In MDG, a state machine is described using finite sets of input, state and output variables, which are pairwise disjoint. The behavior of a state machine is defined by its transition/output relations including a set of reset states. An abstract description of the state machine, called Abstract State Machine (ASM) [21], is obtained by letting some data input, state or output variables be of an abstract sort, and the datapath operations be uninterpreted function symbols. As ROBDDs are used to represent sets of states and transition/output relations for finite state machines (FSM), MDGs are used to compactly encoded sets of (abstract) states and transition/output relations for ASMs. This technique replaces the implicit enumeration technique [22] with the implicit abstract enumeration [15].

The notion of abstract description of state machines is hence a theoretical fundament for a verification methodology that makes it possible to verify sequential circuits automatically at the RT level using abstract sort and uninterpreted function symbols. In this sense, we can say that the verification method is applicable to designs where the data operations are viewed as black boxes [57]. Such a verification process fits well in the verification of RTL designs generated by high-level synthesis. This is because high-level synthesis algorithms schedule and allocate data operation without being concerned with the specific nature of operations. In the next sections, we describe the modeling and verification features of the MDG tools. Interested readers are referred to [15, 20, 21, 54, 56, 57, 59] for more details on the MDG algorithms and tools.

#### 2.2 Modeling Hardware with MDGs

MDGs describe circuits at the RT level as a collection of components interconnected by nets that carry signals. Each signal can be an abstract variable or a concrete variable. The input language for MDG based applications is a Prolog-style HDL, called MDG-HDL. This hardware description language allows the use of abstract variables for representing data signals and uninterpreted function symbols for representing data operations. MDG-HDL supports structural description, behavioral ASM descriptions, or a mixture of structural and behavioral descriptions. A structural description is usually a netlist of components connected by signals. A behavioral description is given by a tabular representation of the transition/output relation or the combinational function block. A complete reference of MDG-HDL can be found in [59].

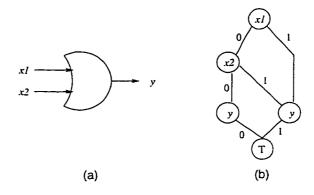

For logic gates, the input and output signals are always of concrete sort, i.e., boolean type. Figure 2.1 shows an OR gates and its MDG representation for a specific ordering of the variables. Boolean MDGs are essentially the same as ROBDDs.

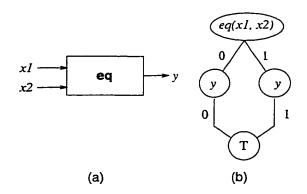

Feedbacks from datapath to control circuitry are represented using *cross-operators*. Figure 2.2(a) shows a comparator that used for the control portion of a circuit. The comparator produces a control signal y from two data inputs  $x_1$  and  $x_2$ . Both  $x_1$  and  $x_2$  are variables of abstract sort while y is a boolean variable. An uninterpreted function symbol eq of type  $[wordn, wordn] \rightarrow bool^1$  is used to denote the functionality of this comparator. If the meaning of eq matters, rewrite rules, such as  $eq(x, x) \rightarrow 1$  should be used. An MDG of the comparator is shown in Figure 2.2(b).

Figure 2.1: The MDG for an OR gate

<sup>1.</sup> The notation  $f: [\alpha \to \beta]$  implies that the function f has argument of sort  $\alpha$  and range of sort  $\beta$ .

Figure 2.2: The MDG for a comparator

Using MDGs tabular construct, we can represent an ITE (If -Then-Else) or CASE formulas. It is analogous to directed formula where a row gives the symbolic values of the variables in the head of the table as a disjunct of the directed formula. Figure 2.3(a) shows a tabular description of a sample ASM, where x is a boolean input, a is an abstract state variable and a is its next state variable. It performs *inc* operation (an uninterpreted function) when x = 1. Figure 2.3(b) shows its MDG representation.

Figure 2.3: The MDG for an ASM

#### 2.3 MDG-based Verification Techniques

The MDG software package includes algorithms for disjunction, relational product, pruning-by-subsumption (PbyS), and reachability analysis. Except for PbyS, the operations are a generalization of first-order terms of algorithms on ROBDD, with some restrictions on the appearance of abstract variables in the arguments. In the reachability analysis procedure, starting from the initial set of states, the set of states reached in one transition is computed by the relational product operation. The frontier set of states is obtained by removing the already visited states from the set of newly reached states using the pruningby-subsumption (PbyS) operation. If the frontier set of states is empty, then the reachability analysis procedure terminates, since there are no more unexplored states. Otherwise the newly reached states are merged (using disjunction) with the already visited states and the procedure continues where the next iteration with the states in the frontier set as the initial set of states. A facility to carry out simple rewriting of terms that appear in the MDGs is also included. This allow us to provide a partial interpretation of an uninterpreted function symbol. For example, if zero is an abstract generic constant of sort wordn and eqz(x) a cross-operator of type [ $wordn \rightarrow bool$ ], then we could provide a partial interpretation of eqz using the rewrite rule  $eqz(zero) \rightarrow 1$ , indicating that equal-to-zero is 1 when the argument is zero (but not revealing anything about the other values). User selected rewrite rules are applied anytime a new term is formed during MDG operations. In general, rewriting simplifies MDGs and helps to remove false negatives during safety property checking. Thus likely avoiding non-termination of the reachability analysis procedure for designs that depend on interpretation of operators for correct operation. A detailed description of the operations and algorithms can be found in [15, 20, 21, 57]; some possible solutions to

the non-termination problem are addressed in [1, 58]. The following sub-sections describe the verification techniques provided by the MDG tools.

#### 2.3.1 Combinational Equivalence Checking

The MDGs representing the input-output relation of each circuit are computed using the relational product of the MDGs of the components of the circuits. Then taking advantage of the canonicity of MDGs, it is verified whether the two MDG graphs are isomorphic. Using this technique, we can verify the equivalence of two combinational circuits. This technique can also be used to compare two sequential circuits when a one-to-one correspondence between their registers exists, e.g., equivalence checking between RTL model and gate level netlist of a design. However, combinational equivalence checking cannot handle the equivalence checking between RTL and behavioral models because these models are developed separately and it is not possible to map each register in the RTL model to that of the behavioral model.

#### 2.3.2 Invariant Checking

Using the symbolic reachability analysis technique, the state space of a given sequential circuit is explored in each state. It is verified that an invariant, i.e., a logical expression, holds over all reachable states. The transition relation of an ASM is represented by an MDG computed by the relational product algorithm from the MDGs of components which are themselves abstract machines. In other words, the relational product computes the (synchronous) product machine of the components ASMs. Using invariant checking, we can verify safety properties of a digital system.

#### 2.3.3 Sequential Equivalence Checking

The behavioral equivalence of two sequential circuits can be verified by checking that the circuits produce the same sequence of outputs for every sequence of inputs. This is achieved by forming a circuit from two circuits feeding the same inputs to both of them and verifying an invariant asserting the equality of the corresponding outputs in all reachable states. It can verify the equivalence between RTL and gate level netlist or RTL and behavioral model which is very important in design verification. The drawback of this technique is that it cannot handle a large design due to state space explosion problem. With the increasing number of state components in synchronous digital design, the state space grows exponentially, which is more severe in the product machine generated for sequential equivalence checking.

#### 2.3.4 Model Checking

MDG model checker provides both safety and liveness property checking facilities using the implicit abstract enumeration of an abstract state machine [54]. In MDG model checking, the design is represented by an ASM and the properties to be verified are expressed by formulae in the first-order ACTL-like temporal logic called  $\mathcal{L}_{MDG}$  [55]. The ASM model of  $\mathcal{L}_{MDG}$  is composed of the original model along with a simplified invariant [55], and the simplified invariant is checked on the composite machine using the implicit abstract enumeration of an ASM. However, only universal path quantification is possible with the current version of MDG model checker.

#### 2.3.5 Counterexample Generation

Using counterexamples, a user can trace errors in the design during a verification process. If an invariant is violated at some stages of the reachability analysis, a counterexample facility generates a sequence of input-state pairs leading from the initial state to the faulty behavior.

## **Chapter 3**

## **Modeling and Verification Methodology**

Abstraction and hierarchical proof can simplify the verification process vastly. To accelerate the design flow and assure the correctness of a complex digital system, a hierarchical design approach shown in Figure 1.1 (Chapter 1) is usually anticipated. This approach has many advantages and is commonly used in practice. It is particularly useful in the context of formal verification. In addition to hierarchical proof, one must use abstraction mechanisms for relating formal descriptions of hardware designs at different levels of design hierarchy [45]. The following two sub-sections will present more about these two methodologies and their applications to the modeling and verification of a Telecom System Block (TSB) using MDGs.

#### 3.1 Hierarchical Proof Methodology

When a design to be proved correct is large, formal method is usually applied hierarchically [24]. The design is structured into a hierarchy of modules and sub-modules, and specifications that describe "primitive components" at one level of the hierarchy then become specifications of the intended behavior at the next level down. The structure of the proof mirrors this hierarchy: the top-level specification is shown in Figure 3.1 to be satisfied by an appropriate connection of modules. At the next level down, each of these modules is shown to be correctly implemented by a connection of sub-modules, and so on — down to the lowest level of the hierarchy. Hierarchical organization of a design not only

makes the verification process natural, it also makes the task tractable. Dealing with the complexity of a complete system description of even modest size, by standards today, is out of bounds for most verification techniques. By splitting this large problem into smaller pieces that can be handled individually, the verification problem is made mangeable. It effectively increases the range of circuit sizes that can be handled in practice.

Figure 3.1: An example of hierarchical proof

We can illustrate the hierarchical proof methodology by using Figure 3.1 with a small example. The design we considered is structured into a three-level hierarchy of modules.

At the top level, i.e., Level 1, there are two modules  $S_I$  and  $S_2$ , interconnected by internal signals. At this level these modules are considered to be primitive devices. The description M implements the behavior of the entire system at this level. It is constructed by composing the modules  $S_I$  and  $S_2$  and hiding the internal signals. The correctness statement at this level of the proof asserts that the model M satisfies the specification of the whole system, represented by symbol S. At the next level down, i.e., Level 2,  $S_I$  and  $S_2$  become specifications of required behavior for the two sub-systems implemented by  $I_I$  and  $I_2$ . These models are constructed from the specifications of the primitive modules at Level 3, i.e.,  $B_I$ ,  $B_2$ ,  $B_3$  and  $B_4$ . At level 2, we have two separate correctness theorems to prove (see Figure 3.1). These theorems assert that the sub-systems modeled by  $I_I$  and  $I_2$  correctly implement the abstract behaviors given by the specifications  $S_I$  and  $S_2$ , respectively. We can conclude from this, and from the correctness result for M proved at the top level, that integrating the two sub-systems modeled by  $I_I$  and  $I_2$  give a concrete implementation of the entire design which is correct with respect to the top-level specification S.

A hierarchical proof of correctness usually has many intermediate levels between the concrete design model and the top-level specification. At each level, correctness theorems relate each sub-module to an abstract specification at the next higher level. In general, there may be many separate theorems at each level, one for each different kind of module used at that level. To obtain a completed proof, we must integrate all these intermediate correctness results into a single correctness theorem that relates a fully concrete model of the entire design to the top-level specification of the intended behavior. There are three separate theorems in the hierarchical proof shown in Figure 3.1.

They are as follows:

Theorem 1: M satisfies S

Theorem 2: I<sub>1</sub> satisfies S<sub>1</sub>

Theorem 3: I<sub>2</sub> satisfies S<sub>2</sub>

Proving these theorems shows only that each module in the hierarchy is correct with respect to its specification. To complete the proof, we must derive a theorem stating the correctness of the entire design with respect to the top-level specification. To do so, the following theorem must be proved.

Theorem 4:

$$B_1 \wedge B_2 \wedge B_3 \wedge B_4$$

satisfies S

This theorem states that a complete and fully detailed design model constructed from the primitive modules  $B_1$ ,  $B_2$ ,  $B_3$ , and  $B_4$  satisfies the top-level abstract specification S. This hierarchical approach to hardware verification is possible in logic because design models and specification use the same language (syntax). Both of them are simply boolean terms, and the model-building operation of composition ( $\land$ ) can be applied to both of them. Terms used as abstract specifications at one level in a hierarchical proof can therefore be treated as models at the next higher level. In a formalism in which specifications and models are syntactic entities of two distinct types, this direct approach to hierarchical verification is not possible.

This hierarchical proof approach has the added advantage that if we reuse sub-modules in the other modules we do not repeat work unnecessarily. Also if we change the implementation of the some modules, we do not need to reverify the whole design. We just need to prove correctness theorems for the new implementations of the modules and recombine the correctness theorems. A further advantage is that separate subtrees of the design can be

verified independently by different people. The interface between teams occurs at the point where the subtrees are joined. Here, provided the behavioral specifications of the modules are agreed on, the upper levels can also be verified independently

# 3.2 Abstraction and Reduction Techniques

As the complexity of a functional blocks increase, the default setting used by most formal verification tools may not be sufficient. We need some kind of abstraction techniques in order to reduce the state space of the design under verification. The more extensive the reachable states, the more CPU time and memory it takes to verify a system. Abstraction is the process by which the important properties of a complex object are isolated for further use and the remaining ones ignored as being irrelevant to the task at hand. An example is the process of procedural abstraction in high level programming languages. Programming languages support this abstraction for dealing with the complexity of programming. In a similar way, abstraction plays an important role in hardware verification. Here, an abstraction mechanism establishes a relationship of abstraction between a complex description of hardware behavior and simpler one. This provides a means for controlling the complexity of both specifications and proofs of correctness. By suppressing the irrelevant information in detailed descriptions of hardware behavior, and thereby isolating the properties of these descriptions which are most important. An effective abstraction and reduction mechanism helps to reduce the size and complexity of the design at each level in the hierarchically-structured design. There are four different kinds of abstraction techniques used in hardware formal verification [45].

### 3.2.1 Behavioral Abstraction

Behavioral abstraction involves proving the correctness of designs with respect to partial specifications of intended behavior. Partial specification does not completely define the full range of behavior that a system can exhibit, but only defines its behavior in environments or states that are of particular interest. In logic, specifications are expressed by constraints on the values allowed on the external signals of a design. The range of behavior defined by a specification is given by the set of values that satisfy these constraints. A partial specification constraints a design's signals to have certain values in situations that are significant or relevant, but leaves unconstrained the signal values in all other situations. This means that in the situations of "undefined" behavior, the predicate defining a partial specification will be satisfied by signals values that would not be allowed by a more complete specification of the system. Thus, the partial specification of a system imposes weaker constraints on its signal values than a complete specification would. For example, in a target system there are several components, e.g., register file and input/output multiplexor, in addition to the main block which controls the main functionality of the system. Also assume that only the verification of the main block is of interest. In that case, the additional blocks can be removed from the top-level of the design, provided that this removal does not change the behavior of the system. The inputs of the main block which are fed by the removed blocks, can be set to primary inputs of the system.

### 3.2.2 Structural Abstraction

Structural abstraction is the most fundamental abstraction technique to hardware verification. It suppresses information about a design's internal structure, i.e., only the behavior of the external inputs and outputs of a module is of interest. The basic idea of structural abstraction is that the specification of a device should not reflect its internal construction. To illustrate this abstraction technique, we can have an example of a *BYTE\_EXTRACTOR* from our case study (see Chapter 4). To keep our description simple, we are taking only a portion of the byte extraction circuit.

In Figure 3.2, the behavioral description of the BYTE\_EXTRACTOR does not contain any information about its internal structure. It reflects only the characteristics of the external signals. All the internal signals, (e.g., c1, c3, cr1, cr3, cr and s1), are hidden in the description of specification. But the implementation contains explicit information about the internal structure.

Figure 3.2: An example of structural abstraction

# 3.2.3 Data Abstraction

The formal description of a system can be more abstract than its realistic model. The specification of intended behavior for a system may be expressed in terms of an abstract notion of the types of values it operates on. The free variables in such a formal description will not stand for the values actually present on the external wires of a design. Instead it will represent more abstract externally observable quantities. The description of a system can be expressed in terms of operations appropriate to these abstract quantities, rather than the operations carried out by the actual hardware on a more concrete representation of these values. The logical types of the variables that represent these abstract values will therefore generally differ from those of the variables in the original design model. A satisfaction relation based on data abstraction must therefore relate concrete variables of one type in the model to more abstract variables of another type in the specification. Both the model and specification express a constraint on free variables that directly correspond to physical wires, but use different logical types to represent the range of values that can appear on them. The model and specification will then be terms of the forms  $M[c_1, c_2, ..., c_n]$  of type  $f_c$  and  $S[a_1, a_2, ..., a_n]$  of type  $f_a$ , respectively. In this case, each variable  $a_i$  in the specification represents the same externally observable value as the corresponding variable  $c_i$  in the implementation. The specification, however, is expressed as a constraint on abstract values of type  $f_a$ , instead of the concrete values of type  $f_c$  that represent actual physical values in the implementation. To formulate a correctness statement that relates these two specifications, we need an appropriately-defined data abstraction function to map these two different descriptions. Given such a mapping function  $f\!\!:\!f_{\!c}\to f_{\!a}$  , a correctness

statement which expresses a relationship of data abstraction between the model and the specification can be formulated by the following theorem [45]:

$$M[c_1, c_2, ..., c_n]$$

satisfies  $S[f(c_1), f(c_2), ..., f(c_n)]$

This theorem states that every combination of values  $c_1, c_2, ..., c_n$  that corresponds to the model M, actually appears on the external wires of the system is a concrete representation at a lower level of data abstraction for a combination of more abstract values  $f(c_1), f(c_2)$ ...,  $f(c_n)$  which is allowed by the specification of that system. The resulting correctness statement asserts that the operations on concrete variables actually carried out by the model correctly implement the required operations on abstract values expressed by the specification. The advantage of data abstraction is that it allows specifications of intended behavior to be written in terms of abstract *high-level* operations on data, without having to specify precisely how this data is represented.

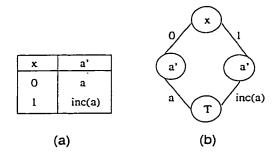

In this thesis, we use MDG-HDL, which is the input language of the MDG tools, to model the design under investigation. One of the major advantages in using MDGs is the ability to handle abstract descriptions. This avoids all the ponderous procedure of defining each bit of a vector of boolean variables. Rather, a vector of boolean variable can be viewed as a single abstract variable. Thus a 24-bit frame-counter can be modeled as a variable of abstract sort worda24 instead of a concrete sort with enumeration {0, 1, ..., 16777215}. Another advantage in using MDGs is the ability to represent data operations by uninterpreted function symbols. This enables the arithmetic and logical blocks to be viewed as black boxes. As a special case of uninterpreted function, cross-operators are useful for modeling feedback from the datapath to the control circuitry. We can illustrate the idea of data abstraction in MDGs using an example (see Figure 3.3) from our case study. The circuit in the example is performing data operations

33

over two operands of different size. It is concatenating 5-bits for matching the size of the operands to be used for addition and extracting twelve bits from the least significant bit positions of the output by truncating the upper bits. Using MDG-HDL, we can abstract the width of the datapath as well as the functionality of the original model. The data operations (e.g., addition, concatenation) can be modeled using *uninterpreted* function symbols (e.g.,  $Add_17$  of type  $[worda17, worda17] \rightarrow worda17$ ), applied to the operands.

Figure 3.3: An example of data abstraction

# 3.2.4 Temporal Abstraction

In temporal abstraction, the sequential or time-dependent behavior of a system is viewed at different grains of discrete time. An example of temporal abstraction is the unit delay or register, implemented by an edge triggered flip flop. At the abstract level of description the device is specified as a unit delay, i.e., one unit of discrete time corresponding to the clock period. This type of abstraction technique has not been applied to our case study as the design is not pipelined and every function is taking one clock period to complete.

### 3.2.5 Model Reduction

In our case study (Chapter 4), we applied the model reduction technique to abstract the behavior of the telecom system block by removing some modules, provided that the main functionality of the system will not be changed. Besides five main functional blocks, the design has one common-bus-interface module and two input/output multiplexors. The common-bus-interface module is used mainly for configuration and testing the interface of the telecom system block. This module contains several read/write registers to store the outputs of other four functional blocks and the interrupt signals are generated by reading these registers. The input/output multiplexors are used for simulation purposes. In our modeling and verification of the Telecom System Block, we can eliminate these three modules which have no effect on the functionality of the system. The system is modeled in such a way that all the intermediate signals between the common-bus-interface and other five modules are to be considered as primary inputs/outputs of the system. We can

conclude from the above descriptions that model reduction of the telecom system block does not change its main functionality at all.

# **Chapter 4**

# Modeling and Verification of RASE TSB: A Case Study

The commercial design that is investigated in this work is a Telecom System Block (TSB) named Receive Automatic Protection Switch Control, Synchronization Status Extraction and Bit Error Rate Monitor (RASE) which is commercialized by PMC-Sierra Inc. [47]. In this Chapter, we apply the hierarchical verification and abstraction methodologies described in Chapter 3 on this TSB. We also present experimental results using MDG and FormalCheck.

# 4.1 The RASE Telecom System Block

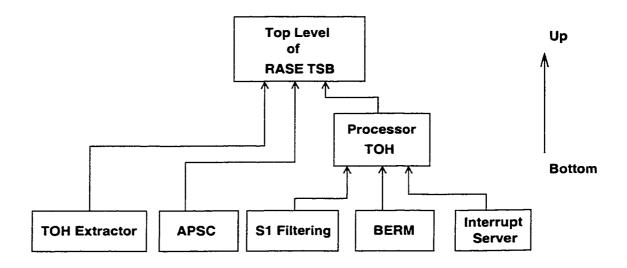

The RASE Telecom System Block (TSB) [47] consists of three types of components: Transport overhead extraction and manipulation, Bit Error Rate Monitoring (BERM) and Interrupt Server (see Figure 4.1). In addition to these blocks, it has an interface with Common Bus Interface (CBI) block which is used mainly for the configuration and testing the interface of the TSB and two inputs/outputs multiplexors. The transport overhead extraction and manipulation functions are implemented by three sub-modules (transport overhead bytes extractor, automatic protection switch control and synchronization status filtering). In this study, all the above modules are of interest except the CBI block and inputs/outputs multiplexer which were used for simulation purposes.

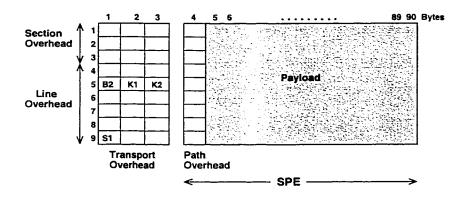

The RASE TSB extracts the Automatic Protection Switch (APS) bytes, i.e., K1 and K2 bytes, and the Synchronization Status byte, i.e, S1 byte, from a SONET frame (see Figure 4.2). After extracting the above bytes, it processes them according to some requirements set by the SONET standard [6].

Figure 4.1: The RASE telecom system block

The TSB also performs Bit Error Rate Monitoring using the BIP-24/8 line of a frame, i.e., B2 bytes (Figure 4.2). The received line Bit Interleaved Parity (BIP) error detection code is based on the line overhead and synchronous payload envelope of the received data stream. The line BIP code is a bit interleaved parity calculation using even parity. The calculated BIP code (pre-defined by programmable registers) is compared with the BIP code extracted from the B2 bytes of the following frame. Any differences indicate that a

line layer bit error has occurred and an interrupt signal will be activated in response to this error. A maximum 192000 (24 BIP/frame x 8000 frames/second) bit error can be detected for Synchronous Transport Signal (STS) -3 rate and 64000 (8 BIP/frame x 8000 frames/second) for the STS-1 rate. The RASE TSB contains two BERM blocks. One BERM is dedicated to monitor for the Signal Failure (SF) error rate and the other BERM is dedicated to monitor for the Signal Degrade (SD) error rate. They work on the same module and offer the same functionality.

Figure 4.2: The STS-1 SONET frame structure

The Automatic Protection Switch (APS) control block filters and captures the receive automatic protection switch channel bytes (K1 and K2), allowing them to be read via CBI bus. These bytes are grouped and filtered for 3 frames before being written to these registers. A protection switching byte failure alarm is declared when 12 successive frames have been received without 3 consecutive frames having the same APS bytes. When 3 consecutive frames have identical APS bytes, the alarm will be removed. The detection of invalid APS codes is done in software by polling the APS K1 and K2 registers, which is not of interest in the current study.

The synchronization status filtering block captures and filters the S1 status bytes, allowing them to be read via CBI bus. This block can be configured to capture the S1 nibble of eight consecutive frames and filters the nibbles/bytes for the same value. It can also be configured to perform filtering based on the whole S1 byte.

The interrupt server activates an interrupt signal if there is a change in APS bytes, a protection switch byte failure, a change in the synchronization status, or a change in the status of Bit Error Rate Monitor (BERM) occur.

The Common Bus Interface (CBI) block provides the normal and test mode registers. The normal mode registers are required for normal operation while the test mode registers are used to enhance the testability of the TSB. The input test multiplexer selects normal or test mode inputs to the TSB. The output test multiplexer selects the outputs modes.

# 4.2 Behavioral Modeling of the TSB using MDGs

The description of a system can be a specification or an implementation. A specification refers to the description of the intended behavior of the hardware design. An implementation refers to the hardware design of the system which can be at any level of the design, i.e., in RT level or gate level netlist. In the MDG system, an abstract description of a state machine (ASM) can be used to describe a specification or an implementation. We adopt a hierarchical approach to model the TSB behavior at different levels of the design hierarchy which in turn enables the verification process to be done at different levels. Figure 3 represents a tree showing the level of design hierarchy of the RASE TSB.

Inspired by [47], we derived a behavioral model of the RASE TSB which consists of five main functional blocks — Transport Overhead Extractor, Automatic Protection Switch,

Synchronization Status Filtering, Bit Error Rate Monitoring and Interrupt Server. These are the basic building blocks of the TSB. We composed the behavioral model of each basic building block in a bottom-up fashion until we reached the top-level specification of RASE telecom system block. In the following sub-sections, we represent the behavioral model of each basic module of the TSB which will be composed to form the complete behavior of the TSB.

Figure 4.3: The hierarchy tree of the TSB

Examples of sorts and uninterpreted functions that are used to model the *RASE TSB* are as follows:

- concrete sort  $bool = \{0, 1\}$ .

- abstract sort worda8 (used to represent 8-bits word).

- generic constant zero of sort wordn.

- cross-operator  $eq\_ex$  of type ([worda8, worda8]  $\rightarrow$  bool) is used to compare the equality.

- uninterpreted function symbol inc of type [worda8 → worda8] is used as an incrementer of 8-bits.

- cross-operators bit0,...,bit3 of type ([worda8]  $\rightarrow bool$ ) are used to extract the boolean value from an abstract variable.

## 4.2.1 Transport Overhead Extraction

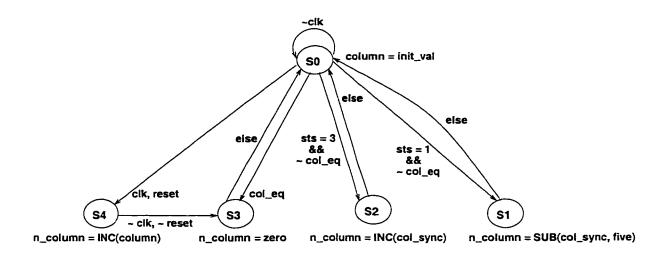

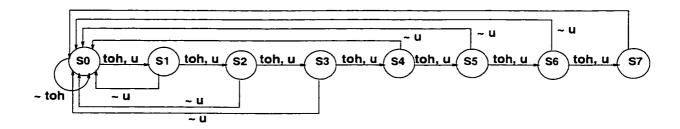

To derive the behavior of transport overhead extraction, we need to have a look into the structure of a SONET frame in Figure 4.1 and the locations of S1, K1, K2 and B2 line overhead bytes within that frame. The basic signal of SONET is the STS-1 electrical signal. The STS-1 frame format is composed of 9 rows of 90 columns of 8-bits bytes, in total 810 bytes [6]. The byte transmission order is row-by-row, left to right. At a rate of 8000 frames per second, that works out to a rate of 51.84 Mbps. The STS-1 frame consists of Transport Overhead (TOH) and Synchronous Payload Envelope (SPE). The Transport Overhead is composed of Section Overhead (SOH) and Line Overhead (LOH). The SPE is divided into two parts: the STS Path Overhead (POH) and the Payload. The first three columns of each STS-1 frame make up the TOH and the last 87 columns make up the SPE. The SPE can have any alignment within the frame and this alignment is indicated by the pointer bytes in the LOH which is not of our interest in this work. The behavior of the extraction module is based on a row and a column counting abstract state machine (ASM) rather than finite state machines and an extractor which extracts the specific byte (i.e., RIN, receive input data stream) within a SONET frame. The column counting ASM has five states — S0, S1, S2, S3 and S4 (see Figure 4.4), while the row counting ASM has three states — S0, S1 and S2 (see Figure 4.5). The symbols '&&', '||', and '~' in all the figures, denote logical AND, OR and negation of the signals, respectively.

Figure 4.4: The column counting ASM

The column counting state machine accepts five signals clk, rst, rfp, sts and col\_eq as its input control signals (see Figure 4.4). The presence and absence of a frame is indicated by rfp signal at high. A SONET frame can be either in STS-1 or STS-3 mode which is indicated by the signal sts. An abstract state variable column represents the current count number of the columns. At each time, the counting state machine has a transition to different state according to the control input signals. In this abstract description of the counter, the count column is of an abstract sort, say wordn. The input control signals, (e.g., clk, rst, rfp and sts), are of concrete sort bool with the enumeration {1, 0}. The uninterpreted function inc of type [ $worda8 \rightarrow worda8$ ] denotes the increment-by-one cross-operator operation. The eq\_ex(column,constant\_signal) of type ([worda8, worda8]  $\rightarrow$  bool) is used to model the feedback to the column counting state machine. This cross-operator represents a comparator which accepts two operands of abstract sort, i.e., column and constant\_signal, and sets the control signal col\_eq ='1' whenever the inputs are equal. State S0 is the reset state from there can be four transitions

depending on the input control signals. In state S1, a data operation will be performed to adjust the column number as per frame modes and the result of the operation will be assigned to the count value. In state S2, the constant signal *column\_sync* will be incremented by one to adjust the frame mode i.e., STS-1, STS-3 and the incremented value will be assigned to the count value. State S3 is the counter roll-over state which depends on the control signal *col\_eq* and *reset*. In state S4, the counter will be incremented by one in each clock cycle if no other transitions are possible and it will remain in that state unless a transition is possible to other state depending on the inputs.

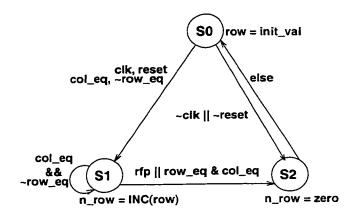

Figure 4.5: The row counting ASM

The row counting state machine, having three states, uses  $col\_eq$  and  $row\_eq$  control signals generated by the  $eq\_ex$  cross-operator to increment or roll-over the row counting variable row (Figure 4.5). State S0 is the initial state where the variable row initialize by its reset value  $init\_val$ . Any frame start pulse rfp or both  $col\_eq='1'$  and  $row\_eq='1'$  makes a transition to state S2 where state variable row assigned to be zero which is a generic constant of abstract sort wordn. The abstract state variable row, in state S1, will be incremented by one using the uninterpreted function symbol inc of type

[worda8  $\rightarrow$  worda8]. Whenever two control signals  $col\_eq = `1'$  and  $row\_eq = `0'$ , given by the cross-operators  $eq\_ex(column\_count, constant\_signal)$  and  $eq\_ex(row, constant\_signal)$ , the abstract state variable row increments by one. The symbol '||', '&&' and '~' denote logical OR, AND and negation of the signals, respectively.

Figure 4.6: Flowchart specification of byte extractor and its MDG model