**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

800-521-0600

**UMI**®

# Generation of SDL Specifications from UML and MSC Use Cases

### Stephan Bourduas

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of

Master of Applied Science

Concordia University

Montreal, Quebec, Canada

June 2001

© Stephan Bourduas, 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-64058-2

#### Abstract

## Generation of SDL Specifications from UML and MSC Use Cases

#### Stephan Bourduas

As software systems are becoming more complex, errors in the implementation of user requirements have become common. Methodologies that incorporate formal and semiformal techniques into the development process thus minimizing errors would be beneficial to the software engineering community as a whole. The inclusion of graphical notations such as UML (Unified Modeling Language), MSC (Message Sequence Charts) and SDL (Specification Description Language) in the development process will allow for a much higher level of automation resulting in fewer errors and ultimately better quality software.

In this thesis, we developed and implemented an approach for specifying distributed systems in UML and MSC, where MSC use cases are used to express the requirements and UML is used to describe the architecture of the distributed system under consideration. To specify the behavior, the MSC language is used to describe high-level use cases that are then refined in a stepwise manner into design MSCs. For each refinement, the newly obtained MSC is validated against the previous MSC using a conformance relation that we defined. UML, more precisely Class Diagrams and Object Diagrams, are used to specify the architecture of the system. A distributed system specification style in UML was developed and mapping rules were defined to enable the translation from a UML to SDL architecture. The approach then makes use of an existing methodology that combines the design MSCs and the SDL architecture into a full SDL specification, which is correct with respect to the design MSCs and is free of deadlocks.

Our approach takes advantage of the formality of SDL while using the two very popular and intuitive notations, UML and MSC, as a front end. The formal semantics of SDL allow for simulation and validation. In addition, commercial tools support automatic code generation.

# Dedication

To my parents, Maria and René.

## Acknowledgements

I would like to express my heartfelt thanks to my supervisor, Dr. Ferhat Khendek, for his patience, guidance and dedication. He motivates students to learn and his door is always open. Dr. Khendek is a credit to the teaching profession, and I could not have asked for a better supervisor.

Words are not sufficient to express my gratitude for the love and support of my parents, Maria and René, without which I would have never made it this far. Thank you for everything.

My cousins, Maria, Venetia and Kosta, deserve thanks for all their support and understanding. I know that whatever lies ahead, I can always count on them to be there, I am forever grateful.

My aunts and uncles, for all your support and love, I cannot thank you enough. I would like to thank in particular Leah and Nick Priftis for all the time they spent helping me and for their friendship.

My dearest Maria, for always being there for me, for all your support, for just listening, for just being you, I thank you endlessly.

I would also like to take this opportunity to thank France Telecom for their financial support.

# **Table of Contents**

| LIST OF | FIGURES X                                               |

|---------|---------------------------------------------------------|

| LIST OF | TABLESXIV                                               |

| INTROD  | UCTION1                                                 |

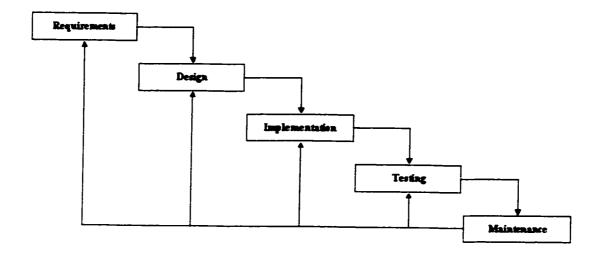

| 1.1 Sc  | oftware Lifecycle 1                                     |

| 1.2 Fo  | ormal and Semi-Formal Notations 3                       |

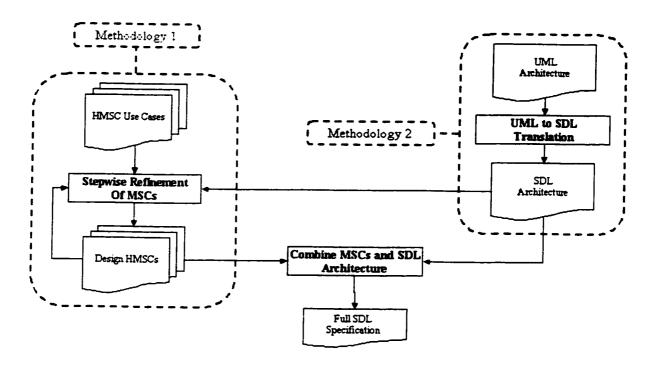

| 1.3 Us  | sing MSC and UML to Generate SDL Design specifications4 |

| 1.4 O   | rganization of Thesis 6                                 |

| BACKGE  | ROUND8                                                  |

| 2.1 Un  | ified Modeling Language 8                               |

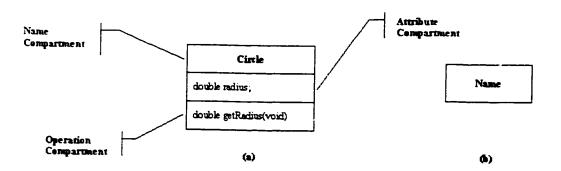

| 2.1.1   | Static Modeling9                                        |

| 2.1.1   | 1 Class9                                                |

| 2.1.1.  | 2 Extending UML                                         |

| 2.1.1.  | 3 Relationships Between Classes 11                      |

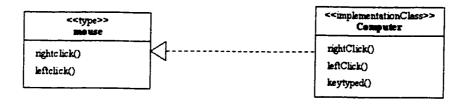

| 2.1.1.  | 4 Type and Implementation Classes                       |

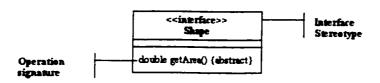

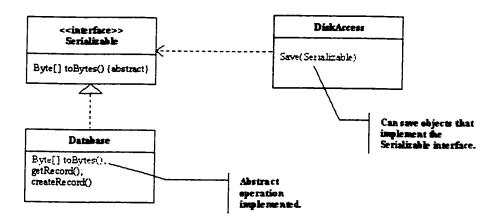

| 2.1.1.  | 5 Interface                                             |

| 2.1.1.  | 6 Package                                               |

| 2.1.2   | Dynamic Modeling                                        |

| 2.2 Me  | ssage Sequence Charts 16                                |

| 2.2.1   | Basic Message Sequence Charts                           |

| 2.2.2   | High-Level Message Sequence Charts                      |

| 2.3 Spe | ecification Description Language21                      |

| 2.3.1   | Structural SDL                                          |

| 2.3.2   | Behavioral SDL                                      | 24 |

|---------|-----------------------------------------------------|----|

| 2.4 M   | ISC to SDL Methodology                              | 20 |

| STEPW   | ISE REFINEMENT OF MESSAGE SEQUENCE CHARTS           | 29 |

| 3.1 In  | ntroduction                                         | 29 |

| 3.2 D   | escribing Use Cases with MSC                        | 30 |

| 3.2.1   | Basic MSC Use Case                                  | 31 |

| 3.2.2   | Using High-Level MSC                                | 31 |

| 3.3 C   | onformance Relation for MSCs                        | 35 |

| 3.3.1   | bMSC                                                | 35 |

| 3.3.2   | HMSC                                                | 39 |

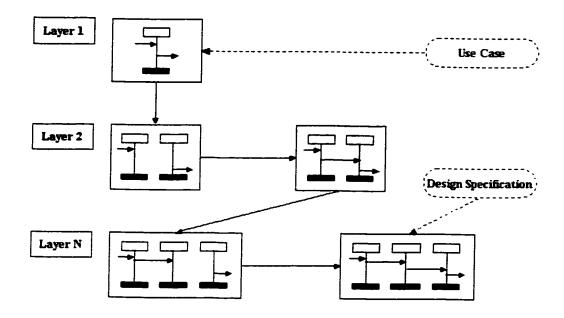

| 3.4 Fr  | om Use Cases to Design Specification                | 40 |

| 3.4.1   | Stepwise Refinement of bMSCs                        | 40 |

| 3.4.1   | .1 Vertical Refinement                              | 41 |

| 3.4.1   | .2 Horizontal Refinement                            | 42 |

| 3.4.1   | .3 Basic MSC Refinement Methodology                 | 43 |

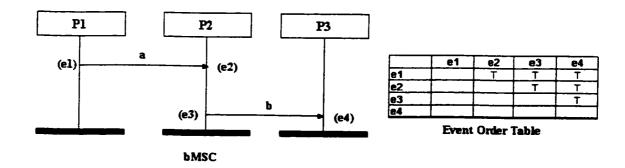

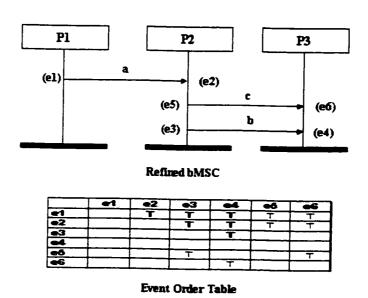

| 3.4.2   | Event Order Tables (EOT)                            | 45 |

| 3.4.3   | Stepwise Refinement of HMSCs                        | 47 |

| 3.5 Ap  | oplication                                          | 50 |

| UML TO  | SDL                                                 | 55 |

| 4.1 Int | troduction                                          | 55 |

| 1.2 Dis | stributed System Architecture Description Using UML | 56 |

| 4.2.1   | Class Diagram                                       |    |

| 4.2.1.  | 1 Subsystems                                        | 57 |

| 4.2.1.  | 2 Communication Between Classes                     | 58 |

| 4.2.1.  | 3 Communication Between Subsystems                  | 59 |

| 4.:          | 2.1.4 Communication with the Environment        | 62 |

|--------------|-------------------------------------------------|----|

| 4.2.2        | Object Diagrams                                 | 62 |

| 4.:          | 2.2.1 Internal Structure Diagrams               | 63 |

| 4.2          | 2.2.2 Interconnection Diagrams                  | 63 |

| 4.3          | From UML to SDL                                 | 64 |

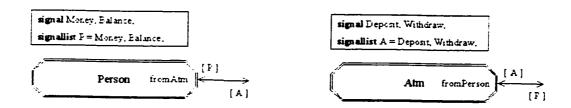

| 4.3.1        | SDL Channel Description                         | 64 |

| 4.3          | 3.1.1 Type and Implementation Class Stereotypes | 64 |

| 4.3          | 3.1.2 The Interface Stereotype                  | 65 |

| 4.3          | 3.1.3 Abstract Classes                          | 65 |

| 4.3.2        | Translation of UML Architectures into SDL       | 66 |

| 4.3          | 3.2.1 Class Diagrams                            | 66 |

| 4.3          | 3.2.2 Additional Concepts                       | 71 |

| 4.3          | 3.2.3 Object Diagrams                           | 73 |

| 4.3          | 3.2.4 Summary of Translations                   | 75 |

| <b>4.4</b> 1 | Related Work                                    | 76 |

| 4.5          | Automatic Teller Machine Example                | 77 |

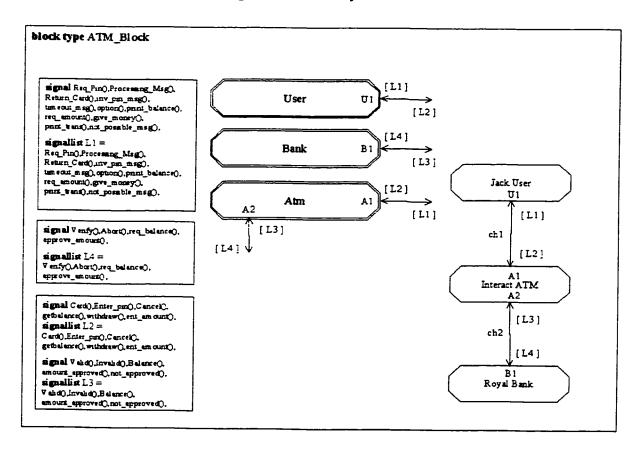

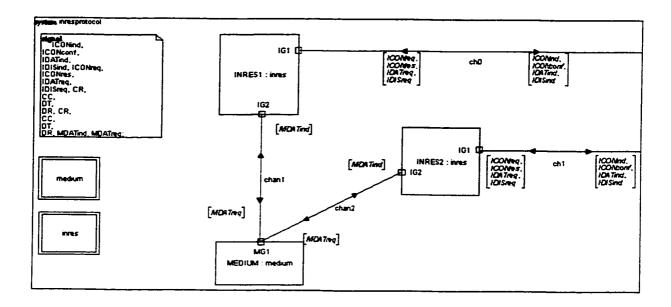

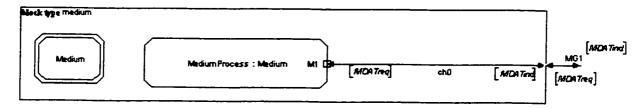

| 4.6 ]        | Inres Protocol Example                          | 79 |

| TOOL         | AND APPLICATION                                 | 82 |

| 5.1          | Overview                                        | 82 |

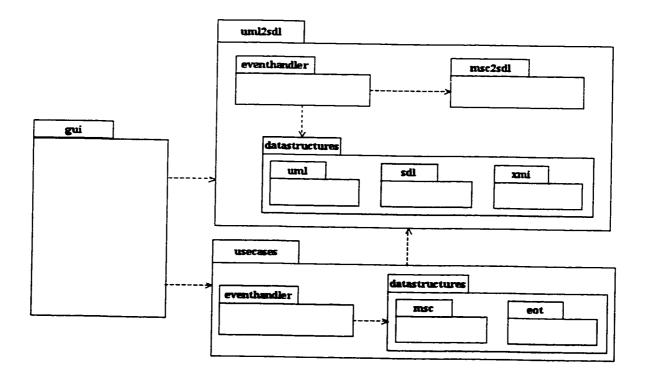

| 5.2 U        | UML to SDL Translation                          | 83 |

| 5.3 S        | Stepwise Refinement of MSCs                     | 84 |

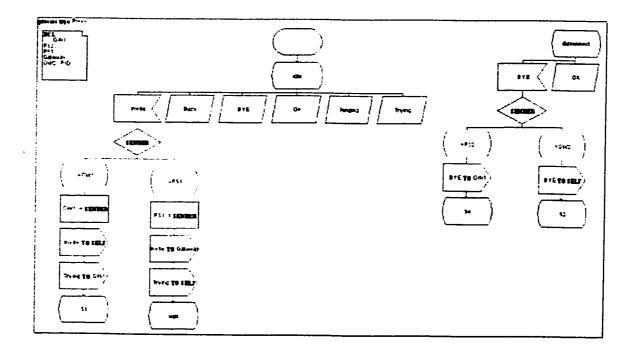

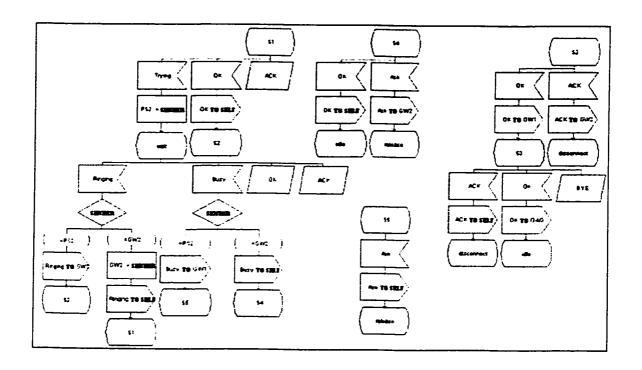

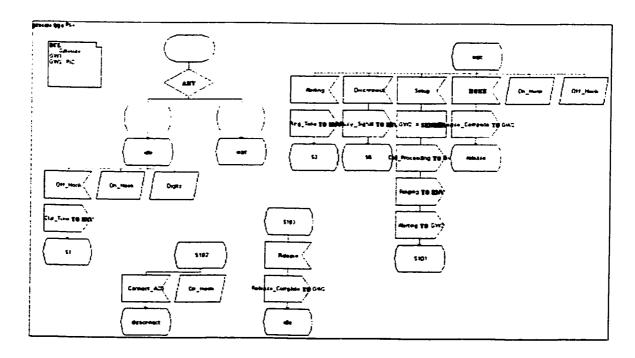

| 5.4 S        | SIP Example                                     | 85 |

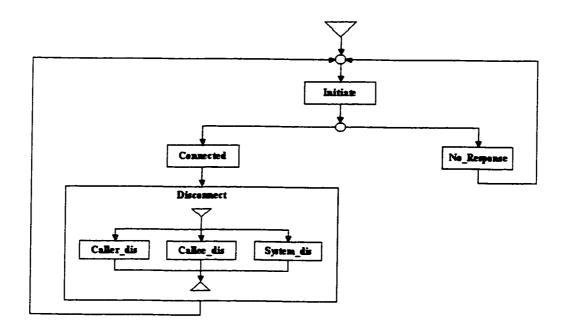

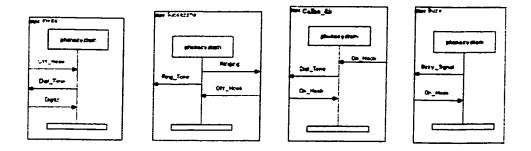

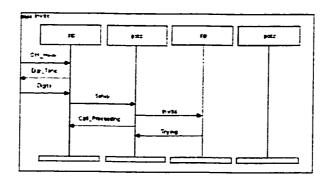

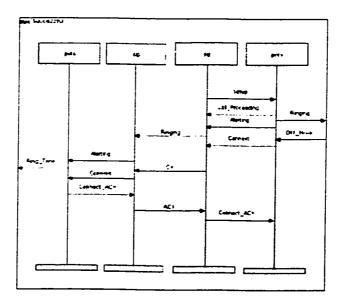

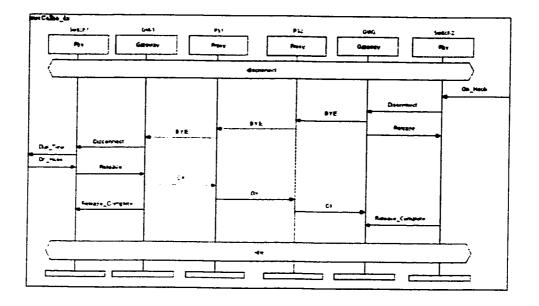

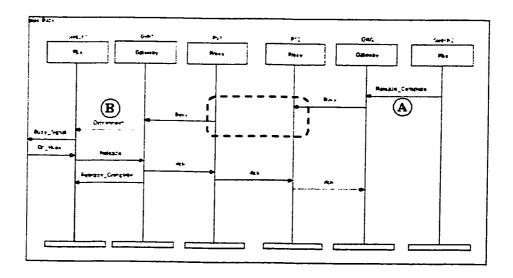

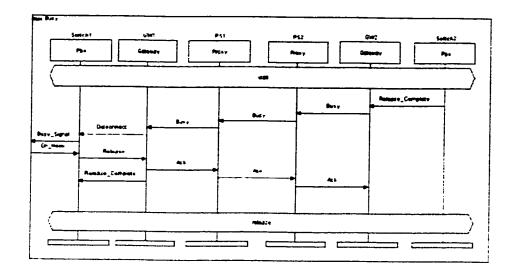

| 5.4.1        | MSC Use Cases                                   | 85 |

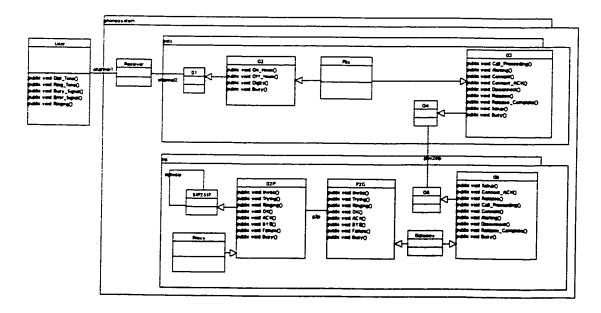

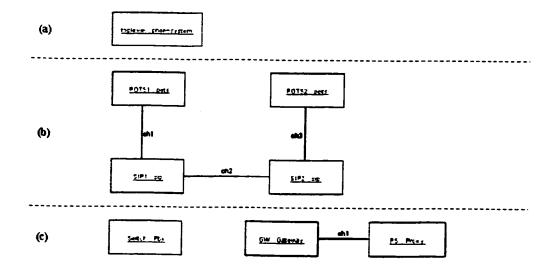

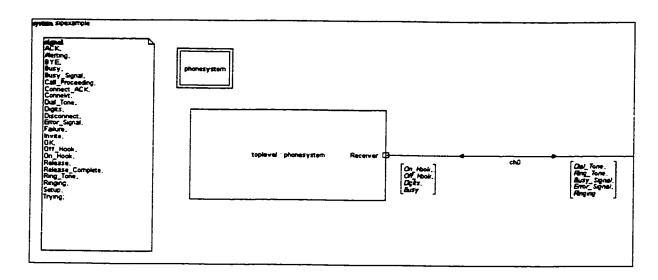

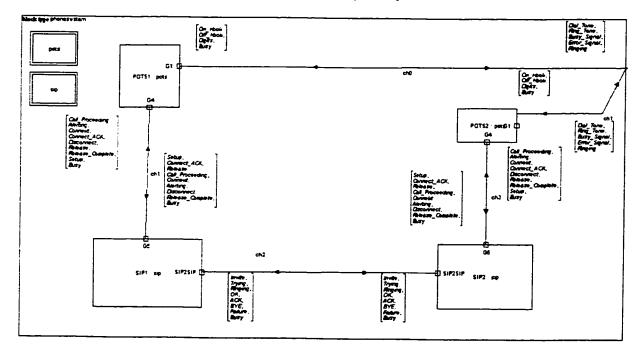

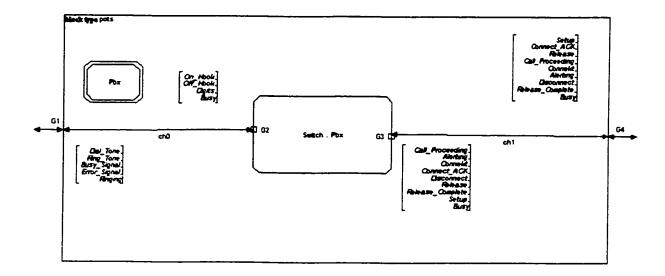

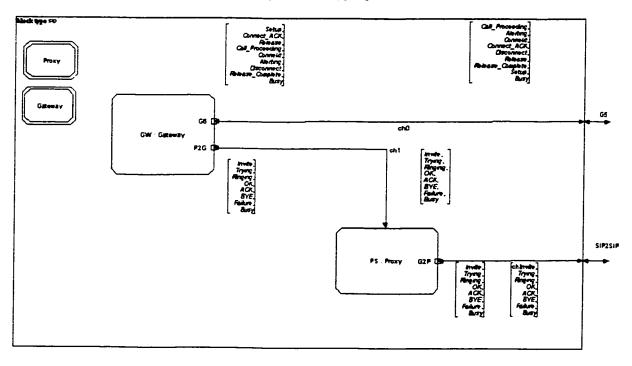

| 5.4.2        | Architecture Specification                      | 87 |

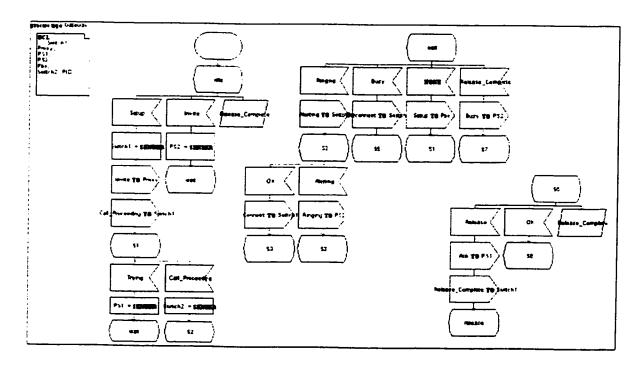

| 5.4.3        | Refinement of Use Cases into Design MSCs        | 91 |

| 5.4.4        | Generated SDL Behavior                          | 95 |

| CON | CLUSION                      | .99         |

|-----|------------------------------|-------------|

| 6.1 | Contributions of this Thesis | . <b>99</b> |

| 6.2 | Future Work                  | . 99        |

# **List of Figures**

| Figure 1.1: Waterfall Lifecycle Model                      |

|------------------------------------------------------------|

| Figure 1.2: The overall process                            |

| Figure 2.1: Representing a class in UML.                   |

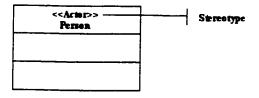

| Figure 2.2: UML stereotypes                                |

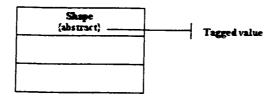

| Figure 2.3: UML tagged values                              |

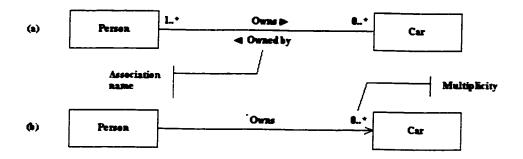

| Figure 2.4: Representing associations in UML               |

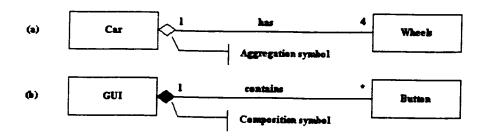

| Figure 2.5: Aggregation and composition in UML             |

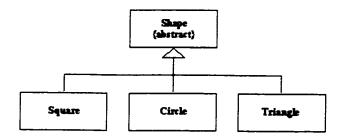

| Figure 2.6: Generalization in UML.                         |

| Figure 2.7: Realization relationship in UML                |

| Figure 2.8: Interfaces in UML                              |

| Figure 2.9: Using an interface in UML                      |

| Figure 2.10: Packages in UML                               |

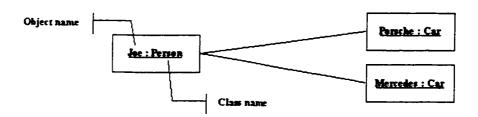

| Figure 2.11: UML Object Diagram                            |

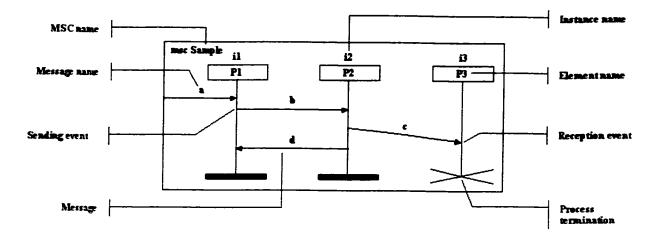

| Figure 2.12: A basic MSC.                                  |

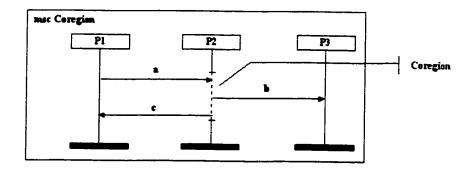

| Figure 2.13: A coregion example                            |

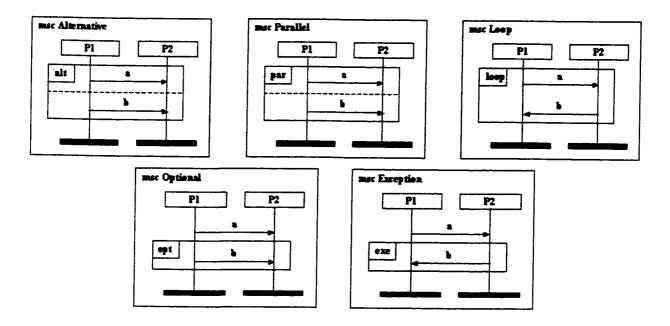

| Figure 2.14: MSC inline expressions                        |

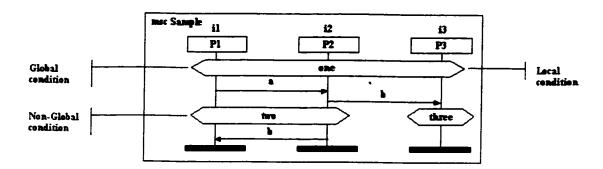

| Figure 2.15: MSC conditions                                |

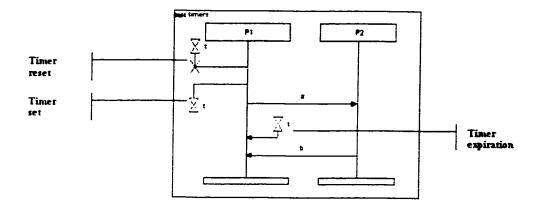

| Figure 2.16: MSC timers                                    |

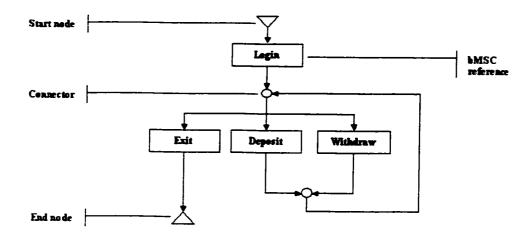

| Figure 2.17: An HMSC example                               |

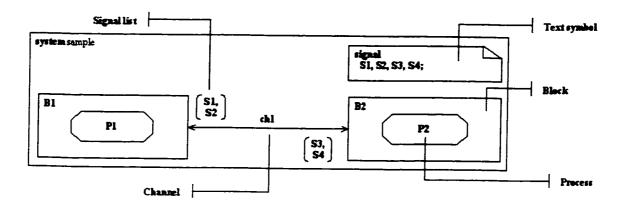

| Figure 2.18: Old style SDL specification                   |

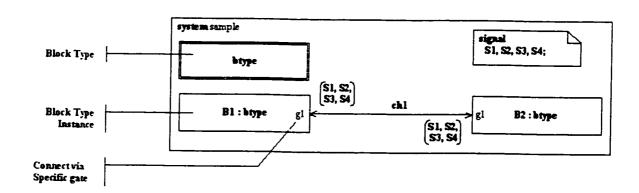

| Figure 2.19: SDL specification using types                 |

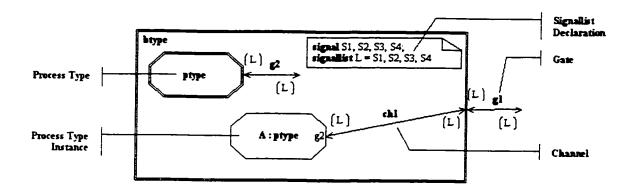

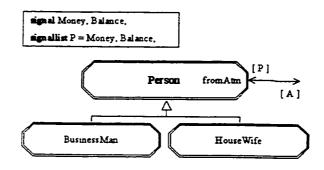

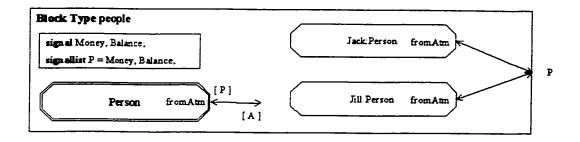

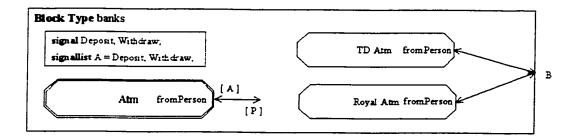

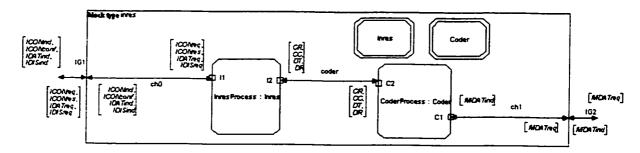

| Figure 2.20: Block Type specification                      |

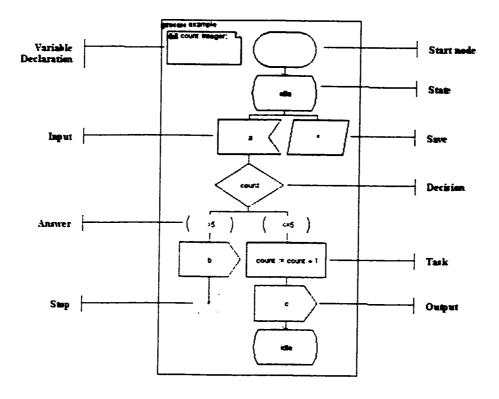

| Figure 2.21: An example of an SDL behavioral specification |

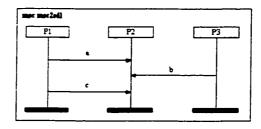

| Figure 2.22: bMSC describing desired behavior.             |

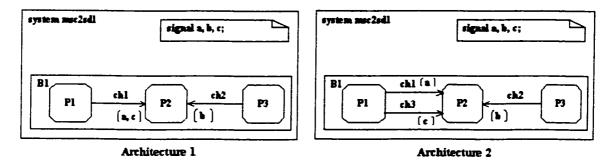

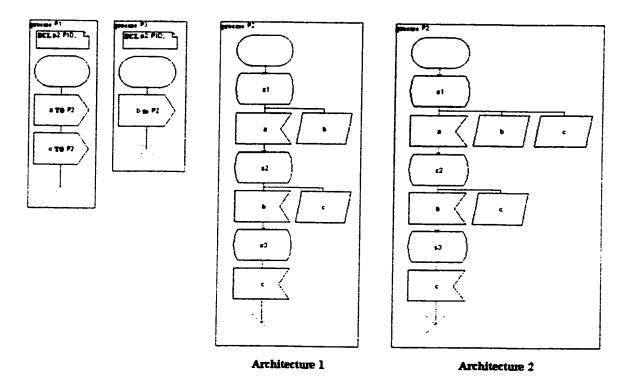

| Figure 2.23: SDL architectutures                           |

| Figure 2.24: Resulting SDL behavior                        |

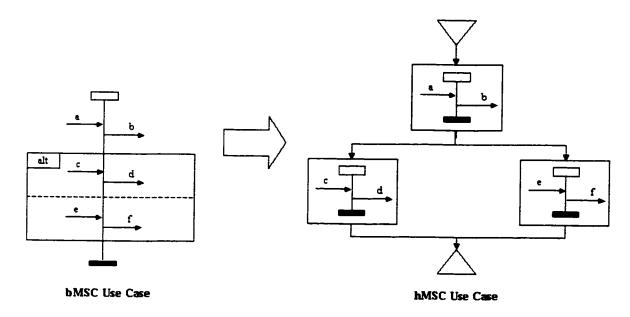

| Figure 3.1: A bMSC use case                                |

| Figure 3.2: A HMSC use case                                |

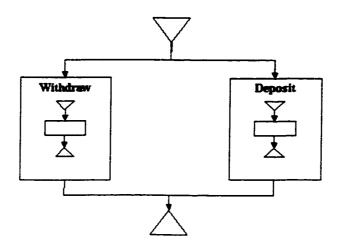

| Figure 3.3: Multiple use cases in one HMSC.                |

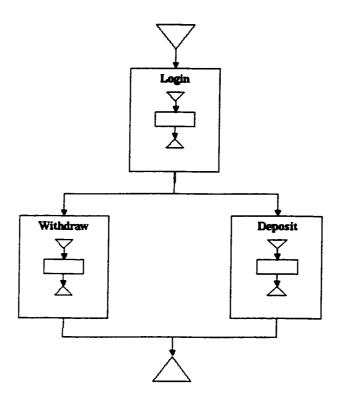

| Figure 3.4: Extracting redundant behavior from use cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 34 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

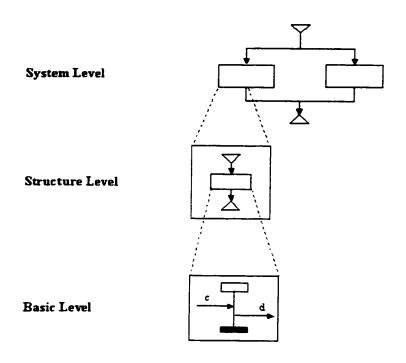

| Figure 3.5: Three levels of abstraction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 35 |

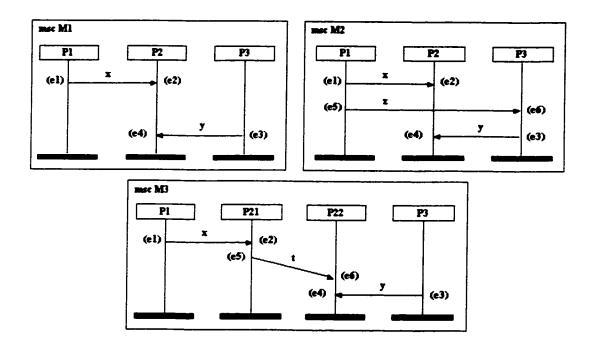

| Figure 3.6: Examples of conformance between bMSCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38 |

| Figure 3.7: Example of non-conformance between bMSCs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38 |

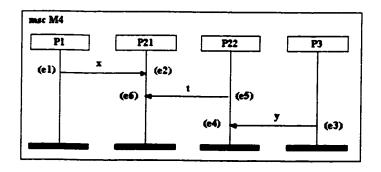

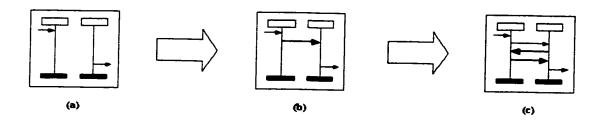

| Figure 3.8: Overall refinement process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 41 |

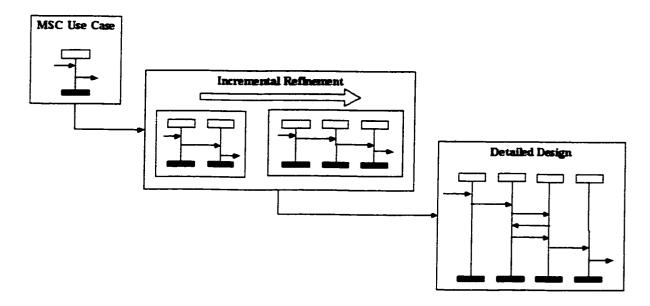

| Figure 3.9: System hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42   |

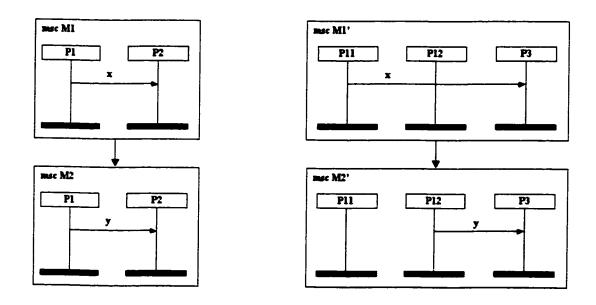

| Figure 3.10: Horizontal refinement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43   |

| Figure 3.11: Overall refinement methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44   |

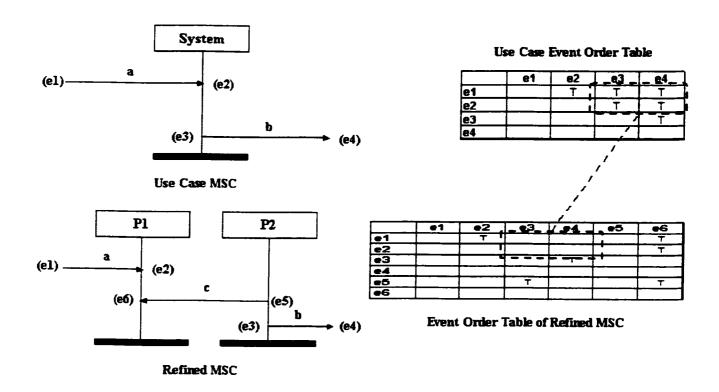

| Figure 3.12: A bMSC and its EOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45   |

| Figure 3.13: Example of conformance using EOTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46   |

| Figure 3.14: Example of non-conformance using EOTs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47   |

| Figure 3.15. Non-conformance between HMSCs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48   |

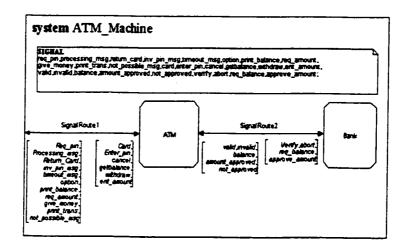

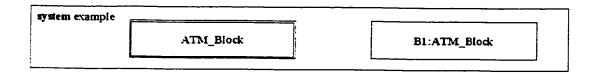

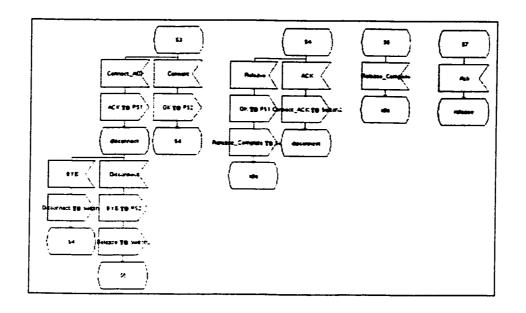

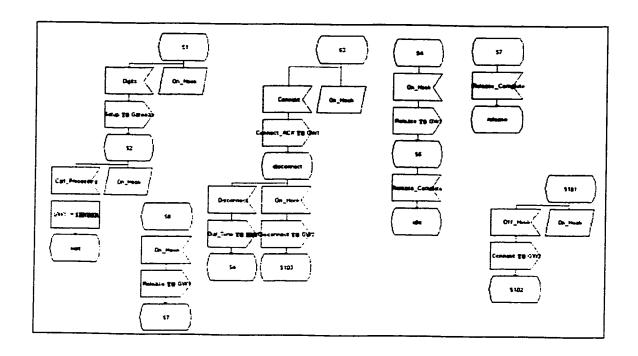

| Figure 3.16: ATM_Machine system architecture in SDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50   |

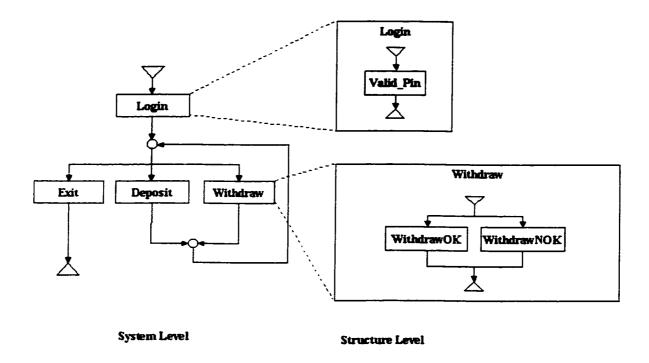

| Figure 3.17: System and structure level HMSCs for the ATM example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51   |

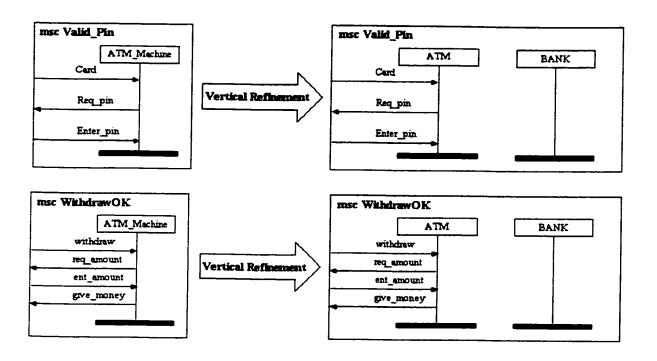

| Figure 3.18: Vertical refinement of ATM use cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52   |

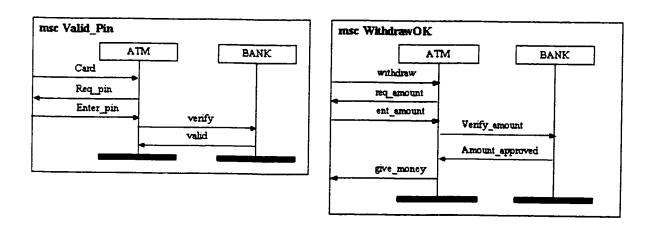

| Figure 3.19: Horizontal refinements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52   |

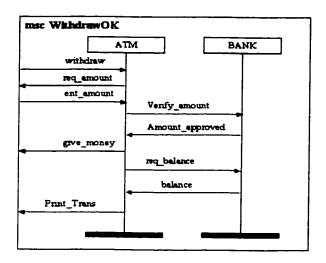

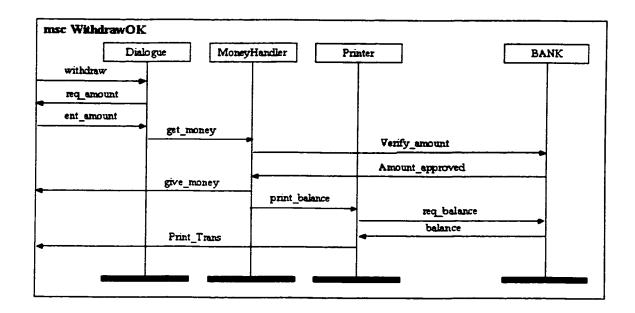

| Figure 3.20: Another horizontal refinement of WithdrawOK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53   |

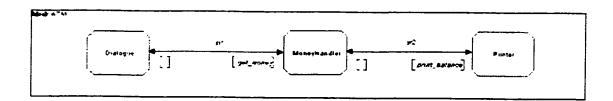

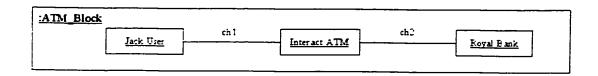

| Figure 3.21: Inside the ATM Block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53   |

| Figure 3.22: Vertical Refinement of WithdrawOK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54   |

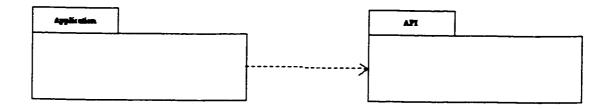

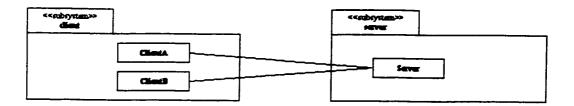

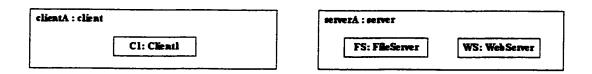

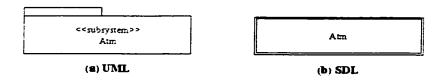

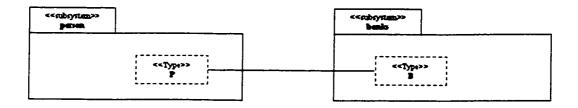

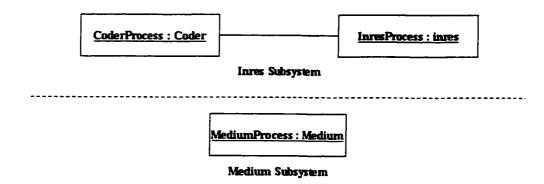

| Figure 4.1: Subsystem representation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

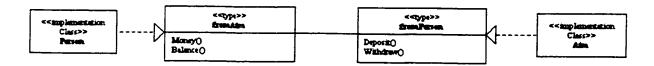

| Figure 4.2: Communication through simple associations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58   |

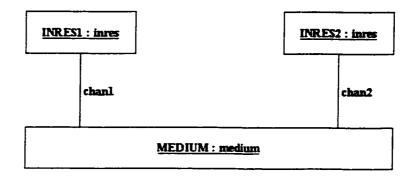

| Figure 4.3: Communication using two channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

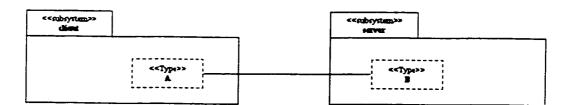

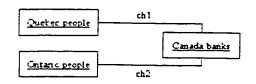

| Figure 4.4: Inter-subsystem communication using normal associations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

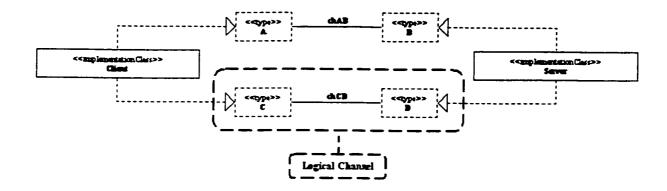

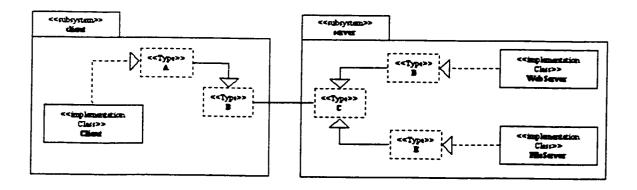

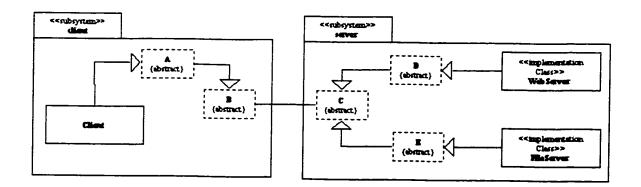

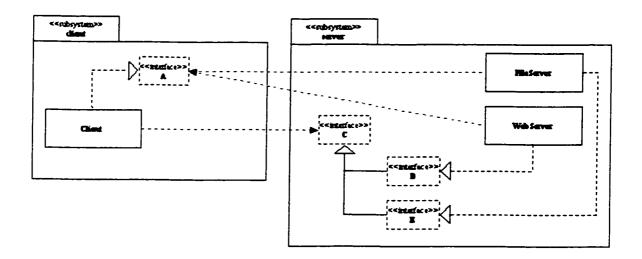

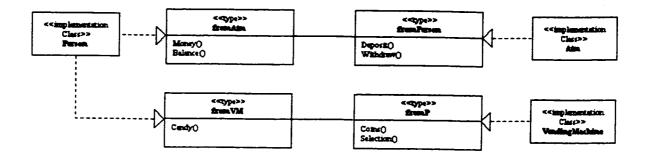

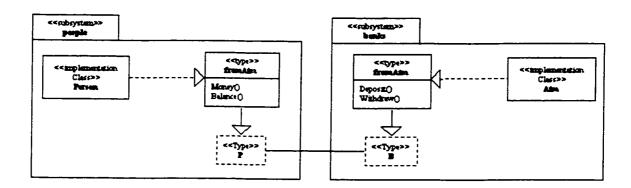

| Figure 4.5: Inter-subsystem communication using type classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

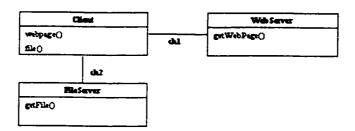

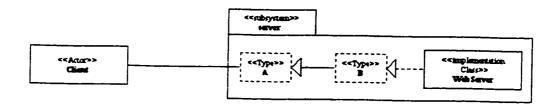

| Figure 4.6: Client/Server class diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

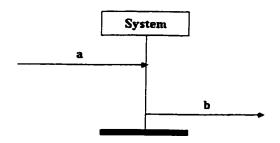

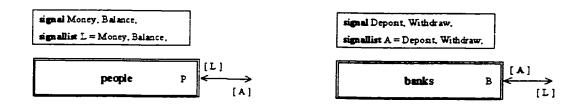

| Figure 4.7: Communication with the environment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Figure 4.8: Internal structure of Client/Server example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Figure 4.9: Subsystem interconnections for Client/Server example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

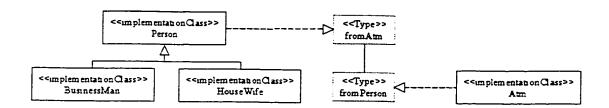

| Figure 4.10: Using abstract classes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Figure 4.11: Client/Server system using unidirectional channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Figure 410 Total State S | 57   |

| Figure 4.13: Communication between components                    | 68   |

|------------------------------------------------------------------|------|

| Figure 4.14: Adding a new class.                                 | 69   |

| Figure 4.15: Process types derived from UML                      | 69   |

| Figure 4.16: Communication between subsystems.                   | 70   |

| Figure 4.17: Classes communicating between subsystems            | 70   |

| Figure 4.18: Block types derived from UML.                       | . 71 |

| Figure 4.19: UML inheritance.                                    | . 71 |

| Figure 4.20: SDL inheritance.                                    | . 72 |

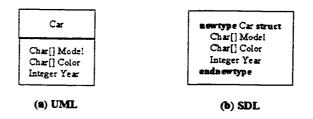

| Figure 4.21: SDL newtype.                                        | . 72 |

| Figure 4.22: Subsystem object diagrams.                          | . 73 |

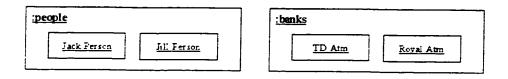

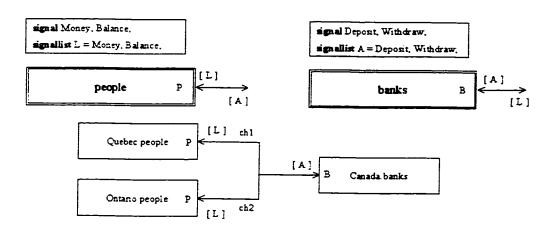

| Figure 4.23: Block Type People.                                  | . 74 |

| Figure 4.24: Block Type Banks.                                   | . 74 |

| Figure 4.25: Interconnecting subsystem instances                 | . 75 |

| Figure 4.26: SDL system representation.                          | . 75 |

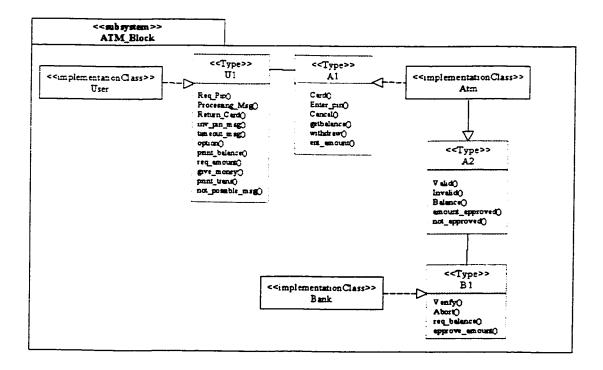

| Figure 4.27: ATM_Block Subsystem                                 | . 77 |

| Figure 4.28: ATM_Block Object Diagram.                           | . 78 |

| Figure 4.29: SDL Representation.                                 | 78   |