**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

800-521-0600

**UMI**®

## A RESONANT AC/DC CONVERTER FOR HIGH FREQUENCY POWER DISTRIBUTION SYSTEMS

#### FARIBORZ MUSAYI

A Thesis

In

The Department

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada.

October 2001

©Fariborz Musavi, 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rétérance

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-68444-X

#### **ABSTRACT**

## A RESONANT AC/DC CONVERTER FOR HIGH FREQUENCY POWER DISTRIBUTION SYSTEMS

#### FARIBORZ MUSAVI

A Resonant AC/DC Converter for High Frequency Power Distribution Systems is presented in this thesis. The proposed converter employs a resonant network consisting of a few passive components. With this resonant network, the converter can attain close to unity power factor and very small total harmonic distortion under all load conditions. The operating principle of the circuit is demonstrated, and the steady state analysis is performed including the effect of leakage inductance. Based on the analysis, criteria for optimal design are given. Experimental and simulation results of a prototype converting the input AC voltage of 28 V rms at 1 MHz, to 1.6 Volt DC at 20 A are given to verify the proof of concept, and analytical work reported in this thesis.

#### **ACKNOWLEDGEMENT**

I would like to express my sincere gratitude to Dr. Praveen K. Jain for his encouragement, support and guidance during the course of this study. His ideas and suggestions were a source of guidance to me and without his timely help this research project would have taken a far longer time to finish. His support and encouragement is highly appreciated.

I would also like to especially thank Mr. Haibo Zhang of Cistel Technology, Ottawa for his invaluable help during the construction and testing phase of the designed prototype.

I want to thank all my friends and colleagues at the P. D. Ziogas Power Electronics Lab at Concordia University, for their friendship, their help, and for many valuable discussions and suggestions.

This work has been financially supported by the strategic grant from National Science and Engineering Research Council of Canada (NSERC).

Dedicated to my parents

## **TABLE OF CONTENTS**

| List of Figures                                                          | x   |

|--------------------------------------------------------------------------|-----|

| List of Tables                                                           | xiv |

| List of Acronyms                                                         | xv  |

| List of Principle Symbols                                                | xvi |

| Chapter 1 Introduction                                                   |     |

| 1.1 Introduction                                                         | 1   |

| 1.2 Power System Delivery of Computers                                   | 3   |

| 1.3 Advances in Computer Performance and Its Impacts on Power Processing | 4   |

| 1.3.1 Low Supply Voltage With Tighter Tolerance                          | 6   |

| 1.3.2 High Supply Current With Tight Slew Rate                           | 7   |

| 1.3.3 Large Load Transient                                               | 7   |

| 1.4 Overall Power Architecture                                           | 8   |

| 1.4.1 Low Voltage DC Distribution                                        | 8   |

| 1.4.2 High Voltage DC Distribution                                       | 10  |

| 1.4.3 High Frequency AC Power Distribution                               | 12  |

| 1.5 Thesis Objective                                                     | 15  |

| 1.6 Thesis Outline                                                       | 15  |

| Chapter 2 A Resonant AC/DC Converter For HF Distribution Systems         |     |

| 2.1 Introduction                                                         | 17  |

| 2.2 Circuit Description                                            | 19 |

|--------------------------------------------------------------------|----|

| 2.3 Steady State Analyses                                          | 20 |

| 2.3.1 Assumption and Some Constants for the Analysis               | 20 |

| 2.3.2 Operating Principle                                          | 21 |

| 2.3.3 Steady Sate Analysis of Each Interval                        | 23 |

| 2.4 Simulation Results                                             | 32 |

| 2.5 Conclusion                                                     | 38 |

|                                                                    |    |

| Chapter 3 Effect of Leakage Inductance                             |    |

| 3.1 Introduction                                                   | 40 |

| 3.2 Circuit Description                                            | 40 |

| 3.3 Steady State Analyses                                          | 41 |

| 3.3.1 Assumption and Some Constants for the Analysis               | 42 |

| 3.3.2 Operating Principle                                          | 43 |

| 3.3.3 Steady Sate Analysis                                         | 45 |

| 3.4 Simulation Results                                             | 55 |

| 3.5 Conclusion                                                     | 61 |

|                                                                    |    |

| Chapter 4 Dynamic Properties                                       |    |

| 4.1 Introduction                                                   | 62 |

| 4.2 Control of HF AC/DC Converter                                  | 63 |

| 4.2.1 Linearization of The Power Stage Using State-Space Averaging | 64 |

| 4.2.2 Compensation of The Voltage Loop     |     |  |

|--------------------------------------------|-----|--|

| 4.3 Simulation Results                     |     |  |

| 4.4 Step Change Responses                  | 77  |  |

| 4.5 Conclusion                             | 80  |  |

|                                            |     |  |

| Chapter 5 Prototyping and Design           |     |  |

| 5.1 Introduction.                          | 81  |  |

| 5.2 Design of The Proposed Converter       | 81  |  |

| 5.2.1 Design Objectives and Specifications | 82  |  |

| 5.2.2 Design Procedure and Example         | 83  |  |

| 5.2.2.1 Design of the Power Circuit        | 83  |  |

| 5.2.2.2 Design of the Control Circuit      | 88  |  |

| 5.3 Simulation and Experimental Results    | 89  |  |

| 5.4 Conclusion                             | 99  |  |

|                                            |     |  |

| Chapter 6 Summary and Conclusion           |     |  |

| 6.1 Summary                                | 100 |  |

| 6.2 Conclusion                             | 101 |  |

| 6.3 Suggestion for Future Work             | 102 |  |

|                                            |     |  |

| References                                 | 103 |  |

| Appendix1                                  | 106 |  |

| Appendix2 | 113 |

|-----------|-----|

| Appendix3 | 121 |

### LIST OF FIGURES

| Figure 1-1 CPU Power Delivery System                                                      | 3    |

|-------------------------------------------------------------------------------------------|------|

| Figure 1-2 Internal Clock Frequency                                                       | 4    |

| Figure 1-3 Number of Transistors                                                          | 5    |

| Figure 1-4 Typical Processor Supply Voltage Waveform during the Load Transition           | 8    |

| Figure 1-5 Low Voltage DC Power Distribution                                              | 9    |

| Figure 1-6 High Voltage DC Power Distribution                                             | 11   |

| Figure 1-7 High Frequency AC Power Distribution                                           | 12   |

| Figure 1-8 (a)High Voltage DC Distribution System (b)HF AC Distribution System            | 13   |

| Figure 2-1 A Generic Diagram of AC/DC Converter                                           | 18   |

| Figure 2-2 The Proposed HF AC/DC Converter Topology                                       | 19   |

| Figure 2-3 Key Waveforms of the Proposed Converter Topology                               | 22   |

| Figure 2-4 The n <sup>th</sup> Harmonics Equivalent Circuit of the Proposed Topology      | 23   |

| Figure 2-5 (a) and (b) The n <sup>th</sup> Harmonics Equivalent Circuit Considering Separ | ated |

| Voltage Sources                                                                           | 23   |

| Figure 2-6 Control Angle versus Resonant Angle                                            | 28   |

| Figure 2-7 Output Voltage versus Control Angle                                            | 29   |

| Figure 2-8 Total Harmonics Distortion versus Control Angle                                | 30   |

| Figure 2-9 The Harmonics % of Input Current versus Control Angle                          | 30   |

| Figure 2-10 Power Factor versus Control Angle                                             | 31   |

|                                                                                           |      |

| Figure 2-11 The Input Voltage and Current, and Output Voltage of Converter                | 33   |

| Figure 2-12 The Voltages in Primary and Secondary of the Transformer                        | 33   |

|---------------------------------------------------------------------------------------------|------|

| Figure 2-13 Current in the Switches and Primary of the Transformer                          | 34   |

| Figure 2-14 Current and Gating of SR <sub>1</sub> , Current in Output Filter and Load       | 34   |

| Figure 2-15 The Input Voltage and Current, and Output Voltage of Converter                  | 36   |

| Figure 2-16 The Voltages in Primary and Secondary of the Transformer                        | 36   |

| Figure 2-17 Current in the Switches and Primary of the Transformer                          | 37   |

| Figure 2-18 Current and Voltage across Synchronous Rectifier SR <sub>1</sub>                | 37   |

| Figure 2-19 Current in Resonant Series Branch, Gating of Main Switches and Vol-             | tage |

| across Resonant Inductor                                                                    | 38   |

| Figure 3-1 The Equivalent Circuit of the Proposed Topology including Leak                   | kage |

| Inductance                                                                                  | 41   |

| Figure 3-2 Key Waveforms of the Proposed Converter Topology                                 | 44   |

| Figure 3-3 The n <sup>th</sup> Harmonics Equivalent Circuit considering Leakage Inductance. | 45   |

| Figure 3-4 The n <sup>th</sup> Harmonics Equivalent Circuit considering Separated Sources   | 45   |

| Figure 3-5 Output Voltage versus Control Angle                                              | 52   |

| Figure 3-6 Total Harmonics Distortion versus Control Angle                                  | 53   |

| Figure 3-7 The Harmonics % of Input Current versus Control Angle                            | 54   |

| Figure 3-8 Power Factor versus Control Angle                                                | 55   |

| Figure 3-9 The Input Voltage and Current, and Output Voltage of Converter                   | 56   |

| Figure 3-10 Current in the Switches and Primary of the Transformer and reso                 | nant |

| Inductor                                                                                    | 56   |

| Figure 3-11 Voltages in Primary and Secondary of the Transformer                            | 57   |

| Figure 3-12 Gating, Current and Voltage across Synchronous Rectifier SR <sub>1</sub> | 57    |

|--------------------------------------------------------------------------------------|-------|

| Figure 3-13 Gating of the Main Switches. Voltage across Resonant Inductor            | and   |

| Capacitor                                                                            | 58    |

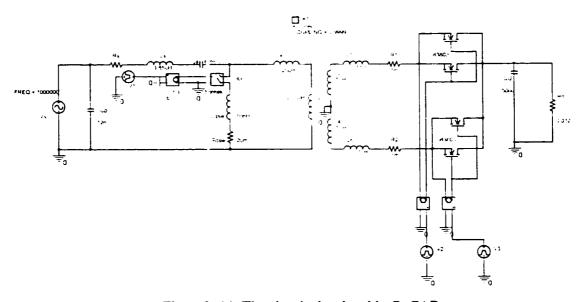

| Figure 3-14 The Simulated Circuit in OrCAD                                           | 58    |

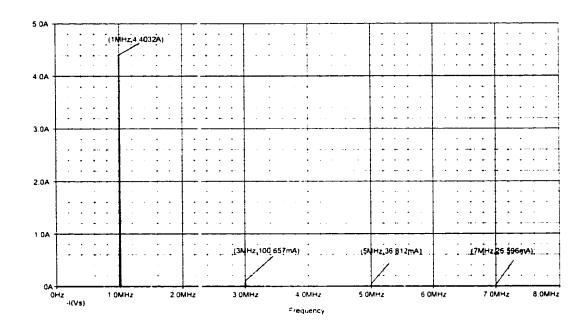

| Figure 3-15 Harmonics due to Input Current of Converter                              | 59    |

| Figure 4-1 The Simplified Proposed Topology                                          | 62    |

| Figure 4-2 Voltage Regulation Feedback Control System                                | 63    |

| Figure 4-3 The Circuit States (a)The Switches are on (b) The Switches are off        | 64    |

| Figure 4-4 The Assumed Current Source Waveform                                       | 69    |

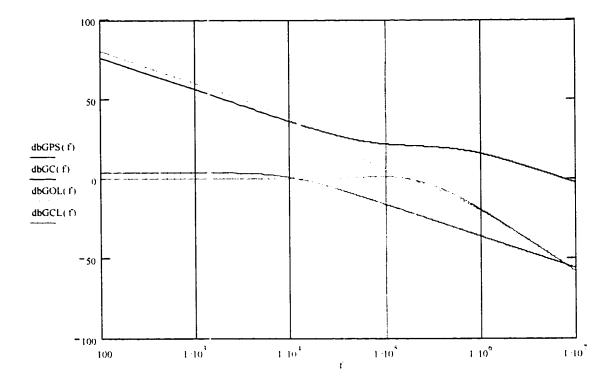

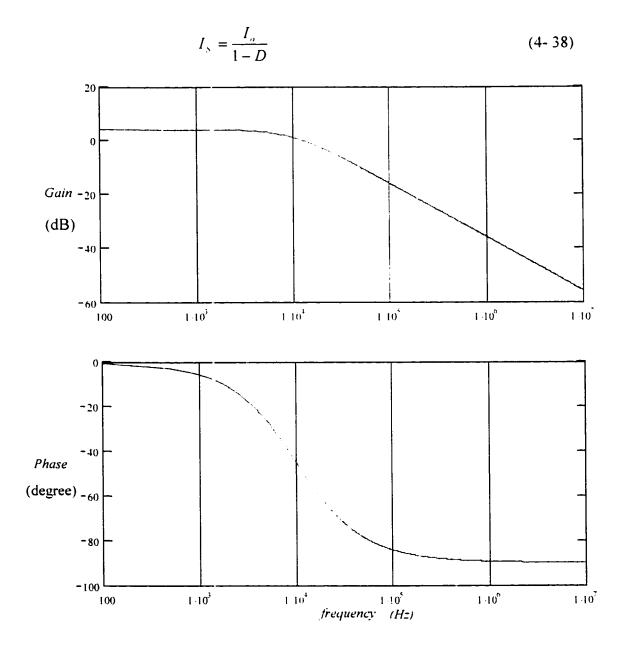

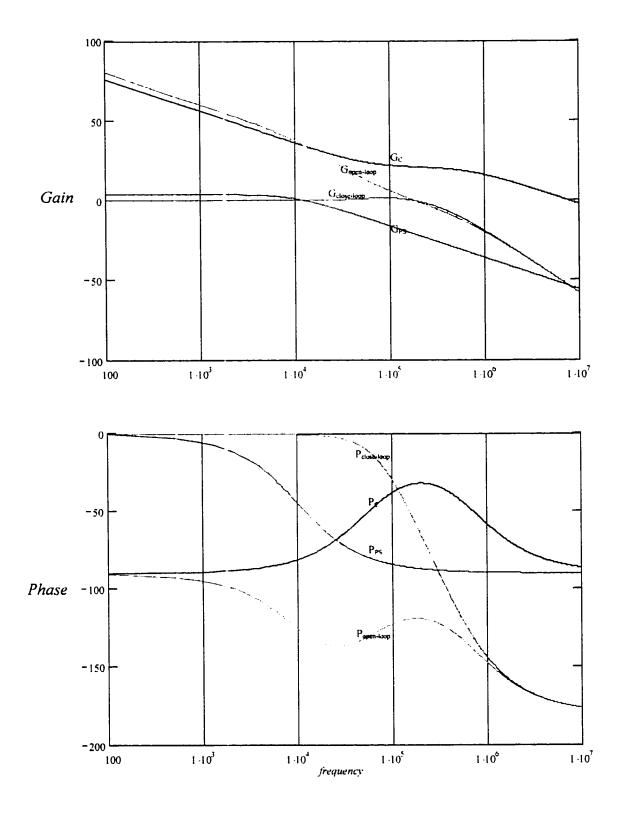

| Figure 4-5 Gain and Phase Characteristic of Power Stage                              | 70    |

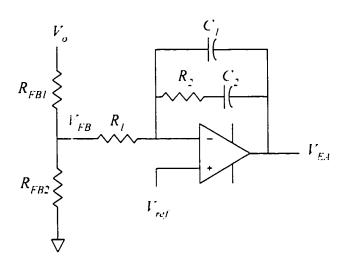

| Figure 4-6 Type-2 Compensation Around the error Voltage Amplifier                    | 73    |

| Figure 4-7 Gain and Phase Characteristic of Controller                               | 74    |

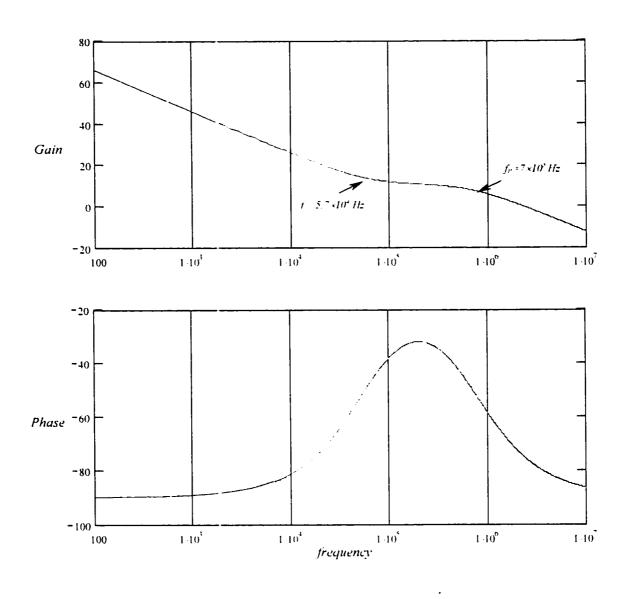

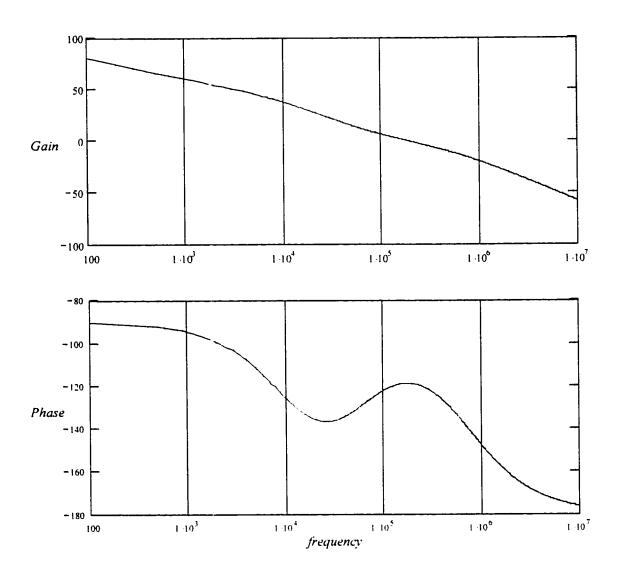

| Figure 4-8 Gain and Phase Characteristic of Open Loop                                | 75    |

| Figure 4-9 Gain and Phase Characteristic of all Transfer Functions                   | 76    |

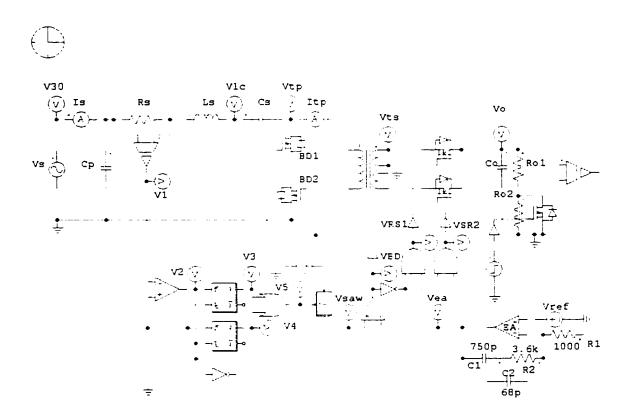

| Figure 4-10 Circuit Schematic for Simulation using PSIM                              | 77    |

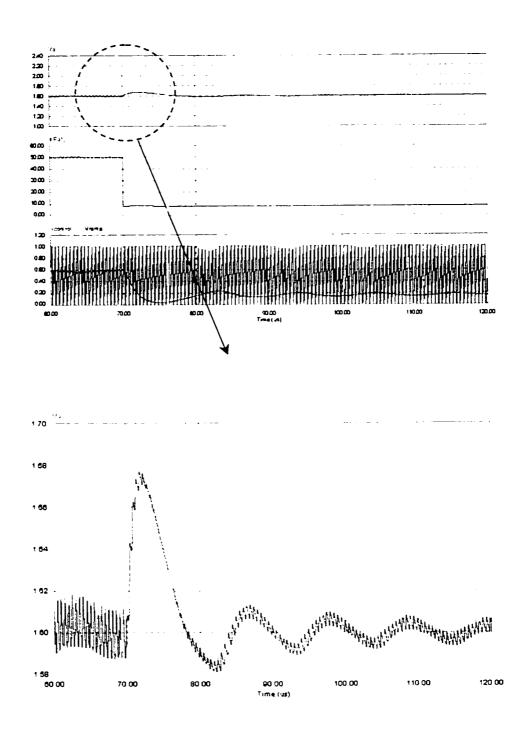

| Figure 4-11 Output Current step down from 50A to 8A with detailed view of Ou         | ıtput |

| Voltage and control Signal                                                           | 78    |

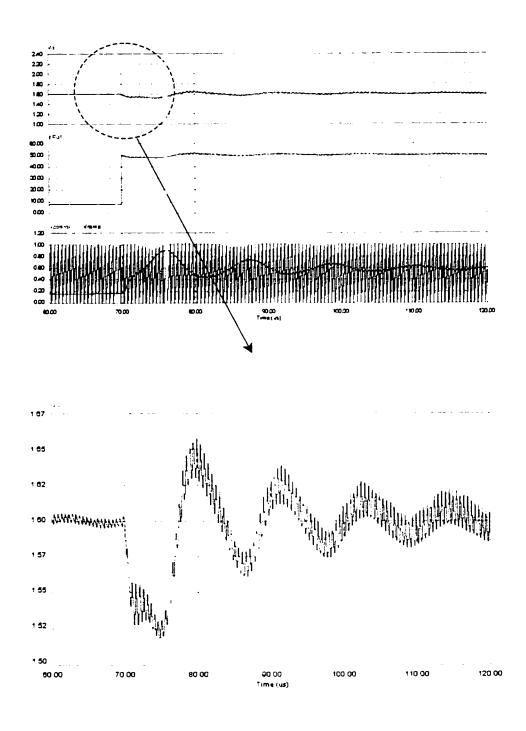

| Figure 4-12 Output Current steps up from 8A to 50A with detailed view of Ou          | ıtput |

| Voltage and control Signal                                                           | 79    |

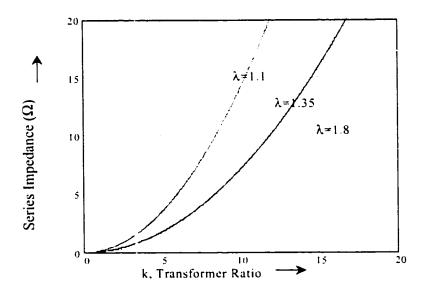

| Figure 5-1 Transformer Ratio versus Series Impedance                                 | 84    |

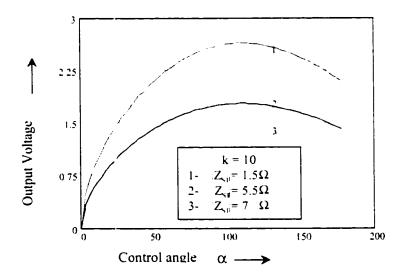

| Figure 5-2 Output Voltage versus Control Angle                                       | 84    |

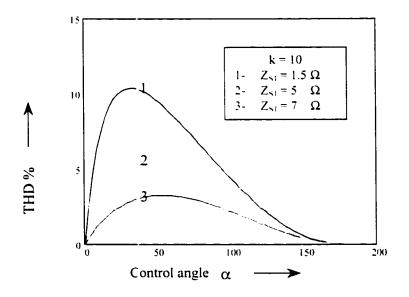

| Figure 5-3 THD versus Control Angle                                                  | 85    |

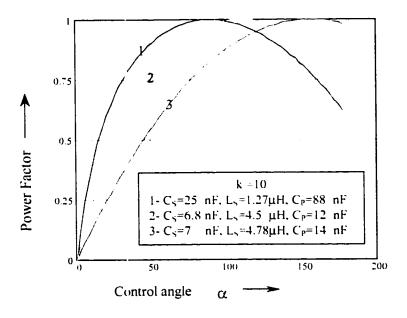

| Figure 5-4 Power Factor versus Control Angle                                        | 86    |

|-------------------------------------------------------------------------------------|-------|

| Figure 5-5 Design of Control Loop for CPU VRM                                       | 89    |

| Figure 5-6 Input Voltage and Current, and Output Voltage of Converter               | 90    |

| Figure 5-7 Gating and Current in Main Switches and Primary of the Transformer       | and   |

| resonant Inductor                                                                   | 91    |

| Figure 5-8 Voltages in Primary and Secondary of the Transformer                     | 91    |

| Figure 5-9 Gating, Current and Voltage across Synchronous Rectifier SR <sub>1</sub> | 92    |

| Figure 5-10 Current and Voltage across Resonant Inductor and Capacitor              | 92    |

| Figure 5-11 Current and Voltage in Different Branches and Devices when both M       | √ain  |

| Switches are Fully Conducting                                                       | 93    |

| Figure 5-12 Current and Voltage in Different Branches and Devices when both M       | √ain  |

| Switches are Fully Off                                                              | 94    |

| Figure 5-13 Current and Voltage in Different Branches and Devices when both N       | Main  |

| Switches are Fully Off                                                              | 95    |

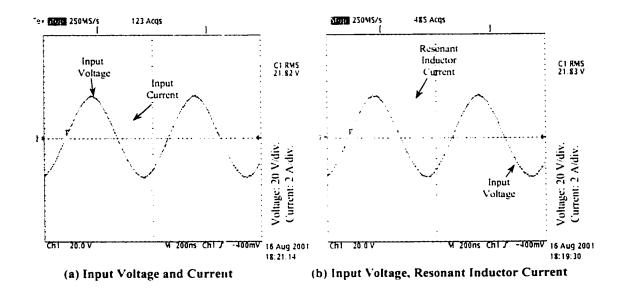

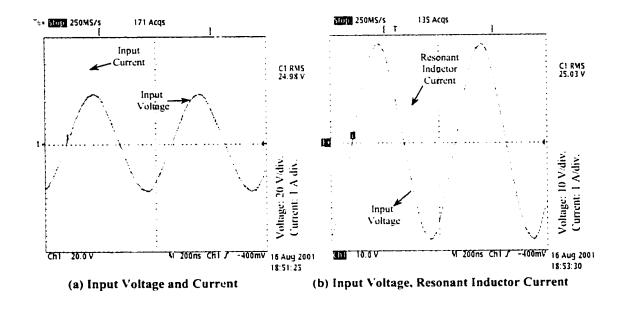

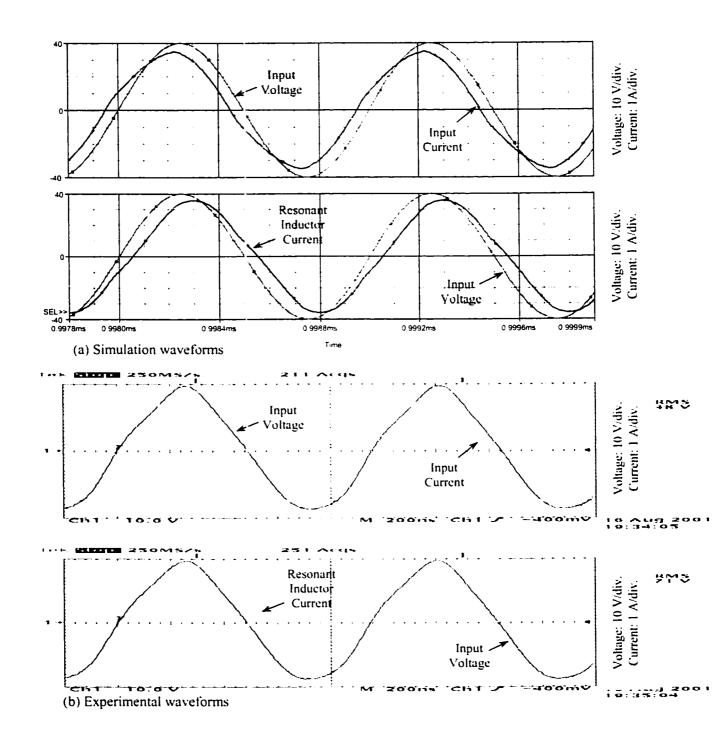

| Figure 5-14 Input Voltage and Current, Resonant Inductor Current (a) Simulation R   | esult |

| (b) Experimental Results                                                            | 96    |

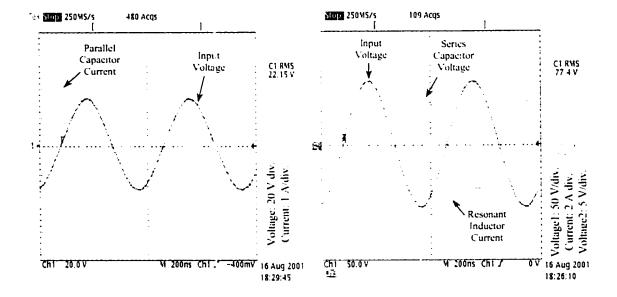

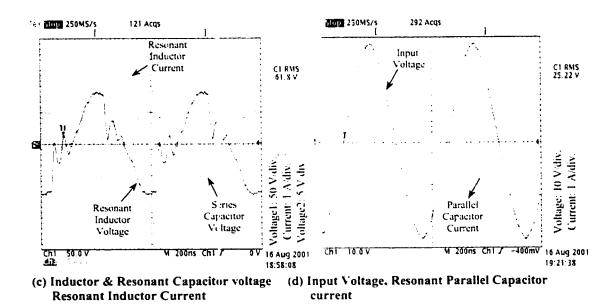

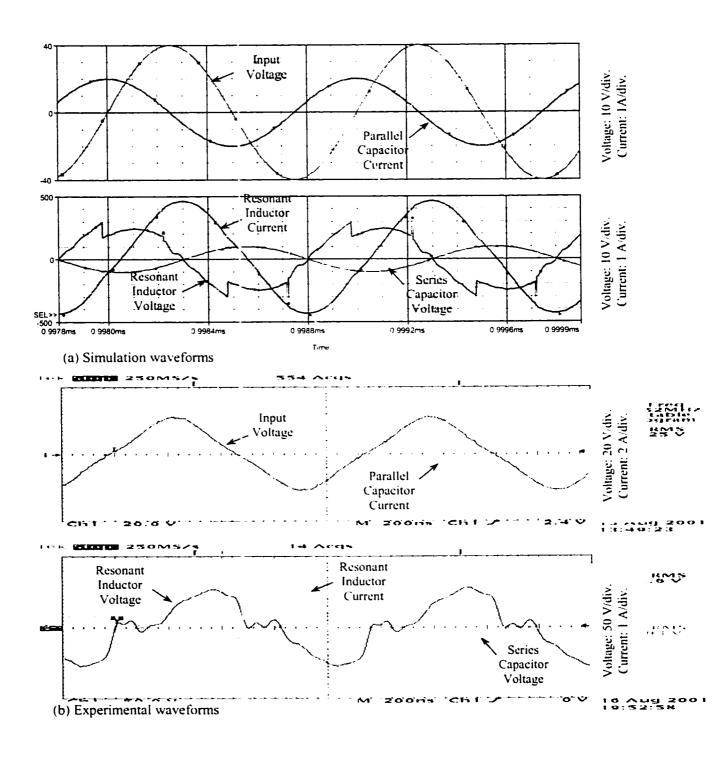

| Figure 5-15 Input Voltage, Resonant Parallel Capacitor and Inductor Current and Vo  | ltage |

| (a) Simulation Results (b) Experimental Results                                     | 97    |

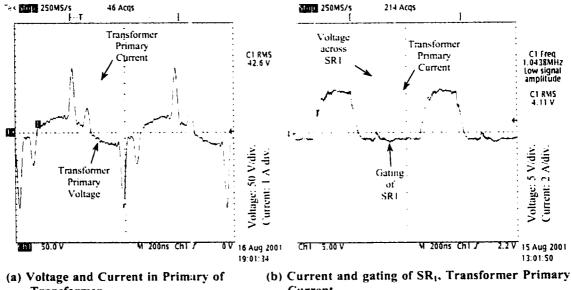

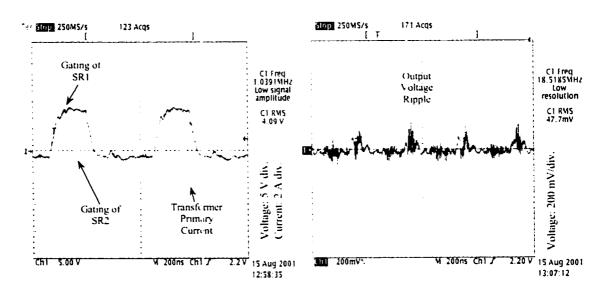

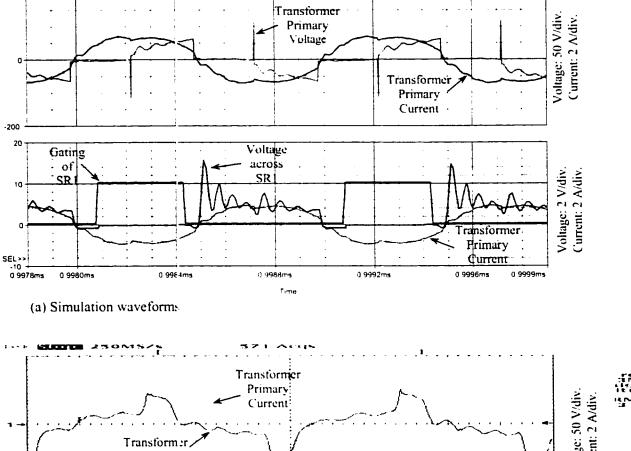

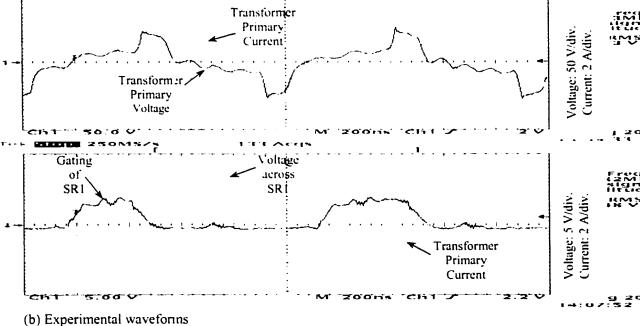

| Figure 5-16 Voltage and Current in Primary of Transformer. Current and Voltage of   | SR    |

| (a) Simulation (b) Experimental Results                                             | 98    |

### LIST OF TABLES

| Table 1-1 The Specification of Future VRM                                            | 2  |

|--------------------------------------------------------------------------------------|----|

| Table 1-2 Advances in Processor Speed and its Impact on Power Supply                 | 5  |

| Table 2-1 Principle Parameters of the Simulated Circuit without leakage Inductance   | 32 |

| Table 2-2 Principle Parameters of the Simulated Circuit including leakage Inductance | 35 |

| Table 3-1 Principle Parameters of the Simulated Circuit in OrCAD                     | 55 |

| Table 3-2 Comparison of Analyses Done and Simulation in OrCAD                        | 60 |

| Table 5-1 Principle Parameters of the Simulation for Designed Converter              | 90 |

#### LIST OF ACRONYMS

AC Alternative Current

CCM Continuous Conduction Mode

CPU Central Processing Unit

DC Direct Current

DCM Discontinuous Conduction Mode

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ESL Equivalent Series Inductor

ESR Equivalent Series Resistor

FB Feedback

HF High Frequency

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PF Power Factor

PWM Pulse Width Modulation

rms Root Mean Square value

SB Silver Box

SR Synchronous Rectifier

THD Total Harmonic Distortion

VRM Voltage Regulator Module

## LIST OF PRINCIPLE SYMBOLS

|                   | control angle of main switches                                     |

|-------------------|--------------------------------------------------------------------|

| $\phi$            | phase angle of resonant current in series branch with respect to   |

|                   | input voltage                                                      |

| $\theta$          | phase angle between input current and voltage                      |

| $\omega_o$        | angular input frequency in radians                                 |

| $C_o$             | output filter capacitor                                            |

| $C_P$             | resonant network parallel capacitor                                |

| $C_{\mathcal{S}}$ | resonant network series capacitor                                  |

| D                 | duty ratio of main switches                                        |

| $f_o$             | input voltage frequency                                            |

| $f_s$             | switching frequency                                                |

| $I_{i}$           | current through the series branch of resonant network              |

| $I_{S}$           | current in the input of converter                                  |

| $I_o$             | nominal output current                                             |

| $I_{tp}$          | current through the primary side of transformer                    |

| $i_i$             | instantaneous series branch current in resonant network            |

| $i_S$             | instantaneous input current                                        |

| k                 | turns ratio of the power transformer primary to secondary windings |

| $L_{\mathcal{S}}$ | resonant network series inductor                                   |

$L_{lk}$ leakage inductance of the transformer number of harmonics in the input current and resonant network n  $N_1/N_2$ turns ratio of the power transformer  $P_{a}$ output power of the converter  $Q_1$  and  $Q_2$ two main switches of the converter  $R_{o}$ the converter load  $R_{eq}$ equivalent load transferred to the primary side of transformer  $SR_1$  and  $SR_2$ two switches of the synchronous rectifiers power transformer  $T_{r}$  $V_{o}$ nominal output voltage  $V_{ref}$ output reference voltage  $V_{\mathcal{S}}$ nominal input voltage voltage across the primary side of transformer  $V_{TP}$ instantaneous voltage of transformer in primary side  $v_{TP}$ instantaneous input voltage  $v_{S}$  $Z_{PI}$ fundamental impedance of parallel branch in resonant network nth impedance of parallel branch in resonant network  $Z_{Pn}$  $Z_{SI}$ fundamental impedance of series branch in resonant network n<sup>th</sup> impedance of series branch in resonant network  $Z_{Pn}$

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 General Introduction

Telecommunication and computer systems have gone through dramatic changes in the last decade to obtain higher speed, larger capability and more advanced functions. As an indispensable part of these systems, the power aspect in terms of power quality, conversion efficiency, reliability, density and cost is becoming an increasingly important issue to attain the advanced performance goals of the entire system.

Continuous advances in semiconductor technology result in ever-increasing functional densities and processing speed of electronic systems. To allow higher processing speed and to minimize power consumption, supply voltage are being reduced in new logic families. With the simultaneous increase in power demand and decrease in supply voltage level, new challenges are presented for the power systems. To decrease power consumption and increase the speed, the next generation of computer microprocessors is expected to operate at a much lower voltage, 0.5V to 1.5V, a much higher current, 50 A to 150 A, at a clock rate above 1 GHz and to exhibit current slew rate of 5 A/ns.

Moreover, the total voltage tolerance will become much tighter. In the future, the total voltage tolerance will be 2% (for 1.6 V output, the voltage deviation can only be  $\pm 32$  mV). Generally, these power supplies are required to have a high power density

and to operate with a high efficiency. To meet these requirements and to provide a fast transient response, the power conversion must be performed at a high switching frequency, so the following challenges are the result of the above trends:

- (i) Load currents are steadily increasing with the time.

- (ii) Operating voltages are decreasing as a result of smaller transistors.

- (iii) Slew rate from the active mode to the sleep mode and vice versa has been increasing.

- (iv) Power densities are steadily going up with time. It is always required to provide more power and occupy less space.

- (v) Efficiency of converters has remained constant at approximately 80%.

Table 1-1 is given the specification of future power supplies for new generation microprocessors [3]:

Table 1- 1: The specification of future VRM.

| Load current             | 50 ~150 A   |

|--------------------------|-------------|

| Output voltage           | 0.5 ~ 1.5 V |

| Slew rate                | 5 A/ns      |

| Efficiency               | > 80%       |

| Density                  | High        |

| Output voltage tolerance | ± 2%        |

In order to select an optimum power system configuration for a specific product in telecommunication, each system has to be considered separately from many points of view. Therefore, in the following sections, we will first know the advances in computer performance and its impact on power processing, and then we will see options for powering telecommunications equipment, to be able to justify our selected architecture.

#### 1.2 Power Delivery System of Computers

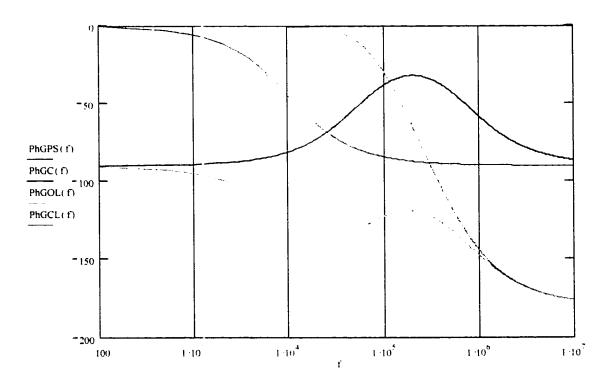

The power system configuration in the computer is shown conceptually in Figure 1-1. From AC utility to the processor (CPU), power delivery system consists of a system power supply (commonly known as "Silver Box" (SB)), voltage regulator module (VRM), decoupling capacitors, processors and distribution [1].

Figure 1- 1: CPU Power Delivery System

The silver box converts the input line AC voltage into DC bus voltage. In the early days of Intel486<sup>TM</sup> processor, SB could directly power the processor since it was easy to maintain 5% voltage tolerance under 1 A load. But starting from the Pentium<sup>®</sup> processor generation, with more and more system components drawing higher current

(>10 A) at lower voltage (<3.3 V), local VRMs have to re-process the intermediate voltage from SB into lower DC voltage. Another fact is that as the speed of processor increases, they are becoming a more dynamic load to their power supplies. To reduce the effect of parasitic impedance of VRM-load connection on the power supply transient response, VRM must be located next to the load (on-board conversion), and a large number of de-coupling capacitors are required to be connected across the processor.

From SB to VRM, the power distribution is traditionally implemented in DC domain. A novel technique know as high frequency AC distribution opens a new horizon for powering the future computer systems. Introduction and comparison of all possible power distribution architecture are described later on in the following sections.

#### 1.3 Advances in Computer Performance and Its Impacts on Power Processing

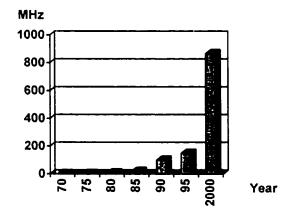

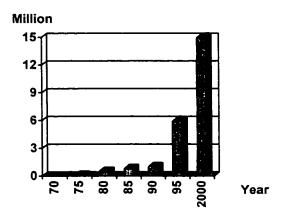

Microprocessor roadmaps indicate a continuing upward-slope in clock frequency Figure 1-2 and transistor density Figure 1-3 to achieve higher performance [1,2]. Increases

Figure 1-2: Internal Clock Frequency

Figure 1-3: Number of transistors

Table 1-2: Advances in processor speed and its impact on power supply

| YEAR | PROCESSOR              | SPEED         | $V_{cc}$  | $I_{cc}$ |

|------|------------------------|---------------|-----------|----------|

| 1979 | 8086                   | 5 ~ 8 MHz     | 5.0 V     | <<1 A    |

| 1985 | Intel386 <sup>TM</sup> | 16 ~ 20 MHz   | 5.0 V     | <1 A     |

| 1989 | Intel486 <sup>TM</sup> | 25 ~ 100 MHz  | 3.3/5.0 V | 1 A      |

| 1993 | Pentium®               | 60 ~ 66 MHz   | 5.0 V     | 3 A      |

| 1994 | Pentium®               | 90 ~ 233 MHz  | 2.8/3.3 V | 5 A      |

| 1995 | Pentium® Pro           | 150 ~ 200 MHz | 3.1/3.3 V | 15A      |

| 1997 | Pentium® II            | 233 ~ 300 MHz | 2.8 V     | 14 A     |

| 2000 | Pentium® III           | 500 ~ 866 MHz | 1.65 V    | 14 A     |

in the processor speed and transistor density have impacted the PC power supply industry significantly, as shown in Table1-2. Compared to Intel486<sup>TM</sup> processor, in Pentium® III processor, speed has increased by 9 times,  $V_{CC}$  voltage has decreased lower than 2 V, and  $I_{CC}$  current is up by more than a factor of 10.

#### 1.3.1 Low Supply Voltage with Tighter Tolerance

In Table1-2, the trend of voltage scaling of power supply is derived from the consideration of power dissipation. The major source of power dissipation in the processor is the dynamic power loss  $P_D$ , which is directly related to the processor speed, gate output capacitance C and the square of supply voltage  $V_{CC}$ :

$$P_D = \alpha C V_{CC}^2 f_C / 2 \tag{1-1}$$

Where,  $\alpha$  is activity scale (0.0 ~ 1.0), and  $f_{\rm c}$  is the clock frequency. This expression refers to a single gate. Total dynamic power dissipation is the sum of all the gates active at any instant-of-time. Currently, due to the dramatic increase in clock rate and transistor count, a reduction in supply voltage is the most effective method for reducing dynamic power loss. This technique is referred to as "voltage scaling". It also allows a reduction in feature size and thinner oxide layers needed for higher transistor density packing. Therefore, 1.65 V in Table1-2 is only a transient stage. The processor supply voltage in future generation of processors will decrease to 0.5 V ~ 1.5 V.

In order to ensure the accurate high speed data transition, voltage scaling technique requires much tighter tolerance on the power supply. Currently, the voltage tolerance is

5% (for 3.3 V VRM output, the voltage deviation can be ± 165mV). In the future, the total voltage tolerance will be 2%, which means for 1.6 V VRM output, the voltage deviation can only be ± 32 mV. For this kind of accuracy, the need for low voltage, precision, temperature stable, and low noise references is a must.

#### 1.3.2 High Supply Current with Tight Slew Rate

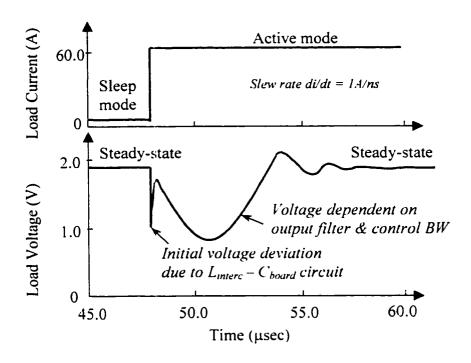

Because more devices are packed on a single processor chip and processor function at higher frequencies, future processors are expected to draw a much higher current, up to  $50 \sim 150$  A, and present much higher slew rate, up to  $1 \text{ A/ns} \sim 5 \text{ A/ns}$ . The most dramatic load transient occurs in the processor transition from the sleep mode (typical load current  $\leq 5 \text{ A}$ ) to the active mode (typical load current  $\geq 50 \text{ A}$ ) and vice versa. Currently, it is in the range of  $10 \sim 100 \text{ A/} \mu \text{ s}$ , for processors operating at around 500 MHz. In future, it will be expected to be  $1 \sim 5 \text{ A/ns}$ , or even higher.

#### 1.3.3 Large Load Transient

Figure 1-4 shows the typical process supply voltage waveform during large load transient. There are two voltage drops that can be observed. The initial voltage deviation caused by the interaction of parasitic interconnection inductance and de-coupling capacitance. After this voltage drop spike, the transient response is governed by the power stage parameters (output filter) and the bandwidth of control loop. To keep supply voltage within the required tight load regulation rang, design consideration for VRM output filter and control loop are becoming more critical issues [5,6].

Figure 1-4: Typical processor supply voltage waveform during the load transition

#### 1.4 Overall Power Architecture

The trend of supplying low voltage with tight regulation and high current with high slew rate in a cost-effective manner is not only related to VRM and the distribution between VRM and processor, but also involves the overall power architecture. Three powering options: low voltage DC distribution, high voltage DC distribution, and high frequency AC distribution will be briefly described below[1,4,10,11,15].

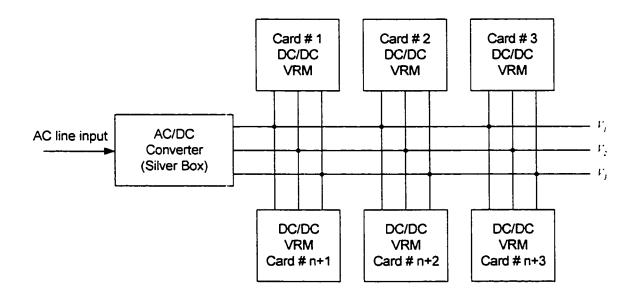

#### 1.4.1 Low Voltage DC Distribution

In the early days of computer systems, lower speed and fewer components were involved; the silver box implemented by a very slow power supply with multiple outputs

was able to meet the requirements of every power demand. Therefore, the simplest and commonly employed approach in powering the computer system is the so-called low voltage DC distribution [1,15], as shown in Figure 1-5. The silver box converts the AC line input voltage into several low DC voltages, which then are distributed through the shelf bus bar or back plane to the various system cards. Most low voltages on each card serve only as the input for several VRMs where these voltages are converted into even lower voltage levels but at higher currents. Also, on each card, a current limiting circuit may have to be used to limit the inrush current during the "hot insertion" of the card.

Figure 1-5: Low voltage DC power distribution

This power scheme is relatively simple, however, it is no longer capable of providing power quality used in the modern and future digital electronics for the following reasons:

- (i) Additional supply voltages, such as +15 V, +5 V, +3.3 V, -5.2 V etc., are required;

- (ii) Very fast transient response at low supply voltage is not practical from a single buck converter:

- (iii) Distribution of a heavy current through the bus bar or back plane introduces loss and requires a large amount of space for heavy wiring;

- (iv) The heat generated in the power conversion process is concentrated within the converter, which may result in a necessity to use forced air cooling;

- (v) Static and dynamic load regulations with tight tolerances at low voltages need regulation at the point-of-use;

- (vi) Cross regulation effects between the outputs of a single bulk converter increases the problems with tight regulation requirement.

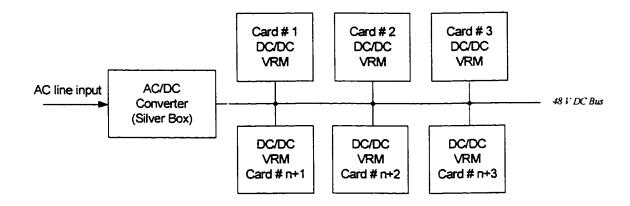

#### 1.4.2 High Voltage DC Distribution

Since some draw backs of previous low voltage DC distribution are direct results of distribution of low voltage at high current levels, better performance can be expected if a higher voltage is used as the intermediate voltage supplying the VRMs. Figure 1-6 shows the configuration of the high voltage DC distribution [1,3].

In this power scheme, the silver box generates only a single voltage at a much higher voltage level (typically 48 V DC), and then the point-of-use power supplies (PUPS) distributed on each system card convert this intermediate voltage into the required voltage level.

Figure 1-6: High voltage DC power distribution

High voltage DC distribution has some advantages over the low voltage DC power distribution as follows:

- (i) Heat produced by the power conversion is distributed through the whole system;

- (ii) The loss within the back plane is minimized since higher voltage and thus smaller current is distributed:

- (iii) Voltage regulation at the point-of-use is excellent:

Although many publications have shown the further performance improvements of such power distribution systems, it still suffers from the following problems:

- (i) Distributed input filters are required for isolation from converter interaction and they are sensitive to impedance instability;

- (ii) More components, filter and converters add a high cost to the system, take a large board space, and lower the system reliability;

- (iii) No provision to efficiency deal with negative high *di/dt*:

- (iv) Inrush current limiting circuit on each card is still needed if "hot insertion" of the system cards is required.

Therefore, several research woks have been done for an improved power distribution scheme, which could provide all the advantages of high voltage DC distribution, but at fewer component, lower cost, smaller size, and higher reliability. A novel technique, high frequency AC power distribution. for the future computer system will be introduced in the next sub-section.

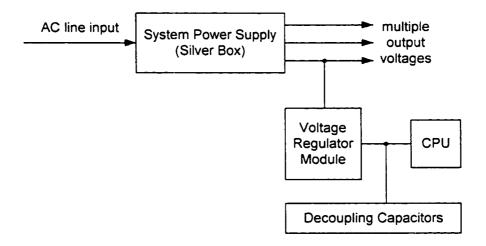

#### 1.4.3 High Frequency AC Power Distribution

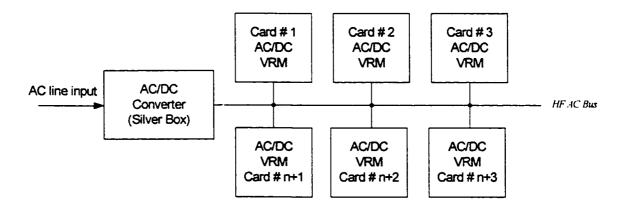

The concept of high frequency AC (HFAC) power distribution system was first proposed by NASA some 25 years ago. Since then a number of industries have been working on this new powering scheme for other applications [1.6,13,14.17]. The basic configuration of the HFAC power distribution system is shown in Figure 1-7.

The silver box generates high frequency AC voltage. The HFAC is distributed through the back plane to the various system cards, where it will be converted to the specific DC voltage level by the local AC/DC converter (ACVRM).

Figure 1-7: High frequency AC power distribution

This new scheme not only combines the advantages of the existing DC powering scheme but also brings new features, which are technically impossible in DC domain. The main features of this powering scheme are discussed as following:

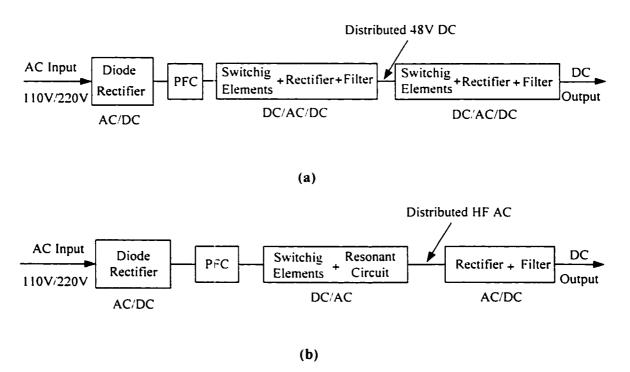

- (i) Excellent transient response. For a properly designed wide-band width feedback control, the large-signal transient response is mainly determined by the response of output filter [6]. Since no low-pass filter is present at the output of the inverter, the feedback loop in AC domain can be closed at a much higher frequency than in case of DC domain.

- (ii) Reduced power conversion stages as shown in Figure 1-8. This results in higher efficiency, lower cost, smaller size, and better reliability.

Figure 1-8: (a) High Voltage DC Distribution system (b) HF AC Distribution System

- (iii) Active energy steering. The energy corresponding to the positive current step must be provided by power delivery system. During the negative current step, however, energy could be either stored or damped. Damping is technically the simplest, but results in poor efficiency. In HFAC distribution, the excess energy can easily be steered to high frequency bus side and be re-used when needed.

- (iv) Simple current limit. The resonant circuits which are incorporated in both silver box and ACVRM provide inherent short-circuit protection at the power interface (fuse-less protection) and limited power transfer to the load (elimination of fire hazard). Therefore, the inrush current can be limited without any other additional circuit if "hot insertion" of the system card required.

- (v) Reduction of thermal stress. This not only increases the system reliability, but also may allow the system to operate with convection cooling rather than the forced air cooling. The elimination of fans will further improve the overall reliability and reduce the maintenance requirement.

- (vi) Connector-less power transfer. This feature, which is technically impossible to be implemented into DC power scheme, becomes the most attractive potential in HFAC power distribution. The transformer used in AC/DC converter can serve as media for magnetic coupling between the back-plane (on which has the main power tracking) and the removable load card (on which has the point-of-use AC/DC converter). To achieve this, the transformer must be constructed in such a way that one half (which contain the primary winding) will be physically located on the load card together with AC/DC converters. The energy then can be coupled

through the magnetic field only, without any metallic connection. This solution has the potential to offer a substantial improvement in system reliability due to the elimination of power connector.

#### 1.5 Thesis Objectives

This thesis presents a High Frequency AC/DC Converter for new generation of microprocessors and telecom systems. The main objectives of the thesis are:

- (i) To develop the topology of HF AC/DC converter. The proposed topology should meet the stringent requirements as follows: tight voltage regulation, fast transient response, high efficiency, high power density, low EMI, and constant operating frequency;

- (ii) To present the steady-state and dynamic performance and characteristics of proposed converter topology;

- (iii) To present the control scheme used to achieve the best dynamic performance:

- (iv) To verify with results from simulation performed in Psim and Pspice:

- (v) To present design characteristics of the converter based on the steady-state analyses, which help in understanding the internal working of the converter:

- (vi) To generate design procedure and curves for industrial applications:

- (vii) To specify the design guidelines with a design example to assist in the design process.

#### 1.6 Thesis Outline

The thesis is organized in the following structure:

In Chapter 2, the possible topologies and the proposed topology are presented. The simplified analysis is performed to understand its steady states characteristics and properties. Simulation results are also presented as proofs of concept. The simulation under a real condition is presented which leads us to the next chapter.

In chapter 3, the proposed topology under a real condition is analyzed, considering the effect of leakage inductance and all inductances and resistors in series with the switches. The results from simplified analyses and detailed analyses are compared with the simulation to justify the analyses.

In chapter 4, the proposed topology under dynamic condition is analyzed. This includes small signal modeling and space-state averaging to linearize the power stage for finding the power stage transfer function, which leads us to compensate the feedback loop to dynamically stabilize the converter. At the end of this chapter, the converter responses to the step changes in the load are shown to verify the design in simulation.

In chapter 5, a design procedure oriented for industrial applications is generated based on the analyses performed in the previous chapters. A design example is also given.

In chapter 6, a summery of the thesis is given. A conclusion and contribution of the thesis are discussed. Suggestions for future works in this area are also suggested.

#### **CHAPTER 2**

# A RESONANT AC/DC CONVERTER FOR HIGH FREQUENCY DISTRIBUTION SYSTEMS

#### 2.1 Introduction

A resonant AC/DC converter for high frequency distribution systems is presented in this chapter. Dr. P.K. Jain at CAL CORPORATION first invented this topology during the development of AC/DC converters for a high frequency technology for the Canadian Space Station Program [19]. In this thesis, the same idea of resonant converter topology is held. However it is now implemented for even higher frequency applications using MOSFETs as the main switches in the primary side of the transformer, and synchronous rectifiers in the secondary side of the transformer.

The proposed converter topology converts a high frequency AC voltage to a controlled output DC voltage while drawing close-to-sinusoidal input current with a near unity power factor. This topology uses only one conversion stage, which results in higher efficiency, and lower weight and volume. Also, the operating frequency of converter is constant and synchronized with the input frequency. Together with the distortion less input current and constant frequency, the EMI/electromagnetic compatibility (EMC) filter requirements are minimized.

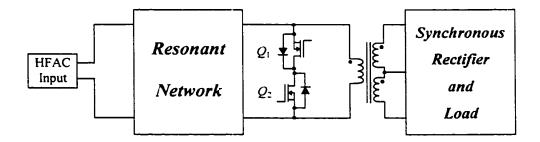

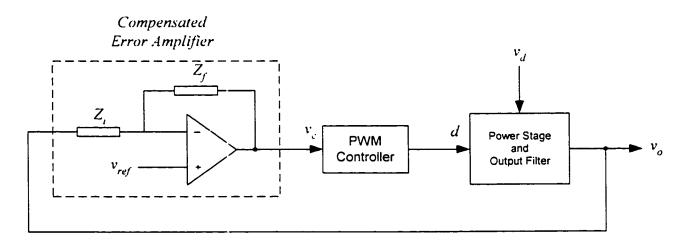

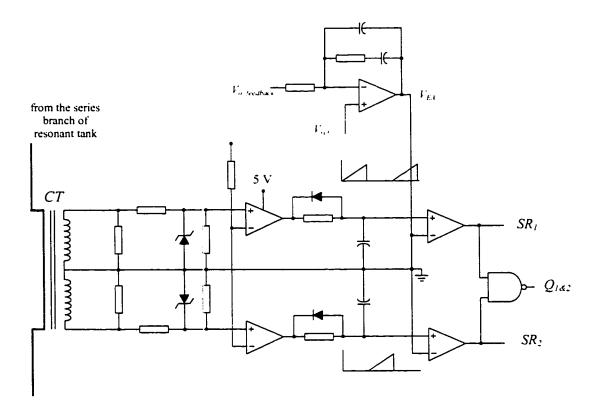

The converter circuit employs an input resonant network to convert the singlephase high-frequency sinusoidal voltage source into a sinusoidal high-frequency bidirectional current source. The output of this current source is rectified by synchronous rectification and is controlled by a bi-directional switch. The controlled rectified current is then filtered to obtain a constant voltage across load. A generic diagram of the AC/DC converter is shown in Figure 2-1. This converter consists of:

- (i) Resonant Network: For converting the single-phase high frequency sinusoidal input AC voltage to a sinusoidal high-frequency bi-directional current source;

- (ii) Current Controller: Connected in parallel to the resonant network to receive the sinusoidal high-frequency current output of resonant network and provide the desired output current from the converter. The current controller consists of two controlled switches,  $Q_1$  and  $Q_2$ , connected in series back to back to each other;

- (iii) Transformer: To provide matching output voltage, and isolation for the output load;

- (iv) Synchronous Rectifiers: Connected to the secondary of transformer, to convert the bi-directional current into a unidirectional current;

- (v) Output filter: Connected to the synchronous rectifier to provide an essentially ripple free, substantially DC output voltage.

Figure 2-1: A generic diagram of AC/DC converter

In order to understand the operating principle and performance characteristics of

the proposed topology, and to provide reference in design procedure in Chapter 5, the steady state analysis is performed in this chapter. The outline of this chapter is as follows:

The proposed topology is presented in Section 2.2. The steady state analysis is performed in Section 2.3. Simulation results are given in Section 2.4 to verify the concepts and theoretical analysis. At the end of this chapter, some conclusions are drawn.

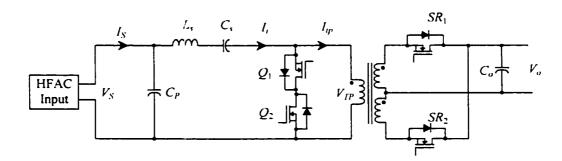

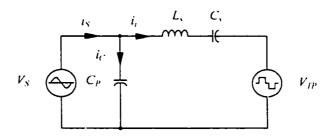

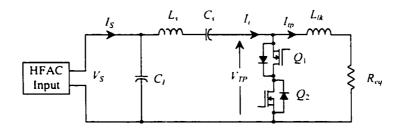

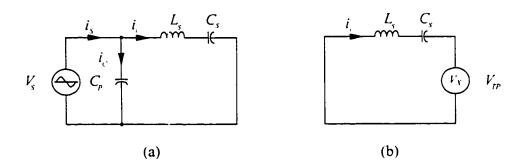

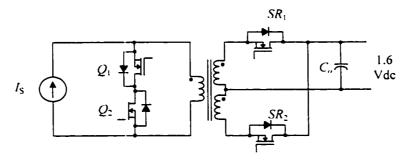

### 2.2 Circuit Description

Figure 2-2 shows the proposed HF AC/DC converter topology. In this type of converter, the resonant network comprises a parallel capacitor  $C_p$ , a series inductor  $L_S$  and a series capacitor  $C_S$ . The capacitor  $C_P$  is connected in parallel with the input source. Both the inductor  $L_S$  and capacitor  $C_S$  are connected in series after capacitor  $C_P$ . The resonant circuit components,  $C_P$ ,  $L_S$  and  $C_S$ , are selected such that a close-to-unity input power factor and a sinusoidal alternating current of near constant amplitude through components  $C_S$  and  $C_S$  under full-load to short circuit condition, are obtained when the single-phase high frequency, sinusoidal waveform AC source voltage  $V_S$  is applied to the input of the resonant network.

Figure 2- 2: The proposed HF AC/DC converter topology.

The main switches  $Q_1$  and  $Q_2$  control the amount of resonant circuit output current that is needed to be rectified to achieve the desired DC output voltage and load current.

### 2.3 Steady State Analysis

This section describes the steady state analysis of the circuit during two switching states. The purpose of this analysis is to obtain characteristics of the converter, which aid in designing the converter. The analysis will be performed with the assumptions made below. In the analysis, the time varying variables such as the current and voltage of the principle components and devices are determined. Based on these variables, the performance of the converter can be illustrated, and the quantities such as power factor (PF), total harmonic distortion (THD) and output voltage can be obtained. These quantities are used to design the converter as presented in Chapter 5. In the analysis presented below, a set of equations solved in frequency domain as a function of the duty cycle  $\alpha$ , the input line voltage  $V_S$  and the output power  $P_o$ .

### 2.3.1 Assumptions and Some Constants for the Analysis

To perform the steady state analysis, the following assumptions are made:

- (i) The steady state conditions have been established and the converter is running at an input AC voltage  $V_o$ , producing the nominal output voltage  $V_o$  and delivering a power of  $P_o$  to a static load.

- (ii) The gating of main switches  $Q_1$  and  $Q_2$ , is synchronizing the gating of switches  $SR_1$  and  $SR_2$ ,

- (iii) The switching frequency is constant  $f_s$ .

- (iv) All components and devices have ideal properties and characteristics, i.e.,

- (1)  $T_r$ : losses and leakage inductance are negligible, and the core does not saturate.

- (2)  $L_S$  is a pure inductor and its losses are negligible, and its inductance is constant,

- (3)  $C_o$ ,  $C_S$ , and  $C_P$ : all capacitors are pure, their equivalent series resistance (ESR) and equivalent series inductance (ESL) are negligible,

- (4)  $Q_1$ ,  $Q_2$ ,  $SR_1$ , and  $SR_2$ : all switches have negligible conduction losses, and the inherent capacitances are 0 F.

- (5) The magnetizing inductance of the power transformer is so great that the magnetizing current is negligible.

- (v)  $C_o$  is large enough to maintain constant and ripple free voltage during the steady state operation.

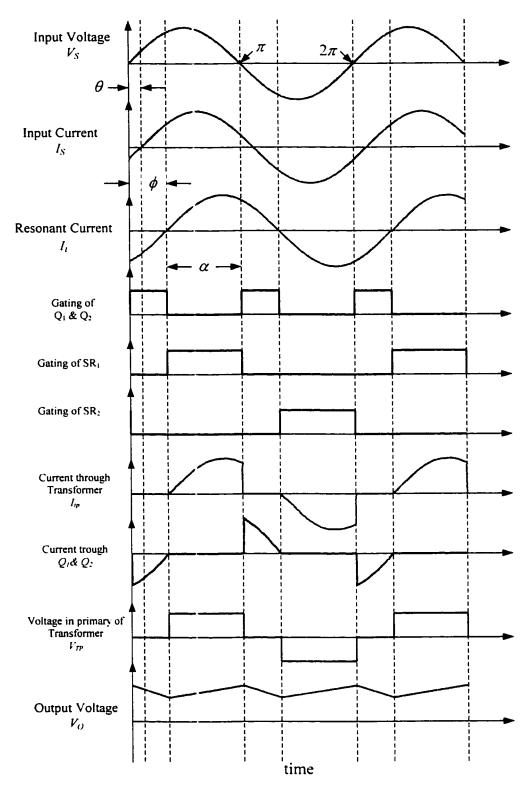

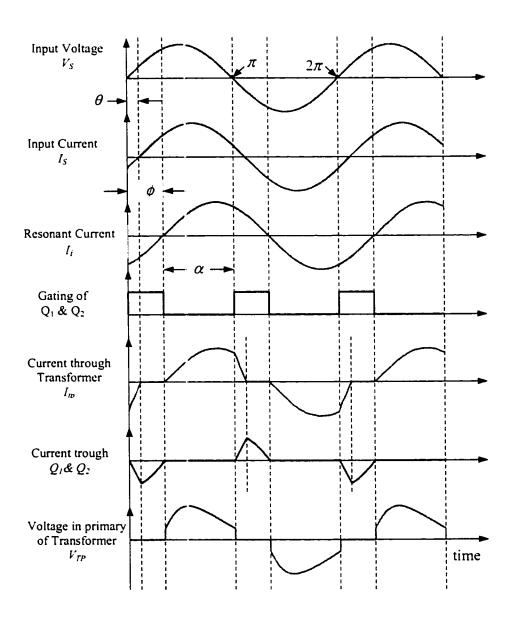

- (vi) Under these assumptions, the operating principle is illustrated with key waveforms shown in Figure 2-3. Each switching cycle can be divided into two distinct intervals.

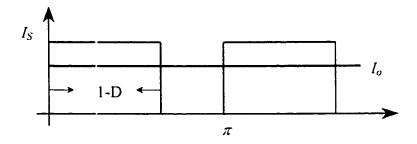

### 2.3.2 Operating Principle

Figure 2-3 shows the operating waveforms. At the position of cycle where  $\omega_0 t = \phi$ ,  $SR_I$  is conducting and the input resonant current  $i_t$  is charging the output capacitor  $C_o$  until  $\omega_0 t = \phi + \alpha$  where the switches  $Q_I$  and  $Q_2$  are turned on. At this time, the input current is instantaneously transferred from  $SR_I$  to  $Q_I$  and  $Q_2$  to end the charging period of  $C_o$ . At  $\omega_0 t = \pi + \phi$  the resonant input current flowing through  $Q_1$  and  $Q_2$  goes

Figure 2-3: Key waveforms of the proposed converter topology. The switching transient is exaggerated.

to zero, thereby the gating signal ends. At this instant,  $SR_2$  conducts and carries the negative input resonant current. The rectification of  $SR_2$  changes the direction of this current at the output and starts the charging of the capacitor  $C_o$ . At  $\omega_0 t = \pi + \phi + \alpha$ , the current flowing through  $SR_2$  goes to zero, because  $Q_1$  and  $Q_2$  are gated on and carry the current at the input.

### 2.3.3 Steady State Analysis of Each Interval

Under the assumptions made, the simplified n<sup>th</sup> harmonic equivalent circuit of the converter is shown in Figure 2-4, which contains two voltage sources.

Figure 2- 4: The nth harmonic equivalent circuit of the proposed converter

Figure 2- 5: The nth harmonic equivalent circuit considering separated voltage sources.

The theorem of superposition is used in obtaining the various currents and voltages of the converter circuit. Figure 2-5 (a) shows the equivalent circuit with only the input source  $V_S$ , and Figure 2-5 (b) shows the equivalent circuit with only the output source  $V_{TP}$ .

For convenience, some constants are defined below. In steady state, the parallel and series impedance for the fundamental and n<sup>th</sup> harmonics are determined by:

$$Z_{p_1} = -j\frac{1}{\omega_o C_p} = -jX_{C_p} \tag{2-1}$$

$$Z_{Pn} = \frac{-jX_{C_I}}{n}$$

(2-2)

$$Z_{S1} = j\omega_{o}L_{S} - j\frac{1}{\omega_{o}C_{S}} = j(X_{LS} - X_{CS})$$

(2-3)

$$Z_{Sn} = njX_{LS} - \frac{jX_{CS}}{n} \tag{2-4}$$

Since the input voltage source  $V_S$  is sinusoidal and contains no harmonics, the following relation presents:

$$v_S = \sqrt{2}V_S Sin(\omega_o t) \tag{2-5}$$

The input current due to source  $V_S$  is given by:

$$i_{S1} = \frac{v_S}{Z_{t1}} = \frac{\sqrt{2}V_S Sin(\omega_o t)}{-j|Z_{t1}|} = \frac{\sqrt{2}V_S}{|Z_{t1}|} Cos(\omega_o t)$$

(2-6)

where:

$$Z_{t1} = \frac{-jX_{C_p} \cdot j(X_{Ls} - X_{C_p})}{-jX_{C_p} + j(X_{Ls} - X_{C_s})} = \frac{-j[X_{C_p}(X_{Ls} - X_{C_s})]}{(X_{Ls} - X_{C_s} - X_{C_p})}$$

(2-7)

The transformer primary voltage has a quasi-square waveform expressed in the

following Fourier series:

$$v_{TP} = \sum_{n=1,3}^{\infty} \frac{4V_{TP}}{n\pi} Sin \frac{n\alpha}{2} Sin(n\omega_{0}t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

(2-8)

The input current due to source  $v_{TP}$  is given by:

$$i_{S2} = \sum_{n=1,3}^{\infty} \frac{4V_{IP}}{n\pi |Z_{Sn}|} Sin \frac{n\alpha}{2} Cos(n\omega_o t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

(2-9)

The total input current is given by:

$$i_{S} = i_{S1} + i_{S2} = \frac{\sqrt{2}V_{S}}{|Z_{t1}|}Cos(\omega_{c}t) + \sum \frac{4V_{TP}}{n\pi|Z_{Sn}|}Sin\frac{n\alpha}{2}Cos(n\omega_{o}t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

$$i_{S} = \frac{\sqrt{2}V_{S}}{|Z_{tt}|}Cos(\omega_{o}t) + \sum \frac{4V_{O}}{n\pi|Z_{Stt}|} \frac{N_{1}}{N_{2}}Sin\frac{n\alpha}{2}Cos(n\omega_{o}t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

(2-10)

### (i) Determination of Angle $\phi$ :

The following equation shows the current in the series branch of resonant network due to the source  $V_S$ :

$$i_{i1} = \frac{v_S}{Z_{S1}} = \frac{\sqrt{2}V_S Sin(\omega_o t)}{j|Z_{S1}|} = \frac{-\sqrt{2}V_S}{|Z_{S1}|} Cos(\omega_o t)$$

(2-11)

and the current in the same branch due to the output source  $v_{TP}$  is given by:

$$i_{i2} = \sum_{n=1,3}^{\infty} \frac{4V_{p}}{n\pi |Z_{Sn}|} Sin \frac{n\alpha}{2} Cos(n\omega_{o}t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

(2-12)

so the resonant current in this branch according to theorem of superposition is:

$$i_{t} = i_{t1} + i_{t2} = \frac{-\sqrt{2}V_{S}}{|Z_{SI}|}Cos(\omega_{o}t) + \sum \frac{4V_{O}}{n\pi|Z_{Sn}|} \frac{N_{1}}{N_{2}}Sin\frac{n\alpha}{2}Cos(n\omega_{o}t - \frac{n(\alpha + 2\phi - \pi)}{2})$$

(2-13)

The resonant Current is  $i_i = 0$  at  $\omega_{ij}t = \phi$ , therefore, from Equation (2-13) the following relations are obtained:

$$\frac{-\sqrt{2}V_S}{\left|Z_{S1}\right|}Cos\phi + \sum \frac{4V_O}{n\pi\left|Z_{Sn}\right|} \frac{N_1}{N_2}Sin\frac{n\alpha}{2}Cos(n\phi - \frac{n(\alpha + 2\phi - \pi)}{2}) = 0$$

$$\frac{\sqrt{2}V_S}{|Z_{S1}|}Cos\phi = \sum \frac{4V_O}{n\pi|Z_{Sn}|} \frac{N_1}{N_2} Sin \frac{n\alpha}{2} Cos \frac{n(\pi - \alpha)}{2}$$

$$Cos\phi = \sum \frac{2\sqrt{2}}{n\pi} \frac{V_O}{V_S} \frac{Z_{S1}}{|Z_{Sn}|} \frac{N_1}{N_2} Sin \frac{n\alpha}{2} Cos \frac{n(\pi - \alpha)}{2}$$

(2-14)

For a given control angle  $\alpha$ , the value of  $\phi$  would have been calculated by using Equation (2-14), if the value of  $\frac{V_O}{V_S}$  were known. The value of  $\frac{V_O}{V_S}$  can be obtained by setting the input power equal to the output power.

Since the input voltage source contains no harmonics, the product of the fundamental input current, the input voltage and the fundamental cosine angle between the two, determines the input power. This leads us to the next sub-section.

### (ii) Output Voltage Control:

Output voltage control is provided by controlling the current controller pulse width (gating of  $Q_1$  and  $Q_2$ ) other word angle  $\alpha$ .

By substituting n = 1, the fundamental time-varying input current from Equation (2-10) is given by:

$$i_{Sf} = \frac{\sqrt{2.V_S}}{|Z_{t1}|} Cos(\omega_0 t) + \frac{4V_O}{\pi |Z_{S1}|} \frac{N_1}{N_2} Sin \frac{\alpha}{2} Cos(\omega_0 t - \frac{\alpha + 2\phi - \pi}{2})$$

(2-15)

The fundamental time-varying current from Equation (2-15) can be simplified by:

$$i_{S} = C.Sin(\omega_{0}t + \theta) \tag{2-16}$$

and

$$A.Cos(x) + B.Sin(x) = C.Sin(\omega_0 t + \theta)$$

(2-17)

where:  $C = \sqrt{A^2 + B^2}$  and  $\theta = \tan^{-1}(A/B)$ , it is carried out that the A and B parameters are:

$$A = \frac{\sqrt{2}}{|Z_{11}|} V_{S} + \frac{4V_{O}}{\pi \cdot |Z_{S1}|} \frac{N_{1}}{N_{2}} Sin \frac{\alpha}{2} Sin \frac{2\phi + \alpha}{2}$$

(2-18)

$$B = \frac{-4V_O}{\pi |Z_{SI}|} \frac{N_1}{N_2} Sin \frac{\alpha}{2} Cos \frac{2\phi + \alpha}{2}$$

(2-19)

The input power is given by:  $F_s = V_S I_{SS} Cos(\theta) = V_S \frac{C}{\sqrt{2}} Cos(\theta) = \frac{V_S}{\sqrt{2}} B$ , therefore:

$$P_{i} = \frac{2\sqrt{2}}{\pi |Z_{SI}|} \frac{N_{i}}{N_{i}} V_{O} V_{S} Sin \frac{\alpha}{2} Cos \frac{2\phi + \alpha}{2}$$

$$(2-20)$$

The output power is given by:

$$P_{O} = \frac{V_{O}^{2}}{R_{O}}$$

(2-21)

Since the input power is equal to the output power, the following relation is obtained from Equation (2-20) and Equation (2-21):

$$\frac{{V_o}^2}{R_O} = \frac{-2\sqrt{2}}{\pi |Z_{S1}|} V_o V_S \frac{N_1}{N_2} Sin \frac{\alpha}{2} Cos(\frac{2\phi + \alpha}{2})$$

or

$$\frac{V_O}{V_S} = \frac{-2\sqrt{2}}{\pi |Z_{S1}|} \frac{N_1}{N_2} R_O.Sin \frac{\alpha}{2} Cos(\frac{2\phi + \alpha}{2})$$

(2-22)

Substituting  $\frac{V_O}{V_S}$  from Equation (2-22) into Equation (2-14), we have:

$$\tan \phi = \frac{\left[\frac{16}{\pi^2} \left(\frac{N}{N}\right)^2 Sin\alpha \sum_{n=1,3}^{\infty} \frac{1}{n} \frac{R_0}{|Z_{Sn}|} Sin \frac{n\alpha}{2} Cos \frac{n(\pi - \alpha)}{2}\right] + 1}{\frac{8}{\pi^2} \left(\frac{N}{N}\right)^2 Sin^2 \frac{\alpha}{2} \sum_{n=1,3}^{\infty} \frac{1}{n} \frac{R_0}{|Z_{Sn}|} Sin \frac{n\alpha}{2} Cos \frac{n(\pi - \alpha)}{2}}{2}$$

(2-23)

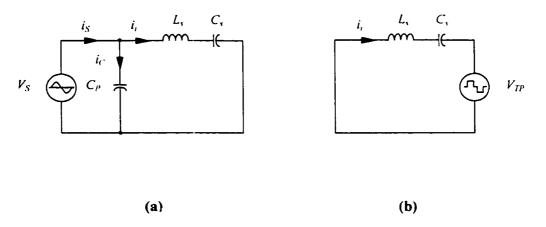

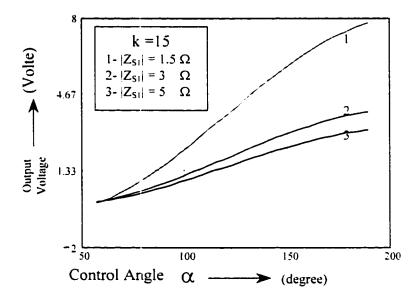

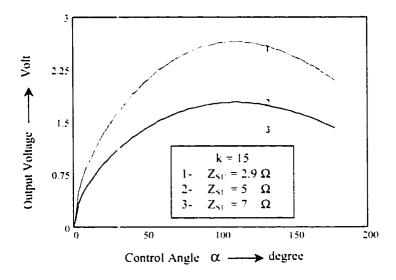

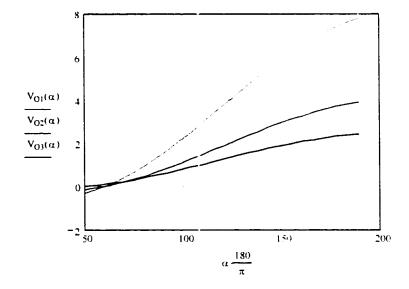

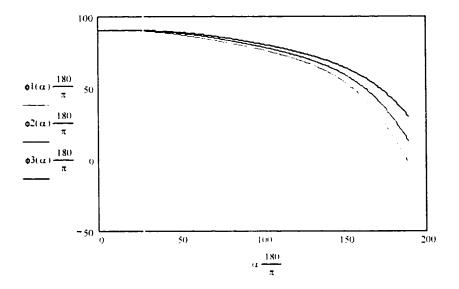

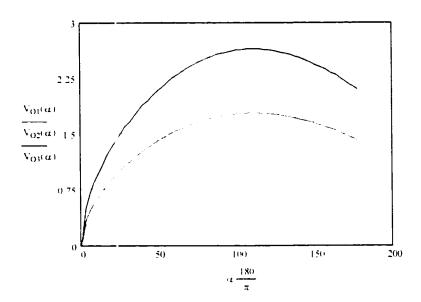

For a given angle  $\alpha$ , output load  $R_0$  and impedance  $Z_S$  the value of  $\phi$  is obtained. Figure 2-6 shows the graph of control angle  $\alpha$  versus resonant current angle  $\phi$  for different values of  $Z_S$ . Figure 2-7 shows the output voltage versus control angle. For different values of  $\frac{N_1}{N_2}$  and  $Z_{SI}$  the converter output voltage has been drawn. The lower the series impedance is, the higher the output voltage is. All graphs are done in Mathcad.

Figure 2- 6: Control angle versus resonant angle

# (iii) Input Current Total Harmonic Distortion:

The total harmonic distortion (THD) of the input current is defined as:

$$THD = \frac{\sqrt{\sum_{n=1}^{\infty} I_n^2}}{I_{,}}$$

Therefore:

$$THD = \frac{4.V_0}{\pi.C} \frac{N_1}{N_2} \sqrt{\sum_{n=1}^{\infty} (\frac{1}{n |Z_{Nn}|} Sin \frac{n\alpha}{2})^2}$$

(2-24)

Figure 2- 7: Output voltage versus control angle

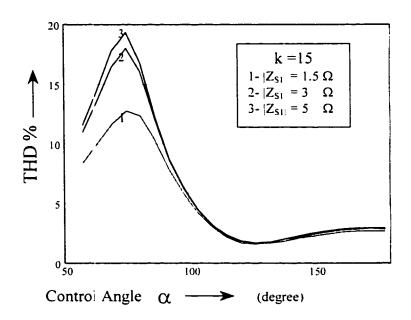

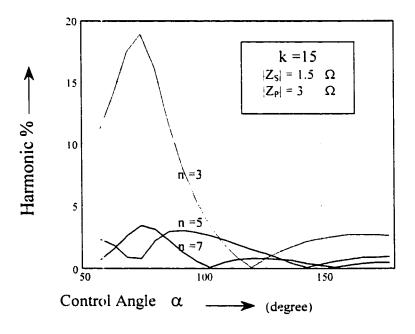

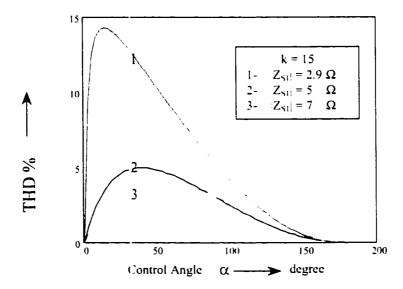

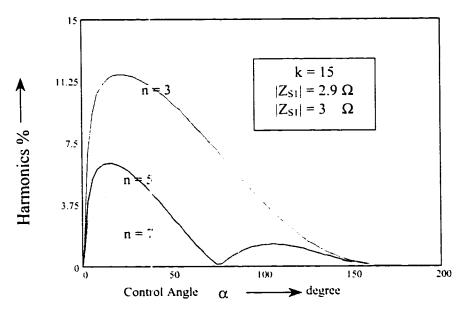

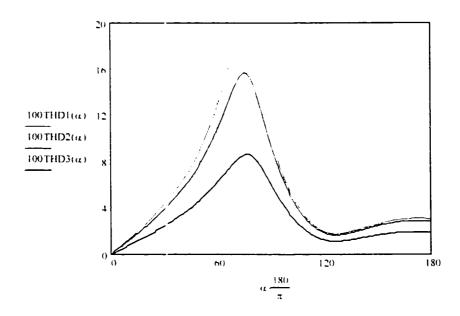

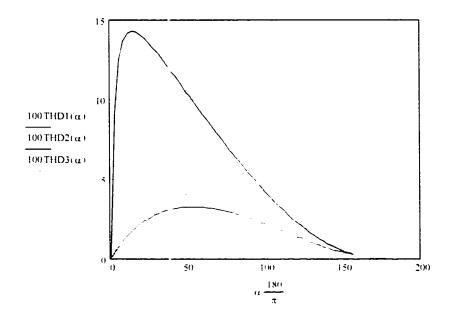

Figure 2-8 shows THD for different values of series and parallel impedance. According to the graphs, for greater values of  $\alpha$ , we have less THD. Due to the fact that the operating point is around  $\alpha = 120^{\circ}$ , a very low THD is attainable.

Figure 2-8: Total Harmonic Distortion

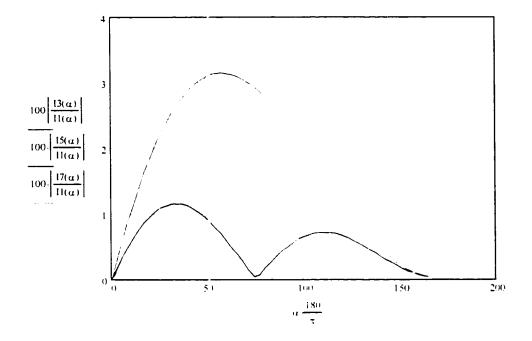

Figure 2- 9: The Harmonics % of input current

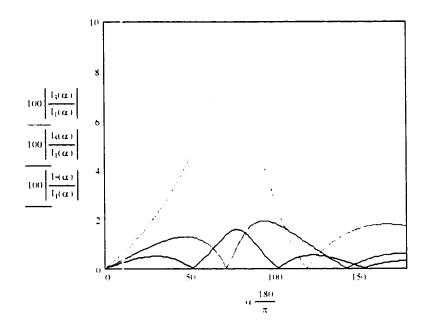

Figure 2-9 shows the %Harmonic of input current. As it is expected, the  $3^{rd}$  harmonic is the least at  $\alpha = 120^{\circ}$ , and very severe at the other points. After that, the  $5^{th}$  harmonic is the most severe one and the rest are less.

## (iv) Input Power Factor:

The converter input power factor is given by:

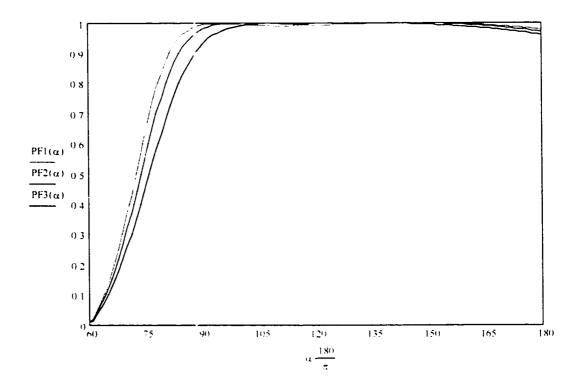

$$PF = -\frac{Cos\theta}{\sqrt{1 + THD^2}} \tag{2-25}$$

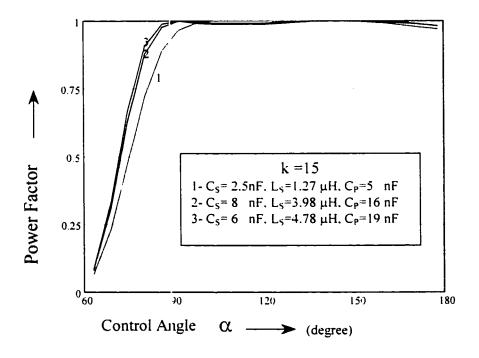

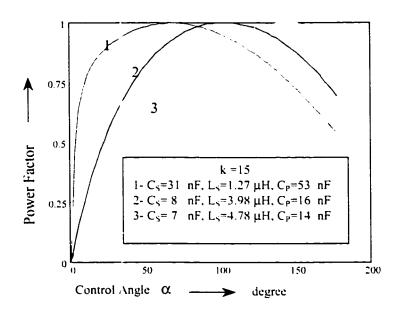

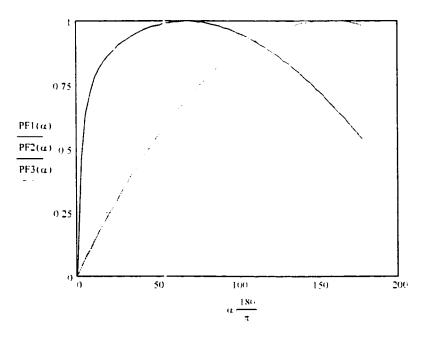

Figure 2-10 shows the power factor versus the control angle. As expected, the power factor is close to unity in almost all condition.

Figure 2- 10: Power Factor versus control angle

### 2.4 Simulation Results

Simulation of the proposed converter topology is performed with PSIM software. This simulation is first done without considering the leakage inductance to verify the concept of analysis carried out in this chapter, and to find out whether the statements are correct. Table2-1 shows the principle parameters of the circuit used in simulation.

Table2- 1: Principle Parameters of the Simulated Circuit without considering the leakage inductance

| Parameter      | Value    | Parameter      | Value  |

|----------------|----------|----------------|--------|

| V <sub>S</sub> | 30 V rms | $C_{o}$        | 480 μF |

| Po             | 80 W     | C <sub>S</sub> | 6.8 nF |

| fs             | 2 MHz    | L <sub>s</sub> | 4.4 μΗ |

| k              | 15:1:1   | C <sub>P</sub> | 20 nF  |

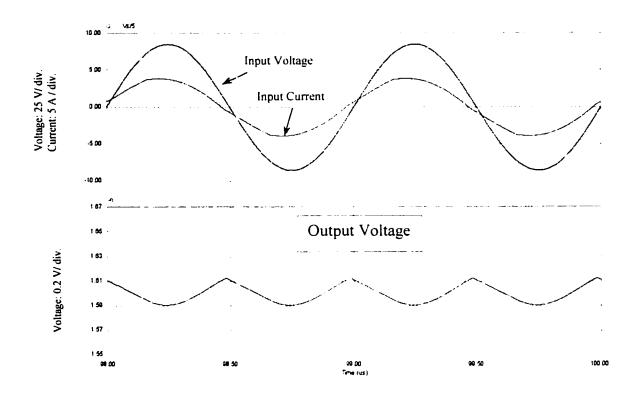

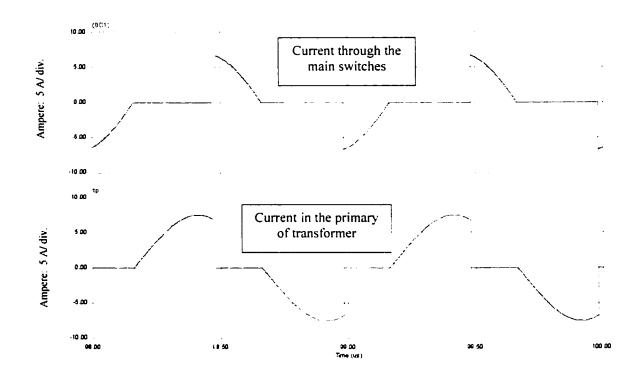

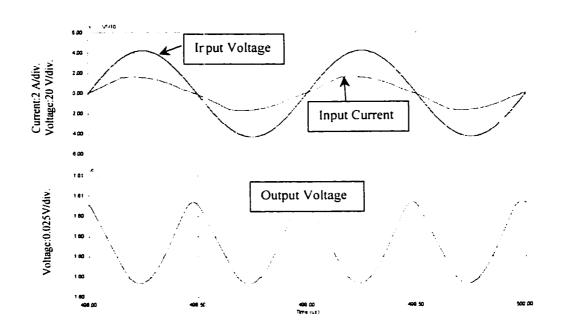

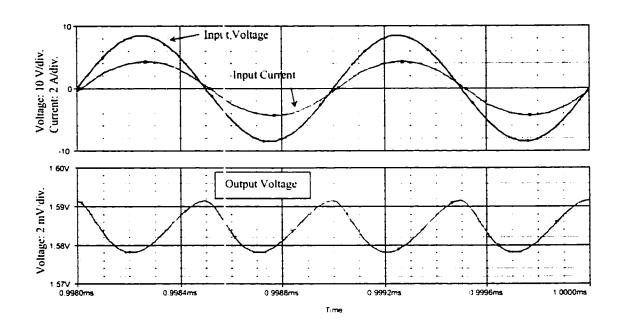

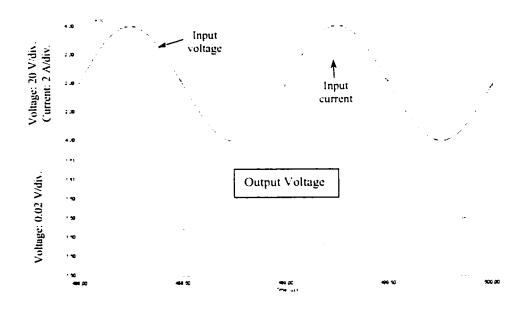

Figure 2-11 shows the input voltage and current along with the output voltage. As expected, the input voltage and current are almost in the same phase, so the power factor is close to unity and that is what expected. To find out the current and voltage in different branches in the converter, it was assumed that voltage in primary side of the transformer to be quasi-square wave. Figure 2-12 shows the voltage in primary and secondary of the transformer, and it proves that the assumption made is right.

Figure 2- 11: The input voltage and current and output voltage of converter

Figure 2- 12: The voltages in primary and secondary of transformer

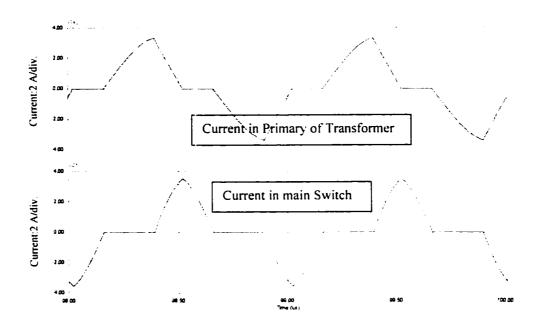

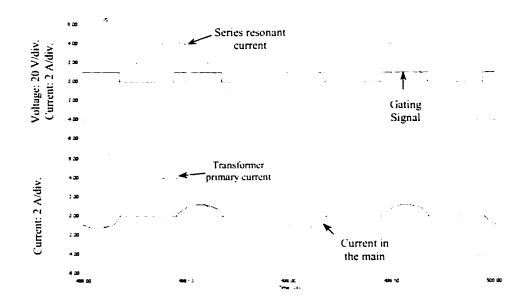

Figure 2- 13: Current in the switches and primary of transformer

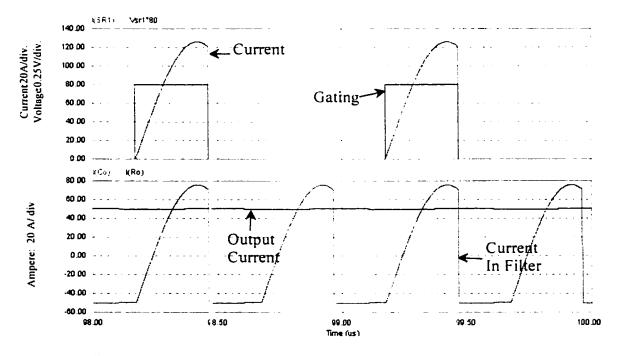

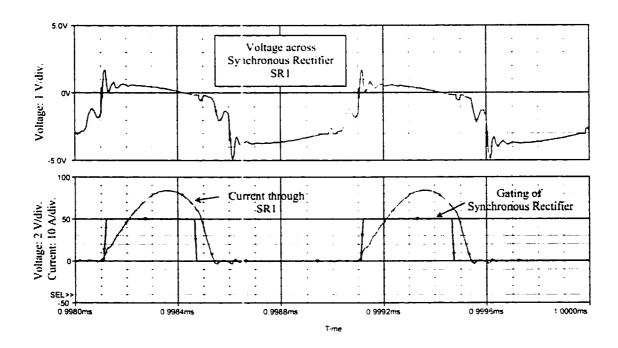

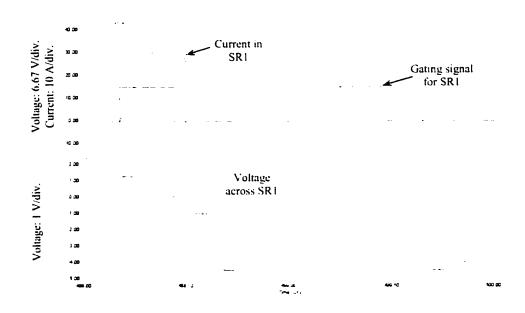

Figure 2- 14: UP; Current in SR<sub>1</sub> and Gating of SR<sub>1</sub>

Down; Current in C<sub>o</sub> and Output Current

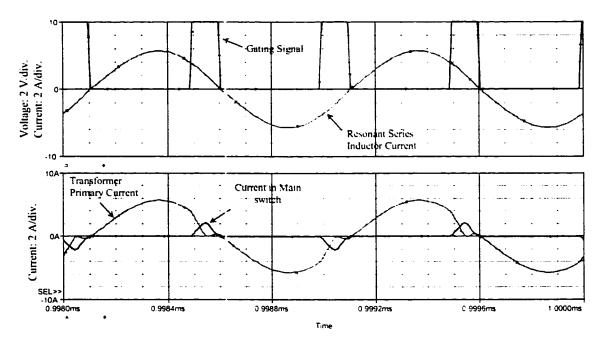

Figure 2-13 shows the current in the switches and primary of the transformer. Due to the fact that the transformer considered to be ideal without any leakage inductance, the current in the primary side of the transformer has a sharp fall, and in the switches has a sharp rise, which in practice it does not occur. This is discussed later in the next chapter.

Figure 2-14 shows the current in the secondary, gating of synchronous rectifier, output current and current in the output filter capacitor.

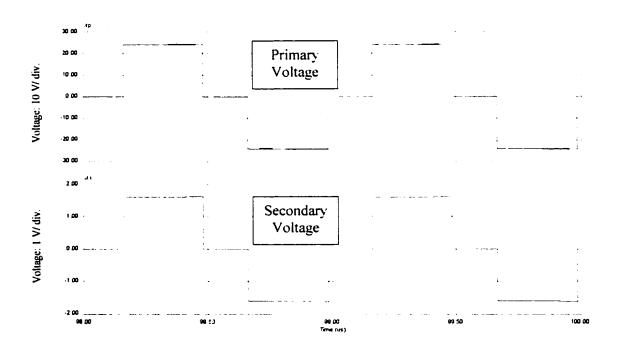

The next simulation is done with considering the leakage inductance, resistance and inductance in series with the switches, ESL and ESR in series with the output filter capacitor without changing any parameters used in previous simulation to compare the result with the simplified simulation. Table 2-2 shows the principle parameters of the circuit used in simulation.

Table2- 2: Principle Parameters of the Simulated Circuit with considering the leakage inductance

| Parameter                   | Value    | Parameter                | Value  |

|-----------------------------|----------|--------------------------|--------|

| $V_{S}$                     | 30 V rms | C <sub>o</sub>           | 480 μF |

| $f_o$                       | 1 MHz    | C <sub>S</sub>           | 6.8 nF |

| $f_{S}$                     | 2 MHz    | L <sub>s</sub>           | 4.4 μΗ |

| k                           | 15:1:1   | C <sub>P</sub>           | 110 nF |

| $R_{ds}$ ( $SR_1 \& SR_2$ ) | 3 mΩ     | $R_{ds}$ ( $Q_1 & Q_2$ ) | 10 mΩ  |

| $L_{sw}$ ( $SR_1 \& SR_2$ ) | 2 nH     | $L_{sw}(Q_1 \& Q_2)$     | 10 nH  |

| $L_{lk}$                    | 0.5 μΗ   | Po                       | 80 W   |

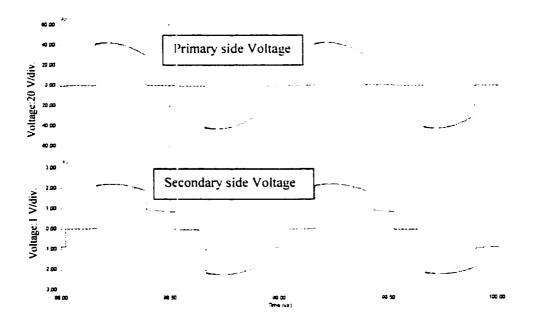

Figure 2- 15: The input voltage and current (up) and output voltage of converter (down)

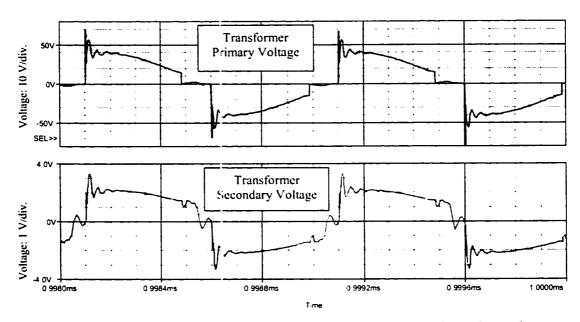

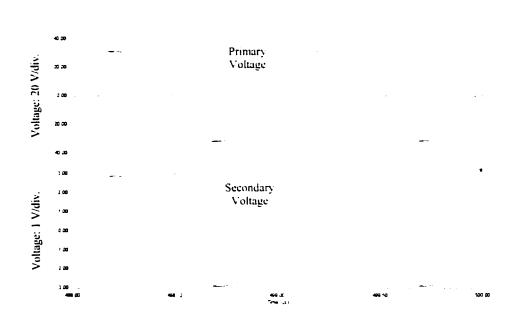

Figure 2- 16: The voltages in the primary (up) and secondary of transformer (down)

Figure 2-17: Current in primary of transformer (down) and the main switches (up)

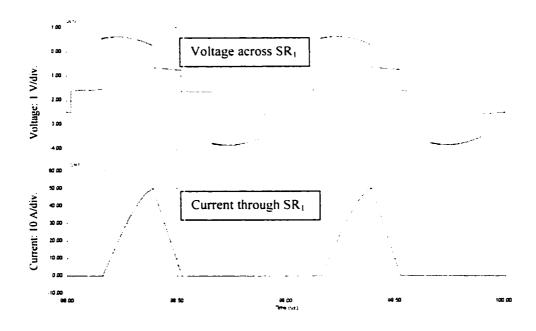

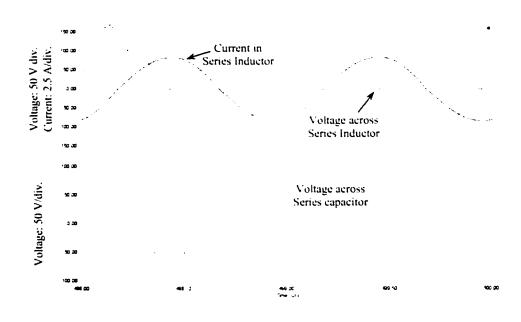

Figure 2- 18: Current and voltage across the synchronous rectification SR1

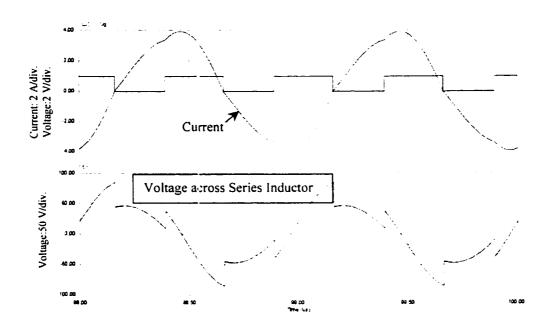

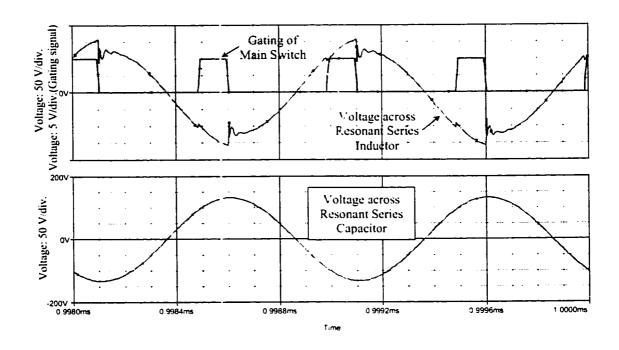

Figure 2- 19: Current in resonant series branch, gating of the main switches (up) and voltage across resonant inductor (down)

### 2.5 Conclusion

Simulation of the proposed converter topology is performed with PSIM software without considering the leakage inductance and with considering it. According to simulation results given in Figure 2-15 to Figure 2-19, it is found that the voltage across the primary side of the transformer was not a quasi-square wave anymore. Also the current in this side didn't have a sharp fall because of the presence of leakage inductance, which is severe in very high frequency. The other important issue is the input current, which was not at the same phase as it was before in the simplified case. Therefore the power factor was not as it is calculated, so the parallel capacitor in the resonant tank is increased to shift the input current and attain better power factor. To get the same output

voltage, either the gating of main switches has to be decreased or the series inductor in resonant network has to be reduced, which has to be compromised. Based on all these dissimilarity, to assume a quasi-square wave in the primary of the transformer, on which the simplified analysis was based, is not valid anymore. Therefore this voltage has to be replaced by a new model with considering the leakage inductance, which leads us to the next chapter.

## **CHAPTER 3**

# EFFECT OF LEAKAGE INDUCTANCE

### 3.1 Introduction

This chapter presents the mathematical analyses of the proposed converter topology with considering the leakage inductance in the primary side of the transformer as well as the inductor and resistor in series with the switches. As seen from the chapter 2, it is assumed that the voltage in the primary side of the transformer is a quasi-square wave, to find out the voltage and current in principle devices and components of converter. But in practice, due to a very high operating frequency, the leakage inductance has significant impact on the performance of the converter and it has to be taken into account in the analyses.

The outline of this chapter is as follows. In Section 3.2, the converter behavior is described under real conditions. In section 3.3, the steady state is performed and an equivalent voltage source to the primary of transformer derived. In section 3.3, the simulation is performed to prove our analysis done in this chapter and to make a comparison between these two cases and the simulation. Finally in section 3.5, a conclusion is drawn.

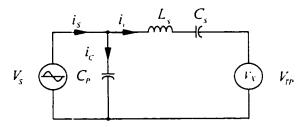

### 3.2 Circuit Description

Figure 3-1 shows the equivalent circuit of the circuit by considering the leakage inductance. The goal in next section is to find out a voltage source to be placed after

resonant network. Therefore, in Section 3.3, an equivalent voltage source to the primary of the transformer is presented.

Figure 3- 1: The equivalent circuit of proposed topology with considering leakage inductance

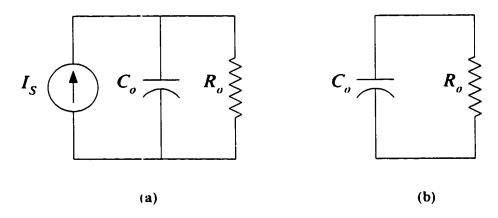

As can be seen in Figure 3-2, the equivalent circuit of proposed topology consists of a resistive load and an inductive load. The resistive load is the resistance in series with the synchronous rectifiers and the load all reflected to the primary side. The inductive load consists of the secondary leakage inductance of the transformer plus inductance in series with synchronous rectifiers all reflected to the primary side added to the leakage inductance in the primary side of the transformer.

### 3.3 Steady State Analysis

This section describes the steady state analyses of the circuit during two switching states. The purpose of this analysis is to obtain the practical characteristics of the converter, which aids in designing the converter.

The analysis is performed with the assumptions made below. Although we take into account the effect of leakage inductance, there is still some assumptions made. In the

analysis, the time varying variables such as the current and voltage of the principle components and devices are determined. Based on these variables, the performance of the converter can be illustrated, and the quantities such as power factor, total harmonic distortion and output voltage can be obtained. These quantities are used to compare with results from Chapter 2, and to design the converter as presented in Chapter 5.

In the analysis presented below, a set of equations is solved in time domain and frequency domain as a function of the control angle  $\alpha$ , the input line voltage  $V_s$  and the output power  $P_o$ .

## 3.3.1 Assumptions and Some Constants For the Analysis

Although the leakage inductance is considered in the analysis, but to perform the steady state analysis, the following assumptions are still made:

- (i) The steady state conditions have been established and the converter is running at an input AC voltage  $V_s$ , producing the nominal output voltage  $V_o$  and delivering a power of  $P_o$  to a static load.

- (ii) The gating of main switches Q<sub>1</sub> and Q<sub>2</sub>, is synchronizing the gating of switches SR<sub>1</sub> and SR<sub>2</sub>,

- (iii) The switching frequency is constant  $f_{ij}$ .

- (iv) All components and devices have ideal properties and characteristics, i.e.,

- (1)  $T_r$ : losses are negligible, and the core does not saturate.

- (2)  $L_s$  Is a pure inductor and its losses are negligible, and its inductance is constant,

- (3)  $C_o$ ,  $C_S$ , and  $C_o$ : all capacitors are pure capacitors, their equivalent series resistance (ESR) and equivalent series inductance (ESL) are negligible,

- (4)  $Q_1$ ,  $Q_2$ ,  $SR_1$ , and  $SR_2$ : all switches have negligible conduction losses, and the inherent capacitances are 0 F.

- (5) The magnetizing inductance of the power transformer is so great that the magnetizing current is negligible.

- (v)  $C_O$  is large enough to maintain constant and ripple free voltage during the steady state operation.

Under these assumptions, the operating principle is illustrated with key waveforms shown in Figure 3-2.

### 3.3.2 Operating Principle

Figure 3-2 shows the operating waveforms. At the position of cycle where  $\omega_0 t = \phi$ ,  $SR_1$  is conducting and the input resonant current  $i_t$  is charging the output capacitor  $C_0$  until  $\omega_0 t = \phi + \alpha$  where the switches  $Q_1$  and  $Q_2$  are turned on. At this time, the input current has to be instantaneously transferred from  $SR_1$  to  $Q_1$  and  $Q_2$  to end the charging period of  $C_0$ . However, due to the leakage inductance in the primary side of the transformer, this current does not go to zero instantaneously. At  $\omega_0 t = \pi + \phi$  the resonant input current flowing through  $Q_1$  and  $Q_2$  goes to zero, thereby the gating signal ends. At this instant,  $SR_2$  conducts and carries the negative input resonant current. The rectification of  $SR_2$  changes the direction of this current at the output and starts the charging of the capacitor

$C_0$ . At  $\omega_0 t = \pi + \phi + \alpha$ , the current flowing through  $SR_2$  must go to zero, because  $Q_1$  and  $Q_2$  are gated on, but the leakage inductance does not allow the current through it to reach zero instantaneously.

Figure 3- 2: Key waveforms of the proposed converter topology. The switching transient is exaggerated.

### 3.3.3 Steady State Analysis

Under the assumptions made, the simplified n<sup>th</sup> harmonic equivalent circuit of the converter is shown in Figure 3-3, which contains two voltage sources.

Figure3-3: The nth harmonic equivalent circuit considering the leakage inductance

The theorem of superposition is used in obtaining the various currents and voltages of the converter circuit. Figure 3-4 (a) shows the equivalent circuit with only the input source  $V_S$ .

Figure3-4: The nth harmonic equivalent circuit considering separated voltage sources

Figure 3-4 (b) shows the equivalent circuit with the only output source  $V_{TP}$ . Therefore, we have to first find out the voltage across the primary of the transformer.

When the main switches are off, the current in the series resonant branch is expressed by:

$$v_{s}(t) = (L_{s} + L_{ik})\frac{di_{t}}{dt} + \frac{1}{C_{s}}\int i_{t}dt + R_{eq}i_{t}$$

(3-1)

where

$$v_s = \sqrt{2}V_s Sin(\omega_a t) \tag{3-2}$$

A particular answer for Equation (3-1) is:

$$i_{i} = E.Cos(\omega_{i}t) + F.Sin(\omega_{i}t)$$

(3-3)

where

$$E = \frac{\sqrt{2} N_s \omega_o}{L_s + L_h} [(\omega_s^2 - \omega_o^2)^2 + (2.5 \omega_o^2)^2]^{-1} (\omega_s^2 - \omega_o^2)$$

(3-4)

$$E = \frac{\sqrt{2} N_s \omega_o}{L_s + L_m} [(\omega_s^2 - \omega_o^2)^2 + (2.5 \omega_o)^2]^{-1} (2.5 \omega_o)$$

(3-5)

and

$$\omega_s = \sqrt{\frac{1}{C_s(L_s + L_n)}} \tag{3-6}$$

$$\xi = \frac{R_{eq}}{2(L_S + L_{lk})} \tag{3-7}$$

The voltage across the primary side of the transformer can be derived by:

$$v_X = L_{lk} \frac{di_i}{dt} + R_{eq} i_i \tag{3-8}$$

This voltage can be expressed by:

$$v_{\lambda} = M.Cos(\omega_{\alpha}t) + N.Sin(\omega_{\alpha}t)$$

(3-9)

where

$$M = R_{aa}.E + L_{\mu}.F.\omega_{\alpha} \tag{3-10}$$

$$N = R_{ca} \cdot F - L_{\mu} \cdot E \cdot \omega_{\alpha} \tag{3-11}$$

In all the above derived equations, we have:

$$R_{eq} = \frac{8}{\pi^2} \cdot (\frac{N_1}{N_2})^2 (R_o + R_{SR_1})$$

(3-12)

Finally, the voltage in the primary side of the transformer can be expressed as:

$$v_{TP}(t) = \begin{cases} v_{x} & \phi < t < \phi + \alpha \\ 0 & \phi + \alpha < t < \phi + \pi \\ v_{x} & \phi + \pi < t < \phi + \pi + \alpha \\ 0 & \phi + \pi + \alpha < t < \phi + 2\pi \end{cases}$$

(3-13)

For convenience, some constants are defined below. In the steady state, the parallel and series impedance for the fundamental and n<sup>th</sup> harmonics are determined by:

$$Z_{s1} = j\omega_{o}L_{s} - j\frac{1}{\omega_{o}C_{s}} = j(X_{Ls} - X_{C_{s}})$$

(3-14)

$$Z_{Sn} = njX_{Ls} - \frac{jX_{Cs}}{n}$$

(3-15)

$$Z_{P1} = -j \frac{1}{\omega_{o} C_{P}} = -j X_{C_{P}}$$

(3-16)

$$Z_{p_n} = \frac{-jX_{Cp}}{n}$$

(3-17)

Since the input voltage source  $V_S$  is sinusoidal and contains no harmonics, it is presented by the Equation (3-2).

The input current due to source  $V_S$  is given by:

$$i_{S1} = \frac{v_S}{Z_{t1}} = \frac{\sqrt{2}V_S Sin(\omega_0 t)}{-j|Z_{t1}|} = \frac{\sqrt{2}V_S}{|Z_{t1}|} Cos(\omega_0 t)$$

(3-18)

Where:

$$Z_{tt} = \frac{-jX_{Cp} \cdot j(X_{Ls} - X_{Cp})}{-jX_{Cp} + j(X_{Ls} - X_{Cs})} = \frac{-j[X_{Cp} \cdot (X_{Ls} - X_{Cs})]}{(X_{Ls} - X_{Cs} - X_{Cp})}$$

(3-19)

The Fourier series of the transformer primary voltage can be expressed by:

$$v_{TP} = \sum_{n=1,2}^{\infty} (a_n.Cos(n\omega_n t) + b_n.Sin(n\omega_n t))$$

(3-20)

where

$$a_n = \frac{1}{\pi} \int_{0}^{0.2\pi} v_{TP}(t) . Cos(n\omega_0 t) dt$$

$$= \frac{Q}{2\pi} \left\{ \frac{-Cos[(n+1)(\phi+\alpha)-\beta]}{n+1} + \frac{-Cos[(1-n)(\phi+\alpha)-\beta]}{1-n} + \frac{Cos[(n+1)\phi-\beta]}{n+1} \right\}$$

$$+\frac{Cos[(1-n)\phi-\beta]}{1-n}+\frac{-Cos[(1+n)(\phi+\pi+\alpha)-\beta]}{1+n}+\frac{-Cos[(1-n)(\phi+\pi+\alpha)-\beta]}{1-n}$$

$$+\frac{Cos[(n+1)(\phi+\pi)-\beta]}{n+1} + \frac{Cos[(1-n)(\phi+\pi)-\beta]}{1-n}$$

(3-21)

and

$$b_n = \frac{1}{\pi} \int_{0}^{0.2.\pi} v_{TP}(t).Sin(n\omega_0 t) dt$$

$$= \frac{Q}{2\pi} \left\{ \frac{Sin(1-n)(\phi+\alpha)-\beta}{1-n} + \frac{-Sin[(1+n)(\phi+\alpha)-\beta]}{1+n} + \frac{-Sin[(1-n)\phi-\beta]}{1-n} \right\}$$

$$+\frac{Sin[(n+1)\phi - \beta]}{n+1} + \frac{Sin[(1-n)(\phi + \pi + \alpha) - \beta]}{1-n} + \frac{-Sin[(1+n)(\phi + \pi + \alpha) - \beta]}{1+n} + \frac{-Sin[(1-n)(\phi + \pi) - \beta]}{1-n} + \frac{Sin[(1+n)(\phi + \pi) - \beta]}{1+n}$$

(3-22)

where

$$Q = \sqrt{M^2 + N^2} \tag{3-23}$$

The input current due to source  $v_{TP}$  is given by:

$$i_{S2} = \sum_{n=1,2}^{\infty} \left( \frac{a_n}{|Z_{Sn}|} Cos(n\omega_0 t) + \frac{b_n}{|Z_{Sn}|} Sin(n\omega_0 t) \right)$$

(3-24)

The total input current is given by:

$$i_{S} = \frac{\sqrt{2}V_{S}}{|Z_{t1}|}Cos(\omega_{0}t) + \sum_{n=1...}^{\infty} \left(\frac{a_{n}}{|Z_{Sn}|}Cos(n\omega_{0}t) + \frac{b_{n}}{|Z_{Sn}|}Sin(n\omega_{0}t)\right)$$

(3-25)

### (i) Determination of Angle $\phi$ :

The following equation shows the current in the series branch of resonant network due to the source  $V_S$ :

$$i_{i1} = \frac{v_s}{Z_{s1}} = \frac{\sqrt{2}V_s Sin(\omega_o t)}{j|Z_{s1}|} = \frac{-\sqrt{2}V_s}{|Z_{s1}|} Cos(\omega_o t)$$

(3-26)

And the current in the same branch due to the output source  $V_{TP}$  is given by:

$$i_{i2} = i_{S2} = \sum_{n=1,2}^{\infty} \left( \frac{a_n}{|Z_{Sn}|} Cos(n\omega_0 t) + \frac{b_n}{|Z_{Sn}|} Sin(n\omega_0 t) \right)$$

(3-27)

So the resonant current in this branch according to theorem of superposition is:

$$i_{t} = i_{t1} + i_{t2}$$

$$= \frac{-\sqrt{2}V_{S}}{|Z_{S1}|} Cos(\omega_{o}t) + \sum_{n=1,2}^{\infty} (\frac{a_{n}}{|Z_{Sn}|} Cos(n\omega_{o}t) + \frac{b_{n}}{|Z_{Sn}|} Sin(n\omega_{o}t))$$

(3-28)

The resonant Current is  $i_i = 0$  at  $\omega_0 t = \phi$ , therefore from Equation (3-28) the following relations are obtained:

$$\frac{-\sqrt{2}V_{S}}{\left|Z_{S1}\right|}Cos\phi + \sum_{n=1,2}^{\infty} \left(\frac{\alpha_{n}}{\left|Z_{Sn}\right|}Cos(n\phi) + \frac{b_{n}}{\left|Z_{Sn}\right|}Sin(n\phi)\right) = 0$$

$$Cos\phi = \frac{\sqrt{2}}{2} \sum_{n=1,2}^{\infty} \left( \frac{|Z_{S1}|}{|Z_{Sn}|} \frac{c_n}{V_S} Cos(n\phi) + \frac{|Z_{S1}|}{|Z_{Sn}|} \frac{b_n}{V_S} Sin(n\phi) \right)$$

(3-29)

For a given control angle  $\alpha$ , the value of  $\phi$  would have been calculated by using Equation (3-29), if the value of  $\frac{V_O}{V_S}$  were known. The value of  $\frac{V_O}{V_S}$  can be obtained by setting the input power equal to the output power.

Since the input voltage source contains no harmonics, the product of the fundamental input current, the input voltage and the fundamental cosine angle between the two determines the input power, which leads us to the next sub-section.

### (ii) Output Voltage Control:

Output voltage control is provided by controlling the current controller pulse width (gating of  $Q_1$  and  $Q_2$ ) other word angle  $\alpha$ .

By substituting n = 1 the fundamental time-varying input current from Equation (3-25) is given by:

$$i_{sf} = \frac{\sqrt{2} \cdot V_s}{|Z_{t1}|} Cos(\omega_0 t) + \frac{a_1}{|Z_{s1}|} Cos(\omega_0 t) + \frac{h_1}{|Z_{s1}|} Sin(\omega_0 t)$$

(3-30)

where

$$a_1 = \frac{Q}{2\pi} \left[ -Cos(2\phi + 2\alpha - \beta) - 2(\phi + \alpha)Sin\beta + Cos(2\phi - \beta) + 2\phi.Sin\beta \right]$$

(3-31)

$$b_1 = \frac{Q}{2\pi} \left[ -Sin(2\phi + 2\alpha - \beta) + 2(\phi + \alpha)Cos\beta + Sin(2\phi - \beta) - 2\phi.Cos\beta \right]$$

(3-32)

The fundamental time-varying current from Equation (3-30) can be simplified by:

$$i_{s} = C.Sin(\omega_{0}t + \theta) \tag{3-33}$$