#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## FPGA Design and Implementation of Systolic Array-Based Viterbi Decoders

Man Guo

A Thesis

in

the Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada

September 2002

@Man Guo, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawe ON K1A 0N4 Cenade Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-72909-5

#### **ABSTRACT**

## FPGA Design and Implementation of Systolic Array-Based Viterbi Decoders

#### Man Guo

The Viterbi algorithm is known to provide an efficient method for the maximum like-lihood decoding of convolutional codes. The algorithm can be formulated by employing a matrix-vector computation and it can be implemented in hardware based on a systolic array architecture. It has been shown that in this implementation, the strongly-connected trellis decoding method can be used to improve the efficiency of the hardware utilization and the throughput of the decoding. However, the employment of the strongly-connected trellis decoding method results in an excessive amount of ACS (addition, comparison and selection) computations in the decoding process as the constraint length becomes large. Further, in the systolic array architecture, the hardware complexity increases exponentially with the constraint length of the code. This makes the adoption of the systolic array architecture not feasible in the design of the Viterbi decoder for decoding a convolutional code with a large constraint length.

In this thesis, a design and FPGA implementation of a Viterbi decoder with a constraint length of 9 and code rate of 1/2 is presented. In this design, a novel systolic array architecture with time multiplexing, arithmetic pipelining and clock-to-data skews tolerance is developed. Further, by modifying this Viterbi algorithm, an adaptive Viterbi algorithm that is based on strongly-connected trellis decoding is proposed.

Using the proposed adaptive algorithm, a design and FPGA implementation of a low-power adaptive Viterbi decoder with a constraint length of 9 and code rate of 1/2 is presented. The systolic array-based architecture used in this adaptive Viterbi decoder is a modified version of the architecture used for the non-adaptive Viterbi decoder in that the latter is modified to include the modules, which are needed for generating the survivor information and for eliminating the spurious toggles in the adaptive Viterbi decoding process. It is shown that the proposed algorithm can reduce up to 70% the average number of ACS (addition, comparison, and selection) computations over that by using the non-adaptive Viterbi algorithm, without a degradation in the error performance. This results in lowering the switching activities of the logic cells, with a consequent reduction in the dynamic power. Further, it is shown that the total power consumption in the implementation of the proposed algorithm can be reduced by up to 43% compared to that in the implementation of the non-adaptive Viterbi algorithm, with a negligible increase in the hardware.

#### **ACKNOWLEGEMENTS**

First and foremost, I would like to thank my supervisors, Dr. Omair Ahmad and Dr. M.N.S. Swamy, for giving me the opportunity to work on this thesis project. Their insight, valuable advice and guidance throughout this study have contributed significantly to this research. Moreover, without the financial support from my supervisors, it would have been extremely difficult to accomplish this investigation. I gratefully acknowledge the support of Micronet, a National Network of Centres of Excellence, through a research grant awarded to Drs. Ahmad and Swamy.

I am greatly indebted to my parents for their love and care, and for their constant support and encouragement throughout my education.

I am very grateful to my husband, Jiyao, and my son, Yiran, for their love and sacrifices, and for providing me encouragement and inspiration during my graduate study at Concordia University.

I would like to specially thank Ted Obuchowicz and Wojciech Galuszka for providing me the help and technical support in the VLSI lab. I would also like to express my fond appreciation to Yi Yang, Wei Wang, and many other friends and colleagues for support and encouragement during my graduate study at Concordia University.

## TABLE OF CONTENTS

|                                                                          | ix   |

|--------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                          |      |

| LIST OF TABLES                                                           |      |

| LIST OF ACRONYMS                                                         |      |

| LIST OF SYMBOLS                                                          | xiii |

|                                                                          | 1    |

| CHAPTER 1. INTRODUCTION                                                  |      |

| 1.1 Introduction                                                         |      |

| 1.2 Architectures for Implementation of aViterbi Decoder                 | 2    |

| 1.2.1 Butterfly Architecture                                             | 2    |

| 1.2.2 Systolic Array Architecture                                        | 5    |

| 1.3 Approaches to Reduce Power Consumption                               | 8    |

| 1.4 Scope of the Thesis                                                  | 9    |

| 1.5 Organization of Thesis                                               | 11   |

| CHAPTER 2. A VITERBI ALGORITHM FOR THE STRONGLY CONNECTED                |      |

| TRELLIS DECODING                                                         | 13   |

| 2.1 Introduction                                                         | 13   |

| 2.2 Encoding of Convolutional Codes                                      | 14   |

| 2.3 Viterbi Decoding Process                                             | 18   |

| 2.4 Strongly-Connected Trellis Decoding Method                           | 20   |

| 2.5 Reformulation of the Conventional Viterbi Algorithm for the strongly |      |

| connected trellis decoding                                               | 21   |

| 2.5.1 Generation of Composite Branch Metric                              | 21   |

| 2.5.2 Updating of Path Metrics                                           | 25   |

| 2.5.2 Updating of Path Metrics                                           |      |

| 2.5.3 Modulo Arithmetic for ACS                                               | 26  |

|-------------------------------------------------------------------------------|-----|

| 2.5.4 Radix-2 <sup>K-1</sup> Trellis Trace-Back Update                        | 27  |

| 2.6 Summary                                                                   | 29  |

| CHAPTER 3. DESIGN AND IMPLEMENTATION OF A VITERBI DECODER                     |     |

| 3.1 Introduction                                                              | 31  |

| 3.2 Systolic Array Architecture for ACS Computations                          | 33  |

| 3.2.1 Adjacency Matrix Partitioning and Time Multiplexing                     | 33  |

| 3.2.2 Arithmetic-Pipelining Technique and Array Processors                    |     |

| 3.2.3 Clock-to-Data Skew and a Scheme for its Avoidance                       |     |

| 3.3 Trace-Back Strategy and Trace-Back Unit                                   | 45  |

| 3.3.1 Trace-Back Strategy                                                     |     |

| 3.3.2 Trace-Back Unit                                                         | 49  |

| 3.4 Input Buffer and One-Stage Branch Metric Generation                       | 50  |

| 3.5 Testability of the Design                                                 | 53  |

| 3.7 Performance Analysis                                                      |     |

| 3.7.1 Speed                                                                   |     |

| 3.7.2 Power                                                                   |     |

| 3.7.3 FPGA Resources Utilization                                              | 60  |

| 3.8 Summary                                                                   | 60  |

| CHAPTER 4. AN ADPTIVE VITERBI DECODING ALGORITHM                              | 63  |

| 4.1 Introduction                                                              | 63  |

| 4.2 Formulation of the Proposed Adaptive Viterbi Algorithm                    | 65  |

| 4.3 Comparisons with the Non-Adaptive Viterbi Algorithm                       | 69  |

| 4.4 Summary                                                                   |     |

| CHAPTER 5. DESIGN AND IMPLEMENTATION OF                                       |     |

| AN ADAPTIVE VITERBI DECODER                                                   |     |

| 5.1 Introduction                                                              |     |

| 5.2 Systolic Array-based Architecture and Spurious Toggle Reduction           |     |

| 5.3 Performance Analysis and Comparison with the Non-Adaptive Viterbi Decodie | r80 |

| 5.3.1 Speed                               | 81 |

|-------------------------------------------|----|

| 5.3.2 Power                               |    |

| 5.3.3 FPGA Resources Utilization          |    |

| 5.4 Summary                               |    |

| CHAPTER 6. CONCLUSION                     |    |

| 6.1 Summary and Conclusions               |    |

| 6.2 Suggestions for Future Investigations |    |

| APPENDIX                                  |    |

| REFERENCES                                |    |

|                                           |    |

## LIST OF FIGURES

| Figure 1.1 | A trellis diagram (K=3) and two butterfly pairs             |

|------------|-------------------------------------------------------------|

| Figure 1.2 | Butterfly structure of an ACS module4                       |

| Figure 1.3 | A strongly-connected trellis diagram5                       |

| Figure 1.4 | A systolic architecture for a Viterbi decoder with K=36     |

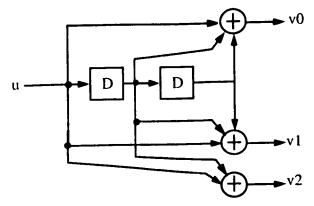

| Figure 2.1 | A (3, 1, 2) binary convolutional encoder15                  |

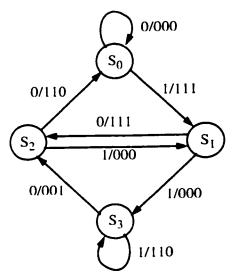

| Figure 2.2 | State diagram for an encoder                                |

| Figure 2.3 | Trellis diagram for a (3, 1, 2) code with L=517             |

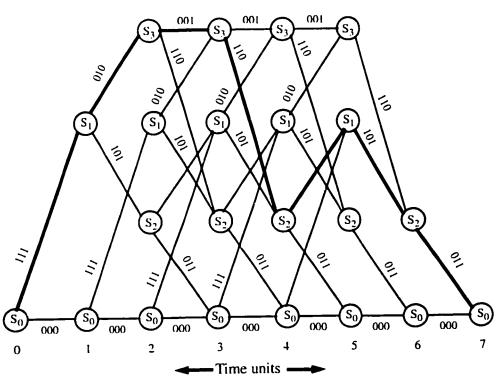

| Figure 2.4 | Convolutional coded system on an additive white gaussian    |

|            | noise channel                                               |

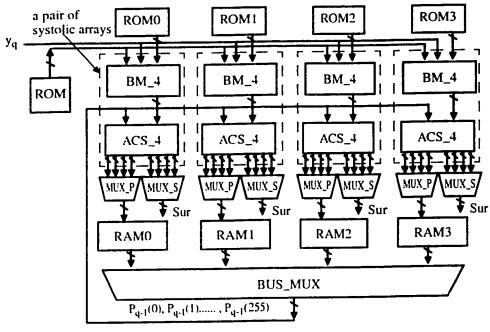

| Figure 3.1 | Systolic array architecture for path metric update34        |

| Figure 3.2 | Architecture of a pair of systolic arrays34                 |

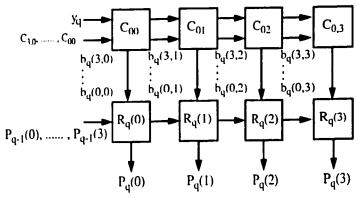

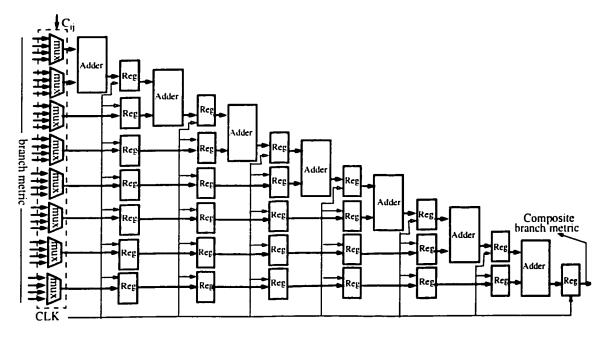

| Figure 3.3 | Arithmetic pipelining processor for a BM_437                |

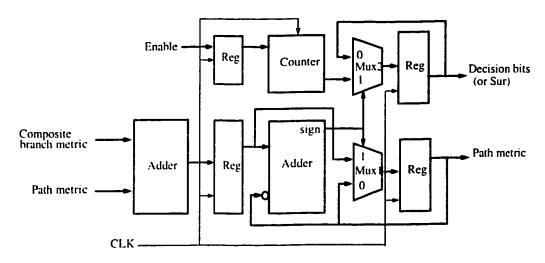

| Figure 3.4 | Arithmetic pipelining processor for a ACS_439               |

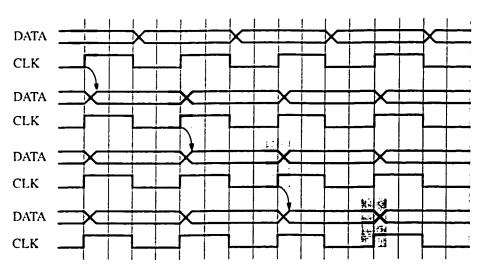

| Figure 3.5 | Trace length mismatches causing clock-to-data skew41        |

| Figure 3.6 | Timing diagram without clock-to-data skew tolerance43       |

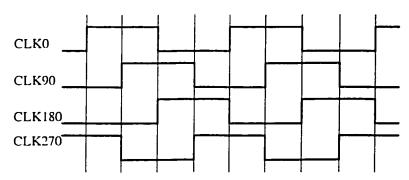

| Figure 3.7 | Clock outputs characteristics                               |

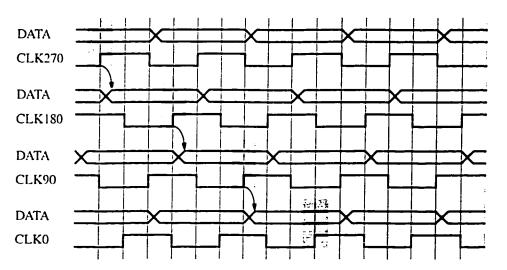

| Figure 3.8 | Timing diagram with clock-to-data skew tolerance45          |

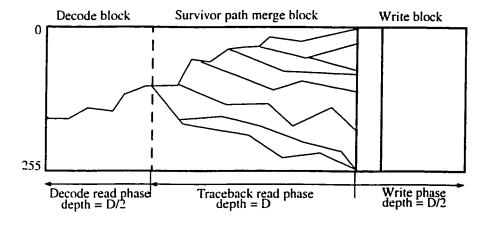

| Figure 3.9 | Organization of the memory for storing the survivor paths46 |

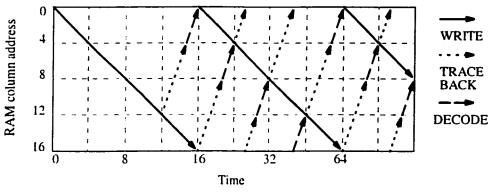

| Figure 3.10 | Trace-back strategy                                                                | 48 |

|-------------|------------------------------------------------------------------------------------|----|

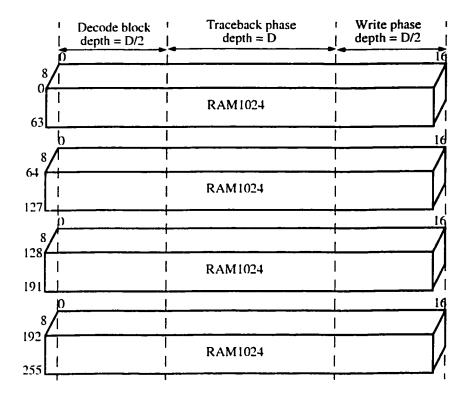

| Figure 3.11 | Survivor path memory structure                                                     | 49 |

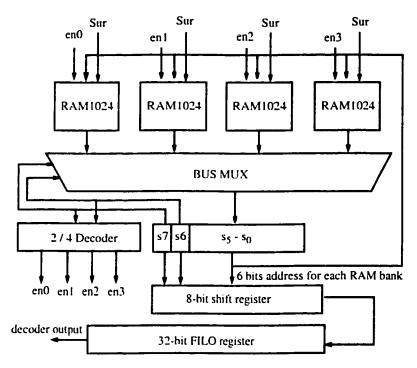

| Figure 3.12 | Architecture of the trace-back unit                                                | 50 |

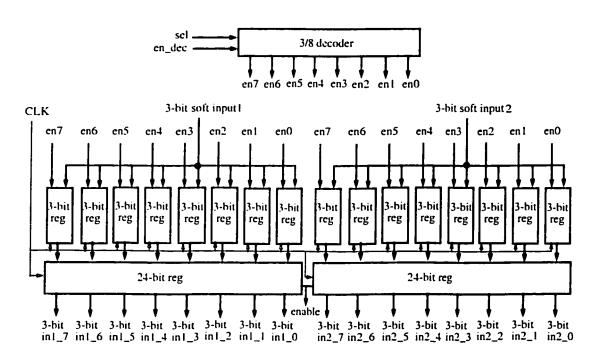

| Figure 3.13 | Input buffer for the two soft inputs                                               | 51 |

| Figure 3.14 | Eight one-stage branch metrics generation unit                                     | 52 |

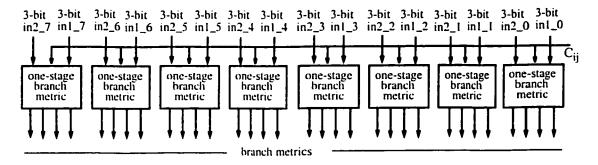

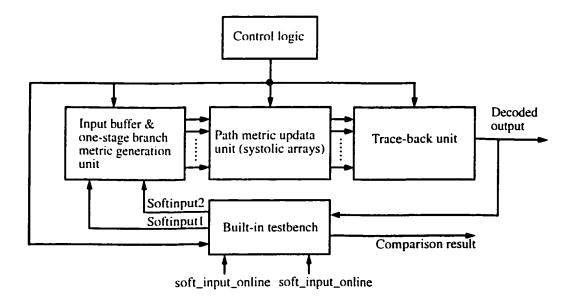

| Figure 3.15 | Architecture of the built-in testbench                                             | 53 |

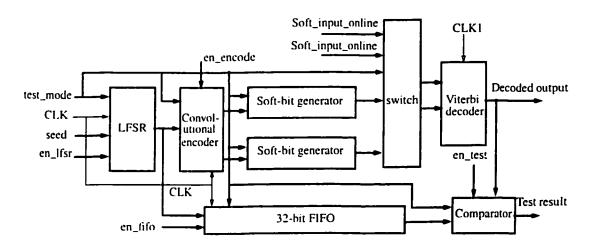

| Figure 4.1  | Error performance for coded and uncoded binary data                                | 70 |

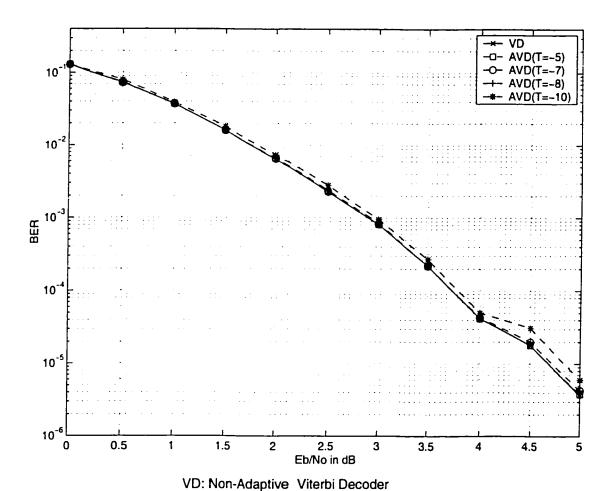

| Figure 4.2  | Performance of the bit-error (BER) as a function of E <sub>b</sub> /N <sub>o</sub> | 71 |

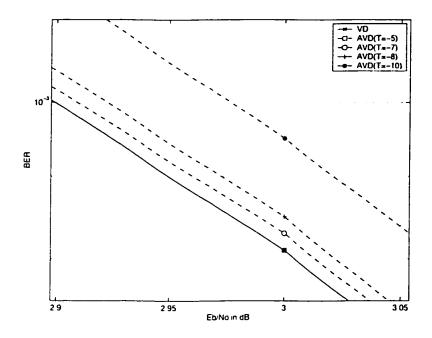

| Figure 4.3  | An expanded form of Figure 4.2 in range of E <sub>b</sub> /N <sub>o</sub>          |    |

|             | from 2.9 dB to 3.05 dB                                                             | 72 |

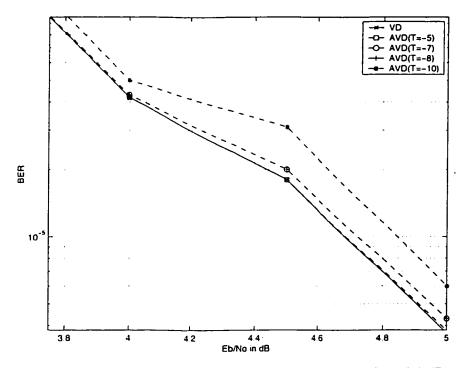

| Figure 4.4  | An expanded form of Figure 4.2 in range of E <sub>b</sub> /N <sub>o</sub>          |    |

|             | from 3.8 dB to 5 dB                                                                | 72 |

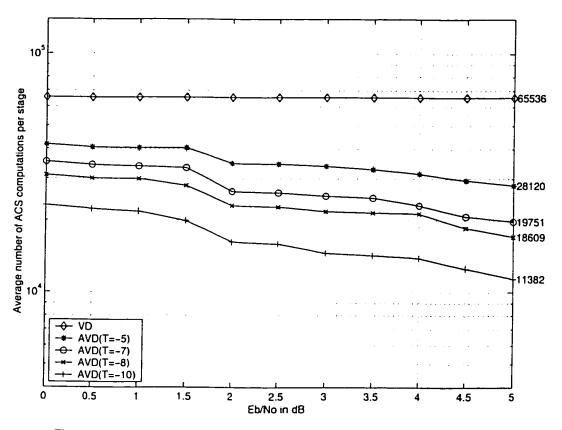

| Figure 4.5  | Average number of ACS computations per stage over E <sub>b</sub> /N <sub>o</sub>   |    |

| Figure 5.1  | Block diagram of the adaptive Viterbi decoder                                      | 77 |

| Figure 5.2  | Systolic array-based architecture for an adaptive Viterbi decoder                  | 79 |

## LIST OF TABLES

| Table 3.1 | Relationship of phase-shifted output clock to period shift          | 44 |

|-----------|---------------------------------------------------------------------|----|

| Table 3.2 | One-stage branch metric evaluation                                  | 52 |

| Table 3.3 | Device quiescent power estimator result                             | 57 |

| Table 3.4 | CLB logic power estimator results                                   | 57 |

| Table 3.5 | Block selectRAM power estimator results                             | 58 |

| Table 3.6 | DCM power estimator result                                          | 59 |

| Table 3.7 | Input/output power estimator result                                 | 59 |

| Table 3.8 | Power estimator results                                             | 59 |

| Table 5.1 | CLB logic power estimator results for the adaptive Viterbi decoder  | 82 |

| Table 5.2 | Power and average toggle rate in CLB logic for the conventional and |    |

|           | adaptive Viterbi decoders                                           | 83 |

| Table 5.3 | Power estimator results for the adaptive Viterbi decoder            | 84 |

| Table 5.4 | Power consumption for the conventional and adaptive                 |    |

|           | Viterbi decoders                                                    | 84 |

| Table 5.5 | FPGA resources utilization for the conventional and                 |    |

|           | adaptive Viterbi decoders                                           | 85 |

## LIST OF ACRONYMS

ASIC: Application Specific Integrated Circuit

AWGN: Additional White Gaussian Noise

ACS: Addition, Comparison, and Selection.

BER: Bit Error Rate

**BPSK:** Binary Phase Shift Key

**CDMA:** Code Division Multiple Access

**DFF:** D-type flip-flop

FPGA: Field Programmable Gate Array

FEC: Forward Error Correction.

FIFO: First-In First-Out

**LUT:** Look-Up Table

LIFO: Last-In First-Out

RAM: Random Access Memory

**ROM:** Read Only Memory

## LIST OF SYMBOLS

$\mathbf{B}_{\mathbf{q}}$ : Adjacency matrix in the matrix-vector ACS computation

$b_q(i, j)$ : The composite branch metric from state i of stage q-1 to state j of stage q of the strongly-connected trellis diagram

Cij: The codeword sequence corresponding to the composite branch

$C_{ij}[k]$ : The k-th element of  $C_{ij}$

C<sub>i0</sub>: The codeword sequences with zero input sequence

$C_{0i}$ : The codeword sequences with zero encoder state

$C_{\mbox{\scriptsize OUTavg}}$ : The average load capacitance

$d_m^q$ : The minimum distance of all the survivor paths

$d_n^S$ : The survivor decision of state  $S_n$

$d_{n,n-1}$ : The composite 2-bit radix-4 decision

$d_{n, n-1, \dots, n-(K-2)}$ : The composite (K-1)-bit radix- $2^{(K-1)}$  decision

F<sub>MAX</sub>: Clock frequency

K: Constraint length of a convolutional code

k: The number of inputs in a convolutional encoder

K<sub>P</sub>: A constant whose value depends on the family of FPGA

m: The number of stages in the shift register used for a convolutional encoder

$min^{-1}$ : The operation of finding the state number in the (q-1)-th stage that yields the minimum distance of the paths at state j of state q

min: The operation of taking the minimum distance of the paths at state j of state q

n: The number of outputs in a convolutional encoder

N: The number of states in a trellis diagram

N<sub>LC</sub>: The number of the logic cells used by the application, F<sub>MAX</sub> the clock frequency

$N_{OUT}$ : The number of outputs in the design

**P**<sub>q</sub>: Path metric row vector in the matrix-vector ACS computation

$p_q(j)$ : The partial path metric from the initial state 0 to state j of stage q of the trellis diagram

P<sub>STAT</sub>: Static power consumption resulting from leakage current by an inactive device connected to the power supply

P<sub>INT</sub>: Internal power dissipation caused by the charging and discharging the capacitance on any internal nodes that are switched

P<sub>IO</sub>: Input and output power dissipation resulting from the charging and discharging of the external load capacitors connected to device pins, and the pull-ups used on the inputs

r: Code rate of a convolutional code

$Sur_q(j)$ : The survivor at state j of stage q

Vcc: Supply voltage

V swing: Output swing voltage

$S_n$ : An arbitrary state of stage n

$S_q(j)$ : The survivor information at the q-th stage

Tog<sub>I,C</sub>: Average toggling rate at each clock

Tog<sub>OUT</sub>: Average toggling rate of the output at each clock

$'\otimes'$ : The ACS operation according to the likelihood criterion

$\Delta_{max}$ : The maximum dynamic range of path metric in the conventional Viterbi algorithm

$\lambda_{max}$ : The maximum branch metric.

$\Gamma_{bit}$ : The worldlength of a path metric

### CHAPTER 1

## **INTRODUCTION**

#### 1.1 Introduction

Convolutional codes are a type of basic error correction codes whose encoding process can be viewed as convolving the message stream with the impulse response of the code. The Viterbi algorithm [1] is known to be an efficient method for maximum likelihood decoding of convolutional codes over a memoryless noise channel. Convolutional codes and the Viterbi algorithm provide a strong forward error correction (FEC) scheme, which has been widely utilized in digital communication applications. It has been shown that the larger the constraint length K used in a convolutional encoding process, the more powerful the code produced. Thus, a convolutional code with a relatively large constraint length of K = 9 is used for the IS-95 code-division multiple access (CDMA) wireless communication standard [2]. The use of a large constraint-length convolutional code, on one hand, can provide a better error correction performance. On the other hand, the complexity of the Viterbi decoding process, both in terms of computations and memory requirements, increases exponentially with the constraint length K of the code. As a result, it would be

difficult to have a hardware implementation of a Viterbi decoder with a large constraint length, such as K=9, to meet the requirements of the power, speed and area. In recent year, Viterbi decoders have been mostly used in mobile systems that require portable battery operations, thus making the power consumption a critical concern to the designers.

The focus of this thesis is on a study of low-power design of a Viterbi decoder. In this chapter, first the currently available architectures for a Viterbi decoder are first reviewed, and then the challenges by employing these architecture to design and implement a large constraint-length Viterbi decoder are discussed. Next, the existing approaches for low-power design of the Viterbi decoders with K=9 are analyzed. Finally, the scope and organization of the thesis are presented.

#### 1.2 Architectures for Implementation of a Viterbi Decoder

Designing an appropriate architecture plays a major role in achieving an efficient hardware implementation of a Viterbi decoder. In this section, two types of Viterbi decoder architectures, namely, the butterfly architecture and the systolic array architecture, are reviewed and discussed in order to propose a novel Viterbi decoder architecture in a later chapter.

#### 1.2.1 Butterfly Architecture

Viterbi algorithm can be viewed as a process which finds the shortest path in a trellis diagram [3] to match the received sequence by a dynamic programming technique [4]. A trellis diagram is obtained by expanding the state diagram of a convolutional encoder in

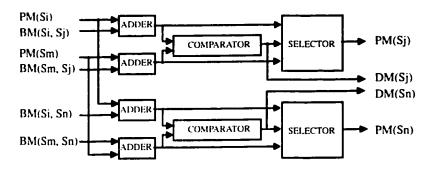

time, and it can be decomposed into butterfly state-pairs in which each pair of its origin and destination states are interconnected together. Figure 1.1 shows an example of a trellis diagram with K=3 and its decomposed butterfly state-pairs. Decomposing a trellis into butterfly state-pairs is straightforward, and it does not change the interconnections of the trellis. Therefore, the commonly used Viterbi decoders are designed based on the butterfly architecture in which each butterfly state-pair in a trellis is processed by a module that performs three operations: addition, comparison, and selection (ACS). This module is usually called ACS butterfly module, shown in Figure 1.2 [5, 6]. In this module, each of the four

Figure 1.1 A trellis diagram (K = 3) and two butterfly pairs

adders is used to compute one of the four path metrics at stage q+1 by adding the branch metric corresponding to one of the four butterfly interconnected branches to the corresponding path metric at stage q. Then, each of the two comparators is used to make a comparison between the two computed path metrics at the state of stage q+1. Finally, each of the two selectors is used to select the path metric with the shortest distance (Euclidean or

Hamming distance) at the state of stage q+1 depending on the comparison result by the corresponding comparator.

BM(Si, Sj), BM(Sm, Sj), BM(Si, Sn) and BM(Sm, Sn): Branch Metric

PM(Si), PM(Sm): Path Metric of state Si and state Sm DM(Sj), DM(Sn): Decisions of state Sj and state Sn

Figure 1.2 Butterfly structure of an ACS module

The butterfly architecture-based Viterbi decoders can be categorized into two classes; serial and parallel. A serial Viterbi decoder sequentially processes the ACS computations at each trellis stage by iteratively using one ACS butterfly module. On the other hand, in a parallel Viterbi decoder, ACS butterfly modules corresponding to all butterfly state-pairs in a trellis diagram are designed to process the ACS computations simultaneously. Obviously, a serial Viterbi decoder can be advantageous from the viewpoint of power dissipation and hardware complexity. However, the number of states per trellis stage increases exponentially with the constraint length K of a code. If a serial architecture is used to implement a large constraint-length Viterbi decoder, there will be a large number of iterations for the ACS computations at each trellis stage. As a result, the speed of a serial Viterbi decoder will be greatly slowed down. On the contrary, a parallel Viterbi decoder is no

doubt able to achieve a high-speed decoding due to its parallel computations. However, for decoding a convolutional code with a large K, a large number of components should be involved to process ACS computations, and the interconnections between components will become very complex. Consequently, the amount of power dissipation and hardware resources (area) would increase exponentially.

#### 1.2.2 Systolic Array Architecture

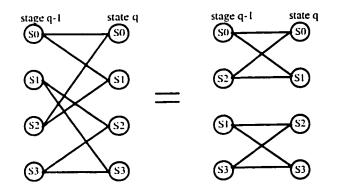

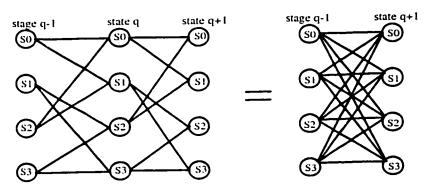

Unlike the serial and parallel architectures that are designed by decomposing states in a conventional low-connectivity trellis diagram into butterfly pairs, a systolic array architecture suggested by Chang and Yao [7] is derived by formulating the Viterbi algorithm employing matrix-vector multiplication. Since the adjacency matrix in this formulation is very sparse, the utilization of the array processors in this systolic architecture is rather poor. In order to resolve this problem, Chang and Yao also proposed the strongly-connected trellis decoding in [7]. As shown in Figure 1.3, a strongly-connected trellis diagram

Figure 1.3 A strongly-connected trellis diagram

is obtained by merging the stages in each group of (K-1) stages in the original low-connectivity trellis, in such a way that every state in the (K-1)-th stage of the group is reachable from the states of the preceding (K-2) stages of the group. Obviously, by using strongly-connected trellis decoding method, the adjacency matrix in the matrix-vector formulation is no longer sparse. As a result, the utilization of systolic array processors as well as the throughput of the decoding can be enhanced

Figure 1.4 A systolic architecture for a Viterbi decoder with K=3

Figure 1.4 shows the systolic array architecture for a Viterbi decoder with K=3 presented in [7]. This is derived by employing the systolic array architecture for processing a matrix-vector multiplication [8]. The modification carried out in this architecture is that array processors do not perform multiplications, but process ACS computations in order to find the shortest path in a trellis diagram. The matrix-vector ACS computation in [7] is given as  $P_q = P_{q-1} \otimes B_q$ , where  $P_q$  represents the path metric row vector of the q-th stage, whose j-th element is denoted by  $P_q(j)$ , and  $P_q$  the adjacency matrix whose ij-th element is denoted by  $P_q(j)$ . This matrix-vector ACS computation is processed by two interconnected linear

systolic arrays. In the upper systolic array, the composite branch metric  $b_q(i, j)$  is generated by calculating the Euclidean distance between the codeword  $C_{ij}$  and the received data  $y_q$ , where  $C_{ij} = C_{i0} \oplus C_{0j}$ , and i, j = 0,..., 3 [7]. The codeword  $C_{0j}$  stays inside each processor, and  $C_{i0}$  moves to the right. In the lower systolic array, the path metric  $P_q(j)$  of stage q is computed. The intermediate ACS result denoted by  $R_q(j)$  stays inside the j-th processor, whereas  $P_{q-1}(j)$  of stage q-1 moves to the right. All data movements in the two systolic arrays are synchronized. This design can thus be viewed as a "result stay" systolic array architecture.

It is seen that the systolic array architecture presented in [7] is a class of pipelined array architectures that feature the properties of modularity, regularity, local interconnectivity, a high degree of pipelining, and highly synchronized multiprocessing. It can provide for different convolutional code structures, a general and local interconnection. However, the numbers of components and pipeline stages in the systolic array architecture presented in [7] increase exponentially with K. As a result, the design will be excessively hardware-resource and power consuming, and at the same time, clock-to-data skews caused by the deep pipelining will become critical for a proper functioning of the system. In addition, the processing times of the two operations, namely, the composite branch metric generation and the path metric update, will differ significantly as K becomes large. Consequently, it is a challenging task to ensure that the two types of processors with different processing times can be synchronized, without slowing down the clock-rate. Moreover, the employment of strongly-connected trellis decoding method carries a drawback that the amount of ACS computations becomes excessive as the constraint length K becomes

large. Consequently, this excessive amount of ACS computations will result in a large amount of power consumption in its hardware implementation.

#### 1.3 Approaches to Reduce Power Consumption

In recent years, some attempts have been made for low-power design of Viterbi decoders with K=9. In this section, we discuss several features of such schemes.

The latest effort in the design of low power bit-serial Viterbi decoder, proposed by Chang, Suzuki and Parhi [9], is based on a parallel butterfly architecture with bit-serial arithmetic. In this design, the employment of bit-serial arithmetic for the ACS computations is the key in reducing the power consumption. By using the bit-serial arithmetic, the number of components and the complexity of the interconnections between components in the Viterbi decoder is reduced over that using a parallel butterfly architecture with parallel arithmetic. As a result, the power dissipation is reduced. A disadvantage for using bitserial arithmetic technique is that extra memory elements are required to store intermediate results of the ACS computations. Since this design is targeted for application specific integrated circuit (ASIC) technology, this problem is solved at the circuit level by developing an area-efficient storage unit for the state metric, which is based on the first-in first-out (FIFO) architecture. In addition, since there are less switching activities generated in a FIFO register than in a conventional shift register, the use of the FIFO registers instead of the conventional shift registers in an ACS unit makes the design of the ACS unit power efficient.

The another low-power ASIC design of the Viterbi decoder has been proposed by Kang and Willson [10]. In this design, the power efficient serial butterfly architecture is obtained by combining a butterfly ACS unit with a flipped butterfly ACS unit. Furthermore, the gated-control scheme was employed to reduce spurious transitions on high-capacitance bus lines, and Gray code was used to reduce the number of transitions in path-memory addressing [10].

Beside the two low-power Viterbi decoders based on ASIC technology discussed above, two Viterbi decoders with a large constraint-length K=9 targeted for FPGA implementations have been proposed by Pandita [5] and by Park and Rho [6]. These two designs simply use a serial butterfly architecture, without using any other power reduction technique.

#### 1.4 Scope of the Thesis

From the discussion above, it is clear that most low-power Viterbi decoders with K=9 are designed based on the serial butterfly architecture with little provision for high speed. There exists just one Viterbi decoder implementation based on the parallel butterfly architecture in which the employment of bit-serial arithmetic technique plays the role of moderately reducing the hardware complexity in order to provide a low-power design. At present, there is no implementation for a large constraint-length, for instance for K=9, Vit-erbi decoder using the systolic array architecture suggested by Chang and Yao [7]. The systolic array architecture in [7] can provide a moderate speed over the serial and parallel architectures due to its high degree of pipelining and multiprocessing. It can also provide, for different convolutional code structures, a general method for a simple adjacent cell

interconnection. It can be naturally mapped into an FPGA device, since (a) there are a large number of D-type flip-flops (DFFs) available in most commercial FPGA devices, such as the Xilinx VirtexII series, and (b) the primitive logic cells of FPGA devices are organized as an array. However, to design the Viterbi decoder for decoding a convolutional code with a large value of K, say, K=9 and a code rate of r=1/2, the complexity of the computations will render the adoption of the systolic array architecture in [7] not to be feasible.

In this thesis, first the conventional Viterbi algorithm is reformulated for the stronglyconnected trellis decoding. Then, a design and implementation of the reformulated Viterbi algorithm for decoding the convolutional code with K=9 and r=1/2 using the Xilinx VirtexII-XC2V1000-4FG256 chip is presented. In this design, a novel systolic array-based architecture with arithmetic pipelining, time multiplexing and clock-to-data skews tolerance is developed. Further, an adaptive Viterbi algorithm that is based on strongly-connected trellis decoding is proposed by modifying the adaptive Viterbi algorithm based on low-connectivity trellis decoding. The objective of this proposed algorithm is to reduce the excessive amount of ACS computations resulting from the strongly-connected trellis decoding. By using this algorithm, the design and implementation of an adaptive Viterbi decoder for decoding the convolutional code with K=9 and r=1/2 using the Xilinx VirtexII-XC2V1000-4FG256 chip is presented. In this design, the proposed systolic arraybased architecture for the Viterbi decoder is modified for the implementation of this adaptive algorithm. A process of spurious toggle reduction is developed to reduce power consumption in the design. Simulation results show that the proposed adaptive Viterbi algorithm can reduce the large amount of ACS computations significantly while maintaining almost the same error performance as that of the non-adaptive Viterbi algorithm. This reduction in the amount of computations results in a substantial reduction in overall power consumption compared to the implementation of the non-adaptive Viterbi algorithm.

#### 1.5 Organization of the Thesis

This thesis presents a study on low-power designs and implementations of systolic array-based Viterbi and adaptive Viterbi decoders. The thesis is organized as follows.

In Chapter 2, a review of the convolutional encoding process, the Viterbi decoding process, and the strongly-connected trellis decoding method is given. This is followed by the formulation of the Viterbi algorithm based on strongly-connected trellis decoding. In Chapter 3, a design and implementation of the Viterbi decoder for decoding the convolutional code with a constraint length of 9, and a code rate of 1/2 using the Xilinx VirtexII-XC2V1000-4FG256 chip is presented. A performance analysis of the decoder in terms of speed, power and FPGA resource utilization is carried out based on implementation results and estimation results by the VirtexII power estimator. In Chapter 4, an adaptive Viterbi algorithm that is based on strongly-connected trellis decoding is proposed, and a formulation of the proposed algorithm for hardware implementation of an adaptive Viterbi decoder is presented. A comparison between the proposed algorithm and the non-adaptive Viterbi algorithm in terms of the error performance and the amount of ACS computations based on the simulation results is presented. In Chapter 5, a design and implementation of a low-power adaptive Viterbi decoder with a constraint length of 9 and code rate of 1/2

using the Xilinx VirtexII-XC2V1000-4FG256 chip is presented. A performance analysis of this design in terms of speed, power and FPGA resource utilization is carried out, and the results of comparison with the Viterbi decoder are presented. Chapter 6 concludes the thesis by highlighting the findings of the investigation undertaken and by suggesting some possible future work in this area.

#### CHAPTER 2

# A VITERBI ALGORITHM FOR THE STRONGLY-CONNECTED TRELLIS DECODING

#### 2.1 Introduction

As noted in Chapter 1, convolutional codes and the Viterbi algorithm are widely used in digital communication systems as a forward error-correction scheme. Convolutional codes were first introduced by Elias [11] in 1955 as an alternative to block codes. Shortly thereafter, Wozencraft [12] proposed sequential decoding as an efficient decoding scheme for covolutional codes, and experimental studies soon began to appear. In 1963, Massey [13] proposed a less efficient but simpler-to-implement decoding method called threshold decoding. In 1967, Viterbi [14] introduced a decoding algorithm that was relatively easy to implement for convolutional codes with constraint length K not larger than 9, and has since become to be known as the Viterbi algorithm. Later, Omura [4] showed that the Viterbi algorithm was equivalent to a dynamic programming solution to the problem of finding the shortest path through a weighted graph. In 1973, Forney [1,3] recognized that it

was in fact a maximum likelihood decoding algorithm for convolutional codes, that is, the decoder output selected is always the codeword that gives the largest value of the log-likelihood function. Often, the process of Viterbi decoding has considered in the literature as equivalent to the solving the shortest path problem in a trellis diagram. In 1989, Chang and Yao showed that the Viterbi decoding process of finding the shortest path in a trellis diagram can be formulated by employing a general matrix-vector multiplication [7], and it can be realized by a systolic array. At the same time, they also presented a strongly-connected trellis decoding method in order to increase the throughput of the decoding and to improve the efficiency of the hardware utilization.

This chapter begins with describing the convolutional encoding and the process of the Viterbi decoding for finding the shortest path in a trellis. Then, the strongly-connected trellis decoding method is described. The processes of generating the composite branch metrics and updating the path metrics, ACS computations using modulo arithmetic, and radix-2<sup>K-1</sup> trellis trace-back updating in the Viterbi decoding are formulated for the purpose of hardware implementation of a Viterbi decoder.

#### 2.2 Encoding of Convolutional Codes

A convolutional code differs from block codes in that the encoder contains memory, and the encoder outputs at any given time depend not only on the inputs at that time unit but also on the previous input blocks. A convolutional code that is defined as (n, k, m) can be generated by an encoder with a k-input, n-output linear sequential circuit including m-stage shift registers. Each information bit remains in the encoder for up to m+1 time units,

and during each time unit can affect any of the n encoder outputs depending on the m-stage shift registers connections. Generally, K=m+1 is defined as the constraint length of a code, and k/n as the code rate of a code. In addition, connections from the m-stage shift register and the current inputs to each output is represented by a sequence called generator sequence. For example, an encoder for a (2, 1, 3) convolutional code is shown in Figure 2.1. Note that the encoder consists of a 3-stage shift register together with 2 modulo-2 adders and a multiplexer for serializing the encoder output. The three generator sequences in this encoder are  $G(0) = (1 \ 1 \ 1)$ ,  $G(1) = (1 \ 1 \ 1)$ , and  $G(2)=(1 \ 1 \ 0)$ . G(0) represents that there are three connections to the bit-v0 output from the current input u, the first stage, and the second stage of the shift register. G(1) represents that there are three connections to the bit-v1 output from the current input u, and the first and the second stages of the shift register. G(2) represents that there are only two connections to the bit-v3 output from the current input u and the first stage of the shift register.

Figure 2.1 A (3, 1, 2) binary convolutional encoder

A generator sequence can be viewed as an impulse response of the encoder. Therefore, it follows that a convolutional code can be obtained by convolving the input sequence with the impulse response of the encoder. The number of stages m in the shift register and the generator sequences to be used affect the minimum Hamming distance of a code that determines the maximal number of correctable bits of a code. The use of a large constraint length K means that m has to be large. As a consequence, a convolutional code with a better error correction capability is produced.

Figure 2.2 State diagram for an encoder

Since a convolutional encoder is a kind of sequential circuit, a convolutional encoding process can be described by a state diagram, in which the binary bits of its shift register represent a state of the encoder. Figure 2.2 shows a state diagram for a (3, 1, 2) code. As mentioned in Chapter 1, the state diagram of an encoder can be expanded in time, and resulting structure is called a trellis diagram. A trellis diagram for a (3, 1, 2) code with an information sequence of length L=5 is shown in Figure 2.3. In this case, the encoder

always starts from state  $S_0$  and returns to state  $S_0$ . This is done by adding a reset sequence consisting of m bits of zeros to the information bits. In the first m (=2) time units the encoder departs from state  $S_0$ , and in the last m (=2) time units the encoder returns to state  $S_0$ . It is seen that not all the states can be reachable in the first m (=2) or the last m time units. However, in the central part of the

Figure 2.3 Trellis diagram for a (3, 1, 2) code with L = 5 [15]

trellis, all the states are reachable, and a trellis at each time unit represents a replica of the state diagram. There are  $2^k(=2^1=2)$  branches leaving and entering each state. At each time unit (or stage), the upper branch leaving each state represents the input '1', while the lower branch represents the input '0'. Each branch is labeled with n (=3) corresponding outputs

called codeword, and each of the  $2^L$  (= 32) codewords of length N=n(L+m)=21 corresponds to a unique path through the trellis. In the general case of an (n, k, m) code and an information sequence of length kL, there are  $2^k$  branches leaving and entering each state, and  $2^{kL}$  distinct paths through the trellis corresponding to the  $2^{kL}$  code words.

#### 2.3 Viterbi Decoding Process

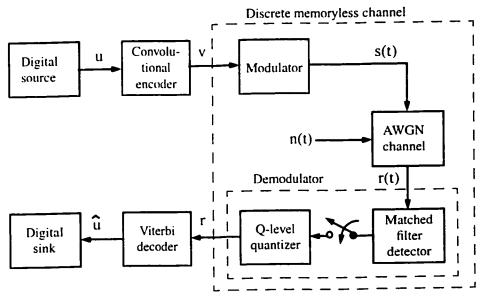

The Viterbi algorithm is a maximum likelihood (ML) method for decoding of convolutional codes over an additive white Gaussian noise (AWGN) channel. Figure 2.4 shows a convolutional coded system on an AWGN channel [15]. At the transmitter end, the output of a convolutional encoder (v) is modulated into signal symbols to be transmitted through

Figure 2.4 Convolutional coded system on an additive white gaussian noise channel the AWGN channel. At the receiver end, the received signal symbols are demodulated and are quantized into several levels depending on using the hard decision or the soft decision. In the hard decision case, the received signal is quantized into two levels, either zero or

one, whereas in the soft decision case, it is quantized into more than two levels. The Viterbi decoder generates the estimate  $\widehat{u}$  of the information sequence u by ML method. In this method, all the codewords are assumed to be transmitted equally likely, and  $P(r \mid v)$  that represents the probability of the received sequence r over the codeword sequence v to be transmitted is maximized. Further, if  $\log P(r|v)$  is maximized,  $P(r \mid v)$  is maximized.

Thus,  $\log P(r|v)$  is called log-likelihood function, and expressed as  $\log P(r|v) = \sum_{i=0}^{N-1} \log P(r_i|v_i)$ .

This can be interpreted with a trellis diagram. The log-likelihood function  $\log P(r|v)$  is called metric associated with the path with the codeword sequence v in a trellis, whereas the term  $\log P(r_i|v_i)$  is called metric corresponding to the i-th branch with codeword  $v_i$  along the path. It has been proved that if the Hamming distance or the Euclidean distance between the received sequence r and the codeword sequence v is minimized,  $\log P(r|v)$  is maximized [15]. This distance can be obtained by accumulating the branch metrics that are represented by the Hamming or Euclidean distance between the received word  $r_i$  and the codeword  $v_i$  (i = 0, 1,..., N-1). Whether to compute the Hamming distance or the Euclidean distance in a ML method depends on whether hard demodulator decisions or soft demodulator decisions are made. The Hamming distance is computed with hard demodulator decisions, whereas the Euclidean distance is computed with soft demodulator decisions. Therefore, it is understandable that the ML decoding of convolutional codes can be viewed as a process of finding the shortest path in a trellis diagram.

In general, the Viterbi decoding process of finding the shortest path in a trellis can be divided into three parts: generation of the branch metrics, updating the path metrics and

making decisions for the survived paths, and the trace-back operation. Generation of the branch metrics computes the distance between two adjacent nodes (states) in a trellis diagram. Updating path metrics and making decisions for survived paths process the ACS computations at each state. At a given stage, all the path metrics entering a given state are computed by adding the branch metrics entering that state to the corresponding path metrics at the preceding stage, and then the computed path metrics of the state are compared and the shortest one selected to update the path metric of that state. At the same time, the survivor is decided corresponding to the path with the shortest distance at the state. In the trace-back operation, the decoded output sequence is produced by tracing the survivor decisions that are stored at each trellis stage. If a reset sequence is appended after each information sequence, the trace-back operation is performed from the initial state at stage m+L back to the initial state at stage 0. However, if a reset sequence is not used, the trace-back length should be at least 5K stages starting from any state of the current stage in a truncated trellis diagram.

# 2.4 Strongly-Connected Trellis Decoding Method

The strongly-connected trellis decoding means that the process of the Viterbi decoding is performed based on a strongly-connected trellis diagram. It has been shown in [7] that for a convolutional code of rate 1/n and constraint length K, groups each containing a minimum of K-1 stages are needed to obtain a strongly-connected trellis diagram from the original low-connectivity trellis diagram. As described in Chapter 1, a strongly-connected trellis diagram can be obtained by organizing the original low-connectivity trellis in

groups of (K-1) contiguous stages and merging the stages in each group. It means that, in a strongly-connected trellis diagram, every state in the (K-1)-th stage of the group is reachable from any state of the preceding (K-2) stages of the group. As a result, the adjacency matrix based on a strongly-connected trellis diagram will have no empty entry. As shown in Figure 1.3, in each group of (K-1) stages of the original low-connectivity trellis diagram, there is only one path between any state of the (K-1)-th stage of the group and any state of the preceding (K-2) stages of the group. This means that a strongly-connected trellis diagram contains all the possible paths corresponding to its original low-connectivity trellis diagram. Thus, when the Viterbi algorithm is used to find the shortest path in a strongly-connected trellis diagram, the feature of the maximum likelihood decoding can not be changed. This maintains the error correction capability of the low-connectivity trellis decoding in the strongly-connected trellis decoding. However, the computations in the strongly-connected trellis decoding process are somewhat different from those required in the low-connectivity trellis decoding process. In the next section, we will reformulate the conventional Viterbi algorithm based on the low-connectivity trellis decoding for stronglyconnected trellis decoding.

# 2.5 Reformulation of the Conventional Viterbi Algorithm for the Strongly Connected Trellis Decoding

### 2.5.1 Generation of Composite Branch Metrics

Let K be the constraint length and r=1/n be the code rate of the given low connectivity trellis diagram. By combining (K-1) branches of the low-connectivity trellis diagram into

one single branch, we can convert it into a strongly-connected trellis diagram; the single branch in the latter is called a composite branch [7]. Let  $b_q(i, j)$  represent the composite branch metric from state i of stage q-1 to state j of stage q of the strongly-connected trellis diagram, and  $C_{ij}$  a binary vector of n(K-1) elements, representing the codeword sequence corresponding to the composite branch. Let  $y_q$  be a quantized vector of n(K-1) elements, representing the received real-valued sequence at stage q. It has been shown in [7] that under the maximum likelihood criterion the evaluation of  $b_q(i,j)$  can be expressed as

$$b_q(i,j) = f(y_q, C_{ij})$$

(2.1)

where f is the likelihood function of  $y_q$  and  $C_{ij}$ . For example, f evaluates the Euclidean distance between  $C_{ij}$  and  $y_q$  with soft demodulator decisions, and computes the Hamming distance between  $C_{ij}$  and  $y_q$  with hard demodulator decisions. In this study, binary phase shift keying (BPSK) modulation and soft demodulator decisions are assumed. Under the BPSK modulation, the minimum and maximum amplitude values -a and a can be used to respectively represent the symbol values '1' and '0' of a binary bit of  $C_{ij}$ . The codeword symbol x[k] can then be expressed as

$$x[k] = \{2C_{ij}[k] - 1\}a, \quad k = 0, 1, ..., n(K-1) - 1$$

(2.2)

where  $C_{ij}[k]$  represents the k th element of  $C_{ij}$ . In this case, (2.1) can be written as

$$b_{q}(i, j) = (y_{q}[0] - (2C_{ij}[0] - 1)a)^{2} + (y_{q}[1] - (2C_{ij}[1] - 1)a)^{2} + \dots$$

$$+ (y_{q}[n(K - 1) - 1] - (2C_{ij}[n(K - 1) - 1] - 1)a)^{2}$$

(2.3)

This is equivalent to the Euclidean distance between the codeword symbols and the received symbols corresponding to the (K-1) branches in the original low-connectivity trellis diagram. Similar to the low-connectivity trellis decoding, in the strongly-connected trellis decoding, comparisons between the path metrics are required to determine the survivor path. Thus, the differences between the path metrics rather than the actual value of the path metrics are of concern. That is, one can arbitrarily add a constant to all the path metrics without changing the comparison result. This constant can be viewed as the one to be added to the composite branch metrics, since the path metrics are made up of the accumulated composite branch metrics. In (2.3), the received sequence  $y_q$  is used to generate the composite branch metrics of stage q so that each composite branch metric of stage qincludes the constant  $y_q[0]^2 + y_q[1]^2 + \dots + y_q[n(K-1)]^2$ . Therefore, if this constant is subtracted from  $b_q[i,j]$ , the comparison result between the path metrics at stage q will not be changed. Furthermore, in (2.3) includes the term  $[(2C_{ii}[0]-1)a]^2 + [(2C_{ii}[1]-1)a]^2 + ....+$  $[(2C_{ij}[n(K-2)]-1)a]^2$ , which equals to n(k-1)  $a^2$  corresponding to  $C_{ij}[k] = 0$  or 1, k=0, 1,..., n(K-1). Likewise, the constant  $n(k-1)a^2$  can be subtracted from  $b_q[i,j]$  and the resulting value divided by 2a without altering the result of comparison between the path metrics of stage q. Therefore, (2.3) can be further simplified as

$$b_{q}[i,j] = -(2C_{ij}[0]-1)y_{q}[0] - (2C_{ij}[1]-1)y_{q}[1] - \dots$$

$$-(2C_{ii}[n(K-1)-1]-1)y_{q}[n(K-1)-1]$$

(2.4)

Thus, the computation of the Euclidean distance for a composite branch is simplified into signed additions depending on whether  $C_{ij}[k] = '0'$  or '1', in the same way as presented in [9]. Note that the simplification could result in the value of the composite branch metric given by 2.4 to be positive or negative. As a result, the hardware implementation would become simple.

From (2.4), it is clear that before the composite branch metric  $b_q[i,j]$  is evaluated, the codeword sequence  $C_{ij}$  should be generated. As noted in [7], a convolutional encoder can be viewed as a linear time-invariant system in which the total response can be decomposed into two parts, the zero-input response and the zero-state response. Thus, the codeword sequence  $C_{ij}$ , with the initial encoder state i and the input sequence j, can be expressed as

$$C_{ij} = C_{i\theta} \oplus C_{\theta j} \tag{2.5}$$

where  $C_{i0}$  represents all the codeword sequences corresponding to i=0,1,...,  $(2^{K-1}-1)$  with zero input sequence,  $C_{0j}$  represents all the codeword sequences corresponding to j=0,1,...,  $(2^{K-1}-1)$  with zero encoder state, and the symbol  $\oplus$  represents bitwise modulo 2 addition. Obviously, if all the codeword sequences  $C_{ij}$  with i, j=0,1,...,  $(2^{K-1}-1)$  are stored, it will need a huge memory space of  $N^2n(K-1)$  bits. In view of (2.5), only the minimum sets of the codeword sequences  $C_{i0}$  and  $C_{0j}$  with i, j=0,1,...,  $(2^{K-1}-1)$  are required to be known and stored, and the other codeword sequences can simply be derived from these  $C_{i0}$  and  $C_{0j}$ .

#### 2.5.2 Updating of Path Metrics

It is known that finding the shortest path in a trellis can be realized mainly by processing the ACS computation for the path metric at each state of each trellis stage. According to [7], the ACS computation corresponding to all the states of a trellis stage can be formulated into a matrix-vector computation. Given an (n, 1, m) convolutional code, the total number of states  $N=2^m$ . Let  $P_q$  be a  $Ix\ N$  row vector, whose jth element is denoted by  $P_q(j)$  representing the partial path metric from the initial state 0 to state j of stage q of the trellis diagram. Let  $B_q$  be an  $Nx\ N$  adjacency matrix, whose ij-th element is denoted by  $P_q(i,j)$  representing the branch metric from state i of stage q-1 to state j of stage q of the trellis diagram. Then, the viterbi algorithm can be formulated as

$$P_q = P_{q-1} \otimes B_q \tag{2.6}$$

where the operator  $\otimes$  denotes the ACS operation according to the likelihood criterion measured by the distance between the received data sequence and the codeword sequence. For example, the path metric at state j of stage q can be expressed as

$$p_{q}(j) = \min\{p_{q-1}(0) + b_{q}(0, j), p_{q-1}(1) + b_{q}(1, j), ..., p_{q-1}(N-1) + b_{q}(N-1, j)\},$$

(2.7)

and the survivor at state j of stage q can be expressed as

$$Sur_{q}(j) = min^{-1} \{ p_{q-1}(0) + b_{q}(0, j), p_{q-1}(1) + b_{q}(1, j), \dots,$$

$$p_{q-1}(N-1) + b_{q}(N-1, j) \}$$

(2.8)

where min represents the operation of taking the minimum distance of the paths at state j of stage q, and  $min^{-l}$  represents the operation of finding the state number in the (q-l)-th stage that yields the minimum distance of the paths at state j of stage q.

Obviously, the adjacency matrix in the matrix-vector ACS computation can provide all the metrics corresponding to the branches from any state of stage q-1 to any state of stage q at a trellis stage. In the formulation based on the low-connectivity trellis decoding, there are only  $2^k$  (i.e k=1) nonempty entries in each row or each column of the adjacency matrix, whereas its other  $2^{m-k}$  entries are empty and do not appear in a regular form, such as a band matrix. As a result, the adjacency matrix is very sparse, and a hardware utilization of a corresponding systolic array is poor. However, by adopting the strongly-connected trellis decoding method, there is no empty entry in the adjacency matrix  $B_q$ . Therefore, the efficiency of hardware utilization can be improved and the throughput of the decoding can be increased.

#### 2.5.3 Modulo Arithmetic for ACS

According to (2.7), the recursive path metric update at each state of a stage results in unbounded word growth due to the accumulations by a branch metric of the stage. To avoid normalization, which costs additional circuits in hardware implementation and increases the processing time, the modulo arithmetic approach [16, 17] is adopted here. It is known that for the original radix-2 trellis, the Viterbi algorithm inherently bounds the maximum dynamic range  $\Delta_{max}$  of the path metric at each state as

$$\Delta_{max} \le \lambda_{max} \log_2 N , \qquad (2.9)$$

where N is the number of states and  $\lambda_{max}$  is the maximum branch metric. In the Viterbi decoding process, any two updated path metrics at a state of stage q,  $P_q[i,j]$  and  $P_q[l,j]$ , are compared using subtraction. It has been shown in [16, 17] that if  $|P_q[i,j] - P_q[l,j]| < \Delta_{max}$ , the comparison can be evaluated as  $(P_q[i,j] - P_q[l,j]) mod 2\Delta_{max}$  without any ambiguity. Hence, the updated path metrics at a state of a stage can be computed modulo  $2\Delta_{max}$ . In this case, the wordlength of the path metric can be evaluated by

$$\Gamma_{bit} = \log_2 \Delta_{max} + 1 \tag{2.10}$$

The strongly-connected trellis can be viewed as a radix- $2^{(K-1)}$  trellis obtained from the original radix-2 low-connectivity trellis. In the strongly-connected trellis decoding, the dynamic range of the path metric increases, since a (K-1)-stage composite branch metric is added at each strongly connected stage. The wordlength of the strongly connected path metric can be deduced as

$$\Gamma_{bit} = \log_2(\Delta_{max} + (K - 1)\lambda_{max}) + 1$$

(2.11)

## 2.5.4 Radix-2<sup>K-1</sup> Trellis Trace-Back Update

The trace-back update can be viewed as a process to generate decoded outputs through tracing back the survivor decisions made according to the path metrics comparison result of each state at a stage, and stored along the trellis stages. The radix-2<sup>(K-1)</sup> trellis trace-

back update can be deduced starting from the trace-back update with the original radix-2 trellis [17].

Given a radix-2 trellis, let n represent the trace-back starting stage,  $S_n$  an arbitrary state of stage n, and  $d_n^S$  the survivor decision of state  $S_n$ . The state of the previous stage  $S_{n-1}$  from which the survived path at state  $S_n$  results is given by

$$S_{n-1} = d_n^{\ S}(S_n >> 1), \tag{2.12}$$

where  $S_n >>1$  represents the right shifting the constant of  $S_n$  by one bit. Hence, the state  $S_{n-1}$  can be traced back by right shifting out the state  $S_n$  one bit at one end of a state register. Meanwhile the decision  $d_n^S$  is shifted in at the other end. If two trellis stages are merged together, an equivalent radix-4 trellis is derived. In such a case, the trace-back iterations from n-th stage to (n-2)-th stage can be expressed as

$$S_{n-2} = d_{n-1}^{S}(S_{n-1} >> 1)$$

$$= d_{n-1}^{S}(d_{n}^{S}(S_{n} >> 1) >> 1)$$

$$= d_{n,n-1}^{S}(S_{n} >> 2),$$

(2.13)

where  $d_{n,n-l}$  is the composite 2-bit radix-4 decision. Similarly, if (K-1) trellis stages are merged together, the strongly connected radix- $2^{(K-1)}$  trellis is obtained. In this case, the trace-back iterations from n-th to (n-(K-1))-th stage can be expressed as

$$S_{n-(K-1)} = d_{n, n-1, \dots, n-(K-2)}(S_n >> (K-1))$$

(2.14)

where  $d_{n, n-1, \dots, n-(K-2)}$  is the composite (K-1)-bit radix- $2^{(K-1)}$  decision. Obviously, instead of decoding only one bit per trace-back iteration in the original radix-2 low-connectivity trellis Viterbi decoding, (K-1) bits can be decoded per trace-back iteration in the trace-

back decoding process based on the strongly connected radix- $2^{(K-1)}$  trellis. Thus, the strongly-connected trellis decoding can increase the throughput by a factor of (K-1) compared to that of using the original low connectivity trellis decoding. Since any state of the radix- $2^{(K-1)}$  trellis diagram can be represented by (K-1) binary bits, (2.14) shows that the bits representing a state of [n-(K-1)]-th stage is equivalent to the (K-1)-bit  $d_{n, n-1, \dots, n-(K-2)}$  decision.

#### 2.6 Summary

In this chapter, the convolutional encoding, the process of Viterbi decoding, as well as the strongly-connected trellis decoding methods have been reviewed. Then, we have reformulated the conventional Viterbi algorithm, which is based on low-connectivity trellis decoding, for the case of a strongly-connected trellis decoding. The processes of generating of the composite branch metrics and updating of the path metrics, ACS computations using modulo arithmetic, and radix-2<sup>K-1</sup> trellis trace-back updating in the Viterbi decoding have been formulated for the purpose of hardware implementation of a Viterbi decoder. It has been shown that a composite branch metric can be generated by evaluating the Euclidean distance between the codeword symbols and the received symbols when a soft demodulator decision is made. The evaluation for generating a composite branch metric has been simplified to process only signed additions instead of multiplications and additions under BPSK modulation. As a consequence, the complexity of the hardware implementation of the composite branch metrics can be reduced. In addition, the use of the modulo arithmetic for the ACS computations has avoided the process of normalization in

updating the path metrics, resulting in savings of the hardware and the processing time overhead. Since a strongly-connected trellis decoding increases the throughput of the decoding by a factor of (K-1) compared to that using the conventional low-connectivity trellis decoding, the process of trace-back updating of a radix-2<sup>K-1</sup> strongly-connected trellis trace-back has been derived from that of radix-2 low-connectivity trellis.

# **CHAPTER 3**

# DESIGN AND IMPLEMENTATION OF A VITERBI DECODER

#### 3.1 Introduction

In the previous chapter, we presented a formulation of the Viterbi algorithm based on the strongly-connected trellis diagram. As mentioned in Chapter 1, the systolic array architecture of the Viterbi decoder presented in [7] can be advantageous in hardware implementation due to its modularity, regularity, local and general interconnections, high degree of pipelining, and highly synchronized multiprocessing. However, the number of pipeline stages (and hence the number of array processors) in the architecture presented in [7] increases exponentially with K. For instance, for decoding a convolutional code with K=9 and r=1/2, there should be 256 processors in the corresponding 256 pipeline stages in both the systolic array for generating the composite branch metrics and the systolic array for processing the path metrics. As a result, the design will be excessively hardware-resource extensive and power consuming, and at the same time, clock-to-data skews

caused by the deep pipelining will become critical for proper functioning of the system. In addition, the processing times of the two operations, namely the composite branch metric generation and the path metric update, will differ significantly as K becomes large. For example, with K=9, the eight Euclidean or Hamming distances corresponding to the eight branches in the original low- connectivity trellis diagram should be computed and added together for generating a composite branch metric, whereas there are only three operations (ACS) in updating a path metric. Consequently, it is a challenging task to ensure that the two types of processors with different processing times can be synchronized, without slowing down the clock-rate.

In this chapter, the design and implementation of the Viterbi decoder for decoding a convolutional code with a constraint length of 9 and code rate of 1/2 using the Xilinx VirtexII-XC2V100-4FG256 chip is presented [18]. In this design, a novel systolic array architecture with arithmetic pipelining and time multiplexing is developed for updating the path metrics. In addition, a scheme for avoiding large clock-to-data skews and for providing a tolerance to low clock-to-data skews is devised to ensure that timings in the design are not violated. Moreover, the trace-back strategy and trace-back unit, the input buffer and one-stage branch metric generation, and the built-in testbench are designed to realize the complete functionality of the system. Finally, the performance analysis in terms of speed, power and FPGA resources utilization is presented based on the implementation results provided by the Xilinx implementation tool and estimation results by the Virtex-II power estimator.

#### 3.2 Systolic Array Architecture for ACS Computations

This section presents a novel systolic array architecture for processing ACS computations for each stage, by exploiting the time multiplexing and arithmetic pipelining tecniques.

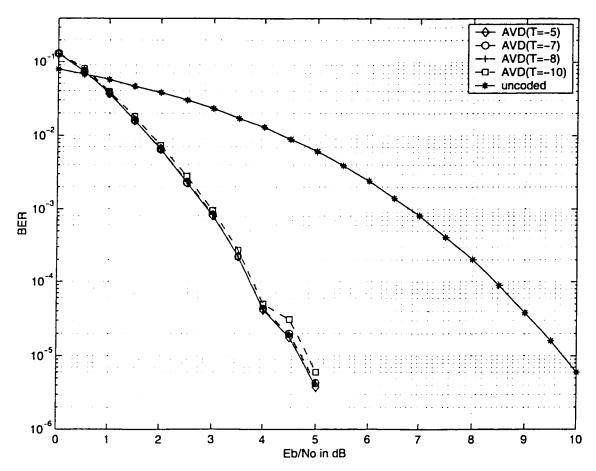

#### 3.2.1 Adjacency Matrix Partitioning and Time Multiplexing

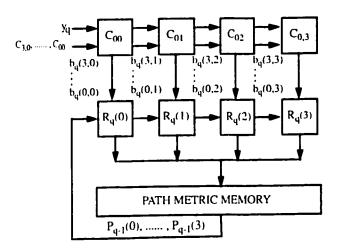

As shown in Chapter 2, updating of the path metrics at a given stage in the Viterbi decoding process can be formulated as a matrix-vector multiplication for ACS computation. For K=9, the matrix-vector ACS computation can be processed by the 256x256 adjacency matrix  $B_q$  and the 1x256 path metric vector  $P_{q-l}$ . In order to process such a large matrix-vector ACS computation with limited hardware resources, we employed an idea that the solution of a large problem can be achieved by partitioning the problem into several smaller subproblems and then solving these sequentially. In this design, the adjacency matrix  $B_q$  is partitioned into four 256 x 64 sub-matrices, and the four submatrices along with the path metric vector  $P_{q-1}$  are used in (2.6) to update the corresponding 256 (= 4x64) path metrics of a given stage. This is achieved by the four pairs of interconnected linear systolic arrays shown in Figure 3.1. Each pair of the linear systolic arrays is formed as suggested in [7] and is shown in Figure 3.2. There are four processors in each of the top systolic array BM\_4 and the bottom systolic array ACS\_4. In each pair of systolic array, BM\_4 is used to process the composite branch metrics given by (2.4) and (2.5), whereas ACS\_4 is used to update the corresponding subset of the path metrics of a given stage according to (2.7) and make decisions on the survivor paths for the corresponding subset

Figure 3.1 Systolic array architecture for path metrics update

Figure 3.2 Architecture of a pair of systolic arrays

of the path metrics of the stage according to (2.8). For computing the corresponding four subsets of  $B_q$  at each stage, the codeword vector  $C_{0j}$  is divided into four 1x64 subvectors to be stored in four ROMs, ROM0 to ROM3, and the codeword vector  $C_{i0}$  stored in ROM. The updated path metric vectors from the four pairs of systolic arrays are selected by the

four multiplexers (MUX\_P), and then written into the corresponding four RAMs, RAM1 to RAM3. At same time, the path metric vectors in the previous stage are read out from the four RAMs and time multiplexed to the inputs of the arrays by the multiplexer BUS\_MUX. In this FPGA implementation, the ROMs and the RAMs are implemented by using the block RAMs provided by the FPGA chip. Globally, the four submatrix-vector ACS computations are carried out simultaneously by the corresponding four pairs of systolic arrays in Figure 3.1. Locally, inside each pair of the systolic arrays, the corresponding submatrix-vector ACS computation is time multiplexed. In this way, the large matrix-vector ACS computation can be implemented with four pairs of systolic arrays, each consisting of 8 processors. On the other hand, the architecture would require 512 processors, if the time multiplexing technique is not employed.

As mentioned in Section 3.1, in the systolic array architecture presented in [7], the number of pipeline stages increases with the constraint length K of a code, and for K=9, there are 256 pipeline stages. Even though it is possible to implement this large design with 256 array processors by using a large enough FPGA chip, the deep pipelining causes large clock-to-data skews, violating the timing constraint of the design. Therefore, the decoder would not function properly. On the contrary, in the proposed design, the four pairs of systolic arrays, with each array having 4 processors, are used to process the matrix-vector ACS computation, and only 4 pipeline stages are needed for each of the systolic array pairs. However, since only 4 systolic array pairs are used due to the limitation on the size of the FPGA chip, the time-multiplexing iterations are needed to process the large matrix-vector ACS computation. In general, the number of the pipeline stages does not change

with the constraint length K of a code. Even though in our implementation, the number of the time-multiplexing iterations increase exponentially with K, it has the flexibility to trade off the number of iteration with the number of the systolic array pairs. In our design of 4 systolic array pairs, there are only 16 time-multiplexing iterations.

#### 3.2.2 Arithmetic-Pipelining Technique and Array Processors

It is seen from (2.4) that to generate a composite branch metric, one needs to process fifteen signed additions, whereas to compute a path metric only three ACS operations are needed. Usually, the global clock period has to be the higher of these two computational times, plus some safety margin so as to achieve the synchronization of the whole system. That is obviously undesirable from the point of view of speed. Fortunately, the use of a smaller clock period could be a solution not only to allow different operations in the array network take different time periods but also to speed up the design. Since one composite branch metric computation and one path metric computation consist of a number of arithmetic steps, the processors corresponding to the two types of computation can be designed with arithmetic-pipelining in which each arithmetic step is treated as a pipeline stage by adding appropriate registers. This implies that each pair of systolic arrays can be realized with a two-level pipelining, pipelining at the global array level from processor to processor and pipelining within a processor.

The arithmetic-pipelining processor for a BM\_4 is shown as Figure 3.3. A composite branch metric can be viewed as the summation of the K-1=8 corresponding one-stage branch metrics in the original low-connectivity trellis decoding. Therefore, these one-

stage branch metrics can be generated before the corresponding composite branch metric is computed. In this design, the computation involved in (2.4) is divided into two parts, the

Figure 3.3 Arithmetic pipelining processor for a BM\_4

computation of the eight one-stage branch metrics and the computation of the summation of those one-stage branch metrics. A module placed outside the arrays is designed to generate, by using a two-bit codeword, all the possible values for each of the eight one-stage branch metrics corresponding to a composite branch metric at a given stage. At a given stage, the array processors in a BM\_4 first select, according to the codeword sequence, the eight computed one-stage branch metrics, and then perform seven signed additions to obtain the corresponding composite branch metric. Thus, the word length corresponding to the maximum composite branch metric can be 7 bits. In this way, an array processor for a BM\_4 can be less complex compared to an array processor with fifteen signed additions

implemented by fifteen pipeline stages. As a result, in an FPGA implementation, the resource utilization will be reduced.

Path metric update processes the ACS computations with the composite branch metrics of the current stage and the path metrics of the previous stage. In general, a feedback is needed in path metric updating, since the path metrics of the previous stage should be fed back to the input of an ACS processor for updating the path metric at the current stage. In the butterfly architecture-based Viterbi decoders [5]-[10], ACS computations cannot be pipelined because of the feedback that would occur between the pipeline stages. However, in the proposed systolic array-based architecture, the ACS computations can be carried out in pipeline. In this design, each path metric update of the qth stage processes 256 ACS computations with 256 corresponding composite branch metrics of the qth stage and 256 path metrics of the (q-1)th stage. In view of this large number of inputs to be processed at a given stage, the proposed architecture is very suitable. Furthermore, the path metrics of the qth stage are fed back to the input of the corresponding processor at the same time as the corresponding composite branch metrics of the (q+1)th stage are generated. More importantly, since a latency of outcome exits in a pipelined design, during the 16th (final) iteration while updating the path metrics for the qth stage, the updating of the path metrics for the (q+1)th stage has already commenced. However, a two-level pipelining can ensure that there is no conflict between the updatings of the path metrics for the qth and the (q+1)th stages.

The arithmetic-pipelining processor for an ACS\_4 is shown in Figure 3.4. This processor is implemented with two pipeline stages. The adder in the first pipeline stage is used to compute the 256 path metrics at any of the corresponding 16 states of a given stage,

whereas the adder in the second pipeline stage is used to make comparisons amongst the 256 path metrics computed by the first pipeline stage. According to (2.14) and (2.16), the

Figure 3.4. Arithmetic pipelining processor for a ACS-4

length of the adders in the two pipeline stages should be 10 bits in order to perform modulo arithmetic. In the second pipeline stage, the comparison between the path metrics computed at the current and previous clock cycles at the state of a given stage are carried out by adding the path metric at the current clock cycle to the compliment of the path metric at the previous clock cycle increased by unity. In this way, as presented in [16], the sign-bit of the adder can represent the result of the comparison between the two path metrics. If the sign-bit is '1', the path metric at the current clock cycle is smaller than the path metric at the previous clock cycle. If the sign-bit is '0', then the former is larger than the latter. In the meantime, the path metric with the shorter distance at the state of a given stage is selected by the multiplexer (Mux1) and sent to Register. In addition, the 8-bit

counter in the second pipeline stage is used to represent the 256 possible states of the previous stages from which the paths originate and terminate at various states of the present stage. One of these 256 paths would be the survivor path depending on the sign bit of the adder in the second pipeline stage, and is selected by the multiplexer (Mux2) at each clock cycle. Thus, at a given stage, the path metric and the survivor corresponding to any of the 16 states can be updated through 256 clock cycles.

If  $\tau$  is the cycle time, the processing times corresponding to the computations in ACS\_4 and BM\_4 are  $7\tau$  and  $2\tau$ , respectively. Once an arithmetic-pipelining processor is full of data a new result is produced at every cycle instead of every 7 or 2 clock cycles, with an ordinary processor if no pipelining is involved. Therefore, employing the arithmetic-pipelinings in ACS\_4 and BM\_4 improves the throughput of the design. In addition, the synchronization between ACS\_4 and BM\_4 can be achieved by simply designing a timing scheme that makes them start at different time instants. This means that at a given stage the processors in an ACS\_4 will not start their computations until the results from the processors in the corresponding BM\_4 have been generated. In this way, throughput of the design will not be changed, but a latency between ACS\_4 and BM\_4 is introduced. This is in fact the latency of any processor in BM\_4.

#### 3.2.3 Clock-to-Data Skew and a Scheme for its Avoidance

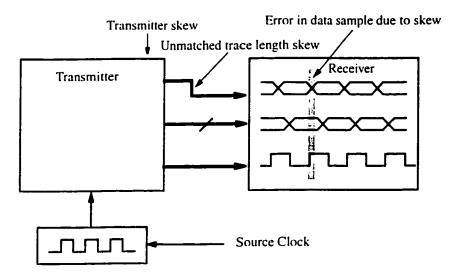

The systolic array architecture described above provides a highly synchronized Viterbi decoder in which a source-synchronous clocking is used, and the clock frequency determines the rate of the decoding. Although the source-synchronous clocking can achieve signal integrity in the design, clock-to-data skew remains a problem to be solved. In an

FPGA implementation-based design, clock-to-data skew is caused by threshold and delay mismatch of driver output cells, edge-rate mismatch between the clock and the data output cells, and trace length mismatches between the clock and the data paths. Usually, in a

Figure 3.5 Trace length mismatches causing clock-to-data skew