#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## Design of High Performance Multiple-Input Pass-Transistor-Logic XOR Circuits

Yuling Yang

A Thesis

in

the Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal. Quebec. Canada

January 2003

© Yuling Yang, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre nilárence

Our file Notes nildeance

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-77726-X

**Canadä**

#### **ABSTRACT**

## Design of High performance Multiple-Input Pass-Transistor-Logic XOR Circuits

Yuling Yang

XOR gates are basic building blocks in the design of almost all kinds of digital circuits for signal processing, generation and control. The performance of the XOR gates can be a factor determining the performance of the complete circuits. In particular, XOR gates with a large number of inputs, which are often used for parallel processing, may make a major contribution to the delay of the circuits. Some reduction of the delay can be achieved but usually at the expense of the power dissipation.

In this thesis, a comprehensive study of the XOR gate design is presented. Based on the study, an approach of designing multiple-input pass-transistor-logic XOR gates is proposed. This approach consists of two aspects. On one hand, the imperfect high-voltage-levels, resulting from the imperfect voltage transmission by single-MOS switches, at some selected intermediated circuit nodes are used to reduce the signal swing so that the power dissipation can be minimized. On the other hand, the voltages at some circuit nodes are compensated to maximize the current capacity in order to reduce the delay. Thus, the XOR gates can be designed to have a significant higher performance, in terms of speed, than other pass-transistor-logic XOR gates and the power dissipation of the circuits can also be lowered. An example of application of this design approach is also presented in this thesis.

### Acknowledgments

The present work has benefited from a number of people who have provided their important help and support. My first and earnest acknowledgment must go to my supervisor. Professor Chunyan Wang, for all her enthusiasm, inspiration, and continuous support through my study at Concordia University. She is acknowledged, in particular, for her substantial dedication of time and energy in helping me in the experiments and thesis writing throughout the work of my thesis. She provided encouragement, good teaching, fruitful ideas, and invaluable suggestions. I have learned various things, from her, not only knowledge, but also new ways of thinking and working. I will forever remain indebted to her for being my mentor and advisor.

Thanks to all at VLSI laboratory for providing such a friendly and supportive environment. I am grateful to my friends David Claveau. Bin Qiu. Jian Zhang and Yi Yang etc., for their help with all types of research and technical problems.

The most heartfelt thank-you goes to my wonderful parents. For always being there when I needed them most. It was their love and trust that made my work worthwhile. They deserve far from more credit than I can even give them.

Last, but no means last, my deepest thanks must go to my husband Jianlong Lin, for his eternal support and enthusiastic encouragement. Thanks for being part of my life, and thanks for many years unfailing loving me and push me to keep balance.

## **Table of Contents**

| List of Figures                              | vii |

|----------------------------------------------|-----|

| List of Tables                               | X   |

| List of Acronyms                             | xii |

| List of Primary Symbols                      | xii |

|                                              |     |

| I. Introduction                              | 1   |

| I-1 Introduction                             | 1   |

| I-2 Perspective and Motivation.              | 2   |

| I-3 Objective of the Thesis                  | 3   |

| I-4 Brief Presentation of the Thesis         | 4   |

|                                              |     |

| II. Basic Building Block - XOR Circuits      | 5   |

| II-1 Introduction                            | 5   |

| II-2 Specifications of Digital Gates         | 6   |

| 2-2-1 Delay                                  | 6   |

| 2-2-2 Power Dissipation                      | 6   |

| 2-2-3 Input Resistance - Fan in and Fan out  | 7   |

| 2-2-4 Output Voltage Level                   | 7   |

| 2-2-5 Size                                   | 7   |

| II-3 Two-Input XOR Cell                      | 8   |

| 2-3-1 Conventional CMOS XOR                  | 8   |

| 2-3-2 Pass-Transistor Logic XOR              | 9   |

| 2-2-3 Mixed Logic XOR Circuits               | 10  |

| II-4 Level Recovering Techniques             | 12  |

| 2-4-1 Partial CMOS Switch XOR Cell           | 12  |

| 2-4-2 Level Recovering Inverter              | 13  |

| 2-4-3 Single Pull-Up PMOS                    | 15  |

| 2-4-4 Self-Cross Pull-Up Pull-Down Structure | 18  |

| 2-4-5 Cross-Coupled Pull-Lip PMOS            | 20  |

| II-5 Conclusion                                                                     | 22        |

|-------------------------------------------------------------------------------------|-----------|

| III. Multiple-Input XOR Circuits                                                    | 24        |

| III-1 Introduction                                                                  |           |

| III-2 Structure of Multiple-Input XOR                                               |           |

| 3-2-1 Chain Structure                                                               |           |

| 3-2-2 Tree Structure                                                                |           |

| 3-2-3 Mixed Structure                                                               |           |

| III-3 An Approach to the Improvement of Speed and Power Dissipation                 | 31        |

| 3-3-1 Description of the Proposed Approach                                          | 31        |

| 3-3-2 Different Schemes of the XOR Gates with Level Restoring                       | 36        |

| III-4 Analysis of the Pass Transistor-Logic XOR Gates with a Large Number           | -         |

| 3-4-1 Analysis of the Delay Caused by the Change of the Input Applied sion Terminal | 43        |

| Terminal                                                                            |           |

| 3-4-3 Effect of the Pull-Up Transistors                                             | 50        |

| 3-4-4 Summary of Section 3-4                                                        | 54        |

| III-5 Simulation of the Multiple-Input XOR Gates                                    | 54        |

| 3-5-1 Simulation of the Four Four-Input XOR Gates                                   | 55        |

| 3-5-2 Simulation Results and Comparison                                             | 58        |

| 3-5-3 Simulation of XOR Gates with a Large Number of Inputs                         | 61        |

| III-6 Conclusion                                                                    | 63        |

| IV. An Application of Multiple-Input XOR Gates - Design of a Hamming                | g Decoder |

| ***************************************                                             |           |

| IV-1 Introduction                                                                   |           |

| IV-2 Hamming Decoder Logic Diagram                                                  |           |

| IV-3 Approach of the Evaluation of the Operation Speed                              |           |

| IV-4 Simulation of the Critical-Path of the Hamming Decoder                         | 71        |

| Ribliography                                                               | 86          |

|----------------------------------------------------------------------------|-------------|

| VI. Conclusion                                                             | 82          |

| IV-6 Conclusion                                                            | 80          |

| 4-5-3 Realization of the Oscillation-Test Circuit                          | 77          |

| 4-5-2 Estimation of Signals Generated by the Test Circuits                 | 76          |

| Method                                                                     | 74          |

| 4-5-1 Design approach for the Evaluation of the Operation Speed by Oscill  | lation-Test |

| IV-5 Design of a Prototype Circuit for Estimation of the Propagation Delay | 74          |

| 4-2-2 Results of the Comparison                                            | 72          |

| 4-4-1 Test Circuits and Test Conditions                                    | 71          |

# **List of Figures**

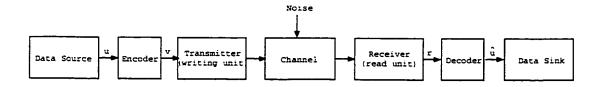

| Figure 1.1  | A typical data transmission or storage system with error control process | 2             |

|-------------|--------------------------------------------------------------------------|---------------|

| Figure 2.1  | Example of the conventional CMOS XOR circuit                             | 8             |

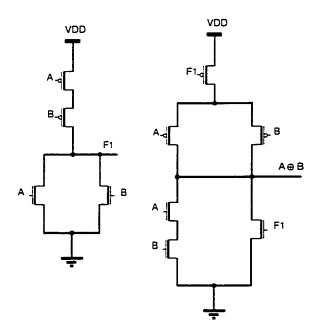

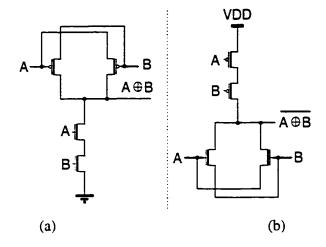

| Figure 2.2  | Basic scheme of two-input pass-transistor-logic XOR cell                 | 9             |

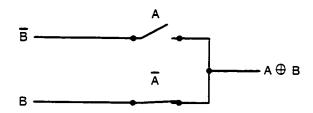

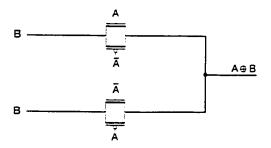

| Figure 2.3  | Pass-transistor-logic XOR cell, using complementary switches             | 9             |

| Figure 2.4  | Cross-coupled XOR and XNOR cell                                          | 11            |

| Figure 2.5  | Pseudo-NMOS and cross-coupled pass-transistor XOR cell                   | 12            |

| Figure 2.6  | One modified version of cross-coupled XNOR cell                          | 13            |

| Figure 2.7  | Level recovering inverter and its operating points                       | 14            |

| Figure 2.8  | Single pull-up PMOS circuit                                              | 16            |

| Figure 2.9  | Simulation results                                                       | 17            |

| Figure 2.10 | Self-cross pull-up XOR-XNOR cell                                         | 18            |

| Figure 2.11 | Example of a troubled dynamic operation of the circuit shown in Figure 2 | 2.10          |

|             |                                                                          | 19            |

| Figure 2.12 | NMOS output $V_F$ Voltage level problem solved by pull-up PMOS using     | $V_{\bar{F}}$ |

|             |                                                                          | 20            |

| Figure 2.13 | Pull-up transistor works in this circuit                                 | 21            |

| Figure 2.14 | Cross-coupled pull-up PMOS circuit                                       | 21            |

| Figure 2.15 | Cross-coupled pull-down NMOS circuit                                     | 22            |

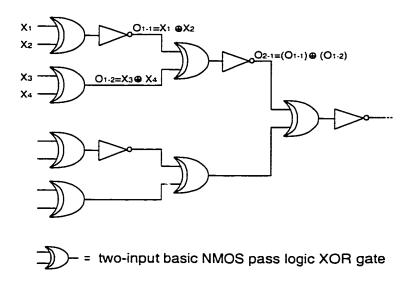

| Figure 3.1  | Multiple-input XOR with a chain structure of two-input XOR gates         | 25            |

| Figure 3.2  | Two-input pass-transistor-logic XOR gates arranged in a chain structure. | 26            |

| Figure 3.3  | Tree structure                                                           | 27            |

| Figure 3.4  | Level problem when two-input pass-transistor-logic XOR cell used in the  | tree          |

|             | structure                                                                | 28            |

| Figure 3.5  | Example of mixed structure of XOR gate                                   | 30            |

| Figure 3.6  | Multiple-input XOR circuit using the proposed approach                   | 33            |

| Figure 3.7  | Using inverters as the level-restoring cell                              | 36            |

| Figure 3.8  | PMOS and NMOS tree structure. PMOS pass-transistor-logic cells are us    | sed           |

|             | to insure a "good-1" voltage level of the signals at the MOS gates       | 37            |

| Figure 3.9  | Short-circuit current in PMOS and NMOS tree structure circuit38                          |

|-------------|------------------------------------------------------------------------------------------|

| Figure 3.10 | Improving the performance of XOR circuit of tree structure by using pull-up              |

|             | PMOS transistors at gate nodes                                                           |

| Figure 3.11 | Charging and discharging processes with and without pull-up PMOS40                       |

| Figure 3.12 | Pass-logic XOR cell42                                                                    |

| Figure 3.13 | MOS pass transistors connecting one of the diffusion input node and the out-             |

|             | put node, when the voltage change occurs at the diffusion input while the gate           |

|             | voltages of the pass transistors are VDD43                                               |

| Figure 3.14 | Equivalent RC-network for the transistor chain44                                         |

| Figure 3.15 | First transistor in the pass transistor chain                                            |

| Figure 3.16 | Modified model of the pass-logic-transistor chain45                                      |

| Figure 3.17 | Computation results using the models of the classical RC-network, modified               |

|             | model with the current-source, respectively, and the Hspice simulation results           |

|             | of the gate circuit46                                                                    |

| Figure 3.18 | Voltage change at gate terminal                                                          |

| Figure 3.19 | Current $i_2$ generated by a changing gate voltage $V_{G2}$ and another current $i_1$ by |

|             | a changing source (drain) voltage $V_I$ . On average, $i_2$ is weaker than $i_I$ during  |

|             | the transition49                                                                         |

| Figure 3.20 | Finite rise/fall time of the gate signals resulting in short-circuit currents50          |

| Figure 3.21 | Discharging and charging process for the complementary output51                          |

| Figure 3.22 | Scheme (b): Pass-transistor-logic XOR gates of tree structure without pull-up            |

|             | PMOS transistors                                                                         |

| Figure 3.23 | Scheme (c): XOR gate consisting of PMOS and NMOS pass-transistor-logic                   |

|             | cells                                                                                    |

| Figure 3.24 | Scheme (d): XOR gates consisting of NMOS pass-transistor-logic cells with                |

|             | pull-up PMOS transistors used to restore the level of the gate voltages56                |

| Figure 3.25 | Test circuit57                                                                           |

| Figure 3.26 | The variation of the input signals corresponding to the worst case delay. For            |

|             | each of the cells, the inputs applied at the gates of the MOS pass transistors           |

|             | are indicated by thick lines                                                             |

| Figure 3.27 | Currents in the transistors of the load inverter in cases of Scheme (b) and              |

|             | Scheme (c) in Figure 3.23 and Figure 3.2460                                        |

|-------------|------------------------------------------------------------------------------------|

| Figure 3.28 | Delay comparison of the three XOR gates62                                          |

| Figure 4.1  | Parity check matrix of the (72, 64) SEC-DED code67                                 |

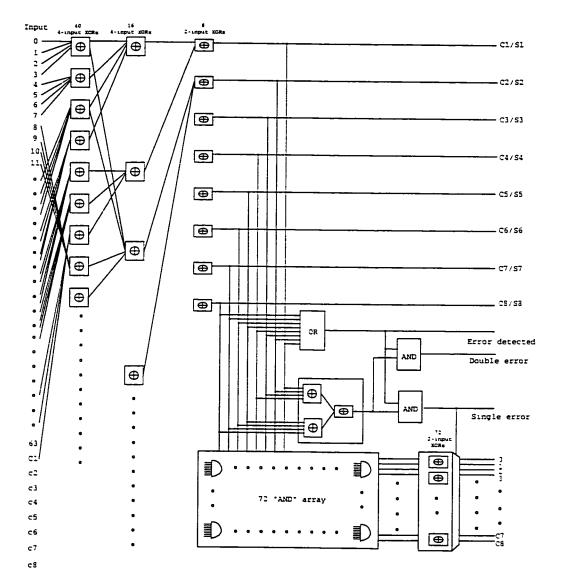

| Figure 4.2  | Logic diagram of a (64, 72) Hamming decoder                                        |

| Figure 4.3  | Critical path of the Hamming decoder for testing the operation speed of the        |

|             | circuit                                                                            |

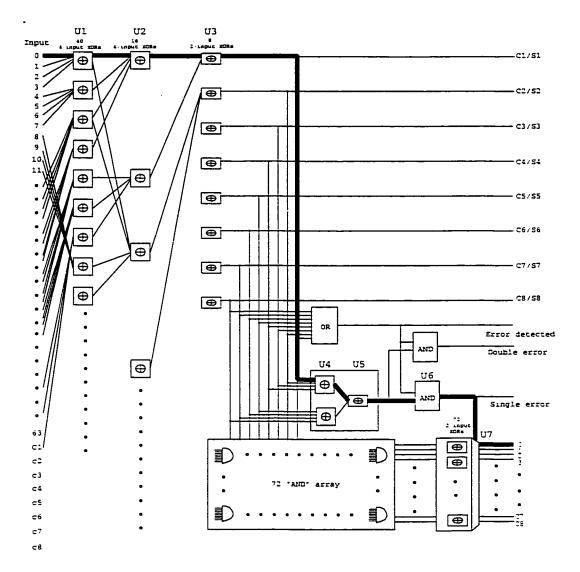

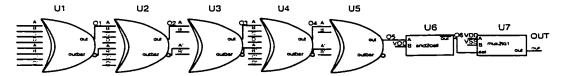

| Figure 4.4  | Simplified critical path of the Hamming decoder. U1, U2, U4 are four-input         |

|             | XOR gates. U3, U5 are two-input XOR gates. U6 is a CMOS two-input AND              |

|             | gate. U7 is a multiplexer70                                                        |

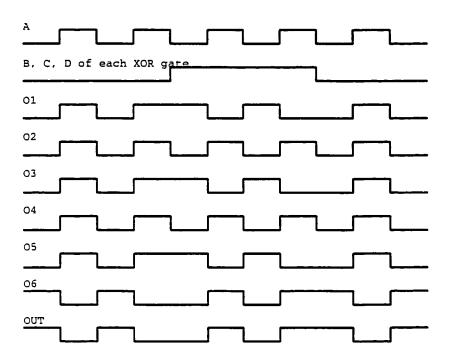

| Figure 4.5  | Part of the signals applied to the circuit shown in Figure 4.4 for the simulation  |

|             | and the expected responses at the MOS gate nodes of the circuit, as well as        |

|             | that at the output node                                                            |

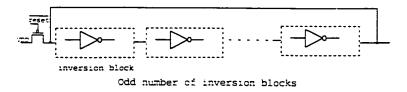

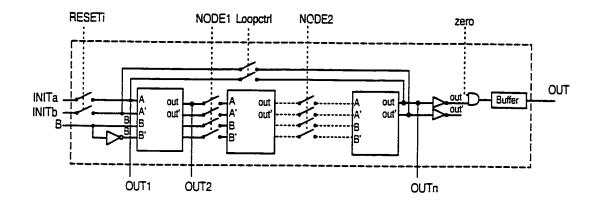

| Figure 4.6  | Digital oscillation-test method for delay test                                     |

| Figure 4.7  | Critical-path block works as an inverter76                                         |

| Figure 4.8  | Structure of the oscillation-test circuit with the controls signals. The detail of |

|             | each block is shown in Figure 4.7. The control signals are as follows78            |

# **List of Tables**

| Table 3.1 Simulation result with 1.8V power supply                      | 58 |

|-------------------------------------------------------------------------|----|

| Table 4.1 Simulation result of the critical-Path circuit of the decoder |    |

| Table 4.2 Cycle-time Estimation of the test circuit                     | 77 |

### **List of Acronyms**

ASIC Application Specific Integrated Circuit

CMOS Complementary Metal-Oxide Semiconductor

ECC Error Correcting Circuit

EDC Error Detection and Correction

DCVS Differential Cascade Voltage Switch

DFF D-type Flip Flop

GND Ground

IC Integrated Circuit

IEEE Institute of Electrical and Electronic Engineers

MOS Metal-Oxide Semiconductor

MOSFET Metal-Oxide Semiconductor Field-Effect Transistors

NMOS N-channel Metal-Oxide Semiconductor

PMOS P-channel Metal-Oxide Semiconductor

PTL Pass Transistor Logic

SEC-DED Single-Error-Correction Double-Error-Detection

SOP Sum-of-Products

VLSI Very Large Scale Integration

# **List of Primary Symbols**

| α                 | Size scale factor in tapered buffers                                                                  |

|-------------------|-------------------------------------------------------------------------------------------------------|

| $\alpha_k$        | Coefficient describing the switching activities at the $k^{th}$ node                                  |

| $C_k$             | Capacitance of the $k^{th}$ node                                                                      |

| $f_{clk}$         | Clock frequency of a signal                                                                           |

| GND               | Ground                                                                                                |

| i(V)              | Voltage control current source                                                                        |

| i <sub>scn</sub>  | Node short-circuit current                                                                            |

| $i_N$             | Current of the $N^{th}$ path                                                                          |

| $I_{avg}$         | Average current                                                                                       |

| $I_{\mathcal{D}}$ | Drain current of a MOSFET                                                                             |

| k                 | Number of circuit stages                                                                              |

| $K_n$             | Trans-conductance coefficient                                                                         |

| n                 | Number of inputs of a multiple-input XOR circuit                                                      |

| N                 | Number of layers of circuits                                                                          |

| $O_{k-i}$         | Intermediate or output node in a tree structure XOR circuit, the $k^{th}$ layer and the $i^{th}$ node |

| $P_d$             | Power dissipation                                                                                     |

| $P_{dyn}$         | Dynamic power dissipation                                                                             |

| $R_{j}$           | Resistance of the $j^{th}$ resistor in an RC-network                                                  |

| τ                 | Time constant of an RC-network                                                                        |

| $\tau_0$          | Delay of a minimum-sized gate                                                                         |

| $T_{ck}$          | System clock period                                                                                   |

| $t_d$             | Delay of a basic cell                                                                                 |

Total delay of an *n*-input XOR  $T_d$ Fall time t<sub>fall</sub> Rise time of an input signal  $t_{r_in}$ Rise time of an output signal  $t_{r\_out}$ Rise time trise Propagation delay of a combinational circuit  $t_{pd}$ Propagation delay time, HIGH-to-LOW-level output  $t_{pHL}$ Propagation delay time. LOW-to-HIGH-level output t<sub>pLH</sub> Delay of a flip-flop  $t_q$  $V_D$ Voltage of the drain terminal of a MOSFET Positive power supply  $V_{DD}$ Voltage of the gate terminal of a MOSFET  $V_{G}$  $V_{i}$ Voltage of the *i*<sup>th</sup> node High-level output voltage  $V_{OH}$ Low-level output voltage  $V_{OL}$ Voltage of the source terminal of a MOSFET  $V_{s}$ Negative power supply  $V_{SS}$ Zero-bias threshold voltage  $V_{t0}$ Threshold voltage of PMOS  $V_{tp}$ Zero-bias threshold voltage of PMOS  $V_{tp0}$ Threshold voltage of NMOS  $V_{tn}$ Zero-bias threshold voltage of NMOS  $V_{tn0}$ W/L Width/Length of a MOS gate *i*<sup>th</sup> input

$X_i$

# Chapter 1

## Introduction

#### I-1 Introduction

In the design of integrated circuits, high-speed, low-power dissipation, and small size are often the essential objectives to be achieved. A higher operation speed is always needed to meet the increasing demand for more capacity of signal processing and communication, whereas minimizing the overall power dissipation and the size of a system has become an important concern while the scale of the integration of devices is increasing. In order to improve the circuit performance in terms of speed and power dissipation, we have been working on the design and implementation of Very Large Scale

Integration (VLSI) circuits in the transistor level, and the emphasis is on the problems in the basic aspects of the circuits.

#### I-2 Perspective and Motivation

The work of this thesis aims at improving the performance of digital systems involving XOR gate. Needless to mention its roles in ALUs. XOR gate is a fundamental unit in all kinds of digital circuits for signal processing, computation and control. XOR gate is also widely used for communications and, in particular, they are basic building blocks in error detection and correction systems, e.g. that for Error-Correcting Circuit (ECC) in data transmission or storage systems as shown in Figure 1.1 [44].

The research on the XOR gates becomes extremely valuable when the major parts of the digital circuits are composed of XOR gates. For example, the number of the XOR gates is over three fourth of the total number of the gates used in an Hamming decoder for ECC. About 90% of the delay of a Hamming decoder is usually contributed by the XOR gates employed [2][3][6]. In other words, an improvement of the XOR gates can result in a considerably better performance of the circuit.

Figure 1.1 Typical data transmission or storage system with error control process.

Besides the error coding circuits. XOR gate are also frequently used in other kinds of digital logic circuits. such as equality (or inequality) comparator, pattern generator, and so on. Some circuits like the ones to realize Exclusive-OR Sum-of-Products (SOP) expressions, e.g., Reed-Muller canonical circuits, which are widely used in logic synthesis [28], are completely composed of XOR gates. It is needless to say how important it is to design a high-speed and low-power XOR gate in these kinds of digital circuits.

#### I-3 Objective of the Thesis

Since XOR function has some special features, it can be implemented more easily and efficiently in other kinds of logic gates than the complementary CMOS ones [19][21][22][45]. As a result, the design and implementation of XOR gates is very diversified. Therefore, the first objective of the thesis work is to investigate the performance of different kinds of XOR circuits in terms of robustness, power dissipation and delay. From the results of the investigation, it can be seen that some measures have been taken to achieve some improvements in these circuits while some new problems emerge. Based on the analyses of previous work, the second objective of the thesis is to design XOR circuits with better performance without losing the robustness of the circuit operations.

It should be noted that in this thesis, the main focus is on the design of XOR gates with a large number of inputs applied in signal processing, communication and storage systems, such as the one applied in an error correcting circuit, a Hamming decoder. Hence, the third and the most important objective of this thesis is to propose a

design approach to improve the performance in terms of speed and power dissipation of the XOR gates that have a large number of inputs. These improvements should be verified by evaluating the performance of a prototype circuit, such as a Hamming decoder in which XOR gates are designed using the proposed approach.

#### I-4 Brief Presentation of the Thesis

The thesis is divided into five Chapters including this introduction.

In Chapter 2, previous work on the design and implementations of varieties of XOR gates is described. Most of them are two-input ones. In particular, a comprehensive study of level restoring techniques used in non-conventional CMOS designs is presented. The effectiveness of these techniques is evaluated.

In Chapter 3, different structures of XOR circuits with a large number of inputs are presented. The speed and power dissipation of each of the structures are described. The emphasis of the work is on the design and analysis of Pass-Transistor-Logic (PTL) XOR circuits. An approach to improving the performance of the XOR gates with a large number of inputs are proposed.

Chapter 4 is dedicated to a circuit example. Hamming decoder, for an assessment of the XOR gates in a processing circuit. The role of XOR gates in the operation of the Hamming decoder is described. An approach of the evaluation of the circuit speed is presented and a related test circuit is proposed Some important issues in the implementations of the test circuit are discussed.

Chapter 5 summaries the work of the thesis and describes briefly the future research on the design and implementation of pass-transistor-logic XOR circuits.

# Chapter 2

# **Basic Building Block – XOR Circuits**

#### II-1 Introduction

The exclusive-OR gate is a fundamental unit in digital circuits. Typical applications include full adders, binary comparators, pattern generators and Error Correcting Circuits (ECC). For example, in many circuits implementing error control codes, XOR gate is one of the most frequently used logic units. The global specifications of ECC circuits depend greatly on the performance of the XOR cells integrated.

In this chapter, we will discuss in detail the performance of different existing two-input XOR circuits. The performance comparison of these circuits will be presented and discussed.

#### II-2 Specifications of Digital Gates

Before presenting different kinds of XOR circuits, we need to have a look at the important specifications of a digital gate, including speed, power dissipation, size, etc.

#### 2-2-1 Delay

The delay of a gate is related to the current driving capacity of the transistors in the gate and the load capacitances. The current is determined by the size ratios (Width/Length) of the transistors in the current path. In case of a complex network circuit, such as a multiple-input XOR gate, the delay depends also on the number of stages and the capacitances contributed by the interconnections. Another factor related to the delay is the voltage levels of input signals and those at the intermediate circuit nodes. This aspect will be elaborated in later sections.

#### 2-2-2 Power Dissipation

In the work related to this thesis, the power dissipation is an important concern. Power dissipation can be divided into two parts: static power dissipation and dynamic power dissipation. The static power dissipation includes that contributed by leakage currents, and in some cases, by the  $V_{DD}$ -to- $V_{SS}$  currents in some circuit branches. The latter results are often from the imperfection of the voltage levels of the binary voltage signals. Dynamic power dissipation has two components: the switching power consumption and the short-circuit power consumption. They are determined by the switch activities and the node capacitances contributed by the silicon layers and metal wires. The equation used to estimate the dynamic power dissipation can be expressed as [45]:

$$P_{dyn} = V_{DD}^2 \cdot f_{clk} \cdot \sum_{k} \alpha_k \cdot c_k + V_{DD} \cdot \sum_{k} i_{scn}$$

(2.1)

where  $V_{DD}$  is the supply voltage.  $f_{clk}$  is the clock frequency of the signal.  $\alpha_k$  is the coefficient describing the node switching activities at the  $k^{th}$  node.  $C_k$  is the node capacitance at the output node of the  $k^{th}$  stage.  $i_{scn}$  is the node short-circuit currents. and k is the number of the stages.

#### 2-2-3 Input Resistance

The input resistance of a CMOS gate is infinite. The input resistances can be a finite value if the input nodes are not gate terminals.

#### 2-2-4 Output Voltage Level

This specification closely relates to the noise margins of the circuits. Moreover, it also relates to the current driving capacity which determines the speed and power dissipation of the circuits. Details will be presented in Section II-3 and II-4.

#### 2-2-5 Size

The circuit size depends on the number of transistors and their sizes. It also depends on the wiring complexity. The minimization of the circuit volume facilitates the integration of a system. Besides, this minimization may reduce the parasitic capacitance of the circuit and power dissipation. However, in terms of the operation speed, it may not lead to optimum results due to smaller transistor sizes.

#### II-3 Two-Input XOR Cell

We describe some two-input XOR cells in this sub-chapter to show some of the problems in the design of XOR circuits.

#### 2-3-1 Conventional CMOS XOR

An example of CMOS XOR gate are shown as shown in Figure 2.1[20][45]. Compared to other kinds of XOR gates, the number of transistors of a complementary CMOS XOR circuit is relatively larger. Moreover, the circuit can be very complex if the number of inputs is large. Therefore, some other kinds of XOR circuits have been proposed to fit different requirements.

Figure 2.1 Example of a conventional CMOS XOR circuit.

#### 2-3-2 Pass-Transistor-Logic XOR

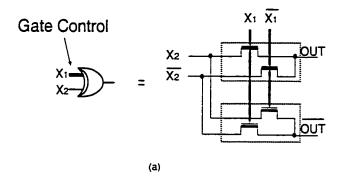

One commonly used logic to build XOR gate is pass-transistor logic which has a structure of a multiplexer as shown in Figure 2.2.

Figure 2.2 Basic scheme of two-input pass-transistor-logic XOR cell.

If each switch is a single MOSFET, it requires a very smaller number of transistors, which reduces delay, power dissipation and the size. However, it has its weakness of non-ideal output voltage levels, called "poor 1" and "poor 0"[45]. The problem can be solved by using complementary switches, as shown in Figure 2.3. However, in this case, complementary switches and control signals have to be used, the number of the transistors has to be doubled, and the circuit wiring will be much more complex, which reduces the significance of the advantages the pass-transistor logic gates have over the CMOS ones.

Figure 2.3 Pass-transistor-logic XOR cell, using complementary switches.

It should be noted that some of the input terminals of pass-transistor logic circuits are source/drain terminals with finite-value resistances. Therefore, any non-ideal operation state in the pass-transistor-logic circuits can affect the operation of the preceding stages. Usually, buffers are needed to separate the stages.

#### 2-3-3 Mixed Logic XOR Circuits

Some other simple XOR circuits based on pass-transistor logic mixed with other logic gates have been proposed. They are discussed below.

#### 2-3-3-a Cross-Coupled XOR and XNOR [45]

The circuits shown in Figure 2.4 are two examples. Each of them consisting of only four transistors to realize the XOR or XNOR function. But they both have the level problem. For example, in the circuit shown in Figure 2.4(a), when both inputs are LOW, the output level is higher than  $V_{SS}$ . Moreover, the circuit does not have infinite input resistances. In conclusion, they have all the problems that pass-transistor-logic circuits of single-MOS transistor switches have.

Figure 2.4 Cross-coupled XOR and XNOR cell.

- (a) Logic gate realizing XOR function. In this circuit, the low level of the output can be higher than zero due to the "poor-0" problem of PMOS.

- (b) Logic gate realizing XNOR function. In this circuit, the high level of the output can be lower than  $V_{DD}$  due to the "poor-1" problem of NMOS.

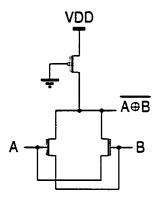

#### 2-3-3-b A Combination of the Pseudo-NMOS and the Pass-Transistor Circuit

The circuit shown in Figure 2.5 [20] is even simpler. There are only three transistors in this XOR cell, which is a combination of pseudo-NMOS and a pass-transistor circuit. In terms of the number of transistors required to form the cell, it is so far the best. However, like pseudo-NMOS gates, this circuit has the problems of non-zero static power dissipation and non-ideal low voltage levels.

Figure 2.5 Pseudo-NMOS and cross-coupled pass-transistor XNOR cell.

#### II-4 Level Recovering Techniques

CMOS XOR gates have the advantages, such as robustness and regularity in the circuit structure. However, it requires large number of transistors, which can cause a larger delay and requires more silicon space. The pass-transistor-logic circuit and mixed logic XOR gates and mixed logic ones are simpler. However, the problem of a "poor-1" or a "poor-0" of single-MOS switches affects the noise margins, speed and power dissipation of the gates. Thus, it is necessary to solve this problem. Several techniques have been proposed. We are going to discuss them in this sub-section.

#### 2-4-1 Partial CMOS Switch XOR Cell

As we discussed in Section 2-3-2, we can solve the level problem by using complementary switches. However, since it requires both inputs have complementary signals controlling the switches, which can eliminate the advantages of the pass-transistor-logic gates over the CMOS ones. Due to this, a modified version is shown in Figure 2.6

[23], which could be seen as a partial CMOS switch circuit. It is also similar to the cross-coupled XOR cell shown in Figure 2.4 except that a PMOS transistor  $P_3$  is added in order to compensate the level difference when A = B = "I". Meanwhile, only one complementary signal of the inputs is required to control the additional switch  $P_3$ .

Although this circuit attempts to keep the structure simple while solving the level problem. This version still does not reach the goal to have a small number of transistors.

Another drawback is that its structure is irregular.

Figure 2.6 One modified version of cross-coupled XNOR cell.

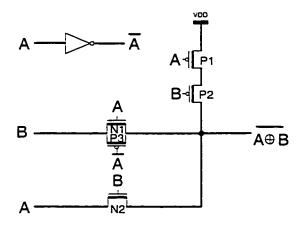

#### 2-4-2 Level Recovering Inverter

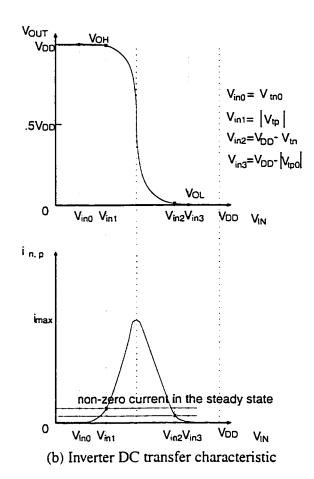

One of the approaches to compensating for the output level is to add a level-recovering inverter, as illustrated in Figure 2.7.

(a) Level recovering using an inverter

Figure 2.7 Level recovering inverter and its operating points. Poor voltage levels can result in static current and power dissipation.

With this approach, the output voltage of the inverter shown in Figure 2.7 can be almost full swinging, i.e.  $V_{OH} \approx V_{DD}$ ,  $V_{OL} \approx V_{SS}$ . However, the following two points should be underlined.

- At least one of the two input voltage levels of the inverter is different from the supply voltage (or the GND) and the difference is large than the zero-bias threshold voltage of the transistors,  $V_{tn0}$  or  $|V_{tp0}|$ . Thus, the static power dissipation of the CMOS inverter is non-zero, as shown in Figure 2.7(b).

- The transistors of the inverter have to be carefully sized, in order that the threshold voltage is correctly set, not to be too close to the voltage level of "poor 1" (or "poor 0"). In other words, there is a critical limitation for sizing the transistors.

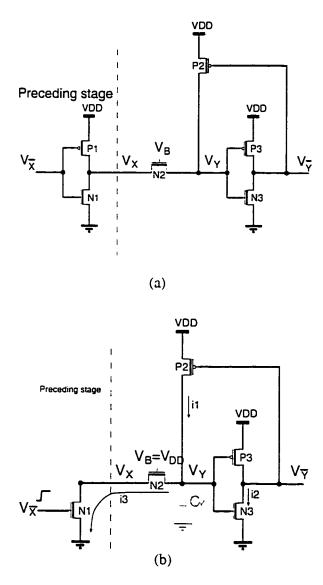

#### 2-4-3 Single Pull-Up PMOS

Another solution proposed to solve "poor 1" problem is to apply a pull-up PMOS transistor[22][45]. As shown in Figure 2.8. if  $V_x$  is high, its output  $V_\gamma$  will be high, which drives  $V_{\overline{\gamma}}$  to a low level. This low level  $V_{\overline{\gamma}}$  drives the pull-up PMOS P<sub>2</sub> on and  $V_\gamma$  is expected to reach  $V_{DD}$  after  $i_l$  charging the capacitor  $C_{\mu}$  Thus, the level of  $V_{\gamma}$  is restored. However, this circuit can have problems in dynamic operation. Assume the circuit is initialized as  $V_{\overline{x}} = 0$ V,  $V_X = V_{DD}$ , and  $V_{\gamma} = V_{DD}$ . Then  $V_{\overline{x}}$  changes from 0 to  $V_{DD}$ , and  $V_X$  intends to change to 0V, so does  $V_{\gamma}$ . While  $V_{\overline{\gamma}}$  is still lower than  $V_{DD} + V_{tp0}$ , both P<sub>2</sub> and N<sub>2</sub> are on. Whether the voltage  $V_{\gamma}$  can be reduced to a low level depends on the difference between the two currents  $i_I$  and  $i_3$ . If  $i_3 > i_1$ , the

capacitor  $C_Y$  will be discharged and  $V_Y$  will reach zero. However, if  $i_3 \le i_1$ ,  $V_X$  and  $V_Y$  will increase or remain the same. An equilibrium may be reached and  $V_Y$  remains at a relatively high level. The simulation results of such a case is shown in Figure 2.9.

Figure 2.8 Single pull-up PMOS circuit.

- (a) Single pull-up PMOS circuit. The PMOS transistor  $P_2$  and the inverter are added to compensate the voltage dropping at  $V_Y$  in case  $V_X = V_{DD}$ . (b) Equivalent circuit during the transitions in case  $V_{AB}$  is changed from  $V_{DD}$ .

- (b) Equivalent circuit during the transitions in case  $V_X$  is changed from  $V_{\rm DD}$  to 0V.

Figure 2.9 Simulation results.

During the period,  $i_3 \le i_1$ , then  $V_Y$  remains high and  $V_{\overline{Y}}$  remains low, which causes logic errors.

To insure  $i_3 > i_1$  during the transition, we should carefully choose the size ratios of the transistors concerned. This is a limitation of this level-recovering technique.

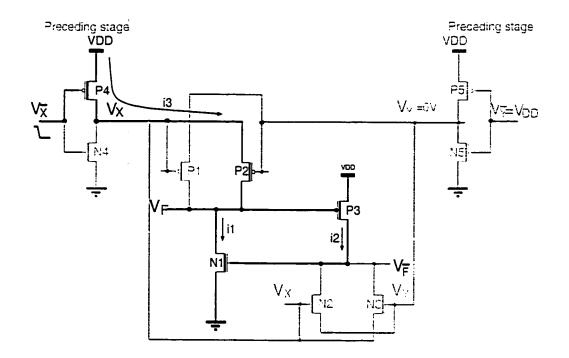

#### 2-4-4 Self-Cross Pull-Up Pull-Down Structure

Another version of the XOR circuit with level compensation has been presented by D. Radhakrishna [27]. As shown in Figure 2.10, the circuit consists of two parts. "a pseudo-NMOS-like" cross-coupled pass-transistor XOR circuit similar to that shown in Figure 2.5, and its complementary version. The two parts make a closed loop with the output signal of each part feed to the other one as shown in Figure 2.10. In each part, the pull-up PMOS (or pull-down NMOS) is controlled by the output from the other part. It attempts to perform both the XOR and XNOR functions simultaneously with full swing voltage levels.

Figure 2.10 Self-cross pull-up XOR-XNOR cell [27].

The circuit seems to have full swing output in the static operation. However, it does have the problem of the level and static power dissipation due to its feedback structure. In the case shown in Figure 2.11, the resulting outputs  $V_F$  and  $V_{\overline{F}}$  may not have good voltage levels and static currents  $i_l$  and  $i_2$  may exist in the circuit.

Figure 2.11 Example of a troubled dynamic operation of the circuit shown in Figure 2.10.

Assume that the input  $V_X$  and  $V_Y$  are respectively from the preceding gates. and the circuit is initialized as  $V_{\overline{X}} = V_{DD}$ ,  $V_{\overline{Y}} = V_{DD}$ ,  $V_X = 0V$ ,  $V_Y = 0V$ , the output  $V_F = 0V$ , and  $V_{\overline{F}} = V_{DD}$ . Then,  $V_{\overline{X}}$  changes from  $V_{DD}$  to  $V_{SS}$ , and  $V_X$  rises toward  $V_{DD}$ .  $V_F$  intends to change to  $V_{DD}$ . However, if  $i_I$  is comparable with  $i_3$ ,  $V_F$  can not rise to a high voltage. Then  $P_3$  can not be cut off completely and  $V_{\overline{F}}$  remains higher than zero. This non-zero signal is fed back to N1 and keeps it on. Therefore, the current  $i_I$ ,  $i_2$  and  $i_3$  are non-zero in static state. It could not only cause the static power dissipation problem but also a logic error.

From above discussion, we have the conclusion that although this circuit requires only a small number of transistors to realize the XOR and XNOR function, there is a great risk that the circuit can not work properly.

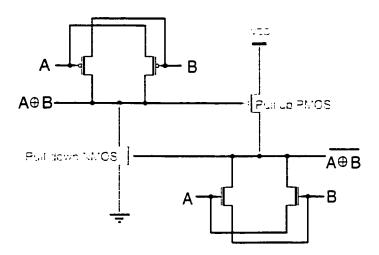

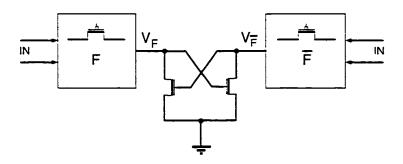

#### 2-4-5 Cross-Coupled Pull-Up PMOS

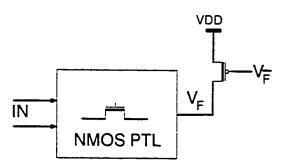

Another solution to the voltage level problem in an NMOS pass-transistor logic circuit is to use only PMOS transistors shown in Figure 2.12 [22]. The PMOS transistor functions as a pull-up transistor. However, unlike the case described in Section 2-4-4, the gate voltage  $V_{\bar{F}}$ , shown in Figure 2.12 is not produced by the pass-transistor logic gate itself, but provided by an independent gate performing the complementary function. Since only NMOS transistors are used in the gate, the output levels should have only the "poor-1" problem. When it occurs, its complementary signal  $V_{\bar{F}}$ , which is also generated by an NMOS pass-transistor logic gate, is expected to be at a low level which is used to drive the pull-up PMOS transistor on and it brings the level of  $V_{\bar{F}}$  to  $V_{DD}$ . It should be noted that, unlike the case shown in Figure 2.11, in the NMOS pass-transistor-logic illustrated in Figure 2.12, there is no node eventually switched to the ground.

Figure 2.12 NMOS output  $V_F$  Voltage level problem solved by pull-up PMOS using  $V_{\overline{F}}$ .

This circuit avoids the possible dynamic operation problem that single pull-up PMOS and self-cross pull-up pull-down structures have. As shown in Figure 2.13, since

there are no current path connecting to  $V_{SS}$ , the output  $V_F$  can be charged to perfect high voltage level  $V_{DD}$  by  $i_I$  and  $i_2$ .

Figure 2.13 Pull-up transistor works in this circuit.

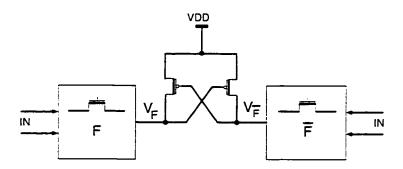

Figure 2.14 Cross-coupled pull-up PMOS circuit.

As the true signal  $V_F$  and its complementary signal  $V_{\overline{F}}$  are required in most of the large circuits, two blocks performing functions F and  $\overline{F}$  can be placed together with

their pull-up PMOS transistors as shown in Figure 2.14. Both output signals have full swing logic levels.

The circuit also works with cross-coupled pull-down NMOS if using PMOS pass-transistor logic. It is shown in Figure 2.15.

Figure 2.15 Cross-coupled pull-down NMOS circuit.

#### II-5 Conclusion

In this chapter, the basic building blocks, XOR circuits have been discussed. Besides the conventional CMOS and pass-transistor logic XOR gates, some existing mixed logic XOR gates, which are simpler than the CMOS ones, are also described. In these circuits, level restoring techniques are usually applied in order to solve the "poor 0" or "poor 1" level problems of NMOS or PMOS switches. However, these techniques have their shortcomings. The partial CMOS switch XOR cell does not reduce the number of transistors and it loses the regularity in structure. The level recovering inverter may cause a static power dissipation and this method has a limitation of selecting the transistor sizes. Another method that using single pull-up PMOS may cause logic error if the size ratio of the transistors are not chosen properly. The similar logic-error could happen in the self-

cross pull-up pull-down structure. Using cross-coupled pull-up PMOS transistors is so far a good solution for level restoring without risk of static power dissipation.

The technique of adding cross-coupled pull-up PMOS transistors can be further explored in the design of multiple-input XOR circuits, which will be discussed in the next section.

### Chapter 3

### **Multiple-Input XOR Circuits**

#### **III-1 Introduction**

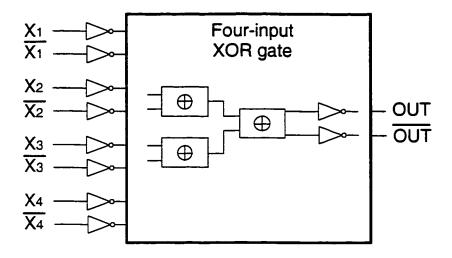

XOR gates employed in signal detecting and processing circuits, such as ECC circuits, often have a large number of inputs ( $\geq 4$ ). To have a reasonable speed and power dissipation combined, we need design specifically structured multiple-input XOR gates, instead of connecting single two-input XOR gates mechanically.

In this section, we first present the analysis of the existing multiple-input XOR circuits. Based on the analysis, an approach to the improvement of speed and power dissipation of PTL XOR circuits are presented. A study of the performance improvements

and implementation of the approach are also described, as well as the evaluation of the performance by Hspice simulation.

#### **III-2** Structure of Multiple-Input XOR

Because of the simplicity of the circuits structure, the approach of PTL is often taken for the design of low-power and high-speed XOR gates. Thus, two-input pass-transistor-logic XOR gates are usually used as the basic unit to build multiple-input XOR blocks. There are three types of XOR structures commonly used: the chain structure, the tree structure, and the mixed structure.

#### 3-2-1 Chain Structure

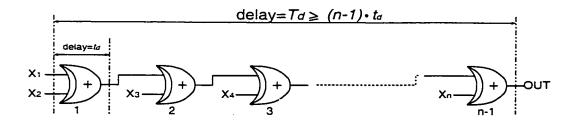

The basic scheme of a multiple-input XOR gate with a chain structure is shown in Figure 3.1. It should be noted that the basic cells in the scheme are two-input XOR gates.

Figure 3.1 Multiple-input XOR with a chain structure of two-input XOR gates.

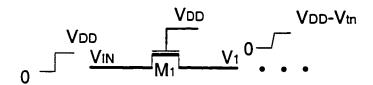

Assume that all the inputs are provided by CMOS gates with full swing voltage levels. All the gates of MOS pass transistors of the circuit are driven by full swing voltage

levels as shown in Figure 3.2. The low level of the output voltage is zero volts, and the high level is  $V_{DD}$ - $V_m$  in the worst cases.

Figure 3.2 Two-input pass-transistor-logic XOR gates arranged in a chain structure.

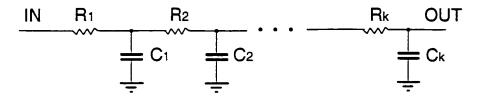

If n is the number of inputs of a multiple XOR gate. n-l two-input XOR gates are required to build the circuit. If each unit has a delay of  $t_d$ , then the total delay of the circuit, consisting of n-l cascading stages, is  $T_d$ , where  $T_d \ge (n-1) \cdot t_d$ . The best case  $(n-1) \cdot t_d$  only occurs when each pass-transistor-logic stages is well isolated, usually by inverters. Otherwise, the delay increases exponentially, because the charging or discharging current required to change the voltage at the output terminal is provided by the preceding gate, the current flows through a chain of pass transistors. Thus, in order not to have a serious delay, a large number of chained stages should be avoided, which limits the number of inputs of the XOR gates.

The power dissipation of this structure  $P_D \approx (n-1) \cdot p_D$ , i.e., it is nearly a linear function of the number of stages.

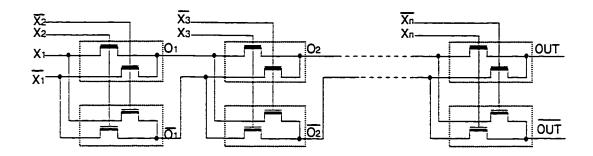

#### 3-2-2 Tree Structure

The multiple-input XOR gate can also be made using basic XOR cells in a tree structure as shown in Figure 3.3.

Figure 3.3 Tree structure.

For an n-input XOR gate of tree structure, the total number of basic two-input units is n-l; same as for the chain structure. Because of the same number of the units used, the power dissipation of the tree structure circuits is similar to the chain structure circuits.

To estimate the delay, the number of stages for signal propagation, N, needs to be examined. In an n-input XOR gate of tree structure,  $N = \log_2 n$ , instead of n-l in a chain structure. Therefore, the former has a total delay of  $T_{d-tree} \ge (\log_2 n) \cdot t_d$ , where  $t_d$  is the delay of the basic unit, compared to  $T_{d-chain} \ge (n-1) \cdot t_d$  for the latter.

Evidently, the tree structure XOR gates have advantages of speed over the chain structure ones, because of their smaller number of layers. However, this advantage may not be significant in some cases and some critical level problems may occur. One such example is shown in Figure 3.4.

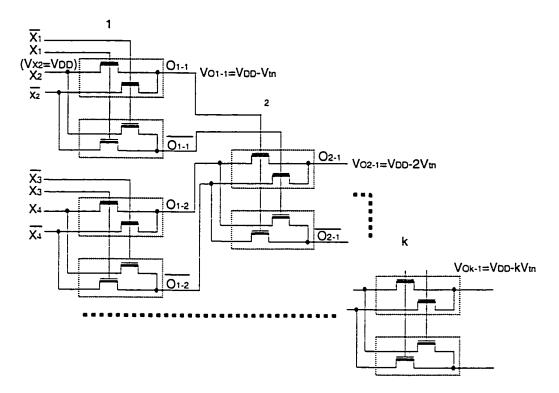

Figure 3.4 Level problem when two-input pass-transistor-logic XOR cell used in the tree structure.

As we can see in a basic cell of the second layer (Figure 3.4), the four inputs of the basic cell are from the first layer, and all of them have "poor-1" problems ( $V_{OH} = V_{DD} - V_{in1}$ ), where  $V_{in1}$  is the threshold voltage of the transistors. Two of these signals are applied at the gate terminal of the cell. The output in the high level of the second layer will be the voltage applied at the gate minus its threshold voltage,  $v_{in2}$ , i.e.,

$V_{OH}=(V_{DD}-V_{tn1})-V_{tn2}$ . When this signal continues to be transmitted to the  $k^{th}$  stage, the high output level will be  $V_{OH}\approx V_{DD}-kV_{tn}$ . Therefore, the poor voltage level of each layer will be propagated and accumulated. In order to insure sufficient noise margins of the circuits, the number of layers cannot exceed two. Otherwise, level recovering techniques have to be taken for the circuits to operate correctly.

The level problem described above affects not only the noise margins of the circuits but also the operation speed. If the "poor-1" voltage signals from the preceding layer are applied at the gates of the pass transistors, the transistor currents will be weakened compared to the case of "good-1" gate voltages. Consequently, the propagation delay will be increased.

From the above discussion, we can conclude that, unless some measures are taken to solve the level problem, the pass-transistor-logic of the tree structure will not have significant advantages over those of the chain structure in terms of power dissipation and operating speed due to the level problem. Moreover, the routing for the tree structure is more complex than that of the chain structure.

#### 3-2-3 Mixed Structure

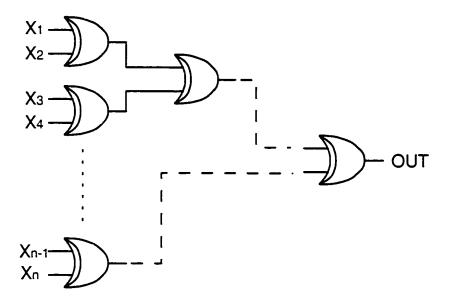

There are some types of multiple-input XOR gates apparently having different features from those of the chain structure and the tree structure. One of the examples is the DCVS circuit. [12][13][16][45].

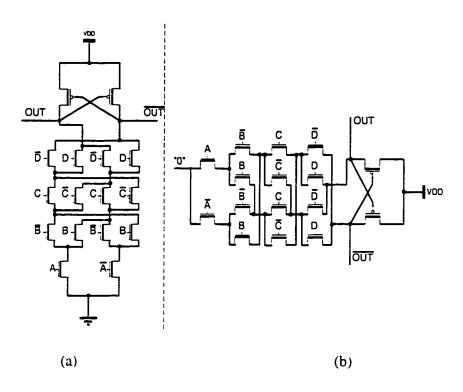

A DCVS (Differential Cascade Voltage Switch) XOR is, in fact, a passtransistor-logic network transferring logic "0" to one of the output terminals, while the voltage of the other output node is pulled to  $V_{DD}$  by means of a PMOS. Since the pass-transistor-logic network consists of NMOS pass transistors, the low-level at the output is zero volts. Thus, there is neither "poor-1" nor "poor-0" problems. A typical DCVS XOR circuit is shown below in Figure 3.5.

Figure 3.5 Example of mixed structure of XOR gate.

- (a) DCVS XOR[45]

- (b) The same circuit (a) placed horizontally to show the transmission of the "0" to the node out or out.

The speed of the DCVS XOR circuit is related to the number of layers in the pass-transistor-logic network. A large number of layers results in a large delay. The advantage of this circuit is that all the inputs voltage signals are applied to the gate terminals of the pass-transistor-logic network. Thus, the resistance of each input terminal

is infinite, and there is no current flowing from preceding stages, which is the same as that in CMOS PUN/PDN gates.

# III-3 An Approach to the Improvement of Speed and Power Dissipation

We have discussed three kinds of multiple XOR gates composed of two-input pass-transistor-logic XOR units: chain structure, tree structure and mixed structure. The chain structure is simple, but in order to avoid a long current path, the number of inputs, i.e., the number of stages has to be limited. The same problem also exists in the mixed structure. The tree structure has fewer layers with a seem-to-be smaller delay compared to the chain structure and the mixed structure. However, due to the problems of "poor-1" or "poor-0" of MOS pass transistors, a successive voltage level loss can be produced, which not only weakens the current driving capacity of the transistors, but also cause logic errors in some cases. Therefore, the chain, tree or mixed structure XOR circuits all have disadvantages in different aspects. A design approach for improving the performance in terms of speed and power dissipation is presented in the following sub-sections.

#### 3-3-1 Description of the Proposed Approach

The improved circuit is based on the tree structure for its advantage of a small number of layers of the gates. By using the tree structure instead of the chain structure, the total delay can be reduced  $\frac{n-1}{\log_2 n}$  times (Section 3-2-2), where n is the number of inputs.

The larger the number of inputs, the greater speed improvement of the tree structure XOR gates over the chain structure gates, if the problem of the poor levels can be solved.

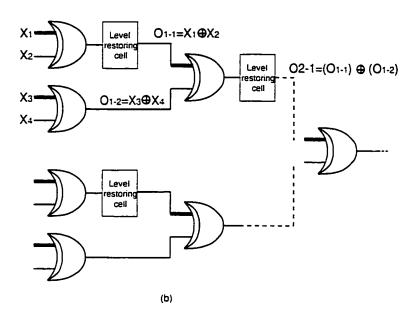

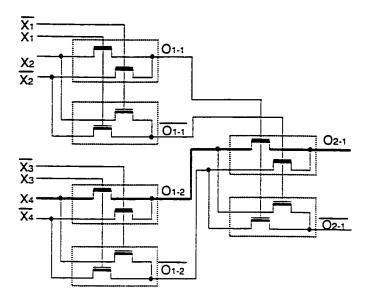

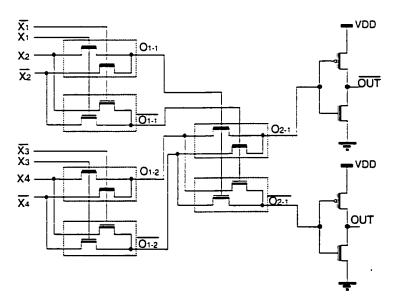

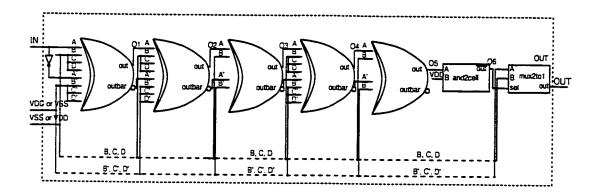

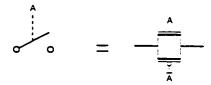

The level problem in the tree structure pass-transistor-logic circuit is due to the successive voltage level reduction. This problem can be solved by applying level-restoring cells to make the gate voltages of all the MOS pass transistors to have a full swing. By doing so, we can not only eliminate successive voltage level degradations, but also maximize the current driving capacity of the MOS pass transistors, which results in a maximum speed. However, for both speed and power concerns, we propose to make only the gate voltages full swing, not the voltages at the diffusion terminals. An example illustrating the approach is shown in Figure 3.6. This is a multiple-input XOR circuit based on basic pass-transistor-logic XOR units and level-restoring cells. Each XOR unit has two inputs. The one drawn in thick gray line (Figure 3.6b) is applied at the MOS gate and the other drawn in thin line at the diffusion node (Figure 3.6a). Level-restoring cells are placed only at the branches connecting to MOS gates, so that all of the gate signals have a full voltage swing. The analysis of the improvement resulting from this arrangement is elaborated in the following paragraphs.

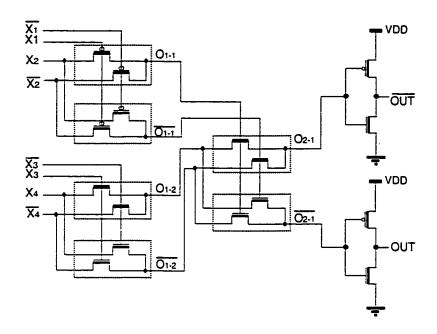

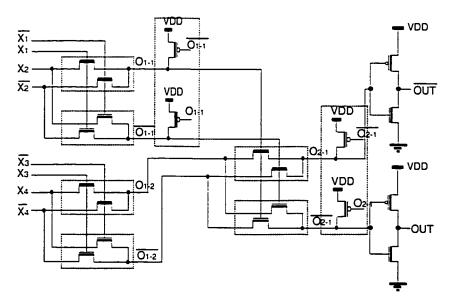

Figure 3.6 Multiple-input XOR circuit using the proposed approach.

- (a) Basic XOR cell with asymmetric inputs.  $X_1$  and  $\overline{X}_1$  are the inputs controlling the gates of MOS pass transistors indicated by thick lines.  $X_2$  and  $\overline{X}_2$  are the signals applied at the diffusion terminals.

- (b) Circuit scheme consisting of the basic XOR cells and level-restoring cells which are used to recover only the levels of the gate voltages.

#### 3-3-1-a Voltage Level

By means of the level-restoring cells, the levels of gate voltages are 0V and  $V_{DD}$ . Those at the diffusion nodes are 0V and  $V_{DD}$ - $V_{tm}$ , in an NMOS pass transistor network. Therefore, the output voltage loss is limited at  $V_{tm}$  no matter how many gate layers there are in the circuit.

#### 3-3-1-b Speed

The level-restoring cell makes the voltage at every gate terminal full swing. The maximized  $V_G$  results in a maximized current driving capacity of the MOS pass transistor and consequently, a short delay.

The charging time is usually longer than the discharging time, because the driving capacity of PMOS transistors is weaker than that of NMOS transistors of the similar size in preceding stages. Therefore, the delay due to rise-time is more critical than that of fall-time.

For each of the MOS pass transistor, during the rise-time, the input of the pass transistor, is the drain terminal of the transistor. The NMOS pass transistor is always in saturation during the transition, as  $V_D \ge V_G - V_{tn}$ . The current is approximately  $i_D \approx K_n \cdot \frac{W}{L} [v_{GS} - V_{tn}]^2$ , For the two cases,  $v_G = V_{DD}$  in the full swing gate voltage and

$$v_G = V_{DD} - V_{tn}$$

in the case of "poor-1" gate voltage, the current ratio  $\frac{i_D|_{V_G = V_{DD}}}{i_D|_{V_G = V_{DD}}}$  can be

expressed as

$$\frac{(V_{DD}-v_S-V_{tn})^2}{(V_{DD}-v_S-2V_{tn})^2}$$

. If  $v_t \approx 0.5V$ ,  $V_{DD}=1.8V$ , at the beginning of the

switching period, the current in the case of  $V_G = V_{DD}$  is  $\frac{(1.8 - 0.5)^2}{(1.8 - (2 \cdot 0.5))^2} = 2.6$

times larger than that of the other case. This example shows, by means of raising the gate voltage from  $V_{DD}$ - $V_{tn}$  to  $V_{DD}$ , the current can be increased by about 2.6 times. With the same  $\Delta V$ , the voltage variation, and load capacitor, the rise-time of transient period is greatly reduced with a full swing high voltage level at the MOS gate, which results in a faster speed for the whole circuit.

#### 3-3-1-c Power Dissipation

The power dissipation of the circuit is optimized by not restoring the voltage level of the signal applied at the diffusion nodes of the basic XOR cell. In this case, the maximum voltage at this node is  $V_{DD}-V_{in}$ ,  $(V_{in}>V_{in0})$ , due to the body effect), the energy storage/dissipation is about  $C(V_{DD}-V_{in})^2$ , instead of  $CV_{DD}^2$ , where C is the node capacitance. Therefore, without the level restoration, the energy loss by charge and discharge at this node is about  $\frac{(V_{DD})^2}{(V_{DD}-V_{in})^2}$  times smaller than that when voltage levels

are restored. If  $v_t \approx 0.5V$ ,  $V_{DD} = 1.8V$ , that is  $\frac{(1.8)^2}{(1.8 - 0.5)^2} = 1.9$  times smaller.

This results in less power dissipation at those nodes.

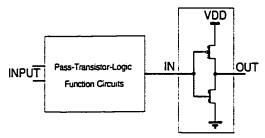

#### 3-3-2 Different Schemes of the XOR Gates with Level Restoring

#### 3-3-2-a XOR Gates with Level-Restoring Inverters

Several level-restoring techniques have been described in Section 2-4. By using an inverter as shown in Figure 3.7, we can easily restore the signal levels. However, the introduction of the inverter brings an additional delay and power dissipation. Moreover, the additional power dissipation is mainly caused by a static current in the inverter. Because of this delay, the improvement of speed may become insignificant or even negative.

Figure 3.7 Using inverters as the level-restoring cell.

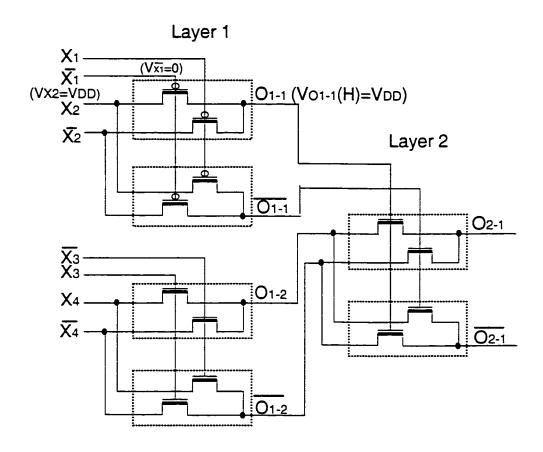

#### 3-3-2-b PMOS and NMOS Pass-Transistor-Logic Tree Structure

As discussed above, the basic point of improving the speed is making the gate voltages of the pass transistors to be equal to  $V_{DD}$ . For this purpose, instead of inserting a level-restoring cell, we may use PMOS pass-transistor-logic cells to generate the "good-1"

signals to be applied to the MOS gates of the next stages, as shown in Figure 3.8. Thus, without placing any level-restoring cells, i.e., no additional delay, high gate voltages of  $V_{DD}$  are insured and the high level of the output voltages will not be lower than  $V_{DD}-V_{tm}$ , the same as that of the circuit in Figure 3.8.

Figure 3.8 PMOS and NMOS tree structure. PMOS pass-transistor-logic cells are used to insure a "good-1" voltage level of the signals at the MOS gates.

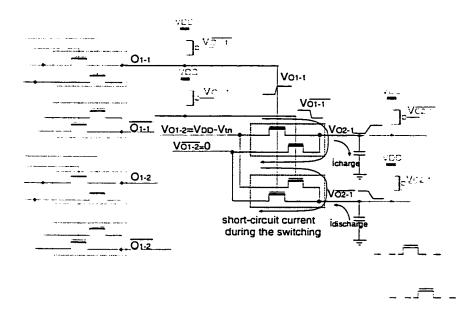

It should be noted that the use of the PMOS cells provides a good high level of the output voltage of the cell. But it results in a "poor-0" level, which leads to a problem of large static power dissipation in the succeeding stage. The poor low voltages, applied at the MOS gates of the succeeding stage make the NMOS transistors of the stage not

completely off. As the two inputs of each XOR gate unit are complementary, and, as mentioned, neither of the two pass transistors are off, a current path from  $V_{DD}$  to  $V_{SS}$  is formed via the two pass transistors, as shown in Figure 3.9. This current results in a static power dissipation.

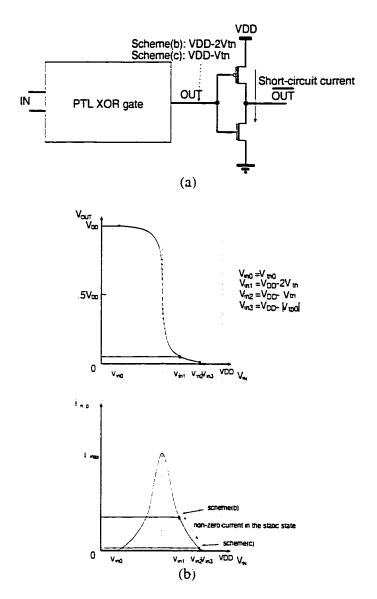

Figure 3.9 Short-circuit current in PMOS and NMOS tree structure circuit.

In conclusion, this approach of the PMOS and NMOS pass-transistor-logic tree structure improves the speed at the expense of power dissipation. Moreover, because of the static currents in the succeeding stage, the levels of the output voltage of that stage are not perfect. This level loss will affect the operation in the following stages. Thus, the number of stages (or layers) of this kind of XOR gates is limited, and inverters must be added at the end to recover the voltage levels.

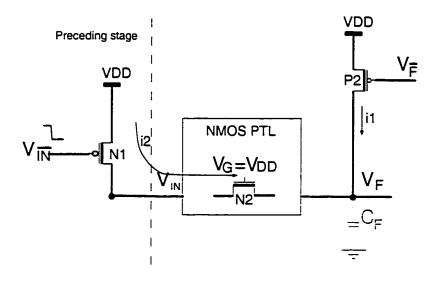

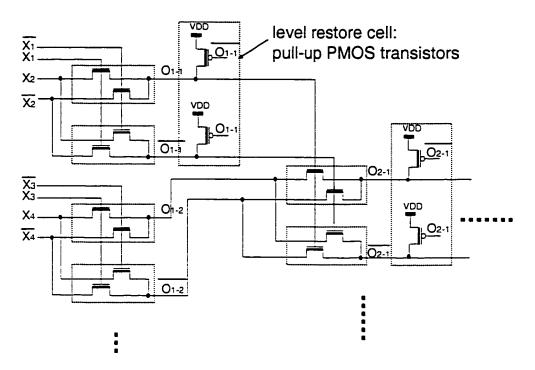

#### 3-3-2-c NMOS Pass-Transistor-Logic Tree Structure with Pull-Up PMOS

An effective method to restore the signal level without introducing an additional delay and power dissipation is to use pull-up PMOS transistor pair controlled by complementary signals, as shown in Figure 3.10.

Figure 3.10 Improving the performance of XOR circuit of tree structure by using pull-up PMOS transistors at gate nodes.

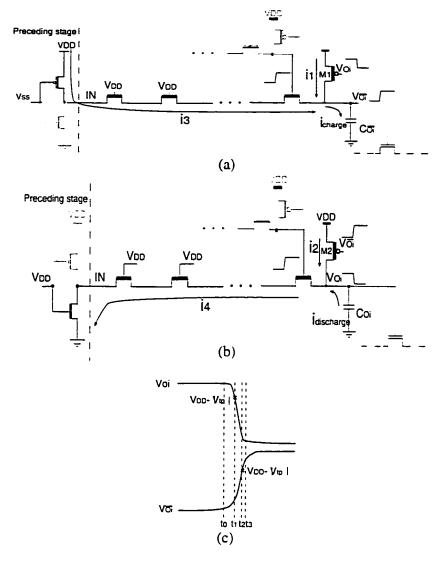

The use of these pull-up PMOS transistors in Figure 3.10 introduces almost zero additional delay to the circuit. Moreover the voltage rise during the transition is accelerated, the PMOS transistors can provide an additional path for the charging current (Figure 3.11). Therefore, with the pull-up PMOS transistors, the rise-time can be shortened and the speed of the circuit can be further improved.

This speed improvement is achieved at almost no expense of power dissipation as the current from the PMOS is designed to contribute neither to the short-circuit current

during the transition, nor the static current in steady state as shown in Figure 3.11 (b) and (d).

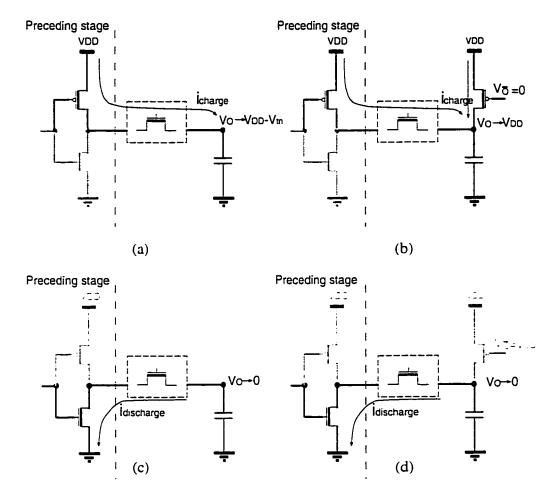

Figure 3.11 Charging and discharging processes with and without pull-up PMOS.

- (a) The charging process in the circuit without pull-up PMOS. There is one current path to charge the capacitor at the output node  $V_O$ .

- (b) The charging process in the circuit with pull-up PMOS. There is two current paths to charge  $V_O$ . Thus, the rise-time is shorter. No path for static current exists.

- (c) The discharging process in the circuit without pull-up PMOS transistor.

- (d) The discharging process in the circuit with pull-up PMOS transistor. The pull-up PMOS is supposed to be off. The difference is the discharged voltage of  $V_O$  changes from  $V_{DD}$ - $V_{tn}$  to  $V_{DD}$ , which is desirable.

As discussed above, we have presented three schemes for level restoring of the gate voltages of the pass transistors: level restoring inverters. PMOS and NMOS tree structure and "complementary" pull-up PMOS transistors. Among these three schemes. only that with the pull-up PMOS transistors can solve the problems of voltage levels and static power dissipation. Moreover, with the pull-up transistors, the tree structure can be easily expanded to multiple layers without the loss of the voltage level. More detailed analysis of this circuit structure will be given in the next sub-section.

# III-4 Analysis of the Pass-Transistor-Logic XOR Gates of with a Large Number of Inputs

As mentioned in previous sub-sections, for a tree structure, if n is the number of inputs and  $n = 2^N$ , the number of the layers is  $N = \log_2 n$ . The tree structure is beneficial for a large n, which corresponds to a relatively small  $\log_2 n$ , i.e., a relatively short path of transistors in series.

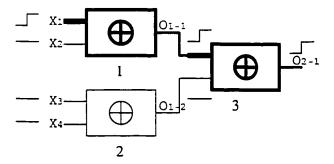

Before starting the discussion about the delay of an XOR circuit of tree structure, it should be noted that such an XOR circuit has its particularity that is discussed in the following paragraph, as shown in Figure 3.12.

Figure 3.12 Four-input pass-transistor-logic gate with two layers of two-input XOR cells.

In each cell, shown in a dashed frame, the complementary input pairs are applied at the gate terminals and the diffusion terminals of the MOS pass transistors respectively. For each of the input cases, the number of transistor between output node  $O_{2-1}$  (or  $O_{\overline{2-1}}$ ) and the input node, is two. (The level-restoring-cells are not shown here in order not to make the diagram complex.)

It is evident that, in a two-input XOR circuit, the change of the output signal from its high level to its low level or vice versa, is caused by the change of only one of the two inputs, e.g.,  $(X_1, \overline{X_1})$  or  $(X_2, \overline{X_2})$ . In other words, if both inputs change, the output should remain the same. In a pass-transistor-logic XOR circuit such as shown in Figure 3.12, the output voltage of each basic cell can be changed only when one of the input pairs changes, and one pair of the inputs is applied at the gate terminal of the pass transistors, while the other is at the diffusion terminals. Therefore, the change of output of the n-input

XOR circuit ( $n = 2^N$ ) is caused by the change either at the input gates or at the input diffusion terminals. To evaluate the time required for the output voltage to change from one level to the other, we can consider the cases that when the input at the gate terminal is changing while that at the diffusion terminal remains the same and vice versa. These two cases will be discussed below.

## 3-4-1 Analysis of the Delay Caused by the Change of the Input Applied at a Diffusion Terminal

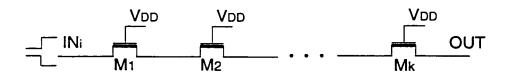

As shown in Figure 3.12, at any time, there is only one current path between the output node OUT (or  $\overline{OUT}$ ) and one of the diffusion input nodes. It should be noted that, for each of the input cases, the number of pass transistors between the input and output nodes remains the same, which is  $\log_2 n$ , where n is the number of inputs of the circuit. To evaluate the delay of an n-input pass-transistor-logic XOR gate, the circuit can be simplified into a chain consisting of  $\log_2 n$ ,  $n=2^l$ ,  $2^2$ ...., as shown in Figure 3.13, in case that the signal is transmitted through the channels of the transistors, while the gate voltage of each transistor is  $V_{DD}$ .

Figure 3.13 MOS pass transistors connecting one of the diffusion input node and the output node, when the voltage change occurs at the diffusion input while the gate voltages of the pass transistors are V<sub>DD</sub>.

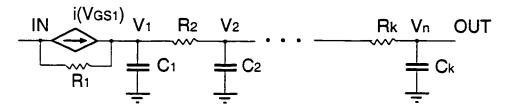

The structure shown in Figure 3.13 is often modeled as an RC-network[46] with a time constant  $\tau = \sum_{j=0}^{k} C_k \sum_{j=0}^{k} R_j$ , where  $R_j$  and  $C_k$  are the resistance and capacitance on the RC network as illustrated in Figure 3.14. However, this model may not be suitable for a transient analysis of the pass-transistor-logic circuit, as the transistors may not always act as resistors during the transient period.

Figure 3.14 Equivalent RC-network for the transistor chain.

In a gate circuit, the rise-time, is usually more critical than the fall-time, because the driving capacity of PMOS transistors is weaker than that of NMOS transistors with a similar size in preceding stages. The pass-transistor-logic gate is not an exception. Thus, we focus on the evaluation of the rise-time. It should be noted that when the input voltage of the circuit changes from low to high, the RC-network model, as shown in Figure 3.14, needs to be modified for evaluating the delay. As shown in Figure 3.15, during the rise process,  $V_I$  changes from zero to  $V_{DD}$ - $V_{In}$ , where  $V_{In}$  is the threshold voltage of the MOS pass transistor  $M_1$ . This pass transistor, if it is on, is always in the saturation mode and behaves as a voltage-controlled current source, and its current is determined by  $V_{GSI}$ = $V_{DD}$ - $V_I$ , the gate-to-source voltage of the transistor. For each of the other NMOS transistors of the circuit shown in Figure 3.13, the drain-source voltage is between zero and  $V_{DD}$ - $V_{In}$ . These transistors are always in the linear region. Therefore, the model for

the evaluation of the delay should be that shown in Figure 3.16, where  $R_I$  is the resistance of  $M_1$  in the saturation mode, and it is much larger than that of the transistors in the linear mode, and the current  $i(V_{GSI})$  is determined by  $V_{GSI}$ .

Figure 3.15 First transistor in the pass transistor chain.

Figure 3.16 Modified model of the pass-logic-transistor chain.

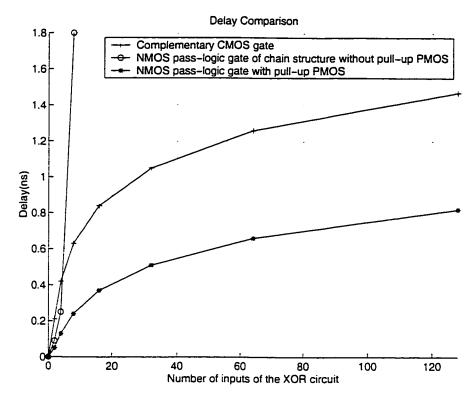

The new model presented above can be used for an evaluation of the delay of an n-input XOR gate with the tree structure when one of the input signals applied at the diffusion input terminals changes, while the gate voltage of each of the transmission transistor is  $V_{DD}$ . The delays of the XOR gates with 2. 4. 8,..., till 128 inputs, respectively, have been calculated using the two models, the classical RC model, and the one of Figure 3.16. The results are plotted in Figure 3.17. The electrical simulation results of the NMOS pass transistor circuit shown in Figure 3.13 are also plotted in the same figure for comparison.

Figure 3.17 Computation results using the models of the classical RC-network, modified model with the current-source, respectively, and the Hspice simulation results of the gate circuit.

From Figure 3.17, we can see a significant discrepancy between the two curves obtained by using the classical RC-network model and the results of the electrical simulation. The curve of the RC-network model deviates from that of the electrical simulation more than 30%. However, the curve obtained by using the modified model including the current-source is almost superposed on the curve of the simulation, and the deviation rate is less than 2%. Therefore, without requiring more computational power, the modified model provides much better results for the evaluation of the delay of the circuit than the RC model.

In conclusion, we proposed a new circuit model for evaluating the delay of the multiple-input XOR circuits in case that the signal is transmitted via the diffusion nodes of the transistors. This model provides a much more accurate delay estimation of the XOR

circuits than the classical RC-network model. As an extension, this model can also be used in transmission lines such as pass-transistor-logic chains.

As mentioned previously, in the XOR circuit, a change of the output voltage can result from a change of the input applied at gate terminal, which will be discussed in next sub-section.

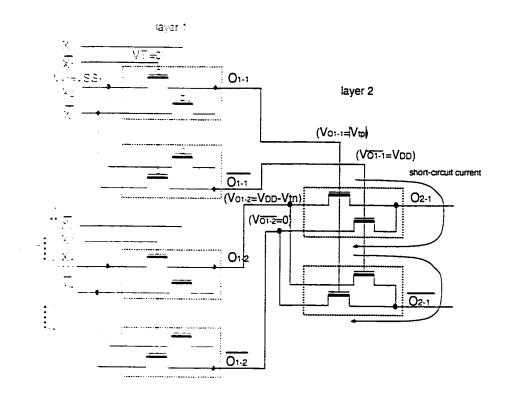

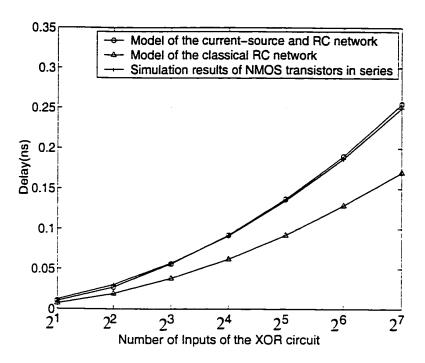

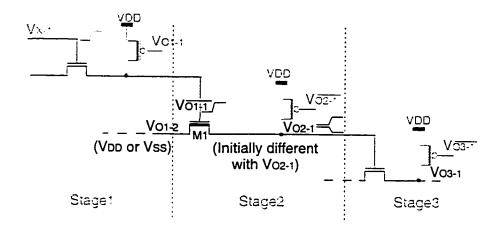

## 3-4-2 Analysis of the Delay Caused by the Change of the Input Applied at a Gate Terminal

As mentioned in the beginning of Section III-4, the level of output voltage can be changed because an input signal applied at a gate terminal changes, while the inputs at the diffusion terminals remain the same. The time required for the output voltage to change is different from the case we have discussed in Section 3-4-1. If the gate voltage of the pass transistor  $M_1$  is initially zero, as shown in Figure 3.18, the transistor is initially off. If the voltages  $V_{O1-2}$  and  $V_{O2-1}$  at the two nodes separated by  $M_1$  are initially different, when the gate input voltage changes from zero to  $V_{DD}$ ,  $V_{O2-1}$  starts to change. This  $V_{O2-1}$  may be applied to a gate of a MOS pass transistor in the next stage. The worst case of delay occurs when the all gate voltages of the MOS pass transistors in the path of the signal propagation need to be charged from the low level to the high level.

Figure 3.18 Voltage change at gate terminal.

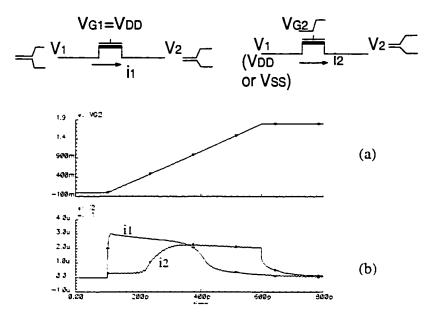

As shown in Figure 3.18, the gate voltage is a response to the signal at the preceding stage, and it has a finite rise-time as shown in Figure 3.19(a). Let's look at the two cases shown in Figure 3.19. As the gate voltage  $V_{G2}$  rises gradually during the transition, as shown in Figure 3.19(b), the current  $i_2$  is weaker than  $i_1$  that is produced by a constant  $V_{G1}=V_{DD}$ . Thus, the propagation delay due to a voltage change at the gate is much larger than that at the diffusion. Moreover, due to the change of the gate voltages, some other problems that are not critical in case of a small number of inputs, may have be taken into consideration in case of a large number of inputs. The problem of short-circuit currents may be the most critical one.

Figure 3.19 Current  $i_I$  generated when the gate voltage  $V_{GI}$  is constantly high and the source (drain) voltage  $V_I$  is changing, whereas  $i_2$  is generated by a changing gate voltage  $V_{G2}$ . On average,  $i_2$  is weaker than  $i_I$  during the transition.

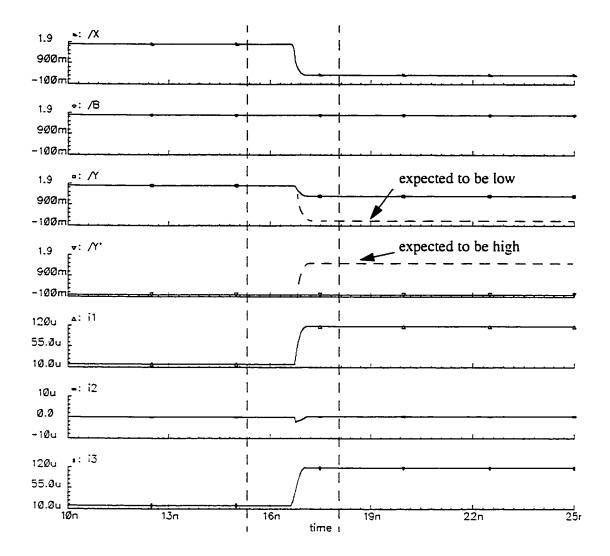

As shown in Figure 3.20, each pair of NMOS pass transistors is controlled by a pair of complementary gate voltages. The complementary output voltages change simultaneously in the opposite direction. During the transition, both NMOS pass transistors are turned on simultaneously. The short current flowing through them weakens the charging or discharging current to the targeted circuit node capacitor and increases the power dissipation. The duration of the short current is related to the rise/fall time of the input voltages at the gate terminals. Thus, a slow variation of the gate signals of the pass transistor results in an even slower variation at the output voltage of the pass transistor. If this output voltage is to be applied to the gate in the succeeding stage, the propagation and power dissipation will be even more critical. Therefore, it is very important that the input signals applied at the gate terminal have short rise and fall times.

Figure 3.20 Finite rise/fall time of the gate signals resulting in short-circuit currents.

#### 3-4-3 Effect of the Pull-Up Transistors

As we know, when the number of inputs of the XOR circuits is large, the current path for charging or discharging consists of several transistors, as shown in Figure 3.21. The transient time increases with the number of transistors. Placing pull-up PMOS transistors can not only restore the high level but also reduce the rise-time of the output voltage by providing an additional current for charging the capacitor at the circuit node. This additional current, shown as  $i_1$  in Figure 3.21(a), flows through only the pull-up PMOS transistor itself. If the PMOS transistor is fully on,  $i_1$  will usually be stronger than  $i_3$  that is the current flowing through the pass transistors in series. Thus, the pull-up PMOS can help to reduce significantly the rise-time. However, it should be noted that such a speed-up can only be obtained when certain conditions are satisfied.

Figure 3.21 Discharging and charging process for the complementary output.

- (a) Pull-up PMOS helping to accelerate the charging process at one of the output nodes.

- (b) Pull-up PMOS slowing down the discharging process at the other output node, as it contributes negatively to the discharge current.

- (c) Transient period divided into three phases.

As described in previous sub-sections, the gate voltages of the NMOS pass transistors in the charging/discharging paths is made to be full swing by means of the pull-

up PMOS transistor pairs. As shown in Figure 3.21: (a) and (b), when one of the complementary output voltages, e.g.,  $V_{\overline{Oi}}$  is changed from zero to  $V_{DD}$ , the other one,  $V_{Oi}$ , is expected to change from  $V_{DD}$  to zero. Each of the two PMOS transistors,  $M_1$  and  $M_2$ , can provide a current to charge the node capacitors respectively at certain moment. The current from  $M_1$ , in this case, is in favour of reducing the delay, but that from  $M_2$  is not desirable. For a better analysis of the transition, the transient period is divided into three phases as shown in Figure 3.21(c). Let us look at the operation of the transistors during these three phases.