Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Notice rete code

Cur file Notre référence

### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# **MULTICAST PACKET SWITCHING**

## - Scheduling, Contention Resolution, Modeling, and Architecture

Xing Chen

A Thesis

in

The Department

of

Electrical & Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University Montréal, Québec, Canada

May 1992

© Xing Chen, 1992

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

You life. Votre reference

Our file Notre reference

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant la Bibliothèque à nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-80973-6

## **ABSTRACT**

Multicast Packet Switching

— Scheduling, Contention Resolution, Modeling, and Architecture

Xing Chen, Ph.D. Concordia University, 1992

This dissertation offers a discussion of various aspects of multicast packet switching. It emphasizes the issues of call scheduling disciplines, contention resolution algorithms, mathematical analysis and switch architecture. We review three call scheduling disciplines, one-shot, SS call splitting, WS call splitting, and propose a novel scheme -revision scheduling, which would give an indication of the best delay-throughput performance under input port queueing. We discuss the contention resolution algorithms by first introducing some well known schemes then proposing two novel algorithms, a cyclic priority access scheme with its combinational logic implementation and a neural network based algorithm. The former features high speed operation, and is compact, reliable and growable. The latter provides higher throughput and lower delay and demonstrates a potential of optimal scheduling. We present some analytic tools of traffic theory for the multicast switching system. We discuss the mathematical analysis of both the random selection policy and the cyclic-priority input access scheme for one shot discipline. Then, we introduce a general unified mathematical model for both one-shot and WS call splitting input access disciplines, by using the matrix-geometric technique. We summarize some proposed multicast packet switches, then propose a shared buffer memory switch structure with maximum queue and minimum allocation, where a shared buffer pool and a reserved buffer pool are allocated for switching and buffering the packets. We estimate the size of buffer memory required for certain packet loss probability under both balanced and unbalanced traffic pattern. The proposed switch accommodates multicasting and priorities and has the modular growth capability.

## **ACKNOWLEDGEMENTS**

I would like to express my thanks to my supervisor, Professor Jeremiah F. Hayes. for his invaluable guidance, encouragement and support throughout the course of this work. He gave me the opportunity and introduced me to various aspects of the telecommunication networks. He contributed a great deal of his time, effort and ideas to the work presented in this dissertation. I consider myself fortunate to have been working in association with him.

I would like to thank Canadian International Development Agency (CIDA) for the support in carrying out my studies under the joint doctoral program between Concordia University and Southeast University (China). I would like to thank Professors Shixin Cheng and Yongbin Chen of Southeast University for reading the dissertation and making valuable comments.

I would also like to thank Professor M. K. Mehmet-Ali and Dr. I. Lambadaris for very helpful discussions and suggestions. I would like to acknowledge the examiners for their valuable comments. Many thanks are extended to all my friends for their friendship and good time. I appreciate the financial assistance in part from Centre de Recherche en Informatique de Montréal (CRIM) through a graduate bursary. Finally, I want to thank my wife Guang for her encouragement, patience and care over many weekends and week nights I spent working away at school, and my lovely daughter Wenjia for her enduring my absence and preoccupation during the period of this work.

# Dedicated to

My parents Shuhua, Fugeng.

My wife Guang,

and My daughter Wenjia

# TABLE OF CONTENTS

| LIST OF FIGURES                                       | ,   |

|-------------------------------------------------------|-----|

| LIST OF TABLES                                        | xiv |

| 1. INTRODUCTION                                       | 1   |

| 1.1. Background                                       | 2   |

| 1.2. Multicast Packet Switching                       | 3   |

| 1.2.1. Addressing of a Multicast Packet               | 3   |

| 1.2.2. Multicast Packet Switch Fundamentals           | 4   |

| 1.2.3. Definition of Throughput                       | 6   |

| 1.3. Interesting Issues                               | 7   |

| 1.4. Outline                                          | 8   |

| References 1                                          | 10  |

| 2. MULTICASTING SCHEDULING                            | 11  |

| 2.1. Introduction                                     | 12  |

| 2.2. Scheduling and its Implementation Considerations | 14  |

| 2.2.1. One-shot Scheduling                            | 14  |

| 2.2.2. SS Call Splitting                              | 15  |

| 2.2.3. WS Call Splitting                              | 18  |

| 2.2.4. Revision Scheduling — A Novel Scheme           | 20  |

| 2.3. Performance Comparison by Simulation             | 22  |

| 2.4. Conclusion                                       | 24  |

| Appendix 2: Simulation Model                          | 25  |

| References 2                                                    | 28  |

|-----------------------------------------------------------------|-----|

| 3. CONTENTION RESOLUTION ALGORITHMS                             | 29  |

| 3.1. Review of Three Algorithms                                 | 3() |

| 3.2. Cyclic Priority Access Scheme with its Combinational Logic |     |

| Implementation                                                  | 34  |

| 3.3. Neural Network Based Algorithm                             | 44  |

| 3.3.1. Preliminary of Hopfield Model of Neural Networks         | 46  |

| 3.3.2. A Model for One-Shot Scheduling                          | 49  |

| 3.3.3. An Extension Model — Windowed service                    | 5(  |

| 3.3.4. A Model for SS Call Splitting                            | 58  |

| 3.4. Conclusion                                                 | 62  |

| References 3                                                    | 65  |

| 4. MODELING AND MATHEMATICAL ANALYSIS                           | 66  |

| 4.1. Introduction                                               | 67  |

| 4.2. Analysis of One-Shot Discipline with Random Selection      | 69  |

| 4.2.1. Mathematical Model                                       | 69  |

| 4.2.2. Numerical Results                                        | 74  |

| 4.3. Analysis of One-Shot Discipline with Cyclic Priority       | 77  |

| 4.3.1. Mathematical Model                                       | 77  |

| 4.3.2. Numerical Results                                        | 83  |

| 4.4. Review of Two Models for WS Call Splitting                 | 88  |

| 4.4.1. Model I by J. F. Hayes et al.                            | 88  |

| 4.4.2. Model II by J. Y. Hui et al.                             | 90  |

| 4.5. A General Unified Model for Performance Analysis           | 91  |

| 4.5.1. Description of the System                                   | 92  |

|--------------------------------------------------------------------|-----|

| 4.5.1.A). Q Matrix for One-Shot Discipline                         | 95  |

| 4.5.1.B). Q Matrix for WS Call Splitting Discipline                | 95  |

| 4.5.2. Solution via Matrix Geometric Approach                      | 98  |

| 4.6. Remarks                                                       | 100 |

| Appendix 4A: Algorithm for the Formation of the Q Matrix (One-Shot |     |

| Scheduling)                                                        | 103 |

| Appendix 4B: Algorithm for the Formation of the Q Matrix (WS Call  |     |

| Splitting)                                                         | 104 |

| References 4                                                       | 105 |

| 5. SWITCH ARCHITECTURE                                             | 106 |

| 5.1. Introduction                                                  | 107 |

| 5.2. A Survey of Multicast Packet Switches                         | 107 |

| 5.2.1. Banyan-Based Space-Division Switch                          | 107 |

| 5.2.2. Knockout Switch                                             | 115 |

| 5.2.3. Shift Switch                                                | 123 |

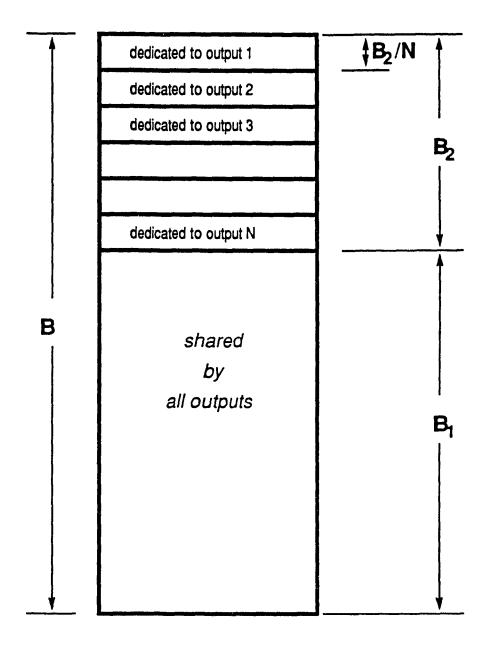

| 5.2.4. Shared Buffer Memory Switch                                 | 127 |

| 5.3. A Shared Buffer Memory Switch with Maximum Queue              |     |

| and Minimum Allocation                                             | 130 |

| 5.3.1. Classifications of Shared Memory Switches                   | 131 |

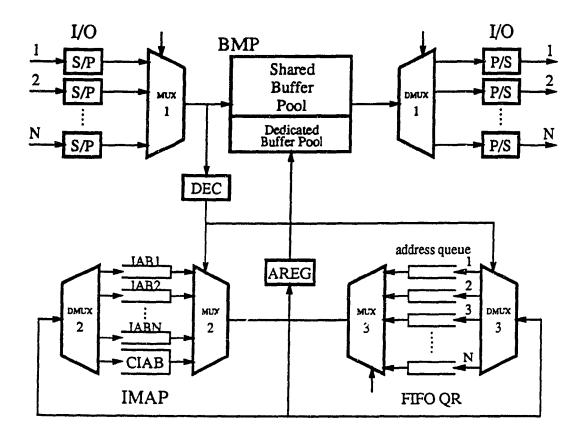

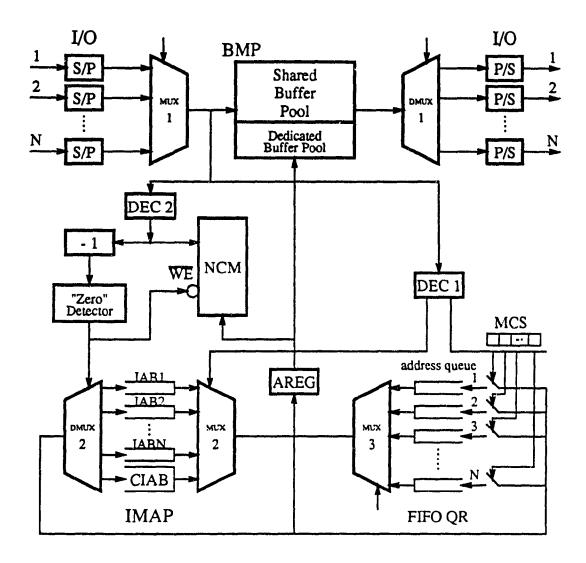

| 5.3.2. The Switch Architecture                                     | 132 |

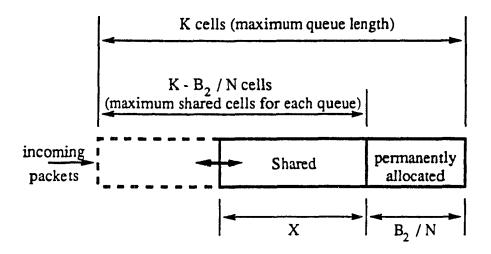

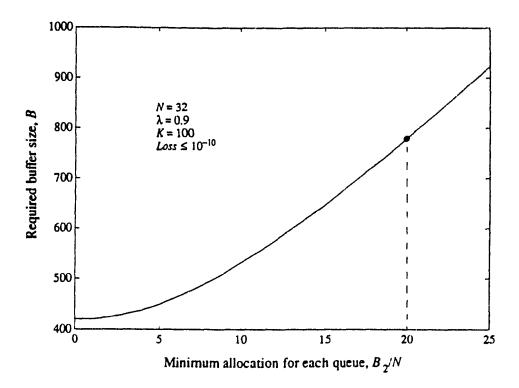

| 5.3.3. Estimation of Packet Loss Probability                       | 137 |

| 5.3.3.1 Balanced Traffic                                           | 140 |

| 5.3.3.2 Unbalanced Hot-Spot Traffic                                | 143 |

| 5.3.4. The Capabilities of Multicasting, Modularity and Priority | 144   |

|------------------------------------------------------------------|-------|

| 5.4. Conclusion                                                  | 148   |

| References 5                                                     | . 150 |

| 6. CONCLUSIONS AND FUTURE RESEARCH                               | . 153 |

| 6.1 Conclusions                                                  | . 154 |

| 6.2 Future Research                                              | . 155 |

# LIST OF FIGURES

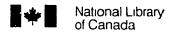

| Figure 1.1.  | ATM packet format                                     | 5  |

|--------------|-------------------------------------------------------|----|

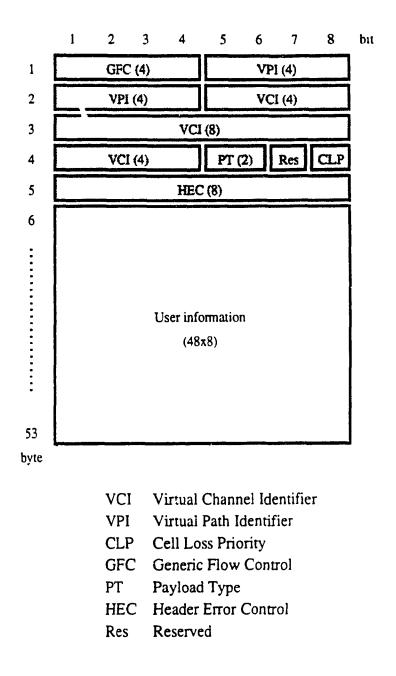

| Figure 1.2.  | A multicast switch                                    | 6  |

| Figure 1.3.  | An example of multicast switch                        | 6  |

| Figure 2.1.  | Concept of one-shot scheduling                        | 15 |

| Figure 2.2.  | A switch fabric for SS call splitting scheduling      | 16 |

| Figure 2.3.  | Multicasting operation                                | 17 |

| Figure 2.4.  | Concept of WS call splitting scheduling               | 18 |

| Figure 2.5.  | Cross-bar structure with WS call splitting scheduling | 19 |

| Figure 2.6.  | Lee's multicast switch                                | 20 |

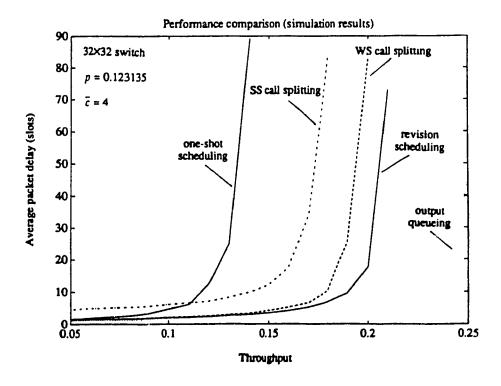

| Figure 2.7.  | Comparison of the delay-throughput performance        | 23 |

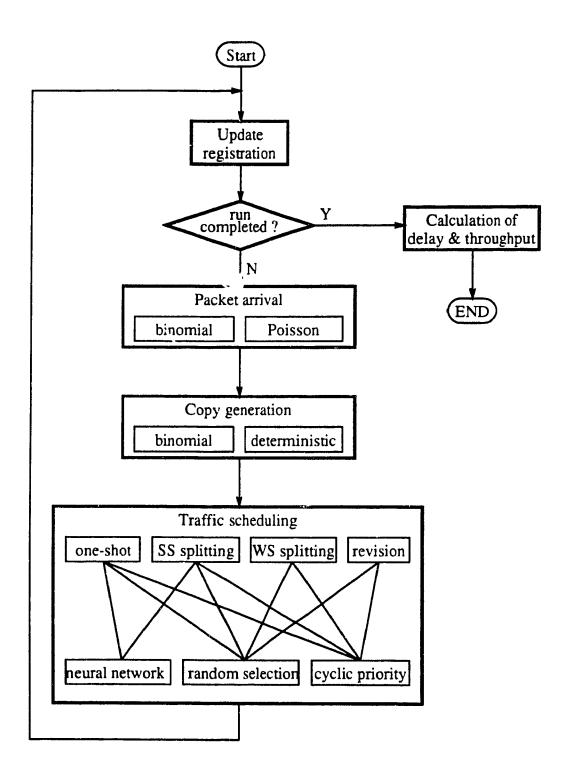

| Figure A2.1  | . A flowchart of the program SIMU                     | 26 |

| Figure 3.1.  | A re-entry network for contention resolution          | 31 |

| Figure 3.2.  | Three-phase algorithm                                 | 32 |

| Figure 3.3.  | Ring reservation-based contention resolution          | 33 |

| Figure 3.4.  | A basic decision element                              | 35 |

| Figure 3.5.  | Cyclic priority assignment                            | 36 |

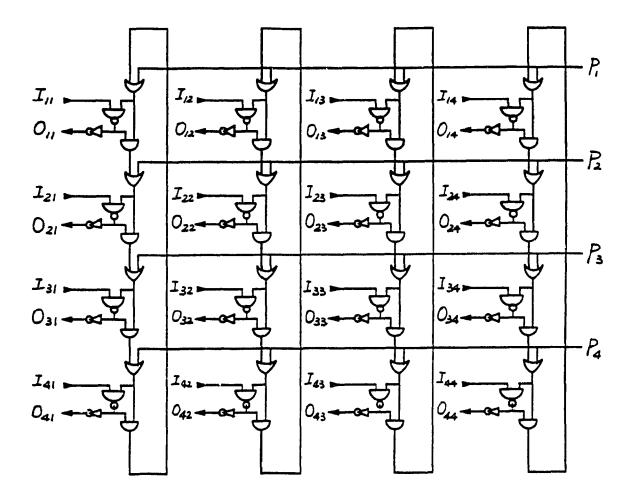

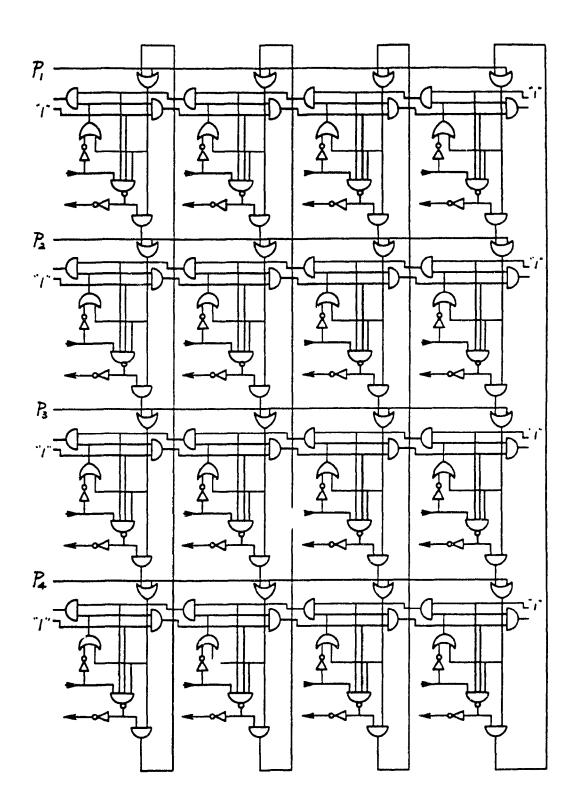

| Figure 3.6.  | A 4×4 decision board for WS call splitting discipline | 37 |

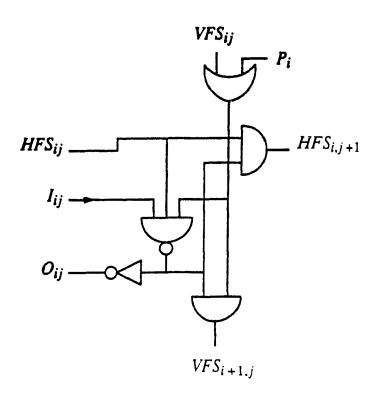

| Figure 3.7.  | A basic element with HFS                              | 38 |

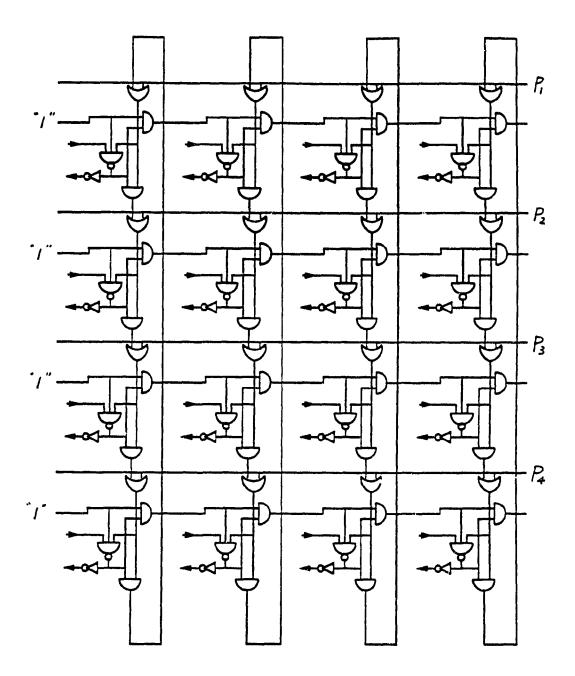

| Figure 3.8.  | A 4×4 decision board for SS call splitting discipline | 39 |

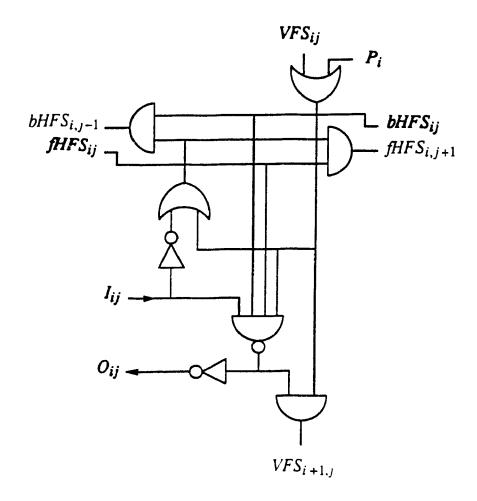

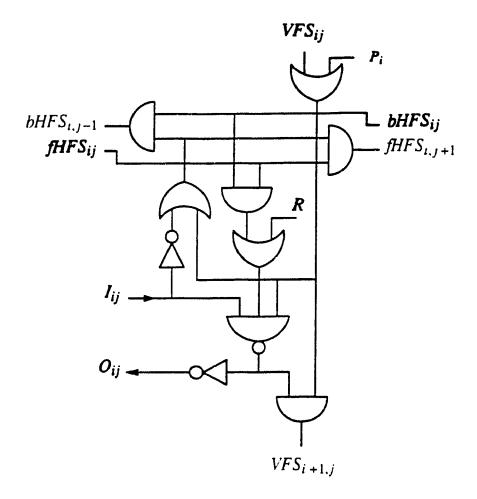

| Figure 3.9.  | A basic element with fHFS and bHFS                    | 40 |

| Figure 3.10. | A 4×4 decision board for one-shot scheduling          | 41 |

| Figure 3.11. | A basic element for revision scheduling                                              | 42 |

|--------------|--------------------------------------------------------------------------------------|----|

| Figure 3.12. | An example of the longest signal routes                                              | 43 |

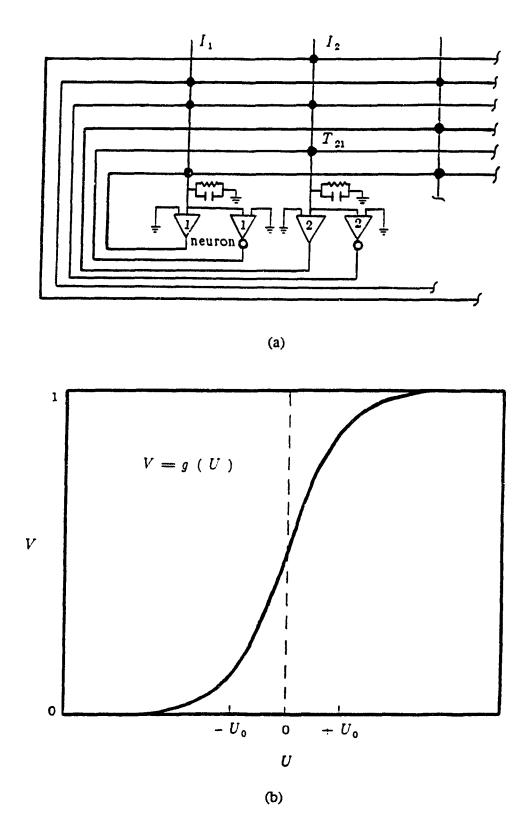

| Figure 3.13. | A Hopfield model of neural network                                                   | 47 |

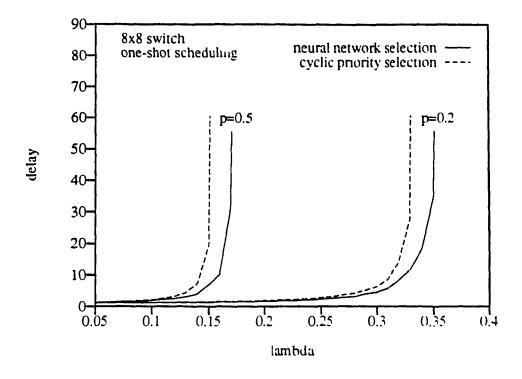

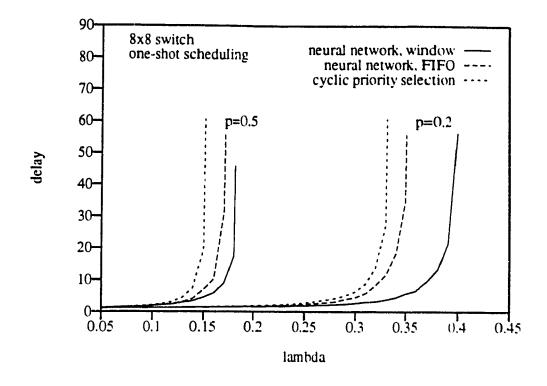

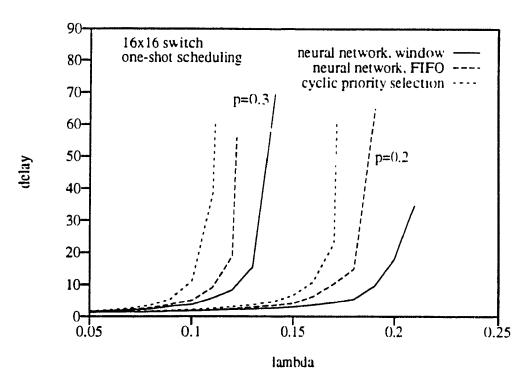

| Figure 3.14. | A comparison of cyclic priority selection and neural network selection               | 55 |

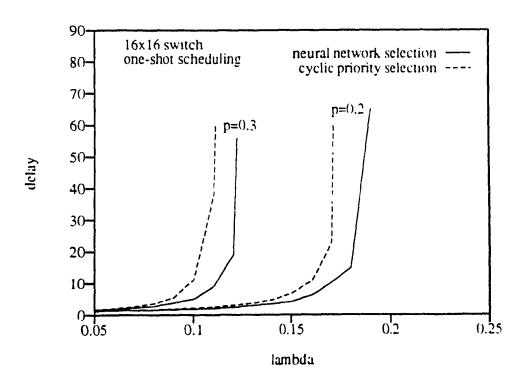

| Figure 3.15. | Input port queueing with windowed service                                            | 57 |

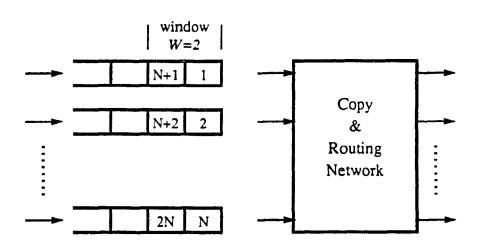

| Figure 3.16. | Improvement of windowed service (window size $W=2$ )                                 | 59 |

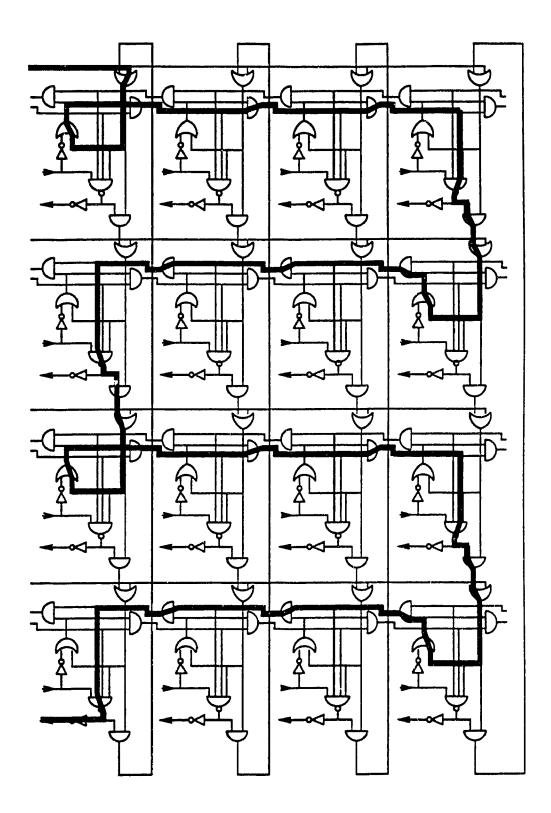

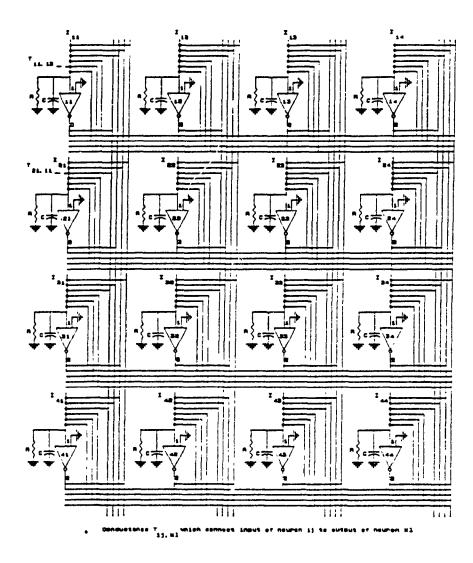

| Figure 3.17. | A two-dimensional structure of Hopfield neural network                               | 60 |

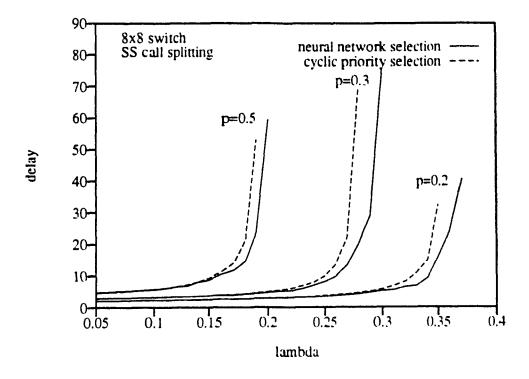

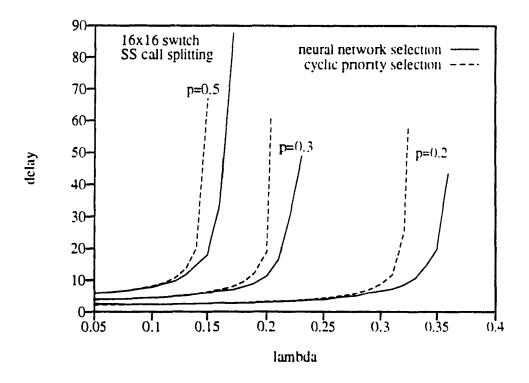

| Figure 3.18. | Improvement by neural network for SS call splitting                                  | 63 |

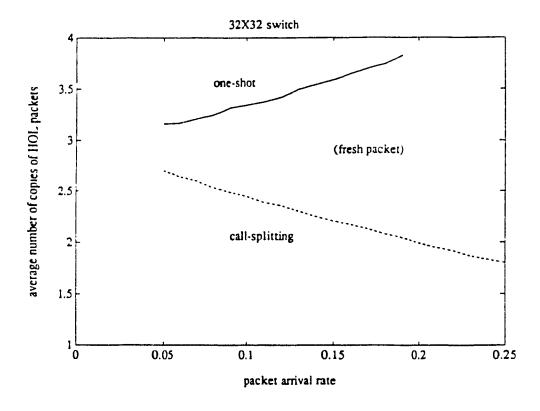

| Figure 4.1.  | Average number of copies of the HOL packet vs. packet arrival rate                   | 68 |

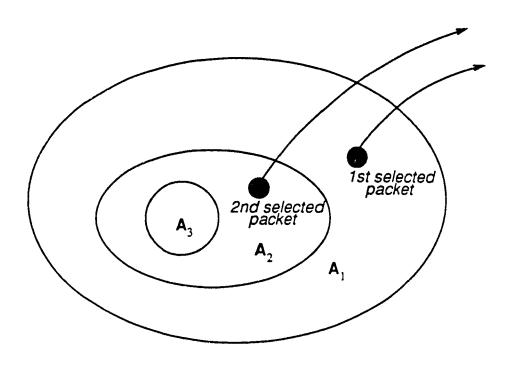

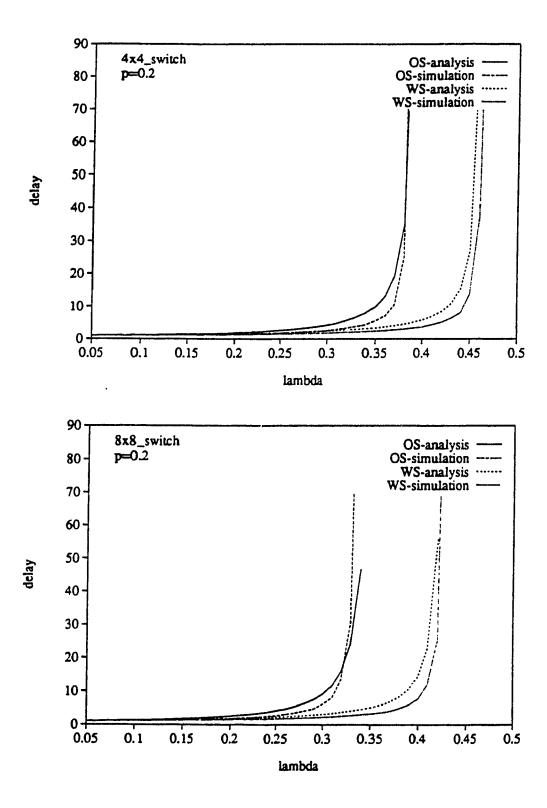

| Figure 4.2.  | Multistage screening process                                                         | 70 |

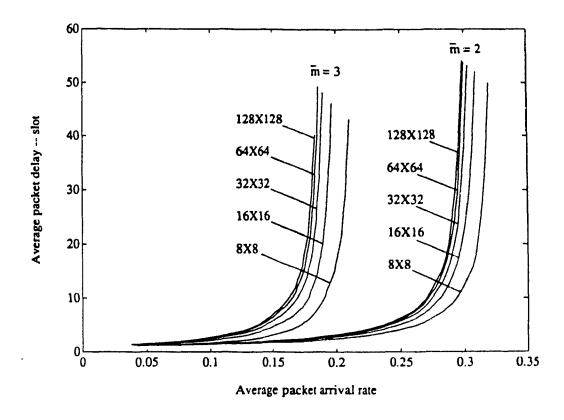

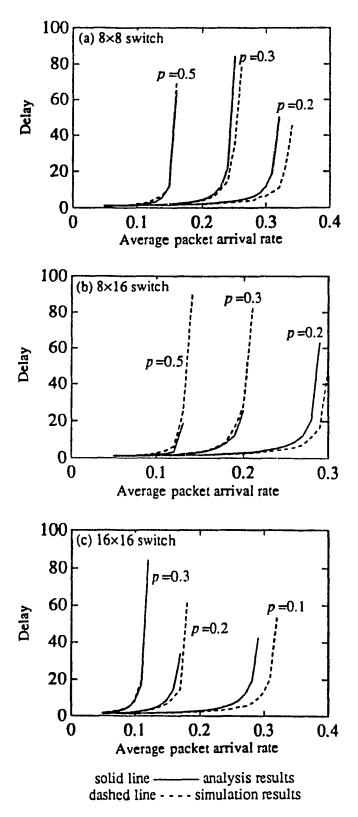

| Figure 4.3.  | Average packet delay for several switch sizes with constant $\overline{m}$ (2 and 3) | 75 |

| Figure 4.4.  | Average packet delay with one-shot scheduling and random-selection                   |    |

|              | policy                                                                               | 76 |

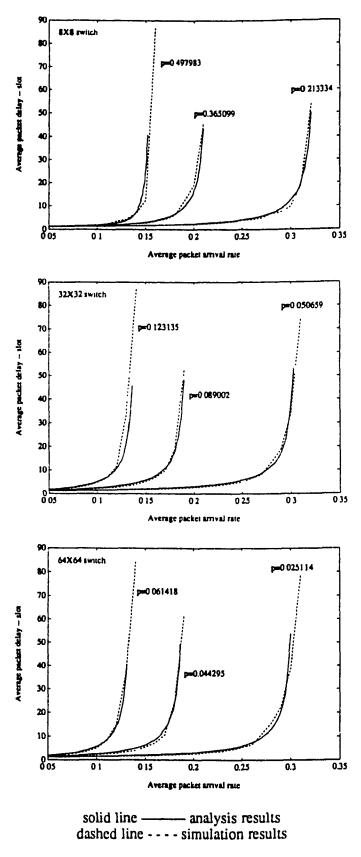

| Figure 4.5.  | Average packet delay with one-shot scheduling and cyclic priority                    |    |

|              | policy where each incoming packet generates copies according to                      |    |

|              | Bernoulli trials with parameter p for each output port                               | 85 |

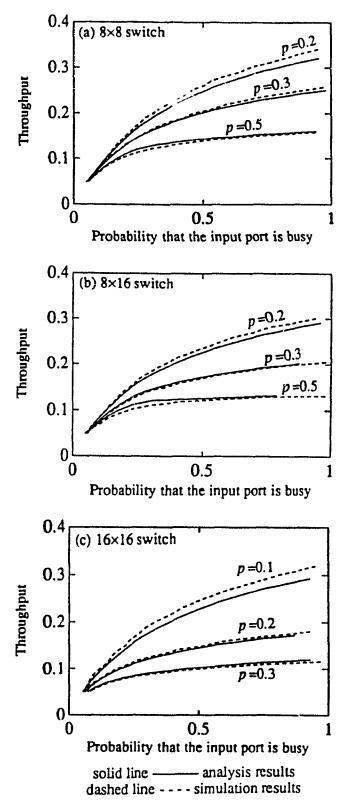

| Figure 4.6.  | Average throughput with one-shot scheduling and cyclic priority                      |    |

|              | policy where each incoming packet generates copies according to                      |    |

|              | Bernoulli trials with parameter p for each output port                               | 86 |

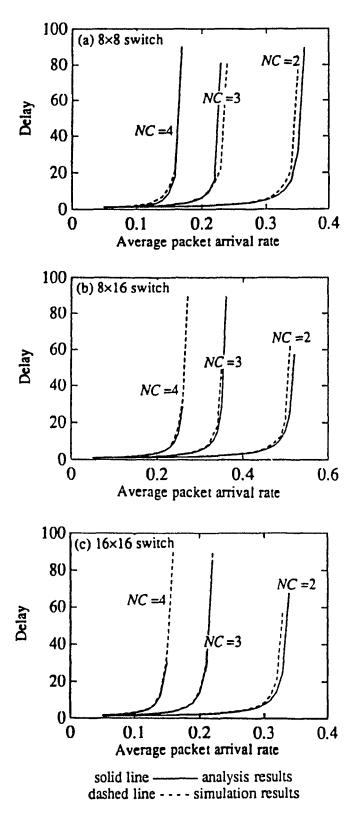

| Figure 4.7.  | Average packet delay with one-shot scheduling and cyclic priority                    |    |

|              | policy where each incoming packet generates NC (a constant number                    |    |

|              | of) copies to a set of output ports                                                  | 87 |

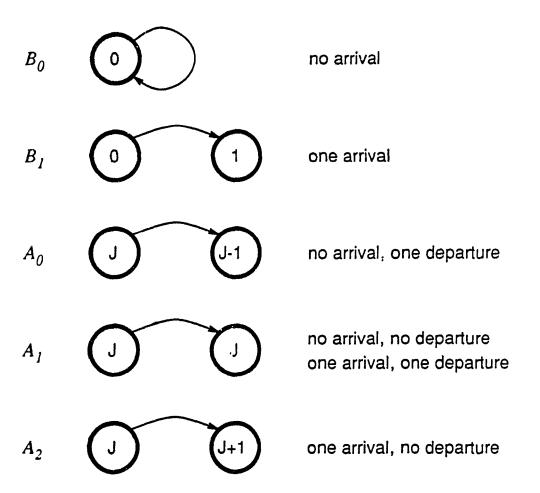

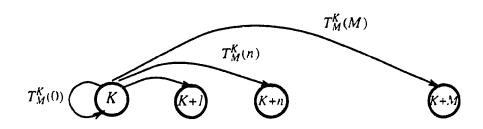

| Figure 4.8.  | Transition of the states                                                             | 92 |

| Figure 4.9.  | Configuration of a block matrix                                                      | 94 |

| Figure 4.10. | Transition of the states within block matrices for one-shot scheduling               | 96 |

| Figure 4.11. Transition of the states within block matrices for WS call splitting       | 97  |

|-----------------------------------------------------------------------------------------|-----|

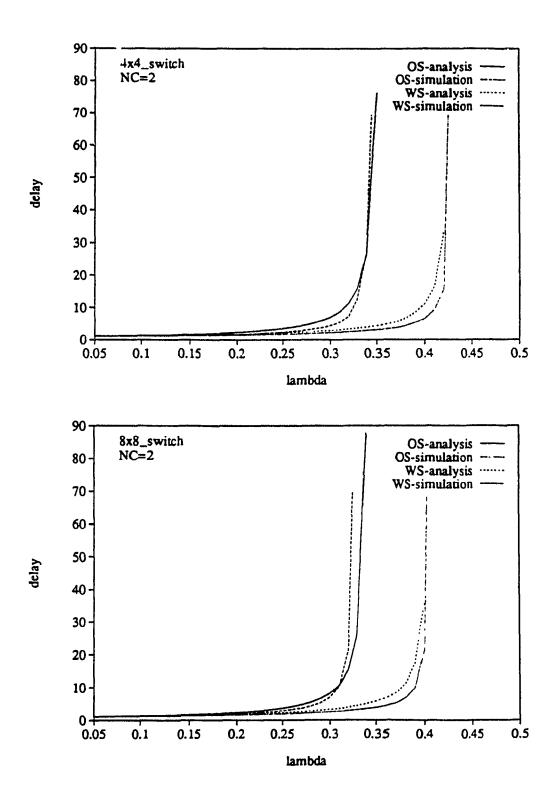

| Figure 4.12. Numerical results with binomial copy distribution                          | 101 |

| Figure 4.13. Numerical results with deterministic copy distribution (constant fanout of |     |

| the packet)                                                                             | 102 |

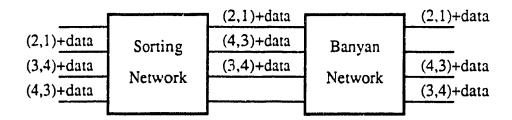

| Figure 5.1. A 8×8 Batcher-banyan nonblocking routing network                            | 109 |

| Figure 5.2. Copy network of Starlite switch                                             | 110 |

| Figure 5.3. Copy network of Turner's broadcast packet switch                            | 111 |

| Figure 5.4. A block diagram of Lee's copy network                                       | 112 |

| Figure 5.5. Multicast switch with centralized controller                                | 113 |

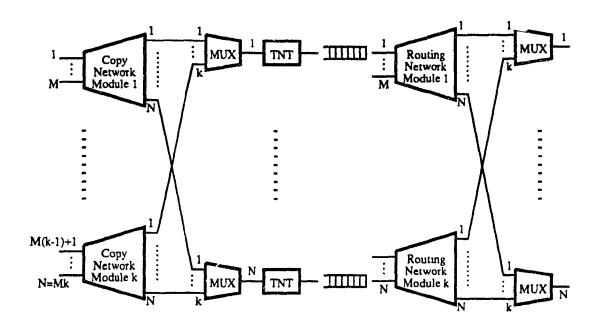

| Figure 5.6. A modular structure of a Batcher-banyan multicast switch                    | 114 |

| Figure 5.7. Knockout switch                                                             | 115 |

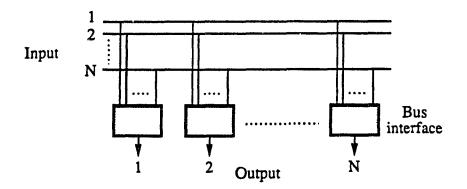

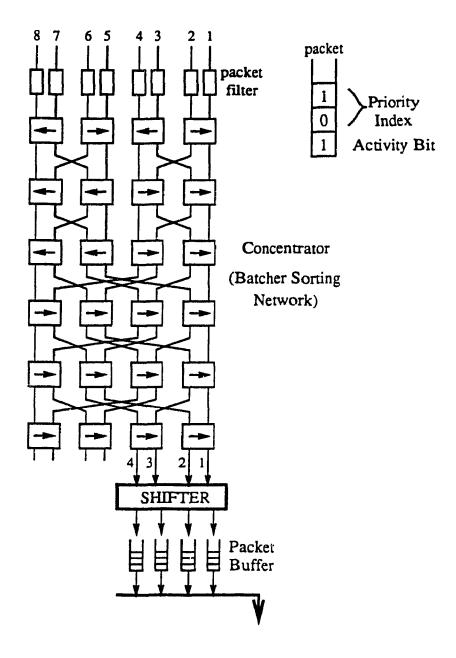

| Figure 5.8. A 8:4 concentrator                                                          | 116 |

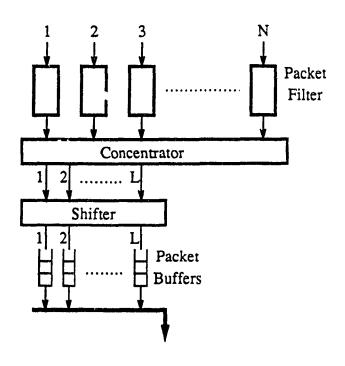

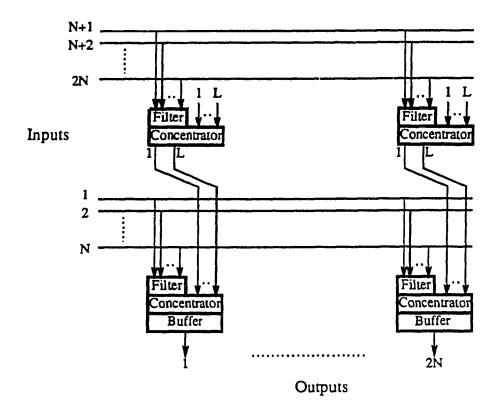

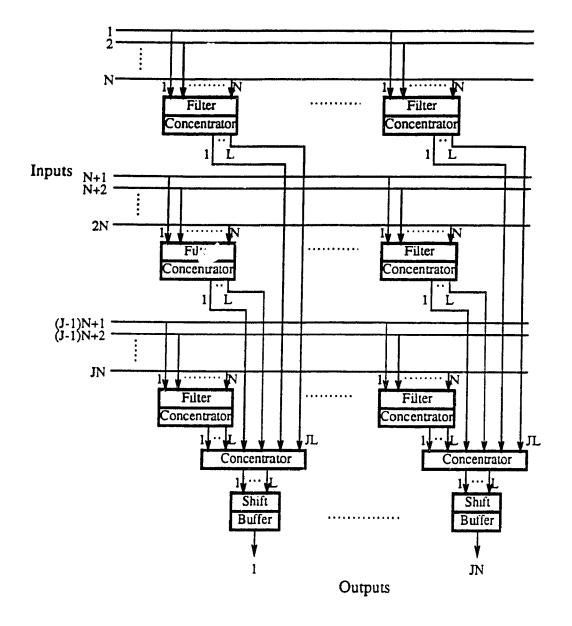

| Figure 5.9. Modular growth of knockout switch                                           | 117 |

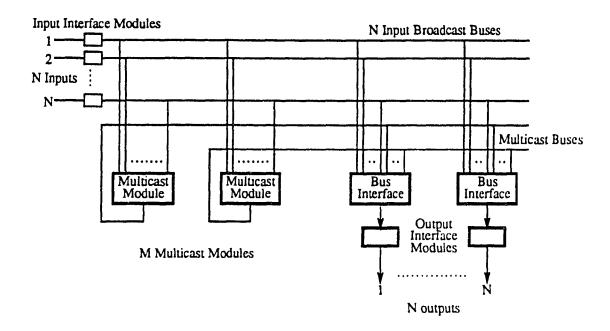

| Figure 5.10. A knockout switch with multicast modules                                   | 118 |

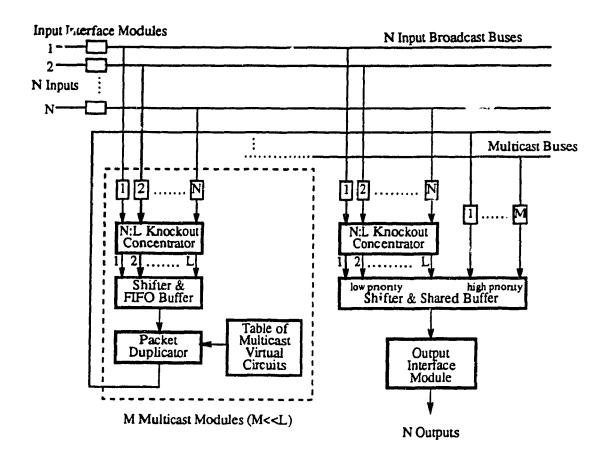

| Figure 5.11. Multicast operation with packet duplicator approach                        | 119 |

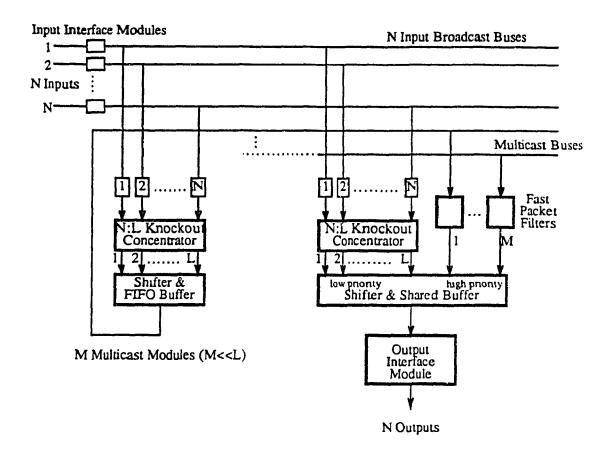

| Figure 5.12. Multicast operation with fast packet filter approach                       | 120 |

| Figure 5.13. Bus interface with sorter-type concentrator                                | 122 |

| Figure 5.14. An alternative of modular structure of knockout switch                     | 123 |

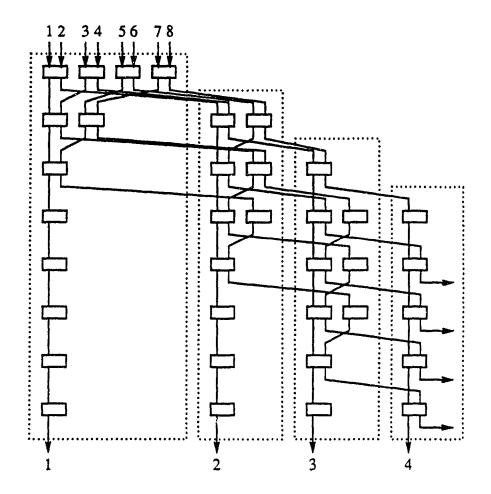

| Figure 5.15. A shift switch                                                             | 124 |

| Figure 5.16. Multicast operation in a shift switch                                      | 126 |

| Figure 5.17. Kuwahara's shared buffer memory switch                                     | 127 |

| Figure 5.18. Output queue chain in shared buffer memory switch                          | 128 |

| Figure 5.19. Multicast operation in shared buffer memory switch                         | 129 |

| Figure 5.^0. Concept of a memory-type switch                                            | 130 |

| Figure 5.21. | A shared buffer memory switch                                          | 133  |

|--------------|------------------------------------------------------------------------|------|

| Figure 5.22. | Memory allocation in proposed switch                                   | 134  |

| Figure 5.23. | FIFO address queue                                                     | 135  |

| Figure 5.24. | Memory resource used by an output queue                                | 138  |

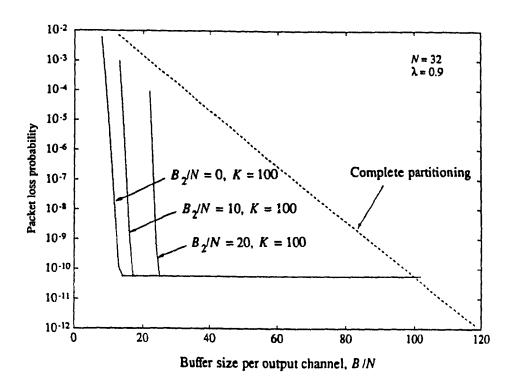

| Figure 5.25. | Buffer requirement vs. $B_2/N$                                         | 14() |

| Figure 5.26. | Packet loss probability vs. buffer size for sharing with maximum queue |      |

|              | length                                                                 | 141  |

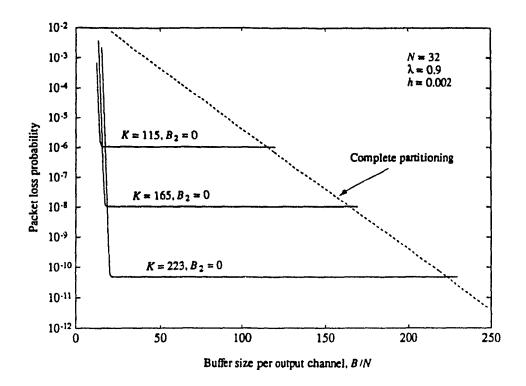

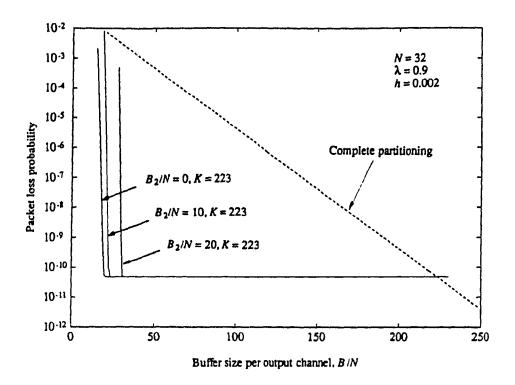

| Figure 5.27. | Packet loss probability vs. buffer size for sharing with maximum queue |      |

|              | and minimum allocation                                                 | 142  |

| Figure 5.28. | Packet loss probability vs. buffer size for sharing with maximum queue |      |

|              | under unbalanced traffic                                               | 144  |

| Figure 5.29. | Packet loss probability vs. buffer size for sharing with maximum queue |      |

|              | and minimum allocation under unbalanced traffic                        | 145  |

| Figure 5.30. | Multicast operation in proposed switch                                 | 146  |

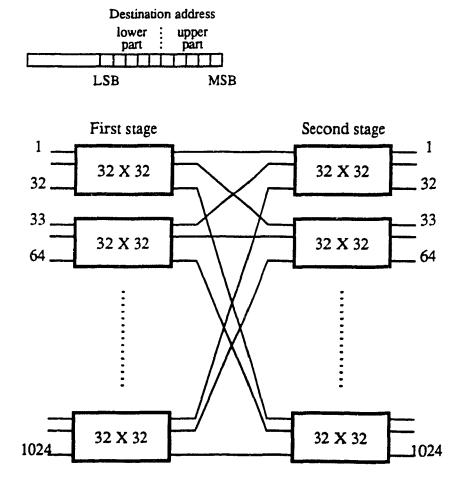

| Figure 5.31. | Modular structure of a 1024×1024 shared buffer memory switch           | 147  |

# LIST OF TABLES

| Table A2.1. Options of SIMU                                | 25         |

|------------------------------------------------------------|------------|

| Table 3.1. Truth table of a basic element                  | 35         |

| Table 3.2. Truth table for the basic element in Figure 3.7 | 38         |

| Table 3.3. Truth table for the basic element in Figure 3.9 | 40         |

| Table 3.4. Comparison in terms of the number of gates      | 44         |

| Table 3.5. Realizable switch size                          | <b>4</b> 4 |

| Table 3.6. Saturated throughput of N×N unicast switch      | 56         |

# CHAPTER 1

# **INTRODUCTION**

- 1.1. BACKGROUND

- 1.2. MULTICAST PACKET SWITCHING

- 1.2.1. Addressing of a Multicast Packet

- 1.2.2. Multicast Packet Switch Fundamentals

- 1.2.3. Definition of Throughput

- 1.3. INTERESTING ISSUES

- 1.4. OUTLINE

- REFERENCES 1

1. INTRODUCTION - 2 -

#### 1.1. BACKGROUND

The information age had been characterized as a time of exploding demand for communications applications of all kinds. These new demands create both great opportunities and difficult challenges for suppliers of telecommunications services and equipment. Most attention currently centers on Integrated Services Digital Network (ISDN). It is in the environment of changing user needs, intelligent digital communication technologies, and declining costs that many of the world's telecommunications networks have begun to deploy ISDN.

Work on ISDN, or narrowband ISDN, has resulted in a standard for a digital line interface, comprising two 64Kb/s circuit switched channels for voice and bulk data and a 16 Kb/s packet switched channel for data and control information. But, the only integration possible is at the level of physical packaging. It has become clear that these transfer modes can not efficiently meet the requirements for faster enhanced communications or multi-media communications.

An information transport network of next generation should be able to provide connections in a wide range of bandwidth. Application, such as telemetry require just a few bits per second, while video may require 100Mb/s or more. An information transport network should be able to handle such extremes, as well as everything in between. New technology, most notably fiber optics, has brought the broadband ISDN (BISDN) closer to reality. For example, using single-mode fibers and single-wavelength lasers, data rate equal to 4Gb/s over 100 km without repeaters has been achieved. While fiber optics technology provides the necessary bandwidth for transmission purposes, the creation of a network that can provide high bandwidth services to the users remains a challenge. The bottleneck comes primarily from switching, which will carry all applications in an integrated fashion and offer the desired flexibility to handle the wide diversity of data rate and latency requirement resulting from the integration of services.

The Asynchronous Transfer Mode (ATM) was proposed for BISDN to meet these requirements by combining the high-speed capability of the circuit mode and the flexibility of the packet mode. ATM specifies fixed-size packets comprising 48 bytes of data and 5 bytes of control information each. Many line speeds are also specified, with nominal rates equal to 155.52Mb/s

1. INTRODUCTION

(required for digitized HDTV), and 622.08Mb/s. The various architectures for such fast packet switches have been reported and were surveyed in [1].

In BISDN, the services will be very diversified. Such diversity of services demands not only point-to-point communications but also multipoint communications. Therefore, ATM switching networks, the essential component in the network, should be able to provide the multicast function. The term multicast would appear to be derived from the term broadcast and means concurrent data transmission to a restricted set of recipients. We shall use the term unicast to indicate the point-to-point connection.

The idea of multicast first appeared in the early 1980s. It was expected to make point-to-multipoint communication less complex, lead to greater concurrency and decrease network load. This would benefit a wide range of applications: resource location in the presence of multiple servers; updates of, and information retrieval from, replicated databases; replicated procedure cells; majority voting systems; distributed parallel computation; routing table dissemination; distributed games; commercial television distribution; voice or video teleconferencing; and clock synchronization. So far, multicast has still not become a standard facility, but is very much alive as a research topic.

### 1.2. MULTICAST PACKET SWITCHING

Multipoint connections could be accomplished by creating multiple copies of the packet at the source node, each destined to one of the desired destinations, and routing the copies independently. Alternatively, multicast routing may be achieved by requiring the switches in the network to have the capability to replicate a packet at several of their output ports, according to information provided for that purpose, thus reaching the multiple destinations from a single packet originating at the source. This mode of operation results in lower traffic throughout the network and gives birth to the ATM multicast packet switch design.

#### 1.2.1. Addressing of a Multicast Packet

1. INTRODUCTION -4-

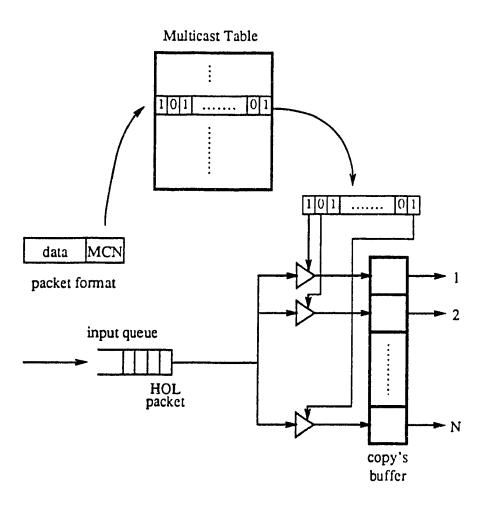

Addressing is one of the key functionality for multicasting communication. A multicast address is the most general form of an address. Common special cases are unicast and broadcast addresses. Whereas the latter may be realized comparably easily in almost all types of networks. multicast addressing turns out to be quite tricky.

In ATM, all information is conveyed through the network in fixed-size packets. Figure 1.1 shows the ATM packet format, as currently conceived by CCITT 1990 Recommendation I.361 [2][3]. When a packet arrives at the input of the switch node, a destination address relevant to local routing inside the switch is derived, based on its header information (mainly VCI). For a multicast packet, it is impracticable to carry all the addresses of the destinations to which the packet is sent, resulting in too much overhead on the multicast packet. An easier way would be that multicast packet only carries a multicast group address (or a multicast channel number) to indicate the subset of destinations. A simple table look-up is usually used to decode the addresses in the multicasting operation. Multicast group addresses need to be integrated into present addressing standards, and be assigned, maintained and managed.

#### 1.2.2. Multicast Packet Switch Fundamentals

The function of a multicast packet switch is to transmit an arriving multicast packet to a set of destinations. Furthermore, it must be flexible enough to support unicast and broadcast connections as special cases. Like unicast switches, the  $N \times N$  multicast switch+ architecture has N input ports (or input lines, or input links) where the traffic arrives and N output ports (or output lines, or output links) where the traffic leaves as shown in Figure 1.2.

The multicasting operation usually comprises two sequential steps: the arriving packet is replicated and the copies of the packet are routed to a set of output ports (Figure 1.3), while in some cases, these two steps are completed simultaneously. In this dissertation, we address the arriving traffic as the packet, and the leaving traffic as the copy without exception even for uni-

<sup>†</sup> It is not necessary that the number of input ports equals to the number of output ports. The nonsquare  $NI \times NO$  switch, with larger fan-out than fan-in  $(NO \ge NI)$ , would be appropriate in some practical applications.

1. INTRODUCTION - 5 -

Figure 1.1. ATM packet format

#### cast connections.

In a multicast packet switch, there are two reasons for buffering. One is that the required total bandwidth exceeds the capacity of the switch, that is the total number of destination requests exceeds the number of output ports. The other is that the required bandwidth for a particular output line exceeds the capacity of the single output line, that is multiple packets request

1. INTRODUCTION - 6 -

Figure 1.2. A multicast switch

Figure 1.3. An example of multicast switch

the same output port simultaneously. Buffering or queueing provides the means to regulate the traffic and prevent the packet loss.

## 1.2.3. Definition of Throughput

In unicast switching, the throughput is defined as the average number of packets being transmitted through the switch node per input/output per time slot, or as the utility of each output line. The saturated throughput is defined as the throughput when all the input queues are 100% full, or as the throughput when packet delay goes up rapidly.

As to the multicast switch, we have two possible definitions. One is the average number of

1. INTRODUCTION - 7 -

copies being transmitted to output ports per output line per time slot, namely copy's throughput. Since the generated copies are for different output ports, the saturated copy's throughput is greater than that of the unicast switch. Another definition is the average number of packets being taken from input port queues per input line per time slot, namely packet's throughput, which is much lower than that of the unicast switch because each packet may generate several copies.

In this dissertation, we shall only use the latter, packet's throughput, simply called throughput. Because the most interesting value of throughput is the saturated throughput, rather than the evolution of the throughput with the change of packet arrival rate, we shall evaluate the switch by showing only the delay-throughput performance, from which the saturated throughput can be read explicitly.

#### 1.3. INTERESTING ISSUES

Multicasting does not only bring promising services, but also raises new research topics which do not arise in unicast switches. The output port conflicts when multiple packets request the same output port concurrently is present in both unicast and multicast cases. Therefore, queueing is required in order to avoid packet loss, in any type of switch structure. In most cases, the queue is located either at the input or at the output of the switch.

If we assume that the switch fabric runs at the same speed as the input and output lines, only one packet can be accepted by any given output line during a time slot, and other packets addressed to the same output must queue on the input lines. Under this assumption, it has been shown that a unicast switch has a maximum throughput of 58.6% of switch capacity, regardless of the contention resolution mechanism [4][5][6]. However, in the multicast switch, we may consider several different service disciplines in terms of scheduling the transmission of the copies of the packet. Such a topic of call scheduling does not arise in unicast switches. We will see that different call scheduling discipline leads to different delay-throughput performance. Furthermore, the delay-throughput performance can be improved by introducing an optimal contention resolution algorithm. Also, the exact mathematical analysis becomes more difficult because of header-of-line (HOL) destination coupling and lack of a model to describe the copy distribution of the

1. INTRODUCTION - 8 -

HOL packet.

In contrast, if the  $N \times N$  switch fabric runs N times as fast as the inputs and outputs or has N parallel paths so that any incoming packet is able to pass through the switch within a time slot, then an output queueing is required instead of input queueing. In this context, the existing traffic theory for unicast switching can be applied to multicast switching just by considering multicasting traffic arrival process. Issues such as call scheduling, contention resolution are not present in output port queueing scheme. Therefore, our interest tends to packet loss probability due to the finite buffer resources for output queueing.

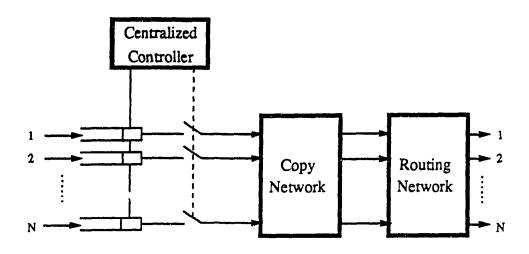

As far as the switch architecture is concerned, in point-to-point communication networks, a switching system is able to connect any incoming channel to any outgoing channel. To support multipoint connections, a switching system must be able to connect any incoming channel to any subset of its outgoing channels. Therefore, an extra network is needed, such as copy network in a banyan-based space-division multicast packet switch [7], multicast module and multicast bus in knockout switch [8] and multicasting controller in shared buffer memory switch [9].

#### 1.4. OUTLINE

The intent of this dissertation is to offer a discussion of various aspects of multicast packet switching. The next three chapters emphasize the issues related to the multicast packet switch with input port queueing: call scheduling disciplines, contention resolution algorithms, and mathematical analysis. Then, we spend one chapter to discuss the multicast packet switch architecture both with input queueing and output queueing.

Chapter 2 reviews three call scheduling disciplines, one-shot, SS call splitting and WS call splitting, and proposes a novel scheme — revision scheduling. By comparison, revision scheduling is most preferred as far as the delay-throughput performance is concerned. Taking into account complexity of implementation as well as performance, each of the four categories does not seem to have distinctive superiority over the others. There is a trade-off between the performance and switch structure complexity.

1. INTRODUCTION

Chapter 3 discusses contention resolution algorithms by first introducing some well known schemes. After that, we propose two novel algorithms, a cyclic priority access scheme with its combinational logic implementation and a neural network based algorithm. The combinational logic scheme features simple and high speed operation, in comparison with the other methods such as the three-phase algorithm [4] and the ring-reservation algorithm [6]. It is compact, reliable and growable. The neural network based algorithm provides higher throughput and lower delay and demonstrates a potential optimal scheduling.

Chapter 4 presents some analytic tools of traffic theory for the input port queue of the multicast switching system. In this chapter, we discuss the mathematical analysis of both the random

selection policy and the cyclic-priority input access scheme for one-shot discipline. Then, we

summarize two analytic models for WS call splitting discipline by Hayes and Hui, respectively.

Finally, we introduce a general unified mathematical model for both the one-shot and the WS call

splitting input access disciplines, by using matrix-geometric techniques. These results could

serve to model the multicast packet switch and to predict the onset of congestion in the system

Although this chapter is devoted to the multicast switch, the analytic model can also be applied

to other queueing problems.

In Chapter 5, we first summarize some proposed multicast packet switches, including the banyan-based space-division switch, the knockout switch, the shift switch and the shared buffer memory switch. Then we propose a shared buffer memory switch structure with maximum queue and minimum allocation, where a shared buffer pool and a reserved buffer pool are handled for switching and buffering the packets. We estimate the size of buffer memory required for certain packet loss probability under both balanced and unbalanced traffic pattern. The proposed switch accommodates multicasting and priorities and has the modular growth capability.

Finally, concluding remarks and directions for future research are given in Chapter 6.

1. INTRODUCTION - 10 -

#### REFERENCES 1

[1] F. A. Tobagi, "Fast packet switch architecture for broadband Integrated Services Digital Networks", Proceedings of the IEEE, Vol.78, No.1, pp.133-167, Jan. 1990.

- [2] H. Ohnishi, T. Takahashi, K. Kuroda, T. Okada, "Switching technologies for B-ISDN", NTT Review, Vol.3, No.3, pp.59-70, May 1991.

- [3] CCITT, "Thirteen B-ISDN recommendations approved by SG XVIII at Matsuyama", Temporary Documents 1 and 9 (XVIII), Nov. 1990.

- [4] J. Y. Hui, E. Arthurs, "A broadband packet switch for integrated transport", IEEE J. Select.

Areas Commun., Vol.5, No.8, pp.1264-1273, Oct. 1987.

- [5] M. J. Karol, M. G. Hluchyj, S. P. Morgan, "Input versus output queueing on a space-division packet switch", IEEE Trans. on Comm., Vol.35, No.12, pp.1347-1356, Dec. 1987.

- [6] B. Bingham, H. Bussey, "Reservation-based contention resolution mechanism for Batcher-Banyan packet switches", Electronics Letters, 23rd, Vol.24, No.13, pp.772-773, June 1988.

- [7] T. T. Lee, "Nonblocking copy networks for multicast packet switching", IEEE J. Select.

Areas Commun., Vol.6, No.9, pp.1455-1467, Dec. 1988.

- [8] K. Y. Eng. M. G. Hluchyj, Y. S. Yeh, "Multicast and broadcast services in a knockout packet switch", Proc. IEEE Infocom'88, pp.29-34, New Orleans, LA., March 1988.

- [9] H. Kuwahara, et al., "A shared buffer memory switch for an ATM exchange", Proc. ICC'89, pp.118-122, Boston, June 1989.

# **CHAPTER 2**

# MULTICASTING SCHEDULING

| <b>つ</b> 1 | TNI       | מיד | $\mathbf{OL}$ | 1 1~ | TI. | $\cap X^{\dagger}$ |

|------------|-----------|-----|---------------|------|-----|--------------------|

| ۷. ا       | $\Pi_{A}$ | I K | $\sigma$      | UCʻ  | 11' | UN                 |

- 2.2. SCHEDULING AND ITS IMPLEMENTATION CONSIDERATIONS

- 2.2.1. One-shot Scheduling

- 2.2.2. SS Call Splitting

- 2.2.3. WS Call Splitting

- 2.2.4. Revision Scheduling A Novel Scheme

- 2.3. PERFORMANCE COMPARISON BY SIMULATION

- 2.4. CONCLUSION

APPENDIX 2: Simulation Model

REFERENCES 2

#### 2.1. INTRODUCTION

We assume that the switch fabric runs at the same speed as the input and output lines, only one packet can be forwarded to any given output line during a time slot, and other packets addressed to the same output must queue at the input ports. Blocking is present in unicast switches and is compounded in multicast switches, i.e. two or more input ports seek to send copies to the same output port in the same time slot. Unlike the unicast switch with saturated throughput 58.6% due to HOL blocking, the multicast switch does not have such a limit, in fact, the throughput of the multicast switch is the function of copy distribution of the packet as well as the traffic arrival rate. Not only that, under the assumption of input port queueing, we may consider the switch performance for several different service disciplines in terms of scheduling the transmission of the copies of the packet in case of output contention at the input ports.

A number of service disciplines were proposed and summarized in [1]. Of these the most interesting are the following three. One-shot scheduling requires all the copies of the same packet to be transmitted in the same time slot. Strict-sense (SS) call splitting and wide-sense (WS) call splitting allow the transmission of the packet to be split over several time slots. SS specifies that each packet can send at most one copy to the destination per time slot; WS does not carry this restriction. In this chapter, a novel scheme, revision scheduling, is proposed to mitigate the HOL blocking effect by sequentially combining the one-shot scheduling and WS call splitting discipline, which may give an indication of the best performance under the assumption of input port queueing.

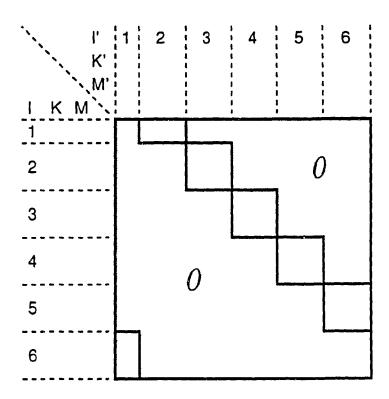

For simplicity, we may use a matrix to describe the call scheduling problem. Suppose there is a matrix where each row and each column correspond to the input line and output line of the switch, respectively. The elements 1's stand for the copies of the HOL packets. In the transmission request matrix,  $I_{ij} = 1$  denotes the HOL packet at input *i* seeks to send a copy to output *j*. In the case of multicasting switching, each row may contain two or more 1's rather than only one 1 as in the unicast case. Since an output port may take only one packet in a time slot, each column has at most one 1 being selected. Of course, one of them must be selected if there is at least one

in the column. Obviously, there are a number of choices to fulfill this requirement. The criteria for the four considered disciplines are set up with respect to the rows of the matrix:

- 1) One-shot scheduling: the 1's at the same row must be all selected or all ignored simultaneously.

- 2) SS call splitting: at most one 1-element can be selected from each row.

- 3) WS call splitting: no restriction on rows.

- 4) Revision scheduling: a sequential combination of a one-shot scheduling and a WS call splitting discipline.

Following are some examples for these disciplines,

1 1 0 0 1 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 0

Transmission request matrix (1: copy request)

| φ φ 0 0 φ<br>0 1 0 0 0<br>0 0 0 φ 0<br>0 1 1 0 0<br>0 0 1 1 0<br>One – shot<br>(1)        | φ 1 0 0 1<br>0 φ 0 0 0<br>0 0 0 φ 0<br>0 1 φ 0 0<br>0 0 1 1 0<br>SS call splitting (2) |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| φ 1 0 0 φ<br>0 φ 0 0 0<br>0 0 0 φ 0<br>0 1 φ 0 0<br>0 0 1 1 0<br>WS call splitting<br>(3) | φ φ 0 0 φ 0 1 0 0 0 0 0 0 φ 0 0 1 1 0 0 0 0 φ 1 0 Revision scheduling (4)              |

Call scheduling disciplines

(\$\phi\$: accepted request 1: rejected request)

These scheduling schemes have their own advantages and disadvantages, based on delaythroughput performance and implementation consideration. This chapter introduces schematic structures for each category of scheduling. The complexity of several implementations is addressed. The simulations were carried out for the comparison of performance.

The remainder of the chapter is organized as follows. Section 2.2 describes four call scheduling schemes and their implementation considerations. A performance comparison by simulation for these four schemes is presented in Section 2.3. Section 2.4 contains the conclusion of the chapter.

## 2.2. SCHEDULING AND ITS IMPLEMENTATION CONSIDERATIONS

Previous studies showed that the delay-throughput performance of the unicast switch does not depend on the way of selecting winning packet from the conflicting packets. However, in the case of multicast switching, our results show that a different call scheduling discipline does provide different performance. In particular, we will show that simple revision scheduling achieves the best performance among the all concerned. Here, we are going to define these scheduling disciplines.

### 2.2.1. One-shot Scheduling

In the case of the one-shot scheduling, all copies of the same packet must be switched in the same slot. If at least one copy loses the contention for an output port, the whole packet must wait in a queue and try again in the next slot. This strategy favors the packet with less copies. The packet with more copies will be blocked more often than that with less copies, because of simultaneous output contention.

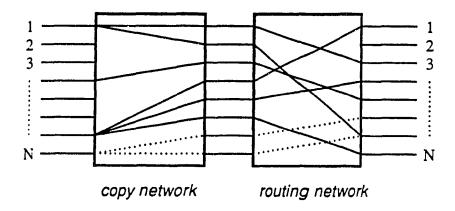

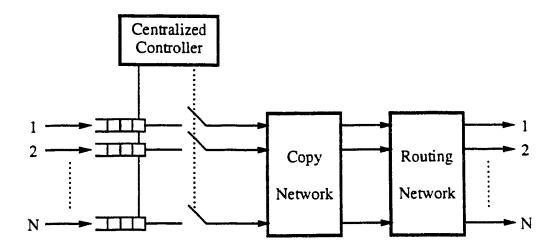

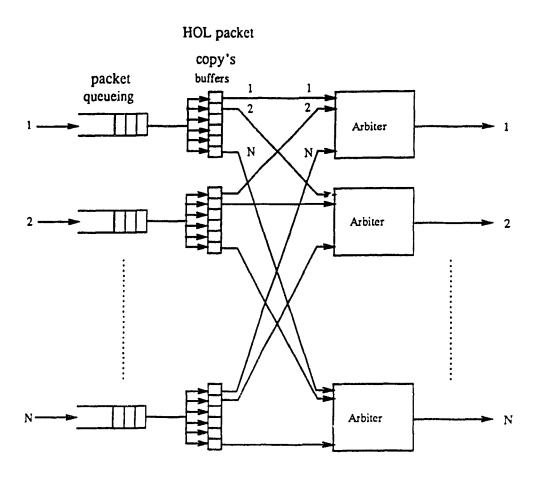

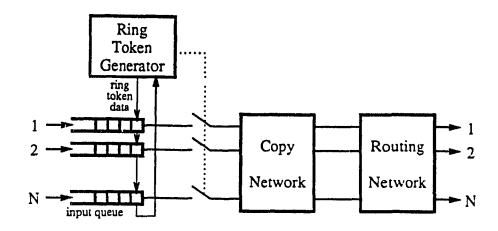

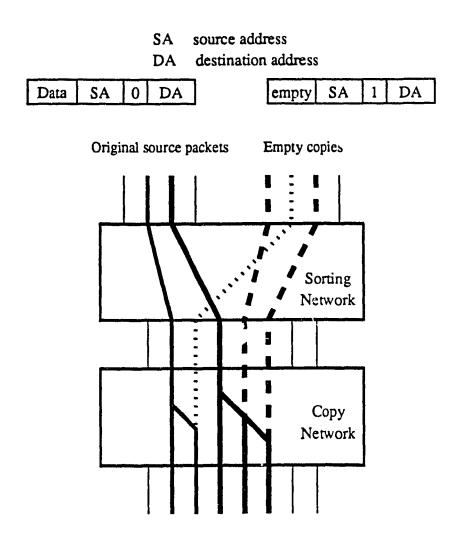

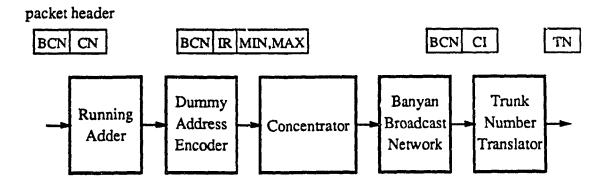

The one-shot discipline can be implemented by a serial combination of an input buffer memory, a copy network [2] and a routing network, as depicted in Figure 2.1. A centralized controller is used to regulate the input traffic. Copy requests of the multicast packet will be considered before these packets enter the copy network. Any selected packet should pass through the switch within a single slot; accordingly, no buffer is needed between the copy network and routing network. Two implementation examples of this scheme are the cyclic-priority input access scheme and the neural network based scheme.

Figure 2.1. Concept of one-shot scheduling

The cyclic-priority input access scheme is a derivative of the token passing ring, and is a simple input access scheme to handle the contention resolution problem. Instead of token ring passing, the cyclic-priority input access scheme can be implemented by a simple combinational logic circuit which will be described in Section 3.2.

The neural network based contention resolution mechanism allows us to select, from all HOL packets in input queues, a particular set of packets as inputs of copy network, which ensures contention-free access to output ports and maximizes packet throughput. The detailed discussion will be seen in Section 3.3.2.

### 2.2.2. SS Call Splitting

A contrasting discipline under consideration is SS call splitting scheduling. In the case of the one-shot discipline, even if only one copy loses the contention, the whole packet (all its copies) is blocked. Obviously, this degrades the utilization of the output lines and suggests that we can transmit copies independently. But, each input can send at most one copy into the switch fabric per time slot, assuming that there is only one line connecting each input port and the switch fabric. The packet with residual copies continues to contend for output ports in the following slots until all of its copies have been transmitted. Obviously, at least C slots are needed to

Figure 2.2. A switch fabric for SS call splitting scheduling

transmit a packet if it has C copies.

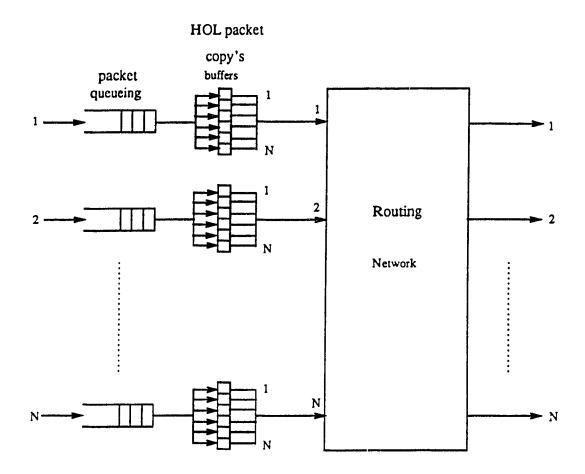

As mentioned in Chapter 1, a multicast packet only carries a multicast channel number (MCN) to indicate the subset of destinations, rather than carry all individual destinations of the copies resulting in too much overhead on the multicast packet. A simple table look-up is usually used to decode the addresses in multicasting operation. Therefore, it is difficult to relabel the multicast packet with residual number of copies in order to prevent both the reduplication and ignorance of the destinations. One way of implementing this is that the copies of a packet are served in a prescribed order [1] so that the switch only sees one copy of a packet at a time and operates as in unicast fashion. The another implementation is to reproduce the HOL packet

before the splitting transmission so that the switch is able to see all the copies of the HOL packet simultaneously. This scheme is functionally shown in Figure 2.2. The multicasting operation is implemented in each input queue by shifting the HOL packet into a set of parallel buffers corresponding to its multicast destinations, as depicted in Figure 2.3. MCN is taken as the primary key of the multicasting table. Each cell of the table consists of N bits to indicate the corresponding destinations by 1's. The destination addresses of the copies are automatically added to the messages in the individual buffers. A centralized controller to select contention-free copies will be discussed in Section 3.2. No special copy network is needed. When all the buffers are cleared, the next packet will be shifted in.

Figure 2.3. Multicasting operation

Again, an optimal selection policy is sought. We will use neural-network-based input access method to deal with this problem in Section 3.3.4.

Figure 2.4. Concept of WS call splitting scheduling

### 2.2.3. WS Call Splitting

SS call splitting results in throughput degradation in light traffic case. Although there may be a case that only one active input line and all the output lines are free for that packet, only one copy can be accepted at a time, so that the utility of the output line is not sufficient. Thus, the third discipline we are interested in is WS call splitting. We allow more than one copy from the same packet to gain access to output ports simultaneously as long as those output ports are free.

Full use is made of the output lines since an output line is used as long as there is at least one copy in the HOLs destined for it.

Figure 2.5. Cross-bar structure with WS call splitting scheduling

The concept of this discipline is illustrated in Figure 2.4. N arbiters are used in place of a routing network. Each such arbiter sees all copies that are proceeding to the corresponding output and selects one of them randomly (or according to some rule). This scheme can be viewed as a derivative of the crossbar switch with input buffering and centralized output arbiters, as depicted in Figure 2.5. N copy's buffers of the HOL packet at an input port are distributed over a row of N

crosspoints. When all the buffers in a row are cleared, a new packet is multicast along the bus connecting to N copy's buffers. The transmission of the copies of the packet will be dispersed over several time slots.

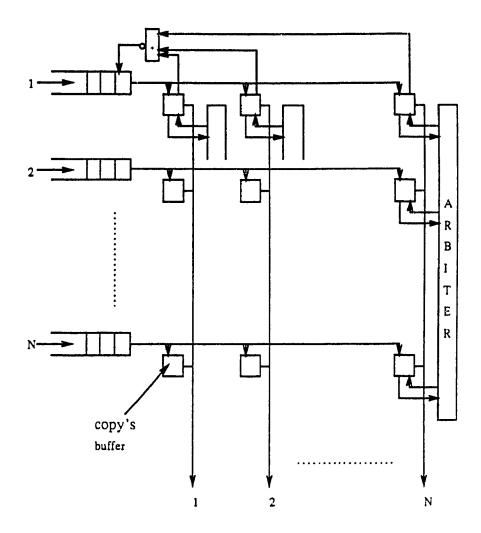

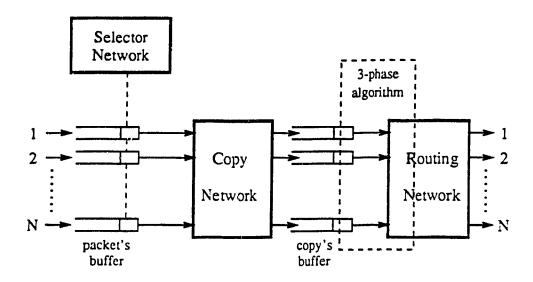

Figure 2.6. Lee's multicast switch

Another implementation was suggested by Lee [3] (see Figure 2.6), where the HOL packets are duplicated, and blocked copies are kept in buffers between copy network and routing network to prevent message loss. The overflows of the copy network are prevented by using selector network and the output contention is resolved by employing a three-phase algorithm [4]. In a sense, this is a true call splitting scheduling, since the copies queueing at the buffers have lost their association with the input packet. Hence, the FIFO principle for incoming packets has been lost as well.

## 2.2.4. Revision Scheduling — A Novel Scheme

As we know, output queueing performs better than input queueing although it may require more complicated designing. It is HOL blocking that causes throughput degradations in input queueing schemes. To mitigate this phenomenon, we try to get as many packets through as

possible so that the packets behind the HOL packets can join the contention in the next slot. For example, in the sense of WS call splitting, the following two choices illustrated below are equivalent. But, (b) is potentially better than (a) because three new packets in (b) will participate in the contention in the following slot, while there will be only one new packet in (a).

| ф 0 1 0 ф        | φοφοφ  |

|------------------|--------|

| 0 1 0 0 0        | ο φοοο |

| 0 <b>0</b> 0 0 1 | 01001  |

| 0000             | 00000  |

| 01000            | 01100  |

| (a)              | (b)    |

The novel service discipline which operates in this fashion is called revision scheduling, the purpose of which is to maximize the number of packets getting through and the number of output lines being busy simultaneously. We first select packets according to one-shot discipline until all remaining packets interfere with the selected packets. Then, we lift the restriction of the one-shot rule, to allow the individual copies of the remaining packets to contend for the remaining output channels. The packets with residual number of copies, called residual packets, would contend for outputs with fresh packets altogether in the next time slot. Obviously, in a specific time slot, revision scheduling is the same as WS call splitting in the sense of utilization of the output lines. Simulation will show us that the overall delay-throughput performance of revision scheduling is better than WS call splitting scheme.

With the cyclic-priority input access scheme, the revision scheduling can be implemented by circulating the token two times around a ring connecting the N input ports. At the token's first visit to the input port, the reservation must be made for the whole packet according to the one-shot rule. At its second visit to the input port, the remaining HOL packets will make reservations for their copies following the WS call splitting discipline. There are two main difficulties in the implementation. One is that some additional control functions are required for identifying the subset destinations of the remaining packets, which might cause complicated control functions. The other is that the speed limit prevents tokens from visiting all input port two times when the switch size increases. To overcome these difficulties, we can use a cross-bar structure and coordinate the arbiters by using combinational logic circuits.

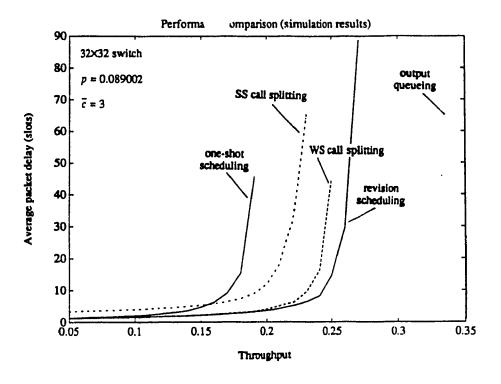

## 2.3. PERFORMANCE COMPARISON BY SIMULATION

We have discussed four categories of call scheduling and their implementation considerations. Simulations of the four disciplines were carried out. Once the contention happens, a random selection policy is used to make a choice. The packet delay and throughput were determined as the basic performance measurements of the scheduling schemes. It is assumed that the arrival of packets to the input is described by a Bernoulli process and each packet generates copies according to independent Bernoulli trial on each output port, with success probability p. This particular distribution was chosen because it provides a way of generating multiple copies which is easy to implement in a simulation. In any case, our focus is upon the comparison of a number of service disciplines. There is no reason to believe that this distribution and random selection policy would lead to contradictory results with alternative distributions and policies. The simulation results for a 32×32 switch are shown in Figure 2.7, where  $\bar{c}$  is  $\pm$ - erage number of copies generated by a packet. We choose the 32×32 switch here because it is supposed to be a module of the configuration of the large size switch. The conclusion made from the plots are also true for the switch with various sizes. Simulations were run over  $10^6$  slots for each value of  $\lambda$  and p considered. The mean values are within 1% of the true mean with 95% confidence. A brief introduction of the simulation program can be seen in Appendix 2.

As a reference, we plotted results for a output queueing scheme which is required when the  $N \times N$  switch fabric runs N times as fast as the inputs and outputs or has N parallel paths. All arrival packets and their copies will be transferred to a set of queues corresponding to their destinations at the slot immediately after their arrival. There is no queueing required at input port, since there is no more than one packet arriving per slot per input link.

The one-shot discipline bears the most stringent restrictions on scheduling so that the saturated throughput is the lowest among the four. However, it is simple and easy to implement.

The SS call splitting discipline relaxes the one-shot restriction in the heavy traffic case. But, it seems rigid in the light traffic case and results in degradation in the performance. Even if there is only one HOL packet, C time slots are still needed if the packet has C desired destinations.

Figure 2.7. Comparison of the delay-throughput performance

The SS call splitting discipline does not require the copy network, however, it does need distributed duplicating operations.

The WS call splitting pursues full use of the output lines, hence achieves higher throughput. It has the same complexity as the crossbar switch does. It is HOL blocking that prevents it from yielding the throughput which the output queueing scheme can provide.

Revision scheduling seeks to mitigate the HOL blocking by trying to get as many packets through as possible while insuring full use of the output lines. This discipline would give an indication of the best performance under the assumption of input port queueing. The switch structure to implement WS call splitting discipline is applicable to the revision scheduling, however, a complicated control logic is predicted.

# 2.4. CONCLUSION

We have classified and discussed four call scheduling disciplines and their implementation considerations. Revision scheduling is preferred as far as the delay-throughput performance is concerned. Taking into account the complexity of implementation as well as the performance. none of the four categories seems to have distinctive superiority over the others. There is a trade-off between the performance and switch structure complexity. Future research should be focused on the switch structures to implement these disciplines efficiently, and to adapt to practical networks.

# **APPENDIX 2: Simulation Model**

Simulation of the multicast packet switch with various service disciplines and various selection policies for input access scheme under different traffic arrival models and copy distribution models, is implemented through a software package SIMU which was written in C and running at Sun Sparc WorkStation. SIMU allows us to specify particular switching strategy very easily. All the options we can choose are listed in Table A2.1. The block diagram of SIMU is shown in Figure A2.1.

Table A2.1. Options of SIMU

| Description             | Option                   |

|-------------------------|--------------------------|

|                         | one-shot scheduling      |

| scheduling discipline   | SS call splitting        |

| schedding discipline    | WS call splitting        |

|                         | revision scheduling      |

|                         | cyclic priority          |

| selection policy        | random selection         |

|                         | neural network selection |

| manket arrival model    | binomial                 |

| packet arrival model    | Poisson                  |

| consideration model     | binomial                 |

| copy distribution model | deterministic            |

|                         | normal                   |

| test mode               | uniform                  |

|                         | fresh                    |

In the simulation, time is segmented into fixed size slots, and a slot is the minimum duration of any event. Packet arrivals at each input port are generated according to a binomial or a Poisson distribution with average rate  $\lambda$ . Then, for each new HOL packet, copies are distributed to output ports as the result of Bernoulli trials with parameter p for each output port, or with a deterministic distribution such that a packet generates and evenly distributes NC (a constant number of) copies to the destinations. The HOL packets contend for output based on one of the four scheduling disciplines, incorporating one of the three selection policies. The blocked packets in current slot are held in buffers for future contention in following slots. In order to keep track of all events during the simulation and to facilitate the manipulation of data, a well defined data structure is adopted. The simulation was made over a specified number of slots for each

Figure A2.1. A flowchart of the program SIMU

specified configuration. The simulation yields a set of performance measures: system load, throughput, delay and confidence interval corresponding to a set of defined system parameters.

# **REFERENCES 2**

- [1] J. Y. Hui, T. Renner, "Queueing strategies for multicast packet switching", Proc. of Globecom'90, pp.1431-1437, San Diego, CA, Dec. 1990.

- [2] T. T. Lee, "Nonblocking copy networks for multicast packet switching", IEEE J. Select.

Areas Commun., Vol.6, No.9, pp.1455-1467, Dec. 1988.

- [3] T. T. Lee, R. Boorstyn, E. Arthurs, "The architecture of a multicast broadband packet switch", Proc. IEEE Infocom'88, pp.1-8, New Orleans, LA, March 1988.

- [4] J. Y. Hui, E. Arthurs, "A broadband packet switch for integrated transport", IEEE J. Select.

Areas Commun., Vol.5, No.8, pp.1264-1273, Oct. 1987.

# **CHAPTER 3**

# **CONTENTION RESOLUTION ALGORITHMS**

- 3.1. REVIEW OF THREE ALGORITHMS

- 3.2. CYCLIC PRIORITY ACCESS SCHEME WITH ITS

COMBINATIONAL LOGIC IMPLEMENTATION

- 3.3. NEURAL NETWORK BASED ALGORITHM

- 3.3.1. Preliminary of Hopfield Model of Neural Networks

- 3.3.2. A Model for One-Shot Scheduling

- 3.3.3. An Extension Model Windowed service

- 3.3.4. A Model for SS Call Splitting

- 3.4. CONCLUSION

**REFERENCES 3**

We have investigated the relative performance of the multicast scheduling disciplines which are designed to regulate traffic and prevent output contention for input port queueing switches. Either the centralized controller or the centralized arbiter is equipped for the purpose. In this chapter, we will discuss contention resolution algorithms by which these disciplines are implemented. The contention resolution algorithm tells us how to select contention-free packets under a specific scheduling discipline. We first introduce some interesting schemes; thereafter, we will propose two novel algorithms, in Section 3.2 and 3.3 respectively.

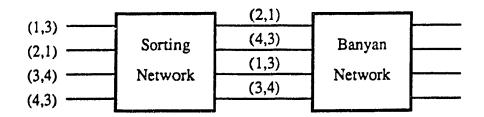

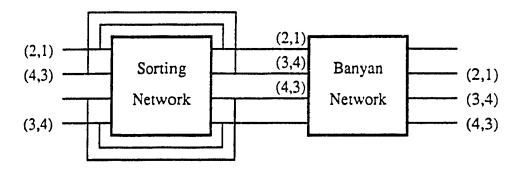

# 3.1. REVIEW OF THREE ALGORITHMS

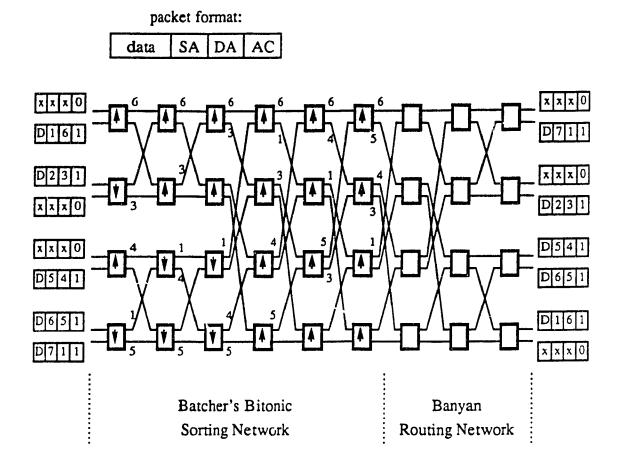

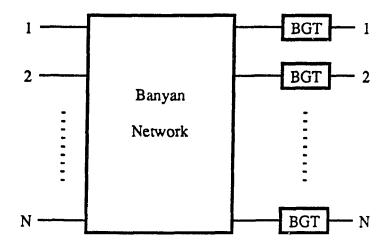

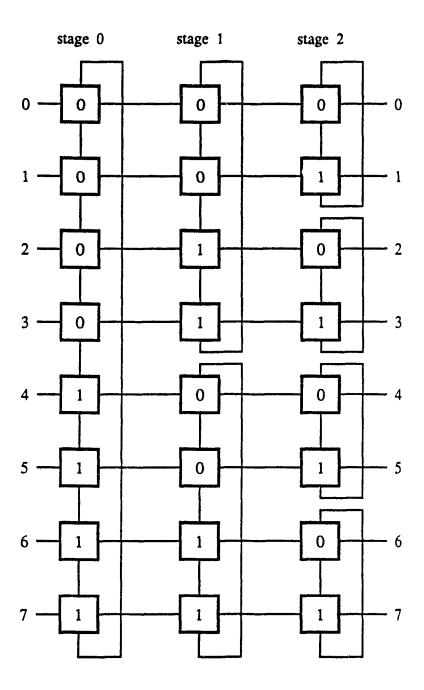

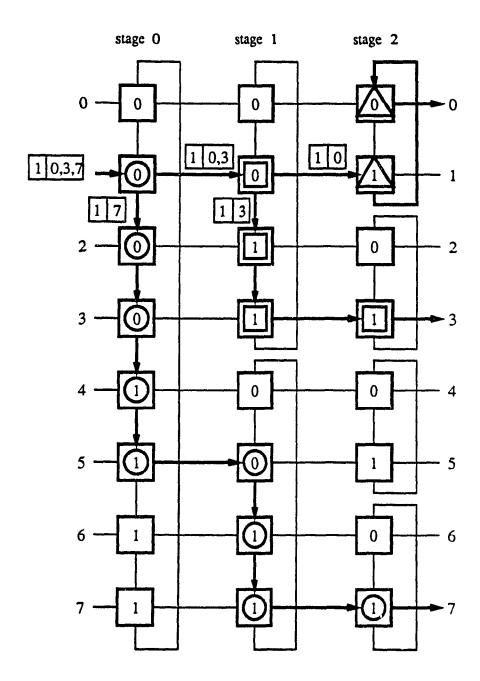

A banyan network is widely used as the routing network of a switch. The banyan network itself is a blocking network. However, the banyan network becomes internally nonblocking if the destinations of input requests are sorted in ascending or descending order. The Batcher's bitonic sorting network can be used to achieve this requirement. Therefore, a combination of Batcher's bitonic sorting network and a banyan routing network is a well known self-routing nonblocking packet switch. The nonblocking property holds if and only if the destinations of all input packets are distinct. However, blocking will occur if there is output contention, i.e. the requests for output ports are not distinct. A good collection of discussions of this issue can be found in [1].

Several contention resolution schemes for point-to-point transmission were proposed [2][3][4] for resolving output conflicts of a Batcher-banyan packet switch, which guarantee that at most one packet addressed to a given output enters the switch at any time.

Huang and Knauer [2] proposed a re-entry network as shown in Figure 3.1. At the output of the sorting network, a packet loses the contention if the packet on the preceding line in the sorted order has the same destination address. The packets which lose the contention are then concentrated by a concentration network, and are fed back to the input of the Batcher network for reentry. The packets which win the contention are not concentrated due to purged packets. Consequently, another concentration network is required in front of the banyan network for skewing all packets to the top lines, filling all holes left behind by purged packets. The drawback of this approach is that the two extra expanded concentration networks require more chip sets and

Figure 3.1. A re-entry network for contention resolution

subsystem designs. Furthermore, FIFO operation will be lost.

Hui and Arthurs [3] suggested a 3-phase algorithm to solve contention problem as shown in Figure 3.2. In phase one, each input port sends a request for a port destination through a Batcher sorting network, which sorts the request destinations in ascending order so that we may easily purge all but one request for the same destination, Figure 3.2a. The winning request acknowledges its originating port from the output of the Batcher network, with the acknowledgment routed through a Batcher-banyan switch according to its input port source address in phase two, Figure 3.2b. In phase three, the acknowledged input port then sends the full packet through the same Batcher-banyan self-routing switch without any contention, Figure 3.2c. Unacknowledged ports buffer the blocked packet for reentry in the next cycle. However, this algorithm requires

Phase 1: Send and resolve request

- \* Send source-destination pair through sorting network

- \* Sort destination in non-decreasing order

- \* Purge adjacent requests with same destination

# (a) Phase one

Phase 2: Acknowledge winning port

- \* Send ACK with destination to port winning contention

- \* Route ACK through Batcher-Banyan network

# (b) Phase two

Ph se 3: Send packet

- \* A knowledged port send packet through Batcher-Banyan network

- (c) Phase three

Figure 3.2. Three-phase algorithm

Figure 3.3. Ring reservation-based contention resolution

stringent timing and synchronization.

Bingham and Bussey [4] proposed a reservation-based contention resolution method as shown in Figure 3.3. Unlike the previous two feed back algorithms, the reservation-based contention resolution method is a ring token passing scheme. At the beginning of a time slot, a cleared token is issued by a token generator. The token has an N-bit field to indicate the availability of N output ports. The token is circulated around a ring connecting the input ports. When the token comes by, the packet at the head of each input buffer will make the reservation. If the intended output is successfully reserved, the packet is transmitted at the next time slot. The reservation cycle and transmission cycle can be overlapped to minimize the overhead. But, it has a growth problem because the duration of the reservation cycle is proportional to the number of input ports. Generally speaking, this is an intrinsic problem of the centralized control schemes.

Certainly, all three resolution algorithms remain valid for Batcher-banyan based multicast switch in a certain sense. The re-entry policy and the three-phase algorithm have the advantage

of distributed operation, however, both need an extra buffer between the copy network and routing network in addition to input port buffer in the front of copy network [2][5]. Because of that, the FIFO principle for incoming packets has been lost. Copies may be out of sequence upon reaching the destination.

It is an apply the ring-reservation algorithm to multicast switches. Although simple, the ring reservation method has the drawback of built-in unfairness since the requests at higher numbered ports are deferred more often. To eliminate this drawback, we suggest a cyclic-priority input access scheme, which is the topic of next section.

#### 3.2. CYCLIC PRIORITY ACCESS SCHEME WITH ITS

#### COMBINATIONAL LOGIC IMPLEMENTATION

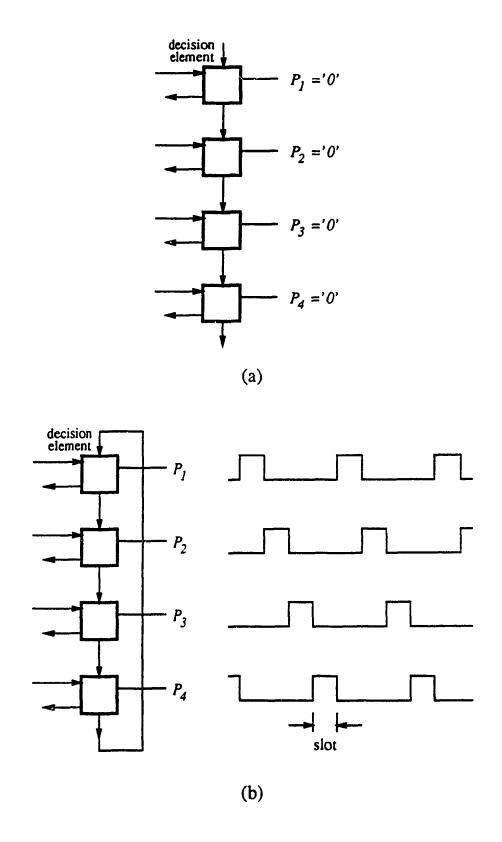

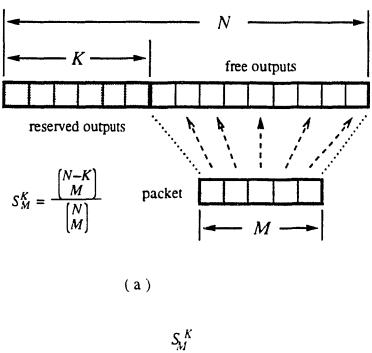

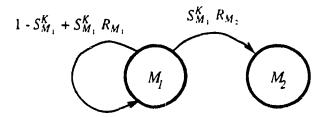

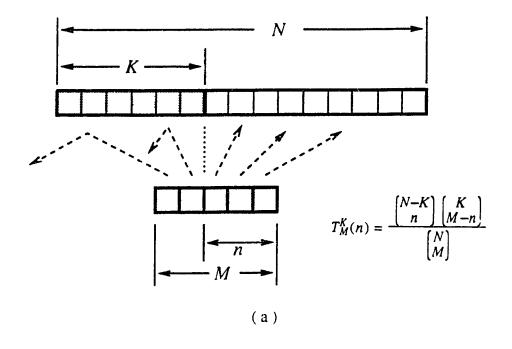

The cyclic priority input access scheme is a derivative of the ring-reservation method. We assign N levels of priority to the N input ports at the beginning of each time slot and rotate the assignment cyclically slot-by-slot. An input port with priority level i in the current slot will have priority level i-1 in the following slot. Input port with priority level 1 (the highest priority) in current slot will have priority level N (the lowest priority) in the following slot, and so on. The HOL packets make reservations according to their priority order. But, with a ring token passing scheme we still have a problem that the speed limit prevents tokens from visiting all input ports when the switch size increases.

In the last chapter, we formulated contention resolution problem as a decision problem in which it is required to obtain a decision matrix O corresponding to a specific scheduling discipline for a given transmission request matrix I. A combinational logic circuit is devised to implement the decision, by incorporating a cyclic priority access policy. This circuit has the advantages of being simple and fair. Without need of stringent timing and synchronization, it is expected to operate fast.

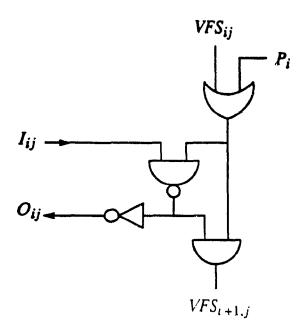

A basic element of a decision board is shown in Figure 3.4 where four gates (one AND, one NAND, one OR and one INV) are connected to make the decision and propagate the vertical for-

Figure 3.4. A basic decision element

Table 3.1. Truth table of a basic element

| $P_i$ | VFS <sub>ij</sub> | 1,, | 0,, | $VFS_{i+1,j}$ |

|-------|-------------------|-----|-----|---------------|

| 0     | 0                 | X   | 0   | 0             |

| 0     | 1                 | 0   | 0   | 1             |

| 0     | 1                 | 1   | 1   | 0             |

| 1     | X                 | 0   | 0   | 1             |

| 1     | X                 | 1   | 1   | 0             |

bidden signal (VFS).  $I_{ij}$  corresponds to the element of the transmission request matrix;  $I_{ij} = 1$  indicates a message in input i seeking to be sent to output j.  $O_{ij}$  corresponds to the element of the decision matrix;  $O_{ij} = 1$  indicates the request from input i to output j being approved. Since in each column, only one request can be accepted, a  $VFS_{ij}$  is needed to cooperate between adjacent decision elements.  $VFS_{ij} = 1$  signals that output j has not yet been selected, input i is allowed to make a reservation if needed.  $VFS_{ij} = 0$  signals that the output j has been used by either input i-1 or previous inputs.  $P_i$  is a priority control signal which will be described later. The truth table for the basic element is shown in Table 3.1.

Figure 3.5. Cyclic priority assignment

Figure 3.6. A 4×4 decision board for WS call splitting discipline

A column of such decision elements is used by an output to select the packet (Figure 3.5a). Once an input has been selected, all of the following requests are eliminated. For fairness, we connect  $VFS_{N+1,j}$  to  $VFS_{1,j}$  to form a ring, and choose input i as the first priority port by setting  $P_i$  = 1, and  $P_i$  = 0 for all  $i \neq i$ , in a slot (Figure 3.5b). The priority level descends along VFS flow. Then, we cyclically change the first priority input port from slot to slot. A 4×4 decision board is

shown in Figure 3.6, which can be used as arbiters in Figure 2.5 for the WS call splitting discipline. It is worthwhile to indicate that this approach can also be applied to unicast case in place of ring-reservation algorithm or three-phase algorithm.

Figure 3.7. A basic element with HFS

| $P_i$ | VFS <sub>ij</sub> | HFS <sub>ij</sub> | $I_{ij}$ | Oij | $VFS_{i+1,j}$ | $HFS_{i,j+1}$     |

|-------|-------------------|-------------------|----------|-----|---------------|-------------------|

| 0     | 0                 | X                 | X        | 0   | 0             | HFS <sub>ij</sub> |

| 0     | X                 | 0                 | X        | 0   | $VFS_{ij}$    | 0                 |

| 0     | 1                 | 1                 | 0        | 0   | 1             | 1                 |

| 0     | 1                 | 1                 | 1        | 1   | 0             | 0                 |

| 1     | X                 | 0                 | 0        | 0   | 1             | 0                 |

| 1     | X                 | 1                 | 0        | 0   | 1             | 1                 |

| 1     | X                 | 0                 | 1        | 0   | 1             | 0                 |

| 1     | X                 | 1                 | 1        | 1   | 0             | 0                 |

To fulfill the SS call splitting discipline, we should introduce a horizontal forbidden signal (HFS), since only one can be selected from each row. One more AND is added to basic element as illustrated in Figure 3.7. The corresponding truth table is shown in Table 3.2. A 4×4 decision

Figure 3.8. A 4×4 decision board for SS call splitting discipline

board for SS call splitting discipline is depicted in Figure 3.8.

The one-shot scheduling can be interpreted as that HFS must come into effect on a row both forward and backward if any request in this row is eliminated by VFS. A pair of ANDs are used

Figure 3.9. A basic element with fHFS and bHFS

| $P_i$ | $\overline{VFS_{ij}}$ | $fHFS_{ij}$ | bHFS <sub>ij</sub> | $I_{ij}$ | Oij | $VFS_{i+1,j}$ | $fHFS_{i,j+1}$ | $bHFS_{i,j-1}$ |

|-------|-----------------------|-------------|--------------------|----------|-----|---------------|----------------|----------------|

| ()    | 0                     | X           | X                  | X        | 0   | 0             | 0              | 0              |

| 0     | X                     | 0           | X                  | X        | 0   | $VFS_{ij}$    | 0              | $bHFS_{ij}$    |

| 0     | X                     | X           | 0                  | X        | 0   | $VFS_{ij}$    | $fHFS_{ij}$    | 0              |

| 0     | 1                     | 1           | 1                  | 0        | 0   | 1             | 1 ′            | 1              |

| ()    | 1                     | 1           | 1                  | 1        | 1   | 0             | 1              | 1              |

| 1     | X                     | X           | X                  | 0        | 0   | 1             | 1              | 1              |

| 1     | X                     | X           | X                  | 1        | 1   | 0             | 1              | 1              |

Table 3.3. Truth table for the basic element in Figure 3.9

to propagate fHFS and bHFS respectively as seen in Figure 3.9. The truth table is as in Table 3.3. A fully connected  $4\times4$  decision board for one-shot scheduling is shown in Figure 3.10, where  $P_{i}$ 's are priority control signals, and the cyclic-priority scheme is easy to implemented by this

Figure 3.10. A 4×4 decision board for one-shot scheduling

structure.

To implement revision scheduling, we need a simple way to switch the operations between one-shot and call splitting. An ATM slot is divided into two phases. A minor modification as shown in Figure 3.11 enables the circuit to connect or disconnect the HFSs by setting R = 0 or R = 1, alternately in two phases of each time slot.

Figure 3.11. A basic element for revision scheduling

These circuits are stable because they are open without any feedback. The decision time is defined as the propagation time of the signal through a proper route. Since the decision period and transmission cycle can be overlapped, the maximum decision time can be a slot time. Assume that the speed of each input line is 150Mbps, each packet contains 53 bytes or 424 bits. The slot time is 2826ns. For simplicity, we assume that various logic gates have the same

Figure 3.12. An example of the longest signal routes

propagation delay. Figure 3.12 shows us one example of the longest signal routes. The number of gates needed for each decision board and the number of gates along the longest signal route are listed in Table 3.4, where N is the switch size.

Table 3.4. Comparison in terms of the number of gates

| Scheduling          | Number of gates in board | Number of gates in the longest route |

|---------------------|--------------------------|--------------------------------------|

| WS call splitting   | 4N <sup>2</sup>          | 3 <i>N</i>                           |

| SS call splitting   | 5№ <sup>2</sup>          | 4 <i>N</i>                           |

| One-shot scheduling | 8N <sup>2</sup>          | N <sup>2</sup> +3N                   |

| Revision scheduling | $10N^{2}$                | N <sup>2</sup> +8N                   |

With current high speed digital IC technologies, sub-100 ps gate-delay can be achieved [6] with 0.3  $\mu$ m CMOS, 0.7  $\mu$ m GaAs DCFL, or 0.5  $\mu$ m emitter Si ECL. The Table 3.5 shows realizable switch sizes N assuming average gate-delay  $t_{gd} = 150$ ps, 500ps and 2ns respectively.

Table 3.5. Realizable switch size

| Schoduling          | Realizable switch size   |                            |                 |  |

|---------------------|--------------------------|----------------------------|-----------------|--|

| Scheduling          | $t_{gd} = 150 \text{ps}$ | $t_{gd} = 500 \mathrm{ps}$ | $t_{gd} = 2$ ns |  |

| WS call splitting   | 4096                     | 1024                       | 256             |  |

| SS call splitting   | 4096                     | 1024                       | 256             |  |

| One-shot scheduling | 128                      | 64                         | 32              |  |

| Revision scheduling | 128                      | 64                         | 32              |  |

We have demonstrated an implementation of cyclic priority selection scheme. We point out that the random selection policy is a mathematical artifice which is used in performance analysis. In real systems, one has to prescribe some kind of order or define some kind of rule, instead of relying on the random action of electronic components. However, through a large number of simulations, we found that the delay-throughput performance for both cyclic priority selection and random selection policies does not show much differences, except that cyclic priority policy attains a slightly smaller confidence interval than the random selection policy.

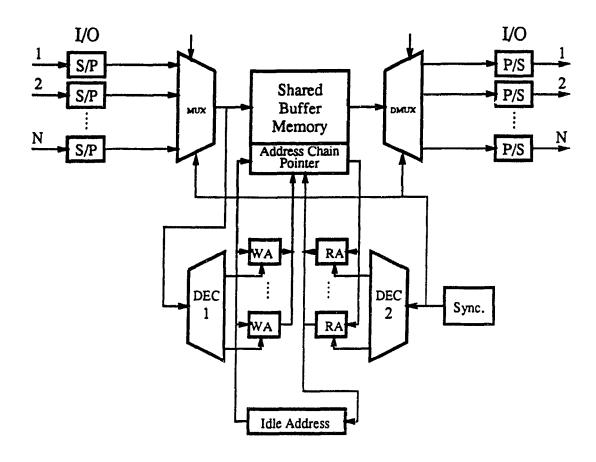

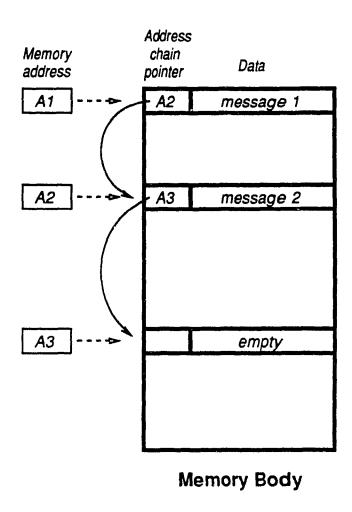

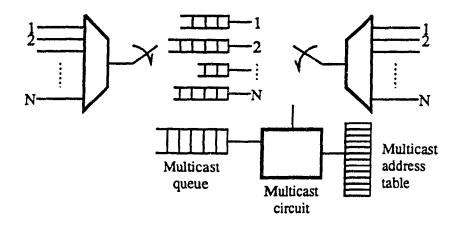

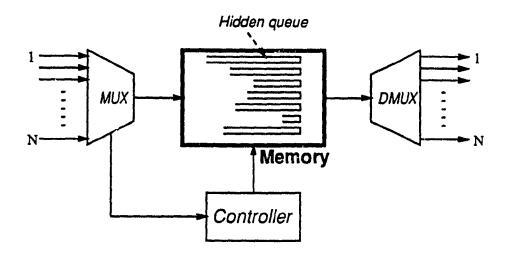

## 3.3. NEURAL NETWORK BASED ALGORITHM