SCI-net: A Very Low Cost CSMA/CD Network for Linking Small Microcomputer Systems

Rene Stanley Hollan

A Thesis

in

The Faculty

of

Engineering .

anď.

Computer Science

Presented in Partial Fulfillment of the Requirements for the degree of Master of Computer Science at Concordia University

Montreal, Quebec, Canada

March 1984

© Rene Stanley Hollan, 1984

#### **ABSTRACT**

SCI-net: A Very Low Cost CSMA/CD Network

for Linking Small Microcomputer Systems

'Rene Stanley Hollan

This is a description of the design and implementation of a carrier sense, multiple access network with collision detection. Included are the basic design philosophy, operating restrictions and parameters, complete hardware and software descriptions, as well as data collected from actual operating tests and computer simulations. The network is unique in that all protocol support functions, mapped onto the first four layers of the International Standards Organization Open Systems Interconnect model are implemented in software, including collision detection.

#### ACKNOWLEDGEMENTS

.The author/wishes to acknowledge the following people for their significant contributions to the development of SCI-net: Dr. Terrill Fancott, for the concept and system specifications of SCI-net; Amitava Sen, for the development of an early prototype version of the hardware interface; Mark Weiser, for assistance with software and hardware development; Jacques Blaison, for assisting in the procurement of components and prototyping boards; and Frank Maselli, for his assistance during the early stages of the implementation of the network design. In addition, and criticisms of Eamon Egan and critical comments Dr. Terrill Fancott were greatly appreciated. The author also wishes to acknowledge the financial support provided by the Natural Sciences and Engineering Research Council.

# TABLE OF CONTENTS

| Chapter 1 - Introduction1                                              |

|------------------------------------------------------------------------|

| 1.0 Introduction                                                       |

| Chapter 2 - A Background Discussion of Networks                        |

| 2.0 Introduction5                                                      |

| 2.1 Definitions                                                        |

| 2.1.2 Raw Bit Rate                                                     |

| 2.1.4 Protocol Overhead                                                |

| 2.2 ISO Layer Model                                                    |

| 2.2.2 The Physical Layer                                               |

| 2.2.4 The Network Layer                                                |

| 2.2.7 The Presentation Layer                                           |

| 2.3 Some Local Area Networks20                                         |

| Chapter 3 - SCI-net: A Software Controlled CSMA/CD Network26           |

| 3.0 Introduction26                                                     |

| 3.1 Factors Governing SCI-net Design27                                 |

| 3.2 ISO Layer Description                                              |

| 3.2.4 SCI-net Transport Layer44 3.2.5 Higher Level SCI-net Functions45 |

| 3.4 Limitations of SCI-net                                             |

| Chapter 4 - SCI-net Hardware50                                         |

| 4.0. Introduction                                                      |

|                                            | •               |

|--------------------------------------------|-----------------|

| 4.1 Block Description                      | 5'Ò 🗋           |

| 4.1.1 Control Circuitry                    | 5.3             |

| 4.1.2 ACIA Circuitry                       | 54              |

| 4.1.3 interval Timer Circuitry             | 22              |

| 4.1.4 Network Interface Circuitry          | 56              |

|                                            |                 |

| 4.2 Detailed SCI-net Interface             | - <b>-</b>      |

| 4.2 Detailed SCI-net Interface Description | <b>)</b> /      |

| 4.3 Interface-System Synchronization       |                 |

| Chapter 5 - SCI-net Software               | 61              |

| 5. Support Software                        |                 |

| 5.1 Software Routined                      | 61              |

| が、1.1 SCI-net READ Call                    | 62 ·            |

| '5.1.2 SCI-net READW Call                  | 63              |

| 5.1. SCI-net WRITE Call                    |                 |

| 5.1.4 SCI-net OPEN Call                    | 64              |

| 5.1.5 SCI-net OPENW Call                   | 65              |

| ' 5.1.6 SCI-net CLOSE Call                 | 65              |

| 5.1.7 SCI-net SPMESS Call                  | 66              |

| 5.2 Additional SCI-net Call Information    | 67              |

| 5.2 Additional Sci-net Call Information.,  | <b>U</b> /      |

| 5.3 Internal SCI-net Driver Routines       | 68              |

| 5:3.1 Internal SCI-net READ I Routine.     |                 |

| 5.3.2 Internal SCI-net RDBYTE Routine.     |                 |

| 5.3.3 Internal SCI-net TIMSER Routine.     |                 |

| 5.3.4 Internal SCI-net WRDRF Routine       |                 |

| 5.3.5 Internal SCI-net WRBYTE Routine.     |                 |

| 5.3.6 Internal SCI-net DELAY Routine       |                 |

| 5.3.7 Internal SCI-net LENGTH Routine.     | 72              |

| 5 ° 4 Chi now Chatus Basishara             | 70              |

| 5.4 SCI-net Status Registers               | 12              |

| 5.5 SCI-net Interrupt Interface            | 74              |

| 5.6 Software Collision Detection           | 75              |

| Chapter 6 - Testing and Simulation         | B.3 •           |

| 6.0 Introduction                           |                 |

| 6.1 Simulation with GPSS                   | 84              |

| 6.2 Simulating SCI-net                     | B7 <sub>.</sub> |

| 6.3 Simulation Results                     |                 |

| 6.4 Observed Measurements                  | 99.             |

| 6 5 Network Overhead                       | 101             |

*:*\* ,

| 6.5.1 Line Monitoring                 |     |

|---------------------------------------|-----|

| Chapter 7 - Conclusions               |     |

| 7.0 SCI-net's Place Among Networks    | 106 |

| References                            | 112 |

| Appendix A - SCI-net Software Listing | 115 |

| Appendix B - GPSS Simulation Program  | 133 |

. ٣

#### CHAPTER 1

#### INTRODUCTION

#### 1.0 INTRODUCTION

Local network architectures using CSMA/CD level protocols present the attractive property of fully distributed control. The success Experimental Ethernet and it's subsequent commercial; implementations has stimulated the development of many CSMA/CD systems with similar characteristics, commonly referred to as 'Ethernet-class' systems [SHOC82]. High systems, using coaxial cable as a performance transmission medium, offer raw transmission speeds of up to 50 megabits per second [FRAN82], while the Ethernet specification provides a 10 megabit rate for 500 metre segments [THUR82]. This performance is, however, bought for a price. Contemporary Ethernet per-station costs, including interface and tap, vary from \$1500 to \$3000. While this is not expensive for networks of high performance computers, it is not reasonable for linking personal computers whose total

cost is in the same order of magnitude.

The need for a low cost networking technology has resulted in the development of a class of Ethernet-like systems based on standard LSI communications devices, and using low cost media such as twisted pair or twinax [THUR82]. Some of these systems, such as the Corvus Omninet or the Cromemco C-net have achieved raw bit rates between 250 kilobits and one megabit, while holding interface prices to about \$1000. Similarly configured research systems based on the Motorola Advanced Data Link Controller (M6854) report speeds of 150 [SMIT82] and 500 [HUTC82] kilobits for relatively low component cost.

This thesis presents the design and implementation of a very low cost CSMA/CD system. At a raw bit rate of 125 kilobits per second, the system has sufficient performance for a medium sized office or laboratory environment, in particular when the usage statistics on the Experimental Ethernet reported by Shoch and Hupp [SHOC80] are considered. Although the theoretical channel utilization for their system is 97%, they reported an average usage of 0.60% to 0.84% over a 24 hour day for 120 users on a 2.94 megabit per second line. These figures suggest that for a large class of applications a significant cost-performance tradeoff is

justified. In our design we push this tradeoff to the limit, moving as many functions into software as is feasible without sacrificing the performance of the individual processors of the network. The result is an interface design only marginally more complex than a standard RS-232C interface, using less than \$15 in components, but fully implementing a CSMA/CD protocol.

Since the primary goal is the development of a low cost system, standard off the shelf LSI components are used in a hardware design that requires only seven integrated devices. The system developed is unique in that collision detection, traditionally performed by hardware, is fully implemented with software. Although this results in delays in detecting message collisions and, as shall be illustrated later, reduces the effective bit rate of the channel when collision detection is in effect, the design presented reduces the overhead incurred to an acceptable level.

Simulations are performed comparing software implementation of key functions such as collision detection and carrier sensing with hardware implementations of the same. The latter are simulated by scaling down the operating speed of Ethernet to that of the software system while retaining relative timing relationships within the protocol.

Although the system is almost entirely software based, the primary limitation upon raw bit rate is determined by the choice of hardware components used. However, faster hardware would not make a significant difference in the maximum atainable raw bit rate unless processor speed were increased accordingly. At present only a two-fold increase increase in processor speed can be obtained.

#### CHAPTER 2

# A BACKGROUND DISCUSSION OF NETWORKS

# 2.0 INTRODUCTION

A computer network is a means for interconnecting two or more computing devices to allow the transfer of information between them. The desire to interconnect several different computer systems via a single network has given rise to some trends and standards governing networks.

This chapter describes some of these standards and examines some common networks in existance today.

#### 2.1 DEFINITIONS

In order to be able to make useful comparisons between different networks, a fundamental understanding of the terms used to describe and define these networks is essential. Thus, terms such as protocol, raw bit

rate, line utilization, protocol overhead, and topology are explained in detail before proceeding any further.

#### 2.1.1 PROTOCOL

A protocol serves to define the means by which a device communicates with other devices on a network. A protocol is usually expressed in terms of its syntax, semantics, and timing.

A protocol's syntax refers to the physical nature of the data sent along a network. At various levels of abstraction it defines the type of electrical signals used, or the ordering of various fields of information in packets or frames, these being the smallest unit of data sent from one, station to another. Such information often includes, but is not limited to, source and destination addresses, the type of the packet, the nature of the data being sent, and the length of the packet.

The semantics of a protocol define how the information passed between devices, or stations, is to be interpreted. In contrast to the syntax, which specifies the manner in which data is formatted, the semantics describe how the various pieces of

information are to be used in supporting the protocol. For example, the type field of a packet may determine whether the data is to be interpreted as protocol management information, or data that is actually being passed between stations via the particular protocol in use. A 'source address' field in one protocol may have an entirely different meaning in another protocol. Furthermore, certain signalling functions such as checksum errors, and packet acknowledgements, can have vastly differing implications in different protocols.

In short, the syntax describes the way in which information is ordered and formatted, while the semantics describe the way in which this information is to be interpreted and used.

A necessary requirement of any protocol is the timing of the protocol. Besides having to specify the timing relationships between successive bits of information, the protocol may place restictions on the timing relationships between successive packets, the maximum allowable time between transmitting a packet and being able to receive the next one, or the minimum allowable time between successive packet transmissions.

For example, the Ethernet protocol specification indicates a serial transmission rate of 10 megabits per

second with no less than 9.6 microseconds between successive packets. [SHOC81]

#### 2.1.2 RAW BIT RATE

The maximum rate at which a network can support the transmission and reception of data is referred to as the raw bit rate. It is the theoretical limit to the speed at which information can pass from one station to another.

Consider Ethernet, with a raw bit rate specification of 10 megabits per second. The actual rate of transmission of information is, in fact, significantly less. Inter-packet spacing, protocol-related information within packets, and various other delays reduce the actual speed at which data can be sent. The same is true of any other protocol since there is always some overhead in arbitration between stations competing for access to the network medium.

A special case of a network protocol is a bus protocol, that is, the method used to transfer data along a parallel bus as opposed to a single serial line. In this case, the maximum bit rate specification

transferred several bits at a time. It is more correct to refer to the parameter as bus bandwidth. This is defined as the capacity of the bus to transfer information. It is still expressed as a quotient of information transfer over time, but the speed requirements of any single bus line are reduced by a factor proportional to the number of data transferring lines in the bus.

#### 2.1.3 LINE UTILIZATION

The line utilization of a particular network is a percentage of the maximum bit rate. It indicates the network's capacity to transfer information, both station-to-station data as well as protocol management information. Factors that contribute to this percentage are turnaround time between sending a message and being able to send the next one, network access arbitration, message length, and the number of stations on the network.

Since the line utilization is dependent on a large number of factors, it is usually expressed under some fixed conditions, such as 'at saturation'. This indicates a measure of the line utilization when all

stations wish to use the network. Typically, the line utilization is an asymptotic function of the number of stations transmitting.

When the line utilization is measured with only one transmitter and one receiver, it indicates the extent to which network arbitration affects performance. The greater the effect, the lower the number of stations that can be adequately supported, all other factors notwithstanding.

#### 2.1.4 PROTOCOL OVERHEAD

The protocol overhead is a simple measure of what percentage of data being transmitted in a packet is for the management of the network protocol. Since this factor directly affects the effective transmission rate from one station to another, it is important to keep it as low as possible. In most protocols, the protocol support information in a packet is always of a fixed length while the protocol may support varying length data fields. Clearly, the greater the packet length, the lower the protocol overhead.

In addition, longer packets imply less arbitration time and may improve line utilization as well. This

apparent improvement does not, however, come without a price. When packets are too long, the average time required to access the network increases and the law of diminishing returns takes effect.

Selecting an appropriate packet length is thus an important factor in the fine tuning of a network.

# 2.1.5 NETWORK TOPOLOGIES

The topology of a network indicates the manner in which stations are connected to the network. Ring, star, and other topologies are all common. A ring topology requires that all stations be connected in a ring, that is a closed loop including all stations. Star networks employ a central network controller or dispatcher that all stations communicate with as an intermediary when sending information to other stations. In addition, the use of repeaters or routing stations affects the manner in which stations can communicate and thus is descriptive of one aspect of the network topology.

The topology of a network places certain restrictions upon the types of protocols that are supported. A network with several message routing

information to be present in packets that circulate around the network. The possibility that some packets might circulate forever must be contended with by the protocol, as well as other topology dependent aspects.

# 2.2 ISO LAYER MODEL

effort to produce an abstract model of network systems introduced the now familiar protocol layer model. The concept of layers of a protocol should follow naturally from the preceding discussion: Protocol layers are analogous to the various levels of abstraction one faces when studying networks. Although designed to describe communications in the long-haul environment, the Open Systems Interconnection Model is also applicable to local area networks.

#### 2.2.1 ISO MODEL OVERVIEW

The ISO Open Systems Interconnection Model [ISO]

(henceforth referred to as 'the ISO model') considers

levels of abstraction within network systems as layers.

Each layer considers a particular aspect of information

transfer from the lowest physical layer to the applications layer.

Relating all networks to a common model facilitates the comparison of such systems and indicates at what level the end user must deal with the system: either direct hardware interfacing, application programs (such as a distributed database query system), or some degree of abstraction between these two extremes.

The ISO model is composed of seven distinct protocol layers. These layers have been designated 1) the physical layer, 2) the link layer, 3) the network layer, 4) the transport layer, 5) the session layer, 6) the presentation layer, and finally, 7) the application layer. The advantages of this modular, layered, system, are clear:

- 1) Facilities necessary for the proper functioning of one layer can be made invisible to other layers.

In particular, a given layer N need only interface to layers N-l and N+l through a set of standard system services.

- 2) Complex systems can be broken up into manageable

sub-systems.

- 3) Changes to a layer are, in most cases, transparent to other layers. Thus, maintenance of the system is simplified.

- 4) Services provided by a particular layer N can make use of all functions offered by lower layers. A strict ordering of layers need not be adhered to, although this offers some benefits.

- 5) Several implementations of a given layer N can co-exist within the system. In particular, there may be several application level interfaces that provide different functions to the user.

- 6) Layers can be modified, or deleted altogther (the model permits layers to be empty) as required throughout the evolution of the system as required. Fine tuning of a system and even major protocol changes can thus be accomplished with a minimum of trouble.

- 7) Each layer may be tested and verified independently of other layers. As stated earlier this increases confidence in the reliability of the overall system. Program verification is an

ongoing area of research and proving correctness of network systems is not trivial.

Although the layer model applies a rigid, modular, structure to network systems, the interpretation of just what services are to be provided by a particular layer are dictated primarily by the subjective opinions of the network designer. Few standards exist, and while the ISO Model provides a convenient means to describe hetwork facilities, it remains to be seen whether standard model layer functions and interfaces will be formed.

#### 2.2.2 THE PHYSICAL LAYER

The physical protocol layer defines the electrical and mechanical specifications of the network. The physical layer performs the transmission and reception of unstructured streams of data bits over the network communications medium.

Common physical layer protocols include the standard RS-232C, RS-442, CCITT X.21 protocols, as well as the myriad of proprietary protocols designed to interconnect various manufacturers' computing

equipment.

#### 2.2.3 THE LINK LAYER

The link protocol layer (also known as the data link layer) performs the transmission and reception of structured streams of bits over the network media. The raw bit stream handled by the physical layer is sub-divided by the link layer into structured frames or packets. Reserved bit patterns, reserved character sequences, or explicit bit counts serve to delimit packets from one another.

Some means of error detection, such as a packet checksum, cyclic redundancy check, or parity bit schemes, are usually implemented in the link layer.

Some standard link layer protocols currently in use include HDLC, SDLC, ADDCP, BiSync, and Ethernet's CSMA/CD sceme.

### 2.2.4 THE NETWORK LAYER

The network layer handles the transmission of a packet from a source node to a destination node. Since

this may involve intermediate routing stations and alternate and/or preferred transmission paths some strategy is required to properly send a packet from source to destination. The network layer provides the mechanism to implement this strategy.

Note that local area networks do not usually have routing or store-and-forward stations. The network layer can thus be very small or, as is often the case, totally empty.

# 2.2.5 THE TRANSPORT LAYER

The transport layer provides reliable end-to-end or host-to-host communication over the network. various schemes used to accomplish this can be divided into two categories: virtual circuits and datagrams. , Virtual circuit systems set up logical or physical between network stations allow connections apparently closed communications links to be set up. Datagrams include as part of their packets routing information which indicates the source and destination of the packet as well as any routing information. Note that datagrams can be used even if no routing is performed (and hence no routing information, need provided).

Virtual circuit protocols have the distinct disadvantage of imposing an overhead in the protocol required to set up the virtual circuits before communication between stations can take place. Despite this disadvantage long-haul systems traditionally employ virtual circuit protocols. This is due to the fact that they are usually easier to implement. [THUR82]

Although more difficult to implement on long-haul, store-and-forward networks than virtual circuit protocols, datagram schemes are easier to implement on local area networks. Thus, one should expect them to be the dominant type of transport layer protocol in future LAN implementations.

#### 2.2.6 THE SESSION LAYER

4

The session layer manages end-to-end communications between processes running stations. Typically it involves the translation of logical process or port names (character strings) into logical and physical unit numbers and network. addressing information. The opening and closing of network transfer links and generation of datagrams as well as managing virtual circuits is all performed by

this ISO Model layer. Of course, the actual functions performed by this layer depend on services provided by the transport and lower layers, as well as local operating system standards and interfacing conventions.

#### 2.2.7, THE PRESENTATION LAYER

The presentation layer is responsible for the translation or transformation of data to be sent to the session layer. For example, a text compression scheme may be employed to reduce the volume of data sent along the network. The presentation layer would then be, responsible for the compression and expansion of information sent to and received from the network.

# 2.2.8 THE APPLICATION LAYER

The application layer provides a variety of application-specific protocols to application programs running on the various stations scattered throughout the network. Such applications include, but are not limited to, electronic funds transfer, mail, distributed database systems, remote job entry, and registration and reservation systems.

As of this writing there do not exist any standard application layer protocols and, due to the diversity

of potential network applications, it is unlikely that there ever will be.

#### 2.3 SOME LOCAL AREA NETWORKS

To familiarize the reader with the types of networks currently available several will be examined.

Due to its success Ethernet deserves close examination.

network employing a coaxial cable with 50 ohm characteristic impedance as the network medium. Data is transmitted along this medium at a rate of ten megabits per second in a Manchester encoded format. This results in a 50% duty cycle and insures a transition in the middle of every bit cell. [SHOC82] The first half of the bit cell contains the complement of the bit value and the second half contains the true value of the bit.

Packets are divided into the following fields: a 64 bit preamble consisting of alternating one and zero bits with the exception that it ends with two successive one bits. Following the preamble is a 48 bit destination address (the least significant bit is transmitted first, by convention), a 48 bit source

address, a 16 bit type field, from 46 to 1500 data bytes (each byte is eight bits wide), and finally, a 32 bit cyclic redundancy check.

The destination address specifies the intended recipients of the packet. If the first bit is zero then the field specifies a unique destination address. If it is one then the remainder of the field specifies a logical group of destination addresses. The special case of all ones indicates that the packet is broadcast to all stations on the network.

The type field specifies which higher level protocol is being used. The variable length data field contains the information that is actually being sent from one station to another. The specification of a minimum 46 byte data field ensures that valid packets will be distinguished from collision fragments.

The cyclic redundancy check (CRC) is computed over the destination address, source address, type field, and data field. This sequence of bits (the first bit of the destination address is taken as the most significant bit) is divided by a specific generating polynomial G(x) to yield a remainder R(x). The bit pattern corresponding to R(x) is transmitted as the CRC.

Ethernet specifies a minimum inter-packet spacing of 9.6 microseconds with a maximum end-to-end round-trip delay of 51.2 microseconds. This places a restriction on the length of cable that can be used and hence the maximum distance between any two stations on an Ethernet network. Furthermore, any packet shorter than the minimum valid packet length is discarded as a collision fragment.

The following control procedure defines how and when a station may transmit packets on the common The purpose of this scheme is the fair resolution of contention for the network among transmitting stations. A station is in DEFER mode when there is a carrier present on the network or minimum packet spacing time after a carrier has been lost has not yet elapsed. A station may enter TRANSMIT mode, and hence send data, if it is not in DEFER mode. It may continue to transmit until either the end of the packet has been reached or a collision is detected. a collision is detected the station enters ABORT mode; transmission of the current packet terminates and a jam of four to six bytes of arbitrary data is sent to ensure that all other transmitting stations also detect After a station has the collision. detected collision and enters ABORT mode, it waits a random retransmission time defined by the following Truncated Binary Exponential Backoff algorithm. The delay before the n'th attempt is a uniformly distributed random number in the range [0, 2\*\*n-1]. For attempts eleven through fifteen, this number is truncated to the range [0, 1023]. After sixteen transmission attempts a higher level protocol decision is required between either attempting further retransmission or abandoning the effort. This algorithm will resolve tairly contention among up to 1024 stations.

Although Ethernet is in widespread use, per-station costs are typically \$1500 to \$3000. Since the cost of small microcomputers is of the same order of magnitude, this may be considered excessive in many potential applications, especially when small numbers of stations are to be networked and the 10 Mb/s bandwidth is not required.

are a host of other networks besides Ethernet available. The Cluster, Magna III manufactured by A. B. Dick Company [THUR82], for example, is based on a loop topology. . Up to stations can be connected to a single loop with as much as 1500 feet between stations. Although this network such diverse applications as word does support processing and electronic mail, and interfaces with CP/M, only Magna III devices are supported. The data rate is a modest 100,000 bits per second. Multiple loops can be interconnected by means of loop gateways.

An interesting concept for a network was developed by Antel Systems Corporation. [THUR82] The physical medium in this network is simply existing AC wiring. Thus, no new cabling need be run when a network such as this is installed. Despite the low data rate of 300 bits per second (modulating a high frequency carrier which is superimposed on the 60 Hz AC line), such a system would appear to be ideal for low volume traffic: up to 2000 stations can be supported over one hundred thousand square feet without the need for signal redistibution. However the cost of the central controller (\$29,500) is completely unacceptable for the large majority of applications.

It is clear, then, that low data rate does not imply low cost. The esoteric nature of the network medium of some networks often dictates the use of expensive technology. Truly low cost network systems are few and far between. This is ironic since the majority of network applications such as small commercial and educational networks do not require the support of large numbers of stations, or great bandwidth, and hence such networks should be relatively inexpensive to implement.

An exception to the high cost network is C-NET, a CSMA/CD protocol network using standard twinax cable, offered by Cromemco Incorporated. Boasting an respectable raw bit rate of 880 kilobits per second, C-NET supports as many as 255 stations up to 2000 meters apart. C-NET will work in a hostile electrical environment, unlike many other networks. The cost per station is a surprising \$500.

SCI-net This thesis introduces (Software Controller Interconnect), a very low cost CSMA/CD network with software implementation of all protocol control functions. As will be seen, to interface costs of approximately \$100 per-station (estimated retail cost) requires minimizing hardware as \much as possible, using conventional network media, and moving as many functions as possible into software. SCI-net is unique in that both carrier sensing and collision detection are performed entirely in software.

#### CHAPTER 3

SCI-NET: A SOFTWARE CONTROLLED CSMA/CD NETWORK

#### 3.0 INTRODUCTION

One of the main objectives in the development of SCI-net was keeping per-station costs as low as possible. This was achieved via compromises in raw bit rate and network performance against hardware complexity. The general idea is to place as many network functions as possible in the network software thus simplifying the hardware considerably. SCI-net is perhaps an extreme example of the application of this philosophy: only seven standard integrated circuits are required to implement a complete SCI-net interface.

The use of a twisted-pair network medium to support a moderate data rate of 125 kilobits per second further reduces installation costs as expensive cable is not employed. An added advantage of using a low data rate is the relative insensitivity of the network

to signal propagation delays. At the present data rate signal degradation due to cable loss is the most significant factor governing the maximum distance that can exist between two stations on SCI-net.

#### 3.1 FACTORS GOVERNING SCI-NET DESIGN

Since hardware complexity and cost were to be kept to a minimum, standard off the shelf LSI (large scale integration) circuits were employed in the circuitry as devices. While certainly opposed custom to contributing to low design and per-unit cost, this what renders collision detection decision is non-trivial 'task. Since the devices software a employed were not specifically designed for local area network applications, making them suitable to such applications required strong software support.

Despite the reliance of SCI-net on the performance of key functions by software, it is nevertheless important not to compromise raw bit rate any more than necessary. As a result the initial release of software to support the SCI-net interface does not display a distinct separation of ISO open model protocol layer functions. Rather, machine code timing is the governing factor in dictating just how the various

software functions are implemented and interfaces.

Furthermore, the overhead of the software required to handle the transmission and reception of messages over the SCI-net twisted pair medium must be kept to a This requirement directly affected the decision to use a hardware interval timer to assist in determining when a particular station is to attend to the network. It is clear that messages not intended for a particular station should be recognized as such as soon as possible so that the remainder of such messages can be ignored. The main purpose of the interval timer is to determine, once software has stopped the monitoring of the network, when the network is to be monitored again. In heavy network significantly reduces the overhead on any particular local station as only those messages that are destined for that station need be received in full. .

SCI-net has been shown to operate very efficiently in a single-process environment. Particular network management functions, for example the transmission of a packet, require the complete attention of the local processor. When a single process is running, clearly it is the one that requested the transmission and thus must wait on the request being completed before being able to continue. Since the process is blocked pending/

the completion of an I/O request the complete use of the processor to service that request is the system. However, this would detrimental to certainly not be the case when several processes would be running since a single SCI-net I/O request would The present implementation of block all processes. software would therefore result SCI-net performance reduction directly proportional to number of messages being sent, and the overhead of link access under heavy traffic conditions.

Since SCI-net is designed as a very low cost local area network, this factor is not unreasonable. A low cost network would normally be used to link small, single user systems. Larger systems would probably justify the increased expense of a more sophisticated network.

Nevertheless, this thesis will show how efficient networks can be derived from the SCI-net concept to efficiently serve multiple process stations without compromising implementation cost.

#### 3.2 ISO LAYER DESCRIPTION

While the SCI-net software does not clearly

reflect the different layers of the protocol used (in the interest of speed), SCI-net can certainly be described in terms of such layers. The architecture of SCI-net has been developed over the first four layers of the ISO reference model. The only exception to this is an empty network layer. However, since there are no intermediate nodes through which packets must pass, an empty network layer is to be expected. This is one of the characteristics of a shared medium system.

The following descussion, therefore, examines SCI-net as a particular realization of an ISO reference model of a network.

#### 3.2.1 SCI-NET PHYSICAL LAYER

As previously stated, SCI-net employs a single twisted pair of conductors as the physical medium through which packets pass from one station to another. This medium accomodates the maximum 125 kilobits per second raw bit rate of the network and has been demonstrated to support over 1/2 mile between stations in similar applications. Testing has shown that although the communications interface drives the network asymetrically in the 1 and 0 states, no negative effects from reflections were observed.

In addition to the network driver proper, the SCI-net interface includes an asynchronous communication interface adapter to support serial transfer of information over the network as well as an interval timer. The interval timer provides timeouts for the various software functions implementing the SCI-net protocol. This relieves the burden of timing functions from software and contributes significantly to efficiency and simplicity of operation: software timing functions are 100% processor intensive, a situation that must be avoided.

The SCI-net hardware is more fully described in chapter four.

### 3.2.2 SCI-NET DATA LINK LAYER

The data link software controls the transmission and reception of packets to and from the network. Software is also responsible for the carrier sense and collision detection functions. Successful transmission and reception of packets is assured through the use of an acknowledge protocol.

Messages are received and held for further processing in a message buffer. As a result, the

current running process need not be synchronized incoming messages and can consume them at any rate. the message buffer is full when a new message message is discarded received the new acknowledgement is sent. After a suitable timeout interval the message will be resent. Eventually the message buffer will be consumed, the new message will and reception will be it. transferred to acknowledged. Currently, transmitting stations are not aware of the speed at which messages can be consumed by receivers. Were the receiver to indicate this to the needless transmission could be transmitter. then avoided and use of the line would improve. This left for future enhancements and upgrades to SCI-net.

Figure 3-1 illustrates the message format.

| SYN SYN -preamble |                  |   |       |      |

|-------------------|------------------|---|-------|------|

| DLE STX           | <br>             |   | . DLE | ETX: |

| . ,               | <br>xt<br>re 3-1 | 6 |       |      |

Currently, the data link software does not perform any error checking. This has been left for future implementation in the session layer. Such a situation should not surprise the reader, who will realize that such a deferment allows the use of several different.

error detection methods without requiring modification of the basic SCI-net software. Since SCI-net is currently in an active research state, this is a logical choice to make.

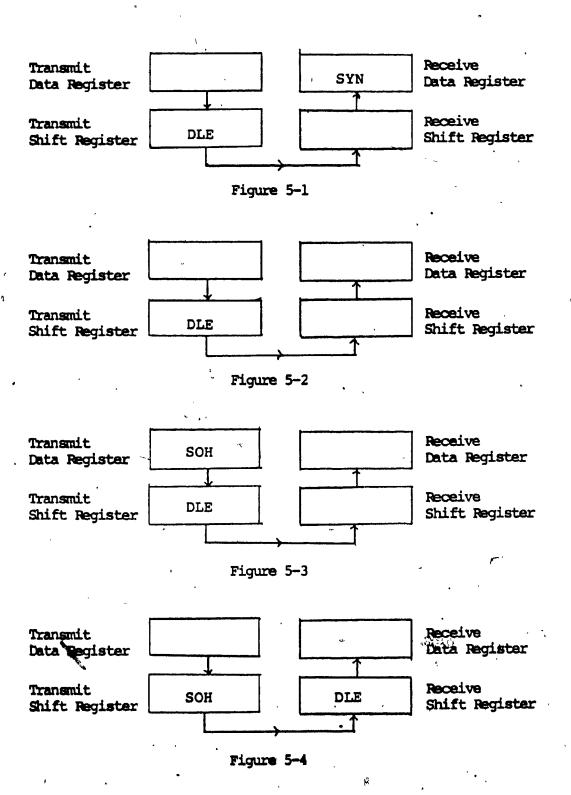

The design of the message format is the key to complete implementation of the protocol in software.

The preamble of SYN bytes insures that all receiving stations are fully synchronized, even in the presence of noise. Furthermore, they allow sufficient time for a station to respond to incoming messages.

A source address byte serves to identify the sender of the message. This byte supports collision detection. In the event that two stations commence transmission simultaneously the senders can detect the collision by comparing their source bytes with the bytes sent on the line. Due to the use of open collector network drivers it is possible that only a single station will detect a collision. This is inconsequential since the rest of the packet being transmitted will either have not been corrupted, if both stations transmit at exactly the same time, or will have been corrupted beyond the point at which it may be received in an incorrect state. In the latter case no receiving station will detect a valid header and so they will simply discard received bytes that

cause SCI-net interrupts. Although this occurrence is not totally avoided, the probability of it occurring is extremely small. The collision detection algorithm serves to reduce the number of timeout and resend attempts due to collisions. The network protocol would continue to function in the absence of such a collision detection algorithm although performance would be significantly compromised. Early slotted-ALOHA used such a scheme.

At this point it is appropriate to describe the various means used to ensure efficient performance. First, when a station has ascertained the network to be free (by monitoring it for a short time), it starts to However, this is transmit. not an indivisible operation in the global sense of the network. exists a 'collision window' during which time another station, may have already started to transmit. Since collision detection takes place only during the transmission of a packet header, this window must be smaller than the time required to transmit such a In fact, the smaller the collision window, the header. lower the probability of a collision occurring since a greater proportion of would-be collisions are avoided. The collision window is presently slightly longer than the time required to transmit a single byte at full Although collisions will not be detected until

after the collision window has passed, stations testing the network to determine its status will find it busy one byte time after transmission begins and will have entered their receive service routine.

If two stations do start transmitting within the collision window then one of two things may happen: both detect the collision and back off, or one detects the collision and backs off.

In either case, if the transmissions perfectly synchronized (an unlikely occurrence), all receivers will be pending on the completion of the As soon as one of the two stations times out packet. and retransmits an ill-formed packet will be received and discarded. Since this is an undesirable situation it is fortunate that the probability of its occurence is practically negligeable. Were the transmission not perfectly synchronized, as is the case with almost all collisions, all receivers would immediately discard the message fragments. If a single station did continue to transmit, its message would simply be discarded. While this is not an ideal situation, the overhead incurred is slight since a non-receipt of acknowledge timeout has been traded for a collision timeout.

The second factor that contributes to improved

network performance is the employment of a random collision timeout. Random timeouts are generally found to be better than constant ones. Consider the case when a fixed collision timeout is implemented: All stations whose transmissions collide with others will detect these collisions at the same time, time but for the same interval, and start retransmitting at the same time. As a result the consequence will be more collisions! Furthermore it is quite possible that such stations will continue to generate collisions infinitum thereby causing themselves to enter infinite loops and depriving other stations from transmitting in created 'collision interval'. prevent this collision timeouts since synchronization will be eliminated before it can start. Two synchronized collisions will, in fact, be quite The reader should note that there is a very rare. close relationship between the size of the collision window and the distribution of the random collision timeout intervals.

A third factor relating to network performance is the number of times in a packet that the occurence of collisions is tested. Although not significantly affecting data transmission rate in proper hardware implementations of collision detection, this has a dramatic effect on transmission rate when implemented in software. When testing for collisions, and using common off-the-shelf serial communications components that nearly almost always employ double buffering, this double buffering must be effectively eliminated since it does no good to test the current byte against the last byte sent. A direct consequence is a pause in the transmission of data. Since the SCI-net protocol needs only to check one byte for possible collisions this effect is reduced as much as possible. Checking more bytes would not reduce the number of collisions, and would have a detrimental effect on network performance.

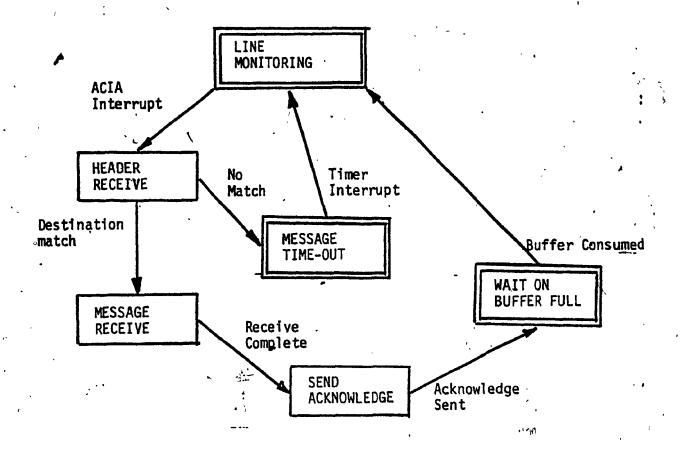

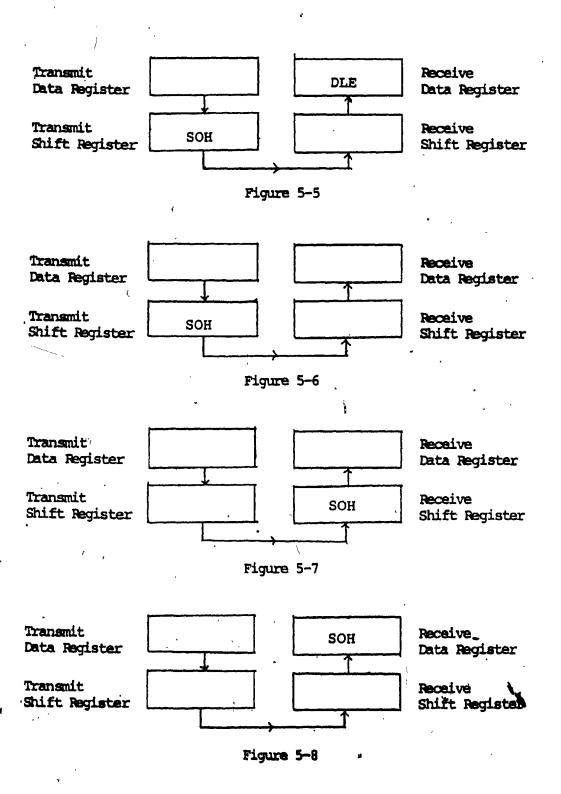

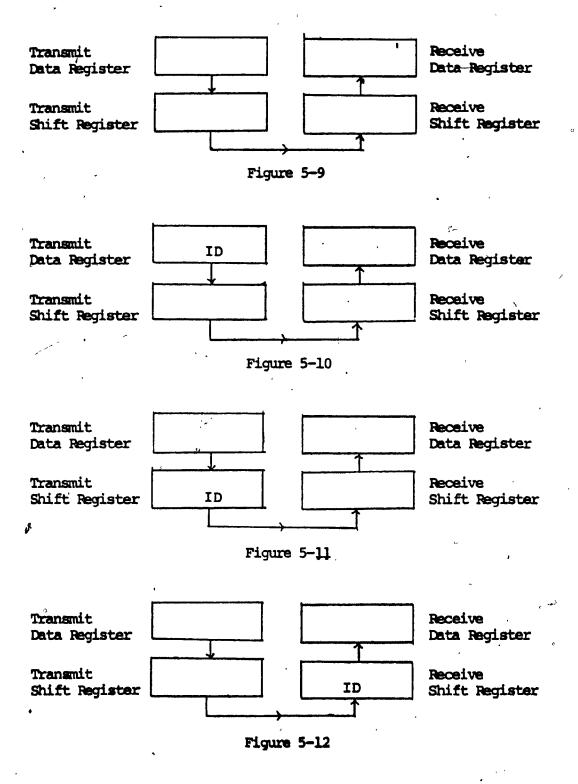

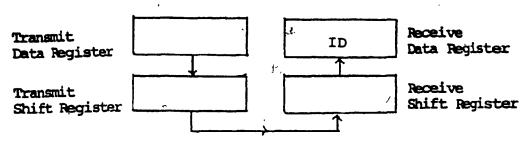

The receive protocol is designed to use as little the processing time of the local processor as possible. In an ideal situation, the local processor should need to examine the line only when it is active and then only during the transmission of the header. This is accomplished by having a receive function design which incorporates several distinct modes of operation (Figure 3-2). In the line monitoring mode the ACIA interrupt is enabled, and the processor continues servicing the user's current process. first byte in a packet to be received by the ACIA causes an interrupt, switching the processor to the header receive mode. This first byte is read and discarded since its purpose is to clear any pending status bits and received data in the ACIA registers.

the ACIA is synchronized to the this point on The header receive software incoming "data stream. monitors the line until it receives the unique sequence SYN DIE SOH. If this sequence is not detected, due to noise on the line, or, more likely, a collision, the packet header fragment/is discarded and the processor returns to line monitoring mode, and the If however, this sequence user task at hand. the processor proceeds to read the SOURCE, received, DEST, and LENGTH bytes. If the destination byte does not match the station then the message is ignored. message may also be ignored if the station is responding to the source of the message or the receive message buffer is full. In any of these cases LENGTH byte is used to determine the length of time the station is to ignore the network. programmed to generate an interrupt after the specified time has elapsed, and interrupts from the ACIA are While the timer is counting down, control re-enabled. is, of course, returned to the user process, although the processor is not in line monitoring mode.

If the local station is capable of receiving the message, NUM is checked to see if it is a duplicated message. Consider the following case: Station A transmits a message to station B. Station B receives the message but the acknowledgement to station A is

lost. As a result station A retransmits the message. Station B detects that it is the same message by examining the NUM byte, and simply sends back an acknowledgement to replace the previous one. Notice that this requires a separate temporary NUM byte buffer for each station with which communication takes place. Currently SCI-net only supports one such buffer and so, a station may communicate with only one other station at any particular time. The preceding does not apply, of course, if reception of multiple messages can be tolerated, or can be handled at a higher protocol layer. SCI-net provides the facility for handling this situation, to some degree, in the data link layer.

Figure 3-2

All successfully received messages are acknowledged by a special acknowledge message, illustrated in Figure 3-3. This is transmitted by the send function.

SYN ... SYN DLE SOH SOURCE DEST LENGTH NUM

DLE STX DLE ACK DLE ETX

Figure 3-3:

The send protocol implements carrier sensing and collision detection. Once the send routine is entered, it will continue to attempt to send a message until it finally succeeds. In contrast to the receive function, this philosophy does not permit local processing while the send routine is waiting on a busy line. The increased complexity of including a 'read while send' function to accommodate this was not justified by the minimal increase in local processing it would allow, considering the fact that each station will normally send only a small proportion of the total messages on the system.

The carrier sense function is indicated by the ACIA read buffer full flag. To avoid any possible noise effects on the line, the receive buffer contents are first read and discarded to reset the flags. The buffer full flag is then inspected after a random delay. If the line is not busy the transmit routine proceeds to send. This initial random delay is to ensure that an equal chance is given to all stations to access the line. It is significant in the case of heavy traffic, where many stations may be waiting for

the end of a transmission. If the line is busy, it is actively monitored until it is free again. When it is free, the send routine transmits the header. When the SOURCE address is transmitted, it is read back from the receive buffer and compared with the station address. A collision will either corrupt the byte sent or result in it not being received at all. Thus, a hard coded timeout is in effect while waiting to read back the SOURCE byte just sent. If it is not the same station address, a collision has occurred, and the routine executes a random delay before retrying. the case of no collision, the full message is sent, and the routine enters a wait for acknowledge timeout. Ιf no acknowledge is received before the end of the timeout, the message is resent. The number of retries before signalling error the local host programmable.

This data link software is capable of sending and receiving continuous bytes at the full 125 kilobits per second speed. The system is fully asynchronous, in the sense that the individual stations need no external signal to synchronize themselves on either a bit, byte, or message level. Furthermore, if they enter the line monitoring mode at any point in a message transmission, they will synchronize themselves at the start of the following message. Incomplete message segments such as

collisions are discarded. Since it is not possible to send the message header without first establishing a quiescent line, and the collision window is less than the time to transmit the header, a collision is guaranteed to never occur within the message text.

### 3.2.3 SCI-NET NETWORK LAYER

As is to be expected, the network layer of the ISO reference model is empty in the case of SCI-net. Since packets do not have to pass through intermediate nodes to reach their destinations this is an expected result and is characteristic of networks with fully distributed control.

It should be noted, however, that there is nothing to prevent a station to interface to more than one SCI-net link. In such instances it is conceivable, and indeed quite likely, that some form of communication across such networks would be desirable. This would require a store and forward mechanism at the intermediate nodes and modification of SCI-net software to support multiple virtual circuits between stations.

Such changes are not conceptually difficult and it is quite feasible to design such a store and forward

node with two (several) SCI-net interfaces, a processor, control ROM, scratchpad RAM, and some control circuitry. This is probably the best way to link several remote SCI-net installations since it is transparent to the basic SCI-net, intermediate nodes or gateways appearing as simple stations to any network they serve.

#### 3.2.4 SCI-NET TRANSPORT LAYER

It has been noted that SCI-net software currently only guarantees no multiple receptions of messages when communication takes place with only one other station. A mechanism is provided whereby user tasks may request channels' created 'open to be restricting communications between the station making the request and the station which is requested. Of course, this does not restrict any other stations from using SCI-net the extent that communication between except to 'foreign' stations and those engaged in an open channel is blocked until the channel is released.

When channel communications open are engaged` terminated. either station in such communications that the channel be request may 'closed'. This is of course, a virtual circuit protocol and SCI-net is immune to multiple open and close channel requests, thus correctly establishing such virtual circuits.

It should be noted that such a protocol need not be used and virtual circuits need not exist to support communications. SCI-net software merely provides facilities to handle multiple receptions of messages when communication takes place with one other station. If the application software can handle multiple receptions of packets then it may implement any degree of virtual circuit communication. SCI-net offers virtual circuits and multiple packet reception immunity under such circuits as a convenience to the application rather than a restriction.

# 3), 2, 5 HIGHER LEVEL SCI-NET FUNCTIONS

Currently SCI-net software offers the ability to send operating system level (FLEX) commands to remote stations. While an application may well be running on such remote stations to intercept such commands, SCI-net is capable of handling packets of such a nature itself. Although this may be construed as a superfluous feature of the network management software, it does serve to illustrate that although such features

have been implemented at the lower protocol levels, for the sake of efficiency, they do not in any way hinder user applications that have no need for them. In this sense virtual circuit support and the routing of packets to the operating system for interpretation are not layers built upon more primitive functions but are rather mini-applications of the network, illustrating primarily the correct, efficient, and cost effective nature of SCI-net.

#### 3.4 LIMITATIONS OF SCI-NET

No description of a network or any other utility would be complete without commenting on the restrictions and limitations that exist. SCI-net is, of course, not the ultimate answer in local area networking and the environments in which it is not suitable must be defined.

When compared to systems such as Ethernet, one immediately comes to the conclusion that SCI-net is both slower and processor (software) dependent. This is quite true. In fact speed and hardware tradeoffs were the primary means of developing a very low cost network. Studies have shown [SHOC80] that networks linking small, single user systems exhibit low average

traffic and only marginally higher peak network traffic. Furthermore, the speed at which an individual station can consume messages from a network is severely limited by its processing power. In the case of microcomputer based systems the processing power is, as expected, quite limited. Even given efficient memory to memory data transfer facilities (DMA, not supported by SCI-net), the increase in effective communication is insignificant, the limiting factor being message consumption rate, a function of processing speed. Shoch and Hupp report [SHOC80] enlightening usage statistics on the Experimental Ethernet (2.94 megabit per second raw bit rate). Average utilization over a 24 hour day for 120 users was only 0.60% to Rates were higher during shorter periods but the busiest hour registered only 3.6%, and the busiest Thus, démands on local processing power minute, 17%. are not as severe as one might be led to believe.

It is relatively simple to show that software implementation of critical network functions such as carrier and collision detection, if done properly, impose little overhead on a single process system. If the network software is only required to examine the network upon receipt of incoming messages to the particular station in question, overhead is kept low since messages can not be sent faster than they can be

consumed. SCI-net approaches this ideal situation closely: only minimal overhead is required to determine that a message is not destined for a particular station, and message retries due to the inability of a station to consume the messages at the would-be data rate can be kept to a low rate (although too low a retry rate results in a reduction of effective data transfer rate and line utilization).

SCI-net requires the complete attention of the local processor when a packet is being transmitted and the corresponding acknowledgement is sent in response. Depending on the existence of virtual circuits blocking reception of the packet, this may take any length of time. However, if a single process is blocked pending successful transmission of a packet across the network then the time it remains blocked is inconsequential since it could not proceed until such a successful transmission.

The case of multiple processes running on a single station is more complex, for SCI-net will block all processes when only a single one has requested transmission of a packet. Despite the limited processing power of small microcomputers, some small operating systems do support such multiple processes, even in a single user environment, and SCI-net should

be able to interface with such systems. In its present implementation this is not possible without an apparent reduction in processing power corresponding to the transmission traffic. However, preliminary estimates and studies indicate that it may be possible to produce an intelligent SCI-net controller with the same complexity as the present one, at little if any, increased cost. With a local buffer or DMA access to main memory, the transmission process would be offloaded from the CPU and would therefore not slow the apparent speed of the system.

# CHAPTER 4

#### SCI-NET HARDWARE

#### 4.0 INTRODUCTION

The architecture of SCI-net has been developed over the first four layers of the ISO reference model. The network layer is empty, a direct consequence of the fully distributed control of the system.

This chapter describes the theory of operation of this SCI-net interface. Beginning with a block diagram, the circuit is described, section by section, with increasing degrees of detail and complexity.

# 4.1 BLOCK DESCRIPTION

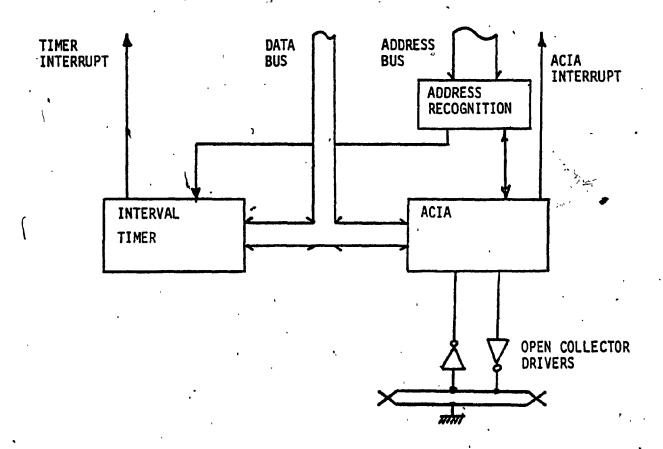

The SCI-net interface contains the following basic components: control circuitry to co-ordinate interface operation, an asynchronous communications interface adapter (ACIA) to convert parallel data to a serial

form, suitable for transmission on the network, a programmable interval timer to assist in keeping track of the busy/free status of the network, and, finally, the network interface. Figure 4-1 illustrates the main signal flow of the interface circuit in block form.

Figure 4-1

# 4.1.1 CONTROL CIRCUITRY

control circuitry is responsible for determining when the central processing unit is with the interface (i.e. communicating interface is addressed by the CPU) and generating clock signal that drives the ACIA and interval timer. When the proper levels are selected on the bus address lines the interface is selected and the processor may read or write to the various registers in the ACIA and The ACIA clock is derived from the interval timer. processor clocks. Two clock signals are available from the processor via the system bus. Commonly referred to as E and Q, these clocks usually run at either 1.000 Mhz or 2.000 Mhz depending upon the top speed of the processor and other system components. In the present experimental system they actually run at 0.895 Mhz rather than 1.000 Mhz due to the crystal in use on the central processor cards.

The SCI-net interface requires a clock rate of 2.000 Mhz for the ACIA. In 2.000 Mhz systems this is obtained directly from E. In 1.000 Mhz systems, advantage is taken of the fact that E and Q are in quadrature to derive a 2.000 Mhz clock from these

signals. Thus systems running at either standard clock rate may be present on the network.

Since the present experimental setup is running at somewhat less than 1.000 Mhz, the interface circuits cards in each station are configured for a 1.000 Mhz system clock and run less than top rated speed. This presents no problems so long as all stations on the network run at the same reduced speed.

# 4.1.2 ACIA CIRCIUTRY

The asynchronous interface adapter is a single integrated circuit that allows data transfer to and from the network. This device can be configured to operate at several data rates and data formats. The SCI-net interface ACIA is always configured to transmit and receive data at a bit rate that corresponds to one sixteenth the ACIA clock rate up to a maximum of 125,000 bits/second. Since the ACIA clock rate normally runs at 2.000 Mhz, the data rate is normally at the maximum data supported by this device.

This device has several registers that can be read and written by the microprocessor. These include a command register, a control register, a status

register, and a data register. The microprocessor writes the appropriate data to the command and control registers to set up the ACIA for the desired data rate and format. The status register can be read by the microprocessor (writing to this register results in a 'software reset' of the ACIA) to determine whether the ACIA can accept the next byte for transmission and if a byte has been received from the network. Note that the ACIA receives its serial input from the same line that its output drives. It is this that allows collision detection to be performed in software with little overhead.

### 4.1.3 INTERVAL TIMER CIRCUITRY

The interval timer, like the ACIA, is a single large scale integration (LSI) circuit. This device has three seperate countdown timers, each of which can be individually accessed by the microprocessor. The programmable interval timer (PIT) is accessed by the microprocessor through the use of several registers that control PIT timers and general operation.

Two of the three timers are used in the SCI-net interface. The first of these is driven by the same clock that drives the ACIA. Since the bit rate of the

ACIA is one sixteenth of this data rate, 16 ACIA clock cycles correspond to the time it takes to transmit (or receive) a single bit. For each byte transmitted there are ten bits sent: a start bit, eight data bits, and a stop bit. Thus the ACIA transmits a single byte in 160 ACIA clock cycles.

The least significant timer is setup to clock the next significant timer every 160 counts. Hence this timer produces a count for every byte transmission time. The PIT is used just for this purpose, to keep track of the probable end of a transmitted message. Thus network software can ignore the network when messages of no interest to a particular station are transmitted. Furthermore, the timer can interrupt the microprocessor when the station should monitor the network for incoming messages once again.

# 4.1.4 NETWORK INTERFACE CIRCUITRY

The ACIA interfaces to the physical network via two signals, the ACIA serial input signal, and the ACIA serial output signal. The serial output signal drives an open collector driver stage whose output is coupled to the network. The serial input connects directly to the output of this driver stage, and hence the network.

Except for a single gate propagation delay, the ACIA serial input follows the serial output exactly. At the present data rate, this propagation delay is of no consequence.

If the network were driven in a different fashion, then some signal conditioning would be required on the ACIA serial input. In the current experimental implementation of SCI-net, this is not necessary.

### 4.2 DETAILED SCI-NET INTERFACE DESCRIPTION

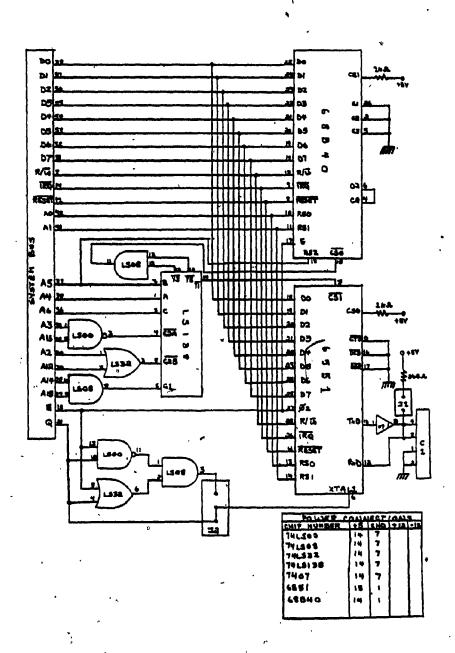

Figure 4-2 is a complete schematic of the SCI-LINK This interface is in the form of a single interface. circuit board (experimental prototype versions were wire-wrapped) that plugs into a slot of the bus of a station. The bus used is a proprietary bus, developed J. Blaison of Concordia University. supports many different eight and sixteen bit processors and is thus well suited for experimental The required bus signals for the SCI-net interface are available on any common microprocessor bus and thus designing SCI-net interfaces for standard busses presents no hardware problems.

As can be seen from Figure 3-2, the address

decoding circuitry is comprised of a 74LS138 address decoder integrated circuit and some support circuitry in the form of NAND and NOR gates. The ACIA occupies four memory locations addressed at \$E018 (henceforth, a dollar sign before a value indicates a hexadecimal value). The PIT occupies two sets of four memory locations addressed at \$E038 and \$E058.

These addresses are not fully decoded. Thus the ACIA and PIT registers are duplicated throughout the memory map of the computer. This simplified the interface design of the prototype SCI-net interface somewhat and is consistent with the partial address decoding schemes used in other interfaces installed in the system.

Figure 4-2

# 4.3 INTERFACE-SYSTEM SYNCHRONIZATION

The PIT is contained in the spingle Motorgla MC6840 As can be seen from the schematic, the LSI circuit. same clock that drives the ACIA (Synertek 6551) also drives this device. It is important, to note that although the timer specifications synchronize clock transitions to E, operation of a timer clock input above 1.000 Mhz is permitted provided that this clock is synchronized to E. This is indeed the case in this circuit. A separate, on-board clock would not only add the component count, but would cause erratic operation of the circuit. The timer clock, and hence the ACIA clock, must be derived from E. In systems. that are based on other processors, there is usually a clock available for generating E and all system However, in asynchronous bus derivatives thereof. systems, such clocks are usually not available and interfacing the SCI-net circuit to such systems' may present problems. In such cases it would be necessary. to use an on-card clock for the timer and ACIA and some means of communicating with the processor by means of the asynchronous bus protocol.

#### CHAPTER 5

# SCI-NET SOFTWARE

# 5.,0 SUPPORT SOFTWARE

The software to support SCI-net consists of several MC6809 assembly language routines that are resident in RAM along with the operating system when the system is running.

These routines have been optimized for speed and thus sacrifices have been made with respect to memory space and readability. However, they occupy approximately one and a half thousand bytes of memory and a set of entry point vectors simplifies routine linkage to application programs. Furthermore, these entry points are at fixed, predefined address to allow for compatibility between existing applications and future modifications to the network driver code.

### 5.1 - SQFTWARE ROUTINES

The SCI-net driver is composed of routines designed to perform distinct functions. The sole purpose of some of these routines is merely to provide an elegant interface to external application code. The rest implement the actual handling of the SCI-net interface.

Interface routines provided include facilities to read a packet, write a packet, wait for a packet to become available and then read it, open and close secure channels (virtual circuits), and open a secure channel after waiting for any open channels to the current station to be closed by a remote station. In addition, there exists a routine for transmitting a special message. Special messages are described below.

### 5.1.1 SCI-NET READ CALL

The SCI-net READ routine transfers a packet in the read buffer to an application program's buffer. On entry the A register contains the length of the receiving buffer and the X register contains the address of the start of the buffer. On exit the A register contains the length of the message received, the B register contains the station identification of the source of the message, and the X register is

unchanged.

It should be noted that a packet must have been received when this routine is called otherwise the contents of the application program's buffer will be indeterminate. A status flag byte, described later, exists to allow applications to determine if a message has indeed been received.

# 5.1.2 SCI-NET READW CALL

This is a convenience call, waiting until a message has been received and then passing it to the application program. The entry and exit conditions are identical to the READ. Real-time programs should not make use of this routine since there is no limit to the time it takes for a message to be received. However, the majority of programs can freely use this routine since it relieves the program from checking for the arrival of a message.

### 5.1.3 SCI-NET WRITE CALL

The WRITE routine allows the transmission of a packet along the network. Since the time taken to

accomplish this function is not known, this call, like the READW call, should not be used in real-time applications. It locks the system into write mode until the transmission is finished and has been acknowledged.

Upon entry, the A register contains the length of the packet to send, the B register contains the station identification of the recipient, and the X register contains the address of the base of the packet to transmit.

In the present implementation the WRITE routine will attempt to transmit a packet indefinitely, there being no provision to abort after a specified number of attempts. Future implementations should allow a variable retry count.

#### 5.1.4 SCI-NET OPEN CALL

b

The SCI-net open routine provides the mechanism by which a single virtual circuit may be established. Such circuits, their relationship to the SCI-net concept, and restrictions upon their use, are described in chapter 3.

On entry to the OPEN routine, the A register contains the station identification of the station with which a secure channel is requested. Since this routine calls WRITE, real-time programs should not make use of it.

This routine will exit when either a secure channel has been established, or a secure channel already exists with a station other than the one specified in the request. In the latter case, the A register will be set to zero upon exit.

# 5.1.5 SCI-NET OPENW CALL

This routine will repeatedly call OPEN until a secure channel has been established. As with the OPEN routine, the A register contains the station identification of the remote station with which a secure channel is desired. This routine is to be used when a currently open channel will be closed by a remote station. It removes the responsibility of constantly calling OPEN by the application program in such a case.

### 5.1.6 SCI-NET CLOSE CALL

This routine will close any secure channel currently open. Since it makes use of the WRITE call, it should not be used in real-time programs.

If no secure channel is currently open with the station in question then CLOSE will set the A register to zero on exit. If this call is to be used to check for this condition it is the responsibility of the application program to ensure that the A register is non-zero prior to calling CLOSE.

### 5.1.7 SCI-NET SPMESS CALL

Although not designed for use by application programs, this call is made available to the user should it be desired to implement additional protocol control functions in the enhancement of SCI-net.

SPMESS expects the same entry conditions as WRITE.

It performs the same function as WRITE with one important exception: WRITE normally doubles DLE bytes encountered in the packet to be transmitted. This allows transparent transmission of eight bit data.

SPMESS inhibits this doubling from taking place.

SPMESS amust be entered with interrupts disabled

and it will exit with interrupts enabled unless the S\_ACK bit (bit 3) within the internal SCI-net status byte was set. This bit it not normally available to application programs.

## 5.2 ADDITIONAL SCI-NET CALL INFORMATION

All SCI-net software routines are called as subroutines with either a BSR, LBSR, or JSR instruction, respecting the particular routine's entry requirements. All routines preserve all registers unless otherwise specified in the above description of the individual routines.

The entry point addresses of these routines are presently as follows:

READ \$2000

WRITE \$2003

OPEN \$2006

**CLOSE \$2009**

READW \$200C

SPMESS \$200F

OPENW \$2012

The dollar sign (\$) indicates a hexadecimal quantity. This convention is adhered to throughout this thesis.

Note that currently the SCI-net routines reside in low memory on the MC6809 computer systems. While adequate for testing and some applications, when incorporated into the FLEX operating system, they should reside just below FLEX's base. This will require reassembly of the SCI-net drivers.

## 5.3 INTERNAL SCI-NET DRIVER ROUTINES

In addition to the SCI-net routines provided as an applications interface, there are several others that perform the actual protocol handling. Although these be used under any circumstances by should not application programs, they are documented here for the sake of completeness and to provide information for persons wishing to make custom changes and modifications.

It should be noted that, to discourage use by application programs, none of the following routines have entry points in the contiguous entry point block used for the application interface.

# 5.3.1 INTERNAL SCI-NET READ\_I ROUTINE

This routine is entered whenever the ACIA on the SCI-net interface generates an interrupt. This routine accepts incoming messages and saves them in a buffer until they can be consumed. Details such as the handling of secure channels, message duplication when using virtual circuits, verification of properly formatted incoming packets, and the ignoring of messages not destined for a particular station are handled in READ-I.

After the initial ACIA interrupt that results in READ\_I being entered, the ACIA is polled for each additional byte that is expected. This is necessary since a fully interrupt-driven scheme serving incoming data on a byte by byte basis would not be fast enough to receive an entire packet.

As previously described, when a packet header is received that is not destined for a particular station, interrupts from the ACIA are disabled and the programmable interval timer is set up to generate an interrupt when the message should end.

Although data is received from the ACIA on a polled basis, a timeout feature ensures that all receivers will not 'lock-up' should transmission of a packet cease unexpectedly.

### 5.3.2 INTERNAL SCI-NET RDBYTE ROUTINE

This routine performs the actual polling of the SCI-net ACIA for incoming data. The timeout function to prevent endless looping when a transmitter unexpectedly stops in the middle of a packet is implemented within RDBYTE.

### 5.3.3 INTERNAL SCI-NET TIMSER ROUTINE

TIMSER handles timer interrupts. The timer serves two purposes: first, it serves to implement some of the timeout functions within the WRITE routine such as checking for acknowledge timeout and retry after collision timeout; second, it keeps track of when ACIA interrupts are to be re-enabled after the transmission of a packet that is not destined for the particular station in question has ended.

TIMSER therefore either re-enables ACIA interrupts

or simply clears a flag depending upon the status of a flag in the SCI-net internal status register. This register is not available to application programs.

# 5.3.4 INTERNAL SCI-NET WRDRF ROUTINE

This routine is employed during collision detection. It waits for either the receive data register within the SCI-net ACIA to become filled with the character just received or timeout, indicating which of the two occurred with the A register either unaltered or zeroed upon exit.

Since collision detection in software is one of the unique aspects of SCI-net it will be discussed separately in section 5.6.

## 5.3.5 INTERNAL SCI-NET WRBYTE ROUTINE

This routine performs the actual transmission of a byte on the network.

# 5.3.6 INTERNAL SCI-NET DELAY ROUTINE

This routine implements a random delay. Such delays are used to ensure fair resolution of contention for the network after detection of a collision and during the initial request for access to the network. Presently, this delay is implemented by referring to a counter that runs between eight and sixteen byte times. Although it may appear that a uniformly distributed delay should be used with less chance of two stations using the same delay time, simulations indicate that there is little difference between the two methods.

## 5.3.7 INTERNAL SCI-NET LENGTH ROUTINE

This routine computes the true length of a buffer after DLE's are doubled.

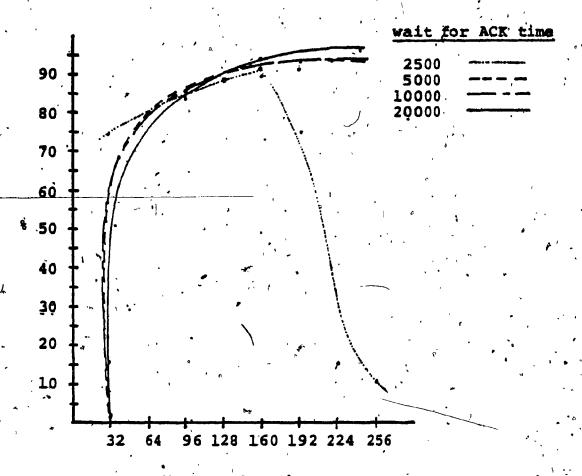

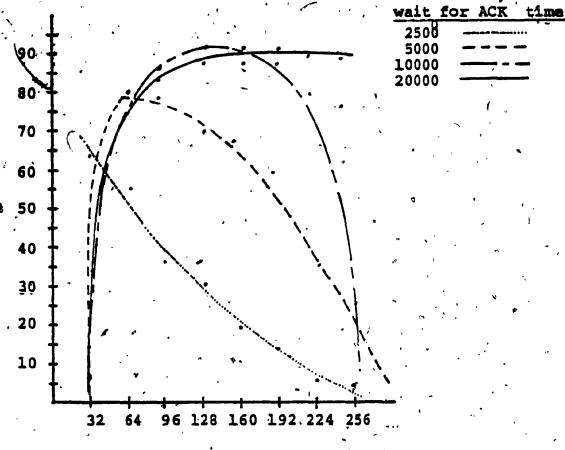

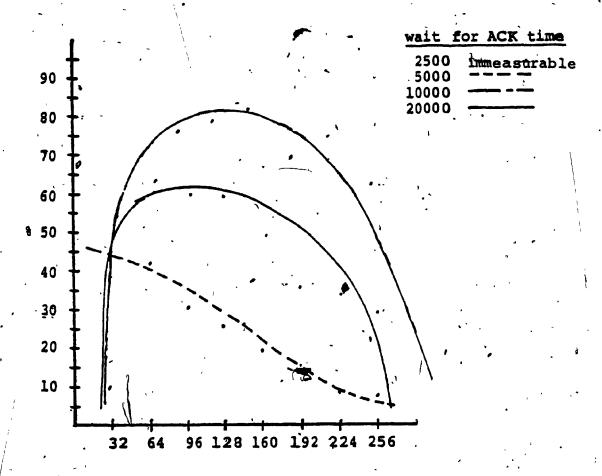

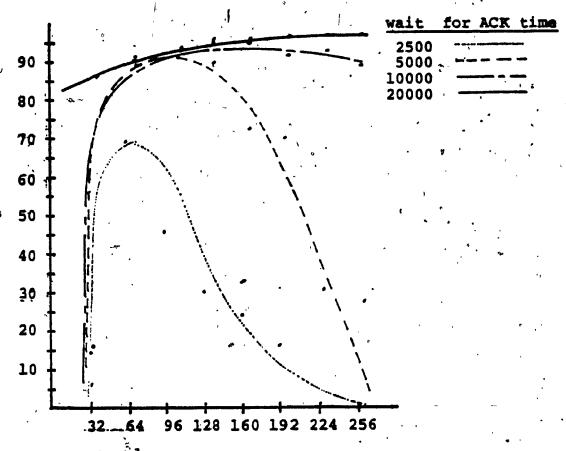

### 5.4 SCI-NET STATUS REGISTERS