National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R S.C 1970, c C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-56094-0

# SMR TOPOLOGIES WITH ADVANCED WAVESHAPING FEATURES

Atluri Rama Prasad

A Thesis

ln

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University

Montreal, Quebec, Canada

October 1989

© Atluri Rama Prasad, 1980

#### **ABSTRACT**

## SMR TOPOLOGIES WITH ADVANCED WAVESHAPING FEATURES

Atluri Rama Prasad, Ph.D. Concordia University, 1989

In switch mode ac-to-dc power conversion, a high quality input ac current and output dc voltage are of primary importance. However switch-mode-rectifier (SMR) converters are often designed to produce clean, well regulated outputs while problems with the input side are either ignored or inadequate compensation is provided through the use of typical L-C filters. The present proliferation of switching converters and other non-linear loads is changing this approach and forcing designers to consider converters as generators of both input ac current and output dc voltage waveforms. These ac-to-dc converters are expected to be rugged, cheap, compact, reliable non-interfering with other loads in the vicinity of the converter and isolated for safety and k ad matching. While these requirements can be met by existing structures at low power levels (less than 1 (one) kW), for medium power levels (3 kW to 20 kW) the above requirements cannot be satisfied because of the bulky L and C components which comprise the various converter filters.

In this thesis, passive and active input-current waveshaping methods suitable for single-phase and three-phase fed ac-to-dc SMR converters are proposed, analyzed and experimentally verified. All these methods discussed maintain high quality input current and output voltage waveforms while providing the necessary ohmic isolation. Finally the associated improved output

voltage control methods needed to compensate for input voltage and load variations are also discussed.

The different modes of operation of the single-phase and three-phase acto-dc SMR converters are analyzed in detail and the design expressions are derived. A systematic and comprehensive analysis and design approach is established. This approach is subsequently used to design and implement of the proposed methods.

Finally, in order to establish the feasibility of the proposed passive and active input current waveshaping methods and the associated output voltage control methods, analytical computer based results are verified experimentally.

### **ACKNOWLEDGEMENTS**

The author wishes to express his gratitude to his research advisor Dr. P.D. Ziogas for his friendship, guidance, support and encouragement during all the stages of this research.

The author's indebtedness to Dr. S. Manias, his research advisor, who initiated this research and has been a source of inspiration is acknowledged. It has been a great honor to be a member of their research team.

The author wishes to acknowledge the financial support provided by the National Science and Engineering Council of Canada (NSERC) and the Quebec Government fee remissions throughout the period of this research.

Thanks are due to my friends and research colleagues Mr. L. Moran, Mr. Joseph Woods and others in the Power Electronics laboratory for the interesting discussions we shared.

### Table of Contents

|                                               | Page  |

|-----------------------------------------------|-------|

| Abstract                                      | 111   |

| Acknowledgements                              | v     |

| Table of Contents                             | vi    |

| List of Figures                               | xl    |

| List of Tables                                | xvii  |

| List of Acronyms                              | xvi'' |

| List of Principal Symbols                     | xix   |

| CHAPTER 1: INTRODUCTION                       | 1     |

| 1.1 General Introduction                      | 1     |

| 1.2 Review of Previous Work                   | 7     |

| 1.2.1 Single-Phase Rectifiers                 | 7     |

| 1.2.2 Three-Phase Rectifiers                  | 8     |

| 1.2.3 DC-DC Converters                        | 10    |

| 1.3 Scope of the Thesis                       | 11    |

| CHAPTER 2: PASSIVE INPUT CURRENT WAVESHAPING  |       |

| SECTION                                       | 15    |

| 2.1 Introduction                              | 15    |

| 2.1.1 Passive Waveshaping Methods             | 17    |

| 2.2 Typical Front-end Passive Filter Topology | 22    |

| 2.2.1 Front-end Rectifier                     | 24    |

| 2.2.2 Rectifier Output Filter                              | 25 |

|------------------------------------------------------------|----|

| 2.2.3 Component Ratings                                    | 27 |

| 2.2.4 Design Example                                       | 28 |

| 2.2.5 Experimental Results                                 | 31 |

| 2.2.6 Conclusions                                          | 33 |

| 2.3 Proposed Front-end Passive Filter Topology             | 33 |

| 2.3.1 Input Filter                                         | 34 |

| 2.3.2 Front-end Rectifier                                  | 40 |

| 2.3.3 Rectifier Output Filter                              | 43 |

| 2.3.4 Component Ratings                                    | 43 |

| 2.3.5 Design Example                                       | 48 |

| 2.3.6 Experimental Results                                 | 50 |

| 2.3.7 Conclusions                                          | 54 |

| 2.4 Conclusions                                            | 54 |

| CHAPTER 3: ACTIVE INPUT CURRENT WAVESHAPING                |    |

| SECTION                                                    | 57 |

| 3.1 Introduction                                           | 57 |

| 3.1.1 Active Waveshaping Methods                           | 57 |

| 3.1.1.1 Boost Active                                       | 58 |

| 3.1.1.2 Synchronous Active                                 | 62 |

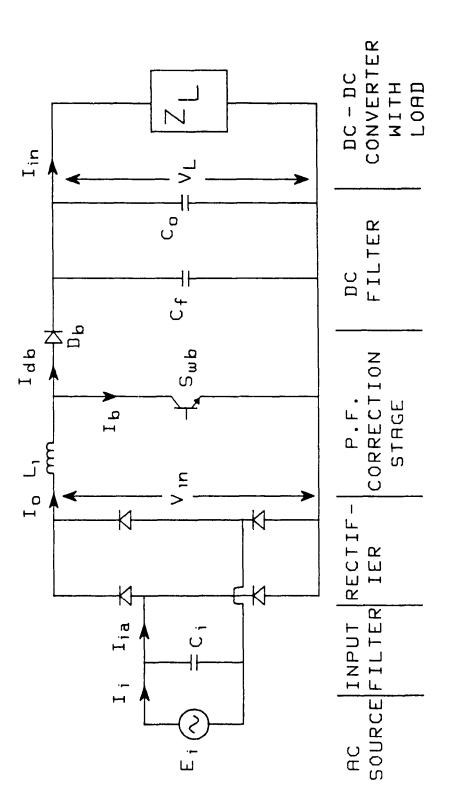

| 3.2 Proposed Single-Phase Fed Boost Active Filter Topology | 64 |

| 3.2.1 Principles of Operation and Topology                 | 67 |

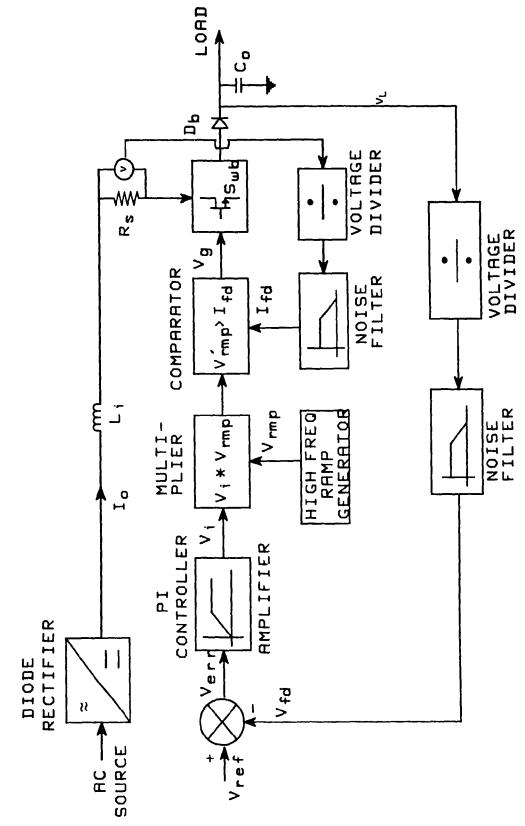

| 3.2.2 Principles of Input Current Control and Waveshaping  | 70 |

| 3.2.3 Front-end Section                                    | 72 |

|     | 3.2.4 Component Ratings                                     | 76  |

|-----|-------------------------------------------------------------|-----|

|     | 3.2.5 Design Example                                        | 79  |

|     | 3.2.6 Experimental Results                                  | 81  |

|     | 3.2.7 Conclusions                                           | 88  |

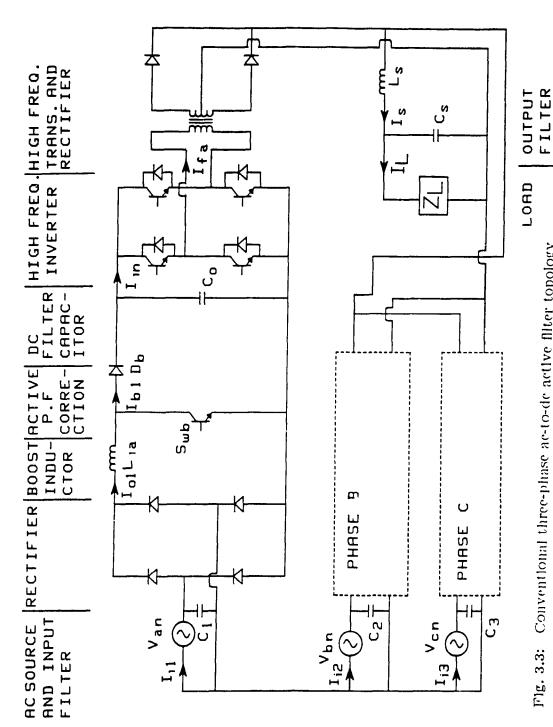

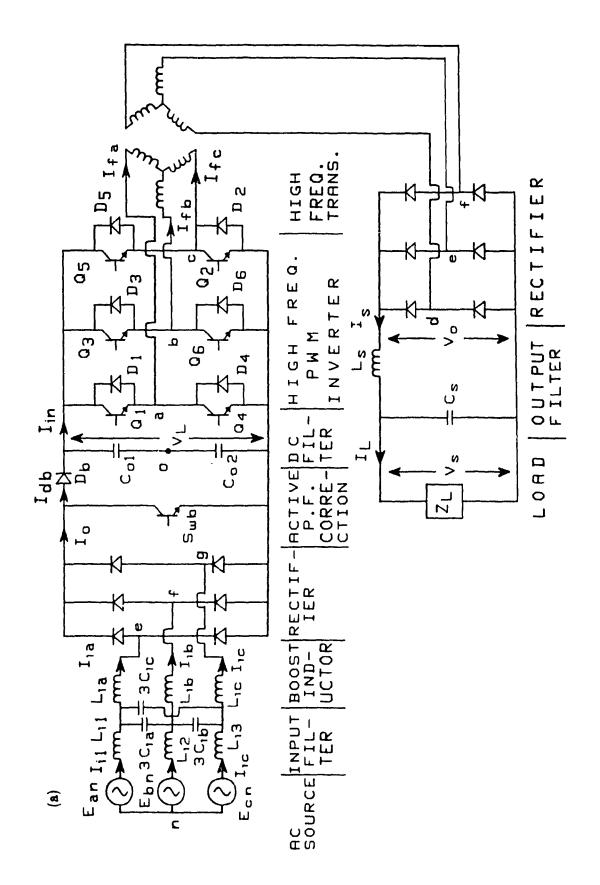

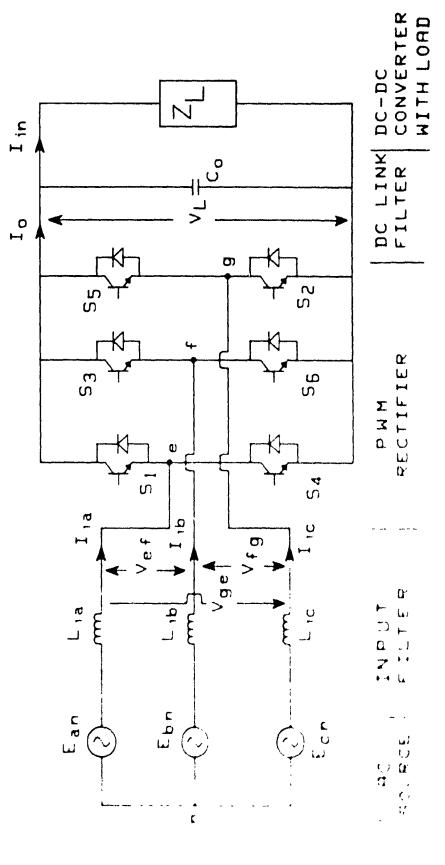

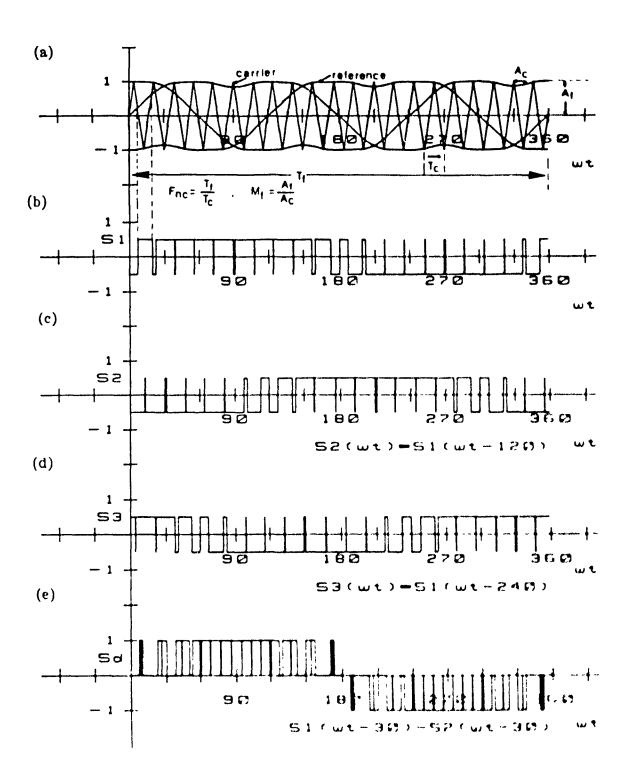

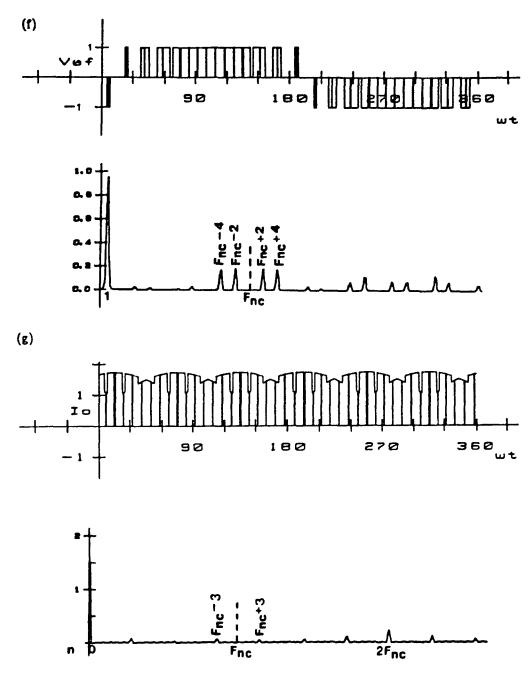

| 3.3 | B Proposed Three-Phase Fed Boost Active Filter Topology     | 88  |

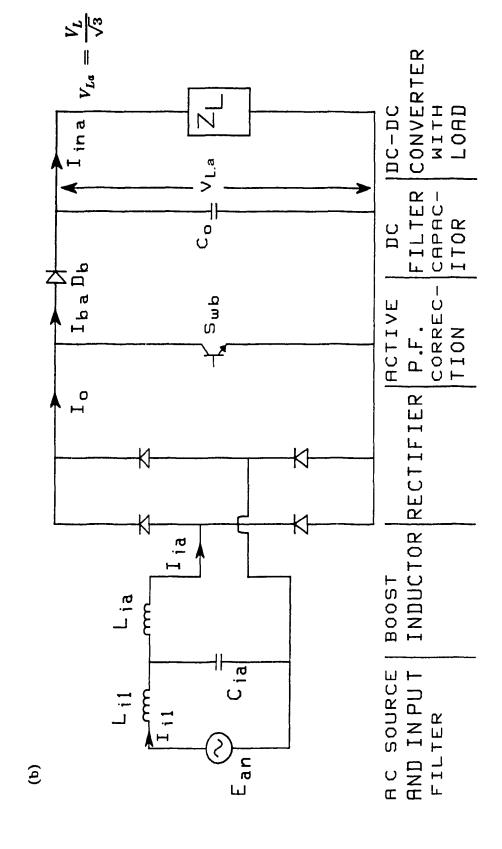

|     | 3.3.1 Principles of Input Current Control and Waveshaping   | 91  |

|     | 3.3.2 Input Current                                         | 95  |

|     | 3.3.3 Front-end Section                                     | 101 |

|     | 3.3.4 Output Filter                                         | 102 |

|     | 3.3.5 Input Filter                                          | 105 |

|     | 3.3.6 Component Ratings                                     | 107 |

|     | 3.3.7 Design Example                                        | 109 |

|     | 3.3.8 Experimental Results                                  | 110 |

|     | 3.3.9 Conclusions                                           | 111 |

| 3 - | Proposed Three-Phase Fed Synchronous Active Filter Topology |     |

|     |                                                             | 116 |

|     | 3.4.1 Principles of Operation                               | 115 |

|     | 3.4.2 Control Principles                                    | 118 |

|     | 3.4.3 Active Synchronous Filter Topology                    | 128 |

|     | 3.4.4 Output Filter                                         | 130 |

|     | 3.4.5 Input Filter                                          | 131 |

|     | 3.4.6 Component Ratings                                     | 132 |

|     | 3.4.7 Design Example                                        | 133 |

|     | 3.4 & Experimental Results                                  | 134 |

. . . .

| 3.4.9 Conclusions                                       | 135 |

|---------------------------------------------------------|-----|

| 3.5 Conclusions                                         | 135 |

| CHAPTER 4: HIGH-FREQUENCY LINK SECTION                  | 139 |

| 4.1 Introduction                                        | 139 |

| 4.1.1 Single-Phase High-Frequency Link                  | 140 |

| 4.1.2 High Frequency Link with Suppressed dc Components | 143 |

| 4.1.3 Three-Phase High-Frequency Link                   | 143 |

| 4.2 Single-Phase High Frequency Link Section            | 147 |

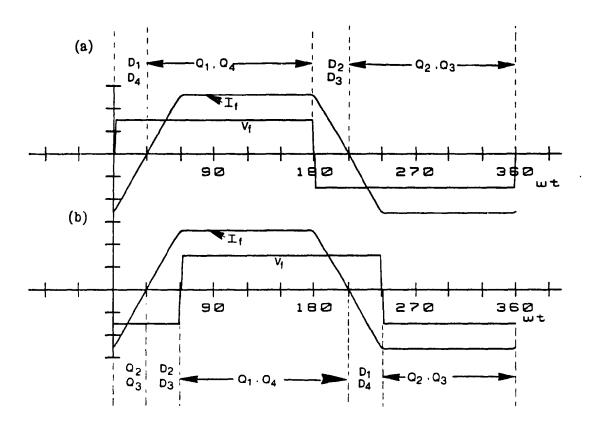

| 4.2.1 Inverter, Rectifier                               | 149 |

| 4.2.2 Output Filter                                     | 158 |

| 4.2.3 Inverter Input Filter                             | 160 |

| 4.2.4 High Frequency Transformer                        | 163 |

| 4.2.5 Inverter Restifier Component Retings              | 164 |

| 4.2.6 Design Example                                    | 165 |

| 4.2.7 Experimental Results                              | 166 |

| 4.2 S Conclustons                                       | 169 |

| 4.3 High Frequency Link with Suppressed do Components   | 169 |

| 4.3.1 Principles of Operation                           | 170 |

| 4.3.2 Centr ! Principles                                | 173 |

| 4.3.3 SMR Converter                                     | 175 |

| 4.3.4 Output Filter                                     | 175 |

| 4.3 5 High Erequincy Transformer                        | 179 |

| 4.3.6 Centratent Ratings                                | 150 |

| 4.3.7 Design Example                        | 181 |

|---------------------------------------------|-----|

| 4.3.8 Experimental Results                  | 182 |

| 4.3.9 Conclusions                           | 182 |

| 4.4 Three-Phase High Frequency Link Section | 184 |

| 4.4.1 Inverter Under Zero Line Inductance   | 185 |

| 4.4.2 Inverter Under Small Line Inductance  | 186 |

| 4.4.3 Inverter/Rectifier                    | 193 |

| 4.4.4 Output Filter                         | 197 |

| 4.4.5 Inverter Input Filter                 | 200 |

| 4.4.8 High Frequency Transformer            | 202 |

| 4.4.7 Inverter/Rectifler Component Ratings  | 203 |

| 4.4.8 Design Example                        | 205 |

| 4.4.9 Experimental Results                  | 207 |

| 4.4.10 Conclusions                          | 210 |

| 4.5 Conclusions                             | 210 |

| CHAPTER 5: SUMMARY AND CONCLUSIONS          | 213 |

| 5.1 Conclusions                             | 213 |

| 5.2 Suggestions for Future Work             | 216 |

| REFERENCES                                  | 218 |

### List of Figures

|           |                                                                        | Page |

|-----------|------------------------------------------------------------------------|------|

| Flg. 1.1  | Block diagram of an ac-to-dc SMR converter                             | 3    |

| Flg. 2.1  | Conventional SMR converter                                             | 16   |

| Fig. 2.2  | Typical SMR converter with front-end passive filter topol-             |      |

|           | ogy                                                                    | 18   |

| Flg. 2.3  | Simulated waveforms                                                    | 20   |

| Fig. 2.4  | SMR converter with resonant input filter                               | 21   |

| Fig. 2.5  | SMR converter with proposed front-end passive filter topol-            |      |

|           | ogy                                                                    | 23   |

| Flg. 2.6  | Variation of input power factor with dc bus voltage $(V_L)$            |      |

|           |                                                                        | 26   |

| Flg. 2.7  | Variation of output power ( $P_{\tau}$ ) with dc bus voltage ( $V_L$ ) |      |

|           | for different values of $L_{\rm r}$                                    | 26   |

| Flg. 2.8  | Variation of Tva with output power ( $P_{	au}$ ) for different         |      |

|           | values of $L_i$                                                        | 29   |

| Flg. 2.9  | Typical front-end passive filter topology experimental                 |      |

|           | waveforms                                                              | 32   |

| Fig 2.10  | Proposed front-end passive filter topology simulated                   |      |

|           | waveforms                                                              | 38   |

| Flg. 2.11 | Variation of input power factor with dc bus voltage $(V_L)$            |      |

|           |                                                                        | 42   |

| Fig. | 2.12 | Variation of output power with dc bus voltage ( $V_L$ ) for     |    |

|------|------|-----------------------------------------------------------------|----|

|      |      | different values of $L_r$                                       | 42 |

| Fig. | 2.13 | Variation of Tva with output power for different values of      |    |

|      |      | L,                                                              | 46 |

| Fig. | 2.14 | Experimental waveforms of the proposed passive SMR con-         |    |

|      |      | verter                                                          | 51 |

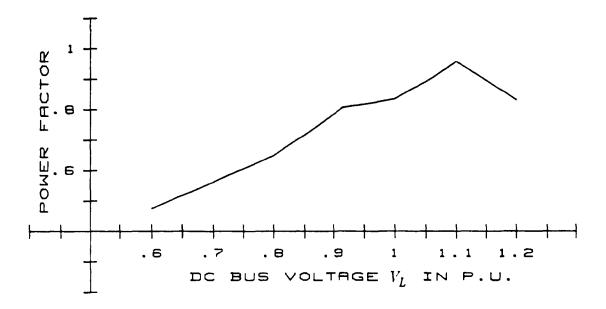

| Fig. | 2.15 | Experimental variation of input power factor with dc            |    |

|      |      | bus voltage ( $V_L$ )                                           | 55 |

| Fig. | 3.1  | SMR converter with front-end active filter topology             | 59 |

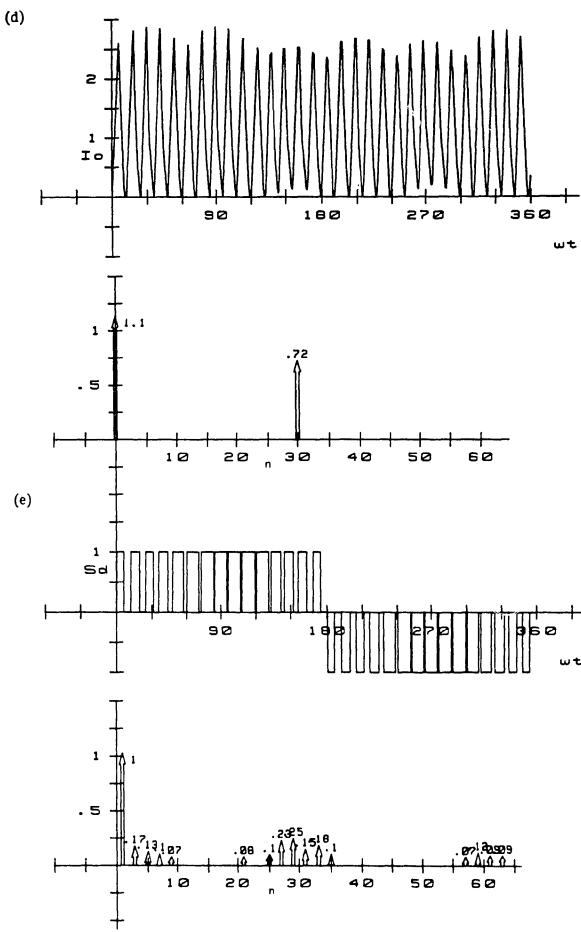

| Fig. | 3.2  | Active input current waveshaping dc link inductor current       |    |

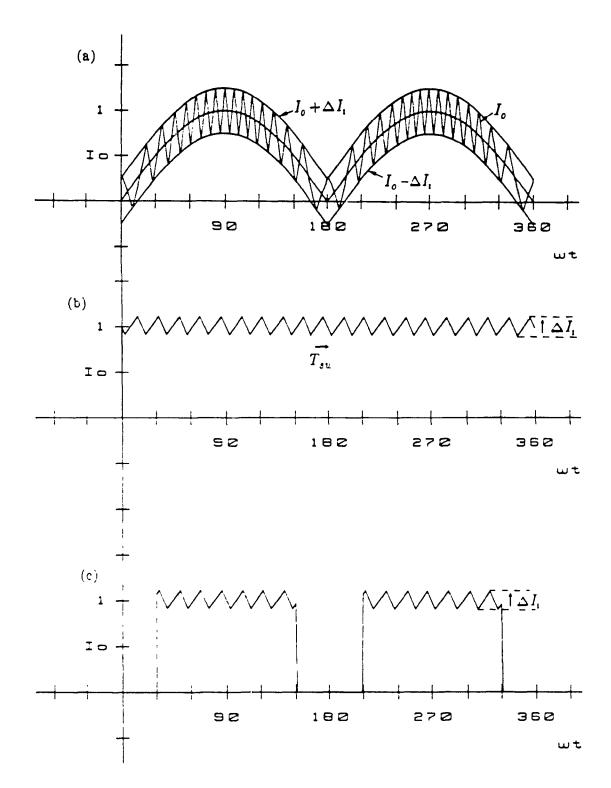

|      |      | $(I_o)$                                                         | 60 |

| Fig. | 3.3  | Conventional three-phase ac-to-dc active filter topology        | 63 |

| Fig. | 3.4  | Proposed front-end active filter topology                       | 66 |

| Fig. | 3.5  | Block diagram of the proposed active input current              |    |

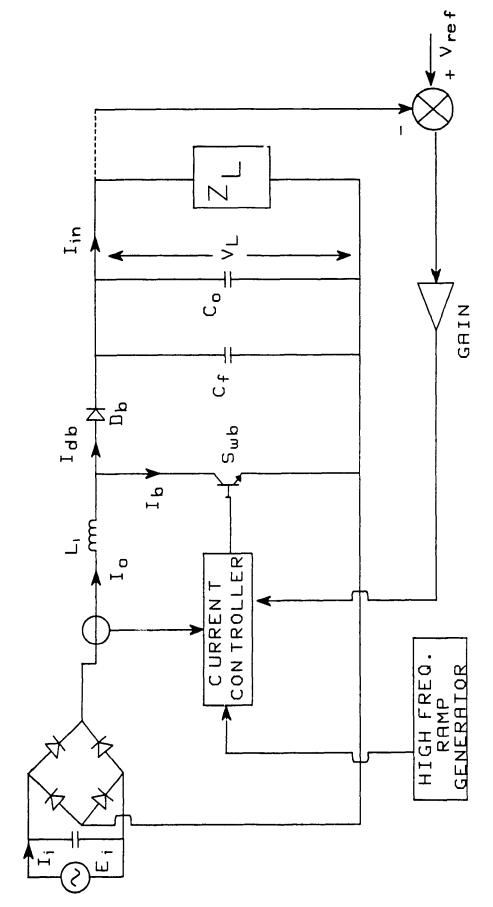

|      |      | waveshaping circuit                                             | 68 |

| Fig. | 3.6  | Simplified circuit of the proposed active input current         |    |

|      |      | waveshaping method                                              | 69 |

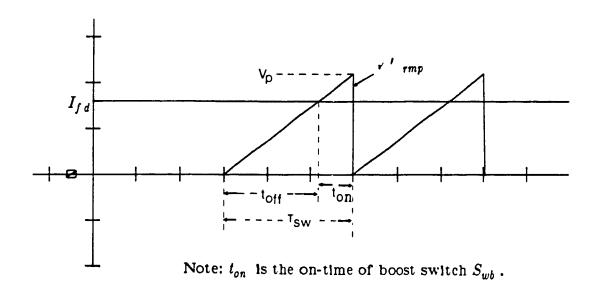

| Flg. | 3.7  | Principle of the active input current current control           | 71 |

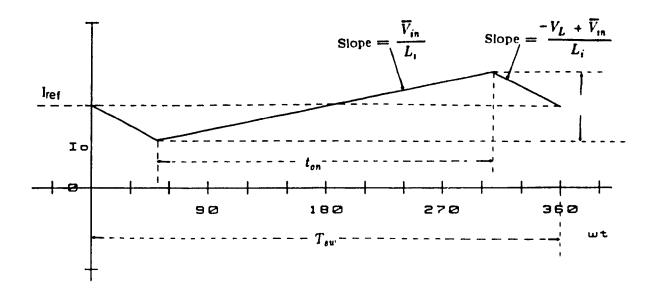

| Fig. | 3.8  | Input current waveform for a random switching period            |    |

|      |      | $(T_{sw})$                                                      | 74 |

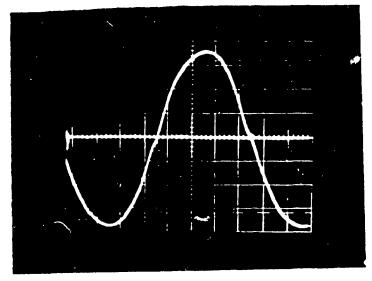

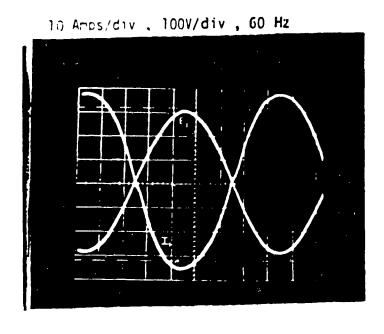

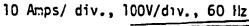

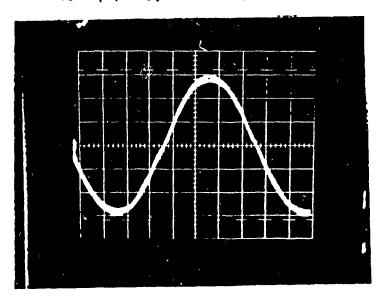

| Fig. | 3.9  | Experimental ac input current ( $I_i$ ) at rated load           | 83 |

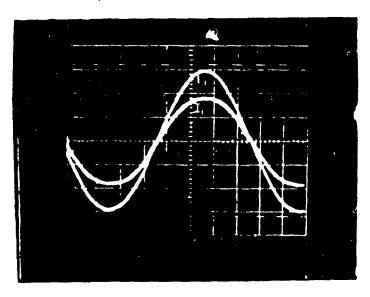

| Fig. | 3.10 | Experimental ac input voltage $(E_i)$ and input current $(I_i)$ |    |

|      |      | at rated load (180° out of phase)                               | 83 |

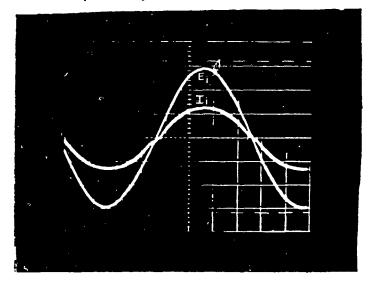

| Fig. | 3.11 | Experimental ac input voltage $(E_i)$ and input current $(I_i)$ |    |

|      |      | at rated load (In-phase)                                        | 84 |

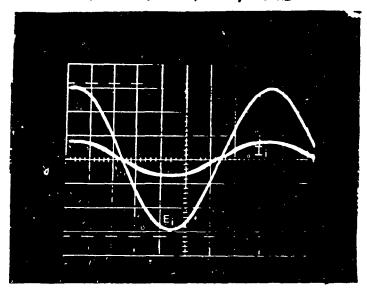

| Fig. 3.12 | Experimental dc link inductor current $(I_o)$ at rated load      | 84  |

|-----------|------------------------------------------------------------------|-----|

| Fig. 3.13 | Experimental ac input voltage $(E_i)$ and current $(I_i)$ at 75- |     |

|           | percent rated load                                               | 85  |

| Flg. 3.14 | Experimental ac input voltage $(E_i)$ and current $(I_i)$ at 50- |     |

|           | percent rated load                                               | 85  |

| Flg. 3.15 | Experimental ac input voltage $(E_i)$ and current $(I_i)$ at 33- |     |

|           | percent rated load                                               | 86  |

| Flg. 3.16 | Experimental ac input voltage $(E_i)$ and current $(I_i)$ at 14- |     |

|           | percent rated load                                               | 86  |

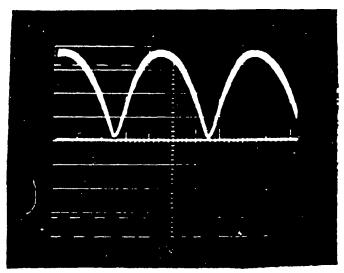

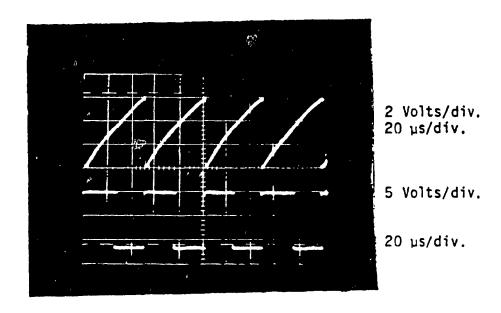

| Fig. 3.17 | Experimental high frequency (20 kHz) ramp waveform               |     |

|           | (upper trace) and respective oscillator output waveform          |     |

|           | (lower trace)                                                    | 87  |

| Fig. 3.18 | Proposed three-phase ac-to-dr active filter topology and its     |     |

|           | single-phase equivalent circuit                                  | 89  |

| Fig. 3.19 | Proposed three-phase ac-to-dc converter simulated                |     |

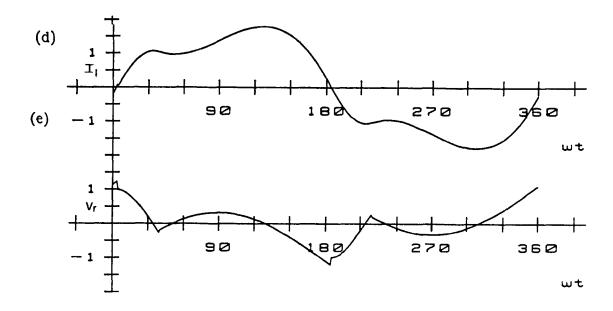

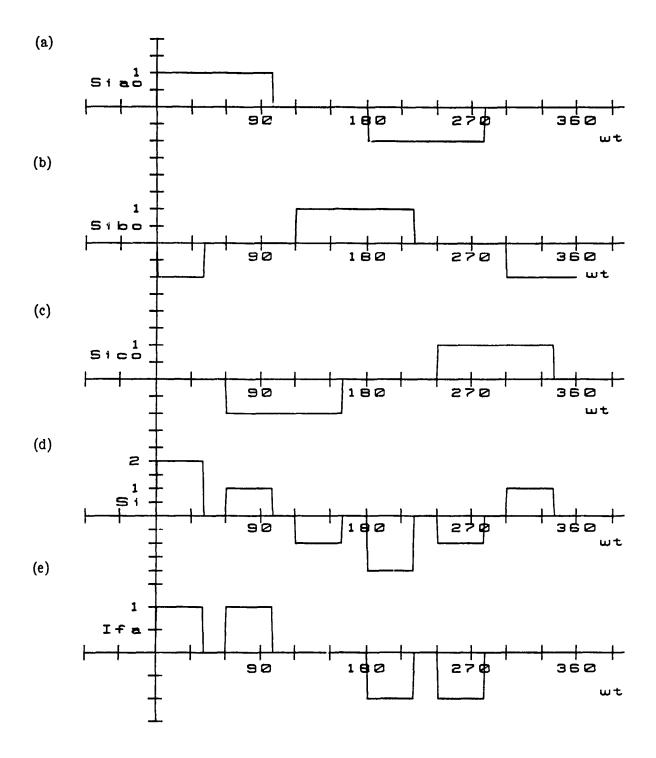

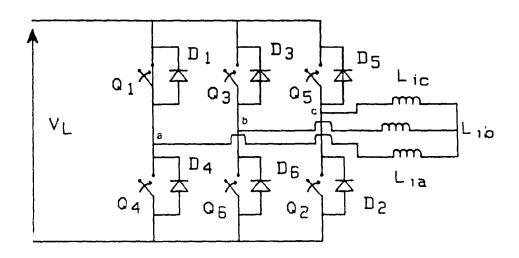

|           | waveforms                                                        | 92  |

| Flg. 3.20 | Equivalent circuits during the boost switch $(S_{wb})$           |     |

|           | operation                                                        | 96  |

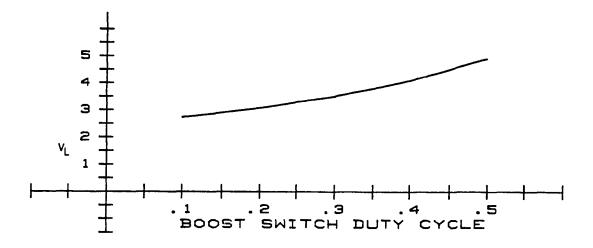

| Flg. 3.21 | Variation of minimum dc output voltage ( $V_L$ ) with the        |     |

|           | boost switch duty cycle                                          | 100 |

| Flg. 3.22 | Variation of power factor (without input filter) with boost      |     |

|           | switch duty cycle                                                | 100 |

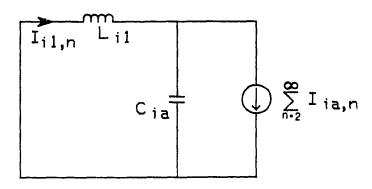

| Flg. 3.23 | Single-phase equivalent circuit for input filter design          | 106 |

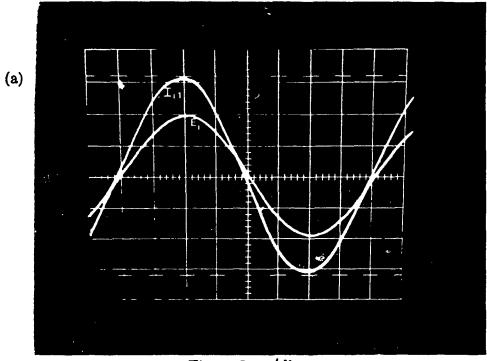

| Flg. 3.24 | Experimental waveforms of the proposed three-phase ac-           |     |

|           | to-dc SMR converter                                              | 112 |

| Fig. 3.25 | Proposed synchronous rectifier fed three-phase ac-to-dc              |     |

|-----------|----------------------------------------------------------------------|-----|

|           | converter                                                            | 113 |

| Flg. 3.26 | Proposed synchronous active filter topology simulated                |     |

|           | waveforms                                                            | 110 |

| Fig. 3.27 | Single-phase equivalent circuit of the synchronous front-            |     |

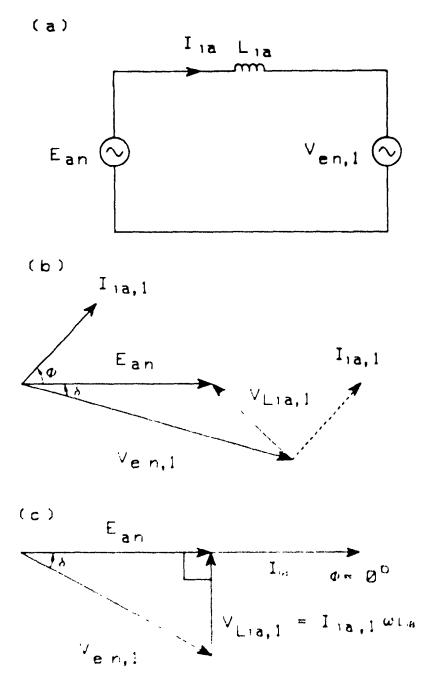

|           | end rectifier section and phasor diagrams                            | 12  |

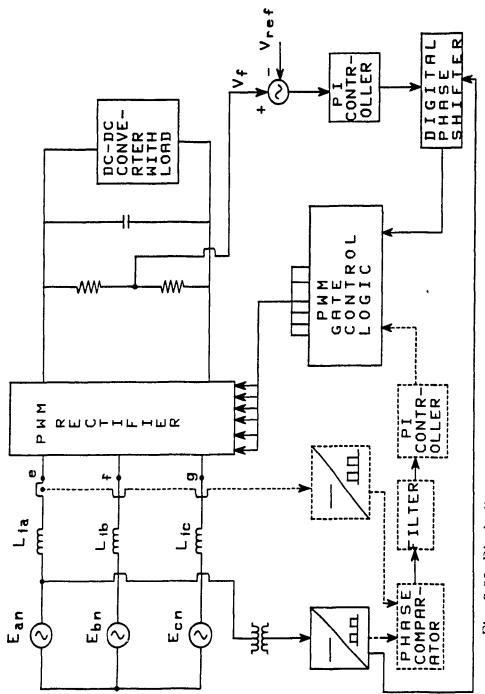

| Fig. 3.28 | Block diagram of the overall SMR unit which includes the             |     |

|           | control loops required to ensure unity input power factor            |     |

|           | and output voltage regulation                                        | 124 |

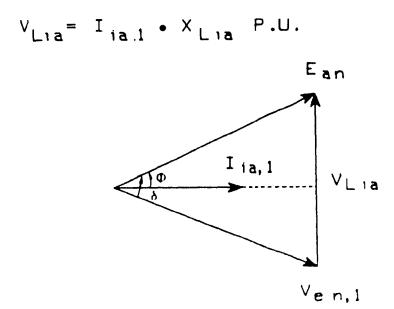

| Fig. 3.29 | Phaser diagram for voltages and currents identified in Fig.          |     |

|           | 3.27(a) by setting $E_{an} = V_{en,1}$                               | 125 |

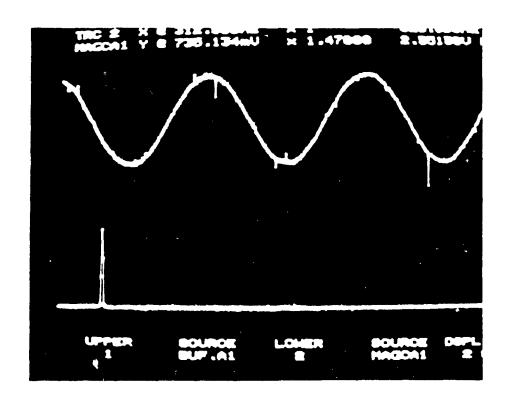

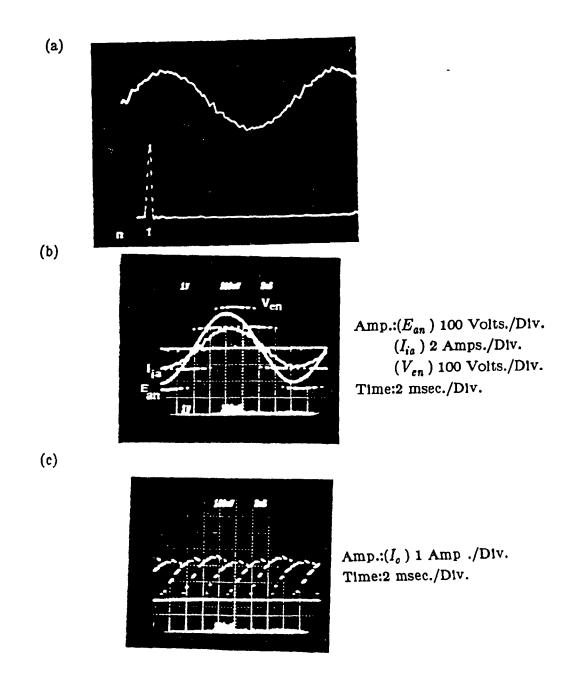

| Fig. 3.30 | Experimental waveforms of the proposed synchronous                   |     |

|           | rectifier                                                            | 138 |

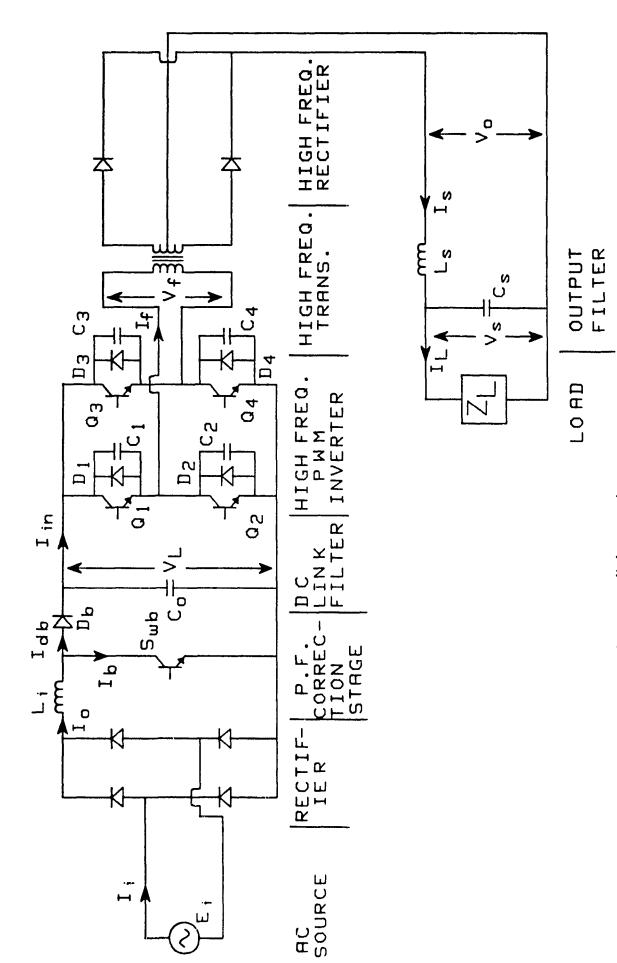

| Fig. 4.1  | Single-phase high frequency link converter                           | 141 |

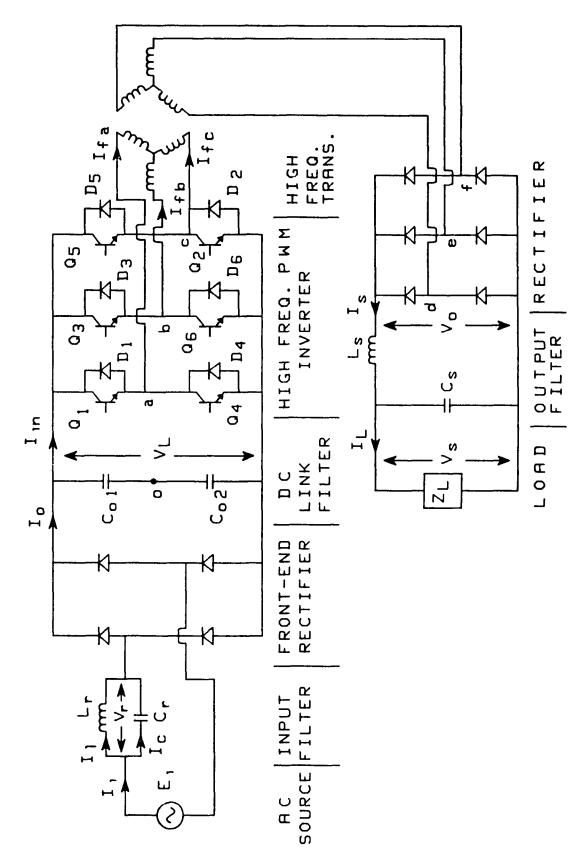

| Flg. 4.2  | Proposed synchronous rectifier fed three-phase ac-to-dc              |     |

|           | converter                                                            | 144 |

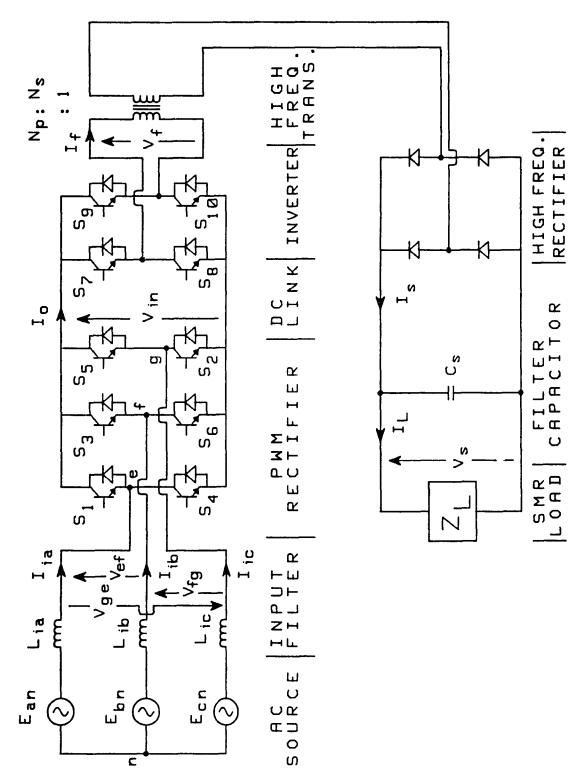

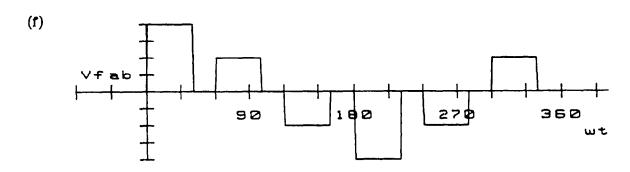

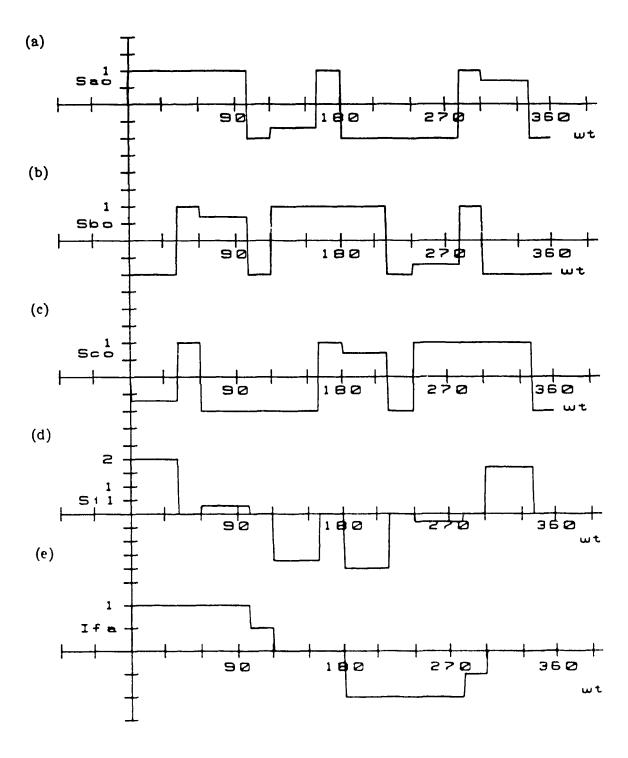

| Fig. 4.3  | Three-phase high frequency link converter                            | 145 |

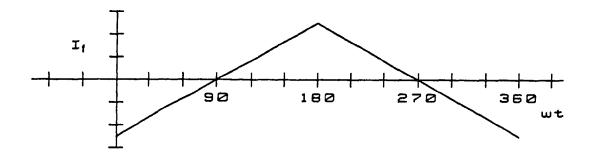

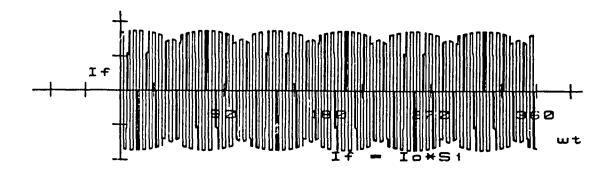

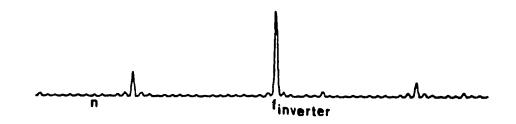

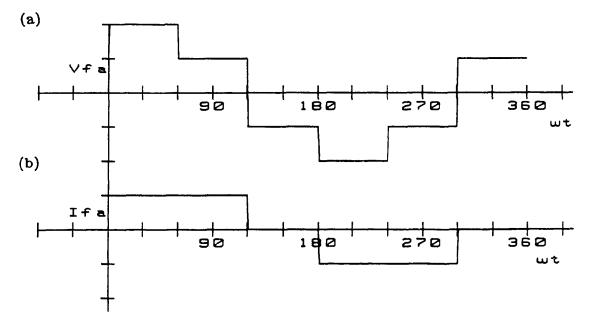

| Flg. 4.4  | High frequency transformer primary voltage, $\boldsymbol{V_f}$ , and |     |

|           | current, $I_f$                                                       | 148 |

| Flg. 4.5  | High frequency transformer primary current ( $I_f$ ) at no           |     |

|           | load                                                                 | 152 |

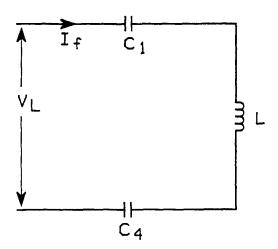

| Flg. 4.6  | Equivalent circuit during turning-off of a transistor                | 154 |

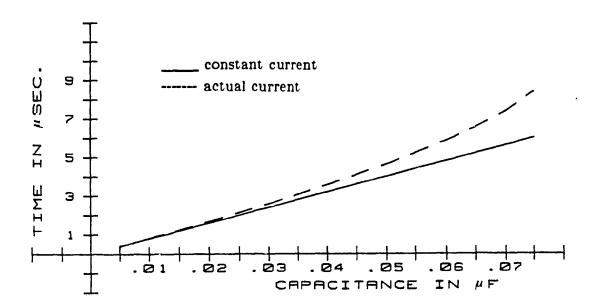

| Fig. 4.7  | Snubber capacitor versus dead time between inverter com-             |     |

|           | plementary switches gating signals at 20 kHz                         | 156 |

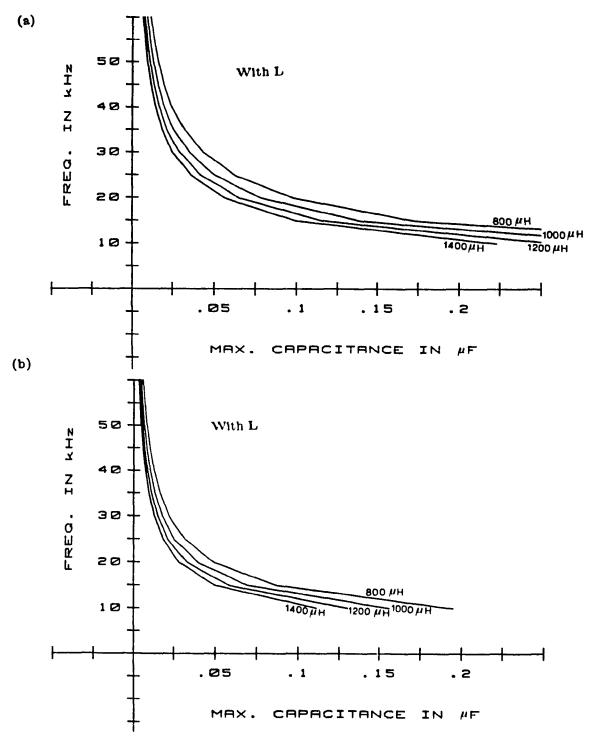

| Flo 4 8   | Maximum snubber canacitance Versus inverter operating                |     |

. . .

|           | frequency                                                          | 157 |

|-----------|--------------------------------------------------------------------|-----|

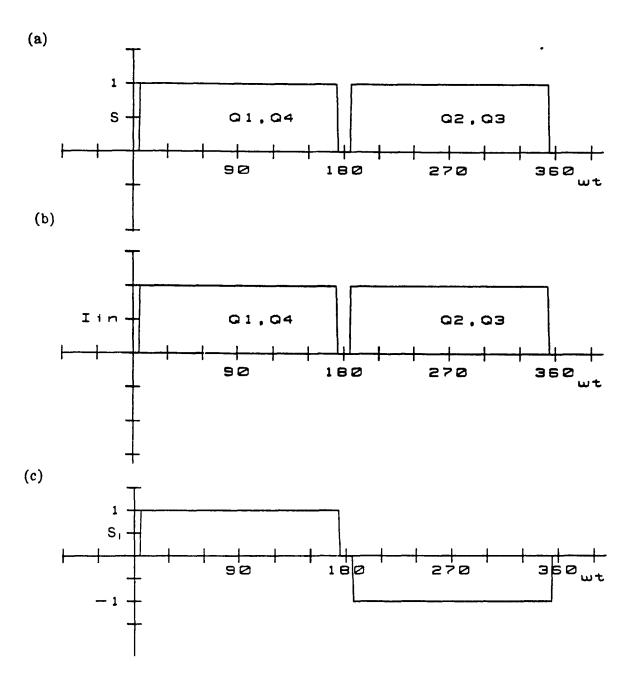

| Flg. 4.9  | Simulated waveforms and the equivalent circuit for the             |     |

|           | output filter design                                               | 159 |

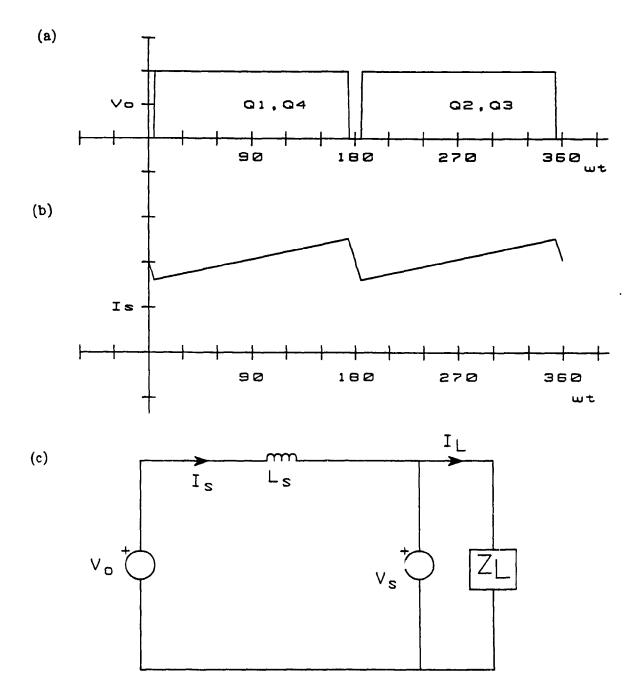

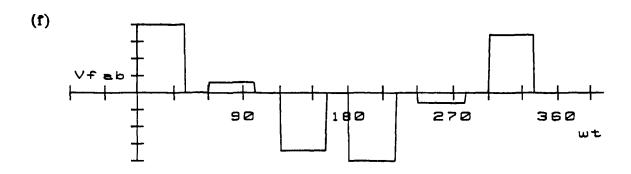

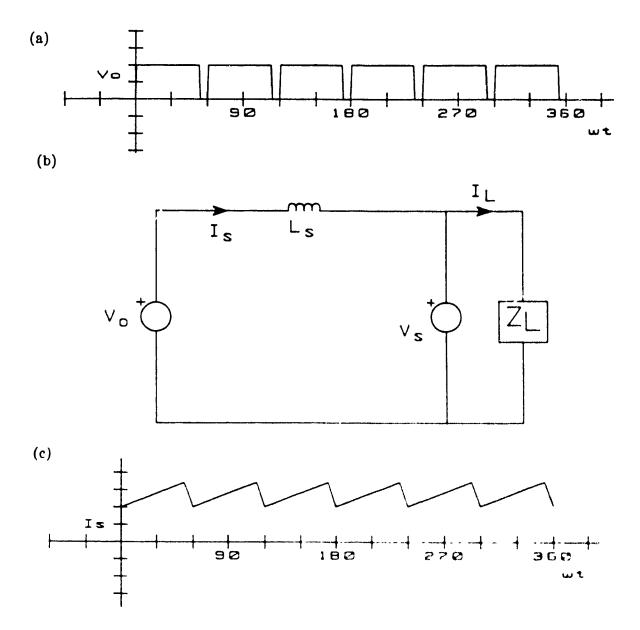

| Flg. 4.10 | Proposed inverter and high frequency link simulated                |     |

|           | waveforms                                                          | 161 |

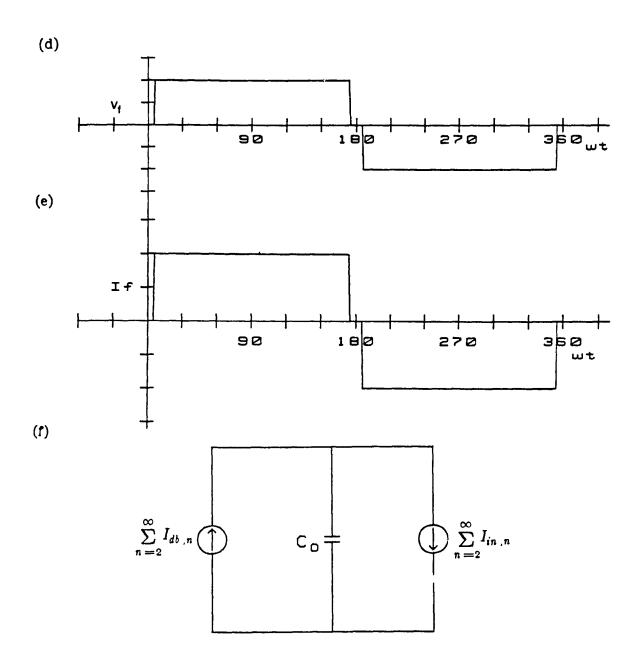

| Fig. 4.11 | Experimental waveforms of the proposed inverter opera-             |     |

|           | tion                                                               | 167 |

| Fig. 4.12 | Proposed synchronous rectifier fed HFL converter simu-             |     |

|           | lated waveforms                                                    | 171 |

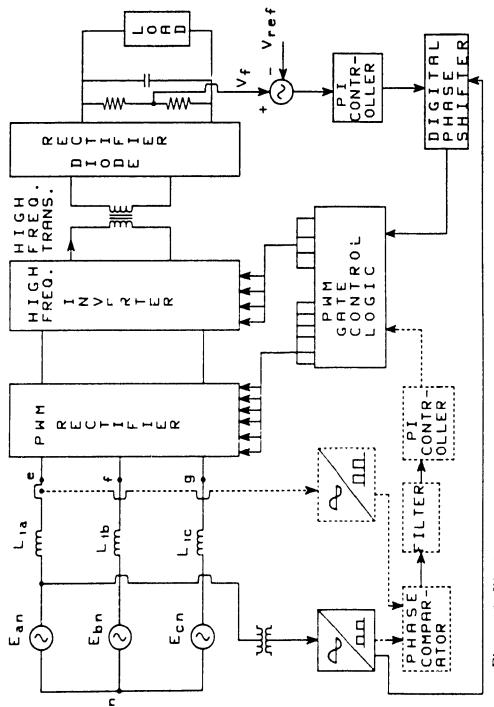

| Fig. 4.13 | Block diagram of the overall SMR unit which includes the           |     |

|           | control loops required to ensure unity input power factor          |     |

|           | and output voltage regulation                                      | 174 |

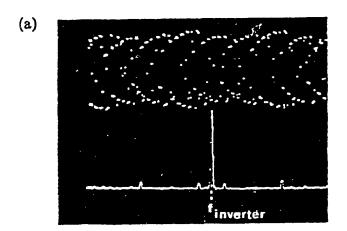

| Flg. 4.14 | Experimental waveforms of the proposed synchronous                 |     |

|           | converter                                                          | 183 |

| Fig. 4.15 | Three-phase high frequency link SMR converter simulated            |     |

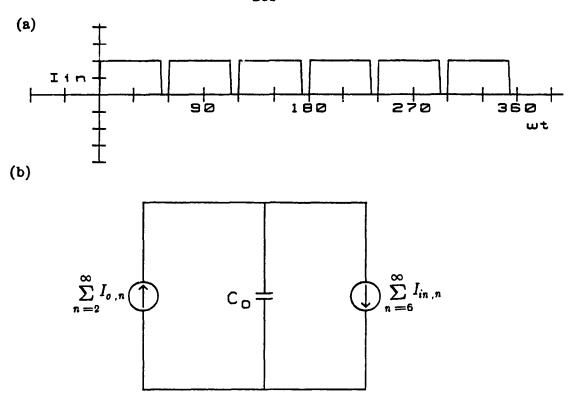

|           | waveforms                                                          | 187 |

| Fig. 4.16 | Three-phase inverter and high frequency link simulated             |     |

|           | waveforms under zero line inductance                               | 189 |

| Fig. 4.17 | Equivalent high frequency link circuit during free-wheeling        |     |

|           | period                                                             | 192 |

| Fig. 4.18 | Three-phase inverter and high frequency link simulated             |     |

|           | waveforms under small line inductance                              | 194 |

| Fig. 4.19 | Simulated waveform and equivalent circuit for the output           |     |

|           | filter design                                                      | 198 |

| F10 420   | Three-phase inverter input current, $I_{\gamma}(\omega t)$ and the |     |

### List of Tables

|           |                                                        | Page |

|-----------|--------------------------------------------------------|------|

| Table 2.1 | Comparative ratings of passive waveshaping methods     | 47   |

| rable 3.1 | Comparative ratings of single-phase waveshaping        |      |

|           | methods                                                | 78   |

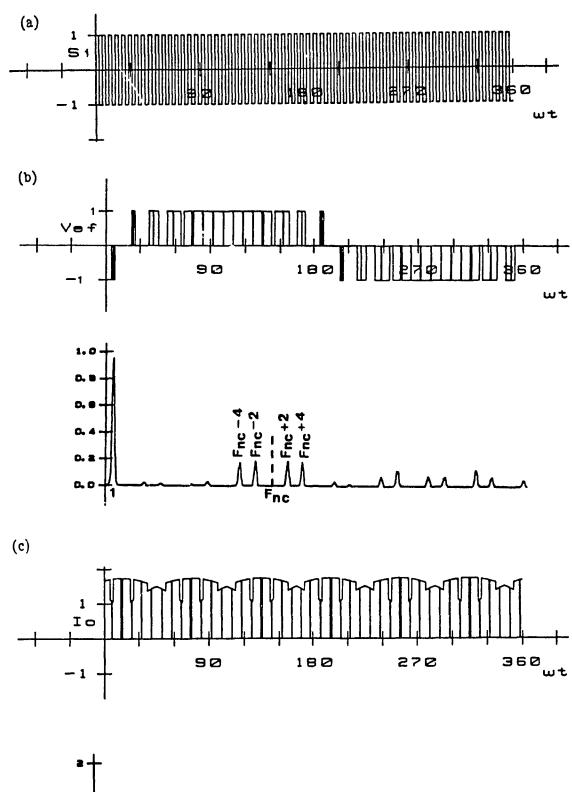

| Table 3.2 | Frequency spectrum of the rectlfier switching function |      |

|           | •••••                                                  | 128  |

### List of Acronyms

HCBR Half-Controlled Bridge Rectifier

HFL High Frequency Link

HFT High Frequency Transformer

PF Power Factor

PWM Pulse Width Modulation

SMR Switch Mode Rectifier

THD Total Harmonic Distortion

VA Volt-Ampere

TVA Total Volt-Ampere

### List of Principal Symbols

| Amplitude of the carrier signal                          |

|----------------------------------------------------------|

| Amplitude of the reference signal                        |

| Dc link high frequency capacitor                         |

| Input ac filter capacitor of single-phase SMR converter  |

| Three-phase SMR converter input ac filter capacitors     |

| De link filter capacitor                                 |

| Resonant ac filter capacitor                             |

| SMR output filter capacitor                              |

| Duty cycle of the boost switch                           |

| Order of the dominant harmonic component                 |

| RMS value of the ac input voltage $(E_i)$                |

| Three-phase SMR converter input ac source phase voltages |

| Peak value of the input ac voltage $E_{\it an}$          |

| Input ac voltage of single-phase SMR converter           |

| Carrier frequency                                        |

| Normalized carrier frequency                             |

| Switching frequency of the inverter                      |

| Boost switching frequency                                |

| Resonant capacitor ( $C_r$ ) current                     |

| Current through the front-end rectifier dlode            |

|                                                          |

| $I_{db}$                             | Boost diode current                                               |

|--------------------------------------|-------------------------------------------------------------------|

| $I_{db,0}$                           | Average dlode current through the dlode $D_{\it b}$               |

| $I_{d,0}$                            | Average current through the front-end rectifier diode             |

| $I_{d,peak}$                         | Peak current through the front-end rectifier diode                |

| $I_{d,rms}$                          | RMS current through the front-end rectifier diode                 |

| $I_f$                                | High frequency transformer primary current                        |

| $I_{fa}$ , $I_{fb}$ , $I_{fc}$       | Three-phase high frequency link line currents                     |

| $I_i$                                | Input ac current of single-phase SMR converter                    |

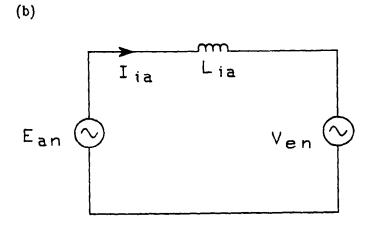

| $I_{ia}$ , $I_{ib}$ , $I_{ic}$       | Three-phase SMR converter front-end rectifier input currents      |

| Iia (peak)                           | Peak value of the current $I_{ia}$                                |

| Iian (rms)                           | RMS value of $I_{ian}$                                            |

| $I_{ia,n}$ , $I_{ib,n}$ , $I_{ic,n}$ | Amplitudes of the $n^{th}$ harmonic components of currents        |

|                                      | $I_{ia}$ , $I_{ib}$ , $I_{ic}$                                    |

| $I_{ia,1(\tau ms)}$                  | RMS value of the fundamental component of current $I_{ia}$        |

| $I_{i,n}$                            | Amplitude of the $n^{th}$ harmonic component of the current $I_i$ |

| $I_{i,peak}$                         | Peak value of current $I_i$                                       |

| $I_{i,rms}$                          | RMS current of $I_i$                                              |

| $I_{i1}, I_{i2}, I_{i3}$             | Three-phase SMR converter input ac currents                       |

| $I_L$                                | SMR dc load current                                               |

| $I_l$                                | Resonant inductor $(L_r)$ current                                 |

| $I_o$                                | Front-end rectifier output current                                |

| $I_{o,0}$                            | Average rectifier output current                                  |

| $I_{o,n}$                            | Amplitude of the front-end rectifier output current $n^{th}$ har- |

### monic component

| RMS current through the inverter switch                       |

|---------------------------------------------------------------|

| SMR output current before filtering                           |

| Amplitude of the $n^{th}$ harmonic component of current $I_s$ |

| RMS value of the $n^{th}$ harmonic component of current $I_s$ |

| Three-phase high frequency transformer equivalent leakage     |

| inductances referred to primary                               |

| DC link filter inductor                                       |

| Three-phase SMR converter inductors                           |

| Three-phase SMR converter input ac filter inductors           |

| Single-phase high frequency transformer leakage inductance    |

| referred to primary                                           |

| Single-phase high frequency transformer magnetizing induc-    |

| tance                                                         |

| Resonant ac filter inductor                                   |

| Modulation factor of the PWM method                           |

| Number of turns on the transformer primary winding            |

| Number of turns on the transformer secondary winding          |

| Order of the $n^{th}$ harmonic component                      |

| SMR output power                                              |

| Front-end rectifier output power                              |

| Overall switching function of the high frequency inverter and |

| rectifier stages                                              |

|                                                               |

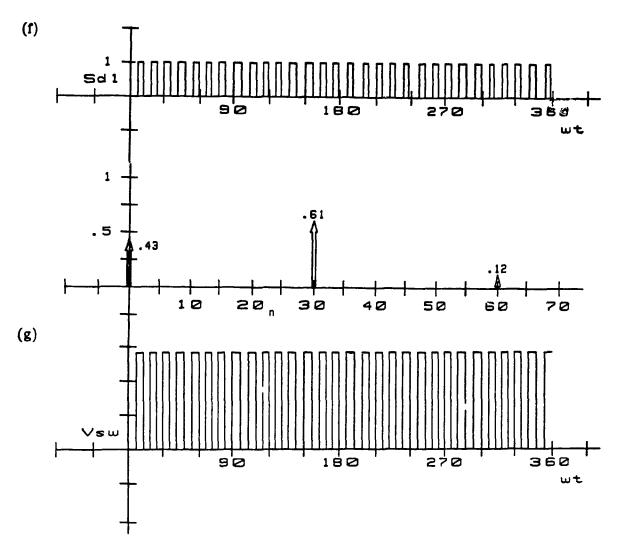

| $S_d$                            | Switching function of the front-end three-phase diode        |

|----------------------------------|--------------------------------------------------------------|

|                                  | rectifier                                                    |

| $S_{d1}$                         | Switching function of the boost diode $(D_b)$                |

| $S_i$                            | Switching function of the inverter stage                     |

| $S_{i1}$                         | Three-phase inverter stage switching function under small    |

|                                  | line inductance                                              |

| $S_{wb}$                         | Boost switch                                                 |

| $T_c$                            | Period of the carrier signal                                 |

| $T_f$                            | Period of the reference signal                               |

| $T_s$                            | Inverter operating time period                               |

| $T_{sw}$                         | Boost switch average operating time period                   |

| $t_{on}$                         | Boost switch 'on' time                                       |

| $t_{off}$                        | Boost switch 'off' time                                      |

| $\overline{t_1}$                 | Average 'on' time of the boost switch                        |

| $\overline{t_2}$                 | Average 'off' time of the boost switch                       |

| $V_{en}$                         | Reflected front-end rectifier input phase voltage            |

| $V_{en,1}$                       | Amplitude of the fundamental component of the reflected      |

|                                  | front-end rectifier input voltage                            |

| $V_{en,d}$                       | Amplitude of the dominant harmonic component of $V_{\it en}$ |

| $V_f$                            | High frequency transformer primary voltage                   |

| $V_{fab}$ , $V_{fbc}$ , $V_{fc}$ | Three-phase high frequency link line-line voltages           |

| $V_G$                            | Gating signal for boost switch                               |

| $V_{in}$                         | Front-end rectifier output voltage                           |

| $V_L$             | DC bus voltage                                                  |

|-------------------|-----------------------------------------------------------------|

| $V_{L(min)}$      | Minimum de bus voltage                                          |

| $V_{r}$           | Voltage across the resonant link                                |

| $V_s$             | SMR output voltage                                              |

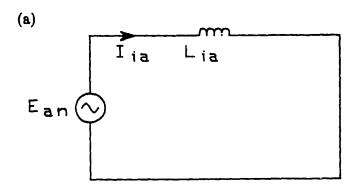

| $V_{sw}$          | Inverter switch peak forward voltage                            |

| $V_{s,o}$         | SMR output de voltage                                           |

| $X_{Cr}$          | Impedance of the $C_r$ at fundamental input frequency           |

| $X_{C \ ia \ ,1}$ | Impedance of the $C_{ia}$ at fundamental input frequency        |

| $X_{L r}$         | Impedance of the $L_{	au}$ at fundamental input frequency       |

| $X_{L \ ia \ ,1}$ | Impedance of the $L_{ia}$ at fundamental input frequency        |

| $Z_n$             | Equivalent $n^{th}$ harmonic impedance of the input resonant    |

|                   | filter                                                          |

| δ                 | Phase angle between the input ac phase voltage and $V_{\it en}$ |

| $\phi$            | Input power factor angle                                        |

| $\phi_1$          | Phase angle between the input fundamental ac input voltage      |

|                   | and the fundamental component of the current                    |

| $\omega$          | Angular frequency of the input ac source at fundamental fre-    |

|                   | quency                                                          |

| $\omega_n$        | Angular frequency of oscillation of the inductor and capaci-    |

|                   | tor                                                             |

| $\omega_s$        | Angular frequency of the inverter output frequency              |

### CHAPTER 1

### Introduction

### 1.1 General Introduction

Today, a large number of power conversion equipment produced for telecommunication, military, and space applications are of either thyristor controlled or ferro-resonant design. In both cases the frequency of conversion is 60 Hz. This results in units that are relatively heavy, large, and noisy. The silicon controlled rectifier (SCR) may not be on its way out, but it is certainly being challenged by a number of new semiconductor devices. Among the new devices are the high-power bipolar-junction transistor (HPBT), the power MOS field-effect transistor (MOSFET), the gate turnoff (GTO) thyristor, and the insulated-gate bipolar transistor (IGBT). More efficient, easier to control, and switching faster than the SCR, they are replacing that old standby power supply in a variety of applications. As the new devices become available in more impressive voltage and current ratings, they are bringing about a quiet revolution for the electrical industry. Designers have embraced their broad usefulness for such diverse tasks as switching and uninterruptible power supplies, electronic ballasts for fluorescent lighting, induction heating and welding, automotive power systems, appliances, drives equipment ranging from robots to railroad locomotives, and adjustable speed drives for brushless de motors and induction motors.

All these new devices function as controlled switches, processing power in conditioning circuits to match the source with the requirements of the load: dc to dc or ac, ac to ac or dc. The high switching frequency means more

circuits can be accommodated into a given space, making power-conditioning systems more compact, since size of inductors, transformers and capacitors needed for filtering and energy storage in such systems shrinks as frequency increases. The high switching frequency also brings faster system response than can be achieved with SCRs.

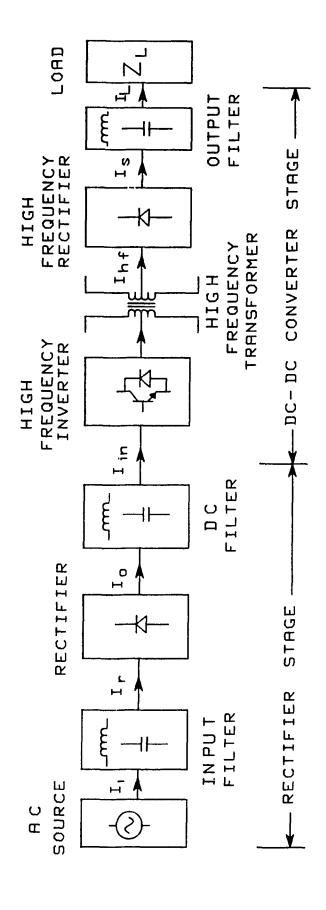

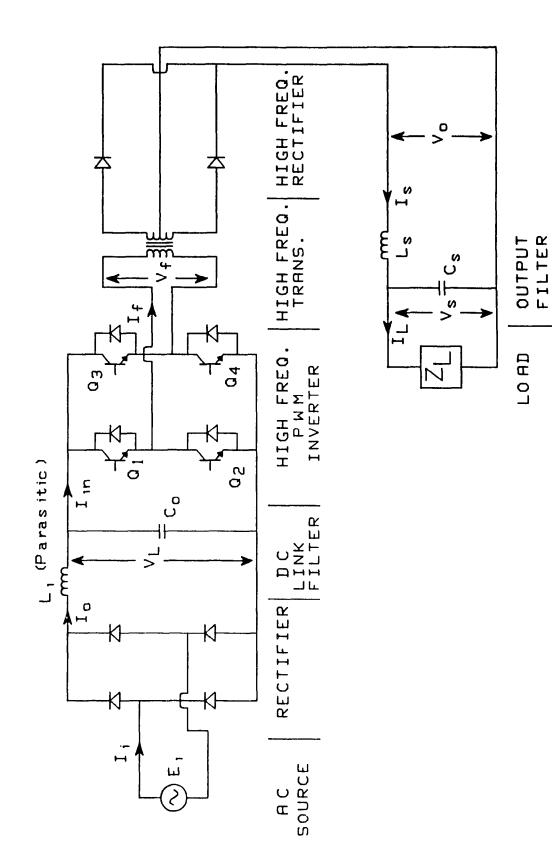

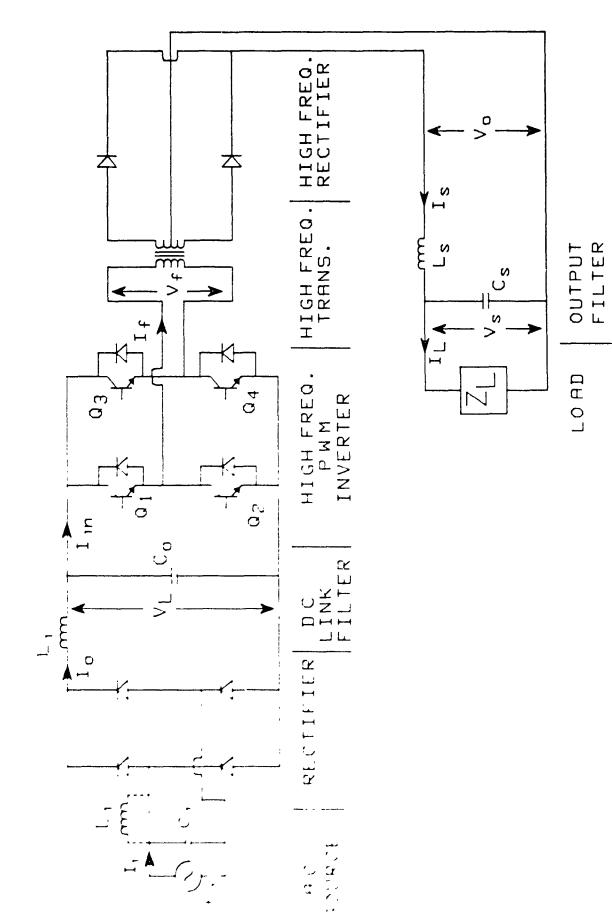

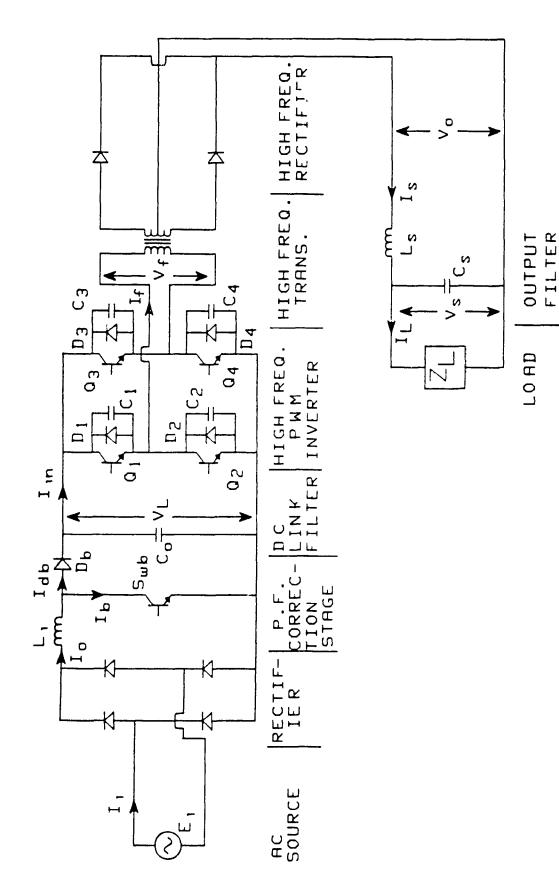

The main design objective in any high frequency ac-to-dc switch-moderectifier (SMR) converter is the minimization of the converter's size and weight while maintaining acceptable component stresses and providing isolation for safety and load matching. Furthermore, control of the output voltage is essential in most power supply systems either to compensate for input source voltage variations and internal regulation or because the load demands adjustable voltage or both. Consequently, SMR converters consist of two main power conversion stages as shown in Fig. 1.1. The first stage is an acto-dc rectifier fed from a single-phase or a three-phase ac source. The second stage is a dc-to-dc converter with a high frequency transformer. An increase In the switching frequency is used for size reduction because the volume of the converter depends mainly on the size of the magnetic components and associated filter capacitors. To increase the switching frequency, the switching losses of the power switching device should be minimized to prevent overheatlng. There are two methods to increase the switching frequency. One is to make use of high speed switching devices and are called Switch mode rectifier (SMR) converters. These SMR converters directly rectify the 60-Hz utility voltage, invert at high frequency, transformer couple, and rectify the load voltage. The advantages of these systems are small size, light weight and high efficiency. These circuits generally operate at fixed frequency and control the load voltage by multi-pulse pulse-width-modulation (PWM) of the inverter switching devices. The switching device current and voltage can be

Fig. 1.1: Block dlagram of an ac-to-dc SMR converter

approximated by rectangular pulses. The main disadvantage of the SMR converter is the nature of the pulsed current being drawn from the input ac source. This pulsed input current creates number of problems for the power distribution network. These problems are explained later in this chapter.

A second form of high frequency inverter incorporates reactive elements (capacitors and reactors) in conjunction with the switching devices to form a resonant inverter. These circuits control the output voltage by varying the operating frequency of the power semiconductor switches. The advantages of these circuits are low semiconductor switching losses and sinusoidal waveforms. However, resonant converters exhibit increased component count, increased switching stresses (peak current, rms current), and require wide operating frequency variations in order to maintain constant output voltage under large variations of ac input voltage and load.

In a conventional ac-to-dc SMR converter front end single-phase or three-phase line commutated rectifiers or diode rectifiers are used. These rectifiers are attractive because of their inherent ruggedness and simplicity. They require few power circuit elements and control signals are easily generated by simple circuitry (or, as in case of diode rectifier, none are required). However, these circuits impose certain disadvantages upon the power system design. The output voltage of the rectifier is not pure dc but contains a substantial ripple component. The magnitude of this ripple becomes worse as the rectifier delay angle is increased and a dc filter must generally be included to reduce the effect of this ripple on the other blocks in Fig. 1.1 (i.e. high frequency inverter and transformer). This filter now creates additional problems at the ac input to the rectifier. The input current waveform, due to combined effects from the filter and from phase-control action, becomes quite non-

sinusoidal. Depending upon the particular de filter configuration, the harmonic content of the input current may vary as the phase delay is increased. Furthermore, as the phase delay angle is increased the fundamental component of the input current becomes increasingly phase shifted with respect to the sinusoidal input voltage.

The nonldeal character of the input current drawn by standard rectifier circuits creates a number of problems for the power distribution network and for other electrical systems in the vicinity of the rectifier. Phase displacement of the current and voltage fundamentals requires that the source and distribution equipment (i.e., generators and transmission lines) handle reactive power thus increasing their volt-ampere rating. Similarly, the harmonic currents which the power system is required to provide cause an increase in heating and sometimes in peak current levels in the power distribution system. In addition, the impedance of the distribution network will cause these harmonics to distort the supply voltage, causing increased losses and interference on the other loads elsewhere on the power lines (such as computers, appliances, industrial motors, power line carrier communication systems, and relaying equipment).

These effects are undesirable in any power system and as the use of offline power conditioning equipment becomes more widespread and densely packed, their effect could well be intolerable. It is clear that some form of correction must be used to restrain these problems. In the past, system designers have employed a number of methods to compensate for the poor quality waveforms drawn by the rectifier equipment. These methods include harmonic and reactive compensation by passive elements, multiphase rectification, and active compensation using shunt power converters with a reactive load. All these methods require extra power handling equipment in addition to the basic rectifier (either 60-Hz capacitors and/or magnetics, or a separate power converter). These extra components add size, weight, and cost to the ac-to-dc conversion system and often have a severe effect on the overall system efficiency, since the rms input current is high.

In a conventional ac-to-dc high frequency link (HFL) converter the second stage consists of an inverter, a high frequency transformer, a high frequency rectifier, an output filter and a load. The inverter block shown in Fig. 1.1 generally operates at fixed frequency and controls the output voltage by multi pulse PWM of the inverter switching devices. Consequently the inverter input current harmonics are pushed to higher frequencies. If the dc filter does not contain any inductance, the inverter input current harmonics can degrade further the input current drawn from the ac input voltage. Therefore some inductance is necessary in the dc filter to improve the input current waveshape. If this dc filter inductor value is too high then it will have a negative impact on the associated inverter control strategy. If the inverter input de voltage contains any unwanted harmonics, these harmonics will propagate into the high frequency link through the inverter and degrades the performance of the high frequency transformer. Operating the inverter at higher frequencies essentially reduces the size and cost of the isolation transformer considerably.

This thesis addresses the design of a class of ac-to-dc HFL converters which in addition to generating high quality output dc voltage they draw high quality current wave forms from the ac power source. In contrast to conventional HFL converters by utilizing active means the proposed design draws a nearly sinusoidal line current which is in-phase with the input line voltage

thus operating under unity input power factor conditions. It therefore avoids harmonic interference with other loads which are connected to the same ac power source. Furthermore, reactive currents are kept out of the power system, so that the most efficient use is made of the generation and transmission equipment. This class of converters are intended for use in critical applications, such as telecommunications, substations, and hospitals.

### 1.2 Review of Previous Work

In this section, previous work related to the single-phase and three-phase acto-dc HFL converters is reviewed.

### 1.2.1 Single-Phase Rectiflers

Previous work on single-phase rectifiers can be classified based on the rectifier input current waveshaping method used as a passive and active methods. One of the passive methods frequently used is the diode rectifier with LC filter [1,3]. The maximum input power factor of this method is 0.763. Other passive methods reported in the literature are (1) resonant input filter and (11) ferro resonant transformer [3]. Both of these methods have the advantage of nearly unity input power factor and also the disadvantage of the high cost of the series capacitor and ferro resonant transformer.

On the other hand, active input current waveshaping methods reduce the size of the rectifier and maintain nearly unity input power factor [3, 12-15,48]. With these methods the dc filter inductor current emulates the ac source voltage and is referred to as a resistor emulator. The disadvantages of this

method are that the switching frequency of the rectifier is load dependent and also that it requires a means of sensing and processing the input ac voltage.

Ohnishi and Okitsu [19] investigated the power factor improvement by means of bias voltage control. In this case the rectifier input voltage is obtained by subtracting the bias voltage from the source voltage. A transformer has been used to give the bias voltage by the output voltage across the load. The cost of the additional transformer and diode bridge makes this scheme not very attractive.

Stihl and Ool [15] investigated the improvement of input current waveform by hysteresis control. In this method all the diodes are replaced with transistors and feed back diodes. If regeneration is not an issue then the rectifier with a diode bridge and a single active switch for chopping is likely to be cheaper. It also has the disadvantages mentioned above for active methods.

Finally Manlas et al. [10], investigated the improvement of the input power factor using a synchronous front end reactor. This method yields nearly unity input power factor using PWM control methods and forces the unwanted harmonic component to higher frequencies. However, it has the disadvantage of complementary switch anti-parallel diode conduction before the transistor turns on and requires the use of at least four additional switches.

### 1.2.2 Three-Phase Rectiflers

Forced commutated rectifiers are chosen in order to eliminate the drawbacks of the traditional line commutated rectifier. Hence, the application of PWM control methods to rectifiers is of great interest. However, mainly because of the ruggedness of the line commutated rectifier, PWM rectifiers have attracted little attention in comparison to PWM inverters.

Ziogas et al. [22], investigated the performance of the PWM rectifier. The input and output filter component sizes are reduced by forcing the unwanted harmonics to higher frequencies. However it has the disadvantage of requiring both input and output filter components, which increases the component count.

Malesani and Tenti [23] investigated the PWM converter analysis to obtain the sinusoidal ac line currents with minimum filter requirements. In this method line currents are forced to emulate the input ac source voltage waveform. However the switching frequency of the converter is load dependent.

Ool et al. [24], investigated the controlled-current PWM converter to obtain the leading power factor. In this method the ac line currents are forced to be within the narrow band of the reference waveform. However this method also has the disadvantage that the switching frequency is load dependent.

The active input power factor improvement method for three-phase rectifiers has been reported in several references [4, 12-14]. In all these references three single-phase rectifiers with active power factor correction method are used with suitable input and output connections. This type of input power factor correction methods exhibits increased component count, and requires complicated input synchronization logic.

### 1.2.3 DC-DC Converters

For low output power levels the conventional buck, boost, and buck-boost circuits are more economical [16,28]. As the output power level increases, the pulsating either input and/or output current of the buck, boost and buck-boost converters requires large either input and/or output filters.

Stelgerwald [11] investigated the performance of high frequency resonant dc-dc converters. However output voltage is controlled by varying the switching frequency of the inverter. This type of output voltage control is not efficient in applications such as these ones considered in this thesis where input ac voltage and load are expected to vary widely.

Jeff Shortt et al. [16], investigated the use of a multi-stage phase-shifted-parallel dc-to-dc converter for reducing the size of the filter components. However this scheme increases significantly the component count and therefore is not of much practical interest.

Al Haddad et al. [43], investigated the resonant dc-dc converter using dual thyristors. In this converter high efficiency of operation is obtained due to the use of lossless snubbers. However this conversion scheme has the disadvantage of requiring wide frequency variation for output voltage regulation.

Manlas et al. [9], proposed the bilateral dc-dc converter using single-phase high frequency link. In this conversion scheme the inverter is operated at high frequency using multi pulse PWM control methods. At low output power levels the proposed converter yields the desired results. However, as the output power level goes up the multi pulse PWM control method becomes less efficient.

The three-phase dc-dc converter was realized by several authors [12,13] using three single-phase dc-dc converters. This method not only increases the component count but it also increases the size of the overall unit.

There has been some previous work reported on the application of dc-dc converters for interfacing a dc source to a utility grid [6,8,47]. In particular Steigerwald et al. [8], investigated the application of high frequency links for interfacing a dc source to a utility grid. Moreover, Rajagopalan et al. [47], investigated the application of dual series resonant converter for utility interface. Also Savary et al. [8], investigated the application of dc-dc converters in photovoltaic array power conditioners. Finally Bhat and Dewan [27] investigated the application of dc-to-dc converter in utility interfaced high-frequency link photovoltaic power conditioning system.

### 1.3 Scope of the Thesis

The previously reviewed ac-to-dc HFL converter topologies can be classified into rectifier and high frequency inverter sections. The input current waveform distortion because of the associated inverter stage operation can be eliminated by proper design of the rectifier output filter inductor and capacitor values. Regarding the front end rectifier stage the disadvantages of existing topologies could be summarized as follows:

- (i) Low efficiency because of large rms value of input current.

- (11) Low Input power factor and contain low order harmonics of considerable amplitude.

- (iii) Input ac mains voltage distortion because of the associated higher peak currents.

- (iv) Interference with other loads.

- (v) Converters are bulky and heavy.

- (vi) Switching frequency is load dependent in active power factor correction method.

- (vii) requires means of sensing and processing the input ac voltage for high input power factor.

However, the power semiconductor industry has been making available more efficient, easier to control and faster switching devices. The objective is to use these new devices to design cheaper, more compact, and more efficient HFL converters which require only few and small passive components. However, because of the aforementioned disadvantages existing ac-to-dc HFL converter topologies cannot be used to achieve these objectives.

The main objective in this thesis is to provide practical and viable solutions to the above mentioned problems including the design of more efficient and reliable ac-to-dc HFL converters capable of maintaining high quality input current and output voltage waveforms.

Moreover, the contributions of this thesis include the analysis and design of single-phase and three-phase fed ac-to-dc HFL converters which maintain high quality input ac current and output dc voltage waveforms while providing the necessary isolation for medium power levels. Different modes of operation of these converters are discussed in detail and design expressions are derived. Finally this thesis also presents for the first time the advantages of introducing three-phase inverters and three-phase transformers in HFL converters to achieve light weight and compact power supplies.

The contents of this thesis have been organized in five chapters as follows.

In Chapter 2, single-phase fed HFL converters with passive input current waveshaping methods have been investigated extensively. Relevant input current and output current waveforms, component ratings, and power factor values have been derived. Different modes of operation are discussed as a means of obtaining high performance. It has been shown that application of the proposed passive input filter topology reduces the size of the reactive components considerably. Finally, predicted results have been verified experimentally on laboratory prototype units.

In Chapter 3, single-phase and three-phase fed HFL converter active input current waveshaping methods have been investigated. It has been shown that application of PWM control method to three-phase diode rectifiers can reduce the size of the SMR converter considerably. Relevant input current and output current waveforms, component ratings, and power factor values have been derived. These methods are next used to control the output voltage of the HFL converters. The different modes of operation of three-phase fed boost active filter topology are analyzed in detail. It has been shown that three-phase and single-phase boost active filter topologies can improve the performance of the converter substantially. Also the proposed synchronous active filter topology controls the output voltage from zero to rated load while maintaining the high input power factor. A laboratory prototype has been built and tested to verify the analytically predicted results.

In Chapter 4, single-phase and three-phase HFL characteristics have been investigated extensively. The commutation of single-phase and three-phase inverters are discussed in detail. The methods of output voltage control in conjunction with the single-phase and three-phase passive and active filter topologies discussed in Chapters 2 and 3 have been presented. The different

modes of operation of three-phase inverter circuits are analyzed in detail. It has been shown that three-phase inverters and three-phase transformers can improve the performance of the converter considerably. It has been shown that converter size can be reduced substantially by eliminating the dc link reactive components. Finally, predicted analytical results have been verified experimentally.

Chapter 5 reviews the entire work presented in this thesis and presents relevant conclusions. It also focuses on future research in the area of SMR converters.

### CHAPTER 2

## Passive Input Current Waveshaping Section

### 2.1 Introduction

Traditionally, conversion of ac line voltages (from utilities or generators) to dc voltages has been done by using a dlode rectifier and a large dc capacitor connected to the rectifier output as shown in Fig. 2.1. Such a conversion approach has the disadvantage of generating pulsed ac line currents drawn from the ac distribution network. As discussed in Chapter 1 the non-ideal character of these input currents creates a number of problems for the power distribution network and for other electrical systems in the vicinity of the rectifier. Shaping of the input current waveforms can be also obtained by using passive reactive components while the output voltage is controlled by a post regulator (dc-to-dc converter). The resulting advantages include more reliability and high input power factor. The object of this chapter is to propose and analyze a novel passive wavesnaping method for single-phase fed acto-dc front-end rectifier which yield high quality input current waveforms, eliminates all the disadvantages discussed in Chapter 1 and exhibits high input power factor values. The passive input current  $(I_i)$  shaping methods generally need more stored energy and hence larger reactive components than active methods.

Fig. 2.1: Conventional SMR converter

4 A 3 L 455 Kg

### 2.1.1 Passive Waveshaping Methods

Power supply systems for low to medium power applications use a frontend single-phase diode rectifier which feeds the respective dc bus capacitors through a very low inductance path (Fig. 2.1). This approach has many disadvantages, including:

- (1) high input current harmonic components;

- (11) low rectifier efficiency because of large rms values of the input current;

- (III) input ac mains voltage distortion because of the associated higher peak currents;

- (iv) maximum input power factor of approximately 0.50 while a larger filter inductor is required for a high input power factor.

In the past system designers have used three passive waveshaping methods to improve the input power factor of a conventional ac-to-dc SMR converter (Fig. 2.1):

- (1) input passive filter method:

- (ii) resonant passive input filter method:

- (ill) ferro resonant transformer method.

All these methods have the advantage of being easy to understand, easy to implement and service, and typically more reliable than active power factor correction methods. A simple way to improve the input current waveform of a conventional diode bridge rectifier (Fig. 2.1) is to place an inductor in series with its output (Fig. 2.2). This method is easy to understand and relatively cheap. The analysis and the design of the diode bridge rectifier with an LC

SAME A STATE WITH BE BY-END PISSIVE BILLY LOPOLOGY ---

filter (Fig. 2.2) have already been discussed in literature [1,3]. This topology is clearly superior to the conventional diode bridge rectifier (Fig. 2.1). For low values of filter inductance  $(L_i)$  the diode bridge rectifier system operates in the discontinuous input current  $(I_i)$  mode and the input current  $(I_i)$  goes to zero before  $\omega t = \pi$ . For sufficiently low values of  $L_i$ , the input current becomes a narrow spike nearly centered in the voltage half-sine wave as shown in Fig. 2.3. The Fourier analysis of such an input current  $(I_i)$ waveform clearly shows the presence of a third harmonic component of considerable amplitude which is the main cause for low input power factor. Consequently, some form of filtering is necessary to remove the third harmonic component from the input current  $(I_i)$  and to improve the input power factor. In other words a larger filter inductor is required to improve the input power factor. However, a larger filter inductor  $(L_i)$  has a negative impact on the associated post regulator control strategy because of increased do source voltage regulation. Improving the input power factor by connecting a capacitor  $(C_i)$  at the input terminals has some disadvantages including:

- low efficiency because of large rms values of the rectifier input current;

- (ii) input ac mains voltage distortion because of the associated rectifier high peak currents.

The second disadvantage is particularly important for office or residential applications. A series resonant filter (Fig. 2.4) is an alternate way to passively shape the input current  $(I_i)$ . When the quality factor and characteristic impedance of the series resonant circuit are both high enough, only currents at the 'notch' frequency can get through to the line and the power factor will be near unity. The major disadvantages of the resonant input filter are the

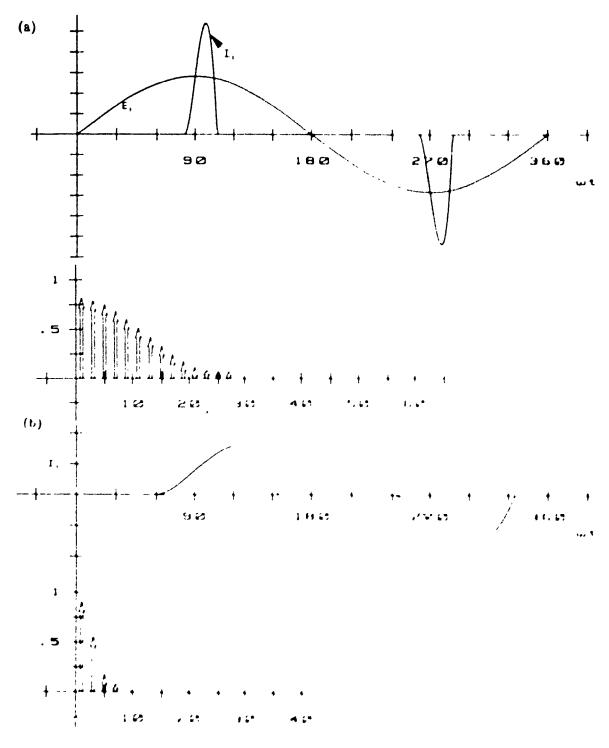

Fig. 2.3. Sitt Pate I wavef ett s

- The Highest cage  $F_{ij}$  by the free  $F_{ij}$  and a specific of even  $G_{ij}$  and  $G_{ij}$

- The displacement of a mentalism aspects on the papers with the second particles.

Fig. 2.4: SMI converter with resonant input filter

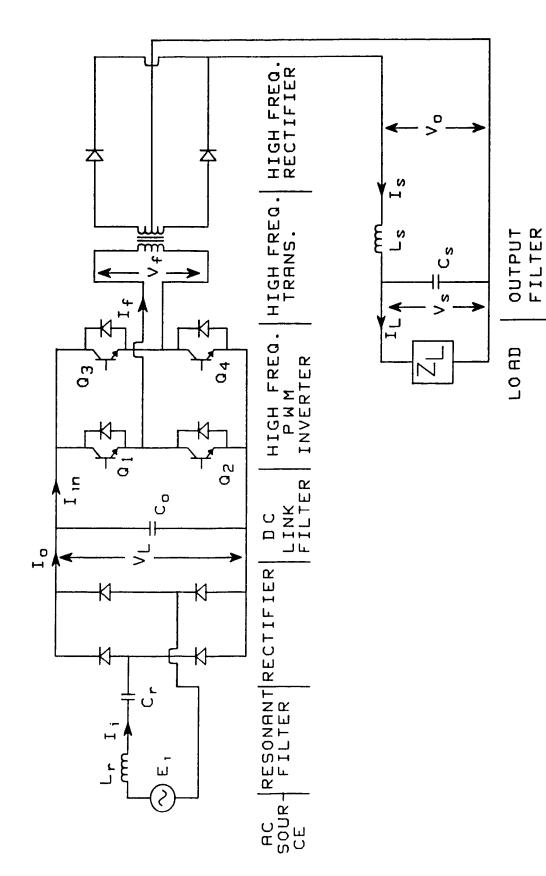

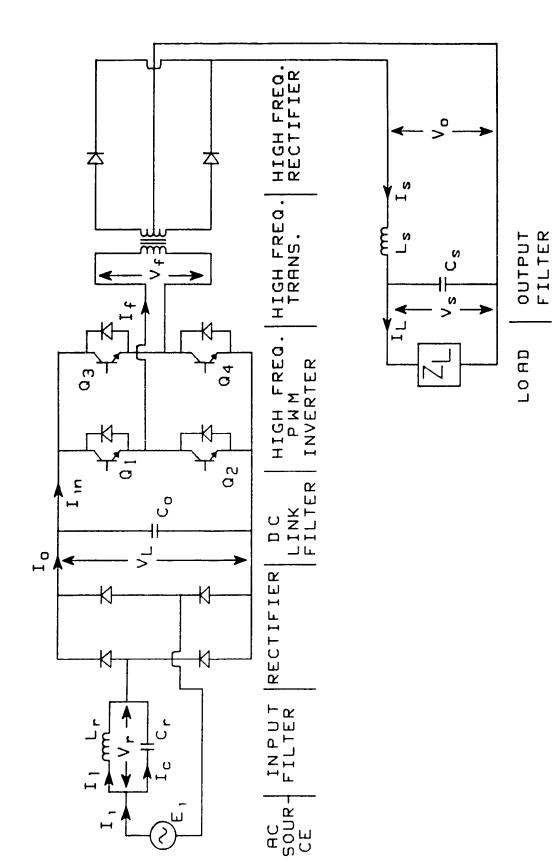

large size of the reactive elements and the large rms currents in the capacitors  $C_0$  and  $C_r$ . The resonant input filter is similar in some ways to the ferro resonant transformer. Like the resonant input filter the ferro resonant transformer is heavy and is considered mainly for its ruggedness. The proposed passive power factor correction method (Fig. 2.5) eliminates all the above disadvantages and improves the input power factor while reducing the size of the passive reactive components. However the proposed passive input current waveshaping method (Fig. 2.5) also has the disadvantage of increased complexity of the operation.

## 2.2 Typical Front-end Passive Filter Topology

The principles of operation of the diode rectifier with input partice filter method (standard diode bridge rectifier Fig. 2.2) are presented in several references [1-3]. Based upon the instant at which the steady state rectifier output current  $(I_0)$  goes to zero, the rectifier system shown in Fig. 2.2 has three  $\psi$  sible modes of operation.

- (1) Discontinuous mode I: The tridge restifier operator in the discontinuous mode I if the steady state output current (I is its entire) ous and goes to zero but relations.

- (II) Discontinuous in the H  $\gamma$  The tritige restrict perate in the  $V\gamma$   $\gamma$  throughout the H M the readout size of  $\mu$   $\gamma$  orders J by the size of courant gives to zero at  $\forall \gamma > t + \tau$ .

- fill Confliction in the III of the things for the operate to the confliction of the confliction of the confliction of the confliction of the confliction.

However the epith of the proposer factor design the the other control of the 20

Fig. 2.5: SMR converter with proposed front-end passive filter topology

the relevant expressions are presented here. The angle,  $\alpha_L$  at which the diodes start conduction is given by  $\sin^{-1}\left[\frac{V_L}{\sqrt{2}E}\right]$ . The input current  $I_i$  in discontinuous mode-I during the period  $\alpha_L \leq \omega t \leq \beta_L$  is given by

$$I_{L}(\omega t) = \frac{\sqrt{2}E}{\omega L_{L}} \left[ \cos(\alpha_{L}) - \cos(\omega t) - m(\omega t - \alpha_{L}) \right]$$

(2.1)

where  $\beta_L$  is the angle at which the input current  $I_i$  becomes zero and  $m=\frac{V_L}{\sqrt{2}E}$ . The performance of the diode bridge rectifier is discussed in the next section.

### 2.2.1 Front-end Rectifier

The analysis of a single-phase fed converter system shown in Fig. 2.2 be based upon the following assumption:

- (i) The filter capacitance ( $C_{\mathfrak{o}}$ ) is assumed to be sufficiently large  $\infty$  that the output voltage ( $V_I$ ) is ripple free constant develtage

- (II) The ac source  $E_i$  is considered ideal

- (III) The losses in inductor  $(L_i)$ , capacity  $r(C_i)$  and the triage resulter are neglected.

- (iv) The load is modeled as a variable restrance three the effect of high frequency ripple is negligible as per accompileto (1).

Moreover, the rated rms as input veltage  $(V_r)$  and rate i resides e at  $V_r$  were  $(P_r)$  are assumed to be

$$P_{s} = 1.0 \text{ pc}$$

In Fig. 2.2 the diode rectifier can operate either in the continuous or discontinuous conduction mode. However a large filter inductor  $(L_i)$  is required in continuous conduction mode to yield a high input power factor. The input power factor of the diode rectifier is calculated from the following expression.

Power Factor =

$$\frac{\frac{I_{i,1}}{\sqrt{2}}}{\sqrt{\sum_{n=1}^{\infty} \left\{\frac{I_{i,n}}{\sqrt{2}}\right\}^2}} \cos(\phi_1)$$

(2.2)

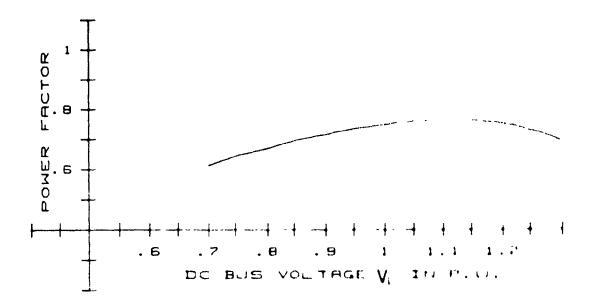

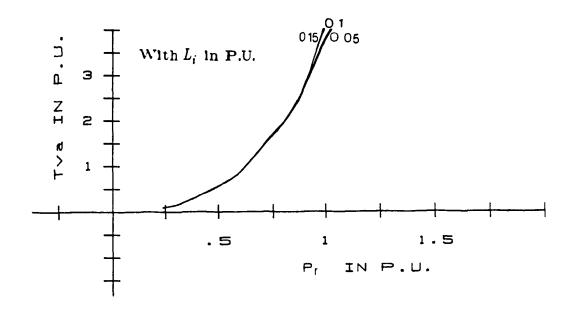

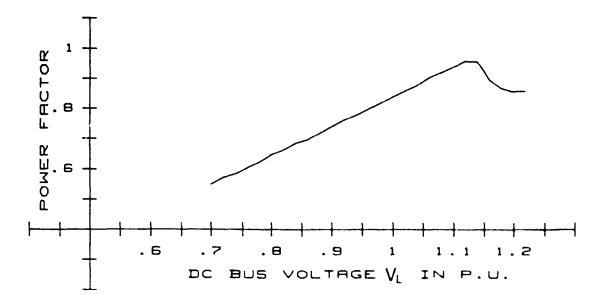

Using Eqn. (2.2) the variation of the input power factor in discontinuous modes-I and II with load voltage  $(V_L)$  is shown in Fig. 2.8. Evidently, the maximum input power factor in the discontinuous mode-I is 0.763. The output power  $(P_r)$  of the bridge rectifier is given by

$$P_r = V_L * I_{0.0} \tag{2.3}$$

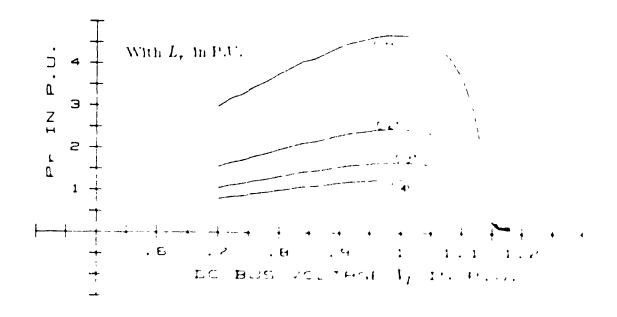

where  $I_{o,0}$  is the average rectifier output current. Using Eqn. (2.3), the variation of the output power  $(P_r)$  is shown (Fig. 2.7) as a function of voltage  $V_L$  for different values of  $L_i$ . From Figs. 2.6 and 2.7 the value of  $L_i$  at maximum input power factor to deliver 1.0 pu  $P_r$  is found to be 0.1 pu.

#### 2.2.2 Rectifier Output Filter

At maximum input power factor the value of the inductor  $(L_i)$  to deliver 1.0 pu output power is 0.1 pu. The amplitude of the second order voltage harmonic component across the rectifier output filter capacitor  $(C_o)$  is given by

$$V_{L,2} = \frac{I_{0,2}}{2\omega C_0} \tag{2.4}$$

Fig. 2.6: Variation of input power factor with ite bus voltage  $(V_I)$

Fig. 2.7. Natiative of computing were  $P_{ij}$  with its the variage  $A_{ij}$  in other than a result  $I_{ij}$

Moreover the allowable inverter input voltage ripple can be defined by

Ripple

$$\% = \frac{100 * V_{L,2(rms)}}{V_{L,0}}$$

Substituting the above equation in Eqn. (2.4) the value of this capacitor is

$$C_o = \frac{100 * I_{o,2}}{\sqrt{2} * V_{L,o} * 2 * \omega * (Ripple \%)}$$

(2.5)

### 2.2.3 Component Ratings

From the aforementioned assumptions and derived analytical expressions the voltage and current rating values of the various system components at maximum input power factor ( $V_L=1.1pu$ ) when  $L_i$  has a value of 0.1 are as follows. The average current ( $I_{d,0}$ ) through the rectifier diode under this condition is given by

$$I_{d,0} = \frac{1}{2\pi} \int_{0}^{\beta} I_{i}(\omega t) d\omega t = 0.4581 \quad pu$$

(2.6)

The rms current  $(I_{d,rms})$  through the diode is given by

$$I_{d,rms} = \frac{I_{i,rms}}{\sqrt{2}}$$

$$I_{d,rms} = \frac{1}{\sqrt{2}} \left[ \sqrt{\sum_{n=1}^{\infty} \left( \frac{I_{1,n}}{\sqrt{2}} \right)^2} \right] = 0.9508 \ pu$$

(2.7)

The peak current  $(I_{d,peak})$  through the dlode is given by

$$I_{d,peak} = \sqrt{\left|\sum_{n=1}^{\infty} (I_{i,n})^2\right|} = 1.901 \ pu$$

(2.8)

where the peak forward voltage of the dlode is 1.414 pu and

the reverse blocking voltage of the diode is 1.414 pu

The rms value of the current through  $L_i$  is 1.345 pu and the peak value of the current through  $L_i$  is 1.901 pu. Moreover because of the discontinuous current mode of operation of the rectifier the filter inductor can be placed on the input ac side as shown in Fig. 2.2 (dotted lines). Therefore the voltampere (VA) ratings of the reactive components are defined as follows: The ac inductor rating is

$$LVA = \sum_{n=1}^{51} \left[ \frac{I_{1-n}}{\sqrt{2}} \right]^2 mX_{L_1}$$

(2.9)

The capacitor rating is

$$CVA = \sum_{n=1}^{61} \left[ \frac{I_{0-n}}{\sqrt{2}} \right]^2 \left[ \frac{X_{C_i}}{n} \right]$$

(2.10)

and the total VA (TVA) is

$$TVA = LVA + CVA \tag{2.11}$$

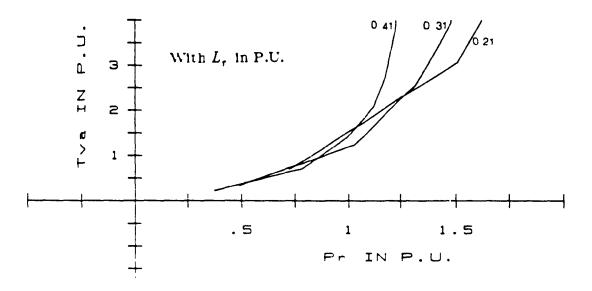

The VA rating of the filter inductor  $(L_i)$  and the value of the output filter capacitor (assuming 5-percent ripple) are calculated using Lqns (2.6) and (2.5). The variation of total VA (TVA) of the reactive components with output power is shown in Fig. 2.8 for different values of  $L_i$ . From Fig. 2.8 the minimum value of TVA to deliver 1.0 puroutput power  $(P_i)$  is 3.8 pm

### 2.2.4 Design Lyangile

To Historie the Significance and validity of the the reliable results obtained in the previous sent on the following teath coarcile in the SMR converter has the following up to active.

Fig. 2.8: Variation of Tva with output power  $(P_{\rm r})$  for different values of  $L_{\rm r}$

$$V_{in} = 208 \text{ rms} \equiv 1 \text{ pu Volts.}$$

$$P_r = 5,000 \text{ W} \equiv 1 \text{ pu Watts.}$$

Output voltage ( $V_L$ ) rlpple = 5%

### From these values

1 pu Current =

$$\frac{5,000}{208}$$

= 24.04 Amps.

1 pu Impedance =  $\frac{208}{24.04}$  = 8.65 Ohms

1 pu Inductance =  $\frac{8.65}{377}$  - 23 mH

1 pu Capacitance =  $\frac{1}{8.65 \cdot 377}$  = 306.65  $\mu$ F

1 pu Angular frequency =  $2\pi f$  = 377 rad./s

From Figs. 2.6 and 2.7 the value of the inductor,  $L_i$  to deliver 1.0 purposed output power is 0.1 purwhich is equal to 2.3 mH. Using the purvalues shown in section 2.2.3 the voltage and current ratings of the rectifier diode and filter capacitor  $C_o$  are as follows:

## Rectifier Diode

Average current,  $I_{d/o}$ : 0.4551 \* 24.04 = -11.01 Amps.

RMS current,  $I_{d \to rns} : 0.95 * 24.04 = -22.84 \text{ Amps.}$

Peak current,  $I_{d-\mathrm{prak}}$  : 1.901 \* 24.04 = 45.7 Amps .

Peak forward voltage:  $\sqrt{2} \cdot 208 = 294.15$  Volt

# DC Filter Inductor L.

Value of the inductor : 0.1 • 23 == 2.3 mH

RMS current: 1 345 + 24 04 - 32 34 Amp.

Peak current: 1 502 \* 24 04 - 45 73 At 1:

# DC Filter Capacitor Co

Peak voltage: 1.12 \* 208 = 232.96 Volts.

120 Hz ripple current,  $I_{o,2}$ : 1.317 \* 24.04 = 31.6 Amps.

Value:  $8.31 * 306.65 = 2549.48 \mu F$

### 2.2.5 Experimental Results

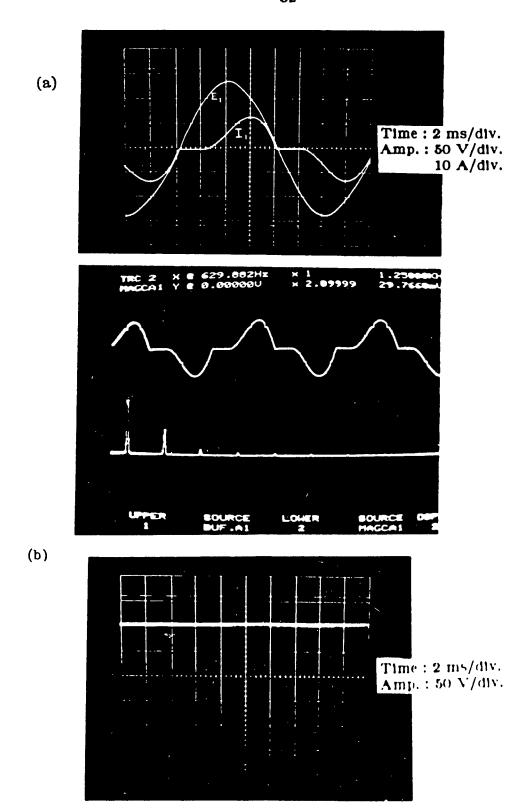

To verify the predicted results a 600 watt experimental SMR has been implemented with the following circuit parameters:

- . AC input rms voltage  $(E_{i(rms)}) = 100$  Volts.

- . Angular frequency of the ac source = 377 rad./sec.

- . Filter inductor  $(L_i) = 8 \text{ mH}$ .

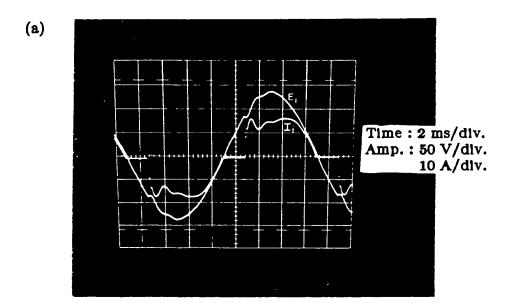

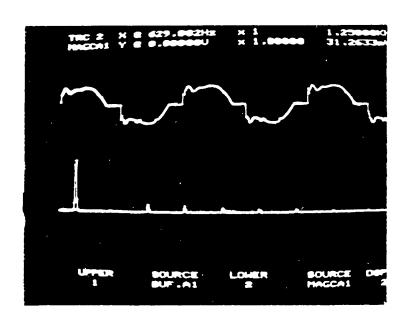

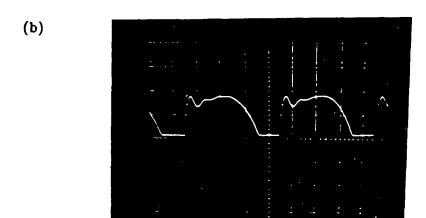

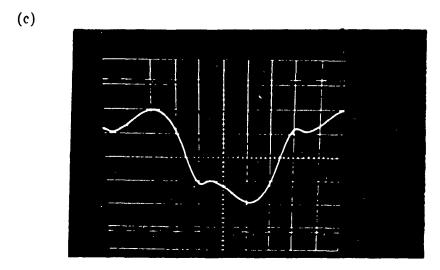

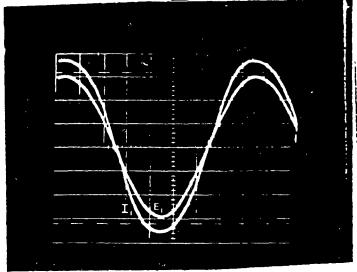

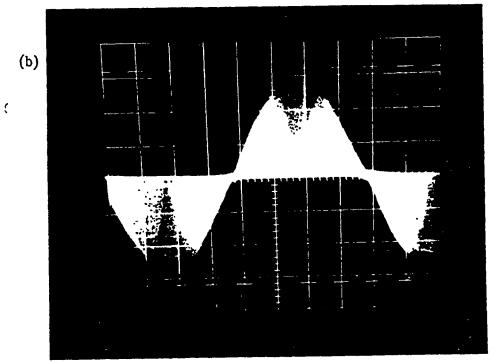

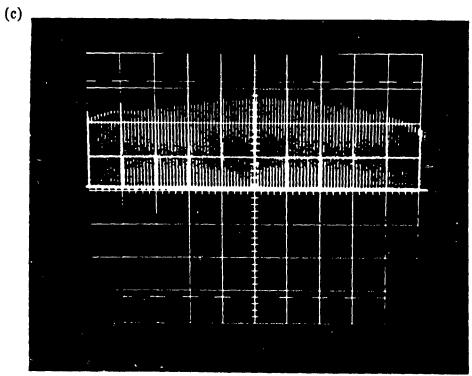

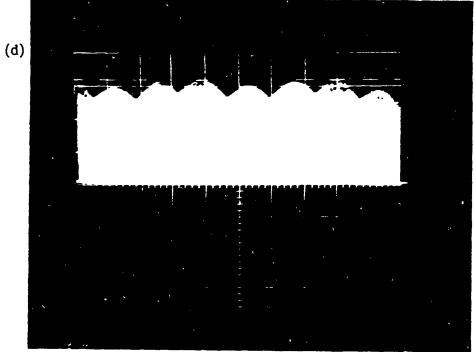

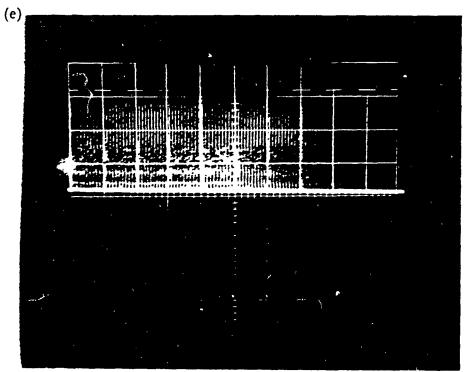

Experimental waveforms of the typical front-end passive filter topology are shown in Fig. 2.9. The input power factor is as follows:

- . AC input rms current  $(I_{i(rms)}) = 8.0$  Amps.

- . Load dc voltage ( $V_L$ ) = 100 Volts.

- . Load dc current  $(I_{in}) = 6$  Amps.

Using the above information the input power factor is given by

$$Power Factor = \frac{100 * 6}{100 * 8.0} = 0.75$$

(2.12)

which is in good agreement with the simulated results shown in Fig. 2.6.

Fig. 2.9: Typical front-end passive filter topology experimental waveform:

(a) Input ac source voltage, input current  $(I_i)$  and its spectrum.

(b) DC bus voltage (  $V_{I}$  )

### 2.2.6 Conclusions

This section has presented the analysis of the front-end input passive filter topology in discontinuous mode of operation. Performance evaluation and related design data were provided for implementation and comparison of the input passive filter topology. Finally, key predicted results were verified experimentally.

# 2.3 Proposed Front-end Passive Filter Topology

For low values of line inductance  $L_i$  the input current of a standard diode rectifier has a third harmonic component (Fig. 2.3) of considerable amplitude which is the main cause for low input power factor. Consequently the proposed passive input filter topology (shown in Fig. 2.5) consists of an input L-C parallel resonant tank whose inductor and capacitor values are selected so that the input filter presents an infinite (theoretically) impedance to the third harmonic input current component. The resulting advantages over the existing passive filter topologies include:

- (1) lower value of input peak current and hence no input voltage distortion;

- (ii) high input power factor;

- (iii) high efficiency because of the low rms values of the input current;

- (Iv) reduced reactive component sizes.

## 2.3.1 Input Filter

The  $n^{th}$  harmonic component of the equivalent impedance of the input parallel resonant filter is given by

$$Z_{n} = \frac{nX_{L_{r}} * \frac{X_{C_{r}}}{n}}{jnX_{L_{r}} - j\frac{X_{C_{r}}}{n}}$$

(2.13)

where

$X_{L_r}$  is the impedance of the input resonant inductor  $(L_r)$  at fundamental frequency.

$X_{C_r}$  is the impedance of the input resonant capacitor  $(C_r)$  at fundamental frequency.

From Eqn. (2.13) the third harmonic impedance of the input resonant filter becomes infinity (theoretically) when

$$3X_{L_i} = \frac{X_{C_i}}{3}$$

or

$$L_{\tau} = \frac{1}{9\omega^2 C_{\tau}} \tag{2.14}$$

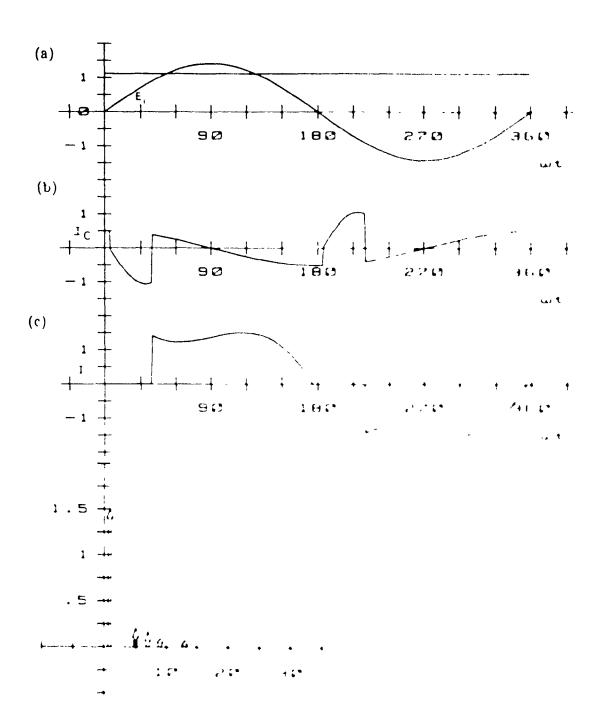

where  $\omega$  is the angular frequency of the input ac source  $(I_{\pm})$ . Based upon the instant at which the steady state rectifier output current  $(I_{\pm})$  goes to zero, the rectifier system shown in Fig. 2.5 has three possible modes of exeration

- (1) Discontinuous mode I: The tridge rectifier operates in the disc not tinuous in de I if the steady state output correct (I h) the attnoous and goes to zero terrors I = 7.

- (the Discontinuous made II). The betage residence per section the mass

tinuous mode II if the steady state output current  $(I_o)$  is discontinuous and goes to zero at  $\pi < \omega t < \pi + \alpha$ .

(iii) Continuous mode III: The bridge rectifier operates in the continuous mode if the steady state output current  $(I_o)$  never falls to zero.

In Fig. 2.5 the angle  $(\alpha)$  at which the diodes start conduction depends upon the voltage,  $V_L$ , and the resonant capacitor voltage,  $V_r$ . The steady state capacitor voltage  $V_r$  can be obtained by considering the initial voltage,  $V_r$ , across the resonating capacitor is zero volts and the initial current,  $I_l$ , through the inductor is zero amperes. During the first positive half cycle of the input voltage  $(E_i)$  wave the angle  $(\alpha)$  at which the conduction starts is given by  $\sin^{-1}(\frac{V_L}{\sqrt{2}E})$ . Where E is the rms value of the input ac voltage  $(E_i)$ . The conduction period  $(\gamma)$  of the rectifier system depends upon the value of the load voltage  $(V_L)$ . Assuming that the input current  $(I_i)$  goes to zero at an angle  $\beta$  and  $\pi < \beta < (\pi + \alpha)$ , then the conduction period is  $\gamma = \beta - \alpha$ . During the period from  $\alpha$  to  $\beta$  the current  $(I_l)$  through the inductor and the current  $(I_l)$  through the capacitor are given by

$$I_{l}(\omega t) = \frac{\sqrt{2}E}{\omega L_{r}} \left[ \cos(\alpha) - \cos(\omega t) - m(\omega t - \alpha) \right]$$

where  $m = \frac{V_{L}}{\sqrt{2}E}$

and

$$I_{c}(\omega t) = \sqrt{2}E * \omega C_{r} * \cos(\omega t)$$

(2.16)

The voltage across the capacitor  $(C_r)$  at the end of the conduction period  $\beta$  is given by

$$V_{r}(\beta) = \frac{1}{C_{r}} \int_{0}^{\beta} I_{c}(\omega t) dt$$

$$= \sqrt{2}E\left[\sin(\beta) - \sin(\alpha)\right] \tag{2.17}$$

At an angle  $\beta$  the input current  $I_r$  goes to zero and the conducting diodes during the positive half cycle of the bridge rectifier system are turned off. During the negative half cycle of the input voltage  $E_r$ , the angle  $(\alpha_1)$  at which the other two diodes start conduction depends upon the value of the capacitor voltage  $(V_r)$ . From  $\beta$  to  $\alpha_1$  the capacitor  $(C_r)$  starts resonating with the inductor  $(L_r)$  and changes its polarity. During the period  $\beta < \omega t < \alpha_1$  the current through the capacitor is given by

$$I_{c}(\omega t) = A \cos(\omega_{n}(\omega t \mid \beta)) + B \sin(\omega_{n}(\omega t \mid \beta))$$

(2.18)

where  $\omega_n = \frac{1}{\sqrt{L_r C_r}}$ ,  $I_c(\beta) = 0$ , and  $V_r(\beta)$  is given by Lqn (2.17). Substi

tuting these initial conditions in Eqn. (2.18) yields