National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Services des thèses canadiennes

Ottawa, Canada K1A ON4

CANADIAN THESES

THÈSES CANADIENNES

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy. c

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed

Reproduction in full or in part of this film is governed by the Canadlan Copyright Act, R.S.C. 1970, c. C-30,

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surfout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

THIS DISSERTATION THAS BEEN MICROFILMED EXACTLY AS RECEIVED

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

Canada

# SOME NOVEL POWER CONVERSION SCHEMES EMPLOYING PULSE WIDTH MODULATED HIGH-FREQUENCY LINKS

Stefanos Manias

A Thesis

in

The Department

of

Electrical Engineering

and

Computer Science

Presented in Partial Fulfillment of the Requirements for the degree of Doctor of Philosophy at Condordia University

Montreal, Quebec, Canada

September 1984

C) Stefanos Manias, 1984

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque, nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-30666-1

#### **ABSTRACT**

Some Novel Power Conversion Schemes

Employing Pulse Width Modulated High-Frequency Links

Stefanos Manias, Ph.D. Concordia University, 1984

Static power conversion schemes employing Pulse Width Modulated.

High-Frequency (HF) links, are investigated in this thesis. The employment of HF links in power conversion schemes results in substantial size, weight and cost reduction of the power converterisolation transformer and reactive components. Therefore, in applications where power density is of prime importance the employment of HF links is the natural choice.

The following power conversion schemes employing an HF link are considered in particular.

A voltage source DC to AC inverter consisting of an HF link and a DC to AC inverter stage is investigated. Its main advantage over conventional inverter configurations is the drastic size and weight reduction of the magnetic components. Furthermore, the proposed inverter offers high operating efficiency, step-up/step-down ability, programmable output frequency and transformer isolation at HF link switching frequencies. Inverter performance is obtained using the results of the analysis and a design procedure is given.

A three-phase Current Source DC to AC inverter consisting of an HF link and a DC to AC inverter stage is investigated. The Current Source is created by the HF link stage which together with a high-frequency transformer provides isolation between the source and the load. The output current regulation and circuit protection is performed

by the HF link stage. The function of the DC to AC inverter stage is to create an output current with low harmonic content by applying fixed switching patterns.

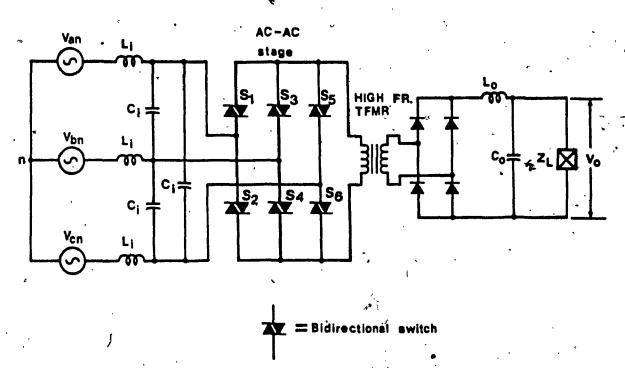

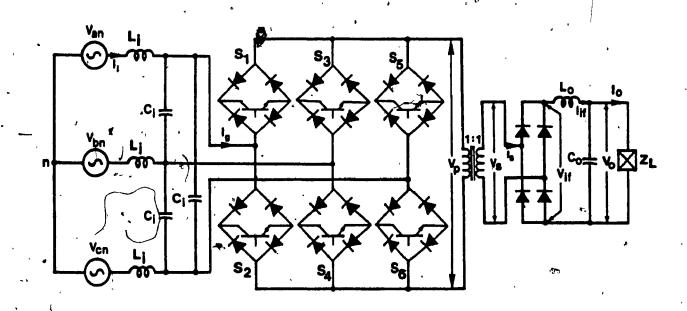

An AC to DC rentverter consisting of an HF link stage is investigated. The proposed power conversion scheme employs an AC to AC cycloconverter as an HF link which together with a high frequency isolation transformer provides isolation between the source and the load. Furthermore, the proposed converter exhibits controlled power factor, step-up/step-down ability and low input Total Harmonic Distortion (THD) with the employment of small sized input filter.

A bilateral HF link power converter is investigated. The proposed power conversion scheme incorporates a battery charger into an inverter by using the existing power circuit components. This power conversion scheme, which can be applied to Uninterruptible Power Supply systems, can also be applied as an AC motor drive and on board battery charger for Electric vehicles where weight and size reduction is of prime—importance.

To facilitate understanding and applicability of the analytical results, design examples are presented for all the proposed power conversion schemes. Also selected predicted results are verified experimentally.

## ACKNOWLEDGEMENTS

The author wishes to express his gratitude to Dr. P.D. Ziogas for his valuable advice, support, guidance and supervision during the course of this thesis.

He would also like to thank Mr. Danny Juras, technician of the University's Power Electronics Laboratory for his assistance and support, and also to Mrs. Madeleine Klein for the typing of the manuscript.

To my wife Maria and our children whose overall support was essential for the completion of my studies

#### LIST OF PRINCIPAL SYMBOLS

## Voltages

E

DC bus voltage

Emin

Lowest expected E value /

$\mathbf{E}_{\max}$

Highest expected E value

Van,Vbn,Vcn

Three-phase line to neutral voltages

Vab,Vbc,Vca

Three-phase line to line voltages

V<sub>m</sub>

Amplitude of line to neutral voltages

V<sub>m(max)</sub>

Highest expected  $\mathbf{V}_{\mathbf{m}}$  value

V<sub>m(min)</sub>

Lowest expected  $V_m$  value

Vo

Load voltage.

V<sub>o,n</sub>

Amplitude of the nth harmonic component of  $\boldsymbol{v_0}$

$v_{o,d}$

Amplitude of the dominant harmonic component of  $\mathbf{V}_{\mathbf{O}}$

۷۱۴ کی

Voltage before output filtering

$v_{if,n}$

Amplitude of the nth harmonic component of Vif

$v_{if,d}$

Amplitude of the dominant harmonic component of  $V_{\mbox{\scriptsize if}}$

۷p

Voltage across the isolation transformer primary

٧s

Voltage across the isolation transformer secondary

#### 2. Current

I

Input filter inductor current

I<sub>i,n</sub>

Amplitude of the nth harmonic component of  $\mathbf{I_4}$

|                      | •                                              |

|----------------------|------------------------------------------------|

| Iō                   | Load current ()                                |

| I <sub>o,n</sub>     | Amplitude of the nth harmonic component of I   |

| I <sub>p</sub>       | Isolation transformer primary current          |

| Is                   | Isolation transformer secondary current        |

| In                   | Output filter inductor current                 |

| I <sub>if,n</sub>    | Amplitude of the nth harmonic component of Iif |

| - <sup>1</sup> ,c    | Commutation current                            |

| I <sub>PT</sub>      | Thyristor peak current                         |

| IRT                  | Thyristor RMS current                          |

| I <sub>AT</sub>      | Thyristor average current                      |

| I <sub>AS</sub>      | Power switch average current                   |

| I <sub>RS</sub> . ') | Power switch RMS current                       |

| IPS                  | Power switch peak current                      |

| 3. Capacitances      | •• · · · · · · · · · · · · · · · · · ·         |

| C <sub>1</sub>       | Input filter capacitance                       |

| c <sub>o</sub>       | Output filter capacitance                      |

| C <sub>s</sub> , ,   | Intermediate filter capacitance                |

| , c <sub>c</sub> *   | Commutation Capacitance                        |

| 4. Inductances       |                                                |

| L,                   | 'Input filter inductance                       |

| L <sub>0</sub>       | Output filter capacitance                      |

| لر                   | Intermediate filter inductance                 |

|                      | · · · · · · · · · · · · · · · · · · ·          |

Commutation inductance

| 5. Impedances                                        |                                                    |

|------------------------------------------------------|----------------------------------------------------|

| , <b>X</b>                                           | Impedance of the commutation inductor              |

| Req                                                  | Equivalent Resistance of the Commutation Circuit   |

| X <sub>C1</sub>                                      | Impedance of the input filter capacitor            |

| X <sub>c</sub> o                                     | Impedance of the output filter capacitor           |

| X <sub>cs</sub>                                      | Impedance of the intermediate filter capacitor     |

| X <sub>L</sub> i                                     | Impedance of the input filter inductor             |

| x <sub>Lo</sub>                                      | Impedance of the output filter inductor            |

| x <sub>L</sub> s<br>x <sub>c1</sub> ,x <sub>c2</sub> | Impedance of the intermediate filter inductor      |

| X <sub>c1</sub> , X <sub>c2</sub>                    | Impedance of the shunt capacitors of the Current   |

| 1>0                                                  | Source Inverter output filter                      |

| z <sub>L</sub>                                       | Load impedance                                     |

| Z <sub>L,n</sub>                                     | Magnitude of $Z_L$ at the nth harmonic frequency   |

| Z <sub>0</sub> .                                     | Input impedance of the load filter                 |

| Zo,n+                                                | Magnitude of $Z_0$ at the nth harmonic frequency   |

| 6. Time                                              |                                                    |

| T                                                    | Waveform period                                    |

| <sup>t</sup> off                                     | Power Semiconductor switch turn-off-time specified |

|                                                      | by the manufacturer                                |

| t <sub>g</sub>                                       | Thyristor turn-off interval                        |

| Δt                                                   | Turn-off time safety margin                        |

| T <sub>f</sub>                                       | Period of the reference signal                     |

Period of the Carrier Signal

Tc

#### 7. Frequencies

f

$\omega_{\mathsf{bo}}$

ω<sub>bi</sub>

for Frequency at which the DC to AC Inverter operates.

(i.e.  $f_0 = 60Hz$ )

Angular Frequency at which the DC to AC Inverter. operates (i.e.  $\omega_0 = 2\pi f_0$ )

AC input voltage frequency

Angular frequency of the AC input voltage

Normalized (with respect to  $f_0$  or  $f_i$ ) carrier frequency

HF link switching frequency

Normalized (with respect to f or f ) HF link frequency

Angular break frequency of the output filter

Angular break frequency of the input filter

## 8. Switching Functions

$\mathcal{S}(\omega t)$  Converter overall switching function

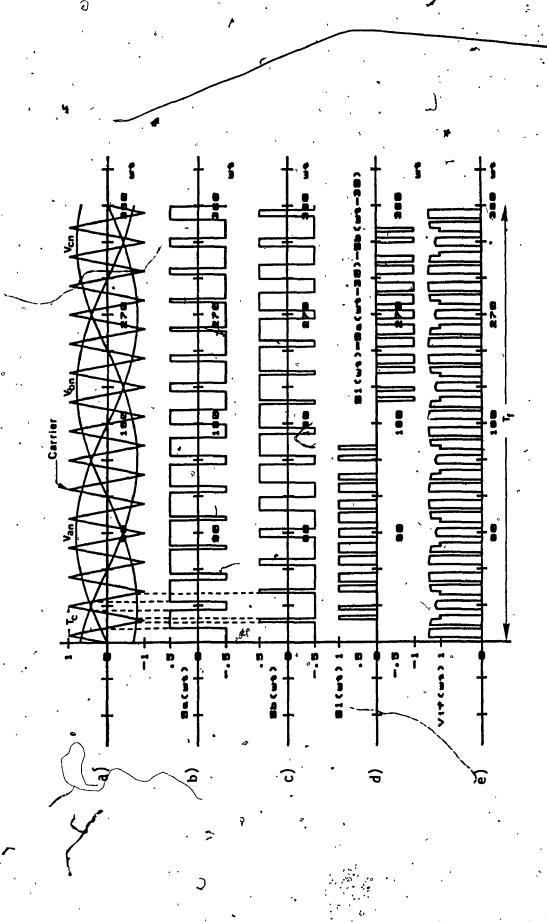

$S_c(\omega t)$  Cycloconverter switching function

S<sub>i</sub>(ωt) Inverter Stage Switching function

$S_r(\omega t)$  Rectifier Stage Switching function

## 9. Miscellaneous Parameters

d Order of the dominant harmonic

Order of the nth harmonic

Order of the kth harmonic

A variable defined as  $K_c = \frac{V_o}{E}$

Input filter inductor current ripple factor

Input filter capacitor voltage ripple factor

Output filter inductor current ripple factor

Output filter capacitor voltage ripple factor

Intermediate filter inductor current ripple factor

Intermediate filter capacitor voltage ripple factor

Modulation factor

Current Source Reactor current ripple

Coil parameter defined as  $Q = \frac{\omega L}{R}$  where  $\omega$ , L and R are the Operation Angular frequency Induactance and coil Resistance respectively

Total Marmonic Distortion

Phase displacement between the nth harmonic components of  $V_{if}(\omega t)$  and  $I_{if}(\omega t)$

Phase displacement between the fundamental components of load voltage and current

Phase displacement between the fundamental components of voltage and current before output filtering

V<sub>+</sub>

0

K<sub>v</sub>

K<sub>i</sub>s

$^{\rm K}{_{\rm V}}_{\rm s}$

Mf

ΔI<sub>s</sub>

Q

THD

$\phi_{n_{\nu}}$

φ

φ.

## TABLE OF CONTENTS

|                                                                                                  | Page          |

|--------------------------------------------------------------------------------------------------|---------------|

| ABSTRACT                                                                                         | 111           |

| ACKNOWLEDGEMENTS                                                                                 | ` <b>v</b>    |

| LIST OF PRINCIPAL SYMBOLS                                                                        | · vii         |

| TABLE OF CONTENTS                                                                                | , xii         |

| CHAPTER 1 - INTRODUCTION                                                                         | 1             |

| 1.1 Introduction                                                                                 | ۱ «           |

| 1.2 General background on conventional Switch-Mode converter configurations                      | . 2           |

| 1.3 Selection of power converter configuration -                                                 | 6             |

| 1.4 Review of Previous Work on HF link techniques                                                | 10            |

| 1.5 Scope of the thesis                                                                          | . 11          |

| CHAPTER 2 A VOLTAGE SOURCE DC TO AC INVERTER USING A DC TO DC CONVERTER AS A HIGH FREQUENCY LINK | 14            |

| 2.1 Introduction                                                                                 | 14            |

| 2.2 System description                                                                           | 16            |

| 2.3 System analysis                                                                              | 20            |

| 2.3.1 Load conditions                                                                            | 20            |

| 2.3.2 Derivation of the inverter stage switching function, $S(\omega t)$                         | 20            |

| * 2.3.3 Inverter stage                                                                           | , 25          |

| 2.3.4 Output Alter                                                                               | 30            |

| 2.3.5 Inverter stage input filter                                                                | i . <b>35</b> |

| 2.3.6 N.F. link stage                                                                            | 39            |

| 2.3.6.1 Flyback configuration                                                                    | 39            |

| 2.3.6.2 Rush-Pull and Full bridge configuration                                                  | 41            |

|                  |                                                                                        | Page              |

|------------------|----------------------------------------------------------------------------------------|-------------------|

| 2.4              | Inverter system main component ratings                                                 | 42                |

| , 2.5            | Design example                                                                         | 44                |

| 2.6              | Control circuit and experimental results                                               | 47 .              |

| <b>\( \)</b> 2.7 | Conclusions                                                                            | 50                |

| CHAPTER 3        | - A CURRENT SOURCE DC TO AC INVERTER USING A DC TO DC CONVERTER AS HIGH FREQUENCY LINK | 51                |

| 3.1,             | Introduction                                                                           | 51                |

| 3.2              | System description                                                                     | 53                |

| ·. ·             | 3.2.1 High Frequency link converter                                                    | " <sup>3</sup> 54 |

|                  | 3.2.2 - Current Source Reactor (CSR)                                                   | 54                |

| o                | 3.2.3 Current Source Inverter (CSI) Stage                                              | 54                |

| <b>,</b> '       | 3.2.4 Output filter                                                                    | 55                |

|                  | 3.2.5 Load conditions                                                                  | 420               |

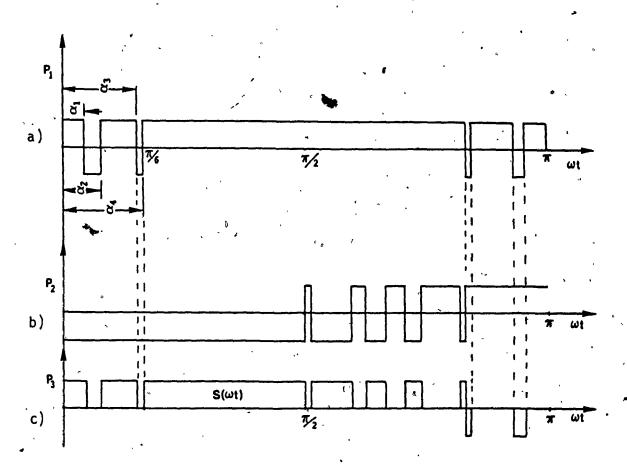

| 3,3              | Synthesis of Switching Functions for CSI's                                             | 59                |

| ;                | 3.3.1 Fixed Pattern Switching Functions                                                | · 59 /            |

|                  | 3.3.2 Variable Pattern Switching Functions                                             | 60                |

| 3.4              | System analysis                                                                        | 61                |

|                  | 3.4.1 Harmonic analysis                                                                | 61                |

|                  | 3.4.2 CSI stage analysis                                                               | 64                |

|                  | 3.4.3 Output filter analysis                                                           | 67                |

| • :              | 3.4.4 CSR analysis                                                                     | 70                |

|                  | 3.4.5 HF link analysis                                                                 | <sub>,</sub> 73   |

| 3.5              | Computer-aided harmonic analysis                                                       | <b>7</b> 6 ·      |

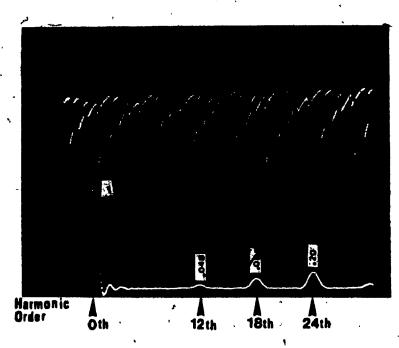

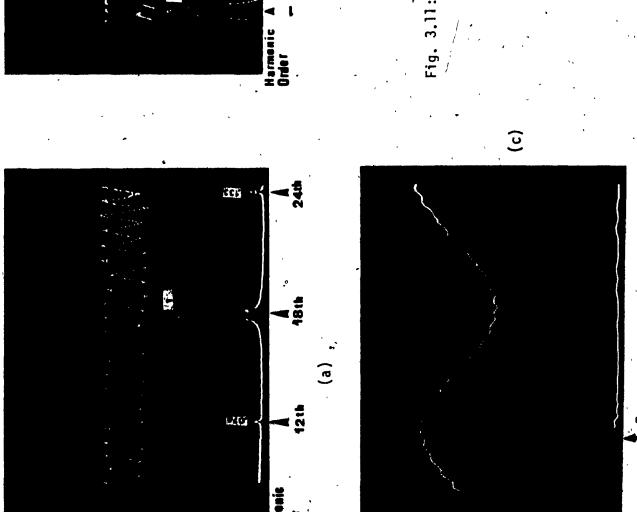

| 3.6              | Experimental results                                                                   | 78                |

| 37               | Annelusions                                                                            | 84                |

|                   |       | · •                                                                                                                                  | <u>Page</u> |

|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CHAP              | TER 4 | - AN AC TO DC CONVERTER USING A CYCLOCONVERTER AS HIGH FREQUENCY LINK                                                                | 85          |

| •                 | 4.1   | Introduction                                                                                                                         | 85          |

|                   | 4.2   | Circuit description                                                                                                                  | 87          |

| · •               | 4.3   | System analysis                                                                                                                      | ` 91        |

|                   | ŕ     | 4.3.1 Load conditions                                                                                                                | 91          |

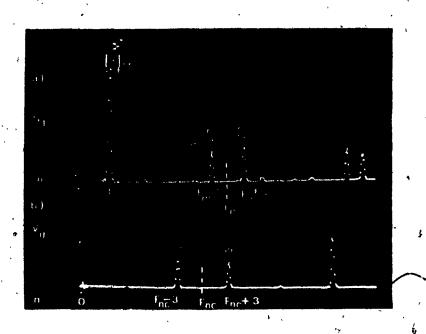

| ,                 | •     | 4.3.2 Derivation of the SPWM output voltage                                                                                          | 91          |

|                   |       | 4.3.3 Output filter                                                                                                                  | 97          |

| v                 |       | 4.3.4 Cycloconverter stage                                                                                                           | 98          |

| •                 |       | 4.3.5 Input filter                                                                                                                   | 103         |

| ,<br>/ <b>3</b> . | 4.4   | Design Example                                                                                                                       | 106         |

| , <b>13</b>       | 4.5   | Conclusions                                                                                                                          | 108         |

| CHAPT             | TER 5 | - A NOVEL BILATERAL HIGH FREQUENCY LINK CONVERTER                                                                                    | 109         |

| •                 | 5.1   | Introduction                                                                                                                         | 109         |

| •                 | 5,2   | System description                                                                                                                   | 110         |

|                   | 5.3   | System analysis in the DC to AC mode                                                                                                 | 114         |

|                   |       | 5.3.1 Load conditions                                                                                                                | 114         |

| •                 |       | 5.3.2 Derivation of the proposed converter input and output quantities $V_{if}(\omega t)$ , $I_{if}(\omega t)$ and $I_{g}(\omega t)$ | 114         |

| 7                 |       | 5.3.3 Output filter                                                                                                                  | 119         |

| •                 |       | 5.3.4 Input filter                                                                                                                   | 120         |

| >                 |       | 5.3.5 Derivation of the cycloconverter and inverter stage switching functions $(S_c(\omega t), S_i(\omega t))$                       | 121         |

|                   | 5.4   | Simulated waveforms obtained in the AC to DC mode                                                                                    | 124         |

|                   | 5.5   | Component ratings                                                                                                                    | 126         |

|                                                                                | Page |

|--------------------------------------------------------------------------------|------|

| E.E. Don't Francis                                                             | 100  |

| 5.6 Design Example                                                             | 126  |

| 5.7 Conclusions                                                                | 131  |

| CHAPTER 6 - CONCLUSIONS                                                        | 132  |

| REFERENCES                                                                     | 134  |

| APPENDIX A - COMPUTER AIDED ANALYSIS METHOD                                    | 139  |

| APPENDIX B - ANALYSIS OF A NOVEL CURRENT IMPULSE COMMUTATED THYRISTOR INVERTER | 141  |

| APPENDIX C - USEFULL DEFINITIONS                                               | 159  |

| APPENDIX D - SWITCHING FUNCTIONS                                               | 163  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

Depending on the power conversion scheme employed, static power converters are divided into two broad\_alasses:

- a) The linear-mode converters

- b) The switch-mode converters

The linear-mode converter offers excellent voltage regulation and is relatively insensitive to variations in input source frequency. Its initial cost is moderate, but because of low power conversion efficiency, its long term cost increases steeply with time. This type of power converter: is widely used on TV sets, audio amplifiers, stereos, and laboratory power supplies, as well as in a wide range of commercial and industrial electronic equipment. In comparison, the Switch-Mode power converter is at least twice as efficient as the linear-mode.

Moreover, Switch-Mode converters offer the advantages of reduced size, weight and cost. However, if improperly designed, they can generate Electromagnetic Interference (EMI) that can degrade other systems. Also, a major shortcoming of Switch-Mode converter technology is that they require more complex design. Even with these disadvantages, Switch-Mode converters are being increasingly accepted in industry, particularly where size, weight, cost and efficiency are of prime importance.

The number of applications of Switch-Mode converters has increased rapidly over the past decade. In addition to their wide spread use as DC regulators, these converters have found employment in a variety of applications involving electrical power conversion, including DC to AC

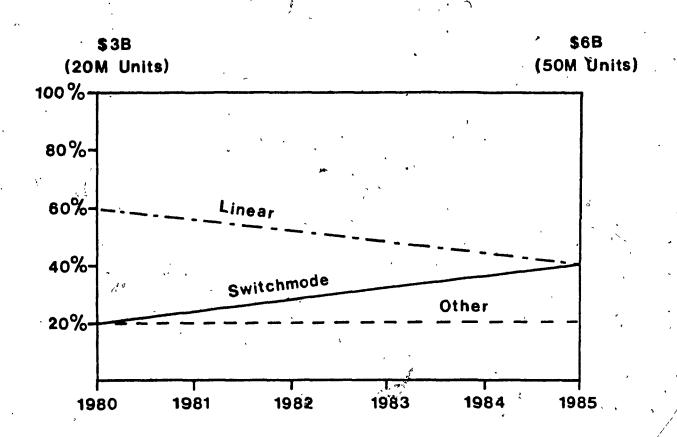

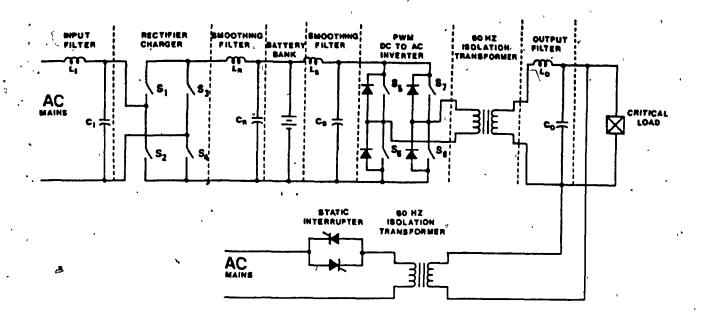

inverters for solar arrays, AC to DC unity input power factor controlled rectifiers for battery charger applications, ringing and tone generators for telephone systems and other applications associated with aerospace and military industries. Fig. 1.1 [1] shows the market distribution of linear and Switch-Mode power converters.

#### 1.2 General background on conventional Switch-Mode converter configurations

Current Switch-Mode converter technology employs five main power converter configurations. These configurations and their salient features are as follows:

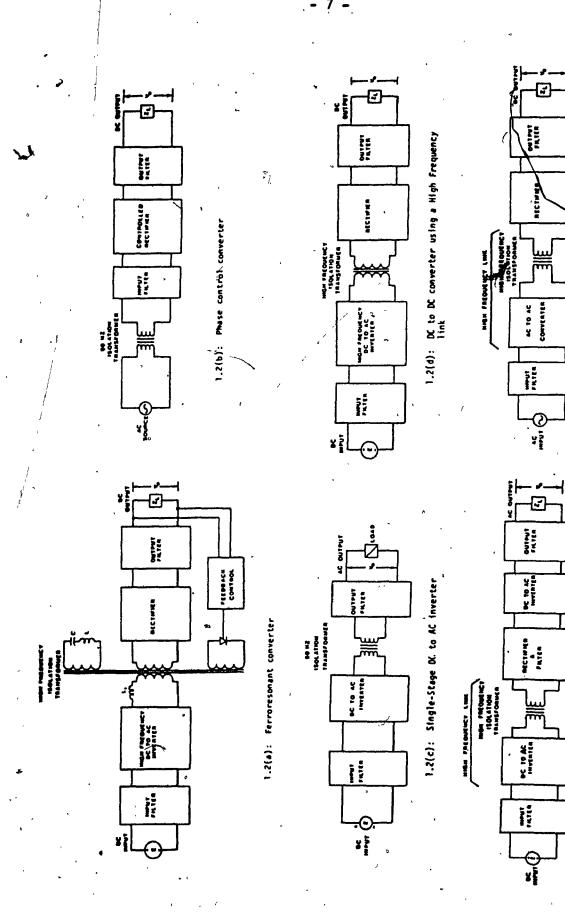

#### a) Ferroresonant converter [2]

Ferroresonant converters, Fig. 1.2(a), operate by resonating a capacitor in the secondary of the isolation transformer with a saturable reactor which is one of the legs of the transformer. Resonance increases the voltage level independently of the input voltage. Its salient features include simplicity, inherent overvoltage protection and poor power factor. Because of its poor power factor and the need for additional reactive components to create the resonance effect the converter becomes complex, bulky and inefficient.

## b) Phase control converter [3]

This power converter configuration, Fig. 1.2(b), is normally used for AC to DC power conversion. The simplest phase control converter operates by turning on the power switches of the rectifier for only a portion of each half cycle of the input voltage to which it is connected. Therefore, the corresponding output voltage consists of segments of the input voltage. The salient features include simplicity, poor power

Fig. 1.1: Market distribution of linear and Switch-Mode power converters.

factor, and creation of low order harmonic components in the output voltage. Therefore, because of the ratings of the input and output filter components and the size of the low frequency isolation transformer, the converter becomes bulky, costly and inefficient.

## c) Single Stage DC to AC inverter [4]

This power converter configuration, Fig. 1.2(c), is widely employed for DC to AC power conversion. The main disadvantage of this converter is that the high inverter switching frequency is not exploited for reducing the size, weight and cost of the isolation transformer. This high switching frequency results from Sinusoidal Pulse Width Modulation (SPWM) control technique which is typically employed for output voltage regulation and elimination of unwanted harmonic components. The employment of SPWM results in size reduction of the input and output filter components.

## d) DC to DC converter using a High Frequency link [5]

This power converter configuration, Fig. 1.2(d), includes all DC to DC converters that are realized using the Boost or Buck chopper configurations or combinations of the two. This scheme of converters employ high switching frequency thus reducing the size of magnetic and reactive components. A further significant advantage of the high switching frequency is that these converters exhibit fast response.

# e) DC to AC, AC to DC and AC to AC converters using a High Frequency link

These configurations include all converters realized by;

i). cascading two single power conversion states

or

11) replacing the unidirectional switching devices of a single conversion stage by bidirectional ones

or

iii) any combination of (i) and (ii)

thus yielding new power schemes with improved properties. These properties include good quality input and output waveforms and substantial size, weight and cost reduction of the reactive elements and isolation transformer.

At present the size and cost of Switch-Mode converter is largely influenced by the:

- i) number of power semiconductor devices needed to implement the power conversion scheme.

- ii) ratings of the reactive elements of the input and output filters.

- iii) ratings of the isolation transformer.

However, power semiconductor technology is rapidly improving, yielding better and better devices at diminishing cost. While reactive elements and magnetic components are not likely to become much cheaper and smaller in the future. Therefore, reactive elements and magnetic components are bound to share increasing amount of the size, weight and cost of the power conversion schemes based on present designs. Consequently, it is preferable to employ two stage power conversion schemes in designs where power density and cost are of prime importance.

Fig. 1.2(e) shows in block diagram form a DC to AC converter which employs a high frequency link. The DC voltage, instead of being directly inverted into the required low output frequency voltage (as in Fig. 1.2(c)), is first inverted into high frequency AC voltage (High frequency link) thus making the size of the isolation transformer to be reduced considerably. The high frequency AC voltage then is rectified and finally inverted by a second power conversion stage to low frequency AC output voltage. Fig. 1.2(f) shows in block diagram form an AC to DC converter which employs a high frequency link. The low frequency input AC voltage, instead of being directly rectified into DC voltage, is first converted into high frequency voltage thus making the size of the isolation transformer to be reduced considerably. The DC output voltage is then obtained by rectifying the high frequency AC voltage. Finally, both power conversion schemes may employ SPWM technique or any other switching function (Appendix D) in order to obtain input and output waveforms with low harmonic distortion using minimum filtering.

## 1.3 Selection of power converter configuration

The widespread use of Switch-Mode converters and the availability of new power semiconductor devices have generated a need for power conversion schemes with the following new properties:

- i) To exhibit high power density (reduction of size and weight)

- ii) To exhibit controlled power factor.

- Distortion (THD) by employing small size filters.

- iv) To provide transformer isolation between the source and the load.

- v) To exhibit high power conversion efficiency.

Fig. 1.2: Current Switch-Mode converter configurations

1.2(f): AC to DC converter using a/High Frequency 11nk

1.2(e): OC to AC inverter using a High Frequency link

- vi) To exhibit high reliability

- vii) To be realized with minimum cost.

These properties have motivated the search for new power conversion schemes (DC to AC and AC to DC) where the High Frequency (HF) Link technique is employed in order to achieve the above mentioned properties. However, since the HF link power conversion schemes generally involve an additional power conversion stage extensive investigation will be required before their credentials are established. For power levels up to few tens of kilo-watts HF links are attractive. Their acceptance has also been accelerated by recent improvements in power semiconductor technology, which have resulted in increased switching speeds for power thyristors and also in continuing improvement in the power handling capability of transistors and MOSFETs. The technique of HF link conversion should therefore become increasingly widespread.

## 1.4 Review of Previous Work on HF link techniques

The use of an HF link in power conversion schemes has been suggested in the past in connection with various applications.

A DC to DC converter utilizing a series resonant inverter as an HF link was proposed by Schwarz [6]. The rectifier load is connected in series with the LC resonant circuit. The converter therefore possesses the characteristics of a current source. Current is regulated by controlling the frequency of operation of the converter.

McMurray investigated an electronic transformer utilizing an HF link [7]. The 60 Hz AC input voltage is chopped at high frequency of about 10 KHz, using thyristor series inverter. The high chopping

frequency results in reduction of the isolation transformer size. The 60 Hz AC waveform is reconstructed on the secondary of the transformer by further thyristor switches which are operated in sychronism with the switches on the primary side. Thus the input and output are isolated with the employment of a high frequency transformer.

The use of HF links has also been considered for high power utility applications. Gyugyi et al investigated an HF link technique for applications such as interconnection of power system [8].

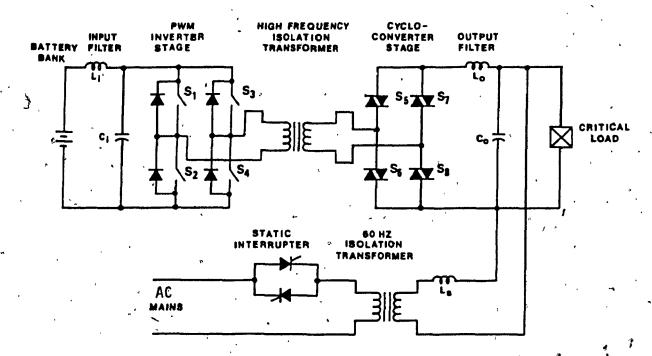

Espelage et al investigated a DC to AC inverter using an HF link [9]. The overall unit consists of two power conversion stages. A DC to AC inverter stage that creates the HF link and a cycloconverter stage that converts the high frequency voltage generated into a low frequency one. In this power conversion scheme the principle of series resonance is applied.

HF link conversion schemes have been proposed for interfacing solar cell arrays to the AC power line. The small transformer size resulting from high frequency operation makes this arrangement attractive [10] [11]. Considerations of weight and size are of major importance in on-board power supplies for electric vehicles. This is another area where the potential offered by HF links has attracted investigation.

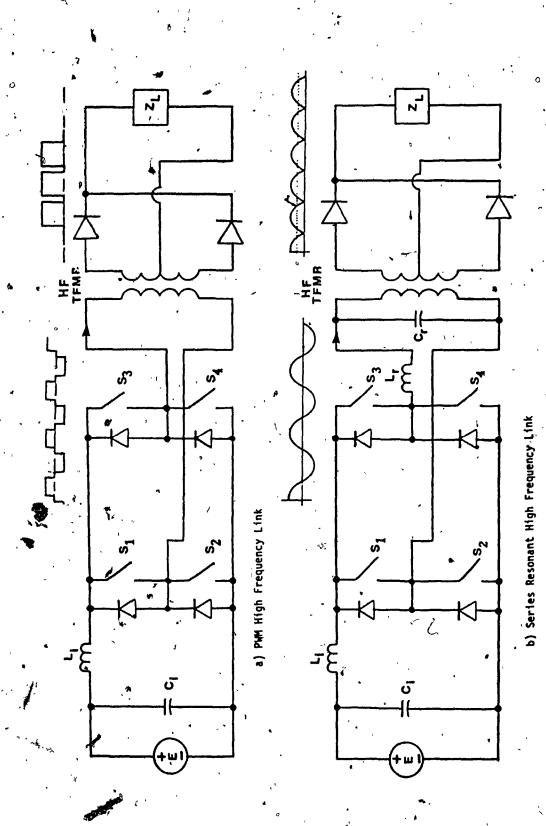

It is noted that most of the previous work on HF links has been focused on converter configurations that incorporate an additional resonance subcircuit. This subcircuit consists of two series connected  $L_r$ - $C_r$  components as shown in Fig. 1.3(a). The function of this subcircuit is to generate a resonant high frequency current and to facilitate current commutation when the main power converter switches are realized by non-Gated turn off devices. The resonant HF link converter when

compared to Pulse Width Modulated (PWM) converter (Fig. 1.3(b)) has the following advantages and disadvantages.

#### <u>Advantages</u>

- (i) Exhibits lower switching losses

- (ii) Exhibits lower Electromagnetic Interference

#### <u>Disadvantages</u>

- (i) Requires additional passive components

- (ii) Exhibits high KVA ratings because of the resonant circuit

- (iii) Power switches are subjected to higher peak currents

- (iv) Operation is feasible only close to resonance frequencies.

The introduction of higher gain switches adds more weight to disadvantages and subtracts weight from the advantages. Therefore, power conversion schemes employing the PWM HF link technology is the natural choise for satisfying the design objective of this research.

## 1.5 Scope of the thesis

Briefly, the main objective of this thesis is to propose four novel power conversion schemes which exhibit the properties presented in section 1.3. The aforementioned schemes are novel in that they have not been either described or analyzed in previously published work. For example the scheme described in Chapter 4 includes a circuit configuration conceived, described and analyzed for the first time by the author. Similarly the power conversion scheme described in Chapter 3 is completely original and has for the first time been reported in technical literature [15] by a paper co-authored by the author of this thesis. Finally, the same degree of originality applies to the work described in Chapter 2 [12], 5 and Appendix B [35].

Fig. 1.3: Types of High Frequency Links

The proposed schemes, which employ an HF link, are analyzed and evaluated in a modular form with the aid of computer simulation. The computer simulation obtains spectra of waveforms of interest, determines component ratings and performs waveform analysis. The computer program computes the real time waveforms over a full cycle.

The guidelines for the design of input and output filters are discussed, and the factors commonly employed for their design are defined in terms of the harmonic content of the power conversion scheme variables.

The proposed power conversion schemes are analyzed under steady state conditions and with the following assumptions:

- All power switching devices are ideal and diodes

forward drop and reverse leakage current are ignored.

- ii) The filter components are ideal.

- iii) The input source voltages are ripple free and in case of a three-phase AC source are balanced.

- iv) In the AC to DC power conversion scheme the output filter inductor current is ripple free.

- v) In the DC to AC inversion schemes the rated load power factor is allowed to vary from .8 capacitive to .6 inductive.

- vi) The input source voltage typically vary from 10% above to 20% below its nominal value.

The contents of this thesis is divided into five chapters and four appendices listed as follows:

In Chapter 2 a novel single phase DC to AC inverter, which employs a DC to DC converter as an HF link, is analyzed. The predicted results are verified experimentally and design guidelines are provided for selecting components.

<u>In Chapter 3</u> a novel three phase current source DC to AC inverter, which employs a DC to DC converter as an HF link, is analyzed. The advantages and disadvantages of Current Source Inverters (CSI) when compared to Voltage Source Inverters (VSI) are briefly discussed. The predicted results are verified experimentally and design guidelines are provided for selecting components.

<u>In Chapter 4</u> a novel AC to DC rectifier, which employs an AC to AC converter (cycloconverter) as an HF link, is analyzed. Design guidelines are produced for selecting components.

<u>In Chapter 5</u> a novel bilateral converter, which employs an HF link in both modes of operation, is analyzed. The predicted results are verified experimentally and design guidelines are provided for selecting components.

In Appendix A the algorithm of the developed computer program, which was used throughout this thesis to analyze the various proposed power conversion schemes, is outlined.

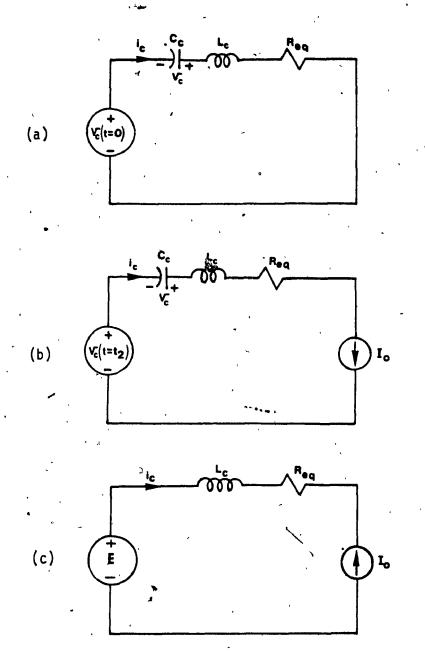

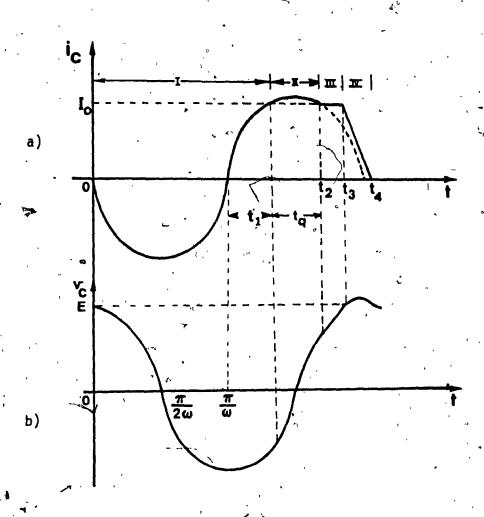

In Appendix B an analysis of a novel current impulse commutated thyristor inverter is presented and analyzed. The proposed inverter is used in this thesis as an HF link for thyristorized power conversion schemes.

In Appendix C the definitions of some important variables used throughout this thesis are presented.  $\gamma$

<u>In Appendix D</u> the switching function approach, which is used for the analysis of the proposed power conversion schemes throughout this thesis, is presented.

#### CHAPTER 2

## A VOLTAGE SOURCE DC TO AC INVERTER USING A DC TO DC CONVERTER AS A HIGH FREQUENCY LINK

#### 2.1 Introduction

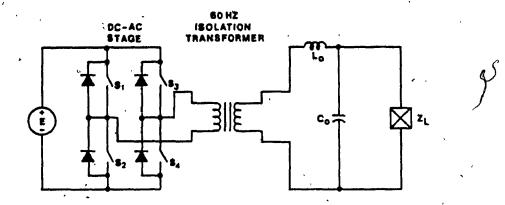

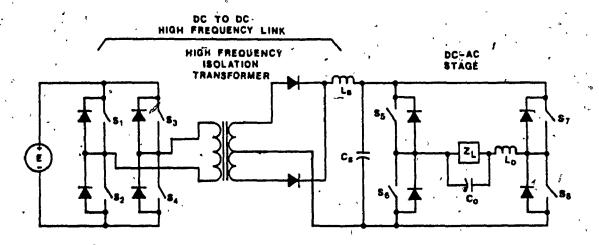

Fig. 2.1 shows the conventional full bridge inverter where Sinusoidal Pulse Width Modulation (SPWM) control technique is applied. The disadvantage of this power conversion scheme is, that the size of the magnetic components must be designed for the fundamental component instead of the inverter switching frequency. Consequently, the high inverter switching frequency cannot be exploited for reducing the size of the isolation transformer. Furthermore, the power conversion scheme shown in Fig. 2.1 has no means of regulating the inverter input voltage or means of changing the inverter input voltage to a level which would optimize the performance of the inverter components. These drawbacks result in substantial power underrating of the overall inverter unit.

Fig. 2.2 shows the proposed power conversion scheme that has none of the above disadvantages, but it does require an additional power conversion stage. This additional stage is a High Frequency (HF) DC to DC link which inputs the unregulated DC bus voltage and outputs a regulated DC voltage at any desired level. The HF link includes a high frequency transformer which provides isolation at switching frequency, thus resulting in substantial cost, size, and weight reduction for the isolation transformer. The remaining power conversion stage consists of a full bridge DC to AC inverter. Note that because of the high switching frequency the input filter

Fig. 2.1: Schematic diagram of the conventional inverter configuration.

Fig. 2.2: Schematic diagram of the proposed inverter configuration.

components can also be reduced. Furthermore, circuit protection is performed in the HF link stage.

#### 2.2 System description

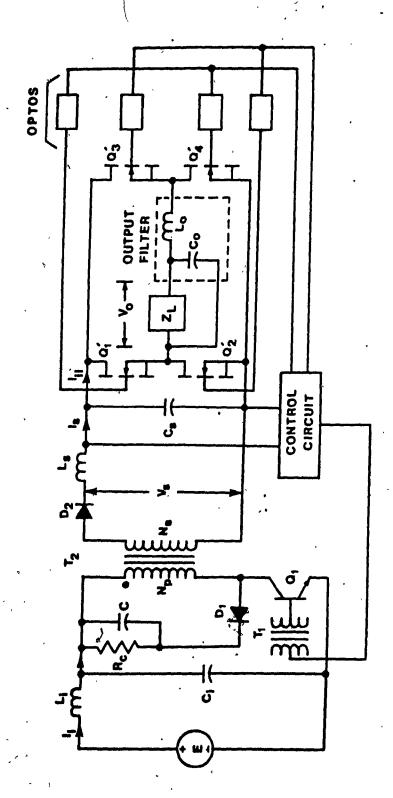

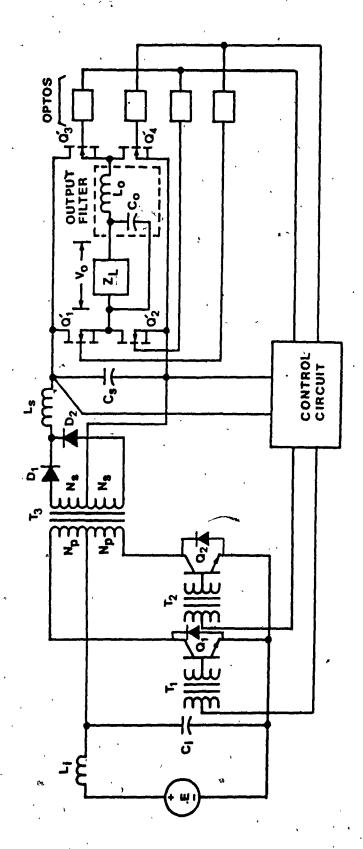

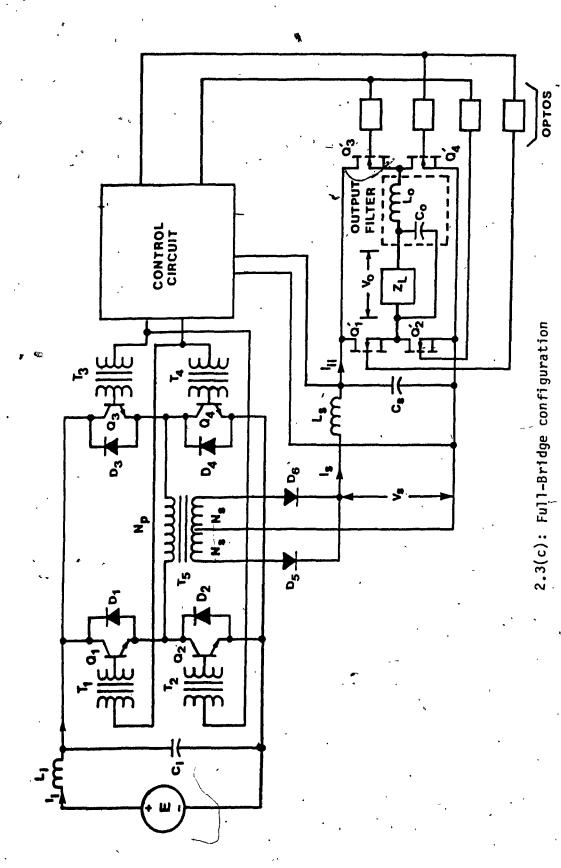

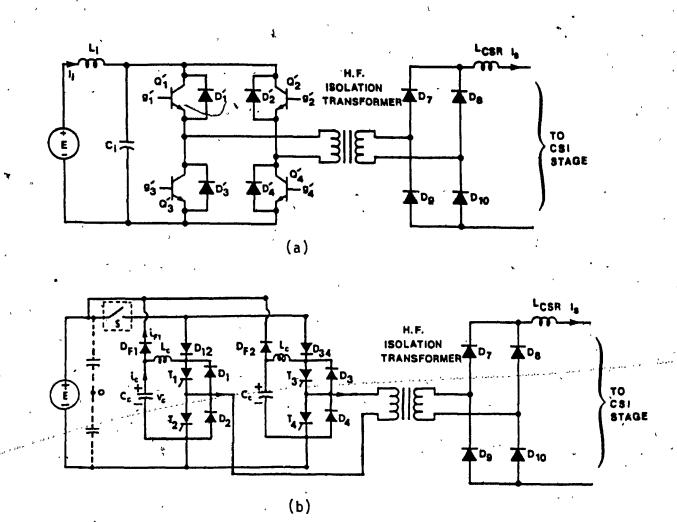

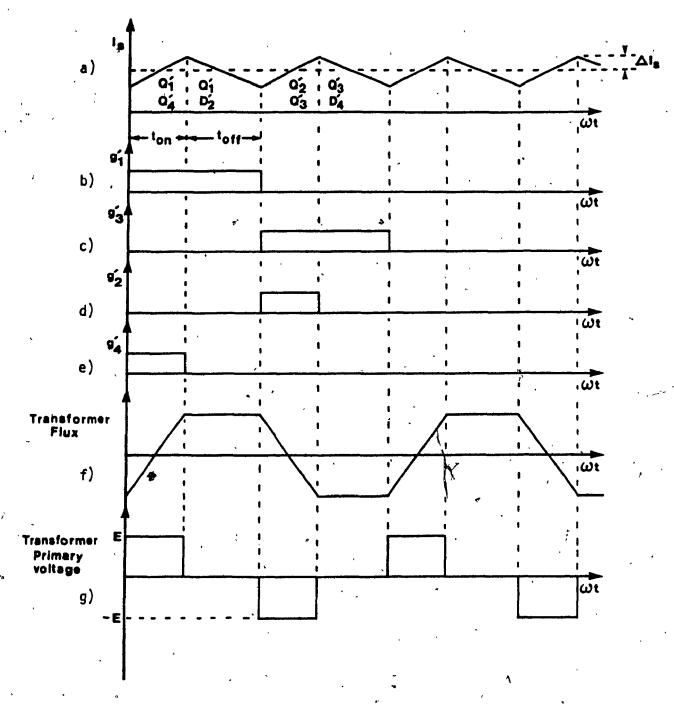

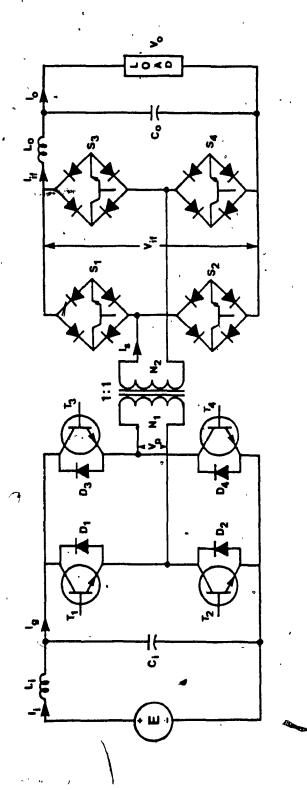

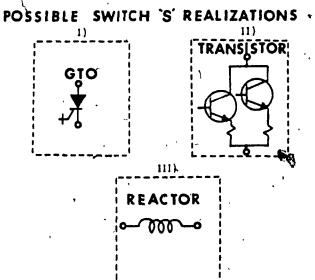

A variety of semiconductor switches are available that can be used to implement the proposed inverter system. Depending on the DC bus voltage and rated output power these devices can be transistors, GTOs, Assymmetrical SCRs or traditional thyristors. Fig. 2.3 shows a family of transistorized power conversion units employing the proposed scheme. Imparticular,

Fig. 2.3(a) shows the flyback configuration,

Fig. 2.3(b) the push-pull configuration, and

Fig. 2.3(c) the full bridge configuration.

The flyback configuration requires fewer components than the others, resulting, in reduced cost and higher reliability. In addition, there is no "switch through" problem with flyback HF link stage. However, in the flyback configuration the voltage and current stresses of the power switches in the HF link stage are increased by a factor of two compared to the stresses of the power switches in the push-pull and full bridge configurations. Moreover, since the flyback is a forward converter it cannot function without a voltage control loop.

For the DC to AC inverter stage, the full bridge inverter was chosen because it utilizes the full DC bus provided by the HF link and also when connected to the HF link there is no need for centertaping. Since the inverter system output voltage waveform consists of train of pulses (Fig. 2.4(d)) some form of filtering is necessary in order

2.3(a): Flyback configuration

2.3(b): Push-Pull configuration

FIG. 2.3: A family of transistorized inverters employing . the proposed Power Conversion Scheme.

to separate the fundamental harmonic component from the unwanted components. Moreover, by employing proper switching function patterns (Appendix D) to the inverter stage, the size, weight, and cost of the inverter stage input and output filter components can be minimized. Finally, for this power conversion scheme, the low pass L-C filter configuration was chosen for harmonic filtering in different parts of the inverter system because it satisfies the harmonic distortion requirements with a minimum number of components.

#### 2.3 System analysis

In this section, the proposed power conversion scheme is analyzed under steady state conditions. The derived expressions are subsequently used to obtain the information necessary for the safe design of the system. Finally, the following analysis has also been presented in reference [12].

## 2.3.1 Load, conditions

In order to generalize the analysis of the proposed power conversion scheme the rated output voltage,  $V_0$ , and rated output current,  $I_0$ , are expressed in per unit as follows:

$$V_{o(rms)} = 1 \text{ p.u. (volts)}$$

(2.1)

$$I_{o(rms)} = 1 \text{ p.u. (Amps)}$$

(2.2)

## 2.3.2 Derivation of the inverter stage switching function, $S(\omega t)$

Experience with static converters has shown that the most useful analytical information is obtained when the converter is viewed by the input and output ports as a multi-frequency AC current and/or voltage source generator (Appendix D).

Consequently the converter can be modelled as a black box whose transfer characteristics are analytically described by the Fourier series expansion of its respective set of switching functions [13], [14], [15]. By multiplying converter switching functions with expressions describing respective input voltages, analytical expressions for the converter output voltages are obtained. Therefore, by properly selecting the expression its input or output ports can be achieved. Moreover, the required component ratings are calculated from the product of line currents and voltages with the appropriate switching functions.

There is a number of switching functions that can be employed with the inverter stage for elimination of unwanted harmonic components. These switching functions can be of the following two types:

Normally these types of switching functions [16].

Normally these types of switching functions are employed where small numbers (up to seven) of unwanted harmonic demponents are to be eliminated, and slow turn-off switching devices (GTOs or Thyristors) are used for the implementation of the power conversion stages. When large numbers of unwanted harmonic components are to be eliminated, this technique becomes analytically very complex. Moreover, considerable computer execution time is needed in order to obtain the required switching angles. Using this technique the resulting maximum RMS value of the fundamental component

of the inverter output voltage is 8.2% less than the value of the DC bus voltage provided by the HF link stage.

Pulse Width Modulation (SPWM) technique by setting the Modulation factor equal to one. These functions can easily employ high switching frequencies. Consequently, they are compatible with fast turn-off switching devices (Bipolars or MosFets). Because of the high switching frequencies that can be realized, the unwanted dominant harmonic component (Appendix C) can be shifted far away from the fundamental (as in Fig. 2.4(e)). This feature can be utilized to reduce the size of the output filter components. Using this technique the resulting maximum RMS value of the fundamental component of the inverter output voltage is 29.3% less than the value of the DC bus voltage provided by the HF link stage.

As mentioned earlier in the introduction of this thesis and in the oduction of this chapter, one of the requirements of the inverter besides the reduction of the isolation transformer was the reduction of the input and output filter components. The reduction of the output filter components requires high-order dominant harmonic components which can be achieved with the employment of high inverter stage switching frequencies. Therefore, since the SPWM fixed pattern can employ high switching frequencies it was chosen as the inverter stage switching function.

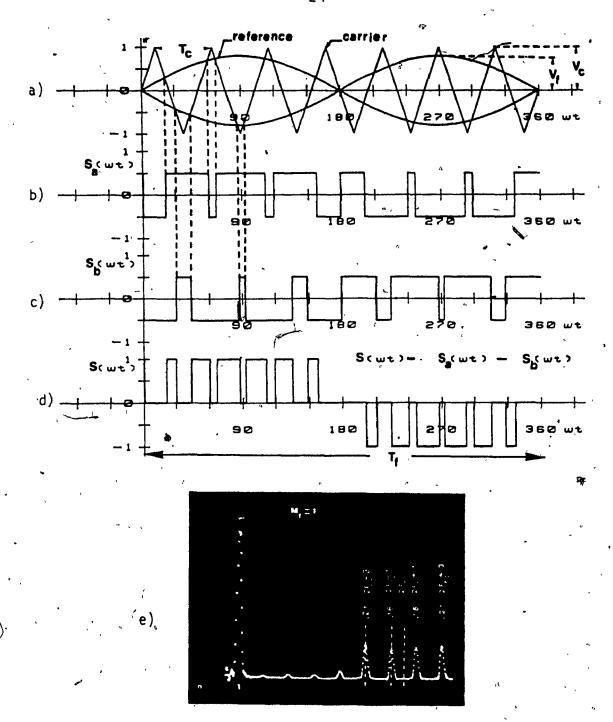

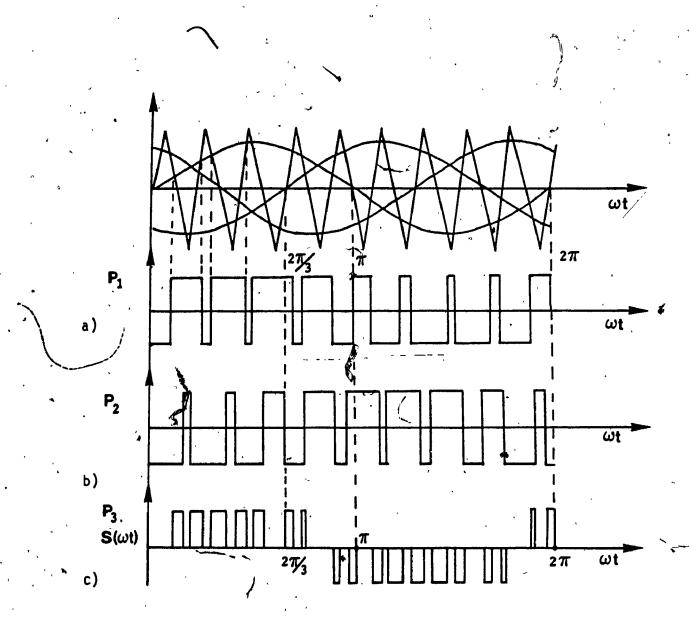

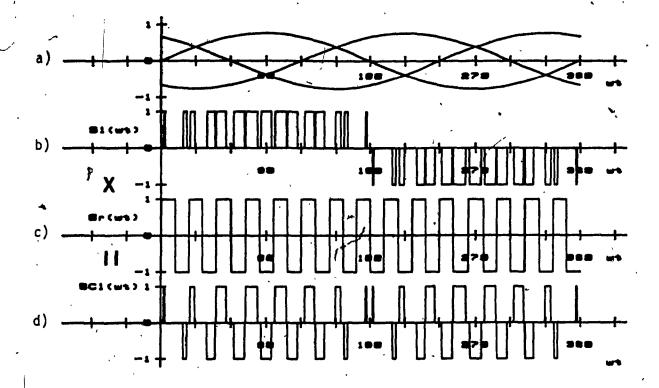

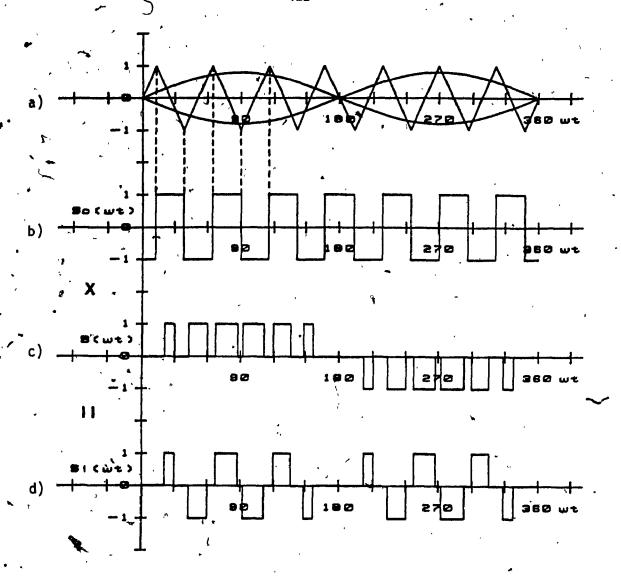

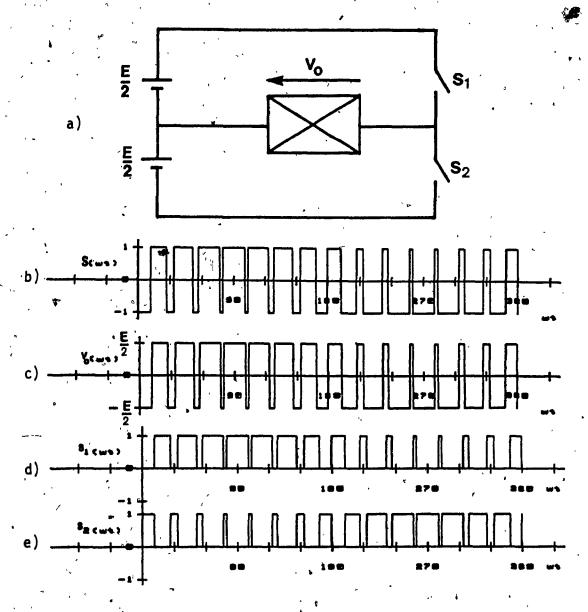

Fig. 2.4 shows the derivation of the inverter stage switching function obtained by applying the single-phase unidirectional SPWM technique. The significant variables in the switching functions resulting from the SPWM technique are:

- a) The ratio of the normalized carrier frequency,  $f_{nc}$ , defined as  $f_{nc} = \frac{T_f}{T_c}$  (Fig. 2.4(a)),

- b) The modulation factor,  $M_f$ , defined as  $M_f = \frac{V_f}{V_c}$  (Fig. 2.4(a)).

Furthermore, results obtained with the developed computer program (Appendix A) have shown that for Modulation factor equal to one

- a) the value of the normalized carrier frequency ( $f_{nc}$ ) and the order of the dominant harmonic component (d) of the switching function ( $S(\omega t)$ ) are related by  $d = 2 f_{nc} 3$  (2.3)

- b) the amplitude of the fundamental component of the switching function  $(S(\omega t))$  is independent of the value of the normalized carrier frequency  $(f_{nc})$  and is given by

$$A_1 = 1 \tag{2.4}$$

c) the amplitude of the dominant harmonic component (d) of the switching function ( $S(\omega t)$ ) is independent of the value of the normalized carrier frequency ( $f_{nc}$ ) and is given by

$$A_d = 0.2$$

(2.5),

Although switching function patterns (such as Fig. 2.4(d)) help to visualize the generated inverter stage voltage and current waveforms,

Fig. 2.4: Derivation of the inverter stage switching function,  $S(\omega t)$ , and its respective frequency spectrum.

they are not suitable for further analytical work. Effective inverter stage analysis requires that the function  $S(\omega t)$  should be expressed mathematically. Such expression can be obtained by deriving its Fourier series expansion which is given by

$$S(\omega t) = \sum_{n=1,odd}^{\infty} A_n \sin(n\omega_o t)$$

$$= A_1 \sin(\omega_0 t) + \sum_{n=d}^{\infty} A_n \sin(n\omega_0 t)$$

(2.6)

where:

$\omega_{\text{n}}$  is the inverter operating frequency,

$A_1$  is the amplitude of the fundamental component of the inverter stage switching function,  $S(\omega t)$ ,

$A_n$  is the amplitude of the nth harmonic component of the inverter stage switching function,  $S(\omega t)$  ,

d is the dominant harmonic component of the inverter stage switching function,  $S(\omega t)$ .

Therefore, using eqn. (2.6) and the expressions given in Appendix D

the inverter stage input and output quantities can be found in mathematical form.

# 2.3.3 Inverter stage

Regarding Fig. 2.3 and using the switching function relations given in Appendix D the inverter stage output voltage and current are given by

$$V_{if}(\omega t) = V_{s,o} S(\omega t) \qquad (2.7)$$

$$I_{if}(\omega t) = \frac{V_{if}(\omega t)}{Z_{o}(\omega t)}$$

(2.8)

where:

$v_{s,o}$  is the dc component of the voltage provided by the HF link stage (Fig. 2.3),

$Z_0$  is the input impedance of the output filter. By employing eqn. (2.6) eqns. (2.7) and (2.8) become

$$V_{if}(\omega t) = V_{s,o} \sin(\omega_{o}t) + V_{s,o} \sum_{n=d}^{\infty} A_{n} \sin(n\omega_{o}t),$$

$$I_{if}(\omega t) = \frac{V_{s,o} \sin(\omega_{o}t + \phi_{1})}{|Z_{o,1}|} + V_{s,o} \sum_{n=d}^{\infty} \frac{A_{n} \sin(n\omega_{o}t + \phi_{n})}{|Z_{o,n}|}$$

$$= \sum_{n=1,odd}^{\infty} B_n \sin(n\omega_0 t + \phi_n) \qquad (2.10)$$

where:

$B_n$  is the amplitude of the nth harmonic component of the inverter stage output current,  $I_{if}(\omega t)$ ,

$|Z_{0,n}|$  is the magnitude of  $Z_0$  at the nth harmonic frequency,

$$\phi_{n} = \tan^{-1} \left( \frac{\operatorname{Imag}(Z_{0,n})}{\operatorname{Real}(Z_{0,n})} \right) \tag{2.11}$$

is the phase displacement between respective fundamental components of  $V_{if}(\omega t)$  and  $I_{if}(\omega t)$ . For  $f_{nc} \ge 17$ ,  $X_{co} = 2 \text{ p.u. and } X_{Lo} < .1 \text{ p.u. was found that } \phi_{1(max)} = 51^{\circ}$  and  $\phi_{1(min)} = 0^{\circ}$  for loads vary from 0.8 leading to 0.8 lagging.

Eqn. (2.9) implies that in order to obtain 1 p.u. rms load voltage (exp. 2.1) the dc component  $V_{s,o}$ , of the inverter stage input voltage must be  $V_{s,o} = \sqrt{2} p.u.$  (2.12)

Also, by using exps. (2.5) and (2.9) the amplitude of the dominant harmonic component of the inverter stage output voltage,  $V_{if,d}$ , is found to be

$$V_{if.d} = V_{s.o} \cdot A_d = (\sqrt{2})(0.2) = 0.28 \text{ p.u.}$$

(2.13)

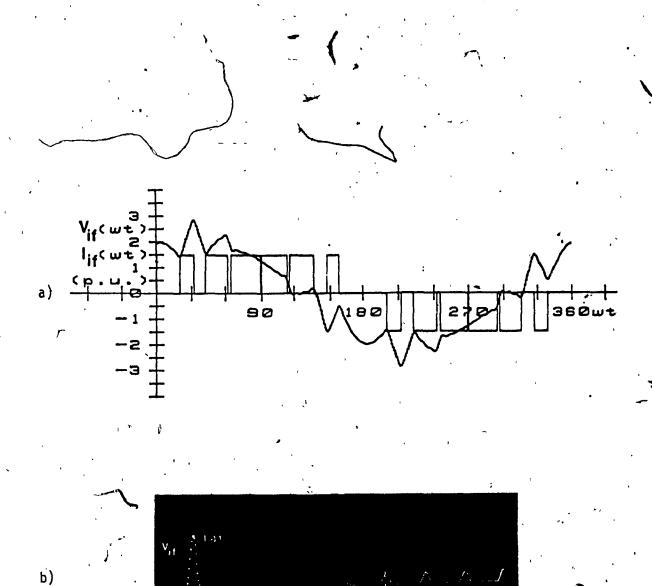

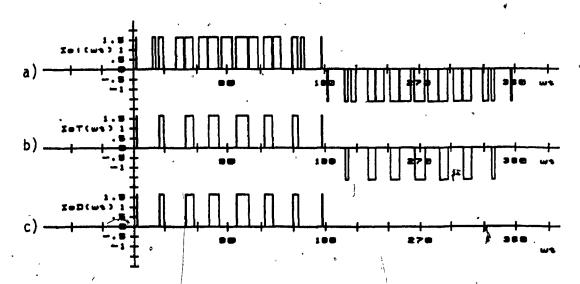

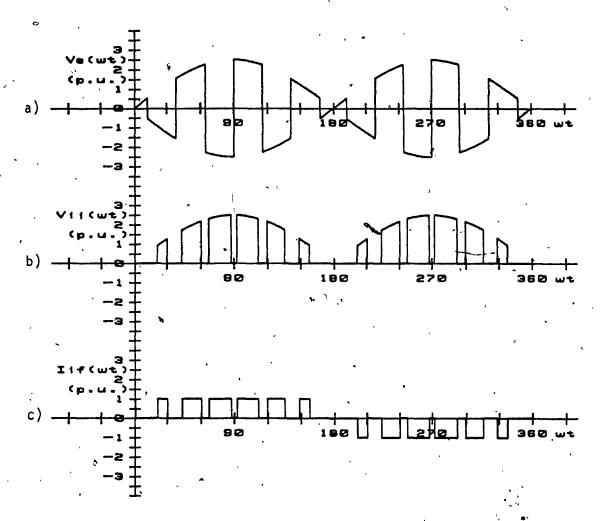

The simulated waveforms with their respective spectra for the voltage and current quantities defined in eqns. (2.9), and (2.10), under worst operating condition for component ratings (0.8 leading power factor) and f<sub>nc</sub> = 7 (f<sub>nc</sub> has been intentionally chosen low and equal to 7 for waveform clarity), are shown in Figs. 2.5(a) and (b). These waveforms have been obtained by incorporating the aforementioned expressions in the computer program discussed in Appendix A and can be used for computing the inverter stage main component voltage and current ratings.

In order to be able to obtain design guidelines for the inverter stage input filter the frequency spectrum of the inverter stage input current has to be known. Therefore, regarding Fig. 2.3 and using the switching function relations given in Appendix D the inverter stage input current,  $I_{ij}(\omega t)$ , is given by

$$I_{ij}(\omega t) = I_{if}(\omega t) \cdot S(\omega t) \qquad (2.14)$$

Substituting eqns. (2.6) and (2.10) into eqn. (2.14)

$$I_{ii}(\omega t) = \sum_{n=1,odd}^{\infty} B_n \sin(n\omega_o t + \phi_n) \cdot \sum_{n=1,odd}^{\infty} A_n \sin(n\omega_o t)$$

(2.15)

Simplifying further eqn. (2.15) the mth harmonic component of the inverter stage input current is given by

Fig. 2.5: Simulated waveforms with their respective frequency spectra for voltage and current before output filtering,  $V_{if}(\omega t)$  and  $I_{if}(\omega t)$ , obtained with  $P_f$ =0.8 leading,  $M_f$ =1 and  $f_{nc}$ =7.

21-3

$$I_{fi,m}(\omega t) = \frac{1}{2} \left[ -\sum_{k=1}^{m-1} A_{m-k} B_{k} \cos(m\omega_{o}t + \phi_{m-k}) + \sum_{k=1,odd}^{\infty} A_{m+k} B_{k} \cos(m\omega_{o}t + \phi_{m+k}) + \sum_{n=1,odd}^{\infty} A_{n} B_{m+n} \cos(m\omega_{o}t - \phi_{n}) \right]$$

(2.16)

hhere:

$$m = 2, 4, 6, 8, \dots$$

Consequently, using eqn. (2.16) the amplitude of the dc and second-order components are given by

$$I_{11.0} \simeq \frac{A_1 B_1}{2} \cos \phi_1 \tag{2.17}$$

$$I_{11,2} \simeq \frac{A_1B_1}{2}$$

(2.18)

where:

A<sub>1</sub> is the amplitude of the fundamental component of the inverter stage switching function given by eqn. (2.4),

$B_1$  is the amplitude of the fundamental component of the inverter stage output current,  $I_{if}(\omega t)$ , given by

$$B_1 = \sqrt{2} \quad p.u.$$

(2.19)

for  $f_{nc} \ge 17$  (Realistic values of  $f_{nc}$  for HF applications)

Furthermore, using exps. (2.4), (2.17), (2.18) and (2.19) and assuming

that the normalized carrier frequency  $f_{nc} \ge 17$  (since high switching frequency is applied to the inverter stage) the following expressions required for the inverter stage input filter design are obtained

$$I_{ii,o(min)} = \frac{(1)(\sqrt{2})(\cos 51^{\circ})}{2} = .5 \text{ p.u.}$$

(2.20)

$$I_{ii,o(max)} = \frac{(1)(\sqrt{2})(1)}{2} = 0.707 \text{ p.u.}$$

(2.21)

$$I_{11,2} = \frac{(1)(\sqrt{2})}{2} = 0.707 \text{ p.u.}$$

(2.22)

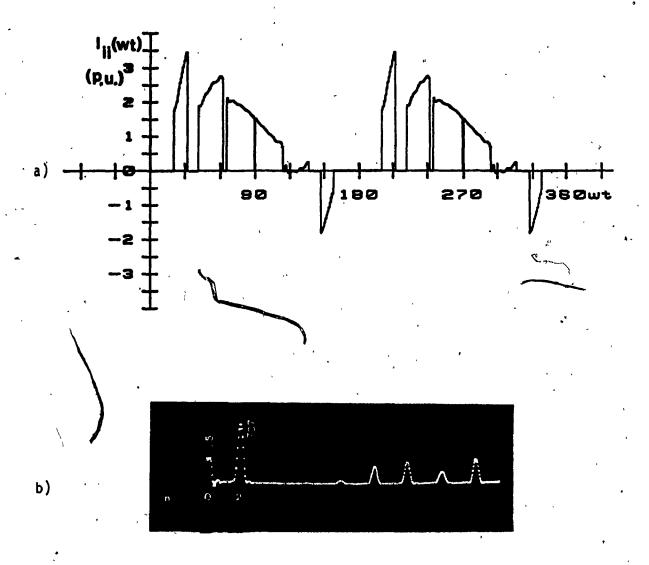

Finally, Fig. 2.6 shows the simulated waveform of the inverter stage input current,  $I_{ij}(\omega t)$ , and its respective frequency spectrum obtained with 0.8 leading power factor and  $f_{nc} = \sqrt{2}$ .

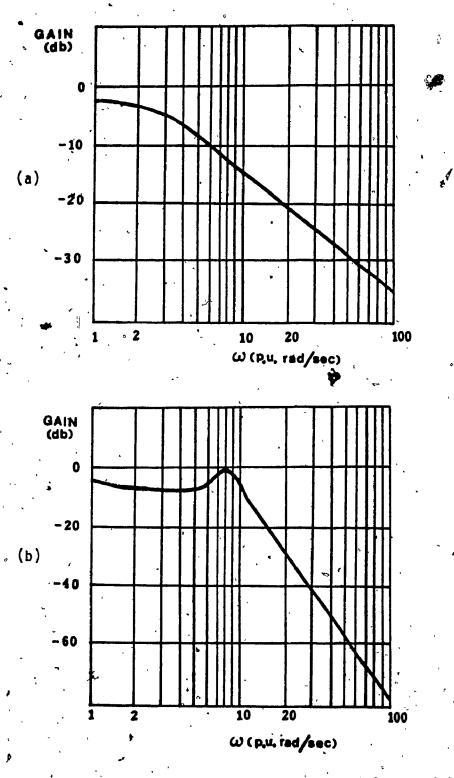

### 2.3.4 Output filter

In most specifications for power supplies the Total Harmonic Distortion (THD, see appendix C) content of the output voltage,  $V_0$ , is  $\leq 5\%$  at rated load and no load conditions [17], [18]. It can be shown that if the amplitude of the dominant harmonic component (2 f<sub>n</sub> -3) is reduced to 3% of the amplitude of the fundamental then, under worst operating condition (0.8 lagging power factor), a THD  $\leq 5\%$  can be insured. Therefore, the value by which the amplitude of the dominant harmonic component has to be attenuated by the output filter is given by

$$\Delta A = 20 \log_{10}(0.03) - 20 \log_{10}(V_{1f,d})$$

(2.23)

Therefore, using exps. (2.13) and (2.23)

$$\Delta A = -19.4 \text{ db}$$

(2.24)

Fig. 2.6: Simulated waveform of the inverter stage input current,  $I_{ij}(\omega t)$ , and its respective frequency spectrum obtained with  $P_f=0.8$  leading,  $M_f=1$  and  $f_{nc}=7$ .

To achieve this attenuation a second order LC filter was chosen for its simplicity (Fig. 2.3). Using the characteristics of the second-order filter and exp. (2.24) the following expression is obtained

$$\frac{19.4}{\log_{10}\omega_{bo}^{-\log_{10}(2f_{nc}-3)}} = \frac{40}{\log_{10}\omega_{bo}^{-\log_{10}10\omega_{bo}}}$$

(2.25)

where:

for is the normalized carrier frequency

$\omega_{bo}$  is the break frequency of the output filter  $= 1/\sqrt{L_0 C_0}$

After further simplification eqn. (2.25) becomes

$$\omega_{\text{bo}} = (2f_{\text{nc}} - 3)(10)^{-19.4/40} \text{ p.u.}$$

(2.26)

where: "

1 p.u. frequency is the inverter system operating  $\label{eq:pull_problem} \text{frequency, } \boldsymbol{\omega}_{0}.$

Consequently, using eqn. (2.26) the output filter components are given by

$$\frac{\chi_{C_{0,1}}}{\chi_{C_{0,1}}} = L_{o}C_{o} = \frac{9.32}{(2f_{nc}-3)^{2}} \text{ p.u.}$$

(2.27)

where:

L is the inductance of the output filter,

to is the capacitance of the output filter,

is the reactance of the output filter inductor at

operating frequency,

is the reactance of the output filter capacitor at operating frequency,

$f_{nc}$  is the normalized carrier frequency.

There is no "right" answer to how the two filter components should be chosen but the following factors should be considered:

i) In order to prevent the resonance condition in the filter the following inequalities must hold  $\omega_0 L_0 < \frac{1}{C \omega_0} \text{ ; for the fundamental component}$

$$d\omega_0 L_0 > \frac{1}{d\omega_0 C_0}$$

; for the dominant component

- ii) A low  $L_0/C_0$  ratio results in larger peak output current, when initially the inverter unit is switched on.

- iii) A low  $L_0/C_0$  ratio will dissipate much more power.

Therefore, since the output filter input quantities  $(V_{if}(\omega t), I_{if}(\omega t))$  are given by eqns. (2.9) and (2.10) respectively and using eqn. (2.27) the expressions for the load voltage and current are expressed as follows:

$$V_{o}(\omega t) = \sum_{n=1, odd}^{\infty} V_{o,n} \sin(n\omega_{o}t + \theta_{v})$$

(2.28)

$$I_o(\omega t) = \sum_{n=1}^{\infty} dd I_{o,n} \sin(n\omega_o t + \theta_I + \phi_n)$$

(2.29)

respectively,

where:

$$V_{o,n} = \sqrt{(V_{s,o} \cdot A_n + B_n \cdot X_{L_o} \sin \phi_n)^2 + (B_n \cdot X_{L_o} \cos \phi_n)^2}$$

(2.30)

$$\frac{1}{1_{0,n}} = \frac{|V_{0,n}|}{|Z_{1,n}|} \tag{2.31}$$

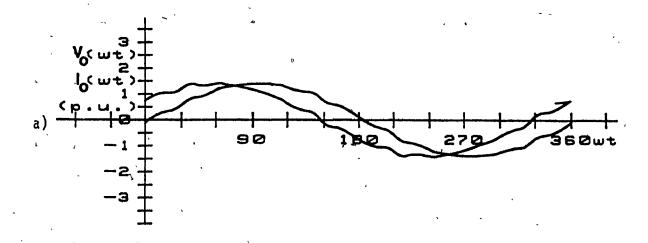

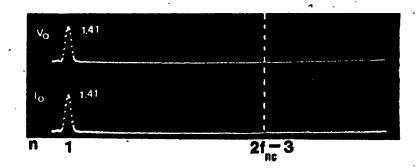

Fig. 2.7: Simulated waveforms with their respective frequency spectra for load voltage and current,  $V_{o}(\omega t)$  and  $I_{o}(\omega t)$ , obtained with  $P_{f}$ =0.8 leading,  $M_{\tilde{f}}$ =1 and  $f_{nc}$ =7.

and where:

- Z<sub>L,n</sub> is the load impedance at the nth harmonic frequency,

- $\theta_{\mathbf{v}}$  is the voltage phase shift introduced by the output filter /

- $\boldsymbol{\theta}_{\boldsymbol{I}}$  is the current phase shift introduced by the output filter

Finally, the simulated waveforms with their respective spectra for load voltage and current quantities,  $V_0(\omega t)$  and  $I_0(\omega t)$ , are shown in Figs. 2.7(a) and (b). These waveforms have been obtained by incorporating the expressions (2.28), (2.29), (2.30) and (2.31) in the computer program in Appendix A.

## 2.3.5 <u>Inverter stage input filter</u>

The factors affecting the reactive components  $(L_s,C_s)$  of the inverter stage input filter are:

- a). The specified filter inductor current ripple factor,  $K_{i}$

- b) The specified filter capacitor voltage ripple factor,  $K_{v_s}$ .

- c) The specified switching frequencies of the HF link and inverter stage.

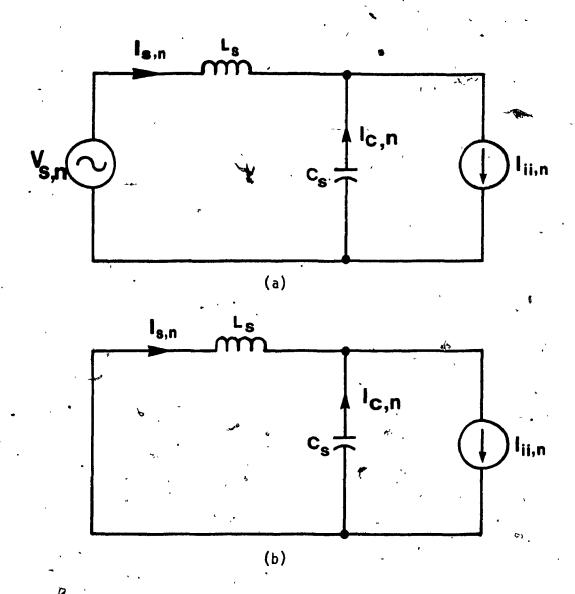

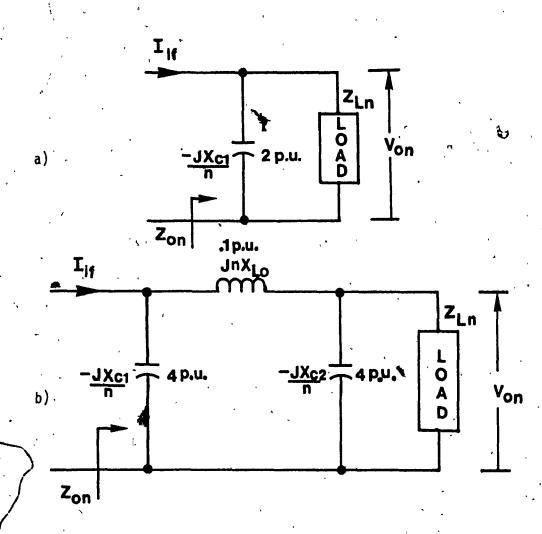

Fig. 2.8(a) shows the harmonic equivalent circuit of the inverter stage input filter. As it can be seen the filter is subjected to two types of harmonics. Current harmonic components reflected by the

inverter stage and voltage harmonic components generated by the HF link stage. However, since the switching frequency of the HF link is normally much higher than the switching frequency of the inverter stage, the main contributor to the size of the filter is the second-order harmonic component that is reflected by the inverter stage.

Therefore, the final harmonic equivalent circuit can be presented as shown in Fig. 2.8(b).

Regarding Fig. 2.8(b) the filter inductor current and filter capacitor voltage are given by,

$$I_{s,n} = \frac{1}{n^2 \chi_{L_{s,1}}} I_{ii,n}$$

$$\frac{\chi_{C_{s,1}}}{\chi_{C_{s,1}}} - 1$$

(2.32)

$$V_{s,n} = \frac{nX_{L_{s,1}}^{X_{C_{s,1}}}}{n^{2}X_{L_{s,1}}^{X_{C_{s,1}}}} I_{ii,n}$$

(2.33)

where:

is the amplitude of the nth harmonic component of the filter inductor currert,

is the reactance of the filter inductor and operating frequency,

n is the harmonic order.

The filter inductor current ripple factor (Appendix C),  $K_{i_s}$ , and filter capacitor voltage ripple factor,  $K_{v_s}$ , are given by

Fig. 2.8: Determination of the inverter stage input ripple current and input ripple voltage.

- a) Harmonic equivalent circuit of the inverter stage input filter

- b) Final harmonic equivalent circuit of the inverter stage input filter

$$K_{1s} = \frac{\left[\sum_{n=1}^{\infty} {}^{1}S, n(rms)\right]^{1/2}}{I_{s,0}} \simeq \frac{I_{s,2(rms)}}{I_{s,0}}$$

$$K_{v_{s}} = \frac{\left[\sum_{n=1}^{\infty} {}^{v_{s,n}(rms)}\right]^{1/2}}{v_{s,0}} \simeq \frac{v_{s,2(rms)}}{v_{s,0}}$$

(2.34)

where:

I<sub>s,o</sub> is the dc component of the filter inductor current = I<sub>ii,o</sub>,

Is,2(rms) is the rms value of the second-order harmonic component of the filter inductor-current,

$V_{s,o}$  is the dc component of the filter capacitor voltage,

V<sub>s,2</sub>(rms) is the rms value of the second-order harmonic component of the filter capacitor voltage.

Substituting eqns. (2.32) and (2.33) into eqns. (2.34) and (2.35)

$$K_{i_{s}} = \frac{X_{L_{s,1}}}{X_{C_{s,1}} - 1} I_{i_{s,0}} (2.36)$$

$$K_{v_{s}} = \frac{2X_{L_{s,1}} X_{C_{s,1}}}{(4X_{L_{s,1}} X_{C_{s,1}}) V_{s,0}} I_{ii,2(rms)}$$

(2.37)

Consequently, substituting exps. (2.12), (2.20) and (2.22) into exps. (2.36) and (2.37) the relations of the filter components as a function of the ripple factors are given by

$$\frac{X_{L_{s,1}}}{X_{C_{s,1}}} = \frac{0.25}{K_{i_s}} + K_{i_s} \quad \text{p.u.}$$

(2.38)

$$\frac{X_{L_{s,1}} X_{C_{s,1}}}{4X_{L_{s,1}} - X_{C_{s,1}}} = 1.414 K_{v_s} p.u.$$

(2.39)

Therefore, given the allowable values of  $K_{1_S}$  and  $K_{V_S}$  and solving the system of eqns. (2.38) and (2.39) the filter component values can be obtained.

## 2.3.6 HF link stage

Depending on the output power requirements of the inverter one of the following configurations of the DC to DC converters can be used as a HF link in order to regulate DC bus of the inverter stage.

# 2.3.6.1 Flyback configuration

Regarding Fig. 2,3(a)

$$\frac{V_{S,0}}{V_{D}} = \frac{N_{S}}{N_{D}} \left( \frac{D}{1-D} \right) \tag{2.40}$$

where:

$N_{p}$  is the isolation transformer primary winding number of turns,

$N_{\rm S}$  is the isolation transformer secondary winding number of turns.

V<sub>p</sub> is the voltage across the primary of the isolation transformer,

V<sub>s,o</sub> is the dc component of the inverter stage input voltage,

D is the Duty cycle = Transistor ON time

Transistor OFF time

but since  $V_p$  is equal to E and using eqn. (2.12) then eqn. (2.40) becomes

$$\frac{N_{S}}{N_{D}} = \frac{\sqrt{2} K_{C}(1-D)}{D}$$

(2.41)

where:

$$K_{C} = \frac{V_{o(rms)}}{E}$$

(2.42)

The number of turns in the primary of the transformer is given by [19]

$$N_{p} = \frac{E \times 10^{8}}{4.44 f_{\varrho} A_{c} B_{max}}$$

(2.43)

where:

is the switching frequency of the HF link stage,  $A_{c}$  is the transformer core cross section area in cm<sup>2</sup>,  $A_{c}$  is the maximum flux density in Gauss (1 Weber/cm<sup>2</sup> =  $10^{8}$  Gauss).

Regarding Fig. 2.3(a) the peak current that flows through the primary of the isolation transformer is given by

$$\hat{I}_{p} = \hat{I}_{s} \left( \frac{N_{s}}{N_{p}} \right) \tag{2.44}$$

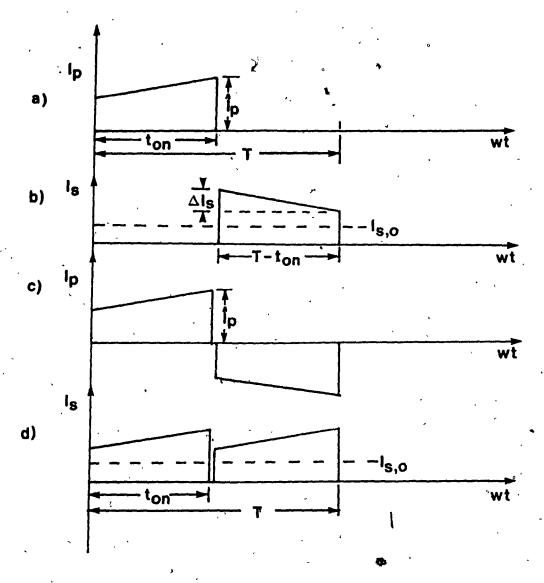

From Figs. 2.9(a) and (b), which illustrate the waveforms of the current that flows through the primary and secondary windings of the isolation transformer, can be shown that

$$\hat{I}_{S} = \frac{I_{S,0}(max)}{(1-D)} + \frac{\Delta I_{S}}{2}$$

(2.45)

where:

$\Delta I_{S^{\circ}}$  is the peak to peak allowable inverter stage input ripple current given by

=

$$2\sqrt{2} K_{is} I_{s,o(max)}$$

(2.46)

is the inverter stage input filter inductor current

ripple factor,

$I_{s,o(max)}$  is the maximum dc component supplied to the inverter stage and is given by eqn. (2.21).

Therefore, substituting eqns. (2.21), (2.45) and (2.46) into (2.44) and assuming maximum duty cycle equal to 0.45 then

$$\hat{I}_p = 1.22K_c(2.2 + \sqrt{2} K_i) p.u.$$

(2.47)

Regarding Fig. 2.3(a) the peak voltage across transistor  $Q_1$  during OFF period is given by

$$\hat{V}_{CE(Q_1)} = E + (\frac{N_p}{N_s}) V_{s,o}$$

(2.48)

and by using eqns. (2.41), (2.42) and (2.13) then eqn. (2.48) for maximum duty cycle of 0.45 becomes

$$\hat{V}_{CE(Q_1)} = \frac{1.8}{K_c} \text{ p.u.}$$

(2.49)

# 2.3.6.2 Push-Pull and Full bridge configurations

Since for the Push-Pull and Full bridge configurations the voltage across the primary of the isolation transformer is equal to E (Figs. 2.3 (b) and (c)) then the transformer turns ratio is given by

$$\frac{N_{s}}{N_{p}} = \frac{V_{s,0}}{2 E D_{max}} = \frac{\sqrt{2} K_{c}}{2 D_{max}}$$

(2.50)

The peak current that flows through the primary of the transformer excluding the magnetizing current is given by

$$\hat{I}_{p} = \hat{I}_{s} \left( \frac{N_{s}}{N_{p}} \right) \tag{2.51}$$

From Figs. 2.9(c) and (d), which illustrates the waveforms of the current that flow through the primary and secondary windings of the transformer, can be shown that

$$\hat{I}_{s} = \frac{I^{1/2}}{2D_{max}} + \sqrt{2} K_{i_{s}} I_{s,o(max)}$$

=

$$I_{s,o(max)} (\sqrt{2} K_{1s} + \frac{1}{2D_{max}})$$

(2.52)

Assuming that the maximum duty cycle is equal to 0.45 and using eqns. (2.21), (2.50) and (2.52) then eqn. (2.51) becomes

$$\hat{I}_{p}^{i} = 1.1 K_{c} (1.1 + \sqrt{2} K_{1s}) p.u.$$

(2.53)

Also, assuming that the magnetizing current is 10% of  $\hat{I}_p$  then the total peak current that flows through the primary is given by

$$\hat{I}_{c} = 1.2 \text{ K}_{c} (1.1 + \sqrt{2} \text{ K}_{1}) p.u. \qquad (2.54)$$

# 2.4 Inverter system main component ratings

In this section the ratings of the inverter main components are given as follows:

Fig. 2.9: Isolation transformer primary and secondary currents.

- (a), (b) Flyback configuration

- (c), (d) Push-Pull and Full bridge configurations

## Inverter Stage

Peak switch current

$$I_{PS} = \sqrt{2} p.u.$$

(2.55)

RMS switch current

$$I_{RS}^{-} = \frac{\sqrt{2}}{2} p.u.$$

(2.56)

Average switch current

$$I_{AS} = \frac{\sqrt{2}}{\pi} p.u.$$

(2.57)

## HF Link Stage

a) Flyback configuration

Peak switch current

$$I_{PS} = 1.22 K_c(2.2 + \sqrt{2} K_1)$$

p.u. (2.58)

Peak forward blocking voltage =

$$\frac{1.8}{K_c}$$

p.u. (2.59)

b) Push-Pull configuration

Peak swith current

$$I_{PS} = 1.2 K_c (1.1 + \sqrt{2} K_{i_c}) p.u.$$

(2.60)

c) Full-bridge configuration

Peak switch current

$$I_{PS} = 1.2 K_c (1.1 + \sqrt{2}K_c)$$

p.u. (2.62)

# 2.5 Design example

In order to illustrate the significance and facilitate the understanding of theoretical results obtained in previous sections the following example is given.

f = Inverter system output frequency = 60Hz

fnc = Normalized carrier frequency = 80

$f_{n\ell} = \frac{f_{\ell}}{f_{\ell}} = Normalized link switching frequency = 350$

Ky = Inverter stage input filter capacitor voltage

s

ripple factor = 0.01

= Inverter stage input filter inductor current

s

ripple factor = 0.2

Thus

1 p.u. volts = 86 V

1 p.u. current = 2 A

1 p.u. impedance =  $\frac{86}{2}$  = 43  $\Omega$

1 p.u. frequency =  $2\pi f_0$  = 377 rad/sec

Because of the output power requirements the flyback configuration inverter is chosen. From the above p.u. values and using eqn. (2.27) the output filter components are obtained

$$\frac{x_{L_{0,1}}}{x_{C_{0,1}}} = c_0 L_0 = \frac{9.32}{(2 \times 80 - 3)^2} = 3.78 \times 10^{-4} \text{ p.u.}$$

(E1)

If a 0.5 p.u. capacitance is chosen for the output filter and using exp. (E1)

$$\chi_{C_{0,1}} = \frac{1}{\omega_0^C} = \frac{1}{1 \times 0.5} = 2 \text{ p.u.}$$

(E2)

$$C_0 = \frac{1}{2 \times 43 \times 377} = 30.8 \, \mu \text{F}$$

(E3)

$$X_{L_{0,1}} = \frac{3.78 \times 10^{-4}}{0.5} = 7.56 \times 10^{-4} \text{ p.u.}$$

(E4)

$$L_{o} = \frac{X_{L_{o},1}}{\omega_{o}} = \frac{7.56 \times 10^{-4} \times 43}{377} = 86 \text{ } \mu\text{H}$$

(E5)

Using eqns. (2.38) and (2.39) the inverter stage input filter components are given by

$$\frac{X_{L_{s,1}}}{X_{C_{s,1}}} = \frac{0.25}{0.2} \neq 0.2 = 1.3 \text{ p.u.}$$

(E6)

$$\frac{X_{L_{s,1}} X_{C_{5,1}}}{4X_{L_{s,1}} - X_{C_{s,1}}} = (1.414)(0.01) = 0.0141 \text{ p.u.}$$

(E7)

Solving the system of eqns. (E6) and (E7)

70

$$X_{C_{s,1}} = 0.046 \text{ p.u.}$$

(E8)

$$X_{L_{s,1}} = 0.06 \text{ p.u.}$$

(E9)

$$C_s = \frac{1}{0.046 \times 43 \times 377} = 1.341 \ \mu F$$

(E10)

$$L_s = \frac{0.06 \times 43}{377} = 6.84 \text{ mH}$$

(E11)

If the maximum duty cycle is taken to be 0.45 and using exp. (2.4) the isolation transformer turns ratio is given by

$$\frac{N_S}{N_p} = \frac{(\sqrt{2})(1.8)(1-0.45)}{0.45} \approx 3$$

(E12)

Finally, using exps. (2.55) through (2.59) the ratings of inverter main components are:

#### HF 11nk stage

Peak forward and reverse blocking voltage = 86 volts (E14)

#### Inverter stage

Peak switch current =

$$(\sqrt{2})(2)$$

= 2.82 Amps (E15)

RMS switch current =

$$(\sqrt{2})(2) = 1.414$$

Amps (E16)

Average switch current =

$$(\frac{\sqrt{2}}{\pi})(2) = 2.25$$

Amps (E17)

### 2.6 Control circuit and experimental results

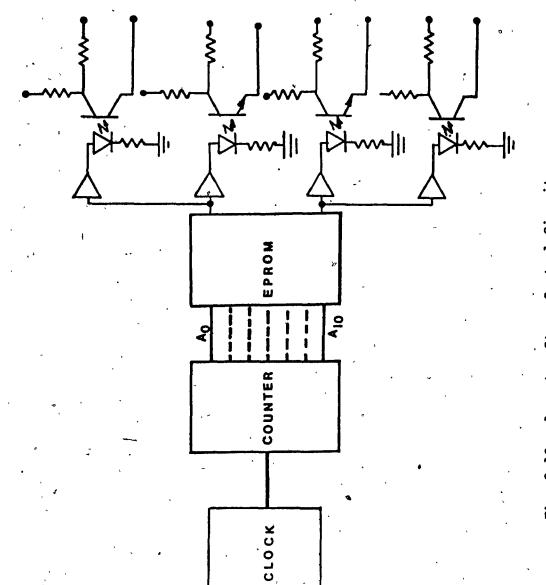

There are numerous control circuits already developed for any of the three configurations of the HF link stage [20], [21]. Therefore, there is no necessity for further explanations. For the inverter stage, the control circuit shown in Fig. 2.10 has been utilized. The intersection points between the reference and carrier signals (Fig. 2.4(a)) were stored in a 16K bit EPROM. The resolution used was 0.2 degrees/bit. The overlapping protection delays between transistors in the inverter stage were incorporated in the gating signals stored in the EPROM.

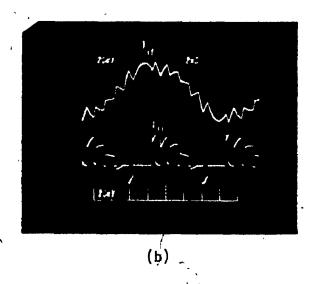

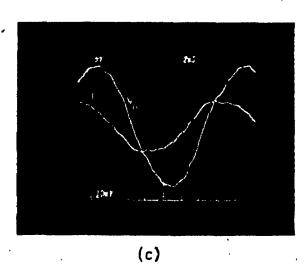

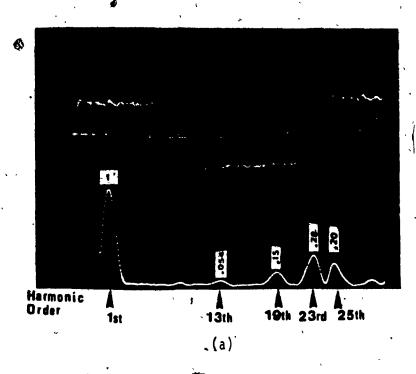

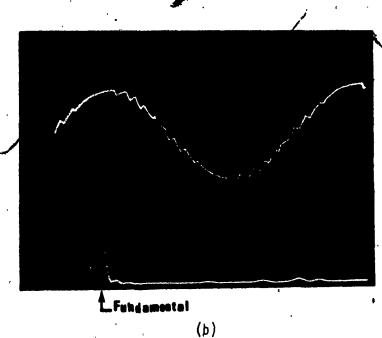

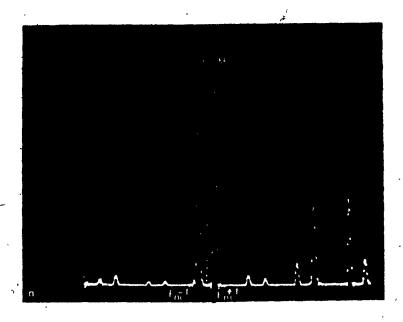

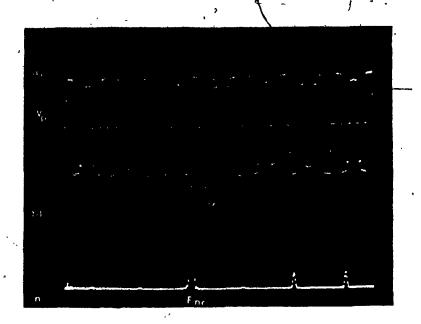

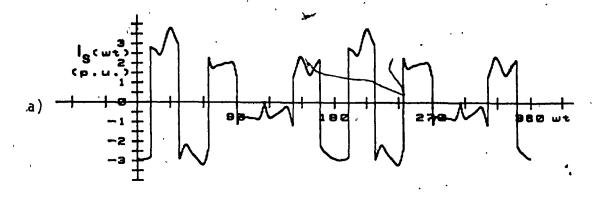

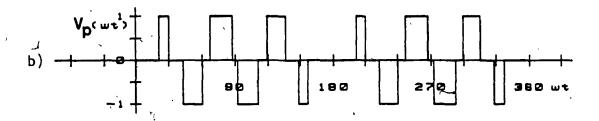

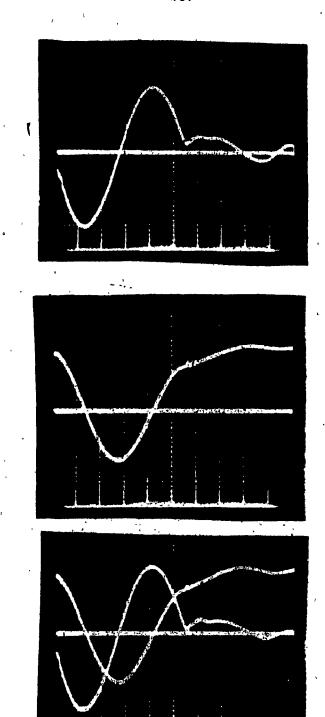

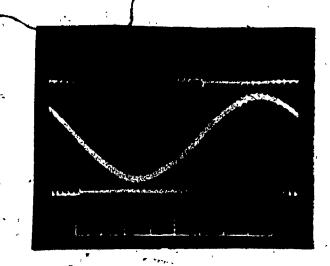

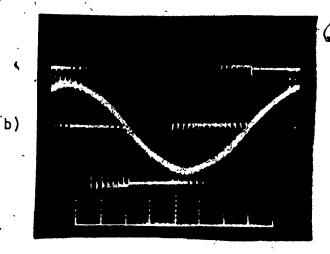

In order to illustrate the significance and facilitate the understanding of theoretical results obtained in previous sections the flyback configuration inverter was built using power MOSFET transistors. Fig. 2.11 shows the experimental results which are in close agreement with the theoretical ones (Figs. 2.5(a), 2.6(a), 2.7(a)).

Fig. 2.10: Inverter Stage Control Circuit.

Man I is a second

Fig. 2.11: Experimental results obtained with  $P_f=0.8$  leading,  $M_f=1$  and  $f_{nc}=7$ .

- a) Voltage and current waveforms before output filtering,  $v_{if}(\omega t)$  and  $I_{if}(\omega t)$

- b) Top: Current waveform before output filtering,  $I_{if}(\omega t)$ Bottom: Inverter stage input current waveform,  $I_{ii}(\omega t)$

- c) Load voltage and current waveforms,  $V_0(\omega t)$  and  $I_0(\omega t)$

## 2.7 Conclusions

In this chapter, a novel two stage DC to AC inverter has been presented. The main inverter features included an HF link stage for transformer isolation and a regulated DC bus for the inverter stage. The proposed inverter system has been analyzed with various HF link configurations suitable for different output power levels. Theoretical and experimental results have shown that the proposed two stage inverter system yields high operating efficiency, programmable output frequency and high power density. Finally, when an extra power "leg" is inserted in the inverter stage, the proposed conversion scheme can be extended to three-phase output system.

#### CHAPTER 3

#### A CURRENT SOURCE DC TO AC INVERTER USING A DC TO DC CONVERTER AS HIGH FREQUENCY LINK

## 3.1 Inteduction

Of the various converter topologies available for power inversion.

Current Source Inverts (CSI) seem to offer certain advantages over the

Voltage Source Inverters (VSI). The former inverters are characterized

by a DC link input which behaves as a DC current source, through the

action of a front end converter and a current regulation loop. The latter

are characterized by a DC link input which behaves as a DC voltage source.

The principle of operation for VSI's is to supply power to the load by holding the output voltage fixed (in phase) relative to the VSI switching function. Consequently, the output current is forced to fluctuate back and forth from negative to positive. Since the semiconductor switches are unidirectional current devices, the VSI needs free wheeling diodes to operate under these conditions.

In the CSI, the output current is held fixed (in phase) relative to the CSI switching function. Consequently, the output voltage is forced to fluctuate from positive to negative. Thus, the need for free wheeling diodes is eliminated. However, the semiconductor switches must now be capable of blocking reverse voltage (If not a diode must be connected in series).

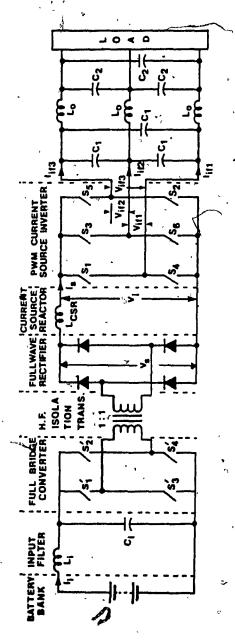

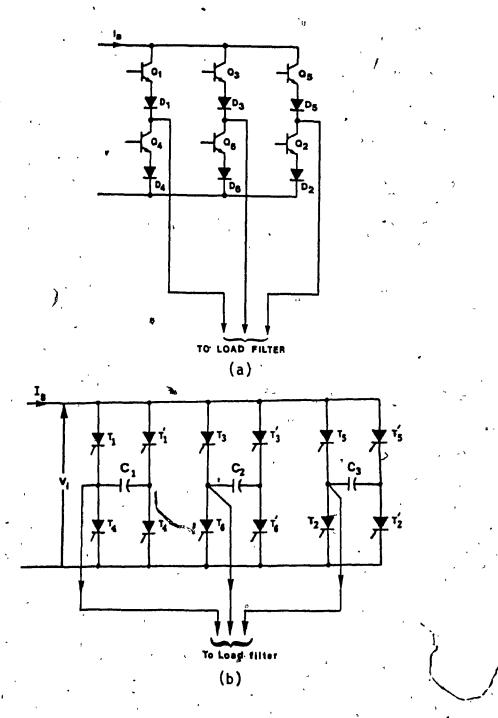

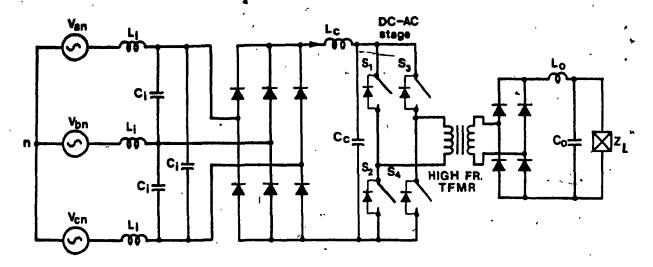

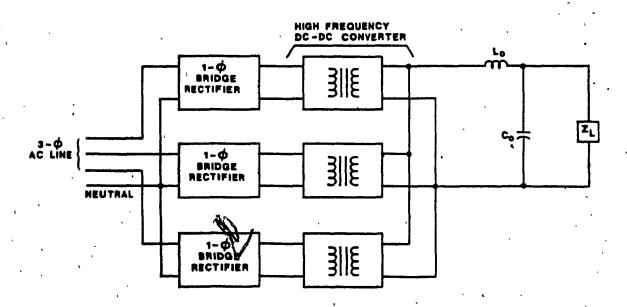

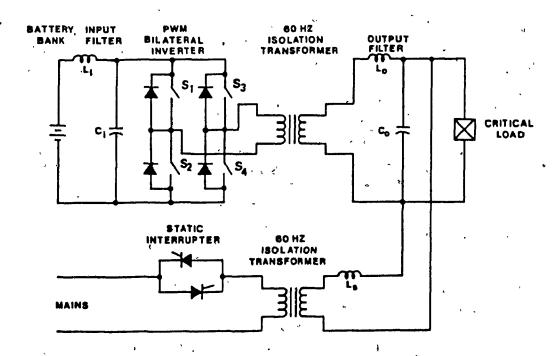

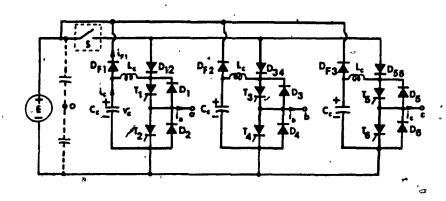

A schématic diagram of the proposed CSI system is shown in Fig.

3.1 which has the following advantages and disadvantages when compared to VSI (Fig. 2.2).

#### a) Advantages

i) Since the input DC current is controlled and limited, misfiring of the inverter switches or short circuit in the load is not catastrophic.

Fig. 73.1: Schematic diagram of the proposed Current Source Inverter.

- inverter to handle reactive or regenerative loads without the use of free wheeling diodes, in contrast to the VSI which reverses its link current.

- iii) The power semiconductor switches are subjected to lower peak current stresses because of the constant supply current.

- vi) Since current spikes are filtered by the Current Source Reactor (CSR), the Electromagnetic Interference (EMI) of the CSI is reduced.

- v) When thyristors are used to realize the CSI power switches, the commutation inductor is eliminated from the commutation circuit.

## b) Disadvantages

- i) Utilizes a relatively large DC filter reactor to exhibit current source characteristics. This is especially true for single-phase output inverter configuration and three-phase configuration under unbalanced load conditions. However, for three phase inverter configuration with balanced load (3-φ synchronous machines), the size of the filter inductor is considerably reduced.

- ii) Exhibits slow current response because of the utilization of the large DC filter reactor.

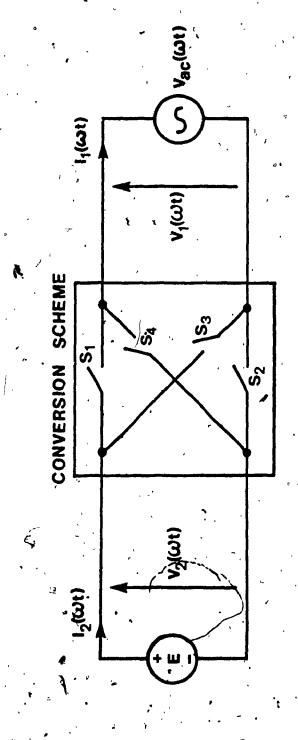

# 3.2 System description 3

A brief description of the function performed and configuration for each system section of the proposed CSI system (Fig. 3.1) is as follows.

#### 3.2.1 High Frequency link converter

The function of the high frequency (HF) link converter is twofold: First, it controls the current level of the current source in response to changes in load and/or changes in the DC voltage feeding the HF link. Second, it provides transformer isolation between the source and the load using a high frequency transformer. The choice of the power switches is based on the output power requirements and input DC bus.

## 3.2.2° Current Source Reactor (CSR)