National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa Ontario K1A 0N4 Bibliotheque nationale du Canada

Direction des acquisitions et des services bibliographiques

395 rue Wellington Ottawa (Ontario) K1A 0N4

Your fee. Notice reference

Carlie Notice reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photopopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# TEST CASE GENERATION AND FAULT DIAGNOSIS METHODS FOR COMMUNICATION PROTOCOLS BASED ON FSM AND EFSM MODELS

Ramalingom Thavasinadar

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy at

Concordia University

Montréal, Québec, Canada

September 1994

© Ramalingom Thavasinadar, 1994

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rua Wellington Ottawa (C<sub>1</sub> tario) K1A 0N4

Your Me Votre reference

Our life. Notre référence

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS.

L'AUTEUR A ACCOPLE. UNE LICENCE IRREVOCABLE FT NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION.

L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODU. TS SANS SON AUTORISATION.

ISBN 0-612-01277-8

#### ABSTRACT

## TEST CASE GENERATION AND FAULT DIAGNOSIS METHODS FOR COMMUNICATION PROTOCOLS BASED ON FSM AND EFSM MODELS

Ramalingom Thavasinadar, Ph.D., Concordia University, 1994

Conformance testing is essential for assuring if an implementation of a computer communication protocol is according to its standard specification. This thesis addresses the problem of 'est case generation as well as the problem of fault diagnosis from a specification which is represented as a Finite State Machine (FSM) or an Extended Finite State Machine (EFSM).

A new problem, called the Basic UIS Assignment Problem (BUAP), is defined. An efficient algorithm based on the Maximum Cardinality Two Matroid Intersection Problem is proposed for selecting a minimum number of transitions and an assignment of an Unique Input Sequence (UIS) for each of these transitions such that the resulting test graph has the minimum number of connected components. Three heuristic algorithms are developed for solving the asymmetric Rural Postperson Problem (RPP). Finally, a new method which combines the solutions to the BUAP and the RPP with the MU-method [SL92] is proposed for generating a minimal length test sequence for any strongly connected FSM which has at least one UIS for each state.

After analyzing the existing FSM-based test sequence generation methods for their fault detection and diagnosis capabilities, we propose two new fault diagnosis methods: the UIDD-method and the CSDD-method for implementations with at most one output or transfer fault. The UIDD-method minimizes the length of the test sequence using the RPP and it provides better fault diagnosis capability than all the UIS-based methods analyzed. This method is illustrated on the NBS TP4 transport protocol. The CSDD-method uses the Characterizing Sequences instead of the UISs and guarantees a superior fault diagnosis capability.

A new methodology is proposed for generating test cases from an EFSM A new type of UIS, called a Context Independent Unique Sequence (CIUS), is defined and an algorithm is developed for computing a CIUS set. Our trans-CIUS-set control flow criterion is to apply the CIUS of every state at the tail state of every transition. Our def-use-ob data flow criterion enables the def-use associations to be externally observable. A two phase breadth first search algorithm is presented for generating a set of executable test cases for the required criteria. The methodology is demonstrated on a class 2 transport protocol.

TO MY PARENTS AND TEACHERS

## Acknowledgments

Lexpress my deepest gratitude to my thesis supervisors Professor K. Thulasiraman and Dr. Anindya Das. The technical guidance and the long discussions we had throughout the course of this thesis were truly valuable.

I am thankful to Professor Jeremiah F. Hayes and Dr. Marc A. Comeau for their suggestions and moral support.

I owe thanks to the members of the PROSOFT research group of University of Montreal which enriched my knowledge in Protocol Engineering. In particular, I am grateful to Professor G. v. Bochmann and Dr. Rachida Dssouli.

I am indebted to all my friends in Montreal for making my stay here pleasant and enjoyable.

Last but not the least, I thank my mother, wife and my late father for their constant inspiration and support.

## Contents

|   | LIS | T OF ABBREVIATIONS                              | х   |

|---|-----|-------------------------------------------------|-----|

|   | LIS | T OF FIGURES                                    | xi  |

|   | LIS | T OF TABLES                                     | xiv |

| 1 | INT | TRODUCTION                                      | 1   |

|   | 1.1 | Conformance Testing                             | :   |

|   | 1.2 | Finite State Machine Model                      | 1   |

|   |     | 1.2.1 Fault Model for FSM                       | (   |

|   | 1.3 | Review of Literature                            | 7   |

|   |     | 1.3.1 FSM-Based Test Sequence Generation        | 7   |

|   |     | 1.3.2 Fault Diagnosis Methods                   | 11  |

|   |     | 1.3.3 EFSM-Based Test Sequence Generation       | 12  |

|   | 1.4 | Expressing Algorithms                           | 19  |

|   | 1.5 | Scope of the Thesis                             | 1!  |

| 2 | TES | ST CASE GENERATION FROM FSM MODEL               | 22  |

|   | 2.1 | Graphs and Matroids                             | 2:  |

|   | 2.2 | UIS-Based Methods and the Need for a New Method | 26  |

|   |     | 2.2.1 The U-method                              | 27  |

|   |     | 2.2.2 MU-method                                 | .)} |

|   |                                                | 2.2.3 Motivation for the New method                   |  |  |  |  |  |

|---|------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

|   | 2.3                                            | Basic UIS Assignment Problem                          |  |  |  |  |  |

|   |                                                | 2.3.1 An Illustration of BUAP                         |  |  |  |  |  |

|   | 2.4                                            | Algorithms for the Rural Postperson Problem           |  |  |  |  |  |

|   |                                                | 2.4.1 A Heuristic Algorithm Based on Augmentations 47 |  |  |  |  |  |

|   |                                                | 2.4.2 A Heuristic Algorithm Based on MST              |  |  |  |  |  |

|   |                                                | 2.4.3 A Heuristic Algorithm Based on Symmetry 56      |  |  |  |  |  |

|   | 2.5                                            | Generalized UIS testing method                        |  |  |  |  |  |

|   |                                                | 2.5.1 The GU-method                                   |  |  |  |  |  |

|   |                                                | 2.5.2 An Illustration                                 |  |  |  |  |  |

|   | 2.6                                            | Summary                                               |  |  |  |  |  |

| 3 | ANALYSIS OF FSM-BASED TEST SEQUENCE GENERATION |                                                       |  |  |  |  |  |

|   | ME                                             | THODS 67                                              |  |  |  |  |  |

|   | 3.1                                            | Test Sequence Generation Methods: Review and Analysis |  |  |  |  |  |

|   |                                                | 3.1.1 Distinguishing Sequence Method 69               |  |  |  |  |  |

|   |                                                | 3.1.2 Characterizing Sequences Method                 |  |  |  |  |  |

|   |                                                | 3.1.3 W-method                                        |  |  |  |  |  |

|   |                                                | 3.1.4 Transition Tour Method                          |  |  |  |  |  |

|   |                                                | 3.1.5 UIS-Based Methods                               |  |  |  |  |  |

|   |                                                | 3.1.6 Wp-method                                       |  |  |  |  |  |

|   | 3.2                                            | Comparison of Test Sequence Generation Methods 93     |  |  |  |  |  |

|   |                                                | 5.2.1 Fault Coverage and Diagnosis                    |  |  |  |  |  |

|   |                                                | 3.2.2 Length of Test Sequences Generated 95           |  |  |  |  |  |

|   | 3.3                                            | Summary                                               |  |  |  |  |  |

| 4 | FAU                                            | LT DIAGNOSIS METHODS 97                               |  |  |  |  |  |

|   | 4.1                                            | UIDD-method                                           |  |  |  |  |  |

|   | 1.2                                            | State Cover Tree and UIS Set Computation              |  |  |  |  |  |

|   |                                                |                                                       |  |  |  |  |  |

|   | 4.3 | An Illustration of the UIDD-method      | 111 |

|---|-----|-----------------------------------------|-----|

|   | 4.4 | CSDD-method                             | 123 |

|   | 4.5 | Fault Localization                      | 129 |

|   | 4.6 | Summary                                 | 132 |

| 5 | TES | ST CASE GENERATION FROM THE EFSM MODEL  | 133 |

|   | 5.1 | The EFSM Model                          | 135 |

|   |     | 5.1.1 An Example                        | 139 |

|   |     | 5.1.2 Unique Input Sequence             | 143 |

|   |     | 5.1.3 Control Flow Fault Model          | 111 |

|   | 5.2 | Test Case Selection Criteria            | 145 |

|   |     | 5.2.1 Control Flow Coverage             | 145 |

|   |     | 5.2.2 Data Flow Coverage                | 147 |

|   | 5.3 | CIUS Computation Algorithm              | 154 |

|   |     | 5.3.1 An Illustration                   | 170 |

|   | 5.4 | Data Flow Graph Manipulation            | 173 |

|   | 5.5 | Automatic Test Case Generation          | 182 |

|   |     | 5.5.1 The Two-Phase Algorithm           | 182 |

|   |     | 5.5.2 Fault Coverage                    | 197 |

|   | 5.6 | Transport Protocol Test Case Generation | 200 |

|   | 5.7 | The Feasibility Problem                 | 212 |

|   | 5.8 | Summary                                 | 21! |

| 6 | SU  | MMARY AND PROBLEMS FOR FUTURE STUDY     | 221 |

|   | 6.1 | Summary                                 | 22  |

|   | 6.2 | Problems for Future Study               | 22  |

|   | RII | RLIOGRAPHY                              | 227 |

## List of Abbreviations

BUAP Basic UIS Assignment Problem

CCITT — Comité Consultatif International Télégraphique et Téléphonique

CCS Cyclic Characterizing Sequence

CIUS Context Independent Unique Sequence

CS Characterizing Sequence

CSP Constraint Satisfaction Problem

DFG Data Flow Graph

DNF Disjunctive Normal Form

EFSM Extended Finite State Machine

EUIO Extended Unique Input Output

FDT Formal Description Technique

FSM Finite State Machine

GC Gomory Cut

IPP Integer Programming Problem

IS Identifying Sequence

ISO International Organization for Standardization

IUT FSM/EFSM Representation of an Implementation Under Test

LP Linear Programming

MCMIP Maximum Cardinality Matroid Intersection Problem

MC2MIP Maximum Cardinality Two-Matroid Intersection Problem

MST Minimum Weight Spanning Tree

OSI Open Systems Interconnection

PET Partial Enumeration Technique

RPP Asymmetric Rural Postperson Problem

RPT Asymmetric Rural Postperson Tour

SDL Specification and Description Language

SPEC FSM/EFSM Representation of a Specification

TCSD Property Tree Characterizing Set Disjoi at Property

TUISD Property Tree UIS Set Disjoint Property

UAP UIS Assignment Problem

UIO Unique Input Output

UIS Unique Input Sequence

## List of Figures

| 1.1 | ISO reference model for OSI                                       | 2    |

|-----|-------------------------------------------------------------------|------|

| 1.2 | Various aspects of Protocol Engineering                           | 2    |

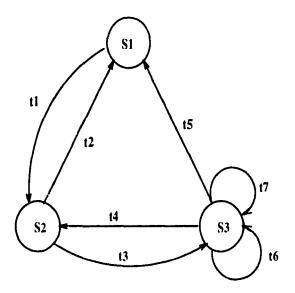

| 2.1 | Simplified transport protocol                                     | 30   |

| 2.2 | An FSM based on the INRES protocol: responder                     | 31   |

| 2.3 | Simplified alternating bit protocol (receiver)                    | 3:}  |

| 2.4 | Cycles in $G'$                                                    | 39   |

| 2.5 | G' for the FSM given in Figure 2.2                                | -4-1 |

| 2.6 | $G_H$ in the first iteration of $basic\_assignment$               | 44   |

| 2.7 | $G_H$ in the second iteration of $basic\_assignment$              | 4.5  |

| 2.8 | $G_H$ in the third iteration of $basic\_assignment$               | 46   |

| 2.9 | Flow graph for the FSM given in Figure 2.2.                       | 64   |

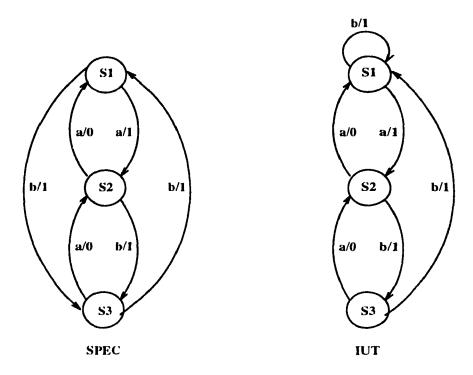

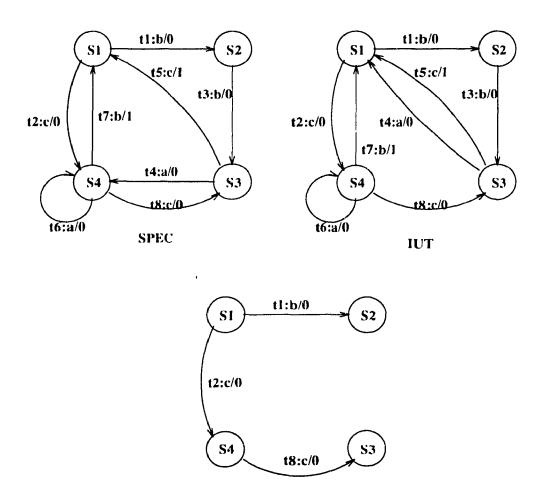

| 3.1 | An Example for the D-method                                       | 71   |

| 3.2 | Protocol passed by the C-method                                   | 75   |

| 3.3 | Illustration of the 1-fault resolution capability of the C-method | 76   |

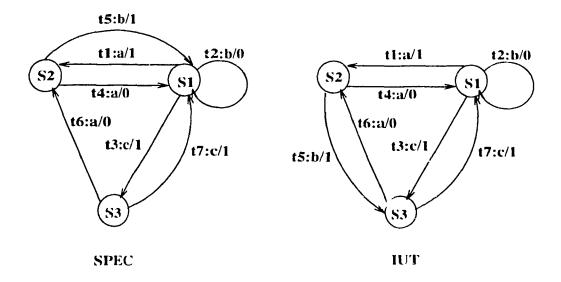

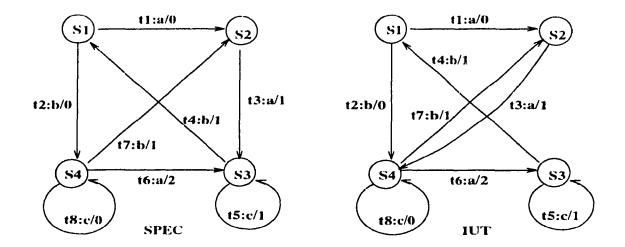

| 3.4 | An Example for the U-method                                       | 83   |

| 3.5 | Protocol passed by the Uv-method                                  | 86   |

| 3.6 | An Example for the Uv-method                                      | 88   |

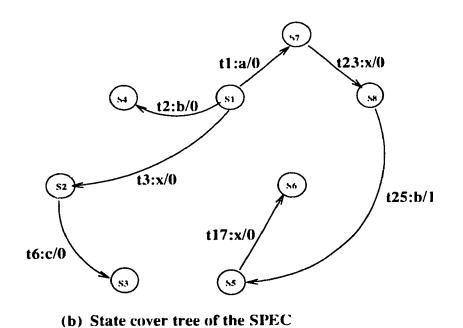

| 3.7 | State cover tree of the SPEC given in Figure 3.1(a)               | 91   |

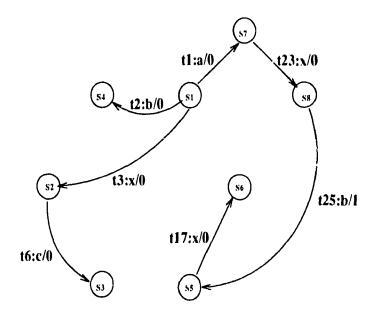

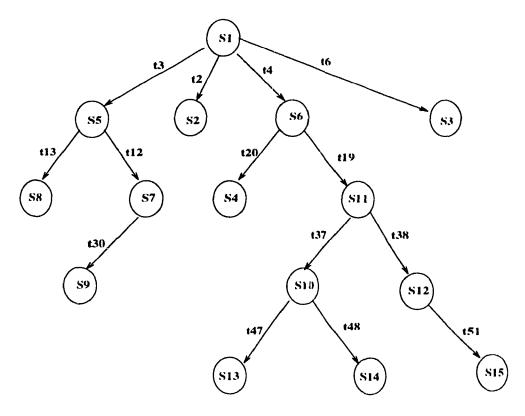

| 1.1 | SPEC and a state cover tree of an abstract protocol               | 115  |

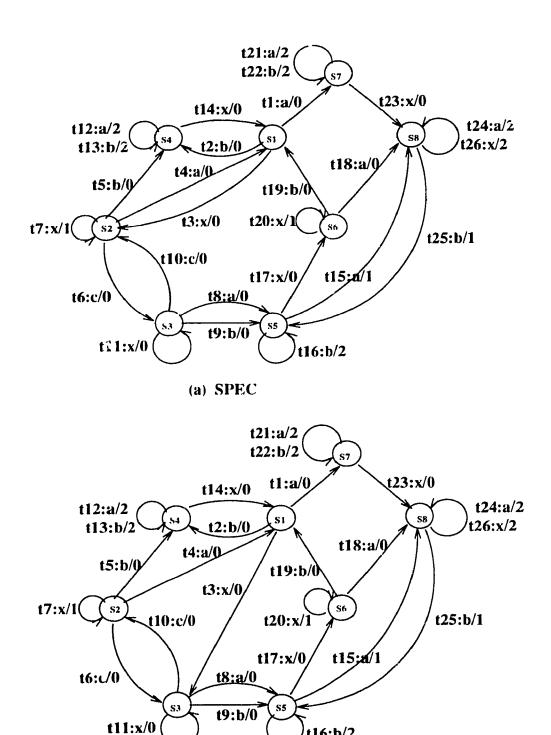

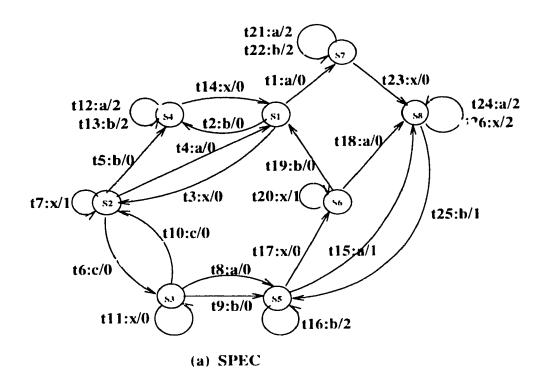

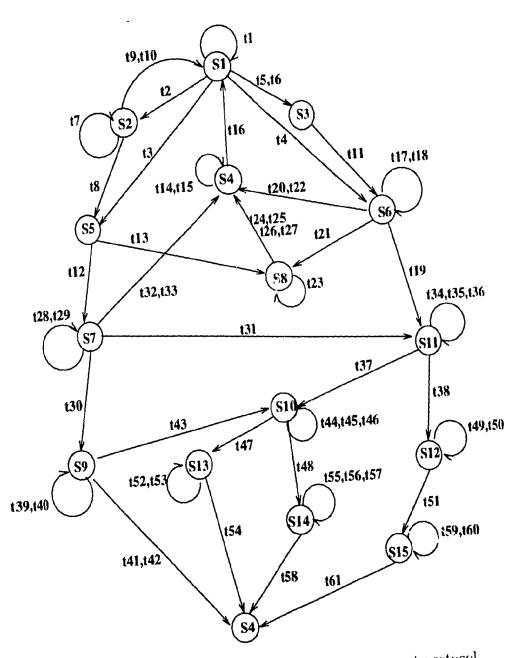

| 4.2 | A SPEC of a subset of NBS TP4 transport protocol                                  | 119 |

|-----|-----------------------------------------------------------------------------------|-----|

| 4.3 | A state cover tree of the transport protocol                                      | 121 |

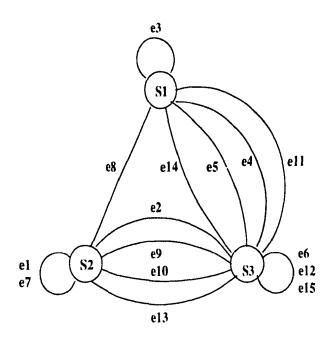

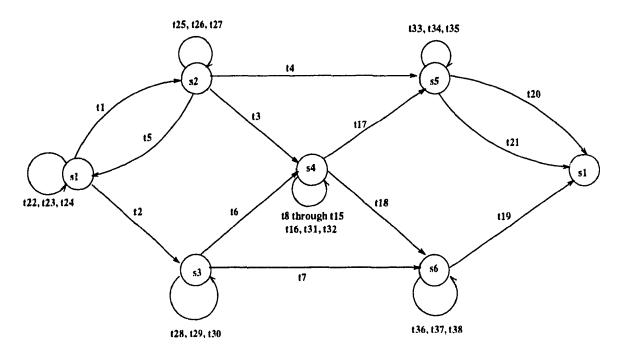

| 5.1 | An EFSM for the AP-module in the Class 2 transport protocol                       | 140 |

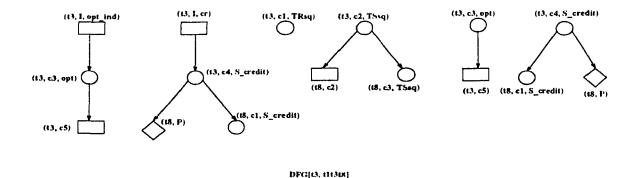

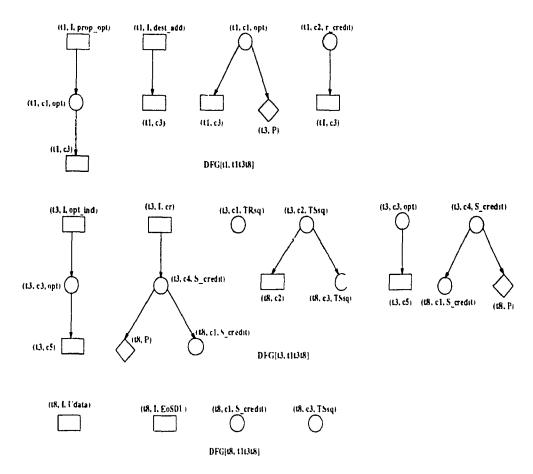

| 5.2 | A data flow graph for $t3$ with respect to the walk $t1t3t8$                      | 152 |

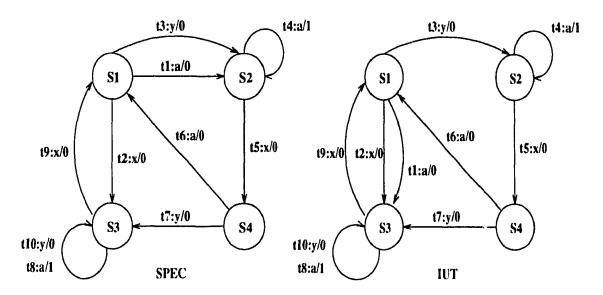

| 5.3 | Different walks with the same behavior sequence $a/o$                             | 151 |

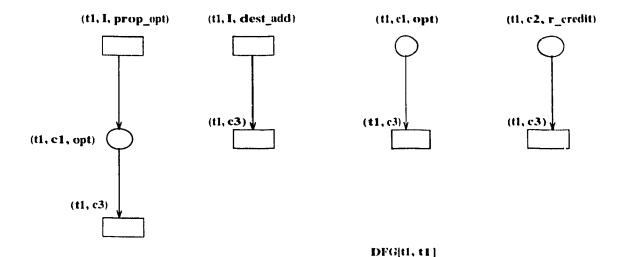

| 5.4 | Data flow graph for the transition $t1$ in the AP-module                          | 204 |

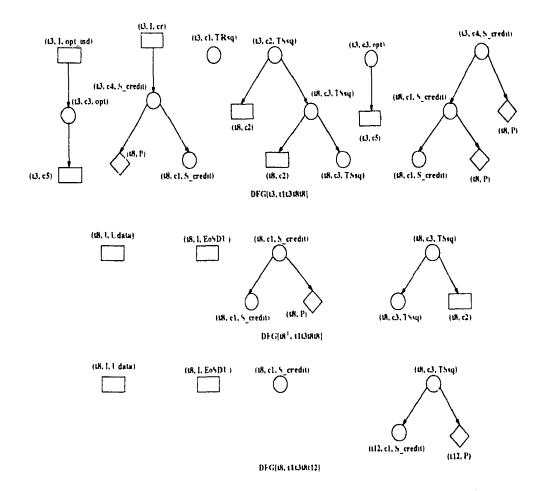

| 5.5 | Data flow graphs for $t1, t3, t8$ with respect to the walk $t1t3t8$ of the        |     |

|     | AP-module                                                                         | 205 |

| 5.6 | Data flow graphs for $t3$ and $t8^1$ with respect to $t1t3t8^1t8^2$ and $t8$ with |     |

|     | respect to $t1t3t8t12 = \dots$                                                    | 206 |

## List of Tables

| 2.1  | Labels for transitions in Figure 2.1                        | 30  |

|------|-------------------------------------------------------------|-----|

| 2.2  | UISs for states of the FSM shown in Figure 2.1              | 30  |

| 2.3  | Labels of the transitions in Figure 2.2                     | 31  |

| 2.4  | Valid UIS assignment without connected test graph           | 32  |

| 2.5  | Valid UIS assignment with connected test graph              | 33  |

| 2.6  | Edge description of $G'$ for the FSM given in Figure 2.2    | 43  |

| 2.7  | Parameters on the edges of the flow graph $G_f$             | 61  |

| 2.8  | UIS assignment using min-cost flow                          | 64  |

| 3.1  | Responses of the SPEC for the distinguishing sequence       | 70  |

| 4.1  | UISs selected by sct_uis for SPEC of Figure 4.1(a)          | 114 |

| 4.2  | Test subtours generated in the first phase of DD-method     | 116 |

| 4.3  | Subtours for testing $\mathcal{U}$ -transitions             | 116 |

| 4.4  | Subtours for testing the tail states of the UISs            | 117 |

| 4.5  | Tour for testing all non-T-transitions                      | 118 |

| 4.6  | Explanation of state symbol notations in transport protocol | 118 |

| 4.7  | Labels of the transitions of NBS-TP4 transport protocol     | 120 |

| 4.8  | UISs generated for the transport protocol                   | 121 |

| 4.9  | Subtours for testing the <i>U</i> -transitions              | 122 |

| 4.10 | An optimal tour for testing non-T- non-U-transitions        | 123 |

| 5.1 | Core transitions in the transport protocol                               | 1-i i |

|-----|--------------------------------------------------------------------------|-------|

| 5.2 | Core transitions in the transport protocol (Contd.)                      | 1.42  |

| 5.3 | Non-core transitions in the transport protocol                           | 142   |

| 5.4 | CIUSs for the states in the AP-module                                    | 172   |

| 5.5 | Data flow coverage in the AP-module                                      | 201   |

| 5.6 | Data flow coverage in the AP-module (contd.)                             | 202   |

| 5.7 | Data flow coverage in the AP-module (Contd.)                             | 203   |

| 5.8 | Preambles and control flow test tours for the transport protocol         | 207   |

| 5.9 | Preambles and control flow test tours for the transport protocol (Contd. | )208  |

## Chapter 1

### INTRODUCTION

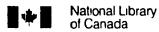

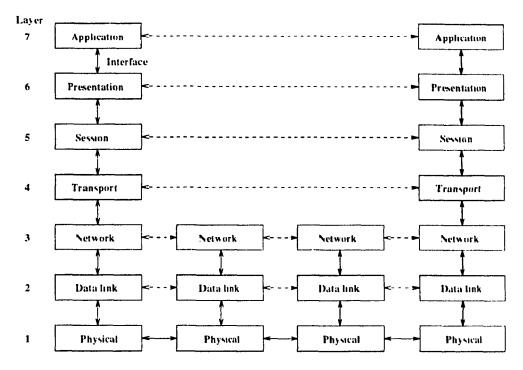

The Open Systems Interconnection (OSI) reference model [IS7498] of International Organization for Standardization (ISO) proposes a seven layer architecture for designing computer communication systems, as shown in Figure 1.1. Each layer performs a well defined function and it consists of many entities. Entities of a given layer communicate with the layer above (below) through service access points. Each layer functions according to a set of well defined rules known as the **protocol** of that layer. As protocols become highly complex systems, protocol design is becoming a challenging problem [Sar93]. A protocol engineering [Liu89] life cycle includes service and protocol specification, validation and verification, implementation, and conformance testing. Figure 1.2—shows the relationship between the different phases of the life cycle.

Traditionally, many protocols are specified in deterministic Finite State Machines (FSMs) [Boc78]. Standardization institutions such as ISO and Comité Consultatif International Télégraphique et Téléphonique (CCITT) have standardized specification languages, also called Formal Description Techniques (FDTs), such as LOTOS [IS8807, BB87], Estelle [IS9074, BD87] and the Specification and Description Language (SDL) [SDL88] for specifying distributed systems, in general, and protocol standards, in particular. While Estelle and SDL are based on the Extended Finite

Figure 1.1: ISO reference model for OSI

Figure 1.2: Various aspects of Protocol Engineering

State Machine (EFSM) model, LOTOS is based on the Calculus of Communicating Systems [Mil89], the Communicating Sequential Processes [Hoa85] and ACTONE [EM85].

Validation of a protocol is a process of checking the (standard) specification for logical self-consistency; it is normally done by checking if the specification satisfies the safety and liveness properties [Zaf78, ZWR+80]. Protocol verification is the process of verifying whether the specification provides the required functions of the protocol as per its service specification [Sab88]. Once the specification is validated and verified, the implementation phase begins. Semi-automatic tools are being developed for deriving an implementation of a protocol from its specification [BGS87, SF87, JJ89, SS91b, SS91a, Bud92, Tel93]. Since the implementation phase involves human interactions, the implementation is error-prone [Nai92]. Therefore, in order to achieve the interworking of heterogeneous computers, the ultimate goal of OSI, it is important to test for the correctness of the implementations of a protocol against its formal specification. Conformance testing [IS9646] is the most practical way of testing an implementation and it has been an active area of research.

#### 1.1 Conformance Testing

Conformance testing of a protocol implementation is intended to assure that the implementation is equivalent to the standard specification of the protocol [Sta93, IS9646]. It involves the generation of test suite from the specification, execution of the test suite on the implementation under a suitable test environment, and analysis of the test results [IS9646, Ray87]. The OSI conformance testing methodology and framework [IS9646] defines a test suite as a set of test cases, where a test case is a set of protocol event sequences. Each test case has an associated purpose of testing a specific protocol function. Also, a verdict of pass, fail, or inconclusive is assigned to each event sequence in a test case. A verdict of a sequence depends on the purpose of

the test case for which it is a member as well as the specification. During conformance testing the implementation under test is viewed as a black box with some **Points of Control and Observation (PCOs)**. Various test architectures for executing the test suite on an implementation are also standardized in [1S9646].

ISO has recently established a working group for studying the application of Formal Methods in Conformance Testing (FMCT) [FMC93]. One of the primary aims of the FMCT group is to enable computer-aided test suite derivation from protocol standards specified in FDTs. As a result, there has been a growing interest in developing methods for automatic test case generation from protocol standards. Since testing involves heavy costs, only a limited number of test cases of finite length are usually selected for testing. Hence, the quality of test cases generated has direct influence on the quality of the test result. Over the last fifteen years or so, research has been carried out for generating test cases of minimum cost with maximum fault coverage. Before reviewing the literature on the test case generation methods, we next introduce the widely used FSM model.

#### 1.2 Finite State Machine Model

An FSM M can be formally defined as a 5-tuple  $M = (S, s_1, I, O, T)$  where  $S = \{s_1, s_2, \ldots, s_n\}$  is the nonempty finite set of states of M,  $s_1$  is a designated state called the **initial state**, and I and O are nonempty finite sets of possible inputs and outputs of the protocol, respectively. The transition function T is a partial function defined as  $T: S \times I \to S \times O$ .  $T(s_i, a) = (s_j, o)$  means that the FSM M at state  $s_i$  makes a transition to state  $s_j$  when the input a is applied producing the output a. If a is a called a transition in a is and a is a called the starting state and the tail state of a is respectively. We shall represent a as a is a in a.

An FSM  $M = (S, s_1, I, O, T)$  can also be represented by a directed labeled graph

G(V, E), where S = V and each transition  $(s_i, s_j; a/o)$  corresponds to an arc in E directed from  $s_i$  to  $s_j$  with label tid: a/o, where tid is a unique transition identification for the transition/arc. The identification tid in the label of the transition is in fact optional. An FSM is said to have **reset capability** if for each state  $s_i$  in S there exists a transition  $(s_i, s_1; r/-)$ , called a **reset transition** which resets the FSM to its initial state where 'r' denotes the 'reset' command and '-' denotes that the FSM does not produce any output for the reset command. Whenever there is no confusion, we represent all the reset transitions in a protocol simply by r.

We call an FSM M completely specified if at each state  $s_i$  in M and for each input a in I, there is an outgoing transition from  $s_i$  with input a. An FSM can be modified into a completely specified one by using what is called a **completeness assumption** [DS88]. The completeness assumption requires that a self-loop transition with input a and output '—' be added for a state  $s_i$  if it does not have an outgoing transition with input a.

An input (output) sequence is a sequence of input (output) symbols. We denote an ordered pair (a,b) of input and output by a/b. An **input-output sequence** is a sequence of input and output pairs. We use the operator '•' for concatenating two inputs (outputs) symbols as well as input-output pairs. '@' is an operator for concatenating two input (output) sequences as well as input-output sequences. These operators are omitted in certain sequences whenever there is no confusion.

A walk is a sequence of a finite number of transitions in the graph G of M, where the tail state of every transition, except the last transition, is the starting state of its successive transition. We use '@' for concatenating walks. This operator is often omitted in the concatenated walks. Note that the same operator is used for concatenating input, output, and input-output sequences. The usage of '@' can easily be distinguished from the context. The starting state (tail state) of the first (last) transition in a walk is called the starting state (tail state) of the walk. A walk is said to be closed if its starting state and the tail state are the same. A

tour is a closed walk whose starting state is the initial state of the FSM. We often identify a state  $(s_i)$  in M by simply referring to its index (i). By Walk(j, inseq), we denote a walk from  $s_j$  of the graph of M such that inseq is the concatenation of the inputs along this walk. It actually denotes the sequence of transitions the FSM will go through when inseq is applied to it when it is at  $s_j$ .

The function **Tail(j, inseq)** accepts the index of the state  $s_j$ ,  $1 \le j \le n$  and an input sequence inseq and returns the index of the state the FSM M will reach on applying the inseq to M when t stays at  $s_j$ . That is, Tail(j, inseq) is the tail state of Walk(j, inseq). Similarly **Dest(t)** will denote the tail state of the transition t. We shall denote the input sequence, the output sequence and the input-output sequence on a walk W by Inseq(W), Outseq(W) and IOseq(W), respectively.

A completely specified FSM M is said to be minimal if for every pair of distinct states in M there exists at least one input sequence of finite length such that M produces different output sequences when this input sequence is applied to M when it is in these two different states. Formally, a completely specified FSM M is minimal if for every pair of states  $(s_i, s_j), i \neq j$ , there exists an input sequence  $D_{ij}$  of finite length such that  $Outseq(Walk(i, D_{ij})) \neq Outseq(Walk(j, D_{ij}))$

In FSM-based testing methods, the specifications and the implementations are assumed to be represented as FSMs. We shall refer to the FSM representations of a specification and an implementation of a protocol as SPEC and IUT, respectively. The methods also assume that the SPEC is strongly connected<sup>1</sup>.

#### 1.2.1 Fault Model for FSM

Our fault model for an FSM-based protocol is similar to the one given in [BDD+91]. The faulty IUTs are assumed to have only two types of faults, namely, the output fault and the transfer fault [BDD+91, DS88]. A transition  $(s_i, s_j; a/o)$  of the SPEC is said to have an **output fault** in the IUT if for the state corresponding to  $s_i$  and for the

<sup>&</sup>lt;sup>1</sup>An FSM M is said to be strongly connected if each state is reachable from all the states.

input a, the IUT produces an output different from a. A transition  $(s_i, s_j; a/a)$  of the SPEC is said to have a transfer fault in the IUT if for the state corresponding to  $s_i$  and for the input a, the IUT makes a transition to a state which does not correspond to  $s_j$ . The fault coverage of a test sequence generation method is the percentage of faulty IUTs the method can detect from the set of all IUTs with any number of output faults and/or transfer faults. Thus, a method is said to have complete fault coverage if the test sequence generated by the method has 100% fault coverage.

In order to detect and diagnose the fault, the test sequence generated is applied to the IUT one by one and the output is observed. If the output is different from the expected one, the testing process is stopped and the IUT is declared faulty. The output sequence obtained thus far is analyzed for diagnosing the fault. A test sequence generation method has **k-fault resolution capability of level 1**, where  $k, l \geq 1$ , if for any IUT with at most k faulty transitions, a test sequence generated by the method can localize at least one faulty transition to within a set of l transitions provided the presence of a fault is detected.

#### 1.3 Review of Literature

#### 1.3.1 FSM-Based Test Sequence Generation

The control flow in a protocol can be represented by an FSM. A major part of the research contributions in test sequence generation so far is based on the FSM model. Some of the earlier work had been done with respect to hardware and software testing [Gil62, Gon70, Koh78, Cho78]. The test suite for an FSM is simply a linear input sequence. The expected output sequence for this input sequence is also known to the tester. Though some of the existing methods, for example, the U-method [SD85], consider the test sequence as an input-output sequence, we uniformly treat the test sequence of an FSM as an input sequence.

In all FSM-based test sequence generation methods, a transition is tested by

bringing the IUT to the starting state of the transition under test and applying the input symbol of the transition and observing the output produced by the IUT to see if it matches with the output of the transition. Most of the methods also confirm the tail state of the transition in the IUT by applying a sequence which can uniquely identify the state [Koh78]. Since such an identification sequence is generated from the SPEC, some methods verify this sequence in the IUT before using it.

The transition tour method (in short, the T-method) [NT81] requires traversal of each of the transitions at least once. Thus, the required test sequence is an input sequence along a minimum length tour which traverses all the transitions. It is reported that this method has only a limited capability of detecting faults in an IUI since it does not confirm the intermediate states as it traverses the transitions [SL89].

The distinguishing sequence method [Hen64, Gon70], also known as the D-method, assumes that the SPEC is completely specified and minimal. The IUT is assumed to have at most the same number of states as the SPEC. The method uses what is called a distinguishing sequence for identifying the states. The method is discussed in detail, later in Chapter 3. It consists of two phases. The test sequence generated in the first phase verifies if the distinguishing sequence of the SPEC is also a distinguishing sequence of the IUT. The second phase is to generate a test sequence for testing all the transitions. A test subsequence for a transition consists of a sequence to put the IUT in the starting state of the transition followed by the input of the transition and the distinguishing sequence. The method has complete fault coverage [FBK+91]. The primary limitation of the method is that some SPECs may not have a distinguishing sequence.

The characterizing sequence method, henceforth referred to as the C-method, proposed by Kohavi et al [KRK74, Koh78] assumes that the SPEC is completely specified and minimal. It uses a set of sequences known as the Characterizing Sequence set (CS set) for identifying the states. C-method is also discussed in Chapter 3. For each state, it defines an Identifying Sequence set (IS set), a

subset of the CS set. It first computes an identifying sequence for each state using the IS set of that state. As in the D-method, the C-method also has two phases. In the first phase, it generates a test sequence for verifying the identifying sequence of each state in the IUT. The sequence generated in the second phase is for testing the transitions. A test sequence for a transition consists of a sequence to put the IUT in the starting state of the transition under test and confirming the state followed by the input symbol of the transition and a sequence to verify the tail state of the transition in the IUT. The latter sequence is based on the identifying sequence of the tail state as well as the characterizing sequences. Unlike the D-method, the C-method can be applied on any SPEC which is minimal.

In [Cho78], Chow proposes a test sequence generation method for SPECs which have the reset capability. The method, called the W-method, assumes that the SPEC and the IUT are completely specified and minimal. It further assumes that the IUT is strongly connected and it has the reset capability. The number of states in the IUT is assumed to be within a known bound. The method first computes the CS set of the IUT from the CS set of the SPEC. The CS set of the IUT is used in the test sequence generation. The W-method uses a fixed path to reach a given state from the initial state. The reset transition is used to reach the initial state from a given state. The test sequence for a transition consists of a set of subsequences, one for each sequence in the CS set. A subsequence in the above set lies along the tour consisting of the fixed path from the initial state to the starting state of the transition under test, the transition itself, the walk starting from the tail state of the transition with the characterizing sequence as its input sequence and the reset transition. The W-method guarantees complete fault coverage [Cho78].

The Wp-method of Fujiwara et al [FBK+91] is an improvement of the W-method in that the length of the test sequence is reduced without compromising the fault coverage. It actually splits the W-method into two phases. Only the transitions in the fixed paths are tested in the first phase. For this the scheme as described in the

W-method is used. The remaining transitions are tested in the second phase. The same scheme is applied in this phase for testing the remaining transitions. However, for confirming the tail state of the transition under test, it uses only the IS set (in the IUT) of the state, instead of the whole CS set of the IUT. The W-method and the Wp-method are described in detail in Chapter 3.

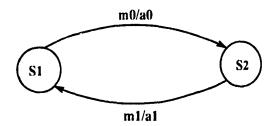

The U-method presented in [SD85, ADLU88, DSU90a, SD88] defines what is called a Unique Input Output (UIO) sequence of each state for state identification. An UIO-sequence of a state is an input-output sequence of shortest length which lies along a walk starting from that state such that no walk starting from any other state has the same sequence. Since we express the test sequence as an input sequence, we extract only the input part of an UIO-sequence and call it as the Unique Input Sequence (UIS) as in [Y' B93]. A test sequence for each transition is an input sequence along a walk which comprises of the transition followed by the walk starting from the tail state of the transition along the UIS of the state. The problem of generating a minimum length test sequence according to the above scheme is formulated in [ADLU88] as an asymmetric Rural Postperson Problem (RPP) [EJ73, Kua62 TS92]. The efficient solution for RPP proposed in [ADLU88] requires a certain auxiliary graph derived from the SPEC for a given set of UISs, to be weakly connected? [ADLU88].

U-method, Shen et al [SLD92, SL92] have recently proposed a method, known as the MU-method. Instead of a single UIS for each state, it uses a number of UISs. The improvement is achieved by suitably assigning an UIS for testing every transition incoming at a state from the set of UISs of that state such that the final test sequence is of minimum length. They have formulated the problem as an UIS Assignment Problem (UAP) and presented an efficient algorithm. The algorithm presented in [SL92] is based on a minimum cost maximum flow problem [Tar83] and it requires

<sup>&</sup>lt;sup>2</sup>A directed graph is said to be weakly connected, if there exists a path between every pair of vertices in the underlying undirected graph.

that a certain graph derived from the SPEC for the given assignment of UISs to the transitions be weakly connected [SL92].

Methods for further minimizing the length of the test sequence by overlapping test subsequences of the transitions are presented in [CCK90, MP91, LJH92]. Boyd and Ural have shown in [BU91] that the problem of finding an optimum length test sequence is NP-complete if the overlapping of the test subsequences of the transitions is allowed.

Though the UIS-based methods as described in [ADLU88, SLD92, SL92, CCK90, MP91, LJH92] have very high fault coverage [MCS93], they do not have complete fault coverage [CVI89]. The improved UIS method of Chan et al [CVI89] is intended to rectify this limitation by verifying the UISs in the IUT as it is done in other methods (for example, D-method, C-method, W-method) for verifying the state identification sequences used in the respective methods. This method assumes that both the SPEC and the IUT are completely specified.

The recent method by Yao et al [YPB93] is for generating test sequences for 3PECs which may not have the reset capability. It assumes that the IUT has at most the same number of states as the SPEC, and that the IUT is completely specified and minimal. The test sequence also includes subsequences for verifying the UISs in the IUT and it guarantees complete fault coverage. The length of the test sequence generated is often very high in this method due to the state verification sequences.

#### 1.3.2 Fault Diagnosis Methods

When an implementation fails the conformance testing, it goes back to the implementation for correction. Apart from assigning a fail verdict to the implementation, if the tester also provides some diagnostic information on the possible functions/operations which are not implemented as per the standard specification, then it certainly speeds up the correction process. All the test case generation methods available in the literature basically detect the presence of faults, if any, in the implementation. Because

of its practical importance, researchers have started designing methods for generating test cases for detecting as well as diagnosing faults in an implementation.

The work by Vuong and Ko [VK90] is for the FSM model and is based on the Constraint Satisfaction Problem (CSP) [Mac77]. Using CSP resolution, they first generate the set of all FSMs whose behavior is the same as that of the IUT for a given test sequence. These FSMs are then checked for their equivalence with the SPEC. If none of them is equivalent to the SPEC, then clearly the IUT is faulty. Therefore, the method generates some additional test sequences to identify from the above set the FSM which is identical to the IUT. The complexity of this method is quite high, as the CSP is an NP-complete problem.

The recent method by Ghedamsi [Ghe92] takes an alternate approach for diagnosing faults in an FSM. As the first step, it applies the test sequence generated by any test generation method, such as the T-method, U-method, W-method, or the Wp-method to the IUT in order to find a set of transitions which could be faulty. We shall refer to this set as the **initial fault resolution set**. In the second step, it computes a set of additional test sequences for further localizing the fault.

The size of the initial fault resolution set depends on the fault detection and diagnosis capability of the test generation method used. Some of the existing methods may produce almost all the transitions in the SPEC as the initial fault resolution set. In this case, the first step is not very useful; also it severely affects the second step since the method needs to avoid all the transitions in the initial fault resolution set while computing the **limited characterizing set** [Ghe92]. Some of the test generation methods, for instance the T-method, may produce an empty initial fault resolution set despite the fact that the IUT is faulty.

#### 1.3.3 EFSM-Based Test Sequence Generation

As its name suggests, the Extended Finite State Machine (EFSM) model is an extension of the FSM model. Here, we provide an informal description of the EFSM

model considered in this thesis. A formal treatment is given in Chapter 5 where we present a test case generation method for this model. While a transition in an FSM has only an input and an output, the one in an EFSM can have an input interaction, a sequence of output interactions, and a predicate. A transition in an EFSM can also use and operate on a set of local variables of the EFSM. The input and output interactions also have a set of interaction parameters. A transition in an EFSM can be executed, if the input interaction specified in the transition is input to the EFSM when it is in the starting state of the transition and the values of the input interaction parameters and the local variables are such that the predicate of the transition is satisfied. When a transition is executed, the EFSM produces a sequence of output interactions as given in the transition, some variables are set to new values as specified by the transition, and the EFSM moves to the tail state of the transition. Specification languages Estelle, and SDL are based on a more powerful EFSM model than the one considered in this thesis [CA91]. For instance, this model supports communicating EFSMs, whereas our model has a single EFSM only. There are techniques available in the literature to transform a protocol specification written in Estelle or SDL into an EFSM model [SB86, Tri92, LL91, CA91, UW93], which is similar to the one considered in this thesis. Protocols expressed in LOTOS have also been transformed into a labeled transition system in order to generate test cases for the protocols [Kar88, Tri92]. Henceforth, by an EFSM, we refer to our restricted model.

As evident from the EFSM model, the input and output interactions are allowed to have parameters, and it has a set of local variables which can be manipulated by executing the transitions. Therefore, as part of conformance testing, data flow aspects of the EFSM have to be tested in addition to the control flow aspects. As the associated predicates have to be satisfied in order to execute the transitions, the feasibility of a walk cannot be taken for granted [UY91, UW93, CZ93]. Therefore, generating test cases which adequately cover the data flow and control flow aspects

of a protocol represented in an EFSM is a challenging problem. In this section we review the EFSM-based test sequence generation methods available in the literature.

#### The Functional Approach

The semi-automatic test case generation method of Sarilaya *et al* [SBC87, FS92] is for a normal form Estelle module [SB86], which is similar to an EFSM. This method is based on the functional approach for software testing [How87]. It selects a set of tours for each functional block. In order to test every function thoroughly a set of test data is selected for executing each tour generated for the function.

The method has limited control flow coverage since the tail states of the transitions are not verified while traversing the transitions. The functional coverage is affected since the feasibility of a tour is considered only after selecting a set of tours for the function. The method does not address the data flow aspects effectively.

#### The Static Data Flow Approach

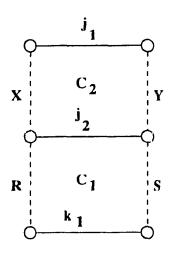

Ural and Yang [UY91] uses the static data flow analysis technique [RW85, Ura87] for selecting test cases for protocols represented as a single normal form Estelle module. An IO-df-chain with respect to a variable is a walk from the starting state of a transition where the variable is defined by an input interaction parameter. The value of the variable affects a chain of variables along this walk. The walk terminates in a transition where this chain ends affecting an output interaction parameter or the predicate in the transition. In order to have finite length, the walk does not include more than two sub-walks for any def-use pair in this walk. A data flow coverage criterion known as the IO-df-chain criterion is used to select a set of tours such that every IO-df-chain in the module is covered by at least one tour in the set.

The tours are not tested for feasibility while selecting them. Due to the limitation imposed on the IO-df-chain for achieving finite length, a number of tours selected may be infeasible. This phenomenon is also observed in [Wey90] with respect to the

all-du-path criterion [RW85]. For the control flow aspects of testing, the method only guarantees the traversal of each transition in the module.

In their recent work [UW93], Ural and Williams have used the all-uses [RW85] data flow coverage criterion to select test cases for protocols specified in SDL. The all-uses criterion requires the selection of a set of tours such that at least one defclear path for every def-use pair in the protocol is covered by some tour. Though the number of tours required to satisfy the all-uses criterion is only quadratic in the number of transitions in the protocol, the use of a variable in the def-use pair may not be observable in the selected tour. Although Ural and Williams do not directly address the feasibility of the selected tours, they have emphasized its importance.

#### **UIO-Based Approaches**

In [CA91], Chun and Amer have applied the U-method [ADLU88, SD88] for selecting test cases for an Estelle module in normal form. As in the U-method, their control flow coverage criterion is to traverse each transition followed by an UIO-sequence of its tail state. Henceforth, we refer to this criterion as the **trans-UIO criterion**. In general, we define the **trans-state-id criterion** as the one which requires a set of tours such that for each transition, the set has at least one tour which traverses the transition followed by a state identification sequence of the tail state of the transition [Koh78, Cho78, FBK+91]. They have also presented a scheme for generating an executable sequence of transitions. They do not, however, consider how this scheme could be used for computing feasible UIO-sequences or for selecting feasible test cases which satisfy the required control flow coverage criterion. The data flow aspect is not addressed in this approach. Due to the tail state confirmation requirement in the transition testing, the test cases selected in this method provide better control flow fault coverage than all the EFSM-based methods discussed thus far.

In [LHHT94], Li et al propose a method for generating control flow test cases from an EFSM. The EFSM is assumed to have only integer type of local variables

and input interaction parameters. Also, the predicates are assumed to be linear. A new type of UIO-sequence known as the Extended UIO-sequence (EUIO-sequence) is introduced. Let W1 (W2) be a walk ending (starting) at a state. The sequence of input and output interactions along W1W2 is called an EUIO-sequence of the state if W1W2 is always feasible and the sequence of input and output interactions along W2 is an UIO-sequence of the state. We refer to W1 as a pre-walk for the EUIO-sequence. Two feasible tours are selected for testing a transition such that they contain the same walk from the initial state to the starting state of the transition under test. Also, while the first tour contains the underlying walk of an EUIO-sequence of the starting state of the transition, the second tour contains the underlying walk of an EUIO-sequence of the tail state of the transition such that the pre-walk has the transition under test as its last transition. The feasibility of the walks are checked using integer linear programming problem.

In order to test all the incoming transitions at a state, more than one EUIO-sequence may be required for that state. Also, the problem of finding if a given UIO-sequence has an EUIO-sequence is, in general, undecidable [LHHT94]. The method does not consider the data flow testing. It assumes a reset transition from every state to the initial state.

#### Combined Testing Approaches

The test case selection method of Miller and Paul, presented in [MP92], covers both the control flow and the data flow aspects of protocols which are specified as a single normal form Estelle module. The trans-UIO criterion is used for control flow coverage. It has been established in [MP91] that, in order to guarantee the trans-UIO criterion, it is enough to find a tour such that (i) it covers all the transitions, and (ii) for each occurrence of any converging transition<sup>3</sup>, the tour covers the transition followed

<sup>&</sup>lt;sup>3</sup>A transition ending at a state is said to be converging if there exists another transition ending at the same state such that both transitions have the same input and the same output

path) with respect to a variable in a data flow graph - a graph extracted from the Estelle module - is a path in the graph such that the variable is defined by an input interaction parameter in the first node of the path and the value flows through other local variables along the path until it is assigned to an output interaction parameter (a variable in the predicate) at the end of the path. Corresponding to each def-ob path (def-puse path) in the data flow graph, there exist def-ob walks (def-puse walks) in the Estelle module such that the required data flow occurs in these walks in the same order as in the def-ob path (def-puse path). The def-ob/def-puse criterion is to cover at least one feasible def ob walk for each def-ob path and at least one feasible def-puse walk for each def-puse path. The method provides a back-tracking approach for selecting a set of tours which cover the set of walks satisfying the combined data flow and the control flow criteria.

Miller and Paul's method takes the white box approach of testing, in contrast to the traditional black-box approach which is suitable for conformance testing of protocol implementations. The method does not address the feasibility issue effectively. For instance, it does not consider the issue of obtaining a feasible def-ob walk (def-puse walk) for a def-ob path (def-puse path) even if such a walk is known to be present. The back-tracking approach of combining the walks is inefficient as the partial tours obtained at a certain point of time may have to be undone if there exists no enabling context for all the uncovered walks.

In their recent work [CZ93], Chanson and Zhu have presented another unified approach for selecting test cases for both control flow and data flow aspects of protocols represented as EFSMs. They use the trans-state-id criterion for control flow coverage. A Cyclic Characterizing Sequence (CCS) [CZ93] is used as the state identification sequence for each state. They propose to use either the all-du-path criterion or the all-uses criterion for the data flow coverage. A set of paths satisfying the required def-use association is first determined. Each path is then augmented

into a tour by prefixing it with a shortest path from the initial state of the EFSM to the starting state of the path and suffixing the path with a shortest path from the ending state of the path to the initial state followed by a CCS of the initial state. The tours are then augmented with a CCS at each converging state<sup>4</sup> [MP91] provided the CCS does not disturb the data flow coverage criterion. In this way, the above—' also covers the control flow criterion for some of the transitions. Some additional tours are also selected for covering the remaining transitions for their control flow. Traditional CSP techniques [Mac77, JL87] are used to check the feasibility of the selected tours. If a tour is infeasible, then the self-loops within the tour which influence the control flow are analyzed for determining the number of times they have to be included so that the tour becomes feasible, if such an augmentation is possible. The remaining infeasible tours are discarded.

The self-loop analysis requires solutions to two mathematically intractable problems: the recurrence relation problem and the feasibility problem [CZ93]. Since the feasibility of the tours are considered only after selecting them to cover the criteria, the control flow and the data flow coverage criteria are affected if some of the tours remain infeasible after the self-loop analysis.

#### The Fault-Based Method

In [WL93], Wang and Liu present a fault model based test case generation method for an EFSM model which is somewhat similar to the EFSM model considered in this thesis. While all the other methods generate test cases independent of any specific fault model, this method selects test cases which have the capability of detecting faults in a prespecified fault model. The method takes an EFSM representation of a protocol specification and a fault model as its input and produces a test case that detects errors in the model. The feasibility issue is not addressed effectively in this

<sup>&</sup>lt;sup>4</sup>A set of states are said to be converging if there exists a set of transitions such that it has one transition from every state in this set to a common state and the transitions in this set has the same input and the same output

method.

#### 1.4 Expressing Algorithms

In this thesis algorithms are described using plain English combined with the widely known Pascal-like syntax [JW74] such as the assignment and the if statements, the for, the while, and the repeat..until structures, the block and the record structures etc. Comments in the algorithm descriptions are surrounded with curly brackets (braces) { }, for example {Input: Specification graph  $G_s$ .}. Curly brackets are also used to denote a set of elements, for example  $E := \{s_i \mid 1 \le i \le n\}$ . Both uses are fairly standard and easy to recognize from the context.

#### 1.5 Scope of the Thesis

This thesis is concerned with the development of new methods for generating test cases for protocols specified either as an FSM or as an EFSM.

Chapter 2 presents a new method for generating a test sequence for a given FSM which has at least one UIS for each state. This method is based on the MU-method and addresses certain shortcomings of this method. The novelty of the U-method and the MU-method is that they minimize the length of the test sequence using optimization techniques such as RPP and minimum cost maximum flow problems [Tar83]. These methods have very high fault coverage [MCS93]. The length minimization techniques of the U-method and the MU-method can be applied only when certain auxiliary graphs constructed from the SPEC are weakly connected. There are real life protocols for which this condition may not be satisfied. This shortcoming is addressed in our method. It requires solutions to two sub-problems: Basic UIS Assignment Problem (BUAP), and the general RPP. The BUAP is formally defined and is shown to be a maximum cardinality two matroid intersection problem [Law76].

An efficient algorithm is proposed based on the algorithms of Lawler [Law75] and Edmonds [Edm79] as given in [NW88]. Heuristic algorithms for the RPP are then presented. Finally, our test sequence generation algorithm carefully combines the above algorithms with the MU-method.

In Chapter 3, we formally analyze the fault detection and fault diagnosis capabilities of the existing FSM-based test sequence generation methods. These methods are now being used for detecting the presence of faults in an implementation. Recently, test sequences generated by these methods have been taken as the initial sequences for diagnosing faults in an implementation [Ghe92]. While the fault detection capabilities of only some of the methods are available in the literature, none of these methods have formally been analyzed for their fault diagnosis capabilities. Therefore, our analysis in Chapter 3 will be useful for the practitioners to choose an appropriate method for testing and diagnosing protocol implementations. The need for similar study is also indicated in [Ura92], Moreover, this study gives us an insight on the complexities involved in designing new methods with better fault diagnosis capabilities.

Two new methods are proposed in Chapter 4 for generating test sequences from specification FSMs for diagnosing a single fault in an implementation. Both methods are based on the Wp-method [FBK+91]. The first method uses a UIS for identifying a state. It applies the RPP optimization techniques at appropriate places in order to minimize the length of the test sequence. This method guarantees the best fault diagnosis capability among all the UIS based methods analyzed in Chapter 3. The second method uses a CS set for identifying the states and it provides superior fault diagnosis capability than the Wp-method.

Chapter 5 presents a new approach for generating test cases for testing both the control flow and the data flow aspects for protocols which are represented as EFSMs. A new type of state identification sequence, namely the Context Independent Unique Sequence (CIUS), is defined and an algorithm for computing a CIUS of a given

is superior to the existing control flow coverage criteria for the EFSM. In order to provide observability, the "all-uses" data flow coverage criterion is extended to what is called the def-use-ob criterion. Finally, a two-phase breadth-first search algorithm is designed for generating a set of executable test tours for covering the selected criteria.

In Chapter 6, we summarize our contributions in this thesis and point out certain problems for future study.

# Chapter 2

# TEST CASE GENERATION FROM FSM MODEL

As pointed out in Chapter 1, the U-method [ADLU88] and the MU-method [SLD92, SL92] generate test sequences of minimal length with very high fault coverage [MCS93] and have practical applications [SU90]. However, these can be applied only for limited classes of protocols which are represented as strongly connected FSMs having at least one Unique Input Sequence for each state. In this chapter, we propose a generalized approach that can be used for generating test sequences for any such protocol.

The necessary definitions from graph theory and matroid theory are provided in Section 2.1. The U-method, the MU-method and the need for a new method for test case generation are discussed in Section 2.2. Our method requires solutions to two sub-problems: the Basic UIS Assignment Problem (BUAP), and the general Rural Postperson Problem (RPP) [EJ73]. In Section 2.3, the BUAP is formally defined and an efficient solution is presented. Heuristic algorithms for the RPP are proposed in Section 2.4. Our generalized method presented in Section 2.5 carefully combines the above algorithms with the MU-method to derive test sequences for a given protocol.

# 2.1 Graphs and Matroids

The following definitions are taken from [TS92, Law76, PR88].

A graph G is a pair (V, E), where V and E are two finite disjoint sets. Elements of V and E are called **vertices** and **edges**, respectively. Each edge is identified with an unordered pair of vertices referred to as the **end vertices** of the edge. An edge is said to be **incident** on its end vertices. Two edges are said to be **adjacent** if they have a common end vertex. An edge is called a **self-loop** if both its end vertices are identical. A **walk** in a graph is a finite sequence of vertices  $(v_0, v_1, \ldots, v_k)$ ,  $k \geq 1$  such that  $(v_{i-1}, v_i)$  for  $i = 1, 2, \ldots, k$ , are edges in G.  $v_0$  and  $v_k$  are called the **end vertices** of the walk and all other vertices are called its internal vertices. The walk  $(v_0, v_1, \ldots, v_k)$  can also be denoted as a sequence of edges  $(t_1, t_2, \ldots, t_k)$  if  $t_i = (v_{i-1}, v_i)$ , for  $i = 1, 2, \ldots, k$ . A walk is **open** if its end vertices are distinct; otherwise it is **closed**. A closed walk is referred to as a **tour**. A walk is called a **trail** if all its edges are distinct. An open trail is a **path** if all its vertices are distinct. A closed trail is called a **cycle** if all its vertices except the end vertices are distinct. A graph is said to be **connected** if there exists a path between every pair of vertices in the graph.

Weighted graphs are those graphs in which a real number, usually called the cost, is associated with each edge. The graph G' = (V', E') is said to be a subgraph of the graph G = (V, E) if  $V' \subseteq V, E' \subseteq E$  and both end vertices of every edge in E' are in V'. A subgraph G' = (V', E') of G = (V, E) is called a spanning subgraph if V' = V. A subgraph G' = (V', E') of G = (V, E) is said to be induced by  $F \subseteq E$  if E' = F and V' is the set of end vertices of all the edges in F. This induced subgraph is denoted by G[F]. If F is a bag¹ of edges from E, then in G[F] each edge in F is repeated as many times as it occurs in F. If K is a set of edges having both their end vertices in V, then G + K denotes the graph obtained from G = (V, E) by adding all

<sup>&</sup>lt;sup>1</sup>A bag is a collection of elements over some domain. Unlike sets, bags can have multiple occurrences of the same element

the edges in K to (the edge set of) G.

If each edge of a graph G = (V, E) is identified with an ordered pair of vertices then G is called a directed graph or simply a digraph. The edges in a digraph are also referred to as arcs. Let  $a = (u, v) \in E$ , where u and v are the vertices in V. u is called an outgoing (incoming) are at u(v). Also, u and v are called the starting **vertex** and the **ending vertex** of a, respectively. A walk in a digraph G is a finite sequence of vertices  $(v_0, v_1, \ldots, v_k)$ ,  $k \geq 1$  such that  $(v_{i-1}, v_i)$  for  $i = 1, 2, \ldots, k$ , are edges in G.  $v_0$  and  $v_k$  are called the starting vertex and ending vertex of the walk, respectively and all other vertices are called its internal vertices. A tour, a path, and a cycle in a digra h can be defined analogous to those in the undirected graph. A digraph is said to be **strongly connected** if there exists a path from any given vertex to any other vertex. A digraph is **weakly connected** if the underlying undirected graph is connected. The digraph G = (V, E) is said to be **symmetric** if the number of incoming arcs at every vertex in V is the same as the number of outgoing arcs at that vertex. Given a strongly connected digraph G = (V, E) with weighted arcs, and a subset of arcs  $F \subseteq E$ , the **Asymmetric Rural Postperson Problem** (RPP) with respect to F is to find a tour with minimum cost such that it covers each arc in F at least once [EJ73, Kua62, TS92]. Such a minimum cost tour is referred to as a **Asymmetric Rural Postperson Tour** (RPT) with respect to F. The RPP is known to be an NP-complete problem [LRK76, Pap76].

A matroid  $M = (E, \mathcal{I})$  is a structure in which E is a finite set of elements and  $\mathcal{I}$  is a family of subsets of E such that

- 1. The empty set is a member of  $\mathcal{I}$ ;

- 2.  $F_1 \subset F$  and  $F \in \mathcal{I}$  imply  $F_1 \in \mathcal{I}$ ;

- 3. If  $F_p$  and  $F_{p+1}$  are sets in  $\mathcal{I}$  having p and p+1 elements respectively, then there exists an element  $\epsilon \in F_{p+1} F_p$  such that  $F_p \cup \{\epsilon\} \in \mathcal{I}$ .

Elements in  $\mathcal{I}$  are called the independent sets in M.

A graphic matroid of a graph G = (V, E) is a matroid  $(E, \mathcal{I})$  such that  $F \subseteq E$  is in  $\mathcal{I}$  iff G[F] has no cycle.

Let  $P = \{E_1, E_2, \dots, E_k\}$  be a partition of the edge set E of a graph G = (V, E). Let  $Q = \{i_1, i_2, \dots, i_k\}$  be a given set of non-negative integers. Let  $(E, \mathcal{I})$  be a system such that  $F \in \mathcal{I}$  iff  $|E_j \cap F| \leq i_j$  for  $j = 1, 2, \dots, k$ . It is known that  $(E, \mathcal{I})$  is a matroid [Law76]. It is called the **partition matroid** of G with respect to the partition P and the index Q.

Let  $(E, \mathcal{I}_j)$ , j = 1, 2, ..., k for some  $k \geq 2$ , be a system of matroids over E. The Maximum Cardinality Matroid Intersection Problem (MCMIP) is to find a maximum subset H of E such that H is independent in  $(E, \mathcal{I}_j)$  for j = 1, 2, ..., k. If k = 2, then the above problem is referred to as the Maximum Cardinality Two Matroid Intersection Problem (MC2MIP). Though the general MCMIP is NP-complete [PS82, PR88], its special case MC2MIP is polynomially solvable [Law76].

An input sequence,  $U_i$  is called a **Unique Input Sequence (UIS)** of the state  $s_i$  of an FSM M if  $U_i$  is a sequence of shortest length such that (i) there exists a walk W from  $s_i$  such that  $\operatorname{Inseq}(i,W)=U_i$  and (ii) for each state  $s_j$ ,  $j\neq i$ , either there is no walk from  $s_j$  with input sequence  $U_i$  or  $\operatorname{Outseq}(j,U_i)\neq \operatorname{Outseq}(i,U_i)$ . Moreover, the input-output sequence  $\operatorname{IOseq}(W)$  is called an **Unique Input Output (UIO)** sequence of  $s_i$ .

Let  $U_i$  be an UIS of  $s_i$ ,  $1 \le i \le n$ . The set  $\mathcal{U} = \{U_i \mid 1 \le i \le n\}$  is referred to as an **UIS set** of the FSM M.

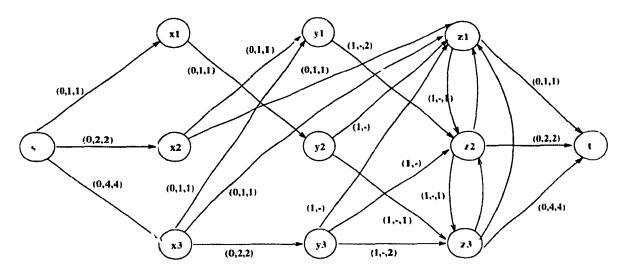

We assign a unit cost to each edge in the specification graph  $G_s = (S, E)$  since we are concerned with test sequence length minimization. Let  $MU_i$  be a nonempty set of UISs for each state  $s_i \in S$ . We assume that the functions  $h\epsilon ad$  and tail will return the starting state and the ending state of any UIS, respectively. Also, the functions  $start(\epsilon)$ ,  $label(\epsilon)$  and  $\epsilon nd(\epsilon)$  will return the starting state, label and the ending state of any transition  $\epsilon$ , respectively. Let  $MU = MU_1 \cup MU_2 \cup ... \cup MU_n$ . Define the relation  $R \subseteq E \times MU$  such that  $(\epsilon, u) \in R$  iff  $\epsilon nd(\epsilon) = h\epsilon ad(u)$ . Clearly, R denotes the set of all possible assignments of UIS from MU for all the transitions in E. We call any subset  $B \subseteq R$  a valid UIS assignment or simply an UIS assignment for the set of transitions  $D \subseteq E$  if dom(B) = D and  $|\{u \mid (e, u) \in B\}| = 1$ , for each  $e \in D$ . That is, each element in  $e \in D$  has exactly one UIS assignment of  $e \in D$  as also referred to as a (valid) UIS assignment of the protocol  $e \in G$ .

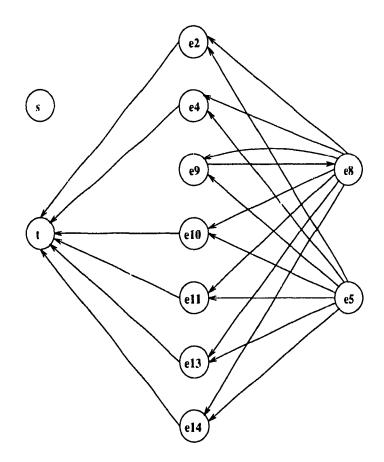

Consider the undirected graph G' = (S, E') where  $E' = \{(start(e), tail(u); label)\}$  $(\epsilon)^{a}u) \mid (\epsilon,u) \in R$ . An edge  $\epsilon' \in E'$  which corresponds to  $(\epsilon,u) \in R$  is often referred to as a **test edge** for the transition  $\epsilon$  since  $\epsilon$  can be tested by applying the sequence along  $\epsilon'$ . For each edge  $\epsilon' = (start(\epsilon), tail(u); label(\epsilon) \circ u) \in E'$  which corresponds to  $(\epsilon, u) \in R$ , the length of the input sequence in  $label(\epsilon) \otimes u$  is taken as the cost of  $\epsilon'$ . It is easy to see that there is a one-to-one correspondence between R and E'. An element of R is often treated as an edge in E' and vice versa. Let B be a valid UIS assignment for  $D \subseteq E$ . The subgraph G'[B] of G' induced by B is called a **test graph** for D. The test graph induced by an UIS assignment of the protocol  $G_s$  is simply referred to as a **test graph for the protocol**. Observe that every test graph for a strongly connected protocol always spans all the states of the protocol. Subgraphs of G' are often extended by adding edges from  $G_s$ , and vice versa. Suppose H' is a subgraph of G' and  $F \subseteq E$ , then H' + F will be treated as an undirected graph as H'is undirected. On the other hand, if H is a subgraph of  $G_s$  and  $F' \subseteq E'$ , then H + F'will be treated as a directed graph as H is directed, the orientation of the edges in F' coinciding with that of the corresponding edge in  $G_s$ .

# 2.2 UIS-Based Methods and the Need for a New Method

Two important methods based on the UISs are described in this section. We study the need for a new method by analyzing the scope of these methods. Recall that SPEC

and IUT denote the FSM representation of a specification and an implementation of a protocol, respectively.

#### 2.2.1 The U-method

The U-method [ADLU88] [DSU90b] requires that the representation graph  $G_s = (S, E)$  of SPEC be strongly connected. Each state of  $G_s$  is assumed to have an UIS. Let  $U_j$  be an UIS for  $s_j$ ,  $1 \le j \le n$ . The U-method tests each transition  $(s_i, s_j; a/o)$ , as follows:

The protocol implementation IUT is first put in state  $s_i$ . Then the input a is applied and the output is verified for o. Finally, to check for state  $s_j$ , the UIS  $U_j$  is applied to the current state of the IUT and the output is examined against the expected output according to the SPEC.

Thus the input sequence  $a \cap U_j$  is  $\mathfrak{t}_{1,r}$  test subsequence for the transition  $(s_i, s_j; a/o)$ . By considering  $MU_j = \{U_j\}, \ 1 \leq j \leq n$ , we get G' = (S, E'), where  $E' = \{(s_i, tail(U_i); a \cap U_j) | (s_i, s_j; a/o) \in E\}$ . Clearly, G' is the unique test graph of  $G_s$ . Let  $G^* = G_s + E'$ . In the U-method, each transition in  $G_s$  is tested by applying the subsequence along its test edge in E'. Thus an optimal test sequence for  $G_s$  lies along an RPT of  $G^*$  with respect to E'. In other words, the optimal test sequence generation problem is equivalent to the problem of finding an RPT of  $G^*$  with respect to E'. Before proceeding further, we introduce a definition. A rural symmetric augmentation of a weighted digraph G = (V, E) with respect to  $F \subseteq E$  is a digraph  $G[F \cup E_1]$  such that (i)  $G[F \cup E_1]$  is symmetric, and (ii)  $E_1$  is a minimum cost bag in E satisfying (i). The polynomial algorithm given in [SD85] for finding an RPT first computes a rural symmetric augmentation  $G^*[E' \cup E_1]$  of  $G^*$  with respect to E', where  $E_1$  is a bag containing elements in  $E \cup E'$ . It then generates a test sequence by concatenating the subsequences and/or inputs along an euler tour of  $G^*[E' \cup E_1]$ . This algorithm can be successfully applied to a protocol  $G_s$  if the test graph G' is

connected [ADLU88]. Note that this is only a sufficient condition. It is also shown that protocols which have either a self-loop at each state or the reset capability always meet this requirement.

#### 2.2.2 MU-method

In the MU-method [SLD92, SL92], Shen ct all have proposed an improvement for the U-method. While the U-method uses only one UIS for each state, this method uses multiple ( $\geq 1$ ) UIS(s) for each state. The improvement is obtained by suitably assigning an UIS for each transition from the set of multiple UISs of its tail state in order to reduce the length of the test sequence. The approach of using multiple UISs for minimizing the length of the test sequence as introduced in [SLD89, SLD92] has two problems:

- (1) The test graph resulting from the UIS assignment computed in the method may not be connected.

- (2) The UIS assignment computed in the method does not necessarily minimize the length of the resulting test sequence.

These two problems were rectified in their recent method as described in [SL92] and we shall consider this modified method as the MU-method. We would like to note that an alternate approach of solving the above two problems is proposed in [Ura92]. Given a set  $MU_t$  of multiple UISs of the minimum length for each state  $s_t$ , i = 1, 2, ..., n of the protocol  $G_s = (S, E)$ , the **UIS Assignment Problem (UAP)** is to find a valid UIS assignment B of the protocol such that the RPT of  $G_s + B$  with respect to B is of minimum length among all valid UIS assignments of the protocol. The MU-method solves certain specific instances of this problem efficiently by transforming it into an equivalent multi-stage minimum cost maximum flow problem [SL92]. As in the U-method, a minimum length test sequence is obtained by concatenating the test subsequences and/or the input of the transitions along the minimum cost RPT. The

MU-method guarantees an optimal test sequence for a protocol  $G_s$  if the test graph G'[B] is connected. It has also been proved that protocols which have either the reset capability or a self-loop at each state always meet this requirement [ADLU88, SLD92]. As we shall see later in this section, this approach of obtaining minimum length test sequences does not work for all protocols.

Methods for further minimizing the length of a test sequence by overlapping test subsequences of the transitions are presented in [CCK90, MP91, LJH92]. In this thesis, we do not consider optimization through overlapping. We shall now illustrate the need for extending the U- and the MU-methods.

#### 2.2.3 Motivation for the New method

It has been reported in [ADLU88] and [CS92] that the U-method can be applied to generate test sequence for any protocol  $G_s$  which satisfies one of the conditions (i) through (v) below. Note that conditions (i) through (iv) are independent of UISs whereas condition (v) is with respect to a particular UIS for each state.

- (i)  $G_s$  has the reset capability [ADLU88].

- (ii)  $G_s$  has a self-loop at each state [ADLU88].

- (iii)  $G_s$  has a state, say  $s_e$ , with a self-loop and a reset edge, and each state has a self-loop, or a reset edge, or an edge to the state  $s_e$  [CS92].

- (iv) For every partition of S into two nonempty subsets  $S_A$  and  $S S_A$ ,  $\exists s_i \in S_A$  and  $s_j \in S S_A$  such that there is an edge to some state  $s_k$  from both  $s_i$  and  $s_j$  [CS92].

- (v) For every partition of S into two nonempty subsets  $S_A$  and  $S S_A$ ,  $\exists s_i \in S_A$  and  $s_j \in S S_A$  such that state  $s_i(s_j)$  has an edge to a state  $s_p(s_q)$  in S and  $tail(U_p) = tail(U_q)$ . Here,  $U_j$  is an UIS for the state  $s_j$ , j = 1, 2, ..., n and it is used for testing every incoming transition at the state  $s_j$  [CS92].

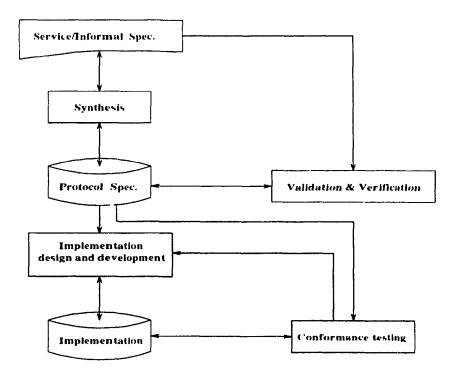

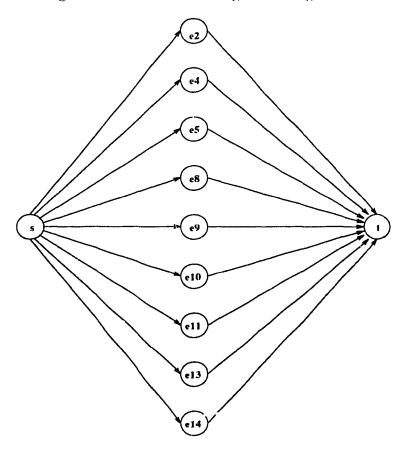

Figure 2.1: Simplified transport protocol

| Transition | Label         | Transition | Label             |

|------------|---------------|------------|-------------------|

| t l        | TCONreq/s-CR  | t2         | r-CR/TCONind      |

| t3         | r-DR/TDISind  | t4         | r-CC/TCONconf     |

| t5         | TDISreq/s-DR  | t6         | r-DR/s-DC&TDISind |

| t7         | null/s-AK     | t8         | r-AK/null         |

| t9         | r-DT/TDATAind | t10        | TDATAreq/s-DT     |

| t11        | TCONresp/s-CC | t12        | TDISreg/s-DR      |

| t13        | r-DC/TDISconf |            |                   |

Table 2.1: Labels for transitions in Figure 2.1

| State | UIS        | State | UIS            |

|-------|------------|-------|----------------|

| $S_1$ | t2 (r-CR)  | $S_2$ | t4 (r-CC)      |

| $S_3$ | t6 (r-DR)  | $S_4$ | tll (TCONresp) |

| $S_5$ | t13 (r-DC) |       |                |

Table 2.2: UISs for states of the FSM shown in Figure 2.1

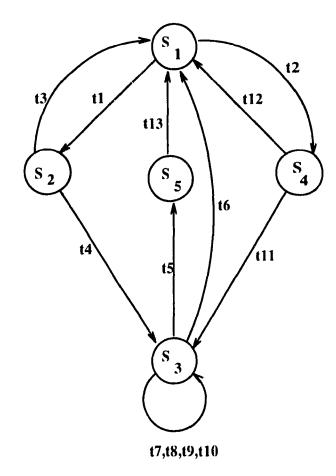

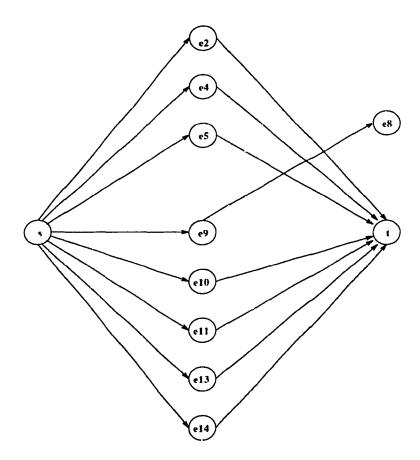

Figure 2.2: An FSM based on the INRES protocol: responder

| Transition | Label          | Transition | Label       |

|------------|----------------|------------|-------------|

| t I        | CR/ICONind1    | t2         | IDISreq/DRI |

| t3         | ICONresp/CC    | 14         | CR/ICONind2 |

| (5         | IDISreq/DR2    | t6         | DT2/AK      |

| 17         | DT1/IDATind&AK | ]          |             |

Table 2.3: Labels of the transitions in Figure 2.2