National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# A MICROPROGRAMMED INTERPRETER FOR CONCURRENT EUCLID

Kuarlall Lall

A Thesis

in

The Department

of

Computer Science

Presented in Partial Fulfillment of the Requirements for the degree of Master of Computer Science at Concordia University

Montreal, Quebec, Canada

December 1988

© Kuarlall Lall 1988

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-49095-0

#### ABSTRACT

# A Microprogrammed Interpreter for Concurrent Euclid

## Kuarlall Lall

There are several methods of executing programs written in a high level language (HLL). The most widely used is to compile the programs into machine language. Another is to translate the programs into some intermediate form and then to execute that form interpretively. A third method is to directly execute either the HLL or the intermediate form.

This study was aimed at investigating the feasibility of directly executing the intermediate representation of the sequential features of Concurrent Euclid (CE) on the SEL 32/75 computer. The CE intermediate code was translated into and a microprogrammed interpreter for Ecode was Ecode, designed and implemented on the SEL, and benchmarked against the compiler. For the CPU-bound prime number algorithm Sieve Eratosthenes, the interpreter was measured to be about twice as slow as the compiler. Ecode was then modified, and translator and interpreter designed and implemented. The same benchmark then yielded comparable results for both We project that further the interpreter and compiler. changes in Ecode design and hardware support would result in substantial Ecode efficiency gains.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincerest thanks to to my thesis supervisor Dr. J. W. Atwood, without whose constant encouragement I probably would have given up on writing this thesis a long time ago. He was always readily available for consultation, and I appreciate the time and effort he put into guiding me through the project and constructing and correcting this thesis.

My thanks also go to Dr. H. Boom and Dr. T. Radhakrishnan for permitting me to incorporate preliminary work on this thesis into their Compiler Construction and Computer Architecture course requirements respectively. I would also like to thank M. Duarte and D. Hargreaves, who provided me with invaluable assistance in implementing this project on the SEL. I gratefully acknowledge the financial support of an FCAC operating grant which made it possible for me complete this project.

I dedicate this thesis to my wife Shamwattee whose patience and moral support helped me through all five years of it, and to my two baby daughters Kristina and Carolyn who are too young to understand why I had to limit our playing time during the final stages of this thesis.

# TABLE OF CONTENTS

| SIGNATUR | RE PAGE i                                   | Li |  |  |  |  |  |

|----------|---------------------------------------------|----|--|--|--|--|--|

| ABSTRACT | : ii                                        | Li |  |  |  |  |  |

| ACKNOWL  | EDGEMENTS                                   | iv |  |  |  |  |  |

| TABLE OF | CONTENTS                                    | v  |  |  |  |  |  |

| LIST OF  | FIGURES                                     | ix |  |  |  |  |  |

| LIST OF  | TABLES                                      | x  |  |  |  |  |  |

|          |                                             |    |  |  |  |  |  |

| CHAPTER  | 1: INTRODUCTION                             | 1  |  |  |  |  |  |

| 1.0      | Introduction                                | 1  |  |  |  |  |  |

| 1.1      | Microprogrammed Interpreters                | 3  |  |  |  |  |  |

| 1.2      | Microprogrammed Interpreter For Concurrent  |    |  |  |  |  |  |

|          | Euclid                                      | 4  |  |  |  |  |  |

| 1.3      | Organization Of This Thesis                 | 5  |  |  |  |  |  |

|          |                                             |    |  |  |  |  |  |

| CHAPTER  | 2: MICROPROGRAMMING                         | 7  |  |  |  |  |  |

| 2.0      | Introduction                                | 7  |  |  |  |  |  |

| 2.1      | Architectural Aspects Of Microprogramming   | 8  |  |  |  |  |  |

|          | 2.1.1 Control Store Organization            | 9  |  |  |  |  |  |

|          | 2.1.2 Microinstruction Format               | 10 |  |  |  |  |  |

|          | 2.1.3 Microinstruction Sequencing           | 11 |  |  |  |  |  |

| 2.2      | Advantages Of Microprogramming Over Machine |    |  |  |  |  |  |

|          | Language                                    | 14 |  |  |  |  |  |

| 2.3      | Evolution Of Microprogramming 14            |    |  |  |  |  |  |

| 2 4      | Applications Of Microporogramming 16        |    |  |  |  |  |  |

|         | 2.4.1 Operating Systems Support                  | 16   |

|---------|--------------------------------------------------|------|

|         | 2.4.2 Fault Diagnosis and Special Purpose        |      |

|         | Systems                                          | 17   |

|         | 2.4.3 High Level Language Support                | 18   |

| 2.5     | Current Aspects Of Microprogramming              | 19   |

| CHAPTER | 3: COMPILERS, INTERPRETERS AND CONCURRENT EUCLID | 22   |

| 3.0     | Compilers and Interpreters                       | 22   |

| 3.1     | Concurrent Euclid                                | 25   |

| 3.2     | Concurrent Euclid Compiler                       | 26   |

| 3.3     | CE Intermediate Code                             | 28   |

|         |                                                  |      |

| CHAPTER | 4: INTRODUCTION TO THE SEL                       | 32   |

| 4.0     | Introduction                                     | 32   |

| 4.1     | SEL Macroarchitecture                            | 33   |

|         | 4.1.1 Registers                                  | 33   |

|         | 4.1.2 Addressing Modes                           | 33   |

| 4.2     | Instruction Reportoire                           | 35   |

| 4.3     | SEL Assembler Directives                         | 35   |

| 4.4     | SEL Microengine                                  | 37   |

| 4.5     | Timing                                           | 38   |

| 4.6     | SEL Data Structure                               | 39   |

| 4.7     | CPU Microword                                    | 42   |

| СНАРТЕР | 5: DESIGN OF ECODE-I                             | 4:   |

|         | Introduction                                     | A    |

| 7 11    | THE COUNTY FOR                                   | 41.0 |

| 5.1     | Instruction Set                                | 46 |

|---------|------------------------------------------------|----|

| 5.2     | Optimizations                                  | 48 |

| 5.3     | Memory Referencing                             | 49 |

| 5.4     | Operand Specification                          | 50 |

| 5.5     | Design Considerations In Operand Specification | 55 |

| 5.6     | Sample Ecode-I Instructions                    | 57 |

| 5.7     | Comparison of Machine Language And Ecode-I     | 59 |

| 5.8     | CE Intermediate Code And Ecode-I               | 60 |

|         |                                                |    |

| CHAPTER | 6: DESIGN OF INTERPRETER I                     | 63 |

| 6.0     | Introduction                                   | 63 |

| 6.1     | Parallel Execution                             | 66 |

| 6.2     | Analysis And Benchmarking                      | 68 |

|         |                                                |    |

| CHAPTER | 7: ECODE-II AND INTERPRETER II                 | 70 |

| 7.0     | Instruction Set                                | 70 |

| 7.1     | Operand Type                                   | 71 |

| 7.2     | Opcode Decode                                  | 74 |

| 7.3     | Operand Specification                          | 75 |

| 7.4     | Sample Ecode-II instructions                   | 77 |

| 7.5     | Design of Interpreter II                       | 78 |

| 7.6     | Parallel Execution                             | 80 |

| 7.7     | Benchmarking                                   | 83 |

|         |                                                |    |

| CHAPTER | 8: ANALYSIS, FUTURE STUDY AND CONCLUSIONS      | 84 |

| 8.0     | Analysis                                       | 84 |

# viii

| 8.1      | Future  | Study | 7       | • • • | • • • •  | • • • • | • •   | • • • | • • • | • • | • • • | • • | • • | • • • | • • | 85  |

|----------|---------|-------|---------|-------|----------|---------|-------|-------|-------|-----|-------|-----|-----|-------|-----|-----|

| 8.2      | Conclus | sions | • • • • | • • • | ••••     | • • • • | • • • | • • • | •••   | • • | • • • | • • | • • | •••   | •   | 88  |

| REFERENC | ES      |       |         |       |          |         |       |       |       |     |       |     |     |       |     | 91  |

| APPENDIX |         |       |         |       |          |         |       |       |       |     |       |     |     |       |     |     |

| APPENDIX | II:     | SEL C | OMPUT   | ER :  | SYST     | EM .    | • •   | • • • | • • • | • • |       |     |     | • • • | • • | 110 |

| APPENDIX | III:    | ECODE | -I AN   | D II  | NTER     | PRET    | ER    | I     |       |     |       |     |     | • • • | • • | 112 |

| APPENDIX | TV:     | FCODE | -TT A   | ND .  | ישייוע ז | 1 G G   | ומיתי | R T   | Τ.    |     |       |     |     |       |     | 126 |

# ix

# LIST OF FIGURES

| 2.1 | Five Basic Functional Units of a Digital Computing |

|-----|----------------------------------------------------|

|     | System 7                                           |

| 2.2 | Memory Array Control Store Design 10               |

| 2.3 | Vertical and Horizontal Microinstructions 11       |

| 2.4 | Serial-Parallel Microinstruction Fetch 13          |

| 3.1 | The Phases of a Compiler and Interpreter 24        |

| 4.1 | SEL 32/75 Microengine 37                           |

| 4.2 | Microinstruction Timing 39                         |

| 4.3 | SEL 32/75 Data Structure 40                        |

| 5.1 | Design of Ecode-I 45                               |

| 5.2 | Operand Decode Algorithm 53                        |

| 6.1 | Implementation Of Ecode-I 64                       |

| 6.2 | Logical Structure of Interpreter I 65              |

| 7.1 | Implementation Of Ecode-II 79                      |

| 7.2 | Logical Structure of Interpreter II 80             |

# LIST OF TABLES

| 4.1 | SEL F and C Addressing Bits                    | 34 |

|-----|------------------------------------------------|----|

| 4.2 | SEL 32/75 Instructions by Category             | 36 |

| 5.1 | Ecode-I Instructions by Category               | 46 |

| 5.2 | Sample Ecode-I Instructions                    | 47 |

| 5.3 | Comparison of SEL Machine Language and Ecode-I | 60 |

| 7.1 | Ecode-II Instructions by Category              | 70 |

| 7.2 | Sample Ecode-II Instructions                   | 71 |

#### CHAPTER 1: INTRODUCTION

#### 1.0 Introduction

There are several methods of executing programs written in a high level language. The most widely used is to compile the programs into machine language. Another is to translate the programs into some intermediate form and then to execute that form interpretively. A third method is to directly execute either the high level language or the intermediate form [HASS76].

A compiler is a computer program which accepts as input a program written a high level language (HLL) and produces as its primary output machine language code that will instruct some computer to produce results equivalent to those defined by the original HLL. Although there are many different ways to write one, all compilers perform two basic processes: analysis of the HLL source text, and synthesis of machine language instructions, or object text.

The use of intermediate languages as a convenient means of developing portable HLLs is now fairly standard. With this approach the compiler for language A compiles the source code into intermediate language I, which is usually pseudo machine language. For each machine that the language is to

be implemented on, there is either a program that converts I into assembler language for that machine or, alternatively, an interpreter may be written which executes the pseudo machine codes directly. The interpreter is usually considerably less efficient than a compiler because it carries the burden of intermediate code analysis in addition to execution.

The justification for the intermediate code approach is that portability of compilers is enhanced. The major sections of the compiler can be written in a high level, portable language to generate machine independent intermediate code, in which the complex HLL constructs have been translated into relatively simple and fewer intermediate code constructs. Portability is then obtained by writing what is a relatively small interpreter or compiler for the intermediate language to machine language.

Portability would be improved if the intermediate language could be executed directly as this would avoid either the step of converting the intermediate language, or the reduced performance resulting from interpreting it. With the availability of writable control store as an option on most minicomputers, there is merit in investigating the feasibility of direct execution of intermediate languages on a mini-computer. If feasible, then this represents an

efficient way to obtain language portability [COOP80].

# 1.1 Microprogrammed Interpreters

The use of microprogrammed interpreters to enhance high level language execution speed has been around for a long time. Papers describing the potential gains were quite common during the early 1970's [BROA75], and the Burroughs B1700/1800 machines were designed to directly execute the intermediate languages that were developed for different HLL's [COOP80]. To date, however, the author has been able to locate only a few published articles describing actual implementations of microprogrammed interpreters, and these are summarized below.

Broca and Mervin found gains of 12-75% in their implementation of a microcoded interpreter for Fortran compared with the Fortran H and G compilers on an IBM 360 computer system [BROC73]. Cooper has implemented a microprogrammed interpreter for subsets of the intermediate code generated from BCPL and Pascal [COOP80]. He did not report extensive benchmarking results but found that Wirth's prime number program [JENS75] ran three times as fast as the compiled version.

A microprogrammed interpreter for the intermediate language of Modula was designed by Habib and Yang using bit-slice AMD 2900 architecture [HABI81]. Schaeffer and Pratt investigated the effect of microcoding selected parts of a software interpreter for the intermediate language of UCSD Pascal. They reported significant improvements though not as high as they expected [SCHA83].

Gee et al have implemented a high performance Prolog engine by directly executing its intermediate form as generated by a Prolog compiler, on the VAX 8600. Their initial results indicate that their system is the fastest implementation of Prolog on a commercially available general purpose processor [GEE86]. Okuno et al implemented a microprogrammed version of a Lisp interpreter on a TAO/ELIS system and their results indicate that the speed of interpreted code of TAO is comparable to that of compiled codes of commercial Lisp machines [OKUN87].

## 1.2 Microprogrammed Interpreter For Concurrent Euclid

This thesis was aimed at investigating the feasibility of directly executing the intermediate representation of the sequential features of Concurrent Euclid (CE) on the SEL 32/75 computer. A CE compiler and source code for the VAX 11/780 and a user microprogrammable minicopmuter, the SEL

for this project. A SEL code 32/75, were available generator was written and the Euclid compiler ported to the SEL. A translator was then designed and implemented to convert the intermediate code generated by the compiler into Ecode, a form more suitable for interpretation on the SEL. A microprogrammed interpreter for Ecode was designed and implemented on the SEL and benchmarked against the compiler. For the CPU-bound algorithm Sieve of Eratosthenes, the interpreter was measured to be about twice as slow as the compiler. Ecode was then modified, and a new translator and The same benchmark interpreter designed and implemented. yielded comparable results for both the interpreter and compiler.

## 1.3 Organization Of This Thesis

The remainder of this thesis describes this project. Chapter two introduces microprogramming and its applications while chapter three introduces compilers, interpreters, Concurrent Euclid and its intermediate code which is translated into Ecode for interpretation. Chapter four gives an overview of the SEL computer, its architecture and microengine. Chapter five describes the design of Ecode, referred to as Ecode-I, and chapter six the implementation of the original microprogrammed interpreter and its benchmarking. Chapter seven describes the modified Ecode,

referred to as Ecode-II, and the microcoded interpreter which yielded comparable results to the compiler. Chapter eight identifies topics for future study and concludes the project.

#### CHAPTER 2: MICROPROGRAMMING

#### 2.0 Introduction

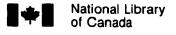

Digital computing systems have traditionally been described as being composed of five basic units: input, output, memory, arithmetic and logic, and control as shown in figure 2.1 below [REIG72].

Figure 2.1 Five Basic Functional Units of a Digital Computing System (from RIEG72)

Machine instructions and data communication among the units (as indicated by the solid lines in figure 2.1) are generally well known and understood. The control signals (as indicated by the dashed lines) are generally less well

known and understood except by the system designer. These control signals generated in the control unit determine the information flow and timing of the system [REIG72].

Microprogramming was first proposed by professor M. V. Wilkes in 1951 as a systematic alternative to the rather adhoc method of designing the control system of a digital computer in use at that time [WILK69]. His thesis was that one can envision the control system of a computer as effecting a number of register-to-register transfers of information, some in sequence and some in parallel, in order to carry out the execution of a single machine instruction. The steps used to execute the instructions in a user machine can be thought of as constituting a program, called a Besides being a more structured microprogram [ROSI69]. design, microprogramming control system approach to introduced a large degree of flexibility in the design, implementation and maintenance of the instruction set of a computer.

# 2.1 Architectural Aspects Of Microprogramming

Juan Linares describes the hardware aspects of microprogramming quite nicely in his master's thesis [LINE82] and the following sections on control storage organization, microinstruction format and sequencing are

reproduced from his thesis.

The study of microprogramming hardware may be divided into three main areas which are related, but complex enough to deserve independent 'consideration. These are: control storage organization, microinstruction format and microinstruction sequencing.

# 2.1.1 Control Storage Organization

Control storage refers to a store from which microprograms are executed. This does not imply that control storage is distinct from main memory, although that is often the case. Most microprogrammed computers store microprograms in a smaller but faster memory, but there are some exceptions such as certain models of the IBM 360 series and the Burroughs B1700 in which microprograms are executed from an area of main memory [DASG79].

One of the major disadvantages of microprogramming compared to hardwired control, is the time involved in fetching microinstructions from control storage. This factor can be made insignificant by appropriate implementations of control storage and microinstruction execution; hence the importance of control storage organization.

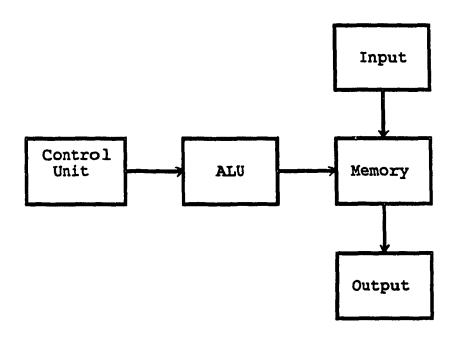

Control storage can be logically organized in several ways.

The simplest and most common structure is the ordinary

memory array with one microinstruction per word. variation of this form is to increase the size of the microword in order to accommodate two microinstructions. The advantage of this is that fewer memory references are required since two microinstructions can be accessed simultaneously. The memory array organization illustrated in figure 2.2. Other organizations include the level organization blocked, split structure and two [LINE82].

One Microinstruction per Word

Two Microinstructions per Word

Figure 2.2: Memory Array Control Store Organization

#### 2.1.2 Microinstruction Format

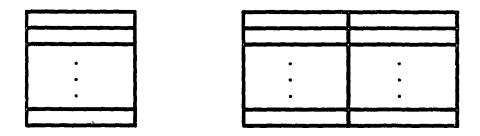

A microinstruction is merely a string of bits whose meaning is determined by the decoding hardware. Of primary interest in the design of microinstructions is the number of resources each microinstruction controls. In this respect microinstructions are classified as vertical or horizontal

[RAUC80] although these designs refer to the extremes of a broad spectrum.

Vertical microinstructions effect single operations such as LOAD, STORE, and BRANCH; they often resemble machine language instructions containing one or more operands. Horizontal microinstructions, in contrast, control many resources which may operate in parallel. A microinstruction might control, for example, the simultaneous and independent operation of the ALU, input and output to main memory, conditional next address generation, etc. These microinstructions have the potential advantage of efficient hardware utilization, but the optimization process is a difficult task. Figure 2.3 below illustrates vertical and horizontal microinstructions.

Figure 2.3: Vertical and Horizontal Microinstructions

## 2.1.3 Microinstruction Sequencing

The microinstructions sequencing mechanism is a great source of variability among microprogrammable machines, since they all have different and often inconvenient addressing

mechanisms [PERS77]. Microinstructions are executed in a general fetch-decode-execute sequence, but details of actual implementation can vary greatly. Generally a microprogram counter is used to indicate the address of the next microinstruction, and a certain field may be set aside within the microword to indicate a branch address. Unlike machine language programming, the effects of the sequencing scheme are not hidden from the microprogrammer and he must cope with them.

In sequencing microinstructions there are two aspects to be considered, one is the fetch-execute cycle of the microinstructions themselves and the other is the sequencing of microoperations within each microinstruction.

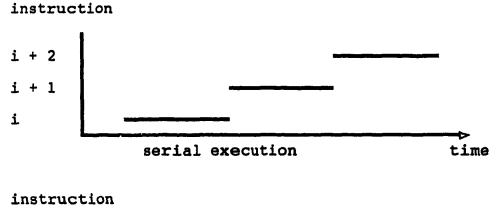

The first aspect is described by the serial-parallel characteristics of the sequencing scheme. In a serial implementation, fetching the next microinstruction does not begin until the execution of the current one terminates. parallel implementation, the fetch of the next microinstruction begins while the current one is being executed. The advantage of the serial approach is simplicity of realization, while the advantage of the parallel approach is the corresponding saving of time. Figure 2.4 illustrates the serial-parallel microinstruction fetch.

Figure 2.4: The Serial-Parallel Characteristics

The second aspect of sequencing is described by the number of minor clock cycles used to execute a microinstruction. In a monophase implementation there are no distinct control cycles and the microinstruction is executed by a single simultaneous issue of control signals. In a polyphase implementation each major clock cycle comprises multiple subcycles and the hardware generates control signals at each subcycle. The advantage of monophase operation is the simplicity of realization, whereas the advantage of polyphase operation is that it allows better utilization of the resources at the expense of more complicated hardware.

# 2.2 Advantages Of Microprogramming Over Machine Language

The main advantages of microprograms over machine language programs are speed and accessability to the hardware data structures of the computer. Microprograms generally execute much faster than machine language programs because of several factors, namely:

- . the ratio of control store speed over main memory

- . the greater power of micro instructions over machine language instructions. A machine language instruction consist of more that one microinstruction.

- . ability of microinstructions to allow parallel operations within the execution timing of a single instruction.

- direct interface of the microinstruction to the hardware, thereby eliminating the need to do memory fetches and decodes of all instructions.

These advantages of microprogramming have been utilized in a number of applications, some of which are described in the following sections.

# 2.3 Evolution of Microprogramming

Following Wilkes's initial investigation microprogramming received some attention during the 1950's, but it was not

until the 1960's that microprogramming was to be used significantly on a commercial scale. The main reason for this was that until the 1960's the simplicity and flexibility offered by microprogramming was more than offset by the tremendous overhead of a memory access for each microinstruction [RAUC80].

With the development of fast, inexpensive semiconductor memories there emerged an interest in microprogramming as a means of designing a range of computers of differing power but with compatible instruction sets. The best example of this is the IBM 360 series in which all machines were at least upward-compatible. In this series all but the largest computer then announced, model 70, had microprogramming based on ROM [STEV64].

This contributed to the development of hardware emulation as an important research topic. Tucker defined an emulator as a package that includes special hardware and a complementary set of software routines [TUCK65]. Emulation therefore does not imply the implementation of an entire instruction set of a computer in a microprogram. A machine instruction may be microprogrammed if its software implementation is too difficult, too inefficient, or if it is used so often as to be worth the effort of microprogramming it.

The latest phase of of microprogramming is characterized by the appearance of user microprogrammable machines which provide tools to carry out research on the various aspects of microprograming. Advances in integrated circuits technology have led to the appearance of powerful microprocessors which have given great impulse to microprogramming. With the development of user microprogrammable machines, minicomputers and bit-sliced microprocessors the application of microprogramming spread to operating system support, fault diagnosis and special purpose systems, and support for high level language execution [RAUS80].

# 2.4 Applications of Microprogramming

As mentioned above, in addition to being an alternate way to design the control system of a computer and machine emulation, microprogramming can be used for operating systems support, fault diagnosis and special purpose systems, and to execute high level languages.

# 2.4.1 Operating systems support

Microprogramming can be used to assist the implementation of operating systems in two basic ways. First, by direct implementation of primitives in microcode and second,

microprograms can support primitives by implementing a suitable virtual machine on which the primitives can be executed. Primitives which are ideal candidates for miprogrammed implementation include bit manipulation operations, search routines, process synchronization, interprocess communication and protection, and interrupt handling. On the Burroughs B1700 computer a microprogrammed kernel handles time critical operating systems functions such as interrupt handling, scheduling, I/O processing and virtual memory management [WILK72].

## 2.4.2 Fault Diagnosis And Special-Purpose Systems

Microdiagnostics are microprograms that diagnose system hardware to detect and locate hardware faults. computer systems, especially real time systems, it is necessary to continue operation even in the presence of hardware failures. Microdiagnostics can generally access all CPU resources and locate hardware faults with a higher resolution and much faster than other methods, and do not require extensive use of main memory. Microprograms are ideally suited for special purpose, CPU intensive applications. These include signal processing, graphics, numerical algorithm implementation, implementation of special systems for research and development purposes.

# 2.4.3 High Level Language Execution

The principal ways of using microprogramming to support high level language processing are: compile the high level language directly into microcode, microprogram critical sections of the high level language program, and use different target codes and microcoded interpreters for each language.

The first approach will generally give the most efficient implementation. In general this approach involves a much more complex operating system and several problems that occur at the machine code level show up again at the microcode level [BROA75]. In spite of these complications such languages and compilers have been designed and implemented on minicomputers and microcomputers. Fagin et  $\mathsf{of}$ al describe the compilation Prolog directly into microcode, resulting in the fastest functioning Prolog system known to them [FAGI85]. This approach continues to be a main focus of microprogramming research in the academic community [SHRI81].

The second approach offers a way to improve the execution speed of a given high level language program by analysis of the program to determine the sections where most of the CPU execution time is used, and microcoding of these parts of

the program. Time critical applications such as real time processing and operating systems are good candidates for this type of support.

The third approach generally involves translating the high level language into an intermediate form and interpreting this intermediate code with a microcoded interpreter. The theory is that the greater speed of the microprogram will offset the higher overheads associated with interpreters. The advantage of this scheme is that it is not as complicated as the first and it is more general that the second. The microprogrammed interpreter for UCSD Pascal on the PDP-11 is an example of this [SCHA83].

#### 2.5 Current Aspects Of Microprogramming

The current microprogramming interest in the academic community can be grouped into three general categories, namely, the automatic generation of correct, compact microcode from a high level language for different target machines, computer architecture design, and development of microprogramming tools.

By far the greatest emphasis is on the first category, with considerable material reported in the literature on projects on high level microprogramming languages (HLMLs), microcode

compilers, microprogram generation systems for retargetable implementations, hardware description languages (HDLs), and microcode compaction and verification schemes [SIGM86], [SIGM85]. The general objective is a microcode generation system which accepts as input an HLML and an HDL for a given machine, and outputs a correct and optimized microprogram for that given target machine.

Microprogramming research in computer architecture design is geared towards the development of processors for a variety of general and special purpose applications. Control Data applying microprogramming techniques to the Corporation is development of a multiple instruction set architecture processor using VLSI and CMOS technology [WILK84]. Patt et report working on microarchitectures for implementing al high performance computing engines [PATT85]. DuBose et al describe the initial design of a microcoded RISC-type machine, MIRIS, under development at George Mason University. The basic difference between MIRIS and other research prototype RISC machines is that the control of MIRIS is microcoded while the others are hardwired [DuBO86].

The increased use of microprogramming in recent years has created a need for sophisticated tools to support the development of microprograms. The literature reports on the development of interactive high level debuggers for

microprograms, and microprogram simulators for given architectures. The latest development is the automatic tool generation process which accepts as input a description of the microarchitecture in an HDL and generates as output an assembler, linkage editor and simulator tailored for that architecture [TRAC85].

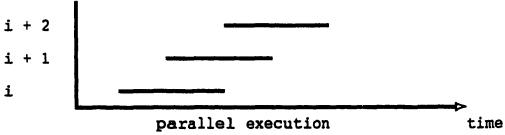

## 3.0 Compilers And Interpreters

A compiler is a translator which converts an input "source" language into an output "object" language which is recognizable to a specific computer hardware configuration. The translation typically occurs in three phases. includes syntactic analysis of the source program to guarantee its correctness and tabulation of all symbols; the second consists of a semantic analysis which converts the source statements into an intermediate text form. phase, referred code generation, converts the to as intermediate text into machine code for a particular hardware system.

An interpreter differs from a compiler in that it does not generate machine code but executes the intermediate text. It is usually considerably less efficient than a compiler because it carries the burden of intermediate code analysis in addition to execution. P. J. Brown [BROW81] explains this difference quite nicely with the following analogy. Assume you are an English speaker who does not understand French very well, and you are given some instructions in French to do a certain job. Assume further that you are a bit stupid, like a computer, and do not remember anything

unless you write it down, and then later read back what you have written.

The simplest way of executing the French instructions is to take each one in sequence, figure out what it means, and then obey the instructions. Thus, performing an instruction consists of two stages: decoding and action. disadvantage of this is that if an instruction is repeated several times you have to repeat the decoding of the French instructions equally many times -- do not forget you are too stupid to remember them automatically. This suggests an approach: first decode all the French alternative instructions into English and write them down; then follow the English instructions.

The second approach is initially more time consuming, because translating into proper written English is more of an effort that figuring out the French instructions in your head. However, it becomes faster overall if the instructions are to be repeated. An interpreter corresponds to the first approach and a compiler to the second approach.

Because of the huge overheads of interpretation of a source language almost all compilers and most interpreters translate the source language into an intermediate form

which is easier to decode. This intermediate code could take a variety of forms. At one extreme it could be machine code, as would be for a compiler; at the other it could be almost the same as the source language, as would be the case (almost) pure interpreter. As the intermediate form moves away from the source language towards machine language the compiler gets steadily bigger but the users' programs run steadily faster. There is a spectrum of possiblilities between these two extremes, and real production compilers and interpreters lie all along the spectrum. Figure 3.1 below shows the steps taken by a compiler and interpreter.

Figure 3.1: The Phases of a Compiler and Interpreter

#### 3.1 Concurrent Euclid

Concurrent Euclid (CE) was designed to support implementation of highly reliable, high performance software such as compilers and operating systems. CE is based on Pascal and borrows Pascal's elegant data structures. Various features of Pascal were "purified" to allow easier verification; for example, in CE functions are prevented by the compiler from having side effects. The major features CE adds to Pascal are:

- Separate compilation procedures, functions and modules can be separately compiled and later linked together.

- 2. Modules a module is the syntactic packing of data structures with the procedures and functions that access the data.

- 3. Concurrency Monitors and processes are supported.

There is a SIGNAL and WAIT statement. A BUSY statement allows CE to be used as a simulation language.

- 4. Control of Scope names of variables, types, etc., are not automatically inherited by scope. Import and export lists are used to control the scope of names.

- 5. Systems programming constructs These include

variables at absolute addresses. Such variables can be device registers in computers with memory mapped I/O.

There are some Pascal features, such as enumerated types, that CE does not support. CE does not allow procedures and functions to be nested inside procedures and functions. More details on CE are presented in Appendix I and a complete description given in [HOLT83].

# 3.2 Concurrent Euclid Compiler

The CE compiler makes four passes over the source input and its intermediate forms. The first three of these (the parser, semantic analyzer and storage allocator) are machine independent. The fourth, the code generator, is the only one that has to be changed to port the compiler to another machine. The intermediate code which will be transformed and interpreted by the microprogrammed interpreter is the output of the storage allocation pass.

A complete formal description of CE is given in [HOLT83]. Below is an example of a CE implementation of a stack. Two operations Push and Pop are defined on a data structure called Table. Push adds an item to Table and Pop returns the item most recently added to Table. The initially block

sets the number of items in Table to zero at the start of execution.

```

var stack:

module

exports (push, pop)

const depth := 1..10

var top: 0..depth

var table: array 1..depth of signedint

procedure push(i:signedint)=

imports (var top, var table)

begin

top := top + 1

table(top) := i

end push

procedure pop(var i:signedint) =

imports (var top, var table)

begin

i := table(top)

top := top - 1

end pop

initially

imports (var top)

begin

top := 0

end

end module

```

# 3.3 CE Intermediate Code

The intermediate form generated as output of the storage allocator pass of the compiler is a string of tokens. The intermediate representation of the procedure "push" is shown below with comments.

| Intermediate Rep  | resen | tatio | n |   |    |     | Comment         |

|-------------------|-------|-------|---|---|----|-----|-----------------|

| aRoutineIndex 0   |       |       |   |   |    |     |                 |

| aldentText 4 push | h     |       |   |   |    |     | procedure push  |

| aNewline 9        |       |       |   |   |    |     |                 |

| aBegin            |       |       |   |   |    |     | begin block     |

| aNewline 10       |       |       |   |   |    |     |                 |

| aDataDescriptor   | 162   | 1     | 0 | 0 | 2  | 0 0 | top             |

| aAssign           |       |       |   |   |    |     | = ·             |

| aDataDescriptor   | 162   | 1     | 0 | 0 | 2  | 0 0 | top             |

| aDataDescriptor   | 1     | 127   | 1 | C | 1  | 0 1 | 1               |

| aAdd              |       |       |   |   |    |     | +               |

| aEndExpression    |       |       |   |   |    |     |                 |

| aNewLine 11       |       |       |   |   |    |     |                 |

| aDataDescriptor   | 162   | 1     | 3 | 0 | 20 | 0 2 | table           |

| aSubs             |       |       |   |   |    |     | start subscript |

| aDataDescriptor   | 162   | 1     | 0 | 0 | 2  | 0 0 | top             |

| aEndExpression    |       |       |   |   |    |     | _               |

| aEndSubs          |       |       |   |   |    |     | end subscript   |

| aDataDescriptor | 1   | 127 | 1 | 0 1 | 0 1   | lower bound      |

|-----------------|-----|-----|---|-----|-------|------------------|

| aDataDescriptor | 1   | 127 | 1 | 0 1 | 0 1   | upper bound-1    |

| aDataDescriptor | 1   | 127 | 1 | 0 1 | 0 9   | size of item     |

| aDataDescriptor | 129 | 127 | 0 | 0 2 | 0 0   | array attributes |

| aAssign         |     |     |   |     |       | =                |

| aDataDescriptor | 162 | 2   | 0 | 0 2 | -1 -4 | I                |

| aEndExpression  |     |     |   |     |       |                  |

| aNewLine 12     |     |     |   |     |       |                  |

| aEndBegin       |     |     |   |     |       | end begin block  |

| aNewLine 13     |     |     |   |     |       |                  |

An aNewline token refers to the source line number that generated the code following it. The most complex structure in the intermediate language is the specification of data objects. A simple data object is represented by an "aDataDescriptor" token which has five fields as shown below:

| Status Base Rep. Value Displ. | ·      |      |      |       |        |

|-------------------------------|--------|------|------|-------|--------|

| Nop.                          | Status | Base | Rep. | Value | Displ. |

The status field is a bit encoded string indicating the addressing and alignment of the operand. The base field describes the location of the operand. The possibilities are: on runtime stack, in global read/write storage area, immediate operand in the descriptor itself, or in a register. The representation and value fields determine the

sign and size of the operand, that is, unsigned byte, signed long (or 4 bytes), array etc. The displacement field gives the displacement of the operand from one of the bases described in the base field. In the case of an immediate operand this field contains the actual value of the operand. The displacement and value fields are both 32 bits long and are implemented as two 16 bit values. The other three fields are 16 bits long.

As an example, consider the data descriptor for the variable "top" in the preceding example of the CE module "stack". The data descriptor is:

aDataDescriptor 162 1 0 0 2 0 0

The values and interpretations of the corresponding fields are as follows:

Status = 162 - bit 1 is set - indicates indirect addressing

bit 5 is set - indicates operand

has a lexic base

bit 7 is set - operand is aligned on a two byte boundary

Base = 1 - indicates operand is on run-time stack

Representation = 0 - representation an value fields

Value = 0 2 - indicate operand is signed 16

bit integer

Displacement = 0 0 - zero indicates that the operand starts at the base address.

An array element requires at least six data descriptors for its specification. These are:

- . start location and size of array 1 data descriptor

- . subscript at least 1 data descriptor

- . lower bound 1 data descriptor

- . upper bound-1 1 data descriptor

- . size of item 1 data descriptor

- . attributes of item (eg. signed/unsigned) 1 data descriptor.

A more detailed description of this intermediate code is given in Appendix I.

#### CHAPTER 4: INTRODUCTION TO THE SEL

#### 4.0 Introduction

The SEL 32/75 is a high speed, general purpose, digital computer system. It is designed for a variety of scientific, data acquisition and real time applications. A basic system includes a central processing unit, main memory subsystem, and microprogrammed I/O controllers.

The CPU has a large instruction set that includes fixed and floating point arithmetic instructions. A special lookahead feature enables the CPU to overlap instruction execution with memory accessing, thereby reducing program execution time. The main memory of 16 megabytes can consist of up to 16 modules of 64K bytes each on each of up to 16 memory busses. Memory can be shared by up to 20 CPU's and their associated I/O processors [SEL1].

The SEL 32 series computers use a microprogrammed control section (CROM) to decode and execute machine instructions. The writable control store (WCS) option consists of one or two 64 x 2K high speed random access memory boards which provide a physical extension of the control store. This feature allows the user to tailor the machine to accommodate any special user needs.

#### 4.1 SEL Macroarchitecture

### 4.1.1 Registers

The SEL 32/75 has eight general purpose registers (GPR's) for use by the assembly language programmer for arithmetic, logical and shift operations. Three of the eight GPR's, RO, R1, R2, can also be used for indexing operations. Register RO can also be used as a link register, and R4 can be used as a mask register.

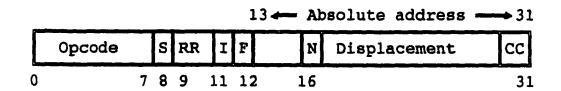

# 4.1.2 Addressing modes

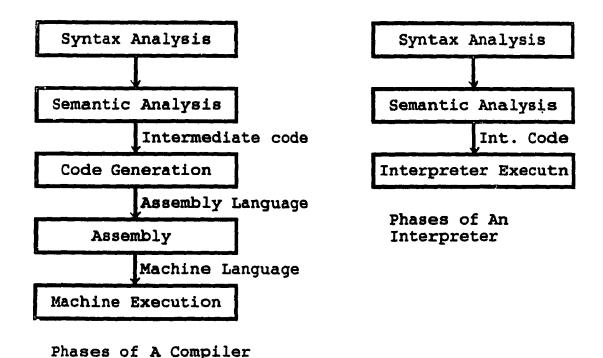

The general format of a memory reference instruction is shown below.

bits 0..5 - opcode

bits 6..8 - source register

bits 9..10 - index register

bit 11 - indirect addressing

bit 12 - F bit. memory addressing

hits 16..31 - displacement or literal

Bits 9..31 have the same format in every memory reference instruction, regardless of whether the effective address is used for storage or retreival, as an indirect address, or to alter program flow. The format of the F and C bits have been selected so that any specified data type byte, 16 bit halfword, 32 bit word, or 64 bit doubleword can be conveniently referenced. The possible combinations of F and C bits are as shown in table 4.1 below:

| F bit (12)                      | C bits (30                                    | ,31) Data type                                                                                                                                           |

|---------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>1 0 | 32 bit word 16 bit half word. bits 015 64 bit doubleword 16 bit half word.bits 1631 byte 0. bits 07 byte 1. bits 815 byte 2. bits 1623 byte 3. bits 2431 |

Table 4.1: SEL F and C Bits Addressing

The following addressing modes are provided:

- Direct addressing the effective memory address is taken directly from bits 13..31 of the memory reference instruction.

- 2. Indexed addressing bits 13..31 are used to produce a memory address by adding it to the contents of the register specified by bits 9..10. Only registers

- 1,2 and 3 can be used as index registers.

- 3. Indirect addressing the address of the operand is contained in the memory word specified by adding the contents of bits 13..31 to the contents of the register specified in bits 9..10.

- 4. Immediate addressing the operand is in bits 16..31 of the instruction.

- 5. Register addressing the operand is in a register specified by bits 6..8.

# 4.2 Instruction Repertoire

The functional classification and number of instructions for the SEL 32/75 computer are shown in table 4.2. A complete list of the SEL 32/75 instructions is given in [SEL1].

### 4.3 SEL Assembler Directives

The Ecode programs interpreted by the microprogrammed interpreter are generated in SEL assembly language which are translated by the SEL assembler into machine code. A partial description of the SEL assembly language directives used in Ecode generation is given below, and a complete list in Appendix II.

| BOUND | N       | forces the program counter to an N      |

|-------|---------|-----------------------------------------|

|       |         | byte boundary; for example N = 4        |

|       |         | indicates fullword boundary and $N = 2$ |

|       |         | indicates halfword boundary.            |

| GEN   | N/B     | define N bits of memory with value B;   |

|       |         | for example GEN 8/1,8/2,8/3,8/4         |

|       |         | generates the bit configuration: 0000   |

|       |         | 0001 0000 0010 0000 0011 0000 0100      |

| LABEL | EQU VAI | UE equals tag; equates LABEL with       |

|       |         | VALUE                                   |

| classification             | number |

|----------------------------|--------|

| Fixed point arithmetic     | 30     |

| floating point arithmetic  | 8      |

| boolean                    | 17     |

| load/store                 | 29     |

| bit manipulation           | 8      |

| zero operand               | 5      |

| shift                      | 13     |

| interrupt                  | 13     |

| compare                    | 11     |

| branch                     | 9      |

| register transfer          | 13     |

| input/output               | 10     |

| control                    | 16     |

| hardware memory management | 4      |

| writable control store     | 3      |

| total                      | 189    |

Table 4.2: SEL 32/75 instructions by category.

#### 4.4 SEL Microengine

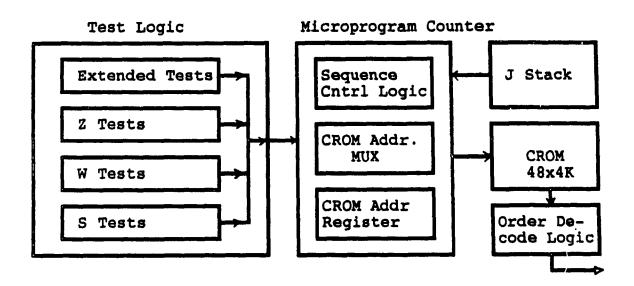

The operation of the SEL 32 computer is controlled by the central processing unit (CPU). In the CPU, the controlling hardware which executes the firmware (microprogram) is referred to as the microengine. Figure 4.1 presents a block diagram of the SEL microengine.

Figure 4.1: Block Diagram of SEL Microengine

The microengine consists of the following hardware sections:

- Control Store (CROM) consists of several read only memories used to store the microprograms.

- 2. Test Logic the basic tests are the first part of the microinstruction to be executed. All basic tests must be completed before execution of the

microinstruction orders.

- 3. Microprogram counter consists of several hardware sections which are used to select from a number of sources the next CROM address to be used by the microprogram.

- 4. Order decode stack the last part of the microinstruction to be executed is the microinstruction orders (or operations). Orders are decoded and executed by this hardware.

- 5. J stack a 4 x 13 bit register stack that acts as a last in, first out microprogram address stack. This can be used to implement microsubroutine calls.

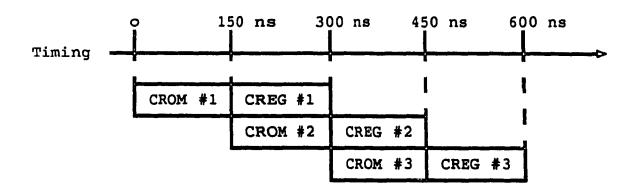

# 4.5 Timing

Instruction execution within the microengine generally requires two cycles, the first being the CROM cycle and the second is the CREG cycle. Each cycle is 150 nanoseconds long thereby requiring a total of 300 nanoseconds to complete an instruction. During the first 150 nanoseconds the basic tests and sequencing are done; the second 150 nanoseconds execute all orders that the microinstruction directs. Although each microinstruction requires 300 nanoseconds to execute fully, one microinstruction can be completed every 150 nanoseconds by overlapping the CROM cycle of the second instruction with the CREG cycle of the

first instruction as shown in figure 4.2.

Figure 4.2: Microinstruction Timing

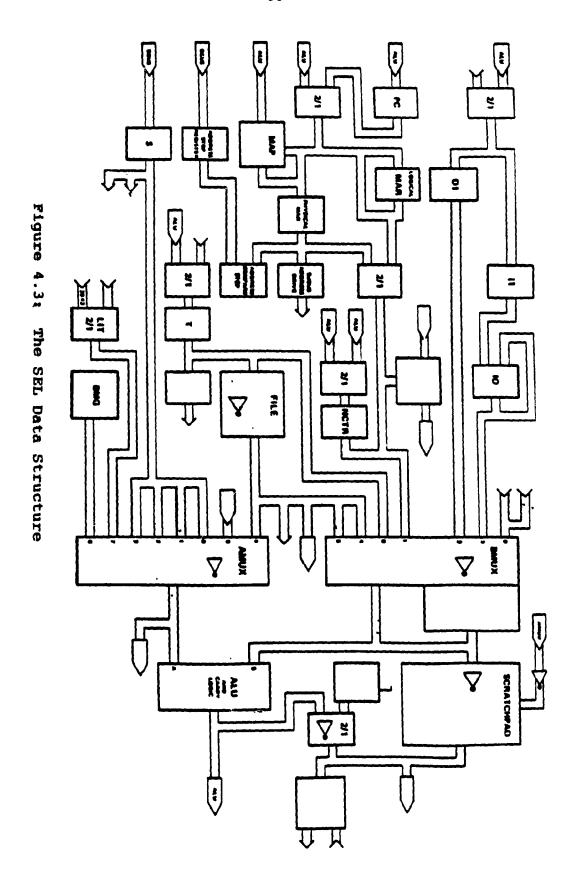

### 4.6 SEL Data Structure

The SEL data structure consists of 32 x 32 general file two multiplexors hardware registers, and registers, organized around an Arithmetic and Logic Unit and a 256 x 32 bit local store. The hardware registers are used for SELBUS communications, temporary storage, and Figure 4.3 shows a diagram of the SEL data structure. Unlike the machine language programmer who has access to only eight general purpose registers, the microprogrammer can directly access the entire SEL data structure. The data structure is presented in the following order:

1. Arithmetic and Logic unit - The ALU is a two-input

32-bit Arithmetic and Logical unit, utilizing four

lookahead carry generators for increased speed of operation. The inputs to the ALU are selected by the A-Mux and B-Mux. The output destination of the ALU may or may not be specified. If not specified the output of the ALU is used for testing purposes only. The output of the ALU can be distributed to any of the registers and WCS output data.

- 2. A-Multiplexor (AMUX) selects input into ALU

- 3. B-Multiplexor (BMUX) selects input into ALU

- 4. Literal Generator generates an 8 bit constant

- 5. General file registers (FILE) 32 x 32 bit general purpose registers organized in two banks of 16 registers each.

- Memory address register (MAR) 24 bit register

used to address main memory

- 7. Program counter register (PC) a 22 bit counter used to address the next instruction to be executed.

- 8. N-Counter register (NCTR) 8 bit binary counter.

Can be incremented or decremented in the CREG

cycle or decremented in the CROM cycle

- 9. Shift register (S) 32 bit register used for shifting, either by nibble (4 bits) or by bits.

- 10. Temporary register (T) 32 bit register used to

- temporarily hold all data to be stored in the general purpose registers.

- 11. Data input register (DI) 32 bit register used to receive operands from memory or data and status from I/O processors.

- 12. Instruction decode register (I0) 32 bit register containing the current instruction being executed.

- 13. Instruction pipeline register (II) 32 bit register used to receive macro instructions as they return from memory. This register usually contains the next instruction to be executed.

- 14. Local store (SCRATCH) 256 x 32 bit RAM storage for fast access data storage.

- 15. Bit mask generator (BMG) generates 32 bit masks for bit manipulation instructions.

#### 4.7 CPU Microword

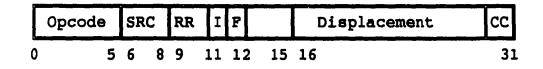

The full CPU microword is 64 bits of which only 48 are directly associated with CPU operations, the remaining 16 bits are used for the optional high speed floating point unit. The microword is divided into 13 fields, each of which define tests and operations to be executed in parallel. These fields are described below.

| 1 | _ |   |   |   | بالمساوي | بطريعات المراجع |   | _ |   | _ |   |   |   |

|---|---|---|---|---|----------|-----------------|---|---|---|---|---|---|---|

|   | T | s | М | A | В        | +               | ם | R | Y | x | P | С | н |

|   |   |   |   |   |          |                 |   |   |   |   |   |   |   |

- 1. Primary test field (T-field) specifies 16 basic tests which are decoded during the CROM timing cycle

- 2. Sequence field (S-field) specifies the address

sequencing

- 3. Control field (M-field) executed in CROM cycle

- 4. A-Mux field (A-field) selects source of A input to the ALU

- 5. B-Mux field (B-field) selects source of B input to the ALU

- 6. ALU field (+ field) selects the ALU function to be performed

- 7. Destination field (D-field) selects destination for ALU output

- 8. File register field(R-field) selects one of 16 registers

- 9. Y-Order field (Y-field) the five order fields

- 10.X-order field (X-field) X, Y, P, C, and H

- 11.P-Order field (P-field) define specific

- 12.C-Order field (C-field) instructions to be carried out on the input/output

13.H-Order field (H-field) - of the ALU.

A complete description of the SEL writable control store can be obtained from [SEL2].

#### CHAPTER 5: DESIGN OF ECODE-I

#### 5.0 Introduction

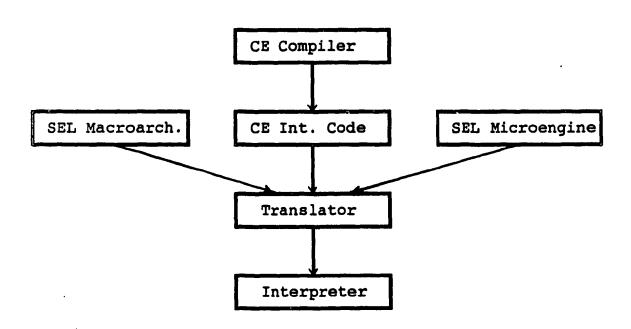

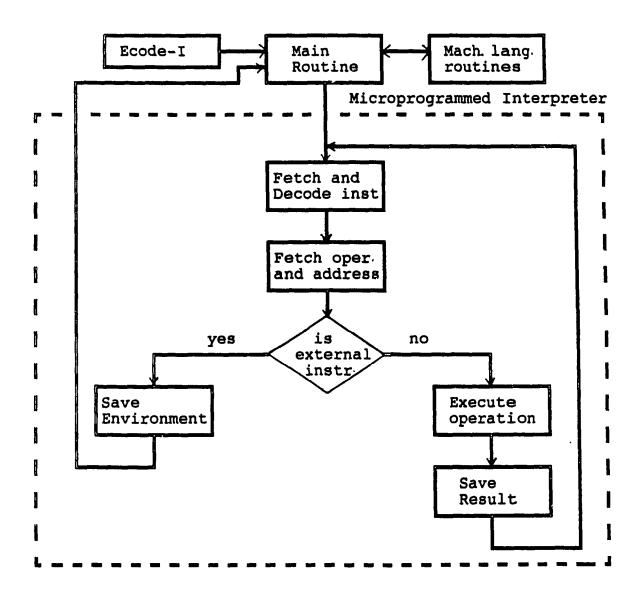

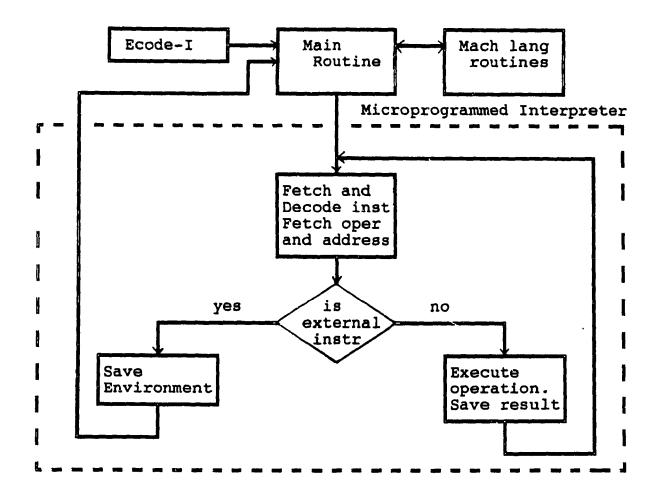

An interpreter generally executes the intermediate code directly instead of translating it into machine language as is done in a compiler. To interpret Concurrent Euclid a translator was written to convert the intermediate code generated by the CE compiler into Ecode-I, a form more suited for interpretation on the SEL. The design of Ecode-I incorporated inputs from the CE intermediate code and the SEL microarchitecture, as shown in figure 5.1 below. The format of Ecode-I is described in the following sections.

Figure 5.1: Design of Ecode-I

### 5.1 Instruction Set

The functional classification and number of instructions in Ecode-I is shown in table 5.1 below.

| Instruction Category   | Number |

|------------------------|--------|

| Branch                 | 9      |

| Fixed Point Arithmetic | 12     |

| Logical                | 4      |

| Set Manipulation       | 2      |

| Shift                  | 2      |

| Short Arithmetic       | 120    |

| Short Logical          | 60     |

| Short Set Manipulation | 30     |

| Miscellaneous          | 14     |

| Total                  | 253    |

Table 5.1: Ecode-I Instructions by Category

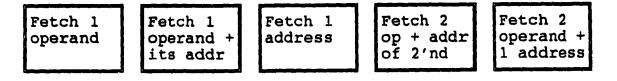

Each instruction consists of an opcode followed by one or more operands. The opcode and the first operand occupy a word of memory. Subsequent operands, if any, occupy additional words. The opcodes indicate the number of operands in the instruction, while the location of each operand is determined at run-time by the interpreter. The length of the instruction depends on the number of operands. The destination operand is always specified after the source operand as this allows fetching of the operands and execution of the operation to be performed in parallel with decoding of the destination address. For example, the

equation "A = B + C" is translated into the Ecode-I instruction "Add3, Operand B, Operand C, Operand A". During execution, operands B and C are fetched and the addition performed while the address of operand A is computed. Sample instructions are illustrated in table 5.2 and a complete list is given in Appendix III.

| Instruction     | # of Operands | . Comment                                                                                   |

|-----------------|---------------|---------------------------------------------------------------------------------------------|

| Branch Equal    | a<br>I        | Branch to specified address if the previous comparison was equal.                           |

| Shift Left      | ]<br>1        | Shifts operand<br>left the number of<br>oits specified by<br>the second operand             |

| Add2            | :             | Adds two operands<br>and stores the<br>result in the<br>second operand.                     |

| Subtract3       |               | Subtracts one operand from the other and stores the result in a third operand.              |

| Logical And3    | •             | Performs a logical AND of two operands and stores the result in a third operand.            |

| Set Difference2 |               | Performs a set subtraction on the two operands and stores the result in the second operand. |

Table 5.2: Sample Ecode-I Instructions

# 5.2 Optimizations

The following optimizations were implemented in the translator to improve the efficiency of Ecode-I:

- 1. A = 0 generates "Zero A"

- 2. A = A + A generates "Shift Left Arithmetic A"

- 3. A = A / 2 generates "Shift Right Arithmetic A"

- 4. A = -A generates "Negate A"

- 5. A = -B generates "Minus Assign A B"

- 6. A = B where both A and B are non-scalar, that is a table or an array, generates "Non-Scalar Assign A B " instead of a loop.

- 7. A = A + i where i is a literal integer between 0 and

15, generates "Short Add2i A"

The "Short" instruction was taken from N. Wirth's implementation of Lilith: A modula Machine [WIRT84], in which literal values between 1 and 15 in were embedded in the opcode itself, thereby shortening the instruction. For example A = A + 2 generates "Short Add22 A" where the value of the literal two is the four least significant bits of the eight bit opcode. There are 220 "Short" instructions in Ecode-I, used for arithmetic, logical and set manipulation instructions.

## 5.3 Memory Referencing

The operand specification is complicated by the SEL addressing and memory logic, and the SEL 32 bit word length. The SEL supports 64 bit doubleword, 32 bit word, 16 bit halfword, and 8 bit byte addressing according to the F and C bits (bits 30 and 31) in the address as shown in table 4.1 which is duplicated below:

| F bit (12)                      | C bits (30,31)                                           | Data type                                                                                                                            |

|---------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0 1 16<br>1 0 64<br>1 1 16<br>0 0 by<br>0 1 by<br>1 0 by | bit word bit half word. bits 015 bit doubleword bit half word.bits 1631 te 0. bits 07 te 1. bits 815 te 2. bits 1623 te 3. bits 2431 |

As indicated by the C bits above, the address of a 16 bit quantity is always one byte greater than the actual address. The SEL memory reference logic recognizes this convention and reads the appropriate halfword. The addresses generated by the storage allocation pass of the CE compiler are machine independent and do not compensate for this addressing scheme. In Ecode-I generation, all known halfword addresses are incremented by one byte, and the F bit forced to a one or zero depending on the size of the operand. If the address is unknown at Ecode-I generation time, then it will be generated at run time, in which case

the SEL memory reference logic automatically stores the adjusted value.

Memory reads on the SEL do not sign extend 16 bit half words or 8 bit byte operands, they are zero filled by the memory reference logic. In CE there are no 64 bit operands, 32 bit operands are always signed, 16 bit operands could be either signed or unsigned and 8 bit operands are always unsigned. The memory read returns 32 bit and 8 bit operands in the correct format from memory, with the most significant bits zero filled for 8 bit operands. The sign bit (bit 8) in Ecode-I is used to indicate whether 16 bit operands should be sign extended or not.

# 5.3 Operand Specification

Opcode - bits 0..7 Indicate the instruction opcode

S - bit 8 Sign extension bit

0 = sign extension required

1 = no sign extension required

RR - bits 9..10 Register number

00 - no register

01 - register 1

|         |            | 10 - register 2 11 - register 3            |

|---------|------------|--------------------------------------------|

| 1       | - bit 11   | Indirect bit                               |

|         |            | <pre>0 = non-indirect memory operand</pre> |

|         |            | 1 = indirect memory operand or             |

|         |            | operand not in memory                      |

| F       | - bit 12   | F bit in SEL addressing                    |

| N       | - bit 16   | Sign of register operands                  |

| Disp    | lacement - | Bits 1631 displacement in                  |

|         |            | address calculations or literal            |

|         |            | values                                     |

| Bits 13 | 31 -       | Absolute addressing                        |

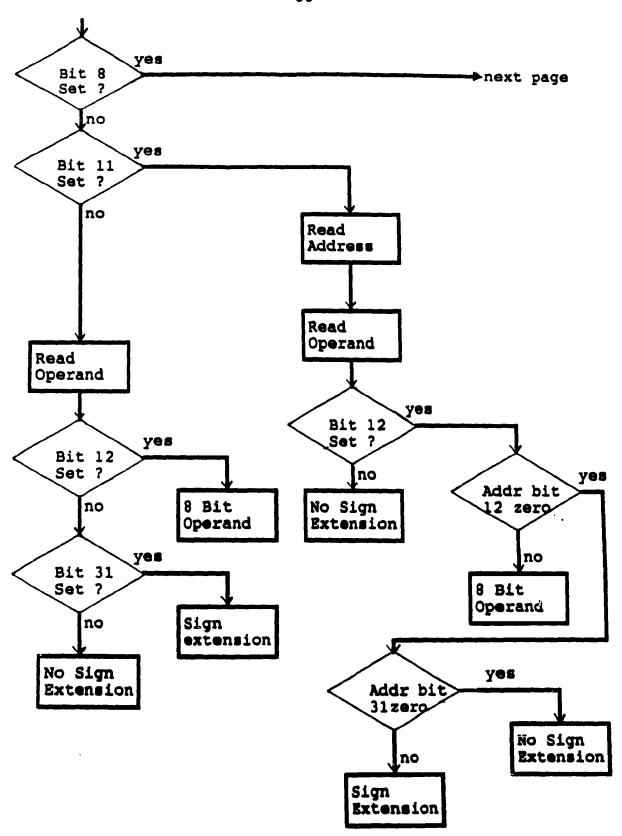

The location of an operand is determined at run-time as follows: Bits 8 and 11 specify the location and sign of the operand according to the following encoding:

| bit 8 | bit 11 |                                       |

|-------|--------|---------------------------------------|

| 0     | 0      | Operand is signed in memory and not   |

|       |        | indirectly addressed                  |

| 0     | 1      | Operand is in memory and indirectly   |

|       |        | addressed                             |

| 1     | 0      | Operand is unsigned and in memory and |

|       |        | not indirectly addressed              |

| 1     | 1      | Operand is an address in a register   |

|       |        | (signed or unsigned) or a literal     |

If the operand is in memory the address is obtained using bits 9 and 10 and bits 12 through 31. Bits 9 and 10 specify the base register and bits 13-31 specify a displacement to be added to the base in computing the address. A base register of zero indicates that bits 13-31 contain the absolute address of the operand. Bit 12 is the F bit as in the SEL machine instructions and is used to specify 32 bit word, 16 bit halfword or 8 bit byte operands.

If the operand is not in memory, that is both bits 8 and 11 are set, and bit 9 is not set then the operand is an address or a literal. If bit 10 is not set the operand is a literal and its value is in bits 16-31 with bit 16 being the sign bit. If bit 10 is set the operand is an address and is computed as above.

If bit 9 is set, the operand is in a register specified by bits 9 and 10 (register 2 or 3) and bit 16 indicates its sign. By default, all addresses stored in memory begin on a word boundary, and the F bit is therefore not necessary when specifying indirectly addressed operands. Instead, for indirectly addressed operands the F bit is used to indicate that sign extension is to be done according to the following convention: 1 = sign extension required, 0 = no sign extension required. The flowchart in figure 5.2 shows this decoding algorithm.

Figure 5.2: Operand Decode Algorithm (Page 1 of 2)

Figure 5.2: Operand Decode Algorithm (Page 2 of 2)

# 5.4 Design Considerations In Operand Specification

The format of Ecode-I was chosen to incorporate many of the features of the SEL microarchitecture and machine language. The following sections describe some of these features.

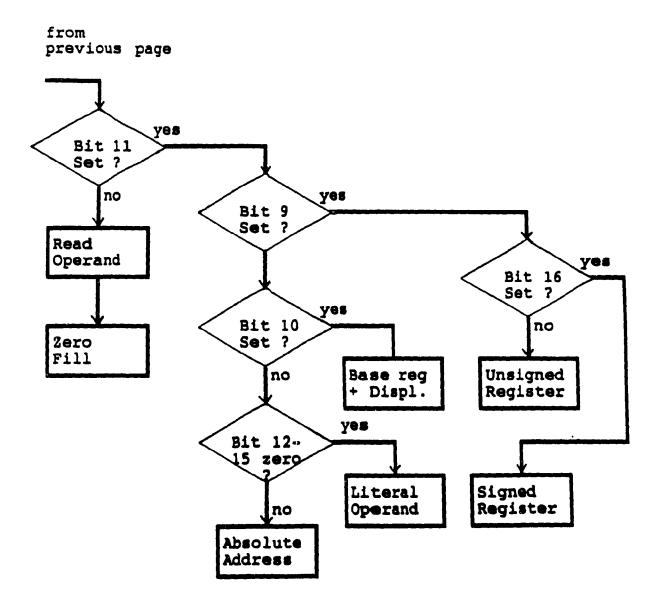

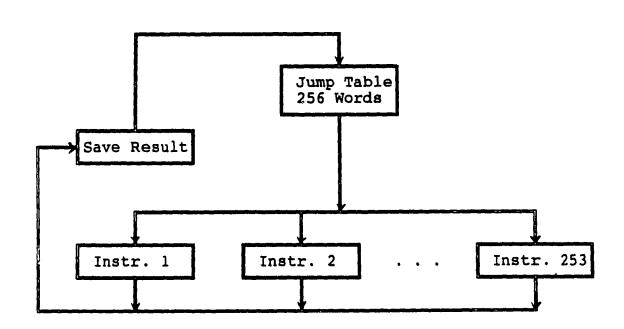

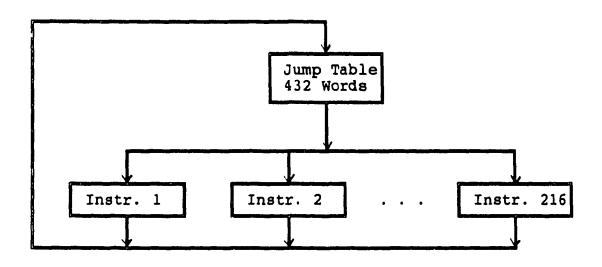

opcode - bits 0-7 - chosen for ease of decoding. The instruction can be stored into the T register and the T and S registers nibble shifted left together with the S acting as the most significant bits. The isolated opcode in the S register can be used as a jump table index.

sign extension bit - bit 8 - Chosen by default

Register operand or base register - bits 9 and 10.

These bits are used to represent the index register in the SEL machine language. The microinstruction repertoire contains instructions which reference these two bits as register numbers. For example microinstruction MARIX adds the value of the base register indicated in bits 9 and 10 and the displacement in bits 12-31 of the instruction register and places the result in the memory address register. R(x) is microinstruction a

referencing the contents of the register indicated in bits 9 and 10.

- Indirect bit bit 11. This bit is used to indicate that an operand is indirectly addressed in memory, and is also used as the indirect bit in the SEL machine language. Microinstruction INDIR directly tests this bit when an address is placed in the memory address register, which facilitates easy checking to determine if a second memory read is necessary.

- operands or the length (32, 16 or 8 bits) of non-indirect operands in memory. This is the addressing scheme is used in the SEL machine language and it takes advantage of the SEL memory reference logic which automatically reads the operands according to the value of this bit. Since this bit is not necessary when reading indirect operands, its use as a sign bit does not interfere with memory referencing.

- Bit 16 Indicates the sign of register operands.

Register operands are indicated in bits 9 and 10

with the rest of the instruction unused. Bit 16

was chosen as the sign bit because it is easily tested by microinstruction BMUX00.

Bits 16-31 - Used as a literal or displacement. This is

the same as in the SEL machine language. The

microinstructions ZE and SE zero fills or sign

extends this 16 bit field of the instruction to

be used in arithmetic operations or to be

stored.

Bits 12-31 - used as an absolute or relative address of an operand. This is the same convention as in the SEL machine language. The microinstruction MARIX loads these bits directly into the memory address register.

# 5.5 Sample Ecode-I Instructions

Below is the Ecode-I instruction generated for the instruction A = A + B, where B is a 16 bit signed integer on the run time stack and A is a 32 bit signed value in memory location at label U.

GEN 8/32,1/0,2/1,1/0,1/0,19/H(0) opcode,operand B

GEN 8/0,1/1,2/0,1/0,1/0,19/W(U) operand A

The representation of each field of this instruction is described below:

| GEN | 8/32,<br>Opcode<br>Add2<br>(32) | 1/0,<br>Sign bit<br>zero.<br>Sign ext.<br>required | 2/1,<br>Base Reg<br>R1      | 1/0,<br>Indirect<br>addr.<br>off | 1/0, 19/H<br>F bit Disp<br>zero zero<br>Oper. half<br>32/16 word<br>bits | ì. |

|-----|---------------------------------|----------------------------------------------------|-----------------------------|----------------------------------|--------------------------------------------------------------------------|----|

| GEN | 8/0,<br>Unused                  | 1/1,<br>Sign ext.<br>not req.                      | 2/0,<br>No base<br>register | 1/0,<br>Indirect<br>addr.<br>off | 1/0, 19/W<br>Oper Disp<br>32/16 word<br>bits addr                        | ì. |

The Ecode-I representation of the CE procedure "push" in the module "stack" described in chapter three, and derived from its intermediate form also described in chapter three, is given below. The Ecode-I representation of the entire module is given in Appendix III.

| Ecode-I | Instruction |  |

|---------|-------------|--|

|---------|-------------|--|

Comment

| PUSH | EQU | \$                             |                 |

|------|-----|--------------------------------|-----------------|

|      | GEN | 8/25,1/1,2/0,1/1,1/0,19/1011   | set line number |

|      | GEN | 8/81,1/0,2/0,1/0,1/0,19/H(U)   | top = top + 1   |

|      | GEN | 8/26,24/0                      | inc. line num   |

|      | GEN | 8/32,1/0,2/0,1/0,1/0,19/H(U)   | store top on    |

|      | GEN | 8'0,1/1,2/1,1/0,1/0,19/W(0)    | run time stack  |

|      | GEN | 8/23,1/1,2/1,1/0,1/0,19/W(0)   | shift top of    |

|      | GEN | 8/0,1/1,2/0,1/1,1/0,19/1       | stack left 1bit |

|      | GEN | 8/80,1/1,2/0,1/1,1/0,19/W(U)+4 | set address to  |

|      |     |                                |                 |

| GEN | 8/0,1/1,2/1,1/0,1/0,19/W(0)   | table + top*2 |

|-----|-------------------------------|---------------|

| GEN | 8/32,1/0,2/1,1/0,1/0,19/W(-8) | table(top)=I  |

| GEN | 8/0,1/1,2/1,1/1,1/0,19/W(0)   |               |

| GEN | 8/29,1/0,2/0,1/0,1/0,19/W(0)  | return        |

# 5.6 Comparison Of SEL Machine Language And Ecode-I

Table 5.3 compares the features of the SEL machine language with Ecode-I. The major difference between the SEL machine language and Ecode-I is that the SEL opcode specifies the location and size of both operands, whereas Ecode-I opcode specifies neither.

| Item                               | SEL                                                                  | Ecode-I                                                                                    |

|------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Number of instructions             | 189                                                                  | <b>253</b>                                                                                 |

| Opcode information                 | Opcodes specify operation, size, and location of operands.           | Opcodes specify operation but not size and location of operands.                           |

| Instruction format                 | Opcode followed by operands. One operand is generally in a register. | Opcode followed by operands. Dest . operand specified last. Operand locat- ion unspecified |

| Number of operands per instruction | Zero, one or two.                                                    | Zero, one, two or three.                                                                   |

| Length of instruction              | 1/2 - 1 word                                                         | 1 - 3 words                                                                                |

| Instruction decode        |                          |                           |

|---------------------------|--------------------------|---------------------------|

| Opcode<br>Source register | bits 0 - 5<br>bits 6 - 8 | bits 0 - 7<br>bits 9 - 10 |

| Index register            |                          | bits 9 - 10               |

|                           | bits 9 - 10              | bits 9 - 10               |

|                           | bit 11                   | bit 11                    |

| addressing                | bit 12                   | bit 12                    |

| C bit memory addressing   | bits 30 - 31             | bits 30 - 31              |

| Sign extension bit        | not required             | bit 8, or bit<br>16       |

Table 5.3: Comparison of SEL Machine Language and Ecode-I

### 5.7 CE Intermediate Code And Ecode-I

Ecode-I is derived from the CE intermediate code described in chapter 3. Each operation token in the intermediate code is mapped to an Ecode-I instruction. Additional Ecode-I instructions may be generated to calculate operand address based on the information in the datadescriptor tokens. For example, the intermediate code of the CE statement "I = table(top) in the procedure "push." includes datadescriptors for table, I and subscript top. This generates three Ecode-I instructions to calculate the address of table(top) and one to perform the assignment. The translation of the intermediate code of procedure "push" to Ecode-I is shown below.

# Intermediate Representation Ecode-I Instruction

| aRoutineIndex 0  |     |     |   |   |    |    |    |    |               |

|------------------|-----|-----|---|---|----|----|----|----|---------------|

| aldentText 4 pus | h   |     |   |   |    |    |    |    |               |

| aNewline 9       |     |     |   |   |    |    |    | 1. | newline 9     |

| aBegin           |     |     |   |   |    |    |    |    |               |

| aNewline 10      |     |     |   |   |    |    |    | 2. | Incr line num |

| aDataDescriptor  | 162 | 1   | 0 | 0 | 2  | 0  | 0  | 3. | Short add21:  |

| aAssign          |     |     |   |   |    |    |    |    | top           |

| aDataDescriptor  | 162 | 1   | 0 | 0 | 2  | 0  | 0  |    |               |

| aDataDescriptor  | 1   | 127 | 1 | 0 | 1  | 0  | 1  |    |               |

| aAdd             |     |     |   |   |    |    |    |    |               |

| aEndExpression   |     |     |   |   |    |    |    |    |               |