Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file - Votre référence

Our file Notre référence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

Canadä

# AC/DC POWER CONVERSION SCHEMES WITH UNITY POWER FACTOR AND MINIMUM HARMONIC DISTORTION

Navid Reza Zargari

A Thesis

in

The Department of Electrical & Computer Engineering

Presented in Partial Fulfilment of the Requirements

for the Degree of Doctor of Philosophy at

Concordia University

Montréal, Québec, Canada

March 1995

O Navid Reza Zargari, 1995

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your Ne. Votre rétérence

Our hie Notre référence

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS.

L'AUTEUR A ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION.

L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

ISBN 0-612-01278-6

#### **ABSTRACT**

# AC/DC POWER CONVERSION SCHEMES WITH UNITY POWER FACTOR AND MINIMUM HARMONIC DISTORTION

Navid R. Zargari, Ph.D.

Concordia University, 1995.

In most line-interfaced power converter applications the ac mains voltage is first rectified into a dc voltage or current, which is subsequently converted into voltages and currents of appropriate amplitude, frequency and shape to meet the load requirements. The front-end rectifier must satisfy three main requirements: (a) Minimum harmonic injection into the ac mains should comply with limits imposed by recommended standards such as IEEE-519, IEC-555. (b) High input power factor to reduce the reactive power requirements. (c) High efficiency and reliability and low cost to ensure competitiveness on the market. The challenge is therefore to provide a conversion scheme which delivers high quality output waveforms without distorting the ac mains and without drawing any reactive power. Successful application of PWM techniques to forced commutated converters has prompted recent investigation in finding more suitable topologies for ac to dc conversion. Two structures have evolved based on the characteristics of the dc link: the current source topology and the voltage source topology. This thesis investigates these two topologies and proposes a number of control schemes to achieve unity displacement factor operation and fast response. For the current source topology two control methods, a closed loop and a feed-forward scheme, are proposed. The feed-forward scheme is based on phase shifting the gating patterns of individual switches to compensate the effect of the input filter and load operating point. Furthermore, the feedforward scheme is combined with a control strategy to eliminate the need for damping resistors. For the voltage source topology, a simple control strategy is proposed to obtain a near unity power factor input stage for voltage source inverter based ac drive applications. Also, performance of current controlled voltage source type rectifiers in rotating and stationary frames is investigated.

Small signal models are developed for both topologies and different transfer functions are derived for each structure. The theoretical considerations are verified by simulation and by experiments on laboratory prototypes.

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere gratitude to my supervisor, Dr. Geza Joos for his valuable guidance and encouragement throughout the course of this study.

Special appreciation goes to late Dr. P.D. Ziogas with whom this work was initiated, for his useful advice and discussions.

Thanks are extended to my many friends in the Power Electronics L.'s, who made the period of this study more pleasant and fruitful. Special thanks to Mr. José Espinoza for many helpful discussions we shared.

Financial support from Natural Science and Engineering Research Council of Canada (NSERC) and Québec Ministry of Education (FCAR) are gratefully acknowledged.

To my parents

# **Table Of Contents**

# CHAPTER 1

|     | Introduction                                                  |    |

|-----|---------------------------------------------------------------|----|

|     | 1.1 AC/DC Conversion                                          | 1  |

|     | 1.2 Front-End Rectifier Topologies                            | 5  |

|     | 1.2.1 Diode Bridge Rectifier                                  | 5  |

|     | 1.2.2 Phase Controlled Rectifier                              | 6  |

|     | 1.2.3 PWM Front-End Rectifiers                                | 7  |

|     | 1.2.3.1 Current Source Topology (PWM Buck Rectifier)          | 8  |

|     | 1.2.3.2 Voltage Source Topology (Synchronous Rectifier) l     | 12 |

|     | 1.3 Scope and Contributions of the Thesis                     | 15 |

|     | 1.4 Thesis Outline                                            | 17 |

|     |                                                               |    |

| CHA | PTER 2                                                        |    |

|     | Performance Comparison of PWM Buck and Synchronous Rectifiers |    |

|     | 2.1 Introduction                                              | 20 |

|     | 2.2 Principles of Operation                                   | 20 |

|     | 2.2.1 Current Source Topology                                 | 20 |

|     | 2.2.2 Voltage Source Topology                                 | 28 |

|     | 2.3 Comparison of the Two Topologies                          | 33 |

|       | 2.3.1 Switch and Converter KVA Ratings                   |   |

|-------|----------------------------------------------------------|---|

|       | 2.3.2 Operating Regions                                  |   |

|       | 2.3.3. Filtering Requirements                            |   |

|       | 2.3.4 Power Factor Considerations                        |   |

|       | 2.3.5 Operation with Unbalanced AC Inputs                |   |

|       | 2.3.6. Control Aspects                                   |   |

| 2     | .4 Summary of Operating Characteristics                  |   |

| 2     | 2.5 Conclusions                                          |   |

|       |                                                          |   |

| СНАРТ | ER 3                                                     |   |

| ]     | input Filter Design for PWM Current-Source Rectifiers    |   |

| :     | 3.1 Introduction                                         |   |

| :     | 3.2 Description of the Filter Characteristics            |   |

| :     | 3.3 Proposed Design Procedure 45                         |   |

| ,     | 3.4 Practical Considerations                             | , |

|       | 3.4.1 Input Power Factor                                 | i |

|       | 3.4.2 KVA Ratings                                        | ) |

|       | 3.4.3 Damping                                            | ļ |

|       | 3.4.4. Parameter Variation 50                            | j |

|       | 3.4.5. Effect of the Filter on the Rectifier Performance | 3 |

|       | 3.5 Design Example                                       | 3 |

|       | 3.6 Results                                              | ļ |

| 3.7 Conclusions                                                              |

|------------------------------------------------------------------------------|

| CHAPTER 4                                                                    |

| Current-Source PWM Rectifier with Feed-Forward Compensation                  |

| 4.1 Introduction                                                             |

| 4.2 Description of the Proposed Compensation Scheme                          |

| 4.3 On-Line Pattern Generator                                                |

| 4.4 Design of the Regulator                                                  |

| 4.5 Limitations of Displacement Compensation                                 |

| 4.5.1 Limitations Based on Filter Components                                 |

| 4.5.2 Effect of Parameter Variation                                          |

| 4.6 Results                                                                  |

| 4.6.1 Steady State and Transient Response                                    |

| 4.6.2 Experimental results                                                   |

| 4.7 Conclusions                                                              |

| CHAPTER 5                                                                    |

| An On-Line Operated Unity Power Factor PWM Rectifier without Passive Damping |

| Requirements                                                                 |

| 5.1 Introduction                                                             |

| 5.2 Description of the Proposed Rectifier                                    |

| 5.2.1 Pattern Generation Scheme 84                                           |

| 5.2.2 Phase-Shifting Circuitry                                       |  |  |  |

|----------------------------------------------------------------------|--|--|--|

| 5.3 Filtering Requirements of Modulating Signals                     |  |  |  |

| 5.4 Design Guidelines 90                                             |  |  |  |

| 5.5 Operating Characteristics                                        |  |  |  |

| 5.5.1 Simulation Result                                              |  |  |  |

| 5.5.1.1 Start Up and Steady State 92                                 |  |  |  |

| 5.5.1.2 DC Transients                                                |  |  |  |

| 5.5.1.3 Effect of Line Transients                                    |  |  |  |

| 5.5.1.4 Regeneration                                                 |  |  |  |

| 5.5.1.5 Operation with Unbalanced Input Voltages 93                  |  |  |  |

| 5.5.1.6 Non-Regenerative Applications                                |  |  |  |

| 5.5.2 Experimental results                                           |  |  |  |

| 5.6 Conclusions                                                      |  |  |  |

|                                                                      |  |  |  |

| CHAPTER 6                                                            |  |  |  |

| A Current-Controlled Current-Source Unity Power Factor PWM Rectifier |  |  |  |

| 6.1 Introduction                                                     |  |  |  |

| 6.2 Proposed Control Scheme                                          |  |  |  |

| 6.2.1 Current Control Loop                                           |  |  |  |

| 6.2.2 DC Voltage/Current Regulation Loop                             |  |  |  |

| 6.2.3 On-Line PWM Pattern Generator 104                              |  |  |  |

| 6.3 Analysis and Design Guidelines                                   |  |  |  |

| 6.3.1 Power Circuit Design                                                                                                                                                                                                                                                                                                             | 5                                      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| 6.3.2 Control Circuit Design                                                                                                                                                                                                                                                                                                           | 15                                     |  |  |  |

| 6.3.2.1 Linear Controllers                                                                                                                                                                                                                                                                                                             | )5                                     |  |  |  |

| 6.3.2.2 Neural Network Controller                                                                                                                                                                                                                                                                                                      | 0                                      |  |  |  |

| 6.4 Results                                                                                                                                                                                                                                                                                                                            | 5                                      |  |  |  |

| 6.4.1 Simulation Result                                                                                                                                                                                                                                                                                                                | 5                                      |  |  |  |

| 6.4.2 Experimental results                                                                                                                                                                                                                                                                                                             | 16                                     |  |  |  |

| 6.5 Conclusions 11                                                                                                                                                                                                                                                                                                                     | 16                                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                        |                                        |  |  |  |

| CHAPTER 7                                                                                                                                                                                                                                                                                                                              |                                        |  |  |  |

| A Near Unity Power Factor Input Stage with Minimum Control Requirements For AC                                                                                                                                                                                                                                                         |                                        |  |  |  |

| A Near Unity Power Factor Input Stage with Minimum Control Requirements For A                                                                                                                                                                                                                                                          | ·C                                     |  |  |  |

| A Near Unity Power Factor Input Stage with Minimum Control Requirements For A<br>Drive Applications                                                                                                                                                                                                                                    | ·C                                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                        |                                        |  |  |  |

| Drive Applications                                                                                                                                                                                                                                                                                                                     | 20                                     |  |  |  |

| Drive Applications 7.1 Introduction                                                                                                                                                                                                                                                                                                    | 20<br>22                               |  |  |  |

| 7.1 Introduction       12         7.2 Description of the Proposed AC Drive System       12                                                                                                                                                                                                                                             | 20<br>22<br>22                         |  |  |  |

| 7.1 Introduction         12           7.2 Description of the Proposed AC Drive System         13           7.2.1 Load Inverter         15                                                                                                                                                                                              | 20<br>22<br>22<br>25                   |  |  |  |

| Drive Applications       12         7.1 Introduction       12         7.2 Description of the Proposed AC Drive System       12         7.2.1 Load Inverter       13         7.2.2 Synchronous Rectifier       15                                                                                                                       | 20<br>22<br>22<br>25<br>29             |  |  |  |

| 7.1 Introduction       12         7.2 Description of the Proposed AC Drive System       15         7.2.1 Load Inverter       15         7.2.2 Synchronous Rectifier       16         7.2.3 PWM Pattern Generator       1                                                                                                               | 20<br>22<br>22<br>25<br>29             |  |  |  |

| 7.1 Introduction       12         7.2 Description of the Proposed AC Drive System       12         7.2.1 Load Inverter       13         7.2.2 Synchronous Rectifier       15         7.2.3 PWM Pattern Generator       1         7.2.4 Design of the DC Bus Capacitor       1                                                          | 20<br>22<br>22<br>25<br>29<br>30       |  |  |  |

| 7.1 Introduction       12         7.2 Description of the Proposed AC Drive System       13         7.2.1 Load Inverter       15         7.2.2 Synchronous Rectifier       16         7.2.3 PWM Pattern Generator       1         7.2.4 Design of the DC Bus Capacitor       1         7.3 Design Example, Results and Comments       1 | 20<br>22<br>22<br>25<br>29<br>30<br>31 |  |  |  |

| 7.3.4 Operation with Unbalanced Input Voltages                                   | ۷  |

|----------------------------------------------------------------------------------|----|

| 7.4 Experimental Results                                                         | 2  |

| 7.5 Conclusions                                                                  | 3  |

|                                                                                  |    |

| CHAPTER 8                                                                        |    |

| Performance Investigation of a Current-Controlled Voltage-Regulated PWM Rectifie | :r |

| n Rotating and Stationary Frames                                                 |    |

| 8.1 Introduction                                                                 | 8  |

| 8.2 Principles of Operation                                                      | 18 |

| 8.2.1 Instantaneous Current Controller and Pattern Generator 13                  | 38 |

| 8.2.2 Stationary (abc) Frame Controller                                          | 39 |

| 8.2.3 Rotating (dqo) Frame Controller                                            | 40 |

| 8.2.4 Comparison of Current Controllers                                          | 41 |

| 8.3 Control System Design                                                        | 43 |

| 8.3.1 Design of Instantaneous Current Controller                                 | 43 |

| 8.3.2 Design of the Stationary Frame Controller                                  | 45 |

| 8.3.3 Design of the Rotating Frame Controller                                    | 46 |

| 8.3.4 Design of Voltage Loop                                                     | 47 |

| 8.4 Results                                                                      | 48 |

| 8.4.1 Steady State                                                               | 48 |

| 8.4.2 DC Transients                                                              | 49 |

| 9.5 Conclusions                                                                  | 50 |

# CHAPTER 9

| SUMMARY AND CONCLUSIONS                                                         |

|---------------------------------------------------------------------------------|

| 9.1 Summary                                                                     |

| 9.2 Conclusions                                                                 |

| 9.3 Suggestion for Future Work                                                  |

| REFERENCES 157                                                                  |

| <b>APPENDIX A</b>                                                               |

| A.1 Introduction                                                                |

| A.2 General Method for Obtaining Small Signal Models of Converter Systems . 166 |

| A.3 Small Signal Model of Synchronous Rectifier                                 |

| A.3.1 Desired Transfer Functions                                                |

| A.4 Small Signal Model of PWM Buck Rectifier                                    |

| A.4.1 Desired Transfer Functions                                                |

| <b>APPENDIX B</b>                                                               |

| B.1 Experimental Set-Up for Testing a Non-Regenerative Current Source Rectifier |

| 179                                                                             |

#### List of Figures

#### CHAPTER 1.

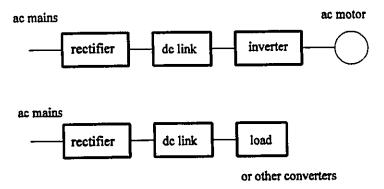

- Fig. 1.1 Typical connection of static converters to ac mains.

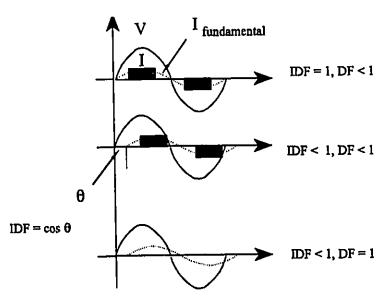

- Fig. 1.2 Representation of Input Displacement Factor, IDF and Distortion Factor, DF.

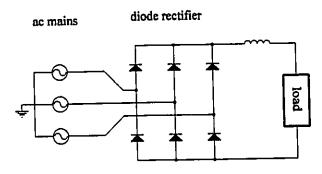

- Fig. 1.3 Three-phase diode bridge rectifier.

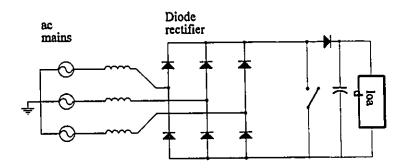

- Fig. 1.4 Diode rectifier with input current waveshaping.

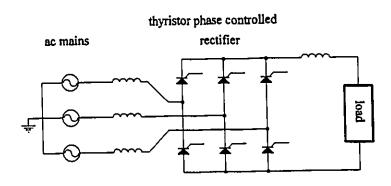

- Fig. 1.5 Line-commutated phase-controlled rectifier.

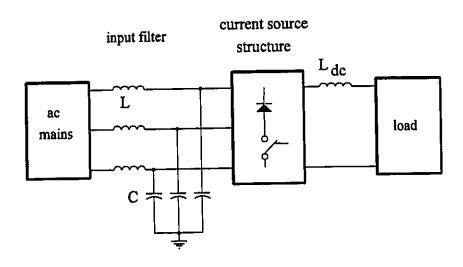

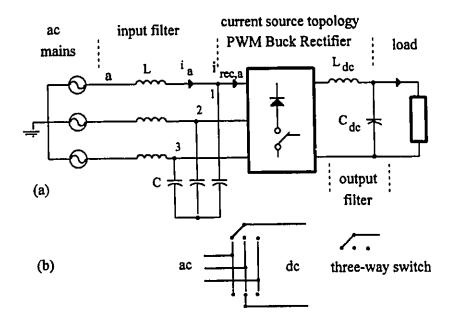

- Fig. 1.6 Current-source topology, PWM Buck rectifier.

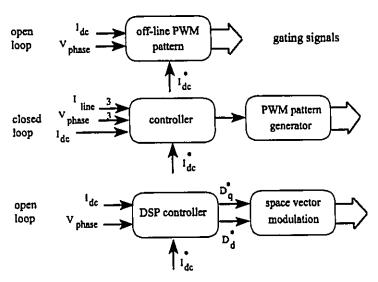

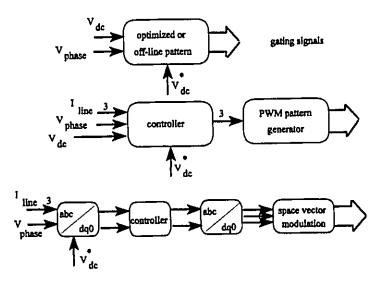

- Fig. 1.7 Control schemes for current source PWM rectifier.

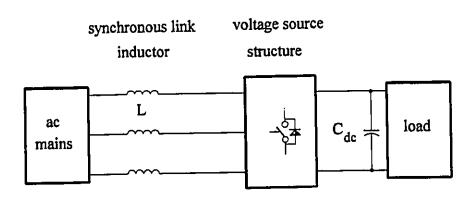

- Fig. 1.8 Voltage-source topology, Synchronous Rectifier.

- Fig. 1.9 Control schemes for Synchronous Rectifier.

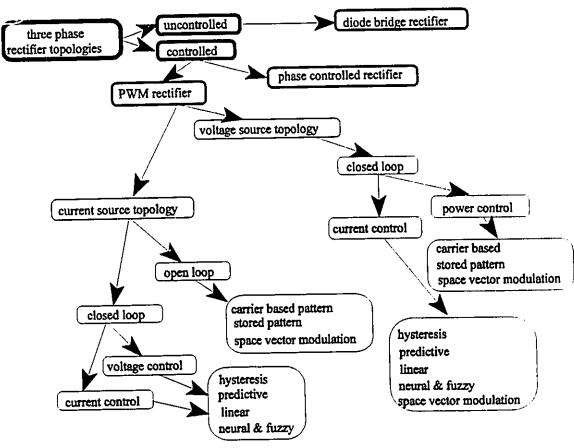

- Fig. 1.10 Existing rectifier topologies.

#### CHAPTER 2.

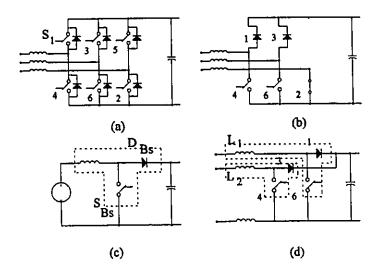

- Fig. 2.1 (a) Current-source topology, PWM rectifier, (b) representation by two "three-way" switches.

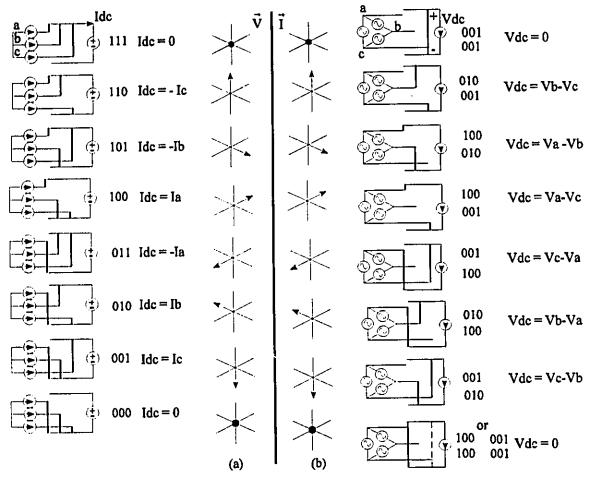

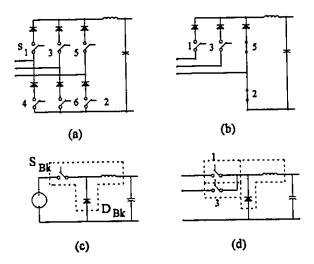

- Fig. 2.2 Possible switch combinations, (a) voltage source topology, (b) current source topology.

- Fig. 2.3 (a) Current source topology, (b) arbitrary state of switches, (c) dc/dc Buck converter, (d) the same switch state as in (b).

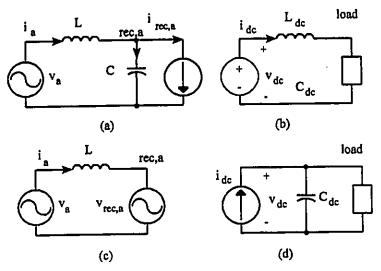

- Fig. 2.4 Current source topology, (a) input (b) output equivalent circuit. Voltage source topology, (c) input, (d) output equivalent circuit.

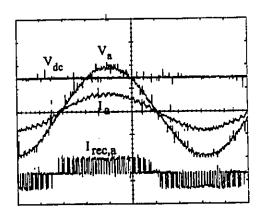

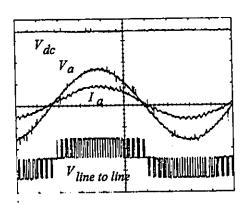

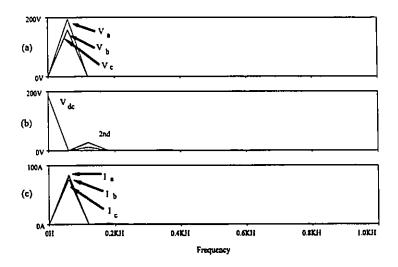

- Fig. 2.5 Experimental results, PWM Buck Rectifier.

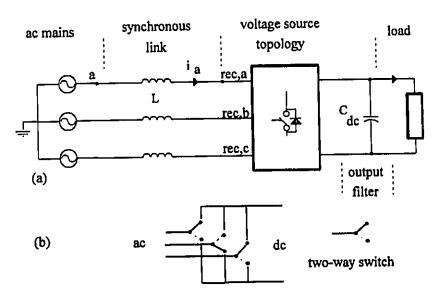

- Fig. 2.6 (a) Voltage-source topology, Synchronous Rectifier, (b) representation by three "two-way" switches.

- Fig. 2.7 (a) Synchronous Rectifier, (b) arbitrary state of switches, (c) dc/dc Boost converter, (d) the same switch state as in (b).

- Fig. 2.8 Experimental results, Synchronous Rectifier.

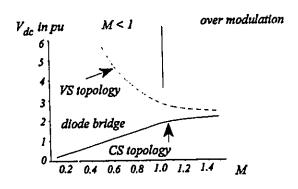

- Fig. 2.9 Operating regions.

- Fig. 2.10 Regions of possible unity power factor operation.

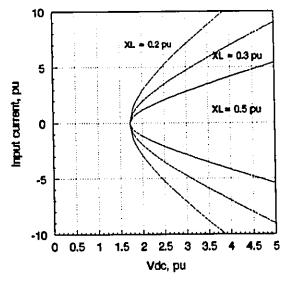

- Fig. 2.11 Input/output characteristics of current source topology without the input filter. (a)

Output dc current, (b) output dc voltage, (c) input line current and phase voltage.

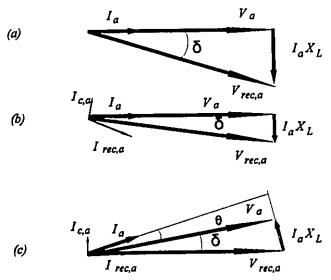

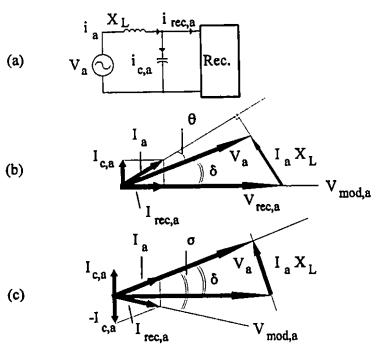

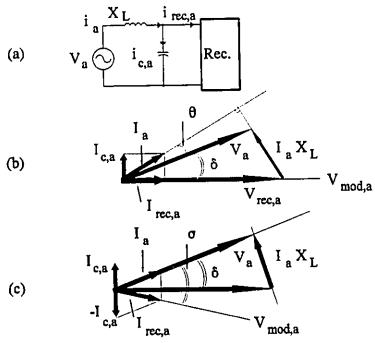

- Fig. 2.12 Phasor diagrams. (a) Voltage source topology with unity PF, (b) current source topology with unity PF, (c) current source topology, pattern in phase with rectifier input voltage.

#### CHAPTER 3.

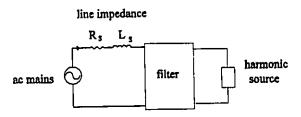

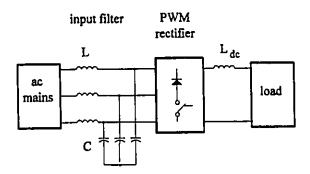

- Fig. 3.1 Typical filter connection.

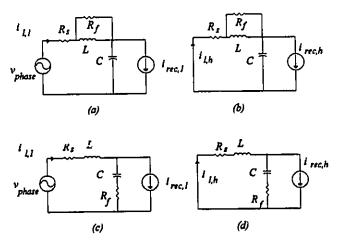

- Fig. 3.2 Single line diagrams for fundamental and harmonic frequencies. (a,b) Filter type B, (c,d) filter type A.

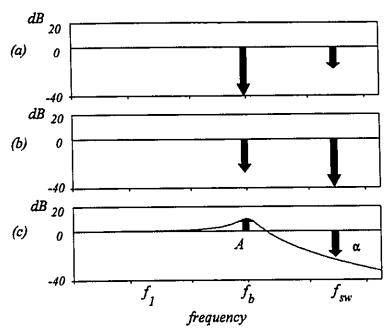

- Fig. 3.3 Frequency spectrum of the harmonic current source, (b) desired frequency spectrum of the line current, (c) characteristics of the input filter (A and  $\alpha$  are in dB).

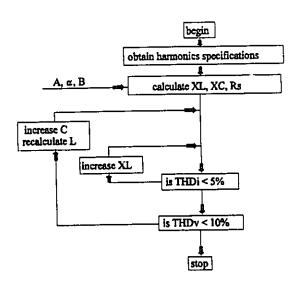

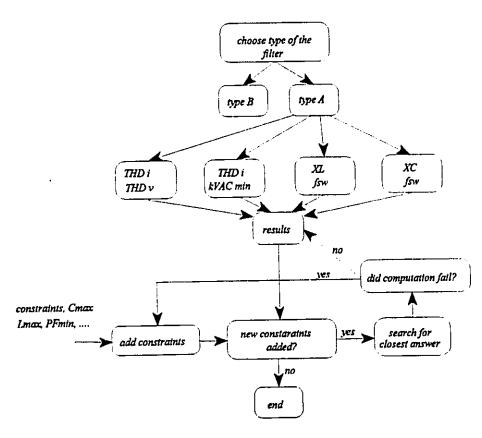

- Fig. 3.4 Flow chart of the filter design procedure.

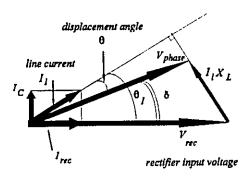

- Fig. 3.5 Phasor diagram of PWM Buck Rectifier, pattern is synchronized with the capacitor voltage.

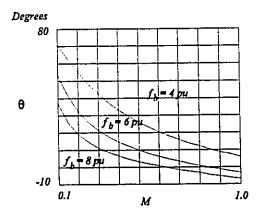

- Fig. 3.6 Displacement angle as a function of modulation index M,  $(X_L = 0.2 \text{ pu}, f_{sw} = 27 \text{ pu})$ .

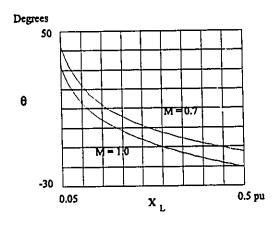

- Fig. 3.7 Displacement angle as a function of filter inductance  $X_L$ ,  $(f_b = 5.4 \text{ pu})$ .

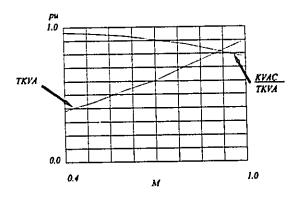

- Fig. 3.8 TKVA as a function of modulation index M.

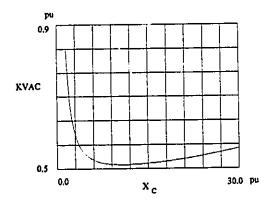

- Fig. 3.9 Capacitive kVA as a function of capacitor impedance  $X_{C}$ .

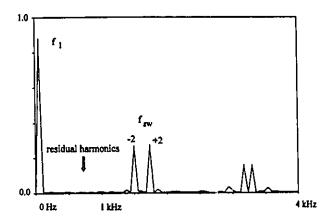

- Fig. 3.10 Harmonic spectrum of SPWM switching pattern ( $M=1, f_{sw}=27$  pu).

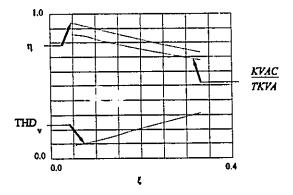

- Fig. 3.11 Effect of damping on the circuit specifications,  $\eta$  = efficiency,  $\xi$  = damping factor.

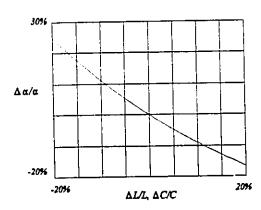

- Fig. 3.12 Effect of parameter variation on the attenuation factor,  $(\alpha)$ .

- Fig. 3.13 Flow chart of the filter design procedure.

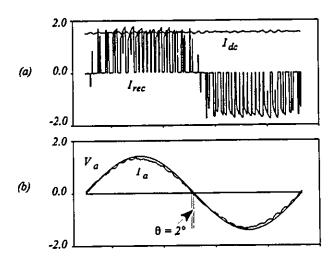

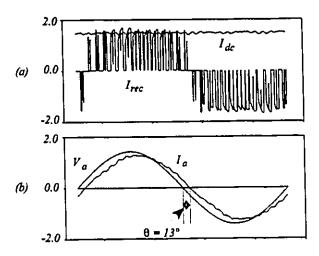

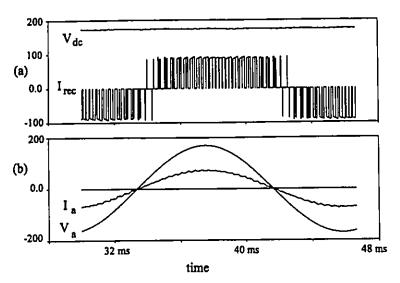

- Fig. 3.14 Simulation results of design A, (a) input rectifier current  $I_{rec}$ , output dc current  $I_{dc}$ . (b) phase a voltage and current waveforms,  $V_a$ ,  $I_a$  (in pu).

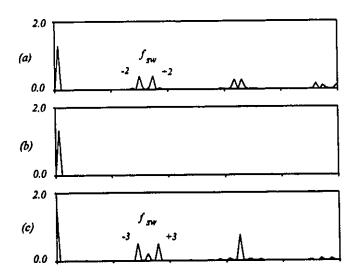

- Fig. 3.15 Frequency spectra of input/output waveforms, (a) rectifier input current, (b) input line current, (c) output dc voltage.

- Fig. 3.16 Simulation results of design B, (a) input rectifier current  $I_{rec}$ , output dc current  $I_{dc}$ . (b) phase a voltage and current waveforms,  $V_a$ ,  $I_a$  (in pu).

#### CHAPTER 4.

- Fig. 4.1 Three-phase current source PWM rectifier.

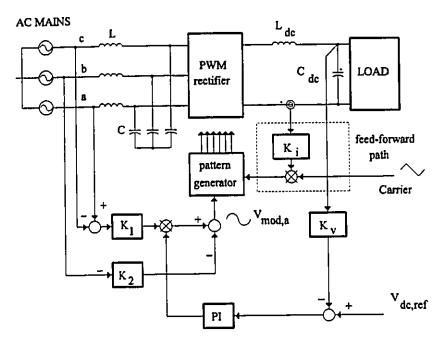

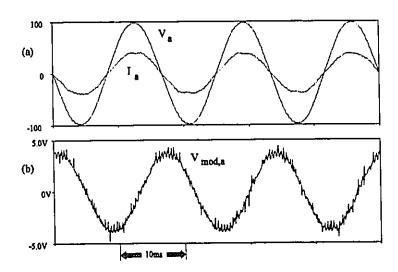

- Fig. 4.2 The proposed input displacement compensation scheme.  $V_{mod,a}$  denotes the modulating signal for phase a.

- Fig. 4.3 (a) Single line diagram, (b) non-unity displacement factor operation (leading power factor), (c) unity displacement factor operation ( $\theta = 0$ ).

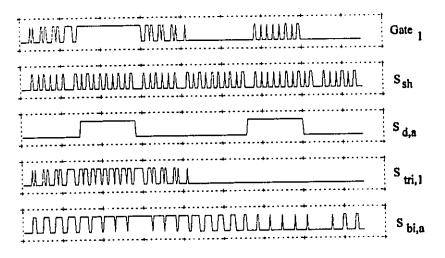

- Fig. 4.4 Waveforms of the on-line pattern generator.

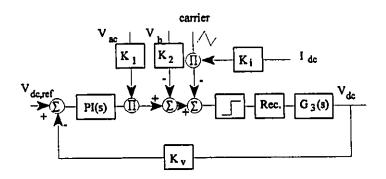

- Fig. 4.5 Block diagram of the control circuit.

- Fig. 4.6 Simplified block diagrams, (a) modulation index control, (b) modulation index and

phase shift control.

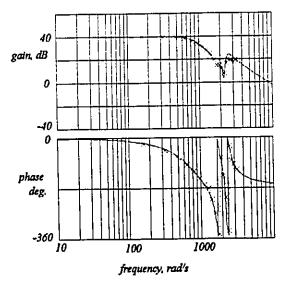

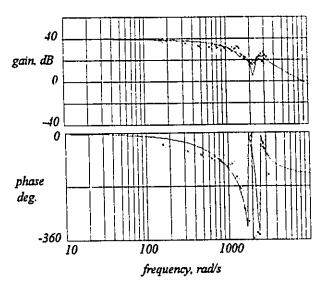

- Fig. 4.7 Closed loop frequency response of the overall system, modulation index control, time domain simulation results are included.

- Fig. 4.8 Closed loop frequency response of the overall system, modulation index and phase shift control, time domain simulation results are included.

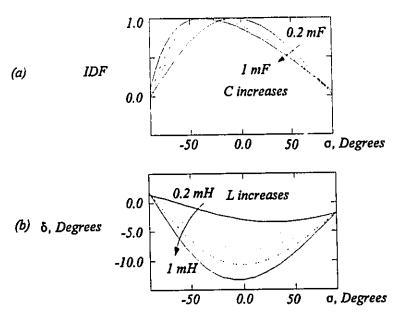

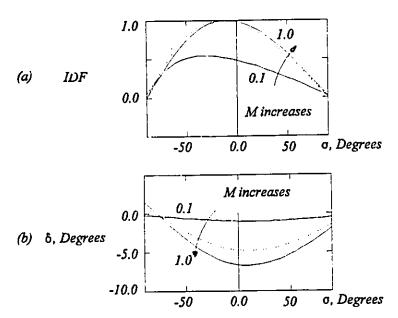

- Fig. 4.9 Effect of pattern phase shifting, (a) on the displacement angle, (b) on the power angle, (M as parameter).

- Fig. 4.10 Effect of pattern phase shifting, (a) on the displacement angle, (C as parameter), (b) on the power angle, (L as parameter), (M = 1).

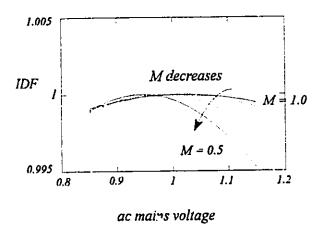

- Fig. 4.11 Effect of input voltage variation on IDF.

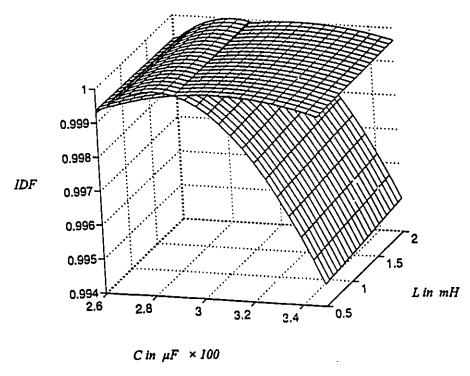

- Fig. 4.12 Effect of parameter (L&C) variation on IDF.

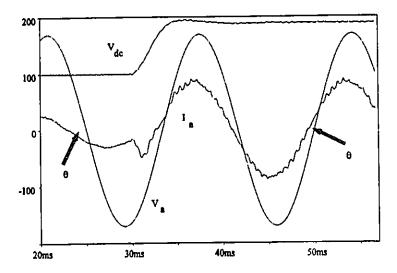

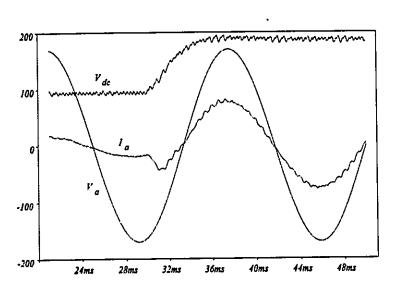

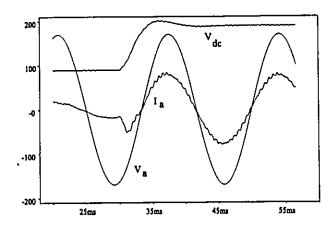

- Fig. 4.13 PWM rectifier without displacement compensation. Output dc voltage  $V_{dc}$ , input line current  $I_a$ , input phase voltage  $V_a$ .

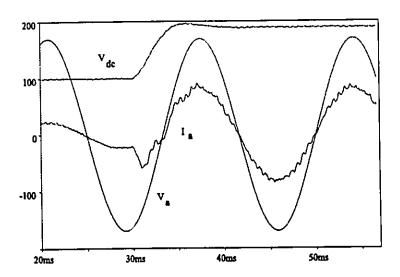

- Fig. 4.14 PWM rectifier with displacement compensation. Output dc voltage  $V_{dc}$ , input line current  $I_a$ , input phase voltage  $V_a$ .

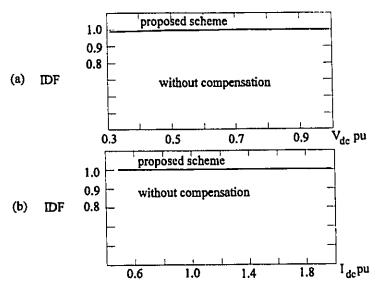

- Fig. 4.15 IDF with and without compensation, (a) output voltage variation, (b) output load variation,  $V_{dc} = 190 \text{ V}$ .

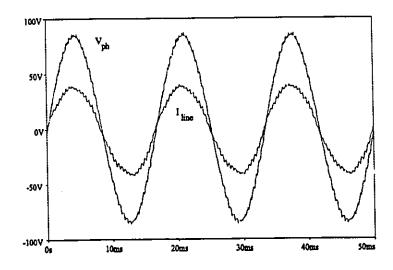

- Fig. 4.16 Experimental results, steady state input voltage and line current (×5).

- Fig. 4.17 Transient response. Input phase voltage and line current.

#### CHAPTER 5.

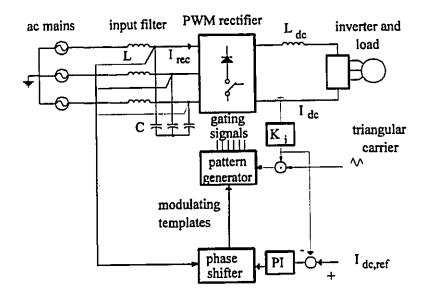

- Fig. 5.1 The proposed PWM rectifier circuit.

- Fig. 5.2 (a) Single line diagram, (b) non-unity displacement factor operation (leading power

- factor), (c) unity displacement factor operation ( $\theta = 0$ ).

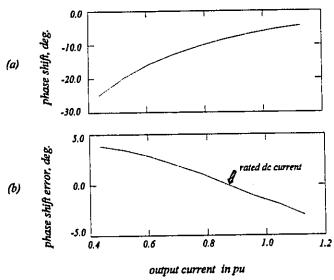

- Fig. 5.3 (a) Generated phase shift, (b) phase shift error with the approximation used.

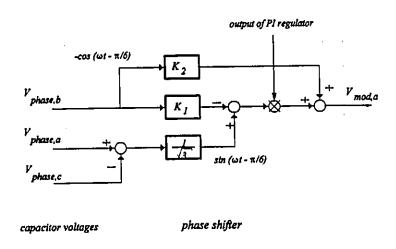

- Fig. 5.4 Generation of phase a modulating signal.

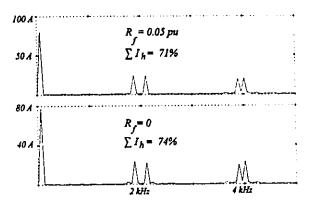

- Fig. 5.5 Frequency spectrum of rectifier input current, (a) conventional scheme, (b) proposed scheme.

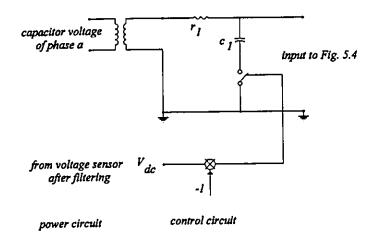

- Fig. 5.6 Filtering of modulating signal of phase a.

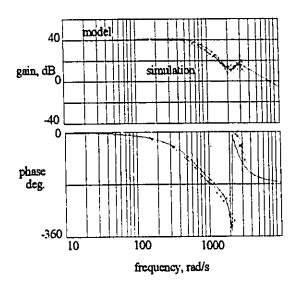

- Fig. 5.7 Closed loop frequency response of the overall system, modulation index control, time domain simulation results are included.

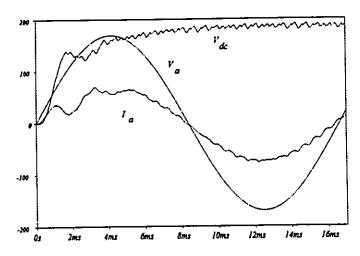

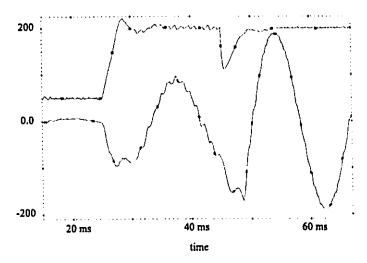

- Fig. 5.8 Start up, proposed scheme with IDF compensation, output dc voltage  $V_{dc}$ , line current  $I_a$ , phase voltage  $V_a$ .

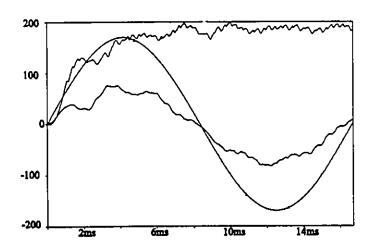

- Fig. 5.9 Start up, conventional scheme with IDF compensation,

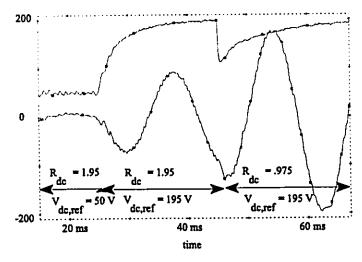

- Fig. 5.10 DC transients, output dc voltage and input line current and voltage are shown.

- Fig. 5.11 Typical connection of rectifier and other loads to ac bus.

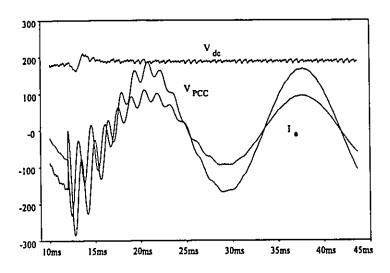

- Fig. 5.12 Line transients. DC voltage  $V_{dc}$ , voltage at PCC  $V_{PCC}$  and line current  $I_a$ .

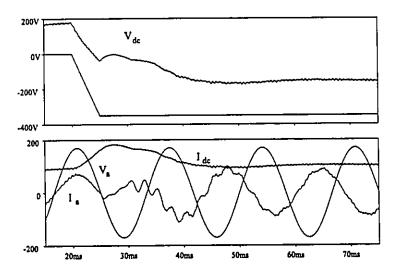

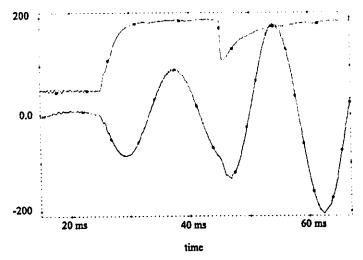

- Fig. 5.13 Regeneration, (a) output dc voltage  $V_{dc}$ , (b) output dc current  $I_{dc}$ , input line current  $I_a$  and voltage  $V_a$ .

- Fig. 5.14 Proposed scheme, (a) unbalanced input voltages, (b) output dc voltage before and after filtering, (c) line currents.

- Fig. 5.15 Balanced pattern, (a) unbalanced input voltages, (b) output dc voltage before and after filtering, (c) line currents.

- Fig. 5.16 Transient response for non-regenerative applications, output dc voltage,  $V_{dc}$ , input line current  $I_a$ , and input ac voltage  $V_a$ .

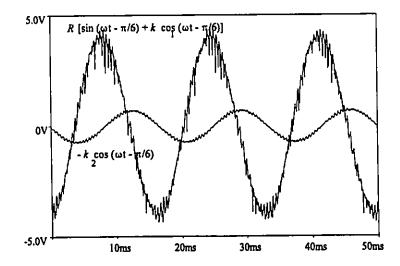

- Fig. 5.17 Experimental results, components of the modulating signal.

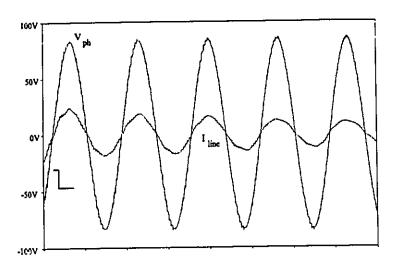

- Fig. 5.18 Experimental results, steady state waveforms  $(I_a \times 5)$ .

- Fig. 5.19 Experimental results for non-regenerative applications, (a) input line current and phase voltage, (b) modulating signal of phase a.

#### CHAPTER 6.

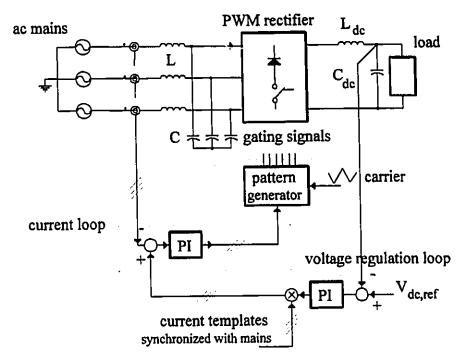

- Fig. 6.1 Proposed current controlled PWM rectifier.

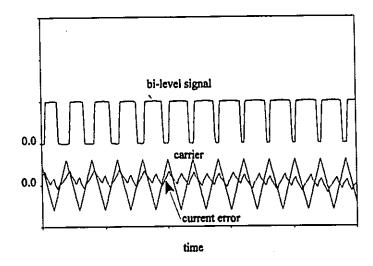

- Fig. 6.2 Principles of operation of the current control technique.

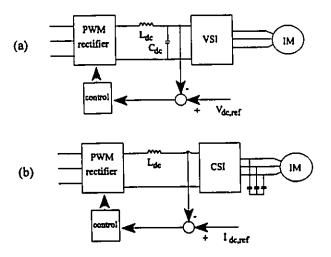

- Fig. 6.3 DC voltage/current regulation loops, (a) VSI drive without regeneration capability, (b)

- CSI drive with regeneration capability.

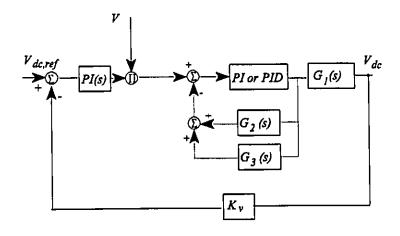

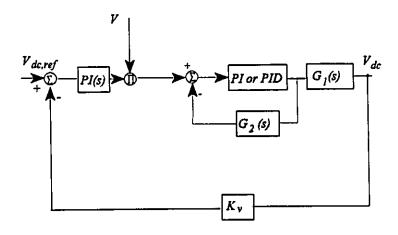

- Fig. 6.4 Block diagram of the overall system.

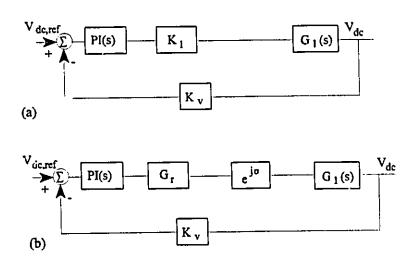

- Fig. 6.5 Simplified block diagram.

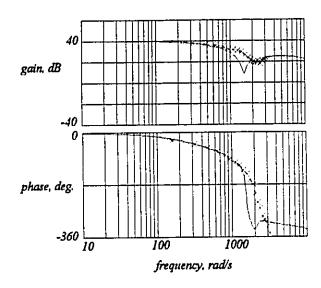

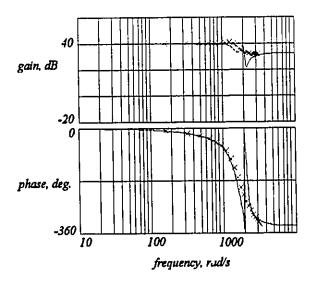

- Fig. 6.6 Closed loop frequency response, (PI regulator in the current loop).

- Fig. 6.7 Closed loop frequency response, (PID regulator in the current loop).

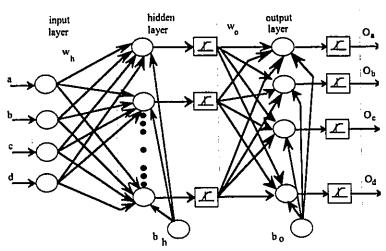

- Fig. 6.8 The NN structure.

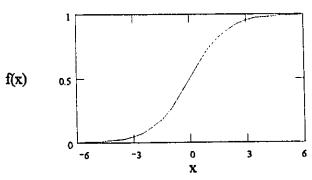

- Fig. 6.9 The characteristic S-shape of the sigmoid function.

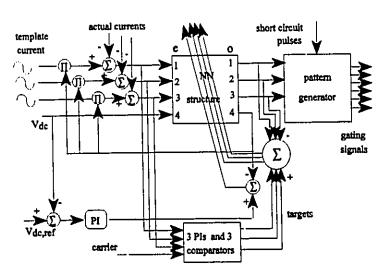

- Fig. 6.10 The proposed NN based controller.

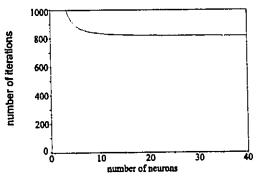

- Fig. 6.11 Effect of number of neurons on the convergence time.

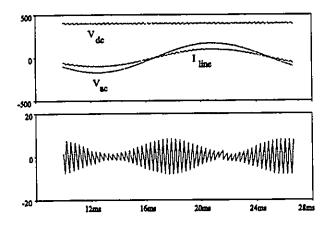

- Fig. 6.12 (a) Output dc voltage,  $V_{dc}$ , rectifier line current  $I_{rec}$ , (b) input line current  $I_{line}$ , and ac voltage  $V_a$ .

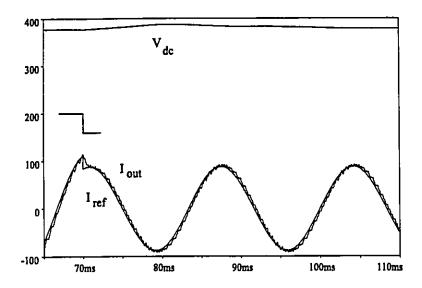

- Fig. 6.13 Transient response, PI controller.

- Fig. 6.14 Transient response, PID controller.

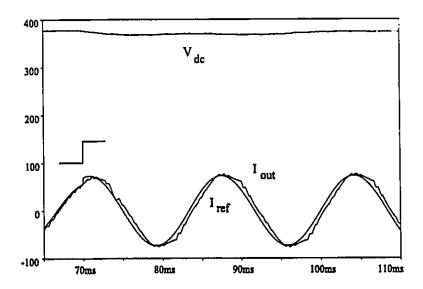

- Fig. 6.15 Transient response, NN based controller.

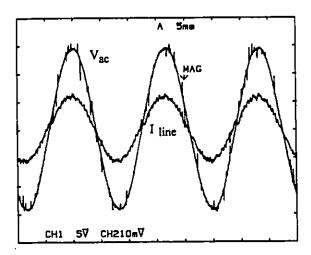

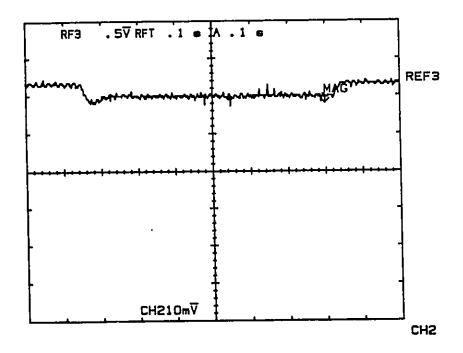

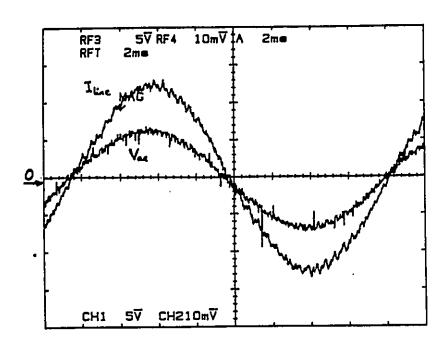

- Fig. 6.16 Experimental results, input line current  $I_{line}$ , input phase voltage  $V_{ac}$  (50V/div, 5A/div, 5ms/div).

- Fig. 6.17 Experimental results, dc voltage transients (50V/div, 5ms/div).

#### CHAPTER 7.

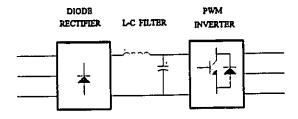

- Fig. 7.1 Conventional ac drive system.

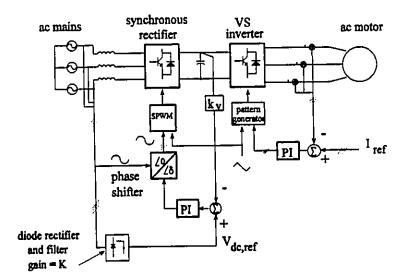

- Fig. 7.2 The proposed ac drive system.

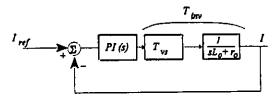

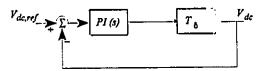

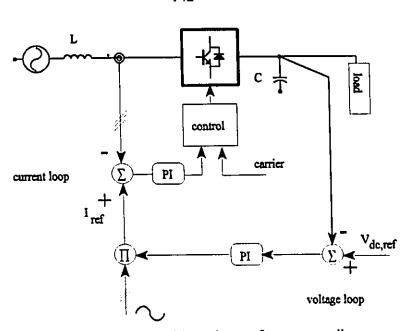

- Fig. 7.3 Block diagram of the current loop.

- Fig. 7.4 (a) Damping factor vs modulation index, (b) damping factor vs Pl time constant.

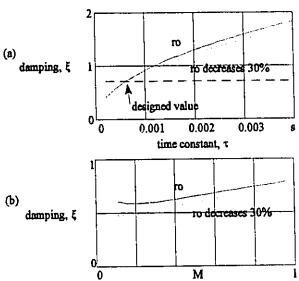

- Fig. 7.5 Design of the current loop, (inverter T<sub>inv</sub>, PI regulator and designed system G<sub>i</sub>).

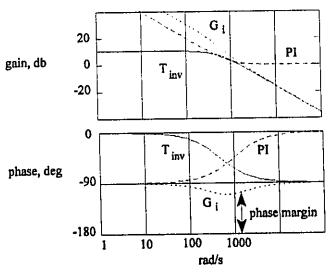

- Fig. 7.6 Phasor diagram of the input Synchronous Rectifier.

- Fig. 7.7 Block diagram of the voltage loop.

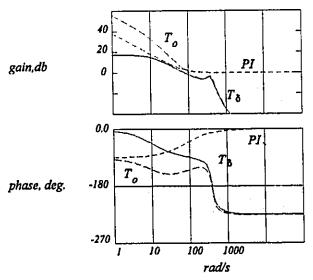

- Fig. 7.8 Design of the control loop of the Synchronous Rectifier.

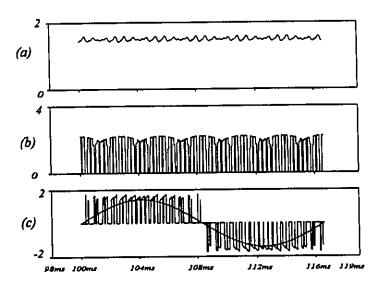

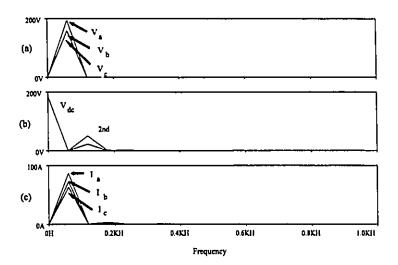

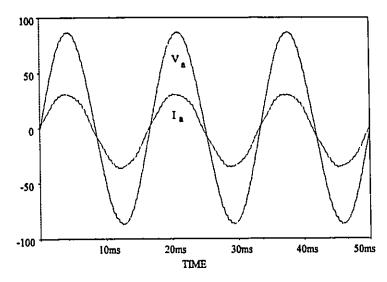

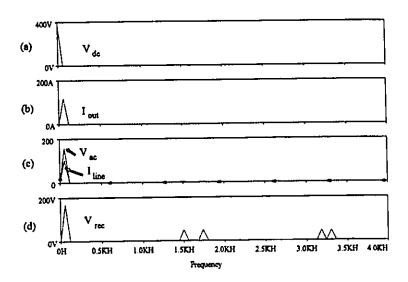

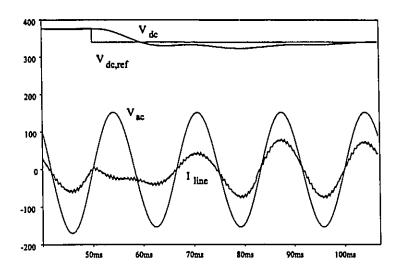

- Fig. 7.9 (a) DC bus voltage, (b) inverter output current, (c) input line current (scaled) and line voltage, (d) rectifier input voltage.

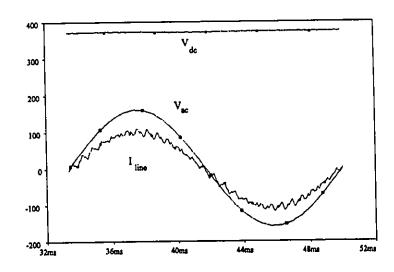

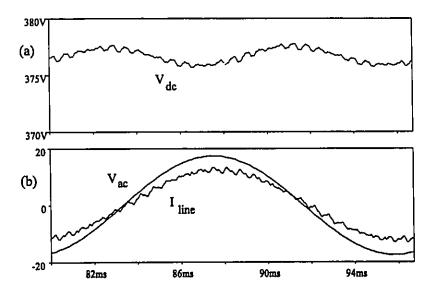

- Fig. 7.10 Steady state waveforms, input line current  $I_{line}$  (scaled), input ac voltage  $V_{ac}$ , dc bus voltage  $V_{dc}$ .

- Fig. 7.11 Step down in the output inverter current. The currents are scaled (× 10).

- Fig. 7.12 Step up in the output inverter current. The currents are scaled (× 5).

- Fig. 7.13 AC transients, 10% step down in the ac line voltages.

- Fig. 7.14 Operation with unbalanced input voltages, (a) dc bus voltage, (b) input line current and voltage.

- Fig. 7.15 Experimental results, line current and phase voltage (50V/div, 5A/div, 2ms/div).

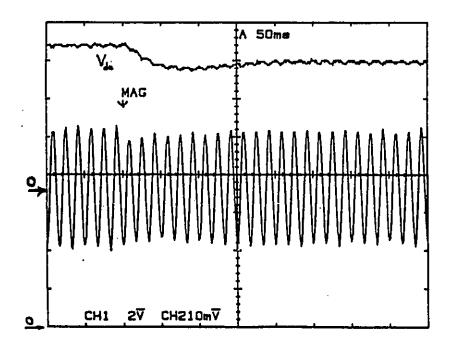

Fig. 7.16 Experimental results, dc voltage transients, line current and dc voltage (50V/div, 10A/div, 50ms/div).

#### CHAPTER 8.

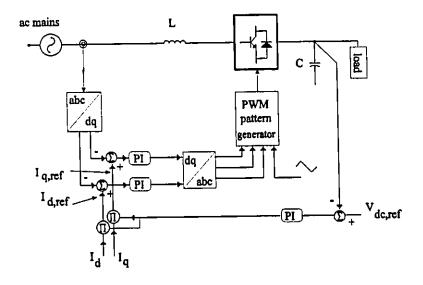

- Fig. 8.1 PWM rectifier with stationary frame controller.

- Fig. 8.2 PWM rectifier with rotating frame controller.

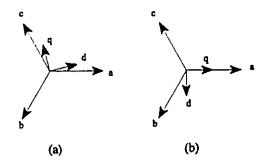

- Fig. 8.3 (a) An arbitrary rotating frame, (b) the chosen reference rotating frame.

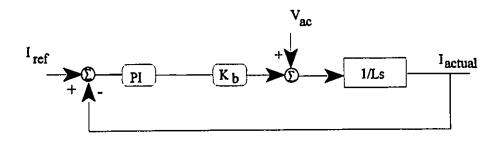

- Fig. 8.4 Block diagram of the current loop.

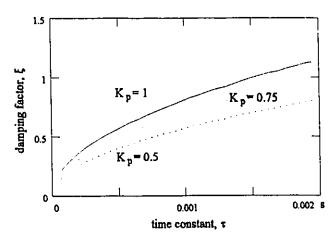

- Fig. 8.5 Damping factor as a function of PI time constant (proportional gain  $K_p$ , as parameter).

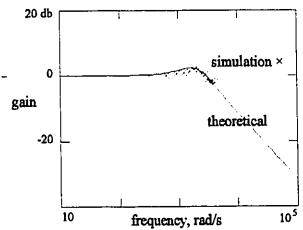

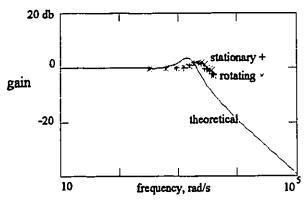

- Fig. 8.6 Closed loop frequency response of the current loop, simulation vs theoretical results.

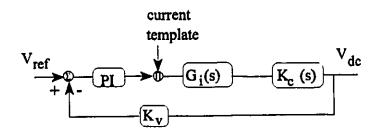

- Fig. 8.7 Block diagram of the voltage loop.

- Fig. 8.8 Closed loop frequency response of the overall system, simulation vs theoretical results.

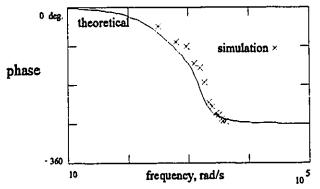

- Fig. 8.9 Phase response of the overall system.

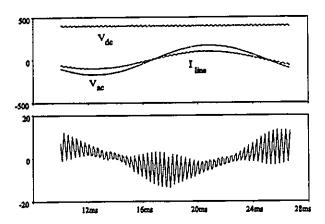

- Fig. 8.10 Simulation results for stationary frame controller, (a) output dc voltage, input phase voltage and current, (b) steady state error.

- Fig. 8.11 Simulation results for rotating frame controller, (a) output dc voltage, input phase voltage and current, (b) steady state error.

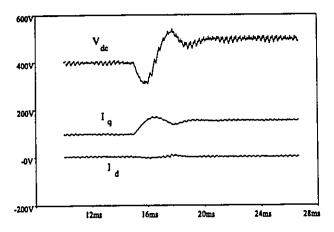

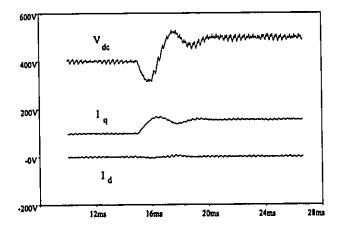

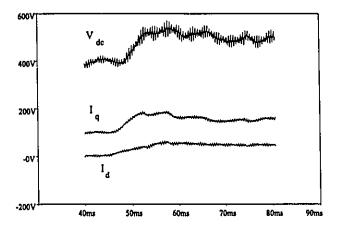

- Fig. 8.12 Transient response for stationary frame controller, output dc voltage  $V_{dc}$ , d-axis and q-axis currents.

- Fig. 8.13 Transient response for rotating frame controller, output dc voltage  $V_{dc}$ , d-axis and q-axis currents.

- Fig. 8.14 Transient response of PWM rectifier with phase shift control, output dc voltage  $V_{\text{dc}}$ , d-axis and q-axis currents.

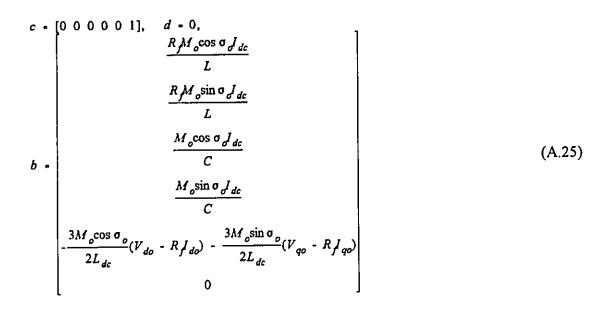

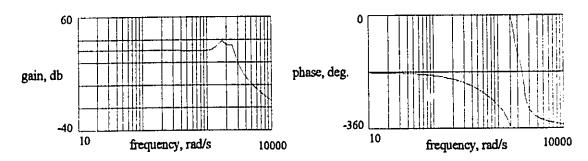

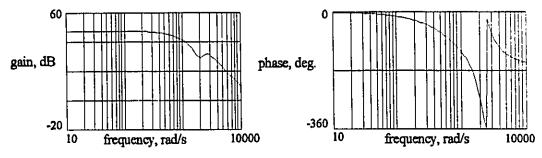

Fig. A.1 Bode plots,

$$\frac{\hat{v}_{dc}(j\omega)}{\hat{\sigma}(s)}$$

.

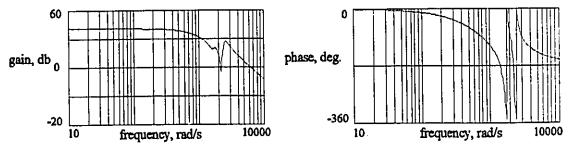

Fig. A.2 Bode plots,  $\frac{\hat{v}_{dc}(j\omega)}{\hat{m}(s)}$ .

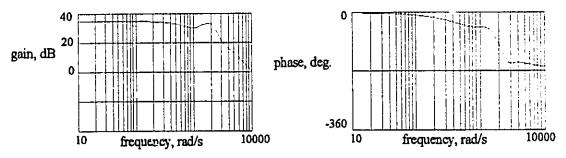

Fig. A.3 Bode plots,  $\frac{\hat{v}_{dc}(j\omega)}{\hat{\sigma}(s)}$ .

Fig. A.4 Bode plots,  $\frac{\hat{v}_{dc}(j\omega)}{\hat{m}(s)}$ .

Fig. A.2 Bode plots,

$$\frac{\hat{v}_{dc}(j\omega)}{\hat{m}(s)}$$

Fig. A.3 Bode plots,

$$\frac{\hat{v}_{dc}(j\omega)}{\hat{\sigma}(s)}$$

Fig. A.4 Bode plots,

$$\frac{\hat{v}_{dc}(j\omega)}{\hat{m}(s)}$$

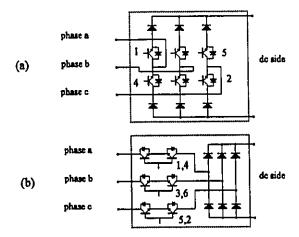

Fig. B.1 (a) Standard PWM rectifier, (b) proposed non-regenerative topology.

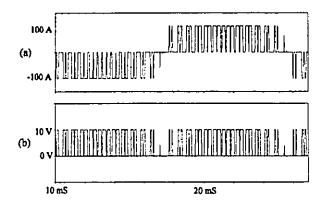

Fig. B.2 Rectifier input current, (b) gating signal applied to switches 1 & 4.

# List of Tables

- Table 2.1 Switch combinations for current source and voltage source topologies.

- Table 2.2 Per unitized values, (M = 1, f = 60 Hz).

- Table 2.3 KVA ratings in pu.

- Table 3.1 Filter components.

- Table 4.1 Design example.

- Table 5.1 Steady state results.

- Table 5.2 Parameters for experimental set up.

- Table 6.1 System specifications.

- Table 7.1 Design example used in simulation.

- Table 8.1 Simulation circuit parameters.

#### xxiii

#### List of Acronyms

ASD Adjustable Speed Drive

CSI Current Source Inverter

DF Distortion Factor

GTO Gate Turn Off thyristor

IDF Input Displacement Factor

IGBT Insulated Gate Bipolar Transistor

HVDC High Voltage Direct Current

NN Neural Network

PF Power Factor

PI Proportional-Integral

PID Proportional-Integral-Derivative

PWM Pulse Width Modulated

PWMBR Pulse Width Modulated Buck Rectifier

PWMSR Pulse Width Modulated Synchronous Rectifier

rms root mean square

SHE Selective Harmonic Elimination

SPWM Sinusoidal Pulse Width Modulated

SVM Space Vector Modulated

THD Total Harmonic Distortion

VSI Voltage Source Topology

#### xxiv

#### List of Main Symbols

#### Currents:

j peak ac current

$I_{rms}$  rms value of the current

I<sub>sw</sub> switch rms current

I average switch current

$I_{dc}$  dc current

I<sub>de,ref</sub> de current reference

$I_{d,ref}$  d-axis current reference

$I_{q,ref}$  q-axis current reference

$i_{c,a}(t)$  filter capacitor current, phase a

$i_{rec,a}(t)$  rectifier input current, phase a

$i_{rec,h}(t)$  hth harmonic component of the rectifier input current

$i_{l,h}(t)$  hth harmonic component of the line current

### Voltages:

V peak ac voltage

$V_{rms}$  rms value of the voltage

$V_{peak}$  peak reverse switch voltage

$V_{dc}$  dc voltage

$V_{dc,ref}$  dc current reference

$V_{phase}$  phase voltage

$v_{rec}(t)$  rectifier input terminal voltage

$v_{c,a}(t)$  filter capacitor voltage, phase a

# Switch and Switch Related Parameters:

$S_i$  switch i

$S_{bi}$  bi-level switching function

$S_{tr}$  basic tri-level switching function

$S_{sh}$  short circuit switching function

Gate, gating signals for switch i

$SW_i$  line-to-line switching function

$SW_p$  phase switching function

# **Power Circuit Components:**

L, C filter components on the ac side

$L_{dc}$ ,  $C_{dc}$  filter components on the dc side

$R_s$  line resistance

$R_f$  filter resistance

$r_o$  motor equivalent resistance

$L_o$  motor equivalent inductance

$Z_L$  line impedance

Z<sub>C</sub> capacitor branch impedance

#### **Control Circuit:**

$K_{\nu}$  current and voltage sensor gains

$K_p$ ,  $\tau$  proportional gain and time constant of the PI regulator

$K_{pdi}$ ,  $K_{ni}$ ,  $K_{di}$  proportional, integral and derivative gain of the PID regulator

# xxvi

# General:

| M          | modulation index                |

|------------|---------------------------------|

| $M_{max}$  | maximum modulation index        |

| $M_{min}$  | minimum modulation index        |

| θ          | input displacement angle        |

| ω          | fundamental angular frequency   |

| $\omega_b$ | filter break frequency in rad/s |

| δ          | power angle                     |

| ξ          | damping factor                  |

| η          | efficiency                      |

| σ          | control (phase shift) angle     |

| α          | filter attenuation factor       |

| $f_m$      | carrier frequency               |

| $f_{sw}$   | switching frequency             |

| $f_b$      | filter break frequency          |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 AC-DC Conversion

Environmental and safety issues related to energy consumption led to a basic question for our society. How can we improve our standard of living without endangering our environment? The answer lies in generating electrical energy by cleaner and more efficient power plants and consuming the generated power more efficiently. One possible solution is energy conservation by wide spread use of Power Electronics. It has been estimated that in the USA roughly 15%-20% of energy can be saved by more efficient use of electricity with the help of Power Electronics. Approximately 60% to 65% of the generated energy is consumed in electrical motors. This has made the motor drive systems a major target for numerous energy-saving schemes. It is well established that Adjustable Speed Drives (ASDs) can save a considerable amount of energy by adding flexibility to the processes. Therefore, more and more customers are using these systems. This means that more electrical devices are connected

Fig. 1.1 Typical connection of static converters to ac mains.

to the ac system. Fig. 1.1 shows a typical configuration. There are also other applications which need interfacing with ac mains. These include indirect frequency changers, dc power supplies, battery chargers and HVDC transmission systems, Fig. 1.1. Interfacing with the ac system is usually achieved through an ac/dc conversion stage, or rectifier. As the number of applications of adjustable speed drives increase and static power converters proliferate, there is a need to understand and quantify their impact on the power system. Interactions between the power system and the converter and conversely the effect of power system disturbances on the converter performance have therefore become a major issue in the widespread use of Power Electronic conversion.

# A. Generation of Harmonics

The switching action of converters causes a current to be drawn from the system which is far from the ideal sine wave shape. The distorted current flowing through the supply system

Fig. 1.2 Representation of Input Displacement Factor, IDF and Distortion Factor, DF.

,

impedances will produce distorted voltages at various points of coupling with other loads in the system. These voltage distortions can interfere with the acceptable operation of loads and other converters, resulting in serious problems such as resonance overvoltage, harmonic instabilities, reduced efficiency and interference with communication circuits. It is possible to express distorted current in terms of the fundamental sinusoidal wave plus a number of other sinusoidal waves of higher frequencies (Fourier series). These sinusoidal components of the periodic waveform with integer multiple of the fundamental frequency are defined as harmonics. Measures must be taken to reduce/eliminate harmonics wherever possible. The role of utility engineers and converter designers is to study the effect of harmonics and: 1) determine the possibility of harmonic resonance occurring and 2) calculate the magnitudes and orders of harmonic voltages and currents under various load conditions. Since it is not economical nor desirable to eliminate the harmonic currents from individual converters, analysis and guidelines are necessary to determine whether or not there will be a problem created by the harmonics injection into the power system. Such useful guidelines and recommendations are provided in standards such as IEEE-519 and IEC-555 to aid in the application of converters and to ensure the high power quality to which North America has become accustomed.

#### B. The Input Power Factor

The power factor of converter is made up of two components: Input Displacement Factor (IDF) and Distortion Factor (DF), Fig. 1.2. The PF can be given by:

$$PF = IDF \times DF$$

(1.1)

The effect of the two are combined to obtain the total Power Factor (PF). The displacement

component is the ratio of the active power (in W), to the apparent power (in VA), considering only the fundamental waveform. This is the power factor seen by the utility metering devices (kW. hs and var. hs). The distortion component is the component associated with harmonic voltages and currents. Displacement power factor is the power factor that is measured by metering equipment, and is the one on which utility penalties are based (utilities expect loads to have a 0.9 PF or better). Therefore, it is necessary to reduce the phase displacement between the fundamental waveforms of current and voltage, in order to reduce the cost of operation.

In order to comply with harmonics limits, and to minimize the amount of kVA drawn from the system, the front-end rectifier must draw near sinusoidal currents at high power factor. Furthermore, the converter must achieve high operating efficiency with low cost, in order to be competitive on the market. In other words, the challenge is to provide a high quality conversion scheme which delivers high quality (low ripple) output waveforms without distorting the ac mains and without drawing any reactive power [1]-[5]. A brief review of the

Fig. 1.3 Three-phase diode bridge rectifier.

existing front-end rectifier topologies is given in the following.

## 1.2 Front-End Rectifier Topologies

# 1.2.1 Diode Bridge Rectifier

A three phase bridge converter for ac/dc conversion is shown in Fig. 1.3. The conversion of power is accomplished by periodic switching in the conducting legs of the converter. The "switches" in the case of Fig. 1.3 are diodes. The ac source is connected to the load by combinations of one top and one bottom switch. The resulting output voltage is made up of the crests of the sinusoidal waveforms ( $60^{\circ}$ ). For the sake of simplicity the dc current is considered to be constant. Therefore, the line currents will consist of square waveforms of  $120^{\circ}$  width. Thus, harmonic current will flow in the supply lines. Fourier analysis confirms that each 6th harmonic in the dc voltage, results in 6n  $\pm$  1 harmonic currents in the ac line. The magnitudes of these harmonic currents are inversely proportional to the harmonic order. Therefore, the diode rectifier injects large current harmonics in the mains, while maintaining

Fig. 1.4 Diode rectifier with input current waveshaping.

a high Input Displacement Factor (IDF = 1). A. R. Parasad et al in [6] proposed a simple method of improving the input power factor of a three phase diode rectifier by waveshaping the input line currents with the help of an additional switch, Fig. 1.4. However, the design of the input filter for this scheme is difficult and the input current must be discontinuous.

# 1.2.2 Phase Controlled Rectifier

The diodes in Fig. 1.3 will start conducting as soon as a voltage is applied in the forward, or current carrying direction. As a result, the output voltage of the converter is uncontrolled. If these diodes are replaced by thyristors, Fig. 1.5, the output voltage can be controlled by delaying the firing angle (the instant at which the thyristors are turned on). Firing angle also influences the magnitude of the current harmonics, [3,4]. This topology is attractive due to its inherent ruggedness, high efficiency and simple control circuitry. However, it has the well-documented drawbacks of:

- poor input power factor,

Fig. 1.5 Line-commutated phase-controlled rectifier.

- large low order harmonics in the input line currents.

The former property is due to the phase displacement required for output power control and is an inherent characteristic of phase-controlled rectifiers. With the growing use of phase control, utility systems are facing serious power quality problems. As it was mentioned before, recently proposed standards tend to severely restrict harmonic injection into power line. Bulky and expensive filters have been used to suppress the injected harmonics. However, the cost and complexity of such compensating schemes, will tend to reduce phase-controlled converters applications in the future [3,4,5].

#### 1.2.3 PWM Front-End Rectifiers

Recent advances in power semi-conductor technology have produced high voltage/high current fast gate turn-off switching devices (such as GTOs and IGBTs.) Consequently, the thyristor switches in converter are being replaced by these devices, making it feasible to apply Pulse Width Modulation (PWM) techniques to converters. By using PWM switching patterns, the frequency spectra of the input waveforms can be shaped and harmonic components moved to a higher frequency. Operation of the converters with PWM switching patterns offers features such as sinusoidal input current at unity displacement power factor and a high quality dc output voltage. This results in reduced input current harmonics and ac voltage distortion of the ac mains [5,7]. These features consequently lead to a smaller size of the input/output filter and reduced losses in the input transformer. Successful application of PWM techniques to forced commutated converters has prompted recent investigations in finding more suitable topologies for ac to dc conversion. Two structures have evolved:

- The current-source topology, Fig. 1.6 or PWM Buck Rectifier;

- The voltage-source topology, Fig. 1.8, (PWM Synchronous or Boost Rectifier).

# 1.2.3.1 Current Source Topology (PWM Buck Rectifier)

The high power and high quality current-source PWM rectifier of Fig. 1.6 has a good potential for applications in high power ac drives and frequency changers. The PWM

Fig. 1.6 Current-source topology, PWM Buck Rectifier.

rectifier shown in Fig. 1.6, establishes a dc current link by means of unidirectional (regarding current)/ bidirectional (regarding voltage) switches. This structure has good reliability and ruggedness. Due to the time-discontinuous operation (switching), energy storage elements must be provided on the dc/ac side in order to make the exchange of power (during switching) possible. As can be seen from Fig. 1.6, since the ac source is not ideal, an LC filter is needed at the ac terminal of the PWM rectifier. The input capacitors also suppress the voltage spikes across the switches. This makes the PWM rectifier prone to resonance problems. Therefore, proper damping must be provided in the filter circuit either by inserting additional resistive

elements or by using control methods. The other difficulty of current source rectifier is the generation of proper switch gating signals. A path for the output dc current must exist at all times which requires short-circuiting pulses when no current is drawn from the ac supply. These must be added to the tri-level gating signals [8]. The control schemes used to operate the PWM Buck rectifier can be divided into open loop and closed loop techniques.

Fig. 1.7 Control schemes for current source PWM Rectifier.

# A. Open Loop Control Schemes

A number of publications have investigated the performance and characteristics of the current source type PWM rectifier operating with off-line PWM patterns [9]-[14]. The control of the output current is obtained by varying the modulation index and/or phase shifting of the pattern. Ideal input/output characteristics such as ripple-free dc link current and sinusoidal input voltages are assumed. These publications mostly deal with the PWM patterns. Pattern generation can be divided into two main categories:(a) carrier based techniques and (b)

programmed PWM techniques. These techniques can be adapted to optimize/minimize certain performance factors/errors. As a general conclusion, the programmed techniques are more suitable for high power applications where the switching frequency is limited. As it was mentioned earlier and in general, using carrier-based techniques for a current source rectifier requires an additional stage to meet the current source pattern requirements. However, use of techniques such as Trapezoidal PWM is straight-forward. Combination of carrier-based and programmed techniques is also suggested [15]. In this scheme the Trapezoidal PWM is used for the low output frequency range and the Selective Harmonic Elimination (SHE) is adopted for the higher frequency range. Reviews of most commonly used carrier-based and programmed techniques are given in [16],[17] respectively.

Different PWM patterns are developed in [18] and the effect of the switching patterns on the harmonics generated and on the size of the input/output filter is studied. Various performance factors are defined and used to evaluate the proposed PWM patterns. Also, an algorithm is presented to achieve optimum design of input/output filters [19]. However, the problem of damping is not considered and the Input displacement Factor of the rectifier is not studied.

The single phase Buck rectifier is studied in [20]. The basis of duality is laid out and a structure which is the dual of the voltage source topology is proposed and investigated [21]. The rectifier is operated with delta modulation control of the input capacitor voltage and the operating limits are determined. A more in depth study of both current source and voltage source topologies and PWM patterns is presented in [22]. The duality of the two structure is studied and similarities are clarified. The above publications are more concerned with the

operation of the current source topology and the method of pattern generation. However, recently and concurrently with the work presented in this thesis, some researchers have focused on the correction of Input Displacement Factor, IDF.

Hiti et al [23] proposed a three-phase PWM rectifier with compensation of the IDF. A control low is derived to obtain unity power factor and DSP implementation of the controller in dqo frame is presented. The pattern generator is based on Space Vector Modulation (SVM) (Fig. 1.7) which is described in detail in [24],[25]. The Space Vector Modulation technique offers the advantage of optimized switching instants and therefore reduces switching losses.

### B. Closed Loop Control Schemes

In all of the studies mentioned above, the PWM Rectifier is controlled in an open loop fashion with modulation index or phase shift control. Since in most cases, the PWM pattern is stored in an EPROM, the modulation index control is discontinuous and speed of response is slow [26,27]. Moreover, sufficient damping must be provided in the power circuitry to avoid oscillations of the input line currents. Recently, attempts have been made to adapt closed loop control techniques for PWM rectifiers. Wang, *et al* developed an on-line PWM pattern generator with Digital Signal Processor (DSP) implementation for current source topologies. The pattern generator is used in [28] to control a PWM Buck Rectifier and obtain unity power factor operation independently of the rectifier operating point. The control circuitry proposed in [28] is complex and requires DSP implementation.

Another control scheme is proposed by Sato et al in [29] in which the state variables of the rectifier and the input filter are controlled in closed loop fashion to obtain sinusoidal steady state ac waveforms and to reduce the transient oscillation of the ac side current. The

proposed circuit however is very complicated and needs extensive use of hardware. The main stream of control techniques applied to current source PWM rectifiers are depicted in Fig. 1.7.

Small signal analysis of current source rectifiers is presented in [30],[31].

Application of current-source rectifiers in ac drives is investigated in [32]-[35]. In these schemes, the dc link current regulation is normally obtained by phase control of the input thyristor rectifier. Increase in speed of response and effective damping the oscillations resulting from the presence of the filter capacitors is still a challenge to designers [32].

Fig. 1.8 Voltage-source topology, synchronous link rectifier.

# 1.2.3.2 Voltage Source Topology (Synchronous Rectifier)

The voltage-source topology finds application in dc voltage link ac drives and self-controlled dc bus var compensators. This topology, interfaces the ac and dc systems by means of bidirectional (current)/ unidirectional (voltage blocking) switches, Fig. 1.8. The structure consists of an inductor on the ac side and a capacitor on the dc side. The gating signals of the

top and bottom switches of the same leg are complementary, hence easy to produce from the PWM pattern. This feature has contributed to the popularity of this structure and as a result, many control strategies have been developed. The literature on the subject is briefly described below, Fig. 1.9.

A current-controlled Synchronous Rectifier was proposed by Ooi *et al* [36]. The three line currents are controlled to obtain sinusoidal currents with unity power factor. The reference current template can be either generated from phase voltages or be stored in an EPROM and synchronized with the ac mains. The amplitudes of the reference currents are varied according the dc load voltage demand. The rectifier is operated with a hysteresis technique which has the drawback of variable switching frequency. Reports of transient test on the proposed converter and application as an ac drive system are presented in [37],[38] respectively. Further investigations on performance and control of synchronous link converters can be found in [39],[40]. The current sensors were eliminated in the indirect current control of synchronous

Fig. 1.9 Control schemes for Synchronous Rectifier.

link rectifier proposed in [41]. However, the region of stability with this control method is very limited. The stability limitation was improved by implementing a more complex control scheme [42].

In [43], a Synchronous (Boost) Rectifier with a predictive current control with fixed switching frequency is proposed. The idea is to correct the error between the reference and the actual current within one switching period. Based on this criterion, the gating signals of the six switches are generated. The calculation of the duty cycle of the switches is dependent of the circuit parameters, making the method sensitive to parameter variation. Analysis of Synchronous Rectifier is presented in [44],[45], but operating region limitations are not brought out. The operation of a Synchronous Rectifier as a var compensator is investigated in [46].

Phase angle control of voltage- source PWM rectifier is presented in [47],[48]. The real and reactive power of the rectifier are controlled based on the derived equations. This means controlling the power angle in a closed loop fashion. The controller can be realized in either stationary (abc) or rotating (dqo) frames. The method is suitable for low switching frequency high power applications, and the speed of response is very slow. The converter may exhibit some oscillatory response under transient conditions. Recently, multi-level voltage source PWM rectifiers with closed loop control are been considered for high power applications [49],[50].

Due to simplicity of derivation of switch gating signals for voltage-source rectifier, many control techniques have been developed and implemented [51],[52]. For DSP implementation, a promising technique in pattern generation is the Space Vector Modulation.

This technique is becoming more and more popular due to the advances in computer technology and price reduction/speed improvement of microprocessors [53-55]. The existing ac/dc conversion schemes with their typical control options are depicted in Fig. 1.10.

# 1.3 Scope and Contributions of the Thesis

In view of the above, this thesis focuses on developing techniques to meet specific performance requirements and to satisfy special applications for PWM ac/dc converters. In particular, improving system performance regarding the Input Displacement Factor is emphasized. By studying similarities and the duality of current-source and voltage-source type

Fig. 1.10 Existing rectifier topologies.

topologies, it is possible to transfer the insights and experiences of one topology to the other. In particular, closed loop techniques developed for voltage source topology can be adopted for current-source type. Therefore, wherever applicable, new methods of control and/or novel topologies are proposed in the thesis, practical problems are addressed and viable solutions are proposed. The particular contributions of this thesis are:

### A. Current Source Topology

- A feed-forward scheme is proposed to achieve unity power factor through compensation of the Input Displacement Factor. The proposed scheme is very simple and does not need any added transducers.

- A user friendly approach to design of input filter for PWM rectifiers is proposed.

Different design objectives are defined and compared and the effects of filter components on the Input Displacement Factor (IDF) are studied.

- The effects of circuit components and control techniques on damping in PWM rectifiers

are investigated. A new control scheme is proposed which needs no damping resistors

in the input filter circuit and results in a better system performance during transient

conditions and a higher efficiency.

- Closed loop control of PWM rectifiers is studied. In particular, a current-controlled PWM rectifier is proposed, analyzed and designed. Load independent unity power factor operation is achieved. Different types of controllers are investigated. These include Proportional-Integral (PI), Proportional-Integral-Derivative(PID) and Neural Networks (NN) based controllers.

#### B. Voltage Source Topology

- A unity power factor input stage with minimum hardware requirements is proposed for ac drive applications.

- A current-controlled voltage regulated dc power supply based on voltage source topology is proposed. The design and performance of the controller in both stationary and rotating frames are investigated and compared. Design procedure is given and transient response is studied using rotating frame transformation.

#### 1.4 Thesis Outline

The thesis is divided into 9 chapters. A brief outline of each chapter is as follows:

In *Chapter 2*, the steady state characteristics of three-phase PWM rectifier topologies are investigated. The study includes: principles of operation, graph and switch realization comparison, converter and switch ratings, operating regions, filtering requirements, power factor considerations and control aspects. The theoretical considerations are verified by simulation and experimental results on laboratory prototypes [56].

Practical problems of input filter design for PWM rectifiers are discussed in *Chapter* 3 and a simple systematic procedure for design of the input filter is proposed [57]. The chapter includes study of power factor, kVA ratings, system efficiency and effect of parameter variations. Two design examples are provided and the corresponding characteristics are compared.

Chapter 4 proposes a compensation scheme to achieve unity Input Displacement Factor independently of the rectifier operating point. The modulating signals are phase shifted according to the rectifier operating point to always result in unity IDF. The control circuit is

very simple and does not require any additional transducer. It uses a feed-forward dc current loop and the standard dc voltage/current regulation loop to regulate the amplitude and phase of the modulating signals. Parameter sensitivity, effect of variations of input voltages and the limitations of the proposed scheme are studied [58].

In Chapter 5 a current source type PWM rectifier with on-line pattern generation and inherent synchronization with the ac mains is proposed. This results in a very fast starting and a much improved transient response. Also, the need for the damping resistors is eliminated due to the effective damping provided through the modulating of the capacitor voltages. The control scheme proposed in this chapter results in a system with higher efficiency due to the elimination of the damping resistors. The proposed scheme is investigated for ac drive applications under various transient and fault conditions. Also, a topology for non-regenerative applications is proposed that requires only three base drives. Experimental results verify the feasibility of the proposed non-regenerative topology and the pattern generation method used [59],[60].

Chapter 6 proposes closed loop control of PWM rectifiers. The three input line currents are controlled to obtain low harmonic currents with unity IDF. The proposed current controlled PWM rectifier exhibits excellent steady state operation and good transient dynamics, a result of the current control method used. Output dc voltage regulation is achieved by varying the amplitudes of the current references. Analysis and design guidelines are provided and the key predicted results are experimentally verified on laboratory prototypes [61]. Different types of controllers are implemented. These include: Proportional Integral (PI), Proportional Integral Derivative (PID) and a Neural Networks (NN) based controller. The performances of the three

controllers are compared [62],[63].

Chapter 7 presents an application of a PWM Synchronous Rectifier as the input stage of an ac drive system, this results in improved performance with a simple control scheme. To allow the output inverter to operate in the PWM mode at rated speed, a Synchronous Rectifier is proposed to slightly boost the dc bus voltage. The output inverter is current-controlled, therefore, the dc bus requirements are not stringent. This allows for a simpler control strategy to be used to operate the input rectifier, the main purpose being to ensure unity power factor operation. Experiments on a laboratory prototype are used to verify the simulation and theoretical results.

Chapter 8 proposes a current controlled PWM Synchronous Rectifier. It provides near sinusoidal input currents with unity power factor and a low output voltage ripple. Moreover, it produces a well-defined input current harmonic spectrum, exhibits fast transient response to load voltage variations and is capable of regenerative operation. PWM pattern generation is based on a carrier technique and the current controller is implemented in the (a) stationary (abc) frame and (b) rotating (dqo) frame. The design and performance of the two controller options are investigated and compared.

#### CHAPTER 2

# PERFORMANCE COMPARISON OF PWM BUCK AND SYNCHRONOUS RECTIFIERS

#### 2.1 Introduction

PWM converters have been shown to offer a better alternative to thyristor phase-controlled rectifiers with respect to power factor and input current/cutput voltage harmonics. This chapter presents a systematic comparison of the two existing topologies (current source, voltage source) from point of view of graph structure and switch realization, converter and switch kVA ratings, PWM patterns, input/output filtering requirements, power factor, operating regions and control aspects. Experimental results obtained on laboratory prototypes are used to validate the theoretical considerations.

## 2.2 Principles of Operation

## 2.2.1 Current Source Topology

The PWM rectifier shown in Fig. 2.1 has current-source characteristics at the dc terminal (dc side inductor, L<sub>dc</sub>) and voltage-source characteristics at the ac terminal (either an ideal voltage source or ac side capacitor). The ac and dc sides are interfaced by operating the six unidirectional (current)/bidirectional (voltage) switches. These switches must be operated so as to avoid an open circuit on the dc link or a short circuit on the ac side. The following criterion is used to generate typical PWM patterns:

- The line currents must be well defined. This means that only two switches are conducting at any instant, one from the top row and one from the bottom row.

The top and bottom row switches in a current source topology can be best represented by two

Fig. 2.1 (a) Current-source topology, PWM rectifier, (b) representation by two "three-way" switches.

Table 2.1 Switch combinations for current source and voltage source topologies.

|       | current source topology |                |                |                |                | voltage source topology |    |                |                |                |    |                |

|-------|-------------------------|----------------|----------------|----------------|----------------|-------------------------|----|----------------|----------------|----------------|----|----------------|

| state | S,                      | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub>          | Sı | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S, | S <sub>6</sub> |

| 0     | 1                       | 0              | 0              | 1              | 0              | 0                       |    |                |                |                |    |                |

|       | 0                       | 0              | 1              | 0              | 0              | 1                       | 1  | 0              | 1              | 0              | 1  | 0              |

|       | 0                       | 1              | 0              | 0              | 1              | 0                       | 0  | 1              | 0              | 1              | 0  | 1              |

| 1     | 1                       | 1              | 0              | 0              | 0              | 0                       | 1  | 1              | 0              | 0              | 0  | 1              |

| 2     | 0                       | 1              | 1              | 0              | 0              | 0                       | 1  | 1              | 1              | 0              | 0  | 0              |

| 3     | 0                       | 0              | 1              | 1              | 0              | 0                       | 0  | 1              | 1              | 1              | 0  | 0              |

| 4     | 0                       | 0              | 0              | 1              | 1              | 0                       | 0  | 0              | 1              | 1              | 1  | 0              |

| 5     | 0                       | 0              | 0              | 0              | 1              | 1                       | 0  | 0              | 0              | 1              | 1  | 1              |

| 6     | 1                       | 0              | 0              | 0              | 0              | 1                       | 1  | 0              | 0              | 0              | 1  | 1              |

$S_i = 0$  means the i-th switch is open.

$S_i = 1$  means the i-th switch is closed.

Fig. 2.2 Possible switch combinations, (a) voltage source topology, (b) current source topology.

"three-way" switches, Fig. 2.1.b. Therefore, the number of possible switch combinations can be calculated as:

number of combinations =

$$(number \ of \ ways)^{(number \ of \ switches)} = 3^2 = 9$$

(2.1)

These nine combinations result in only seven different states since three of these combinations are the zero states during which the ac side is insulated from the dc side and the dc link current is circulating

through one of the bridge legs. An ideal current source PWM rectifier with all possible switch combinations are depicted in Fig. 2.2.b and the switch combinations are tabulated in Table 2.1, where  $S_i = 0$  means that the i-th switch is open and  $S_i = 1$  means that it is closed. In Fig. 2.2.b the ac side consists of three voltage sources connected in delta and the dc side is a current source. Thick lines show a connection through the corresponding switch either, to the top or the bottom dc bus.

Any three functions of time that satisfy  $g_a(t) + g_b(t) + g_c(t) = 0$ , can be represented by a vector  $\vec{G}$  in a two-dimensional space by using the following transformation:

$$\vec{G} = \frac{2}{3} \left( g_a(t) + g_b(t) e^{j\frac{2\pi}{3}} + g_c(t) e^{-j\frac{2\pi}{3}} \right)$$

(2.2)

Therefore, the states shown in Table 2.1 can be transformed to vectors in two-dimensional space. For example, for state 1, we have:

$$\begin{cases} i_{a}(t) = I_{dc} \\ i_{b}(t) = 0 \\ i_{c}(t) = -I_{dc} \end{cases}$$

(2.3)

and this will obtain the following vector as depicted in Fig. 2.2.b:

$$\vec{I}_1 = \frac{2}{3} \left( I_{dc} + 0 - I_{dc} e^{-j\frac{2\pi}{3}} \right) = \frac{2}{\sqrt{3}} I_{dc} e^{\frac{j\pi}{6}}$$

(2.4)

where  $I_{dc}$  is the amplitude of the dc link current. The transformation of these six states forms a hexagon. Each vector presents the location of the line current vector in the new space. The zero state is located at the centre of this hexagon, representing zero line currents, Fig. 2.2.b.

The input/output equivalent circuits of the PWM rectifier are shown in Fig. 2.4(a,b). Here output dc current and input rectifier voltage are the independent variables and output dc voltage and rectifier input currents are the dependent variables. Therefore, the input/output current/voltage relationships are given by:

$$v_{dc}(t) = SW_{l,a}(t)v_{rec,a}(t) + SW_{l,b}(t)v_{rec,b}(t) + SW_{l,c}(t)v_{rec,c}(t)$$

(2.5)

$$i_{recj}(t) = SW_{lj}(t) \ i_{dc}(t) \quad for \ j \in \{a,b,c\}$$

(2.6)

where:  $v_{dc}(t)$  = rectifier output dc voltage,  $SW_{lj}(t)$  = line-to line switching function,  $v_{rec,j}(t)$  = input rectifier voltages,  $i_{dc}(t)$  = rectifier output dc current,  $i_{rec,j}(t)$  = rectifier input currents. From (2.5), the dc output voltage can be obtained as:

$$V_{dc} = \frac{3}{2} ||SW_i|| V_{rec} M \tag{2.7}$$

where

$$M_{\text{max}} = \frac{2}{\sqrt{3}}$$

and  $\|SW_I\|_{\text{max}} = \frac{\sqrt{3}}{2}$  (2.8)

where  $\|SW_i\|$  is the magnitude of the line to line switching function, M is the modulation index, and  $V_{rec}$  is the peak value of the rectifier input phase voltage. The maximum voltage that can be obtained by a current source topology is:

$$V_{dc,max} = \frac{\sqrt{3}}{2} \sqrt{6} V_{rec,rms} = 2.12 V_{rec,rms}$$

(2.9)

where  $V_{rec,rms}$  is the rms value of the rectifier input phase voltage.

As it can be seen from (2.7), the output dc voltage is proportional to the modulation index M. Therefore, the converter behaves as a buck configuration as far as the dc output voltage is concerned. The similarity between current-source PWM rectifier and dc/dc Buck converter can also be realized by comparing the "switch-diode-inductor" arrangement. A single phase Buck converter and a current source PWM rectifier (for one possible state of the switches) are depicted in Fig. 2.3. It is assumed that phase c is the most negative phase, hence switch 2 is always conducting. It is seen

Fig. 2.3 (a) Current source topology, (b) arbitrary state of switches, (c) dc/dc Buck converter, (d) the same switch state as in (b).

Fig. 2.4 Current source topology, (a) input (b) output equivalent circuit. Voltage source topology, (c) input (d) output equivalent circuit.

Fig. 2.5 Experimental results, PWM Buck Rectifier.

that when  $S_2$  is closed, a buck configuration is obtained with either  $S_1$  or  $S_3$  acting as the Buck switch,  $S_{Bk}$ . The role of  $S_5$  is similar to that of the Buck diode,  $D_{Bk}$  in the buck topology. The switch-diode combination shown in Fig. 2.1 can be realized by using a single GTO switch with reverse blocking