Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous à fait parvenir une photocopie de qualité inférieure

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents

# The Design of PAAP: Programmable Asynchronous Array Processor

Marco A. Zelada

A Thesis

in

The Department

of

Computer Science

Presented in Partial Fulfillment of the Requirements for the Degree of Master in Computer Science at Concordia University

Montréal, Québec, Canada

April 1992

© Marco A. Zelada, 1992

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A ON4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-73669-0

#### **ABSTRACT**

## The Design of PAAP: Programmable Asynchronous Array Processor

#### Marco Zelada

This thesis explores architectural features appropriate to massively parallel architectures such as, Processing Element (PE) and Routing Element (RE) programmability within an array processor environment, unrestricted data flow direction, and true array scalability. We illustrate these features through an array design, which we term the Programmable Asynchronous Array Processor (PAAP).

The PAAP proposes a methodology for mapping high-level computation into hardware structures. This feature is shared with systolic and wavefront arrays. However, the PAAP differs in that its PEs can be dynamically programmed to work in an MIMD fashion. They can also be interconnected via dyadic programmable REs to form asynchronous pipelines. In contrast, most systolic and wavefront arrays work in an SIMD fashion, have static interconnections and implement a single special purpose hard-wired instruction. Those which are programmable and work in an MIMD fashion lack the interconnection reconfigurability and data flow control present in the PAAP.

PE and RE instructions and data are not fetched from memory. Instead, the PE and RE are programmed to execute the desired instruction and routing scheme during the program load phase, and data flows through the complete array during the program execution phase. The essence of the architecture is captured by the configurable routing which gives the PAAP its flexibility and power. The RE is a four way bidirectional router which provides maximum flexibility in the definition of pipeline routes. It permits a pipeline to be defined in any direction across the array, downward, sideways in either direction, and upwards.

The PAAP addresses the three main asynchronous circuit problems, namely, computational interference, signal ordering, and transfer interference. It uses a modified two-phase signal protocol which allows the active and passive end of the circuit to implement their own return-to-zero synchronization upon the receipt of the proper protocol sequence [BrozozowskiJ89].

#### Acknowledgment

I would like to thank some of the people that made this work possible through their patience and understanding. First, I want to thank Dr. T. Fancott for his faith in me and his excellent guidance, which helped me carry this project to completion. Thanks also go to Henry Polley, with whom I spent many long hours discussing the architecture and design issues, and without which the thesis text revisions would not have possible.

My deepest thanks go to my wife Li-Yuin Tam for her devoted moral support.

Thanks also go to Hala Tabl and Sam Alexander for their invaluable review comments. The list of other people that have influenced my research and helped in one way or another is too long to mention here. I would like to just say thank you all.

## **Table of Contents**

| Acknowledgment    | ••••••                                     | ii   |

|-------------------|--------------------------------------------|------|

| Table of Contents | ***************************************    | iii  |

| List of Tables    | ***************************************    | . iv |

| List of Figures   |                                            | . v  |

| Chapter 1         | Introduction                               | . 1  |

| Section 1.1       | The Motivation of This Research            | . 2  |

| Section 1.2       | Thesis Introduction                        | . 4  |

| Chapter 2         | Parallel Architecture Concepts             | . 5  |

| Section 2.1       | Parallel Processing                        | . 5  |

| Section 2.2       | Parallel Architecture Taxonomies           | . 6  |

| Section 2.3       | Architectural Issues                       | .9   |

| Section 2.4       | Parallel Processing Implementations        | . 11 |

| Section 2.5       | MIMD Parallel Architecture Overview        | . 14 |

| Section 2.6       | Systolic and Wavefront Arrays              |      |

| Section 2.7       | Asynchronous Design                        |      |

| Section 2.8       | The CHiP Architecture                      |      |

| Chapter 3         | PAAP Architecture Overview                 |      |

| Section 3.1       | Introduction to the PAAP Array             |      |

| Section 3.2       | PAAP Array Building Blocks                 |      |

| Section 3.3       | The Smallest PAAP Array Configuration      |      |

| Chapter 4         | The PAAP Programming Paradigm              |      |

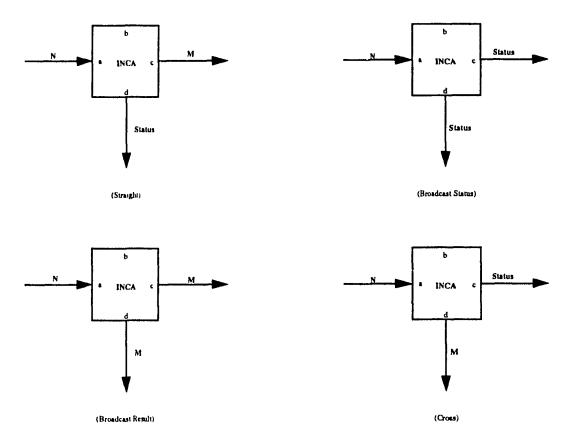

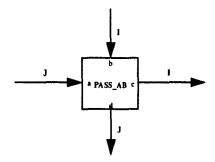

| Section 4.1       | Operational View of the Architecture       |      |

| Section 4.1       | PAAP Programming Variants                  |      |

| Section 4.3       | Examples of Algorithmic Units.             |      |

| Section 4.3.1     | Pre-increment                              |      |

| Section 4.3.2     | Swap                                       |      |

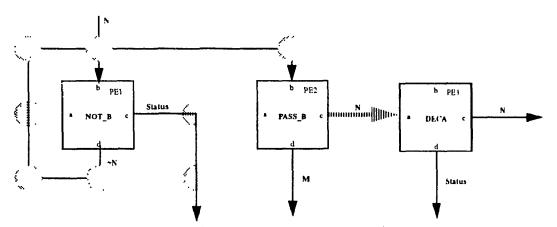

| Section 4.3.3     | Post-decrement                             |      |

| Section 4.3.4     | Arithmetic and Logic Expression Evaluation |      |

| =                 | Inclusion of Constants in the Computation  |      |

| Section 4.3.5     |                                            |      |

| Section 4.3.6     | Boolean Expression Evaluation              |      |

| Section 4.3.7     | High Level Language IF Construct           |      |

| Section 4.3.8     | High Level Language Looping Constructs     |      |

| Section 4.4       | Examples of Complex Operations             |      |

| Section 4.4.1     | Min/Max Search Algorithmic Units           |      |

| Section 4.4.2     | A Sort Algorithmic Unit                    |      |

| Section 4.4.3     | A Match Algorithmic Unit                   |      |

| Section 4.4.4     | A Factorial Algorithmic Unit               |      |

| Chapter 5         | The PAAP PE and RF Architecture            |      |

| Section 5.1       | A Processing Element                       |      |

| Section 5.2       | A Routing Element                          |      |

| Chapter 6         | Practical Issues                           | 79   |

| Section 6.1       | The Design Environment                     | 79   |

| Section 6.2       | A Simulation Example                       | 81   |

| Chapter 7         | Conclusion                                 | 85   |

| References        |                                            | 87   |

| Appendix A        | Programming the PAAP                       |      |

| Appendix B        | Automatic Vector Generation Setup Files    |      |

| Appendix C        | PAAP Detailed Circuit RNL Netlist          | 108  |

| Appendix D        | Automatic Simulation Makefile              | 125  |

| Appendix E        | Automatic Simulation Step Output           | 126  |

| Appendix F        | Partial Simulation Results                 |      |

| =                 |                                            |      |

## **List of Tables**

| TABLE 1.  | Feature Size Shrink Trend           | 3  |

|-----------|-------------------------------------|----|

| TABLE 2.  | Parallel vs. Sequential Computation | 3  |

| TABLE 3.  | Addressable PAAP Registers          |    |

| TABLE 4.  | Byte Parallel Operations            |    |

| TABLE 5.  | The PAAP Array Control Register     |    |

| TABLE 6.  | The PAAP Array Status Register      |    |

| TABLE 7.  | PE Instruction Set                  |    |

| TABLE 8.  | PE Output Routing                   | 40 |

| TABLE 9.  | RE Instruction Set                  |    |

| TABLE 10. | The ALU Status Bus Bits             | 67 |

|           |                                     |    |

## List of Figures

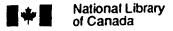

| FIGURE 1.  | Architecture and IC Performance Growth                       | 1   |

|------------|--------------------------------------------------------------|-----|

| FIGURE 2.  | Design Rule Shrink Trend                                     |     |

| FIGURE 3.  | А РААР Агтау                                                 | 23  |

| FIGURE 4.  | PAAP Ruilding Block ICs                                      | 25  |

| FIGURE 5.  | A 1089 PE PAAP Array Configuration                           | 25  |

| FIGURE 6.  | The Smallest PAAP Array Configuration                        | 26  |

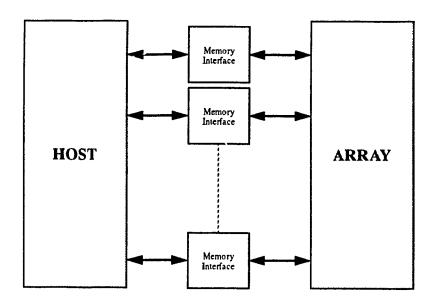

| FIGURE 7.  | A Possible Host/Array Interface                              | 31  |

| FIGURE 8.  | A Pre-increment Implementation                               | 43  |

| FIGURE 9.  | A Swap Implementation                                        | 43  |

| FIGURE 10. | A Post-decrement                                             | 44  |

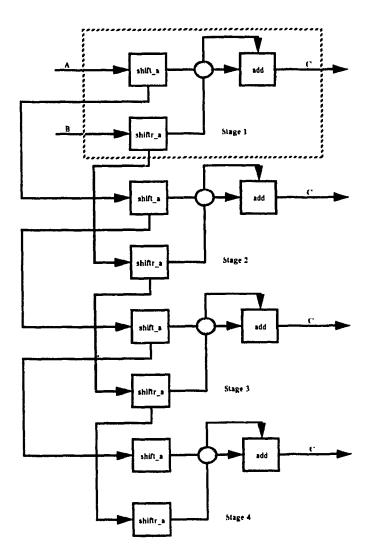

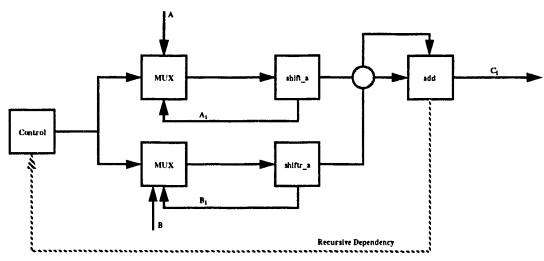

| FIGURE 11. | An Arithmetic and Logic Expression Evaluation Implementation | n45 |

| FIGURE 11. | An Inclusion of Constants Implementation                     | 46  |

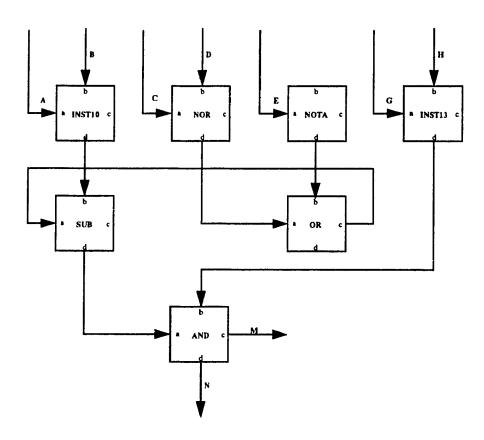

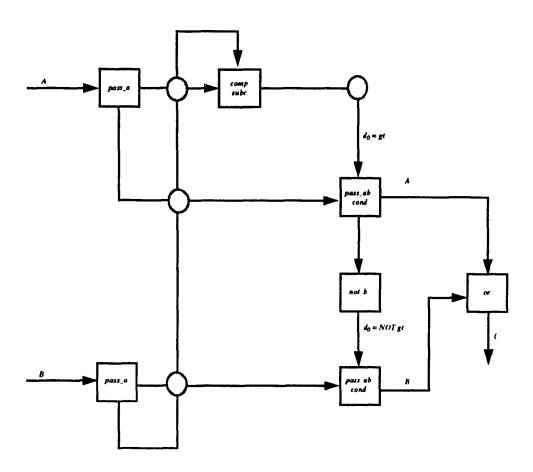

| FIGURE 13. | A Boolean Expression Evaluation Implementation               | 46  |

| FIGURE 14. | An IF Statement Implementation                               | 47  |

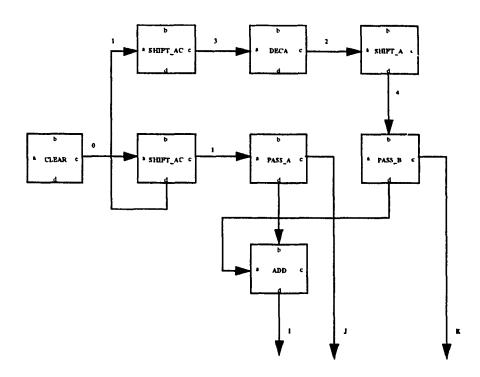

| FIGURE 15. | A FOR Loop implementation                                    |     |

| FIGURE 16. | Deadlock Synchronization                                     | 49  |

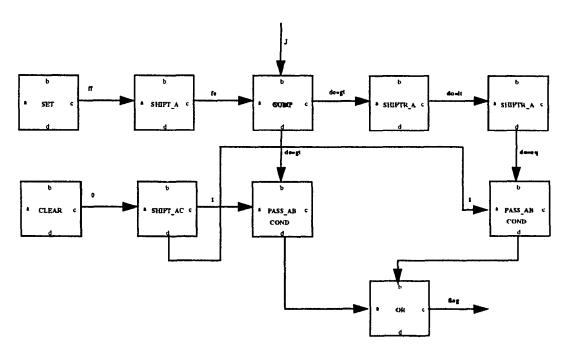

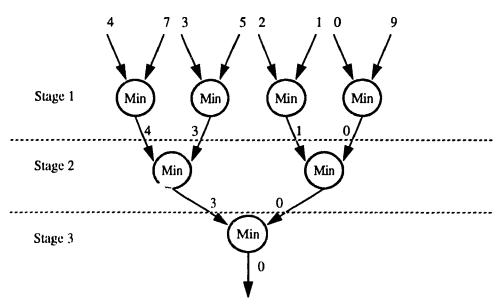

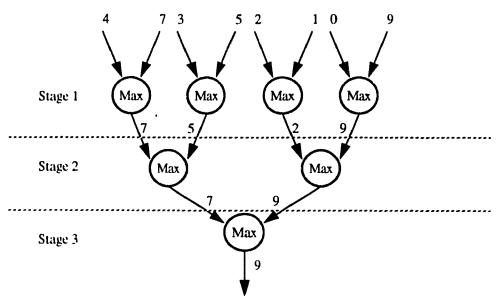

| FIGURE 17. | A Max Algorithmic Unit Implementation                        | 5(  |

| FIGURE 18. | A Min Algorithm Implementation                               | 51  |

| FIGURE 19. | A Max Algorithm Implementation                               | 51  |

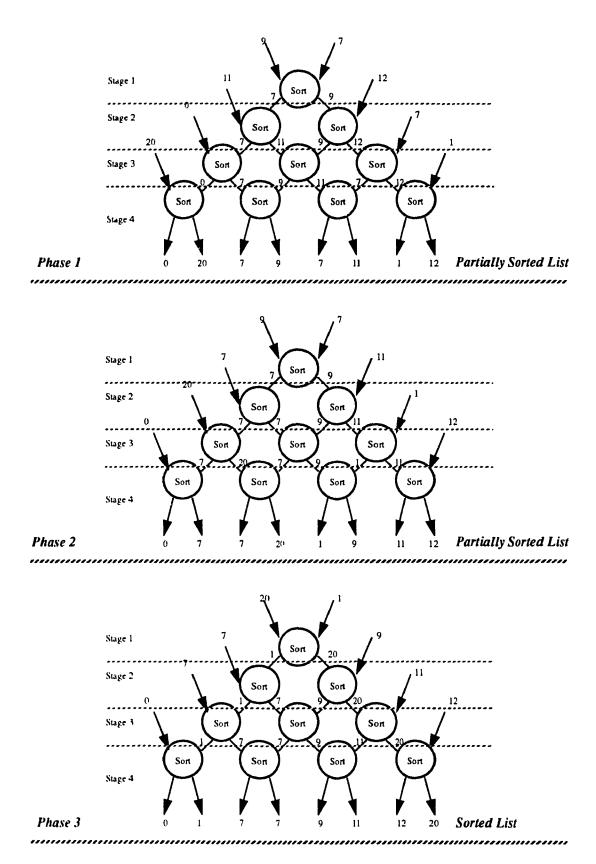

| FIGURE 20. | A Descending Sort Algorithmic Unit Implementation            | 52  |

| FIGURE 21. | An Ascending Sort Algorithm Implementation                   | 53  |

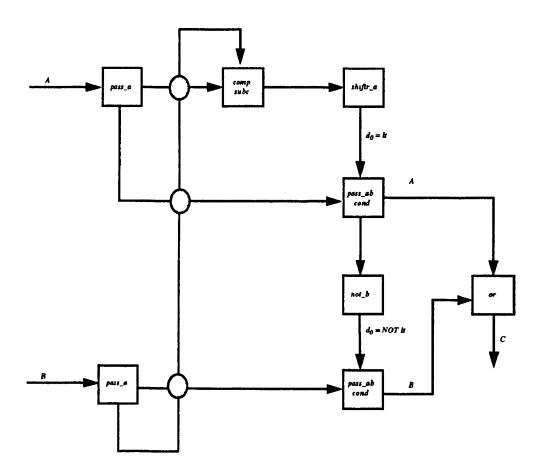

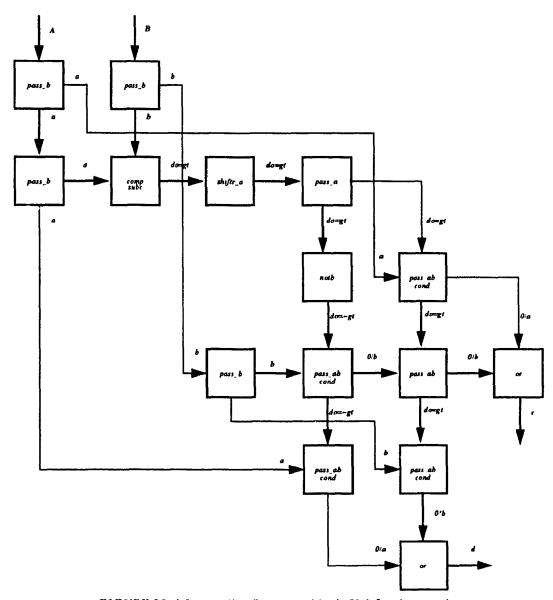

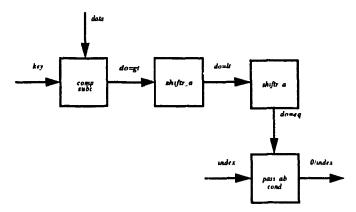

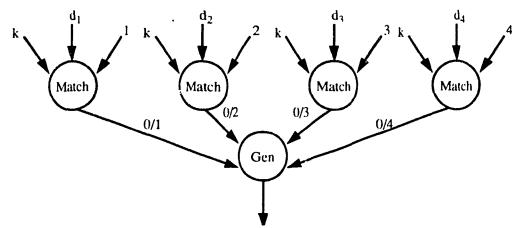

| FIGURE 22. | A Match Algorithmic Unit                                     | 54  |

| FIGURE 23. | A Match Algorithm Implementation                             | 54  |

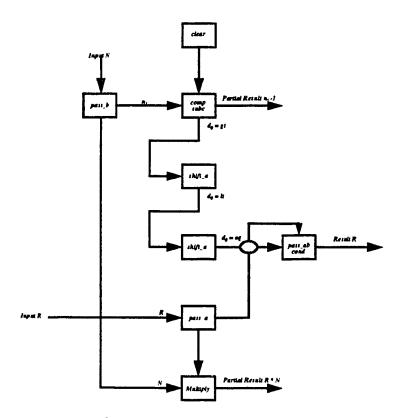

| FIGURE 24. | A Partial Factorial Program                                  | 55  |

| FIGURE 25. | The Processing Element Block Diagram                         | 57  |

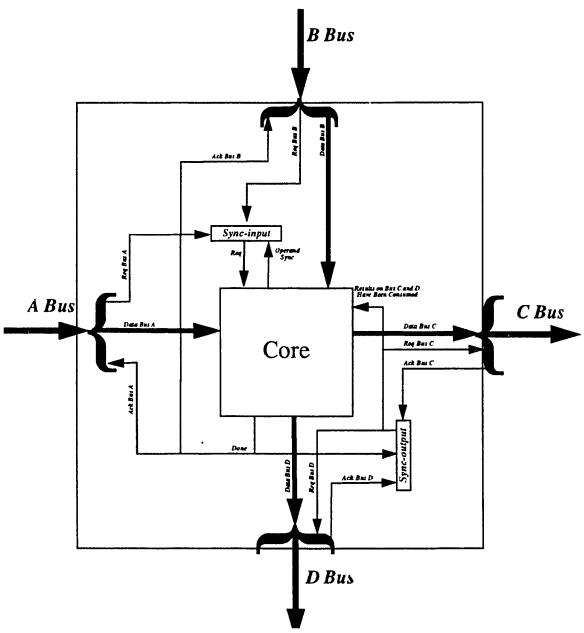

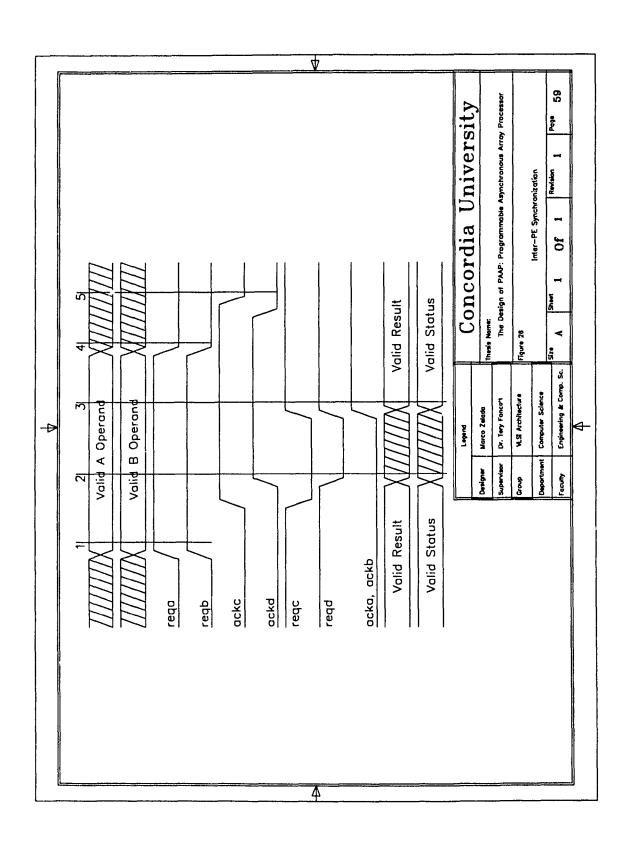

| FIGURE 26. | Inter-PE Synchronization                                     | 59  |

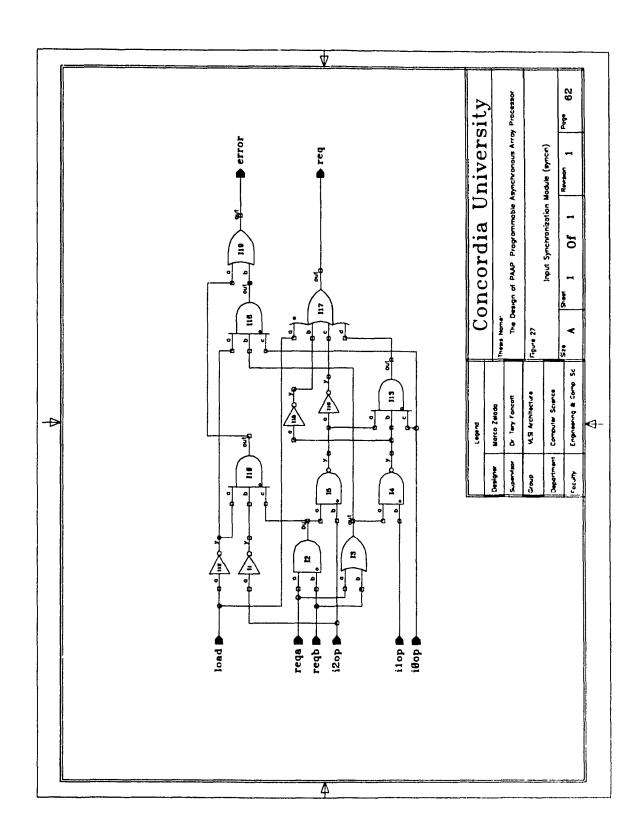

| FIGURE 27. | Input Synchronization Module Schematic Diagram               | 62  |

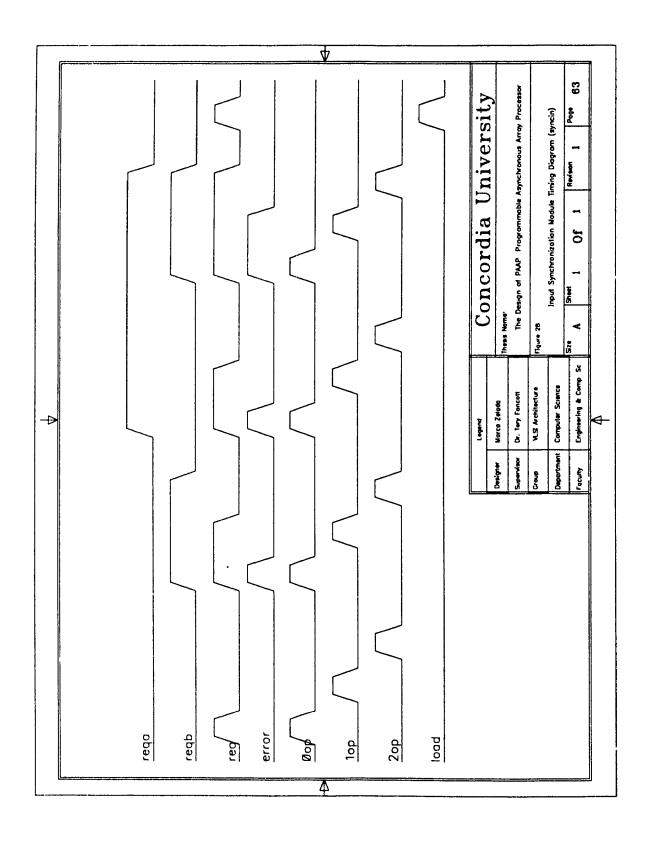

| FIGURE 28. | Input Synchronization Module Timing Diagram                  | 63  |

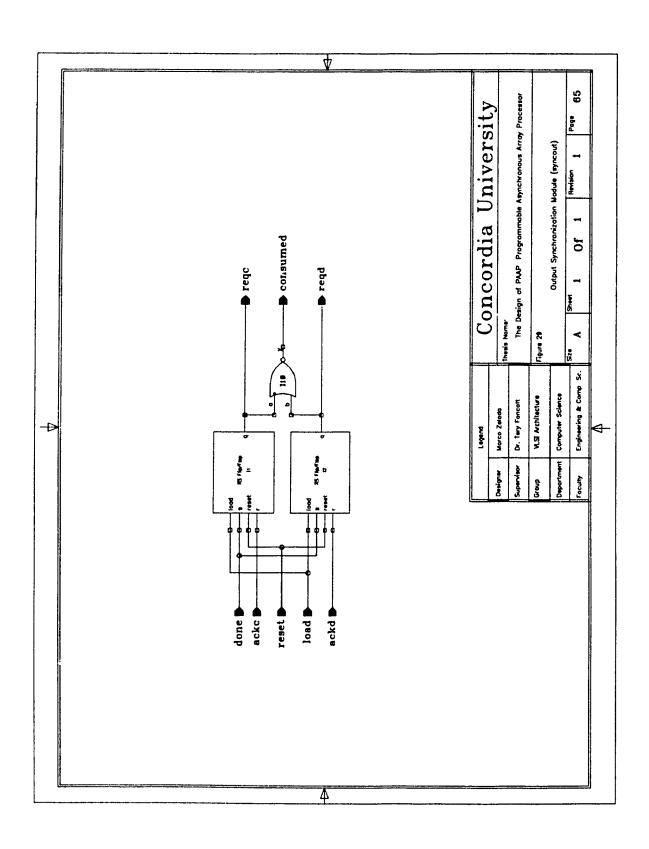

| FIGURE 29. | Output Synchronization Schematic Diagram                     | 6   |

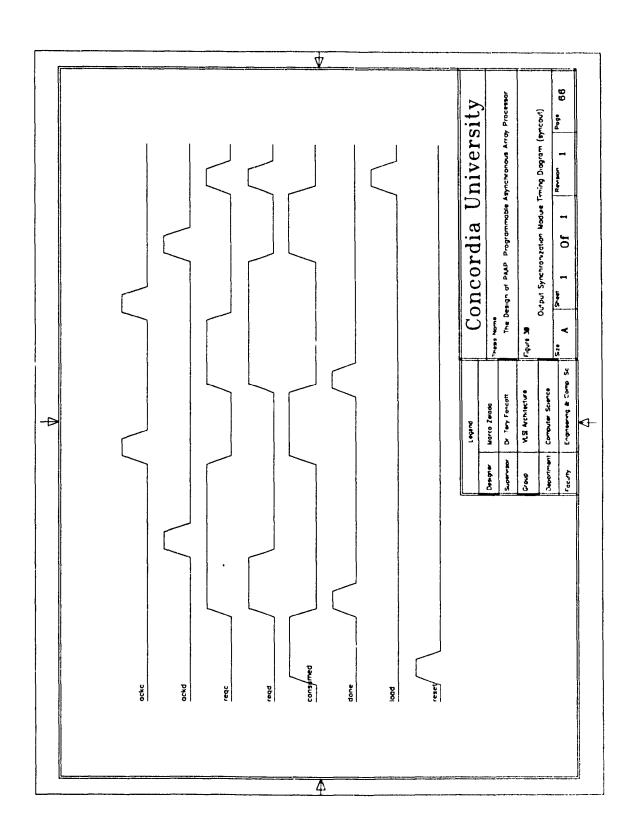

| FIGURE 30. | Output Synchronization Timing Diagram                        | 60  |

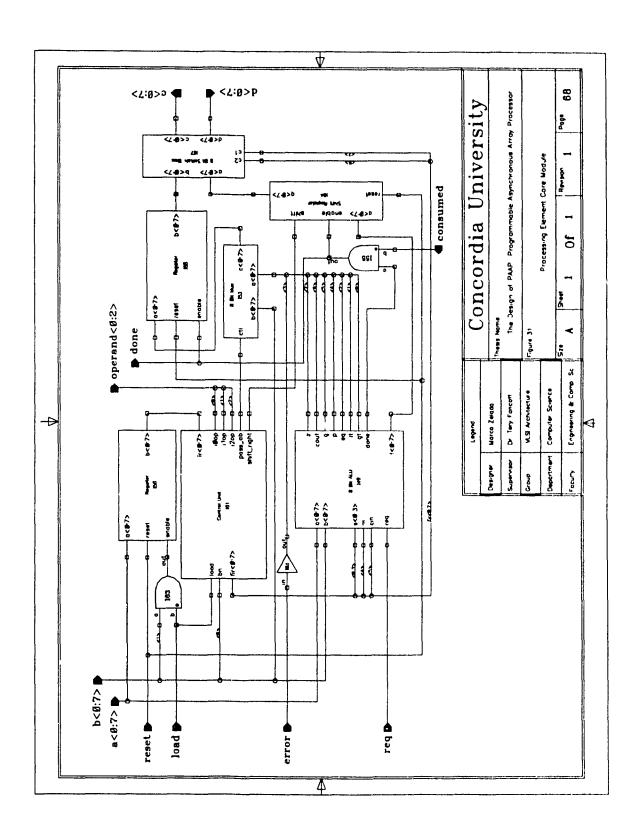

| FIGURE 31. | PE Core Schematic Diagram                                    | 68  |

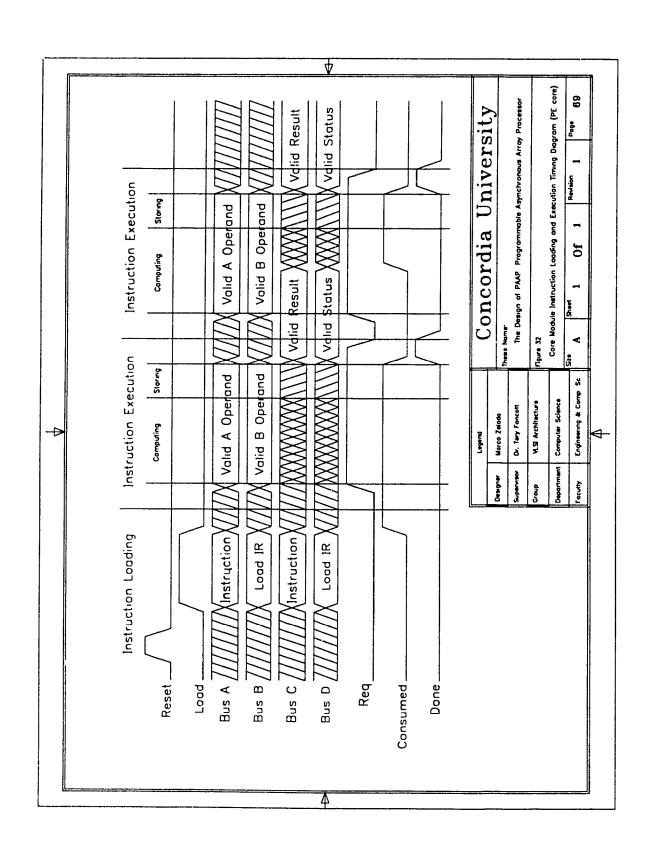

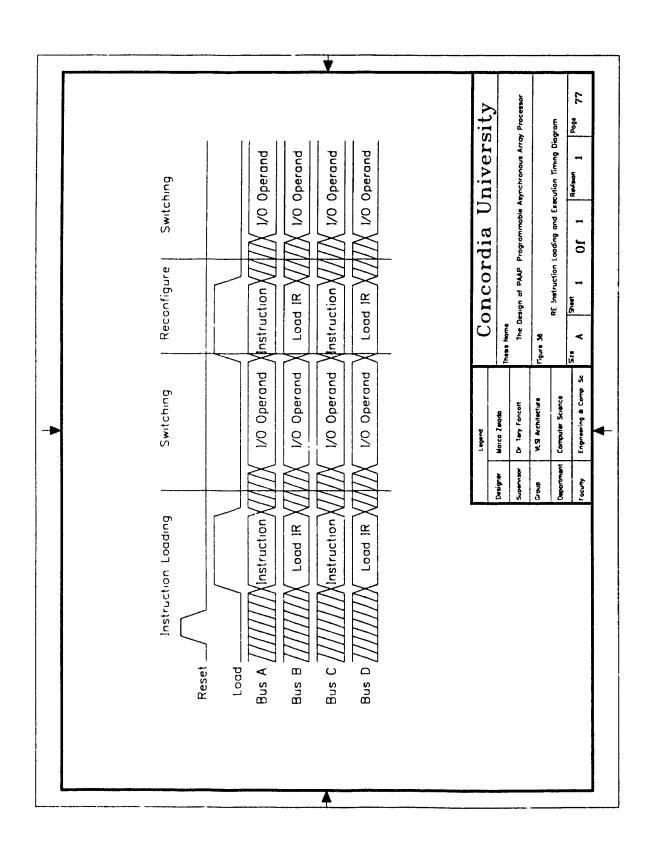

| FIGURE 32. | PE Core Instruction Loading and Execution Timing Diagram     | 69  |

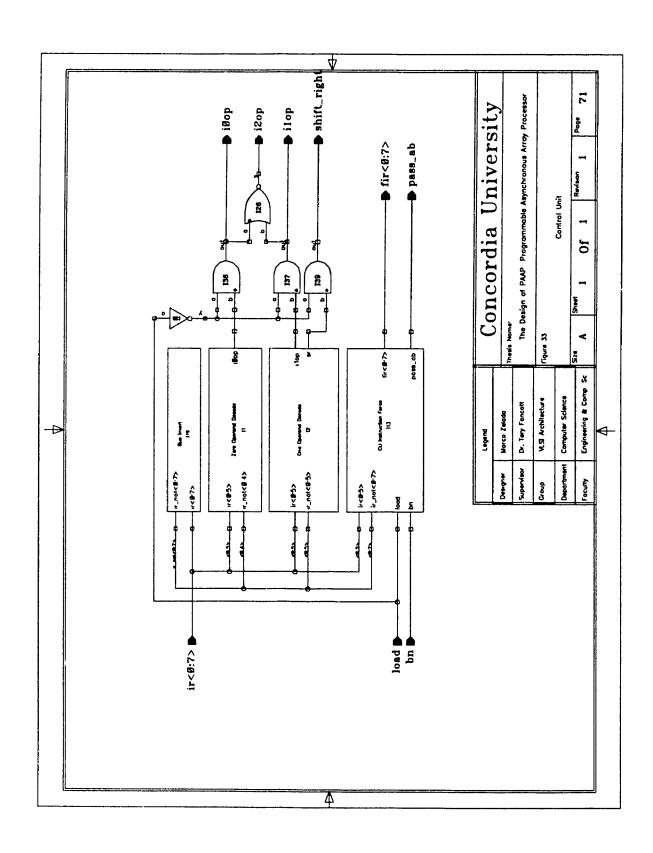

| FIGURE 33. | Control Unit Schematic Diagram                               |     |

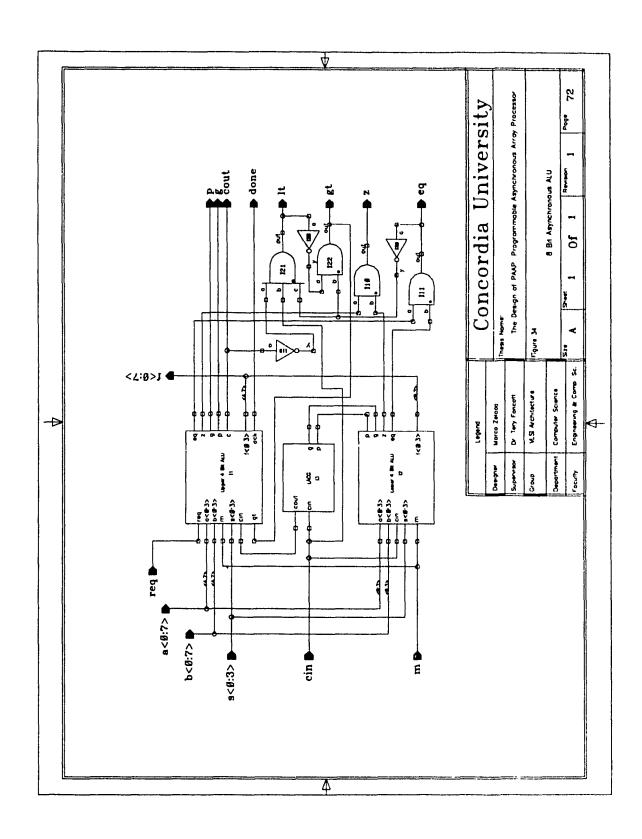

| FIGURE 34. | ALU Schematic Diagram                                        | 72  |

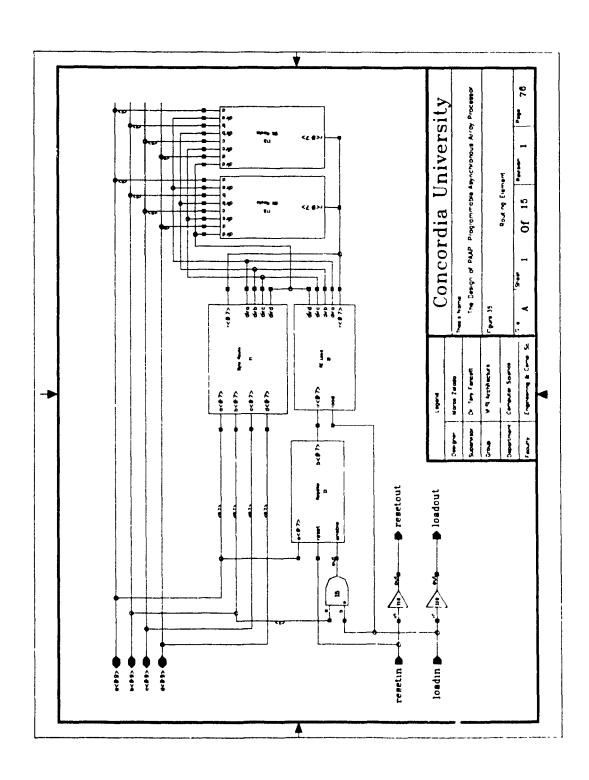

| FIGURE 35. | RE Schematic Diagram                                         | 70  |

| FIGURE 36. | RE Instruction Loading and Execution Timing Diagram          | 7   |

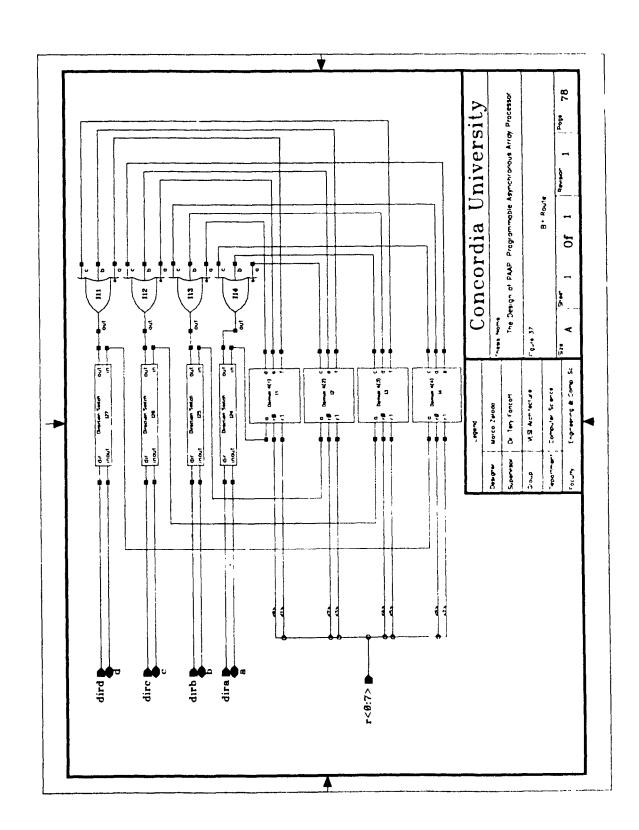

| FIGURE 37. | Bit-route Schematic Diagram                                  | 7   |

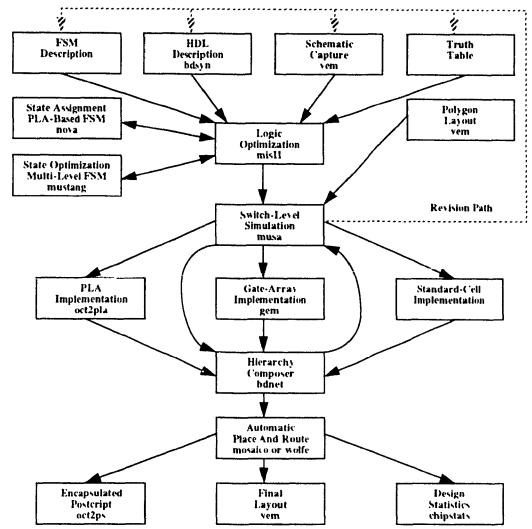

| FIGURE 38. | The Oct Tool Set Flow Chart                                  | 80  |

#### Chapter 1 Introduction

The speed and power of computers is growing at a rate unimaginable a decade ago. Many factors have contributed to this growth, such as improved IC production techniques and architectural innovations. The interaction between computer architecture and IC technology is complex and bidirectional. The characteristics of various IC implementations affect decisions architects make by influencing performance, cost and other attributes. At the same time computer architecture developments impact the viability of IC technologies by emphasizing different technology characteristics such as density, power and speed (see figure 1) [HennessyJ91].

FIGURE 1. Architecture and IC Performance Growth 1

This growth is also fueled by increased requirements placed on the hardware by new software packages and by intense commercial competition, which forces IC manufacturers to continuously improve their products. The coming of age of standards in operating systems, communications, and software interfaces has thrown the market open to a broad spectrum of manufacturers who can concentuate on specific aspects of the industry without having to cope with all facets involved in producing an integrated hardware/software system. Examples of such industry specialized products are: microprocessors (Intel, Motorola), computers (IBM, Apple), CAD tools (Cadence, Mentor), etc. Nevertheless, such high growth rate has brought the industry close to the physical barriers inherent in any given semiconductor material, such as minimum feature size and maximum speed [RettbergR90][PeaseD91].

<sup>1</sup> Source Hennessy J. L. and Joupt N.P., "Computer Technology and Architecture: An Evolving Interaction", IEEE Computer Vol. 24, No. 9, pp. 18-28, 1991

#### 1.1 The Motivation of This Research

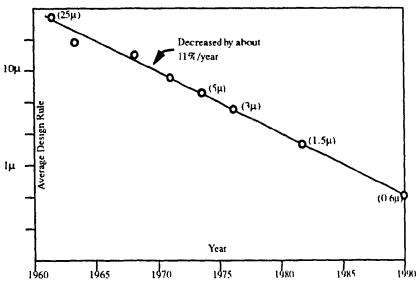

As demands emerge for greater computer processing speeds and capabilities, traditional sequential processors have begun to reach their performance upper bounds. Advanced IC fabrication technology improvements have accelerated this computer revolution by constantly shrinking device sizes (see figure 2) [VoltmerF85].

FIGURE 2. Design Rule Shrink Trend 2

The major benefit of scaling down feature sizes is the ability to increase the number of devices that can be integrated onto a single IC without changing the power supply requirements. This has lead to exponential improvements in IC complexity, which translates into increased performance and cost per function. The average die size has steadily increased despite the impact of periodic feature size reductions, (see table 1). The feature size prediction for the end of this century in table 1 is based on the current research patterns and published papers from places like IBM and AT&T Research Labs. The literature reports experimental devices made under very controlled conditions where they measure the feature size of working devices in terms of the number of aligned molecules [WeberS88]. However, this improvement trend cannot continue for much longer because current IC processing technologies are approaching the physical limits below which silicon products become unreliable. The current generation of processors are being manufactured at around 0.8 micron feature sizes, and feature sizes of usable commercial devices below 0.1 microns are expected before the end of the century [SantoB88] [SavariaY(a)86] [SavariaY(b)86].

<sup>2</sup> Source Volumer F. W., and Jones N. W., "Factors Contributing to Increased VLSI Density", VLSI Handbook, Chapter 1, Figure 3, Flonda Academic Press, p. 4, 1985.

TABLE 1. Feature Size Shrink Trend 3

| Decade | Chip Size    | Feature Size | Transistors Per IC |

|--------|--------------|--------------|--------------------|

| 1960   | 1 x 1 mm     | 30.0 Microns | 20                 |

| 1970   | 2.5 x 2.5 mm | 10.0 Microns | 1250               |

| 1980   | 6 x 6 mm     | 3.0 Microns  | 80,000             |

| 1990   | 12 x 12 mm   | 0.8 Microns  | 1,500,000          |

| 2000   | 25 x 25 mm   | 0.1 Microns  | 10,000,000         |

Device feature size reduction alone will not guarantee continued performance improvements and thus other avenues must be explored. Parallel processing is the obvious choice for continued performance improvements beyond the current sequential architectures and physical limits of the known semiconductor materials.

A typical example of the order of magnitude improved performance attainable by parallelizing sequential algorithms can be found in general problem-solving techniques such as state-space search, which are widely used in AI and VLSI CAD applications. Its sequential implementation is computationally intensive; yet, it experiences an almost linear speedup as the number of parallel processors increases. This performance increase trend continues even with a very large number of parallel processors. The literature shows that one of the best ways to improve performance is to adopt parallel processing techniques over their equivalent sequential ones (see table 2) [GottliebA82] [KumarV90] [KumarV87] [NagashwaraV87] [ArvindamS90].

TABLE 2. Parallel vs. Sequential Computation 45

| Algorithm                     | Parallel Time | Sequential Time |  |

|-------------------------------|---------------|-----------------|--|

| Permutations of N objects     | O(logN)       | O(N)            |  |

| Partial sums of N elements    | O(logN)       | O(N)            |  |

| Merging 2 lists of N elements | O(logN)       | O(N)            |  |

| Sorting N elements            | $O(\log^2 N)$ | O(NlogN)        |  |

| FFT                           | O(10gN)       | O(NlogN)        |  |

<sup>3</sup> Source Forester T, "The Microelectronics Revolution The Complete Guide to the New Technology and Its Impact on Society", Cambridge MA: The MIT Press, 1989

<sup>4</sup> Source Gotheb A and Schwartz J.T., "Networks and Algorithms for Very-Large-Scale Parallel Computation", IEEE, Computer, Vol. 15, No. 1, pp. 27-34, Jan 1982

<sup>3.</sup> This table assumes that there is an infinite number of processors to implement the algorithm.

#### 1.2 Thesis Introduction

Architectural innovation is the path to pursue in order to ensure rapid and continued growth. In the short term the easiest and most accessible route is a superscalar architecture which analyses instruction streams and allocates processing units according to a special algorithm which ensures maximum instruction overlap. Alternatively, multiple computer architectures can be used to distribute the task to particular server units; however, architectures must ultimately move to massive parallelism to afford continued growth and computing power [Suaya90].

This thesis explores some new architectural features appropriate to massively parallel architectures, and illustrates these features through a model processor array design, which we term the Programmable Asynchronous Array Processor (PAAP).

PAAP is but a small element of an overall massively parallel architecture design, and consequently many issues peripheral to the array design remain simply defined, but not illustrated. The full design of a computer is beyond the scope of this thesis; however, array programmability aspects are explored and demostrated by simulation. Relevant circuit elements designed using both university and commercial level tools, such as the Oct Set of Tools from UC Berkeley and the Cadence Set of tools from Cadence Design Systems, are illustrated.

Advances in IC fabrication technology have made it possible for VLSI architectures such as the PAAP array design to be feasible. We can conceive of large numbers of PEs and REs (sub-array units) being built as packaged ICs with current technology. These packaged sub-array units could then be used to build larger arrays on standard extension cards that may be attached as peripheral co-processor cards to standard compute engine hosts.

The thesis is organized into seven chapters. In Chapter 1 we find a general thesis introduction that briefly describes the work and motivation. In Chapter 2 we compiled the relevant theoretical background into a focused set of reference information points that span parallel architectures and design, current architecture implementations, an MIMD overview, systolic and wavefront arrays, asynchronous concepts, and wafer scale integration. Chapter 3 describes the minimum computational environment that the PAAP array requires, as well as its functional operation. Chapter 4 provides a programming example and looks at possible related software issues. Chapter 5 describes the PAAP PE and RE design, schematic level and timing diagrams are included for the most important subcomponents. Chapter 6 discusses practical issues such as the design environment used, and overviews simulation results. Chapter 7 is the conclusion, which summarizes the work and outlines design shortcomings and possible future enhancements.

#### Chapter 2 Parallel Architecture Concepts

The most relevant parallel processing concepts to this thesis are presented in this chapter. First we look at the original computer architecture taxonomy by Flynn and an updated taxonomy by Duncan. The reader may then be able to properly place the PAAP array design within the existing parallel architecture taxonomies. We then examine the architectural issues faced in designing a massively parallel architecture and examine currently available implementations. The reader should have an appreciation for the design choices taken in the PAAP array design. Last, we overview the main characteristics of MIMD architectures as well as wavefront arrays and asynchronous design techniques. This will give the reader an understanding of the PAAP array as a reconfigurable-programmable-MIMD wavefront array.

#### 2.1 Parallel Processing

The decades of the 80s and early 90s have seen the introduction of a wide variety of commercial parallel architectures that complement and extend the major approaches to parallel processing developed in the 60s and 70s. Their design motivation and market areas cover a broad spectrum: (a) Transaction processing systems, such as parallel UNIX systems for data processing applications (i.e. The Balance from SEQUENT), (b) Numeric supercomputers such as Hypercube systems for scientific and engineering applications (i.e. The iPSC from INTEL), (c) VLSI architectures, such as parallel microcomputers for exploiting very large scales of integration (i.e. The transputer from INMOS), and (d) Neurocomputers, such as the Connectionist computers for general purpose pattern matching applications (i.e. The Connection Machine (CM) from THINKING MACHINES) [TreleavenP88].

Massive parallel processing can be thought of as a problem of event scheduling and resource management. These resources can be memory or processing elements as well as communication channels, and the events refer to computation requests. In order for any real computation to take place, in a parallel system, operations have to be properly scheduled on the available resources. Previously it was believed that processing and switching elements were more important and thus system performance was based on measuring how well such units performed with no regard for how they were interconnected. At the present time it is believed that interconnections are the ultimate performance limit on any type of architecture.

Minimizing the cost of Inter-PE communication and at the same time providing a flexible enough communication scheme is always desirable. Unfortunately, striking the perfect balance between low communication overhead and flexibility is not a simple task. If the algorithm being executed does not map the physical connectivity of the machine well, then we may find an excessive amount of idle processors due to communication overhead. The ultimate communication scheme would adapt its connectivity configuration to the algorithm being performed [KuckD86].

Parallel architectures have problems which have prevented them from being widely accepted. [SakaiS90] makes reference to at least 5 different areas which need great improvements before general-purpose parallel computers can achieve significant higher performance:

- · Extracting the maximum parallelism from a user program automatically,

- · Minimizing synchronization overhead,

- · Minimizing communication overhead,

- · Obtaining the optimal load balancing, and

- · Ensuring reliability.

Many proposed parallel architectures have addressed some or all of these issues, but there is still much more work ahead because users still perceive parallel computers as being not general purpose. Another problem is that they are difficult to program because either their programming environments still use the sequential model of computation adapted for the target parallel architecture, or one must learn the underlying architecture in great detail before attempting to write any useful programs. Both approaches are clumsy and time consuming, yet, attempts are underway to correct these problems by the development of object-oriented languages and of sophisticated software development environments that automatically extract the parallelism embedded in user programs and optimize such programs for the target architecture.

However, general trends of research are looking forward to bringing general purpose parallel processing and many commercially available parallel computers are beginning to show promising results in their software environment implementations, in the adoption of standards on such crucial system components as the Operating System and User Interface. Other factors influencing the proliferation of parallel processing technology are the advances in VLSI architecture and the emergence of new parallel architectures [DenningP86] [KatevenisM84] [MelvinS87].

#### 2.2 Parallel Architecture Taxonomies

In his classic paper, which still retains its validity, Flynn proposed a taxonomy for parallel computers which defines four classes of Von Neumann-based computers depending on the multiplicity of the instruction and data streams [FlynnM56]:

Single Instruction Single Data (SISD) corresponds to the sequential Von Neumann machine we all know, which can only execute one instruction and work on one data item at a time. SISD computers are traditionally Von Neumann uniprocessors, but by a clever extension of the concept of horizontal microprogramming it is possible to connect multiple uniprocessors and control them simultaneously. The approach is called Very Long Instruction Word (VLIW). The idea is that if a 32-bit uniprocessor can perform the required computation, by adding the proper control structures, one may be able to extend the 32-bit to 64-bit or 128-bit word size. Operands are thus properly partitioned to the appropriate section to work on their own section of the word, and at the end, their results are collected and the result word is assembled from the partial word results generated by each of the processors. The main difference between VLIW and MIMD machines is in the very long instructions that control the machine, using words of up to thousands of bits long [FisherJ84].

- Single Instruction Multiple Data (SIMD) corresponds to the parallel execution of a single instruction. This types of architectures include vector-arrays, array processors, the CM, etc.

- SIMD machines are usually composed of a single Control Unit (CU) which fetches and decodes instructions, and some N number of interconnected Processing Elements (PE). Once the instruction is on line to the CU, it is either executed by the CU (a jump instruction) or it is broadcast to the PE pool for execution. The PEs operate synchronously, but each has its own memory which may contain different data items and individual partial results. SIMD architectures can come in different arrangements: vector processors, array processors, associative processors. This classification is done based on the CU's complexity, the processing power and addressing method of each PE, and the interconnection facilities between PEs. In array processors the CU has limited capabilities and its PEs communicate through a connection networ<sup>1</sup>. Array processors are thus well-suited for grid problems and in some cases vector processing. Other implementations make the CU a full-size computer which communicates with PEs via message-passing schemes [HordR(a)90].

- Multiple Instruction Single Data (MISD) corresponds to pipelined processors that allow for

consecutive instructions of a program to be in different stages of execution by advancing

through pipelines of functional units in a staggered fashion, one function at a time. Examples

of this architecture include machines based in high-end processors such as the 80486 or the

68040.

MISD-type architectures utilize consecutive program execution modules. At any given time, a different part of an instruction is executing in stages and it advances through the pipelines of functional units in a staggered fashion. The pipelined processor is an MISD processor which partitions each instruction into simpler computational steps that can be executed independently by functional units. Each one of these computational units is called a pipeline segment.

Multiple Instruction Multiple Data (MIMD) could be better described as a number of SISD

configured to communicate among themselves in the course of a program.

In MIMD architectures, several processors operate in parallel in an asynchronous manner and share access to a common memory module. Each processor is capable of running its own instruction, which allows for a problem to be subdivided and mapped onto an array of MIMD-type PEs. Data also flows across PEs as initial data and partial or fully computed results. Data can be used to synchronize the machine and some PEs may have to wait for other PEs to generate the proper results [SutherlandJ89].

In 1990, Duncan updated Flynn's taxonomy by adding architectures that can not be easily accommodated within Flynn's taxonomy. For example, pipelined vector processors exhibit substantial concurrent arithmetic execution and can work on hundreds of vectors in parallel. However, they lack the single instruction execution property found in SIMD architectures and do not classify as MIMD because their PEs are not asynchronously autonomous. Duncan's taxonomy also excludes architectures that only provide low-level parallel mechanisms such as instruction pipelining, multiple CPU functional units, and separate CPU and I/O processors. The reasoning behind this exclusion is that even though they contribute to an increase in performance they do not make the architecture parallel. The complete taxonomy can be summarized as follows [DuncanR90]:

- Synchronous: Concurrent operations are coordinated in lockstep via global clocks, central

control units, or vector unit controllers.

- Pipelined vector processors: Characterized by multiple, pipelined functional units, which implement the needed operations for both vector and scalar operands, and which can work concurrently.

- SIMD: As defined in Flynn's taxonomy.

- Processor arrays: Implemented as an array of special purpose processors with local connectivity between them and the local memory associated with each processor.

- Associative memory: They use a special comparison logic to access and store data in parallel according to its contents.

- Systolic arrays: Pipelined multiprocessors in which data is pulsed in a rhythmic fashion from memory and through a network of processors before returning to memory.

- MIMD: As defined in Flynn's taxonomy.

- Distributed memory: The nodes share data by explicitly passing messages via the interconnection network which can be one of the following topologies: ring, mesh, tree, hypercube, reconfigurable.

- Shared memory: Interprocess coordination is done via a global shared memory that each processor can access via: bus, crossbar, multistage networks.

- MIMD paradigms: These architectures are considered hybrids which are based on MIMD princ'oles such as asynchronous operation and multiple operation and data streams; however, they also exhibit distinctive organizing principles which are attributed to other architecture types.

- MIMD/SIMD: Selected parts of the MIMD machine can be controlled in an SIMD fashion.

- Dataflow: Instructions are executed as soon as all of the needed operands are available.

- Reduction: Instructions are executed when its results are required as operands for another instruction already enabled for execution.

- Wavefront arrays: They combine the systolic data pipelining concept with an asynchronous dataflow approach.

#### 2.3 Architectural Issues

Parallel architectures can be classified by their granularity because it is the size of work units that are allocated to a single processor. The main subdivisions are coarse and fine grain. Coarse-grain parallel architectures can be distinguished by the low number of complex processors. On the other hand, fine-grain parallel architectures utilize a large number of very simple processors. There are also some researchers that would further divide parallel architectures by grain and define medium-grain architectures as a compromise between coarse and fine grain architectures. Yet in a complex system, the actual delivered performance is algorithmically-specific and not architecturally bound. This is related to how well a particular architecture is suited for the particular problem being processed [MohanJ83].

Fine-grain parallelism has the potential of being faster, provided that the algorithm maps very well into the mesh of processors present in the machine's architecture.

Coarse architectures are better understood because of their similarity to sequential processing. This influences the state of software technology that is available for such parallel systems. It may also explain why it is not uncommon to find parallelizing compilers that retarget languages such as FORTRAN, C, PASCAL, etc., to coarse-grain computers such as the Encore Multimax, and no parallelizing software for fine-grain computers such as the CM [KruatrachueB88].

Even though there is an attempt by some portions of the parallel architecture research community to make their designs commercially acceptable via their ease of programming, most of the research effort has concentrated on speeding up solutions to specific problems or classes of problems. As a result, the large number of proposed parallel processing architectures exhibit such great diversity of concept combinations.

The most important issues to consider while designing a parallel architecture are [BasuA84]:

- Loosely vs. tightly coupled systems: The distinction here is based on how the memory system

is structured, whether each processor has access to its own local memory (loosely) or the

memory system is a global shared memory model (tightly).

- Parallel vs. distributed: The divergence point here is the way the computation gets done, whether the computing elements are concentrated in one place and work in parallel with very little communication overhead (parallel), or scattered around and have to incur a large communication overhead (distributed).

- Shared memory vs. message passing: This division follows from the memory system structure.

Depending on whether the system is tightly or loosely coupled, processor communication can take place via shared-memory variables or message-passing.

- Synchronous vs. asynchronous: The distinction here is based on how the PEs synchronize with

each other. Synchronous systems utilize a general system-wide clocking scheme.

Asynchronous systems do not have a global clocking scheme, they utilize local clocking

schemes that ensure timing error-free computation.

- SIMD vs. MIMD: The main distinction here is the number of instructions that can be executed in parallel by the system.

- Special vs. general purpose: This division is done on the basis of how flexible the PE interconnection network is and the generality of the computation that each PE can perform.

Some proposed designs such as systolic arrays provide static PE interconnections, others provide programmable PE interconnections. Most PEs have some level of programmability, but the issue is how general purpose such basic instructions are.

#### 2.4 Parallel Processing Implementations

The advent of the supercomputer term occurred in the 1975 time frame when it was applied to the CDC-7600, the Illiac-IV and other high performance machines of the day. The term became firmly established with the introduction of the CRAY-1. This section briefly covers a few interesting parallel computers that in most cases classify as today's supercomputers.

We start with the Illiac-IV which was the first large scale array computer that incorporated high levels of parallelism and pipelining. Operational in 1975, it consisted of a single CU that broadcast instructions to its 64 PEs. Each PE has 2K 64-bit words of working memory and the main memory is implemented on disk with a capacity of 8 million words at a transfer rate of up to 500 megabits per second.

The CU has access to all of the core memory with a cycle time of 60ns. The CU fetches and decodes all instructions; after decoding, some instructions are broadcast to the PEs for execution, while some other instructions are executed by the CU. There are three data paths available for communication among PEs and between PEs and the CU.

- The CU can access all of the core memory so it can load or store data on any one of the PE's local memory.

- The CU can communicate with all PEs by broadcasting the same word to all PEs simultaneously.

- The PEs can communicate with each other via the ROUTE instruction which transfers data from a source PE to a destination PE.

The Illiac-IV was capable of performing 300 MIPS in 32-bit mode, and even though it was built using electronic components from the late 60s, for certain important classes of applications it was the fastest computer of its time [HordR(b)90].

A more recent computer, the CM, was first introduced in 1986. The 1000 MIPS CM-1, used up to 64K 4K-bit RAM, single-bit processors. The second connection machine, the 2500 MFLOPS CM-2, was introduced in 1987. It still used up to 64K single-bit processors, but this version provided 8K-byte RAM per processor, faster clock speed, and floating point hardware support.

The CM's interprocessor communication network is called a hypercube. In this scheme there are up to 2<sup>N</sup> nodes, and each node has N directly connected nodes; the longest path between any two nodes (diameter) has at most N steps through other nodes; in the CM's diameter is 16. The heart of the system is the parallel processing unit, which consists of thousands of processors, each with thousands of memory bits which can be considered as shared memory. The processors can process data stored in their local memory, as well as form logical interprocessor connections so that data can be exchanged among processors. An important concept is that the CM implements parallel programming constructs directly in hardware. Parallel data structures are spread across the data processors with a single element stored in each processor's memory. When parallel data structures have more than 64K elements, the hardware operates in virtual processor mode, presenting the user with a large number of processors, each with a correspondingly smaller memory. Scalar data is held at the front-end processor, which also controls the overall data parallel program. Program steps that require parallel data are passed over an interface to the CM parallel processing unit, where they are broadcast for execution by all processors at once. Front-end controllers, of which there can be up to 4, provide the programming environment for the CM; they also serve as network communication gateways and for storing programs. For every group of 8K data processors there is one I/O channel. Each channel may be connected to either a high-resolution graphics display framebuffer module or one general I/O controller supporting an I/O bus to which several DataVault mass storage devices may be connected.

Data processors are implemented using four chip types. A proprietary custom chip that contains the ALU which can execute variable length operand instructions, flag bits, router interface, NEWS grid interface, I/O interface for 16 data processors, and proportionate pieces of the router and NEWS grid network controllers. The memory consists of commercial RAM chips. The floating-point accelerator consists of a custom floating-point interface chip and a floating-point execution chip; one is required for every 32 data processors.

The CM-2 parallel unit has a structured communication mechanism called the NEWS grid. In the CM-1 the grid is a fixed two-dimensional grid, but the CM-2 supports programmable grids with arbitrarily many dimensions. The NEWS grid allows processors to pass data according to a regular rectangular pattern. For example, in a two-dimensional grid each processor could receive data from its neighbor to the east thus shifting the contents of the grid one position to the left. The advantage of the NEWS grid over the router is that the routing overhead of specifying destination addresses is eliminated. This is an optional optimization that some applications can use [HordR(c)90].

One of the disadvantages of the CM is that its computation gets done in an SIMD single-bit fashion, as well as the difficulty in scaling the machine beyond 64K processors without a major redesign effort. An

interesting alternative is the 32-bit INMOS transputer, which was designed as a basic building block for processor arrays of any size. It provides a direct implementation of a message-passing loosely coupled architecture.

The transputer architecture was targeted for the efficient execution of programs written in the OCCAM parallel processing language. In OCCAM programs, the basic computational modular component is the process that communicates with other concurrent processes through channels. A transputer contains a processor that in some models includes a floating-point unit, a 4K byte memory, and 4 standard point to point communication links that allow direct connection to other transputers. Concurrency is supported by hardware support for scheduling. The design philosophy is in accordance with the RISC approach; however, repetitive operations such as multiply and block moves are implemented in microcode with hardware assistance [DeCegamaA(a)89].

Another interesting implementation is the WARP machine from CMU, which is a high-performance systolic array computer designed for computation-intensive applications. There are three major components to the system: the WARP processor array, the interface unit (IU), and the host.

The WARP array performs the computation-intensive routines such as low-level vision routines or matrix operations. The IU handles the I/O between the array and the host and can generate addresses and control signals for the WARP array. The host supplies data to and receives results from the WARP array. In addition it executes those code parts that are not mapped onto the WARP array. Each WARP ceil is implemented as a programmable horizontal micro-engine, with its own micro-sequencer and program memory for 8K instructions. The cell data path consists of a 32-bit floating-point adder, a multiplier and two local memory banks for resident and temporary data, a queue for each intercell communication channel and a register file to buffer data. All of these components are connected via a crossbar.

In a typical configuration, the WARP machine consists of a linear systolic array of 10 identical cells, each of which is a 10 MFLOPS programmable processor; thus the peak performance is 100 MFLOPS. The machine can be connected to any general purpose host machine running UNIX as an attached processor. It is then accessed via procedure calls on the host or through interactive, programmable command interpreter called the WARP shell [DeCegmaA(b)89].

It is a challenge to provide a uniform address space that implements shared memory constructs with minimum access conflicts in order to maximize performance. Considerable research has been devoted to developing interconnections schemes for array processors, which allow parallel, conflict-free memory access [BalakrishnanM88]. Contemporary shared-memory multiprocessors such as the BBN Butterfly-I

(GP1000), the Butterfly-II (TC2000), and the Sequent-Balance 21(000 have implemented some of the important concepts learned from this research.

The BBN systems are physically distributed-memory multiprocessors running a flavor of the MACH operating system that offers a logically shared virtual space to the programmer. This is made possible by a specially designed Multistage Interconnect Network (MIN) that allows any PE to access any memory module. The MIN, known as the butterfly switch, is the key component that provides the BBN systems with a scalable memory access bandwidth capable of supporting multiple memory accesses. A local memory access directly bypasses the interconnection network, but a remote reference is serviced via the network. Conflicts are resolved by dropping the conflicting requests and later retries. The GP10(0) is built using the Motorola 881(0) RISC processor [GP88] [TC89].

The Balance is a truly shared-memory multiprocessor running the Dynix operating system. The system is built around a high bandwidth bus to which all PEs, memory modules and I/O interfaces are attached. All memory references are serviced through the bus, and multiple requests are pipelined onto the bus so that it is available for reuse while a memory access request is being serviced. The processor does not hold the bus for the entire duration of the memory access cycle. Access to hardware locks is arbitrated over a separate bus [Balance84].

#### 2.5 MIMD Parallel Architecture Overview

The most common parallel processing approaches are: the Von Neumann-based, the dataflow-based, and the reduction-based.

The Von Neumann approach consists of interconnecting two or more Von Neumann-type processors in a variety of configurations. The main distinction is that processing takes place via a single thread of control. Having more than one processor means that there may be multiple threads of control, and the overall system control is a problem in this approach.

The dataflow approach executes instructions as soon as their operands are ready instead of following a thread of execution, as in the Von Neumann approach.

The reduction approach consists of performing instructions when results are needed for other calculations. Programs are viewed as nested applications and execution precedes by reducing the innermost applications, according to some semantics, until there are no further applications to reduce.

There is yet another approach called hybrid which combines the dataflow and reduction functionalities. In this approach processors will work first on the instructions that have been demanded of them if the operands for such instructions are ready. If operands are not ready then the processor will demand them from other processors and work on lower priority items. This results in a more balanced use of the resources because instructions are performed in order of importance.

One of the key elements in designing a general purpose parallel architecture is that users want to use the extra compute power but they are not interested in how such performance improvement is delivered. As a consequence, the new parallel systems must be able to appear completely transparent to the user.

MIMD architectures use a variety of interconnection mechanisms. Some use a bus structure and handle all processors and memory modules from the bus. <sup>6</sup> Data transfer operations are controlled by an I/O controller module that acts as a bus arbiter to resolve access contention problems. Due to bus conflicts, memory access cycles will be increased, which results in lower performance. A way to aid in bus contention problems is to provide the processors on the bus with some amount of cache so as to reduce their dependence on the bus for data. The only problem here is that the distributed cache subsystems have to be kept synchronized. Cache synchronization consists of the correct read/write sharing of replicated data. This implies that processors must have exclusive rights to writing shared data elements. Processors must also be able to get the latest version of a shared data item and they must be blocked from getting transitionary data elements. If the required data is available, multiple read accesses should also be allowed. Most of these implications can be implemented in software; however, there is a need for hardware support by means of flags and counters for the memory objects that are shared [BitarP86].

An alternative to the bus MIMD is the crossbar switch system interconnection, which provides the best performance of any interconnection system at the expense of complexity, size, and cost. The crosspoint switch must have major hardware capabilities such as including switching parallel transmissions and resolving multiple requests with different priorities for access to the same memory module. A representative system is the CMU C.mmp system, which has 16 processors and 16 memory modules [FullerS78].

The interconnection network of an MIMD machine can be either single-stage or multistage. The single-stage network can be viewed as an interconnected set of N input units and N output units. The allowable interconnections are determined by the way the input units are connected to the output units. There are 4 different ways to connect single-stage units: mesh, cube, shuffle-exchange, plus-minus 2<sup>1</sup>. The

<sup>6</sup> At the present time there are commercially available systems that offer this type of configuration. Vendors include Encore Computer's Multimax, Sequent Computer's Balance, Alliant Computer's FX/8, etc.

plus-minus  $2^1$  network is a superset of the mesh network because it connects any given address X to address  $X + 2^1$  and  $X - 2^1$ . A popular basic MIMD structure is the multistage interconnection network. It consists of multiple stages of intelligent switches capable of providing at least one path between any two system elements (processor, memory modules) with minimum complexity and cost. Multistage networks are built from stages of the basic single-stage networks [MapplesC85].

Processors in loosely coupled systems (LCS) communicate by exchanging messages while tightly coupled systems (TCS) have their processors communicate via shared memory variables. LCSs use local memory, and if a processor requires access to data in another processor's memory, it must request the data via a message. It is up to the message receiver to send the requested data, thus there is a large message-passing overhead involved in this data access mechanism, because data cannot be accessed deterministically due to the message passing delay. The process of getting the required data item may take any number of tries before the data is actually made available to the requesting PE. Every message generated has to travel through the communication subsystem; if such a communication scheme is not well-structured and controlled, this medium may become the system bottleneck.

TCS provide a global shared memory system which is accessible to any processor. Such a system may be organized as a single memory module that is connected to a bus-like medium with local cache modules to improve performance. Another organization may put local memory modules with its own secondary interconnection mechanism to make the memory space look like it is consolidated when in reality it is totally distributed. Each PE and its memory are located at a node. Collectively this configuration may actually form a shared memory system; thus any processor can access any other processor's memory by using the secondary communication mechanism. <sup>7</sup> From the programmer's point of view the only real difference in memory access to another processor's memory is the response time. The major advantage of communicating via shared memory is an almost unlimited buffer for asynchronous IPC. At the same time, the programming model for the machine becomes much easier and this allows higher hardware utilization. However, the overhead incurred by the secondary interconnect network can be sometimes out of reach, except for very specialized applications. Using just one interconnection network for both memory and processor communication leads to the usual access conflicts and thus performance degradation.

The basic dataflow concepts were developed in the 60s mainly by compiler experts who used dataflow graphs as tools to optimize sequential programs. A dataflow graph is a directed graph in which the nodes represent primitive functions, such as add and multiply, and the arcs represent data dependencies between

<sup>7.</sup> BBN Advanced Computers has already announced a commercial TCS computer with a butterfly interconnected memory module, which makes the memory appear as a monolitic shared memory module. This new system runs MACH 2.5, a message passing OS, and no longer requires a front end to communicate with users.

functions. In the 70s it was realized that if the dataflows were executed directly in hardware the architecture would be massively parallel. These machines are thus language-based; the architecture implements the formal behaviors of the program graph and the compiler translates the source code into the architecture's equivalent program graph. When the machine is in an execution stage, it is activated by the presence of an operand value in each operand field. The content of the execution template (instruction) defines the operation packet (result) <opcode, operand, destination>. Such an operation packet specifies one result packet with the information <value, destination> for each destination field of the template. When a result packet is delivered, the result value is placed in the operand field defined by its destination field. To this date, no commercial dataflow machine has ever been constructed. There have been several research projects, but critics argue that they will never really make it out of the laboratories because the designs have trouble dealing with large arrays and incur an excessive computational overhead. Another problem of practical importance is that debugging both the hardware and software on such machines is still not well understood [SriniV86].

#### 2.6 Systolic and Wavefront Arrays

A synchronous array of parallel processing elements under the supervision of one or more control units is called an array processor. In most known designs array processors are SIMD. In some cases all PEs will get the instruction and execute it; in other cases PEs will be selectively octivated to execute the current instruction. All PEs not selected to execute the instruction will then be inactive for this execution cycle. The array processor is usually interfaced to a host computer through the CU. In most cases the host computer is a general-purpose machine whose function is to manage the array processor resources. The array CU directly controls the execution of programs on the array and the host computer takes care of the I/O functions required to complete the task.

It is of paramount importance to be able to transfer data among memory modules after computational steps. The number of data transfer steps must be minimized by lowering the possibility of memory access conflicts. In message-passing array processors, the interconnection network is made up of interchange boxes that are capable of setting themselves up dynamically to establish a desired connection. This is done by examining message header packet field. These fields must be setup by the compiler; however, this type of machine level control may require the compiler to know detailed information about the computational and data transfers of the particular application. The application domain of array processors covers image processing computer vision, nuclear physics, structure analysis, speech, sonar, radar, seismic, weather, astronomical, medical signal processing applications, etc. [SchendelU84].

An interesting array processor is the systolic array, which consists of a set of simple processors interconnected in a regular manner to perform a simple instruction. The interconnection is usually static and the PEs are not general purpose; instead they perform hard-wired instructions geared towards a particular application. The PEs in a systolic array are typically connected in the form of a pipeline, array mesh, triangular, etc., and communication with the outside world occurs only at the array periphery. The basic principal in systolic arrays is that the standard CPU can be replaced by a systolic array. Therefore, this can increase the processing power without increasing the memory bandwidth.

A problem with systolic arrays is that cell synchronization in very large arrays requires long delays between clock signals due to clock skew problems. At the same time, the synchronization of large data transfers leads to large current surges as the array elements are simultaneously energized or change state. A simple solution to the synchronization problem is to make the arrays data-driven or asynchronous; these arrays are called wavefront arrays [KungH82].

The main difference between systolic and wavefront arrays is how their particular elements are synchronized. In a wavefront array, the information between PEs follows a simple protocol. Whenever data is available, the transmitting PE informs the receiver PE, which accepts it when it is ready. Once accepted, the receiver communicates with the sender to acknowledge that the data has been used. The scheme can be implemented by a simple handshaking circuit and ensures that computational wavefronts propagate in an orderly manner without crashing into one another. The biggest advantage over systolic arrays is that since there are no clock delays, a wavefront array is scalable, exhibiting a linear increase in performance as the array size increases.

Programming wavefront arrays involves the definition and assignment of computation to each PE. Systolic arrays require in addition scheduling computation. Fault tolerance is implied in wavefront arrays because if one PE fails, all subsequent computation that depended on the faulty PE will stop automatically. In order to perform the same type of fault tolerance, systolic arrays must make use of global error-halt signals, which is not desirable because of the added wire area. This particular feature makes wavefront arrays good candidates for Wafer Scale Integration (WSI), where one may be able to reroute around the faulty PEs.

The massive concurrency in systolic/wavefront arrays is derived from pipeline processing, parallel processing, or both. Although most of the current array processors stress only word-level pipelining, the new trend is to exploit the potential of multiple-level pipelining (i.e. at the bit-level, word-level, and array-level granularity) [KungH78].

Systolic arrays and wavefront arrays are characterized by inflexible and highly dedicated structures. Hard-wired dedicated processors offer high processing speed but suffer from long redesign time as one attempts to accommodate for new algorithmic requirements. With the advent of modern algorithm/ architecture analysis, the programmable array processors will become not only more economical but also more appealing in coping with constant changes of system specifications [KungS85].

A very desirable quality of array processors is reconfigurability. Here the term is used to mean the ability to alter the interconnection patterns between the PEs for certain intended applications such as multifunction or fault tolerance. Two types of reconfiguration strategies are applicable: Static reconfiguration is used to establish a preprocessing step wherein the network is configured prior to the initiation of the tasks, and dynamic reconfiguration is used to reconfigure the execution paths during run time. This latter capability is particularly desirable in applications where the communication patterns are non-deterministic. The choice of either static or dynamic reconfiguration is constrained by application-specific goals, such as real-time response, reliability, or both [YungH88].

[Koren188] proposes a data-driven programmable array processor, which was designed and fabricated with good results. DFG algorithm mapping techniques and performance results are also presented. Much of the other research on wavefront arrays has concentrated on the scalability and synchronization, but neglected the general purpose PE and reconfigurable connection concepts. [KungS88] presents work that suggests programmable systolic and wavefront arrays are being researched, but the inter-PE connections are still static.

#### 2.7 Asynchronous Design

Asynchronous design techniques have the advantage of being free from the lockstep constraints. At the same time they map very well the distributed computation system requirements and even provide embedded self diagnostic capabilities. Synchronous systems operate on a central clocking scheme where the clock period must be greater than the slowest combinational path possible during a clock cycle. This is in contrast to asynchronous systems, which operate at varied computational rates. Asynchronous systems synchronize their PEs by a special synchronization circuit that is local to each PE. Delay-insensitive circuits are defined as circuits that implement the synchronization function by a logical behavior which is independent of the driving module and wire delays.

The protocol definitions presented in [BrozozowskiJ89] describes a four-phase or two-phase signaling protocol used to synchronize two or more systems. In order to use such type of protocol two or more systems are connected via a synchronization channel that consists of two signals request (req) and acknowledge (ack). The end of the channel that initiates the synchronization is called active and the other

end is called passive. The four-phase protocol at the active end is as shown in eq 1 and the one at the passive end is shown in eq 2:

•

$$\underline{req}^+$$

;  $\underline{ack}^+$ ;  $\underline{req}^-$ ;  $\underline{ack}^-$  (eq 2)

These two equations describe the complete four-phase signal protocol, which is sometimes called the return-to-zero protocol. Note that the last two signal representations in each signal sequence are bringing the req and ack signals back to zero after the computation has taken place. In the two-phase protocol, the interface circuits skip the return-to-zero phase (the underlined signal identifies a wait)

Asynchronous circuit design has a number of problems which must be properly addressed. One condition that may arise in delay insensitive circuits is transmission interference. This occurs when the active end of the circuit places two conflicting signal levels on its channel. For example a req<sup>+</sup> followed shortly by a req<sup>-</sup>, the passive end of the circuit would get confused and malfunction because of unstable synchronization signal values.

Another problem is signal ordering. Modules must be capable of receiving their synchronizing signals in any particular order, proper computation must not be tied to signals arriving only in a specific order. This is due to possible transitional delays induced on signal lines. For example, the passive end expects its synchronization to be done by signal a<sup>+</sup> followed by signal b<sup>+</sup> and both signals are properly generated by the active end. Yet, due to extra delays on the wire the signal order gets reversed. The result would be that the passive end would not work properly. If signal sequencing must be used, then all possible signal order combinations must be allowed.

A synchronization problem may also arise if the active end sends inputs to a passive end that is not ready to utilize them. If the previous inputs were not properly latched, then one computation step will interfere with the next computation step by contaminating the next step's input data. This problem is called computational interference because there is a mixing of current and previous inputs. The way to overcome this problem is to have the inputs latched by a signal sequence that implies that the current computation is finished and that there are more inputs to be latched, much like the protocol shown in equation 2 [GopalakrishnanG90].

<sup>8.</sup> The active side sets the req signal high, then it waits for the passive side to make the ack signal have a low to high transition. Once the ack signal has been received by the active side it sets the req signal low and waits until the passive side makes the ack signal have a high to low transition.

<sup>9</sup> The passive side waits for the active side to make the req signal have a low to high transition. Once the req signal has been received by the passive side it sets the ack signal high, then it waits for the active side to make the req signal have a high to low transition. Once the req signal has been reset by the active side the passive side sets the ack low.

#### 2.8 The CHiP Architecture

The CHiP architecture is of particular importance to this thesis due to its relevance. We refer back to this architecture in later chapters as we describe our work. Some of the PAAP architectural features are based on concepts introduced by the CHiP architecture. Only the most important architectural highlights are included here, for a more complete description refer to [SnyderL82].

The CHiP is a loosely coupled MIMD architecture composed of a collection of homogeneous PEs placed at regular intervals in a two-dimensional lattice of programmable switches. Each PE is capable of performing floating point operations, and has its own local memory bank for programs and data. There is no concept of a global memory, and access to secondary storage is accomplished via the perimeter of the lattice. Switches are used to connect PEs in different ways, each switch has enough memory to store several different pre-loaded configurations such as binary-tree, hypercube, mesh, etc.

Large computational problems are implemented on the CHiP by decomposition into a sequence of parallel algorithms called phases. Each phase is described by a graph, which is directly implemented on the computer by programming the switches; the processes are implemented by writing sequential programs for each PE. The ability to configure the parallel machine dynamically to match the algorithm topology enables this type of computer to be a universal parallel computer [SnyderL81] [KungH82].

The CHiP approach to general purpose MIMD computation was shown to be feasible. The main idea behind it was that at different times during the execution of a parallel algorithm, processors may need to communicate in a variety of ways. For example, during one step a tree configuration may be needed to sum a set of numbers, in another step a rectangular mesh may be required to execute a systolic-like operation. [GannonD86] shows how the SIMPLE computation algorithm, which can greatly profit from the flexible routing mechanism provided, can be mapped onto the CHiP architecture. <sup>10</sup>

The CHiP's switch provides a set of predefined routing configurations. This feature turns into a restriction when a new or partial switch configuration that is not in the predefined routing set is desired.

Each CHiP PE implements a loosely coupled memory model because it has access to its own local memory. Data and programs are first loaded into the local PE memory and fetched as they are needed. This implies that the PEs may work independent of one another, but memory access cycles have to be synchronized, which limits the design's scalability. At the same time, no provisions are made for fault tolerance, and its implementation would require extra circuitry.

-

<sup>10</sup> The SIMPL1 algorithm simulates the flow of a pressurized liquid as it moves inside a sphenical shell.

#### Chapter 3 PAAP Architecture Overview

The PAAP array proposes a methodology for mapping high-level computation into hardware structures. This feature is shared with systolic and wavefront arrays; however, the PAAP architecture differs from standard systolic or wavefront arrays in that its PEs can be dynamically programmed and interconnected via programmable REs. In contrast, systolic and wavefront arrays have static interconnections and implement only a single special purpose hard-wired instruction.

In Flynn's taxonomy, the PAAP architecture would be classified as an MIMD because each PE can execute its own instruction in an asynchronous autonomous manner, and data can flow in parallel to the PEs; data may flow as initial data and partial or fully computed results. A further MIMD classification places the PAAP array as a tightly coupled MIMD architecture because each PE does not have its own local memory, and relies on a host processor for both its instructions and data. The only problem with this classification is that Flynn's MIMD taxonomy does not fit well on array processor architectures, and the PAAP array is a wavefront-type architecture. [KungS85] discusses the different features that qualify wavefront arrays; however, there is no real definition for arrays that can be built using the PAAP architecture as a building block. Based on Duncan's taxonomy, the PAAP architecture classifies as a new type of MIMD Paradigms, the Configurable-Routing-Programmable-Element Wavefront Array (CRPE Wavefront Array).

The PAAP array addresses the 3 main asynchronous circuit problems by design. Our asynchronous approach uses a modified two-phase signal protocol which allows the active and passive end of the circuit to implement their own return-to-zero synchronization upon the receipt of the proper protocol sequence.

Transmission interference is not a problem because both the active and passive sides of the circuit depend on each other for resetting their synchronization signals. Once a signal has been set by the active side, the active side will wait until it receives its acknowledge before it attempts to modify the value of the protocol signal. Signal ordering is not a problem because all required synchronization signals are buffered upon arrival, thus computation only takes place when all required signals are present. Computation interference is addressed by buffering all of PE. The output synchronization mechanism makes sure that outputs are only latched in at the appropriate times in order to guarantee data consistency.

### 3.1 Introduction to the PAAP Array

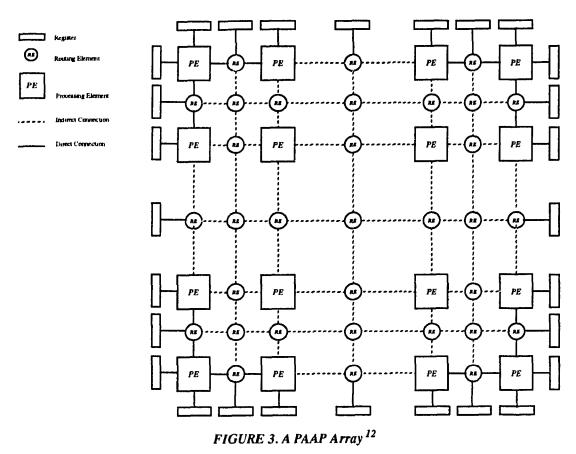

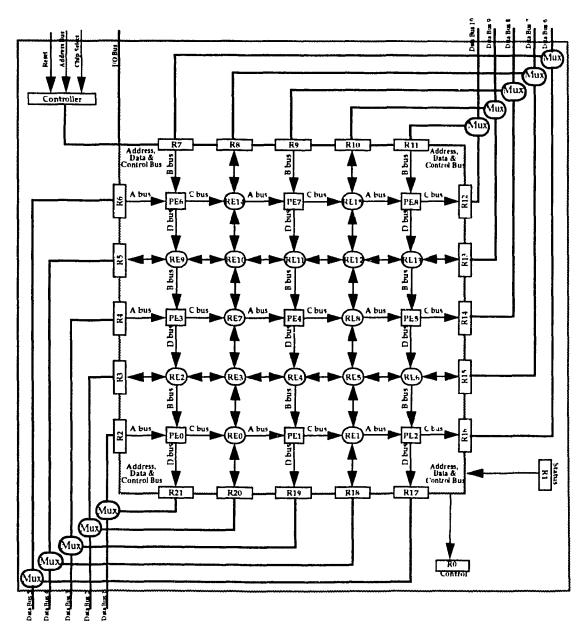

A PAAP array is built by arranging 8-bit PEs in a regular lattice interconnected via 8-bit polymorphic REs as shown in figure 3. Each PE and Routing Element (RE) can be programmed to execute its own instruction, which makes the PAAP design an MIMD-type array processor. The PE implements an integer RISC-like instruction set. Programming examples in a later chapter, will show how the PE almost supports

high-level constructs without an assembler or a microcode decode stage. The RE implements a bidirectional-2-in-to-2-out instruction set. 11

The RE's functionality is based on Snyder's switch lattice concept, but its implementation is original. This PAAP RE improves on the CHiP's switch predefined routing configurations restriction by allowing individual port direction and source to target controllability. This means that the compiler can build any switching network it requires and is not restricted to H-tree, Binary-tree, Mesh, etc. configurations. Any RE port can be programmed to be an input or an output, and can flow to any one of the remaining ports. The switch implementation is novel and unique to this work.

The PE implements an original programmable wavefront array element, as such, instructions and data are not fetched from memory as in the CHiP design. Instead, each PE and RE is programmed to execute the desired instruction and routing scheme respectively during the program load phase and data flows through the complete array in wavefronts during the program execution phase. The PE provides built-in

<sup>11</sup> This strategy allows any two buses to become either an input or an output. Once their direction has been chosen, then the buses can be connected to any other uncommitted input or output buses

<sup>12.</sup> The indirect connection signifies the existence of many more PEs and REs that are not shown

fault tolerance without incurring extra hardware overhead. The host should be able to dynamically map-out groups of PEs that do not reply to request signal chains and reroute around them. However no real hardware support for this feature is provided for it is an inherent capability in the reconfigurability of the REs and the asynchronous timing of the PEs.

The PAAP array implements a tightly coupled memory model and the shown periphery registers serve as buffers for the host to provide input data to the array and to receive calculated results from the array. The PAAP array is truly scalable because it does not suffer from clock skew synchronization problems, which may limit the array size.

#### 3.2 PAAP Array Building Blocks

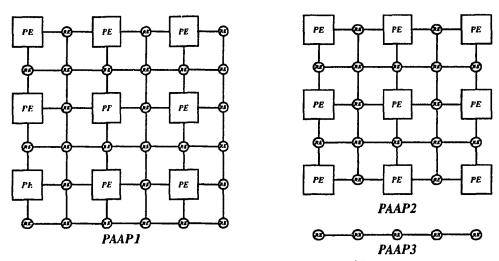

We envision a PAAP array being built by using a combination of the PAAP building blocks as shown in figure 4. These building blocks should be fabricated as separate ICs as follows:

- PAAP1 targeted to be a member of the array which provides RE capabilities on all of its output busses. This would allow us to tile the PAAP1 and create an array of any size with ready to use inter-PE connections (see figure 5). However, if this were the only IC we could use, there would be extra REs on all of the periphery output busses, which may or may not be desirable.

- PAAP2 targeted to be a periphery array element. It would be used to form the left-most column

or bottommost row of the array.

- PAAP3 targeted to be used in conjunction with the PAAP2. This IC would be used to add

routing elements in between the bottommost row elements. As a result the bottommost row

elements will have inter-IC routing to the left. The IC would also be used to add routing

elements in between the left-most column elements. As a result the left-most column elements

will have inter-IC routing to the bottom.

The PAAP1 IC would use 24, 10-bit buses, therefore it would require 240 pins, plus 2 pins for gnd and 2 pins for vdd. This totals 244 pins, which can now be achieved in some advanced PGA packages to provide us with full parallel I/O to/from all busses. The PAAP2 IC would use 204 pins and the PAAP3 IC would use 124 pins. <sup>13</sup>

A PAAP array that contains 1089 PEs would be build as shown in figure 5. Notice that the first 10 rows from top to bottom are composed of 10 PAAP1 ICs arranged from left to right. The right most column is composed of a PAAP2, which provides the right side of the array with connections to periphery

<sup>13</sup> We need two separate vid and gnd pins, one of each for the logic and one of each for the pad rings. This helps reduce the signal noise level

PEs. In order to provide inter-row routing for all right-most column members, we use the PAAP3 element. The bottommost row is composed of a PAAP2, which provides the bottom side of the array with connections to periphery PEs. In order to provide inter-column routing for all bottommost row members, we use the PAAP3 element.

FIGURE 4. PAAP Building Block ICs 14

| PAAP2 | ,    | PAAP. | ,        | PAAP     | ,     | PAAP  | ,     | PAAP  | ,     | PAAF                                             | ,     | PAAP                                             | ,     | PAAP  | ,     | PAAF  | ,     | PAAF  | ,     | PAAF  |   |      |       |  |       |  |       |  |   |      |   |      |