Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

# NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

## **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# The Homogeneous Multiprocessor: Memory Modules and the Interbus Switch Controller

Terry L. Segal

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Engineering at Concordia University Montréal, Québec, Canada

February 1989

© Terry L. Segal, 1989

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-53037-5

#### ABSTRACT

# The Homogeneous Multiprocessor: Memory Modules and the Interbus Switch Controller

#### Terry L. Segal

The Homogeneous Multiprocessor is a tightly-coupled, MIMD architecture consisting of a number of identical processing elements, and two types of interconnection pathways: (1) a distributively controlled network of switches ("extended buses") which permits each processor to access the memory of its two immediate neighbours, and (2) a fast local area network (H-Network) which permits each processor to communicate with all the other processors in a point-to-point or broadcast mode.

The design and implementation of two memory systems is given, one being a dynamic design incorporating error detection and correction to boost the reliability of the system and the other a static design using the newest 32 Kilobyte static RAMs. These two memory modules are prototypes that will be used in the Homogeneous Multiprocessor. Depending on cost, efficiency, speed of operation and area required on the circuit boards, one may be a better solution than the other. The Interbus Switch Controller has been designed and tested using standard off the shelf integrated circuits. The Interbus Switch Controller is a network of switches that are controlled in a distributive fashion. The Interbus Switch Controller is capable of creating the extended bus to allow a processor to access the memory modules of its two immediate neighbours.

#### **ACKNOWLEDGEMENTS**

I would like to thank my parents Carole and Martin and my flancee, Kelly for inspiring and supporting me during the endless hours of work.

I wish to express my sincerest gratitude to my thesis supervisor, Dr. N. J. Dimopoulos, for his caring guidance throughout my undergraduate and graduate studies. He was always available to direct and to advise whenever the occasion arose.

I would like to thank all the people who have been associated with this project, especially Kin Li, M. Robillard and G. Gosselin for their assistance in making the hardware operative.

# Table of Contents

| ABSTRACT                                          | iii |

|---------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                  | iv  |

| TABLE OF CONTENTS                                 | v   |

| LIST OF FIGURES                                   | vii |

| LIST OF TABLES                                    | ix  |

| LIST OF SYMBOLS                                   | хi  |

| LIST OF APPENDICES                                | xv  |

| CHAPTER 1: Introduction                           | 1   |

| 1.1 Classification of Architectures               | 2   |

| 1.2 Applications for Parallel Processors          | 3   |

| 1.3 Parallel Processor Structures                 | 4   |

| 1.4 Existing Multiprocessors                      | 5   |

| 1.4.1 The Butterfly                               | 5   |

| 1.4.2 The Cm*                                     | 7   |

| 1.4.3 The C.mmp                                   | 20  |

| 1.4.4 The Cosmic Cube                             | 12  |

| 1.4.5 The NYU Ultracomputer                       | 13  |

| 1.5 The Homogeneous Multiprocessor Proper         | 14  |

| 1.5.1 The Performance Analysis of the Homogeneous |     |

| Multiprocessor                                    | 20  |

| 1.5.2 Software Design for the Homogeneous         |     |

| Multiprocessor                                   |    |  |

|--------------------------------------------------|----|--|

| 1.6 Objectives of This Research                  | 22 |  |

| CHAPTER 2: The Interbus Switch                   | 23 |  |

| 2.1 Phase I                                      | 26 |  |

| 2.1.1 Design and Implementation                  | 27 |  |

| 2.2 Phase II                                     | 32 |  |

| 2.2.1 Design and Implementation                  | 37 |  |

| 2.2.1.1 Normal Access without Potential Deadlock | 41 |  |

| 2.2.1.2 Potential Deadlock                       | 45 |  |

| 2.2.1.3 Amalgamation - Normal Access including   |    |  |

| Potential Deadlock                               | 51 |  |

| 2.3 Experimental Results                         | 56 |  |

| CHAPTER 3: Conclusion and Future Work            | 57 |  |

| References                                       | 60 |  |

| Appendicies                                      | 62 |  |

# List of Figures

| 1.1  | The Block Diagram of the Node                               | 6  |

|------|-------------------------------------------------------------|----|

| 1.2  | A 4 x 4 Butterfly Switch                                    | 6  |

| 1.3  | A 16-Node Butterfly Processor                               | 7  |

| 1.4  | The Block Diagram of a Module in the Cm*                    | 8  |

| 1.5  | A Cluster of Computer Modules                               | 8  |

| 1.6  | A Network of Clusters                                       | 9  |

| 1.7  | The Architecture of the C.mmp                               | 10 |

| 1.8  | The Structure of a Processor in the C.mmp                   | 11 |

| 1.9  | The Cosmic Cube Interconnection Network                     | 12 |

| 1.10 | The Block Diagram of the NYU Ultracomputer                  | 13 |

| 1.11 | The Block Diagram of an Omega Network for N=8               | 14 |

| 1.12 | A Block Diagram of a Node in the Homogeneous Multiprocessor | 16 |

| 1.13 | The Homogeneous Multiprocessor Proper                       | 17 |

| 2.1  | The Block Diagram of the Interbus Switch Controller         | 25 |

| 2.2  | State Diagram for Phase I                                   | 28 |

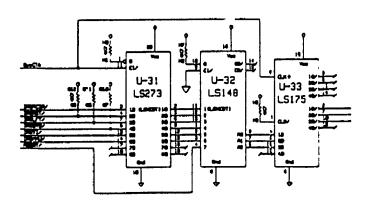

| 2.3  | Hardware Implementation for Phase I                         | 31 |

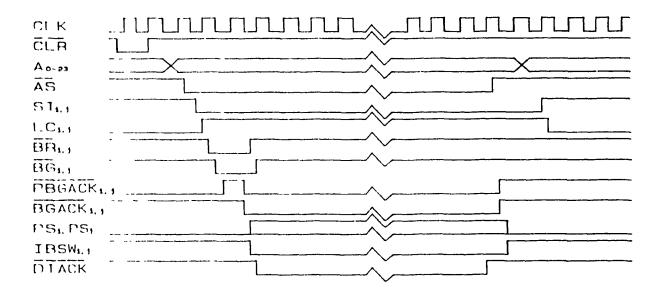

| 2.4  | Timing Diagram for Mastering the Bus                        | 33 |

| 2.5  | Case I of Potential Deadlock                                | 34 |

| 2.6  | Case II of Potential Deadlock                               | 36 |

| 2.7  | Case III of Potential Deadlock                              | 37 |

| 2.8  | State Diagram for Handshaking During Phase II               | 38 |

| 2.9         | Hardware Implementation for Handshaking During Phase II         |     |

|-------------|-----------------------------------------------------------------|-----|

| 2.10        | A Detailed Block Diagram of the Homogeneous Multiprocessor      | 42  |

| 2.11        | Hardware Implementation for Phase II                            | 55  |

| <b>A.1</b>  | The Mitsubishi M5M4256S-15 Dynamic RAM                          | 63  |

| <b>A.2</b>  | A Simple Storage System                                         | 65  |

| <b>A.3</b>  | A Typical Data Storage System Employing Error Detection         |     |

|             | and Correction                                                  | 66  |

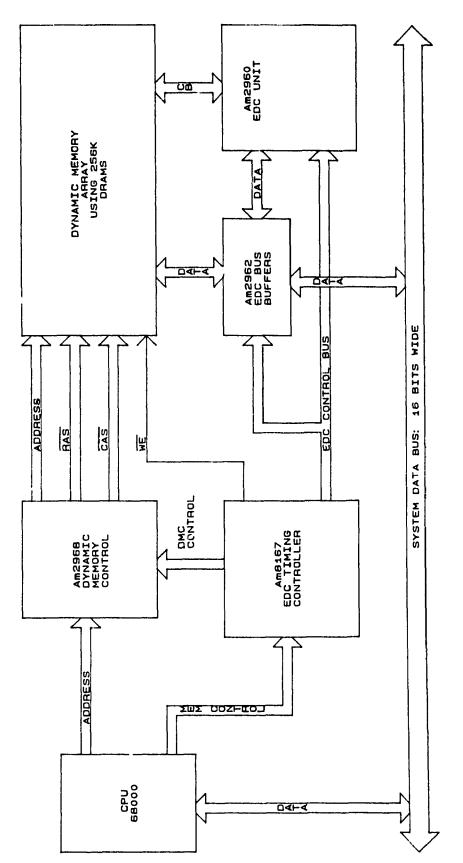

| ۸.4         | The Dynamic Memory Subsystem                                    | 74  |

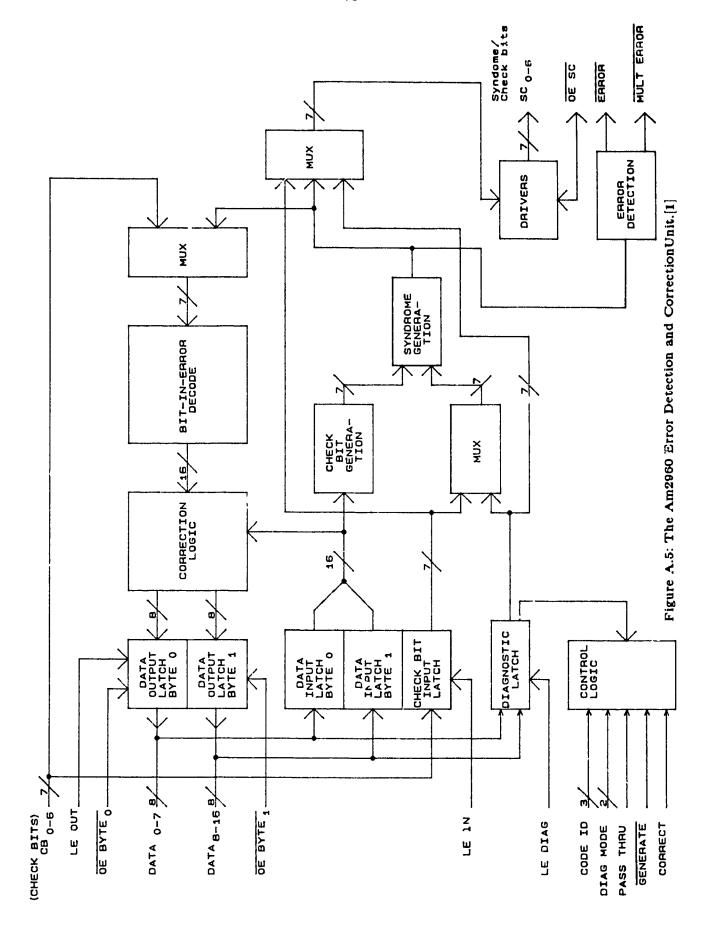

| A.5         | The Am2960 Error Detection and Correction Unit                  | 76  |

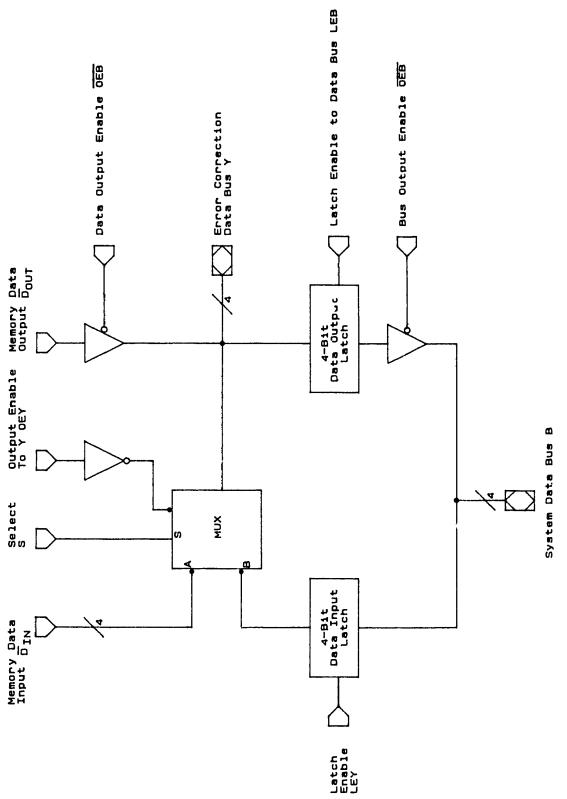

| <b>A</b> .6 | The Am2962 Bus Buffer                                           | 80  |

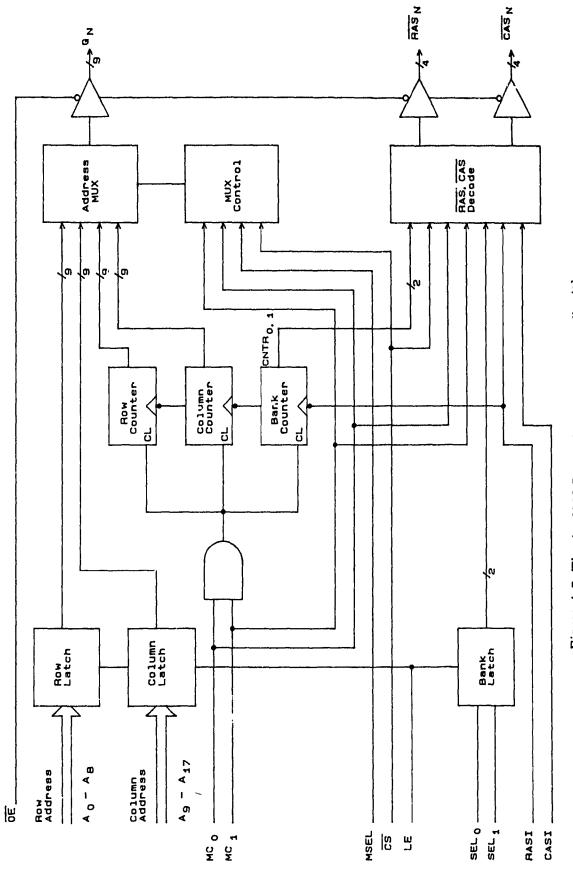

| A.7         | The Am2968 Dynamic MemoryController                             | 81  |

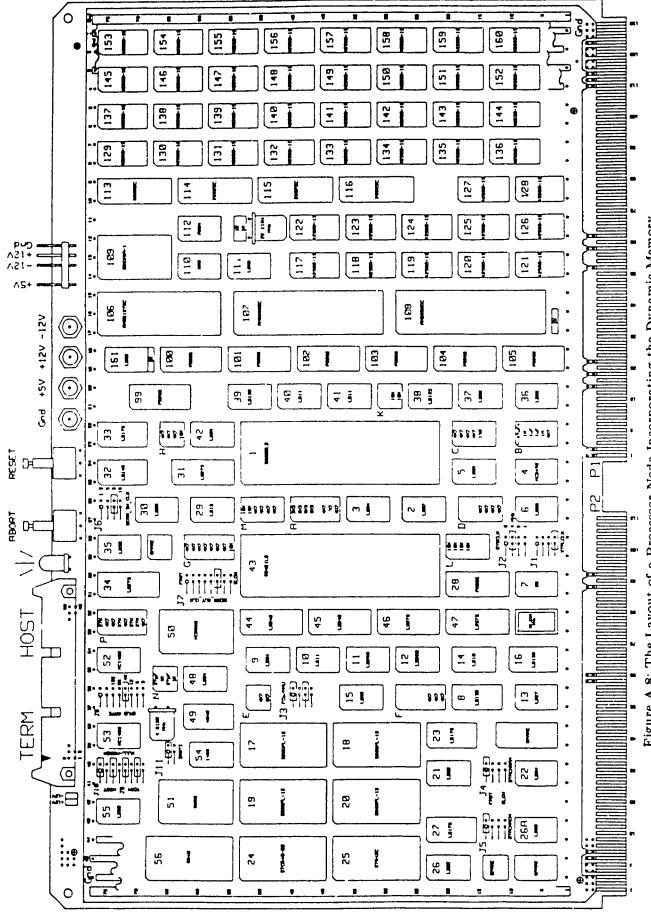

| <b>A.8</b>  | The Layout of a Processor Node Incorporating the Dynamic Memory | 88  |

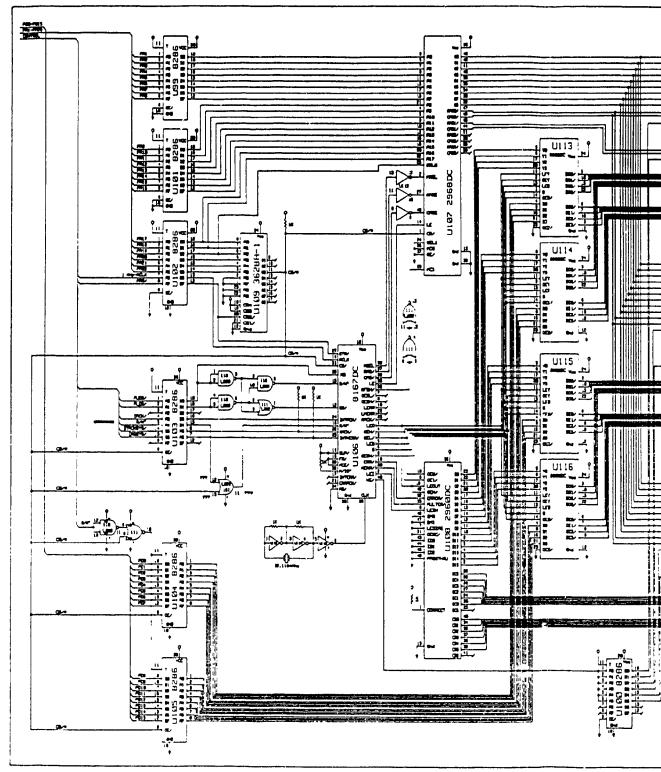

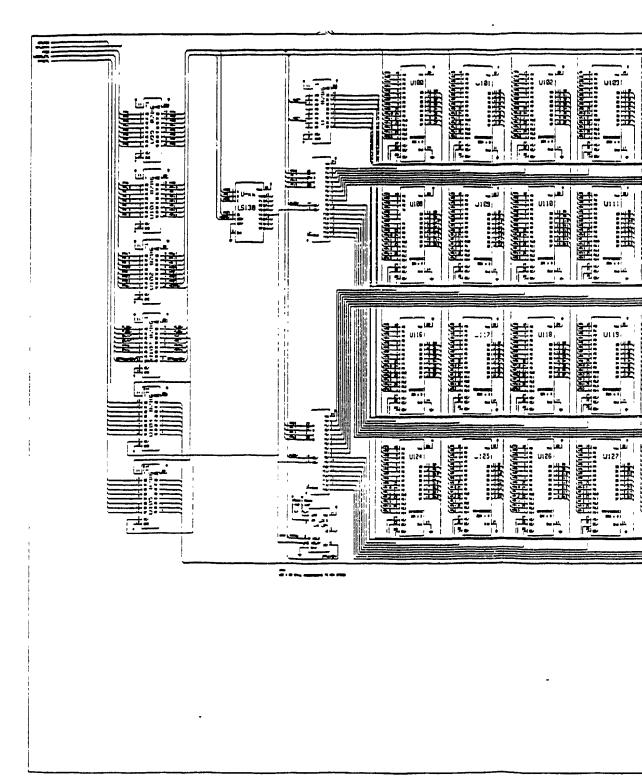

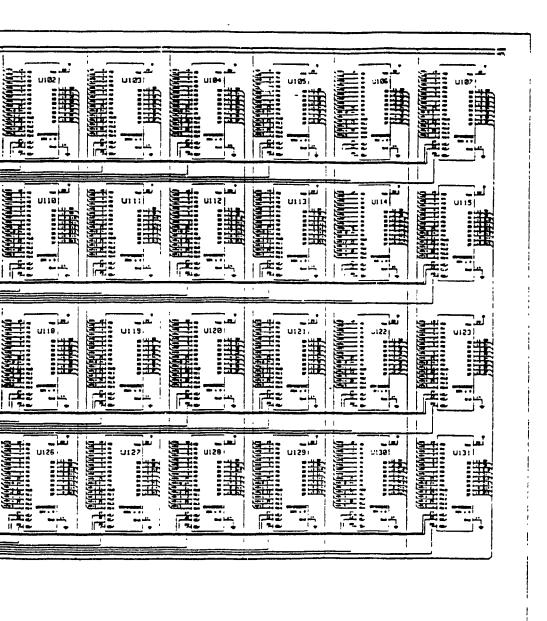

| A.9         | The Schematic Design of the Dynamic Memory                      | 89  |

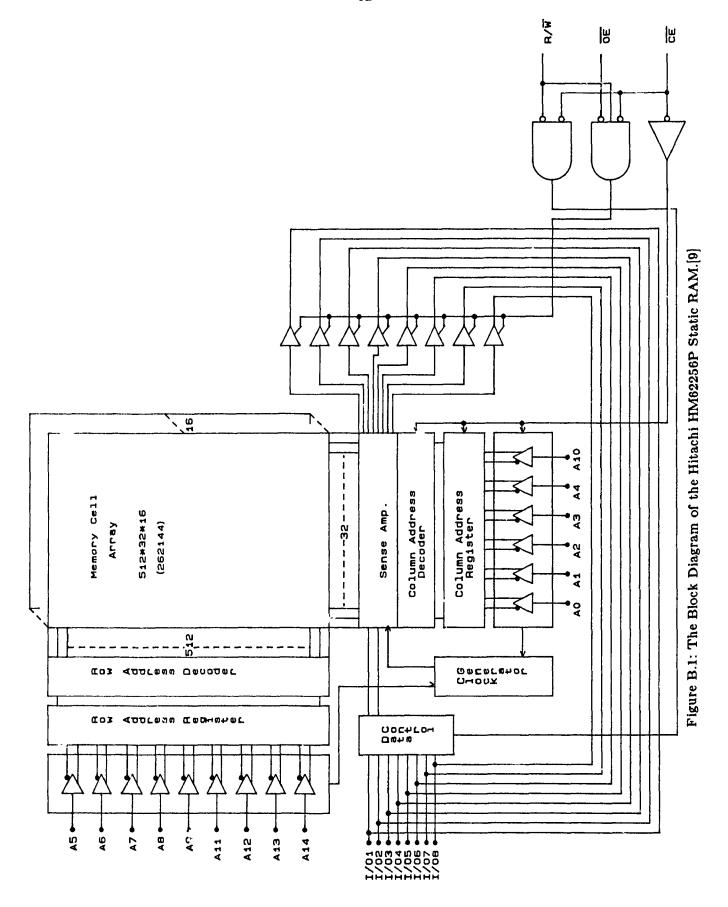

| B.1         | The Block Diagram of the Hitachi HM62256P Static RAM            | 92  |

| B.2         | Timing Diagram for the Data Transfer Acknowledge                | 96  |

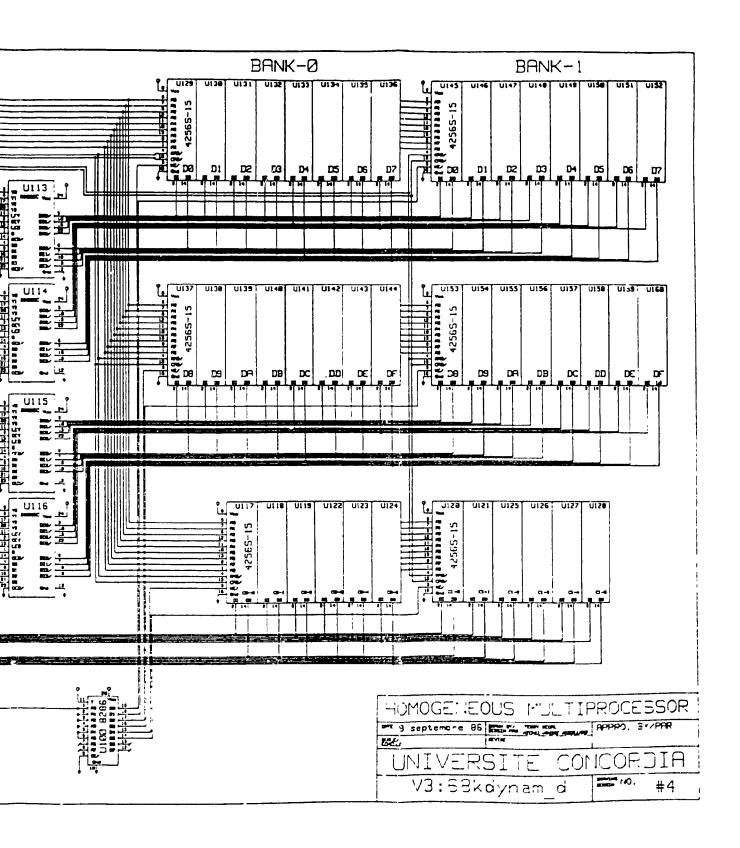

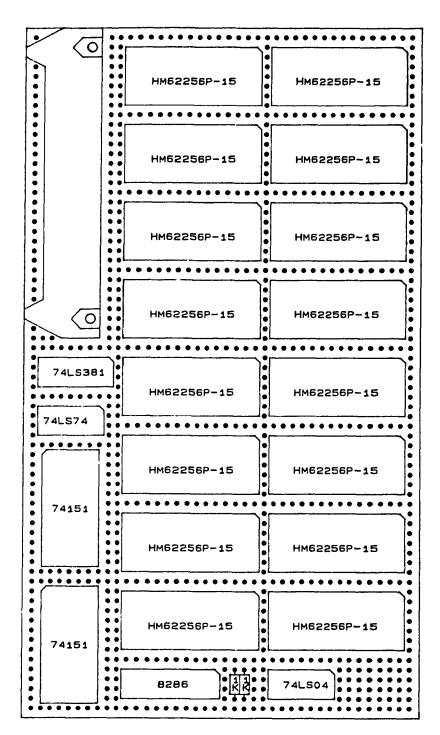

| B.3         | The Layout of the Static Memory Subsystem                       | 98  |

| B.4         | The Schematic of the Static Memory                              | 99  |

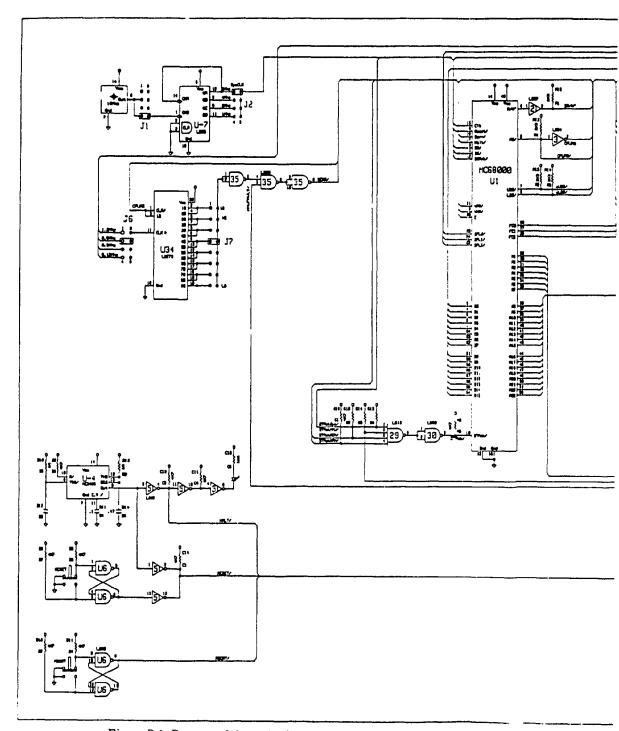

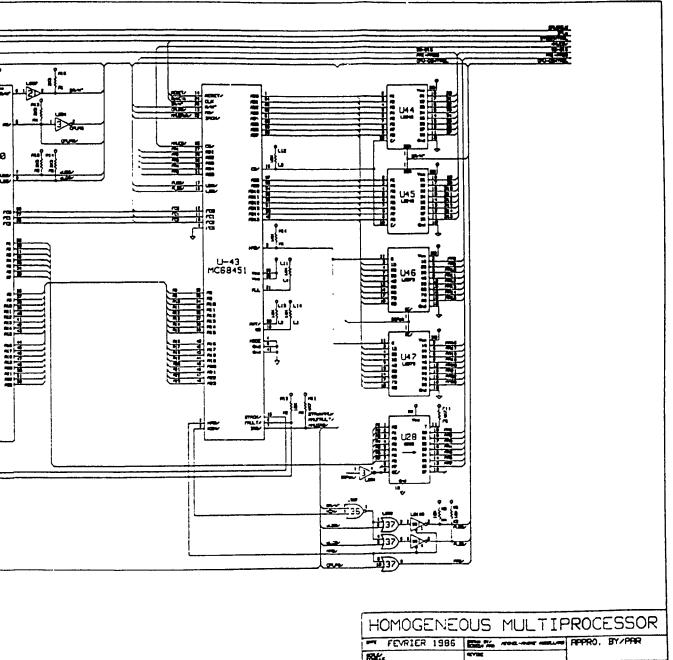

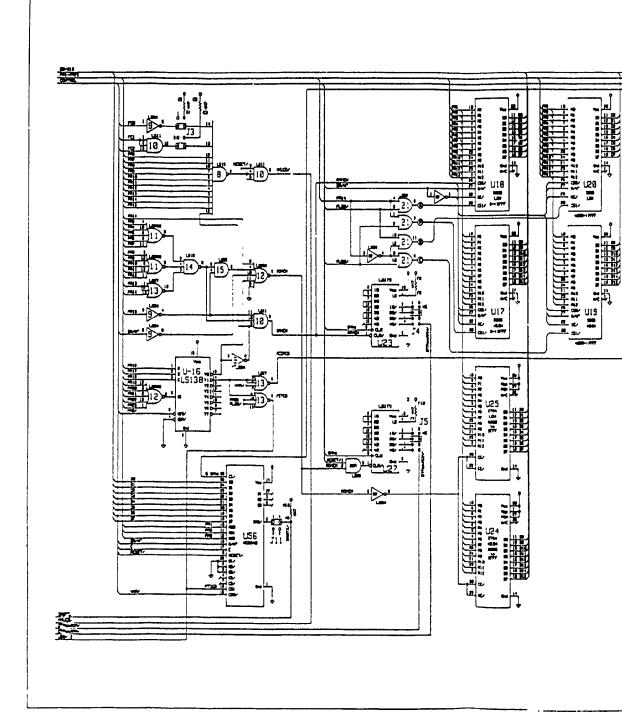

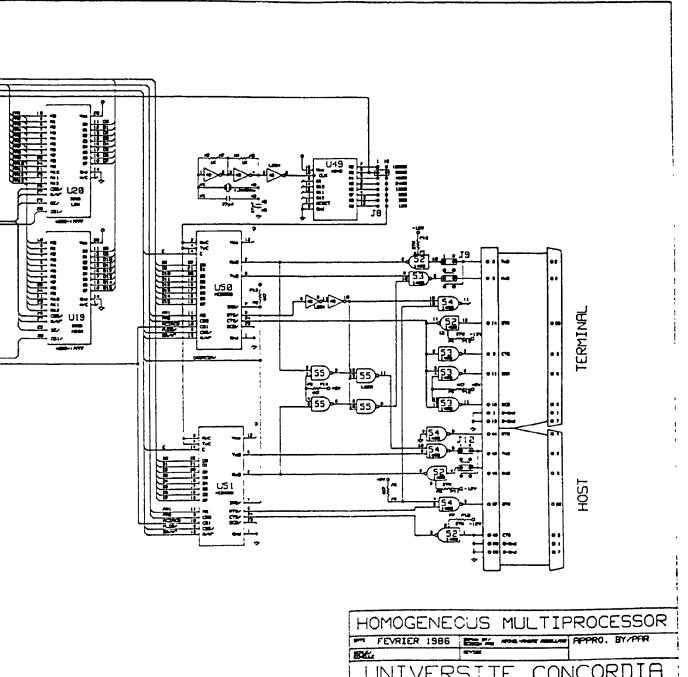

| D.1         | Processor Schematics (Sheet 1 of 3)                             | 111 |

| D.2         | Processor Schematics (Sheet 2 of 3)                             | 112 |

| D.3         | Processor Schematics (Sheet 3 of 3)                             | 113 |

# List of Tables

| 2.1        | The Interbus Memory Map                                            | 23 |

|------------|--------------------------------------------------------------------|----|

| 2.2        | State Assignment for Phase I                                       | 28 |

| 2.3        | State Assignment for the Handshaking in Phase II                   | 39 |

| 2.4        | Truth Table for the 8286 Buffer                                    | 41 |

| 2.5        | Truth Table for Closing the Interbus Switch                        | 43 |

| 2.6        | Truth Table for Address and Control Directional Signal             | 44 |

| 2.7        | Truth Table for Data Direction in the Interbus Switch              | 44 |

| 2.8        | Case I of Potential Deadlock                                       | 45 |

| 2.9        | Case II of Potential Deadlock                                      | 46 |

| 2.10       | Case III of Potential Deadlock                                     | 47 |

| 2.11       | State of the Switches During Potential Deadlock                    | 48 |

| 2.12       | Switch Control Information                                         | 49 |

| 2.13       | Directional Control for the Interbus Switch                        | 49 |

| 2.14       | Truth Table for the Processor Switch                               | 52 |

| 2.15       | Truth Table for Address and Control signals of the Interbus Switch | 52 |

| 2.16       | Truth Table for Data Bus Direction Through the Interbus Switch     | 53 |

| 2.17       | Truth Table for the State of the Interbus Switch                   | 54 |

| <b>A.1</b> | Check Positions                                                    | 67 |

| <b>A.2</b> | Encoding a 4-Bit Message and Locating the Error                    | 68 |

| <b>A.3</b> | Syndrome Bit Definition                                            | 71 |

| <b>A</b> 4 | Check Rit Encoding                                                 | 78 |

| <b>A</b> .5 | MC68000 to Am8167 Interface                    | 82 |

|-------------|------------------------------------------------|----|

| B.1         | Memory Partition at the First Level            | 93 |

| B.2         | Truth Table for the 4-to-16 Decoders           | 94 |

| B.3         | Propagation Delays in the Static Memory System | 95 |

# List of Symbols

| Symbol                                     | Description                                 | Page |

|--------------------------------------------|---------------------------------------------|------|

| $\mathbf{A_i}$                             | Address bit i                               | 23   |

| ALU                                        | Arithmetic Logic Unit                       | 4    |

| ĀS                                         | Address Strobe                              | ง3   |

| $\overline{AS}_{l}$                        | Address Strobe originating from Processor i | 31   |

| b                                          | Local bus                                   | 17   |

| BE                                         | Back End                                    | 17   |

| BG                                         | Bus Grant                                   | 33   |

| BGACK                                      | Bus Grant Acknowledge                       | 33   |

| $\overline{\mathrm{BGACK}}_{\mathrm{i,j}}$ | Bus Grant Acknowledge (from i to j)         | 25   |

| BR                                         | Bus Request                                 | 33   |

| $\overline{BR}_{i,j}$                      | Bus Request (from i to j)                   | 25   |

| $BYTE/\overline{WORD}$                     | 8 or 16 bit data                            | 82   |

| $\mathbf{C_i}$                             | Check bit i                                 | 67   |

| CAS                                        | Column Address Strobe                       | 63   |

| CLK                                        | Clock                                       | 25   |

| CLR                                        | Clear Circuit                               | 25   |

| <del>CS</del>                              | Chip Select                                 | 91   |

| $D_i$                                      | Data bit i                                  | 70   |

| DI                                         | Data Input line                             | 70   |

| DS                                         | Data Strobe                                 | 82   |

| DTACK                                      | Data Transfer Acknowledge                   | 33   |

| DO                                         | Data Output line                            | 64   |

| ERROR                                      | Single bit error                            | 76   |

| EPROM                                      | Electrically Programmable Read Only Memory  | 18   |

| FE:                                                                                      | Front End                                                                                                | 17 |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----|

| HS                                                                                       | Network station i                                                                                        | 17 |

| ${\operatorname{IBS}}_{i,j}$                                                             | Interbus Switch Controller located between processor i and processor j                                   | 17 |

| $IBSW_{i,j}$                                                                             | Interbus Switch located between processor i and processor j                                              | 17 |

| $LC_{l,j}$                                                                               | Logical Closure for Interbus Switch located between processor i and processor j                          | 25 |

| LDS                                                                                      | Lower Data Strobe                                                                                        | 33 |

| LE IN                                                                                    | Latch Enable Input                                                                                       | 75 |

| LE OUT                                                                                   | Latch Enable Output                                                                                      | 76 |

| m                                                                                        | # parity bits                                                                                            | 66 |

| $M_{l}$                                                                                  | Memory Module i                                                                                          | 17 |

| MMU                                                                                      | Memory Management Unit                                                                                   | 5  |

| 3.1S                                                                                     | Mass Storage                                                                                             | 17 |

| MULT ERROR                                                                               | Multiple bit error                                                                                       | 70 |

| n                                                                                        | # message bits                                                                                           | 86 |

| Ni                                                                                       | Message bit i                                                                                            | 67 |

| ŌĒ                                                                                       | Output Enable                                                                                            | 41 |

| $\widehat{\mathrm{OE}}_{\mathbf{i}}$                                                     | Output Enable for Processor i                                                                            | 51 |

| $\widetilde{\mathrm{OE}}_{\mathbf{A},\mathbf{C},\mathbf{D}}$                             | Output Enable fo. Address, Control and Data lines                                                        | 43 |

| $\overline{\text{OE}}_{\mathbf{A},\mathbf{C},\mathrm{D}}$ IBS $_{\mathbf{i},\mathbf{j}}$ | Output Enable for Address, Control and Data lines on Interbus Switch between processor i and processor j | 25 |

| $\overline{\mathrm{OE}}_{\mathbf{A},\mathbf{C},\mathrm{D}}\mathrm{PS}_{\mathbf{j}}$      | Output Enable for Address, Control and Data lines on Processor Switch i                                  | 25 |

| Pi                                                                                       | Processor i                                                                                              | 17 |

| PAS                                                                                      | Physical Address Strobe                                                                                  | 38 |

| PAS                                                                                      | Physical Address Strobe originating from Processor i                                                     | 25 |

| PBGACK                                                                                   | Physical Bus Grant Acknowledge                                                                           | 38 |

| PBGACK                 | Physical Bus Grant Acknowledge                                                  | 38 |

|------------------------|---------------------------------------------------------------------------------|----|

| PD                     | Potential Deadlock                                                              | 48 |

| PDTACK                 | Pysical Data Transfer Acknowledge                                               | 38 |

| PE                     | Processing Element                                                              | 4  |

| PLDS                   | Physical Lower Address Strobe                                                   | 38 |

| PNC                    | Processor Node Controller                                                       | 5  |

| PNI                    | Processor Network Interface                                                     | 13 |

| PR                     | Preset Circuit                                                                  | 96 |

| PS <sub>1</sub>        | Processor Switch i                                                              | 45 |

| $PS_{i}IBS_{i,j}$      | Processor switch control line orginating from Interbus<br>Switch Controller i,j | 51 |

| PUDS                   | Physical Upper Address Strobe                                                   | 38 |

| R                      | Sum of all requests                                                             | 27 |

| R/G                    | Bus request/grant                                                               | 17 |

| $R_1$                  | Request from Processor i                                                        | 27 |

| $R/\overline{W}$       | Read / Write Signal                                                             | 43 |

| $R/\overline{W}_i$     | Read / Write signal from processor i                                            | 25 |

| RAM                    | Random Access Memory                                                            | 12 |

| RAS                    | Row Address Strobe                                                              | 63 |

| RCLK                   | Refresh timer                                                                   | 82 |

| Request <sub>i,j</sub> | Request originating from processor i and terminating at processor j             | 45 |

| $S_i$                  | Symdrome bit i                                                                  | 70 |

| $SL_{i,j}$             | Status of Switch on Left of Interbus Switch located between processors i and j  | 25 |

| $SR_{1,j}$             | Status of Switch on Right of Interbus Switch located between processors i and j | 25 |

| STL                    | Interbus Switch Status (OPEN or non-OPEN)                                       | 25 |

| Т                           | Buffer Direction control                                                                                    | 41 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------|----|

| $T_{A,C}$                   | Directional Control for Address and Control lines                                                           | 41 |

| $T_D$                       | Directional Control for Data Lines                                                                          | 43 |

| $T_{A,C}IBS_{l,j}$          | Directional Control for Address and Control lines on<br>Interbus Switch between processor i and processor j | 25 |

| $T_{D}IBS_{i,j}$            | Directional Control for Data lines on Interbus Switch<br>between processor i and processor j                | 25 |

| $T_{A,C}PS_1$               | Directional Control for Address and Control lines on Processor Switch i                                     | 25 |

| $T_DPS_i$                   | Directional Control for Data lines on Processor Switch i                                                    | 25 |

| TE                          | Terminal                                                                                                    | 17 |

| UDS                         | Upper Data Strobe                                                                                           | 33 |

| $\overline{ m WE}$          | Write Enable                                                                                                | 74 |

| $\overline{\mathbf{Y}}_{1}$ | Decoder Output i                                                                                            | 93 |

# List of Appendices

| APPENDIX A: | The Dynamic Memory Subsystem             | 62  |

|-------------|------------------------------------------|-----|

| APPENDIX B: | The Static Memory Subsystem              | 90  |

| APPENDIX C: | Design of the Interbus Switch Controller | 100 |

| APPENDIX D: | Schematics for the Processor Subsystem   | 111 |

#### 1. Introduction

In the past decade, the development of microprocessor technology and electronic circuits along with the desire to have larger and faster computers have prompted an increase in the research activities in the area of computer architecture. Computer designers have proposed numerous distributed and multiprocessing architectures. These systems have used mostly off the shelf commercially available components and more recently, implementing specific architectures or specialized components, Very Large Scale Integration (VLSI).

The definition of a multiprocessor is a computer that contains two or more processor units working on a shared memory under integrated control. However, the processor units can have their own small local memories. There must exist an integrated operating system which controls all of the hardware and software of the system. There are many ways of organizing the interconnection network required by the multiprocessors such as: a timed-shared bus; a crossbar switch; an n-dimensional cube; nearest neighbour matrices; and a cluster bus to name a few. [12]

As defined in the past, a multiprocessing system consists of two or more processors each of which can operate independently but at the same time can exchange information via an interconnection network and/or shared memory. In the Homogeneous Multiprocessor Proper an interconnection network known as the InterProcessor Bus allows processors to access the memories of their two immediate neighbours.

Some of the more popular multiprocessing systems that have been proposed and built that contain varying degrees of coupling and homogeneity are the Butterfly [2], the Cm\* [19], the C.mmp [21], the Cosmic Cube [18], the NYU Ultracomputer [7], etc.

--

#### 1.1 Classification of Architectures

There are four basic classifications for a computer. The four categories determined by the multiplicity of instruction and data streams. These classifications were introduced by Michael J. Flynn.

SISD: Single Instruction stream - Single Data stream

SIMD: Single Instruction stream - Multiple Data stream

MISD: Multiple Instruction stream - Single Data stream

MIMD: Multiple Instruction stream - Multiple Data stream

Most commercially available computers available today are SISD, they contain one processor, control unit, and memory.

Array processors are SIMD. They contain multiple processing elements and one control unit. Each of the processing elements receives the same instructions to execute on different data.

MISD computers contain n processing units. Each processing unit receives different instructions to execute on the same data. The output of processor i is used as the input to processor j.

An MIMD computer consists of n processors that interact on an input derived from the same data space shared by all processors. The computer is said to be tightly-coupled if the degree of interaction among the processors is high. [10] In an MIMD system, care must be taken to avoid unecessary overhead due to interference caused by accessing shared resources such as main memory and synchronization. [6]

### 1.2 Applications for Parallel Processors

Just about any application can be accomplished on a parallel computer. The justification for using one is a significant decrease in the time required to complete the job. A most obvious example is weather forcasting. There is no point forcasting the weather using a computer if the time required for the computations is greater than the forcast time less the current time, i.e. if it is 9:00 AM, the weather being forcast is for 10:00 AM and the computer requires two hours to do the forcast. Reduction in computation time is a major justification, but it is not the only one. In some instances, the sheer complexity of the problem may be a factor.

There are various categories where parallel computers can play a major role.

Weather forcasting: Solving the general circulation model equations.

Oceanography and Astrophysics: Ocean climate, fishery management, ocean resources, and tides.

Artificial Intelligence and Automation: Image processing, pattern recognition, computer vision, speech understanding, machine interface, CAD/CAM/CAI/OA, intelligent robotics, expert systems, and knowledge engineering.

Finite element analysis: Design of dams, bridges, ships, jets, buildings, and space vehicles. I.E. large systems of algebraic an partial differential equations.

Computational dynamics: Aircraft and spacecraft lift, turbulence studies.

A host of other applications are also applicable: remote sensing, energy resources exploration, seismic exploration, reservoir modeling, plasma fusion power, nuclear reactor safety, computer assisted tomography, genetic engineering, weapon research and defense.[10]

#### 1.3 Parallel Processor Structures

Parallel computers are divided into three configurations:

Pipeline computers

Array processors

Multiprocessor systems.

There are four major steps involved in normal processing within a Pipelined processor. They are:

Instruction Fetch (IF): From main memory

Instruction Decoding (ID): Identify the operation

Operand Fetch (OF): If required for execution

Execution (EX): Execute the operation

In a non-pipelined processor, once an instruction fetch is complete, the next one cannot proceed until the current instruction has run to completion, i.e. instruction decode, operand fetch, and execution. In a pipelined processor, at any given time, there can be as many as four (or as many stages as there are in the pipe) instructions running at different stages of completion. The rate at which instructions are clocked through the pipe is equal to the slowest stage in the pipe. In theory, a pipelined processors with n stages can be at most n times faster than a non-pipelined processor.

Array processors are synchronous parallel computers comprising of processing elements (PE). A processing element contains an ALU with registers and local memory. The processing elements are connected by a data-routing network. The processing elements are synchronized to perform the same function at the same time, and of course the data-routing mechanism must be established among them. There is also a control unit which fetches and decodes instructions from local and control memory and executes the scalar and control-type instructions. The data routing is accomplished by the control unit. Vector instructions are received by the processing elements from the control unit

for distributed execution for use with different operands fetched directly from the Prolocal memory

A multiprocessor contains two or more processors that have comparable capabilities. Memory modules, I/O channels, and peripheral devices are shared between all of the processors. Each processor also has its own local memory and peripheral devices. A multiprocessor is controlled by a single integrated operating system that provides interaction between processors and their programs at various levels. The processors, memories, and peripheral devices are organized by the interconnection structure. Some of these interconnection structures are a time-shared common bus, a crossbar switch network, and multiport memories.[10]

#### 1.4 Existing Multiprocessors

Currently, there are many multiprocessors that have been designed and built. Some of them are research projects while others are commercially available. In the following sections, descriptions of some of the multiprocessors that have been conceived through University research are given. These multiprocessors are: The Butterfly; the Cm\*; the C.mmp; the NYU Ultracomputer; and the Homogeneous Multiprocessor.

#### 1.4.1 The Butterfly

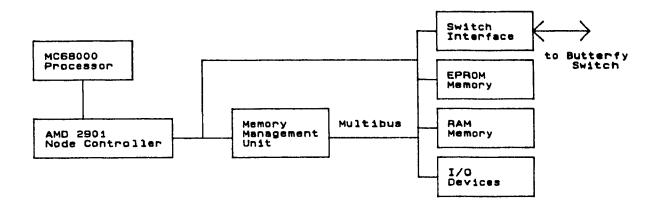

The Butterfly Multiprocessor consists of nodes each of which contains a processor and local memory and is connected to a high performance switch. Each node comprises of a Motorola MC68000 with up to 4 Megabytes of local memory, an Advanced Micro Devices AMD2901 processor which implements the Processor Node Controller (PNC) function, and a Memory Management Unit (MMU). Shown in figure 1.1 is the block diagram of the node.[3]

Figure 1.1: The Block Diagram of the Node.[3]

The Butterfly can contain up to 256 nodes. Through a virtual memory interface access to the Butterfly switch is accomplished. This is done by the PNC, it interprets the virtual address to determine if the request is local or on a remote node. If the request is local, the virtual address is passed to the Memory Management Unit for translation into a physical memory location. If the request is destined for a remote node, the PNC sends a message to through the Butterfly switch to the remote node, where the reference is satisfied and if necessary, a reply is returned. The message contains a physical memory address and a node address for the remote node.

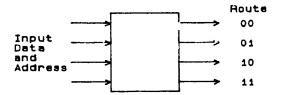

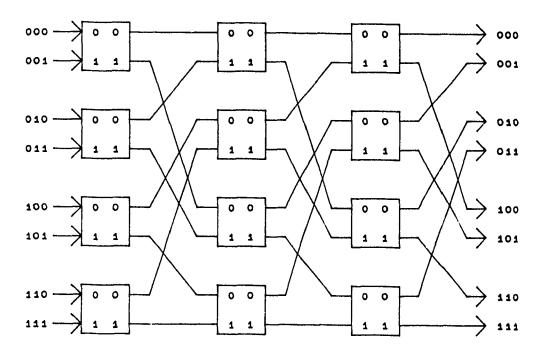

The backbone of the processor is the Butterfly Switch. Shown in figure 1.2 is the building block of the Butterfly Switch, a 4 x 4 switch.

Figure 1.2: A 4 x 4 Butterfly Switch.[3]

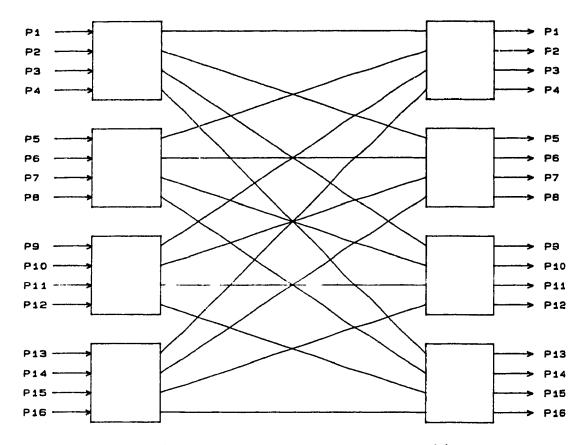

When accessing the Butterfly Switch, a remote address and data arrive on an input path, and depending on the address, exit the appropriate path. Refer to figure 1.3, for a 16-node Butterfly processor.

Figure 1.3: A 16-Node Butterfly Processor.[3]

#### 1.4.2 The Cm\*

The Cm\* is an MIMD distributed multiprocessor. It was developed at Carnegie Mellon University in the mid 1970's. All of the processors in the Cm\* share a single virtual address space, i.e. each processor has associated with it, a portion of the total memory. Processors are grouped into clusters and processors in different clusters communicate via packet-switches. The hierarchy of the Cm\* consists of three levels: modules (processors); clusters (groups of modules); and system.

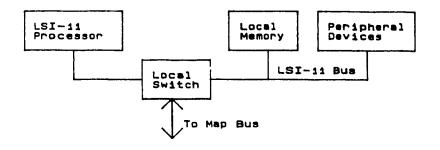

A Module comprises of a processor, a local memory, and peripheral devices. The contents of the Module communicate with each other via the Modules' processor bus. The processor within the Modules is a DEC LSI-11. The LSI-11 is a 16-bit computer with an address range of 64 Kilobytes. Shown in figure 1.4 is the block diagram of a Modul. in the Cm\*. Each of the modules is connected to the other Modules in the Cluster via the local switch.[3]

Figure 1.4: The Block Diagram of a Module in the Cm\*.[3]

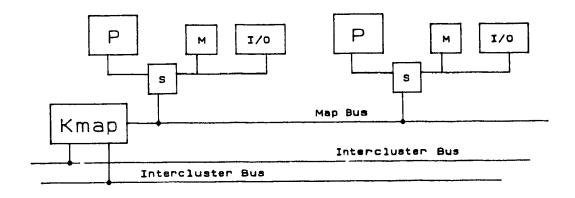

A Cluster is a group of 14 Modules or Cms. The Clusters are connected via the Intercluster buses. Referring to figure 1.5, a cluster of computer modules.

Figure 1.5: A Cluster of Computer Modules.[10]

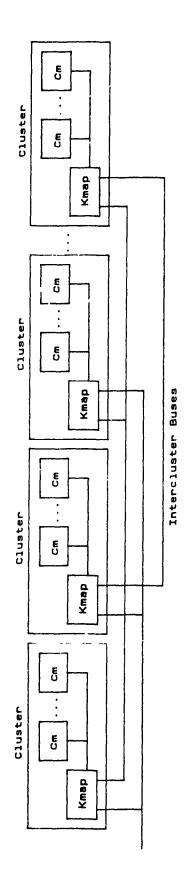

The Local Switch in the Module allows the processor to communicate with its memory and peripheral devices. The Local Switch maps local addresses by using an internal relocation table that segments local memory on 4 Kilobyte boundaries. If a reference on non-local, it is determined by the Local Switch and it is routed automatically onto the Map bus. The Kmap unit arbitrates access to the Map bus. The Pmap unit, located within the Kmap unit is a microprogrammed processor that determines if a reference is local or to the cluster. [3] Finally, in figure 1.6, a network of clusters.

Figure 1.6: A network of clusters.[10]

## 1.4.3 The C.mmp

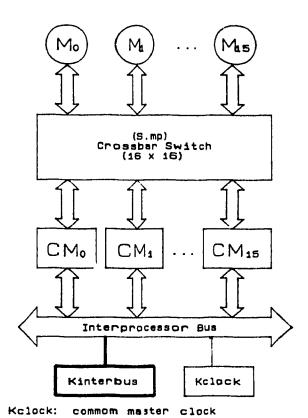

The C.mmp was designed and built at Carnegie-Mellon University in the early 1970's. It was built from slightly modified Digital Equipment Corp. PDP-11/40E computers. The modification was to remove some of the instruction set.[10] Shown in figure 1.7 is the basic architecture.

Kinterbus: interprocessor bus control

Figure 1.7: The architecture of the C.mmp.[10]

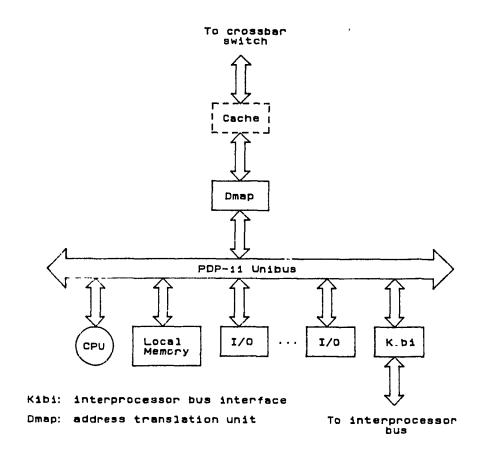

The C.mmp comprises of 16 computer modules connected to 16 shared memory modules via a 16 x 16 crossbar switch. Refer to figure 1.8 for the structure of a processor

Figure 1.8: The structure of a processor in the C.mmp. [10]

Each processor in the C.mmp contains the following: 8 Kilobytes of local memory for operating system functions, four 40 Megabyte disk controllers and three 30 Megabyte disk controllers. The operating system that the C.mmp uses is called the Hydra.

#### 1.4.4 The Cosmic Cube

The Cosmic Cube, designed and built at Caltech consists of 64 small computers that are connected by a network of point-to-point communication channels arranged as a six-dimensional hypercube. The hardware used in each of the nodes consists of an Intel 8086 processor along with an Intel 8087 floating point coprocessor. The memory consists of 128 Kilobytes of dynamic RAM with with parity check.[18]

An n dimensional hypercube contains  $2^n$  processing elements, each of which is connected to n of its neighbours. In the case of the Cosmic Cube, n=6.[3] Therefore, there are  $2^6$  processing elements or 64, each connected to six of its neighbours as shown in figure 1.9.

Figure 1.9: The Cosmic Cube Interconnection Network.

### 1.4.5 The NYU Ultracomputer

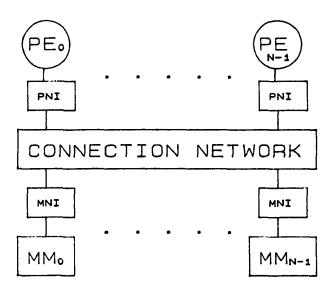

The NYU Ultracomputer is a project at New York University which proposes the design of a shared-memory MIMD parallel machine composed of thousands of autonomous processing elements. An Omega network is used for enhanced message switching between the processors. It is proposed that each of the processing elements be custom made and will be attached to the network via a processor network interface. Each of the memory modules will be attached to the network via a memory network interface. The fetch-and-add primitive is used to achieve interprocessor synchronization.

Shown in figure 1.10, the block diagram of the NYU Ultracomputer. Each of the processing elements (PE) is connected to the network using a processor network interface (PNI). Each of the memory modules (MM) is connected using a memory network interface (MNI).[7]

Figure 1.10: The Block Diagram of the NYU Ultracomputer.[7]

The communication network incorporated in the NYU Ultracomputer is of the Omega type. An Omega network is similar in design and operation to a Butterfly network. An address is placed on the bus and it is then decoded to route the data through the appropriate *switches* to connect to the destination memory module. Refer to figure

### 1.11 for the block diagram of an Omega network.

Figure 1.11: The Block Diagram of an Omega Network for N = 8.[7]

### 1.5 The Homogeneous Multiprocessor Proper

In the design of multiprocessors, the availability of information pathways between processors is a major architectural concern. Many of the established MIMD multiprocessors are either very expensive or slow due to their designs which have opted for a complete graph network which incorporates either crossbar switches or microprogrammed controllers.

Problems can be formulated in a way such that each of the computational processes would require information from only its nearest neighbour process to obtain the final result. By reducing the scope of the interprocessor communication, and at the same time making these communication pathways very fast, these problems would benefit greatly. This has been the realization of the homogeneous multiprocessor.[4]

The Homogeneous Multiprocessor Proper is a microprocessor based, tightly coupled, multiple instruction, multiple data (MIMD) machine that incorporates shared memory and networking. Some of the applications that are intended for the Homogeneous

multiple instruction, multiple data (MIMD) machine that incorporates shared memory and networking. Some of the applications that are intended for the Homogeneous Multiprocessor are: distributed simulation; relaxation processing; image processing; and speech processing.

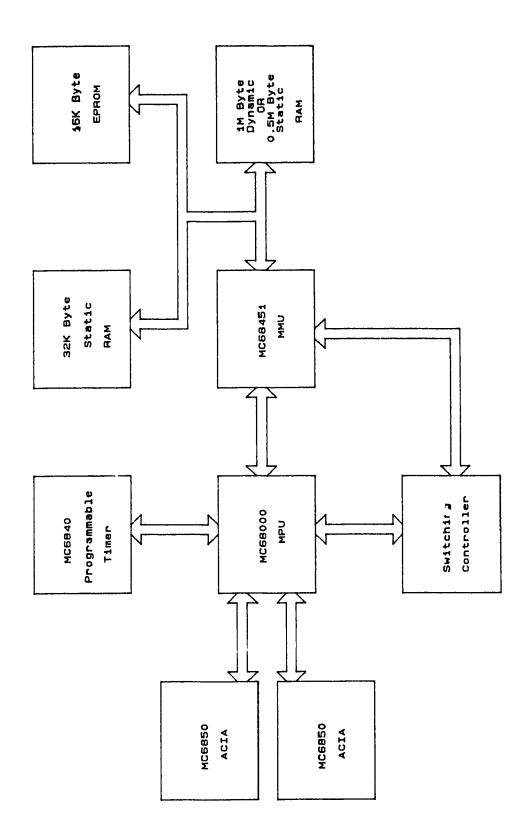

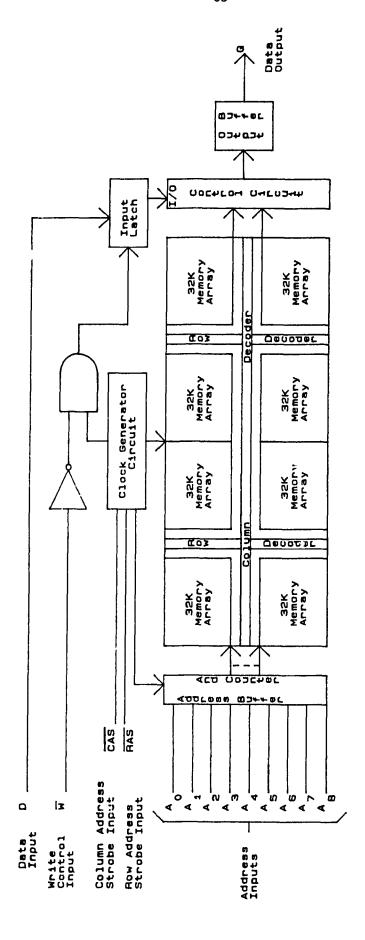

As shown in figure 1.12, a block diagram of a node in the Homogeneous Multiprocessor. Each node consists of an 8 MHz Motorola MC68000 processor, a MC68451 Memory Management Unit (MMU), 16 Kilobytes of EPROM, 32 Kilobytes of static RAM, and a main memory. The main memories that have been designed and built are a 1 Megabyte dynamic memory with error detection and correction, and a 0.5 Megabyte static memory.

The memory management unit performs virtual to physical address mapping by information stored in the 32 MMU descriptors. If the processor attempts to access a protected or out-of-range segment the MMU will generate an interrupt. The MC68000 has two modes of operation both of which can be used, a supervisor state or a user state. A low level protection scheme can be implemented by using both the MMU protection mechanism and the two modes of operation of the processor.

Currently, a Motorola Tutor monitor [14], is placed in the 16 Kilobytes of EPROM.

This allows for testing and debugging the hardware and software.

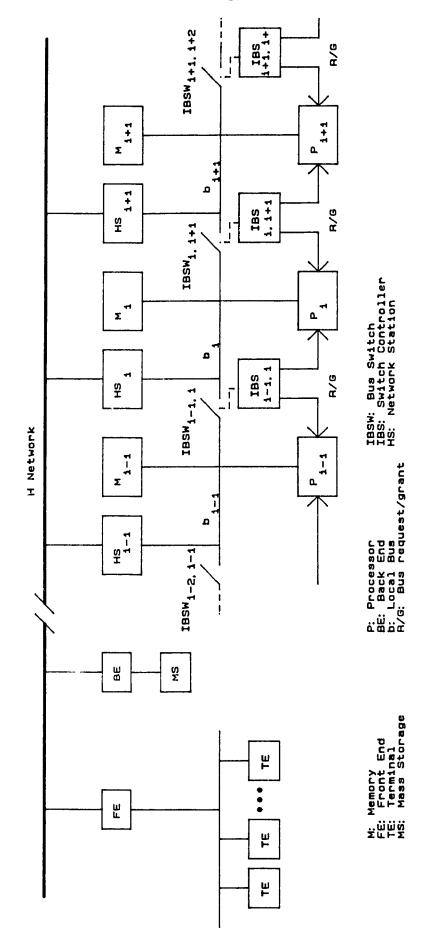

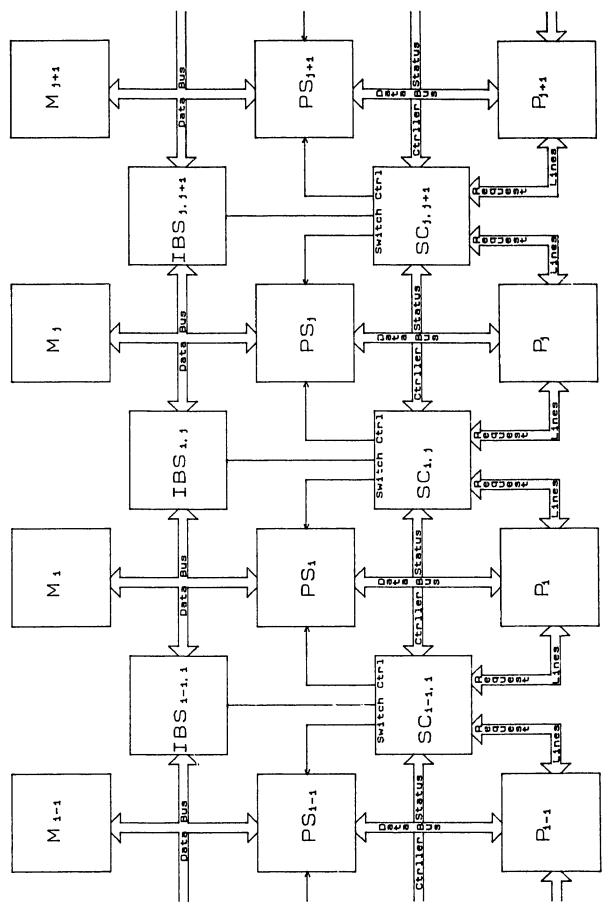

The Homogeneous Multiprocessor has a tightly coupled architecture. The block diagram of the Homogeneous Multiprocessor is displayed in figure 1.13. The standard system comprises k ( $k \geq 3$ ) processing elements, k memory modules, k-1 interbus switches that control the Interprocessor Bus, and the H-Network which is a fast local area network used for point to point communication between nonadjacent processor and for broadcast mode communication.

Figure 1.12: A Block Diagram of a Node in the Homogeneous Multiprocessor.

Figure 1.13: The Homogeneous Multiprocessor Proper. [5]

Each of the Processor Elements consists of the following: a processor P<sub>i</sub>; a memory module M<sub>i</sub>; a local bus to facilitate communication between the processor and memory M<sub>i</sub>. The Interbus Switch is physically connected to the local buses of two adjacent Processing Elements. The Processing Elements communicate over the local area network via their network stations HS<sub>i</sub> which are also connected to the local buses. The network interface, the H-Station is currently in the design stages. The submodule that is responsible for network acquisition within the H-Station has been designed using CMOS-VLSI technology has been sent for fabrication.

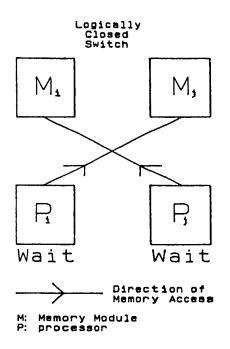

As stated previously, the Interbus Switches are used for nearest neighbour communication. When a processor accesses a neighbour's memory, an Extended bus is created. The switch physically extends a requesting processor's bus to include the memory module of the neighbour. At the same time it excludes the neighbouring processor from accessing its memory module.

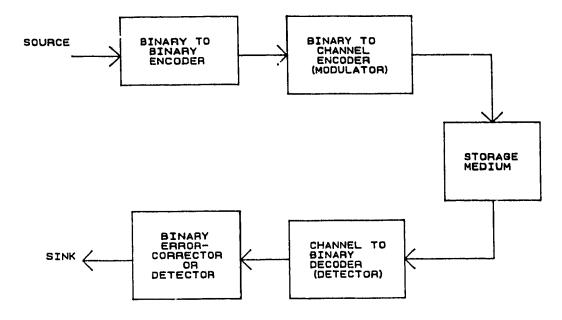

An Extended Bus is defined as the dynamic fusion of two neighbouring local buses effected through the closing of the intervening switch after a request from either or both processors adjacent to the Interbus Switch. Once this Extended Bus is created, it will exist for one memory access cycle, which is also the duration of the request. The creation of the extended bus comprises of two parts commonly known as Phase I and Phase II. Phase I, which is processor independent, ensures that deadlock scenarios will never exist and the operation of the switches are mutually exclusive. During Phase II, which is processor dependent, the switch physically closes. Once the first phase has completed with success, the second phase begins.

After the cycle, the Extended Bus deteriorates to its original separate local buses. Once this happens, the Interbus Switch is ready to comply with any pending or next request for an Extended Bus. More details on the operation of the Interbus Switch can be found in chapter 2.

The second method of communication is the H-Network. The H-Network is a high speed (approximately 7 Megabytes/second) Local Area Network similar in structure to the Ethernet. It differs in that it contains distinct pathways for data transmission, network acquisition, and collision detection. The signal propagation delay is extremely short because the H-Network has been designed with a span of the order of 10 meters. This, coupled with the parallelism of the distinct pathways has the effect of increasing the performance of the network.

The Homogeneous Multiprocessor is built on Versabus boards and utilizes the Versabus card cage. The Versabus system is used because at the time of adoption (circa 1982), it was the only 32 bit bus supported by Motorola. A note of interest is that the VME bus was adopted by Motorola in subsequent years. The Versabus has been modified for our purposes. The main connector has been left unmodified. This provides the processor memory interface, and it contains all the bus control signals coming out of the MC68000. The alternate or second connector, is used for access to neighbouring processors (using the Interbus Switch). The original purpose of the alternate connector of the bus was to extend it to 32 bit, as well as to provide I/O lines.

Architectural Innovation is present in the design of the Homogeneous Multiprocessor in that it is capable of behaving as a distributed system coupled through a fast local area network and as a tightly coupled pipeline of processors. Applications such as distributed file systems, distributed databases, distributed simulation, etc, exist in an ideal environment provided by the H-Network. Finally, algorithms such as the ones found in vision and digital signal processing, and relaxation processing can be implemented efficiently due to the Extended Bus mechanism.

At the time of this writing there are three Processing Elements that are fully operational (processor and memory subsystems). One of the Processing Elements contains 1 Megabyte of Dynamic RAM while the other two contain 0.5 Megabyte of Static RAM. In the memory design incorporating static memory it is possible to expand this to one

Megabyte. Included in the dynamic design, there is also error detection and correction which facilitates the most reliable and cost effective method for reducing corruption of data when using dynamic memories. The static memory design does not require error detection and correction due to the nature of the memory chips. As far as expandability is concerned, the only limiting factor is space and the addressing capabilities of the MC68000.

### 1.5.1 Performance Analysis of the Homogeneous Multiprocessor

The structure of the Homogeneous Multiprocessor has been simulated to obtain a performance evaluation. The simulator that was written is based on an 8 Milz MC68000 that implements the second phase of the interbus switch controller which is processor dependent. The first phase which is processor independent uses Algorithm 1.2 (described in chapter 2).

The behaviour of the Homogeneous Multiprocessor was obtained for two scenarios.

The first scenario simulates the performance of the system based on the demand to the Interbus switching network and the second scenario simulates a distributed algorithm.

The distributed algorithm determines the autocorrelation functions of a given signal.

The first simulation determined that the idle time of a processor never exceeded 30% of the total processing time. The idle time of a processor is attributed to waiting while a neighbouring processor accesses its memory module. Even in the most demanding cases, the idle time remained within acceptable bounds.

The results of the second simulation were as follows. The simulation comprised of 19 processors processing 1024 samples. This obtained a speed up factor of 11.85 which is approximately 62% of the theoretical value.[5]

#### 1.5.2 Software Design for the Homogeneous Multiprocessor

To provide users with a programming environment as well as controllable access to the hardware, an important feature to any computing system is the operating system. While constructing and testing the hardware, the operating system was being designed. Using the first prototype board, the lower layers of a preliminary single node operating system was tested and debugged. It should be noted that some hardware defects were uncovered through the operating system design.

One of the major concerns to the designers of the operating system for the Homogeneous Multiprocessor was to give to the users the raw architectural features in a usable fashion. The main objective in the design of the operating system was to enable the addition or subtraction of processing elements without having to do major redesigning in either the hardware or the software. The operating system is designed in a modular fashion thus enabling additional routines or software packages to be added to the system with grace and ease.

The operating system is based on a nucleus structure - the HM-Nucleus. It provides the basic mechanisms for utilising the the bare hardware. This enables resource management and application software to be conveniently built on top of it. Primitives for interprocess communication, capability checking, memory management, process management, an I/O handling are provided. Each processor has a copy of the nucleus residing in it. Therefore there is no globally shared memory in the Homogeneous Multiprocessor. When the HM-Nucleus is complete, an objective is to have the operating system utilities residing only in some nodes and applications will be assigned to them on demand. There will be no swapping of memory, an application will remain resident until execution is complete.[11]

## 1.6 Objectives of This Research

Summarizing, the objectives of the research presented in this thesis are the following. In chapter 2, the design and implementation of the Interbus Switch, as per the specifications, are presented. In appendix A and appendix B, the designs of the dynamic and static memory are presented, respectively. In appendix C, the numerical analysis and schematics for the interbus switch are provided. And finally in appendix D, the schematics for the Homogeneous Multiprocessor are presented.

In this thesis, the entire process of design and implementation for the memory systems is presented. For the Interbus Switch, the design, prototyping in discrete components and testing are presented, however, final implementation by using high density technology (eg. PLA / gate array) is yet to be accomplished.

#### 2. The Interbus Switch

The interbus switch is used to connect a processor's local bus to the bus of one of its neighbours. The primary objective of this scheme, is to enable a processor to access memory belonging to a neighbour, and thus establish interprocessor communication. This process of communication is accomplished by an extended bus. (An extended bus is formed by physically connecting the local buses of two neighbouring processors. This is accomplished by opening/closing appropriate intervening switches). In doing this, the processor has potential access to three memory modules. It can access its own memory (normally), the memory of its neighbour on the left, or its neighbour on the right (through the creation of an extended bus).

In order for the processor to access a memory module, it presents an address on the Interbus Switch Controller. The two most significant bits of the address are used to determine which memory module the processor wants to access. Shown in table 2.1 is the memory map that is used to determine which module the processor is requesting. From this point onward, it is up to the interbus switches to give access to the memory module in question.

Table 2.1: The Interbus Memory Map.

| A <sub>23</sub> | A <sub>22</sub> | Mapping             |  |

|-----------------|-----------------|---------------------|--|

| 0               | 0               | I/O                 |  |

| 0               | 1               | Memory on the Left  |  |

| 1               | 0               | Memory on the Right |  |

| 1               | ì               | Own Memory          |  |

Once the interbus switch intercepts the address, it will determine where the processor wants to access and then, depending on the surrounding environment, eventually allow access to the memory module in question. The processes that occur in the interbus switch are divided. The first process that occurs is identified as Phase I, followed by Phase II. Once these processes are completed, the memory access is granted.

Phase I determines whether it is safe to close the switch it controls. The determina-

tion of safe closure is based on the state of the two neighboring switches. If either one or both are physically closed, or is about to close, the present switch must stay open so as not to cause collisions on the extended bus.

Phase I, more commonly known as Logical Closure of the switch is used to determine the state(s) of the neighbouring switches. The state of the neighbouring switches is very important. If a neighbouring switch is Physically or Logically Closed, then Phase I must interpret this information and take an appropriate action in order not to cause collisions on the extendea bus. A collision could cause disastrous effects on the Homogeneous Multiprocessor.

Collisions can occur if for example, two processors are connected to the same memory module. If this were to happen, both processors would attempt to access the memory module, and their address lines would short with each other. Hence, a collision. Another example of a collision is if a processor is connected to two memory modules, and it attempts a read access. The data lines carrying the information from the memory modules would be shorted and a collision would occur. These types of occurrences must be prevented at all costs to ensure the proper operation of the software and hardware.

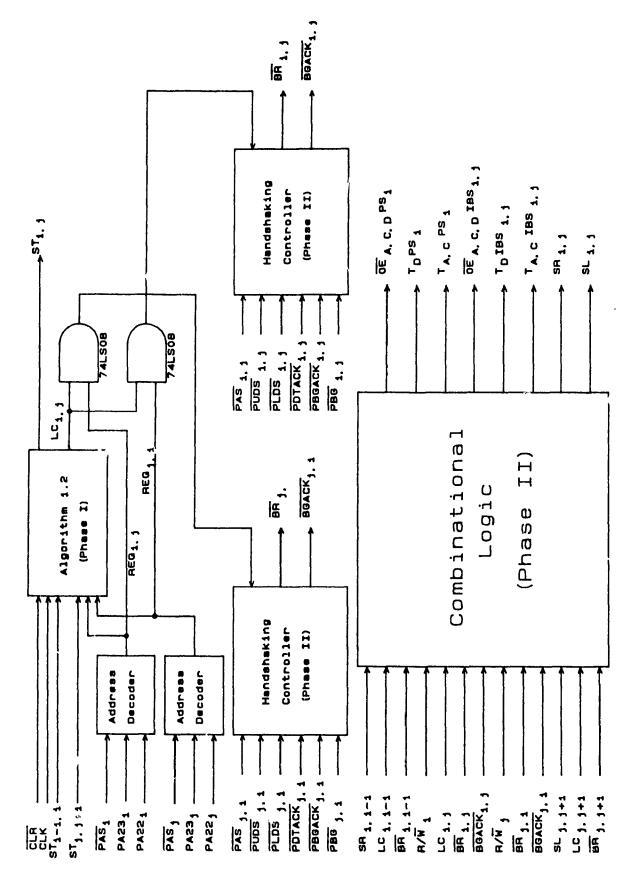

Phase II, also known as Physical Closure of the switch consists of two parts. The first part is a bus arbiter that adheres to the operation of the 68000 CPU. It uses the method of arbitration required by the 68000 CPU for a bus request that is identical in every respect to one that a coprocessor would adhere to. Once arbitration is completed (if necessary), various combinational circuits will Physically Open and/or Close the bus switches. Depicted in figure 2.1 is the block diagram of the Interbus Switch Controller (IBS<sub>1,1</sub>).

Figure 2.1: The Block Diagram of the Interbus Switch Controller.

#### 2.1 Phase I

As stated in the previous section, Phase I is used to determine the Logical Closure of a switch. The Logical Closure of the switch is based on an algorithm known as Algorithm 1.2.[5] Algorithm 1.2 describes a procedure required for the safe (i.e. no two adjacent switches will close at the same time) and live (i.e. a switch requested to close will eventually do so).

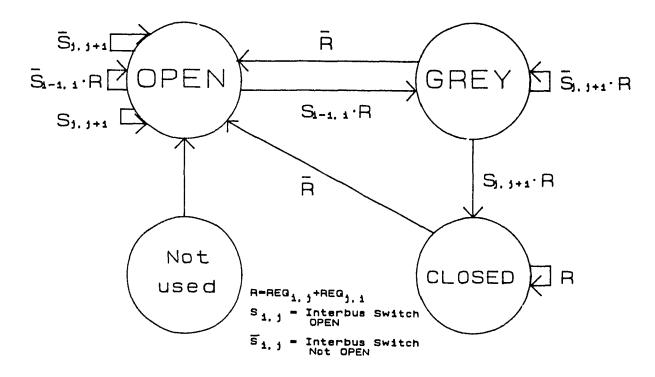

The switches exist in one of three states. They are Open, Grey, and Closed. Their definitions are as follows:

OPEN: This state signifies that no request exist or if a request exists it will not be honoured immediately, because a neighbouring switch is currently servicing a request.

GREY: This state signifies that a request is acknowledged and that service (i.e. switch closure) will be granted in the immediate future.

CLOSED: This state signifies that it is safe for a switch to close. The actual closure of the switch will take place during Phase II which commences immediately after a switch enters the Closed state.

For a switch IBS<sub>I,1</sub>

If no other request exists, it becomes Open;

Otherwise, if a request exists then:

If Open, it becomes Grey provided that the switch to its left,  ${\rm IBS}_{l-1,l}$ , is Open. Otherwise, it remains Open.

If Grey, it becomes Closed provided that the switch to its right, IBS<sub>1,j+1</sub>, is open.

Otherwise, it remains Grey.

If Closed, it remains Closed.

The leftmost switch IBS<sub>0,1</sub> and rightmost switch IBS<sub>n,n+1</sub> are always Open.

When a processor requests access to its neighbours' memory, the request remains asserted during the request period which terminates with an acknowledgement (from the

requested Memory Module to the requesting Processor). This request is intercepted by the appropriate Interbus Switch Controller and is forwarded to the requested Memory Module after the switch closes, then the Memory Module acknowledges the transfer of data to the requesting Processor, and the cycle terminates. Algorithm 1.2 guarantees the safe (i.e. no two adjacent switches will close at the same time) and live (i.e. a switch requested to close will eventually do so) operation of the network of Interbus Switches.

In order for a switch to actually close, the Processor of the requested Memory Module must take itself off the Local Bus, in order for the memory access to proceed without interference. We have tried to mak the Interbus Switch Controller compatible with the Motorola MC58000 CPU operating at a frequency of 8 MHz. Algorithm 1.2 requires three clock cycles to reach a stable state reflected by the number of transitions (Open-Grey-Closed). It is therefore expected that the state of the Phase I will stabilize within one CPU clock cycle (i.e. Phase I operating at least at 24 MHz).

## 2.1.1 Design and Implementation of Phase I

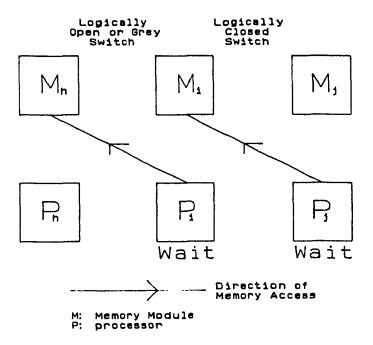

Shown in figure 2.2 below is the state diagram for Algorithm 1.2. R is the existence of a request which is determined by the logical OR of a request from the processor on the left, denoted as  $R_1$ , and a request from the processor on the right, denoted as  $R_1$ .  $ST_{l-1,l}$  is the status of the Interbus Switch on the left and  $ST_{l,l+1}$  is the status of the Interbus Switch on the right. The status indicators  $ST_{l,l}$  denote whether the switch is OPEN  $(ST_{l,l})$  or non-OPEN  $(\overline{ST_{l,l}})$ .

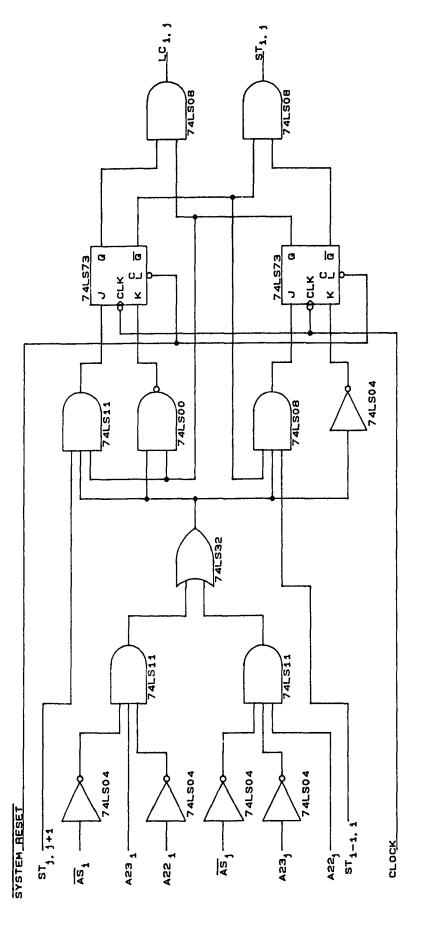

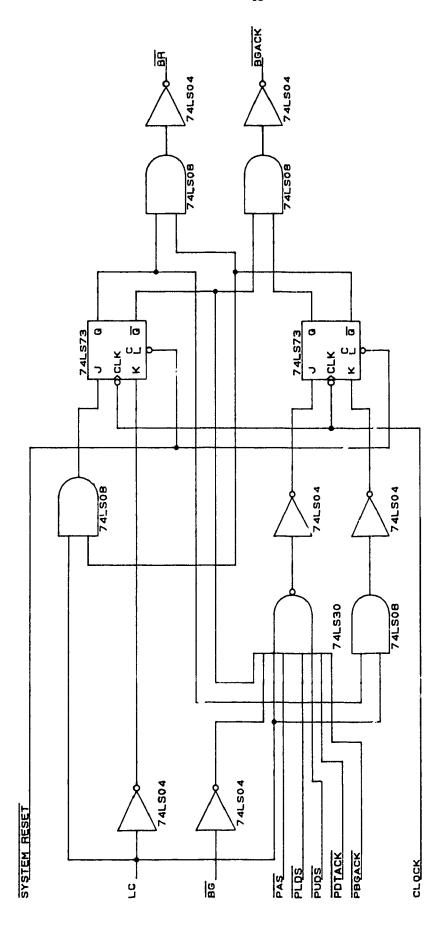

The hardware was designed and implemented to execute Algorithm 1.2. The design was carried out extensively to determine the minimum amount of integrated circuits required. The design was carried out using various state assignments and then determining the circuits using both J-K flip flops and D-type flip flops. Only the most efficient design procedure will be derived in the following text. The hardware consists of 2 J-K flip flops arranged as a three state machine. The fourth possible state that is not used is setup such that if it is ever entered, then the circuit will be forced into the initial state.

Shown in table 2.2 below is the state assignment for the machine which is derived from the state diagram.

Figure 2.2: State Diagram For Phase I.

Table 2.2: State Assignment For Phase I.

| State    | $Q_1 Q_0$ |

|----------|-----------|

| Open     | 0 0       |

| Grey     | 0 1       |

| not used | 10        |

| Closed   | 1 1       |

Upon power up or reset, the machine enters the OPEN state. If there is no request, the switch remains in the OPEN state. If the switch on the left, IBS<sub>I-1,I</sub> is non-OPEN and a request exists, then the machine also remains in the OPEN state. Once the switch on the left, IBS<sub>I-1,I</sub> opens, the machine changes to the GREY state. Once in the GREY state, if the request ceases to exist, then the machine returns to the OPEN state. Otherwise, if the request continues to exist and the switch on the right, IBS<sub>I,I+1</sub>, is non-OPEN, then the machine remains in the GREY state. If the switch on the right, IBS<sub>I,I+1</sub> is open and

the request still continues to exist, then the machine changes to the CLOSED state. Once in the CLOSED state, as long as the request exists, the machine will remain in the CLOSED state. When the request ceases to exist, then the machine returns to the initial OPEN state. The existence of a request is only dependent on the logical OR of the request line from the adjacent processing elements. As far as Phase I is concerned, it does not matter which processor exerts the request.

In the design of Phase I, only three of the four states are required. The operation of the sequential machine is quite simple. At first, the flip-flops are cleared, denoting the OPEN state. The first operation that will occur is changing  $Q_0$  from a logical 0 to a 1. This is equivalent to changing from the OPEN state to the GREY state. To allow the machine to enter into the GREY state, it must verify that the neighbouring switch on the left,  $IBS_{l-1,l}$  is open. The following equations, 2.1 and 2.2 denoted the equations for  $J_0$  and  $K_0$ , respectively.

$$J_0 = \overline{Q_1} \cdot R \cdot ST_{i-1,i} \tag{2.1}$$

$$K_0 = R \tag{2.2}$$

The first equation (2.1),  $J_0$  is used to change the sequential machine from the OPEN state to the GREY state. This is achieved by checking for the existence of the request R, the switch on the left,  $\mathbb{BS}_{l-1,l}$ , is OPEN, and that the machine is in the OPEN state ( $Q_1 = 0$ ). If at any time, the request (R) ceases to exist,  $K_0$ , equation 2.2, will return the flip flop to the initial state ( $Q_0 = 0$ ). The next two equations, 2.3 and 2.4 represent  $J_1$ , and  $K_1$ , respectively.

$$J_1 = Q_0 \cdot R \cdot ST_{J,J+1} \tag{2.3}$$

$$K_1 = \overline{Q_0 \cdot R} \tag{2.4}$$

The second flip-flop only comes into action once the first flip-flop is set, (GREY state). This is accomplished by  $J_1$  checking the existence of the request (R), the switch on the right (IBS<sub>J,J+1</sub>) is OPEN, and that the sequential machine is in the GREY state ( $Q_0 = 1$ ). If all of the above conditions are true, then the flip flop changes state putting

the sequential machine into the CLOSED state. Once in the CLOSED state, the machine will remain there until the request ceases to exist, as shown by equation 2.4. The other term in equation 2.4  $(Q_0)$  is used to reset the machine if it enters the unused state  $(Q_1Q_0=10)$ . The derivation of these equations can be found in Appendix C.

The schematic shown below in figure 2.3 is the hardware implementation of Algorithm 1.2. It is composed of five standard 74LSXX series chips. The inputs to the circuit are the address strobe and two most significant address bits of the processors on the left and right. Also, the status of the Interbus switchs on the left and right. There are also a clock and a clear. The clock is active all the time while the clear is only activated during power up or reset. Based upon the data sheets supplied by TI, the circuit should operate at least at 24 MHz so that the algorithm can run from Open to Closed in one CPU clock cycle (8 MHz) given that the neighbouring Interbus Switches are open. If one or both of the Interbus switches are not Open, then there will be a time delay before the Algorithm runs to completion. This is due to the waiting period until the neighbouring switch that is not Open returns to the Open state. At that point, the Algorithm will continue to run until it reaches the Closed state. Upon "power up" of the Multiprocessor, it is possible for Phase I to exist in the state 10 (not used), however, the reset signal that is supplied by the system at power up time, will force the switch to the open state. The Logical Closure signal is fully decoded and the unused state will not affect the operation. If by chance the sequential machine enters the unused state, the circuit is designed to force the machine into the reset state which will open the Interbus Switch.

Figure 2.3: Hardware Implementation For Phase I.

In the design of the hardware for Phase I, the following inputs were required: clear the flip-flops (denoted as  $\overline{CLR}$ ); a 24 MHz clock (denoted as CLK); the status of the neighbouring switches (denoted as  $ST_{l-1,l}$  and  $ST_{l,l+1}$ ); and the request inputs (denoted as  $R_l$  and  $R_l$ ). There are two outputs from Phase I, they are: Logical Closure (denoted as LC) which will be used as an input to Phase II; and the Status (denoted as ST) which is the status bit used for the neighbouring Switch Controllers.

The  $\overline{\text{CLR}}$  input is used to reset any flip-flops in Phase I during a power up or reset of the system. The CLK input is used to clock data into the J-K flip-flops that are used in Phase I. Requests are generated for an Interbus Switch to physically close via the  $R_1$  and  $R_1$  inputs. These inputs are obtained by using gates to check the upper two address bits and the address strobe  $(A_{23}, A_{22}, \text{ and } \overline{\text{AS}})$  of a processor. If the appropriate address and strobe are produced then the existence of a request is concrete. The status bits are used by Phase I to determine if a neighbouring switch is closed or about to close. This is important because two neighbouring switches should never be closed at the same time. These inputs are obtained from the neighbouring Phase I circuits. They are the Status outputs (ST).

The Logical Closure (LC) is used to inform Phase II that it may start its own procedure which is described below. The status output is used as an input to the neighbouring Phase Is. Each Phase I has two status bits, one from the neighbour on the left, and the other from the neighbour on the right. Therefore the neighbouring Phase Is will use the ST output to determine the status of this switch. As long as this switch is not Gray or Closed, the ST signal will be active.

#### 2.2 Phase II

Once Phase I has run to completion (i.e. in the Closed state), Phase II begins. During Phase II, the Physical Closure of the switch is accomplished. Phase II consists of two parts, one of them is a handshaking controller which conforms to the protocol of Mastering the Bus of a MC68000 Processor (i.e. equivalent to that of a DMA for example), and

--

the second is an arbiter. The purpose of the arbiter is to resolve potential deadlocks in the system.

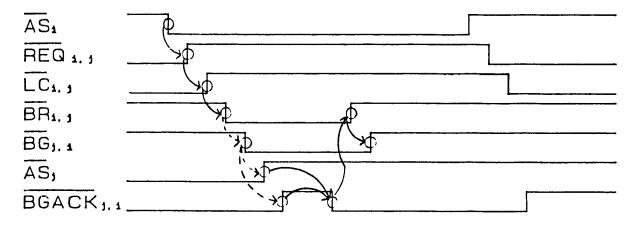

In the simplest case, the requesting processor in Phase II will output a Bus Request ( $\overline{BR}$ ) to a neighbouring processor for its memory. It will then wait until it receives a Bus Grant ( $\overline{BG}$ ). Finally the requesting processor will issue its own Bus Grant Acknowledge ( $\overline{BGACK}$ ) at the end of the previous cycle (i.e. when all  $\overline{AS}$ ,  $\overline{DTACK}$ ,  $\overline{UDS}$  and  $\overline{LDS}$  at the bus of the requested processor are negated) for the duration of the memory access. Once the memory access is completed, the  $\overline{BGACK}$  is removed and normal processing continues. Refer to figure 2.4 for the proper timing for Mastering the Bus. However, as stated previously, this is not always the case. The deadlock situations (discussed below) occasionally interfere with this protocol. Therefore some extra hardware is required to rectify this p: blem.

Figure 2.4: Timing Diagram For Mastering the Bus.

As previously stated, Phase II must first check for potential deadlocks in the system before it allows the arbiter to start (i.e. activate the  $\overline{BR}$ ). There are three cases of potential deadlock. Each one of them will be discussed in the following sections. A deadlock can occur when two adjacent processors request the same switch to close. Upon the completion of Phase I, the processors are waiting for a Bus Grant ( $\overline{BG}$ ). However, if the processor that is supposed to assert this Bus Grant is itself waiting for a Bus Grant

then, both processors will wait indefinitely and hence never complete the pending Extended Memory access cycles. Phase II has been designed to recognize these potential deadlock cases and resolve them by giving priority to one of the requesting processors.

In the first case of potential deadlock, two adjacent processors request the Interbus Switch located in between them to close as shown in figure 2.5. According to the asynchronous bus protocol of the processors, each processor will wait for the Data Transfer Acknowledge (DTACK) from the Memory Module they have requested, respectively. The DTACK will never arrive due to the deadlock and hence the memory access cycle can never run to completion. Ideally, Phase II would request the bus from one of the two processors and wait for the Bus Grant (BG) which would be asserted from the requested processor at the end of its current bus access cycle. Since both processors are in the middle of a bus access cycle waiting for the Interbus Switch to close, they will not assert the Bus Grant until they finis: their bus access cycle and at the same time they cannot complete the access cycle because the Interbus Switch is waiting for their Bus Grant in order to close the Interbus Switch to allow them to complete their access cycles.

Figure 2.5: Case I of Potential Deadlock.

Phase II will resolve this case of potential deadlock by first granting access to the processor located on the light side of the Interbus Switch. This is accomplished by forcing the processor located on the left of the Interbus Switch off the bus. Then the processor on the right will complete its Extended Memory access by receiving the DTACK. Finally the processor on the left, which has been waiting for this to occur will be granted the bus allowing it to complete its Extended Memory access cycle.

The second case of potential deadlock is depicted in figure 2.6. In this scenario two adjacent processors,  $P_i$  and  $P_j$ , request their neighbours memory modules on the left,  $M_{i-1}$  and  $M_i$ , respectively. Both of the processors initiate a bus access cycle and issue Bus Requests to Interbus Switches,  $IBS_{i-1,1}$  and  $IBS_{i,j}$ , respectively. Now, if processor  $P_j$  requests switch  $IBS_{i,j}$  to close at the same time or earlier than processor  $P_i$  requests switch  $IBS_{i-1,1}$  to close, then according to Algorithm 1.2, switch  $IBS_{i,j}$  will eventually Logically Close while switch  $IBS_{i-1,1}$  will remain either Logically Open or Logically Gray.

At this point, processor P<sub>j</sub> is in the middle of Phase II, having asserted its Bus Request and awaiting a Bus Grant. Processor P<sub>j</sub> has asserted the appropriate address on the bus and is in the middle of Phase I, but not yet Logically Closed. Now, even though processor P<sub>j</sub> has not yet reached Phase II, it still cannot assert a Bus Grant to processor P<sub>j</sub> because it is waiting to complete its memory cycle in order to do so. It is waiting for Interbus Switch IBS<sub>1,j</sub> to become Logically Open in order to finish its cycle. Interbus Switch IBS<sub>1,j</sub> cannot become Logically Open until processor P<sub>j</sub> completes its own Extended Memory access cycle, which at the moment is waiting for processor P<sub>j</sub> to assert the Bus Grant. Hence, the deadlock situation.

The potential deadlock situation is corrected in Phase II by granting mastership of the bus to the processor on the right, P<sub>j</sub>. During this time processor P<sub>l</sub> waits for processor P<sub>l</sub> to complete its Extended Memory access cycle. Once completed, processor P<sub>l</sub> will eventually become Logically Closed and then assert the Bus Request for the bus and wait for the Bus Grant to complete its own Extended Memory access cycle.

Finally, the third case of potential deadlock. As shown in figure 2.7, it is very similar to the previous situation. In this case, processors  $P_i$  and  $P_j$  request the memory modules of the neighbours on their right,  $M_j$  and  $M_{j+1}$ , respectively.

In this situation, processor  $P_i$  has completed Phase I and now has the Logical Closure required to start Phase II. At the same time, processor  $P_i$  has requested its neighbouring memory by outputting the appropriate address but it is in the Logical Open state due to Algorithm 1.2 (i.e. the neighbour on the left is Logically Closed, therefore wait). Now, processor  $P_i$  is waiting for the Bus Grant from processor  $P_i$ , but it will never appear because processor  $P_i$  is itself in the middle of a memory access cycle which can only be completed once it becomes Logically Closed and runs through Phase II and eventually receives its  $\overline{DTACK}$ .

Figure 2.6: Case II of Potential Deadlock.

Figure 2.7: Case III of Potential Deadlock.

Phase II will resolve this case of potential deadlock by forcing processor P<sub>j</sub> off the bus. Then processor P<sub>i</sub> completes its Extended Memory access cycle and finally processor P<sub>j</sub> receives the bus to complete its own Extended Memory access cycle.

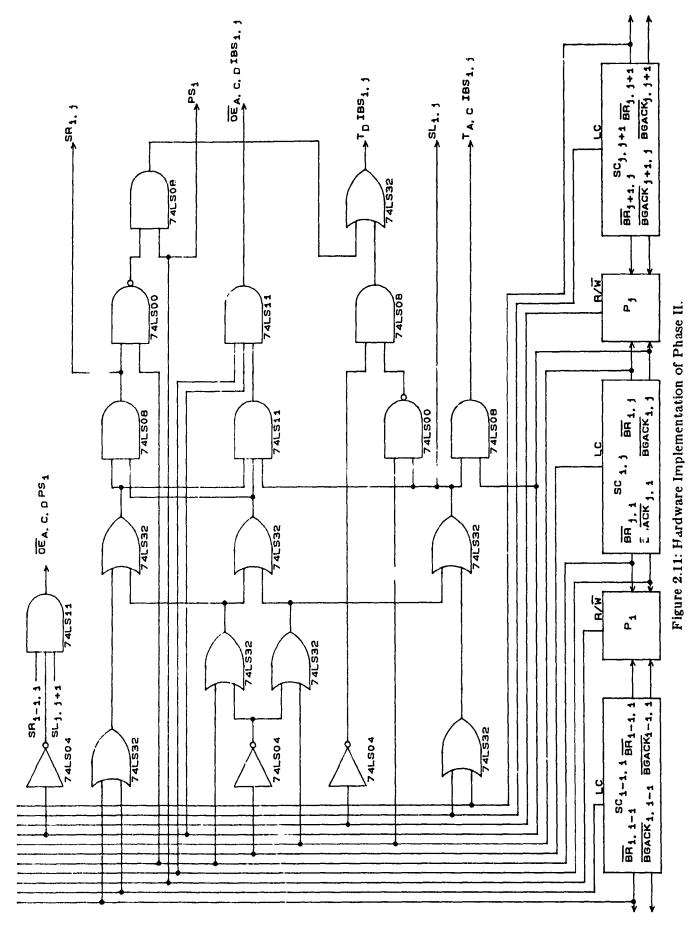

## 2.2.1 Design and Implementation

In this section we present the design of Phase II. Phase II, consists of two parts, the first part is a simple three state sequential machine that is used for mastering the bus (i.e. for a processor to obtain the neighbours bus). The second part of Phase II is the switch controlling circuitry which consists of two parts. The switch controller must operate the switches during normal access which consists of regular processor - memory interactions and processor - neighbouring memory interactions. The second part must also resolve the three cases of potential deadlock so that processing can continue.

In order for a processor to obtain the neighbours bus, the handshaking described in the previous section must be implemented. The processor that makes the request puts the appropriate address on the bus. This then generates the request R. Eventually, the Logical Closure appears from Phase I. These two signals logically ANDed create an

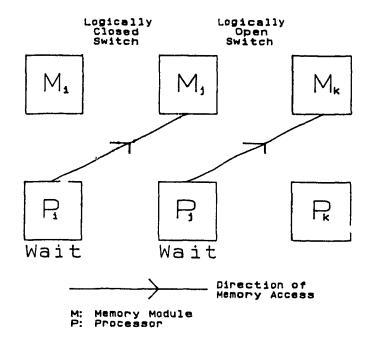

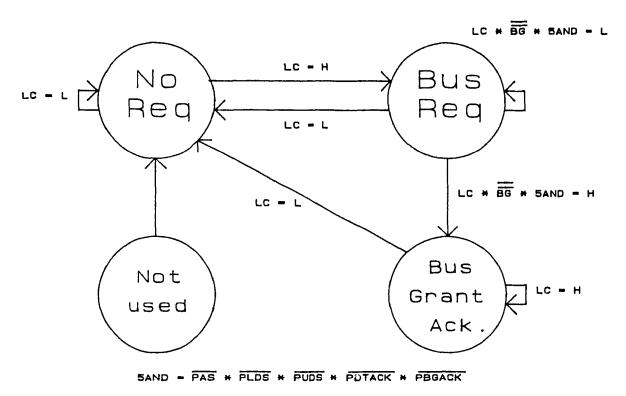

enable line for the handshaking signal. This enable is required because there will be two of these circuits in each of the Interbus Switch Controllers. One of them is for the processor on its left to obtain the bus of the processor on its right, and the other for the processor on its right to obtain the bus of the processor on its left. Since the Logical Closure does not in any way describe which processor wants to access the bus of the other, two separate enables are required. Figure 2.8 depicts the state diagram for the handshaking required during Phase II.

Figure 2.8: State Diagram for Handshaking During Phase II.

As stated earlier, the handshaking can only begin once both the Logical Closure and the Request are asserted. The first state, A, represents the sequential machine when neither the  $\overline{BR}$  nor the  $\overline{BGACK}$  are asserted. Once the Logical Closure and Request signals are active, the machine enters state B. During state B, the  $\overline{BR}$  is asserted and the machine waits for the requested processor to assert its  $\overline{BG}$  and at the same time wait for the current cycle of the requested processor to reach completion by negating its  $\overline{BGACK}$ ,  $\overline{AS}$ ,  $\overline{LDS}$ ,  $\overline{UDS}$ , and  $\overline{DTACK}$ . Once this occurs, the sequential machine enters state C.

While in state C, the BGACK gets asserted and the requested processor will inactivate its BG. During the time that the BGACK is active, the requesting processor has control of the requested processors bus (unless there is a potential deadlock). When the requesting processor finishes its cycle, i. removes the address and address strobe from the bus, thereby deactivating the request R, causing the handshaking controller to return to the initial state. Shown in table 2.3 below is the state assignment for the revised state diagram.

Table 2.3: State Assignment for the Handshaking in Phase II.

| State  | $Q_1$ | $Q_{o}$ |

|--------|-------|---------|

| NO REQ | 0     | 0       |

| BR     | 0     | 1       |

| BGACK  | 1     | 1       |

| N.U.   | 1     | 0       |

The Following are the equations that describe the handshaking controller.

$$J_0 = \overline{Q}_1 \cdot LC \tag{2.5}$$

$$K_0 = \overline{LC} \tag{2.6}$$

$$J_{1} = Q_{0} \cdot LC \cdot \overrightarrow{BG} \cdot \overrightarrow{PAS} \cdot \overrightarrow{PDTACK} \cdot \overrightarrow{PUDS} \cdot \overrightarrow{PLDS} \cdot \overrightarrow{PBGACK}$$

(2.7)

$$K_1 = \overline{Q_0} + \overline{LC} \tag{2.8}$$

$$\overline{BR} = \overline{Q_1 \cdot Q_0} \tag{2.9}$$

$$\overline{BGACK} = \overline{Q_1 \cdot Q_0} \tag{2.10}$$

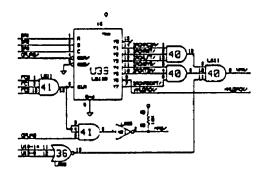

Shown in figure 2.9, the hardware implementation for the handshaking during Phase II.

Figure 2.9: Hardware Implementation for Handshaking During Phase II.