### Power Reduction Techniques in Clock Distribution Networks with Emphasis on LC Resonant Clocking

Seyed Ebrahim Esmaeili

A Thesis In the Department of Electrical and Computer Engineering

### Presented in Partial Fulfillment of the Requirements For the Degree of Doctor of Philosophy at Concordia University Montreal, Quebec, Canada

July 2011

© Seyed Ebrahim Esmaeili, 2011

#### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Seyed Ebrahim Esmaeili

Entitled: Power Reduction Techniques in Clock Distribution Networks with Emphasis on LC Resonant Clocking

and submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY (Electrical & Computer Engineering)

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|                   | Chair                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------|

| Dr. G. Gouw       |                                                                                               |

|                   | External Examiner                                                                             |

| Dr. E.G. Friedman |                                                                                               |

|                   | External to Program                                                                           |

| Dr. A. Youssef    |                                                                                               |

|                   | Examiner                                                                                      |

| Dr. R. Raut       |                                                                                               |

|                   | Examiner                                                                                      |

| Dr. C. Wang       |                                                                                               |

|                   | Thesis Co-Supervisor                                                                          |

| Dr. A. Al-Khalili |                                                                                               |

|                   | Thesis Co-Supervisor                                                                          |

| Dr. G. Cowan      |                                                                                               |

| oved by           |                                                                                               |

|                   | Chair of Department or Graduate Program Director<br>Dr. M. Kahrizi, Graduate Program Director |

| 1, 2011           |                                                                                               |

|                   | Dr. Robin A.L. Drew, Dean                                                                     |

|                   | Faculty of Engineering & Computer Science                                                     |

#### ABSTRACT

# Power Reduction Techniques in Clock Distribution Networks with Emphasis on LC Resonant Clocking

Seyed Ebrahim Esmaeili, Ph.D. Concordia University, 2011

In this thesis we propose a set of independent techniques in the overall concept of LC resonant clocking where each technique reduces power consumption and improve system performance.

Low-power design is becoming a crucial design objective due to the growing demand on portable applications and the increasing difficulties in cooling and heat removal. The clock distribution network delivers the clock signal which acts as a reference to all sequential elements in the synchronous system. The clock distribution network consumes a considerable amount of power in synchronous digital systems. Resonant clocking is an emerging promising technique to reduce the power of the clock network. The inductor used in resonant clocking enables the conversion of the electric energy stored on the clock capacitance to magnetic energy in the inductor and vice versa.

In this thesis, the concept of the slack in the clock skew has been extended for an LC fully-resonant clock distribution network. This extra slack in comparison to standard clock distribution networks can be used to reduce routing complexity, achieve reduction in wire elongation, total wire length, and power consumption. Simulation results illustrate that by utilizing the proposed approach, an average reduction of 53% in the number of wire elongations and 11% reduction in total wire length can be achieved.

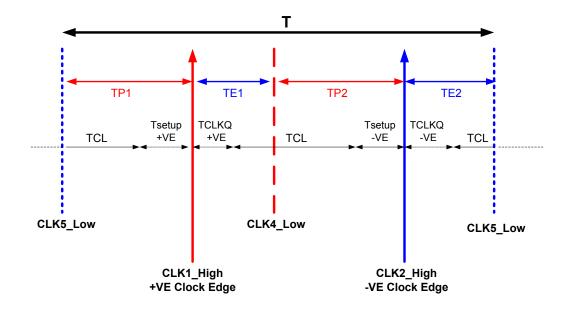

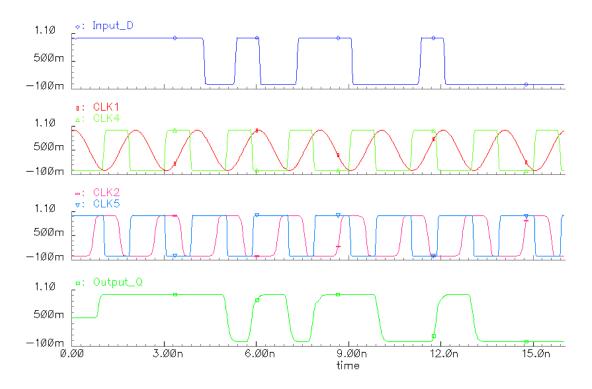

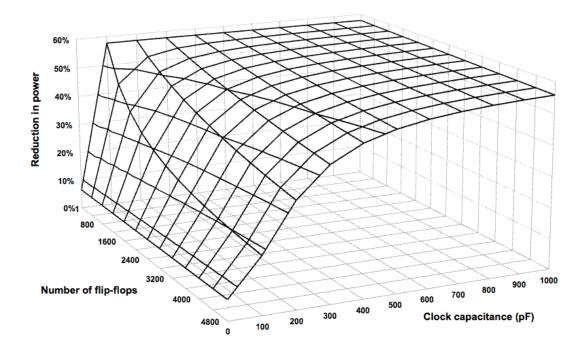

A dual-edge clocking scheme introduced in the literature to enable the operation of the flip-flop at the rising- and falling edges of the clock has been modified. The interval by which the charging elements in the flip-flop are being switched-on was reduced causing a reduction in power consumption. Simulating the flip-flop in STMicroelectronics 90-nm technology shows correct functionality of the Sense Amplifier flip-flop with a resonant clock signal of 500 MHz and a throughput of 1 GHz under process, voltage, and temperature (PVT) variations. Modeling the resonant system with the proposed flip-flop illustrates that dual-edge compared to single-edge triggering can achieve up to 58% reduction in power consumption when the clock capacitance is the dominating factor.

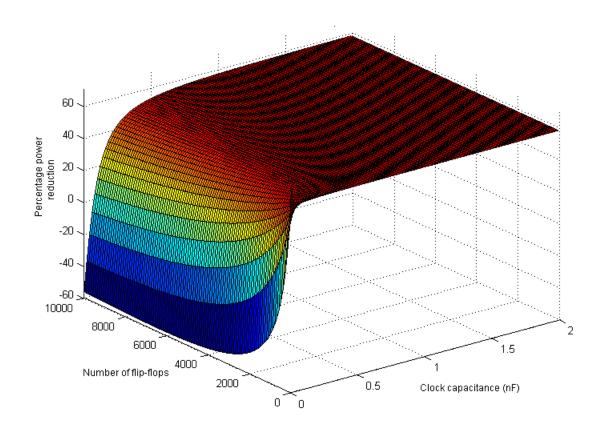

The application of low-swing clocking to LC resonant clock distribution network has been investigated on-chip. The proposed low-swing resonant clocking scheme operates with one voltage supply and does not require an additional supply voltage. The Differential Conditional Capturing flip-flop introduced in the literature was modified to operate with a low-swing sinusoidal clock. Low-swing resonant clocking achieved around 5.8% reduction in total power with 5.7% area overhead. Modeling the clock network with the proposed flip-flop illustrates that low-swing clocking can achieve up to 58% reduction in the power consumption of the resonant clock.

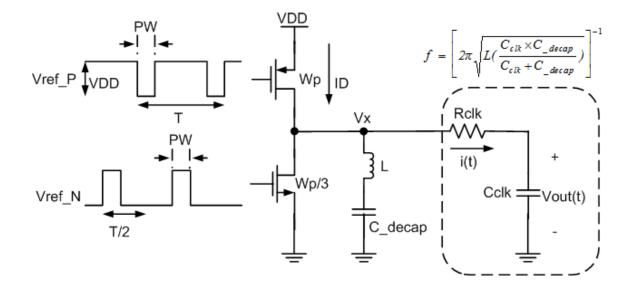

An analytical approach was introduced to estimate the required driver strength in the clock generator. Using the proposed approach early in the design stage reduces area and power overhead by eliminating the need for programmable switches in the driving circuit.

### Acknowledgments

I would like to express my sincere and profound gratitude to my supervisors, Prof. Asim Al-Khalili and Dr. Glenn Cowan for their guidance and generous support. I was truly blessed for working under their supervision. This work would never have been done without their valuable advice, criticism, experience, and insight.

I want to thank my thesis defense committee members: Dr. Eby Friedman, Dr. Amr Youssef, Dr. Rabin Raut, and Dr. Chunyan Wang for their helpful comments and suggestions. Special thanks go to my external examiner, Dr. Eby Friedman, for the time he took to read my dissertation. His comments and insightful suggestions helped me enhance this work significantly.

I am grateful to Prof. Yousef Shayan of the ECE Department at Concordia University for his permission to use the equipments in the Wireless Lab for chip testing. Special thanks to Prof. Mojtaba Kahrizi and his Ph.D. student Svetlana Spitsina for taking chip images using the microscope in the Nano Lab. Also, thanks to Tadeusz Obuchowicz for his prompt feedback and help in solving some of the problems faced with Cadence even during weekends and especially his kind help in running the TSMC 90-nm kit before the tape-out deadline. I would like also to thank Dave Chu from the ECE workshop for lending me the "T" fitting for BNC connectors. Thanks to the ECE staff members, Pamela, Diane, Connie, Lyne, Tatyana, and Kimberly for all their kindness and help. I am also grateful to CMC, especially Hsu L. Ho, Jim J. Quinn, Sarah. J. Neville, Kathryn K. Campbell, and Mariusz Jarosz for their help in facilitating chip fabrication and for loaning us the Agilent 81130 pattern generator. I thank my friend Ali Farhangi for his cooperation with me in the skew compensation scheme, specifically in writing the C++ code for the MDME Algorithm. I am also grateful to all of my friends in the office, in the VLSI group, and my roommates.

To my mother, I cannot really express what I feel. I know that these years were harder on you than they were on me. Thank you for your kindness, support, and for your prayers. I am grateful to my parents, sister, and two brothers for their support during my long academic journey.

I am in debt to my wife Hanan Al-Hashemi who had the patience to wait for me during these long years, the courage to take care of our children Hashem and Yasmin in my absence, and for making me laugh even at the saddest of moments. I thank Hashem for being the man of the house and I apologize to Yasmin for missing her first word and her first step. I promise that I will do my best to make it up to all of you, especially Yasmina.

I would like to thank Canada, this friendly and beautiful country who welcomed me with open arms. Thank you for restoring my belief in myself, humanity, and equality, basic principles that I had lost faith in before coming here.

Last but not least, I would like to use this last paragraph in remembering my uncle Is'haq who passed away in Bahrain during my Ph.D. and I was not able to attend his funeral. I still cannot believe that you left us and my eyes always fill up with tears whenever I think of you.

To everybody who knew me, helped me, or wished me luck, thank you.

## Dedication

To my beloved parents, wife, son, daughter.

### Contents

| List of Figures                                                          | xi            |

|--------------------------------------------------------------------------|---------------|

| List of Tables                                                           | XV            |

| List of Acronyms                                                         | xvi           |

| Chapter 1 Introduction                                                   | 1             |

| 1.1 Motivation                                                           | 1             |

| 1.2 Contributions                                                        | 2             |

| 1.3 Dissertation Overview                                                | 4             |

| Chapter 2 Background                                                     | 6             |

| 2.1 Clock Distribution Network Design Objectives                         | 6             |

| 2.1.1 Clock Skew                                                         | 6             |

| 2.1.2 Clock Jitter                                                       | 7             |

| 2.1.3 Clock Power                                                        | 7             |

| 2.2 Clock Distribution Network Structure                                 | 8             |

| 2.3 Resonant Clocking Techniques                                         | 10            |

| 2.3.1 Standing-Wave Resonant Clocking                                    | 11            |

| 2.3.2 Rotary Traveling-Wave Resonant Clocking                            | 13            |

| 2.3.3 LC Resonant Clocking                                               | 15            |

| 2.3.3.1 LC Globally-Resonant Locally-Square Clock Distribution Networ    | <b>·ks</b> 16 |

| 2.3.3.2 LC Fully-Resonant Clock Distribution Networks                    | 20            |

| 2.4 Challenges Associated with LC Resonant Clocking                      | 21            |

| 2.4.1 Dependency of the Sinusoidal Clock Rise Time on Its Frequency      | 21            |

| 2.4.2 Area Occupied by the Inductor                                      | 23            |

| 2.4.3 Clock Gating                                                       | 24            |

| 2.5 Sinusoidally Clocked Flip-Flops                                      | 24            |

| 2.5.1 Differential Conditional Capturing Flip-Flop (DCCFF)               | 26            |

| 2.5.2 Single-Ended Conditional Capturing Flip-Flop (SCCFF)               | 27            |

| 2.6 Conclusion                                                           | 28            |

| Chapter 3 Skew Compensation in LC Resonant Clock Distribution Networks . | 29            |

|                                                                          |               |

| 3.1 Lower Skew Bounds for the Proposed Technique                          | 30                |

|---------------------------------------------------------------------------|-------------------|

| 3.2 Skew Compensation in Short and Long Delay Paths                       | 37                |

| 3.3 New Modified Differed Merge Embedding (DME) Algorithm                 | 43                |

| 3.4 Simulation Results                                                    | 49                |

| 3.4.1 Matched Delay Values for the SCCFF                                  | 49                |

| 3.4.2 Comparing Data, Clock, and Flip-Flop Power Consumption for the F    | <sup>r</sup> ast, |

| Standard, and Slow Versions of the SCCFF                                  | 53                |

| 3.4.3 Effects of Process, Supply Voltage, and Temperature Variation on Fl | ip-               |

| Flop Speed                                                                | 56                |

| 3.4.4 Clock Tree Construction Using the New Compensation Technique        | 59                |

| 3.5 Conclusion                                                            | 60                |

| Chapter 4 Dual-Edge Triggered Sense Amplifier Flip-Flop for LC Resonant ( | Clock             |

| Distribution Networks                                                     | 62                |

| 4.1 Introduction                                                          | 62                |

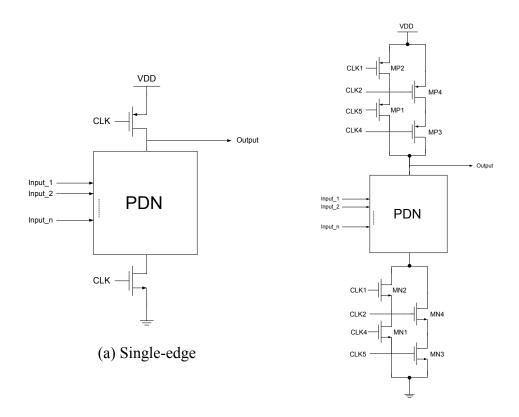

| 4.2. Dual-Edge Triggered Dynamic Logic                                    | 63                |

| 4.3. Dual-Edge Sense Amplifier Flip-Flop (DE-SAFF)                        | 66                |

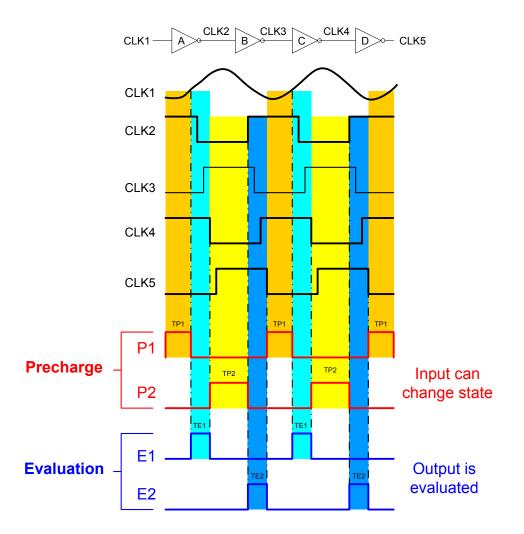

| 4.4. Timing Characterization of Dual-Edge Triggering                      | 69                |

| 4.5. Simulation Results                                                   | 71                |

| 4.5.1 Dual-Edge Flip-Flop Response at Positive and Negative Clock Edges,  | J                 |

| Schematic vs. Post Layout Simulation                                      | 72                |

| 4.5.2 Effects of Process, Supply Voltage, and Temperature (PVT) Variatio  | ns on             |

| the Generated Precharge and Evaluation Intervals                          | 74                |

| 4.5.2.1 Corner Analysis                                                   | 75                |

| 4.5.2.2 Supply Voltage                                                    | 77                |

| 4.5.2.3 Temperature Variation                                             | 78                |

| 4.5.2.4 Extreme Case                                                      | 79                |

| 4.5.3 Sharing the Inverter Chain                                          | 80                |

| 4.5.4 Comparing the DE-SAFF to Other Flip-Flops                           | 81                |

| 4.5.5 Potential Power Savings Achievable Through Dual-Edge Clocking       | 83                |

| 4.6 Conclusion                                                            | 86                |

| Chapter 5 Application of Low-Swing Clocking to LC Resonant Clock I | Distribution |

|--------------------------------------------------------------------|--------------|

| Networks                                                           | 88           |

| 5.1 Introduction                                                   | 89           |

| 5.2 Low-Swing LC Resonant Clocking                                 | 89           |

| 5.2.1 Low-Swing Differential Conditional Capturing Flip-Flop (LS-  | DCCFF) 89    |

| 5.2.2 Delay Associated with Low-swing LC Resonant Clocking         | 91           |

| 5.2.3 Power                                                        |              |

| 5.3 Test Chip                                                      |              |

| 5.4 Test Chip Extracted Simulation and Measurements                |              |

| 5.5 Conclusion                                                     |              |

| Chapter 6 Estimating Required Driver Strength in the LC Resonant C | lock         |

| Generator                                                          |              |

| 6.1 Introduction                                                   | 105          |

| 6.2 Estimating Required Driver Strength                            | 107          |

| 6.3 Simulation Results                                             | 111          |

| 6.4 Conclusion                                                     |              |

| Chapter 7 Conclusion                                               | 114          |

| 7.1 Summary and Contributions                                      | 114          |

| 7.2 Future Work                                                    |              |

| References                                                         | 120          |

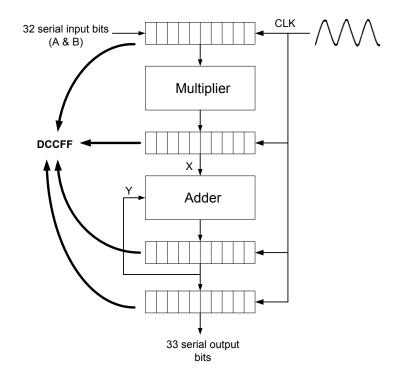

| Appendix A Multiply-Accumulate (MAC) Unit Design                   |              |

| A.1 Multiply-Accumulate (MAC) Unit Design                          |              |

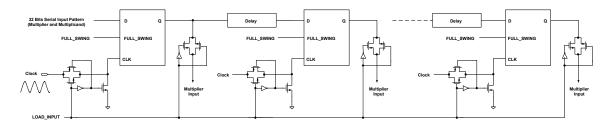

| A.1.1 Serial-In Parallel-Out Shift Register                        |              |

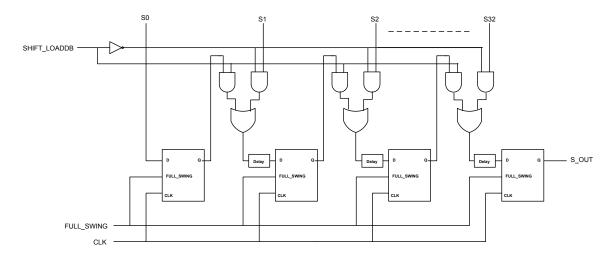

| A.1.2 Parallel-In Serial-Out Shift Register                        |              |

| A.2 Test Chip                                                      |              |

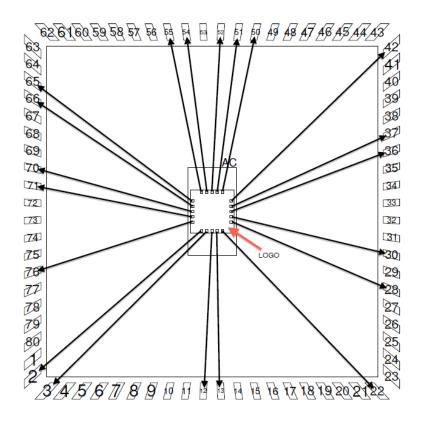

| A.2.1 Pad Description                                              |              |

| A.2.2 Chip Packaging and Test Fixture                              |              |

# **List of Figures**

| Figure 2.1: Schematic of a 3-D clock tree [12]                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2: Common structures of clock distribution networks [8]                                                              |

| Figure 2.3: Tree-driven grid global clock distribution [13] 10                                                                |

| Figure 2.4: Standing-wave clock distribution network [16] 12                                                                  |

| Figure 2.5: Clock buffer simulated performance [16] 12                                                                        |

| Figure 2.6: Basic rotary clock architecture. The "=" signs denote points with equal phase                                     |

| [19]                                                                                                                          |

| Figure 2.7: Custom rotary clock architecture [19]13                                                                           |

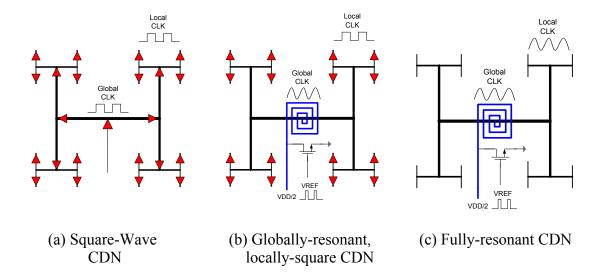

| <ul> <li>Figure 2.8: Simplified Square-wave, globally-, and fully-resonant CDNs</li></ul>                                     |

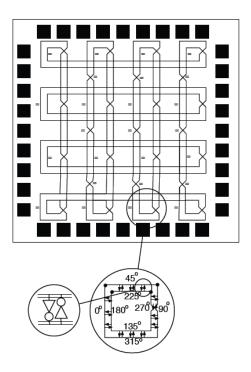

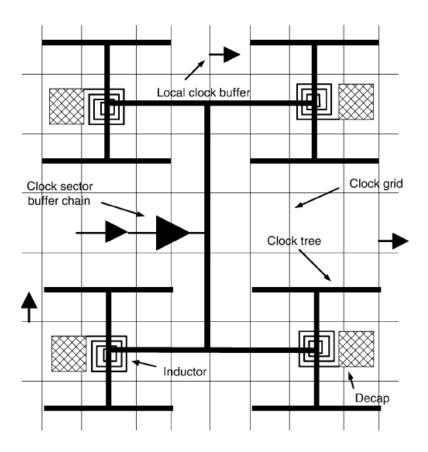

| <ul> <li>Figure 2.9: Globally-resonant locally-square clock distribution networks [23]</li></ul>                              |

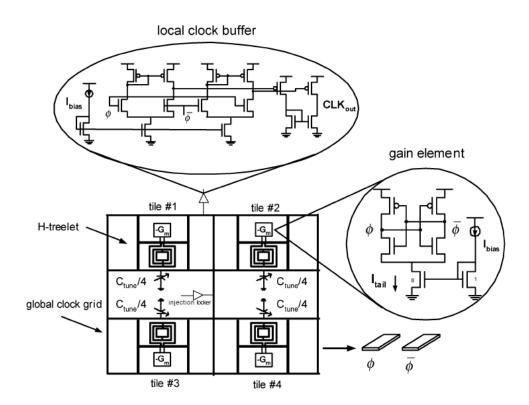

| Figure 2.10: Distributed differential oscillator (DDO) global clock network [25]19                                            |

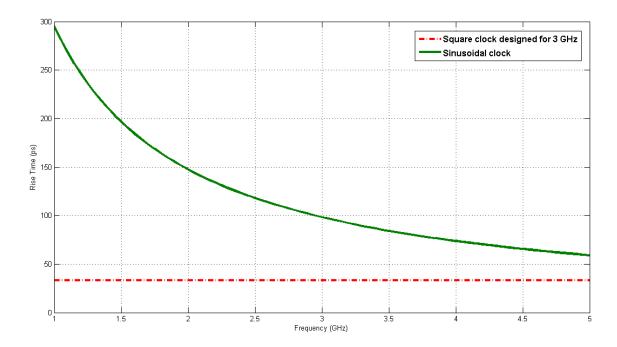

| Figure 2.11: Rise time of resonant and square-wave clock signal with rise time of 33ps 22                                     |

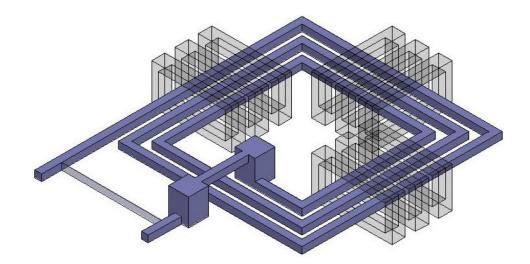

| Figure 2.12: Spiral inductor with magnetic ring structure [30] 23                                                             |

| Figure 2.13: Differential Conditional Capturing Flip-Flop (DCCFF)                                                             |

| Figure 2.14: Single-Ended Conditional Capturing Flip-Flop (SCCFF)                                                             |

| Figure 3.1: Effect of long rising time of the sinusoidal clock signal on the operating speed<br>of the flip-flop              |

| (b) Flip-flop $T_{DQ}$ vs. $T_{DCLK}$                                                                                         |

| <ul> <li>Figure 3.2: Effect of short rising time of the square clock signal on the operating speed of the flip-flop</li></ul> |

| <ul> <li>Figure 3.3: Using one version of the flip-flop</li></ul>                                                             |

| Figure 3.4: Using three versions of the flip-flop                                                                             |

| (b) Flip-flop output with respect to skewed clock                                                                          |        |

|----------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>Figure 3.5: Matched delay for short and long delay paths</li></ul>                                                | 38     |

| Figure 3.6: Sequentially adjacent flip-flops<br>(a) Positive skew<br>(b) Negative skew                                     | 40     |

| Figure 3.7: Tuning a merging segment by changing the flip-flop type in left or right tree.                                 |        |

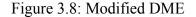

| Figure 3.8: Modified DME<br>(a) Clock tree topology<br>(b) Determining flip-flop type based on minimum wire length merging | 47     |

| <ul><li>Figure 3.9: Pseudo Code for modified DME algorithm</li></ul>                                                       |        |

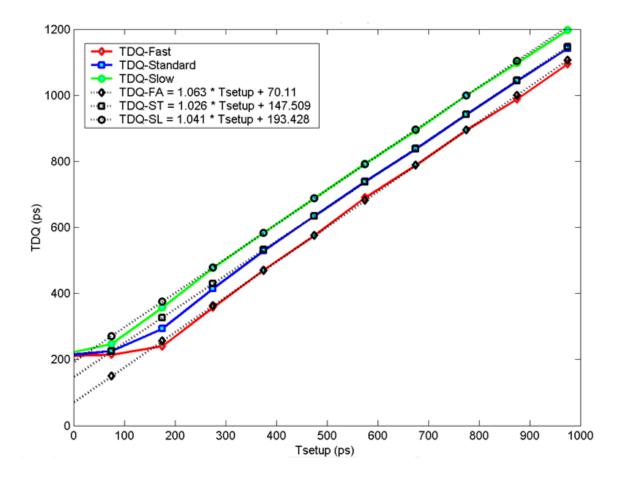

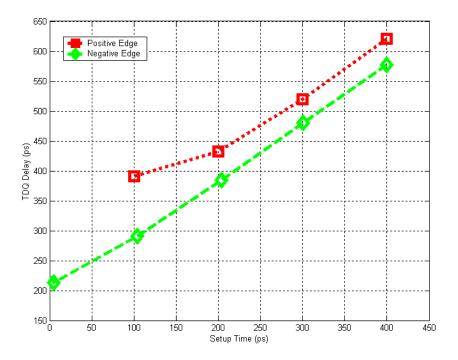

| Figure 3.10: T <sub>DQ</sub> vs. T <sub>setup</sub> (T <sub>DCLK</sub> )                                                   | 50     |

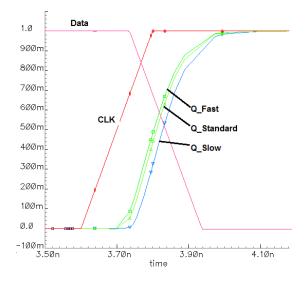

| Figure 3.11: Slow, standard and fast flip-flop response with respect to a square cloc signal                               |        |

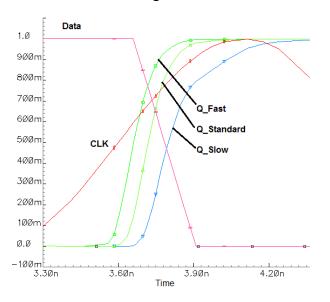

| Figure 3.12: Slow, standard and fast flip-flop response with respect to a sinusoidal signal                                |        |

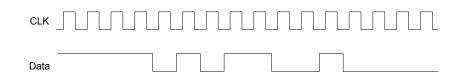

| Figure 3.13: Pseudorandom Sequence                                                                                         | 53     |

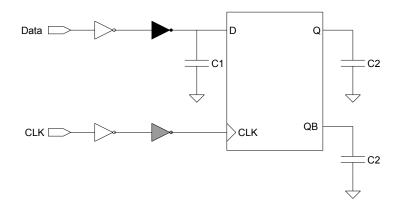

| Figure 3.14: Power measurement circuit                                                                                     | 55     |

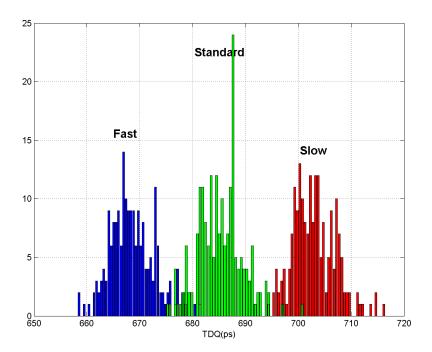

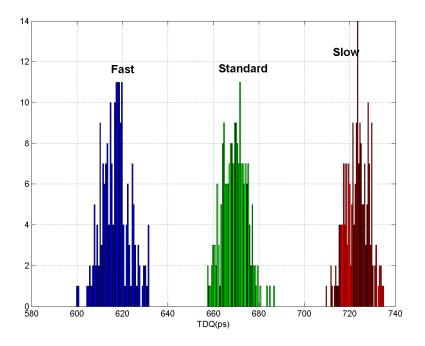

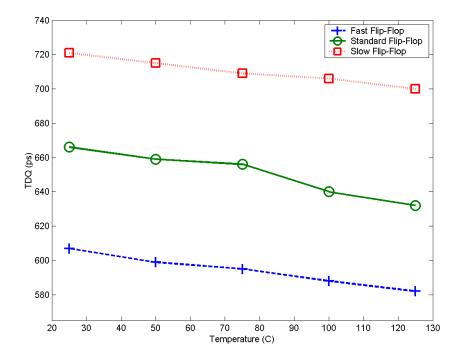

| Figure 3.15: Monte-Carlo simulation<br>(a) $T_{DQ}$ with a square clock<br>(b) $T_{DQ}$ with a sinusoidal clock            | 57     |

| Figure 3.16: Temperature effect on the TDQ delay                                                                           | 58     |

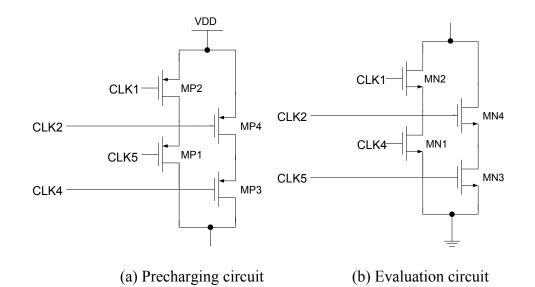

| Figure 4.1: Circuits used to enable precharging and evaluation at both clock transiti                                      | ons 64 |

| Figure 4.2: Clocking scheme used to enable dual-edge triggering in CMOS dynami                                             | -      |

| (a) Precharging circuit<br>(b) Evaluation circuit                                                                          | 64     |

| Figure 4.3: Single and dual-edge triggered dynamic CMOS logic<br>(a) Single-edge<br>(b) Dual-edge                          | 66     |

| Figure 4.4: Single-Edge Sense Amplifier Flip-Flop (SE-SAFF)                                                                | 67     |

| Figure 4.5: Dual-Edge Sense Amplifier Flip-Flop (DE-SAFF)                                                                  | 68     |

| Figure 4.6: Dual-edge triggering timing diagram                                                                      | 71    |

|----------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4.7: T <sub>DQ</sub> delay vs. T <sub>setup</sub> (T <sub>DCLK</sub> ), schematic simulation                  | 73    |

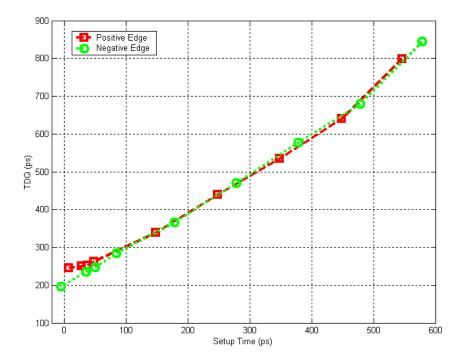

| Figure 4.8: T <sub>DQ</sub> delay vs. T <sub>setup_time</sub> (T <sub>DCLK</sub> ), post-layout simulation           | 73    |

| Figure 4.9: Effect of supply voltage variation on TP2                                                                | 78    |

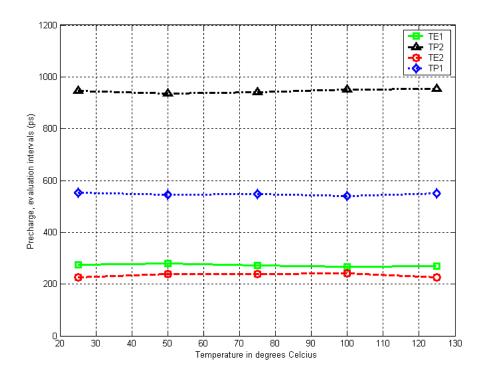

| Figure 4.10: Temperature variation effect on precharging and evaluation intervals                                    | 79    |

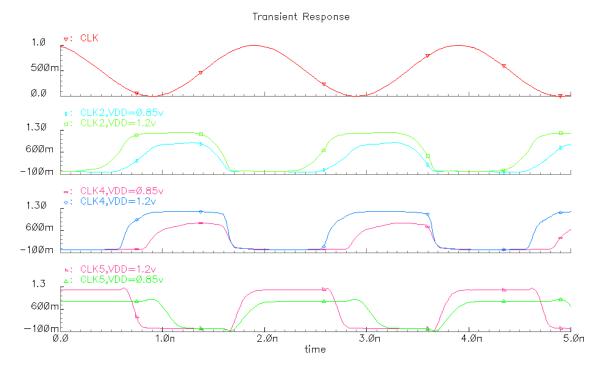

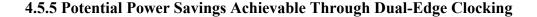

| Figure 4.11: Dual-edge triggered flip-flop output                                                                    | 83    |

| Figure 4.12: Dual-edge clocking percentage reduction in power                                                        | 86    |

| Figure 5.1: Low-Swing Differential Conditional Capturing Flip-Flop (LS-DCCFF)                                        | 90    |

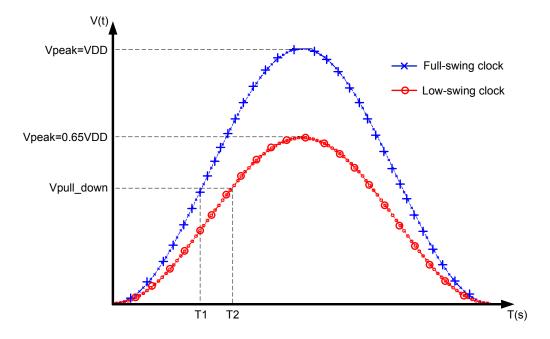

| Figure 5.2: Delay between the low- and full-swing resonant clock signals to reach $V_{pull\_down}$                   | 91    |

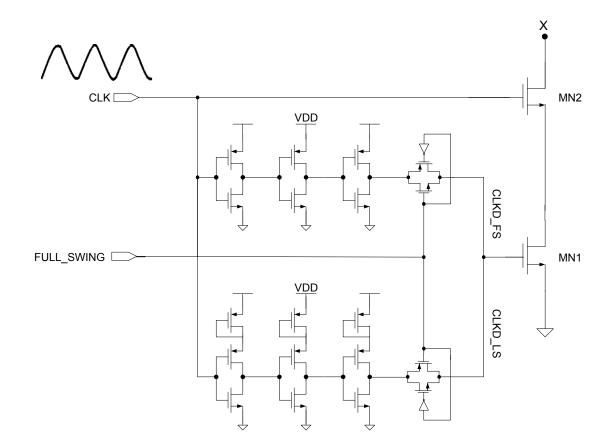

| Figure 5.3: Modification to enable full- and low-swing flip-flop clocking                                            | 94    |

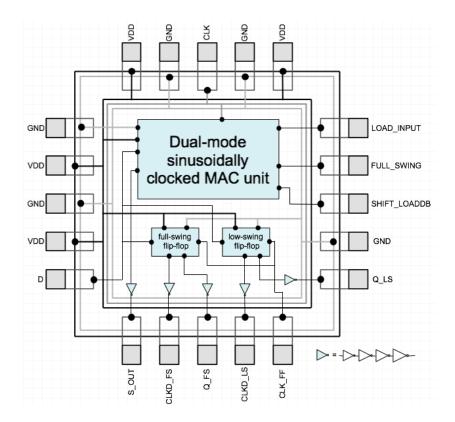

| Figure 5.4: Simplified floorplan of the test chip                                                                    | 95    |

| Figure 5.5: Die photopgraph of the test chip                                                                         | 95    |

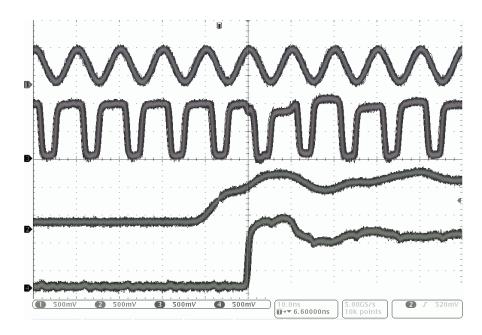

| Figure 5.6: Measurement waveforms of the LS-DCCFF at 100MHz                                                          | 97    |

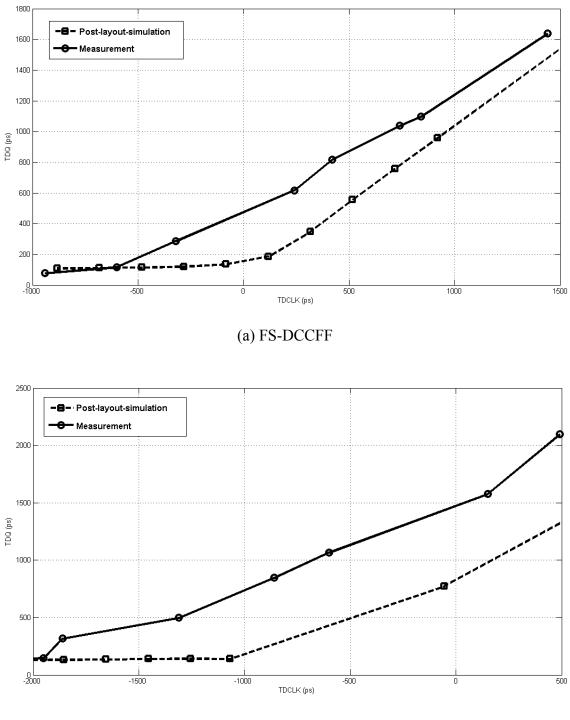

| <ul> <li>Figure 5.7: <i>T<sub>DQ</sub></i> delay versus setup time for the full- and low-swing flip-flops</li></ul>  | 98    |

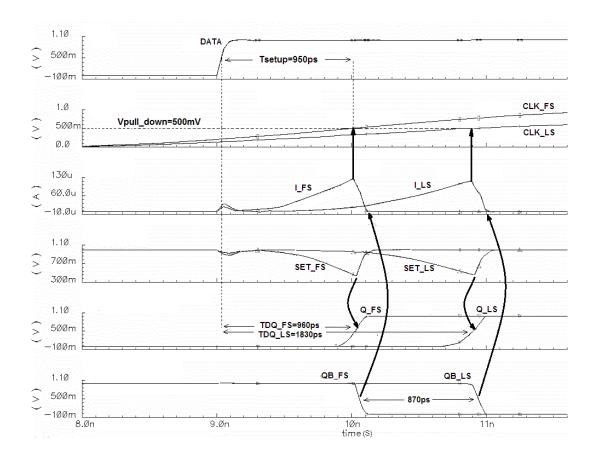

| Figure 5.8: $T_{DQ}$ for the full- and low-swing flip-flops at the same setup time – extracted simulation.           |       |

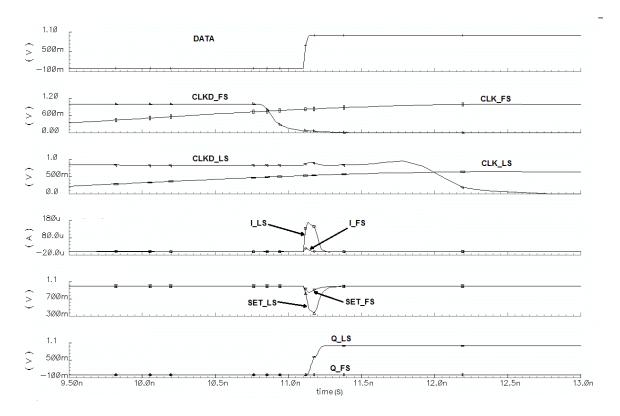

| Figure 5.9: $T_{DQ}$ for the full- and low-swing flip-flops at a negative setup time of -1,10 – extracted simulation |       |

| Figure 5.10: Percentage reduction in power for the resonant clock network achievable through low-swing clocking      |       |

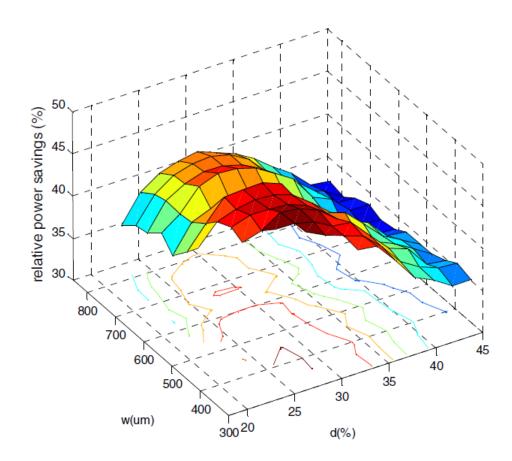

| Figure 6.1: Relative power savings as a function of driver transistor width (w) and reference signal pulse (d) [54]  | . 106 |

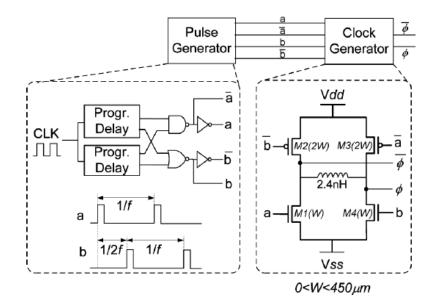

| Figure 6.2: Clock generator with programmable delay [55]                                                             | . 106 |

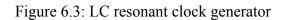

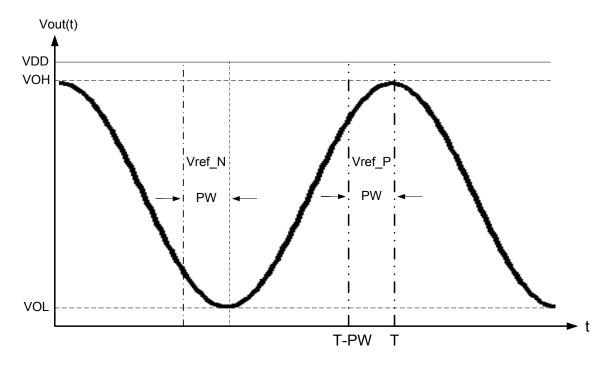

| Figure 6.3: LC resonant clock generator                                                                              | . 108 |

| Figure 6.4: Generated sinusoidal clock signal                                                                        | 108   |

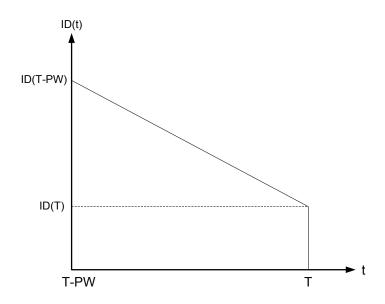

| Figure 6.5: PMOS drain current during the application of Vref_P                                                      | . 110 |

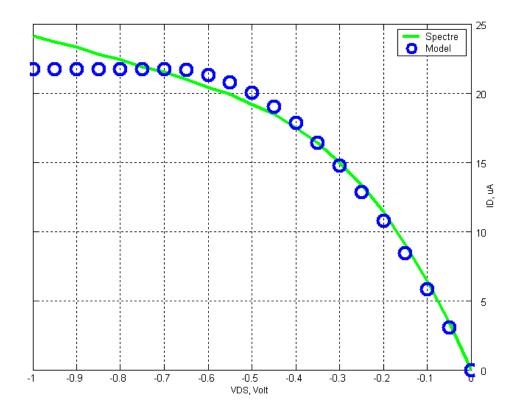

| Figure 6.6: $I_D$ vs. $V_{DS}$ for PMOS with $W_p$ =120 nm, L=100 nm                                                 | . 112 |

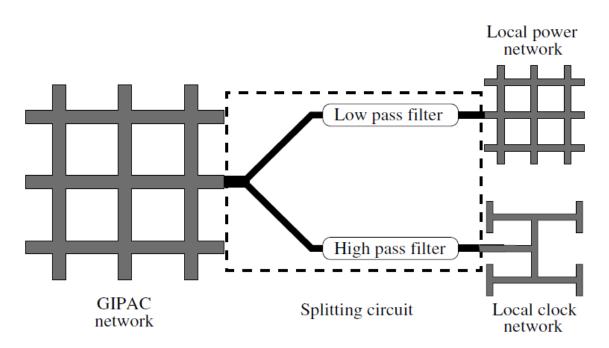

| Figure 7.1: Globally integrated power and clock (GIPAC) distribution network [57]                                    | . 117 |

| Figure A.1: MAC unit                                                                                                 | . 128 |

| Figure A.2: Serial-in parallel-out shift register                                                                    | . 129 |

| Figure A.3: Parallel-in serial-out shift register | 130 |

|---------------------------------------------------|-----|

| Figure A.4: Bonding diagram for the CFP80 package | 132 |

| Figure A.5: RF CFP80TF test fixture [58]          | 132 |

## **List of Tables**

| Table 3.1    Matched delay (ps) for a clock period of 2ns    51                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2 Power consumption (µW)                                                                                                                                                                   |

| Table 3.3 Supply voltage effect on matched delay values                                                                                                                                            |

| Table 3.4 Comparison of MMM-DME and the new modified DME using the proposedskew compensation technique                                                                                             |

| Table 4.1 Timing characteristics of the DE-SAFF – post layout simulation                                                                                                                           |

| Table 4.2 DE-SAFF precharge and evaluation intervals obtained for different corners 75                                                                                                             |

| Table 4.3 Combinational logic delay obtained for each corner at positive and negative clock edges                                                                                                  |

| Table 4.4 Supply voltage effect on precharging and evaluation intervals                                                                                                                            |

| Table 4.5 Timing characteristics of the DE-SDFF, DE-DCCFF, and DE-SAFF at a clock frequency of 250MHz       81                                                                                     |

| Table 4.6 Timing characteristics of the CD-SAFF, AC-SAFF, and DE-SAFF at a clockfrequency of 500MHz82                                                                                              |

| Table 5.1 Area and power comparison between full- and low-swing clocking                                                                                                                           |

| Table 6.1 Estimated driver strength at different pulse widths ( <i>PW</i> ) for $C_{clk}$ =30 pF, $R_{clk}$ =0.5 $\Omega$ , <i>f</i> =1 GHz, $V_{DD}$ =1 V, $V_{OH}$ =0.95 V, and $V_{OL}$ =0.05 V |

| Table A.1 Pad name, type, and description    131                                                                                                                                                   |

# List of Acronyms

| AC-SAFF  | Adaptive Clocking Dual-edge Sense Amplifier Flip-Flop     |  |  |

|----------|-----------------------------------------------------------|--|--|

| ASIC     | Application Specific Integrated Circuit                   |  |  |

| CDN      | Clock Distribution Network                                |  |  |

| CD-SAFF  | Conditional Capturing Dual-edge Sense Amplifier Flip-Flop |  |  |

| СМС      | Canadian Microelectronics Corporation                     |  |  |

| DCCFF    | Differential Conditional Capturing Flip-Flop              |  |  |

| DDO      | Distributed Differential Oscillator                       |  |  |

| DE-DCCFF | Differential Conditional Capturing Flip-Flop              |  |  |

| DE-SAFF  | Dual-Edge Sense Amplifier Flip-Flop                       |  |  |

| DE-SDFF  | Dual-Edge Static Differential Flip-Flop                   |  |  |

| DME      | Differed Merge Embedding                                  |  |  |

| FF       | Fast-Fast                                                 |  |  |

| FO4      | Fan Out of Four                                           |  |  |

| FPGA     | Field Programmable Gate Array                             |  |  |

| FS       | Fast-Slow                                                 |  |  |

| FS-DCCFF | Full-Swing Differential Conditional Capturing Flip-Flop   |  |  |

| GIPAC    | Globally Integrated Power and Clock                       |  |  |

| HVT      | High Threshold Voltage                                    |  |  |

| LS-DCCFF | Low-Swing Differential Conditional Capturing Flip-Flop    |  |  |

| LSDFF    | Low-Swing Clock Double-Edge Flip-Flop                     |  |  |

| LVT      | Low Threshold Voltage                                     |  |  |

| MAC     | Multiply and Accumulate                       |  |  |

|---------|-----------------------------------------------|--|--|

| MMM     | Method of Means and Medians                   |  |  |

| PDN     | Pull-Down Network                             |  |  |

| PLL     | Phase-Locked Loop                             |  |  |

| PUN     | Pull-Up Network                               |  |  |

| PVT     | Process, Voltage, and Temperature             |  |  |

| PW      | Pulse Width                                   |  |  |

| SAFF    | Sense Amplifier Flip-Flop                     |  |  |

| SCCFF   | Single-ednded Conditional Capturing Flip-Flop |  |  |

| SE-SAFF | Single-Edge Sense Amplifier Flip-Flop         |  |  |

| SF      | Slow-Fast                                     |  |  |

| SS      | Slow-Slow                                     |  |  |

| SVT     | Standard Threshold Voltage                    |  |  |

| SWO     | Standing-Wave Oscillators                     |  |  |

| TT      | Typical-Typical                               |  |  |

| ZST     | Zero Skew Clock Tree                          |  |  |

## Chapter 1 Introduction

#### **1.1 Motivation**

Microprocessor power consumption is increasing by approximately 20% per year [1]. In deep sub-micron technology, the substantial increase in power leads to additional difficulties in cooling and heat removal [2]. Furthermore, low-power design is becoming a crucial objective due to the increasing demand on portable applications [3]. Approximately 30-50% of microprocessor power consumption is dissipated in the clock distribution network (CDN) which has the highest capacitance in the system and operates at high frequencies [4].

An attractive approach to reduce power is to scale down the supply voltage which has a quadratic effect on power consumption. However, scaling down the supply voltage would require decreasing the transistor threshold voltage level in order to maintain transistor driving capability. This leads to substantial increase in leakage power. In addition, decreasing the supply voltage would increase system susceptibility to variations [3]. As a result, there is an increasing demand for power reduction schemes that do not require a reduction in the supply voltage.

An emerging technique to reduce the power of the CDN is resonant clocking where low energy dissipation is achieved by recycling the energy stored on the clock capacitance [5]. From the three resonant clocking techniques offered to date, namely: standing-wave, rotary traveling-wave, and LC resonant clocking; LC resonant clocking has proven to be the most convenient since it requires minimum change from conventional square-wave design and its practicality was verified on functional chips.

Clock skew and jitter in buffered clock distribution networks are proportional to clock latency which is increasing relative to clock cycle in recent microprocessors. Resonant clocking techniques in addition to their low-power consumption enable phase stability and low jitter due to resonance [6].

The traditional approach for LC resonant CDNs is to use the LC tank to drive the global clock distribution while the local clock is being delivered through conventional clock buffers. However, around 66% of clock power is being dissipated in the last buffer stage driving the flip-flops [7] leading to minor power savings in LC globally-resonant locally-square CDNs. In order to achieve maximum power savings, the LC tank should drive the entire clock network (both global and local) without using intermediate buffers (see Figure 2.8 in Chapter 2).

Power reduction techniques for LC resonant CDNs in which the entire network including the flip-flops is being driven with a resonant (sinusoidal) clock signal will be the focus of this dissertation. The schemes and techniques developed in this thesis are applicable to both square and resonant CDNs.

#### **1.2 Contributions**

Given that the bulk of the CDN capacitance is in its leaves, the largest power advantage will come by extending the LC resonance down to the flip-flops. This would require understanding flip-flop performance with the sinusoidal characteristic of the clock signal generated in LC resonant networks. We have followed a similar approach to the one proposed in [7] in which the clock buffers are removed to allow the clock energy to resonate between the inductor and the clock capacitance enabling maximum power savings.

Our goal is to further reduce the power of an LC fully-resonant CDN through manipulating and modifying the characteristics of flip-flops under a sinusoidal clock signal.

• We have introduced a new type of slack in the skew that can be compensated for to reduce the CDN routing complexity and as a byproduct/substitute we can achieve reductions in wire elongations and total wire length as well as power consumption. The slack in the skew can also be used for incremental routing adjustments. The concept itself is applicable to both sine-wave resonant as well as conventional square-wave clocking if flip-flops of different delays are used. However, in our demonstration of the proposed technique, we took advantage of the slow rise time of the sinusoidal resonant clock signal and the different transistor threshold voltage levels available in the STMicroelectronics 90-nm technology to generate different delays of the flip-flop with separate means. In order to further illustrate the concept, five clock tree benchmarks with nominal zero skew have been constructed using a Modified Differed Merge Embedding Algorithm that takes advantage of the skew slack introduced by the new technique to highlight its benefits and practicality.

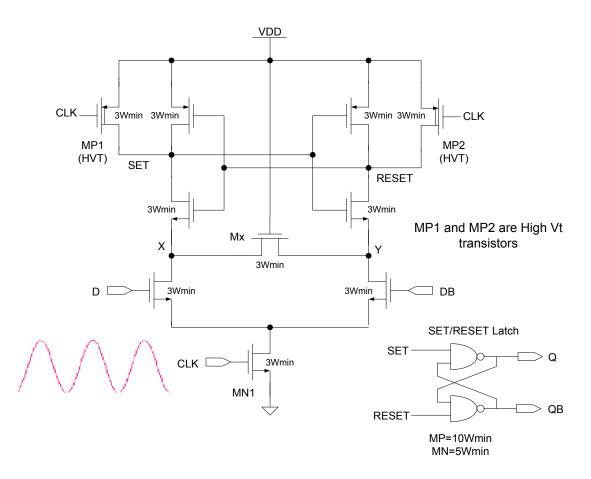

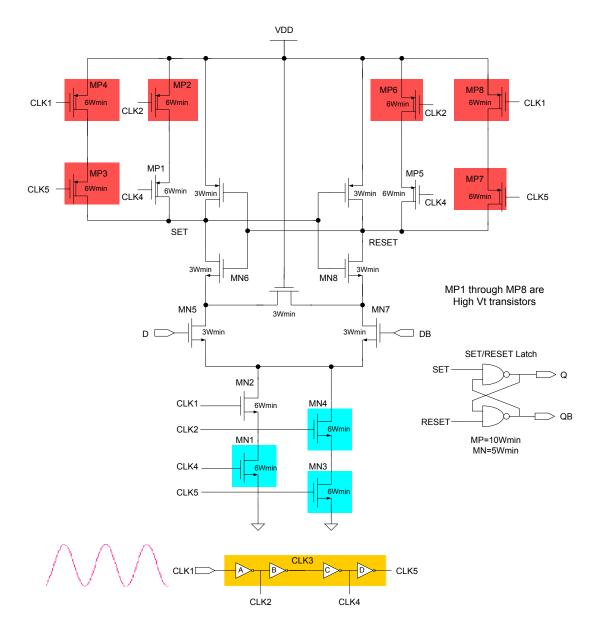

• We have also introduced a new Dual-Edge Sense Amplifier Flip-Flop (DE-SAFF) for LC fully-resonant CDNs using a modified clocking scheme that can be extended to enable dual-edge clocking in any dynamic CMOS logic circuit. In this work, the PMOS transistors used for precharging the nodes in the flip-flop are only switched on for a portion of the clock cycle in order to reduce short circuit power. Correct operation of the proposed flip-flop was verified on the extracted circuit layout in STMicroelectonics 90-nm technology under a sinusoidal clock at a frequency of 500 MHz.

• The application of low-swing clocking on LC fully-resonant CDNs is investigated. The Differential Conditional Capturing Flip-Flop (DCCFF) was modified to operate with a low-swing sinusoidal clock. The proposed low-swing resonant clocking scheme operates with one voltage supply and does not require additional supply voltage. The feasibility of low-swing resonant clocking and the power advantages were investigated on-chip in TSMC 90-nm technology.

• Though the main concentration of the dissertation is aimed at the flip-flop level, estimating the power savings achievable through dual-edge and low-swing resonant clocking required estimating the power of the clock driver. In doing so, an analytical approach was introduced to estimate the required driver strength in the resonant clock generator. Using the proposed approach early at the design stage eliminates the need for programmable switches in the driving circuit, thus reduces area and power overhead.

Although all proposed schemes have been simulated and tested under a sinusoidal clock signal assuming a fully-resonant LC CDN, the proposed techniques are equally applicable to conventional square-wave CDNs.

#### **1.3 Dissertation Overview**

This dissertation is organized as follows. Chapter 2 introduces the main objectives and metrics of CDN design. Different resonant clocking techniques introduced in the literature are reviewed and their advantages in reducing clock skew, jitter, and power are

shown. The remainder of Chapter 2 is devoted to discussing LC resonant CDNs with the concentration on LC fully-resonant CDN. Sinusoidally clocked flip-flops are also presented at the end of this chapter. The skew compensation technique for LC resonant CDNs is discussed in Chapter 3. Lower skew bounds for the proposed technique, the Modified Differed Merge Embedding Algorithm, and the results obtained on five benchmark CDNs are then presented. In Chapter 4, the new dual-edge clocking scheme, the Dual-Edge Sense Amplifier Flip-Flop (DE-SAFF), timing characterization for the proposed scheme, and potential power savings achievable through dual-edge clocking are described. Chapter 5 presents the Low-Swing Differential Conditional Capturing Flip-Flop (LS-DCCFF) modified to operate with a low-swing sinusoidal clock. Measured results from the test chip are also viewed. The analytical approach used to estimate required driver strength in the clock generator is introduced in Chapter 6. Conclusion that has been drawn from this work and ideas for future extension of this thesis are presented in Chapter 7.

## Chapter 2 Background

This chapter introduces the main design objectives for the clock distribution network. Different clock architectures are presented. Different resonant clocking schemes that have been proposed in the literature are reviewed and the promise in reducing clock skew, jitter, and power is shown. LC-based resonant clock distribution networks are examined in more detail. Challenges associated with LC resonant clocking are identified and sinusoidally clocked flip-flops are then discussed.

#### 2.1 Clock Distribution Network Design Objectives

CDNs in synchronous digital integrated circuits deliver the clock signal that controls the flow of data within the system. The input at each clock sink, i.e., flip-flop, is captured at the rising or falling clock edge (single-edge triggered flip-flops), or on both edges of the clock (dual-edge triggered flip-flops), or based on the voltage level of the clock (latches). The main objectives in the design of CDNs are to minimize skew, jitter, and power.

#### 2.1.1 Clock Skew

Clock skew is defined as the difference in the arrival time of the clock edges at different locations in the CDN. Skew is mainly caused by variations between clock buffers, interconnect widths, and loading at different clock paths. The main cause of skew in balanced well-designed CDN is the clock buffers [8]. It should be noted that skew is

only relevant in sequentially adjacent flip-flops. Since it is highly unlikely for a signal in one clock cycle to propagate across the entire chip, the skew between different parts of the chip is not important. However, due to the complexity of controlling skew in complicated and condensed clock paths, any skew is undesirable.

#### 2.1.2 Clock Jitter

Clock jitter is defined as the difference in the arrival time of the clock edge at the same location in the CDN. Jitter can make the clock period shorter or longer than nominal period. Jitter is mainly caused by temperature variation, power supply noise, and the phase-locked loop (PLL). Since the design of PLLs has improved, the main source of jitter in today's microprocessors is the CDN [9].

#### 2.1.3 Clock Power

Low-power design is becoming a crucial design objective due to the increasing demand on portable applications and the increased cost of cooling. 40% of the power in the 200 MHz 21064 Alph microprocessor is dissipated in the CDN [10]. The CDN and latches dissipate around 70% of the IBM POWER4 1.3 GHZ microprocessor's power [11].

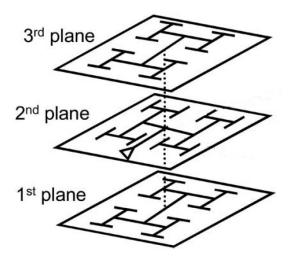

The latest developments in integrated circuit design specifically in 3-D integration where multi-plane synchronization is required, lead us to believe that the power consumption of the CDN will remain at these high levels. Figure 2.1 shows the schematic of a 3-D clock tree. The clock driver as illustrated is on the second plane [12].

Figure 2.1: Schematic of a 3-D clock tree [12]

### 2.2 Clock Distribution Network Structure

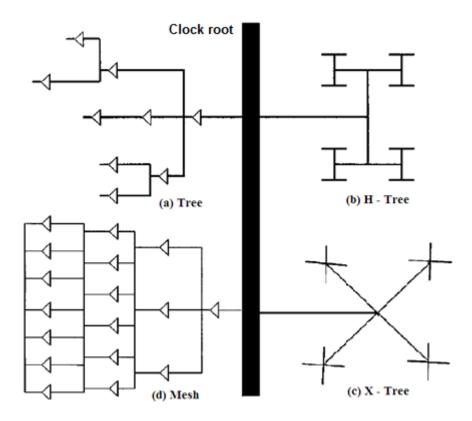

Figure 2.2: Common structures of clock distribution networks [8]

Various clock distribution structures have been developed given that the routing area and complexity, speed, and power dissipation of the system are all factors affected by the clock network design. Figure 2.2 illustrates common CDN structures. An asymmetric buffered tree structure is shown in Figure 2.2(a). In this structure, the wire as well as the buffer delay is balance in each path in order to achieve zero skew at the clock leaves. When the clock sinks are uniformly distributed, a symmetrical tree structure is used such as the H- and X- tree structures shown in Figure 2.2(b), (c). Although the balanced trees shown in the figure are not buffered, buffers are usually inserted to drive different sections of the tree. Properly matched buffers and interconnect delays as well as loading capacitances in clock trees can achieve under ideal conditions zero skew. However, in reality some skew will certainly be present due to variations in interconnect parameters as well as mismatches in clock buffers.

Clock grid or mesh (Figure 2.2(d)) is another alternative to distribute the clock signal. The mesh actively reduces skew by connecting path resistances in parallel [8]. In the mesh structure, the skew is independent of unbalanced distribution of loading. However, unlike clock trees, the mesh structure uses more wiring resources and consume more power.

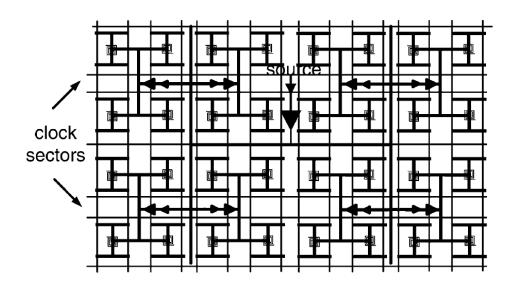

The clock signal in modern microprocessors is distributed using a hierarchical approach in which a global distribution delivers the clock signal across the chip and a local distribution carries it to sequential elements.

In IBM microprocessors [13], the global clock distribution consists of a tree-driven grid (Figure 2.3). The clock signal is distributed across the chip using a balanced clock tree while a global grid is used to short the clock tree ends together.

| FILI | FII   | FILT    |       |

|------|-------|---------|-------|

| FILT | FILT  |         | IT IT |

| FILT | FILT  | ITIIII  |       |

| FILI | FILI  | FIL     |       |

| FILI | FILIT | ITILIT. |       |

| FIFI | FILT  | ITI ITI |       |

| FILT | FILIT |         |       |

|      |       |         |       |

Figure 2.3: Tree-driven grid global clock distribution [13]

In this scheme, low wiring resources by the balanced clock tree and load-independent minimum skew by the grid are achieved. The local clock is distributed by additional levels of buffers which deliver the clock signal to the circuits.

#### 2.3 Resonant Clocking Techniques

Resonant clocking reduces power dissipation in CDNs while enabling the generation of high frequency clock signals. There are three resonant clocking techniques offered to date [14]. The first one is the standing wave oscillation which generates a clock signal with varying amplitude and constant phase [15]. The second technique is the travelling rotary-wave oscillation which generates a clock signal with constant amplitude and varying phase making it suitable for non-zero clock skew systems. The third technique is the LC oscillation which generates a clock signal with constant amplitude and phase and requires minimum change from conventional clock design [14].

#### 2.3.1 Standing-Wave Resonant Clocking

The interaction of two identical waves of equal magnitude and frequency propagating in opposite directions forms a standing-wave [15]:

$$V_f(x,t) = V_A \sin(\omega t - \beta x)$$

(2.1)

$$V_r(x,t) = V_B \sin(\omega t + \beta x)$$

(2.2)

where  $V_f$  and  $V_r$  are the forward and reverse travelling waves,  $V_A$  and  $V_B$  represent the amplitudes,  $\omega$  is the angular frequency, t is the time,  $\beta$  represents the phase constant, and x represents the position. Setting  $V_A = V_B$  and adding the two waves at location x and time t results in a standing wave [15]:

$$V(x,t) = V_A(\sin(\omega t - \beta x) + \sin(\omega t + \beta x)) = 2V_A \sin(\omega t) \cos(\beta x)$$

(2.3)

Equation (2.3) illustrates that the phase shift in an ideal standing-wave is independent of position but the amplitude varies sinusoidally [15]. Within any region in which the sign of  $\cos(\beta x)$  or  $\sin(\omega t)$  does not change, the phase of the standing wave remains constant. However, this is not the case in traditional travelling-wave clocking where the phase changes linearly with position. In travelling-wave clock signals and in order to lower the skew, delay of the propagating signal from clock source to the sinks must be balanced.

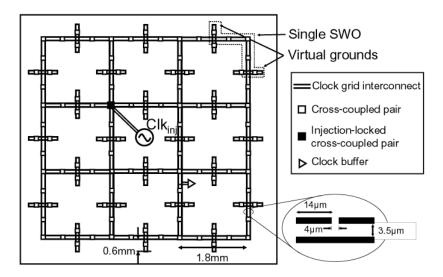

In [16], on-chip design and operation of a 10-GHz global standing-wave clock distribution network using coupled oscillators is described. As illustrated in Figure 2.4, standing-wave oscillators (SWO) are coupled together to create a grid of standing waves.

Figure 2.4: Standing-wave clock distribution network [16]

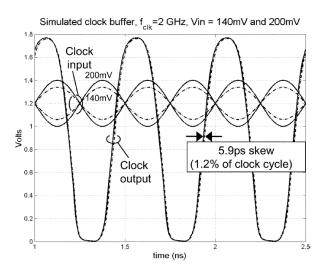

Figure 2.5: Clock buffer simulated performance [16]

Due to the large losses of on-chip interconnects, a clock buffer is used to convert the low-swing standing-wave clock signal to digital levels to enable the generation of a conventional digital clock at the clock sinks (Figure 2.5).

### 2.3.2 Rotary Traveling-Wave Resonant Clocking

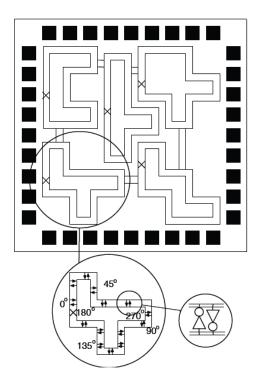

Figure 2.6: Basic rotary clock architecture. The "=" signs denote points with equal phase [19]

Figure 2.7: Custom rotary clock architecture [19]

Another technique of resonant clocking is the rotary traveling-wave CDN. In [17], an average of 63% power savings were reported for a rotary traveling-wave clock network compared to conventional clock tree in microprocessor design.

Transmission line rings are used to distribute the clock signal. A rotating multiphase (360°) square-wave within a closed-loop differential transmission line is driven by distributed anti-parallel CMOS inverter pairs as shown in Figure 2.6. Line losses are overcome and phase lock is achieved by the anti-parallel inverters [18]. The traveling wave is generated by turning ON the power supply. Afterwards, at least one set of anti-parallel inverters are needed to overcome interconnect loss and maintain resonance. The clock frequency is determined by the length of the transmission line ring.

$$f_{osc} = \frac{1}{2\sqrt{L_T C_T}} \tag{2.4}$$

where  $L_T$  and  $C_T$  are the total inductance and capacitance along the rotary signal path in the ring [19].

Unlike the case in standing-wave resonant clocking where the clock signal has a sinusoidally varying amplitude, the amplitude of the rotary traveling-wave clock is constant. However, the phase of the rotary traveling clock changes with position.

As illustrated in Figure 2.6, the waveforms in the two signal lines at any point of the loop are 180° out of phase. To implement a zero skew synchronized circuit using rotary clocking, all synchronous elements need to be connected to the same location in the loop [14]. However, in [20], the feasibility of using rotary clocking as a zero clock skew synchronizing technology was proven.

In [19], a custom rotary clock router was introduced. Rotary oscillations can be sustained for non-regular custom structures like the one shown in Figure 2.7. Though

regular rectangular rings have advantages in terms of manufacturability, non-regular custom rings can easily be used in multi-core implementations where an independent core is synchronized by each ring. Custom ring topologies also reduce the tapping (connecting) wire lengths between the oscillatory ring and the registers.

In [19, 20], rotary traveling-wave CDNs with regular and custom structures were used to implement zero skew circuits by taking advantage of the delay associated with the tapping wire length used to connect the register to the ring at a particular tapping point with known phase. For phase information, a point along the ring is chosen as a reference point with clock delay t = 0 and phase  $\theta = 0$ . The clock delay t and phase  $\theta$  at any point on the ring can be obtained using  $\frac{\theta}{360} = \frac{t}{T}$  where T is the clock period. All synchronous elements can connect to the ring at specific nodes with known phase called tapping points. Each tapping point has two locations one on the inner line and the other on the outer line of the ring separated by 180°. The delay between registers connected to different tapping points is equalized by manipulating the tapping wire length and hence the delay associated with it.

#### 2.3.3 LC Resonant Clocking

Figure 2.8(a) illustrates a simplified balanced clock tree structure for a conventional square-wave based CDN. Bufferes are used to drive different sections in the tree. As shown in the figure, the clock signal propagating in the global tree to the lower bracnhes which in turn feed the local clock and flip-flops is a square-wave clock signal. A globally-resonant locally-square CDN is shown in Figure 2.8(b). An inductor is connected at the center of the H-tree in order to generate a resonanting clock signal at the

Figure 2.8: Simplified Square-wave, globally-, and fully-resonant CDNs

fundamental ferquency of the clock node. Lower branches of the H-tree are driven by buffers which in turn convert the sinosodial clock to sqaure-wave signal feedign the flipflops. Design guidelines and methodology for globally-resonant H-tree are presented in [21]. The bufferes in globally-resonant locally-square CDN are removed in Figure 2.8(c) where the resonant clock signal is distributed all the way down to the flip-flop level.

LC resonant CDNs in addition to their low-power consumption have the advantage of generating a clock signal with uniform phase and amplitude. It also requires minimum change from conventional square-wave design. In the following, globally-resonant locally-square, and fully-resonant CDNs will be discussed.

#### 2.3.3.1 LC Globally-Resonant Locally-Square Clock Distribution Networks

In [22], the design of a resonant global CDN was introduced. In their approach, the traditional tree-driven grids are augmented with on-chip inductors to resonate the clock

capacitance at the fundamental frequency of the clock node as shown in Figure 2.9. The energy resonates between electrical form in the clock capacitance and magnetic form in the inductor. As shown in the figure, at the center of the H-tree is the clock driver which consists of a buffer chain. One end in each spiral inductor is connected to the clock tree and the other end is connected to a large decoupling capacitance. This capacitance provides dc voltage around which the clock oscillates.

Resonance results in a reduced effective capacitance of the clock grid which in turn reduces clock latency. It also allows a reduction in the driving strength as well as the number of buffer stages required to drive the grid. This reduction in number of buffers leads to improvements in clock skew and jitter since the effect of power-supply noise on these buffers is reduced.

Simulation results using model extraction at a frequency of 1.1 GHz have shown a power reduction of over 80% as well as improved clock latency [22].

The resonant global clock distribution proposed in [22] was fabricated on chip using 90 nm 1 V ten-level Cu CMOS technology [23], [24], and 0.18  $\mu$ m 1.8 V six-level Al mixed-signal CMOS technology, where on-chip measurements showed approximately 20% of the energy being recovered and reused in each cycle. In addition, the ability to significantly scale down the required buffers in the global clock distribution allows total power savings of about 80%.

The natural band-pass characteristics of the resonant network along with buffer reduction, results in over 60% improvement in jitter [24]. A drawback in the resonant global clock distribution proposed in [22]-[24] is the requirement of large on-chip decoupling capacitance to serve as a charge reservoir.

17

(a) Global clock distribution with a resonant load – eight clock sectors

(b) Components and topology of a resonant clock sector

Figure 2.9: Globally-resonant locally-square clock distribution networks [24]

Figure 2.10: Distributed differential oscillator (DDO) global clock network [26]

Another resonant clock design with a distributed differential oscillator (DDO) global clock network is presented in Figure 2.10 [25], [26]. Here, the distribution is differential where spiral inductors and negative differential transconductors are placed between two clock phases. The negative differential transconductor acts as a gain element to maintain oscillation and overcome losses. Clock amplitude is controlled by the bias current in the gain element. The distribution network is injection-locked to an external reference. In this approach the need for large decoupling capacitors is eliminated. In addition, jitter and skew caused by process variation, power-supply noise, and common-mode noise sources are reduced due to differential detection at local clock buffers.

The practicality of globally resonant clocking has been proven on an LC resonant clock in a fully-functional Cell Broadband Engine processor [27]. Hardware measurements show full functionality at 3.2 GHz and power savings of 25% in the global clock and 5% in total chip power at 4 GHz. It should be noted that in [27], only the global clock tree was modified to enable resonant clocking where an additional metal layer was added on top of the conventional tree to attach the inductors and decoupling capacitors. The local clock sectors were buffered; hence the clock signal feeding the registers is a square signal and not a sinusoidal one.

# 2.3.3.2 LC Fully-Resonant Clock Distribution Networks

In all of the resonant clocking techniques presented so far, the local clock signal feeding the flip-flops was a square-wave signal. In resonant clocking, the largest power advantage is achieved by extending the resonance all the way down to the flip-flop level given that the bulk of the capacitance is in the leaves of the clock tree [24]. In this approach, the clock buffers are removed to allow the clock energy to resonate between the inductor and the clock capacitance (Figure 2.8(c)). However, this would require more understanding of flip-flop performance with the sinusoidal clock characteristics of the LC fully-resonant CDNs.

In [7], a fully-resonant CDN was fabricated in an IBM 0.13 µm process. Though the target design frequency was in the gigahertz range using integrated inductors, external inductors were used instead due to startup difficulties and the chip was operational at the megahertz range. Test results show approximately 35% power savings compared to a conventional buffered CDN.

Two 64×64 pipelined multipliers were fabricated on-chip in TSMC 0.25-µm CMOS process with LC fully-resonant CDN [28]. One was designed with resonantly clocked flip-flops and the other with conventional square-wave clocked flip-flops. Overall power savings of 25%-69% in the resonantly clocked multiplier were measured depending on data switching activity.

A two-phase fully-resonant LC CDN was used in ultra-low power hearing aid applications. An experimental test chip with more than 2,500 resonantly clocked latches was fabricated and tested in 0.25µm process. Results show that compared to single-edge triggered one phase benchmark, resonant clocking dissipates less energy by 7.5% [29].

#### 2.4 Challenges Associated with LC Resonant Clocking

Despite the promising power savings achieved in resonant CDNs, resonant clocking presents several design challenges because of the dependency of the clock rise time on its frequency and the susceptibility to process variation due to the long rise time of the clock, the need for different inductor values to generate different frequencies, the additional chip area occupied by the inductor, and the difficulty in clock gating without affecting energy recovery.

# 2.4.1 Dependency of the Sinusoidal Clock Rise Time on Its Frequency

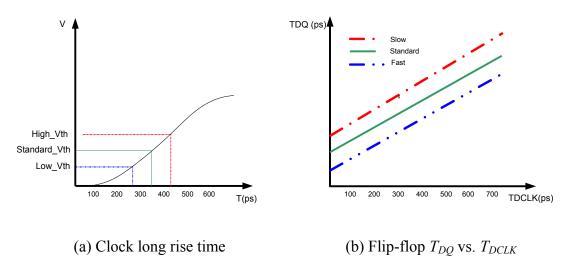

The rise time of the conventional square-wave clock signal does not depend on clock frequency and is restricted to less than 10-15% of the clock period [30]. However, this is not the case in resonant clocking where the rise time of the sinusoidal clock signal depends on its frequency. Let the generated resonant clock signal be given by the

Figure 2.11: Rise time of resonant and square-wave clock signal with rise time of 33ps

following equation:

$$v(t) = \frac{1}{2} V_{DD} \sin(2\pi f t) + \frac{1}{2} V_{DD}$$

(2.5)

Taking the rise time of the clock signal as the time difference between the 10-90% of the clock peak, the rise time of the sinusoidal clock signal would be given by the following equation:

$$T_{rise} = 0.29T \tag{2.6}$$

where T is the clock period.

Equation (2.6) illustrates the dependency of the rise time of the sinusoidal clock signal on its frequency. It also shows that the clock rise time does not depend on its amplitude. Figure 2.11 illustrates the difference in rise time for the resonant clock signal as compared to a square wave clock with a constant rise time of 33.33 ps (10% of clock period at 3 GHz).

### 2.4.2 Area Occupied by the Inductor

Figure 2.12: Spiral inductor with magnetic ring structure [31]

As was discussed in section 2.3.3.1, LC resonant CDNs require several inductors to be integrated and distributed across the chip. The difficulty of inductor on-chip integration and the large area occupied by the inductor complicates the design of LC resonant CDNs and limits their applications.

A promising technique to solve this problem is the use of magnetic inductors (Figure 2.12) in LC resonant clocking. Magnetic inductors are compatible with CMOS process and occupy nearly 100× less area compared to conventional inductors. They can achieve for example inductance values of up to 4 nH and a quality-factor of 3 at 1 GHz [31]. Using magnetic inductors in LC resonant CDN reduces area overhead associated with distributed inductors.

# 2.4.3 Clock Gating

By using logic gates (NAND/NOR), clock gating in conventional square-wave CDNs is achieved by using an ENABLE signal that controls the clock feeding a specific sector. However, this approach is not desirable in LC resonant CDNs since it would reduce the energy being recovered from the remaining capacitance of that sector. In [28], a clock gating scheme was proposed for LC resonant CDN by adding a NOR gate with an ENABLE signal at the clock input of every resonantly clocked flip-flop. Simulation results show that clock gating would reduce the power consumption of the flip-flop by more than 1000× in the idle mode compared to the power consumed without clock gating for 50% data switching activity [28]. However, the extra routing resources and complexity of connecting the ENABLE signal to the input of each flip-flop as well as the power overhead associated with it was neglected.

#### 2.5 Sinusoidally Clocked Flip-Flops

LC resonant clocking needs the least modification from traditional CDN design due to the constant phase and amplitude of the generated clock signal. In addition, LC resonant clocking up to this date, is the most developed and practical resonant clocking technique.

The clocking scheme adopted and assumed in this dissertation from here on is the fully-resonant LC scheme. The clock signal feeding the flip-flops is assumed to be purely sinusoidal clock since extending the resonance down to the flip-flop level results in most power savings as discussed previously.

The long rise time of the sinusoidal clock signal compared to that of the square clock where the rise time is restricted to around 10-20% of the clock period affects the flip-flop

speed, power, and susceptibility to variations. In [32], the performance and power of six flip-flops in 130-nm process were analyzed under square and sinusoidal clocking at an operating frequency of 1GHz. Simulation results show that the dominating effects are an increased flip-flop delay of 20-30% for a sinusoidal clock with a rise time  $10\times$  slower than that of the conventional clock. It is also illustrated that as the frequency increased from 1 to 3 GHz, the difference in rise time between sinusoidal and square clock reduced causing an improvement in flip-flop performance.

In [33], a study was conducted on the effect of clock slope on the energy and performance of fifteen flip-flops covering the pulsed, differential, and dual-edge triggered flip-flop classes in 65-nm CMOS technology. Smoother clock slope, i.e., longer rise time, increases flip-flop power due to the increase in short-circuit current between the pull-up and pull-down networks. Furthermore, as occurs in any CMOS logic circuit, longer rise time results in increased delay. Post-layout simulation illustrates that the increase in flipflop delay as the clock slope increase by  $6\times$  is modest and is less than 5.5%. Results also show that the flip-flop setup and hold times have low sensitivity to clock slope. Furthermore, flip-flops with negative setup time experience more negative setup time with increased clock slope since the transparency window expands with longer fall time due to the falling-edge of the clock being smoother. The flip-flop power increases by no more than 70% as the clock slope deccreases  $6\times$ . It should be noted that the increase in flip-flop power due to the long rise time of the sinusoidal clock compared to square-wave clock with 0.1T rise time would be much less than 70% since the ratio between the rise times is 2.9.

Any flip-flop can operate at both square and/or sinusoidal clocks since a sine-wave can be considered as a square-wave with longer rise and fall times. In the following, a brief description of two flip-flops that were proposed in the literature as energy-recovery flip-flops that operate with a sinusoidal clock will be presented: these are; the Differential Conditional Capturing Flip-Flop (DCCFF) and the Single-Ended Conditional Capturing Flip-Flop (SCCFF) [5]. The Sense Amplifier Flip-Flop (SAFF) will be presented in Chapter 4.

# 2.5.1 Differential Conditional Capturing Flip-Flop (DCCFF)

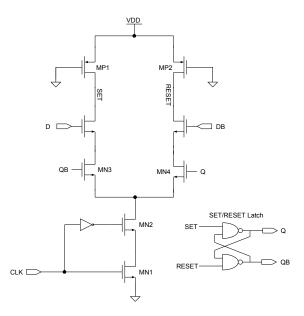

Figure 2.13: Differential Conditional Capturing Flip-Flop (DCCFF)

The DCCFF is shown in Figure 2.13. Conditional capturing is used to minimize flipflop power at low data switching activities by eliminating redundant internal transitions. The DCCFF operates in a precharge and evaluate fashion. Pull-up PMOS transistors are used for charging nodes *SET* and *RESET*. The effect of charge sharing can be reduced by ensuring a constant path to  $V_{DD}$ . This is done by properly sizing the PMOS transistors. A short evaluation interval occurs after the rising edge of the clock when both the clock and inverted clock signals applied to transistors MN1/MN2 are above the threshold voltage level of the NMOS transistor. The DCCFF uses a NAND latch for storage. Using feedback from the output to control transistors MN3 and MN4 in the evaluation paths ensures conditional capturing. Therefore if the state of the input data is not changed, *SET* and *RESET* are not discharged.

Figure 2.14: Single-Ended Conditional Capturing Flip-Flop (SCCFF)

Figure 2.14 presents the SCCFF. The SCCFF is a single ended version of the DCCFF. Transistor MN3 controlled by the output *QB*, provides conditional capturing. The right-hand-side evaluation path is static and does not require conditional capturing. If input *D*

was low and then goes high. Node QB would still be high from the previous state, thus pulling the gate of the PMOS transistor to ground and turning it on. The input node of the cross-coupled inverters will be pulled up to  $V_{DD}$ , their output QB becomes low and Qbecomes high. If the state of the input D remains the same, QB remains low, and transistor MN3 will be turned off and no discharging occurs since there is no path to ground.

### **2.6 Conclusion**

Reducing clock skew, jitter, and power are the main design objectives in CDNs. Though the main objective of the resonant clocking techniques is to reduce the clock power, they also enable reduction in clock skew and jitter as well. LC resonant clocking is still the most suitable low-power clocking scheme generating a clock signal with constant phase and amplitude and requires minimum change from conventional square-wave clock design. LC resonant clocking still, however, presents several design challenges associated with the long rise time of the sinusoidal clock, area occupied by the inductor, and clock gating.

# Chapter 3 Skew Compensation in LC Resonant Clock Distribution Networks

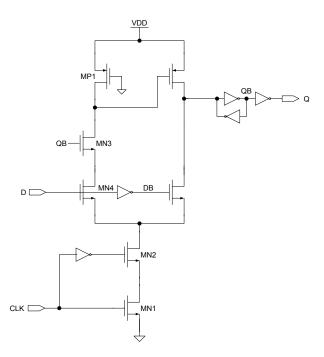

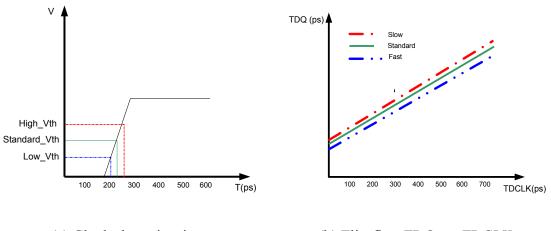

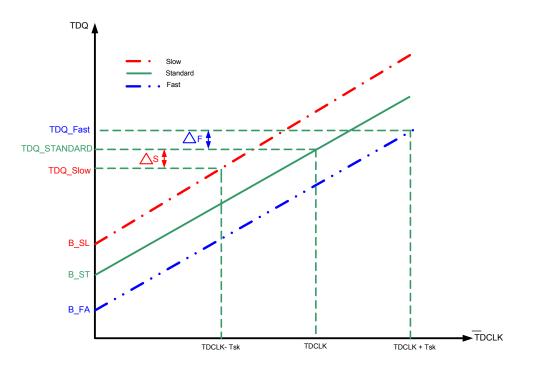

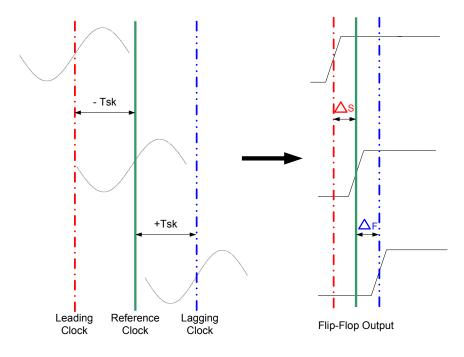

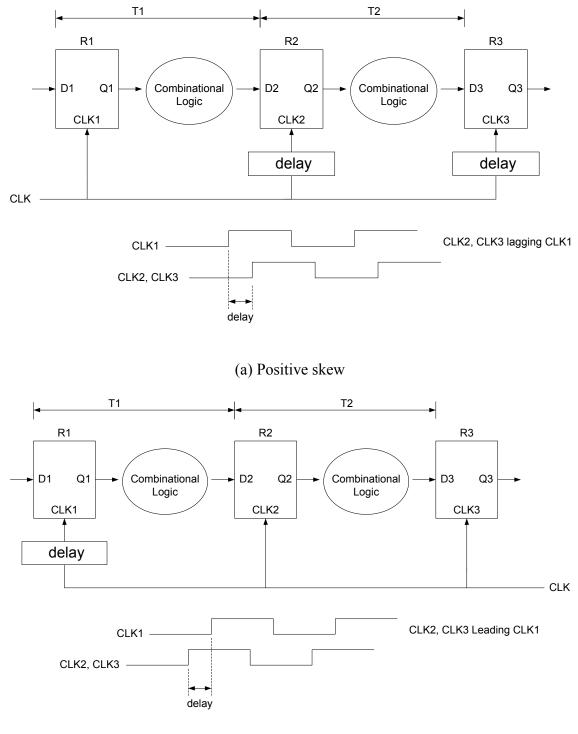

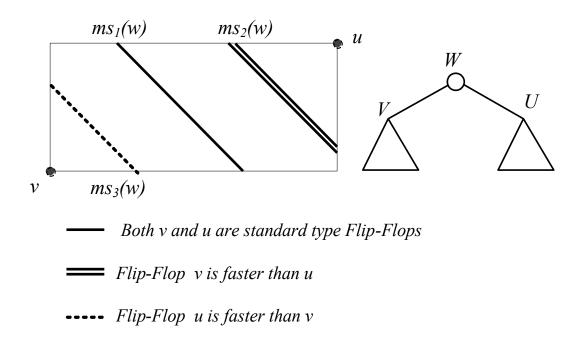

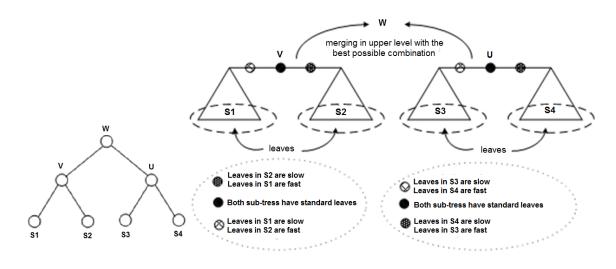

In this chapter a new approach for skew compensation in LC fully-resonant CDNs is introduced by manipulating the operating speed of the flip-flops. The STMicroelectronics 90-nm technology allows the use of devices with different threshold voltages, namely: HVT (High threshold voltage), SVT (Standard threshold voltage), and LVT (Low threshold voltage). Three types of flip-flops of equal input load: "fast", "standard", and "slow" are used. Timing parameters of the flip-flops are adjusted by manipulating the switching threshold of the clock port of the flip-flops. A fast/slow flip-flop has a shorter/longer  $T_{DQ}$  delay, compared to a standard flip-flop for the same setup time  $(T_{DCLK})$ . Distributing flip-flops according to their delay requirements would reduce the effect of the clock skew on the outputs of sequentially adjacent flip-flops. Due to the slow rise time of the sinusoidal clock signal generated in LC resonant CDNs compared to the conventional square-wave clock, the skew that can be compensated for in LC resonant CDNs using this approach would be much higher than in square-wave CDNs. This approach increases the skew bounds required by algorithms to balance the skew in the clock tree leading to reduced design complexity.

Theoretical analysis and simulation results using STMicroelectronics 90-nm technology at a clock frequency of 500 MHz show that this approach is feasible and effective where a skew of up to 6.2% of the clock period can be compensated for in the example used. In addition, constructing clock trees using the skew slack provided in the

proposed technique in a new modified Differed Merge Embedding (DME) algorithm on five benchmarks has shown that the proposed technique enables an average reduction of 11.5% in total wire length and 53.2% reduction in the number of wire elongations. As an example of illustrating the proposed methodology, we have used the Elmore delay model with a selected sinusoidally clocked flip-flop to verify the practicality of the proposed scheme. The method can generally be applied to resonant or square-wave clocking if different flip-flops of various speeds are used.

### **3.1 Lower Skew Bounds for the Proposed Technique**

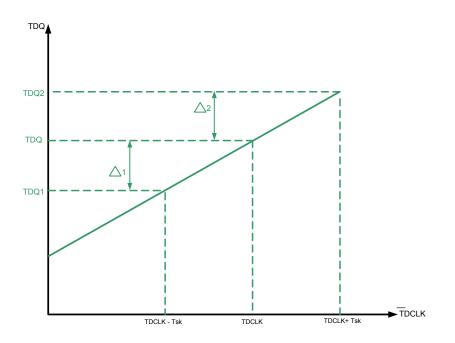

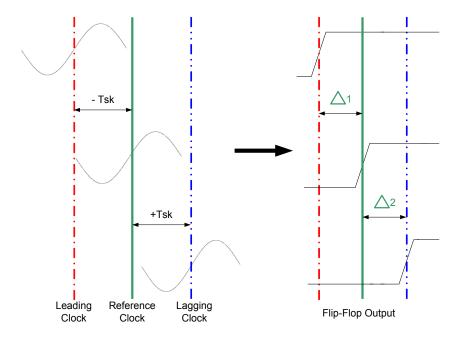

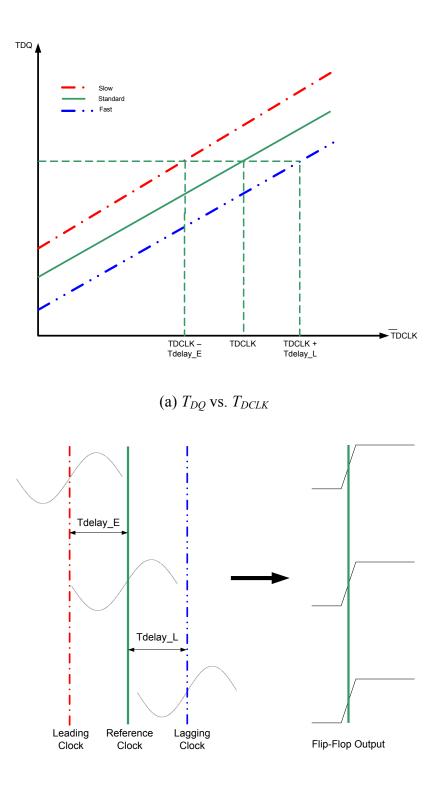

Figures 3.1 and 3.2 illustrate the effect of the slow rising time of the sinusoidal clock signal generated in LC fully-resonant CDN on the speed of the flip-flops. The data to output delay ( $T_{DQ}$ ) versus data to clock delay ( $T_{DCLK}$ ) is plotted for the slow, standard, and fast flip-flops as compared to a square-wave clock signal with short rise time. As shown in these figures, the increase in the required time for the sinusoidal signal to reach from one threshold voltage level to the next is reflected in the increase in the difference between the operating speeds of the flip-flops. The opposite is true for the square-wave, since the short time required for the square signal to reach from one threshold voltage level to the next signal to reach from one threshold voltage level to the square signal to reach from one threshold voltage level to the square signal to reach from one threshold voltage to the next causes small differences in the flip-flops operating speed. Here  $V_{th}$  refers to the threshold voltage of the NMOS transistors triggered by the clock. The beginning of the evaluation phase in each flip-flop starts when the clock voltage exceeds the threshold voltage. The fast, standard, and slow flip-flops are defined in the following:

Figure 3.1: Effect of long rise time of the sinusoidal clock signal on the operating speed of the flip-flop

(a) Clock short rise time (b) Flip-flop *TDQ* vs. *TDCLK*

Figure 3.2: Effect of short rise time of the square clock signal on the operating speed of the flip-flop

1- Standard flip-flop: the threshold voltage of the NMOS devices triggered by the clock signal in the standard flip-flop is the standard threshold voltage for the technology  $(V_{th \ standard}= 0.24 \text{ V}).$

- 2- Fast flip-flop: for the same setup time ( $T_{DCLK}$ ), a fast flip-flop will have a shorter  $T_{DQ}$  delay as compared to the standard and slow versions of the flip-flop. This is due to the fact that the threshold voltage of the NMOS devices triggered by the clock signal in the fast flip-flop is lower ( $V_{th\_low}$ = 0.18 V) than the threshold voltages for the same devices used in the standard and slow flip-flops.

- 3- Slow flip-flop: for the same setup time ( $T_{DCLK}$ ), a slow flip-flop will have a longer  $T_{DQ}$  delay as compared to the standard and fast versions of the flip-flop. This is because the the threshold voltage of the NMOS devices triggered by the clock signal in the slow flip-flop is higher ( $V_{th_high}$ = 0.32 V) than the threshold voltages for the same devices used in the standard and fast flip-flops.

Note that all the transistors in the three versions of the flip-flop have the same size and present equal load to the CDN. Only the threshold voltage of the NMOS transistors connected to the clock signal changes from one flip-flop version to the other.

Due to the fact that the speed of the flip-flops is highly affected by the threshold voltages of the NMOS devices connected to the clock signal and in order to make sure that two versions cannot have the same speed of operation, the following two constraints must be fulfilled:

$$V_{th\_standard\_max} < V_{th\_high\_min} \tag{3.1}$$

$$V_{th\_low\_max} < V_{th\_standard\_min} \tag{3.2}$$

where  $V_{th\_standard\_max}$  refers to the maximum value of the standard threshold voltage,  $V_{th\_high\_min}$  refers to the minimum value of the high threshold voltage,  $V_{th\_low\_max}$  refers to the maximum value of the low threshold voltage, and  $V_{th\_standard\_min}$  refers to the minimum value of the standard threshold voltage of the NMOS devices used in each version of the flip-flop due to process and environmental effects.

In the following timing definitions, flip-flop equations, and lower skew bounds for implementing this technique will be presented. Let  $T_{DCLK}$  be given by:

$$T_{DCLK} = T_D - T_{CLK} \tag{3.3}$$

The time difference between arrival of data and the edge of the clock due to the skew  $(T_{sk})$  would affect the  $T_{DCLK}$  time for each flip-flop. For a lagging clock signal by  $T_{sk}$  the  $\overline{T_{DCLK}}$  of the flip flop would be:

$$\overline{T_{DCLK}} = T_{DCLK} + T_{sk} = T_D - T_{CLK} + T_{sk} + \Delta skew$$

(3.4)

and for a leading clock signal by  $T_{sk}$ :

$$\overline{T_{DCLK}} = T_{DCLK} - T_{sk} = T_D - T_{CLK} - T_{sk} + \Delta skew$$

(3.5)

The bar on the  $T_{DCLK}$  shown in equations 3.4 and 3.5 is used to distinguish between the nominal value of  $T_{DCLK}$  with a zero skewed clock signal and its value with a lagging or a leading clock signal. It should be noted that the deviation from the skew value  $T_{sk}$ due to process and environmental variations ( $\Delta skew$ ) is assumed to be small compared to  $T_{sk}$  and is neglected to simplify the analysis.

(a)  $T_{DQ}$  vs.  $T_{DCLK}$

(b) Flip-flop output with respect to skewed clock Figure 3.3: Using one version of the flip-flop

Figure 3.3(a) and (b) shows an illustration of the effect of different  $T_{DCLK}$  on the difference between  $T_{DQ}$  delays for a single flip-flop. Figure 3.4(a) and (b) shows an illustration of the effect of different  $T_{DCLK}$  on the difference between  $T_{DQ}$  delays for flip-flops with different operating speeds. Note that Figures 3.3 and 3.4 have the same time scale. Assuming that the equations for the  $T_{DQ}$  lines for the slow, standard, and fast flip-flops are given by:

$$T_{DQ\_SLOW}(T_{DCLK}) = B_{SL} + m \times T_{DCLK}$$

(3.6)

$$T_{DQ\_STANDARD}(T_{DCLK}) = B_{ST} + m \times T_{DCLK}$$

(3.7)

$$T_{DQ\_FAST}(T_{DCLK}) = B_{FA} + m \times T_{DCLK}$$

(3.8)

where *m* is the slope of the  $T_{DQ}(T_{DCLK})$  line, and  $B_{SL}$ ,  $B_{ST}$ , and  $B_{FA}$  denote the intercepts on the  $T_{DQ}$  axis for the slow, standard, and fast flip-flops, respectively. It should be noted that all the lines in Equations 3.6 to 3.8 are assumed to be parallel and have the same slope of *m*. Also, note that the equation of  $T_{DQ\_STANDARD}$  is also the one of the line of Figure 3.3(a). Equations 3.6 to 3.8 present the relationship between  $T_{DQ}$  and  $T_{DCLK}$  in the linear operating region of the flip-flop.

As shown in Figure 3.3(a) and (b), the difference between the  $T_{DQ}$  delay of a single standard flip-flop due to a leading clock signal is referred to by  $\Delta 1$  where:

$$\Delta 1 = T_{DQ} - T_{DQ1}$$

=  $(B_{ST} + m \times T_{DCLK}) - (B_{ST} + m \times (T_{DCLK} - T_{sk}))$

=  $m \times T_{sk}$  (3.9)

(a)  $T_{DQ}$  vs.  $T_{DCLK}$

(b) Flip-flop output with respect to skewed clock

Figure 3.4: Using three versions of the flip-flop

Figure 3.4(a), shows that the leading clock signal is fed to a slow flip-flop instead of the standard flip-flop. The difference between the  $T_{DQ}$  delays of the standard and slow flip-flops is given by  $\Delta S$ :

$$\Delta S = T_{DQ\_STANDARD}(T_{DCLK}) - T_{DQ\_SLOW}(T_{DCLK} - T_{sk})$$

=  $(B_{ST} + m \times T_{DCLK}) - (B_{SL} + m \times (T_{DCLK} - T_{sk}))$

=  $B_{ST} - B_{SL} + m \times T_{sk}$  (3.10)