# A Fuzzy Logic Based Approach for High-Level Synthesis of DSP Data-Flow Graphs onto Multiprocessor Systems

#### Awni H. Itradat

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

April 2004

© Awni Itradat, 2004

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-91050-4 Our file Notre référence ISBN: 0-612-91050-4

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la

Bibliothèque nationale du Canada de

reproduire, prêter, distribuer ou

vendre des copies de cette thèse sous

la forme de microfiche/film, de

reproduction sur papier ou sur format

électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

# **ABSTRACT**

A Fuzzy Logic Based Approach for High-Level Synthesis of DSP Data Flow Graphs onto Multiprocessor Systems

#### Awni H. Itradat

In recent years a great deal of research has been conducted in the area of synthesizing and scheduling the DSP data flow graphs onto multiprocessor systems. During the design of a DSP application, there exist many sources of uncertainty. For example, the design acceptability subject to certain constraints may be imprecise, since different designers may have different rules in determining an acceptable design. Another source of uncertainty could be that in the high level synthesis the final form of the hardware implementation of a functional unit is uncertain and imprecise, and therefore, its characteristics also uncertain. This thesis is concerned with the study of these sources of uncertainties in the module selection, allocation, and scheduling of the resources for DSP applications.

A fuzzy logic approach for module selection and process allocation of fully static DSP data flow graphs (DFG) onto multiprocessor systems is proposed. Fuzzy rule base systems are used to minimize the area and maximize the utilization of the processors within the constraint of a specified latency. The proposed technique provides the designer with more flexibility to explore the design space by using different types of processor modules for the same task. Both heterogeneous and general-purpose processor units are used during the resource allocation process. It is shown that in most cases, moving from a

fully homogenous to a fully heterogeneous architecture results in decreasing the design area. However, a hybrid multiprocessor architecture brings about a trade off between the area and the resource sharing.

Most of the static scheduling techniques assume the worst-case computational delay of the functional units used in the target architecture. This assumption is not realistic, since some of the computational time of the DSP tasks may be imprecise due to the fact that the design of the functional units may not have been completed at the layout level. Even if they are so designed, the fabrication process introduces variations in the resulting area and time. In this thesis, the impreciseness in the system components is taken into account by representing the computational time as a fuzzy set and efficiently constructing rate-optimal schedule using fuzzy arithmetic. The proposed approach can be incorporated into any technique for scheduling of cyclic or acyclic data flow graphs in order to obtain a more efficient schedule. By employing a fuzzy rule base system, the characteristics of the derived system, namely the latency and area, are then used to infer the acceptability of the design of the target architecture. The design acceptability inferred by the proposed approach is shown to be close to the one inferred by the conventional scheduling approach, when the best computational times of the functional units are assumed.

To My Loving Family

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude and heartfelt thanks to my thesis supervisors Drs. M.O. Ahmad and Ali Shatnawi for their interest, guidance and constructive criticism throughout this work. I am grateful for their extremely careful and thorough review of my thesis. I feel privileged for having the opportunity to work with them. Their advice and close support have been invaluable.

I am grateful to my family members for their constant prayers, love and support, and for the sacrifices they made in their lives in bringing me up. Special thanks are due to my wife, Dalal, for her patience, encouragement and love. She provides me with the peace of mind and the determination to complete this work.

Finally, I would like to dedicate this thesis to the soul of my father who passed away only a few days prior to my thesis defense. Yabah, I promise that I will do my best to keep up to your expectations.

# TABLE OF CONTENTS

| L  | IST O | F FIGURES                                                          | x  |

|----|-------|--------------------------------------------------------------------|----|

|    |       | OF TABLESOF SYMBOLS                                                |    |

|    |       | duction                                                            |    |

|    | 1.1   | General                                                            |    |

|    |       |                                                                    |    |

|    | 1.2   | Data Flow Graph                                                    | 3  |

|    | 1.3   | High-Level Synthesis                                               | 5  |

|    | 1.4   | The Synthesis Task                                                 | 7  |

|    | 1.4   | 1.1 Scheduling                                                     | 8  |

|    | 1.4   | 2.2 Classification of Multiprocessor Scheduling Techniques         | 13 |

|    |       | Allocation Process                                                 |    |

|    |       | .4 Combined Scheduling and Allocation                              |    |

|    | 1.4   | 5.5 Module Selection                                               | 20 |

|    | 1.5   | Design Space Exploration                                           | 20 |

|    | 1.6   | The Weaknesses of the Current Research in the High-Level Synthesis | 21 |

|    | 1.7   | Scope and Organization of the Thesis                               | 23 |

| 2. | Fuzz  | y Logic and Uncertainty                                            | 25 |

|    | 2.1   | Introduction                                                       | 25 |

|    | 2.2   | Definition of the Uncertainty                                      | 26 |

|    | 2.2   | 2.1 Zimmerman's Point of View                                      | 26 |

|    | 2.2   | 2.2 Klir's Point of View                                           | 28 |

|    | 2.2   | 2.3 Dubois and Prade's Point of View                               | 29 |

|    | 23    | Fuzzy Sets and Fuzzy Logic                                         | 30 |

| 2.4    | Classical Set and Fuzzy Set                                           | 32    |

|--------|-----------------------------------------------------------------------|-------|

| 2.5    | Representation of a Fuzzy Set                                         | 33    |

| 2.6    | Basic Characteristics of Fuzzy Sets                                   | 35    |

| 3. A I | Module Selection Scheme in the High Level Synthesis using Fuzzy Logic | 37    |

| 3.1    | Introduction                                                          | 37    |

| 3.2    | Previous Work                                                         | 38    |

| 3.3    | The Proposed Module Selection Scheme                                  | 39    |

| 3      | 3.3.1 Fuzzy Rule Base System to Infer the Acceptability of the Design | 44    |

| 3      | 3.3.2 Utility Adjustment                                              | 46    |

| 3.4    | An Example of Module Selection                                        | 48    |

| 3.5    | Experimental Results                                                  | 51    |

| 3.6    | Summary                                                               | 53    |

| 4. Pro | ocess Allocation of DSP Data Flow Graphs onto Multiprocessor Systems  | 55    |

| 4.1    | Introduction                                                          | 55    |

| 4.2    | Time Scheduling                                                       | 57    |

| 4.3    | The Process Allocation Algorithm                                      | 61    |

| 4.5    | An Example                                                            | 66    |

| 4.7    | Summary                                                               | 69    |

| 5. Sc  | heduling of DSP Data Flow Graphs with Processing times Characterize   | ed by |

| F      | uzzy Sets                                                             | 70    |

| 5.1    | Introduction                                                          | 70    |

| 5.2    | Preliminary                                                           | 72    |

| 5.3    | Building the Time Schedule using Fuzzy Arithmetic                     | 73    |

| 4      | 5.3.1 Preferred Firing Time of a Node                                 | 75    |

| 5.4     | Time Scheduling Algorithm                   | 76 |

|---------|---------------------------------------------|----|

| 5.5     | An Example                                  | 78 |

| 5.6     | Comparison with the Conventional Approaches | 81 |

| 5.8     | Summary                                     | 82 |

| 6. Conc | clusions and Future work                    | 83 |

| 6.1     | Conclusion                                  | 83 |

| 6.2     | Future Research Directions                  | 86 |

| REFE    | RENCES                                      | 87 |

# LIST OF FIGURES

| Figure 1.1: | A simple data flow graph with four nodes                                       |

|-------------|--------------------------------------------------------------------------------|

| Figure 1.2: | The data flow graph for second-order filter                                    |

| Figure 1.3: | (a) A data flow graph (b) As Soon As Possible scheduling (c) As Late As        |

|             | Possible scheduling                                                            |

| Figure 2.1: | The support, alpha-cut, core and height of a fuzzy set                         |

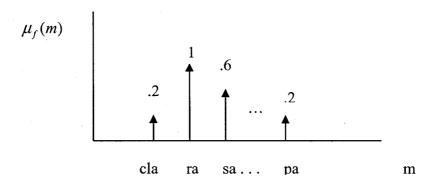

| Figure 3.1: | A utility memberships for some possible modules of addition functional unit    |

|             | 41                                                                             |

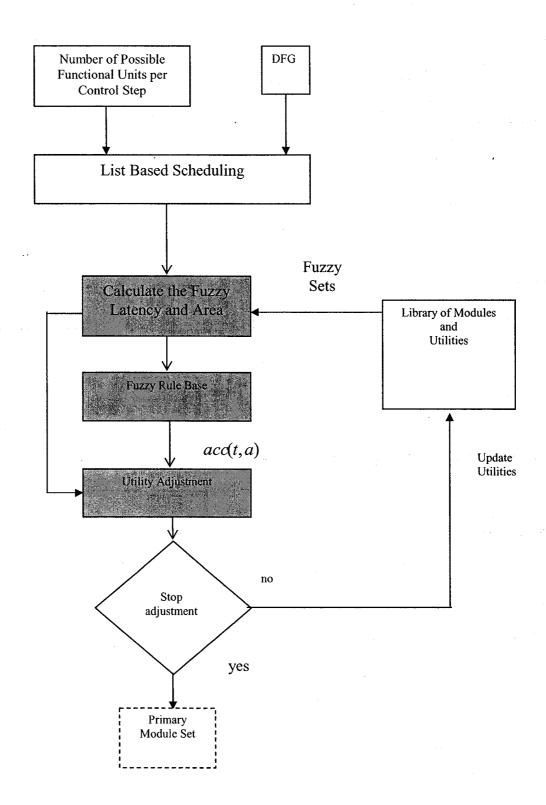

| Figure 3.2: | The proposed module selection scheme                                           |

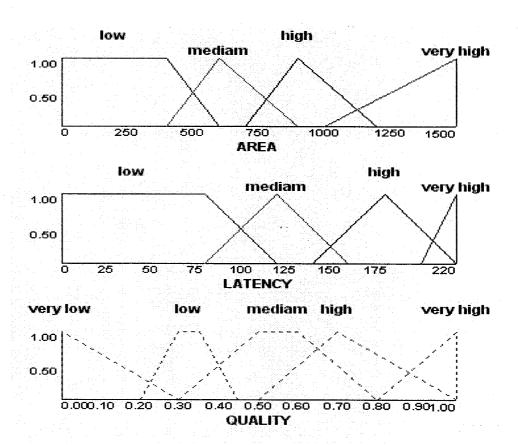

| Figure 3.3: | Membership functions of area, latency, and acceptability linguistic variables  |

|             | 45                                                                             |

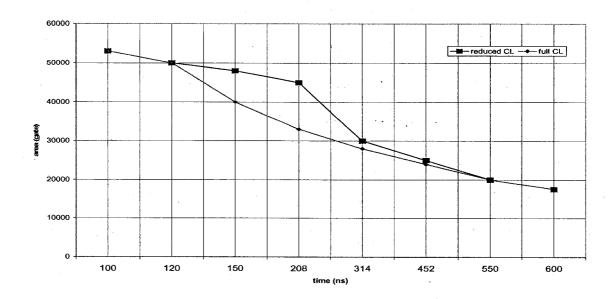

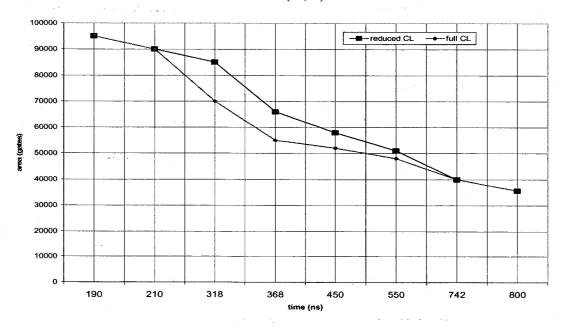

| Figure 3.4: | Area versus latency for EWF with module selection using complete CL and        |

|             | reduced CL, with resource set (+2,*3)                                          |

| Figure 3.5: | Area versus latency for DCT with module selection using complete CL and        |

|             | reduced CL, with resource set (+2,*3)                                          |

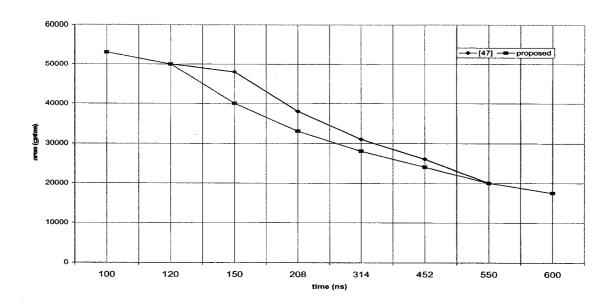

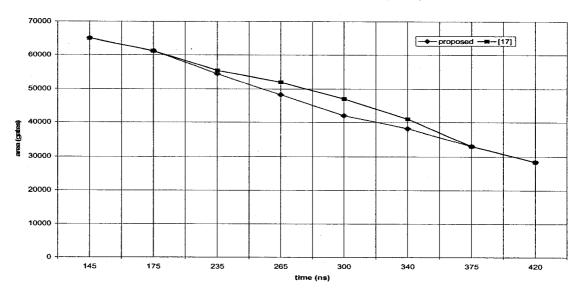

| Figure 3.6: | Area versus latency for fifth-order EWF with module selection using the        |

|             | proposed scheme and the scheme given in [17], with resource set (+2,*2) 53     |

| Figure 3.7: | Area versus latency of fourth-order lattice filter with module selection using |

|             | the proposed scheme and the scheme given in [17], with resource set (+2,*1).   |

|             |                                                                                |

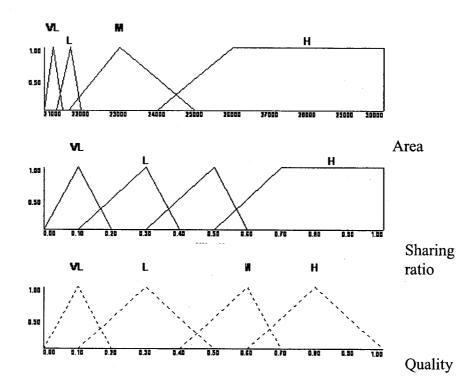

| Figure 4.1: | Area, sharing ratio, and quality membership functions                          |

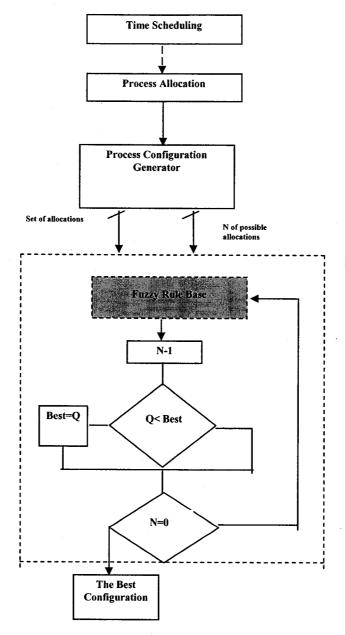

| Figure 4.2: | The proposed process allocation scheme                                         |

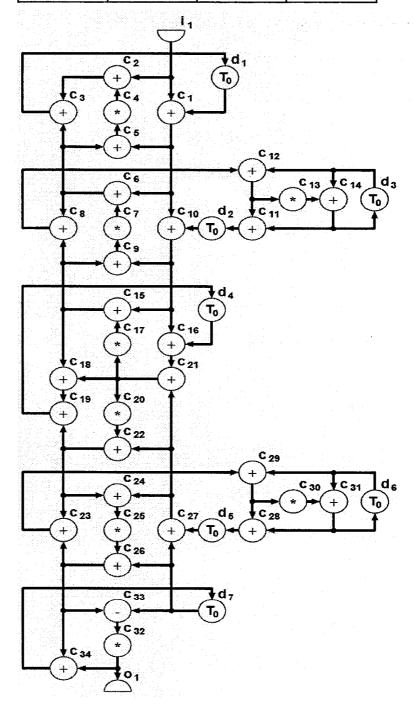

| Figure 4.3: | DFG of a fifth-order elliptic wave digital filter                              |

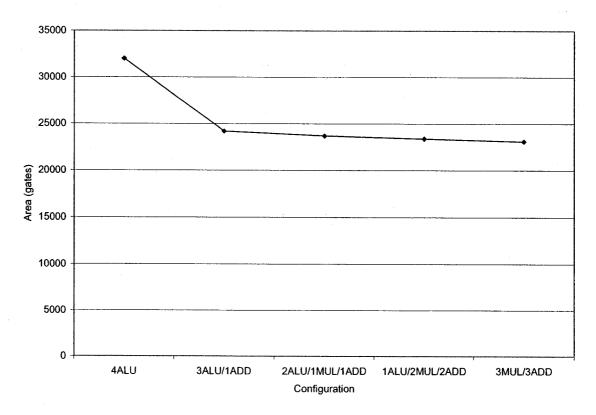

| Figure 4.4: | The total area versus configuration ranging from a fully homogenous to a       |

|             | fully heterogeneous multiprocessor                                             |

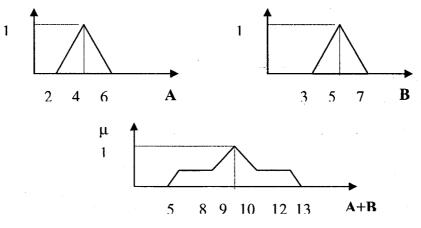

| Figure 5.1: | A fuzzy addition operation                                                     |

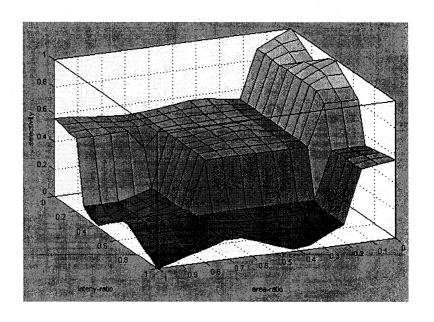

|             | The surface of the fuzzy rule based                                            |

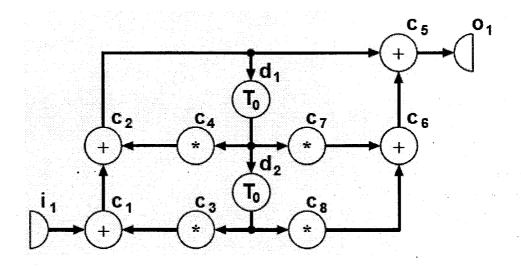

| Figure 5.3: | A DFG of a second-order filter                                                 |

| Figure 5.4: | The fuzzy longest path matrix of the second-order filter                       |

# LIST OF TABLES

| TABLE 1.1: | A COMPARISON OF RESOURCES CONSTRAINED SCHEDULING ALGORITHMS                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| TABLE 1.2: | THE WEAKNESSES IN THE PREVIOUS ALGORITHMS FOR SCHEDULING, PROCESS ALLOCATION, AND MODULE SELECTION IN THE HIGH LEVEL SYNTHESIS |

| TABLE 3.1: | ACCEPTABILITY RULE BASE FOR THE AREA AND LATENCY 45                                                                            |

| TABLE 3.2: | INITIAL LIST-BASED SCHEDULE WITH GENERIC RESOURCES 49                                                                          |

| TABLE 3.3: | COMPONENTS LIBRARY AND THE ASSOCIATED UTILITIES FOR EACH COMPONENT MODULE                                                      |

| TABLE 3.4: | THE UTILITY VALUES FOR ADDER AND MULTIPLIER MODULES OF <i>EWF</i>                                                              |

| TABLE 4.1: | QUALITY RULE BASE FOR THE AREA AND SHARING RATIO 63                                                                            |

| TABLE 4.2: | SPECIFICATIONS OF FUNCTIONAL UNITS 67                                                                                          |

| TABLE 4.3: | DIFFERENT CONFIGURATIONS AND THE CORRESPONDING QUALITIES                                                                       |

| TABLE 4.4: | ALLOCATION MATRIX OF THE FIFTH-ORDER ELLIPTIC WAVE DIGITAL FILTER CORRESPONDING TO THE BEST ALLOCATION 68                      |

| TABLE 5.1: | SELECTIVITY RULE BASE FOR AREA_RATIO AND LATENCY_RATIO                                                                         |

| TABLE 5.2: | THE TIME SCHEDULE OF THE SECOND-ORDER FILTER80                                                                                 |

| TABLE 5.3: | THE LATENCY RESULTS FOR DIFFERENT BENCHMARK PROBLEMS USING THE PROPOSED APPROACH VS. THE CONVENTIONAL APPROACH [36]            |

#### LIST OF SYMBOLS

VA node in a data flow graph  $\boldsymbol{E}$ An edge in a data flow graph Path between the two nodes  $(v_0, v_k)$  $p_{v_0v_k}$  $T_0$ Iteration period bound  $D_{l}$ Total computational delays of all the nodes in loop l $N_{i}$ Number of ideal delay elements loop lST(l)The slack time of a loop lUUniverse of discourse A Arbitrary fuzzy set  $\mu_{A}(u)$ Membership value of the element u  $\eta_+(m)$ Positive contribution of module *m*  $\eta_{-}(m)$ Negative contribution of module m  $adj_f(m)$ Adjustment of utility of module m EFTEarliest firing time Latest firing time LFT  $M(v_i)$ Mobility of node *v*

Set of multiprocessor configurations

β

# Chapter 1

# Introduction

#### 1.1 General

Digital signal processing (DSP) and image processing are among the areas demanding a very high computational power for the implementation of the underlying tasks. Due to the parallelism within the DSP applications, a multiprocessor system is a natural choice for the implementation of these applications. Furthermore, the progress in VLSI technology has resulted in an enormous increase in the hardware execution speed. This has resulted in a wide variety of signals to be processed by digital circuits. Not too long ago, the digital processing of signals was restricted to low-bandwidth signals such as speech. The DSP applications have now been extended to include real-time processing of high-quality audio and video signals.

VLSI technology has now advanced to a stage that it would be rather complex to design a digital system starting at the transistor level or logic level. In the VLSI design, high-level synthesis refers to designing a system at the register transfer level (RTL), rather than looking at the components at the logic gate level. In such a design, a behavioral description or block diagram is used. At this level, an adder, for instance, is viewed as a functional unit instead of as a series of flip-flops and NAND gates. The attributes such as latency, area and type of functional units, however, can be taken into consideration without having to deal with low-level implementations. Scheduling, allocation and module selection are the key tasks that influence these attributes in the

high-level synthesis. A general goal of the high-level synthesis is to find hardware structures that minimize these design attributes subject to certain constraints.

Generally, the design flow of digital systems can be divided into three phases: high level synthesis, logic synthesis and layout synthesis. The higher the level of synthesis, the more the degree of freedom. However, at a higher level of synthesis, less information available about the final circuit parameters to guide the design, and the quality of the final result is considerably affected by the decisions made about the circuit parameters at a higher level of synthesis. Wrong decisions made at a higher level of synthesis could be more expensive than those of lower level. For instance, if a mistake is detected after placing and routing, the whole design process may have to be restarted.

One of the most important issues in high-level synthesis of a DSP task is to obtain a good schedule so as to reduce the overall computation time and the total area. In order to implement and execute a system efficiently, one has to determine an execution order or schedule of all operations in the data flow graph of the DSP application. In order to construct an effective execution order, the knowledge of the characteristics of the functional units, namely, the area and the execution time should be available. However, during the high-level synthesis both the timing and area information of a design component remain imprecise, and ignoring the impreciseness in the synthesis may result in an overly expensive and time consuming design.

In order to achieve a better design of a DSP application, the impreciseness in the design attributes during the synthesis task needs to be properly treated. In a high-level synthesis the impreciseness refers to the lack of the exact knowledge of the relationship between the architectures of the functional units or their final implementations and the

performance of the overall design. The impreciseness during the synthesis of DSP data flow graphs may arise from several sources. It could be from the fact that there exist various choices of off-the-shelf processor modules that can be used to implement a functional unit; hence, the decision as to which architecture should be chosen is ambiguous. Moreover, the detailed characteristics of the functional units are not known at this stage. Since the exact implementation is unknown, the functional unit's characteristics remain imprecise.

Since scheduling, process allocation and module selection are the most critical tasks in the multiprocessor the synthesis of a DSP application represented by data flow graph, on a multiprocessor system, an efficient scheme should be developed to accommodate the imprecise environment. The following sections will first provide a brief review of the necessary background material for the high-level synthesis of the DSP tasks onto multiprocessors. In order to provide motivation for the research work under taken in this thesis, the weaknesses of the current research in the high-level synthesis of such applications and the shortcomings of the schemes of scheduling and allocation in the underlying multiprocessor systems are also discussed. Finally, the objectives of the research and the organization of this thesis are described.

# 1.2 Data Flow Graph

The operations and their precedence relations in an application constitute its specification, which is generally modeled by a vertex-weighted directed graph. The graphical format is thus the representation of the data flow mechanism implied by the system algorithm. The data flow graph (DFG) is proven to be an efficient representation

of the system specification due to its ability to explore the hidden concurrency between the operations of the underlying algorithm. Since DSP applications are known for their inherent parallelism, the DFG model is thus suitable for the behavioral representation of DSP applications.

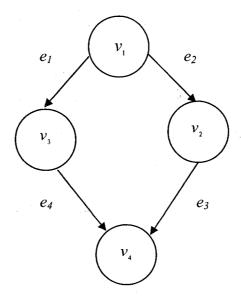

Before discussing the properties of DFGs, some definitions used in the graph theory are first given in here: A graph G, such as the one shown in Figure 1, can be represented by the pair (V, E), where V is a set of vertices or nodes, and E is a set of elements called edges. Each edge is associated with a pair of nodes. A graph is directed if each edge in G is associated with an ordered pair of nodes [4].

The symbols  $v_1, v_2 \dots v_{n-1}, v_n$  are used to represent the nodes and the symbols  $e_I, e_2, \dots$  are used to represent the edges of the graph. A directed edge  $e_{ij} = (v_i, v_j)$  is incident out of the node  $v_i$  and incident into the node  $v_j$ . A directed edge is usually called an arc. The nodes  $v_i$  and  $v_j$  are called the end nodes of the edge  $e_{ij}$ . The node  $v_i$  is called the initial node, and the node  $v_j$  the terminal node of the edge  $e_{ij}$ . If  $v_i = v_j$  then the edge  $e_{ij}$  is called a self-loop. The arcs of DSP graphs represent the precedence constraints between their end nodes.

A direct path  $p_{v_0v_k}$  is a finite sequence of distinct nodes  $v_0 \dots v_k$  and distinct edges such that the edge  $(v_i, v_{i+1})$  is present in the path  $p_{v_0v_k}$ . If  $v_0 = v_k$  then this path is called a directed circuit or loop. Each loop in a DSP graph must contain at least one ideal delay element for the graph to be computable. The data flow graph that contains at least one directed circuit is called the *cyclic graph*, otherwise it is *acyclic*.

Figure 1.1: A simple data flow graph with four nodes.

# 1.3 High-Level Synthesis

A high-level synthesis can be described as the process of transformation of a behavioral description into a structural description that consist of a set of connected components collectively called the data path and a controller that sequences and controls the functionality of these components. The synthesis task starts at behavioral level and proceeds downwards to register transfer level (RTL), logic level and finally circuit level, each time adding some additional information needed at the next level of synthesis.

The synthesis task is to take the specification of the behavioral requirement of a system and a set of constraints and goals to be satisfied, and then to find a structure that implements the behavioral requirement while satisfying these goals and constraints. The behavior means the way the system and its components interact with their environment, i.e., the mapping from inputs to outputs. The structure refers to the set of components and

their interconnection that is used to implement the system. Usually there are many different structures that can be used to realize a given behavior. One of the tasks of the synthesis is to find the structure that best meets the constraints, such as the limitations on the cycle time, area or power, while minimizing other costs. For example, the goal might be to minimize the area while achieving a certain minimum-processing rate [1].

In recent years there has been a trend toward carrying out the synthesis at higher and higher levels of the design hierarchy. High-level synthesis is gaining acceptance in industry, and there has been considerable interest shown in the synthesis at higher levels. There are a number of reasons for this [1, 2]:

- a. Shorter design cycle. Since more of the design processes at lower levels are automated, it is possible to hit the market window by carrying out the synthesis at higher levels. Furthermore since much of the cost of the chip is in the design development, automating more of that process can lower the cost significantly.

- **b.** Fewer errors. Having more automation in the design process eliminates the errors due to human factors and reduces the verification time of the design.

- c. The ability to search the design space. A good synthesis system can produce several designs for the same specification in a reasonable amount of time. This allows the developer to explore different trade-offs between cost, speed, power, and so on, or to take an existing design and produce a functionally equivalent one that is faster or less expensive.

It is expected that the trend toward the high level synthesis will continue. Already there are a number of research groups working on high-level synthesis, and great deal of progress has been made in finding good techniques for optimizing and for exploring design trade-off. These techniques are very important because decisions made at the high level trend to have a much greater impact on the design than those at lower levels.

In general there are many advantages of investigating a design at high level. First, designer can concentrate on studying the design behavior rather than the detailed implementation. Second, RTL design of a digital system is usually less complex than the design details at the logic level. Thus, its simulation can be done faster. Further, studying an RTL design also allows the designers to quickly explore the design space and decide as to which architecture best fits their needs.

Some of the applications that need such high level synthesis are digital signal processing (DSP), communications, and image processing. These applications demand a high computational power. That is, these applications are computational intensive, and must be executed at high speed with high throughput. Furthermore, issues such as low cost, low power and small chip area are other important issues. Due to the parallelism within DSP applications (e.g. digital filters), a multiprocessor system is a natural choice for the implementation of these applications [2, 3].

An interesting technique used to implement a DSP application is known as application specific integrated circuit (ASIC). The ASICs are integrated circuits that are dedicated to perform specific tasks. They can be designed at the RTL level from multiprocessing elements, memory storage, and necessary interconnection.

# 1.4 The Synthesis Task

Scheduling, allocation, and model selection are the most important steps in the synthesis task. They represent the core of transforming the behavior into a structure. They are

closely interrelated and depend on each other. Scheduling consist in assigning the operations to the control steps to be executed. The control steps are fundamental sequences in a synchronous system; they correspond to a clock cycles. Allocation consists in assigning the operations to generic hardware resources. Module selection is the process of selecting suitable functional unit subject to constraints.

#### 1.4.1 Scheduling

Scheduling is one of the basic tasks in a high-level synthesis to produce an execution order of each operational node. The aim of the scheduling is to minimize the amount of time or the number of the control steps needed to complete of the application given certain constraints on the available hardware resources [5-7].

Scheduling is significant when the relative execution order of the operations has an effect on the speed, throughput, or any other performance measure of the system design. Thus, an important purpose of the scheduling process is to achieve some objective functions, while satisfying some design constraints, e.g., iteration period, throughput, hardware resources, input-output delay, area cost, and power [7].

#### Some Basic Concepts in Scheduling

When the operations that have to be scheduled and the precedence relations are known beforehand, the scheduling can take place at the compile time. This is known as *static* scheduling. Static scheduling differs from *dynamic scheduling*, which schedules the operations at run time. In this thesis, only static scheduling is considered.

Another characteristic of a scheduling method is whether or not it allows operations to be interrupted once their execution has begun. If it is possible and the interrupted operations can be resumed at a later time, the scheduling is called *pre-emptive scheduling*. In contrast, *non pre-emptive scheduling* requires that operations are executed without interruptions.

When an algorithm is scheduled for execution on a multiprocessor, several optimization goals can be set. It is possible to minimize the *throughput delay* (or *latency*) which is the time between the consumption of an input sample and the production of the corresponding output sample. This optimization goal is typical for *resource-constrained scheduling*. For resource constrained scheduling the hardware is specified and it cannot be changed by the scheduling method. In contrast, a *time-constrained scheduling* tries to use as little hardware as possible when an execution speed is given.

Scheduling methods exploit the parallelism that exists between operations of the same iteration of a cyclic data flow graph (*intra-iteration parallelism*). However, the cyclic data flow graphs often contain parallelism between operations from different iterations (*inter-iteration parallelism*). Scheduling algorithms can also exploit this parallelism by allowing operations from different iterations to be executed in parallel. The schedules that are then produced are called *overlapped schedules*. These schedules contrast the *non-overlapped schedules*, where for every iteration period only operations belonging to that iteration are executed.

Cyclo-static schedules form a special class of overlapped schedules. In a cyclo-static schedule an operation does not have to be executed on the same processing element for every iteration period. Schedules corresponding to subsequent iterations can have a

constant displacement in the processor space. Cyclo-static schedules differ from *fully-static schedules* in which each operation is assigned to the same processing element for all iterations.

#### **Performance Bounds**

There are some performance bounds for multiprocessor scheduling problems. These bounds give the minimum values for some of the optimization goals that can be chosen. These bounds cannot always be achieved for every multiprocessor configuration, yet they provide a means to estimate the quality of schedules found by a scheduling algorithm. Furthermore, they can be used by the scheduling method to guide its search for a good schedule. Some bounds that are commonly used [8, 9] are now briefly described.

The *iteration period bound* (IPB) gives a lower bound on the iteration period when unlimited hardware is available. When the DFG contains no loops, the iteration period can be made arbitrarily small. Otherwise IPB is calculated as

$$T_{o} = IPB = \max \left[ \frac{D_{i}}{N_{i}} \right]$$

where l represents a loop in the cyclic DFG and  $D_l$  is the sum of the computational delays of all the nodes in loop l, and  $N_l$  is the number of its ideal delay elements. The loop l that results in the IPB is called the *critical loop* of the DFG.

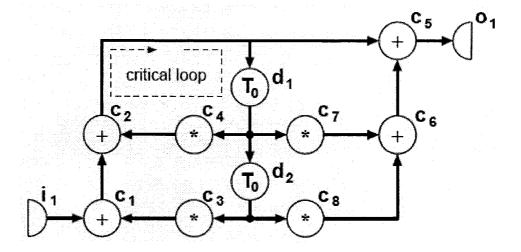

To give an example, consider the second-order filter given in Figure 1.2. Assume that an addition requires 1 TU (time unit) to execute and a multiplication 2 TU. The critical loop of this example is shown Figure 1.2. It easily follows that the iteration period bound is 3.

The slack time of a loop l is defined as the number of control steps by which the loop can be expanded before violating any inter-iteration precedence constraints, and is given by

$$ST(l) = T_0 N_l - D_l$$

where  $T_0 = IPB$ , the slack time of the critical loop of a schedule is usually zero. A slack time of zero implies that when one operation in the loop is scheduled, there is no freedom in choosing the firing times of the other operations in the loop. These firing times are then all fixed. When the slack time of a loop is larger than zero, there is more freedom of choice in scheduling the operations in the loop.

Another bound is the *periodic delay bound* (PDB), which gives the lower bound on the latency of the schedule when the iteration period is equal to IPB. The bound is given by

$$PDB = L_{0} = \max_{P \in I/\rho \text{ path}} \left( D_{P} - T_{0} N_{P} \right)$$

where P is the set of paths from input to output. The path P that determines the value of PDB is called the critical path.

The third bound is the *processor bound* (PB), which gives the minimum number of processors that are necessary to have a schedule with  $T_0 = IPB$ .

$$PB = \left\lceil \frac{D_{DFG}}{T_0} \right\rceil_{T_0 = IPB}$$

Figure 1.2: The data flow graph for second-order filter

#### **Determining the Time Frames of the Schedule**

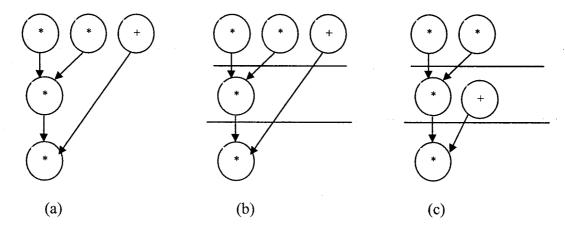

In general, DFGs expose parallelism in DSP applications. Each node has a range of possible control steps that can be assigned to it. Most of scheduling algorithms that will be described later require the earliest and the latest bounds within which an operation in the DFG can be scheduled (time frames). The first and simplest schemes that are used to determine these bounds are called as *soon as possible* (ASAP) and as *late as possible* (ALAP) algorithms.

#### **ASAP Algorithm**

A simple scheme to find the earliest control step for an operation to be scheduled is carried out by using the "as soon as possible" algorithm, as is done in Carnegie Mellon University's Emerald/Facet system [10] and CATREE system from University of Waterloo [11].

The ASAP algorithm starts with the highest nodes (that have no parents) in the DFG and assigns these nodes to control steps in increasing order as it proceeds downwards. It follows a simple rule, that is, a successor node can be executed only after

its parent has been executed. This algorithm clearly results in a schedule with least number of control steps but never takes into account the resource constraint. Figure 1.3b illustrates an ASAP schedule for the DFG shown in Figure 1.3a.

#### **ALAP Algorithm**

This algorithm is a refinement of the ASAP scheduling concept with conditional postponement of operation [12]. This algorithm is used to find the latest control step for an operation to be scheduled. The ALAP algorithm works exactly in the same way as the ASAP Algorithm expect that it starts at the bottom of the DFG and proceeds upwards given a certain latency. This algorithm gives the slowest possible schedule that takes the maximum number of control steps. However, this does not necessarily reduce the number of functional units used. Figure 1.3c illustrates an ALAP schedule for the DFG shown in Figure 1.3a.

#### 1.4.2 Classification of Multiprocessor Scheduling Techniques

Over the years researchers have tried to come up with various kinds of solutions [10-21] to the scheduling problem. Several algorithms have been put forth and each one has its own advantages and disadvantages. Scheduling algorithms can be broadly classified into time-constrained scheduling and resource-constrained scheduling, based on the goal of the scheduling problem. In time-constrained scheduling, the number of functional units tends to be minimized for a fixed number of control steps. On the other hand, in resource-constrained scheduling, the number of control steps tends to be minimized for a given design cost (number of functional units and storage units).

#### (a) Time-Constrained Scheduling

The time constrained scheduling is also called fixed control steps approach. The time constrained scheduling is important for the designs targeted towards application in real time systems such as digital signal processing (DSP) systems, where the main objective is to minimize the cost of the hardware. An example of a time constrained scheduling algorithm is the force-directed scheduling method.

Figure 1.3: (a) A data flow graph (b) As Soon As Possible scheduling (c) As Late As Possible scheduling.

#### **Force-Directed Scheduling**

The force-directed scheduling (FDS) is a heuristic method [14, 15] that is a very popular scheduling technique for time constrained scheduling. This algorithm achieves the goal of minimizing the total number of functional units by uniformly distributing the operations of the same type over the available control steps. This algorithm is briefly explained below.

FDS uses a guiding factor called force, which is calculated for each operation.

This guiding factor is used in the selection of the operation to be scheduled and in the

choice of the control step. The force between an operation and a particular control step is proportional to the number of the operations of the same type that can be scheduled for that control step. The schedule is built by giving a priority to the minimum force value for a pair of operation and control step. Then, the forces are updated and the process repeated. The advantage of this technique is that it can be used in scheduling with pipelined functional units.

The complexity of the FDS algorithm is  $O(cn^2)$ , where c is the number of control steps and n is the number of the operations in the DFG. The FDS algorithm does not always produces an optimal solution.

#### (b) Resource-Constrained Scheduling

In applications where the design is restricted by the silicon area, resource constrained scheduling algorithm is useful. The goal of these algorithms is to produce a design with the best possible performance but still meet the given resource constraints. The schedule is gradually constructed, one operation at a time, so that the resource constraints and data dependencies are not violated. The number operations scheduled in any control step should not exceed the number of functional units available. Also the algorithm ensures that all the predecessors are scheduled before that operation. The following is the description of two popular scheduling algorithms in this category.

#### **List-Based Scheduling**

The scheduling technique described in [16] belongs to list-based scheduling algorithms. List-based scheduling is a generalization of the ASAP scheduling algorithm with the inclusion of the resource constraint. A list-based scheduling maintains a priority list of ready nodes, i.e., nodes whose predecessors have already been scheduled. The priority

order for each operation is sorted with a priority function that resolves any resource contention. In any iteration, operations with higher priority are scheduled first and lower priority operations are deferred to later control steps. Scheduling an operation to a control step makes other succeeding operations ready, to be added to the priority list. A simple priority function can be inversely proportional to the mobility (the difference between ALAP and ASAP schedules), i.e., the greater the mobility the lower the priority and vice versa.

As can be seen, the success of a list scheduler depends mainly on the priority function used. Mobility is a good priority function, since smaller the mobility higher the urgency for scheduling. There are many other priority functions that have been proposed. The time and space complexity for this approach is slightly higher than the other list-based scheduling algorithms, since several lists have to be maintained dynamically.

#### **Static List Scheduling**

This approach [17] starts by creating a single large list before starting scheduling. This algorithm differs from the ordinary list-based scheduling algorithm in both the assignment of control steps as well as in maintaining the priority list. The algorithm first uses the ASAP and ALAP algorithms to obtain the earliest and the latest possible control step assignments for each operation. The algorithm then sorts all the operations in an ascending order of latest possible control step labels as the primary key and then sorts each set of operations with the same latest control step labels in a descending order of the earliest possible control step labels as the secondary key.

Once the priority list is created the operations are scheduled sequentially starting with the last operation in the priority list (i.e., the operation with the highest priority). In

each iteration when the limit for the number of resources is reached, the rest of the operations are deferred to later control steps. This scheduling technique has an advantage over the ordinary list based approach: A list is constructed once statically and not grown dynamically.

#### **Comparison of List-Based and Static List Scheduling Algorithms**

The two scheduling algorithms described above are the most popular methods for scheduling operations under resource constraints. Table 1.2 gives a comparison between the two approaches.

TABLE 1.1: A COMPARISON OF RESOURCES CONSTRAINED SCHEDULING ALGORITHMS

| Properties               | 📜 List-based 🔭  | Static list            |

|--------------------------|-----------------|------------------------|

| Computational complexity | High            | Not very high          |

| Quality of schedule      | Mostly optimal  | Mostly optimal         |

| Space complexity         | Very high       | Not high               |

| Input problem size       | Any size        | Any size               |

| Execution speed          | Slower than FDS | Faster than list-based |

#### 1.4.3 Allocation Process

Allocation is a task of determining generic resources (functional units) on which operational nodes are executed. It involves assigning operations and variables to hardware resources and specifying their usage while trying to minimize the amount of hardware resources needed. It assumed that an instance of a generic resource could only start one operation at a time. In particular, this includes two subtasks, which are to determine the number of generic resources used and to bind nodes to resources. A generic resource type may be, for instance, an adder unit, a multiplier unit, or an ALU which is capable of performing multiple operations such additions, multiplications, etc.

In order to the minimize of the number of hardware resources required for the implementation of a digital system, the operations (nodes) of a DFG can be grouped to share a single hardware unit if they have mutually exclusive schedule or life time. Sets of these mutually exclusive nodes are formed. A single hardware resource is then allocated to each distinct set. Thus, the minimization problem is the problem of decreasing the number of sets. This type of allocation is known as folding. Folding is usually affected by the types of hardware resources.

Hardware functional units may be homogenous or heterogeneous. The functional units are homogenous if all of them are of the same type and execute the same set of different types of operations. Each type of operations has a different computational delay, since such functional units usually require more hardware resources to support multiple operations. Homogenous functional units if used in the synthesis process may result in inefficient designs. Arithmetic logic units (ALUs) are suitable for homogenous design. The heterogeneous functional units, on the other hand, vary in the operations they support, and have different execution delays [15].

Data path allocation involves the mapping operations, onto the functional units, and also assigning values to registers, and providing interconnections between the operators and registers using buses and multiplexers. The optimization goal is usually to minimize some objective function, such as the total interconnect length, the total number of registers, the bus driver and multiplexer cost, or the critical path delays. There may also be one or more constraints on the design which limit the total area of the design, the total throughput, or the delay from input to output.

The techniques used to perform data path allocation can be classified into two types, the global type and the iterative/constructive type. The global techniques find simultaneous solutions to a number of assignments at a time, whereas the iterative/constructive techniques assign nodes one at a time. Exhaustive search is an extreme case of the global technique. The iterative/constructive techniques generally look for a smaller of the search space than the global techniques do, and therefore, are more efficient, but are less likely to find the optimal solutions.

### 1.4.4 Combined Scheduling and Allocation

Both scheduling and allocation are the required tasks in a high level synthesis. To achieve optimized synthesis results, the scheduler must have some knowledge in advance about the hardware resources available and those needed by the target system. This knowledge includes the information about the hardware units, such as the computational delay, access time, and interconnection. This information is available after the hardware allocation process has been completed. In addition, the allocation process needs to know the control step at which an operation is to be scheduled. As a result, the minimum number of hardware required and the operations assigned to them are determined. Thus, there is an interdependence between the scheduling and the process allocation.

Many researchers focus on performing the tasks of scheduling and allocation in two different stages. Since there are interactions between these tasks, another attractive approach is to solve both of these tasks simultaneously. Regardless of the approach used, using the constraints specified in advance under the user control, it is possible to start with the one that best achieves these constraints.

#### 1.4.5 Module Selection

In the scheduling and allocation techniques discussed in sections 1.4.1-1.4.4, the resource types have been assumed to be generic. That is, all the adders (multipliers) are of the same kind, if more than one adder (multiplier) is needed. In the module selection problem, this assumption is no longer valid. For instant if two multipliers are required, these may be of different kinds, e.g. fully parallel and serial-parallel multipliers. Both the multipliers can provide the same functionality but have different characteristics, such as one is faster than the other and/or one smaller than the other. When considering module selections, multiple design attributes, such as timing, area, and power etc. are often involved. These attributes normally conflict with each other. The task of module selection is to find a mapping from the functional units to the existing modules (architectures) in a library, which leads to an optimized design depending on the design criteria.

Besides finding the schedule and the allocation, the module selection is another important phase in a high-level synthesis. They all have relationships with one another. Different selected modules may result in a different schedule/allocation and vice versa. This then results in a system with a different performance.

# 1.5 Design Space Exploration

Since there are various choices of the modules to be used in a synthesis process, a system can have several implementations. Each implementation has a different set of properties. The design space in this context refers to the set of all possible module bindings as well as their schedules. Given a module binding, the best schedule needs to be generated for a design, in order for it to be evaluated and compared with other designs.

Considering the tradeoffs among the conflicting criteria in evaluating the module bindings and their schedules in the design space, the design exploration, therefore, is the process of finding the most desirable design from the design space. The meaning of the term "desirable" depends on the design criteria. If our goal is to minimize both the latency and the area, an optimal design refers to the design whose latency and area is the least.

High-level synthesis provides a designer with the capability of a rapid design space exploration. A designer can examine the tradeoffs between the various designs without getting into the details of the implementation. The exploration of the design space at a lower level, say at logic level, is limited, since changing each gate level design is a time consuming task.

# 1.6 The Weaknesses of the Current Research in the High-Level Synthesis

In the previous sections, a review of the existing work in the high-level synthesis has been given. Table 1.2, summarizes the weaknesses in the previous research that has been conducted in the area of high-level synthesis. Scheduling, process allocation, and module selections are inter-dependent tasks in a high-level synthesis. The result of one can affect the others. Because of their complexity, some researchers have ignored the dependencies between these tasks and tackle each one as an individual phase. Leive *et al* [18] have presented a solution to the module selection problem. In this scheme, the module selection phase is carried out without taking into account the effects of the scheduling and process allocation on that selection. Jain and Parker [19] have developed a module

selection framework in high-level synthesis. However, they have assumed that the module selection phase is performed prior to the scheduling and process allocation.

**TABLE 1.2:** THE WEAKNESSES IN THE PREVIOUS ALGORITHMS FOR SCHEDULING, PROCESS ALLOCATION, AND MODULE SELECTION IN THE HIGH LEVEL SYNTHESIS

| Algorithm      | Weaknesses 117 Table 144                                                                           |

|----------------|----------------------------------------------------------------------------------------------------|

| Reference [18] | Does not consider simultaneous scheduling, process allocation, module selection.                   |

| Reference [19] | Does not consider simultaneous scheduling, process allocation, module selection.                   |

| Reference [20] | Uses exponential ILP approach to find the schedule, which is time consuming                        |

| Reference [21] | Impractical for large systems                                                                      |

| Reference [22] | Uses branch and bound approach to find the best modules bindings which time consuming.             |

| Reference [23] | Generates too many numbers of schedules to find the best module binding.                           |

| Reference [24] | Does not consider multiple design criteria in evaluating the synthesis results in the design space |

In the work concerning a combined scheme of scheduling, process allocation, and module selection, several heuristics have been proposed. Some approaches use artificial intelligence methods or simulated annealing [23], whereas others use an iterative heuristic [24]. All these methods can not be applied to large systems in practical sense. Other techniques [20] have attempted to find an optimal solution via an integer linear

programming (ILP) approach. However, the complexity of the approach grows exponentially.

Regardless of the consideration of the interaction between the synthesis tasks, none of the approaches cited in Table 1.2 consider the impreciseness in the system attributes in developing the synthesis models.

### 1.7 Scope and Organization of the Thesis

As discussed above, none of the previous work in the scheduling, process allocation and module selection for the high-level synthesis considers the impreciseness that arises from the lack of the exact knowledge of the relationship between the architecture of the functional units and their final implementations and the performance of the overall design. The objective of this thesis is to incorporate these sources of impreciseness into a more general model of a high-level synthesis in order to find the scheduling, process allocation, and module selection that are practically more realistic in achieving the final implementation. In this thesis, the impreciseness incorporated in the synthesis model is represented by using fuzzy theory and fuzzy rule base.

The inter-dependence among the scheduling, process allocation, and module selection is included in the synthesis framework developed in this thesis. This framework tends to explore the design space more efficiently; since it allows various choices of the modules to be used during the synthesis process. Having more flexibility in the choice of modules in the high-level synthesis provides the designer the ability to find a more optimized design.

In Chapter 2, background material on fuzzy logic necessary to characterize the impreciseness in the system attributes and in developing the synthesis model is reviewed. In Chapter 3, a framework using fuzzy rule base and the theory of fuzzy logic for the module selection that allows the designer to select the best modules for the design depending on the tradeoffs between the system attributes, area and latency, is proposed. Chapter 4 presents a new allocation technique that use fuzzy rule base to find the best multiprocessor configuration for rate-optimal scheduling of a fully static data flow graph (DFG). In Chapter 5, a new algorithm for scheduling of DSP data flow graphs with processing time characterized by fuzzy sets is proposed. Chapter 6 concludes the thesis by highlighting the contribution of this research and making some suggestions for possible future work.

# Chapter 2

# **Fuzzy Logic and Uncertainty**

### 2.1 Introduction

Fuzzy logic was developed by Lotfi A. Zadeh in the 1960s in order to provide mathematical rules and functions which permitted natural language queries. Fuzzy logic provides a means of calculating intermediate values between absolute true (a value of 1) and absolute false (a value of 0). With fuzzy logic, it is possible to calculate the degree to which an item is a member of a set. Fuzzy logic calculates the shades of gray between black/white and true/false.

Fuzzy logic is a superset of the conventional (or Boolean) logic and contains similarities and differences with the Boolean logic. Fuzzy logic is similar to the Boolean logic, in that Boolean logic results are returned by fuzzy logic operations when all the fuzzy memberships are restricted to 0 and 1. Fuzzy logic differs from the Boolean logic in that it is permissive of natural language queries and is more like human thinking; it is based on degrees of truth.

This chapter gives an introduction to the fundamental notions and concepts of fuzzy logic and fuzzy sets. In the following section, we address different points of view about the definition of uncertainty.

### 2.2 Definition of the Uncertainty

In this section we review different points of view about the definition of uncertainty, its types, and causes. These points of view belong to Zimmerman [25], Klir [26] and Dubois and Prade [27].

### 2.2.1 Zimmerman's Point of View

Zimmerman [25] defines "certainty" as "the case when one has the appropriate quantitative and qualitative information to describe, prescribe or predict deterministically and numerically a system, its behavior or other phenomena". Anything not described by this definition shall be called "uncertain". Furthermore, Zimmerman introduces a classification of uncertainty causes based on the quality and quantity of the available information. He classifies the causes of uncertainty as follows.

#### Lack of information

This cause of uncertainty may be considered as the most frequent one. For example, in decision logic, one calls "decision under uncertainty" the case in which a decision making process lacks information about the possible states of nature that will occur. This kind of information which is not available can be considered as quantitative lack of information. The counterpart of this kind of information lack is the qualitative one. In this case, the decision making process has information about the probabilities for the occurrence of various states but it is not sure which state will occur; this is called "decision making under risk". "Approximation" is another situation that can be described by the lack of information. This depends on the situation presented. For instance, one can consider that the available information is sufficient for his/her situation and he/she does

not have or does not want to gather more information to make an exact description.

Transition from a situation of "uncertainty" caused by a lack of information to a situation of "certainty" can be achieved by increasing the available information or collecting information with better quality which depends on the situation.

#### Abundance of information

This is due to the capability of a system to process a large amount of data at the same time. To reduce the complexity, people tend to classify the available data into understandable form by using coarser grid or rougher "granularity" or by concentrating on the most important features and neglecting the not useful information for that situation. To do so, especially in scientific activities, some kind of "scaling" is used.

#### • Conflicting evidence

This situation occurs when the available information describing two different behaviors of a system are conflicting. The reason for this conflict may be the erroneous available information, it may also be information of irrelevant features of the system is being used, or the model of the system which the observer has is wrong. In this situation, correcting the available information can make transition from "uncertain" to state of "certain.

### • Ambiguity

Ambiguity is a situation in which certain information has a different meaning based on the situation. From the mathematical point of view, it is the situation in which we have one-to-many mapping. This type of uncertainty can be classified under lack of information because adding more information about the situation may put us in a situation closer to certainty.

#### Measurement

Measurement means describing the physical properties of a system or objects such as weight, temperature, length, etc. The precision of the measured quantity depends on the accuracy of the used tools. The quality of measuring technology has increased with time but it has not reached the perfection. In this situation we have uncertainty about real measure and the only available information is the indicated measure.

#### Belief

This cause of uncertainty appears when subjective information is available as a kind of belief in a certain situation. This belief is built by an observer (expert) from past subjective information about the system or by statistical data about the system.

#### 2.2.2 Klir's Point of View

Klir [26] found that there are six definitions of the word "uncertain" in the dictionary:

- Not certainly known, questionable, problematical.

- Vague, not definite or determined.

- Doubtful, not having certain knowledge, not sure.

- Ambiguous

- Not steady or constant, varying.

- Liable to change or vary, not dependable or reliable.

When a more detailed investigation about these meanings was conducted, Klir found that uncertainty can be captured by two classes; vagueness and ambiguity. The former is related to the difficulty of making sharp or precise distinction in the world. The latter is associated with one-to-many relations, which means situations with two or more

alternatives in which the choice between them is left unspecified. In addition, Klir introduced a recent definition of uncertainty based on its connection with the information theory. The most fundamental aspect of this connection is that uncertainty included in any situation is a result of some information deficiency. Information may be incomplete, imprecise, fragmentary, not fully reliable, vague, contradictory, or deficient in some other way.

#### 2.2.3 Dubois and Prade's Point of View

Dubois and Prade [27] state that imprecision and uncertainty can be considered as two complementary aspects of a single reality, that of imperfect information. It has been observed that much of this information often cannot be obtained as precise and definite numbers for various reasons; imperfect measuring instruments, the fact that the sole source of information is a human being and the information is imprecise, incoherent, and in any case incomplete. Doubois and Prade could clearly distinguish the concepts of imprecision and uncertainty: imprecision is associated with the content of a piece of information, while uncertainty is associated with its truth. Imprecision refers to lack of knowledge about the value of a physical parameter. The possible values of the parameter are represented by a certain interval obtained experimentally or from an expert. This interval represents the imprecision in the physical parameter. Certainty refers to the degree of truth that the value of the physical parameter belongs to a certain interval. In other words, each element belonging to this interval has a certain possibility to be the actual value of the physical parameter. This possibility is associated with a weight that is derived from the available knowledge about the physical parameter. When there are different imprecision intervals representing the value of the physical parameter, then

these intervals are used to construct a new interval without sharp boundaries. This interval is represented by a fuzzy set as it is explained later in this chapter. Each element belonging to this interval has a degree of truth of being the actual value of the physical parameter. Therefore, this new interval represents the uncertainty of the physical parameter.

Uncertainty can be judged by means of different qualifiers such as probable, possible, or necessary. Probable has two different meanings, one is related to statistical experiments, and the other is related to subjective judgment. Like probable, possible has two interpretations as well: physical (as a measure of material difficulty of performing an action), and subjective judgment. On the other hand, necessary has much stronger notion, in either the physical or the subjective sense. A piece of information will be called precise when the subset associated with its value or component cannot be subdivided. From the above overview about uncertainty and its causes, it is seen that Dubois and Prade's definition of uncertainty is more comprehensive and practical than those the others.

### 2.3 Fuzzy Sets and Fuzzy Logic

Fuzzy sets were introduced in 1965 by Lotfi Zadeh [28], as a means to model the uncertainty of the real world. They are used to represent imprecise, ambiguous, or vague information. Fuzzy logic which was introduced in 1973 by the same author [29], is a superset of the conventional Boolean logic that has been extended to handle the intermediate values between "completely true" and "completely false".

Boolean logic has two values often defined as true or false, on or off, black or white. However, in the real world there are many situations where events are not black or

white but some shade of gray. Fuzzy logic is a continuous form of logic that allows us to describe the shades of gray. If one is asked to describe his/her day in Boolean logic, it would be good or bad. Fuzzy logic might recognize the day as being very bad, bad, poor, average, better than average, good, very good.

Classic logical systems are based on Boolean logic, which assumes that every element is either a member or a non-member of a given set (never both). Unfortunately, this system imposes an inherent restriction on the representation of imprecise concepts. Assuming that Boolean logic is used to identify whether a room temperature is "hot" or "cold", most people would agree that 100°F is a "hot" room temperature and 25°F is a "cold" room temperature. However, if the room temperature falls to 75°F, it becomes much harder to classify the temperature as "hot" or "cold"; Boolean logic does not provide the means to identify an intermediate value.

Fuzzy logic extends Boolean logic to handle the expression of vague concepts and, as a result, solve the preceding problem. To express imprecision in a quantitative fashion, it introduces a set membership function that maps elements to real values between zero and one (inclusive); the value indicates the "degree" to which an element belongs to a set. A membership value of zero indicates that the element is entirely outside the set, whereas a one indicates that the element lies entirely inside a given set. Any value between the two extremes indicates a degree of partial membership to the set. In the example discussed in the previous paragraph, if fuzzy logic is used to represent the "hotness" of a room, 100 °F would have a membership value of one and 25 °F would have a membership value of 0. On the other hand, 75 °F would have a membership value between zero and one.

Zadeh defines the process of "fuzzification" as a methodology to generalize any specific theory from a crisp to a fuzzy form. This is achieved by applying the extension principle. Researchers have applied this principle on many areas such as control, reasoning, mathematical programming, decision making, pattern recognition, and many others.

In addition to its role in modeling and processing imprecise or ambiguous information, fuzzy logic is used to model complex systems. These systems are difficult to be described using mathematical relations. In addition, mathematical modeling becomes more difficult when there are uncertainties and ambiguities in the systems to be modeled.

Zadeh's approach was later expanded into fuzzy systems modeling by Sugeno and Yasukawa [30], Bezdek [31]]. Fuzzy modeling is a qualitative modeling scheme by which we qualitatively describe system behavior using natural language. The relation between the inputs and outputs of the system is given in the form of IF-THEN rules. There are two approaches of fuzzy systems modeling: one is *subjective* where the system behavior is established based on the knowledge of an expert and the other is *objective* where the system behavior is established from input-output data via fuzzy clustering algorithms [32].

### 2.4 Classical Set and Fuzzy Set

Let U be the universe of discourse which consists of all possible elements that are associated with a particular context or application. A crisp set A defined on U may be represented by listing all the elements that satisfy the definition of A in the case that A is

finite (the list method). If A is infinite, it can represented by specifying the rules that must be satisfied by the elements of U to be considered elements of A (rule method). The former method is limited. On the other hand, the later method is more general. The membership function  $\mu_A(x)$  of a classical set A defined on U by using the rule method is defined by:

$$\mu_{A}(u) = \begin{cases} 1, & \text{if } u \in A \\ 0, & \text{if } u \notin A \end{cases}$$

This means that an element u is either a member of set A (with  $\mu_{A}(u) = 1$ ) or not a member (with  $\mu_{A}(u) = 0$ ). A fuzzy set, introduced by Zadeh [27], is a set with graded membership. In a fuzzy set each element of U belongs to the set A with a membership degree characterized by a real number in the closed interval [0, 1] (i.e.,  $\mu_{A}(u) \in [0, 1]$ ). An element may belong to the fuzzy set with lesser degree than another element; however, they both belong to the same fuzzy set.

Since a fuzzy set may contain elements with zero degree membership and elements with one degree membership, then we can consider the concept of a crisp (classical) set to be a special case of the more general concept of a fuzzy set.

### 2.5 Representation of a Fuzzy Set

There are two methods to represent fuzzy sets:

1. A set of ordered pairs representation: a fuzzy set A in U may be represented as a set of ordered pairs of a generic element u and its membership value, that is

$$A = \{(u, \mu_A(u) | u \in U\}$$

When U is discrete A is commonly written as

$$A = \sum_{i=1}^{m} \mu_A(u_i) / u_i = \mu_A(u_1) / u_1 + ... + \mu_A(u_m) / u_m$$

In this equation the summation sign does not represent arithmetic addition, it represents the collection of all points  $u \in U$  with the associated membership function  $\mu_{A}(u)$ .

**Example:** Let A = integer close to 10, then one possibility to define this fuzzy set is as follows:

$$A = 0.1/7 + 0.5/8 + 0.8/9 + 1/10 + 0.8/11 + 0.5/12 + 0.1/13$$

The following can be noted for this fuzzy set

- The integers not explicitly shown all have membership values equal to zero.

- The membership values were chosen by a specific individual; except for the unity membership value when u = 10, they can be modified based on our own personal interpretation of the phrase "close."

- The membership function is symmetric about u = 10, because there is no reason to believe that integers to the left of 10 are close to 10 in a different way than are integers to the right of 10. But again, we are free to make other interpretations.

- 2. Functional representation: In this representation functional description is used to represent fuzzy sets. An example is the functional description of a trapezoidal-shaped fuzzy set, as

$$\mu_{A}(u) = \begin{cases} \frac{u - a1}{a2 - a1} & \text{If} \quad a_{1} \le u \le a_{2} \\ 1 & \text{If} \quad a_{2} \le u \le a_{3} \\ 1 - \frac{a3 - u}{a3 - a4} & \text{If} \quad a_{3} \le u \le a_{4} \end{cases}$$

## 2.6 Basic Characteristics of Fuzzy Sets

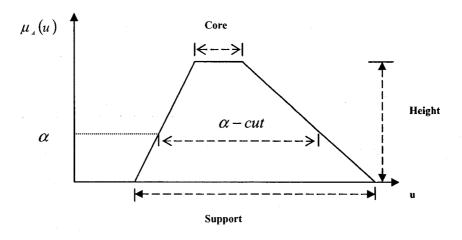

We now introduce some important characteristics associated with the fuzzy sets. These characteristics are illustrated in Figure 2.1 and explained below.

1. The support of a fuzzy set A within a universe of discourse U is the crisp set that contains all elements of U that have nonzero membership in A, that is,

$$\operatorname{supp}(A) = \left\{ u \in U \mid \mu_{A}(u) > 0 \right\}$$

2. The core of a fuzzy set A within a range U, is the crisp set that contains all elements of U that have the membership of unity in A, that is,

$$core(A) = \{u \in U \mid \mu_{A}(u) = 1\}$$

note that the core of a fuzzy set is a subset of its support.

Figure 2.1: The support, alpha-cut, core and height of a fuzzy set

3. The height of a fuzzy set A is the largest membership grade obtained by any element in that set, that is,

$$h(A) = \sup_{u \in U} \mu_A(u)$$

A fuzzy set with a height equal to 1 is called normal and with h(A) < 1 subnormal.

4. An  $\alpha$ -cut of a fuzzy set is a crisp set  $A_{\alpha}$  that contains all the elements in U that have membership values in A greater than or equal to  $\alpha$ , that is,

$$\alpha - cut(A) = \{ u \in U \mid \mu_{A}(u) \ge \alpha \}$$

The core of a fuzzy set is an  $\alpha$ -cut with  $\alpha = 1$ .

# Chapter 3

# A Module Selection Scheme in the High Level Synthesis using Fuzzy Logic

### 3.1 Introduction

Module selection is one of basic architectural synthesis tasks that allows optimizing the cost of a target circuit under a real time constraint. Adding the area factor to the optimization problem changes the working domain from one dimension (time) to two-dimensions (time and area). However, solving this problem by the best selection of modules from a complex library of modules remains unresolved.

Most of the techniques for high level synthesis of real time architectures use a specific hardware module for a given type of functional units to optimize the design area. Although by using a specific module for each type of functional units reduces the complexity of the synthesis process, it may prevent a designer from meeting the design goal. On the other hand, having various choices of the modules to be used during the synthesis process is more flexible in the high-level synthesis; it provides the designer the ability to find a more optimized design. In this chapter a new framework for the module selection in high-level synthesis is proposed. The proposed framework employs a fuzzy rule base and fuzzy theory to find the *module set* that satisfies a given time constraints while at the same time tends to minimize the total design cost in terms of the area. However, the meaning of the term *module set is* the complete set of modules that are

selected from the components library (CL) to implement the design. This set may include no or many instances of a given module that exists in the CL.

# 3.2 Previous Work

During the design space exploration process, the designers seek to find an optimized implementation for a given behavioural specification. In the SEHWA algorithm [33] effort is devoted to select the modules by analyzing the time/area design space. This selection is performed at the first step during the high-level synthesis followed by the scheduling and process allocation. This algorithm allows the use of either fast or slow module in a design, but a simultaneous use of both fast and slow modules is not considered.

Gajski in [34] perform the selection of modules prior to the scheduling and process allocation. Then, the scheduling and process allocation is carried out and the results are evaluated. If the constraints are not met, the set of modules is changed by an if-then rule base system. This iterative process is only partial, since for each selection of the modules, a complete design has to be generated and evaluated, which is a time consuming process.

MSSR algorithm [35], attempts to solve the scheduling, process allocation and module selection at the same time. The algorithm is based on an iterative improvement and structured in three procedures. The procedure *OPSL*, which is the third procedure in the algorithm structure, is used to select an appropriate module from the associated library to be mapped to each operation in a DFG. This procedure starts with modules that have the largest area. Then, it iteratively investigates modules with smaller area until the

time constraint is violated. Depending on the given time constraint, this approach may need to explore the possible solutions.

In [20], an algorithm for module selection using unrestricted module library is proposed. The algorithm starts by initial module selection, and then the scheduler tries to meet the time constraints with this selection. If the scheduler does not succeed, the module selection has to be reviewed until a correct selection is made. The algorithm formulates the module selection problem using the ILP formulation and iterates the module selection, which is a very time consuming process, before finding the best schedule

Sllame and Drabek in [17] used a genetic algorithm for the scheduling, allocation and module selection. Genetic algorithms are global probabilistic search techniques that start from an initial population of generated potential solutions to a problem, and gradually evolve towards better solutions through a repetitive application of genetic operators such as crossover and mutation. In this approach, each chromosome in the initial population consists of two parts: the priorities of nodes, and the possible modules of each type of functional units. The priority of each node in a chromosome is determined by the number of nodes succeeding that node in given DFG, which is a weak priority function that will lead to inefficient schedules; hence, it will affect the module selection process.

### 3.3 The Proposed Module Selection Scheme

In this section, a scheme for the module selection problem is presented. In this scheme, each module is associated with a utility value, which represents the usefulness of a

module for a given design goal. Ideally, the utility values of modules are either 0 or 1. The design using those modules with the utility value of 1 should be of the highest quality. However, in reality, the usefulness of a module is dependent on the other modules that can be used. The module may be present in good design which optimizes a certain goal and/or part of a bad design that does not satisfy the design goal. Accordingly, we allow the utility value of a module to be any real number between 0 and 1 to handle the ambiguity in estimating the usefulness of a module.