# **NOTE TO USERS**

This reproduction is the best copy available.

# Tuning and Topology Optimization of the Clock Distribution Network Under Obstacle Constraints

# **Haydar Saaied**

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University Montreal, Quebec, Canada

October 2004

© Haydar Saaied

Library and Archives Canada

chives Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 0-494-04058-0 Our file Notre référence ISBN: 0-494-04058-0

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

Tuning and Topology Optimization of the Clock Distribution Network Under Obstacle Constraints

Haydar Saaied, Ph.D. Concordia University, 2004

Our research focuses on routing the Clock Distribution Network (CDN). The CDN consumes an increasing portion of all resources in terms of wiring area, power, and design time. Different approaches that have been proposed, such as Deferred-Merge Embedding algorithm (DME) and Greedy-DME (GDME), require the re-calculation of the whole solution when there is a change in the skew constraint or the location or the load capacitance of the clock pins. Redesigning the CDN would be an extremely computation intensive process for a complex system, and very painful with the increase in demand for shorter time to market. For this reason, we have used an incremental routing scheme. The incremental routing or ECO (Engineering Change Order) routing is a new field that has been introduced to meet the demand of high performance and complex designs.

We propose a new method, called Adaptive Wire Adjustment (AWA), to minimize the skew of a given CDN to any given bound by tuning its wire lengths in order to cope with minor modifications in System on Chip (SoC) during the design process. The proposed algorithm outperforms DME and GDME for implementing ECO for large CDNs. Moreover, to speed up AWA's convergence, we propose the use of a Local Topology Modification (LTM) technique. Additionally, LTM helps to enhance the CDN's quality in terms of total wire length and wire elongations. We show that GDME relies heavily on wire elongations and offers a solution that suffers from large Standard Deviation of the Path Lengths (SDPL) between clock pins and the CDN's root. To our knowledge, this thesis is one of the first of its kind that deals with minor CDN's modifications and local topology modification.

In addition to satisfying the timing requirements, the CDN has to be routed with minimum wire length. Moreover, it is often the case that the interconnects of a net must not intersect with some obstacles in the routing plane. We propose a simple model called Shortest Paths Polygon (SPP) to describe the routing area of shortest paths between two points among obstacles. A methodology is proposed to determine the SPP of two points using a gridless graph. The SPP model facilitates a better routing of any multi-terminal net since it determines all shortest paths. Consequently, using the SPP would provide a good correlation between detailed routing and other design phases. This is important because it satisfies the system requirements and supports ECO routing effectively. The SPP model is applied to three problems related to the CDN routing: tuning the CDN under obstacle constraints, designing a ZSCDN under obstacle constraints, and routing the CDN in two layers.

#### **ACKNOWLEDGMENT**

I have been very fortunate to have Dr. Dhamin Al-Khalili and Dr. Asim J. Al-Khalili as my supervisors and it is hard to acknowledge them in few words. Dr. Dhamin was always there with his knowledge, good advice and deep insight. His patience and compassion will always be remembered. Dr. Asim made me love the field of VLSI. Ever since, I've been knocking on his door, day and night, seeking his guidance and wisdom.

I wish to express my gratitude to Dr. B. Jaumard from University of Montreal, the optimization centre, for her support and expert advice on optimization.

I am grateful to Dr. Mohamad Nekili for his support and encouragement. I benefited so much from his insightful thoughts on high speed interconnect.

Many thanks to my wife, Mrs. Ibtihal Fadhil, for her kind support and encouragment.

I would like to reserve my deepest thanks for my first teachers: my parents, Mr. and Mrs. Al-Taraihi, and my uncle, Dr. Taki Al-Taraihi. I am extremely indebted to them for their unconditional love, sincerity, and their tradition of encouraging me and my brothers to pursue science.

# TABLE OF CONTENTS

| Chapter 1: Introduction                                           | 1  |

|-------------------------------------------------------------------|----|

| 1.1 System on Chip Design                                         | 1  |

| 1.1.1 Chip Interconnects                                          | 2  |

| 1.1.2 The Design Methodology                                      | 3  |

| 1.2 Clock Distribution Network                                    | 5  |

| 1.3. Overview of the Dissertation                                 | 7  |

| Chapter 2: Clock Distribution Network                             | 10 |

| 2.1 Introduction                                                  | 10 |

| 2.2 Clock Skew                                                    | 10 |

| 2.3 Preliminaries of The CDN Synthesis                            | 14 |

| 2.3.1 Graphical Model of the CDN                                  | 14 |

| 2.3.2 Delay Model of The CDN                                      | 15 |

| 2.3.3 Power Dissipation of The CDN                                | 16 |

| 2.3.4 Problem Definition                                          | 17 |

| 2.4 CDN Synthesis Using Geometric Approaches                      | 17 |

| 2.4.1 H-Tree                                                      | 18 |

| 2.4.2 Method of Means and Medians (MMM)                           | 19 |

| 2.4.3 Geometric Matching Algorithm (GMA)                          | 20 |

| 2.5 CDN Synthesis Using Elmore Delay Model                        | 21 |

| 2.5.1 Tsay's Method                                               | 21 |

| 2.5.2 Differed Merge Embedding (DME) Algorithm                    | 23 |

| 2.5.3 Greedy Differed Merge Embedding (GDME) Algorithm            | 26 |

| 2.6 Shortcomings of Previous Approaches                           | 27 |

| Chapter 3 Tuning the Clock Distribution Network                   | 29 |

| 3.1 Introduction                                                  | 29 |

| 3.2 Clock Distribution Network Tuning by Adaptive Wire Adjustment | 30 |

| 3.3 Convergence of AWA Algorithm                                  | 36 |

| 3.4 Implementation and Results                                    | 42 |

| 3.4.1 Comparing AWA's Performance to DME and GDME                 | 44 |

| 3.4.2 CDN's Tuning Using AWA                                      | 49 |

| 3.5 Summary                                                       | 54 |

| Chapter 4: Local Topology Modification                            | 56 |

| 4.1 Introduction                                                            | 56  |

|-----------------------------------------------------------------------------|-----|

| 4.2 Quadratic Tree vs. Binary Tree                                          | 58  |

| 4.3 Local Topology Modification Using a Search Tree                         | 62  |

| 4.4 Applying the LTM Method to AWA, DME and GDME Algorithms                 | 66  |

| 4.5 Implementation and Results                                              | 69  |

| 4.5.1 Applying LTM to AWA, DME and GDME Algorithms                          | 69  |

| 4.5.2 Impact of LTM on the Convergence of AWA Algorithm                     | 72  |

| 4.6 Summary                                                                 | 74  |

| Chapter 5: Tuning the Clock Distribution Network Under Obstacle Constraints | 76  |

| 5.1 Introduction                                                            | 76  |

| 5.2 Definitions                                                             | 79  |

| 5.2.1 Manhattan Arc                                                         | 79  |

| 5.2.2 The notations Y and Q                                                 | 80  |

| 5.2.3 Problem Formulation                                                   | 81  |

| 5.3 Shortest Paths Polygon                                                  | 82  |

| 5.3.1 Polarity of a Convex Point of an Obstacle                             | 86  |

| 5.3.2 SPP's Vertices                                                        | 88  |

| 5.4 SPP Determination                                                       | 90  |

| 5.4.1 The interrelated Shortest paths                                       | 92  |

| 5.4.2 Boundary Arcs Determination                                           | 92  |

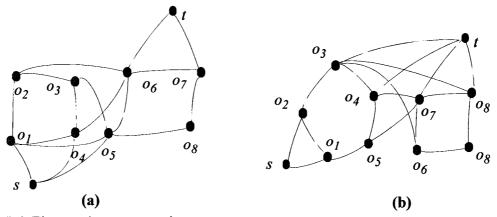

| 5.5 Balancing Segment Determination                                         | 97  |

| 5.6 Incorporating the SPP Methodology into AWA Algorithm                    | 100 |

| 5.7 Implementation and Results                                              | 102 |

| 5.7.1 Building ZSCDN Using SPP-AWA                                          | 103 |

| 5.7.2 CDN Tuning Under Obstacle Constraints                                 | 104 |

| 5.8 Summary                                                                 | 106 |

| Chapter 6: Incorporation of SPP Model for Special Cases                     | 110 |

| 6.1 Introduction                                                            | 110 |

| 6.2 Preliminary                                                             | 112 |

| 6.3 Determination of a Link in the Visibility Graph                         | 115 |

| 6.3.1 Link Determination Between a Point and an Arc                         | 115 |

| 6.3.2 Link Determination Between Two Arcs                                   | 120 |

| 6.4 Applying the SPP Model to the DME Algorithm                             | 122 |

| 6 5 Planar Clock Distribution Network                                       | 124 |

| 6.5.1 The Inner Product Operation                                      | 127 |  |

|------------------------------------------------------------------------|-----|--|

| 6.5.2 The SPP Formation                                                | 128 |  |

| 6.5.3 Applying SPP to Planar CDN Determination                         | 131 |  |

| 6.6 Results                                                            | 132 |  |

| 6.6.1 Clock Distribution Network Under Obstacle Constraints            | 133 |  |

| 6.6.2 Planar Clock Distribution Network                                | 136 |  |

| Chapter 7: Conclusions and Future Work                                 | 139 |  |

| 7.1 Summary                                                            | 139 |  |

| 7.2 Contributions                                                      | 143 |  |

| 7.3 Suggestions for Future Work                                        | 144 |  |

| 7.3.1 Incorporation the LTM and SPP Concepts into Different Algorithms | 144 |  |

| 7.3.2 Incremental Buffer Insertion into the CDN                        | 144 |  |

| 7.3.3 Incremental Link Insertion into the CDN                          | 144 |  |

| 7.3.4 Differential CDN                                                 | 145 |  |

| 7.3.5 Applying RLC Delay Model to Proposed Approaches                  | 145 |  |

| 7.3.6 Wire Length Estimation Under Obstacle Constraints                | 146 |  |

| 7.3.7 SPP Router                                                       | 146 |  |

| 7.3.8 Incremental Place and route                                      | 147 |  |

| References                                                             | 148 |  |

| Appendix A: Local Topology Modification Using Quadratic Optimization   | 159 |  |

| Appendix B: Determination of the Arc Projection                        |     |  |

### LIST OF FIGURES

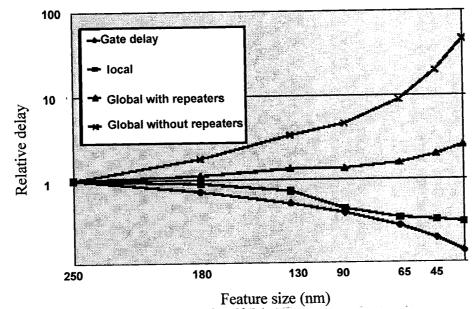

| Figure 1.1  | Delay for interconnect versus feature size (courtesy ITRS 2003) [1].                                                                                                                                         | 3  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

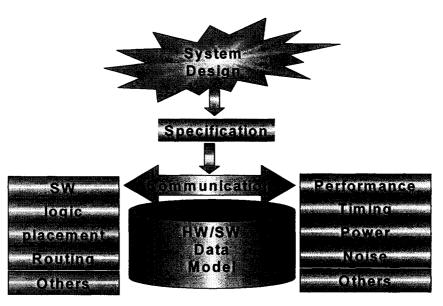

| Figure 1.2  | Design methodology as projected by ITRS 2003 for technology less than 65 nm.                                                                                                                                 | 4  |

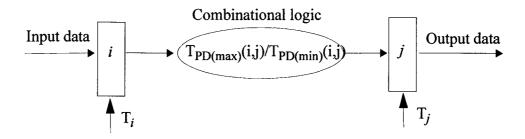

| Figure 2.1  | Pair of sequentially adjacent registers                                                                                                                                                                      | 11 |

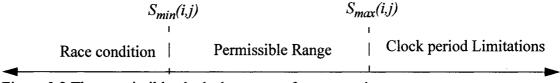

| Figure 2.2  | The permissible skew ranges of two registers                                                                                                                                                                 | 13 |

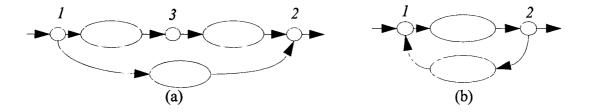

| Figure 2.3  | Global data path (A) A Parallel data path (B) A feedback data path                                                                                                                                           | 14 |

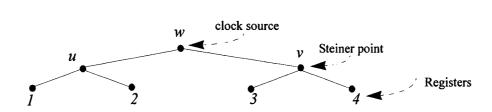

| Figure 2.4  | The topology tree of a CDN                                                                                                                                                                                   | 15 |

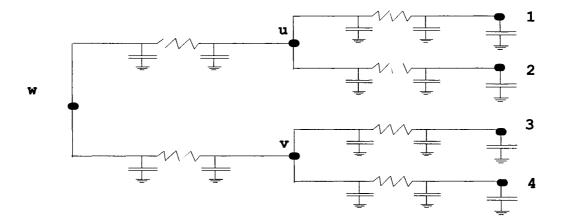

| Figure 2.5  | The RC-Tree of the tree shown in Figure 2.4                                                                                                                                                                  | 16 |

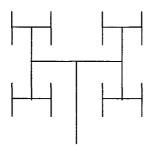

| Figure 2.6  | The H-tree                                                                                                                                                                                                   | 18 |

| Figure 2.7  | The MMM algorithm                                                                                                                                                                                            | 19 |

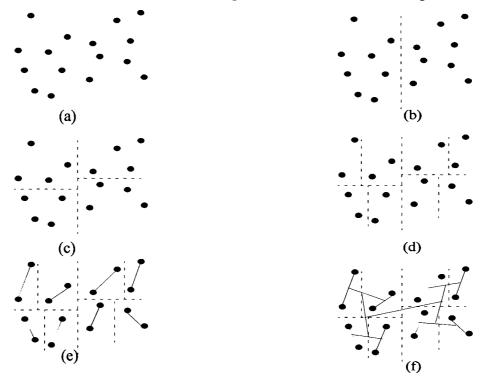

| Figure 2.8  | The GMA algorithm                                                                                                                                                                                            | 20 |

| Figure 2.9  | The Determination of the edge lengths using Tsay approach                                                                                                                                                    | 23 |

| Figure 2.10 | The wire elongation                                                                                                                                                                                          | 23 |

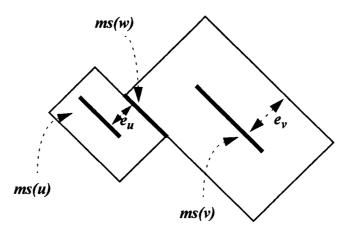

| Figure 2.11 | Calculating the merging segment of $w$ during the first phase when $0 < x < 1$                                                                                                                               | 25 |

| Figure 2.12 | Selecting the exact location of a node from its merging segment                                                                                                                                              | 26 |

| Figure 3.1  | Selecting the balancing node in a tree.                                                                                                                                                                      | 32 |

| Figure 3.2  | The leaf delay ranges of the sub-trees rooted at nodes $u$ , $v$ and $w$ of Figure 3.1.                                                                                                                      | 32 |

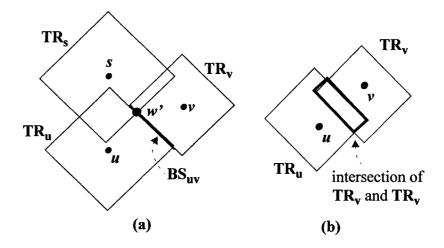

| Figure 3.3  | (a) Determination of $\mathrm{BS}_{uv}$ and the new location of the balancing node, $w'$ .<br>(b) The intersection of $\mathrm{TR}_u$ and $\mathrm{TR}_v$ is a tilted rectangle when $e_u + e_v > Rect_{uv}$ | 34 |

| Figure 3.4  | The AWA algorithm                                                                                                                                                                                            | 35 |

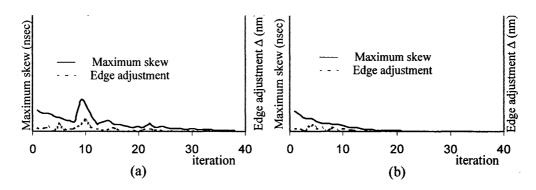

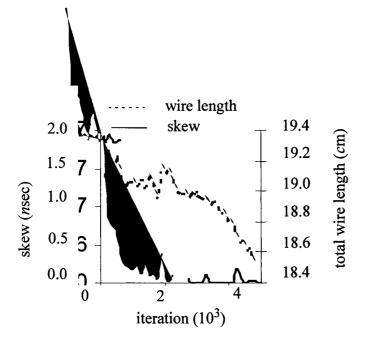

| Figure 3.5  | For a set of 32 clock pins (a) the skew convergence of AWA algorithm (b) the skew convergence of AWA algorithm when the BN's edge is adjusted theoretically as in Equation 3.10.                             | 42 |

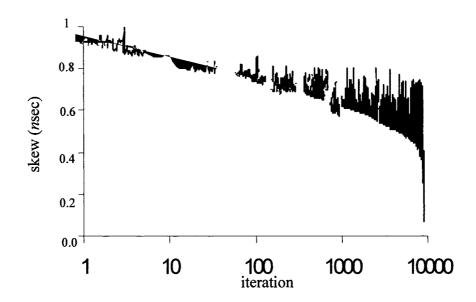

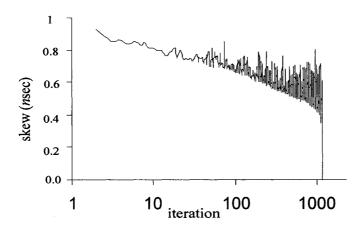

| Figure 3.6  | The AWA skew convergence for the benchmark r3.                                                                                                                                                               | 45 |

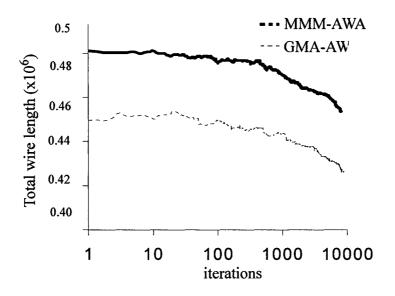

| Figure 3.7  | Relation between AWA's iteration and the total wire length for the benchmark r3.                                                                                                                             | 45 |

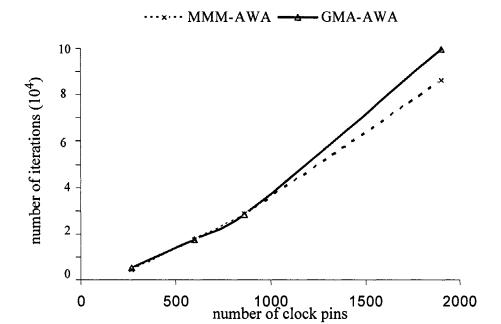

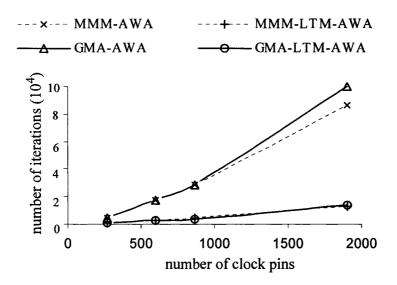

| Figure 3.8  | Relation between the number of clock pins and the number of iterations of AWA algorithm.                                                                                                                     | 47 |

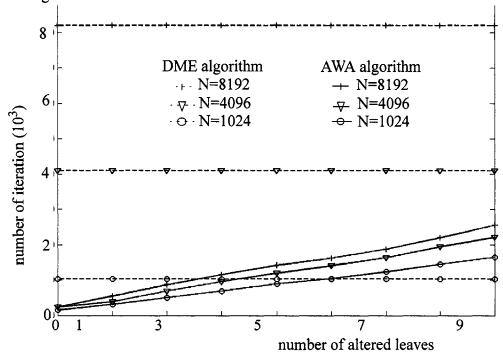

| Figure 3.9  | Relation between AWA's iteration and the number of altered leaves for ZSCDNs of different benchmarks of clock pins.                                                                                          | 48 |

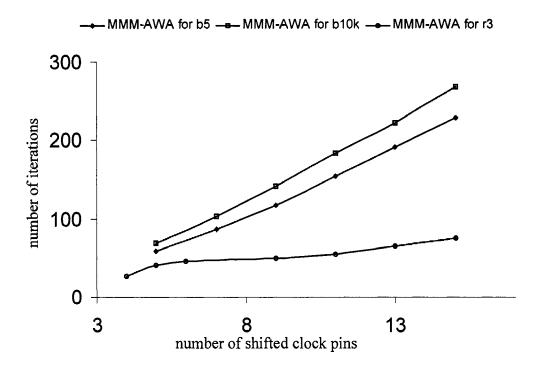

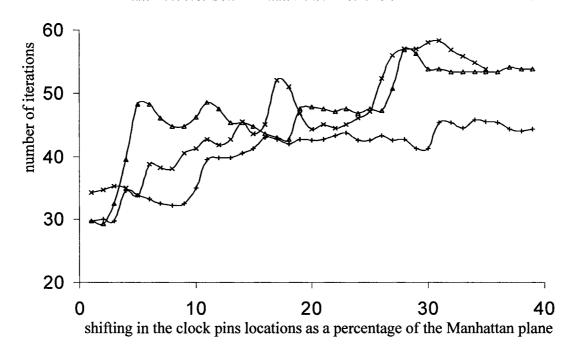

| Figure 3.10 | Relation between AWA's iteration and the number of shifted clock pins for benchmarks r3, b5k and b10k.                                                                                                       | 50 |

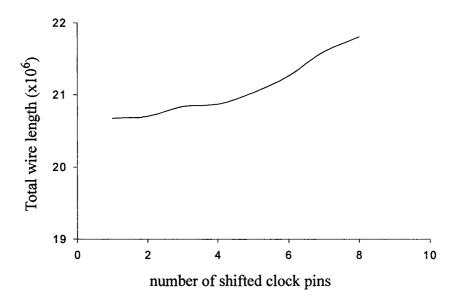

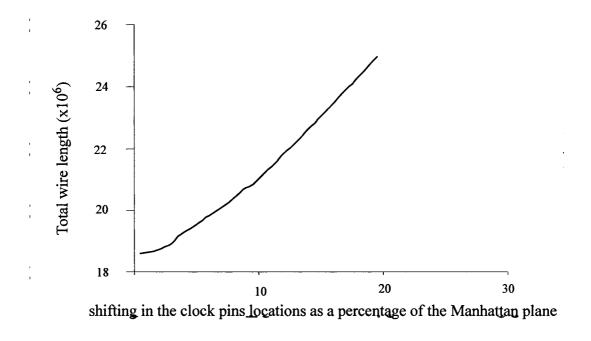

| Figure 3.11 | Relation between the total wire length and the number of shifted clock pins for benchmark b5k.                                                                                                       | 51 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.12 | Relation between the number of iteration and the shifting in the location of                                                                                                                         | 52 |

|             | ten clock pins in benchmarks r3, b5k and b10k.                                                                                                                                                       |    |

| Figure 3.13 | Relation between the total wire length and the shifting in the clock pins for                                                                                                                        | 52 |

|             | the benchmark b5k                                                                                                                                                                                    |    |

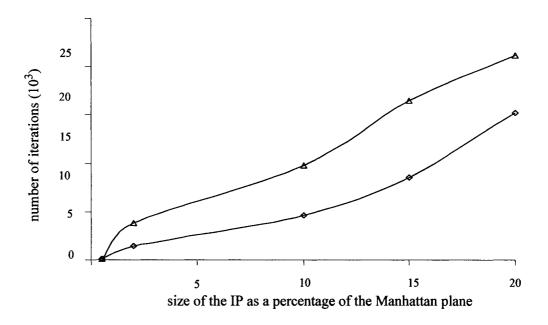

| Figure 3.14 | Relation between AWA's iteration and the size of the deleted and inserted IP. The size is given as percentage of the whole die area.                                                                 | 54 |

| Figure 4.1  | An example of minimizing the total wire length by modifying the topology                                                                                                                             | 59 |

| Figure 4.2  | The Quadratic tree.                                                                                                                                                                                  | 59 |

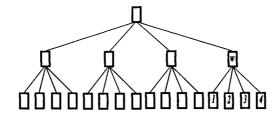

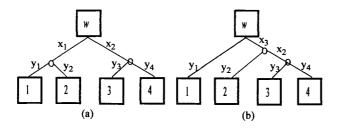

| Figure 4.3  | The primary topologies of connecting a node to its four children.                                                                                                                                    | 60 |

| Figure 4.4  | The non primary topologies of connecting a node to its four children.                                                                                                                                | 61 |

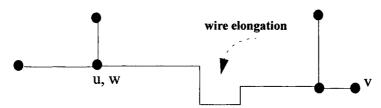

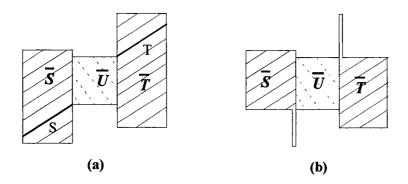

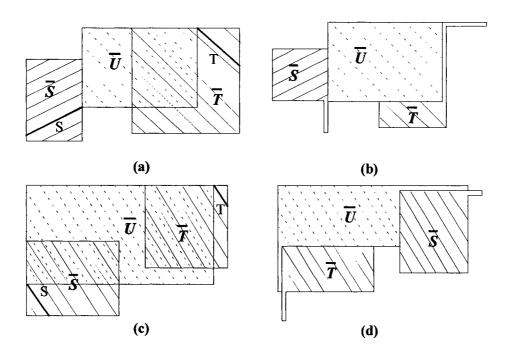

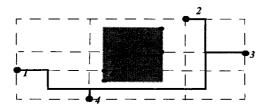

| Figure 4.5  | Avoiding wire elongation by modifying the topologies of the RST and/or                                                                                                                               | 63 |

|             | the clock signal flow (the drawing is not to scale).                                                                                                                                                 |    |

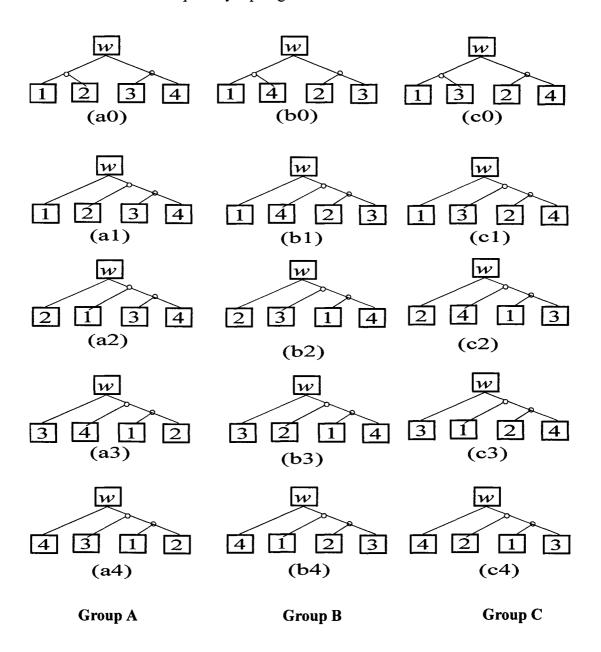

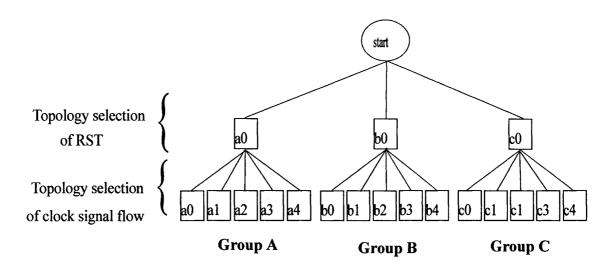

| Figure 4.6  | The searching tree for the optimal topology. The labels refer to topologies labeling in Figure 4.3.                                                                                                  | 64 |

| Figure 4.7  | The LTM procedure.                                                                                                                                                                                   | 66 |

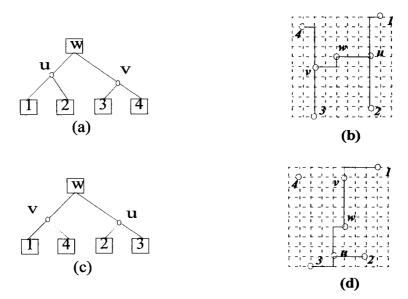

| Figure 4.8  | Applying LTM helps node to be swapped                                                                                                                                                                | 65 |

| Figure 4.9  | The LTM-AWA algorithm.                                                                                                                                                                               | 67 |

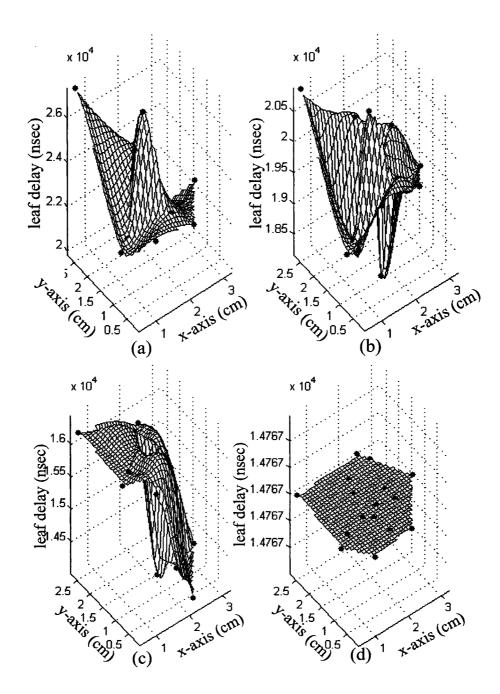

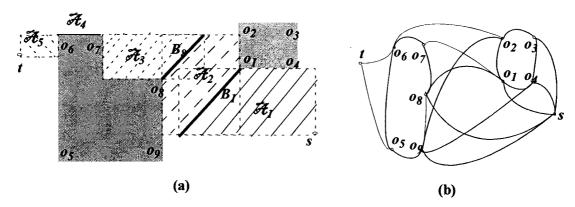

| Figure 4.10 | Leaf delays plane of a tree of 16 leaves during the running of LTM-AWA at: (a) the beginning (b) iteration 1 (c) iteration 9 (b) iteration 10.                                                       | 68 |

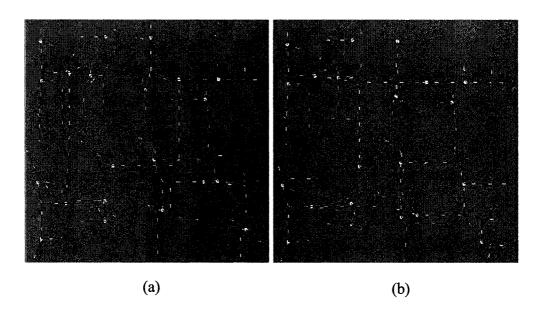

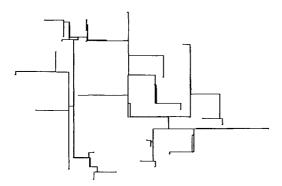

| Figure 4.11 | The resulting ZSCDN for 64 clock pins by using (a) DME (b) LTM-DME.                                                                                                                                  | 70 |

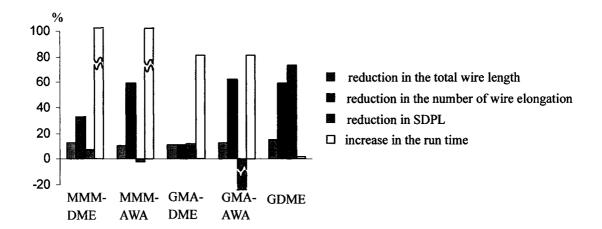

| Figure 4.12 | The comparisons of different parameters for benchmark r3 when the LTM                                                                                                                                | 72 |

|             | is applied to different algorithms.                                                                                                                                                                  |    |

| Figure 4.13 | The skew convergence of LTM-AWA for the benchmark r3.                                                                                                                                                | 73 |

| Figure 4.14 | Relation between the number of clock pins and the number of iterations of AWA and LTM-AWA.                                                                                                           | 73 |

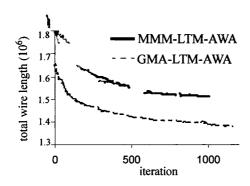

| Figure 4.15 | The relation between LTM-AWA's iteration and the total wire length for benchmark r3.                                                                                                                 | 73 |

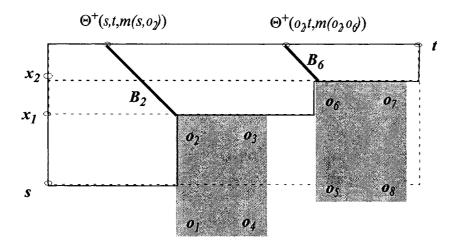

| Figure 5.1  | The Manhattan arc                                                                                                                                                                                    | 80 |

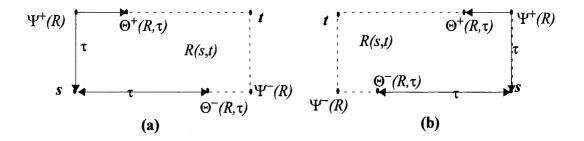

| Figure 5.2  | The notations $\Psi$ and $\Theta$ .                                                                                                                                                                  | 81 |

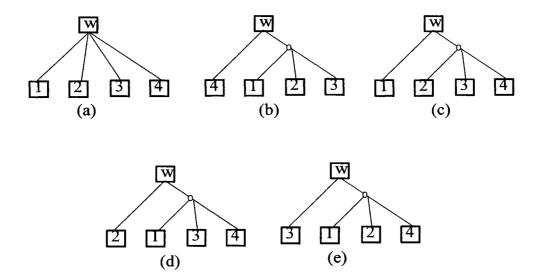

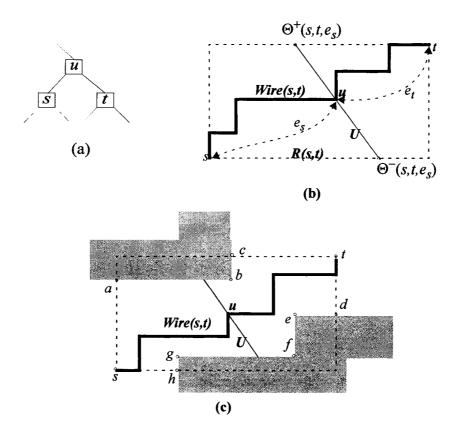

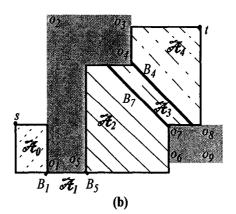

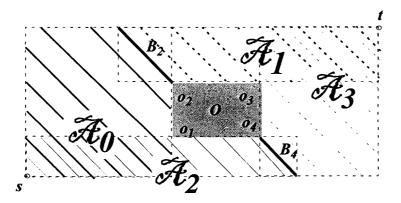

| Figure 5.3  | An example of connecting two nodes (a) the connection topology (b) the routing area of the connection without obstacle constraints (c) the routing area of the connection with obstacle constraints. | 83 |

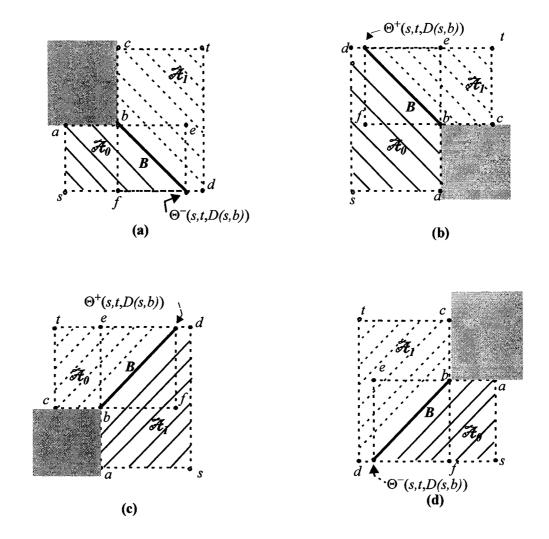

| Figure 5.4  | The sign and slope of the corner $o_1$ (a) $\alpha=-1$ and $\beta=-1$ (b) $\alpha=+1$ and $\beta=-1$ | 85  |

|-------------|------------------------------------------------------------------------------------------------------|-----|

|             | (c) $\alpha=-1$ and $\beta=+1$ (d) $\alpha=+1$ and $\beta=+1$                                        |     |

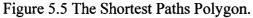

| Figure 5.5  | The Shortest Paths Polygon.                                                                          | 89  |

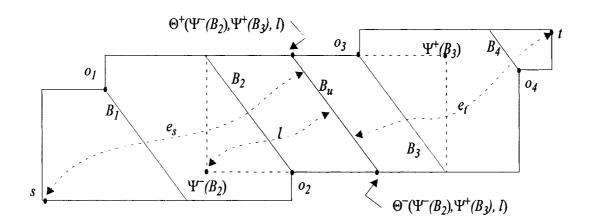

| Figure 5.6  | The graph representation.                                                                            | 91  |

| Figure 5.7  | The extension of the boundary arcs. (b) The visibility graph.                                        | 93  |

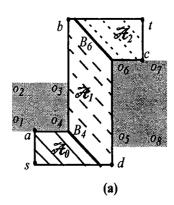

| Figure 5.8  | The overlapping between different parts of a merging segment.                                        | 96  |

| Figure 5.9  | Merging segment determination.                                                                       | 99  |

| Figure 5.10 | The Merging Segment Determination procedure                                                          | 99  |

| Figure 5.11 | (a) The possible arcs of the merging segment have $\pm 1$ slope. (b) The visibility graph            | 102 |

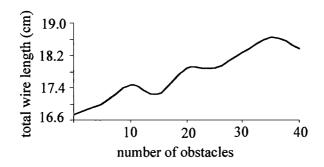

| Figure 5.12 | Skew convergence and total wire length for r1 with 40 obstacles                                      | 107 |

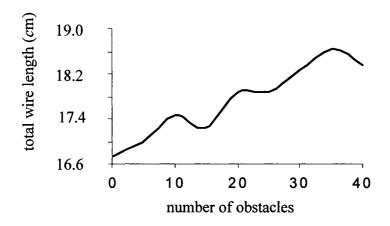

|             | Total wire length vs. number of obstacles for r1                                                     | 107 |

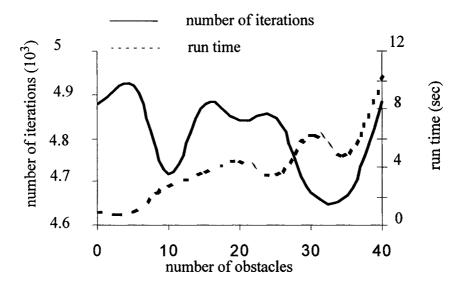

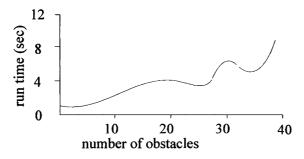

|             | Number of iterations and run time vs. number of obstacles for r1                                     | 108 |

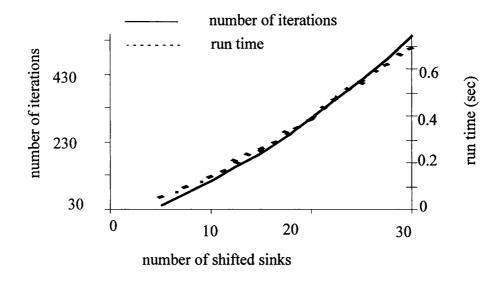

|             | Iterations and run time vs. number of shifted sinks for r5                                           | 108 |

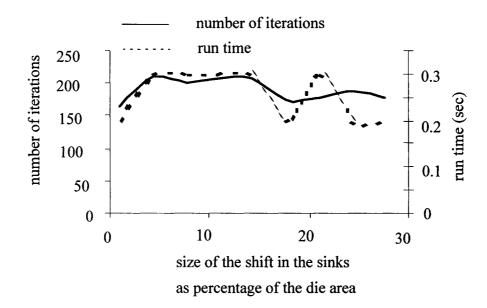

|             | Iterations and run time vs. the size of the shift of five sinks for r5.                              | 109 |

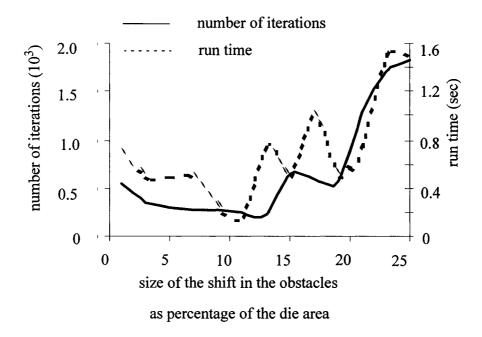

|             | Iterations and run time vs. the size of the shift of three obstacles for r5.                         | 109 |

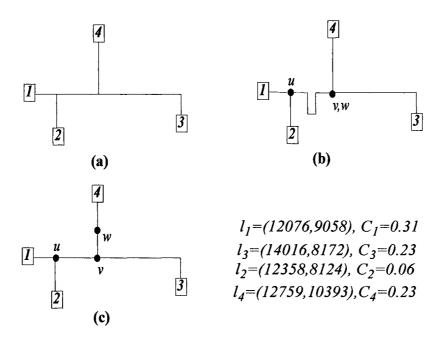

| Figure 6.1  | An example of a CDN tree                                                                             | 111 |

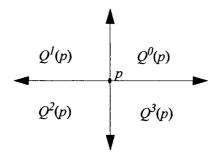

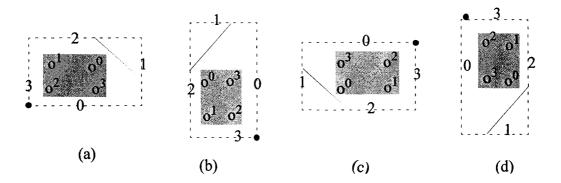

| Figure 6.2  | The four quarters of a point in the Manhattan plane.                                                 | 112 |

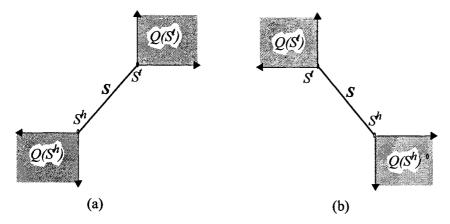

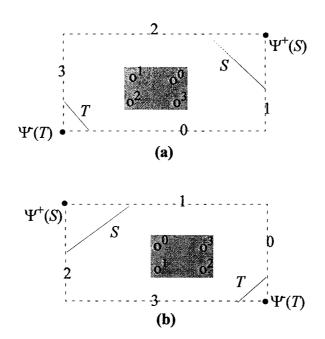

| Figure 6.3  | The quarters of the head and tail of an arc, $S$ (a) $S_{slope} = 1$ (b) $S_{slope} = -1$ .          | 113 |

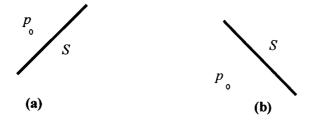

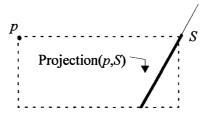

| Figure 6.4  | The relationship between a Manhattan arc and a point (a) $p \uparrow S$ (b) $p \downarrow S$ .       | 113 |

| Figure 6.5  | The projection of a point on an arc.                                                                 | 114 |

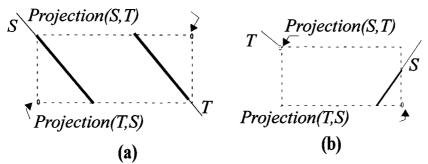

| Figure 6.6  | The projections of two arcs on each other when they are (a) parallel and (b) perpendicular           | 115 |

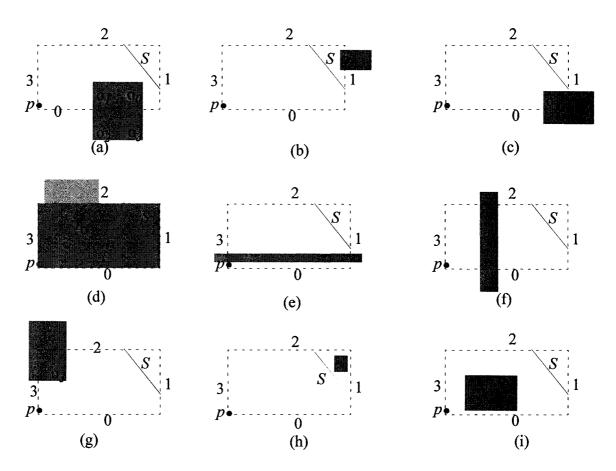

| Figure 6.7  | The impact of an obstacle on connecting an arc $S$ to a point $p$ .                                  | 117 |

| Figure 6.8  | Different possible cases the relationship between an arc and a point.                                | 118 |

| Figure 6.9  | Procedure of Link Determination between an arc and a point                                           | 119 |

| Figure 6.10 | The impact of an obstacle on connecting two arcs.                                                    | 121 |

|             | Procedure of Link Determination between two arcs, Sand T.                                            | 121 |

|             | The Top-Down Procedure of the SPP-DME.                                                               | 124 |

| Figure 6.13 | Modifying the SPP $\overline{S}$ and $\overline{T}$                                                  | 129 |

| Figure 6.14 | Other scenarios of modifying the SPP.                                                                | 130 |

| Figure 6.15 | The procedure of merging segment determination without intersection with other wires.                | 132 |

| Figure 6.16 | The resulting ZSCDN for the benchmark r1 under 20 obstacle constraints.                              | 135 |

| Figure 6.17 | Total wire length vs. number of obstacles for rlusing Planar-DME       | 135 |

|-------------|------------------------------------------------------------------------|-----|

| Figure 6.18 | run time vs. number of obstacles for the benchmark r1 using Planar-DME | 135 |

| Figure 6.19 | The planar ZSCDN for the first 32 clock pins of the benchmark r1.      | 136 |

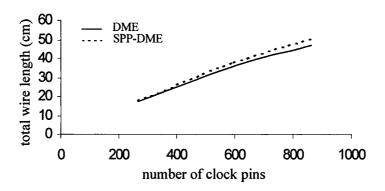

| Figure 6.20 | Total wire length vs. number of clock pins for different benchmark.    | 137 |

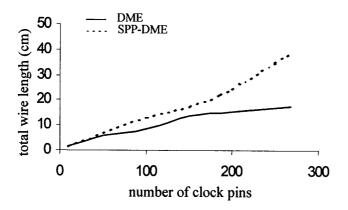

| Figure 6.21 | Total wire length vs. number of clock pins for the benchmark r1.       | 138 |

## LIST OF TABLES

| Table 3.1 | Parameters of the benchmarks that are used in the experiments                                                                                 | 43  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2 | Different metrics of DME, AWA and GDME for different benchmarks. Both DME and AWA are tested with two different initial topology; MMM and GMA | 46  |

| Table 3.3 | Number of iterations required by AWA for different benchmarks                                                                                 | 48  |

| Table 3.4 | Number of clock pins per IP for benchmarks b5k and b10k.                                                                                      | 53  |

| Table 4.1 | Different metrics of LTM-AWA, LTM-DME and LTM-GDM for different benchmarks.                                                                   | 71  |

| Table 4.2 | Number of iterations required by AWA and LTM-AWA for different benchmarks                                                                     | 74  |

| Table 5.1 | Signs of the corners                                                                                                                          | 87  |

| Table 5.2 | Different metrics for different benchmarks using SPP-AWA. Each benchmark is compounded with 40 obstacles                                      | 104 |

| Table 6.1 | The look Up Table for the case $S_{slope}$ =-1 and $S\tilde{A}Q^{0}(p)$                                                                       | 119 |

| Table 6.2 | Different metrics for different benchmarks using obstacle free DME and SPP-DME with 40 obstacles.                                             | 136 |

| Table 6.3 | Different metrics for different benchmarks using DME and Planar-SPP-DME                                                                       | 137 |

#### LIST OF ACRONYMS

**AWA** Adaptive Wire Adjustment BB**Balance Bipartition** Bounded Skew Clock Distribution Net-**BSCDN** work clock distribution network **CDN DME** Differed Merge Embedding **GDME Greedy DME GMA** Geometric Matching Algorithm local topology modification LTM **ITRS** International Technology Roadmap for Semiconductor LTM-AWA Applying LTM approach to AWA algorithm LTM-DME Applying LTM approach to DME algorithm LTM-Applying LTM approach to GDME algo-**GDME** rithm MMM Method of Means and Median **SDPL** standard deviation of the path lengths between the root and the clock pins of a **CDN SPP** shortest paths polygon Applying SPP model to AWA algorithm SPP-AWA Applying SPP model to DME algorithm SPP-DME **ZSCDN** Zero Skew Clock Distribution Network

### LIST OF SYMBOLS

| α      | The first sign of a concave point of a poly-                   |

|--------|----------------------------------------------------------------|

|        | gon                                                            |

| Α      | Manhattan arc set                                              |

| β      | The second sign of a concave point of a polygon                |

| C      | capacitance of a subtree                                       |

| $c_0$  | capacitance per unit length                                    |

| Centre | centre of delay range                                          |

| D()    | Manhattan distance between two arguments                       |

| e      | edge length                                                    |

| 1      | location of a node of a CDN in the Manhattan Plane             |

| L      | Left poiter of a node of a CDN                                 |

| m      | cost of the shortest path                                      |

| Max    | The Maximum a leaf delay range                                 |

| Min    | The Minimum a leaf delay range                                 |

| $r_0$  | resistance per unit length                                     |

| R      | Right poiter of a node of a CDN                                |

| Range  | leaf delay range                                               |

| SPP()  | Shortest Paths Polygo of two arguments                         |

| Θ      | An operation that determines the end points of a Manhattan arc |

| Wire() | The wire that connects two points or two arcs                  |

| Ψ      | An operation that determines the corners of a Rectangle        |

# Chapter 1

# Introduction

# 1.1 System on Chip Design

A System on a Chip (SoC) combines several homogenous or heterogeneous blocks, which vary in complexities and specification, on a single chip in order to carry out numerous integrated operations. The design of a SoC is challenging and can be very complicated compared to the design of Application Specific Integrated Circuits (ASIC) due to the scale of the problem. Accordingly, no single designer will be able to handle this huge design task. To cope with such a challenging task, it is necessary to develop more sophisticated design approaches.

One approach to design the SoC is to have a number of design teams that work concurrently in a common user-friendly design environment. This approach is manifested in the growing trend among designers to import pre-designed macro functions, called Intellectual Property (IP) blocks, from various providers [12]. According to International Technology Roadmap for Semiconductor (ITRS), the complexity and the size of the SoC will continue to drive designers to reuse IPs over the next decade [1]. These third party IP blocks may cover up to 96% of the area of the chip [1]. However, the major challenges posed by the SoC design are system complexity, signal integrity and verification of the implementation. Other two factors influencing the SoC design are the constant

demand for the reduction in the time to market and the power consumption. Therefore, the SoC design imposes new challenges that need to be addressed by the designers and EDA community.

## 1.1.1 Chip Interconnects

One of the major challenges of the SoC design that have surfaced is the role and performance of the interconnects [2-8]. The role of the interconnects is to distribute data, control signals and system clock and its derivatives across the chip. It also feeds power and ground to various circuits of the system. Due to the size and complexity of a SoC, different metal layers are used to lay out the massive interconnects. It is projected that future SoC will use some 14 metal layers by 2011 [1]. Local interconnects normally use lower level metals, while global interconnects use high level layers. The latter include signals between IPs, power busses and clock distribution networks [7]. The process of laying out the interconnect is very complex; and furthermore, the signal propagation through the interconnect is not linear [2].

The reduction in the feature size renders the device delay smaller. However, the delay of the interconnect increases with the reduction in the feature size due to the increase in the resistivity of the interconnect [2-4]. In addition, due to the impact of the parasitic capacitance, the delay increases exponentially with the length of the interconnect. Figure 1.1 shows a comparison between the impact of feature reduction of the interconnect and gate delay [1]. Local interconnects are relatively unaffected by the shrinking in the technology. However, the delay of the signal is primarily influenced by the global interconnects.

nects [1]. In fact, the global interconnect delay will continue to increase with the technology scaling. As a result, one of the most challenging problems of the SoC is to maintain the signal integrity at the targeted performance [2-8].

# 1.1.2 The Design Methodology

The SoC has to be designed according to a methodology that orchestrates the steps of the design process in order to fulfill the system requirements [12, 65]. Thus, the design methodology holds the key answer to the challenges posed by the SoC design. Nowadays, different design tasks communicate with each other at different design steps making the process tedious and complex [48]. Indeed, the designer has to go back and forth between different design steps in order to meet the system requirements.

Figure 1.1 Delay for interconnect versus feature size (courtesy ITRS 2003) [1].

In order to cope with the challenges of the SoC design, different design tasks need to

communicate with each other, operate concurrently and share data memory. Figure 1.2 shows, in general, the projected design methodology for feature size less than 65 nm according to ITRS [1]. In addition, different design steps have to be executed incrementally in the case where minor modification are required. Supporting different design steps with efficient Engineering Change (EC) techniques, and executing these steps in parallel would improve engineering productivity and reduce time to market.

Figure 1.2 Design methodology as projected by ITRS 2003 for technology less than 65 nm [1].

With the dominance of the interconnect role in determining SoC performance, the task of routing becomes more important than the optimization of the devices [2-4]. Thus, there is a definite need for efficient EC techniques that can handle any local modification in the layout of interconnects of the SoC [48]. Kahng et. al. showed that the crucial role of the interconnect promotes a need for interconnect tuning [49]. The rise in SoC complexity and interconnect dominance team up to intensify a specific challenge to the

Clock Distribution Network (CDN)[5-24]. The challenge stems from the CDN's crucial role of integrating different IP cores into a single synchronous SoC.

### 1.2 Clock Distribution Network

High performance systems may contain hundreds of thousands of combinational logic elements and tens of thousands of registers. All registers, memory elements and dynamic circuits in a synchronous digital system are synchronized by a single clock signal or multiple clock signals. The function of the clock signal is to deliver a time reference so that the correct data propagates throughout the system. The clock signal is normally delivered by a network of interconnects commonly known as a Clock Distribution Network (CDN) [5].

The clock signal is a performance bottleneck for any SoC because of its characteristics that distinguish it from other signals in the system. One of the most important characteristics is that the clock signal must feed all registers around the system. Hence, the CDN is largest net occupying a significant portion of the chip area. The increase in the size of the CDN implies an increase in the power consumption of the CDN. This power is almost dynamic power in nature due to the charge and discharge of the massive interconnection capacitance of the CDN. Furthermore, the CDN with its heavy fanout load has to operate at the highest speed among all other signals. Thus, designing the CDN is a critical step in the design process of a SoC. The approach of designing the CDN would affect the arrival time of the clock signal to the corresponding registers; and consequently, would impact the CDN's quality.

The difference between arrival times of the clock signal is referred to as clock skew. The skew effects on the system performance depend on the data propagation paths between the registers. In general, the clock skew can either enhance or degrade the system performance depending on the magnitude and polarity of the skew. The skew can harm the system performance in terms of speed, power and reliability. Worst than that, if the skew is not properly controlled, it might lead to a system failure.

The skew problem can be tackled by devising a CDN so that the skew is zero between all registers. Such a CDN is called Zero Skew Clock Distribution Network (ZSCDN) [39-43]. Other researchers focused on achieving a Bounded Skew CDN (BSCDN) instead of ZSCDN due to the difficulties of achieving ZSCDN [44-47]. The skew impact on system performance [25-28] motivated researches to explore various techniques of clock scheduling with the objective of optimizing clock skew [29-33].

This thesis focuses on the performance of different CDN design approaches in light of the new challenges of the SoC design process. The run time and the complexity of different CDN design approaches become a concern with the increase in the number of sinks to be connected to the CDN. The new challenges that are imposed by the SoC require different design approaches for the CDN. The main shortcoming of previous approaches is that they are not incremental; and hence, the whole solution has to be recalculated whenever a design change is required. The main challenge is to have a CDN design approach that can handle minor modifications in the system. Other shortcoming of previous approaches is that the locations of the Steiner points of a CDN are deter-

mined regardless of the routabilty of the wires. Indeed, most of the CDN approaches solve the skew problem by determining the required wire lengths between different points of the CDN without considering the realization of such wire lengths. Furthermore, most of these approaches resort to wire elongation in order to achieve the skew requirements. However, it is not always possible to route a wire with a specific length due to the difficulties of the routing task. Also, it is often the case that vias are required in order to avoid routing through obstacles and to route the wire in different layers. Thus, it is necessary to consider the routability of each wire of the CDN during the determination of the CDN in order to meet the timing requirements.

### 1.3. Overview of the Dissertation

This work provides one of the first studies of CDN redesign, called CDN tuning, which focuses on incremental synthesis of the CDN in order to meet the timing constraints. A novel algorithm, called Adaptive Wire Adjustment (AWA), is proposed here with a main goal to enable a quick Engineering Change (EC) to the CDN [64]. A secondary goal is to reduce the CDN wire length and number of wire elongations under to help with routing and to minimize power consumption [60-63]. This thesis is organized as follows:

Chapter 2 covers background material related to the work presented in this thesis. The chapter presents an overview of the skew problem; and different approaches that have been used to solve it. The chapter further presents different algorithms that are used to generate the initial topology.

Chapter 3 presents a new incremental algorithm, called Adaptive Wire Adjustment, in order to manage small modifications in the CDN. It also details the proof of convergence of the algorithm. The chapter further presents various figures of merit used to evaluate AWA and other algorithms. The issue of small modifications are addressed by devising different scenarios that are similar to the scenarios of small modifications in a SoC design process.

Chapter 4 presents a method of Local Topology Modification (LTM) in order to enhance the convergence of AWA algorithm. A new method to select the topology using a search tree will be presented. The chapter further introduces figures of merit to demonstrate the advantage of using the LTM method into AWA and other CDN synthesis algorithms.

Chapter 5 studies the shape of the routing area of an interconnect of a CDN under obstacle constraints. An obstacle might be a pre-placed macro cell with blocked region or a previously routed wire. The chapter presents a simple model, called Shortest Paths Polygon (SPP), to describe all shortest paths between two points in the presence of obstacles. The chapter also presents the incorporation of the SPP model into AWA algorithm in order to tune the CDN under obstacle constraints.

Chapter 6 focuses on the obstacles that stand for previously routed wires. A method is presented to determine the SPP of each wire of the CDN such that the wires do not intersect with each other. Specifically, the CDN is routed in one and two layers. The chapter presents a comparison between this method and other methods. It shows the advantage

of using the SPP model in terms of reducing the total wire length. Furthermore, the impact of the planarity on the total wire length will be studied.

Finally, Chapter 7 concludes and summarizes the contributions provided in this work.

The chapter also discusses future research directions in designing CDNs.

# Chapter 2

# Clock Distribution Net-

# work

## 2.1 Introduction

The clock skew problem is a direct result of the feature reduction; and it is the main problem that has to be resolved by any CDN synthesis approach in order to meet the system requirements. This chapter discusses this problem and different approaches that address it. The following sections provide the background and the terminology of the issues involved in this thesis. Throughout this thesis, a simple synchronous system is considered using positive edge triggered flip flops under a single phase clocking scheme.

The Clock Distribution Network (CDN) refers to the circuits and interconnections that are used to deliver the clock signal to all registers and dynamic circuits in a synchronous system.

## 2.2 Clock Skew

A typical scenario for a synchronous system is a data flow between two registers, i and j, as shown in Figure 2.1. Such registers are called sequentially adjacent since there is a

combinational logic (or just an interconnection) that connects the output of i to the input of j. If i and j are properly functioning, then the data latched by i must be captured by j with the next latching clock edge. However, the delay of the interconnection of the CDN results in different arrival times of the clock signal to the registers i and j,  $T_i$  and  $T_j$  respectively. The difference between  $T_i$  and  $T_j$  is called the clock skew between i and j, S(i,j); and it is given as:

$$S(i, j) = T_i - T_j$$

(2.1)

Note that S(i,j) can be positive or negative depending on whether the  $T_j$  lags or leads  $T_i$ .

Figure 2.1 Pair of sequentially adjacent registers

On the other hand, data signal encounters a delay when it propagates from i to j. The data propagation delay between two adjacent registers,  $T_{PD}(i,j)$ , is due to the registers, combinational logic and the interconnection; and it can be determined as follows:

$$T_{PD}(i,j) = T_{O}(i) + T_{C}(i,j) + T_{int}(i,j) + T_{s}(j)$$

(2.2)

Where:

$T_Q(i)$ : the switching delay of register i

$T_C(i,j)$ : the propagation delay of the combinational logic between the registers i and j

$T_{int}(i,j)$ : the propagation delay of the interconnect between i and j

$T_s(j)$ : the required time for data to be stable in order to be latched by j

Note that there are minimum and maximum values for  $T_{PD(min)}(i,j)$ ,  $T_{PD(min)}(i,j)$  and  $T_{PD(max)}(i,j)$  respectively, depending on the minimum and maximum values of different delay components.

In order to latch the correct data by j, the clock skew and the data propagation delay between i and j have to be controlled. In more details, two constraints must be satisfied:

1) the data that propagates from i should not reach j before the arrival of the clock signal at j,  $T_j$ . Otherwise, the data will propagate through i and j in the same clock cycle (double clocking or race condition). Mathematically, the skew should satisfy the following relationship:

$$S(i, j) \ge T_H(j) - T_{PD(min)}(i, j)$$

(2.3)

where  $T_H(j)$  is the hold time of register j.

2) the data should not reach j with a delay greater than the time difference between the next clock edge at j and the current clock edge at i. Otherwise, the data will not be latched by j at the following clock pulse (zero clocking). Mathematically, the skew should satisfy the following relationship:

$$S(i,j) \le T_{clk} - T_{PD(max)}(i,j)$$

(2.4)

where T<sub>clk</sub> is the clock cycle time

The magnitude and polarity of S(i,j) and  $T_{PD}(i,j)$  affect the system performance. For example, the later constraint determines the maximum clock frequency, f, as follows:

$$\frac{1}{f} \ge S(i,j) + T_{PD(max)}(i,j)$$

(2.5)

Based on the above discussion, Equations 2.3 and 2.4 define, respectively, the lower  $(S_{min}(i,j))$  and upper  $(S_{max}(i,j))$  bounds of the permissible range of S(i,j) as shown in Figure 2.2.

Figure 2.2 The permissible clock skew range for two registers.

Two registers may be connected by more than one data path as shown in Figure 2.3, where the system is modeled as a directed graph. Each vertex refers to a register; and each edge refers to a combinational logic path (or just a wire) between two registers. In addition, each edge has two weights that correspond to the maximum and minimum data propagation delay between its two vertices. For example, the registers 1 and 3 shown in Figure 2.3(a and b) are connected by two data paths; and each path has a different permissible skew range. Thus it is important to determine the permissible skew range properly in order to ensure that 3 latches the correct data.

Figure 2.3 Global data path (a) A Parallel data path (b) A feedback data path

# 2.3 Preliminaries of The CDN Synthesis

#### 2.3.1 Graphical Model of the CDN

Consider a set of registers  $R=\{1, 2,.., n\}$  to be connected by a CDN. Each register  $i \in R$ , is associated with a load capacitance,  $C_i$ , and a location in the Manhattan plane  $l_i$ . The set R can be connected by different CDNs depending on the approach used to generate the CDN. The objective of the early CDN design approaches was the minimization of the total wire length. This is due to the fact that the interconnect delay was insignificant compared to the device delay. As such, the CDN design problem is reduced to the problem of connecting a set of registers with minimum wire length, which is known as the Steiner tree problem. Indeed, the CDN would have a tree topology since there is a unique path from the clock source to each register (the topology here refers to the graph that represents the connection between registers and the clock source). Furthermore, the Steiner tree connects the set R through intermediate nodes, called Steiner points, so that the total wire length is minimized.

The connection between the set R and the Steiner points can be depicted by a topology tree T. The leaves of T correspond to the registers and the internal nodes in T correspond

to the Steiner point in the CDN as shown in Figure 2.4. Any node k,  $k \in T$ , is connected to its parent by an edge  $e_k$ . For any two nodes w and k, where w is the ancestor of k, there is a unique path from w to k in T; which is denoted as Path(w,k).

Figure 2.4 The topology tree of a CDN

#### 2.3.2 Delay Model of the CDN

The edge of node k,  $e_k$  in the CDN can be modeled as a  $\pi$ -type circuit with a resistor  $r_k$  and two capacitors  $c_k/2$ , where  $r_k$  and  $c_k$  are the resistance and capacitance of  $e_k$  respectively. Consequently, the CDN can be modeled as an RC tree as shown in Figure 2.5. Under the Elmore delay model, the arrival time of the clock signal to a node, k, is given by [3]:

Delay(w, k) =

$$\sum_{i \in Path(w, k)} r_i \left(\frac{c_i}{2} + C_i\right)$$

(2.6)

where:  $C_i$  is the total capacitance of the sub-tree rooted at node i w is the source of the clock signal.

Figure 2.5 The RC-Tree of the topology tree shown in Figure 2.4

#### 2.3.3 Power Dissipation of the CDN

Each transition of the clock signal changes the state of each node in the CDN. Consequently, the primary component of the power dissipated by the CDN is the dynamic power due to charging and discharging the capacitance load of the CDN. The dynamic power dissipated by CDN depends on the capacitance of the CDN, swing voltage and clock frequency as follows [24-29]:

$$P = C_1 V_{DD}^2 f (2.7)$$

Where:  $C_L$  is the CDN capacitance

V<sub>DD</sub> is clock signal swing

Normally, the CDN consumes around 40% of the system power consumption [24-29]. Minimizing the power of the CDN can be achieved by minimizing the signal swing and/ or CDN capacitance. Minimizing the CDN capacitance requires the reduction of the

total wire length of the CDN. Thus, it is important to design the CDN with minimum wire length in order to reduce the power dissipation.

#### 2.3.4 Problem Definition

For a given set of registers R, where each register is associated with a location and a load capacitance, let the skew constraint between every pair of registers be given by the set  $S=\{S(i,j)=(S_{\min}(i,j),S_{\max}(i,j))\}$ . The CDN design problem can be formulated as follows: Find the CDN that satisfies the skew constraints S with minimum wire length.

The CDN synthesis requires the determination of the location and the edge length of each node in the CDN. If there is no skew constraints, then the problem becomes a Rectilinear Steiner Tree problem. This problem is NP-hard, and much work has been devoted to designing good heuristics and approximation algorithms [3, 71, 73, 77]. Nevertheless, such an assumption is not true, and the skew constraints must be carefully determined and satisfied.

A close look into the relation 2.3, which determines  $S_{min}(ij)$ , reveals that it is usually  $S_{min}(i,j)<0$  since  $T_H< T_{PD}$ . On the other hand, according to the relation 2.4, it is usually true that  $S_{max}(i,j)>0$  since  $T_{PD}< T_{clk}$ . Thus, one may deduce that a zero skew CDN (ZSCDN), or a bounded skew CDN (BSCDN), would satisfy the skew requirements.

# 2.4 CDN Synthesis Using Geometric Approaches

Early approaches of designing a ZSCDN are based on linear delay model. According to

this delay model, the clock signal down a path in the CDN is assumed to increase linearly with the length of the path. In general, there are three geometric approaches considered in this thesis: H-tree, method of means and median and geometric matching algorithm.

#### 2.4.1 H-Tree

Let the set of registers, R, to have a symmetric distribution such that the set R can be divided into two symmetric sets recursively and alternatively by vertical and horizontal lines until each set has one register only. Then, it is possible to connect the set R using recursive H-shapes; and the resulting CDN is called H-tree as shown in Figure 2.6. The clock source is connected to the center of the first H structure; and the four corners of each H-structure provide inputs to the next level of the H tree, and so on. The final destination points of the H-tree are used to drive the local registers.

Figure 2.6 The H-tree

The H-tree increases the path lengths from the center of the first H to all registers so that all paths become equal. That is, the H-tree method trades of the total wire length for zero skew. In addition, the H-tree requires that the registers to have a symmetric distribution.

Also, all registers must have equal capacitance load in order to achieve a zero skew between all registers.

#### 2.4.2 Method of Means and Medians (MMM)

At each iteration, The method sorts a set of registers R according to their x-coordinates (or y-coordinates). Then the method finds the median of the x-coordinate (or y-coordinate) of all elements of R; and groups the elements into two sub-sets based on whether each element is located to the left or right of the median. This process continues recursively for each sub-set from a previous iteration with alternation between the x and y coordinates until each sub-set has two registers at most as shown in Figure 2.7.

Figure 2.7 The MMM algorithm

#### 2.4.3 Geometric Matching Algorithm (GMA)

This algorithm constructs the CDN by matching the closest nodes iteratively in a bottom up manner. In the first iteration, the algorithm finds the pair of registers that are closest to each other in a given set of registers R. The pair of registers are replaced by a node in R; where this node becomes the parent of the pair of registers. At each iteration, the algorithm reduces the number of nodes in R by one as shown in figure 2.8. The algorithm stops when R is reduced to one node that stands for the root of the CDN. Due to the process of selecting the two nodes that are closest to each other, the GMA algorithm takes longer time to reach its solution as compared to the MMM. However, the GMA produces a better CDN in terms of total wire length.

Figure 2.8 The GMA algorithm

#### 2.5 CDN Synthesis Using Elmore Delay Model

Various CDN synthesis algorithms were developed based on Elmore delay model to generate relatively accurate solutions [3]. Some of these approaches require an initial connection topology of the CDN. Such a topology can be generated using the MMM or GMA approaches; and it is traditionally a tree since there is a single path from the root to each leaf.

#### 2.5.1 Tsay's Method

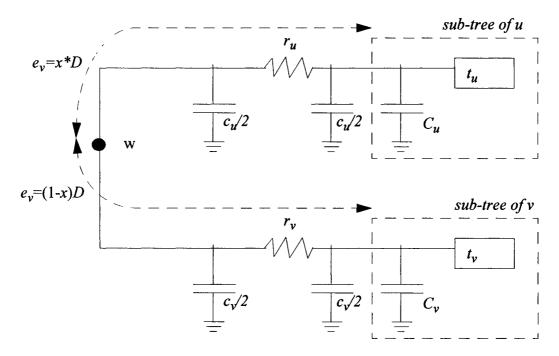

Tsay proposed a method that produces a ZSCDN based on Elmore delay model [39]. It requires the topology tree of the CDN to be defined initially. Then, the method determines the edge lengths of the tree such that the clock signal arrives to all leaves, registers, at the same time. Specifically, the Steiner points of the tree are selected iteratively in a bottom-up manner; and the two child edge lengths of the selected Steiner node are determined. Assume that during the progression, Steiner point w is reached, where u and v are the children of w as shown in Figure 2.9. This implies that the method has determined the edges of the sub-tree rooted at u (and v) such that the clock delays from u (and v) to all its leaves are equal. Let  $t_u$  and  $t_v$  be the clock delays from u and v to their leaves respectively. In order to achieve a zero skew between all the leaves that are connected to w, the edge lengths of u and v,  $e_u$  and  $e_v$  respectively, have to satisfy the following equation:

$$e_u r_0 \left(\frac{e_u c_0}{2} + C_u\right) + t_u = e_v r_0 \left(\frac{e_v c_0}{2} + C_v\right) + t_v$$

(2.8)

where  $r_0$  and  $c_0$  are the resistance and capacitance per unit length of wire respectively

Let the rectilinear distance between u and v be D. Also, let x be a factor,  $0 \le x \le 1$ , that denotes the partitioning of D between  $e_u$  and  $e_v$  such that:

$$e_{y} = xD$$

$e_{y} = (1-x)D$  (2.9)

Then, Equation 2.8 can be written as follows:

$$xDr_0(\frac{xDc_0}{2} + C_u) + t_u = (1 - x)Dr_0(\frac{(1 - x)Dc_0}{2} + C_v) + t_v$$

(2.10)

Solving Equation 2.10 for x yields:

$$x = \frac{(t_v - t_u) + r_0 D(\frac{Dc_0}{2} + C_v)}{r_0 D(c_0 D + C_u + C_v)}$$

(2.11)

If the resulting x is  $0 \le x \le 1$ , then it is possible to balance the two subtrees by a wire of length D; and  $e_u$  and  $e_v$  are determined according to Equation 2.9. However, if  $x \le 0$  (or  $x \ge 1$ ) then a wire of length D cannot balance the skew between the two subtrees. The case  $x \le 0$  implies that  $t_u >> t_v$ ; and hence, the node w must coincide on node u. That is  $e_u = 0$ ; and  $e_v$  can be calculated from Equation 2.8 as follows:

$$e_{v} = \frac{\sqrt{(r_{0}C_{v})^{2} + 2r_{0}c_{0}(t_{u} - t_{v}) - r_{0}C_{v}}}{r_{0}c_{0}}$$

(2.12)

Similar equation can be derived for the case  $x \ge 1$ . The cases  $x \le 0$  and  $x \ge 1$  imply that  $e_v > D$  and  $e_u > D$  respectively. Consequently, there would be a wire elongation as shown in Figure 2.10. Such a wire elongation results in an increase in the chip area and power consumption; and in addition, it is cumbersome for the CDN routing.

Figure 2.9 The determination of the edge lengths using Tsay approach

Figure 2.10 The wire elongation

#### 2.5.2 Differed Merge Embedding (DME) Algorithm

The Tsay method determines the edge lengths of the tree such that the skew become zero

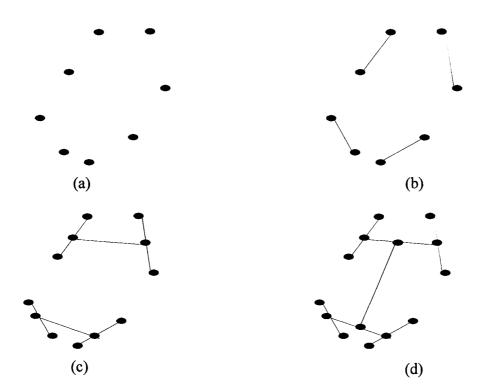

between all registers. However, this method does not consider all locations of the Steiner points in the routing plane. For example, node w shown in Figure 2.9 can be located in different locations for a given  $e_u$  and  $e_v$ . Considering all possible locations of each Steiner node would help to minimize the total wire length of the CDN. This shortcoming was addressed by the Differed Merge Embedding (DME) algorithm [40-42]. The DME algorithm uses the Tsay method, which is based on Elmore delay model, in order to determine the edge lengths. In addition, it determines all possible locations of each Steiner point in the Manhattan plane, which will be called the merging segment. The merging segment of a node is a Manhattan arc whose slope is  $\pm 1$  as shown in Figure 2.11. The DME reaches its solution in two phases: a bottom-up phase and top-down phase as will be described next.

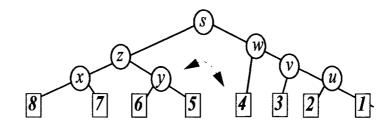

The first phase determines the merging segment of each Steiner node in bottom-up mannar. Assume that the algorithm has reached the Steiner node w whose child nodes are u and v as shown in Figure 2.9. The edge lengths  $e_u$  and  $e_v$  are determined using Tsay method. Then the merging segment of w, ms(w), is determined such that ms(u) and ms(v) can be connected with the edge lengths  $e_u$  and  $e_v$ . Note that the points that have equal distances form a Manhattan arc constitute a *Tilted Rectangle*, TR, as shown in Figure 2.11. The Manhattan arc of a TR is called the core of the TR; and the distance between the core and the border of the TR is called the radius of the TR.

Let  $TR_u$  be the TR of node u such that the core is ms(u) and the radius is  $e_u$  as shown in

figure 2.11. Similarly, let  $TR_v$  be the TR of node v. Then, ms(w) would be the intersection of  $TR_u$  and  $TR_v$ :

$$ms(w) = TRR_{u} \cap TRR_{v}$$

2.13

Figure 2.11 Calculating the merging segment of w during the first phase when 0 < x < 1

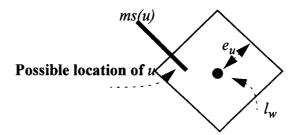

The output of the first phase of the DME is a tree of merging segments that will be used as input for the second phase. The second phase selects the exact location of each internal node from its merging segment in a top-down manner. Assume that the procedure has reached node u, where the location of its parent w,  $l_w$  has already been decided. Then,  $l_u$  is determined by constructing a  $TR_w$  whose core is  $l_w$  and radius is  $e_u$  as shown in Figure 2.12. Since the ms(w) is constructed from the intersection of tilted regions of

its children, a portion of ms(u) will lay in  $TR_w$ , which can be denoted as  $ms(u) \cap TR_w$ . The final location of u is a point that belongs to  $ms(u) \cap TR_w$  [41].

Figure 2.12 Selecting the exact location of a node from its merging segment

The DME algorithm also requires an initial topology. The type of the initial topology has a significant impact on the total wire length of the resulting ZSCDN. In general, using a topology obtained by GMA would yield less total wire length. Since, the initial topology is generated without considering the capacitance load of the CDN, the total wire length of the synthesized tree can be minimized further by generating the topology and the ZSCDN simultaneously as will be described next.

#### 2.5.3 Greedy Differed Merge Embedding (GDME) Algorithm

The Greedy DME is the best known ZSCDN design approach in terms of total wire length [42]. This algorithm generates a ZSCDN in two phases. The first phase determines, in a greedy bottom-up manner, the edge lengths, the merging segments and the topology. The edge lengths are determined using Tsay method; and the merging segments are determined using the DME algorithm. The edge length and the merging segments are determined using the DME algorithm.

ment of a Steiner node are determined by defining the child nodes of the Steiner node as will be described next.

Consider a set of registers, R. Each register stands for a node in the CDN, where each node is associated with a merging segment of zero length. Let the set of nodes be Q, where Q=R at the beginning of the algorithm. At each iteration, the GDME algorithm finds the pair of nearest neighbors in Q. Let these two nodes be u and v. That is, the distance between ms(u) and ms(v) is the minimum. The two selected nodes, u and v, will be replaced by a new node, w, in Q. In the final solution, the node w becomes the parent of u and v. The merging segment of w, ms(w), is determined from ms(u) and ms(v) as described in Section 2.5.2.

The bottleneck of GDME is the selection of the pair of nodes at each iteration. The complexity of GDME is  $O(n^2)$  [42]. The computation time of GDME can be reduced by finding several nearest neighbor pairs simultaneously; and the complexity is enhanced to  $O(n \log n)$ . This can be achieved using an efficient implementation of the nearest neighbor computation based on the Delauny triangulation[43].

#### 2.6 Shortcomings of Previous Approaches

The main shortcoming of the previous CDN synthesis approaches is that they are not incremental. As a result, the solution has to be re-calculated whenever a modification is required. Such a modification is expected often in the course of designing a SoC. Also,

to improve system performance, some level of tuning the synthesized CDN is required.

Therefore, the need for incremental algorithms to tune the network or to implement

Engineering Changes (ECs) in CDN is critical in the SoC design cycle.

In addition, previous approaches satisfy the time requirements by determining the location of each Steiner node of the CDN in the Manhattan plane. However, these approaches cannot guarantee the routablity of the wires that connect the registers through the Steiner nodes to the source of the clock tree. In fact, routing the DME or GDME solutions result in many intersections between the wires. The intersections might be resolved by using vias or lengthening the wires, but the solution would not necessarily meet the time budget. This problem becomes advent due to the increase in the difficulties of the routing problem in complex systems. Thus, it is important to produce a solution that solves both the timing and routing problems.

In this thesis, an incremental synthesis for small design modifications will be presented first. Then, the issue of routability of the CDN in the presence of obstacles will be discussed later.

### Chapter 3

# Tuning the Clock Distribution Network

#### 3.1 Introduction

Designing a Bounded Skew CDN (BSCDN) in a SoC has become increasingly challenging, as the clock network consumes an increasing portion of all resources in terms of wiring area, power and design time. Furthermore, it is sometimes required to insert or remove IPs or to perform localized modifications without affecting the performance of the CDN. Hence, there is a need for implementing the EC by tuning the BSCDN instead of redesigning it.

The approaches that are presented in Chapter 2 produce Zero Skew CDN (ZSCDN) based on Elmore delay model. These approaches control the skew by using Tsay's approach, which may resort to wire elongation [40-47]. Such a wire elongation compounds the complexity and increases the power consumption of the CDN. Furthermore, a change in the locations or the load capacitance of clock pins would require a recalculation of the whole CDN solution as in Deferred Merging Embedded (DME) algorithm

[40-42]. This will be an extremely computation intensive process for a complex system. In fact, it is often that IPs are inserted or removed, which changes the CDN's topology and the loading and placement of the clock pins [48]. Such changes may affect the entire CDN and may require a redesign of the clock network. However, in complex system, it is only practical to implement these minor modifications through an incremental algorithm to tune the CDN. This specific process has received little attention in the literature. Elboim et. al. [54] have reported that the repetitive redesign of the CDN can be eliminated by inserting programmable delay circuits in the CDN in order to tune the clock delay. Indeed, these delay circuits enable a quick integration of the IPs into SoC by avoiding the redesign of the CDN itself. However, the same goal can be achieved by enabling a quick redesign of the CDN and thus avoiding the penalty of introducing extra circuitry, which may result in an increased area and power dissipation. This work provides one of the first studies of redesigning CDN, called CDN tuning, using the physical information of the CDN so that it better meets the timing constraints. A novel algorithm, called Adaptive Wire Adjustment (AWA), is proposed with a main goal to enable a quick EC to the CDN [55, 64]. A secondary goal is to reduce the CDN wire length and number of wire elongation to help with routing and to minimize power consumption.

## 3.2 Clock Distribution Network Tuning by Adaptive Wire Adjustment

The Adaptive Wire Adjustment (AWA) algorithm [55] takes a CDN as an input in the form of a linked tree data structure and checks for the maximum skew in the tree then minimizes it by adjusting the wires of the tree. Whenever a skew exists between two

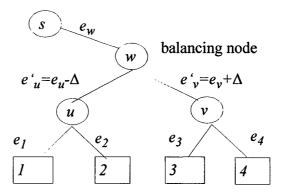

leaves, the paths to these two leaves must be adjusted so that the skew becomes smaller. To adjust these two paths, the algorithm finds the node that can be shifted, by adjusting its child edges, so that the skew is minimized. Such a node, called the **Balancing Node**, **BN**, is the first ancestor of the same two leaves. For example, consider the CDN shown in Figure 3.1. In order to minimize the skew between leaves I and I, their BN, I, I, is shifted by adjusting its child edges I and I suffers higher delay than leaf I, then I w must be shifted by I towards node I and away from node I. Thus, the edge I decreases and edge I increases in the following manner:

$$e'_{u} = e_{u} - \Delta$$

,  $e'_{v} = e_{v} + \Delta$  (3.1)

where,  $e'_u$  and  $e'_v$  are the new values of  $e_u$  and  $e_v$

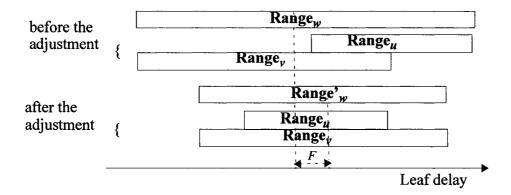

In order to determine the edge adjustment,  $\Delta$ , the delay from node w to its leaves have to be considered. In fact, the leaf delays of the subtrees rooted at u and v span ranges in the time domain as shown in Figure 3.2. Note that the leaf delays of a sub-tree are calculated from the root of the sub-tree. Consequently, in order to minimize the skew between the two sub-trees, the ranges of u and v must be shifted in opposite directions. Let us define the leaf delay range of a sub-tree rooted at node  $\alpha$ ,  $Range_{\alpha}$  be the maximum and the minimum delays in that range calculated from the node  $\alpha$  as follows:

$$Range_{\alpha} = Max_{\alpha} - Min_{\alpha} \tag{3.2}$$

where  $Max_{\alpha}$ =Maximum{Delay( $\alpha,\beta$ )}

$Min_{\alpha}$  =Minimum{Delay( $\alpha,\beta$ )}

for every leaf  $\beta \in$  subtree rooted at  $\alpha$

In general, the balancing node can be defined as the node that has the maximum range and belongs to the lowest level in the tree. Let the center of the range of a node  $\alpha$ , **Center** be the average of maximum and minimum delays of that range as follows:

$$Centre_{\alpha} = \frac{Max_{\alpha} + Min_{\alpha}}{2}$$

(3.3)

Figure 3.1 Selecting the balancing node in a tree

Figure 3.2 The leaf delay ranges of the sub-trees rooted at nodes u, v and w of Figure 3.1

Using the range centre as a time reference, the skew between a pair of internal nodes, u and v, is defined as:

$$S(u, v) = \left[ e_u r_0 \left( \frac{e_u c_0}{2} + C_u \right) + Centre_u \right] - \left[ e_v r_0 \left( \frac{e_v c_0}{2} + C_v \right) + Centre_v \right]$$

(3.4)

Equation 3.4 can be used to determine a BN's edge adjustment,  $\Delta$ , so that the skew between the BN's children, u and v, becomes zero by substituting  $e_u$  and  $e_v$  by  $e'_u$  and  $e'_v$  respectively in Equation-6 and equating it to zero as follows:

$$\left[ \left( \mathbf{e}_{\mathbf{u}} - \Delta \right) \mathbf{r}_{0} \left( \frac{\left( \mathbf{e}_{\mathbf{u}} - \Delta \right) \mathbf{c}_{0}}{2} + \mathbf{C}_{\mathbf{u}} \right) + \mathbf{Centre}_{\mathbf{u}} \right] - \left[ \left( \mathbf{e}_{\mathbf{v}} + \Delta \right) \mathbf{r}_{0} \left( \frac{\left( \mathbf{e}_{\mathbf{v}} + \Delta \right) \mathbf{c}_{0}}{2} + \mathbf{C}_{\mathbf{v}} \right) + \mathbf{Centre}_{\mathbf{v}} \right] = 0$$

(3.5)

$$\Delta = \frac{\frac{r_0^c_0}{2} \left(e_u^2 - e_v^2\right) + \left(\text{Centre}_u - \text{Centre}_v\right) + r_0 \left(e_u^c_u - e_v^c_v\right)}{r_0 \left(e_0^c_u + e_v\right) + c_u^c + c_v^c\right)}$$

(3.6)

The value of  $\Delta$  refers to the required adjustments for the child edges of the BN,  $e_u$  and  $e_v$ , in order to minimize the skew.

Adjusting  $e_u$  and  $e_v$  by  $\Delta$  would shift the BN along a **Balancing Segment**, **BS**, which represents all possible locations of the BN. The BS of u and v, BS $_{uv}$  can be determined from the intersection of two tilted rectangles,  $TR_u$  and  $TR_v$ , whose centers are nodes u and v and whose radii are  $e'_u$  and  $e'_v$  respectively as shown in Figure 3.3(a). Note that this is true only when

$$e'_{u} + e'_{v} = d(u, v)$$

(3.7)

where d(u, v) is the distance between the locations of u and v.

If  $e'_u + e'_v > d(u,v)$ , then the intersection of  $TR_u$  and  $TR_v$  is a TR as shown in Figure 3.3(b). For such a case, it might be possible to shorten both  $e'_u$  and  $e'_v$  while minimizing the skew between u and v. But, this is not always the case. Specifically, if there is a need for wire elongation, then  $e'_u + e'_v > d(u,v)$ . For such cases, one of the edges,  $e'_u$  or  $e'_v$  would be zero; and the BN coincides on the nodes whose edge is zero.

For the general case, the final location of the BN, w, is determined by the intersection of  $BS_{uv}$  and  $TR_s$  whose centre is s and its radius is the BN edge  $e_w$  as shown in Figure 3.3(a). The BN's edge,  $e_w$ , has not been considered yet, and its length would affect the total wire length. In fact, the total wire length can be minimized by determining the BN's edge as the minimum length between the BS and the BN's parent.

Figure 3.3 (a) Determination of  $BS_{uv}$  and the new location of the balancing node, w'. (b) The intersection of  $TR_u$  and  $TR_v$  is a tilted rectangle when  $e_u + e_v > Rect_{uv}$

Adjusting the BN's child edges, as described before, would minimize the maximum

skew between the leaves of the BN. As such, the BN's range gets smaller as the child ranges are shifted in opposite directions so that their centres coincide on each other as shown in Figure 3.2. However, if the centres of the child ranges have already coincided, then it is impossible to shorten the BN's range by adjusting its child edges. Also, if the BN's range is equal to one of its child ranges, then shifting the child ranges would not help to minimize the BN's range. In such a case, the BN's child that has the greater range have to be selected as the balancing node. From the previous discussion, we can draw the AWA algorithm to achieve a bounded skew for a given tree by minimizing the maximum skew in the tree iteratively. At each iteration, a BN is selected and its child edges are adjusted according to Equations 4-8. The description of AWA algorithm is shown in Figure 3.4.

Input: Initial CDN, as a linked tree T, for a set of clock pins R

Output: Bounded Skew CDN by B

while maximum skew >B:

**Find** the BN that has the maximum skew in T, and it belongs to the lowest level in T Calculate the required adjustment,  $\Delta$ , to balance the child nodes of the BN, u and v. Construct  $TR_u$  and  $TR_v$  as following:

$core(TR_u) = location of u, radius(TR) = e'_u$  $core(TR_v) = location of v, radius(TR_v) = e'_v$

Calculate the  $BS_{uv}$  as  $TR_u \cap TR_v$

Locate BN at the closest point of  $BS_{uv}$  to the parent of BN, s.