# Simulation of Controller Configurations for Static Synchronous Series Compensators & Interline Power Flow Controllers with EMTP-RV

#### Sasan Salem

A Thesis

in

The Department

Of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

February 2006

© Sasan Salem, 2006

Library and Archives Canada

nives Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 0-494-14280-4 Our file Notre référence ISBN: 0-494-14280-4

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **Abstract**

# Simulation of Controller Configurations for Static Synchronous Series Compensator and Interline Power Flow Controller with EMTP-RV

#### Sasan Salem

This thesis deals with Flexible AC Transmission Systems (FACTS) based on Voltage Source Converters (VSC). In particular, the emphasis is on series-connected VSC into transmission lines, known as Static Synchronous Series Compensator (SSSC) and Interline Power Flow Controller (IPFC). These are modern series compensators with fast response and high performance.

The SSSC and IPFC applications are simulated with the help of EMTP-RV software, where detailed models of the power system and controllers are implemented and the dynamic performances are considered.

The proposed VSC is based on a 3-level Neutral-Point-Clamped (NPC) VSC employing PWM techniques to generate firing pulses for the VSC switches. The VSC main circuit configuration, function and operating principles are first described.

The proposed VSC is used as the major building block of the SSSC. The detailed model of SSSC (with two different control strategies) is then presented. The controllers are designed to regulate the transmission line impedance by injecting a set of 3-phase voltages with controllable magnitude and phase angle. The stability of the proposed SSSC under various system conditions is investigated and the two different control strategies are compared.

Finally, two SSSCs with a common DC-link are used to configure an IPFC. The proposed IPFC is applied to two parallel transmission lines to regulate their impedances. The validity of the proposed control techniques under various system conditions is also investigated.

#### Acknowledgement

I express my sincere gratitude to Dr. V.K. Sood for his continuous assistance, and sharing of his knowledge and experience during the research and implementation of the thesis.

I also wish to acknowledge the invaluable advices of Dr. K. Khorasani.

I would like to extend my thanks and appreciation to the rest of the faculty members of the Department of Electrical and Computer Engineering at the Concordia University. Also, I would like to give special thanks to my friends and colleagues Farbod Jahanbakhsh, Yansong Leng, Yongan Deng, Nikunj Shah, Jian Qi, Abu Sayeed Bapary, Nasima Monsur, and Muhammed Abu Zahid for their cooperation, discussion, and advices on the project.

Finally, I would like to express my deep appreciation to my parents, Mehri and Hossein, as well as my brother and sister, Kamran and Saghar, for their moral support. Also, special thanks to my lovely girlfriend Afsaneh Mokhtari for her love and support throughout my study.

## **Table of Contents**

| List of Fi | gures                                                     | X   |

|------------|-----------------------------------------------------------|-----|

| List of Ta | ables                                                     | xv  |

| List of A  | cronyms                                                   | xvi |

|            |                                                           |     |

| Chapter    | 1: Introduction                                           | 1   |

| 1.1        | General                                                   | 1   |

| 1.2        | Flexible AC Transmission System (FACTS)                   | 2   |

| 1.3        | Power transmission system constraints                     | 4   |

| 1.4        | Basic principle of active and reactive power flow control | 5   |

| 1.5        | Compensation in AC transmission lines                     | 8   |

| 1.5.1.     | Shunt compensation                                        | 9   |

| 1.5.1      | Series compensation                                       | 12  |

| 1.6        | Literature review                                         | 16  |

| 1.7        | Problem definition                                        | 17  |

| 1.8        | Thesis contributions                                      | 17  |

| 1.9        | Thesis outline                                            | 18  |

| 1.10       | Summary                                                   | 18  |

| Chapter    | 2: Voltage Source Converter (VSC) and FACTS topologies    | 19  |

| 2.1        | Introduction                                              | 19  |

| 2.2        | High power switch-mode converters                         | 19  |

| 2.3        | Power switches                                            | 20  |

| 2.4     | Modeling of a 3-phase VSC                                      | 21 |

|---------|----------------------------------------------------------------|----|

| 2.5     | 3-level Neutral Point Clamped (NPC) VSC                        | 24 |

| 2.5.1   | Sinusoidal Pulse Width Modulation (SPWM) technique             | 26 |

| 2.5.2   | Operating principle of a 3-level NPC VSC                       | 28 |

| 2.6     | Snubber circuit                                                | 29 |

| 2.7     | Passive component design                                       | 31 |

| 2.7.1   | DC-link capacitor                                              | 31 |

| 2.7.2   | AC side filer design                                           | 33 |

| 2.8     | Reference Wave Generator                                       | 37 |

| 2.9     | VSC topologies                                                 | 40 |

| 2.9.1   | STATCOM                                                        | 40 |

| 2.9.2   | SSSC                                                           | 41 |

| 2.9.3   | UPFC                                                           | 42 |

| 2.9.4   | IPFC                                                           | 43 |

| 2.9.5   | GUPFC                                                          | 45 |

| 2.10    | Summary                                                        | 46 |

| Chapter | 3: Modeling and Controller Design of Static Synchronous Series |    |

|         | Compensator (SSSC)                                             | 47 |

| 3.1     | Introduction                                                   | 47 |

| 3.2     | Power circuit of the SSSC                                      | 47 |

| 3.3     | Operating principle of the SSSC                                | 49 |

| 3.4     | SSSC control strategies                                        | 50 |

| 3 / 1   | DC link Releasing Controller                                   | 52 |

| 3.4.2     | Indirect controller                      | 53  |

|-----------|------------------------------------------|-----|

| 3.4.3     | Direct controller                        | 58  |

| 3.5       | Simulation results                       | 61  |

| 3.5.1     | Power system                             | 61  |

| 3.5.2     | Indirect controller                      | 63  |

| 3.5.3     | Direct controller                        | 73  |

| 3.6       | Discussion                               | 80  |

| 3.7       | Summary                                  | 81  |

|           |                                          |     |

| Chapter   | 4: Interline Power Flow Cotroller (IPFC) | 82  |

| 4.1       | Introduction                             | 82  |

| 4.2       | Basic principle of IPFC operation        | 83  |

| 4.2.1     | Active power exchange of IPFC            | 84  |

| 4.2.2     | Power flow at the receiving-end          | 85  |

| 4.3       | IPFC constraints                         | 85  |

| 4.3.1     | Operating limits                         | 85  |

| 4.3.2     | The active power in DC-link              | 86  |

| 4.4       | IPFC controller strategy                 | 86  |

| 4.5       | Simulation results                       | 91  |

| 4.5.1     | IPFC controller                          | 92  |

| 4.6       | Discussion                               | 100 |

| 4.7       | Summary                                  | 100 |

| Ch and an | 5. Complysion                            | 101 |

| References  | 104 |

|-------------|-----|

| Appendix A  | 108 |

| Appendix B  | 111 |

| Appendix C. | 113 |

# **List of Figures**

| Figure 1-1:  | Power transmission line model 5                                  |

|--------------|------------------------------------------------------------------|

| Figure 1-2:  | Voltage phasor diagram of the transmission line                  |

| Figure 1-3:  | Power angle curve                                                |

| Figure 1-4:  | Power transmission line model with shunt compensation9           |

| Figure 1-5:  | Active power versus transmission line angle                      |

| Figure 1-6:  | Static var compensator (a) TCR, TSC, and FC (b) TCR, and FC 11   |

| Figure 1-7:  | Schematic of STATCOM                                             |

| Figure 1-8:  | (a) Model of a power system with series compensation (b) Phasor  |

|              | diagram                                                          |

| Figure 1-9:  | Schematic of TCSC                                                |

| Figure 1-10: | (a) Model of a power system with a synchronous voltage source in |

|              | series (b) Phasor diagram                                        |

| Figure 1-11: | Transmitted power versus angle with various degrees of           |

|              | compensation                                                     |

| Figure 1-12: | Transmitted power versus angle in SSSC                           |

| Figure 2-1:  | Diagram of a 3-phase VSC                                         |

| Figure 2-2   | (a) AC side equivalent of VSC (b) DC side equivalent of VSC 22   |

| Figure 2-3:  | Schematic of a 3-level Neutral Point Clamped VSC                 |

| Figure 2-4:  | Modulation wave of 2-level PWM                                   |

| Figure 2-5:  | Modulation wave and switching signals of a 3-level PWM           |

| Figure 2-6:  | One pole of 3-level NPC VSC                                      |

| Figure 2-7:  | Output waveform of 3-level NPC VSC                                    |

|--------------|-----------------------------------------------------------------------|

| Figure 2-8:  | Model of the switch with snubber circuits                             |

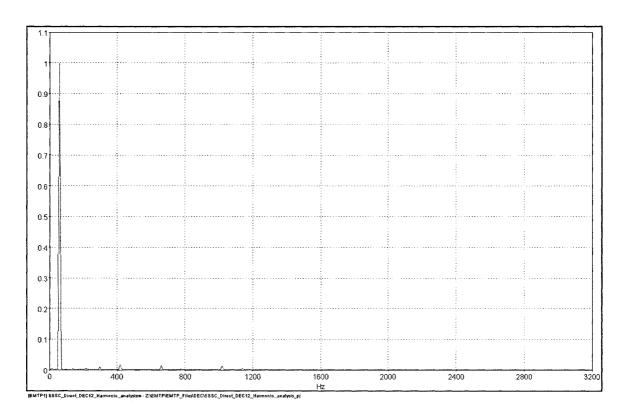

| Figure 2-9:  | Harmonic spectrum of 3-level NPC VSC                                  |

| Figure 2-10: | Harmonic spectrum of 3-level NPC VSC output voltage after             |

|              | filtering                                                             |

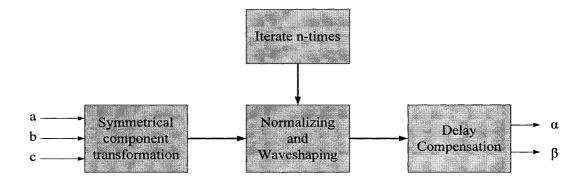

| Figure 2-11: | Block diagram of Reference Wave Generator (RWG) [36]38                |

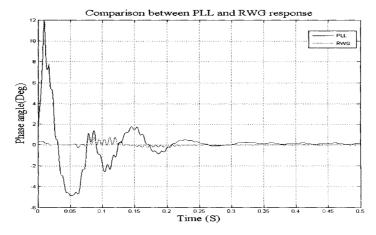

| Figure 2-12: | Comparison of a conventional PLL and RWG39                            |

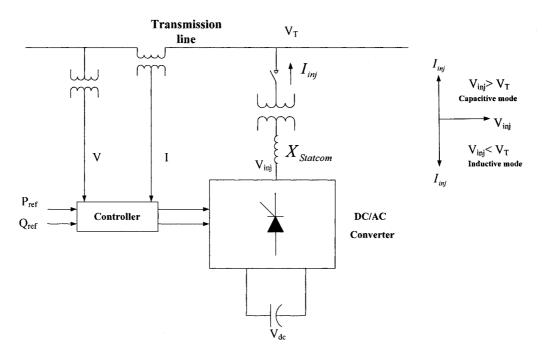

| Figure 2-13: | Diagram of STATCOM                                                    |

| Figure 2-14: | Diagram of SSSC                                                       |

| Figure 2-15: | Schematic of UPFC                                                     |

| Figure 2-16: | Schematic of IPFC                                                     |

| Figure 2-17: | Schematic of GUPFC                                                    |

| Figure 3-1:  | SSSC power circuit                                                    |

| Figure 3-2:  | Phasor diagram of SSSC                                                |

| Figure 3-3:  | Indirect control block diagram of SSSC                                |

| Figure 3-4:  | Direct control block diagram of SSSC                                  |

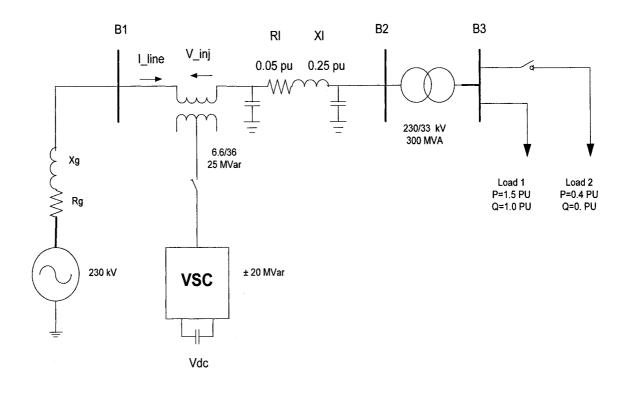

| Figure 3-5:  | Single line diagram of the power system used for simulation 62        |

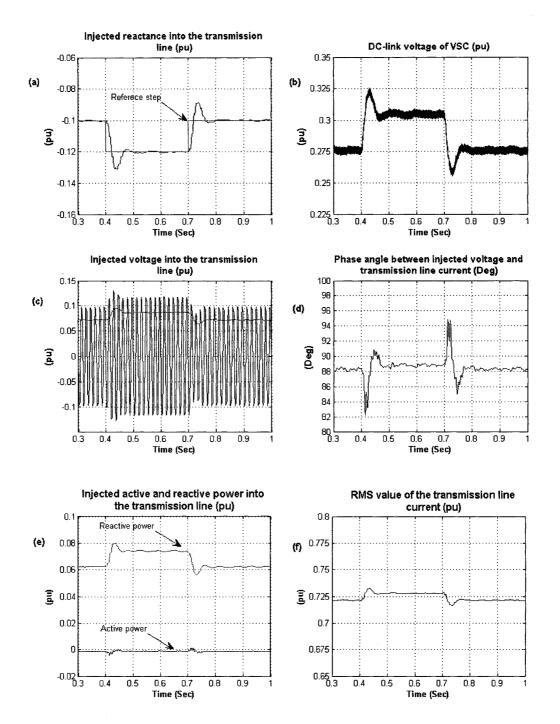

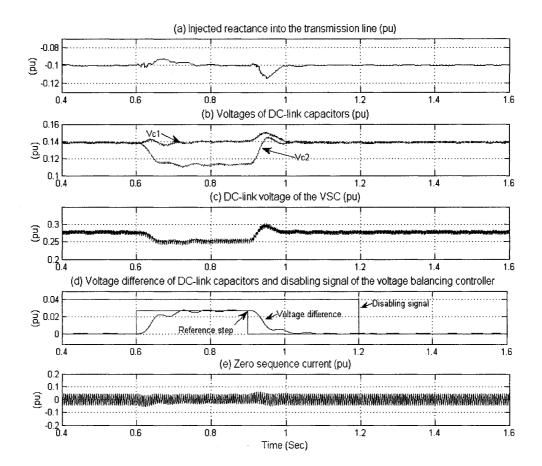

| Figure 3-6:  | System response to step change in the controller reference value      |

|              | (a) Injected reactance (b) DC-link voltage (c) Injected voltage into  |

|              | the transmission line (d) Phase angle between the injected voltage    |

|              | and the transmission line current (e) Injected active and reactive    |

|              | power into the line (f) RMS value of the transmission line current 65 |

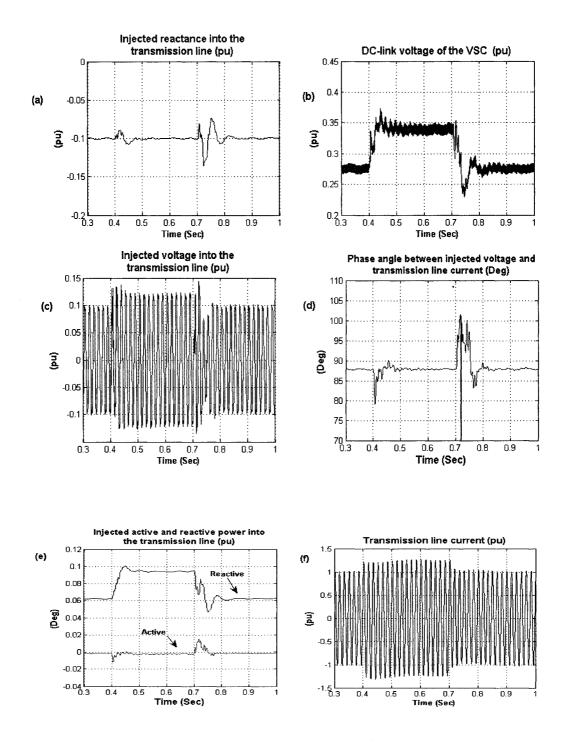

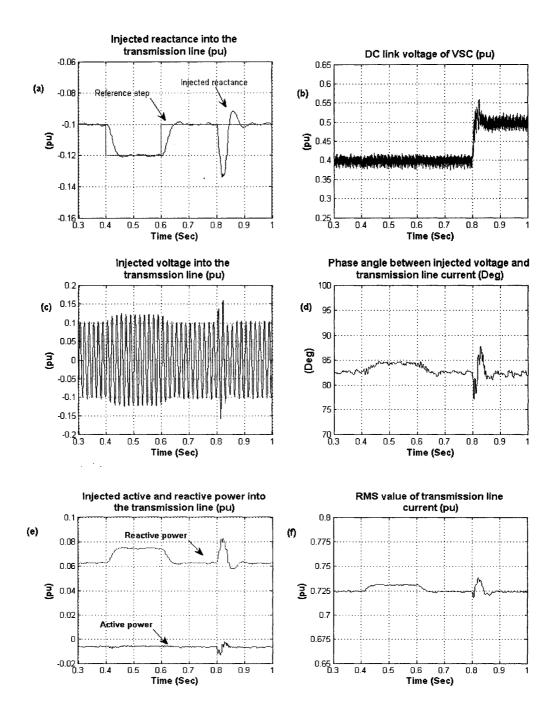

| Figure 3-7:  | Impact of load variation (a) Injected reactance (b) DC-link voltage        |

|--------------|----------------------------------------------------------------------------|

|              | (c) Injected voltage to the line (d) phase angle between injected          |

|              | voltage and line current (e) injected active and reactive power (f)        |

|              | Transmission line current                                                  |

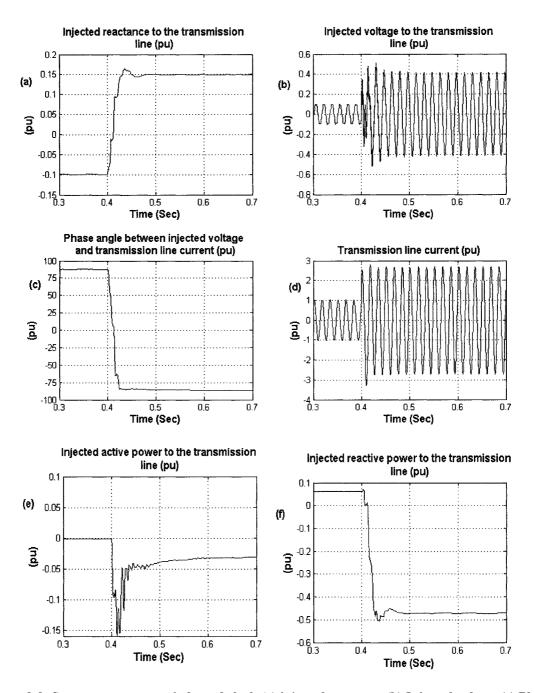

| Figure 3-8:  | System response to a balanced fault (a) injected reactance (b)             |

|              | Injected voltage (c) Phase angle between injected voltage and              |

|              | transmission line current (d) Transmission line current (e) Injected       |

|              | active power (f) Injected reactive power                                   |

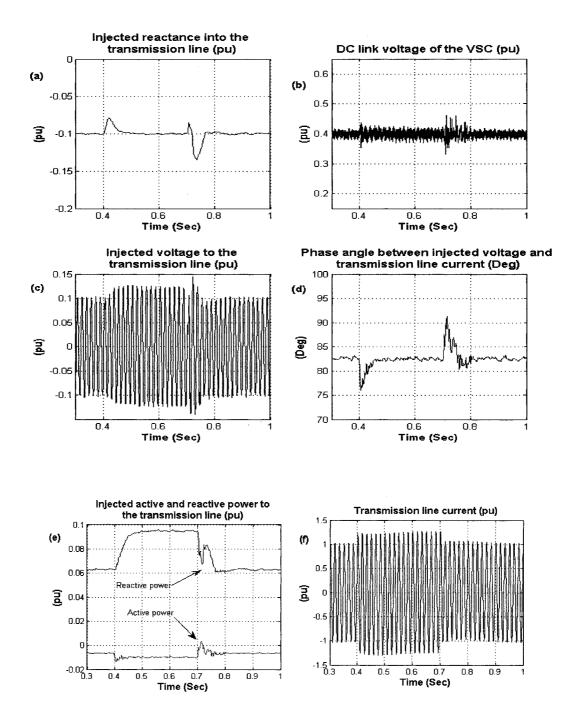

| Figure 3-9:  | Impact of DC voltage balancing circuit (a) Injected reactance into         |

|              | the transmission line (b) DC-link voltages $V_{dc1}$ and $V_{dc2}$ (c) net |

|              | DC-link voltage $(V_{dc1}+V_{dc2})$ (d) Voltage difference and disabling   |

|              | signal (e) Zero sequence current                                           |

| Figure 3-10: | System response to step change in controller reference values (a)          |

|              | Injected reactance (b) DC-link voltage (c) Injected voltage to the         |

|              | transmission line (d) Phase angle between the injected voltage and         |

|              | the transmission line current (e) Injected active and reactive power       |

|              | to the line (f) RMS value of transmission line current                     |

| Figure 3-11: | Impact of load variation (a) Injected reactance (b) DC-link voltage        |

|              | (c) Injected voltage to the transmission line (d) Phase angle              |

|              | between the transmission line current and the injected voltage (e)         |

|              | Injected active and reactive power into the line (f) Transmission          |

|              | line current                                                               |

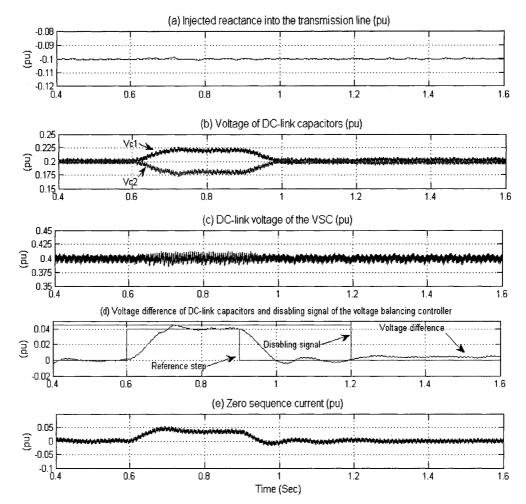

| Figure 3-12: | Impact of DC voltage balancing circuit (a) Injected reactance into         |    |

|--------------|----------------------------------------------------------------------------|----|

|              | the transmission line (b) DC-link voltages $V_{dc1}$ and $V_{dc2}$ (c) net |    |

|              | DC-link voltage ( $V_{dc1}+V_{dc2}$ ) (d) Voltage difference and disabling |    |

|              | signal (e) Zero sequence current                                           | 79 |

| Figure 4-1:  | Schematic of an IPFC                                                       | 82 |

| Figure 4-2:  | Basic Schematic of an IPFC                                                 | 83 |

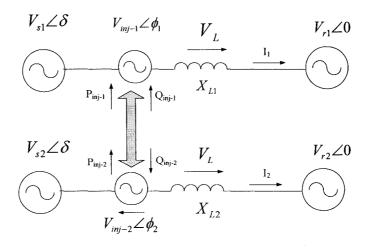

| Figure 4-3:  | Phasor diagram of IPFC (a) System 1 (b) system 2                           | 84 |

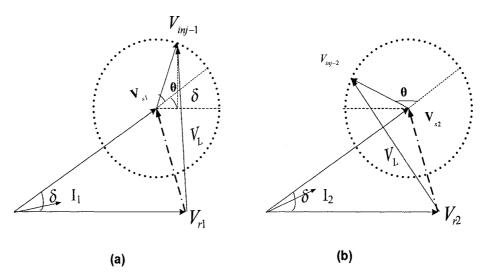

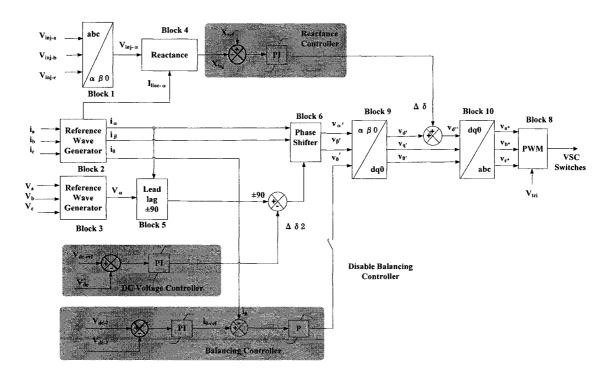

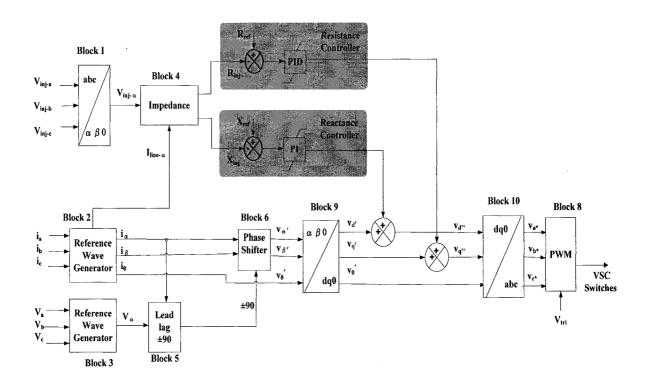

| Figure 4-4:  | IPFC second block                                                          | 87 |

| Figure 4-5:  | IPFC first block                                                           | 89 |

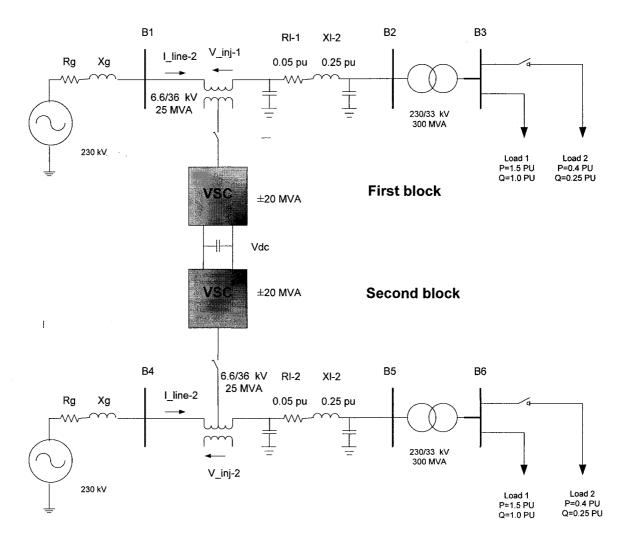

| Figure 4-6:  | Single line diagram of the power system used for simulation                | 91 |

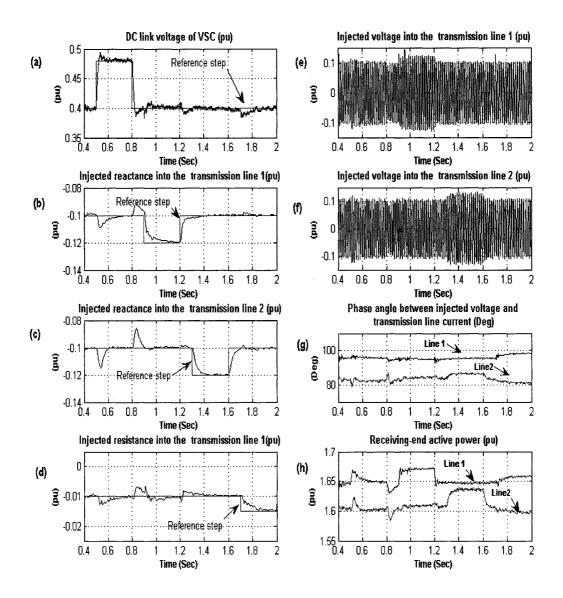

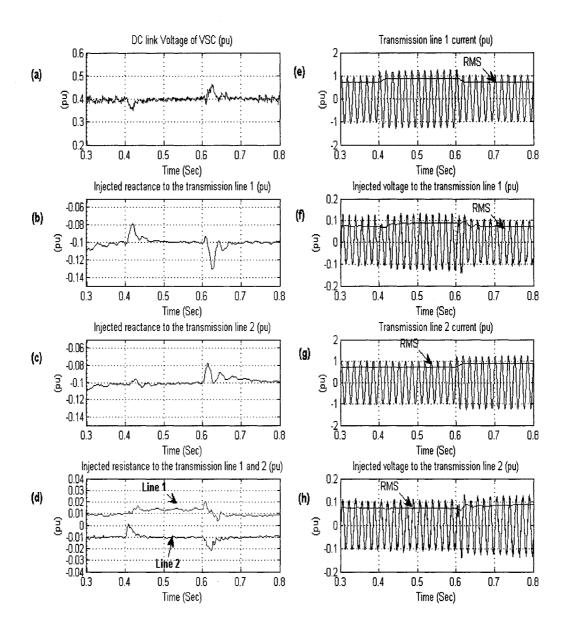

| Figure 4-7:  | System response to step change of the controller reference values          |    |

|              | (a) DC-link voltage (b) Injected reactance into the Line1 (c)              |    |

|              | Injected reactance into the Line2 (d) Injected resistance into the         |    |

|              | Line1 (e) Injected voltage into the Line1 (f) Injected voltage into        |    |

|              | the Line2 (g) Phase angle between the injected voltage and the             |    |

|              | transmission line current (h) Receiving-end reactive power in Line         |    |

|              | 1 and Line 2                                                               | 95 |

| Figure 4-8:  | System response to step change in controller reference values              | 96 |

| Figure 4-9:  | Impact of load variation (a) DC-link voltage (b) Injected reactance        |    |

|              | into the Line 1 (c) Injected reactance into the Line 2 (d) Injected        |    |

|              | resistance into the Lines 1 and 2 (e) Current in Transmission Line         |    |

|              | 1 (f) Current in Transmission Line 2 (g) Injected voltage into the         |    |

|              | Line 1 (h) Injected voltage into the Line 2                                | 98 |

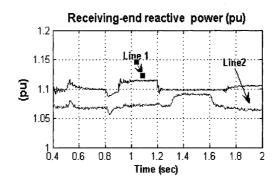

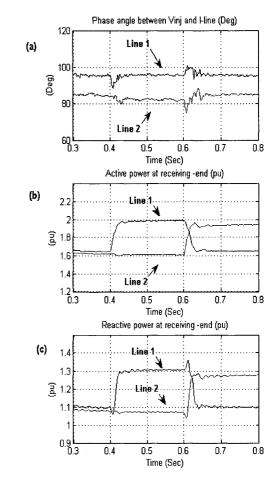

| Figure 4-10: | Impact of load variation (a) Phase angle between the injected    |

|--------------|------------------------------------------------------------------|

|              | voltage and the transmission line current in Lines 1 and 2. (b)  |

|              | Receiving-end active powers (c) Receiving-end reactive powers 99 |

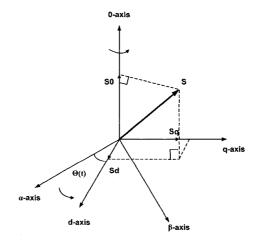

| Figure A-1:  | Physical meaning of d-q-0 transformation                         |

### **List of Tables**

| Table 2-1: | Switching pattern of one pole of a NPC VSC              | 28  |

|------------|---------------------------------------------------------|-----|

| Table 3-1: | Power system parameters                                 | 62  |

| Table 3-2: | Comparison of direct and indirect controller            | 81  |

| Table B-1: | Power circuit values and size of the DC-link capacitors | 111 |

| Table B-2: | Load and switch data of VSC                             | 112 |

| Table B-3: | Snubber circuit elements                                | 112 |

#### **List of Acronyms**

CSC:

**Current Source Converter**

EMTP-RV:

Electro Magnetic Transients Program Restructured Version

**FACTS:**

Flexible AC transmission System

FC:

**Fixed Capacitor**

GTO:

Gate Turn-off Thyristors

**GUPFC**:

Generalized Unified Power Flow Controller

**IEGT:**

Injection Enhanced Gate Transistor

**IGBT**:

Insulated Gate Bipolar Transistor

**IGCT**:

Integrated Gate-commutated Thyristor

IPFC:

Interline Power Flow Controller

NPC:

Neutral Point Clamped

PWM:

Pulse width Modulation

SSSC:

Static Synchronous Series Compensator

STATCOM:

Static Synchronous compensator

SVC:

Static Var Compensators

TCR:

Thyristor Controlled reactor

TCSC:

Thyristor-controlled Series Capacitor

TSC:

Thyristor Switched capacitor

TSSC:

Thyristor Switched Series Capacitor

**UPFC**:

**Unified Power Flow Controller**

VSC:

Voltage Source Converter

#### Chapter 1

#### Introduction

#### 1.1 General

Over the past few years, improving the traditional power transmission systems to utilize the maximum apparatus capacities as well as maintaining reliability and security of power systems have become important concerns. The rising electrical energy demand, both in developing and developed countries, is pushing transmission systems closer to their thermal and stability limits. Furthermore, the conventional transmission systems are not able to manage the control requirements of today's complex and vastly interconnected grid. Thus, fierce competition in the power market is now a reality, since deregulation has occurred in many countries. More profitable operation, as well as improved security and reliability in power systems, are demanded by shareholders and consumers. The conventional solutions of developing the power systems by constructing new transmission lines, substations, and power plants are both expensive and difficult to justify. In the past years, different approaches such as series/shunt compensation and phase shifting have been applied to increase the load-ability and consequently the security of the power systems. These devices were mechanically controlled so they were relatively slow to damp out dynamic and transient oscillations and were only useful in steady state operation. Therefore, transmission systems were designed with large stability margin as a protection against dynamic and transient problems.

The development of high power semiconductor switches opened up a new era of control techniques in power transmission systems. These applications with advanced control technology were introduced as alternatives to improve the utilization of the existing power systems and improve their operational reliability. Known as Flexible AC Transmission Systems (FACTS), these power electronic-based equipments provide cost-effective solutions to new operating requirements of modern power systems.

Power electronics technology was first applied in power systems compensation in the 1970's with the introduction of high power semiconductor diodes and thyristors [2]. Some of the first applications were in High Voltage DC (HVDC) transmission systems. In parallel, Static Var Compensators (SVC) using solid-state switches were employed in AC systems for var compensation. Hingorani first defined the concept of FACTS in 1988 as High power electronics and flexible AC transmission system [7]. At first, Thyristor Controlled Reactor (TCR) and Thyristor Switched Capacitor (TSC) were developed and installed individually or together with conventional capacitors [3],[4]. The rapid development of solid-state switches, with higher voltage/current ratings, and turn-off ability (i.e. GTOs and IGBTs), facilitated the production of a new generation of FACTS controllers based on converter topology.

#### 1.2 Flexible AC Transmission System (FACTS)

The FACTS devices represent a relatively new technology for power transmission systems. They provide the same benefits as conventional compensators with mechanical switches (circuit breakers) in steady-state power system operation; in addition, they improve the dynamic and transient performance of the power system. This is achieved by fast switching time and repeatable operation of solid-state switches as compared to

mechanical switches. The switching time of a solid-state switch is a portion of a periodic cycle; and this is much faster than that of a circuit breaker with a switching time of a number of cycles. In addition, the other advantages of FACTS controllers are their smooth control and repeatable operation [7][8]. Recent advances in semiconductor technology have introduced solid-state switches with higher voltage and current for thyristors (8.5 kV and 4.5 kA), and for Gate turn-off thyristors (GTOs) (6 kV and 6 kA). Also, Insulated Gate Bipolar Transistors (IGBTs) are used for converters with lower rating range, but with higher switching frequencies in the range of up to 3-10 kHz [9].

FACTS controllers can be categorized into two major groups:

- Thyristor-controlled FACTS controller

- Converter-based FACTS controller

Thyristor-controlled FACTS controllers operate by switching a capacitor/reactor in series/shunt to the power system. They provide rapid, continuous control of reactive power over the selected lagging/leading power factor range. Several units have been installed since 1991; one of the first installations was a Thyristor Switched Series Capacitor (TSSC) on a series capacitive compensated 345 kV transmission lines in West Virginia[3].

In converter-based FACTS controllers, either a Voltage Source Converter (VSC) or a Current Source Converter (CSC) is used to generate an appropriate current or voltage, and inject it into the power transmission line. Converter-based FACTS controllers include the Static Synchronous Compensator (STATCOM) for shunt reactive power compensation, the Static Synchronous Series Compensation (SSSC) for series reactive compensation, the Unified Power Flow Controller (UPFC) with unique capability of

#### Chapter 1 Introduction

independently controlling both the active and reactive power flow in the line, and the Interline Power Flow Controller (IPFC) to control active and reactive power flow in parallel lines. In 1991, the first ± 80 Mvar Static synchronous Compensator (STATCOM) was installed at the Inuyama switching station in Japan [5], [6].

The following definitions for FACTS and FACTS controllers are defined by IEEE Power Engineering Society (PES) Task Force of FACTS working group [10]:

- Flexible AC Transmission System (FACTS): Alternating current transmission systems incorporating power electronic-based and other static controllers to enhance controllability and increase power transfer capability.

- *FACTS Controller:* A power electronic-based system and other static equipment that provide control of one or more AC transmission system parameters.

#### 1.3 Power transmission system constraints

The three major factors that limit the loading capability of transmission lines can be categorized as thermal limits, voltage drop limits and stability limits [11]. Thermal limit is a function of ambient temperature, wind condition, conductor loading, and ground clearance. Voltage drops are limited by designed tolerance (about 10% over-voltage), besides the transient over voltage. From the stability point of view, the following items limit the transmission line capability:

- Transient stability

- Dynamic stability

- Steady-state stability

- Frequency collapse

- Voltage collapse

- Subsynchronous Resonance (SSR)

The load-ability of a short length line (less than 80 km) is determined by its thermal limit. For a medium length line (less than 300 km), the voltage drop is the limiting factor. And in long transmission lines (over 300 km), the stability is the main concern in load-ability of the line [11].

In the past, power systems were protected against dynamic changes of power flow by using appropriate stability margins. Devices such as shunt/series capacitors, used to increase the line loading and security of the power system were controlled mechanically. Therefore, they were only suitable for steady state operation in power systems [11].

#### 1.4 Basic principle of active and reactive power flow control

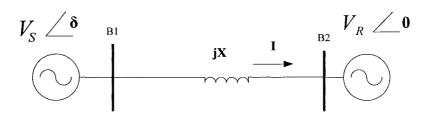

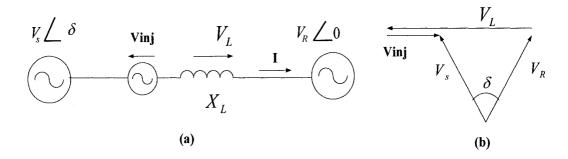

A basic model of a power transmission system is shown in Figure 1-1. The two voltage sources could be two power systems which contain generators and loads.  $V_s$  and  $V_R$  are the sending-end and receiving-end voltages respectively, while  $\delta$  is the phase angle between these voltages. The line resistance is neglected, and the transmission line impedance can be represented by its reactance X.

Figure 1-1: Power transmission line model

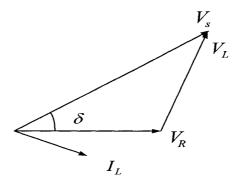

Figure 1-2 shows the voltage phasor diagram of such a system. The line current is perpendicular to the voltage drop  $(V_s - V_R)$  in the transmission line. The active and reactive components of the transmission line current at the sending end are:

$$I_{ps} = \frac{(V_R \sin \delta)}{X}$$

$$I_{qs} = \frac{(V_s - V_R \cos \delta)}{X}$$

(1-1)

And similar equations for transmission line current at the receiving end are:

$$I_{pR} = \frac{(V_s \sin \delta)}{X}$$

$$I_{qR} = \frac{(V_R - V_s \cos \delta)}{X}$$

(1-2)

Figure 1-2: Voltage phasor diagram of the transmission line

Hence, the active and reactive power in the sending-end and the receiving-end can be obtained. Since the active power loss in the transmission line in Figure 1-1 is zero, the sending-end and receiving-end active powers are equal (i.e. Ps=P<sub>R</sub>). Therefore, the active power at the sending-end and receiving-end is:

Chapter 1 Introduction

$$P = \frac{V_s * V_R}{X} \sin \delta \tag{1-3}$$

where  $\delta$  is the angle between the two voltage sources.

The reactive power at the sending-end is:

$$Q_s = \frac{V_s(V_s - V_R \cos \delta)}{X} \tag{1-4}$$

and the reactive power at the receiving-end can be found from:

$$Q_R = \frac{V_R (V_S \cos \delta - V_R)}{X} \tag{1-5}$$

Figure 1-3: Power angle curve

Equations (1-2) to (1-5) show that controlling the voltage, angle and/or impedance of the power system can regulate the active and reactive power. Impedance control is more effective in active power flow control. Regulating sending-end and receiving-end voltages is more effective in reactive power flow control. Figure 1-3 demonstrates the power angle curve of the system shown in Figure 1-1. The maximum active power occurs

at  $\delta = 90$  degrees, but the system is only stable if the derivative  $\frac{dP}{d\delta}$  is positive and operates in Area I of Figure 1-3. In order to keep the power system stable from dynamic and transient oscillations, an adequate margin must also be maintained. In practice, the transmission angle is kept below 45 degrees [14].

#### 1.5 Compensation in AC transmission lines

Reactive power compensators have been applied in power systems to increase steadystate power transmission by regulating voltage profile along the transmission lines.

Conventionally, fixed or mechanically switched reactors/capacitors have been used for

this purpose. Besides this, rotating synchronous condensers have been also employed in

transmission lines for reactive shunt compensation. They have high capacitive output

current at low system voltages and do not generate harmonics that resonate with the grid.

However, they are vulnerable to rotating instability and have slow response with low

short circuit impedance, and high maintenance cost [12]. The new generation of

compensators is based on power electronic devices. They are suitable for fast reactive

power compensation in power systems. Therefore, they are effective in dynamic

compensation and real time control of power flow in power systems. These compensators

are used in series, shunt or a combination of them in power transmission lines for

different purposes. In the following sections, the concepts of shunt and series

compensation are briefly reviewed.

#### 1.5.1. Shunt compensation

Basically, shunt compensators are used to regulate the voltage in a transmission line; this is achieved by exchanging reactive power with the transmission line. Shunt reactors are used to reduce the line over-voltage under light loads, and shunt capacitors are applied to keep voltage at the desired level under heavy load conditions [1].

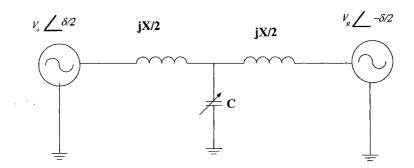

In Figure 1-4, a simple model of a transmission line is shown in which a shunt compensator is connected at the midpoint of the transmission line. Sending-end and receiving-end voltages are assumed equal (i.e.  $V_s = V_R = V$ ), and an inductor ( $X_L$ ) represents the line impedance.

Figure 1-4: Power transmission line model with shunt compensation

While the transmission line is lossless, the active power at the sending-end and receiving-end are identical and can be obtained from the following equation:

$$P_c = 2\frac{V^2}{X_L} \sin \frac{\delta}{2} \tag{1-6}$$

where  $\delta$  is the phase angle between sending-end and receiving-end voltages. The reactive power is:

$$Q_c = 4\frac{V^2}{X_L} (1 - \cos\frac{\delta}{2}) \tag{1-7}$$

Figure 1-5 shows the  $P_c$  (active power with an ideal midpoint compensator), P (active power without compensator) versus  $\delta$  characteristic of the shunt compensation model (Figure 1-4). The transmitted power is significantly increased compared to an uncompensated line.

Figure 1-5: Active power versus transmission line angle

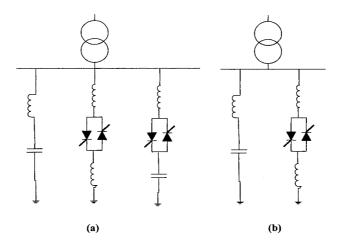

The thyristor-based FACTS controllers are well known and widely used in power system compensation since the late 70s. Generally, a combination of thyristor-based FACTS controllers with fixed capacitors is used. Figure 1-6 shows two typical configurations of Static Var Compensators (SVC). In Figure 1-6a, the SVC consists of a TCR, a TSC and fixed capacitor (FC). Figure 1-6b shows a TCR and FC together. By controlling the firing angles of the thyristors, reactive power compensation can be adjusted to the desired value. One of the first SVCs, with 40 Mvar rating, was installed at the Shannon substation in Minnesota Power and Light system in 1978 [13].

Figure 1-6: Static var compensator (a) TCR, TSC, and FC (b) TCR, and FC

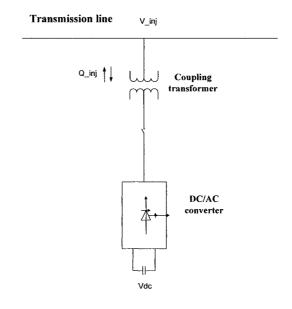

A FACTS shunt compensation scheme, called STATCOM, is shown in Figure 1-7. A STATCOM generates a set of 3-phase voltages in phase with the transmission line voltages, and is capable of exchanging reactive power with the line. By regulating the STATCOM voltage,  $V_{inj}$ , the direction of the reactive power can be controlled [14].

Figure 1-7: Schematic of STATCOM

#### 1.5.1 Series compensation

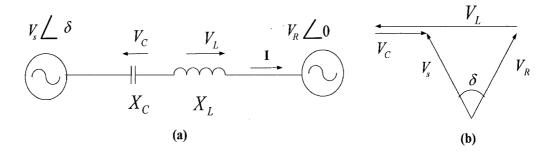

The purpose of series compensation in power transmission lines is to control the reactive line impedance. In fact, by adding a series compensator such as a capacitor, a series voltage in opposition to the transmission line voltage drop is injected; thereby, the voltage drop across the transmission line and the effective line impedance are reduced. Consequently, the transmission line current increases. The drawbacks of series compensators are the need for protection devices that must be installed for protecting against high currents during fault periods and also the possibility of subsynchronous resonance exists that may damage generator shafts [1],[3].

Figure 1-8a shows a simple model of a power system with a capacitor in series. Figure 1-8b shows the corresponding phasor diagram.

Figure 1-8: (a) Model of a power system with series compensation (b) Phasor diagram

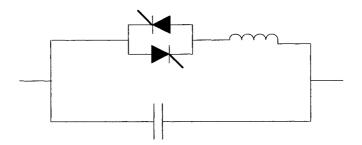

Figure 1-9 shows a Thyristor-Controlled Series Capacitor (TCSC), which is a thyristor-based series FACTS controller. It is employed in transmission lines for rapid control of line reactance; by controlling the firing angle of the thyristors, the effective reactance value is changed.

Figure 1-9: Schematic of TCSC

In converter-based FACTS controllers the same objective is achieved by adding a desired voltage in series with the transmission line. Figure 1-10 demonstrates a synchronous AC voltage source, whose output is equivalent to the voltage of the series capacitor  $(V_{inj} = V_c = -jX_CI)$ . The Static Synchronous Series Compensator (SSSC) emulates the same functional behavior of a conventional series capacitor; in addition the following benefits are achieved by applying SSSC in a power transmission line [1].

Figure 1-10: (a) Model of a power system with a synchronous voltage source in series (b) Phasor diagram

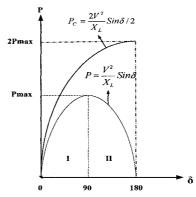

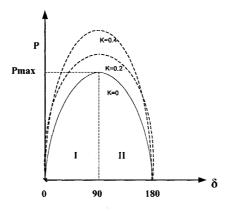

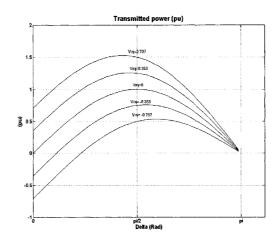

#### • Transmitted power versus transmission angle characteristics

The voltage across the capacitor is proportional to the line current i.e. a function of the angle between the sending-end and receiving-end voltages (transmission angle). By assuming  $V_S = V_R$ , the real transmitted power can be found from:

Chapter 1 Introduction

$$P = \frac{V_S V_R}{(1 - k) X_L} \sin \delta = \frac{V^2}{(1 - k) X_L} \sin \delta \tag{1-8}$$

where  $k = \frac{X_c}{X_l}$  is the degree of series compensation.

The transmitted power versus transmission angle is shown is Figure 1-11. By increasing the degree of compensation the transmitted power can be increased.

Figure 1-11: Transmitted power versus angle with various degrees of compensation

In SSSC, the series compensation degree is independent of the line current, and the transmitted power can be found from the following equation:

$$P = \frac{V^2}{X_L} \sin \delta + \frac{V}{X_L} V_{inj} \cos(\delta/2)$$

(1-9)

Where the injected voltage,  $V_{inj}$ , is in quadrature with the line current. The transmitted powers versus transmitted angle curves are plotted in Figure 1-12.

As is shown in Figure 1-11 and 1-12, the transmitted power in the series capacitor increases by a fixed transition angle, but in SSSC the maximum transmitted power increases independently of the transmitted angle in the important range of  $0 \le \delta \le 90^{\circ}$  [1].

Figure 1-12: Transmitted power versus angle in SSSC

Also, the SSSC is capable of operating in both capacitive and inductive modes; therefore, it is able to operate as a reactor to decrease the line current.

#### Capability of active power compensation

An important requirement in series compensation is to keep the ratio X/R high enough (over 10). A low ratio of X/R could gradually increase the reactive power demand, which results in line losses and voltage collapse. A SSSC, with the availability of an energy source, is able to exchange both reactive and active power with the transmission line. Therefore, SSSC is able to regulate both R and X in transmission lines in order to keep the X/R ratio high.

#### Immunity to subsynchronous resonance

Series capacitors are vulnerable to subsynchronous resonance, but the fast response of a SSSC makes it capable of damping subsynchronous resonance.

#### 1.6 Literature review

Since the focus of this thesis is on series connected VSC-based FACTS controllers, a brief literature review on this topic is presented below.

Gyugyi first proposed the converter-based, solid-state series compensator in 1979 [15]. Schauder and Mehta developed a mathematical model of a VSC with direct and indirect controllers by using Park's transformation in 1991[16]. In[17], Ooi et al reported a laboratory-based research on a series converter-based FACTS controller by using VSC and CSC topologies. They used a 1 kVA bipolar transistor converter with a 2-level Pulse Width Modulation (PWM) controller as the laboratory model. Gyugyi presented the application of a synchronous voltage source implemented by a multi-pulse GTO in AC transmission lines for series compensation in 1989[18] and introduced SSSC in 1996 [19]. Sen, Schauder, and Gyugyi first introduced the IPFC for multi-line transmission systems in 1999 [20]. A few papers on IPFC have been published that investigated the basic model and steady state operation of an IPFC [21], [22]. In [23], the ability of an IPFC in power flow control and damping system oscillation was considered. Much research has been done after developing the basic theory of a series converter-based FACTS controller. Several articles on SSSC have been published [24], [25], [28], and [44] to investigate the controller function and increase the efficiency of the converter's power circuit in order to reduce the losses and improve the quality of output voltage. IPFC is a relatively new topology and less published research is available on it [21], [22], [23]. Unlike STATCOM and UPFC, SSSC and IPFC have not been installed and utilized as yet in any transmission systems. More research is required in this area before practical use in power transmission systems.

#### 1.7 Problem definition

This thesis investigates the theory and design of series converter-based FACTS controllers such as SSSC and IPFC. Both these applications use the VSC as the basic building block. The operating principles and design of the VSC are, therefore, first presented.

The thesis objective is to study the steady state and dynamic operation of VSCs in series with transmission systems. More precisely, the applications of SSSC and IPFC are considered. Both direct and indirect control methods in SSSC application are studied. Two SSSCs, with a common DC-link, are used to build an IPFC application. The models of the power system and the controllers are implemented using the EMTP-RV simulation package and results are obtained.

#### 1.8 Thesis contributions

The Static Synchronous Series Compensator (SSSC) and the Interline Power Flow Controller (IPFC) are designed and implemented in EMTP-RV. The SSSC with direct and indirect controllers is presented and the dynamic performance of the two controllers is studied and compared. Several tests are conducted to validate the operation of the SSSC and the IPFC to compensate the impedance and limiting the fault current in the transmission line.

#### 1.9 Thesis outline

Chapter 2 gives a general introduction to modeling, operating principles and passive component design of a 3-level Neutral Point Clamped (NPC) VSC. Also, the method to generate switching pulses for the converter is described. And finally, the VSC topologies in FACTS controllers are presented.

Chapter 3 concentrates on the application of a VSC in series with a power transmission line. This series connected VSC is called Static Synchronous Series Compensator (SSSC). The operating principle and control strategies that are used are explained. The simulation results, with an EMTP-RV model that includes a detailed representation of a 3-level PWM-controlled SSSC are given in this chapter.

Chapter 4 describes the operating principles and controller design of an Interline Power Flow Controller (IPFC). The theory and control function of the IPFC are explained, and the simulation results with EMTP-RV are presented.

Chapter 5 presents the conclusions and future direction of the research in this thesis.

#### 1.10 Summary

This chapter gives a basic principle of series/ shunt compensation in transmission systems and the potential advantages of converter based FACTS controller for series/shunt compensation. Also it provides an overview of the thesis objectives, and methodology.

#### Chapter 2

#### Voltage Source Converter (VSC) and FACTS topologies

#### 2.1 Introduction

Switch mode power converters are a major building block of converter-based FACTS controllers. A converter is capable of generating a set of 3-phase sinusoidal voltages with controllable magnitude and phase angle. In this chapter, the design fundamentals and basic operating principles of a 3-level Pulse Width Modulation (PWM) Voltage Source Converter (VSC) are explained. This PWM-controlled VSC is the basic building block of SSSC and IPFC that will be used for digital simulation in later chapters.

#### 2.2 High power switch-mode converters

Voltage Source Converters (VSCs) and Current Source Converters (CSCs) are two major groups of power converters that are employed in FACTS devices. They are connected in series or shunt with the power transmission lines, and inject voltage or current with appropriate magnitude and phase angles. CSCs operate as a current source, and their DC side contains a current source such as a charged inductor. The DC current in CSC always has one polarity and power reversal takes place through a reversal of DC voltage polarity. Therefore, semiconductor switches with bi-directional voltage blocking must be used in CSCs. VSCs operate as a voltage source, and they have an energy source such as a charged capacitor on the DC side. In VSCs, the DC voltage always retains one polarity, and power reversal takes place through reversal of DC current polarity. So VSCs

require semiconductor switches with an ability of unidirectional voltage blocking. In FACTS applications, VSCs are preferred because of better performance and economical reasons. In this thesis, only VSCs are discussed and used for DC/AC conversion in FACTS controllers.

#### 2.3 Power switches

Semiconductor switches that are suitable for high power FACTS applications include the Insulated Gate Bipolar Transistor (IGBT), the Gate Turn-off Thyristors (GTO), Injection Enhanced Gate Transistor (IEGT), and the Integrated Gate-Commutated Thyristor (IGCT). GTO and IGBT are likely to be replaced by new generation devices like the IGCT and IEGT respectively, because of their advantages [38]. IGCT and IEGT do not require individual snubber circuits. Also, an IGCT has better turn-off characteristics with lower switching and conducting losses when compared to a GTO and an IGBT. The maximum rating of an IEGT is presently 4.5kV/1.5 kA [39]. The maximum rating of an IGCT reaches 5.5-kV/1.8 kA for a reverse-conducting IGCT, and 4.5 kV/4 kA for an asymmetrical IGCT [40].

The cost of semiconductor switches for a 100 MVA installation is typically 1% of the total project cost [38]. However, it influences on the performance and, therefore, on the capital and operational cost of the applications. The following factors must be considered for selecting semiconductor switches:

- 1. Low cost

- 2. High reliability

- 3. Simple maintenance and assembly

- 4. Low dv/dt and di/dt

- 5. High voltage and current rating

- 6. Low losses (switching and conducting)

- 7. Fast switching

- 8. High frequency operation

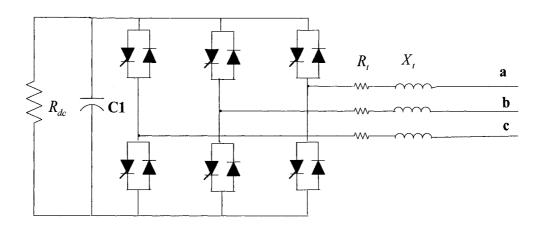

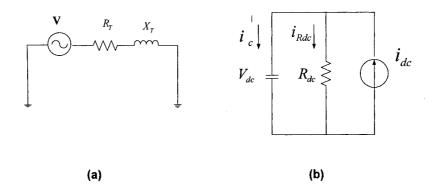

# 2.4 Modeling of a 3-phase VSC

A VSC can be represented by a synchronous sinusoidal voltage source with controllable magnitude and phase angle. The scheme of a 3-phase VSC is shown in Figure 2-1. The series inductance " $X_t$ " in the AC side of the VSC accounts for the leakage of the coupling transformer, and the series resistance " $R_t$ " represent the transformer and VSC losses. The DC side of the VSC consists of a DC capacitor and a shunt resistance " $R_{dc}$ " that represents the switching losses of the VSC.

Figure 2-1: Diagram of a 3-phase VSC

It is assumed that the 3-phase output voltages of the VSC are balanced for a 3-wire system, and free of harmonics. The AC side and DC side equivalent circuit are shown in Figure 2-2.

Figure 2-2 (a) AC side equivalent of VSC (b) DC side equivalent of VSC

The mathematical model of the VSC in terms of instantaneous variables in the AC side can be written as:

$$\begin{cases} L\frac{di_a}{dt} = U_a - V_a - R_a i_a \\ L\frac{di_b}{dt} = U_b - V_b - R_b i_b \\ L\frac{di_c}{dt} = U_c - V_c - R_c i_c \end{cases}$$

(2-1)

where U<sub>a</sub> is the transmission line voltage and V<sub>a</sub> is the VSC output voltage. The DC side of the VSC from Figure 2-2 (b) is defined by:

$$C\frac{dV_{dc}}{dt} = i_{dc} - \frac{v_{dc}}{R_{dc}} \tag{2-2}$$

By transforming eq. (2-1) in the a-b-c reference frame into the d-q-0 synchronous rotating reference frame, as explained in Appendix A, the following equations are obtained:

$$\frac{d}{dt} \begin{bmatrix} i_d \\ i_q \\ i_o \end{bmatrix} = \begin{bmatrix} -\frac{R\omega}{L} & -\omega & 0 \\ \omega & -\frac{R\omega}{L} & 0 \\ 0 & 0 & -\frac{R\omega}{L} \end{bmatrix} \begin{bmatrix} i_d \\ i_q \\ i_o \end{bmatrix} + \frac{\omega}{L} \begin{bmatrix} (U_d - V_d) \\ (U_q - V_q) \\ (U_0 - V_0) \end{bmatrix}$$

(2-3)

where  $\omega$  is the angular frequency.

Using the same method from a-b-c frame to d-q-0 frame, the power balance between AC and DC side of the converter (assuming no losses) gives the following equation:

$$v_{dc}i_{dc} = \frac{3}{2} \left( u_d i_d + u_q i_q + u_0 i_0 \right) \tag{2-6}$$

where:

$$u_d = m_a v_{dc} \cos(\Phi)$$

$$u_q = m_a v_{dc} \sin(\Phi)$$

(2-5)

and  $m_a$  is the modulation index of the VSC, and  $\Phi$  is the phase angle between the injected voltage and the line current.

Therefore, from eqs. (2-2), (2-4), and (2-5), the DC side equation of VSC in d-q-0 frame will be:

$$\frac{dv_{dc}}{dt} = \frac{3}{2C} \left( m_a \cos(\Phi) i_d + m_a \sin(\Phi) i_q \right) - \frac{v_{dc}}{CR_{dc}}$$

(2-6)

By combining eqs. (2-3) and (2-6), the mathematical model of VSC is obtained:

$$\frac{d}{dt}\begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \\ v_{dc} \end{bmatrix} = \begin{bmatrix}

-\frac{R\omega}{L} & \omega & 0 & -\frac{m_{a}}{L}\cos(\Phi) \\

-\omega & -\frac{R\omega}{L} & 0 & -\frac{m_{a}}{L}\sin(\Phi) \\

0 & 0 & -\frac{R\omega}{L} & 0 \\

\frac{3m_{a}}{2C}\cos(\Phi) & \frac{3m_{a}}{2C}\sin(\Phi) & 0 & -\frac{1}{CR_{bc}}

\end{bmatrix} \begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \\ v_{dc} \end{bmatrix} + \begin{bmatrix} \frac{\omega}{L} & 0 & 0 & 0 \\

0 & \frac{\omega}{L} & 0 & 0 \\

0 & 0 & \frac{\omega}{L} & 0 \\

0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} U_{d} \\ U_{q} \\ U_{0} \\ 0 \end{bmatrix} \tag{2-7}$$

Since it is assumed that the 3-phase voltages are always balanced, the zero sequence component is zero, and only d-q components exist. In reality, this is far from the truth. Consequently, the zero sequence will be considered for DC-link voltage balancing separately in Chapter 3. The d-q-0 transformation is briefly explained in Appendix A.

# 2.5 3-level Neutral Point Clamped (NPC) VSC

VSCs, through a proper switching algorithm, convert DC voltage into a set of 3-phase AC voltages or currents with controllable amplitude and phase angle at fixed frequency equal to transmission line frequency (50 or 60 Hz). The converter DC terminals are connected to DC capacitors or a DC voltage source, while the AC side is connected to a power system through a coupling transformer. The DC capacitors must be large enough to maintain constant DC voltage during DC current changes. The coupling transformer connects the VSC to the power system. The transformer inductance protects the DC capacitor against short-circuits and sudden discharge.

Regulating the DC-link voltage or varying AC to DC gain of the converter can be used to control the AC voltage magnitude. In the first method, known as indirect control [1], the DC voltage is regulated in order to provide the desired amplitude in the AC side and the converter's AC to DC gain is kept constant. The disadvantage of this method is that the AC voltage range is limited due to the size of the DC side capacitor. In the second method of controlling the converter's AC to DC gain, the AC side voltage amplitude is regulated while the DC voltage is fixed (Direct control method). Both control methods are presented in this thesis for AC voltage regulation. The VSC has the capability to operate either as an inverter or a rectifier, and exchange active power with the power system; this is achieved by regulating the phase angle of the AC side voltage.

Several configurations for DC/AC converters exist, such as multi-pulse converters, and PWM converters [43]. PWM techniques offer lower harmonic components, with excellent dynamic response. Two-level PWM topology is the simplest and most commonly used, but it has the drawback of generating high switching-frequency

harmonics, and high dv/dt due to synchronous commutation of series devices. Multi-level PWM VSCs have the advantage of lower voltage stresses and generating lower harmonic components; also, they operate at a lower switching frequency [26].

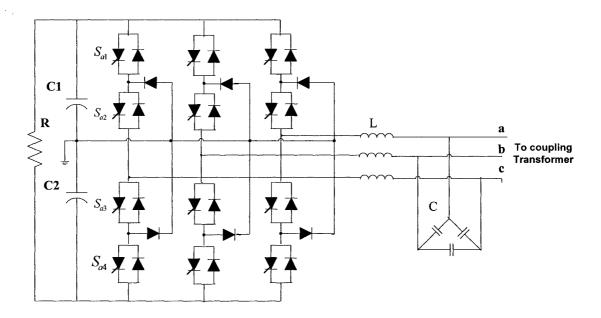

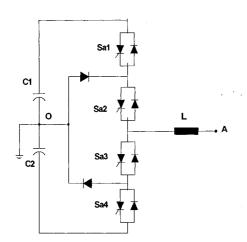

An m-level converter (where  $m \ge 3$ ), typically consists of m-1 capacitors in the DC-link and generates m-levels of voltages. Here, for simplicity, a 3-level PWM VSC is studied in detail and used for simulation. Figure 2-3 shows the schematic diagram of a 3-phase Neutral Point diode Clamped (NPC), 3-level VSC; the circuit consists of twelve valves and two DC capacitors. Each valve consists of a solid-state switch with turn-off capability and an anti-parallel diode. The anti-parallel switches ensure the bidirectional current flow, so that the converter is capable of operating in both rectifier and inverter modes.

Figure 2-3: Schematic of a 3-level Neutral Point Clamped VSC

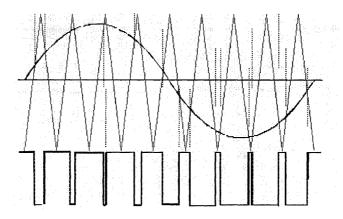

#### 2.5.1 Sinusoidal Pulse Width Modulation (SPWM) technique

In SPWM technique, a reference sinusoidal waveform is compared with a triangular carrier wave. The frequency of the triangle carrier is selected to be much higher than the reference waveform. These two signals are compared, and when the sinusoidal wave is greater than the carrier, the SPWM trigger signal is high; otherwise it is at the low level. In a 3-phase converter, similar to the converter shown in Figure 2-1, a set of 3-phase balanced waveforms must be compared with a triangular carrier wave to generate appropriate firing pulses for the converter's switches. Consequently, the output voltage of the converter has the same frequency as the reference sinusoidal waveform, and the magnitude of the generated voltage is proportional to the modulation index that is defined by the ratio of the amplitude of the reference wave over the maximum value of the carrier. Figure 2-4 shows how the switching pulses are generated in a conventional 2-level SPWM converter.

Figure 2-4: Modulation wave of 2-level PWM

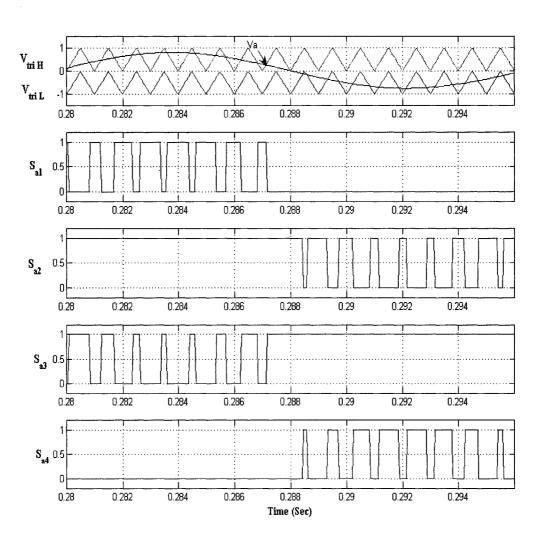

In an m-level PWM converter, m-1 carrier waves are required to generate the switching pulses. Figure 2-5 shows the schematic for one phase of a 3-level PWM. The

3-level PWM uses two carrier waves, and the 3-level output waves are made with the following rules for the scheme shown in Figure 2-5:

- If  $Va > V_{tri-H}$ ,  $S_{a1}$  is ON else  $S_{a1}$  is OFF.

- If  $Va > V_{tri-L}$ ,  $S_{a2}$  is ON else  $S_{a2}$  is OFF.

- Only two series devices can be turned ON at the same time so:

- $\circ$  S<sub>a1</sub> and S<sub>a3</sub> have opposite functions.

- $\circ$  S<sub>a2</sub> and S<sub>a4</sub> have opposite functions.

Figure 2-5: Modulation wave and switching signals of a 3-level PWM

#### 2.5.2 Operating principle of a 3-level NPC VSC

Figure 2-6 shows one pole of the 3-phase, 3-level NPC VSC, and the corresponding switching pattern is shown in Table 2-1. In a 3-level NPC VSC, the output voltage of the converter is made of 3-level voltages ( $+V_{dc}/2$ , 0,  $-V_{dc}/2$ ).

There are three switch combinations to make a 3-level voltage in the output, namely:

- For  $V_{a} = +V_{dc}/2$ , upper switches  $S_{a1}$  and  $S_{a2}$  are ON.

- For  $V_a = -V_{dc}/2$ , two lower switches  $S_{a3}$  and  $S_{a4}$  are ON.

- For  $V_a = 0$ ,  $S_{a2}$  and  $S_{a3}$  are ON.

Table 2-1: Switching pattern of one pole of a NPC VSC

| Switching<br>State | S <sub>1a</sub> | S <sub>2a</sub> | S <sub>3a</sub> | S <sub>4a</sub> | Van    |

|--------------------|-----------------|-----------------|-----------------|-----------------|--------|

| Positive           | 1               | 1               | 0               | 0               | Vdc/2  |

| Zero               | 0               | 1               | 1               | 0               | 0      |

| Negative           | 0               | 0               | 1               | 1               | Vdc/2- |

Figure 2-6: One pole of 3-level NPC VSC

In Table 2-1, the voltage levels and related switching states are shown. State "1" indicates that the switch is ON and state "0" indicates that the switch is OFF. Switches  $S_{a1}$ ,  $S_{a3}$  and  $S_{a2}$ ,  $S_{a4}$  are complimentary, i.e. if a switch is "ON" the other switch is "OFF" and vice versa. Figure 2-7 shows the output waveform of the 3-level VSC.

Figure 2-7: Output waveform of 3-level NPC VSC

# 2.6 Snubber circuit

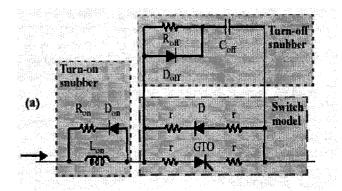

Snubber circuits are used in a VSC to protect semiconductor switches from electrical stresses during the switching operations. In semiconductor switches, the over voltages during switch-off and turn-on currents during switch-on must be limited. Hence, these switches require turn-on and turn-off snubber circuits. Figure 2-8 shows the model of a switch with snubber circuits that are used in the converter model.

The equivalent switch identified as "GTO" and the anti-parallel diode D are represented as ideal switches in EMTP-RV. The small resistor r, in series with GTO and anti-parallel diode, represents the switch conduction losses and assists in avoiding any singularity on the inversion of the conductance matrix of circuit.

Figure 2-8: Model of the switch with snubber circuits

The polarized parallel R-L turn-on snubber circuit limits the rise rate of current, and the polarized R-C circuit limits the over-voltage during switch turn-off. An approximate value of the snubber circuit can be obtained from the following equations [30]:

$$\begin{cases} R_{on} = \frac{\Delta V_{CE}}{I_o} \\ \Delta V_{CE} = 10\% U_d \\ L_{on} = \frac{\Delta V_{CE} * t_{ri}}{I_o} \\ C_{off} = \frac{I_O * t_{fi}}{2 * U_d} \\ R_{off} = \frac{5 * U_d}{I_O} \end{cases}$$

(2-8)

where

$t_{ri}$ : is the current rise time of the switch when the anode voltage falls from 90% to 10%  $t_{fi}$ : is the current fall time of the switch when the anode current falls from 90% to 10%.  $\Delta V_{CE}$ : is the voltage drop across the switch during turn-on.

R<sub>off</sub>: is the resistor in the turn-off snubber.

L<sub>on</sub>: represents the inductor in the turn-on snubber.

# 2.7 Passive component design

#### 2.7.1 DC-link capacitor

#### • Balancing the DC-link voltages

In a 3-level converter topology, the unequal voltage charging of the DC-link capacitors due to the circuit behavior may eventually damage the semiconductor switches. Since the charging and discharging time of the capacitors are not the same, an accumulating unbalance voltage may cause a high voltage on the semiconductor switches and surpass the switch rating [31] and may destroy the switches. Several methods, such as using separate DC voltage sources [32], or modified PWM patterns and voltage vector selections [33] can be used as solutions. To balance the voltages, a simple algorithm from [31] is applied that is based on zero sequence current. The unbalanced voltage is sensed and amplified by a PI controller, and compared to the zero sequence component of the converter output current to feed forward to the PWM. The same method is used here for DC-link voltage balancing and it will be discussed in more detail in Section 3.4.1

#### • Design of DC capacitor

The DC capacitor of VSCs has a major impact on the system operation. By using a large capacitor, the DC voltage ripple will be reduced, but the system will have a slower response to DC voltage regulation. Also the capacitor cost will be higher. Therefore, a capacitor with minimum capacity that satisfies the DC waveform quality is desired [41]. In this section, the optimum capacitor size with the respect to the DC voltage ripple is investigated.

If the parallel resistor with the DC-link capacitors (representing the converter losses) and the stored line inductor energy is neglected, by applying KCL:

$$C_{dc} \frac{dV_{dc}}{dt} + \frac{V_{dc}}{R_{dc}} = S^{T} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix}$$

(2-9)

where S is the switching function and can be defined by:

$$S = \begin{bmatrix} S_a \\ S_b \\ S_c \end{bmatrix} = m_a \begin{bmatrix} \sin(\omega t) \\ \sin(\omega t + 120^\circ) \\ \sin(\omega t + 240^\circ) \end{bmatrix}$$

(2.10)

It is assumed that the harmonic components caused by the switching action are neglected. For simplicity, one pole of the 3-level converter is considered to determine the minimum capacitor size.

$$S^{T} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = m_{a} \begin{bmatrix} \sin(\omega t) \\ \sin(\omega t + 120^{\circ}) \\ \sin(\omega t + 240^{\circ}) \end{bmatrix} \begin{bmatrix} I_{m} \cos(\omega t + \phi) \\ I_{m} \cos(\omega t + \phi + 120^{\circ}) \\ I_{m} \cos(\omega t + \phi + 240^{\circ}) \end{bmatrix}$$

$$= \frac{m_{a} I_{m}}{2} \begin{bmatrix} \sin 2(\omega t + \phi) \\ \sin 2(\omega t + \phi + 120^{\circ}) \\ \sin 2(\omega t + \phi + 240^{\circ}) \end{bmatrix}$$

(2-11)

At any instant  $(S_a i_a + S_b i_b + S_c i_c)$  is equal to one of the AC phase current with value of  $\frac{I_m m_a}{2}$ . In steady-state, the DC voltage has a small ripple that is defined as the difference between the maximum and minimum value of DC voltage  $\Delta V_{dc} = V_{dc \, max} - V_{dc \, min}$ , with average value of  $V_{dc,ave}$ . By considering a short period of time that DC-link voltage is

charged from  $V_{dc\, {

m min}}$  to  $V_{dc\, {

m max}}$ , the variation of DC voltage can be shown with  $\frac{\Delta V_{dc}}{\Delta t}$ .

Therefore, eq. (2-9) becomes:

$$C_{dc} \frac{\Delta V_{dc}}{\Delta t} + \frac{V_{dc}}{R_{dc}} = \frac{I_m m_a}{2} \tag{2-12}$$

Hence, the minimum value of the DC-link capacitor can be defined by the following equation:

$$C_{dc} = \frac{\left(\frac{I_{m}m_{a}}{2} - \frac{V_{dc,ave}}{R_{dc}}\right) * \Delta t}{\Delta V_{dc}} = \frac{\frac{I_{m}m_{a}}{2} - \frac{V_{dc,ave}}{R_{dc}}}{\Delta V_{dc} * f_{s}}$$

(2-13)

where  $f_s$  is the converter's switching frequency, and  $\Delta V_{dc}$  is the acceptable ripple in the DC-link.

## 2.7.2 AC side filter design

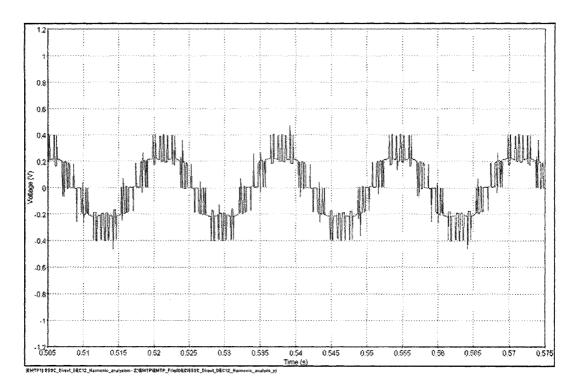

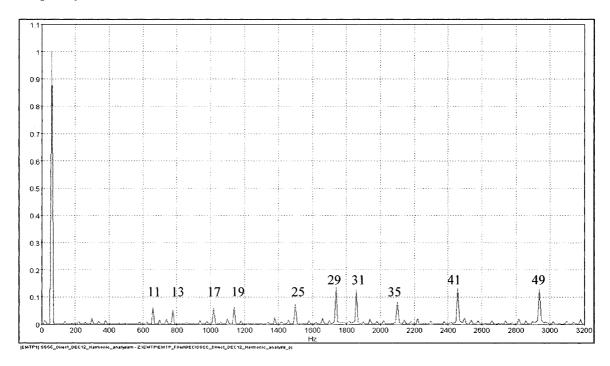

It is important to keep the harmonics on the AC side of the converter at an acceptable level. In a practical scheme, either 4 or 8 multiple converters with a transformer arrangement are used to reduce the generated harmonics, and produce a very high quality sinusoidal output waveform with 24 or 48 steps. Therefore, in these cases, no output filter will be required [34]. A high power PWM converter generates high order harmonics on the AC side of the converters because of finite and limited switching frequency. Figure 2-9 shows the harmonic spectrum of the designed 3-level NPC VSC. A low-pass filter is, therefore, applied to keep the harmonics at an acceptable level.

### • Total Harmonic Distortion (THD)

The AC voltage generated by PWM is given by:

$$V(t) = \sum_{i}^{\infty} V_{i} Sin(2\pi f_{i}t + \phi_{i})$$

(2-14)

If the ratio of the switching frequency over fundamental frequency is very high, the current harmonics are independent of the load, and only depend on the switching frequency  $f_s$ , DC-link voltage, the modulation index  $m_a$ , and number of levels. Figure 2-9 shows the harmonic spectrum of the designed 3-level NPC VSC with 900 Hz switching frequency.

Figure 2-9: Harmonic spectrum of 3-level NPC VSC

The performance of the switching converter topologies can be evaluated by Total Harmonic Distortion (THD) of the voltage and current at the output of the converter. The THD factor indicates how closely the PWM generated voltage resembles the reference sinusoidal waveform with fundamental frequency. THD is defined as:

Chapter 2 Voltage Source Converter (VSC) and FACTS topologies

$$THD = \sqrt{\frac{\sum_{n=2}^{\infty} V_n^2}{V_1^2}} \tag{2-15}$$

Where  $V_n$  is the RMS value of the harmonic n, and  $V_1$  is the RMS value of the fundamental voltage. Note that THD is independent of the frequency.

#### • Weighted Total Harmonic Distortion (WTHD)

Weighted Total Harmonic Distortion (WTHD) is another indicator to evaluate the converter's performances. Like THD, WTHD is based on the sum of the squared harmonics over fundamental frequency component; in addition, the order of the harmonics is considered.

$$WTHD = \sqrt{\frac{\sum_{n=2}^{\infty} (V_n / i)^2}{V_1^2}}$$

(2-16)

In [37], an analytical approach is presented to determine THD and WTHD for multi-level PWM converters. The following equations are obtained for a 3-level PWM converter:

$$THD = \sqrt{\frac{1}{m} \left(\frac{4}{\pi} - m\right)} \tag{2-17}$$

$$WTHD = \sqrt{\frac{2}{m^2} \left(\frac{f_1}{f_s}\right) \frac{\pi}{3} \left[\frac{m^2}{2} - \frac{8m^3}{3\pi} + \frac{3m^4}{8}\right]}$$

(2-18)

Where *m* is the modulation index of the PWM converter.

#### • Low Pass Filter design

PWM harmonics are defined in [37] for 3-level PWM converters. The harmonics are:

Chapter 2 Voltage Source Converter (VSC) and FACTS topologies

$nm_f \pm k$

where

$$\begin{cases} n = 1,3,... & \text{and } k = 0,2,4,... \\ n = 0,2,4,... & \text{and } k = 1,3,... \end{cases}$$

For 900 Hz switching frequency,  $m_f$ =15 and consequently the first set of harmonics are: 15, 15±2, 15±4 ...

In [35], the low-pass filter design for a 3-level PWM converter is defined. The filter performance is determined by its resonant frequency. The best filter performance is reached when the resonant frequency of the filter is well below the lower harmonic frequency caused by the PWM, and much higher than the fundamental frequency. Since, in high power PWM converters, switching frequency is limited around 1kHz, so the filter resonant frequency must be chosen between 60 Hz and 1 KHz. The resonant frequency of the filter is defined based on the pulse frequency of the converter. The following equation is used in [35] to select an appropriate low-pass filter for a 3-level high power PWM converter:

$$f_r = 0.8 * \left(\frac{f_p}{2}\right) \tag{2-19}$$

where  $f_r$  is the resonant frequency, and  $f_p$  is the pulse frequency.

The pulse frequency in a 3-level PWM is twice the switching frequency. Therefore, for a 900Hz 3-level PWM converter, the resonant frequency will be  $f_r = 720$ . From knowledge of the resonant frequency, the L and C values of the low-pass filter can be determined by:

$$\omega_r = \frac{1}{\sqrt{L_f C_f}} \tag{2-20}$$

There are several choices for selecting  $L_f$  and  $C_f$ , but it should be noted that the capacitor is usually the cheaper device. Sufficiently high value for the inductor must be selected in the order to limit the current that the converter carries to charge the filter capacitors. Figure 2-10 shows the harmonic spectrum of the VSC output voltage after filtering.

Figure 2-10: Harmonic spectrum of 3-level NPC VSC output voltage after filtering

#### 2.8 Reference Wave Generator

The transmission line voltages and currents can be severely distorted by harmonics, and unbalance in the system. Therefore, one of the major concerns in controller design is providing an appropriate reference signal from the transmission system to synchronize the controller. A Reference Wave Generator (RWG) is used to extract the fundamental

waveforms from the distorted line voltages or currents, and generates the reference waveform. The designed RWG is based on [36]. This method when compared to the conventional phase-looked-loop (PLL) [42] has very fast response to any distortion and is almost without any transient delay.

Figure 2-11: Block diagram of Reference Wave Generator (RWG) [36]

The 3-phase transmission line currents ( $i_a$ ,  $i_b$ , and  $i_c$ ) are used as the reference signals by the controller to generate either leading or lagging voltages by 90 degrees. Figure 2-11 shows the block diagram of the RWG. The 3-phase transmission line currents are transformed into positive, negative and zero sequence components (a-b-c coordinates to  $\alpha$ - $\beta$ -0 coordinates), as indicated in the following equation:

$$\begin{bmatrix} i_0 \\ i_{\alpha} \\ i_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \\ 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$$

(2-21)

While the 3-phase currents are sinusoidal and balanced,  $i_{\alpha}$  and  $i_{\beta}$  become sinusoidal and orthogonal, and the zero sequence become equal to zero. In case of any distortions or

harmonics,  $i_{\alpha}$  and  $i_{\beta}$  sinusoidal waveforms and 90 degrees phase angle will be changed. In order to keep  $i_{\alpha}$  and  $i_{\beta}$  waveforms sinusoidal and perpendicular, a normalizing block and band-pass filter is applied.

The normalizing and wave-shaping block must be iterated several times to obtain a set of two sinusoidal waveforms with a 90 degrees phase shift. Hence, a time delay occurs that depends on the number of iterations and time step of the simulation. The time delay can be calculated as:

$$\phi_{Delay} = nt_s(2\pi f) \tag{2-22}$$

where n is the number of iteration and  $t_s$  is the time step, and f is the utility frequency.

The time delay caused by iteration is compensated by using the following equation:

$$\begin{bmatrix} V_{caref} \\ V_{\beta ref} \end{bmatrix} = \begin{bmatrix} \cos \phi_{Delay} & -\sin \phi_{Delay} \\ \sin \phi_{Delay} & \cos \phi_{Delay} \end{bmatrix} \begin{bmatrix} V'_{\alpha} \\ V_{\beta} \end{bmatrix}$$

(2-23)

The generated reference waveform has a unit value. Figure 2-12 shows a comparison between a conventional PLL and RWG. The graph demonstrates the angle between the input and output of the PLL and RWG. RWG has almost no oscillations with a very fast settling time.

Figure 2-12: Comparison of a conventional PLL and RWG

# 2.9 VSC topologies

VSCs can be connected in series, parallel or a combination of them into the transmission lines. They can be used for power flow control in a single as well as multiple transmission lines. STATCOM and SSSC are the most commonly used topologies in converter-based FACTS controllers; other less popular topologies include UPFC, IPFC and GUPFC.

#### **2.9.1 STATCOM**

A Static Synchronous Compensator (STATCOM) is a shunt connected power converter that exchanges reactive power with the transmission line. The capability of the STATCOM is analogous to a rotating synchronous compensator, and can be used for dynamic compensation of power systems, increasing transient stability and providing voltage support. The IEEE definition of the STATCOM is[10]:

**Static Synchronous Compensator (SSC or STATCOM):** "A static synchronous generator operated as a shunt-connected static var compensator whose capacitive or inductive output current can be controlled independent of the AC system voltage."

The schematic diagram of a STATCOM is shown in Figure 2-13. The DC voltage  $V_{dc}$  is converted to a set of 3-phase AC voltages with controllable amplitude and phase angle. By regulating the output voltage amplitude into the transmission line the reactive power exchange can be controlled. The phase angle between injected voltage  $V_{inj}$  and bus voltage  $V_{T}$  is controlled in order to regulate the active power exchange with the transmission line. If the converter's losses are neglected, the injected voltage and bus

voltage are in phase, and the STATCOM output current is in quadrature with the bus voltage. Hence, the STATCOM output current can be found by the following equation:

$$\left|I_{inj}\right| = \frac{V_{inj} - V_T}{X_{Stateom}} \tag{2-24}$$

Figure 2-13: Diagram of STATCOM

If the magnitude of  $V_{inj} > V_T$ , the STATCOM operates in capacitive mode and supplies reactive power to the transmission line, and if  $V_{inj} < V_T$ , the STATCOM operates in inductive mode and absorbs reactive power from the transmission line.

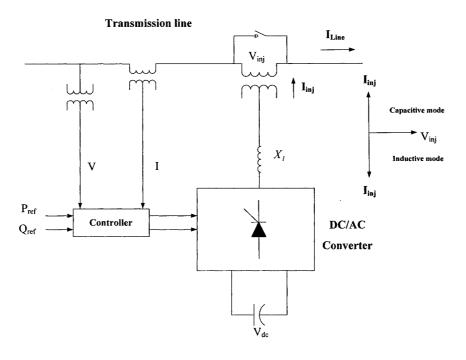

#### 2.9.2 SSSC

A Static Synchronous Series Compensator (SSSC) is a power converter connected in series with the transmission line and it injects a voltage in quadrature with the line current to emulate a series capacitive or inductive reactance into the transmission line. A SSSC

equipped with energy storage system and/or absorbing devices is also able to exchange real power with the power system.

Figure 2-14: Diagram of SSSC

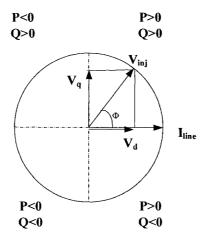

The diagram of SSSC is shown in Figure 2-14. Similar to a STATCOM, reactive power exchange is controlled by the magnitude of the injected voltage to the transmission line, and angle control is used to regulate the active power exchange. The inductive or capacitive mode of operation is set by the injected voltage phase angle with respect to the transmission line current. When injected voltage is leading the line current, reactive power is absorbed and SSSC operates in inductive mode. In capacitive mode, injected voltage is lagging the line current and injects reactive power to the transmission line.

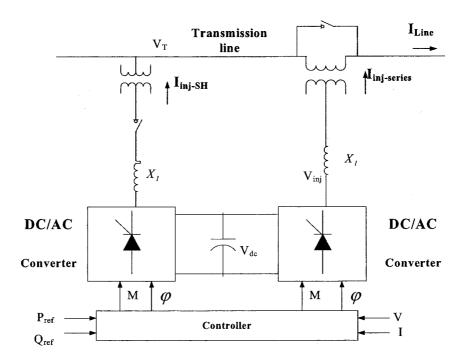

#### 2.9.3 **UPFC**

A Unified Power Flow Controller (UPFC) consists of a SSSC and a STATCOM connected together in a back-to-back arrangement through their DC-link. Figure 2-15

shows the block diagram of an UPFC. The UPFC is capable of exchanging reactive power with the power system through both series and shunt connections. In addition it is able to exchange active power through the DC-link.

Figure 2-15: Schematic of UPFC

The shunt connection is used to maintain a constant voltage on the DC- link while regulating the active power in the series connection. However, the shunt connection is only used to exchange reactive power with the transmission line.

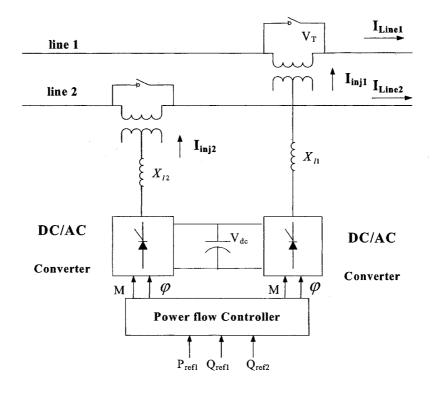

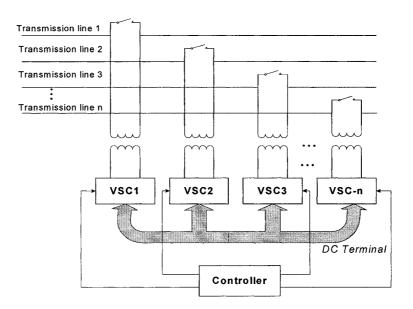

#### 2.9.4 IPFC

An Interline Power Flow Controller (IPFC) consists of two or more SSSCs that share a common DC-link, and are used to control power flows of multi-lines or a sub-network. Each SSSC has the capability of exchanging reactive power with the transmission lines. Furthermore, active power can also be transferred through the DC-link between SSSCs.

However, the active power that is injected by one SSSC to the transmission line must be equal to the active power taken away from the other transmission lines (neglecting the losses).

Figure 2-16: Schematic of IPFC

An IPFC with a multi-converter configuration is shown in Figure 2-16. IPFC can be used to equalize active and reactive power between transmission lines, and transfer power from overloaded lines to lines that are under-loaded. One series branch has one degree of freedom but the remaining branches have two degrees of freedom and provide both active and reactive compensation.

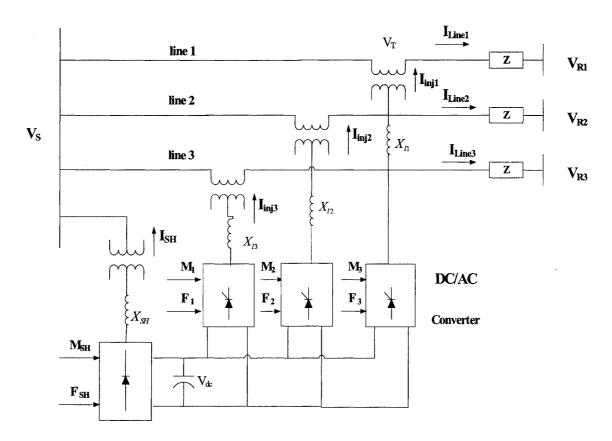

#### **2.9.5 GUPFC**

A Generalized Unified Power Flow Controller (GUPFC) is composed of a shunt power converter and several series converters with a common DC-link. Similar to IPFC, a GUPFC can be used to control power flow of several transmission lines.

Figure 2-17: Schematic of GUPFC

The series converters control active and reactive power flow in the transmission lines, and the shunt converter (with one degree of freedom) supports the real power requirement of the series converters via the common DC-link. A GUPFC is shown in Figure 2-17.

# 2.10 Summary

This chapter has discussed the fundamental of 3-phase VSC that is used as the basic building block for SSSC and IPFC in the next chapters. The mathematical model of VSC is presented; and the operation principle of a 3-level NPC VSC is explained.

The design of snubber circuits and passive component in the VSC is discussed. The guidelines for designing DC capacitors and the AC side filter for the VSC are presented.

A fast synchronizing method for generating reference waveforms are explained. All possible topologies for converter based FACTS applications are presented.

# **Chapter 3**

# Modeling and Controller Design of Static Synchronous Series Compensator (SSSC)

#### 3.1 Introduction

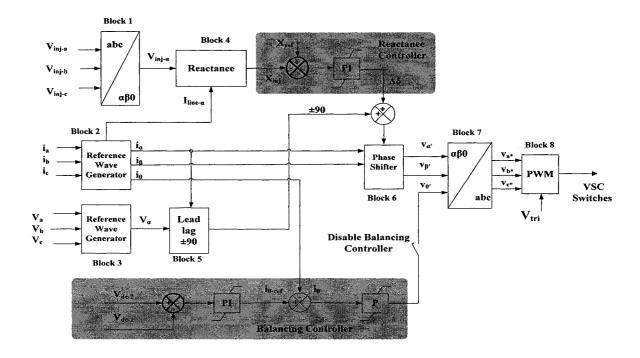

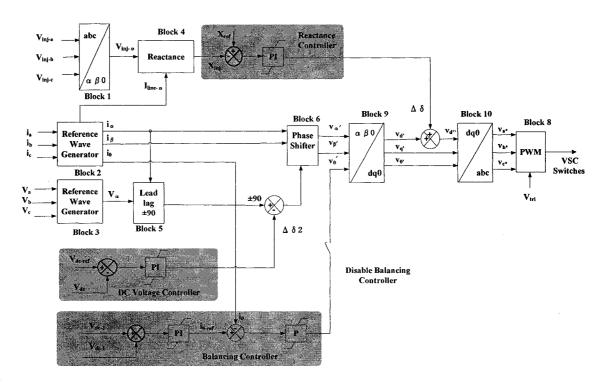

This chapter presents the operation and control strategies of the SSSC. For this purpose, a dynamic model is developed by linearizing equations at fundamental frequency. Both direct and indirect controllers of SSSC are proposed. The accuracy of the mathematical model is verified by the results obtained from time-domain simulations with EMTP-RV.

#### 3.2 Power circuit of the SSSC

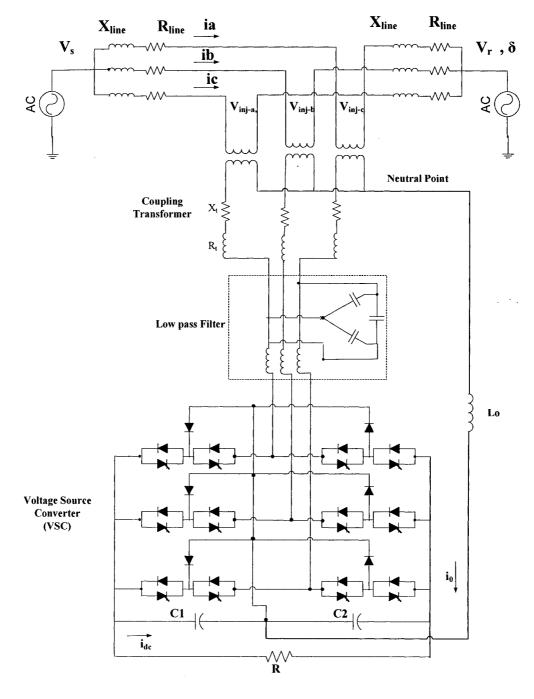

A Static Synchronous Series Compensator (SSSC) consists of a VSC connected in series with the transmission line through a coupling transformer. The VSC generates a set of 3-phase voltages with controllable magnitude and phase angle at the desired frequency; thus, a SSSC is analogous to a synchronous sinusoidal voltage source. A detailed 3-phase diagram of the SSSC is given in Figure 3-1. Where  $V_s$  and  $V_r$  are voltages at the sending-end and receiving-end of the transmission line, and  $R_{line}$  and  $X_{line}$  are transmission line resistance and reactance respectively. The phase angle between  $V_s$  and  $V_r$  is  $\delta$ . The coupling transformer primary windings are star-connected and the secondary windings are connected in series with each phase of the transmission line. The

turn's ratio of the coupling transformer is 1:1.  $R_t$  and  $X_t$  are the internal resistance and leakage inductance of the coupling transformer.  $V_{inj-a}$ ,  $V_{inj-b}$ , and  $V_{inj-c}$  are output voltages of VSC that are injected in series into the transmission line. The transmission line currents are  $i_a$ ,  $i_b$ ,  $i_c$ . The voltage across the DC-link of VSC is  $V_{dc}$ .

Figure 3-1: SSSC power circuit

# 3.3 Operating principle of the SSSC