# Low power design of Motion Compensation Module for MPEG-4 Video Transcoder in DCT-domain

Wan Hoi Cheung

A Thesis

In

The Department

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science (Electrical) at

Concordia University

Montreal, Quebec, Canada

August 2006

© Wan Hoi Cheung, 2006

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-20740-6 Our file Notre référence ISBN: 978-0-494-20740-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

# Low power design of Motion Compensation Module for MPEG-4 Video Transcoder in DCT-domain

#### Wan Hoi Cheung

For the 21<sup>st</sup> century, the Internet has matured into the de facto data transport platform that analog media such as videotape, film, and broadcast will be supplanted by a digital media infrastructure. This digital infrastructure will allow data to be transferred between any two computing machines on the planet in a heterogeneous network environment. In the case where data is transmitted from the SONET network to PSTN network, dynamic bit-rate adaptation/reduction at the gateways is then required due to the transmission media has a lower capacity than the capacity required by the bitstream. There are many different approaches to this problem of bit rate conversion. A robust scheme is to implement a transcoder module to perform dynamic adjustments of bit rate of the coded video bitstream to the desired transmission rate.

The emphasis in this thesis is on the study of the transcoder's Motion Compensation module of MPEG-4 compressed video stream in the DCT domain on both algorithmic and implementation level.

For the algorithmic level of Motion Compensation in DCT-domain (MC-DCT) design, the 3-2-1 partial information scheme is integrated into the DCT Coefficient Translation and Truncation Transformation Matrix (DCTTTM)-based algorithm with two bit precision on the element of DCT-Constant Matrix (DCT-CM) to process the MC-DCT operation.

For the VHDL hardware-level design, data-dependent signal processing has been applied to the MC-DCT module to reduce power consumption via various manoeuvres such as zero bypassing, custom handling of internal bandwidth, the implementation of multiplication-free module, the 3-2 Wallace tree propagation-delay-free addition map and the logic-based addition module.

**Keywords:** MPEG-4, Motion Compensation, transcoder, drift error correction, discrete cosine transform (DCT) domain, requantization, data-dependent logic, low power.

### Acknowledgements

The work presented in this thesis would not have been possible without the continuous help and substantial guidelines from my supervisors Dr. Asim J. Al-Khalili and Dr. William E. Lynch. I am so glad finally to be afforded this opportunity to express my deepest gratitude and appreciation toward them, for their patience and exceptional assistance all these "years" during my master study, I mean, second to none. I would also like to thank Mr. Cheung-Yu Pai and Mr. Chen HongQuan for all their "giga-byte" help on, if not 24/7, would be 12/5 basis.

Thanks to National Sciences and Engineering Research Council of Canada (NSERC) and MRC Networks for the sponsorship of the Industrial Post-Graduate Scholarship (IPS) to financial support my work.

Thanks to my mentor Michel Lortie who helps me to mob up all the grammatical errors inherently embedded deep down in the thesis. An extremely talent guy who has been guiding me through all the predicaments at work, indeed, a "lovely" fellow you may only got one chance to meet...

Finally, I would love to dedicate this work to my family for their love and support.

Thanks!!!

## **Table of Contents**

| List of Figures                                                                | ix |

|--------------------------------------------------------------------------------|----|

| List of Tables                                                                 | X  |

| List of Acronyms                                                               | xi |

| 1. Introduction                                                                | 1  |

| 1.1. Research Motivation                                                       | 1  |

| 1.2. Figures of Merit                                                          | 3  |

| 1.3. Thesis Organization                                                       | 4  |

| 2. An Overview of Video Transcoder Architecture an Compressed Video Bitstreams |    |

| 2.1. Open-Loop Transcoder                                                      | 6  |

| 2.2. Cascaded Pixel Domain Transcoder (CPDT)                                   | 8  |

| 2.3. Fast Pixel Domain Transcoder (FPDT)                                       | 9  |

| 2.4. DCT Domain Transcoder (DDT)                                               | 12 |

| 2.5. Transcoding of MPEG-4 Bitstreams                                          | 13 |

| 2.4. Chapter Summary                                                           | 14 |

| 3 | . Algorithmic Design Choices for MC-DCT Module15                                 |

|---|----------------------------------------------------------------------------------|

|   | 3.1. DCT-Domain Motion Compensation15                                            |

|   | 3.2. Chang and Messerschmitt's algorithm20                                       |

|   | 3.3. DCTTTM-based Motion Compensation25                                          |

|   | 3.4. Analysis of computational complexity for DCTTTM-based MC-DCT using          |

|   | partial DCT information31                                                        |

|   | 3.5. Simulation study on the impact of difference schemes of partial information |

|   | used to video quality35                                                          |

|   | 3.6. Quantization over Constant Transformed Coefficients                         |

|   | 3.6.1 Design of Quantizer for the elements of DCT-CMs38                          |

|   | 3.7. Simulation Results of PSNR performance for DCTTTM-based MC-DCT with         |

|   | n-bit precision after binary point40                                             |

|   | 3.8. Chapter Summary44                                                           |

|   |                                                                                  |

| 4 | . Implementation of MC-DCT Module45                                              |

|   | 4.1. Block Diagram of MC-DCT module                                              |

|   | 4.2. Customized Component for Low Power MC-DCT Design51                          |

|   | 4.2.1. Encoded DCT-CM Storage Unit                                               |

|   | 4.2.2. Logic Multiplication Unit (LMU)53                                         |

|   | 4.2.3. Logic Addition Unit (LAU)62                                               |

|   | 4.3. Synthesis Result of MC-DCT Components                                       |

|   | 4.4. Chapter Summary68                                                           |

| 5. Conclusion and Future Work                               | 69 |

|-------------------------------------------------------------|----|

| 5.1. Conclusion                                             | 69 |

| 5.2. Possible Improvement for Future Research               | 71 |

| References                                                  | 72 |

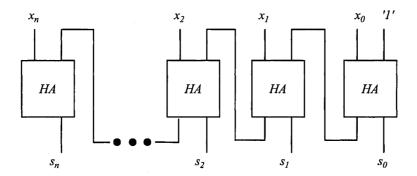

| Appendix A Implementation of Incrementor using (CLA) scheme | •  |

# **List of Figure**

| Figure 1.1  | A scenario where the transcoder is deployed between two heterogeneous networks                                                                                                                                                                                                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1  | Transcoder structure with no drift-error correction6                                                                                                                                                                                                                                 |

| Figure 2.2  | Cascaded quantization provides the same result as direct quantization                                                                                                                                                                                                                |

| Figure 2.3  | Cascaded quantization induces extra distortion                                                                                                                                                                                                                                       |

| Figure 2.4  | Cascade of decoder and encoder as a transcoder8                                                                                                                                                                                                                                      |

| Figure 2.5  | Fast Pixel-Domain Transcoder (FPDT)11                                                                                                                                                                                                                                                |

| Figure 2.6  | DCT-Domain Transcoder (DDT)12                                                                                                                                                                                                                                                        |

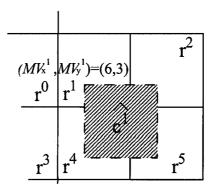

| Figure 3.1  | Estimated current frame in (c) is motion-compensated from reference frame in (b). Notice that the estimated current MBs are likely mapped to reference frame in a non-block boundary fashion                                                                                         |

| Figure 3.2  | Graphical interpretation of Equation (3.2) above where $\widehat{c^1}$ straddles four adjacent MBs $r^1$ , $r^2$ , $r^4$ , $r^5$ in the reference frame                                                                                                                              |

| Figure 3.3a | a In general, estimated MB is unlikely to be mapped into fixed block boundary position                                                                                                                                                                                               |

| Figure 3.31 | b MB is made up of at most four neighbouring MB n reference frame                                                                                                                                                                                                                    |

| Figure 3.4  | Using matrix multiplication to $r^1_{LR}$ and translate it to upper right corner                                                                                                                                                                                                     |

|             | Partial DCT-REs information. • refer to the locations of an 8 x 8 DCT Requantization Error Block (DCT-REB) where values are taken into account for the computation of motion compensation and assumed to be non-zero. Non-marked locations are ignored and assumed to be zero-valued |

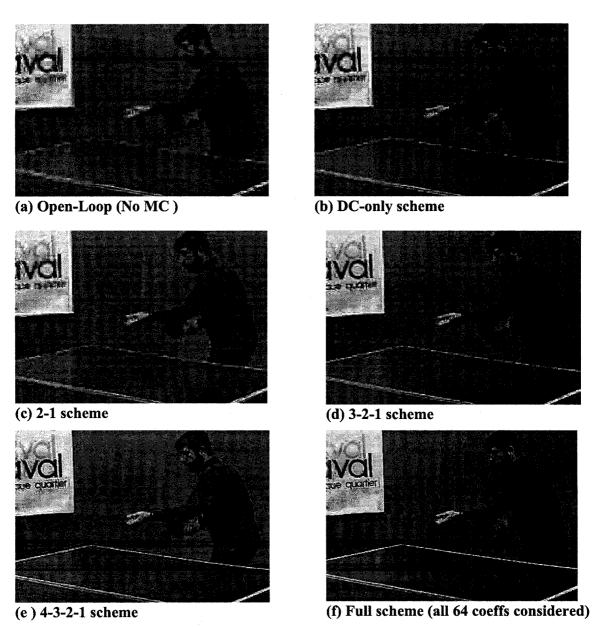

| Figure 3.6  | (a)-(e): the 61 <sup>th</sup> motion-compensated frame of video sequence Table Tennis using different partial information scheme                                                                                                                                                     |

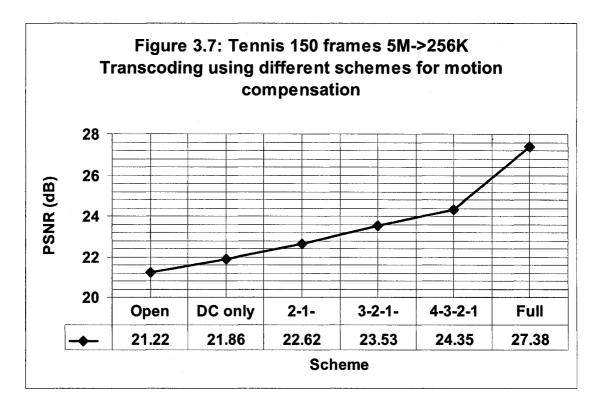

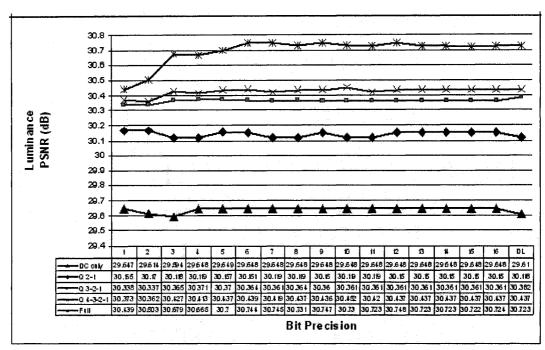

| Figure 3.7  | Average PSNR for Tennis 150 frames Transcoding using different schemes for motion compensation                                                                                                                                                                                       |

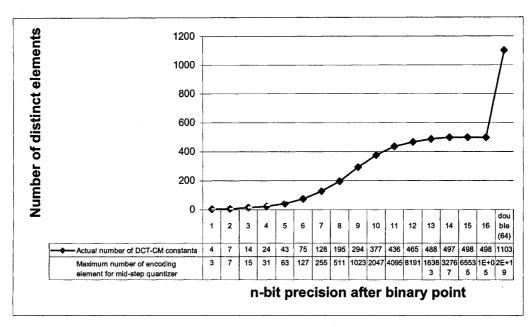

| Figure 3.8 The relation between the number of bit-precision (after binary point) used and the number of resulted distinct quantized DCT-CM Elements40 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

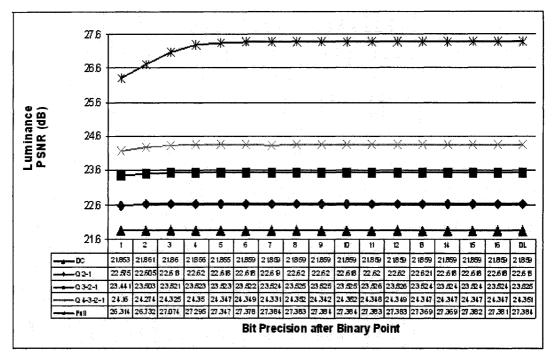

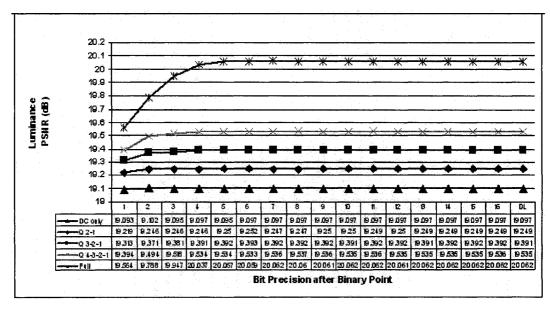

| Figure 3.9 PSNR measure on transcoding Table Tennis using different partial information schemes for motion compensation                               |

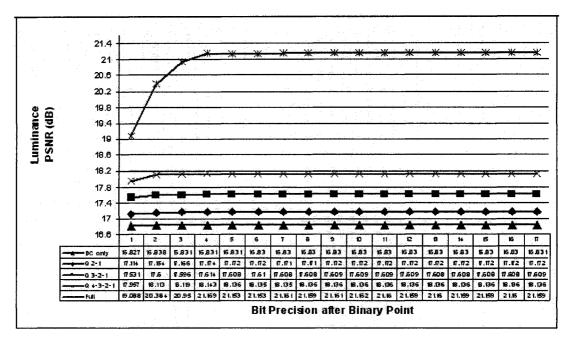

| Figure 3.10 PSNR measure on transcoding Flower-garden using different partial information schemes for motion compensation                             |

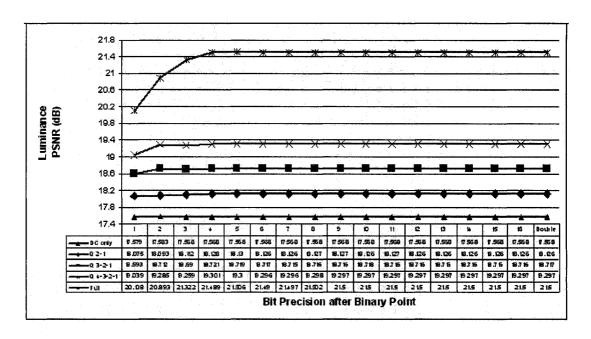

| Figure 3.11 PSNR measure on transcoding Football using different partial information schemes for motion compensation                                  |

| Figure 3.12 PSNR measure on transcoding Miss American using different partial information schemes for motion compensation                             |

| Figure 3.13 PSNR measure on transcoding Mobile using different partial information schemes for motion compensation                                    |

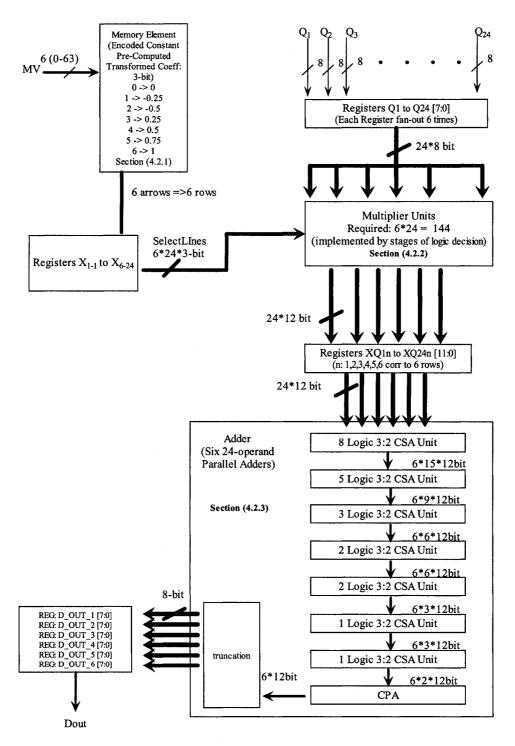

| Figure 4.1 Overall architecture of MC-DCT                                                                                                             |

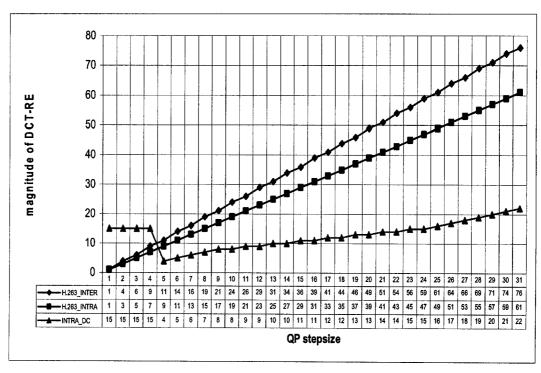

| Figure 4.2 Max DCT- ReQuantization Error vs StepSize QP for H.263 Quantization Scheme                                                                 |

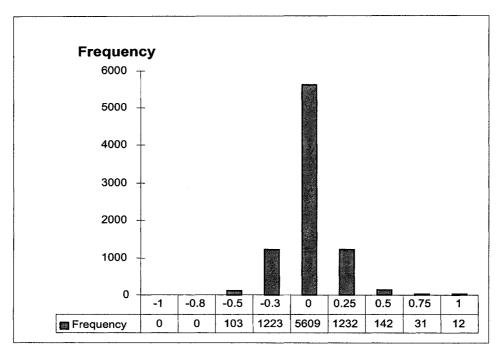

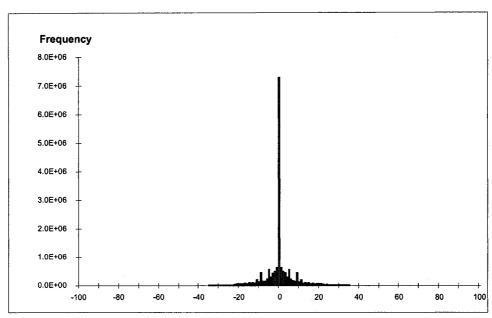

| Figure 4.3 Histogram of DCT-CM's Constant54                                                                                                           |

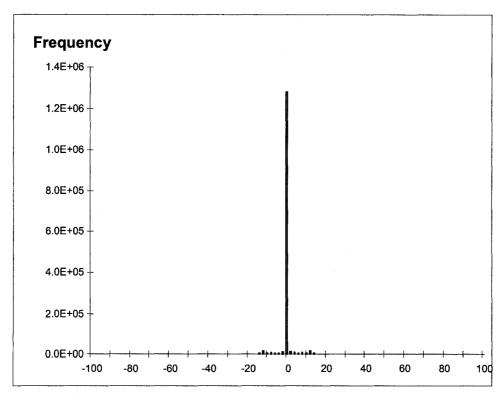

| Figure 4.4 Histogram of Intra DCT-RE's for video Table Tennis                                                                                         |

| Figure 4.5 Histogram of Inter DCT-RE's for video Table Tennis                                                                                         |

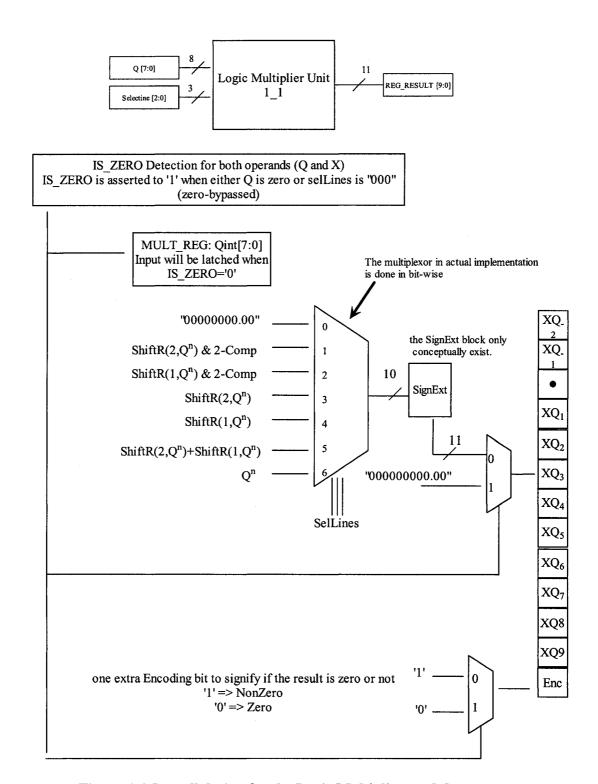

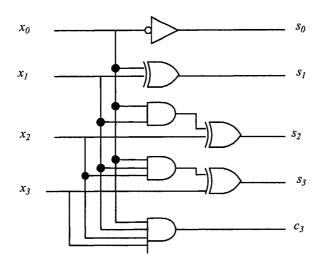

| Figure 4.6 Overall design for the Logic Multiplier module                                                                                             |

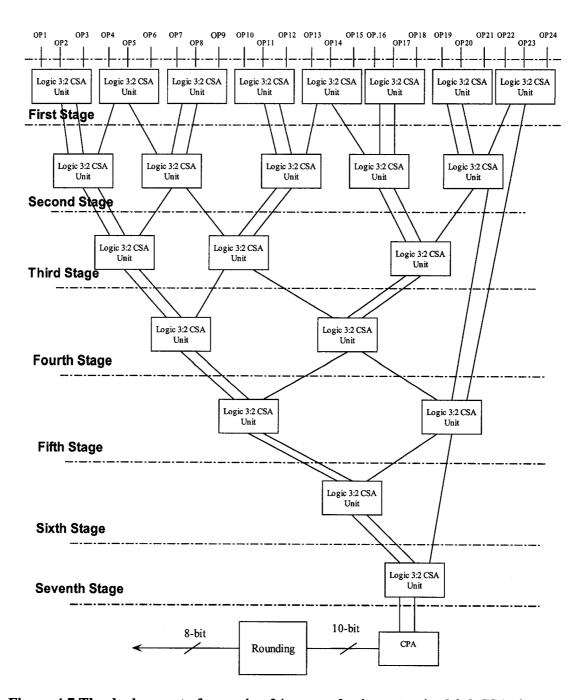

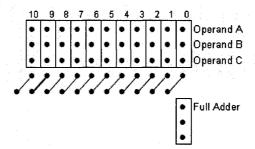

| Figure 4.7 The deployment of summing 24 operands via customized 3:2 CSAs in a carry propagate free manner                                             |

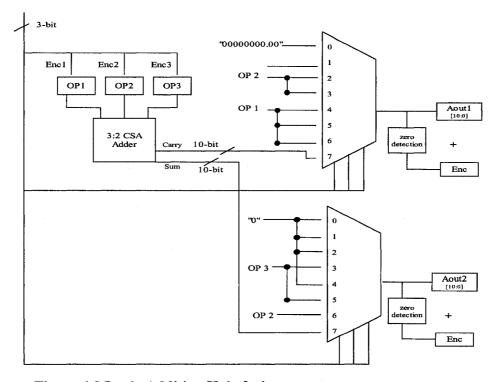

| Figure 4.8 Logic Addition Unit design64                                                                                                               |

| Figure 4.9 dot-diagram of 10-bit 3-2 CSA                                                                                                              |

## **List of Tables**

| Table 3.1 Average Percentage of Non-Zero Coefficient for Table Tennis                              | 32 |

|----------------------------------------------------------------------------------------------------|----|

| Table 3.2 Average Percentage of Non-Zero Coefficient for Flowergarden                              | 32 |

| Table 3.3 Average Percentage of Non-Zero Coefficient for Miss American                             | 32 |

| Table 3.4: Computation cost in term of mult-and-add count for different partial information scheme | 34 |

| Table 3.5 Possible encoding scheme for DCT-CM constants of 2-bit precision with one integer bit    | 39 |

| Table 4.1 Maximum DCT-RE for H.263 scheme                                                          | 50 |

| Table 4.2: Element of DCT-CM (DCT-Constant Matrix) in 2-bit precision after binary point map       | 51 |

| Table 4.3: DCT-CM matrix for MVrow =0 and MVcol = 2                                                | 52 |

| Table 4.4 Percentage of occurrence of the associated values for DCT-CM's constants                 | 55 |

| Table 4.5 Percentage of occurrence of the associated values for DCT-RE's coefficients Intra frame  | 56 |

| Table 4.6 Percentage of occurrence of the associated values for DCT-RE's coefficients Inter frame  | 57 |

| Table 4.7 Operations required to achieve the multiplication for different DCT-CM Multiplicand      | 60 |

| Table 4.8 The function mapping for the two MUX inside the LAU design                               | 65 |

| Table 4.9 Specification and power consumption of MC-DCT design                                     | 67 |

| Table 4.10 Power consumption of MC-DCT module under different operational frequency                | 67 |

### List of Abbreviations and Symbols

ATM Asynchronous Transfer Mode

**CPDT** Cascade Pixel Domain Transcoder

**DCT** Discrete Cosine Transform

**DCT-CM** DCT-Correction Matrix

**DCTTTM** DCT Coefficient Translation and Truncation Transformation Matrix

**DDT** DCT-Domain Transcoder

**DSL** Digital Subscriber Line

**FPDT** Fast Pixel Domain Transcoder

**GOP** Group of Picture

**ISDN** Integrated Service Digital Network

MC Motion Compensation

MoMuSys Mobile Multimedia System

MPEG Moving Picture Experts Group

MSE Mean Squared Error

**POTS** Plain Old Telephone System

**PSNR** Peak Signal to Noise Ratio

**PSTN** Public Switch Telephone Network

**RE** Requantization Error

**SDH** Synchronous Digital Hierarchy

**SONET** Synchronous Optical Networks

VHDL Very High Speed Integrated Circuit (VHSIC) Hardware Description Language

#### Chapter 1

#### Introduction

#### 1.1. RESEARCH MOTIVATION

Visual information is of vital importance if human beings are to perceive, recognize, and understand the surrounding world. As the Internet matures into the de facto data transport platform for the 21st century, it seems clear that analog media such as videotape, film, and broadcast will be supplanted by a digital media infrastructure built on the Internet and Internet-related technologies. In addition, services like teleconferencing, video on demand, distance learning, and remote surveillance for provide a convenient means of acquiring visual information from remote locations. This digital infrastructure will allow visual data to be readily transferred between any two computing machines on the planet, if so desired. However, the speed at which this data can be transmitted will depend on a number of factors, but primarily on the network infrastructure. Most existing networks such as POTS, ISDN, DSL over PSTN, ATM over SONET (Synchronous optical network) or SDH (Synchronous Digital Hierarchy), and 3G Wireless are interconnected resulting in a heterogeneous network environment. On one hand, POTS over PSTN networks planned with copper wires laid down over a century ago and intended for analog voice communications are used with modem technology to transmit data at speeds as high as 56 kb/s. On the other hand, ATM over SONET via optical fiber technology allows data and/or voice transfers at 51.840 Mbit/s and higher. In the case where data is transmitted from the SONET network to PSTN network, dynamic bit-rate adaptation/reduction at the gateways is required since the receiving transmission medium has a lower capacity than the capacity required by the originating bitstream [1].

One solution is to use the scalable coding feature inherent in the MPEG-4 standard where the video is coded at two or more layers, a base layer and one or more enhancement layers. The base layer stores the most critical information while the other enhanced layers supplement the video quality. The enhanced layers maybe skipped (dropped) in the case of changing network environments. This approach is nonetheless not sufficiently flexible to handle finer scaling since the scalability in MPEG-2 provides only a limited number of possible transmission bit rates.

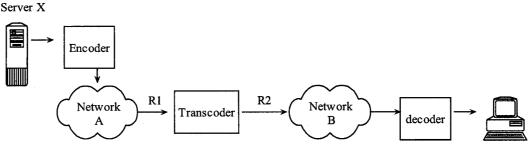

A more robust scheme is to implement a transcoder module to perform dynamic adjustments of the bit rate of the coded video bitstream to match the desired downstream network. This can be done by first partial decoding of the bitstream and then requantizing the DCT coefficients coarsely to achieve bit rate reduction. Figure 1.1 shows a diagram of the transmission of a video stream from a server X to end user Y where a transcoder is deployed at the gateway between two heterogeneous networks. One raw uncompressed video at server X is compressed by an encoder at a bit rate R1. The encoded video is converted to a bit rate R2 < R1 by the transcoder module when the transmission medium has a lower capacity than the bitstream requires. The decoder at the end user Y decompresses the transcoded video bitstream for display.

Figure 1.1 A scenario where the transcoder is deployed between two heterogeneous networks

#### 1.2. FIGURE OF MERIT

The process of converting a compressed high bitrate stream into a lower bitrate stream introduces distortion. Conventionally, the distortion can be measured using one of two schemes; subjective assessment and objective assessment.

Subjective assessment requires human perception and/or opinion about a group of degraded target pictures evaluated based on a predefined scale to determine the quality of the degraded pictures as compared to the original undistorted ones. While the result of this scheme is generally more reliable than any objective assessment, the cost remains prohibitively high and the process is extremely time-consuming as in all man-in-the-coop processes. In this thesis, the formal subjective assessment method is not considered; however, informal subjective evaluation is included in deciding the application of the optimization technique.

Objective measurement provides a much cheaper and time-efficient means of simulating human observer grading via mathematical models. The simplest objective measure and yet the most popular method employed within the video/audio and the signal processing community is known as the peak-to-peak signal-to-noise ratio (PSNR) and defined as:

$$PSNR = 10\log_{10} \frac{255^{2}}{\frac{1}{N} \sum_{i} \sum_{j} (Y_{ref}(i, j) - Y_{rec}(i, j))^{2}}$$

Where  $Y_{ref}(ij)$ , and  $Y_{rec}(ij)$ , are the pixel values of the reference and reconstructed images respectively. N is the total number of pixels in the image. The larger the PSNR logically implies the better the reconstructed image; it is however not necessarily true at all times. A case where image A has lower PSNR than image B with noise spreading all

over might yield a better subjective quality for human perception than an image B with higher PSNR but having noise concentrated within a tiny area which can easily be spotted visually.

In general, the gain of better PSNR for a reconstructed picture requires the expense of computation complexity. In chapter 3, several factors to reduce the computational complexity of the core module in the transcoding process are investigated and analyzed in order to achieve a balance between the saving in computational load and the cost in the objective PSNR measure.

#### 1.3. THESIS ORGANIZATION

The organization of this thesis is as follows: in Chapter 2, an overview of video transcoder architecture and MPEG-4 compressed video bitstream is provided. Chapter 3 reviews the pioneering work for Motion-Compensation in Discrete Cosin Transform (MC-DCT) algorithm by Chang and Messerschmitt's [20] and presents an optimization based on a 3-2-1 partial information scheme. Chapter 4 illustrates the VHDL design to implement the MC-DCT module via Xilinx FPGA technology. Chapter 5 summarizes the proposed schemes and the contribution of this thesis. Future work is also discussed.

#### Chapter 2

#### AN OVERVIEW OF VIDEO TRANSCODER ARCHITECTURE AND MPEG-4

#### COMPRESSED VIDEO BITSTREAMS

Transcoders can be broadly classified into two types, open-loop and closed-loop. The first, open-loop type of transcoder uses a straightforward requantization method without compensating for drift errors. The drift error occurs when the reconstructed pictures used for prediction in the encoder are not the same as the reconstructed pictures in the decoder due to the loss of high frequency data. This error will propagate if the reconstructed picture is to be used as reference for future pictures. In MPEG standard, this error is terminated when the I frame is processed. This type of transcoder demands little hardware, requires no frame buffer and is suitable for low cost and/or low delay application [2][3].

The second type of transcoder is built with a feedback loop to compensate for drift error. This approach provides a higher quality transcoding, but comes at the price of more complexity and greater memory requirements.

In this chapter, we will examine each mainstream transcoder's architecture proposed in the literature, Open-Loop transcoder, Cascade Pixel Domain Transcoder (CPDT), Fast Pixel Domain Transcoder (FPDT) and DCT Domain Transcoder (DDT) in Sections 2.1, 2.2, 2.3, 2.4 respectively [4][5][6][7][8]. Section 2.5 discusses the video signal streams compiled to the Moving Picture Experts Group Compression Standard Version 4 (MPEG-4) under the context of transcoding. In this thesis, the MPEG-4 standard is the video compression scheme used for all the simulations.

#### 2.1. OPEN-LOOP TRANSCODER

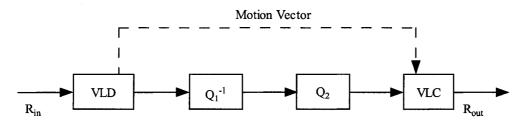

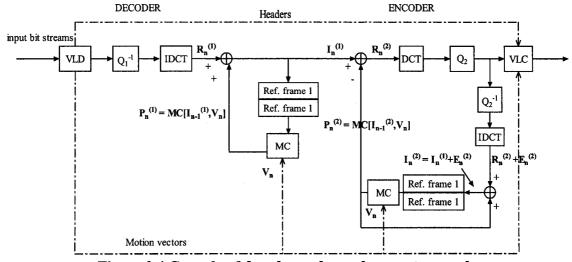

The open-loop transcoder architecture achieves the bit-rate reduction by implementing the requantization process without feedback path for drift correction. Conceptually, the transcoding process with this structure is done by first inversely quantizing the encoded bitstream by mean of the finer quantizer Q1 and then heavily compressing with the coarse quantization Q2 (i.e. the step size for the quantization of Q2 is larger than the step size of Q1) to achieve the lower target bit rate. The basic structure is shown in Figure 2.1:

Figure 2.1 Transcoder structure with no drift-error correction

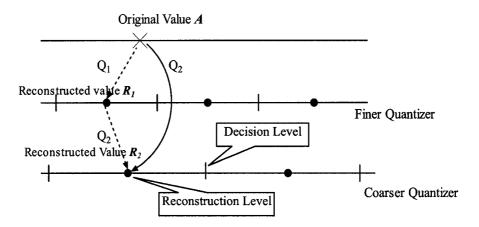

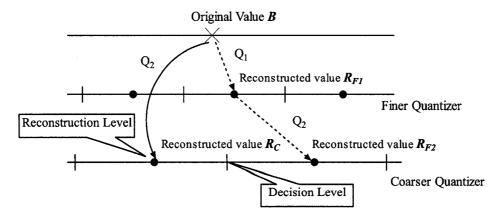

While such arrangements will always lead to increased distortion due to the lossy nature of quantization when the reconstructed values differ from the original ones or when some nonzero coefficients in the input frame become zero after quantization, this simple bit rate-conversion process may introduce an additional error which can be avoided by directly quantizing the DCT coefficients with the same coarser step size. This additional error is called Requantization Error (RE). Figures 2.2 and 2.3 below illustrate the cases where additional requantization error may occur:

Figure 2.2 Cascaded quantization provides the same result as direct quantization

Figure 2.3 Cascaded quantization induces extra distortion

In Figure 2.1, the original value A is first quantized by a finer quantizer Q1, and then heavily quantized with Q2 resulting in the final reconstructed value  $R_I$  (paths indicated by the two dash-line arrows). The same reconstructed  $R_I$  may also be obtained by directly quantizing A by the coarse quantizer Q2 (path indicated by the solid-line arrow). In this case the direct coarse quantization and requantization distortions are equal. However, in Figure 2.3, the reconstructed value  $R_{F2}$  of coefficient B resulted from requantization is different from that of direct coarse quantization. This is caused when the

finer interval is completely contained by the coarse interval, no cascading error is introduced. On the other hand, if the finer interval overlaps the decision level of the coarse interval and if the original value falls into a coarse interval different from that of the interval where the coarse quantizer will resolve the value to, the requantization error subsequently becomes larger. In fact, by carefully selecting the ratio of Q2/Q1 to avoid critical ratios of the cascaded quantizations during the transcoding process, the magnitude of the requantization error could be greatly reduced [9][10][11].

The open-loop transcoder structure is straightforward and requires no frame memory; it is recommended for low delay and low cost application in which minor drift error is considered to be tolerable. It should be noted that having video stream with a small group of pictures (GOP) may considerably reduce the effect of drift error.

#### 2.2. CASCADED PIXEL-DOMAIN TRANSCODER (CPDT)

A simple drift-free transcoder can be produced by first fully decoding the video streams into reconstructed pixels and then re-encoding them to a lower bit rate. The structure can be built with a decoder cascading an encoder as in Figure 2.4:

Figure 2.4 Cascade of decoder and encoder as a transcoder

The structure Figure 2.4 is inherently drift-free due to the complete isolation of the encoder loop from the decoder loop. Assuming the ideal environment of no transmission noise, the reconstructed frame resulting from the decoding section of the transcoder would be identical to the one generated by the front-encoder once motion compensation is applied. Likewise, the reconstructed transcoded frame in the encoding part of the transcoder would be the same generated by the end-decoder. Nonetheless, the direct implementation of the CPDT is not attractive due to high complexity, high cost and long delays. Knowing that the motion compensation is undoubtedly the most computationally expensive process in the CPDT structure, Petro in [12] derived a step-by-step simplification to realize the Fast Pixel-Domain Transcoder which reused the motion vector to reduce the overall computational complexity and hence improve the performance by an order of magnitude.

#### 2.3. FAST PIXEL-DOMAIN TRANSCODER (FPDT)

Referring to Figure 2.4, let  $V_n$  represent the motion vector field of thencurrent picture n, x be the position of a pixel in the picture, and the motion compensated signal  $MC[I_{n-1}^{(1)}, V_n]$  where  $MC[\cdot]$  denotes a simple shift operation (in essence, Motion Compensation (MC) can be understood as a space/time-domain operation to form an estimate of the current frame by extracting the MC block from the location specified by the Motion Vector (MV('s)) in the reference frame(s), refer to the detailed discussion in Chapter 3), n-l stands for the previous frame, superscript (l) indicates the decoding part of the transcoder, and the encoding part of the transcoder is denoted as superscript (l).  $I_{n-1}^{(1)}$

for example is the previous decoded signal from the decoder. Therefore, the current predictive frame can be estimated as

$$P_n^{(1)} = MC[I_{n-1}^{(1)}, V_n] (2.1)$$

Alternatively, it can be expressed per pixel as follows:

$$P_n^{(1)}(x) = MC[I_{n-1}^{(1)}, V_n](x) = I_{n-1}^{(1)}(x + V_n(x))$$

(2.2)

where  $V_n(x)$  is equal to the displacement for each pixel within a Macroblock (In MPEG standard, Macroblock is defined as a composition of four 8 x 8 blocks).

Since the Motion Compensation process is a linear operation, the predictive frame of the encoding part of the transcoder is to be formulated by the following equation:

$$P_n^{(2)} = MC[I_{n-1}^{(1)} + E_{n-1}^{(2)}, V_n] = MC[I_{n-1}^{(1)}, V_n] + MC[E_{n-1}^{(2)}, V_n]$$

(2.3)

where  $E_n^{(2)}$  is the requantization error caused by the second quantizer Q2. Thus the residual  $R_n^{(2)}$  can be written as:

$$R_n^{(2)} = I_n^{(1)} - MC[I_{n-1}^{(1)} + E_{n-1}^{(2)}, V_n]$$

$$= I_n^{(1)} - MC[I_{n-1}^{(1)}, V_n] - MC[E_{n-1}^{(2)}, V_n]$$

(2.4)

And the decoded picture  $I_n^{(1)}$  can be written as:

$$I_n^{(1)} = R_n^{(1)} + MC[I_{n-1}^{(1)}, V_n]$$

(2.5)

Substituting Equation (2.5) into Equation (2.4), we get:

$$R_n^{(2)} = R_n^{(1)} - MC[E_{n-1}^{(2)}, V_n]$$

(2.6)

Equation 2.6 implies that the residual  $R_n^{(2)}$  can be computed directly by subtracting the motion-compensated requantization error  $E_{n-1}^{(2)}$ . Here,  $MC[E_{n-1}^{(2)}, V_n]$  is the so called drift error in the transcoding process. Based on the Equation (2.6), only the previous

requantization errors  $E_{n-1}^{(2)}$  need to be stored in frame memory and the frame storage for  $I_n^{(1)}$  can be discarded. This development leads to a simplified architecture for fast transcoding. Figure 2.5 shows the block diagram of a Fast Pixel-Domain Transcoder (FPDT).

The underlying premise for the simplification to achieve the FPDT architecture makes use of the linearity of the Motion Compensation property such that the requantization\transcoding error can be isolated out for the Motion Compensated operation. The partial decoding methodology of reusing the Motion Vector (MV's) also contributes to simplifying the FPDT architecture since the process of Motion Estimation is no longer required. By doing so, only one reconstruction loop and one DCT/IDCT pair are needed.

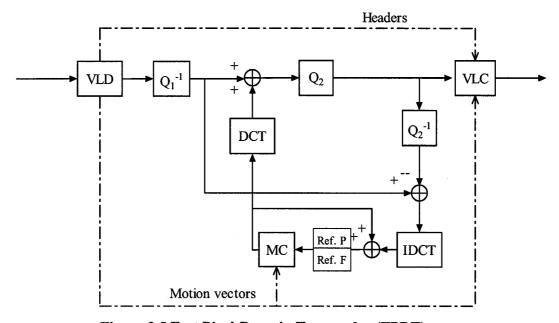

Figure 2.5 Fast Pixel-Domain Transcoder (FPDT)

#### 2.4. DCT-DOMAIN TRANSCODER

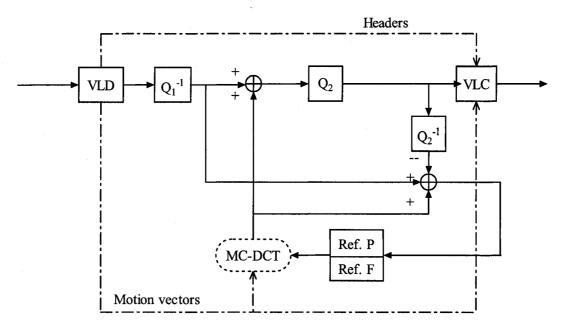

The DCT/IDCT modules would no longer required if the bitstream could be transcoded entirely in the DCT domain. Figure 2.6 shows the architecture of this conceptual design:

Figure 2.6 DCT-Domain Transcoder (DDT)

From Figure 2.6, the transcoding/requantization errors are accumulated in the DCT domain and compensated in the DCT block of the current picture through the module MC-DCT (Motion Compensation in Discrete Cosine Transform domain). In this thesis, the MC-DCT module is to be investigated thoroughly in later chapters. Chapter 3

will discuss in detail a step-by-step deviation for computing motion compensation in DCT-domain.

#### 2.5. TRANSCODING OF MPEG-4 BITSREAMS

A feature of MPEG-4 in contrast to MPEG-2 or MPEG-1 is its content-based coding of images and video to allow the separate decoding and reconstruction of arbitrarily shaped video objects. This thesis only considers rectangular shaped video objects in the simulations, therefore the shape information is not specified and no shape coding was developed. In essence, only the texture content of MPEG-4 compressed video is transcoded.

For MPEG-4 visual bitstream syntax, similarin concept to MPEG-1 and -2, each GOV (Group of Video Object Planes) may include three types of VOPs (Video Object Plane), Intracoded (I-VOP), predictive-coded (P-VOP) and bi-directionally predictive-coded (B-VOP). Since I-VOPs are self-sufficient with no need of prior information, no Motion Compensation is applied. Given our choice of the transcoder architecture in Figure 2.6, the requantization errors (the differences of DCT coefficients between Quantizing parameters Q1 and Q2) are to be stored in the frame memory for compensating the next P- or B-VOP. P-VOP is motion-compensated by using the same Motion Vector computed by the front-encoder and its requantization errors are subsequently saved for motion compensating the next P- or B-VOP. Since there is no referrence for B-VOP, the requantization error was not calculated [13]. For simplicity, only the IPPP...IPPP GOV structure was used for all the simulations in this thesis.

With regard to transcoding of MPEG-4 compressed video bitstreams using a DDT architecture, motion vectors of the input bitstream are reused to avoid the most computationally intensive operation, motion estimation, of the MPEG-4 encoding algorithm.

#### 2.6. CHAPTER SUMMARY

In this chapter, an overview of video transcoder architectures was presented. Two types of transcoders with different complexity and memory requirements were discussed. The transcoder with no drift correction has a lower complexity and requires no frame buffers. The more complex transcoder is structured with a closed loop to perform drift compensation. A drift-free CPDT transcoder can be designed by cascading a decoder to an encoder. While the CPDT design requires no special customization, this structure suffers from long delay and high complexity. A more versatile DDT design was addressed conceptually where DCT/IDCT modules are removed from the CPDT design to gain substantial reduction in the architectural complexity. The chapter also discussed the properties of MPEG-4 video stream used in the simulations completed as part of the thesis.

#### Chapter 3

#### ALGORITHMIC DESIGN CHOICES FOR MC-DCT MODULE

In Chapter 2, the fast DCT-domain transcoder architecture was introduced by removing the Inverse DCT and the DCT modules. The underlying premise is that Motion Compensation (MC) can be done in the DCT-domain which would allow this simplified architecture to be implemented without hampering the transcoder's correct functionality. In this chapter, the problem of MC in the DCT-domain (MC-DCT) is dealt with in full detail.

The practice of manipulating video signals in the compressed/transform domain originated over a decade ago [14][15][16][17][18][19]. With video compression systems incorporating Motion Compensation (MC) such as MPEG, the major challenge in providing common video editing functions in the compressed domain, including overlap, translation, scaling, linear filtering, rotation, and pixel multiplication etc, is the development of a fast algorithm. MC-DCT reconstructs the video in the compressed domain by Inverse Motion Composition without requiring conversion back to the time/spatial domain. In [14], it has been shown that compositing the DCT-compressed images directly in the DCT domain can save computations for many of the compositing operations mentioned above compared to the straightforward spatial-domain approach which composites images pixel by pixel.

Several fast MC-DCT algorithms based on Chang and Messerschmitt's [20] have been proposed in the literature [21][22]. In [21], Neri use a factorization of computing 8-point DCT to achieve 32% computational complexity savings compared to a spatial domain approach, while 81% reduction of complexity was realized in [22] by

approximating the translated matrices to binary numbers with maximum distortion of 1/32 to allow the execution of basic operations such as shift-right and add. In [23], Bovik approached the problem by analyzing the statistical properties of natural video data to avoid processing those DCT coefficients outside the estimated local bandwidth to gain 25%~55% computational improvement over the method proposed in [20]. They also present a Look Up Table (LUT)-based implementation scheme to obtain another 31%~48% improvements in computational complexity. Based on the fact that motion compensation in MPEG is done on a macroblock basis, Song and Yeo [24] exploit the shared information in the predictions of multiple neighboring blocks to speed up the MC-DCT algorithm. Song and Yeo show that their method can be implemented on top of the already fast algorithm proposed in [21] and [22], and provide incrementally about 19% and 13.5% above these techniques respectively..

In Section 3.1, the operation of Motion Compensation in the spatial domain is reviewed. The inherent obstacle to performing motion compensation in the frequency (DCT) domain is then examined. One of the MC-DCT algorithms reported in the literature, Chang and Messerschmitt's algorithm [20], is presented in Section 3.2. Section 3.3 introduces the DCT-Coefficient-Translation-and-Truncation-Transformation-Matrix based (DCTTTM) MC-DCT algorithm [25] which addressed the MC-DCT problem from a different perspective.

The computational complexity of DCTTTM-based MC-DCT algorithm can be dramatically reduced by considering only partial DCT information and quantizing the constant transformed matrices to finite precision. Section 3.5 studies the impact of applying these two maneuvers to the quality of five video test sequences.

#### 3.1. DCT-Domain Motion Compensation

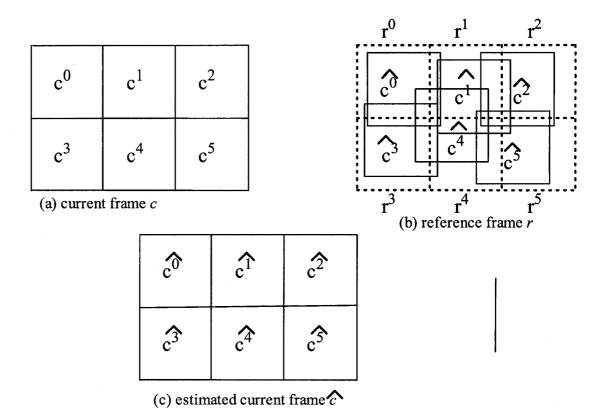

Motion Compensation (MC) can be understood as a space/time-domain operation to form an estimate of the current frame by extracting a MC block from the location specified by Motion Vector (MV('s)) in the reference frame(s). In general, neither the vertical nor the horizontal component of the MV is an integer multiple of the block size; hence, it is likely that a MC block extracted from a reference frame straddles four adjacent DCT blocks in the reference frame.

For Block Motion Compensation, the frames are partitioned into blocks of pixels in the spatial domain (e.g. macroblocks of  $16 \times 16$  pixels). Each block is predicted from a block of equal size in the reference frame. These will be called Motion Blocks (MBs) with their size  $(p = 8) \times (q = 8)$  where p is the number of rows and q is the number of columns. The blocks are not altered in any way other than being shifted to the position of the predicted block. This shift is represented by a motion vector.

Let c be the current frame, r be the reference frame,  $\hat{c}$  be the estimated current frame. When a superscript is attached to these symbols it represents one MB. Thus  $r^5$  represents the fifth MB in the reference frame. V is the vector field made up of all of the MVs for one frame. For MB k, its MV has horizontal and vertical components  $MV_{row}^{\phantom{row}k}$  and  $MV_{col}^{\phantom{row}k}$  respectively. The MVs are the result of the Motion Estimation. The position of a pixel in a frame is denoted by x and y. For example, assuming we a frame size of  $(m=16)\times(n=24)$  where m is the number of rows and n is the number of columns, then, the current frame c, the estimated current frame  $\hat{c}$ , and the reference frame r can be partitioned into  $(16\times24)/(8\times8)=6$  MBs as shown in Figure 3.1:

Figure 3.1: Estimated current frame in (c) is motion-compensated from reference frame in (b). Notice that the estimated current MBs are likely mapped to reference frame in a non-block boundary fashion.

Figure 3.1: Estimated current frame in (c) is motion-compensated from reference frame in (b). Notice that the estimated current MBs are likely mapped to reference frame in a non-block boundary fashion.

Each estimated MB  $\widehat{c^k}$  has a particular  $\overrightarrow{MV}^k$  associated to it. Therefore, its  $\widehat{c}$  can is determined:

$$\hat{c} = MC[r, V] \tag{3.0}$$

Essentially, the MC[•] operation is simply a shift operation for each MB. For an MB, Equation 3.0 can be written explicitly as

$$\widehat{c^k}(x,y) = r(i + MV_x^k, j + MV_y^k)\Big|_{\substack{i = [(k \bmod (n/q))^*q] + x, \\ j = [floor(k/(n/q))^*p] + y}}$$

(3.1)

for

$$x = 0... p-1$$

,  $y = 0... q-1$ , and  $k = 0... [(m \times n)/(p \times q)] - 1$

where  $MV_{row}^{k}$  and  $MV_{col}^{k}$  (for  $0 \le MV_{x}^{k}$ ,  $MV_{y}^{k} \le 7$ ) are constant for each pixel in the same MB k. Taking the above example with p = q = 8, m = 16, n = 24, k = 1,  $MV_{row}^{l} = 6$  and  $MV_{col}^{l} = 3$ , Equation (3.1) becomes,

$$\widehat{c}^{1}(x,y) = r(i+6,j+3)|_{\substack{i=8+x,\j=y}}$$

for  $x = 0...7$  and  $y = 0...7$  (3.2)

which graphically allows the estimated current block  $\hat{c}^1$  to be depicted as the following Figure 3.2:

Figure 3.2: Graphical interpretation of Equation (3.2) above where  $\widehat{c}^1$  straddles four adjacent MBs  $\mathbf{r}^1$ ,  $\mathbf{r}^2$ ,  $\mathbf{r}^4$ ,  $\mathbf{r}^5$  in the reference frame.

For MPEG motion-compensated encoding, the previously reconstructed reference frame r (either an I or P frame) is stored, in the spatial domain, in a frame memory for use by the MC operation. In the transcoder proposed in this thesis, however, all previously stored frame data are in the form of DCT-Requantization Error Blocks (REBs). Given that the conventional mechanism of the MC operation only handles blocks in the spatial domain, one way to motion-compensate current DCT-REB from the reference DCT-REB can be achieved in the following manner:

- Perform Inverse DCT for each DCT-REB to transform it back to the spatial domain.

These are the REBs.

- 2. Motion compensate each REB as defined in Equation (3.1) above.

- Perform the DCT operation for each REB to transform REB back to DCT domain.These are the DCT-REB's.

Because DCT and inverse DCT are linear operations it is possible to go directly from the DCT-REBs in the reference frame to correction factors for the DCT-REBs in the current frame, via a linear transformation. The particular transformation depends on the Motion Vector for each MB. In the next section, details of the appropriate linear transformations are given.

#### 3.2. Chang and Messerschmitt's algorithm

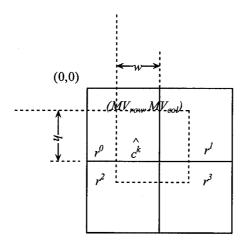

Chang and Messerschmitt's algorithm [20] proposed that the MC could be performed in the DCT domain by matrix multiplication with an appropriate 8x8 prematrix  $p_1$  and postmatrix  $p_2$  to eliminate the conversion process back and forth between the DCT and the spatial domains.

$r^{0} \qquad r^{1}$   $r^{0}_{LR} \stackrel{\wedge}{\underset{C}{\wedge}} r^{J}_{LL}$   $r^{2}_{UR} \qquad r^{3}_{UL}$

Figure 3.3(a): In general, estimated  $\hat{c}^k$  MB is unlikely to be mapped into fixed block boundary position

Figure 3.3(b):  $\hat{c}^k$  MB is made up of at most four neighboring MB in reference frame

In the Figure 3.3(a) and 3.3(b) above, the  $k^{th}$  estimated block in the current frame,  $\widehat{c^k}$  is composed of parts of four adjacent 8 x 8 blocks,  $r^0$ ,  $r^1$ ,  $r^2$ , and  $r^3$  in the reference frame, namely the lower-right corner  $(r^{0e}{}_{LR})$  of MB  $r^0$ , the lower-left corner  $(r^{1}{}_{LL})$  of MB  $r^1$ , the upper-right corner  $(r^{2}{}_{UR})$  of MB  $r^2$  and the upper-left corner  $(r^{3}{}_{UL})$  of MB  $r^3$ . These are exactly the parts of the  $r^1$  (i=0 to 3) that should be used to form  $\widehat{c^k}$ . Notice that the formation of  $\widehat{c^k}$  requires the translations of  $r^0{}_{LR}$  from lower right corner into upper left corner of  $\widehat{c^k}$ ,  $r^1{}_{LL}$  from lower left corner into upper right corner of  $\widehat{c^k}$ , and similarly for  $r^2{}_{UR}$  and  $r^3{}_{UL}$  as shown in the Figure 3.3(b). These translations can be mathematically

achieved by pre and post-multiplying the  $r^0$ ,  $r^1$ ,  $r^2$ , and  $r^3$ , by appropriate matrices,  $p_{il}$  (prematrix) and  $p_{i2}$  (postmatrix) where the first subscript designates which r submatrix is being multiplied (i.e. i = 0...3) and the second subscript indicates whether this is a pre (1) or post (2) multiply matrix. Note that  $p_{il}$  and  $p_{i2}$  also depend on the motion vector; this dependence is suppressed in the notation for readability. These  $p_{il}$  and  $p_{i2}$  are defined in Equation (3.3) as follows:

$$p_{11} = p_{01} = \begin{bmatrix} 0 & I_h \\ 0 & 0 \end{bmatrix}$$

$$p_{02} = p_{22} = \begin{bmatrix} 0 & 0 \\ I_w & 0 \end{bmatrix}$$

$$p_{21} = p_{31} = \begin{bmatrix} 0 & 0 \\ I_{8-h} & 0 \end{bmatrix}$$

$$p_{12} = p_{32} = \begin{bmatrix} 0 & I_{8-w} \\ 0 & 0 \end{bmatrix}$$

(3.3)

where I are identity matrices with size specified by their subscript h and w ( $1 \le h, w \le 8$ ) are the number of rows and columns overlapped by part of  $\widehat{c^k}$ ). Also, h and w depend on the motion vector and they are related to  $MV_{row}$  and  $MV_{col}$  as follows (refer to Figure 3.3):

$$\begin{cases} h = 7 - MV_{row} + 1, & 0 \le MV_{row} \le 7, 1 \le h \le 8 \\ w = 7 - MV_{col} + 1, & 0 \le MV_{col} \le 7, 1 \le w \le 8 \end{cases}$$

(3.4)

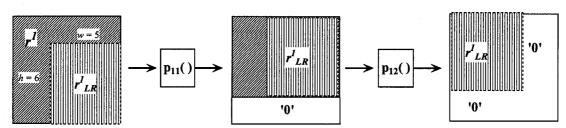

As an example, for h=6 and w=5, the translations of  $r^{I}_{LR}$  from lower right corner into upper left corner of  $\widehat{c^{k}}(\widehat{c^{k}}_{UL})$  can be formulated in matrix form as Equation (3.4) below:

$$\widehat{c_{UL}^{k}} = r_{LR}^{1} = p_{01}r^{1}p_{02} = \begin{bmatrix} 0 & I_{6} \\ 0 & 0 \end{bmatrix}r^{1} \begin{bmatrix} 0 & 0 \\ I_{5} & 0 \end{bmatrix}$$

(3.5)

where

the effect of premultiplying  $r^1$  by  $p_{01}$  is to shift the bottom six rows up vertically and roll in zeros for the two bottom rows while the postmultiplication by  $p_{02}$  horizontally translates the rightmost five columns to the left and zeros stuffs the remaining three most right columns. This can be illustrated as in Figure 3.4 below:

Figure 3.4: Using matrix multiplication to extract  $r^1_{LR}$  and translate it to upper right corner

Thus, following the same convention as above,  $\widehat{c^k}$  in the spatial domain can be computed by the matrix Equation (3.6)

$$\widehat{c^{k}} = r_{LR}^{1} + r_{LL}^{2} + r_{UR}^{3} + r_{UL}^{4} = \sum_{i=1}^{4} p_{i1} r^{i} p_{i2}$$

$$= p_{01} r^{1} p_{02} + p_{11} r^{2} p_{12} + p_{21} r^{3} p_{22} + p_{31} r^{4} p_{32}$$

(3.6)

For an 8 x 8 matrix  $x = x(i, j)|_{i,j=0}^{7}$ , the 2D Forward DCT (FDCT) transforms x from the spatial domain into the frequency domain X[24]

$$X = X(k,l)|_{k,l=0}^{7}$$

where  $X = DCT(x) = DxD^{t}$  (3.7)

where

$$D = d(e, f) = \frac{a(e)}{2} \cos(\frac{2f+1}{16} \cdot e\pi) \Big|_{e, f=0}^{7},$$

$$a(0) = \frac{1}{\sqrt{2}}, a(e) = 1 \quad \text{for} \quad e > 0$$

(3.8)

The superscript t denotes matrix transposition. Its counterpart 2D Inverse DCT (IDCT) is then defined as

$$IDCT(X) = x = D^{-1}XD^{-t} = D^{t}XD$$

(3.9)

where the second equality follows from the orthonormality of D (i.e.  $D^t=D^{-1}$ ) [24]. Following from the orthonormal property:

$$DCT(a) \times DCT(b) = DaD^{t}DbD^{t} = DaD^{-1}DbD^{t} = DabD^{t} = DCT(a \times b)$$

(3.10)

The DCT-domain of  $\widehat{c^k}$  can then be computed directly from  $r^l$ ,  $r^2$ ,  $r^3$ , and  $r^4$  by the following,

$$\widehat{C}^{k} = D\widehat{c}^{k}D^{t} = \sum_{i=0}^{3} D(p_{i1}r^{i}p_{i2})D^{t} = \sum_{i=0}^{3} Dp_{i1}D^{t} \times Dr^{i}D^{t} \times Dp_{i2}D^{t}$$

$$= \sum_{i=0}^{3} P_{i1}R^{i}P_{i2}$$

(3.11)

where  $P_{il}$  and  $P_{i2}$  are the DCT of  $p_{il}$  and  $p_{i2}$  respectively. In the Messerschmidt and Chang paper, they proposed,  $DCT(p_{il})$  and  $DCT(p_{i2})$  for  $1 \le i \le 4$  can be pre-computed at design time. The straightforward implementation of Equation (3.11) requires  $4*2*8^3 = 4096$  multiplications and  $4*2*(8-1)*8^2 = 3584$  additions.

In this thesis, we apply this concept to MPEG-4 video transcoding, bit-rate conversion from high bit-rate to low bit-rate in a heterogeneous networking environment.

#### 3.3. DCT-Coefficient-Translation-and-Truncation-Transformation-

#### **Matrix (DCTTTM) based Motion Compensation**

The development in Section 3.2 was aimed at generating the DCT coefficients of a block from the DCT coefficients of four blocks which it straddled. In contrast, in transcoding the important information from the four straddled blocks is requantization errors, not DCT coefficients. That is, one must use the method of Section 3.2 to take information from the reference DCT-REB's and put it in a form to be used by the current motion compensated DCT-REB. Unlike the algorithms [20] in Section 3.2, DCTTTM motion compensation hides the shifting detail and puts an emphasis on the contribution of each coefficient in the four DCT-REBs of the reference frame to that of one estimated current DCT-REB via a linear operation of matrix multiplication.

Consider a DCT-REB called E. It is an 8 x 8 matrix of DCT Requantization Errors (DCT-RE's). The elements of E are  $e_{ij}$ , for  $1 \le i,j \le 8$  which can be written as:

$$E = \sum_{i=1}^{8} \sum_{j=1}^{8} e_{ij} \times Q_{ij}$$

(3.12)

where  $Q_{ij}$  is an 8 x 8 matrix with only one non-zero coefficient '1' designated by the indices ij. For example, for the element in the third row and second column, i=2 and j=1 (index starts from zero):

The IDCT of Equation (3.12), due to the property of linearity, can be written as:

$$IDCT(E) = \sum_{i=0}^{7} \sum_{j=0}^{7} e_{ij} \times IDCT(Q_{ij})$$

(3.14)

The DCT of the  $Q_{ij}$  matrices can be pre-computed at design time.

Similar to the scenario illustrated in the Figure 3.3(a), four 8\*8 blocks of DCT-RE's in the reference frame will contribute to the DCT-REB in the current motion compensated block. Call these DCT-RE's  $e_{ij}(n)$  where n indicates which of the four blocks the DCT-RE originated from (using the numbering convention of Figure 3.1) and i and j indicate which DCT-RE. Given a specific  $\overline{MV}^k$ , the motion compensated DCT-REB, in the current frame (call it  $E_{MC}$ ), can be written as a linear combination of the 256 DCT-RE's in the four straddled blocks in the reference frame. That is:

$$E_{MC} = \sum_{i=0}^{3} \sum_{j=0}^{7} \sum_{i=0}^{7} e_{ij}(n) \times \hat{Q}_{ij}(n)$$

(3.15)

where  $\hat{Q}_{ij}(n)$  is called the DCT-Correction Matrix (DCT-CM).

In deriving the  $\hat{Q}_{ij}(n)$ , three steps are followed. First, each of the four straddled blocks of DCT-RE's in the reference frame are put in the space domain via an IDCT. (Note that this is a linear operation, and is independent of the motion vector). Second, given the motion vectors, appropriate pieces of the four straddled blocks (now in the space domain) are partitioned off and assembled to form an 8\*8 block. This partitioning is a linear operation. Third, the assembled block is returned to the DCT domain. This is, of course, a linear operation.

Mathematically:

Step 1:

$$q_{ij}(n) = IDCT(Q_{ij}(n))\Big|_{\substack{i,j=0.7\\n=0.3}}$$

(3.16)

where  $q_{ij}(n)$  is the space domain representation of the  $Q_{ij}(n)$  via an IDCT. As mentioned above, this operation is independent of the motion vector, therefore:

$$q_{ii}(0) = q_{ii}(1) = q_{ii}(2) = q_{ii}(3) \text{ i,j=0..7}$$

(3.17)

Step 2:

Given the motion vector  $(MV_{row}, MV_{col})$  and based on Equations (3.4) and (3.5), the assembled block, call it  $q_shift_{ij}(n)$  can be found as follows:

$$q_{shift_{ij}}(n) = p_{(n1)} * q_{ij}(n) * p_{(n2)} \Big|_{\substack{i,j=0...7\\n=0...3}}$$

(3.18)

As in Equation 3.3  $p_{(n1)}$  is the matrix which when it pre-multiplying matrix  $q_{ij}(n)$  effects the appropriate partition for the given motion vector. Thus  $p_{(n1)}$  is dependent on the motion vector. Specifically, the motion vector generates h and w from Equation 3.4 and then these are used in Equation 3.3 to generate the appropriate  $p_{(n1)}$ . Similar comments can be made for the post-multiply matrix  $p_{(n2)}$ .

Step 3:

The assembled block  $q_shift_{ij}(n)$  is transformed back to the DCT domain via linear DCT operation:

$$\hat{Q}_{ij}(n) = DCT(q \ \_shift_{ij}(n))\Big|_{\substack{i,j=0..7\\n=0.3}}$$

(3.19)

Note that there are a total of 256 8 x 8  $\hat{Q}_{ij}(n)$  which is referred to as DCT-CMs.

### 3.3.1 Example Generation of a DCT-CM $\hat{Q}_{ij}(n)$

Assume  $MV_{row} = 0$ ,  $MV_{col} = 4$ , i = 2 j = 1 and n = 0, therefore  $\hat{Q}_{21}(0)$  can be computed as below:

Step 1: Perform the IDCT on  $Q_{21}$ .

Step 2: Translate the spatial-domain  $q_{21}(0)$  into the location specified by  $(MV_{ro}, MV_{col})$ .

In the case of n=0,  $MV_{row}=0$  and  $MV_{col}=4$  (i.e., h=8, w = 4 from Equation 3.4),  $q_{shift_{21}}(0)$  using Equation 3.18 is:

$$q_{-}shift_{21}(0) = p_{01} * q_{21}(0) * p_{02} = \begin{bmatrix} 0 & I_h \\ 0 & 0 \end{bmatrix} * q_{21}(0) * \begin{bmatrix} 0 & 0 \\ I_w & 0 \end{bmatrix}$$

$$= \begin{bmatrix} -0.0451 & -0.1283 & -0.1920 & -0.2265 & 0 & 0 & 0 & 0 \\ -0.0187 & -0.0532 & -0.0795 & -0.0938 & 0 & 0 & 0 & 0 \\ 0.0187 & 0.0532 & 0.0795 & 0.0938 & 0 & 0 & 0 & 0 \\ 0.0451 & 0.1283 & 0.1920 & -0.2265 & 0 & 0 & 0 & 0 \\ 0.0451 & 0.1283 & 0.1920 & 0.2265 & 0 & 0 & 0 & 0 \\ 0.0187 & 0.0532 & 0.0795 & 0.0938 & 0 & 0 & 0 & 0 \\ -0.0187 & -0.0532 & -0.0795 & -0.0938 & 0 & 0 & 0 & 0 \\ -0.0451 & -0.1283 & -0.1920 & -0.2265 & 0 & 0 & 0 & 0 \end{bmatrix}$$

$$(3.21)$$

Step 3) Perform the DCT on  $q_shift_{21}(0)$ :

Thus if the DCT-RE is 1 for the DCT position in the 3<sup>rd</sup> row (i=2) and 2<sup>nd</sup> column (j=1) for the DCT Block in the reference frame that forms the upper left portion of the estimated block (n=0), the above  $\hat{Q}_{21}(0)$  represents the resulting error in each of the 64 DCT coefficients of the residue. This can be seen mathematically in Equation 3.15. Thus, given the ( $MV_{row}$ ,  $MV_{col}$ ) pair, there are a total of 256 8 x 8 DCT-CMs (the  $\hat{Q}_{ij}(n)$ ) generated in a similar fashion as  $\hat{Q}_{21}(0)$ .

Rearranging each of the 8 x 8 DCT-CMs into 64 x 1 vectors and making these vectors the columns of a new composite matrix W of size 64 x 256. Converting the 8\*8 matrix  $E_{MC}$  (the motion compensated DCT-REB from Equation 3.15) into a 64 x 1 vector, called  $\hat{Z}$ , Equation 3.15 can be rewritten as:

$$\hat{Z} = \sum_{i=0}^{255} e_i \times W_i \tag{3.23}$$

where  $e_i$  again for  $0 \le i \le 255$  are the DCT-RE's of the four overlapped MB  $r^0$ ,  $r^1$ ,  $r^2$ ,  $r^3$ , and  $W_i$  for  $0 \le i \le 255$  is 64 x 1 and the *i*th column of the 64 x 256 composite matrix W. For all 64 combinations of  $MV_{row}$  and  $MV_{col}$  where  $0 \le MV_{row}$ ,  $MV_{col} \le 7$ , there is a particular composite matrix W associated and hence 64 such composite matrices are generated. The computational complexity of implementing Equation (3.23) requires 256\*64 = 16384 multiplications and (256-1)\*64 = 16320 additions for each motion compensated block.

In comparison with Chang and Messerschmitt's algorithm reviewed in Section 3.2 which requires 4096 multiplication and 3584 additions, the multiplication-and-add count of the DCTTM approach is greater. However, the  $e_i$ 's are formed by the requantization of already quantized (from the first compression) DCT coefficients. Many of these already quantized DCT coefficients are in fact 0. Note that if a DCT coefficient was quantized to 0 in the first quantization its  $e_i$  is also 0. For example if it is known that, all of the DCT coefficient in the  $7^{th}$  row and all of the DCT coefficients in the  $7^{th}$  column were always (or almost always) 0 there would be no need to calculate the corresponding terms in Equation 3.23. Thus we could replace the 256\*64 composite matrix by a 256\*49 composite matrix. This will result in a reduction of computation.

In the second quantization, higher DCT frequencies will tend to be quantized much more heavily than lower frequencies. This, coupled with the fact that these DCT coefficients are small (even with the addition of the DCT-RE's), means that one is likely to end up with zero in these coefficients after the second quantization. This observation suggests that we may neglect rows in the composite matrix W corresponding to higher frequencies. This further reduces computation.

In the next section an analysis will be done to determine which rows and columns of the composite matrix W may be neglected.

## 3.4. Analysis of computational complexity for DCTTM-based MC-DCT using partial DCT information

For Equation (3.17) to render one DCT-REB, all the correction factors of the composite matrix W from every location of four overlapped DCT-REBs in the reference frame are taken into account. Consequently, this approach induces a very high cost in term of computational complexity. However, it is known that typically the low frequency DCT coefficients contain most of the energy of the signal, and also that these frequencies are most important for human perception [33]. Thus one may reduce the computational complexity of the DCTTTM algorithm by using only partial DCT information.

For every coefficient discarded, the quality of the video sequence is expected to be degraded. Consequently, it would be preferable to keep the most significant DCT coefficients, with the others discarded to maximize computational savings.

Simulations were perfeormed on several video sequences in order to make judgments of which coefficients should be kept. Table 3.1, 3.2, and 3.3 show the average

percentage of non-zero DCT-REs for the video sequences of 150 frames, table-tennis, flowergarden and Miss America respectively:

| Та    | Table 3.1: Average Percentage of Non-Zero Coefficient for Table Tennis   |      |      |      |      |      |      |  |  |  |  |

|-------|--------------------------------------------------------------------------|------|------|------|------|------|------|--|--|--|--|

| (Grid | (Grid location below corresponding to actual positioning of a 8x8 block) |      |      |      |      |      |      |  |  |  |  |

| 71.2  | 71.2 64.1 59.9 58.6 56.4 55.0 51.5 48.6                                  |      |      |      |      |      |      |  |  |  |  |

| 64.7  | 58.2                                                                     | 55.3 | 53.5 | 52.3 | 50.1 | 47.3 | 44.2 |  |  |  |  |

| 61.3  | 56.1                                                                     | 52.9 | 51.4 | 50.1 | 48.1 | 45.4 | 42.2 |  |  |  |  |

| 60.2  | 55.6                                                                     | 52.6 | 51.0 | 49.3 | 47.4 | 44.6 | 41.5 |  |  |  |  |

| 58.9  | 55.4                                                                     | 52.4 | 50.6 | 48.8 | 46.6 | 44.0 | 40.6 |  |  |  |  |

| 58.2  | 54.1                                                                     | 51.1 | 49.3 | 47.7 | 45.7 | 42.6 | 39.5 |  |  |  |  |

| 56.2  | 52.9                                                                     | 50.4 | 48.3 | 46.2 | 44.5 | 41.5 | 38.3 |  |  |  |  |

| 54.4  | 51.5                                                                     | 48.3 | 46.2 | 44.6 | 42.7 | 39.9 | 36.5 |  |  |  |  |

| Та    | Table 3.2: Average Percentage of Non-Zero Coefficient for Flowergarden |       |      |         |      |      |        |  |  |  |  |

|-------|------------------------------------------------------------------------|-------|------|---------|------|------|--------|--|--|--|--|

| (Grid | locati                                                                 | on be |      | corresp |      |      | actual |  |  |  |  |

| 86.3  | 86.3 78.9 76.0 74.3 72.4 70.9 68.6 65.9                                |       |      |         |      |      |        |  |  |  |  |

| 79.6  | 75.2                                                                   | 73.5  | 71.9 | 70.2    | 68.7 | 66.8 | 63.7   |  |  |  |  |

| 76.1  | 73.4                                                                   | 72.1  | 70.6 | 69.1    | 67.8 | 65.7 | 62.9   |  |  |  |  |

| 74.2  | 72.0                                                                   | 70.7  | 69.8 | 68.2    | 67.0 | 64.8 | 61.8   |  |  |  |  |

| 72.7  | 70.9                                                                   | 69.6  | 68.7 | 67.5    | 66.2 | 63.9 | 61.1   |  |  |  |  |

| 71.2  | 69.7                                                                   | 68.5  | 67.5 | 66.2    | 65.0 | 62.8 | 60.1   |  |  |  |  |

| 68.5  | 67.6                                                                   | 66.5  | 65.5 | 63.9    | 62.7 | 60.8 | 58.2   |  |  |  |  |

| 64.7  | 64.1                                                                   | 63.2  | 62.3 | 60.8    | 59.8 | 58.0 | 55.7   |  |  |  |  |

| Та    | Table 3.3: Average Percentage of Non-Zero Coefficient for Miss America |      |      |         |        |      |        |  |  |  |  |

|-------|------------------------------------------------------------------------|------|------|---------|--------|------|--------|--|--|--|--|

| (Grid | locati<br>oning o                                                      |      |      | corresp | onding | to   | actual |  |  |  |  |

| 88.6  | <del>,,,,,</del>                                                       |      |      |         |        |      |        |  |  |  |  |

| 60.1  | 47.3                                                                   | 41.8 | 35.6 | 31.4    | 29.6   | 29.9 | 33.0   |  |  |  |  |

| 49.2  | 42.0                                                                   | 37.6 | 32.6 | 28.8    | 27.1   | 26.4 | 27.7   |  |  |  |  |

| 43.1  | 37.1                                                                   | 33.1 | 29.0 | 25.8    | 24.1   | 22.7 | 21.8   |  |  |  |  |

| 37.4  | 32.7                                                                   | 29.2 | 26.1 | 23.3    | 22.1   | 20.3 | 20.6   |  |  |  |  |

| 33.1  | 28.6                                                                   | 25.5 | 23.1 | 20.9    | 19.6   | 18.1 | 17.8   |  |  |  |  |

| 29.6  | 26.5                                                                   | 23.3 | 22.2 | 19.9    | 19.8   | 18.3 | 21.4   |  |  |  |  |

| 24.3  | 22.1                                                                   | 19.2 | 18.4 | 16.2    | 16.3   | 15.2 | 17.7   |  |  |  |  |

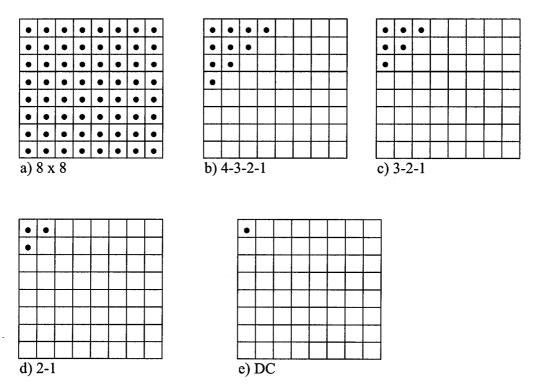

Notice that the average percentages of non-zero coefficients decrease as one gets further from the top left corner of the DCT matrices. These are of course the low

frequencies. Following on this observation, in this thesis schemes which preserve only these coefficients are studied. Figure 3.5b-e) show four schemes labeled 4-3-2-1, 3-2-1, 2-1 and DC. A dot indicates that the corresponding DCT coefficient will be used.

Figure 3.5: Partial DCT-REs information. • refer to the locations of an 8 x 8 DCT Requantization Error Block (DCT-REB) where values are taken into account for the computation of motion compensation and assumed to be non-zero. Non-marked locations are ignored and assumed to be zero-valued.

For example, in the case of Figure 3.5(c), we assume only the six RE's on the top-left corner are nonzero-valued and zero elsewhere and refer to it as the 3-2-1 scheme. For the DCTTTM algorithm, the 3-2-1 scheme implies the computation of one motion-compensated REB from six RE's in each of the four overlapped REBs in the reference frame. Thus, a total of twenty-four RE's are used. Applying this scheme to Equation 3.15,  $E_{MC}$  (now call it  $E_{MC}$  321) becomes:

$$E_{MC_{321}} = \sum_{n=0}^{3} \sum_{i=0}^{2} \sum_{j=0}^{2-i} e_{ijn} \times \hat{Q}_{ijn}$$

(3.24)

For each RE, there is a  $\hat{Q}$  matrix associated to the transformation. Therefore, rather than having a composite-matrix W of size 64 x 256 where all four REBs locations are taken into account, the matrix W is shrunk to 64 x 24. Further computational reductions can be achieved by applying the partial information scheme to the motion-compensated REB; of the 64 REs coefficients, only the six located in the top-left corner designated by the 3-2-1 scheme are assumed to be non-zero value. By doing so, the size of the composite matrix W can be scaled down from its original 64 x 256 to 6 x 24. The computational complexity of one motion-compensated REB is thus reduced to a simple matrix-vector multiplication of 6 x 24 times 24 x 1. The Equation of (3.24) becomes:

$$\hat{Z}_{321} = \sum_{i=0}^{23} e_i \times W_{321i} \tag{3.25}$$

where  $e_i$  again for  $0 \le i \le 23$  is the DCT-RE's of the four overlapped MB  $r^0$ ,  $r^1$ ,  $r^2$ ,  $r^3$  as per 3-2-1 scheme,  $W_{321i}$  is the 6 x 1 DCT vector derived from the *i*th column of the 64 x 24 matrix  $W_{321}$  and  $\hat{Z}_{321}$  is the motion-compensated DCT-REB. The direct implementation of Equation (3.18) matrix-vector multiplication requires 24\*6 = 144 mults and 23\*6 = 138 adds. Table 3.4 outlines the computational cost for the five schemes:

| Table 3. | Table 3.4: Computation cost in term of mult-and-add count for different partial information scheme |                |              |                                           |  |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------|----------------|--------------|-------------------------------------------|--|--|--|--|--|--|--|

|          | Size of the composite-<br>matrix (row x col)                                                       | Mult.<br>Count | Add<br>Count | % of Mult Count reduction relative to 8x8 |  |  |  |  |  |  |  |

| 8 x 8    | 64 x 256                                                                                           | 16384          | 16320        | N/A                                       |  |  |  |  |  |  |  |

| 4-3-2-1  | 10 x 40                                                                                            | 400            | 390          | 97.56%                                    |  |  |  |  |  |  |  |

| 3-2-1    | 6 x 24                                                                                             | 144            | 138          | 99.12%                                    |  |  |  |  |  |  |  |

| 2-1      | 3 x 12                                                                                             | 36             | 33           | 99.78%                                    |  |  |  |  |  |  |  |

| DC       | 1 x 4                                                                                              | 4              | 3            | 99.98%                                    |  |  |  |  |  |  |  |

This section has examined the potential savings in computation to be reaped by neglecting the errors in some DCT-REs in the reference frame and in omitting the calculation of the effect of all errors on certain DCT coefficients in the residue of the current frame under different schemes. In the next section, the cost in both subjective and objective quality implied by omitting these coefficients is examined.

# 3.5. SIMULATION STUDY ON THE IMPACT OF DIFFERENCE SCHEMES OF PARTIAL INFORMATION USED TO VIDEO QUALITY

Both subjective measure and objective measure are used to assess the tradeoff between computational cost and video quality, when one considers only partial DCT-RE information, The video sequence *Table Tennis* is simulated. The MoMuSys MPEG-4 encoder and decoder software V1.0 [26] are used in the simulations. Only integer (full) pixel motion estimation is employed limiting the motion vector to only 64 possible displacements with respect to the top-left corner pixel location of the top-left block of the four straddled blocks. *IPP...IPP* structure with M=1 (Number of B-VOPs [M-1] between two consecutive P-VOPs) and N=15 (Number of P-VOPs [M-1] between two consecutive

I-VOPs) transcoding from 5Mbps to 256Kbps for various cases. The transcoder software was based on the work of Mr. Hong Quan Chen [25] and was modified to implement different schemes of partial information. The same set of parameters is applied in all the simulations for the rest of this chapter.

Figure 3.6 (a)-(e): the 61<sup>th</sup> motion-compensated frame of video sequence *Table Tennis* using different partial information scheme

Subjectively, the simulation suggests that for an open-loop implementation (Figure 3.6(a)) without drift correction, the blocking artifacts are clearly noticeable, severely degrading the visual quality when compared to full pixel drift error compensation (Figure 3.6 (e)). While there is still noticeable quality improvement by employing the 3-2-1 scheme (Figure 3.6 (d)) over the 2-1 scheme (Figure 3.6(c)), there is virtually no noticeable enhancement in the 4-3-2-1 scheme from the 3-2-1 scheme.

Figure 3.7 shows the average PSNR for *Table Tennis* using different schemes in the transcoding process. The curve in Figure 3.7 exhibits an enhancement of around 1dB as one moves from one scheme to the next.

Figure 3.7: Average PSNR for Tennis 150 frames Transcoding using different schemes for motion compensation

This section has examined the cost in quality, measured both subjectively and objectively, in either neglecting the effects of errors in some DCT-RE coefficients in the reference frame, or in omitting the calculation of the effect of all errors on certain DCT coefficients in the residue of the current frame. Given our goal is to reduce the computational cost to the greatest extent possible (99.12% gain in computational saving when comparing with full 8 x 8 full information scheme) while minimizing video quality degradation, the analysis in the previous two sections suggest that the 3-2-1 Scheme provides a fair balance between these conflicting requirements. For the rest of this thesis, the 3-2-1 Scheme is the algorithm used for implementing the MC-DCT module.

In addition to employing the 3-2-1 Scheme, further computational savings may be achieved by reducing the precision of constants in the DCT Correction Matrices (DCT-CMs)  $\hat{Q}$ . In the next section, an appropriate quantizer design and the effect of the subsequent quantization inherent in transcoding on video quality are examined.

#### 3.6 QUANTIZATION OVER CONSTANT TRANSFORMED COEFFICIENTS

The precision in bits is a very important parameter for hardware implementation. Each additional bit of precision costs extra resources. To further reduce computations this thesis considers heavily quantizing the constants in the DCT-CMs  $\hat{Q}$ ,

#### 3.6.1. Design of Quantizer for the elements of DCT-CMs

The design of an appropriate quantizer for these constant coefficients should depend on the characteristics of these matrices. First, there are many zeros within these matrices, thus a zero reconstruction level is required. This suggests a mid-step quantizer. However, the drawback to mid-step quantizer is that there is always an odd number of

reconstruction levels. Thus, in a hardware implementation, the reconstruction levels can not be economically represented in a base-two numerical system.

In the following, if there are n bits to the right of the binary point we say that we are using n bit precision. Note that in fact, an extra bit is required. Specifically n bit precision requires n+1 bits. For example, if 2-bit precision after binary point is used (ie. Step size of 0.25) to quantize the DCT-CM constants,  $7 \le 2^{(1+2)}=8$  distinct elements result; they are 1, 0,  $\pm$ 0.25, 0.75,  $\pm$ 0.5 (notice that -0.75 and -1 never appear in examining all DCT-CMs). In other words, these quantized values can be encoded using 3 bits only. Table 3.5 shows one possible encoding scheme:

| Table 3.5 Possible encoding constants of 2-bit precision |                         |

|----------------------------------------------------------|-------------------------|

| <b>Actual Quantized Value</b>                            | Encoded Value in binary |

| 0                                                        | 000                     |

| -0.25                                                    | 001                     |

| -0.5                                                     | 010                     |

| 0.25                                                     | 011                     |

| 0.5                                                      | 100                     |

| 0.75                                                     | 101                     |

| 1                                                        | 110                     |

Inside each of the 64 DCT-CM's there are only a finite number of *distinct* values. As these values are more heavily quantized, there will be fewer and fewer *distinct* values. Figure 3.8 shows the result by exhaustively counting the number of distinct values in all 64 DCT-CM's for different bit-precisions.

Figure 3.8: The relation between the number of bit-precision (after binary point) used and the number of resulted distinct quantized DCT-CM elements

It should be noted from Figure 3.8, with  $2^{(1+n)}$  -1 bit budget, (except for one bit precision scheme), all other precision schemes could safely and economically encode the quantized DCT-CM constants.

In the next section, different precision schemes are employed to run the simulations against five video test sets to assess the impact of PSNR quality versus bit precision.

## 3.7. SIMULATION RESULTS OF PSNR PERFORMANCE FOR DCTTTM-BASED MC-DCT WITH N-BIT PRECISION AFTER BINARY POINT

Here simulation results are given that examine the various partial information schemes (DC only, 2-1, 3-2-1 and 4-3-2-1), as well as different bit precisions. Figure 3.9 to 3.12 shows the PSNR video quality measure for five video sequences, *Table Tennis*, *Flowergarden, Football, Miss America*, and *Mobile*. Note again the horizontal-axis represents the bit precision used after the binary point.

Figure 3.9 PSNR measure on transcoding *Table Tennis* using different partial information schemes for motion compensation

Figure 3.10 PSNR measure on transcoding *Miss America* using different partial information schemes for motion compensation

Figure 3.11 PSNR measure on transcoding *Football* using different partial information schemes for motion compensation