# Towards First-Order Symbolic Trajectory Evaluation using MDGs

Donglin Li

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at

Concordia University

Montréal, Québec, Canada

April 2006

© Donglin Li, 2006

Library and Archives Canada

chives Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 0-494-14270-7 Our file Notre référence ISBN: 0-494-14270-7

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

# Towards First-Order Symbolic Trajectory Evaluation using MDGs

#### Donglin Li

SoC design becomes more complex with the increasing amount of different kinds of IPs on the chip. How to ensure correctness of functionality in an SoC chip is one of the biggest challenges in SoC designs. Traditional BDD-based symbolic model checking techniques are an attractive subset of formal verification methods because of their high automation and little requirement for human effort to guide the proof process, whereas they usually suffer from the state explosion problem. Symbolic Trajectory Evaluation (STE) technique and MDG-based model checking technique improve the traditional BDD-based symbolic model checking approaches in two different ways. In this thesis, we investigate the possibility of combining STE and MDGs, for each of which we study the underlying theory and methodology, discuss the verification tool, and provide a detailed case study. The main purpose of these two case studies is to obtain an in-depth understanding of the underlying theories and methodologies of these two model checking techniques, which may facilitate the achievement of their combination. Two attempts to combine the STE with the MDG are discussed: one in the STE verification environment and the other in the MDG tools. We focus on the second attempt and propose a hybrid approach of First-Order Symbolic Trajectory Evaluation using MDGs, which can not only increase the scale of circuits verified using STE but also improve the performance of STE by raising the level of abstraction. This study may also provide direction for further research in the application of MDGs.

To my family

#### **ACKNOWLEDGEMENT**

I would like to express my sincere gratitude and appreciation to my supervisor Dr. Otmane Ait Mohamed for providing me the opportunity to work in this challenging but exciting field and to be part of his research group, for his expert guidance, and for his support and encouragement throughout my research and thesis process.

Thanks must also go to Dr. Sofiène Tahar, who put great efforts to provide a truly wonderful research environment. I benefited a lot from his inspiring lectures as well.

I also owe a debt of gratitude to all the members of the HVG group. They were always friendly, supportive and encouraging to me. We really had a large group and it is almost impossible to name them all. Special thanks to Haja and Nasser for their valuable comments on the thesis.

I would especially like to thank Fariborz, his wonderful wife and lovely daughter.

They were like family to me, who brought me happiness and helped me out whenever I was in difficulties.

Finally, acknowledgement and thanks to my parents and sister. I appreciate your love, support and understanding.

## TABLE OF CONTENTS

| LIST OF | FIGURES                                      | X    |

|---------|----------------------------------------------|------|

| LIST OF | TABLES                                       | XII  |

| LIST OF | ACRONYMS                                     | XIII |

| СНАРТЕ  | R 1 INTRODUCTION                             | 1    |

| 1.1     | BACKGROUND                                   | 4    |

| 1.1.1   | l Model Checking                             | 4    |

| 1.1.2   | 2 BDDs                                       | 8    |

| 1.1.3   | 3 Symbolic Model Checking                    | 9    |

| 1.1.4   | 4 MDGs                                       | 10   |

| 1.2     | THESIS CONTRIBUTIONS                         | 12   |

| 1.3     | SCOPE OF THESIS                              | 12   |

| СНАРТЕ  | R 2 SYMBOLIC TRAJECTORY EVALUATION           | 14   |

| 2.1     | BASICS                                       | 14   |

| 2.1.    | 1 Lattice                                    | 15   |

| 2.1.2   | 2 Symbolic Simulation                        | 18   |

| 2.2     | Modeling                                     | 24   |

| 2.3     | SPECIFICATION LANGUAGE                       | 27   |

| 2.4     | VERIFICATION METHODOLOGY                     | 29   |

| 2.5     | SYMBOLIC FORMULATION                         | 32   |

| 2.6     | ILLUSTRATIVE EXAMPLE                         | 36   |

| 2.7     | STE BASED VERIFICATION TOOL AND FL LANGUAGE  | 40   |

| 2.8     | SUMMARY                                      | 43   |

| CHARTE  | R 3 VERIEVING LOOK-ASIDE INTERFACE USING STE | 44   |

| 3.1   | LA-1 INTERFACE SPECIFICATIONS                         | 44 |

|-------|-------------------------------------------------------|----|

| 3. 1  | 1.1 Signal Descriptions                               | 45 |

| 3.1   | 1.2 Port Operation specifications                     | 45 |

| 3.2   | RELATED WORK                                          | 47 |

| 3.3   | VERIFYING AHMED'S LA-1 RTL DESIGN USING STE           | 48 |

| 3.3   | 3.1 Design                                            | 48 |

| 3.3   | 3.2 Verification                                      | 50 |

| 3.3   | 3.3 Experimental Results                              | 53 |

| 3.4   | VERIFYING MODIFIED LA-1 RTL DESIGN USING STE          | 55 |

| 3.4   | 4.1 Modifications                                     | 55 |

| 3.4   | 4.2 Modified Design                                   | 57 |

| 3.4   | 4.3 Verification                                      | 60 |

| 3.4   | 4.4 Experimental Results                              | 61 |

| 3.5   | Summary                                               | 62 |

| СНАРТ | TER 4 MDG-BASED MODEL CHECKING                        | 63 |

| 4.1   | Many-sorted First-order Logic                         | 63 |

| 4.2   | MULTIWAY DECISION GRAPHS                              | 66 |

| 4.3   | Modeling                                              | 67 |

| 4.4   | SPECIFICATION LANGUAGE                                | 68 |

| 4.5   | VERIFICATION METHODOLOGY                              | 70 |

| 4.5   | 5.1 Reachability Analysis in MDG-based Model Checking | 70 |

| 4.5   | 5.2 Model Checking of L <sub>MDG</sub> Properties     | 73 |

| 4.6   | MDG-BASED VERIFICATION TOOLS                          | 73 |

| 4.7   | SUMMARY                                               | 75 |

| СНАРТ | TER 5 VERIFYING LOOK-ASIDE INTERFACE USING MDGS       | 76 |

| 5.1   | Mapping STE Assertions to $L_{ m MDG}$ Properties     | 76 |

| 5.2   | VERIFYING MODIFIED LA-1 RTL DESIGN USING MDGS         | 80 |

| 5.2    | .1 Modeling                                           | 80     |

|--------|-------------------------------------------------------|--------|

| 5.2    | .2 Properties                                         | 83     |

| 5.2    | 3 Experimental Results                                | 84     |

| 5.3    | Summary                                               | 85     |

| CHAPT  | ER 6 FIRST-ORDER SYMBOLIC TRAJECTORY EVALUATION USING | MDGS86 |

| 6.1    | Purpose                                               | 86     |

| 6.2    | IMPLEMENTING THE COMBINATION IN FORTE                 | 87     |

| 6.3    | IMPLEMENTING THE COMBINATION IN THE MDG TOOLS         | 90     |

| 6.3    | Logic Extension                                       | 90     |

| 6.3    | 2.2 Implementation of STE Modeling                    | 91     |

| 6.3    | 3 Implementation of STE Assertions                    | 94     |

| 6.3    | .4 Implementation of STE Verification Methodology     | 96     |

| 6.4    | ILLUSTRATIVE EXAMPLE                                  | 99     |

| 6.5    | Summary                                               | 102    |

| СНАРТ  | ER 7 CONCLUSION AND FUTURE WORK                       | 103    |

| DEEEDI | ENCES                                                 | 106    |

## LIST OF FIGURES

| FIGURE 1.  | MODEL CHECKING PROCESS                                                                                         | 4  |

|------------|----------------------------------------------------------------------------------------------------------------|----|

| FIGURE 2.  | BDD AND TRUE TABLE FOR FUNCTION $F(A, B, C, D) = (A \land B) \lor (C \land D)$                                 | 9  |

| FIGURE 3.  | FROM BDDs to MDGs                                                                                              | 11 |

| FIGURE 4.  | LATTICE STRUCTURE FOR THE POWER SET OF {A,B,C}                                                                 | 17 |

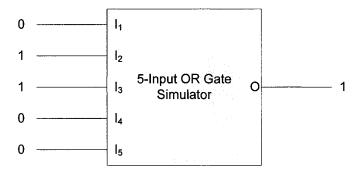

| FIGURE 5.  | SIMULATOR FOR A 5-INPUT OR GATE                                                                                | 19 |

| Figure 6.  | SYMBOLIC SIMULATOR FOR A 5-INPUT OR GATE                                                                       | 20 |

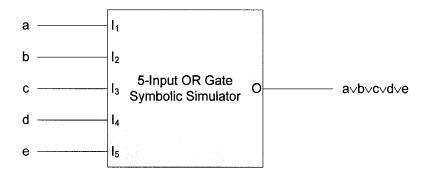

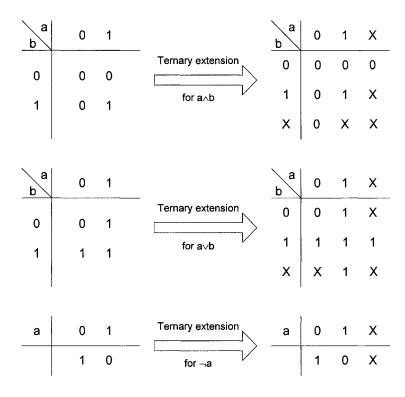

| Figure 7.  | TRUE TABLES OF BOOLEAN OPERATIONS AND THE TERNARY EXTENSIONS                                                   | 21 |

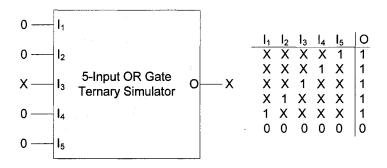

| Figure 8.  | TERNARY SIMULATOR MODEL FOR A 5-INPUT OR GATE                                                                  | 21 |

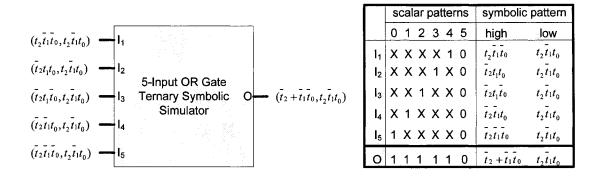

| FIGURE 9.  | TERNARY SYMBOLIC SIMULATOR FOR A 5-INPUT OR GATE                                                               | 23 |

| FIGURE 10. | SYMBOLIC TENARY SIMULATOR FOR A 5-INPUT OR GATE                                                                | 24 |

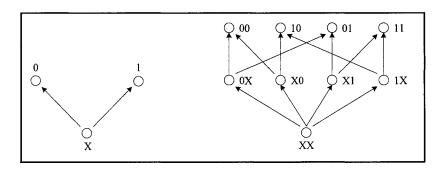

| FIGURE 11. | Partial orders over $\{0, 1, X\}$ and $\{0, 1, X\}^2$                                                          | 25 |

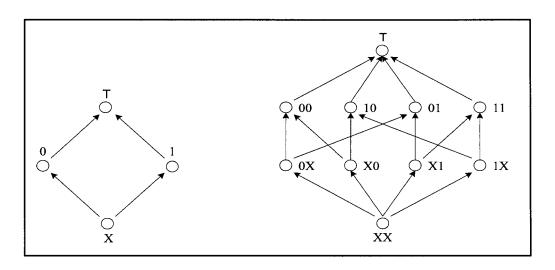

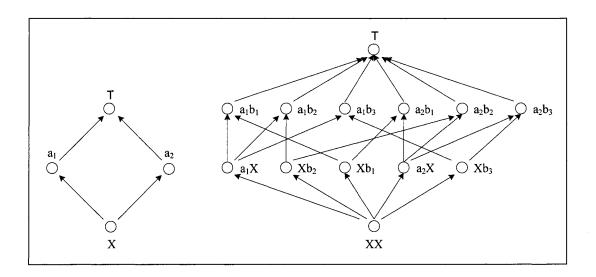

| FIGURE 12. | Hasse diagrams of complete lattices ( $\{0,1,X\} \cup \{T\},\leq \}$ and ( $\{0,1,X\}^2 \cup \{T\},\leq \}$ ). | 26 |

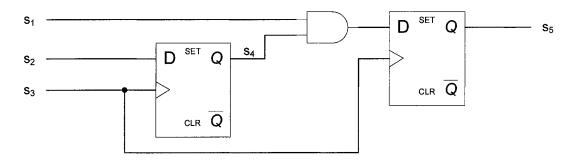

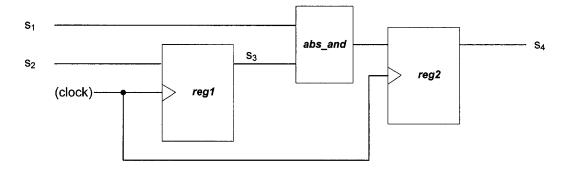

| FIGURE 13. | DIAGRAM FOR A VERILOG MODEL OF A SEQUENTIAL CIRCUIT                                                            | 36 |

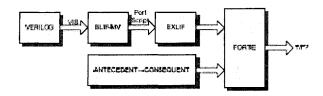

| FIGURE 14. | VERIFICATION USING FORTE                                                                                       | 41 |

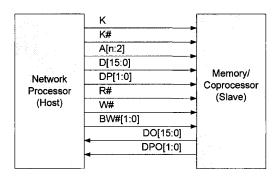

| FIGURE 15. | LA-1 INTERFACE BUSES                                                                                           | 45 |

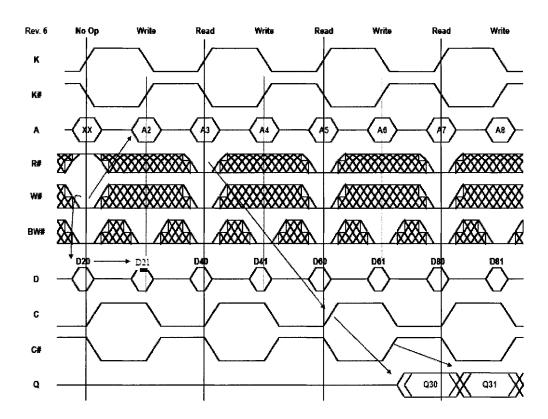

| FIGURE 16. | LA-1 PORT OPERATION TIMING DIAGRAM                                                                             | 46 |

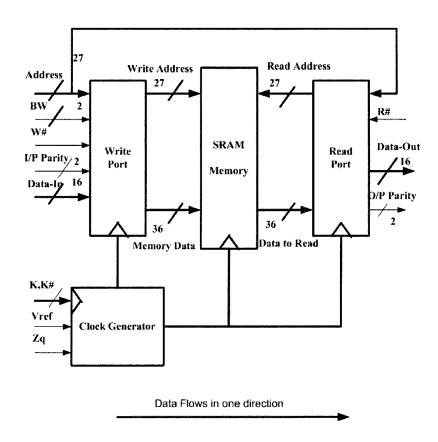

| Figure 17. | ARCHTECTURE OF AHMED'S LA-1 RTL DESIGN                                                                         | 47 |

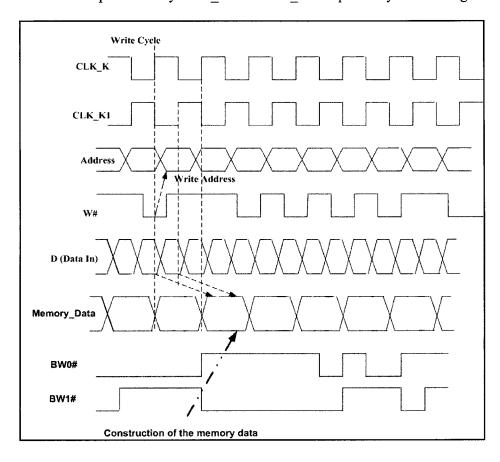

| FIGURE 18. | TIMING DIAGRAM FOR THE LA-1 INTERFACE WRITE PORT                                                               | 48 |

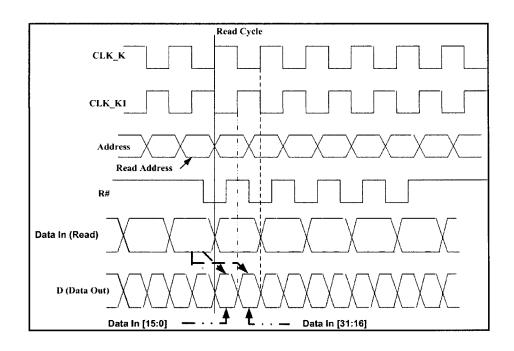

| Figure 19. | TIMING DIAGRAM FOR THE LA-1 INTERFACE READ PORT                                                                | 49 |

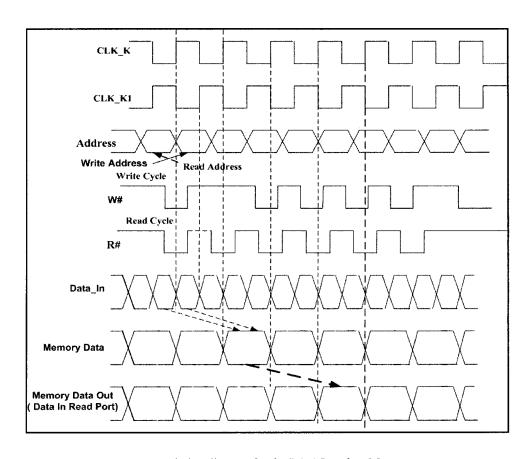

| FIGURE 20. | TIMING DIAGRAM FOR THE LA-1 INTERFACE MEMORY                                                                   | 49 |

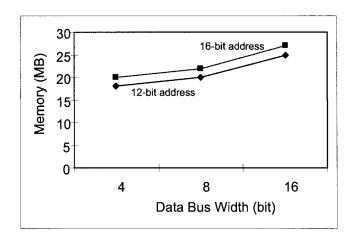

| FIGURE 21. | MEMORY USAGE FOR AHMED'S LA-1 RTL DESIGN VERIFICATION USING STE                                                | 54 |

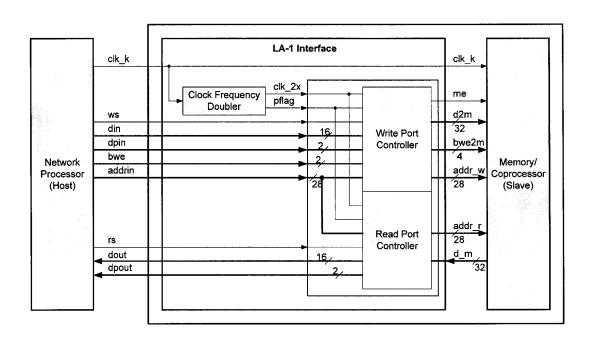

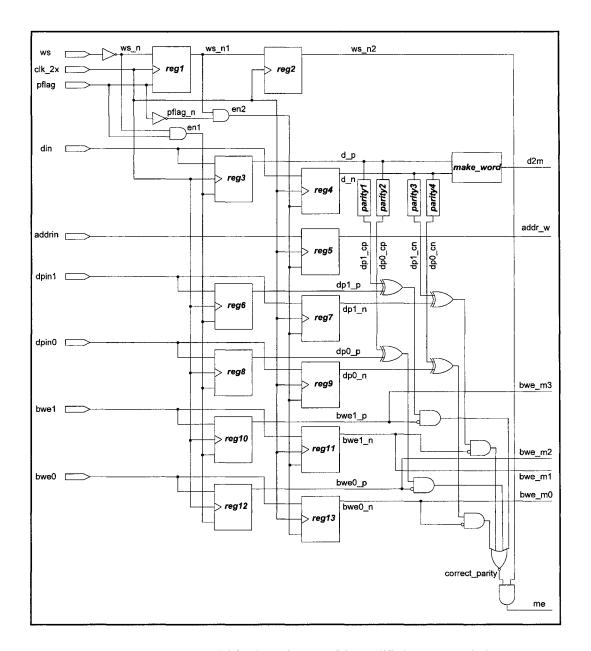

| FIGURE 22. | MODIFIED LA-1 RTL DESIGN                                                                                       | 57 |

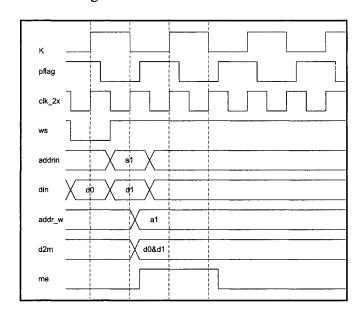

| FIGURE 23. | TIMING DIAGRM FOR WRITE PORT CONTROLLER                                                                        | 58 |

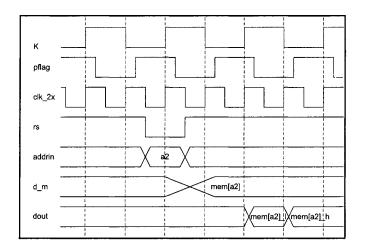

| FIGURE 24. | TIMING DIAGRAM FOR READ PORT CONTROLLER                                                                        | 58 |

| FIGURE 25  | VIDTOV DI I BLOCK DIACRAM                                                                                      | 50 |

| FIGURE 26. | REACHABILITY ANALYSIS ALGORITHM IN MDG-BASED MODEL CHECKING71                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 27. | MDG-HDL MODEL FOR THE WRITE PORT OF THE MODIFIED LA-1 RTL DESIGN81                                                                        |

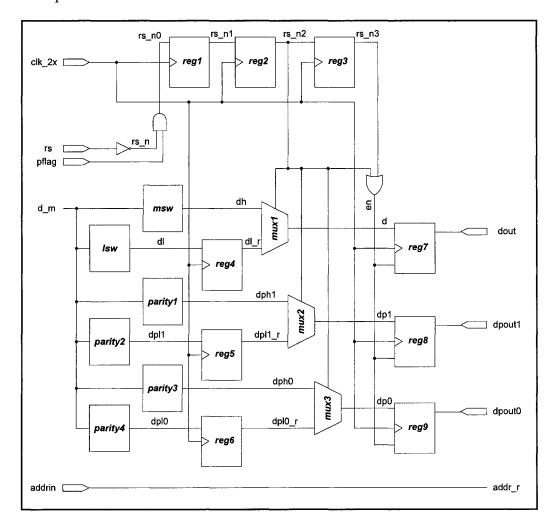

| FIGURE 28. | MDG-HDL MODEL FOR THE READ PORT OF THE MODIFIED LA-1 RTL DESIGN82                                                                         |

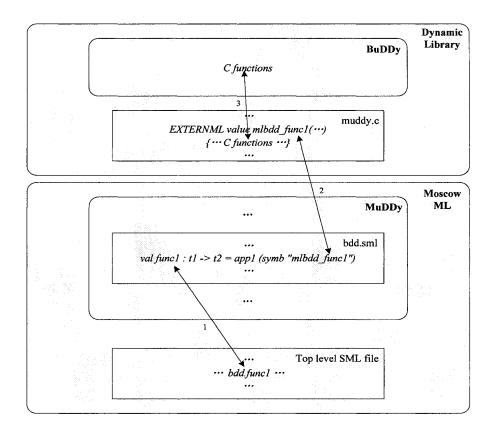

| FIGURE 29. | MUDDY IN MOSCOW ML SYSTEM                                                                                                                 |

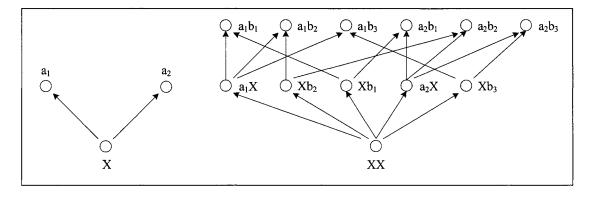

| FIGURE 30. | Partial orders over $\{a_1, a_2, X\}$ and $\{a_1, a_2, X\} \cdot \{b_1, b_2, b_3, X\}$ 92                                                 |

| FIGURE 31. | COMPLETE LATTICES $(\{a_1, a_2, X\} \cup \{T\}, \leq_{mdg})$ AND $(\{a_1, a_2, X\} \cdot \{b_1, b_2, b_3, X\} \cup \{T\}, \leq_{mdg})$ 93 |

| FIGURE 32. | MDG_STE ALGORITHM IN THE MDG-STE ENGINE                                                                                                   |

| FIGURE 33. | DIAGRAM FOR A MDG-HDL MODEL OF A SEQUENTIAL CIRCUIT100                                                                                    |

## LIST OF TABLES

| TABLE I.   | DEFINING SYMBOLIC TRAJECTORY OF THE ANTECEDENT                | 39  |

|------------|---------------------------------------------------------------|-----|

| TABLE II.  | SYMBOLIC DEFINING SEQUENCE OF THE CONSEQUENT AND COMPARISON   | 39  |

| TABLE III. | STATISTICS FOR AHMED'S LA-1 RTL DESIGN VERIFICATION USING STE | 53  |

| TABLE IV.  | VERIFICATION STATISTICS FOR THE $L_{ m MDG}$ PROPERTIES       | 85  |

| TABLE V.   | SYMBOLIC DEFINING TRAJECTORY OF THE ANTECEDENT                | 101 |

| TABLE VI.  | SYMBOLIC DEFINING SEQUENCE OF THE CONSEQUENT AND COMPARISON   | 101 |

### LIST OF ACRONYMS

ABV Assertion-Based Verification

AP Atomic Proposition

ASM Abstract State Machine

BDDs Binary Decision Diagrams

CAM Content Addressable Memory

CTL Computation Tree Logic

DAG Directed Acyclic Graph

DF Directed Formula

DLL Delay-Locked Loop

LA-1 Look-Aside Interface

LTL Linear Temporal Logic

MDGs Multiway Decision Graphs

ML Meta Language

NPU Network Processing Unit

PSL Property Specification Language

QDR Quad Data Rate

SML Standard Meta Language

SoC System-on-Chip

STE Symbolic Trajectory Evaluation

# Chapter 1

## Introduction

System-on-Chip (SoC) design becomes more complex with the increasing amount of different kinds of IPs on the chip. How to ensure correctness of functionality in an SoC chip is one of the biggest challenges in SoC designs. Any SoC verification plan must cover the verification of the individual cores as well as that of the whole chip. The better knowledge of the external interfaces of each IP and their interactions with the SoC, the more complete the SoC verification will be. That is why people are putting more and more focus on the verification of different interfaces for SoC design. As for the SoC verification methods, basically there are no new relevant techniques which are different from what we have applied to the ASIC verification but just some adapted methodologies, like assertion based verification, theorem proving, model checking, etc. In this thesis, we are interested in two model checking techniques: Symbolic Trajectory Evaluation (STE) and model checking based on Multiway Decision Graphs (MDGs).

Model checking is a formal method for automatically verifying correctness of finite state transition systems, which has been studied since early 1980's and several important results of which have been established [18] [8]. These early model checking techniques were attractive because of their high automation and little requirement for human effort to guide the proof process, whereas they usually suffer from the state explosion problem and the size of the transition systems that could be verified were very limited. The

introduction of Bryant's Binary Decision Diagrams (BDD's) [20] into the original model checking algorithms led to a breakthrough in the size of transition systems that could be handled. A number of researchers have explored this BDD-based symbolic technique in the field of model checking and have published results of separate studies [17][24][13][14]. These symbolic model checking techniques provided exhaustive verification of a system by implicitly representing a state space through the use of a symbolic representation [12], and could deal with larger designs than traditional model checking techniques. However these BDD-based techniques were still not powerful enough for many real systems, when their models were larger than 100000 states [25], due to the state explosion problem.

Two model checking approaches: Symbolic Trajectory Evaluation and MDG-based model checking have been proposed to improve the traditional BDD-based symbolic model checking approaches.

Symbolic Trajectory Evaluation is a symbolic simulation based bounded model checking approach devised by Bryant and Seger [23]. By complementing the exhaustive analytical capabilities symbolic checking with the circuit of model modeling/manipulation methods of symbolic quaternary simulation, which gives STE the desirable property that the number of variables needed for the BDD's in an STE run depends only on the assertion being checked, not on the size of the circuit, STE effectively overcomes the state explosion problem and can verify much larger circuits, although it has its own limitation on the kind of properties it can handle. It's widely used at Intel, Compaq, IBM, and Motorola. At Motorola, it has been used to verify several memory units, some with millions of transistors [22]. Also in [16] [42] STE has been used to verify CAMs (Content Addressable Memories) and PowerPC microprocessors.

The MDG-based model checking approach was proposed by Corella et al. in 1997 [10]. An MDG is an extended BDD-like data structure with arbitrary number of children for each node and with much more powerful labeling capability for both the nodes and the edges. BDDs can be viewed as a special case of MDGs. In this MDG-based approach, data signals are denoted by abstract variables instead of Boolean variables, and data operators are represented by uninterpreted or partially interpreted function symbols instead of Boolean functions. Thus, the verification based on abstract implicit state enumeration can be carried out independently of data path width, which therefore can effectively alleviate the state explosion problem.

The Symbolic Trajectory Evaluation technique and MDG-based model checking technique improve the traditional BDD-based symbolic model checking approaches in two different ways: the first one can dramatically reduce the computations for the next state space and enhance the computational efficiency, while the latter one can simplify the data path operations and thus can effectively alleviate the state explosion problem. This observation led to the idea of combining these two techniques, which makes it possible for us to take the advantages of both of them. The basic idea of such a combination is to replace the use of the BDDs with the MDGs for the encoding of the symbolic expressions and to implement the STE algorithm at a higher level of abstraction which can further alleviate the state explosion problem in STE. This combined approach will be discussed in detail in a later chapter of this thesis.

## 1.1 Background

#### 1.1.1 Model Checking

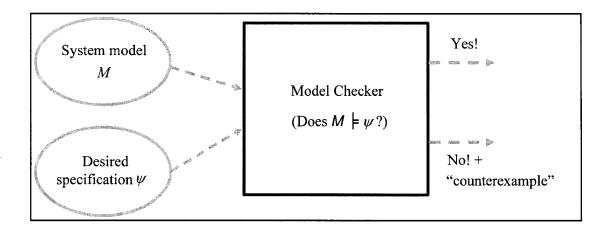

Figure 1. Model checking process

Typically a model checking process involves three major aspects: system modeling, a specification language and a model checking algorithm, shown in Figure 1.

The first step in model checking a design is to develop a formal model, usually expressed as a finite state transition system, for the circuits under study. The desired specifications of the design (properties) are captured by a specification language based on temporal logic. A model-checking tool accepts the system model and specifications. By exhaustively exploring the state space of the state transition system, the tool then returns "yes" if the given model satisfies the given specifications and "no" with a counterexample otherwise. The counterexample demonstrates how the error occurs. The termination of model checking is guaranteed by the finiteness of the model.

#### 1.1.1.1 Modeling

A finite state transition system can be described as a Kripke structure: M = (S, SI, T, L), where

- S: a finite set of states,

- $SI \subseteq S$ : the set of initial states,

- $T \subseteq S \times S$ : a transition relation with  $\forall s \in S \ (\exists s' \in S \ ((s,s') \in T))$ ,

- L:  $S \to 2^{AP}$ : a labeling function, associating each state with a set of atomic propositions (APs).

Note that every state must have a successor in T, which means that it is always possible to have an infinite sequence of states in the Kripke structure.

A path is an infinite sequence of states such that each state is related to its successor by the transition relation.

Atomic propositions represent the basic properties that hold in the associated states.

#### 1.1.1.2 Specification Languages

The properties of a design are expressed as temporal logic formulas [2][15]. Temporal logic is a kind of logic which views time as a sequence of states. Linear Temporal Logic (LTL) and Computation Tree Logic (CTL) or *branching time logic* are two most commonly used temporal logics in the context of model checking. LTL expresses temporal properties over a linear execution sequence, i.e. a single sequence of states, of the state transition system. CTL, on the other hand, can express properties across several different sequences of states simultaneously.

Temporal logics use atomic propositions as their building blocks and combines theses propositions into formulas using logical operators and temporal operators. Atomic propositions (p, q, ...) are variables which can either be true or false. The logical operators used in temporal logic formulas are the usual connectives:  $\neg$ ,  $\lor$ ,  $\land$ ,  $\rightarrow$  and  $\leftrightarrow$ . The temporal operators are classified into two groups: state operators and path operators. State operators are used to select states: Gp ("always p", "globally p"), Fp ("sometime p", "finally p"), Xp ("nexttime p") and pUq ("p until q"). Path operators are used to select paths: A ("all paths"), E ("there exists a path").

Note that path operators are only applied to CTL formulas since in LTL there is no concept of branching and hence no need for selecting paths. We can say that the absence of A and E path operators in LTL formulas which reflects the linear-time paradigm (as opposed to branching-time paradigm in CTL) is the major difference between LTL and CTL.

The model M defined in previous section can be viewed as a temporal model where each state represents a point in time. Within each state, atomic propositions are true or false; hence a temporal logic formula can be evaluated to true or false from its subformulas in a recursive fashion until reaching atomic propositions. Note that a temporal logic formula that is true in some states might not hold in other states for a given model.

A temporal formula p is satisfied by a model M = (S, SI, T, L) if it is true for all the initial states SI of the model, i.e.  $SI \subseteq \{s \in S \mid M, s \neq p\}$ . The recursive definition of  $\not\models$  for a CTL formula is as following:

•  $M, s_0 \models p \text{ iff } p \in L(s_0).$

- M,  $s_0 \models \neg p$  iff not M,  $s_0 \models p$ .

- M,  $s_0 \models (p_1 \land p_2)$  iff M,  $s_0 \models p_1$  and M,  $s_0 \models p_2$ .

- M,  $s_0 \models AXp$  iff for all states  $s_0'$  with  $(s_0, s_0') \in T$ , M,  $s_0' \models p$ .

- M,  $s_0 \models EXp$  iff for some state  $s_0'$  with  $(s_0, s_0') \in T$ , M,  $s_0' \models p$ .

- M,  $s_0 \models A[p_1 \cup p_2]$  iff for all paths  $(s_0, s_1,...)$ , there exists an  $j \ge 0$  with M,  $s_j \models p_2$ , and M,  $s_i \models p_1$  holds for all  $0 \le i < j$ .

- M,  $s_0 \models E[p_1 \cup p_2]$  iff for some path  $(s_0, s_1,...)$ , there exists an  $j \ge 0$  with M,  $s_j \models p_2$ , and M,  $s_i \models p_1$  holds for all  $0 \le i < j$ .

#### 1.1.1.3 Model Checking Algorithms

A Model checking algorithm is used to decide if a system satisfies a temporal property and generates a counterexample otherwise. Different temporal logic model checking algorithms have been devised to target LTL model checking and CTL model checking.

The complexity of model checking algorithms with temporal logics have been studied since early 1980's and several important results have been established.

In 1985 Pnueli and Lichtenstein [18] presented a model checking algorithm with linear time temporal logic formulas and the complexity of this algorithm was shown to be exponential in the length of the formula but linear in the size of the transition system.

Clarke, Emerson and Sistla [8] devised an algorithm for CTL model checking and the complexity of the algorithm was proved to be linear in the length of the formula and also linear in the size of the transition system.

Another type of branching-time logic is CTL\*, introduced by Clarke, Emmeson and Sistla[8], which combined CTL and LTL and could be checked with the same time complexity as the LTL formulas.

These early model checking algorithms are so-called state exploration algorithms which require explicitly constructing the state graph of the circuit under study and a complete exploration of the state space. They were attractive because of their high automation and little requirement for human effort to guide the proof process, whereas they usually suffered from the state explosion problem and the size of the transition systems that could be verified by them were very limited.

Several techniques were developed to overcome this problem in certain aspects, among which symbolic algorithms have shown great success.

#### 1.1.2 BDDs

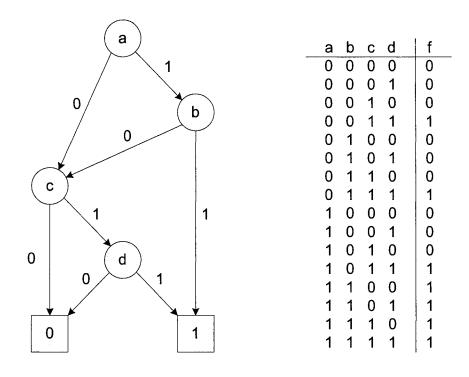

A Binary Decision Diagram is a data structure which allows us to represent a Boolean function as a rooted acyclic-directed graph where each non-terminal vertex is labeled by a variable and has two directed edges, labeled 0 and 1, respectively. Terminal vertices are labeled either 0 or 1. Figure 2 shows a BDD for the function  $f(a, b, c, d) = (a \land b) \lor (c \land d)$  with a truth table representing this function at the right.

To evaluate the represented Boolean function for a given valuation of the function arguments, a path is traced in the BDD from the root vertex down to a terminal by taking at each vertex the edge labeled with the value of the labeling variable of this vertex. The value of the labeling variable of the terminal reached by this path defines the value of the Boolean function under the current valuation. For example, to evaluate f(a=0, b=1, c=1, d=1), start at the root a, traverse down the edge labeled 0 to c, then down two edges labeled 1 until reach the terminal labeled 1, which means that the value of f is 1 with respect to the valuation (a=0, b=1, c=1, d=1).

Figure 2. BDD and true table for function  $f(a, b, c, d) = (a \land b) \lor (c \land d)$

As shown by Bryant [20], a reduced ordered BDD offers a canonical representation of a given Boolean function, in other words, every Boolean function can be represented by a unique reduced BDD for a given ordering of the input variables. By using reduced ordered BDD's, a set of algorithms can be developed for manipulating Boolean functions with a high degree of efficiency.

#### 1.1.3 Symbolic Model Checking

The basic idea of symbolic model checking is to represent the state space symbolically. Burch, Clarke, McMillan, and Dill [14] presented a symbolic CTL model checking algorithm to verify sequential circuits, where the transition relation for the entire system is represented symbolically as a characteristic function of all of state variables in the system. By manipulating the BDD representations of the state space and the temporal

formula, model checking can be performed with efficient algorithms existing for BDD-Based Boolean Manipulation.

The strength of this algorithm stems from the fact when this symbolic representation captures the right structural uniformities in the graph, it is much smaller than an explicit table of all of the states [13], and thus it can be applied to verify some very large sequential circuits.

However, this method can not be generally applied to verify all the large circuits with complex data paths, and in many cases it will still have the state explosion problem. Another drawback of the algorithm is that it can be very computationally consuming to generate this characteristic function [23].

#### 1.1.4 MDGs

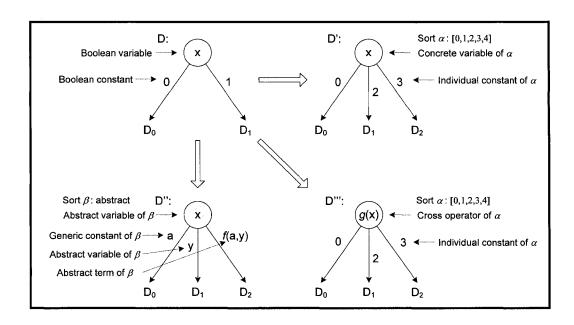

MDGs can be viewed as a generalization of BDDs. BDDs offer representations of Boolean formulas. Graph D in Figure 3 depicts the BDD for the Boolean formula  $(\neg x \land F_0) \lor (x \land F_1)$ , where  $F_0$  and  $F_1$  are the Boolean formulas represented by the subgraphs  $D_0$  and  $D_1$  respectively.

Alternatively, graph D can be viewed as representing a formula  $((x=0) \land F_0) \lor ((x=1) \land F_1)$  in a many-sorted first-order logic. More generally, node a can range over a larger set of values than  $\{0,1\}$  and can even range over abstract terms. It is also possible that a cross operator can be a decision node in a generalized decision graph. The definitions of an abstract term and a cross operator can be found in Chapter 4 where more details about the many-sorted first-order logic and MDGs are presented.

Figure 3. From BDDs to MDGs

Three possible generalizations of BDD D and the corresponding formulas are shown in Figure 3 and below, where  $F_0$ ,  $F_1$  and  $F_2$  are first-order formulas represented by the sub-graphs  $D_0$ ,  $D_1$  and  $D_2$  respectively:

- From D to D':  $x \in \{0,1\} \to x \in \{0,2,3\}$ , and Graph D' represents the formula  $((x=0) \land F_0) \lor (x=2) \land F_1) \lor (x=3) \land F_2).$

- From D to D'':  $x \in \{0,1\} \to x \in \{a, y, f(a, y)\}$ , and Graph D'' represents the formula  $((x = a) \land F_0) \lor (x = y) \land F_1) \lor (x = f(a, y)) \land F_2).$

- From D to D''':  $x \in \{0,1\} \to g(x) \in \{0,2,3\}$ , and Graph D''' represents the formula  $((g(x) = 0) \land F_0) \lor (g(x) = 2) \land F_1) \lor (g(x) = 3) \land F_2).$

The above generalized decision graph D, D' and D'" are examples of Multiway Decision Graphs (MDGs).

### 1.2 Thesis Contributions

The main contributions of the thesis are as follows:

- We investigated the underlying theory and methodology of Symbolic Trajectory

Evaluation (STE) and MDG-based model checking techniques by a detailed case

study for each of them.

- We proposed a hybrid approach of performing first-order Symbolic Trajectory

Evaluation using MDGs, which can not only increase the scale of circuits that can be

verified using STE but also improve the performance of STE by raising the level of

abstraction.

## 1.3 Scope of Thesis

Symbolic Trajectory Evaluation (STE) and MDG-based model checking are two model checking techniques which improve the traditional symbolic model checking approaches in two different ways. The aim of this thesis is to investigate the possibility of using MDGs to perform STE. The motivation of combining these two techniques is to develop a more powerful model checking technique which will take the advantages of both of them.

The rest of the thesis is organized as follows:

In Chapter 2, we study the underlying theory and methodology of Symbolic Trajectory Evaluation, provide an illustrative example of this approach, and describe an STE-based verification tool.

Chapter 3 provides a case study of STE. We first make a brief introduction to the Look-Aside Interface (LA-1), and then, after the discussion of some related work including a previous RTL design for the LA-1 interface, present a modified RTL design for the LA-1 interface. Finally, the verification processes of both the designs using STE are illustrated followed by experimental results.

Chapter 4 introduces the theoretical foundations and methodology of MDG-based model checking followed by an illustrative example, and discusses MDG-based model checking tools.

In Chapter 5, we use the MDG tools to verify the same properties of the LA-1 Interface. Our goal is to compare the two methods and prepare the ground for our proposal to define a symbolic trajectory evaluation in MDG. This experiment involves a mapping from STE assertions to  $L_{\rm MDG}$  properties. We will provide a method to perform this mapping. Experimental results are given at the end of this chapter.

Based on the exploration of STE and MDG-based model checking through case studies, in Chapter 6, we describe two attempts to combine these two model checking techniques: one in the STE verification environment and the other in the MDG tools. We focus on the second attempt and propose a hybrid approach of performing first-order Symbolic Trajectory Evaluation in the MDG tools.

Finally, in Chapter 7, we conclude this thesis and present the future work.

# Chapter 2

# **Symbolic Trajectory Evaluation**

This chapter describes the underlying theory and methodology of Symbolic Trajectory Evaluation (STE), a symbolic simulation based bounded model checking technique. Firstly, lattice and symbolic simulation are described, which are the theoretical foundations of STE. Next, the chapter discusses in detail the modeling, specification language and verification methodology of STE, followed by an illustrative example. An STE-based verification tool is described at the end.

#### 2.1 Basics

Symbolic Trajectory Evaluation is a symbolic simulation based bounded model checking approach devised by Bryant and Seger [23], which relates most closely to the symbolic model checking algorithm proposed by Bose and Fisher [24]. In Bose and Fisher's algorithm, an explicit representation of the next state function for every state variable in the system is extracted using symbolic simulation. In one simulation run, each state variable and each input signal is represented by a distinct Boolean variable, and a Boolean representation of the next state behavior is computed. A temporal logic formula can then be checked using symbolic Boolean manipulation. This extraction process for the explicit next state function can be quite costly [23].

What distinguishes STE from Bose and Fisher's method and other symbolic model checking algorithm is its representation of state space and the next state behavior.

- The state space is represented using a lattice-based model.

- The next state function is represented implicitly as a result of combining the circuit structure and the simulation algorithm, and the next state behavior is computed only for the particular patterns required for the verification of a given assertion.

These particular patterns involve far fewer variables than is required in Bose and Fisher's method [23]. The strength of STE comes largely from the fact that the complexity of an STE run depends only on the complexity of the STE assertion itself rather than that of the circuit being checked. STE offers an effective alternative to classical symbolic model checking techniques which often suffer from state explosion and hence can verify much larger circuits, although it has its own limitation on the kind of properties it can handle.

#### 2.1.1 Lattice

In this thesis, we view a lattice as a partially ordered set. The discussion of other uses of lattice is outside the scope of this thesis and will not be included here.

A partial order is a binary relation on a set which is reflexive, antisymmetric, and transitive. Given a partial order R on a set S, for all  $a, b, c \in S$ , we should have:

- a R a (reflexivity),

- $(a R b \text{ and } b R a) \rightarrow a = b \text{ (antisymmetry)}, \text{ and}$

- $(a R b \text{ and } b R c) \rightarrow a R c \text{ (transitivity)}.$

This partial order relation formalizes the intuitive concept of an ordering of the set elements, which represents a hierarchy of information or knowledge. More specifically, the higher order an element has, the more information it contains. The 'partial' here indicates that such an ordering does not necessarily need to be total, that is, not all pairs of elements in the set are mutually comparable.

We call a set with a partial order a partially ordered set.

**Definition 2.1.1.1:** A partially ordered set  $(L, \leq)$  [9] is a lattice if for any elements a and b of L, the set  $\{a, b\}$  has both a least upper bound (join) and a greatest lower bound (meet), where L is the so called ground set and  $\leq$  is the partial order.

The join of a and b is denoted by  $a \lor b$ , and the meet is denoted by  $a \land b$ , where  $\land$  and  $\lor$  are binary operations.

**Definition 2.1.1.2:** A complete lattice is a partially ordered set  $(L, \leq)$  which has both a greatest lower bound (meet) and a least upper bound (join) for every subset A of L, denoted by glb(A) and lub(A), respectively.

In other words, a complete lattice is a complete relation with a bound on every subset. Note that each complete lattice has a unique greatest element (often called universal upper bound) and a unique least element (often called universal lower bound). A complete lattice is a special case of lattices.

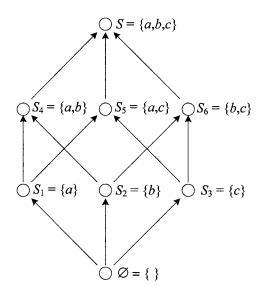

The power set (the collection of all subsets) of a given set S forms a complete lattice using "subset of" as the ordering relation  $\leq$ . Meet and join of subsets can be obtained by the set operations intersection and union, respectively. In this class of lattices, the empty set is least element, and S is greatest element. A lattice based on the power set of  $\{a,b,c\}$  is shown in Figure 4. A diagram of a partial order that leaves out the transitive relations is referred as a Hasse diagram. The ground set L of this lattice is  $\{\emptyset, S_1, S_2, S_3, S_4, S_5, S_6, S\}$ . The ordering of these elements is listed below:

•  $\emptyset \leq S_1, \emptyset \leq S_2, \emptyset \leq S_3$ ;

- $\bullet \quad S_1 \leq S_4, S_1 \leq S_5;$

- $S_2 \leq S_4, S_2 \leq S_6$ ;

- $S_3 \leq S_5, S_3 \leq S_6;$

- $S_4 \leq S$ ;

- $S_5 \leq S$ ;

- $S_6 \leq S$ ;

Figure 4. Lattice structure for the power set of {a,b,c}

The ordering relation is represented by a directed edge pointing from the element with lower order to the one with higher order. Note that there is no ordering relation applied to the element pairs of  $\{S_1, S_2\}$ ,  $\{S_1, S_3\}$ ,  $\{S_2, S_3\}$ ,  $\{S_4, S_5\}$ ,  $\{S_4, S_6\}$  and  $\{S_5, S_6\}$ , since the two elements in each of the above pairs are not mutually comparable under the relation "subset of", which reflects the "partial" feature of this ordering.

It is not hard to tell from the diagram that each of the  $2^8$  subsets of L has a unique least upper bound and a unique greatest lower bound.

#### 2.1.2 Symbolic Simulation

In digital hardware verification, the term simulation is referred to a modeling technique which describes the state transitions, inputs and outputs of a digital system. Simulators are often used to test logic designs before constructing the real hardware.

Figure 5 illustrates a simulator example of a 5-input OR gate. During simulation, a sequence of input patterns 01100, 10011, ... are fed into the input ports of the simulator which models the behavior of the circuit, and the corresponding output response patterns are sampled and checked against the expected values at the output ports of the simulator. A single run of this simulator can only determine the behavior of the OR gate, that is the output response in this case, for a single input pattern. In order to verify this 5-input OR gate exhaustively, we need 32 (2<sup>5</sup>) test patterns to cover all the possibilities of the input signals and, therefore, need 32 simulation runs

The number of the required test patterns for exhaustive verification will grow exponentially with the number of input signals. In this case of sequential circuit simulation, the situation will be even worse. We need to take into consideration not only the input sequence but also the initial state of the system. Thus, simulation is only applicable for verifying very small systems, the limitation of which comes from the stimulus generation and simulation runtime.

Symbolic simulation is a promising method to generalize the traditional simulation technique and make it feasible to larger systems. A symbolic simulator resembles a traditional simulator, except that it simulates the design using Boolean variables instead of constant binary values at the inputs of the circuit model.

Figure 5. Simulator for a 5-input OR gate

During simulation the values of the circuit state and the circuit output are represented as Boolean functions over these initial variables. At the same time, logic operations, such as AND, OR and NOT, should be refined to operate over Boolean functions rather than over the constants 0 and 1. At the end of each simulation run, a set of Boolean functions representing implicitly all set of states that are reachable by the current circuit state in one clock cycle for the input variables can obtained by manipulating Boolean operations, and so can the Boolean functions for the outputs. This method allows all the next state behaviors of a circuit in a specific state under all possible inputs to be verified with a single simulation run simultaneously. In other words, a single symbolic simulation run can compute information that would otherwise need to be obtained by multiple traditional simulation runs.

The symbolic simulator of the same 5-input OR gate is shown in Figure 6. The input signals of the simulator are represented by Boolean variables a, b, c, d and e, respectively. The output of the simulator is a Boolean function over these five variables. In this case, we only need 1 symbolic test pattern, abcde, to verify this 5-input OR gate exhaustively.

Figure 6. Symbolic simulator for a 5-input OR gate

One problem with symbolic simulation is that it needs to exhaustively manipulate the circuit functionality and requires extensive manipulation of Boolean expressions.

Ternary simulation [21] is another generalized simulation approach, in which three-valued logic is used instead of two-valued logic. Three-valued logic extends the existing 1 (true) and 0 (false) values in two-valued logic with an unknown or "don't care" value X. In order to perform ternary simulation, functions defined over Boolean values {0, 1} need to be extended to ones defined over ternary values {0, 1, X}. The extensions should obey the following rule: if a circuit node is computed to be either 0 or 1, this result will not change if the X's contained in the stimulus pattern are replaced partially or completely by 0 or 1. This extension rule guarantees that the simulator of a circuit will produce the same response to a certain input pattern even if some bits of it are set to X. As an example, the truth tables of some Boolean operations and their ternary extensions are shown in Figure 7.

Since each use of value X covers two cases of using 0 and 1 in ternary simulation, the number of test patterns required to verify a circuit will be reduced dramatically by introducing X's when applicable. Take the same 5-input OR gate discussed above as an

example. The ternary simulator model and the corresponding truth table of it are given in Figure 8. Compared with the 32 test patterns required by the traditional simulation, only six test patterns, XXXX1, XXX1X, ..., 1XXXX and 00000 are needed to do the exhaustive verification of this 5-input OR gate using ternary simulation. The strength of this approach stems from its computational efficiency.

Figure 7. True tables of Boolean operations and the ternary extensions

Figure 8. Ternary simulator model for a 5-input OR gate

Note that the use of X value may cause information loss of the circuit. Let us take a look at the 5-input OR gate model in Figure 8 again. When four of the inputs are set to 0, the attempt to set the left input to X will lead to an X value at the output of the simulator, a meaningless result in verification. To avoid this, we have to be careful with our choice of using X values in the simulation.

Symbolic simulation and ternary simulation improve the performance of traditional simulation technique in two different ways. Symbolic simulation can dramatically cut down the number of required stimulus patterns and, therefore, the number of simulation runs at the price of increasing the computation complexity and the memory usage. Ternary simulation, on the other hand, can significantly enhance the computational efficiency, but may have the problem of information loss in some cases. If we can combine these two techniques, it is possible for us to take the advantages of both of them. A successful attempt was made by Beatty, Bryant and Seger [5], whose approach is named ternary symbolic simulation.

The key idea of this ternary symbolic simulation approach is to parameterize ternary values by Boolean variables, which can further reduce the number of required test patterns. Figure 9 illustrates how the six test patterns required by the 5-input OR gate ternary simulator are compressed to one symbolic pattern in ternary symbolic simulation.

First, we index the six scalar patterns with numbers from 0 to 5, which are then encoded with three ( $\lceil \log(5+1) \rceil$ ) Boolean variables  $t_0$ ,  $t_1$  and  $t_2$ . Next, for each input of the 5-input OR gate, we represent the six ternary values gathering from the corresponding bits of the six test patterns as a function pair (high, low) over these three variables. Function "high" and "low" indicate the positions of value 1 and 0, respectively, and the

unrepresented positions are of value X. Thus, in our example, we have one symbolic test pattern consisting of five function pairs over three variables to replace all the six scalar test patterns. The output of the ternary symbolic simulator is also a (high, low) function pair.

Figure 9. Ternary symbolic simulator for a 5-input OR gate

Recalling the 32 test patterns required for the traditional simulator of 5-input OR gate, 1 symbolic test pattern over 5 variables for the symbolic simulator and 6 ternary test patterns for the ternary symbolic simulator, our ternary symbolic simulator has the best performance among all these simulators.

Note that reduced ordered BDDs can also be applied in ternary symbolic stimulation, since ternary values are manipulated implicitly via binary encodings mentioned above.

Note also that the above ternary symbolic simulation approach just shows us one of the ways to combine ternary modeling technique with symbolic simulation and in practice we may have our own ways to do the combination depending on the applications.

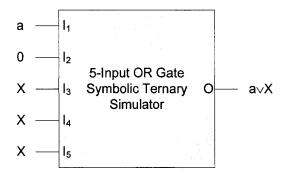

Figure 10. Symbolic tenary simulator for a 5-input OR gate

Another possible way to symbolize the ternary simulation is to partially symbolize the test patterns using ternary variables and ternary constant. An example of a partially symbolized test pattern for the 5-input OR gate is shown in Figure 10, where input signal  $I_1$  is represented by variable 'a' over ternary values  $\{0, 1, X\}$ , input  $I_2$  is represented by ternary constant 0, and input  $I_3$ ,  $I_4$  and  $I_5$  are all represented by ternary constant X. This partially symbolized test pattern covers three possible ternary test patterns: X0XXX, 00XXX and 10XXX, and the corresponding outputs of the circuit will be of values X, X and 1 respectively.

Note that for some special simulators, the "don't care" value X appearing at the output of a gate may have specific meaning for the verification and should not be deemed as meaningless.

# 2.2 Modeling

Symbolic trajectory evaluation (STE) extends symbolic simulation with some of the analytic capability of temporal logic model checking techniques [6]. As in a model checking approach, STE also develops a formal model for the circuit under verification,

but different from the temporal logic model checkers, it uses a lattice-based model instead of a Kripke structure.

The lattice-based model in STE is a tuple  $M = [(S, \leq), Suc]$ , where:

- S is a set of finite states,

- $\leq$  is a partial order over S,

- $(S, \leq)$  is a complete lattice,

- Suc:  $S \rightarrow S$  is the next state function, monotone with respect to  $\leq$ .

A function between ordered sets is monotone if it preserves the given order. For function Suc, whenever  $s_i \leq s_j$  and  $s_i, s_j \in S$ , then  $Suc(s_i) \leq Suc(s_j)$ .

The state space  $S = \{0, 1, X\}^n$  is a set of n-length vectors over ternary values for some natural number n. The partial order  $\leq$  is defined over  $\{0, 1, X\}$  first and extended to  $\{0, 1, X\}^n$ . Figure 11 illustrates the partial orders over  $\{0, 1, X\}$  and  $\{0, 1, X\}^2$ .

Figure 11. Partial orders over  $\{0, 1, X\}$  and  $\{0, 1, X\}^2$

According to the definition of complete lattice,  $(\{0, 1, X\}^n, \leq)$  is not a complete lattice, since not every subset of  $\{0, 1, X\}^n$  has a least upper bound. In order to make  $(S, \leq)$  a complete lattice, we introduce a top element T to the state set S. We use T to

represent a unique "overconstrained" state [4], where some node of the state vector is set to both 0 and 1 at the same time. Thus, the state set  $S = \{0, 1, X\}^n \cup \{T\}$  and the partial order  $\leq$  form a complete lattice with T as the universal upper bound and  $\bot = X, ..., X$  as the universal lower bound. The Hasse diagrams of complete lattices ( $\{0, 1, X\} \cup \{T\}, \leq$ ) and ( $\{0, 1, X\}^2 \cup \{T\}, \leq$ ) are shown in Figure 12.

Figure 12. Hasse diagrams of complete lattices ( $\{0,1,X\} \cup \{T\}, \leq$ ) and ( $\{0,1,X\}^2 \cup \{T\}, \leq$ )

The next state function Suc:  $\{0, 1, X\}^n \cup \{T\} \rightarrow \{0, 1, X\}^n \cup \{T\}$  is used to compute constraints on the possible values of the successor states of the current states. In other words, for a given state  $s \in S$ , function Suc(s) computes the least specified (most general) successor state the system can be in one time step later. The "least specified (most general)" is defined by the partial order  $\leq [4]$ . As mentioned in previous section, in a partially ordered set, the lower order an element has, the less specified it is. In this sense, for example, value X is less specified than values 0, 1 and T in the complete lattice ( $\{0, 1, X\} \cup \{T\}, \leq$ ). Note that the constraints computed by the next state function are the ones

imposed by the circuit itself and are irrelevant to the circuit inputs which are controlled externally.

For a given state vector  $s = c_0 c_1 \dots c_{n-2} c_{n-1} \in S$ , the next state function Suc(s) is actually a vector of next state functions for each node (component) of s, i.e.,  $Suc(s) = t_0(c_0)t_1(c_1)\dots t_{n-2}(c_{n-2})t_{n-1}(c_{n-1})$ , where  $c_i$ :  $\{0, 1, X\}^n \to \{0, 1, X\}$  for  $1 \le i \le n-1$ . If node  $c_i$  is associated with an input of the circuit, the next state function  $t_i(c_i) = X$ , and otherwise  $t_i(c_i)$  is determined by the circuit structure. A constraint of value X indicates that no constraint is imposed on that node. For the state vector T, the next function Suc(T) equals T.

The next state function works like a filter that can filter out irrelevant sequences of states which are not useful for reasoning about model behaviors. We call these useful sequences trajectories. Formally, given a model  $M = [(S, \leq), Suc]$ , an infinite sequence  $(s_0, s_1, s_2,...)$  of states of S is a trajectory iff

$$Suc(s_i) \le s_{i+1}$$

for  $i \ge 0$ .

The set of all trajectories of model M is denoted as J(M).

# 2.3 Specification Language

In STE, a design specification is expressed as a trajectory assertion in a restricted temporal logic. A trajectory assertion is of the form  $[Ante \rightarrow Cons]$ , where both Ante and Cons are trajectory formulas. The main verification task is to evaluate whether or not every trajectory satisfying Ante (called the antecedent) also satisfies Cons (called the consequent).

The basic component of a trajectory formula is a simple predicate. Given a model  $M=[(S,\leq), Suc]$ , a predicate over S is a function that maps S to a special complete lattice containing only two elements false and true, with element false as the universal lower bound and element true as the universal upper bound. A predicate  $\rho$  over S is called simple if it is monotone and there exists a unique element  $d_{\rho}$  in S such that for all  $s \in S$  with  $d_{\rho} \leq s$ ,  $\rho(s) = true$ . The  $d_{\rho}$  here is called the defining value of predicate  $\rho$ .

**Definition 2.3.1:** If we denote a set of simple predicates over S by P, a trajectory formula of model M is then defined inductively as below:

- A simple predicate  $\rho \in P$  is a trajectory formula.

- The conjunction  $(f_1 \wedge f_2)$  is a trajectory formula if both  $f_1$  and  $f_2$  are trajectory formulas.

- The domain restriction (b → f) is a trajectory formula if b is Boolean constant 0 or 1

and f is a trajectory formula.

- The next time expression (Nf) is a trajectory formula if f is a trajectory formula and

N is the next-time operator.

If a trajectory formula f of model M is satisfied by a trajectory  $a = (a_0, a_1, a_2, ...)$  of the same model, we write  $a \models_M f$ . The satisfaction relation  $\models_M$  is defined as follows:

- $a \models_M \rho \text{ iff } \rho(a_0) = \text{true.}$

- $a \models_M (f_1 \land f_2)$  iff  $a \models_M f_1$  and  $a \models_M f_2$ .

- $a \models_M (1 \rightarrow f) \text{ iff } a \models_M f;$

- $a \models_M (0 \rightarrow f)$  always holds.

- $a \models_M (\mathbf{N}f)$  iff  $(a_1, a_2, ...) \models_M f$

### 2.4 Verification Methodology

The definition of simplicity can be extended directly from predicates to formulas. A formula f of model M is called simple if it is monotone and there exists a unique trajectory  $\alpha_f$  in M, called defining trajectory of formula f, such that for all  $a \in J(M)$  with  $\alpha_f \leq a$ ,  $a \models_M f$  holds. We will see later that trajectory formulas are simple and we can construct the defining trajectory for every trajectory formula. Thus, the main verification task that checks whether or not every trajectory satisfying Ante also satisfies Cons can be implemented in this way: compute the defining trajectory for the trajectory formula Ante first, and then verify that this defining trajectory satisfies trajectory formula Cons.

Before constructing a defining trajectory for a given trajectory formula f in M, we will first show how to construct its defining sequence  $\beta_f$ . This sequence should be the least possible sequence in M that satisfies f, i.e., for all sequence a with  $\beta_f \leq a$ ,  $a \models_M f$  holds.

**Definition 2.4.1:** Given a model  $M = [(S, \leq), Suc]$  and a set P of simple predicates over S, the recursive definition of the defining sequence  $\beta_f$  of a trajectory formula f in M is as following:

- $\beta_{\rho} = d_{\rho} \perp \perp \dots$  if  $d_{\rho}$  is the defining value of  $\rho \in P$ .

- $\beta_{f_1 \wedge f_s} = \text{lub}(\beta_{f_1}, \beta_{f_2})$ , where *lub* is the lowest upper bound function.

- $\beta_{(b \to f)} = b? \beta_f$ , where b is a Boolean constant, "?" is an infix "multiplexing" function, and  $b? \beta_f = \begin{cases} \beta_f & \text{if } b = 1 \\ \bot \bot \dots & \text{otherwise} \end{cases}$ .

•  $\beta_{Nf} = \perp \beta_f$ .

It can be proved [4] that for any given trajectory formula f in M and its defining sequence  $\beta_f$  constructed as above,

$$a \models_M f \Leftrightarrow \beta_f \leq a$$

, for all  $a \in J(M)$ .

Note that  $\beta_f$  is not necessary a trajectory of M whereas our goal is to construct the defining trajectory, that is the least possible trajectory that satisfies f, and therefore we need to go one step further. One possible way is to combine the constraints on a sequence imposed by  $\beta_f$  and those from the next state function Suc to obtain the required trajectory.

**Definition 2.4.2:** Given any trajectory formula f of model  $M = [(S, \leq), Suc]$ , assuming that  $\beta_f = \beta_f^0 \beta_f^1 \dots$  is the defining sequence for f, a sequence  $\chi_f = \chi_f^0 \chi_f^1 \dots$  can be defined inductively as follows:

$$\chi_f^i = \begin{cases} \beta_f^0 & \text{if } i = 0\\ \text{lub}(\beta_f^i, Suc(\chi_f^{i-1})) & \text{otherwise} \end{cases}.$$

For the sequence  $\chi_f$  constructed as above, it can be proved [4] that,

- $\chi_f \in J(M)$ ,

- $\chi_f \models_M f$ , and

- $a \models_M f \Leftrightarrow \chi_f \leq a$ , for all  $a \in J(M)$ .

Thus, we can view  $\chi_f$  as the defining trajectory of f and it is also safe to say that every trajectory formula is simple.

More precisely, a trajectory assertion is defined as  $[Ante \rightarrow Cons]$  with dep(Ante) = dep(Cons), where Ante and Cons are trajectory formulas and dep(Ante) and dep(Cons) are the depths of formulas Ante and Cons Respectively. Generally, the depth of a formula f, denoted as dep(f), can be defined recursively as below:

- $dep(\rho) = 1$  if  $\rho \in P$  is a simple predicate,

- $dep(f_1 \wedge f_2) = \max(dep(f_1), dep(f_2)),$

- $dep(b \to f) = dep(f)$ , and

- dep(Nf) = 1 + dep(f).

If all the trajectories of model M satisfy a trajectory assertion  $[Ante \rightarrow Cons]$  of the same model, we write  $\models_M [Ante \rightarrow Cons]$ , where the satisfaction relation is defined as follows:

$$\models_M [Ante \to Cons]$$

holds iff  $a \models_M Ante$  implies  $a \models_M Cons$  for all  $a \in J(M)$ .

Finally, with the methods established for constructing the defining sequence and the defining trajectory for a given trajectory formula, we can apply the theorem below [4] to achieve our verification goal:

**Theorem 1:** Given  $\chi_{Ante}$  and  $\beta_{Cons}$  as the defining trajectory and the defining sequence of trajectory formulas Ante and Cons in model M, respectively,

$$\models_M [Ante \rightarrow Cons] \text{ holds iff } \beta_{Cons} \leq \chi_{Ante}$$

.

Note that although both the defining sequence and the defining trajectory are infinite by definition, we need only to compute the bounded prefix of them, since it is easy to show that for a given trajectory f with the defining sequence  $\beta_f = \beta_f^0 \beta_f^1 \dots$  we have  $\beta_f^i = \bot$  for  $i \ge dep(f)$ .

### 2.5 Symbolic Formulation

In this section, we will first introduce symbolic methods for representing trajectory formulas and trajectory assertions and then we will see how to verify these assertions using symbolic simulation. With these symbolic extensions, we can effectively reduce the number of required test cases and simulation runs.

Several ways can be used to realize the symbolization of trajectory formulas and what we present here is the one described in [4].

**Definition 2.5.1:** Given a model  $M = [(S, \leq), Suc]$ , a set U of Boolean variables, and a set P of simple predicates over S, the recursive definition of a symbolic trajectory formula of M is as follows:

- A simple predicate  $\rho \in P$  is a symbolic trajectory formula of M.

- The conjunction  $(f_1^s \wedge f_2^s)$  is a symbolic trajectory formula if both  $f_1^s$  and  $f_2^s$  are symbolic trajectory formulas of M.

- The domain restriction  $(B \to f^s)$  is a symbolic trajectory formula if B is a Boolean function over U and  $f^s$  is a symbolic trajectory formula of M.

- The next time expression (N  $f^s$ ) is a symbolic trajectory formula if  $f^s$  is a symbolic trajectory formula of M and N is the next-time operator.

As we can see from the above definition, the only modification from the original definition of trajectory formula is in the domain restriction part, where the domain constraint is generalized from a Boolean constant to a Boolean function.

The definition of a symbolic trajectory assertion (shown as below) can then be easily developed by simply replacing the trajectory formulas with the symbolized ones:

A symbolic trajectory assertion is of form  $[Ante^s \to Cons^s]$  with  $dep(Ante^s) = dep(Cons^s)$ , where  $Ante^s$  and  $Cons^s$  are symbolic trajectory formulas and  $dep(f^s)$  denotes the depth of a symbolic formula  $f^s$ .

For an assignment  $\eta: U \to \{0, 1\}$  to the Boolean variables in a given symbolic trajectory formula  $f^s$  of model  $M = [(S, \leq), Suc]$ , the evaluation of  $f^s$  denoted by  $f^s(\eta)$  is defined recursively as follows:

- $\rho(\eta) = \rho$ , if  $\rho \in P$  is a simple predicate over S.

- $(f_1^s \wedge f_2^s)(\eta) = f_1^s(\eta) \wedge f_2^s(\eta)$ , if both  $f_1^s$  and  $f_2^s$  are symbolic trajectory formulas of M.

- $(B \to f^s)(\eta) = B(\eta) \to f^s(\eta)$ , if B is a Boolean function over U and  $f^s$  is a symbolic trajectory formula of M.

- $(Nf^s)(\eta) = (N(f^s(\eta)))$ , if  $f^s$  is a symbolic trajectory formula of M and N is the next-time operator.

Accordingly, the evaluation of a given symbolic trajectory assertion  $[Ante^s \to Cons^s]$  of the same model for the assignment  $\eta: U \to \{0, 1\}$ , denoted by  $[Ante^s \to Cons^s](\eta)$ , is defined as:

$$[Ante^s \rightarrow Cons^s](\eta) = [Ante^s(\eta) \rightarrow Cons^s(\eta)].$$

In the rest of this section, we will show how to verify these symbolic trajectory assertions using symbolic simulation. A symbolic trajectory evaluation algorithm can be easily developed by symbolically extending the functions and relations used in the scalar trajectory evaluation algorithm discussed in the previous section.

Let H be the set of all assignments to the Boolean variable set U, i.e.,  $H = \{\eta \mid \eta : U \to \{0,1\}\}$ . The state set  $S = \{0,1,X\}^n \cup \{T\}$  is extended to a symbolic state set  $S(U) = \{g \mid g : H \to S\}$ . Each symbolic state in S(U) is a function mapping a Boolean assignment  $\eta \in H$  to a vector of ternary values (a scalar state) in S. For any given state  $s \in S$ , we let  $s^c$  denotes the constant function that has  $s^c(\eta) = s$  for any assignment  $\eta \in H$ . Particularly,  $\bot^c$  denotes the constant function for the state  $\bot$ . The next state function  $Suc: S \to S$  is then extended to the symbolic next state function  $Suc: S \to S$  is then extended to the symbolic next state function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ . The lowest upper bound function  $Suc: S(U) \to S(U)$ .

Note that in order to apply BDD technique in the symbolic trajectory evaluation algorithm, we need to represent the state space as Boolean functions. Thus, we treat the symbolic state in S(U) bit by bit. Let  $X^c$ ,  $1^c$ , and  $0^c$  be the constant functions for value X, 1 and 0, respectively. Each bit of the symbolic state can be a constant function  $X^c/1^c/0^c$ , a Boolean function, or a "mux" function taking either of them as the result by the control of another Boolean function. Actually this "mux" function can also be viewed as a Boolean function with a constant  $X^c/1^c/0^c$ .

**Definition 2.5.2:** Given a model  $M = [(S, \leq), Suc]$  and a set P of simple predicates over S, the defining symbolic sequence of a given symbolic trajectory formula  $f^s$  of model M, denoted by  $\beta_{f^s}^s$ , can be defined as follows:

- $\beta_{\rho}^{s} = d_{\rho}^{c} \perp^{c} \perp^{c} \dots$  if  $d_{\rho}$  is the defining value of  $\rho \in P$ .

- $\beta_{f_1^s \wedge f_2^s}^s = \text{lub}^s(\beta_{f_1^s}^s, \beta_{f_2^s}^s)$ , where  $\text{lub}^s$  is the symbolic extension of lub.

- $\beta_{B \to f^s}^s = B?^s \beta_{f^s}^s$ , where B is a Boolean function and  $?^s$  is the symbolic extension of ?.

- $\bullet \quad \beta_{Nf^s}^s = \perp^c \beta_{f^s}^s.$

The evaluation of the defining symbolic sequence  $\beta^s_{f^s}$  for any assignment  $\eta \in H$ , denoted by  $\beta^s_{f^s}(\eta)$ , is  $\beta^s_{f^s}(\eta) = \beta^s_{f^s(\eta)}$ .

**Definition 2.5.3:** Given any symbolic trajectory formula  $f^s$  of model  $M = [(S, \leq), Suc]$ , assuming that  $\beta_{f^s}^s = \beta_{f^s}^{s0} \beta_{f^s}^{s1} \dots$  is the defining sequence for  $f^s$ , the defining symbolic trajectory  $\chi_{f^s}^s = \chi_{f^s}^{s0} \chi_{f^s}^{s1} \dots$  can be defined inductively as follows:

$$\chi_{f^s}^{si} = \begin{cases} \beta_{f^s}^{s0} & \text{if } i = 0\\ \text{lub}^s(\beta_{f^s}^{si}, Suc^s(\chi_{f^s}^{s(i-1)})) & \text{otherwise} \end{cases}.$$

The evaluation of the defining symbolic trajectory  $\chi^s_{f^s}$  for any assignment  $\eta \in H$ , denoted by  $\chi^s_{f^s}(\eta)$ , is as below:

$$\chi_{f^s}^s(\eta) = \chi_{f^s(\eta)}^s.$$

We can also extend the satisfaction relations symbolically for a symbolic trajectory formula and for a symbolic trajectory assertion, respectively.

Given a symbolic trajectory formula  $f^s$  of model M, which is satisfied by a trajectory  $a=(a_0,a_1,a_2,...)$  of the same model, we define the symbolic satisfaction relation  $\models^s_M$  for the assignment  $\eta:U\to\{0,1\}$  as:

$$(a \models^{s}_{M} f^{s})(\eta) = 1 \text{ iff } a \models_{M} f^{s}(\eta).$$

Similarly, for a symbolic trajectory assertion, we have:

$$( \models^{s}_{M}[Ante^{s} \to Cons^{s}])(\eta) = 1 \text{ iff } \models_{M}([Ante^{s} \to Cons^{s}](\eta)).$$

At last, we can apply the theorem below [4] to verify if a symbolic trajectory assertion is satisfied by a model M:

**Theorem 2:** Given  $\chi^s_{Ante^s}$  and  $\beta^s_{Cons^s}$  as the defining symbolic trajectory and the defining symbolic sequence of symbolic trajectory formulas  $Ante^s$  and  $Cons^s$  in model M, respectively, for every  $\eta \in H$ ,

$$\models^{s}_{M}[Ante^{s} \to Cons^{s}](\eta) = 1 \text{ iff } \beta^{s}_{Cons^{s}}(\eta) \leq \chi^{s}_{Ante^{s}}(\eta).$$

For a given model M and a symbolic trajectory assertion of it, the symbolic evaluation algorithm yields a Boolean function denoting the set of assignments under which the assertion is satisfied as compared with the simple yes/no answer from the scalar algorithm. Since the verification task requires that the assertion should hold under all variable assignments, this Boolean function should simply be the constant function  $1^c$ , i.e., the function that returns 1 for all assignments.

## 2.6 Illustrative Example

In this section, we will present an illustrative example for Symbolic Trajectory Evaluation.

Figure 13. Diagram for a Verilog model of a sequential circuit

Consider the Verilog model of a sequential circuit shown in Figure 13. Signals  $s_1$  and  $s_2$  are two inputs to the circuit. The other input  $s_3$  severs as a clock signal. Signals  $s_4$  registers  $s_2$  at the positive edge of clock  $s_3$ . Finally, signal  $s_5$  is the registered output of the circuit, the value of which equals  $s_1 \wedge s_4$ . The time unit we use here is half clock cycle and we assume there is no time delay at the and gate.

We represent the circuit state as a 5-bit vector  $s = s_1 s_2 s_3 s_4 s_5$ . The next state function  $Suc^s = t_1 t_2 t_3 t_4 t_5$  is defined as follows:

$$t_1(s_1) = X^c, t_2(s_2) = X^c, t_3(s_3) = X^c, t_4(s_4) = s_3s_2 + \overline{s_3}s_4, t_5(s_5) = s_3s_1s_4 + \overline{s_3}s_5.$$

As mentioned before, no next state constraint is imposed on a state vector component associated with an input signal, that is, its next state function should be the constant function for value X.

Assume that we want to verify the following symbolic trajectory assertion for the above circuit model:

$$((s_1 = a)^{\{4\}} \land (s_2 = b)^{\{2\}} \land (s_3 = 0) \land N(s_3 = 1) \land N^2(s_3 = 0) \land N^3(s_3 = 1))$$

$$\rightarrow (N^4(s_5 = ab))$$

where the expression  $(s_1 = a)$  stands for the symbolic trajectory formula  $(a \to (s_1 = 1)) \land (\overline{a} \to (s_1 = 0))$ ,  $(s_2 = b)^{\{2\}}$  denotes  $(s_2 = b) \land N(s_2 = b)$ , and  $N^i$  denotes i next time operators. Generally, we use  $(s_i = B)$  as the shorthand for the symbolic formula  $(B \to (s_i = 1)) \land (\overline{B} \to (s_i = 0))$ , and represent the symbolic formula  $f^s \land N f^s \land N^2 f^s \dots \land N^{i-1} f^s$  as  $(f^s)^{\{i\}}$ , where  $f^s$  is a symbolic trajectory formula.

The simple predicates involved in the above assertion and the corresponding defining values are listed below:

- $s_1 = 0$  with defining value  $\langle 0, X, X, X, X \rangle$ ,

- $s_1 = 1$  with defining value  $\langle 1, X, X, X, X \rangle$ ,

- $s_2 = 0$  with defining value  $\langle X, 0, X, X, X \rangle$ ,

- $s_2 = 1$  with defining value  $\langle X, 1, X, X, X \rangle$ ,

- $s_3 = 0$  with defining value  $\langle X, X, 0, X, X \rangle$ ,

- $s_3 = 1$  with defining value  $\langle X, X, I, X, X \rangle$ ,

- $s_5 = 0$  with defining value  $\langle X, X, X, X, 0 \rangle$ ,

- $s_5 = 1$  with defining value  $\langle X, X, X, X, I \rangle$ .

From Definition 7, we get the defining symbolic sequence of symbolic trajectory formula  $(s_1 = a)$ , a shorthand expression for  $(a \rightarrow (s_1 = 1)) \land (\overline{a} \rightarrow (s_1 = 0))$ , as:

Similarly, we get the defining symbolic sequence of  $(s_2 = b)$  as:

$$\beta^s_{((b \to (s_2=1)) \land (\bar{b} \to (s_2=0)))} = \langle X^c, b, X^c, X^c, X^c, X^c \rangle \langle X^c, X^c, X^c, X^c, X^c \rangle \langle X^c, X^c, X^c, X^c, X^c \rangle \dots$$

Then the defining symbolic sequence of  $(s_1 = a) \wedge (s_2 = b)$  is computed as:

$$\beta_{(s_1=a)\land(s_2=b)}^s = \text{lub}^s(\beta_{(s_1=a)}^s, \beta_{(s_2=b)}^s)$$

=  $\langle a, b, X^c, X^c, X^c \rangle \langle X^c, X^c, X^c, X^c, X^c \rangle \langle X^c, X^c, X^c, X^c, X^c \rangle \dots$

By recursively applying Definition 7, we can get the defining symbolic sequence of the antecedent:

$$Ante^{s} = ((s_{1} = a)^{\{4\}} \land (s_{2} = b)^{\{2\}} \land (s_{3} = 0^{c}) \land N(s_{3} = 1^{c}) \land N^{2}(s_{3} = 0^{c}) \land N^{3}(s_{3} = 1^{c})) \quad ,$$

and then compute its defining symbolic trajectory according to Definition 8, the procedure of which are shown in Table I.

TABLE I. DEFINING SYMBOLIC TRAJECTORY OF THE ANTECEDENT

|    | $oldsymbol{eta}^{si}_{Ante^s}$ |                |                |                |                | $Suc^{s}(\chi_{Ante^{s}}^{s(i-1)})$ |                |                |                |                | $\chi^{si}_{Ante^s}$ |                      |                |                |                       |                |                 |

|----|--------------------------------|----------------|----------------|----------------|----------------|-------------------------------------|----------------|----------------|----------------|----------------|----------------------|----------------------|----------------|----------------|-----------------------|----------------|-----------------|

| i  | S <sub>1</sub>                 | S <sub>2</sub> | $s_3$          | S <sub>4</sub> | <b>S</b> 5     |                                     | S <sub>1</sub> | s <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> 5           |                      | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> 5      |

| 0  | а                              | b              | 0°             | Xc             | Xc             |                                     |                |                |                |                |                      |                      | а              | b              | 0°                    | Xc             | Xc              |

| 1  | а                              | b              | 1 <sup>c</sup> | Xc             | Χ <sup>c</sup> | ļ                                   | .X°            | X <sup>c</sup> | .X°            | Χ°             | X°                   | lub <sup>s</sup>     | а              | b              | 1°                    | Χ°             | Xc              |

| 2  | а                              | Xc             | Oc             | Χ <sup>c</sup> | Χ <sup>c</sup> |                                     | Χ <sup>c</sup> | Χ°             | Χ°             | b              | aX <sup>c</sup>      | lub <sup>s</sup>     | а              | Χ°             | 0°                    | b              | аХ <sup>с</sup> |

| 3  | а                              | Xc             | 1°             | Xc             | Xc             |                                     | .X°            | .X°            | Xc             | b.             | aXc                  | lub <sup>s</sup>     | а              | Xc             | 1 <sup>c</sup>        | b              | аХ <sup>с</sup> |

| 4  | Xc                             | Xc             | Xc             | Xc             | Xc             | ļ                                   | Χ°             | Xc             | Xc             | Χ°             | ab                   | lub <sup>s</sup>     | Xc             | Χc             | Χ°                    | Xc             | ab              |

| ≥5 | Xc                             | Xc             | Xc             | Xc             | Χ°             |                                     | Xc             | Xc             | X°             | Χ°             | abX⁰                 | ▶lub <sup>s</sup> ·► | Xc             | Xc             | Xc                    | Xc             | abX⁰            |

TABLE II. SYMBOLIC DEFINING SEQUENCE OF THE CONSEQUENT AND COMPARISON

|    |                | /              | $eta_{\scriptscriptstyle Cons^s}^{si}$ |                |            |                  | ${\cal X}^{si}_{Ante^s}$ |                |                |                |                  |  |

|----|----------------|----------------|----------------------------------------|----------------|------------|------------------|--------------------------|----------------|----------------|----------------|------------------|--|

| i  | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub>                         | S <sub>4</sub> | <b>S</b> 5 |                  | S <sub>1</sub>           | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> 5       |  |

| 0  | Xc             | Xc             | Xc                                     | Xc             | Xc         | ····► <u>≤</u> s | а                        | b              | 0°             | Xc             | Xc               |  |

| 1  | Xc             | Xc             | Xc                                     | Xc             | Xc         | <b>&gt;</b> ≤ s  | а                        | b              | 1 <sup>c</sup> | Xc             | Xc               |  |

| 2  | Xc             | Xc             | Xc                                     | Xc             | Xc         | ····►≤s •····    | а                        | Xc             | Oc             | b              | аХ <sup>с</sup>  |  |

| 3  | Xc             | Xc             | Xc                                     | Xc             | Xc         | ►≤s              | а                        | Xc             | 1°             | b              | аХ <sup>с</sup>  |  |