## **Parallelizing Games for Heterogeneous Computing Environments**

Wessam AlBahnassi

A Thesis

in

The Department

of

Computer Science and Software Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Software Engineering) at

Concordia University

Montreal, Quebec, Canada

October 2012

© Wessam AlBahnassi, 2012

## **CONCORDIA UNIVERSITY**

## **Department of Computer Science and Software Engineering**

This is to certify that the thesis prepared

By: Wessam AlBahnassi

## Entitled: Parallelizing Games for Heterogeneous Computing Environments

and submitted in partial fulfillment of the requirement for the degree of

## Master of Applied Science (Software Engineering)

Complied with the regulations of the University and meets with the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|               |                          | Chair                       |

|---------------|--------------------------|-----------------------------|

| Dr. Peter Rig | by                       |                             |

|               |                          | Examiner                    |

| Dr. Bipin C.  | Desai                    |                             |

|               |                          | Examiner                    |

| Dr. Hovhann   | es Harutyunyan           |                             |

|               |                          | Co-Supervisor               |

| Dr. Dhrubajy  | oti Goswami              |                             |

|               |                          | Co-Supervisor               |

| Dr. Sudhir P. | Mudur                    |                             |

| proved by     |                          |                             |

|               | Chair of Department or C | Graduate Program Director   |

| 20            |                          |                             |

|               | Robin A.L. Drew          | , Ph.D.,ing., Dean          |

|               | Faculty of Engine        | eering and Computer Science |

## ABSTRACT

#### **Parallelizing Games for Heterogeneous Computing Environments**

#### Wessam AlBahnassi

Game applications nowadays run on platforms that contain multiple and different types of processors. Benefiting from the available processing power requires: (1) Code to be designed to run in parallel; and (2) Efficient mapping techniques to schedule tasks optimally on appropriate processors for increasing performance. The work in this thesis is directed towards improving the execution time performance of game applications on host platforms. The methodology adopted consisted of the following different stages: (1) Studying the main features of game applications; (2) Investigating parallelization opportunities within these applications, (3) Identifying/designing the programming structures needed to realize those opportunities; and (4) Designing, implementing, verifying and testing the parallel programming structures developed to support heterogeneous processing and maximize use of available processing power.

The research reported in this thesis presents a new framework for parallel programming of games. This framework consists of two major components which form the two main contributions of our work. These are (1) Sayl, a new design pattern to enable parallel programming of game applications and to reduce the amount of programmer work when writing parallel code; and (2) Arbiter Work Stealing, a new task scheduler capable of efficiently and automatically scheduling dynamically generated tasks to processors in a heterogeneous processing and memory environment. The framework was used to successfully parallelize the serial code of a sample game application to work in a heterogeneous processing environment. The parallel version shows far superior performance as compared to the serial version.

## ACKNOWLEDGEMENTS

First and foremost, I wish to express my profound gratitude to my supervisors Dr. Sudhir P. Mudur and Dr. Dhrubajyoti Goswami for their continuous commitment, encouragement, and support. I feel privileged for having the opportunity to work with them and share passion for research. I would like also to extend my appreciation to my committee members and to all professors who provided me with their valuable knowledge during my studies at Concordia. I would like to pass my special thanks and gratitude to all my family members and friends:

- My parents. There is nothing I can do to return even an iota of favor for you.

- My wife for her pure love, support and patience and my son Omar for being the most wonderful thing in life.

- My brother Homam who supported me throughout the entire process with guidance and experience, and his wife and son 'Aws' whose name was used in this thesis.

- My friend Abdulrahman Al-lahham for his valuable help during my course work.

Additionally, I would like to thank my colleagues at Electronic Arts Montreal for their support and understanding during pressure times of my thesis.

Finally I would like to dedicate this work to all heroes of the Syrian Revolution and all the humanitarian values it is carrying. Names like Hamza Al-Khateeb and Husein Harmoosh will remain engraved in my heart forever. Victory is eventual, god willing.

# **TABLE OF CONTENTS**

| LIST OF FIGURES |         |                                      |     |

|-----------------|---------|--------------------------------------|-----|

| ABBRI           | EVIATIC | DNS                                  | XII |

| CHAP            | FER 1   | INTRODUCTION                         | 1   |

| 1.1             | GENER   | AL BACKGROUND                        | 1   |

| 1.2             | THE RE  | ESEARCH PROBLEM                      | 2   |

| 1.3             | RESEA   | RCH OBJECTIVES AND METHODOLOGY       | 2   |

| 1.4             | CONTR   | IBUTIONS                             |     |

| 1.5             | THESIS  | S STRUCTURE                          | 5   |

| CHAP            | FER 2   | LITERATURE REVIEW                    | 6   |

| 2.1             | INTRO   | DUCTION                              | 6   |

| 2.2             | GAME    | APPLICATIONS                         | 6   |

| 2.3             | GAME    | HARDWARE                             | 9   |

| 2.3.1           | The     | e Graphics Processing Unit           | 9   |

| 2.3.2           | Per     | sonal Computer Architecture          | 11  |

| 2.3.3           | Mie     | crosoft Xbox360 Architecture         |     |

| 2.3.4           | Sor     | y Playstation 3 Architecture         |     |

| 2.4             | PARAL   | LEL DESIGN PATTERNS                  |     |

| 2.5             | TASK S  | SCHEDULING                           | 20  |

| 2.6             | SUMM    | ARY AND CONCLUSIONS                  |     |

| CHAP            | FER 3   | A NEW GAME PARALLELIZATION FRAMEWORK |     |

| 3.1             | INTRO   | DUCTION                              |     |

| 3.2             | SAYL I  | DESIGN PATTERN                       |     |

| 3.2.1           | The     | e Problem Domain                     |     |

| 3.2.2           | Sol     | ution Strategy                       |     |

| 3.2.3           | Say     | l Front-end                          |     |

| 3.2.4           | Say     | l Back-end                           |     |

| 3.2.5           | Imp     | plementation                         | 39  |

| 3.2.6           | Dis     | cussion                              | 46  |

| 3.3             | ARBITI  | ER WORK STEALING SCHEDULER           | 50  |

| 3.3.1   | The Problem Domain                                                    | 0  |

|---------|-----------------------------------------------------------------------|----|

| 3.3.2   | AWS scheduler basic concepts 5                                        | 1  |

| 3.3.3   | AWS scheduler details                                                 | 2  |

| 3.3.4   | Interface                                                             | 7  |

| 3.3.5   | Discussion                                                            | 8  |

| 3.4     | SUMMARY AND CONCLUSIONS                                               | 0  |

| СНАРТ   | ER 4 CASE STUDY                                                       | 2  |

| 4.1     | INTRODUCTION                                                          | 2  |

| 4.2     | TEST SETUP DETAILS                                                    | 2  |

| 4.3     | TESTS AND RESULTS                                                     | 8  |

| 4.3.1   | Set 1: Sayl versus Cascade                                            | 8  |

| 4.3.2   | Set 2: Homogeneous processing versus heterogeneous processing         | 0  |

| 4.3.3   | Set 3: Heterogeneous work stealing with the Arbiter versus without th | ie |

| Arbiter | 71                                                                    |    |

| 4.4     | DISCUSSION AND ANALYISIS                                              | 3  |

| 4.5     | SUMMARY AND CONCLUSIONS                                               | 7  |

| СНАРТ   | ER 5 SUMMARY, CONCLUSIONS AND FUTURE WORK 7                           | 9  |

| 5.1     | SUMMARY                                                               | 9  |

| 5.2     | CONTRIBUTIONS                                                         | 0  |

| 5.3     | LIMITATIONS AND FUTURE WORK                                           | 1  |

| REFER   | ENCES                                                                 | 3  |

| APPEN   | DICES                                                                 | 0  |

## **LIST OF FIGURES**

| Figure 2.1: A simple game loop (Valente, Conci, & Feijó, 2005)7                          |

|------------------------------------------------------------------------------------------|

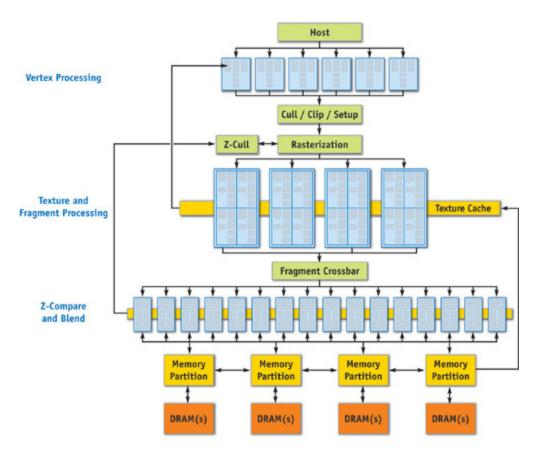

| Figure 2.2: A block diagram of a GPU (Kilgariff & Fernando, 2005) 10                     |

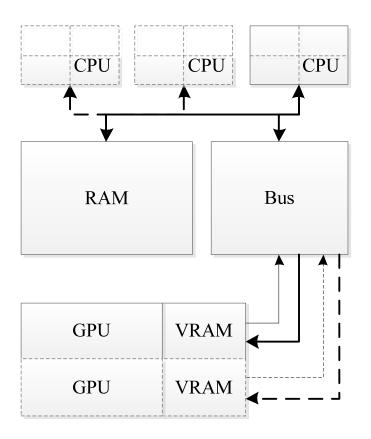

| Figure 2.3: An abstract high-level architecture graph for common PC platform systems     |

| focusing on processor, memory and bus components. Lines represent memory                 |

| access between components. Arrows represent direction allowed for data transfer.         |

| Thick lines represent faster data transfer compared to thin lines. In this               |

| architecture, the number of CPUs and GPUs is flexible. Moreoever, each CPU               |

| might have a number of cores                                                             |

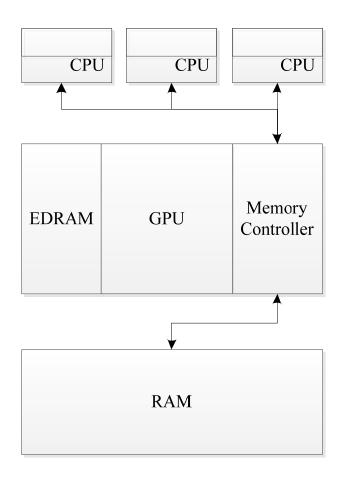

| Figure 2.4: An abstract high-level architecture graph for the Microsoft Xbox 360         |

| platform focusing on processor, memory and bus components. Lines represent               |

| memory access between components. Arrows represent direction allowed for data            |

| transfer                                                                                 |

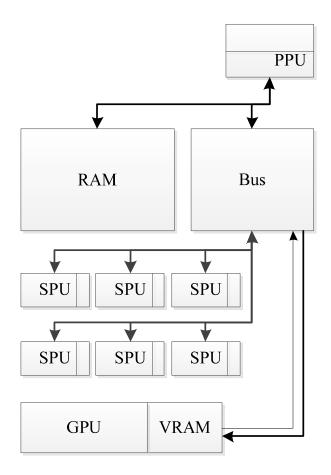

| Figure 2.5: An abstract high-level architecture graph for the Sony Playstation3 platform |

| focusing on processor, memory and bus components. Lines represent memory                 |

| access between components. Arrows represent direction allowed for data transfer.         |

| Thick lines represent faster data transfer compared to thin lines. Note that each        |

| SPU has a small local memory block attached to it                                        |

| Figure 2.6: Fork-Join pattern (Kim & Agrawala, 1989)                                     |

| Figure 2.7: The data-flow pattern (Manolescu, September, 1997)                           |

| Figure 2.8: The Cilk model of multithreaded computation. Circles represent threads       |

|                                                                                          |

| which are grouped into procedures. Straight lines represent spawns and curved            |

| Figure 2.9: Declaring a task graph using Cascade (Best, et al., 2009)                  |

|----------------------------------------------------------------------------------------|

| Figure 2.10: A task with work kernel for Cascade (Best, et al., 2009)                  |

| Figure 2.11: Qilin's adaptive mapping technique (Luk, Hong, & Kim, 2009)               |

| Figure 2.12: Procedures of the MATEHa algorithm (Giusti, Chichizola, Naiouf, & Giusti, |

| 2008)                                                                                  |

#### Figure 3.2: A graph representing methods called in a hypothetical game application..... 37

| Figure 3.5: Sayl methods that drive the back-end | 41 |

|--------------------------------------------------|----|

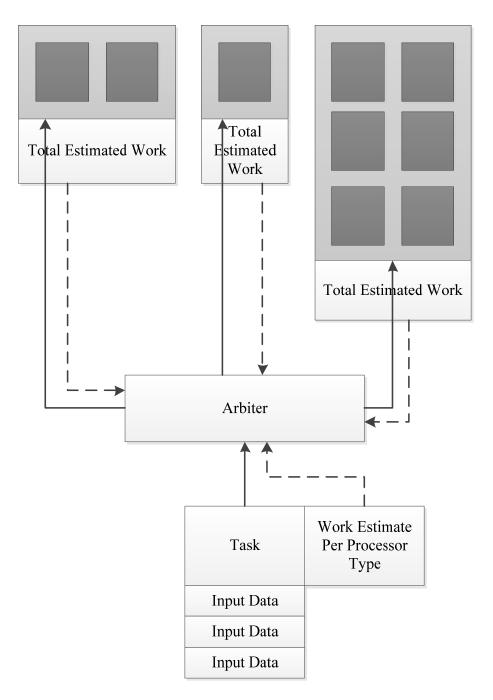

- Figure 3.10: An illustration of the conceptual components involved in AWS algorithm. The light gray blocks are processor groups, which contain one or more processors depicted by dark gray blocks. Solid arrows represent "submission" communication, and dashed arrows represent information flowing towards the Arbiter for decision making.

56

Figure 3.11: Data structures representing the interface to AWS.

57

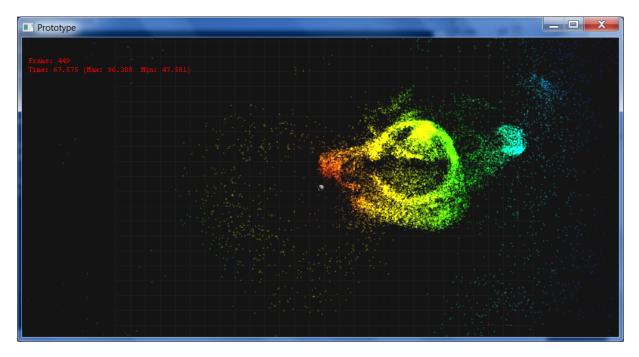

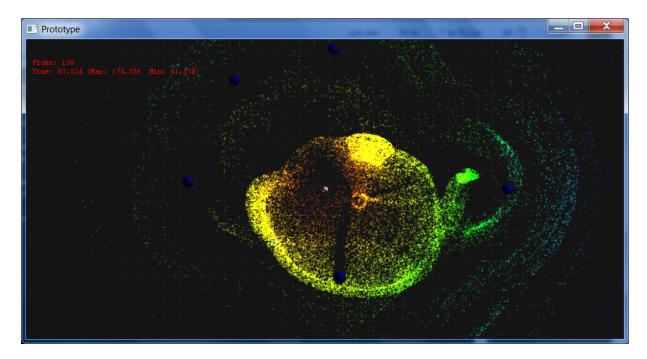

Figure 4.1: Screen shot from the sample game application.

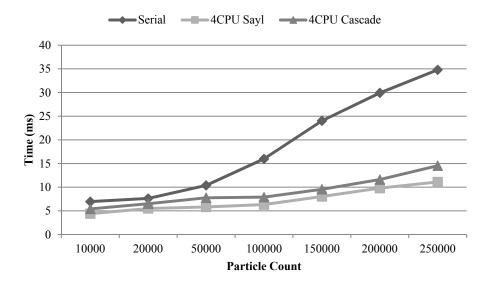

| Figure 4.4: Run-time performance results for the serial, 4CPU Sayl and 4CPU Cascade     |

|-----------------------------------------------------------------------------------------|

| versions of the sample game and their relationship to the number of simulated           |

| particles in the game                                                                   |

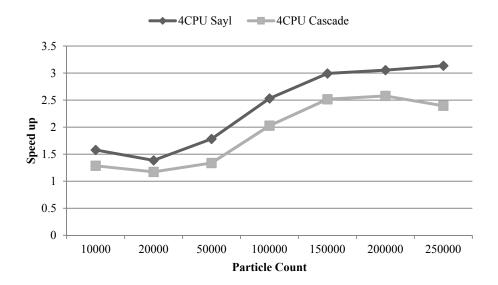

| Figure 4.5: Speed up values for the run-time performance tests in Figure 4.4            |

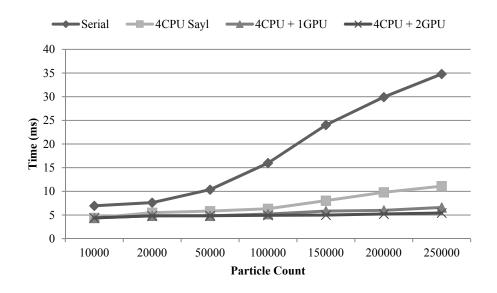

| Figure 4.6: Run-time performance results for the serial, 4CPU Sayl, 4CPU+1GPU and       |

| 4CPU+2GPU versions of the sample game and their relationship to the number of           |

| simulated particles in the game70                                                       |

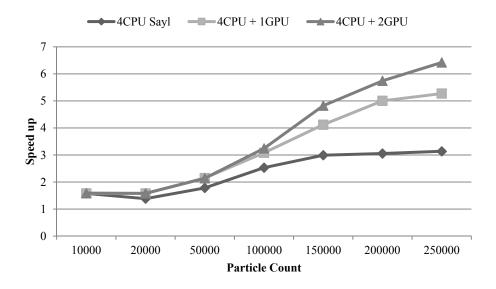

| Figure 4.7: Speed up values for the run-time performance tests in Figure 4.6            |

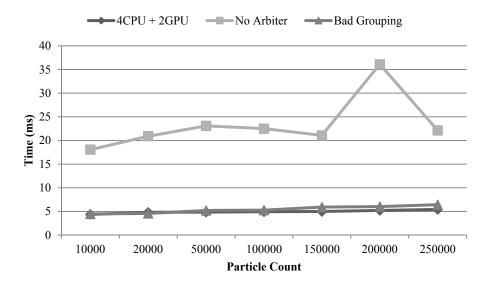

| Figure 4.8: Run-time performance results for the 4CPU+2GPU, No Arbiter and Bad          |

| Grouping versions of the sample game and their relationship to the number of            |

| simulated particles in the game                                                         |

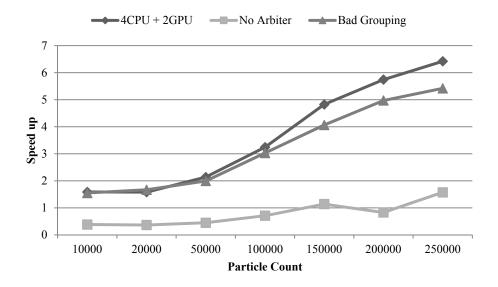

| Figure 4.9: Speed up values for the run-time performance tests in Figure 4.8            |

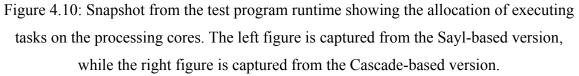

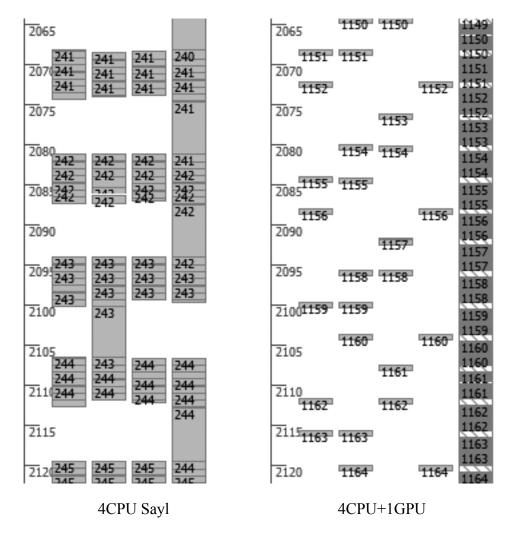

| Figure 4.10: Snapshot from the test program runtime showing the allocation of executing |

| tasks on the processing cores. The left figure is captured from the Sayl-based          |

| version, while the right figure is captured from the Cascade-based version 75           |

| Figure 4.11: Snapshot from the test program runtime showing the allocation of           |

| executing tasks on the processing cores. The left figure is captured from the 4CPU      |

| Sayl parallel version, while the right figure is captured from the 4CPU+1GPU            |

| parallel version, where the right-most column represents tasks executed on the          |

GPU. 76

## **ABBREVIATIONS**

| 2D   | Two-dimensional                   |

|------|-----------------------------------|

| 3D   | Three-dimensional                 |

| AI   | Artificial Intelligence           |

| API  | Application Programming Interface |

| AWS  | Arbiter Work Stealing             |

| CPU  | Central Processing Unit           |

| DAG  | Directed Acyclic Graph            |

| GPU  | Graphics Processing Unit          |

| PPE  | Parallel Programming Environment  |

| PPU  | Power Processing Unit             |

| PS3  | Sony Playstation3®                |

| SDK  | Software Development Kit          |

| SLOC | Source Lines of Code              |

| SPU  | Synergetic Processing Unit        |

UI User Interface

## CHAPTER 1 INTRODUCTION

#### **1.1 GENERAL BACKGROUND**

The domain of game applications continues to grow in complexity and size. With the ubiquity of multi-core processors, it is important that game programs be designed to make effective use of this commodity parallel processor architecture. Most applications in this domain have originally been written for a single processor environment. At their core, these programs usually include a game/simulation loop. In any iteration of this loop, all tasks required for each frame are carried out. In recent years, some of the existing games have started transitioning to support multiple processors. This is usually done by converting selected sections of their code to run in parallel. Tasks within a single iteration (frame) of the game loop are usually parallelized but not the tasks across frames. Newly written games should be able to maximize use of the available multiple processors. Detecting parallel tasks throughout the application rather than confining to a single iteration of the game-loop is therefore important. Whether the programmer is parallelizing existing serial game code or writing new parallel game code from scratch, there is a need for appropriate parallelization models which can make this parallel program development simple and straight forward. Unfortunately, there is not much published work found on this topic.

The interest in utilizing the graphics processor unit (GPU) for general-purpose computations (commonly known as GPGPU) has increased after those processors have shown significant computational powers in addition to being wide-spread among commodity machines. A large portion of GPGPU work has mostly been focused on programming specific algorithms to work efficiently on the GPU (e.g., matrix operations, image filters, and sort algorithms). A game application can include a much wider variety of computations (e.g., artificial intelligence, physics simulation, character animation, and 3D rendering), and can also benefit from the GPU as a general purpose processor. The environments in which games are usually run include at least one CPU and one GPU on the same machine, in addition to, possibly, other processor types (e.g., the SPUs on the Sony Playstation3 game console). Some of the computations in such applications map better to the capabilities of one processor over another. It is thus important to be able to execute computations in parallel on the different processors in a way that execution time is minimized, and hence overall performance is maximized. Supporting heterogeneous processing environments is important but adds considerable complexity to the scheduling problem.

#### **1.2 THE RESEARCH PROBLEM**

Based on the above our research problem can be stated as follows:

What are the parallelization models which take into account the specific characteristics of game applications and make parallel program development on heterogeneous computing environments simple and straight forward, and also result in performance improvements as compared to their serial code versions?

#### **1.3 RESEARCH OBJECTIVES AND METHODOLOGY**

The main objective of this research is to investigate the process of parallelization of game applications from both code design and run-time perspectives and to develop suitable structures to minimize programmer effort and maximize application performance while considering the heterogeneous processing capabilities of game host environments.

The research methodology followed has the following stages:

- 1. Identify parallelization opportunities in game applications by studying their common structure and dependencies, and the distinctive capabilities of the different computing components in a heterogeneous computing environment.

- 2. Propose a new framework for parallelization of game programming on such heterogeneous computing environments. The framework should simplify the job of writing parallel game code or parallelize existing serial game code and minimize the amount of programmer effort involved in the process. It should exploit parallelization opportunities in the game applications. Further, it should automate the job of optimally mapping and scheduling subtasks in the game application to appropriate computing elements in the environment so as to be able to achieve the best application performance.

- 3. Implement, test and verify the performance of the proposed framework on sample game applications running in an environment with heterogeneous computing elements.

### **1.4 CONTRIBUTIONS**

From this research our main thesis is that game applications have specialized parallelization requirements in the form dynamic tasks which need to be executed in different frames of the game and that these requirements can be met with a game parallelization framework consisting of a parallel design pattern in the front end and a task scheduler at the back end which maps and assigns tasks to processing elements based on minimizing a cost function taking into account processor type, processor loading, data transfer times and data locality. The framework not only simplifies the parallelization task in terms of programmer effort but also helps improve the performance of games significantly by better utilization of the processing elements in the heterogeneous computing environment.

The main goal is to improve performance of game applications by better utilization of the heterogeneous parallel processing capabilities available in their host environments. In order to do so, first the game code must be written to express game tasks in parallel. Then, these tasks must be efficiently scheduled to processing elements in such a way that attempts to achieve optimal overall performance. We propose a new game parallelization framework for achieving these goals.

To achieve the first goal, the framework includes a new parallel design pattern that – when applied- will build a dynamic task graph of all game tasks, honoring their dependencies. The second goal is achieved by including a task scheduler that can take tasks from the dynamic task graph and schedule them to processing elements in the host environments, depending on their loading, their capabilities, data transfer costs and data locality.

By applying this framework, game applications can scale their performance with the processing capabilities of their host environments.

Our specific contributions in this thesis are:

- Design and implementation of the Sayl parallel design pattern for game applications and

- Design and implementation of the Arbiter Work Stealing scheduler, a task scheduler that supports efficient dynamic scheduling of tasks to processing elements in heterogeneous environments.

## **1.5 THESIS STRUCTURE**

The rest of this thesis is organized as follows. In the next chapters, a comprehensive literature review is first presented in Chapter 2 including game applications, game hardware, parallel design patterns and task scheduling algorithms. In Chapter 3, we present the new game parallelization framework consisting of a design pattern for parallel game programming and a task scheduling system for heterogeneous processing environments. In Chapter 4, the case studies involving parallelization of a sample game application using this framework are presented, including a summary of the framework implementation details, and a discussion of the test and results. The research contributions and future work are described in Chapter 5.

## CHAPTER 2 LITERATURE REVIEW

#### **2.1 INTRODUCTION**

This chapter focuses on related topics from game applications structure, parallel design patterns and task scheduling algorithms. The purpose is to investigate the trends in research for parallelization and scheduling techniques that can support the parallelization process of game applications.

#### **2.2 GAME APPLICATIONS**

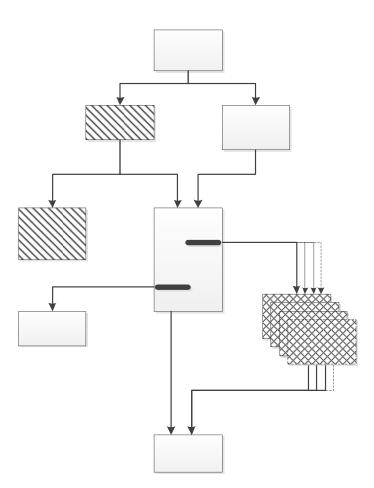

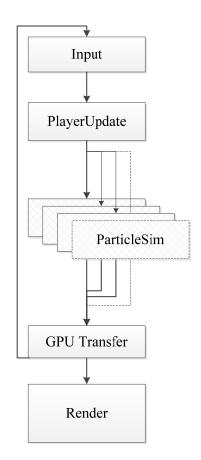

The process of programming game applications has been growing in complexity due to the growth and expansion of the various aspects in games. Nowadays games may include a combination of artificial intelligence algorithms, 3D rendering techniques, audio processing algorithms, multiplayer and online gaming support and input device processing in addition to game logic (Blow, 2004). Those tasks generate data and update the state of the game and output graphics and audio to the player. The tasks are usually executed in a certain order in a continuous loop commonly called the *game loop*, which is a standard structure most game applications are built around. The game loop is iterated in a certain frequency, usually at 30 hertz or 60 hertz that matches the display device's refresh rate. In each loop iteration or *frame*, the game gathers user input and uses it to update the logic and state of the game before finally outputting results to the player (e.g., graphics display, audio output and input device feedback) (Valente, Conci, & Feijó, 2005). Figure 2.1 shows a simplified graph of a game loop.

Figure 2.1: A simple game loop (Valente, Conci, & Feijó, 2005)

Each iteration of the game loop must finish execution within 16.6 milliseconds or 33.3 milliseconds depending on whether the game targets 60 hertz or 30 hertz display refresh rates respectively. However, the continuous growth in size and complexity of game computations makes it challenging to execute all tasks in a single game loop iteration within the time limit. Thus, optimization techniques became necessary to increase efficiency of calculations. Such optimizations include:

- Space partitioning techniques such as Binary Space Partitioning Trees (BSP Trees) and Octrees to speed up queries of game entities (Ericson, 2005).

- Frustum view culling to reduce the number of displayed game entities.

- Vectorization of calculations using Single-Instruction-Multiple-Data (SIMD) compiler intrinsics (Gschwind, 2007) such as SSE (Intel Corporation, 2007) and AltiVec (Diefendorff, Dubey, Hochsprung, & Scales, 2000). Vector and matrix operations are commonly optimized with this technique.

Even though these optimizations help improve performance, they are not always enough to bring down the time taken to complete a frame to fit within the limit. Additionally, it is not possible anymore to rely on faster processors to be able to run the game fast enough. The growth of processing power by increasing processor clock speed has stagnated and instead processing power now grows by employing additional processing cores in the machine. Games written using the classical game loop structure cannot automatically benefit from such kind of processing power growth without changing the code to be able to run in parallel on the available processing cores. The work of (Rhalibi, Merabti, & Shen, 2006) offers a framework with which games can be modeled as cyclic-taskdependency graphs by analyzing the dependencies between the different tasks in the game. The tasks in the graph are then executed on a multithreaded system in a manner that preserves task dependency, thus benefiting from parallel processing power in a shared memory system with more than one processor, but of the same kind.

The graphics processing unit (GPU) has become nowadays an integral part of commodity personal computers as well as game consoles. This is yet another processor available for game applications that is targeted mainly towards accelerating 3D graphics rendering and display. The work in (Joselli, Clua, Montenegro, Conci, & Pagliosa, 2008) and (Joselli M., et al., 2009) offloads some of the game tasks such as physics to the GPU such that these tasks run in parallel to other tasks in the game loop. It is thus clear that performance scalability of games on modern hardware considerably depends on the amount of parallelization the game code supports.

#### **2.3 GAME HARDWARE**

This section reviews the major characteristics of hardware on which games are hosted in recent years.

## 2.3.1 The Graphics Processing Unit

Unlike the general purpose central processing unit (CPU), the GPU is a specialized processor which holds a large collection of fixed-function and software-programmable processing resources (Fatahalian & Houston, 2008). It contains an arithmetic logic unit (ALU) with comparatively high peak floating-point rates. It is originally designed to process 3D graphics, which is often described as an *embarrassingly parallel* task (Hansen, Crockett, & Whitman, 1994). This explains the decision behind the current architecture of the GPU (Kilgariff & Fernando, 2005), which is built around a series of connected components matching the pipeline steps used to process 3D graphics from input mesh and texture data set until outputting pixels on the screen (Figure 2.2).

Figure 2.2: A block diagram of a GPU (Kilgariff & Fernando, 2005)

The most notable feature of these components is the presence of multiple *vertex processing units* (VPU) and *fragment processing units* (FPU). Each group of these processors can be configured to run a *shader program* which is set by the programmer through APIs like OpenGL (Khronos Group, 1997) and Direct3D (Microsoft Corp., 2012). This processing power has attracted researchers as well as game programmers to utilize the GPU for more than just graphics output tasks. The interest in utilizing the GPU for general-purpose computations (commonly known as GPGPU) has increased. A number of APIs have been developed to facilitate GPGPU computations such as CUDA (NVIDIA Corp., 2007), OpenCL (The OpenCL Specification, 2010) and DirectCompute (Boyd, 2008). In addition, C++ AMP (Microsoft Corp., 2012) is a set of language

extensions that allows running computational kernels written in C++ on the GPU and the CPU. This has considerably simplified program development for these processors.

A large portion of GPGPU work has mostly been focused on the programming of specific algorithms to work efficiently on the GPU (e.g., matrix operations, image filters, and sort algorithms). Game applications have a much wider variety of computations and can also benefit from the GPU as a general purpose processor.

#### 2.3.2 Personal Computer Architecture

Most personal computers (PCs) are built around an architecture that contains one or more main CPUs -where each CPU could be a multi-core processor of its own- in addition to one or more GPUs residing on graphics cards (see Figure 2.3). In such systems, the CPUs have direct access to the system's main memory (RAM), while the GPU may have its own local memory that is built in the graphics card (VRAM). In this architecture, the GPU has no access to RAM, but the CPU has read/write access to the VRAM (Hovland, 2008). In most cases, write speed from CPU to VRAM is multitudes faster than read speed (Gregg & Hazelwood, 2011).

Figure 2.3: An abstract high-level architecture graph for common PC platform systems focusing on processor, memory and bus components. Lines represent memory access between components. Arrows represent direction allowed for data transfer. Thick lines represent faster data transfer compared to thin lines. In this architecture, the number of

CPUs and GPUs is flexible. Moreoever, each CPU might have a number of cores.

## 2.3.3 Microsoft Xbox360 Architecture

The Microsoft Xbox360 is one among recent common game consoles. From a high-level architectural point-of-view, the Xbox360 shares some similarities with the PC's CPU/GPU high-level architecture. The Xbox360 (Andrews & Baker, 2006) has a CPU made of three hyper-threaded cores, in addition to a GPU chip. One major difference to the PC architecture is that the Xbox360 is built around unified memory architecture (UMA), and the GPU itself is the memory controller of the system. In this case, data

transfer times between the CPU and the GPU are similar, and the GPU has full access to the system's RAM (Figure 2.4).

Figure 2.4: An abstract high-level architecture graph for the Microsoft Xbox 360 platform focusing on processor, memory and bus components. Lines represent memory access between components. Arrows represent direction allowed for data transfer.

## 2.3.4 Sony Playstation 3 Architecture

Another recent game console is the Sony Playstation 3 (PS3). Its architecture is special among others in that it utilizes IBM's CELL processor (Kahle, et al., 2005), which can be described as one dual-threaded CPU and 6 Synergetic Processing Elements (SPUs) capable of fast vector computations exposed to the programmer. Each SPU has 256kB local memory in addition to full access to RAM via DMA requests. The PS3's GPU

(similar to the PC) has its own VRAM and has restricted access to RAM. Transfer speeds between the CPU and the GPU are also similar to that of the PC architecture (Figure 2.5).

Figure 2.5: An abstract high-level architecture graph for the Sony Playstation3 platform focusing on processor, memory and bus components. Lines represent memory access between components. Arrows represent direction allowed for data transfer. Thick lines represent faster data transfer compared to thin lines. Note that each SPU has a small local memory block attached to it.

## 2.4 PARALLEL DESIGN PATTERNS

Design patterns are general reusable solutions to commonly occurring problems within a given context in software design. Game applications, having a set of common characteristics and could benefit from design patterns that help solve problems often

occurring in these applications. One such problem that is the focus of this thesis is parallelization of tasks in a game application. Thus, it is worth looking into existing work to solve this problem for the specific domain of games.

Task Parallelism (Mattson, Sanders, & Massingill, 2004) is a design pattern that describes a solution strategy for task-based parallelism expressed in the form of a task graph. It assumes that the problem can be decomposed into a collection of tasks that can execute concurrently. The tasks can have dependencies among them. They may be known at the beginning of the computation or arise dynamically as the computation unfolds. The task parallelism pattern can be considered a generic pattern, as it does not specify how to express tasks and their different types of dependencies (e.g., the data-flow type dependencies). Moreover it does not specify how to execute these tasks on parallel computing architectures. The pattern thus could serve as a basis for specialization into a domain-specific design pattern.

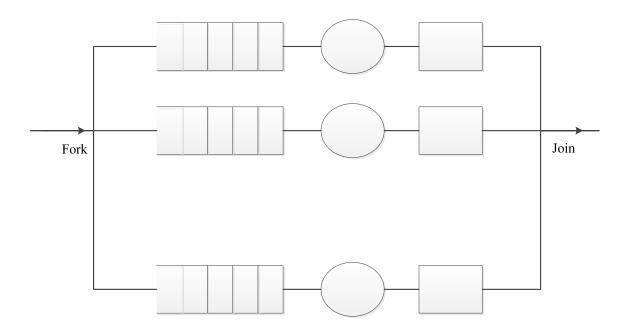

Fork-Join (Kim & Agrawala, 1989) is a classic pattern that specifies a queue where incoming tasks are split for execution by threads and joined before departure (Figure 2.6).

Figure 2.6: Fork-Join pattern (Kim & Agrawala, 1989)

The pattern only has support for specific types of data-flow dependencies (fork-join type) and it only supports parent-child synchronization via join. It cannot be used to model more irregular dependency types.

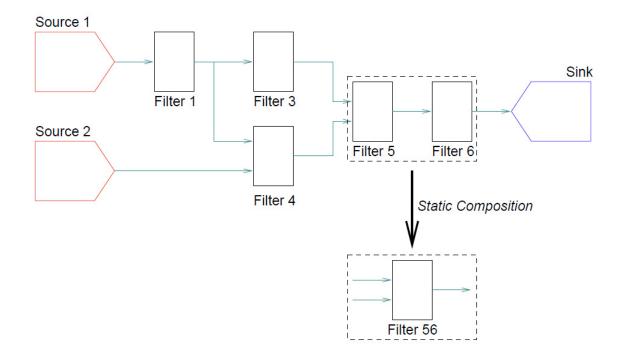

The data-flow pattern (Manolescu, September, 1997) is based on the data-flow paradigm introduced in the late 1960s (Adams, 1969) (Rodrigues & Bezos, 1969). The pattern models parallel programs as modules of execution which take input and produce output (Figure 2.7). Those modules can only run when all their inputs have been evaluated. When the module finishes executing, it sends outputs that then become available to other modules. Output generated from a data-flow module is sent as input to other modules only when the module calculating the output has finished.

Figure 2.7: The data-flow pattern (Manolescu, September, 1997)

The Task Graph pattern (Miller, 2010) is a task-parallel pattern that specifies breaking down the computation into a series of atomic tasks with clearly defined dependencies to form a directed acyclic graph. Tasks in the task graph are specified at compile time, but they are scheduled at run-time to run on a pool of processing elements. This allows the graph to adapt to the run-time environment setup and thus scale with the number of processing elements available. Once the tasks and their dependencies are specified by the programmer then the task graph can be executed. Dynamically spawned tasks are not supported directly by the pattern, but a suggestion is made as to emulate the dynamic spawning behavior by using conditional tasks. Such tasks may be present in the graph but the task and the conditions under which it executes are defined by the program prior to execution of the graph.

The Dynamic Task Graph (DTG) pattern (Johnson, Davis, & Hadfield, 1996) describes the same task graph concepts as the previously mentioned works, but adds the capability to dynamically spawn tasks in the task graph. The DTG pattern requires each task in the program to be uniquely identified by a string name. This name is a key piece of information for referencing tasks in the graph. It is important to note that processors in the DTG pattern block execution when a task requests the output of another task that has not become eligible for execution.

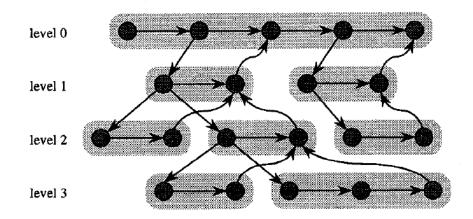

Cilk (Blumofe, et al., 1995) is a language extension to the C language. It is based on a run-time system for multithreaded parallel programming which uses a work-stealing scheduler. Programs built with Cilk dynamically unfold as a directed acyclic graph (Figure 2.8). The program consists of a collection of "procedures". A procedure is broken into a sequence of "threads". A thread is effectively a non-blocking C function. Such functions will run as soon as they are called without blocking the caller. A function can itself spawn other threads. A thread may have data dependencies which effectively prevent its execution until they are fulfilled. Code written in Cilk language is translated to C to interface with application code.

Figure 2.8: The Cilk model of multithreaded computation. Circles represent threads which are grouped into procedures. Straight lines represent spawns and curved lines represent data dependencies (Blumofe, et al., 1995).

The work of (Best, et al., 2009) describes an effort made to parallelize a game engine. This effort led to the creation of Cascade, which is a parallel programming environment (PPE) specifically addressing the games domain. Cascade allows the programmer to organize game tasks in a graph with dependencies in a fashion similar to the Task Graph pattern by (Miller, 2010). It supports an efficient parallel implementation of the producer/consumer pattern. It also supports multi-instance tasks, that is, spawning the same task multiple times simultaneously but with different data sets to work on for each of the task instances (Figure 2.9 and Figure 2.10). Similar to (Miller, 2010), Cascade does not allow for dynamically generated tasks in the task graph.

```

// Create task objects.

// Task A: 1 instance

A a( 1 );

// Task B: batch size 2, 1 instance

B b( 2, 1 );

// Task C: batch size 1, 4 instances

C c( 1, 4 );

// Task D: batch size 1, 3 instances

D d( 1, 3 );

a->addDependent( b );

b->connectOutput( c );

c->connectOutput( d );

```

Figure 2.9: Declaring a task graph using Cascade (Best, et al., 2009).

```

class C : public Task<int,int>

{

public:

C(int batchSize, int numThreads) :

Task<int,int>(batchSize, numThreads) {}

void work_kernel(TaskInstance<int,int>* tI) {

for(int i=0; i < tI->receivedBatch->size(); i++)

tI->sendOutput(tI->receivedBatch->at(i)+1);

}

};

```

Figure 2.10: A task with work kernel for Cascade (Best, et al., 2009).

#### 2.5 TASK SCHEDULING

The problem of task scheduling on parallel processing environments has been thoroughly researched in general and many different scheduling algorithms have been developed. Some works support heterogeneous processing, while others only work in homogeneous processing environments. In both cases, only a few works exist specifically for game applications. Throughout the rest of this section, we use the terms 'mapping' and 'scheduling' interchangeably for the same meaning, that is, assigning a task to a processor in the system.

The works of (Joselli, Clua, Montenegro, Conci, & Pagliosa, 2008), (Joselli M., et al., 2008), (Joselli M., et al., 2009) and (Joselli M., et al., 2010) are among those. The focus is on a few select types of tasks in games like physics simulation. In these works, a number of strategies for automatically distributing tasks between the CPU and GPU are proposed as follows:

- 1. **Starting**: this strategy executes the task and computes the time taken to finish a number of frames on the GPU and then the same number of frames on the CPU. With these times, it selects the fastest processor to process all the frames of the application.

- 2. **Cycle**: this strategy repeats the previous strategy every period of time during the application's lifetime.

- 3. **Starting full test**: this strategy repeats the starting strategy for the same task multiple times. In each iteration the value of one of the parameters of the task is increased and the timings are stored. Based on those computed times, the simulation can determine which processor is faster for a determined parameter value of the task.

- 4. Adaptive: this strategy runs with the starting strategy at the beginning, then after a period of time it starts checking how different the task's parameter values are since the start of the application. If they differ above a certain threshold then the "starting" strategy is repeated again.

Those strategies all revolve around executing and sampling the tasks on each of the processors for a certain period of time, and then continuing to use whichever processor is generally faster or has less work load (as measured by operating system API functions).

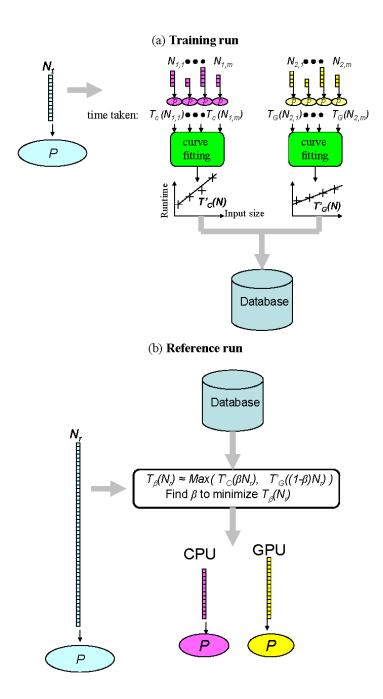

Qilin (Luk, Hong, & Kim, 2009) is a programming system that supports automatic adaptive mapping to map computations to processing elements on heterogeneous multiprocessors. The decision behind mapping a task to a certain processor is directed by a database that provides execution-time projection for all the programs Qilin has ever executed. The first time that a program is run under Qilin, it is used as the training run, where timings are measured under the different processors. The timings are then analyzed with curve fitting to build a projection function that can be used at run-time to determine the best processor type to execute a task depending on the task's input parameters size (Figure 2.11).

Harmony (Diamos & Yalamanchili, 2008) is a runtime system that relies on compute kernels that can be executed either in each kernel's local memory or in global memory. The former case is used to sample kernel performance on processors without affecting program data, while the second case is used for actual kernel execution. The kernel's performance is sampled with its data to make a decision on the best processor to use for execution. The sampled data is cached to avoid continuous kernel evaluation.

In all of the works above, data transfer times between processors is not taken into account. The Hybrid Remapper (Maheswaran & Siegel, 1998), the MATEHa algorithm (Giusti, Chichizola, Naiouf, & Giusti, 2008) and AMTHA algorithm (Giusti, Luque, Chichizola, Naiouf, & Giusti, 2009) on the other hand support a communication matrix that specifies data transfer times between the processors (read and write speeds). However, they do not support dynamically generated tasks, and require that conditional tasks and loops be embedded in larger tasks.

Figure 2.11: Qilin's adaptive mapping technique (Luk, Hong, & Kim, 2009)

The Hybrid Remapper (Maheswaran & Siegel, 1998) is a dynamic mapping algorithm that uses the run-time values that become available for task completion times and

machine availabilities during application execution time to conduct mapping decisions. It uses some results based on an initial static mapping in conjunction with information available only at execution time (hence the name).

MATEHa (short for Mapping Algorithm based on Task dependencies in Heterogeneous Architecture) (Giusti, Chichizola, Naiouf, & Giusti, 2008) is a mapping algorithm that works on DAGs representing tasks and their dependencies. It sections the DAG into "levels" that are then further processed to map tasks in each level to processors. The algorithm works in two steps: The first step determines the level of each graph node, and the second step consists in evaluating to which processor each graph task should be allocated (Figure 2.12).

AMTHA (short for Automatic Mapping Task on Heterogeneous Architectures) (Giusti, Luque, Chichizola, Naiouf, & Giusti, 2009) is an iterative static mapping algorithm that is applied to DAGs describing tasks and their dependencies. The mapping supports heterogeneous processing environments with heterogeneous communication times between the processors. Tasks in the DAG must carry timing estimations for each of the supported processor types. AMTHA then maps the tasks in the DAG one by one until none is left. Procedure MATEHa (G(V,E)) Calculate the level of each node corresponding to V of G. Allocate each task to a processor. } Procedure CalculateLevel (G) ł Given a graph G, the level of an LN(T) node is defined as the minimal number of tasks that should have started its execution for the tasks corresponding to node T to be started as well. The following formula expresses all that has been stated above:  $LN(T) = \min_{Tin \in S} d(T_{in}, T)$ where: S is the set of initial nodes (tasks that do not depend on any other task to start its execution), and  $d(T_{in},T)$  corresponds to the minimal number of arches that have to be crossed from T<sub>in</sub> to T. } Procedure AllocateTaskToProcessor (G) ł This algorithm starts from an initial list where tasks are ordered from lowest to highest LN(Ti)value, and carries out the following steps in order to obtain task allocation in the processors: a. Select the first level n without allocation. b. Calculate the maximal max gain(Ti) gain for those tasks at level n that have not yet been allocated, together with the proc opt(Ti processor to which the task should be allocated. Order the tasks in a decreasing manner

- according to max\_gain(Ti).

- c. Allocate the first task Ti of the list generated in step b to the proc\_opt(Ti) processor.

- d. If there are still tasks without allocation at level n, one should follow with step b.

- e. If there still remain levels without processing, one should go back to step a.

- }

Figure 2.12: Procedures of the MATEHa algorithm (Giusti, Chichizola, Naiouf, & Giusti,

2008)

Tasks are first ranked according to a function that takes into account the time of the task and how many of its dependents are done, and the number of processors of each type in the environment. The task with the highest rank is selected for mapping in each iteration of the algorithm. The selection finds the processor that will result with the minimum time after executing the task in addition to its previous work load. Figure 2.13 lists the general algorithm steps.

Calculate rank for each task.

Whereas (not all tasks have been assigned)

- 1. Select the next task t to assign.

- 2. Chose the processor p to which task t should be assigned.

- 3. Assign task t (selected in step 1) to processor p (selected in step 2).

- 4. Update the rank of the tasks involved in step 3.

Figure 2.13: Pseudo-code with the basic steps of the AMTHA algorithm.

The SASH algorithm (short for Self-Adjusting Scheduling for Heterogeneous Systems) (Hamidzadeh, Lilja, & Atif, 1995) is a dynamic scheduling algorithm supporting tasks that are dynamically generated at arbitrary times during program execution. It utilizes a dedicated processor to execute the scheduling algorithm. SASH performs repeated scheduling phases in which it generates partial schedules. At the end of each scheduling phase, the scheduling processor places the tasks scheduled in that phase on to the working processors' local queues. Scheduling uses an on-line optimization technique that minimizes an execution cost function which takes into account task execution times as well as communication times in heterogeneous environments, and it shares some similarities with the selection function in AMTHA. The algorithm searches through a space of all possible partial and complete schedules represented by a tree. In each iteration the node with the lowest cost is expanded by extending the partial schedule with

an additional edge (a scheduled task). The expansions continue until all of the tasks have been scheduled or the scheduling phase uses its allowed time.

The work stealing algorithm (Blumofe & Leiserson, 1999) is a randomized scheduling algorithm that has been shown to give optimal results when run on homogeneous environments with negligible communication times, which is the case for multi-core systems with shared memory. The algorithm is simple. Each processor is first associated with a local work deque onto which tasks can be pushed. Tasks (or work) are initially assigned at random to any processor. A processor pops tasks from its deque one by one and executes them. When the processor's deque becomes empty, it enters work stealing mode and operates as follows. The processor becomes a *thief* and attempts to steal work from a *victim* processor chosen uniformly at random. The thief queries the deque of the victim's ready deque is empty then the thief tries again by picking another victim at random. The algorithm is capable of scheduling dynamically generated task graphs. However, it does not support heterogeneous processing environments.

CellCilk (Werth, Schreier, & Philippsen, 2011) extends the Cilk language (Blumofe, et al., 1995) to work on the IBM CELL processor (PPU and SPUs) (Kahle, et al., 2005) by utilizing different work stealing strategies applied on different scheduling levels:

- 1. Nano: The scheduling level where the worker adds and pulls tasks from its local work queue and executes them.

- Micro: The scheduling level used when stealing from another work of the same processor type.

Macro: The scheduling level at which tasks are transferred from one processor type to another.

CellCilk adds 5 new keywords to the Cilk language, which include spu\_spawn in addition to the Cilk spawn keyword. The latter being used to spawn tasks for the SPU explicitly, as the original spawn keyword does not hide this detail from the programmer.

StarPU (Augonnet, Thibault, Namyst, & Wacrenier, 2011) offers a flexible plug-in based run-time system that supports scheduling dynamically generated tasks in heterogeneous processing environments. The system is targeted towards numerical kernel designers. It offers a high level library for transparently performing data movements between the different memory locations of system, in addition to a unified task execution model. StarPU can use one of multiple scheduling policies available to determine the best processor to be used for dynamically generated tasks. The paper lists 4 different scheduling policies (the Work Stealing algorithm being one of them). However, none of those policies seem to take into consideration data transfer times between processors in their decisions.

# 2.6 SUMMARY AND CONCLUSIONS

A number of works in the literature describing game application design and game hardware was reviewed. In addition, previous work on parallel design patterns and task scheduling algorithms and run-time systems for multi-processor environments was also discussed. In spite of the extensive work, it is clear that there is need for a specialized framework for parallelizing games which takes into account dynamic tasks, processor capabilities, data transfer and data locality.

# CHAPTER 3 A NEW GAME PARALLELIZATION FRAMEWORK

# **3.1 INTRODUCTION**

As discussed in Chapter 2, the growing complexity of game applications requires that these applications be able to make efficient use of their host environments. Since these environments offer parallel processing capabilities in the form of heterogeneous processors, it is important that games be able to execute their tasks on those processors to maximize performance. This cannot be automatically obtained from the classical code structure that games are usually built upon. Many games nowadays are built upon a game engine, which is a reusable collection of utilities and functionality common to a number of games. Many game engines exist with different capabilities and supporting different game types. Most of those engines have been written for serial execution. Converting a game engine to work in parallel is a difficult task that often requires refactoring code and data structures. It is thus important to consider reducing this effort as much as possible when suggestion a solution to parallelizing games. Of equal importance, if the solution was easy to use for programmers, then newly written games will also benefit from this feature. A design pattern is by definition a solution strategy that can be applied to problems of similar type. Since games share a similar code structure, it is desirable to find a design pattern that can address parallelizing this type of applications. Using this design pattern, the programmer should be able to express game tasks in such a way that maximizes parallelism between these tasks. Unfortunately, very little of the previous work on design patterns targets the game domain. Other works exist but mostly fail to

match the special requirements of game applications. Without fulfilling these requirements the game application cannot realize its full parallelization potential, and thus will not result in optimal performance.

Once the parallel game tasks have been generated, a run-time system must be able to schedule them to be executed on one of the processing elements available in the host environment. As has already been shown in section 2.3, the host environments onto which games are run nowadays offer heterogeneous processing capabilities. It is thus important to find a strategy for efficiently scheduling game tasks in a heterogeneous processing environment consisting of different processor types with different memory access policies and speeds. Again, research that targets the games domain in this area is limited. Other works fall short in one or more detail that would render the application of the solution inefficient.

In this research we propose a new game parallelization framework consisting of a parallel design pattern as the front end to simplify the game parallelization task for programmers and a game task scheduler at the back which automatically maps and assigns tasks to processors using a cost function that takes specific aspects of game applications into account and results in improved performance with better utilization of the heterogeneous computing resources available in the host environment. We describe these two major components of our framework in the rest of this chapter.

We split this chapter into two main sections. The first section presents a parallel design pattern for the game applications. It starts by highlighting properties of game applications that lead to deriving a set of requirements needed to maximize parallelization in this type of applications. Then, a new design pattern fulfilling these requirements is developed. By applying the design pattern, a game application will have generated at run-time a set of tasks to be scheduled. The second section focuses on the design and implementation of a dynamic scheduler which can take tasks generated from the work in the first section and map them to processing elements in a heterogeneous environment in a manner that maximizes overall application performance.

#### **3.2 SAYL DESIGN PATTERN**

In this section, we first describe the major characteristics of computations in the games application domain. A directed acyclic graph (DAG), with a few additional properties to capture specifics of this domain, is used to represent these computations as tasks with dependencies among them. Possible solution strategies are discussed and then Sayl<sup>1</sup> is presented, a new domain-specific design pattern for parallel programming of games and simulations, with support for creation of dynamic task graphs. We describe a sample implementation which is then compared with some other works in this domain.

#### **3.2.1** The Problem Domain

Games usually involve a variety of computations, including:

1. **Functional calculations**: Calculations which transform input data to output data of possibly different size and type. Tasks of this type can be functional (i.e., they have no side effects). However, it is also common in game applications that tasks of this

<sup>1</sup> The name Sayl is the pronunciation of the Arabic word meaning "stream". The name is inspired from the properties of a river stream, that is, a group of parallel threads of water flowing endlessly next to each other. This is similar to what results when using the Sayl design pattern: a stream of continuously-generating tasks executing in parallel threads.

type use additional acceleration structures to increase performance (e.g., cache). This invalidates the status of these tasks as having no side effects, and hence requires additional care when parallelizing such tasks. A typical example is world culling, which requires determining of game entities that fall within the view range of the 3D world camera. Another example is character bone update, which requires calculation of bone transforms for animated characters.

- 2. State-based calculations: Calculations which depend on continuous tracking and update of state. This is commonly associated with game entity updates (e.g., enemies, cars, etc.) which occur at every frame of the game. Data accessed in such tasks usually involves other objects (e.g., a character querying a nearby object for a certain value). An example is game AI, which is frequently implemented using finite state machines. Such tasks rely on evaluating current state to make a decision and possibly update that state.

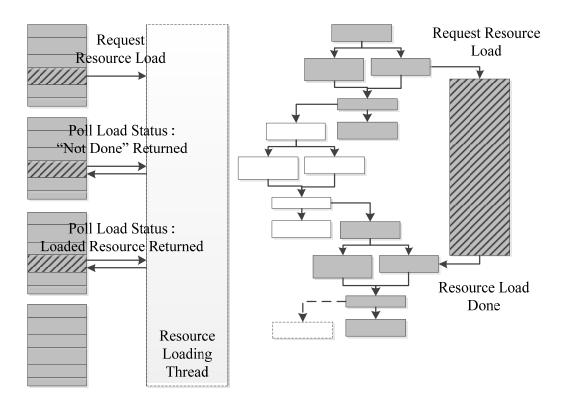

- 3. **Data-retrieval**: Almost all game applications rely on graphics and sound as a medium of output to the user. This requires loading, generating, or gathering data from input sources for further processing. Such tasks usually do not involve complex computations, but rather a lot of interfacing with the operating system to request the data. One example is load resources resources such as textures, 3D geometry, sounds, images, etc., are usually stored on a storage device, and must be loaded into memory before being used. Another example is read device games require user interaction usually through a controller device connected to the computer.

From the above, it can be seen that a typical game application has wide diversity in the types of tasks that need to be carried out. Some of the tasks are data-dependent on other

tasks in order to progress. For example, game input is required to determine how to update the player's state, which in turn affects other aspects of the game. Generally, as a task executes it may produce multiple pieces of data at different times during its execution. These data may be required by other tasks. Ideally, for increased parallelism, the data should be available to the dependent tasks as soon as they are produced even if the originating task has not finished execution.

Furthermore, the set of tasks that a game executes might change depending on various conditions and logic. For example, consider a game that draws an explosion effect made of particles on each bullet hit. Here the number of explosions and number of particles change depending on how many bullets have been shot and what materials did they hit. If no bullets were shot, then no tasks for particle simulation need to be executed.

Based on the previous discussion, following is a list of the major characteristics of the tasks in a typical game application:

- 1. **Heterogeneity of tasks**: Game tasks perform different operations (e.g., particle simulation, character animation, path-finding, etc.). Additionally, there could be considerable variations in their completion times and functionalities.

- 2. **Data-flow type dependency**: Some tasks depend on data from other tasks before they can execute. This dependency between tasks can be represented by a connected directed acyclic graph (DAG), where each edge represents a dependency in the form of a data-flow (Figure 3.1).

- 3. **Dynamic set of active tasks**: The task graph repeats itself in each frame of the game for the entire life-time of the application. However a different subset of tasks may run

in different iterations, which is represented by the dashed arrows and nodes with crossed patterns in the task graph (Figure 3.1). In other words, the task graph is dynamic.

Our goal is to create a solution for specification and parallel execution of such a dynamic task graph with the game domain-specific characteristics listed above.

Figure 3.1: A directed acyclic graph representing tasks and their dependencies in a game application (boxes represent tasks, and arrows represent data flow dependency between tasks). Tasks hatched with a cross pattern illustrate that the actual number of tasks of that type is determined at runtime. The thick lines inside some task boxes represent points in time at which a certain piece of data is calculated and is ready to be sent to other tasks in the graph. Boxes that do not have outgoing arrows are output tasks (display to screen,

audio output, etc.).

## 3.2.2 Solution Strategy

For the purpose of separation of concerns, we can identify three main components in the problem: tasks. their dependencies, scheduling. given and The game designer/programmer deals with the first two components. Thus, we will refer to these two components as the front-end, which is detailed in section 3.2.3. The scheduler component is the back-end (detailed in section 3.2.4) and the game designer/programmer is not directly involved in its design or programming. In essence, the front-end is concerned with generating tasks, while the back-end is concerned with how to execute them.

It may be noted that the work described in this thesis does not at present address automatic parallelization of existing sequential code. Hence, it is assumed that designers/programmers will manually decompose the given sequential algorithm into tasks of suitable granularity, and will identify their dependencies. As described next, their work is considerably simplified since creation of the dynamic task graph is implicitly embedded in the front-end pattern. A few of the computations may be more difficult to decompose than others. Data retrieval tasks for example may involve two-way communication between threads, which cannot be directly expressed using a DAG. Section 3.2.6 presents a method of addressing this situation.

#### 3.2.3 Sayl Front-end

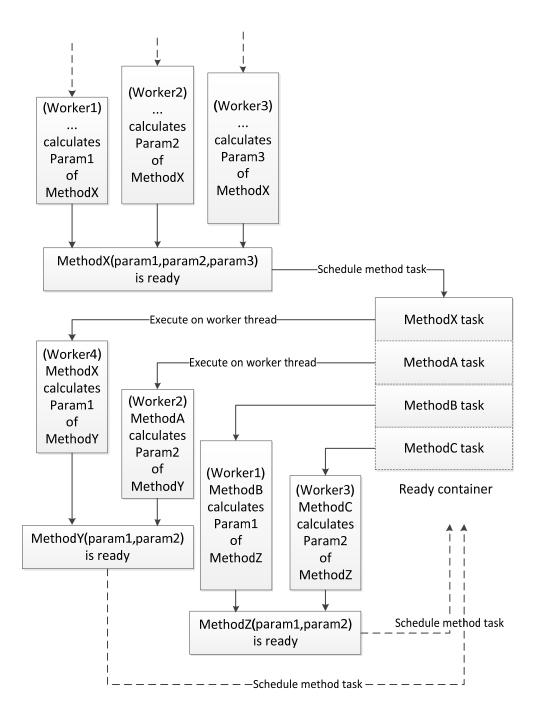

The Sayl Front-end component is based on the concept of invoking methods with eager parameter evaluation in imperative programming languages. This pattern lets the programmer model the tasks and their dependencies as method calls with parameters. By doing so, the programmer has implicitly defined the tasks and their dependencies in a data-flow fashion. Parameters can be evaluated in parallel if no dependencies exist between them and then passed to the method requiring them. Once a task has received all of its parameters its execution is started as in eager parameter evaluation.

The above programming methodology implicitly results in a dynamic task graph. Execution of a task may result in generation of other tasks, as shown in a following subsection. The back-end component discussed next gives strategies for executing these tasks efficiently.

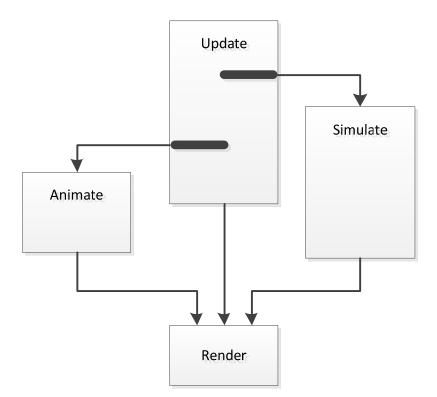

# 3.2.4 Sayl Back-end

It is the job of the back-end component to take the tasks generated by Sayl front-end and schedule them for execution as soon as their parameters become available. Any task with two or more parameters is stored in a prepare container until all its inputs have been fulfilled, after which the task is moved to the ready container. Tasks with at most one parameter are stored directly in the ready container. Thus, the ready container contains only tasks which are ready for execution (Figure 3.2 and Figure 3.3) in an order independent fashion. The dependency requirement is maintained by the fact that only methods which have their parameters fulfilled are scheduled for execution.

Figure 3.2: A graph representing methods called in a hypothetical game application.

In addition to these two containers, the back end also has a pool of continuously running threads, called worker threads. The number of worker threads should match the number of available processing elements so that each thread runs on a processing element without context switching overhead. A worker thread removes a task from the ready container, executes it to completion, and then looks for another task. Any tasks generated by the executing task are put back into appropriate containers.

Figure 3.3: Run-time interaction diagram in the back-end. A number of worker threads consume tasks from the ready container. Upon execution, the task (method) calculates the value of one (or more) parameters of another method. When the second method's parameters are fulfilled, it is inserted into the ready container to be picked up for execution by a worker thread.

The order of queuing or executing tasks in the ready container is irrelevant to the correctness of the program. This flexibility allows the implementation to utilize any container design which is found efficient to achieve high performance in task scheduling or to fulfill additional task requirements. For example: if the tasks in the ready container have priorities, then an implementation using binary heap based priority queues may be quite efficient. Figure 3.3 illustrates the run-time interaction in the back-end of the Sayl pattern.

#### 3.2.5 Implementation

A sample implementation of the Sayl pattern in C++ is described in the following. The front-end interfaces with the back-end via APIs (see Figure 3.4).

Starting with the back-end, each WorkerThread object has two member fields: an event named Wake, and a Boolean variable named Exit. The ReadyTasks container holds tasks pending execution. The PreparingTasks container holds tasks that are not ready as some of their parameters are not yet available. IdleWorkers is a container storing idle worker threads at any time during execution.

| Front-end                |            |             |               |

|--------------------------|------------|-------------|---------------|

| AddTask() AddTaskParam() |            |             |               |

| Back-end                 |            |             |               |

| PreparingTasks           | ReadyTasks | IdleWorkers | WorkerThreads |

Figure 3.4: Pattern interface APIs and implementation components.

The code in Figure 3.5 below shows the two main methods driving the back-end component of the pattern.

The WorkerThread is a thread running the internal method WorkThread. This method is a simple loop that continues while the method OnTaskDone returns true. OnTaskDone checks the ReadyTasks container to see if the thread can pick a new task to execute. If no tasks are found in the container, then the thread adds itself to the IdleWorkers container and sleeps waiting for its Wake event to be signaled. The method returns false when thread termination is determined.

```

internal method WorkThread()

{

while (OnTaskDone()) {};

}

internal method OnTaskDone()

Task TaskToExecute = ReadyTasks.PopAny();

if (TaskToExecute != null)

TaskToExecute.Execute();

return this.Exit;

}

int IdleWorkersCount = IdleWorkers.Push(this);

if (IdleWorkersCount == WorkerThreadsCount)

{

while (true)

ł

Thread IdleWorker = IdleWorkers.PopAny();

if (IdleWorker == null)

break;

IdleWorker.Exit = true;

SignalEvent(IdleWorker.Wake);

}

return false;

}

else SleepUntilSignalled(this.Wake);

return this.Exit;

}

```

Figure 3.5: Sayl methods that drive the back-end.

The front-end of the pattern is implemented by exposing the only two public methods the user needs to deal with, namely AddTask and AddTaskParam (Figure 3.4). Figure 3.6 below shows the implementation for both.

```

public method AddTask(TaskMethod, optional Param)

ReadyTasks.Push(TaskMethod,Param);

Thread WorkerThreadObj = IdleWorkers.PopAny();

if (WorkerThreadObj != null)

SignalEvent(WorkerThreadObj.Wake);

}

public method AddTaskParam(

TaskMethod,

TaskSubID, ParamsCount,

ParamID, ParamValue)

{

EnterCriticalSection(PreparingTasks)

TaskParamsEntry TaskParams =

PreparingTasks.Find(TaskMethod,TaskSubID);

if (TaskParams == null)

TaskParams = PreparingTasks.AddNew(

TaskMethod,ParamsCount);

Assert(TaskParams.ParamsCount == ParamsCount);

TaskParams.SetParam(ParamID,ParamValue)

bool TaskReady =

(TaskParams.Count == ParamsCount);

if (TaskReady == true)

PreparingTasks.Remove(TaskParams);

ExitCriticalSection(PreparingTasks)

ReadyTasks.Push(TaskMethod,

TaskParams.ParamsList);

Thread WorkerThreadObj = IdleWorkers.PopAny();

if (WorkerThreadObj != null)

SignalEvent(WorkerThreadObj.Wake);

}

```

Figure 3.6: Pseudo-code implementing front-end methods of Sayl.

AddTask adds a new task to the ReadyTasks container and wakes an idle thread to execute it if available. AddTaskParam is a more powerful version of AddTask that allows passing parameters to a task that takes two or more parameters, which could be

generated by different tasks. It requires the user to specify the total number of parameters the task needs, and an ID for the task to uniquely identify it from other instances if they may exist. Such tasks are added to the PreparingTasks container. Each call to AddTaskParam passes the value of one of the parameters to the task. When all parameters have been provided, the task is added to the ReadyTasks container. Until then the task remains in the PreparingTasks container.

Using just these two API calls, Sayl users can express tasks and their dependencies with the guarantee that these dependencies will be correctly preserved.

The code in Figure 3.7 below shows an example of how Sayl-front-end can be used to express an execution graph for a small part of a hypothetical game application as shown in Figure 3.2.

From the previous example, it can be seen that using the Sayl pattern, spawning tasks to execute methods in parallel is a simple transition from writing sequential code. This quality is very important as it contributes significantly to the ease-of-use aspect of this pattern. At the same time, it shows the fundamental differences with traditional fork-join and similar approaches (e.g., the Render method is data-flow dependent on the other methods).

```

public method Update()

... /* Update code */

AddTask(Simulate, Player)

... /* Update code */

AddTask (Animate, PlayerModel)

... /* Update code */

AddTaskParam(

Render,FrameIndex,3,Param Camera,Camera);

}

public method Simulate(PlayerToSimulate)

... /* Simulation code */

AddTaskParam (Render, FrameIndex, 3,

Param SimPlayer,PlayerToSimulate);

}

public method Animate(PlayerToAnimate)

... /* Animation code */

AddTaskParam(Render, FrameIndex, 3,

Param AnimModel,PlayerToAnimate);

}

public method Render(Camera,

SimPlayer, PlayerModel)

{

... /* Rendering code */

```

Figure 3.7: Pseudo-code using Sayl to represent an execution graph for a small part of a hypothetical game application.

One of the commonly found tasks in games is data retrieval, which could require twoway communication with other tasks. Games often run a secondary resource loading thread in addition to the main game loop thread. The loading thread receives commands to load particular resources and executes them without blocking the game loop while the data is being transferred. In each game loop iteration (represented by a colored block in Figure 3.8 left), the requested resources are polled for completion. Using Sayl, it is possible to achieve the same functionality without a secondary resource loading thread as follows: when a task determines that a resource needs to be loaded, it spawns a new task and passes it the resource identifier and the identifier of the task that requires the resource. The new task (represented by a hashed box in Figure 3.8 right) then loads the resource when it runs. When done, it simply passes the loaded resource as a parameter to the specified task.

Figure 3.8: Left: Multiple iterations of a hypothetical game loop, in which there is a resource load request being communicated with a resource loading thread. Right: The same game loop after applying the Sayl design pattern. The resource load request becomes spawning a task that loads the resource and passes it to the task that needs it. Each group of solid colored tasks represent tasks belonging to a single game loop iteration.

## 3.2.6 Discussion

The Sayl pattern has a number of advantages:

- A task is only spawned when its dependencies are fulfilled. For game applications, this is more efficient than spawning tasks that keep polling to check their dependencies for completion. This way precious processing power is not wasted.

- 2. Tasks in Sayl are only allocated in memory when they are preparing to be executed (i.e., on demand); whereas in some other patterns (e.g., Cascade and Task Graph) tasks are allocated up-front and they wait until their dependencies are fulfilled before they become ready to execute. Thus, Sayl implementations should be able to utilize memory for storing tasks at run-time more efficiently than some of the other patterns.

- 3. In Sayl, the programmer has implicitly defined the tasks and their dependencies by writing the program using methods and parameters. Consequently the programmer need not explicitly declare dependencies for each task as in the case of Task Graph and Cascade. This is what makes programming using this pattern rather simple.

- 4. Sayl can also help convert existing game code bases into parallel versions with greater ease, thus motivating increased code reuse.

- 5. Not mandating any order of execution for the tasks in the back-end opens more opportunities for choosing the appropriate type of task container.

For game applications, supporting dynamic task graphs makes a difference versus statically defined task graphs. For example, Cascade is a parallel programming environment (PPE) specifically addressing the games domain. While it has support for task heterogeneity and task dependencies, it lacks the support for dynamic task graphs.

The Sayl pattern, on the other hand, enables the programmer to build the task graph dynamically by spawning tasks only on demand by the executing task(s).

In any static task graph-based approach, the programmer must define all tasks and their dependencies beforehand and the graph has to be fully constructed prior to its execution. Typically, it only represents a portion of the application's lifetime (e.g., one frame because subsequent frames may require modifications to the task graph). The program therefore has to wait for the current static task graph to finish before executing the next one, even if it were possible to execute some tasks from the current graph in parallel with tasks from the next graph (e.g., pure output tasks). On the other hand, the dynamic task graph is capable of implicitly representing all the frames in the entire lifetime of a game.

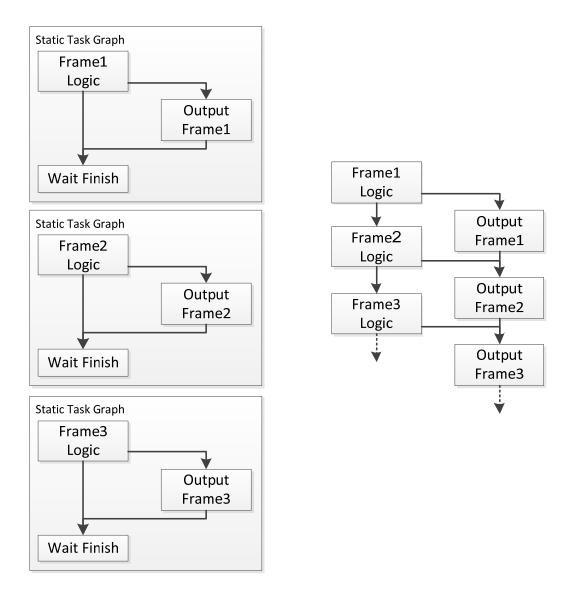

Figure 3.9 illustrates how overlapped executions among frames are possible using a dynamic task graph. As shown, tasks from the next frame are invoked by tasks from the current frame as the execution proceeds, and hence task executions are not bounded by frame boundaries. The same is not possible when static task graphs are used.

Moreover, the realization of the static task graph requires allocating it entirely in memory prior to executing it. More specifically, using Cascade, the programmer builds the task graph in a three-step process as follows:

- Define a class for each type of task. The class contains the implementation of the task's method, in addition to implementation of an interface to define the inputs and outputs of the task.

- 2. Define instances of the tasks in the task graph.

- 3. Specify dependencies between the tasks instances.

Figure 3.9: Task graphs representing methods called in a hypothetical game application.Left: Multiple static task graphs, where each instance computes one frame of the game.Right: The dynamic task graph is capable of running the logic for the next frame while output of the current frame is being processed in parallel.

The above 3 steps incur significant overhead to the programmer in terms of programming efforts required. On the other hand, defining the task graph using Sayl involves writing the task's method along with specifying its parameter list. Within the method, parameters are passed to other task(s) (method(s)) as soon as they are computed. Sayl extracts

dependency information directly from methods and their parameters. The net outcome is that Sayl involves less programmer work in writing parallel game applications.