# **EMTP-RV Simulation of a Chain Link STATCOM**

Nikunj Mahesh Shah

**A Thesis**

In

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

August 2007

© Nikunj Mahesh Shah, 2007

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-34777-5 Our file Notre référence ISBN: 978-0-494-34777-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# **ABSTRACT**

#### **EMTP-RV Simulation of a Chain Link STATCOM**

### Nikunj Mahesh Shah

An advanced static VAr compensator (ASVC), using a voltage-source-converter (VSC), popularly known as a static synchronous compensator (STATCOM), is generally acknowledged as the next-generation reactive power controller in power systems. Its mode of operation is analogous to that of a rotating synchronous condenser and it provides dynamic voltage compensation, increased transient stability and damping for the power system. Several STATCOMs, based on high power semiconductor switches (e.g. Gate Turn Off thyristors, GTOs or Insulated Gate Bipolar Transistors, IGBTs) and a special zigzag transformer have been put into operation. These STATCOMs have advantages over conventional static VAr compensators (SVCs) of lower harmonic generation, improved performance and a smaller reactor size. However, the zigzag transformers used in these STATCOMs are bulky, expensive and as yet unreliable. An alternative method to eliminate the zigzag transformer and to increase the STATCOM rating with a corresponding reduction in harmonics is to use a multilevel converter, which produces a 'multi-stepped' output voltage waveform in a close approximation to a sine wave.

A recent addition to the multilevel converter based STATCOM family has been obtained by connecting a number of VSCs in series on the ac side of the system forming a 'chain' per phase. Each VSC is a 1-phase, full-bridge converter and forms a 'link' of a

'chain'. This STATCOM configuration is referred to as a 'Chain Link STATCOM'

(CLS). In this thesis, a GTO is used as a switch for the CLS. However, any other high

power semiconductor switch (e.g. IGBT) may also be used instead. Each GTO of the

CLS, is switched on/off only once per cycle of the fundamental frequency by employing

a sinusoidal pulse width modulation (SPWM) technique. Approximate models of a 3-

phase CLS using dq-transformation are derived to design two cascaded controllers for

controlling reactive current and ac voltage to stabilize the power system voltage at the

point of common coupling (PCC). A novel technique, called the rotated gate signal

pattern (RGSP), is used for balancing the voltages of the link dc capacitors of the VSC.

The performance investigation of the CLS system when used in a radial line transmission

system is carried out under steady- and transient-state operating conditions by means of

the simulation package EMTP-RV.

Index terms: Chain link STATCOM, VSC, SVC, STATCOM, FACTS, EMTP-RV.

iv

# **ACKNOWLEDGEMENTS**

Seldom, a research project is an achievement of an individual. For the completion of this project also, I had the assistance and support from the following individuals. I would like to express my sincere gratitude and heartfelt thanks to all of them.

Dr. Vijay K. Sood for being my technical guru, sharing his unique power system insights, granting me freedom of work, his invaluable guidance, advice, encouragement, and financial support throughout the course of this study.

Dr. V. Ramachandran for being a wonderful supervisor and providing me his continuous financial support and advice during this research.

Abhay Shah, Sasan Salem, Saurin Patel, Shetul Patel, Hetal Desai, Neil D'Souza and Nasima Monsoor for their smart suggestions, helpful discussions and providing the assistance when needed.

Above all, my parents, brother, sister, my in-laws and especially my wife Elsa, for providing me constant moral support, inspiration, encouragement and assistance to complete this research project.

With love, praise and honour, I dedicate this thesis to my family.

Nikunj M. Shah

to my family.....

# TABLE OF CONTENTS

| Lis                     | LIST OF FIGURES                              |                       |

|-------------------------|----------------------------------------------|-----------------------|

| Lis                     | T OF TABLES                                  | XV                    |

| Lıs <sup>-</sup>        | T OF ACRONYMS                                | XVI                   |

| Сн                      | APTER-1 INTRODUCTION                         | 1                     |

| 1.1.                    | GENERAL                                      | 1                     |

| 1.2.                    | REACTIVE POWER COMPENSATION [1-4]            | 1                     |

| 1.2<br>1.2<br>1.2<br>Co | METHODS OF REACTIVE POWER COMPENSATION [1-8] | 2 6 10 11 12 13 14 15 |

| 1.3.                    | EMTP-RV: OVERVIEW [1]                        | 19                    |

| 1.4.                    | LITERATURE REVIEW                            | 19                    |

| 1.5.                    | SCOPE AND CONTRIBUTION OF THIS THESIS        | 21                    |

| 1.6.                    | THESIS OUTLINE                               | 23                    |

| 1.7.                    | SUMMARY                                      | 25                    |

| CHA  | TER-2 CHAIN LINK STATCOM: THEORY                   | 26 |

|------|----------------------------------------------------|----|

| 2.1. | INTRODUCTION                                       | 26 |

| 2.2. | BASIC CIRCUIT ARRANGEMENT & PRINCIPLE OF OPERATION | 26 |

| 2.3. | GATING STRATEGY                                    | 30 |

| 2.3  | . General                                          | 30 |

| 2.3  | . SPWM technique for a CLS                         | 30 |

| 2.4. | HARMONIC ANALYSIS OF THE CLS OUTPUT VOLTAGE [19]   | 33 |

| 2.5. | CLS: IMPORTANT FEATURES [1, 10]                    |    |

| 2.5  | General                                            | 34 |

|      | . Ratings                                          |    |

|      | . Losses                                           |    |

|      | . Redundancy                                       |    |

| 2.5  |                                                    |    |

| 2.5  | A                                                  |    |

|      | Advantages of a CLS [1, 10]                        |    |

| 2.5  | . Main constraints of a CLS                        | 39 |

| 2.6. | CLS FOR THE NATIONAL GRID COMPANY, UK [1, 10]      | 39 |

| 2.6  | . Basic layout of SVC system for NGC, UK           |    |

|      | . Key design features of the CLS for NGC, UK       |    |

| 2.7. | SUMMARY                                            | 42 |

| Сна  | TER-3 CLS POWER CIRCUIT & SYSTEM MODELING          | 43 |

| 3.1. | INTRODUCTION                                       | 43 |

| 3.2. | POWER CIRCUIT OF THE CLS SYSTEM                    | 43 |

| 3.3. | GTO-DIODE SWITCH MODEL ('SW')                      | 45 |

| 3.4. | VSC LINK MODEL                                     | 47 |

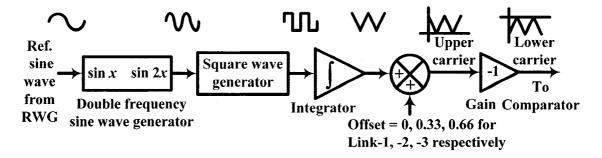

| 3.5. | SPWM CIRCUIT MODEL                                 | 47 |

| 3.5  | Triangular carrier generator for a link.           | 48 |

| 3.5  | Comparator                                         | 49 |

| 3.6. | CLS SYSTEM MODELING                                |    |

| 3.6  |                                                    |    |

| 3.6  | <b>,</b>                                           |    |

| 3.6  | Steady-state model of the CLS                      | 56 |

# CHAPTER-4 OPEN-LOOP CONTROL & PRELIMINARY SIMULATION

|             | STUDY OF 1-PHASE CLS WITH EMTP-RV                                                                                                                                         | 59             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.1.        | INTRODUCTION                                                                                                                                                              | 59             |

| 4.2.        | OPEN LOOP CONTROL PHILOSOPHY                                                                                                                                              | 60             |

| 4.3.<br>4.3 | ROTATED GATE SIGNAL PATTERN (RGSP)                                                                                                                                        |                |

|             | 3.2. Basic principle                                                                                                                                                      |                |

| 4.4.        | START-UP PROCEDURE OF THE CLS                                                                                                                                             | 68             |

| 4.5<br>4.5  | PRELIMINARY SIMULATION RESULTS  5.1. Initialization of the CLS system  5.2. DC capacitor voltage balance  5.3. Steady state performance  5.4. Transient state performance | 70<br>71<br>73 |

| 4.6.        | DISCUSSION & CONCLUSION                                                                                                                                                   |                |

| Сна         | APTER-5 CLOSED-LOOP CONTROL STRATEGIES & DESIGN                                                                                                                           |                |

|             | OF CONTROLLERS                                                                                                                                                            | 85             |

| 5.1.        | INTRODUCTION                                                                                                                                                              | 85             |

|             | OPEN LOOP TRANSFER FUNCTIONS (OLTF)                                                                                                                                       | 85             |

| 5.3.        | REACTIVE CURRENT & AC VOLTAGE CONTROLLERS                                                                                                                                 | 87             |

|             | DESIGN OF CONTROLLERS                                                                                                                                                     | 89             |

| Сна         | APTER-6 SIMULATION RESULTS                                                                                                                                                | 94             |

| 6.1.        | INTRODUCTION                                                                                                                                                              | 94             |

| 62          | STEADY-STATE PERFORMANCE                                                                                                                                                  | 94             |

| 6.3. TRANSIENT-STATE PERFORMANCE            |           |

|---------------------------------------------|-----------|

| 6.3.1. Initialization of the CLS-system     |           |

| 6.3.2. Step change in voltage reference     |           |

| 6.3.3. Step change in the load              |           |

| 6.3.4. Balanced three-phase fault at bus B2 |           |

| CHAPTER-7 CONCLUSIONS                       | 97        |

| 7.1 SUMMARY                                 | 104       |

| 7.2 CONTRIBUTION                            | 105       |

| 7.3 SUGGESTIONS FOR THE FUTURE WORK         | 107       |

| References                                  | 108       |

| APPENDIX - A CLS SYSTEM PARAMETERS          | 111       |

| APPENDIX – B DESIGN CALCULATIONS OF CONTROL | LLERS 112 |

| APPENDIX - C LIST OF PUBLICATIONS           | 117       |

# LIST OF FIGURES

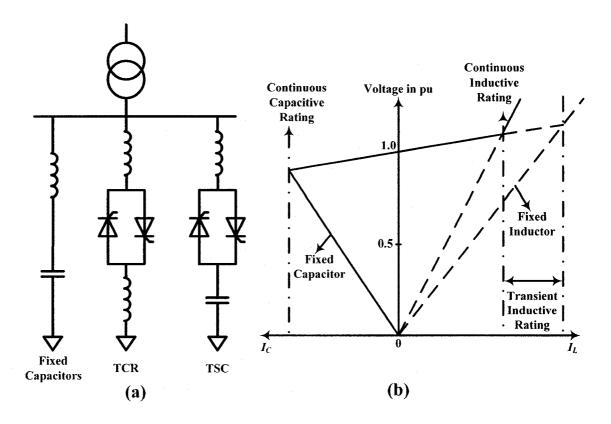

| Figure 1.1. | (a) Conventional SVC System, and its (b) V-I characteristic4       |

|-------------|--------------------------------------------------------------------|

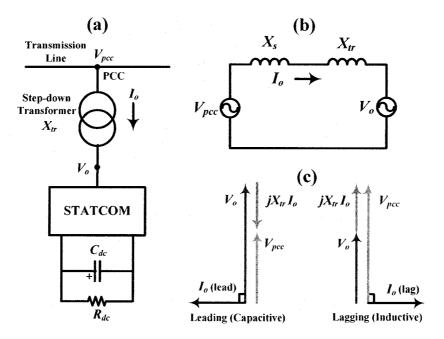

| Figure 1.2. | (a) Single line diagram of the STATCOM system, (b) Simplified      |

|             | equivalent circuit of a STATCOM connected to the AC system,        |

|             | and (c) Phasor diagrams7                                           |

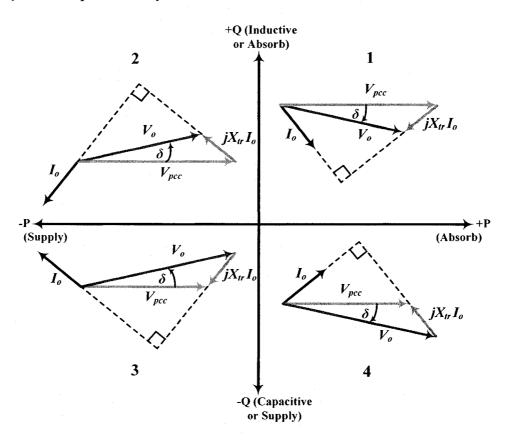

| Figure 1.3. | Phasor diagrams for power exchanges in a STATCOM9                  |

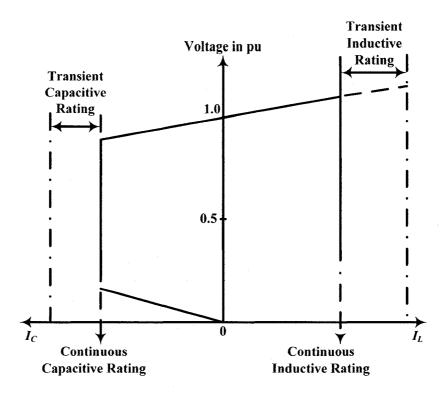

| Figure 1.4. | V-I characteristic of STATCOM11                                    |

| Figure 1.5. | Conventional 3-phase 6-pulse VSC based STATCOM circuit             |

| Figure 1.6. | 3-phase 5-level diode clamp converter16                            |

| Figure 1.7. | 3-phase 5-level flying capacitor converter                         |

| Figure 2.1. | General circuit arrangement of a 1-phase CLS with 'N links'27      |

| Figure 2.2. | (a) Block diagram and (b) Simplified circuit diagram of a 1-phase  |

|             | VSC link                                                           |

| Figure 2.3. | 3-level output voltage $(v_k)$ of a 1-phase VSC link               |

| Figure 2.4. | (2N+1) level output phase voltage waveform of a CLS with 'N' links |

|             | per phase29                                                        |

| Figure 2.5. | (a) SPWM technique with six triangular carrier bands for 3-links,  |

|             | (b) SPWM output voltage of the CLS, and its fundamental frequency  |

|             | component, (c), (d) and (e) SPWM output voltage of the link-1, -2  |

|             | and -3 respectively31                                              |

| Figure 2.6. | Configuration of SVC system in NGC's East Claydon                                 |

|-------------|-----------------------------------------------------------------------------------|

|             | substation, UK                                                                    |

| Figure 3.1. | Single line diagram of the CLS system44                                           |

| Figure 3.2. | GTO-diode switch model 'SW' in EMTP-RV 45                                         |

| Figure 3.3. | Model of VSC link in EMTP-RV47                                                    |

| Figure 3.4. | Triangular carrier generator for each link48                                      |

| Figure 3.5. | Comparator to generate the gate signals for each switch 'SW'49                    |

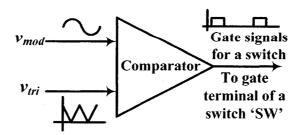

| Figure 3.6. | (a) Thevenin equivalent circuit of CLS system and (b) its space                   |

|             | vector diagrams51                                                                 |

| Figure 3.7. | Block diagram of a VSC link53                                                     |

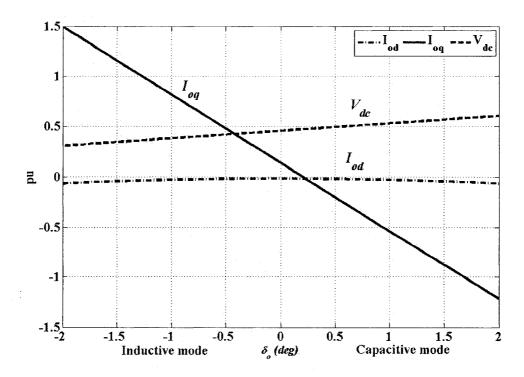

| Figure 3.8. | Steady-state variation of $I_{o\_d}$ , $I_{o\_g}$ and $V_{dc}$ against $\delta_o$ |

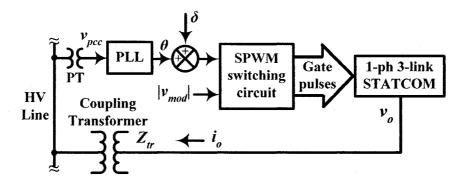

| Figure 4.1. | Open-loop control of a 1-phase 3-link CLS                                         |

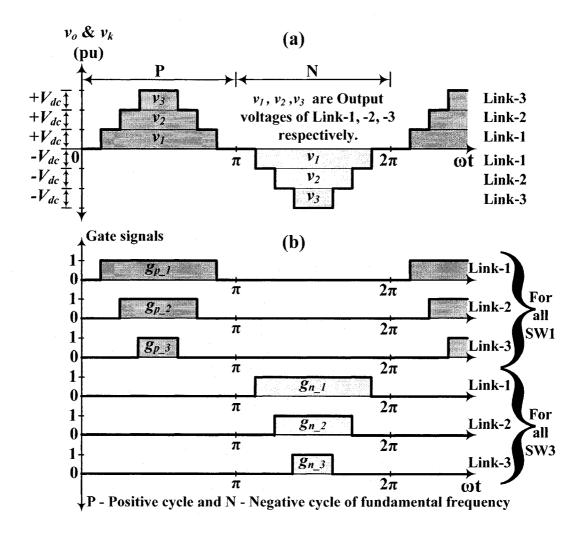

| Figure 4.2. | (a) Output voltage waveform and (b) gate signals per phase without                |

|             | RGSP for a CLS having three-links per phase                                       |

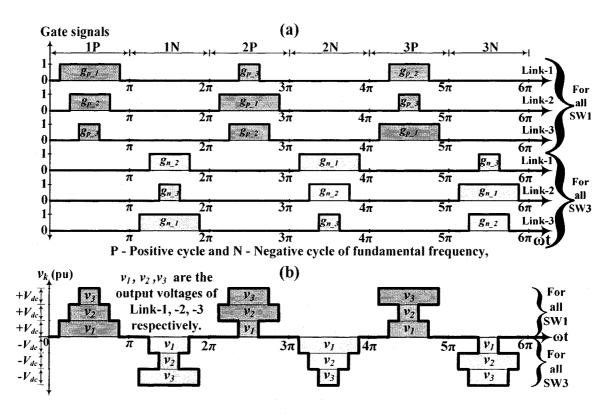

| Figure 4.3. | (a) Rotated gate signal pattern (RGSP) per phase and (b) Link output              |

|             | voltages per phase, for a CLS having 3-links per phase                            |

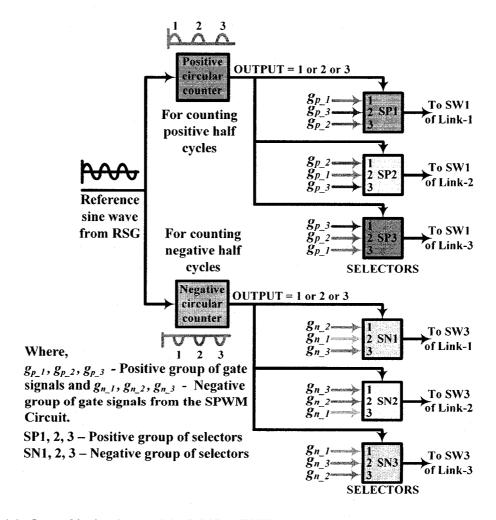

| Figure 4.4. | Control logic scheme of the RGSP in EMTP-RV                                       |

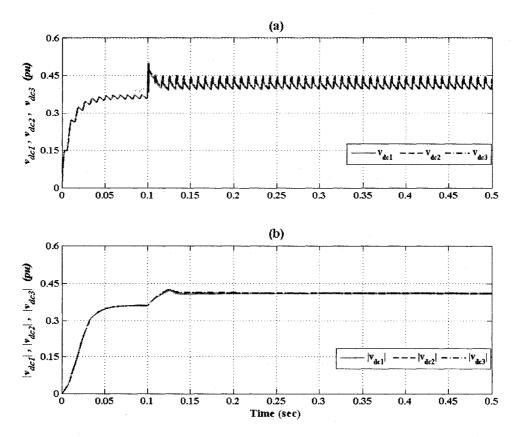

| Figure 4.5. | (a) Instantaneous (b) average dc capacitor voltages of all three links            |

|             | of a 1-phase 3-link CLS70                                                         |

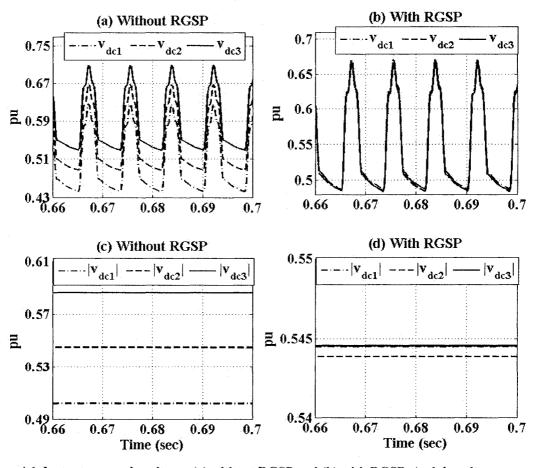

| Figure 4.6. | Instantaneous dc voltages (a) without RGSP and (b) with RGSP,                     |

|             | and dc voltage magnitudes (c) without RGSP and (d) with RGSP72                    |

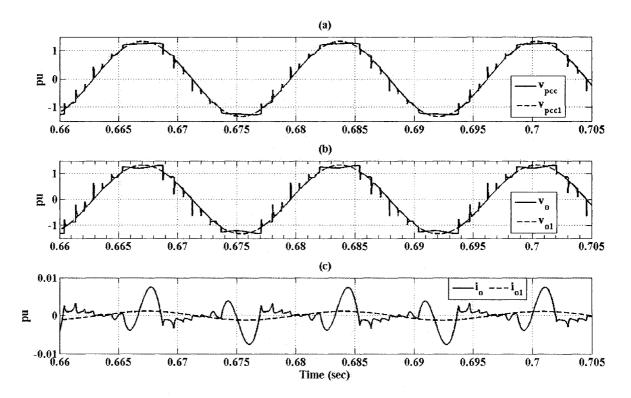

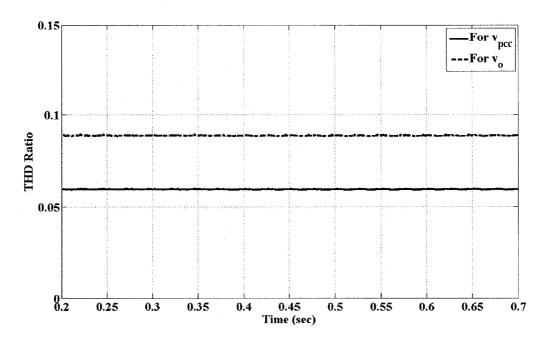

| Figure 4.7.  | Steady state waveforms (a) $v_{pcc}$ (b) $v_o$ (c) $i_o$ of a 1-phase CLS                |

|--------------|------------------------------------------------------------------------------------------|

|              | having 3-links                                                                           |

| Figure 4.8.  | Total harmonic distortion (THD) ratio of $v_o$ , $i_o$ and $v_{pcc}$                     |

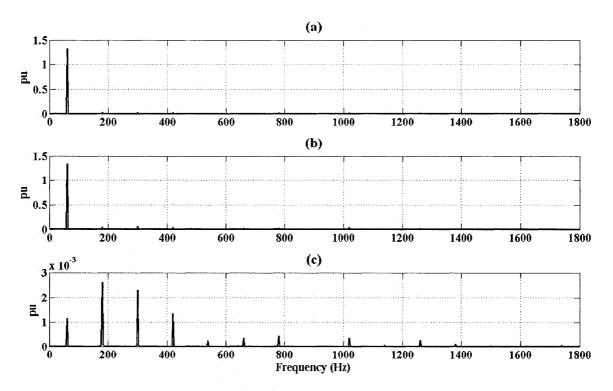

| Figure 4.9.  | Harmonic spectrum (a) $v_{pcc}$ (b) $v_o$ and (c) $i_o$                                  |

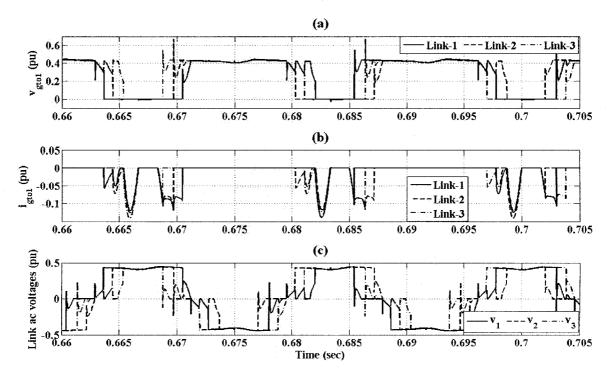

| Figure 4.10. | Steady state waveforms of (a) $v_{gtol}$ (b) $i_{gtol}$ and (c) Link ac voltages         |

|              | (i.e. $v_1$ , $v_2$ & $v_3$ ) of all three links of a 1-phase CLS                        |

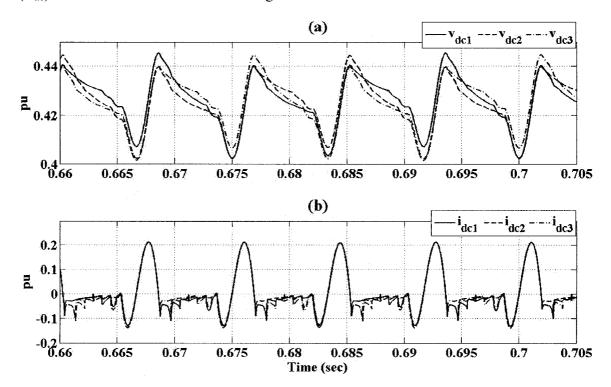

| Figure 4.11. | Steady state waveforms of (a) the dc voltage, $v_{dcl}$ and                              |

|              | (b) the dc current, $i_{dcl}$ of link-1                                                  |

| Figure 4.12. | Transient state performance, $\pm 2\%$ Step-change in $ v_{mod} $                        |

| Figure 4.13. | Transient state performance, $\pm 5\%$ Step change in $\delta$                           |

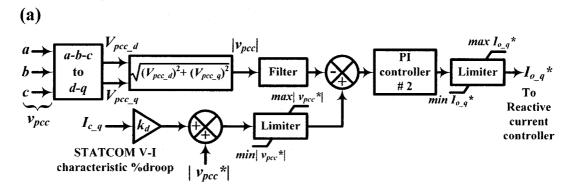

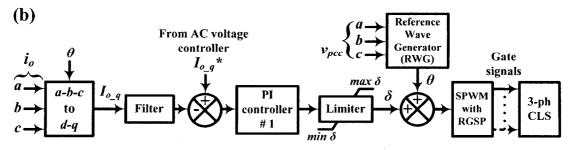

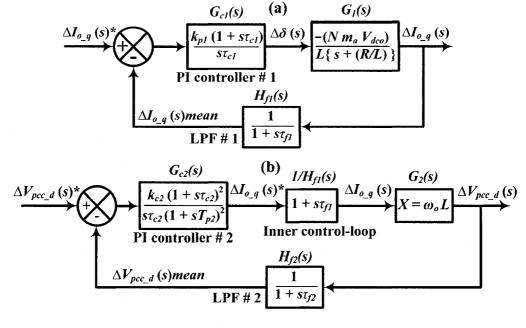

| Figure 5.1.  | (a) AC voltage and (b) reactive current controllers                                      |

| Figure 5.2.  | Block diagrams of (a) inner (reactive current), and                                      |

|              | (b) outer (ac voltage) control-loops                                                     |

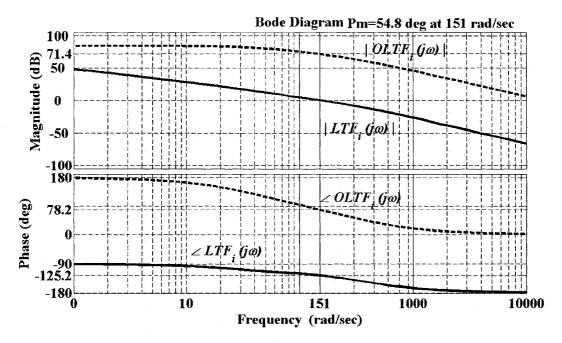

| Figure 5.3.  | Bode plots of inner reactive current control loop for                                    |

|              | $OLTF_{i}(s) = G_{I}(s).H_{fI}(s) \& LTF_{i}(s) = G_{cI}(s).G_{I}(s).H_{fI}(s) \dots 90$ |

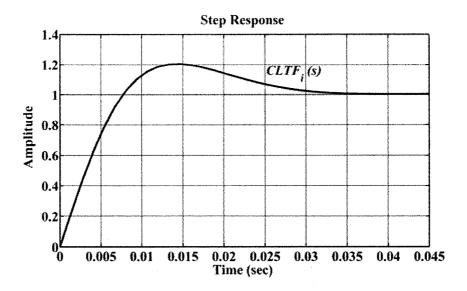

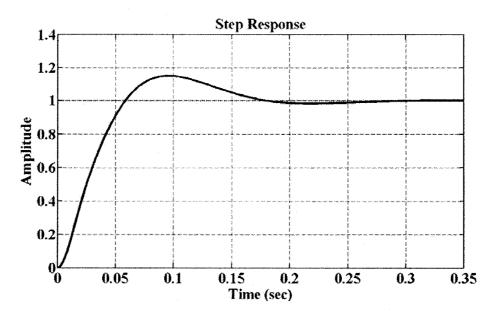

| Figure 5.4.  | Step response of the inner reactive current control loop                                 |

|              | i.e. $CLTF_i(s) = \{G_{cl}(s).G_l(s)\} / \{I + G_{cl}(s).G_l(s).H_{fl}(s)\} \dots 91$    |

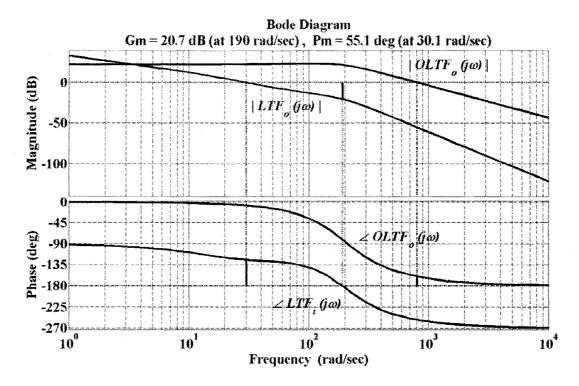

| Figure 5.5.  | Bode plots of $OLTF_o(s) = G_2(s).H_{f2}(s)/H_{f1}(s)$ &                                 |

|              | $LTF_o(s) = G_{c2}(s).G_2(s).H_{f2}(s)/H_{f1}(s)$                                        |

| Figure 5.6.  | Step response of the outer ac voltage control loop                                       |

|              | i.e. $CLTF_0(s) = \{G_{c2}(s), G_2(s)\} / \{H_0(s) + G_{c2}(s), G_2(s), H_D(s)\}93$      |

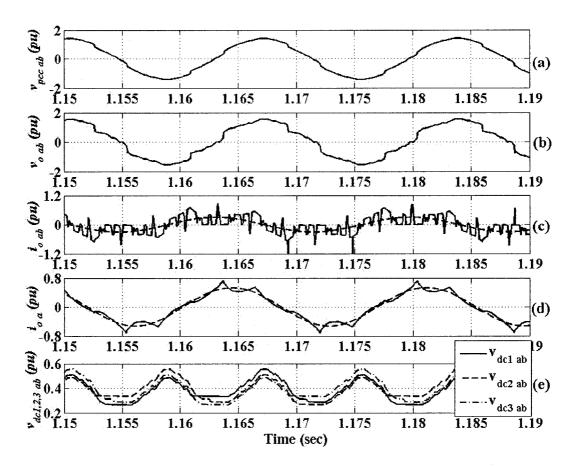

| Figure 6.1. | Steady-state waveforms: (a) voltage at the PCC ( $v_{pcc\_ab}$ ), (b) CLS output             |

|-------------|----------------------------------------------------------------------------------------------|

|             | voltage $(v_{o\_ab})$ (c) CLS output phase current $(i_{o\_ab})$ , (d) CLS output line       |

|             | current $(i_{0\_a})$ , and (e) link dc voltages $(v_{dc1\_ab}, v_{dc2\_ab}, v_{dc3\_ab})$ 95 |

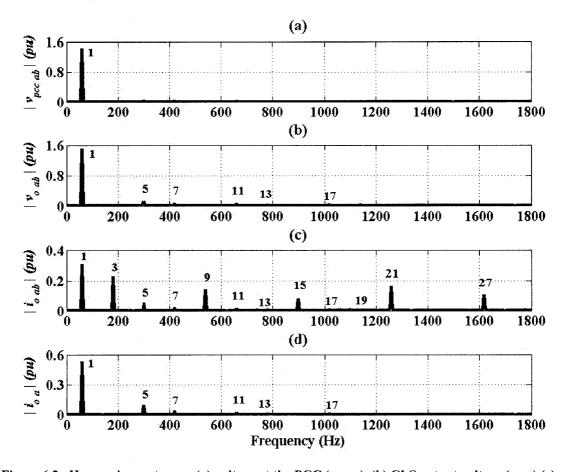

| Figure 6.2. | Harmonic spectrums: (a) voltage at the PCC $(v_{pcc\_ab})$ , (b) CLS output                  |

|             | voltage $(v_{o\_ab})$ (c) CLS output phase current $(i_{o\_ab})$ , and (d) CLS output        |

|             | line current $(i_{o\_a})$ 96                                                                 |

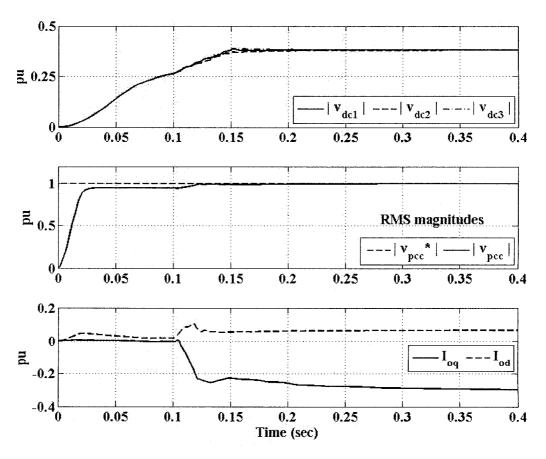

| Figure 6.3. | Initialization of the CLS system: (a) DC voltage magnitudes of                               |

|             | link-1, -2 & -3, (b) rms value of the voltage at the PCC, and                                |

|             | (c) CLS output currents in dq-axis97                                                         |

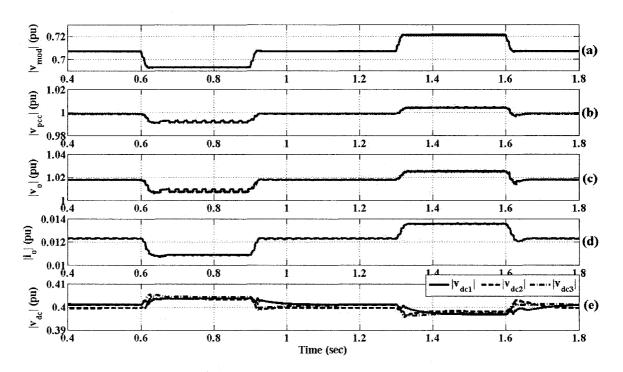

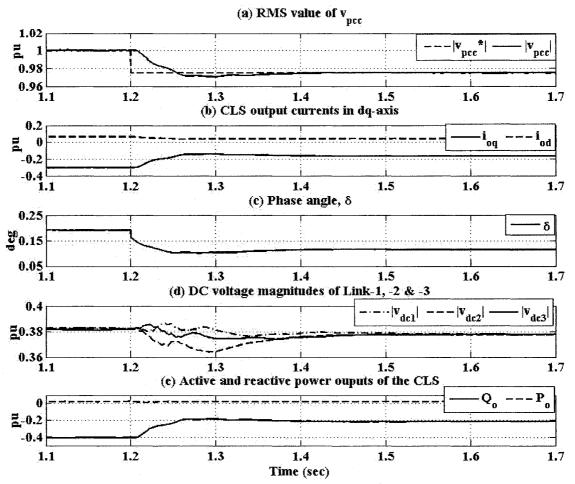

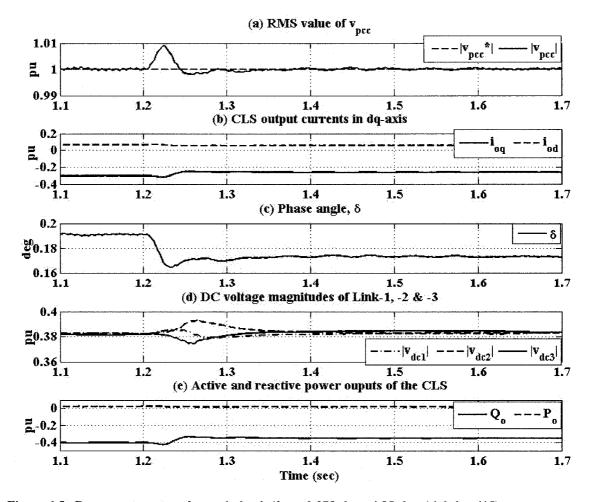

| Figure 6.4. | Response of step change in voltage reference ( $k_{pl}$ =-0.078, $k_{il}$ =-4.85,            |

|             | $k_{p2}$ =14.6, $k_{i2}$ =415)99                                                             |

| Figure 6.5. | Response of step change in load. ( $k_{pl}$ =-0.078, $k_{il}$ =-4.85, $k_{p2}$ =14.6,        |

|             | <i>k</i> <sub><i>i</i>2</sub> =415)                                                          |

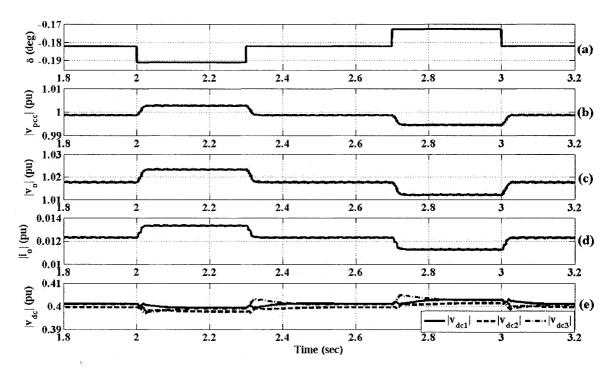

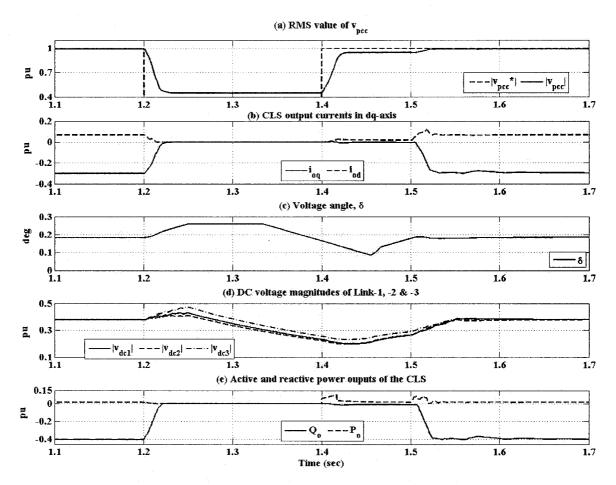

| Figure 6.6. | Response of the balanced 3-phase fault at bus B2 ( $k_{pl}$ =-0.078,                         |

|             | $k_{i1}$ =-4.85, $k_{p2}$ =2, $k_{i2}$ =980)                                                 |

# LIST OF TABLES

| Table 2.1. | Switching sequence of any link-k per cycle of the fundamental   |    |

|------------|-----------------------------------------------------------------|----|

|            | Frequency                                                       | 28 |

| Table 3.1. | Distribution of the comparators required per phase in           |    |

|            | the SPWM circuit                                                | 49 |

| Table 4.1. | Rotated gate signal pattern (RGSP) per phase for the CLS having |    |

|            | 3-links per phase                                               | 65 |

# LIST OF ACRONYMS

ASVC Advanced Static VAr Compensator

CLC Chain Link Converter

CLS Chain Link STATCOM

CSC Current Source Converter

EMTP Electro-Magnetic Transient Program

FACTS Flexible AC transmission System

FC Fixed Capacitor

GTO Gate Turn-off Thyristor

IGBT Insulated Gate Bipolar Transistor

IGCT Integrated Gate-commutated Thyristor

NGC National Grid Company

PCC Point of Common Coupling

PWM Pulse width Modulation

RGSP Rotated Gate Signal Pattern

SSSC Static Synchronous Series Compensator

STATCOM Static Synchronous Compensator

SVC Static VAr Compensator

TCR Thyristor Controlled Reactor

TCSC Thyristor-controlled Series Capacitor

TSC Thyristor Switched Capacitor

TSSC Thyristor Switched Series Capacitor

VSC Voltage Source Converter

# **CHAPTER-1**

# Introduction

## 1.1. GENERAL

The modern power supply system is widely interconnected for economic reasons, to reduce the electricity cost and to improve reliability of the power supply. It comprises of many generating stations, transmission lines, loads, controllers and telecom links. Such an interconnected network, while bearing many advantages, suffers from large voltage, frequency and power excursions because of sudden load changes, faults and controller actions, which occur locally and/or remotely. In the worst case, these excursions, if not dampened, may result in the collapse of the power system. Therefore, it is essential to balance the supply and demand of active and reactive power in an electric power system.

The electrical power transmitted in an ac power system depends upon the transmission line voltage profile under steady state and dynamic conditions, over a wide range of network contingencies. Therefore, it is desirable to regulate the voltage within a narrow range (+5%, -10% in most utilities) of its nominal value. Appropriate voltage and reactive power control is one of the most important factors of stable power system operation.

# 1.2. REACTIVE POWER COMPENSATION [1-4]

As transmission & distribution lines, transformers, generators etc., have mainly inductive impedance at line frequency, the internal impedance of the ac system seen by the load is mainly inductive. Hence, reactive power appears in every ac power system.

Therefore, it is the reactive power change in the power system that has the most adverse effect on the voltage regulation.

Moreover, with a long-distance ac power transmission and load growth, the reactive power increases the transmission system losses, reduces the power transmission capability of the transmission lines and causes large amplitude variations in the power system voltage & consequently power oscillations. Therefore, by controlling the reactive power (VAr) flow in the line, the voltage profile along the transmission line can be controlled in a more effective way. Furthermore, the reactive power compensation increases the utilization of the existing transmission systems and improves the system damping and stabilizes the power systems.

# 1.2. METHODS OF REACTIVE POWER COMPENSATION [1-8]

# 1.2.1. General [1-4]

Contrary to the active power balance, which has to be affected by the generators alone, a proper reactive power balance can and often has to be affected both by the generators and by dispersed special reactive power devices capable of producing and absorbing reactive power. The use of shunt devices i.e. shunt compensation, is a classic reactive power compensation method. The use of series capacitors i.e. series compensation, is a 'line reactance compensation' method. As the series compensation method is not in the scope of this thesis report, only the shunt compensation methods for the reactive power compensation will be discussed next in brief.

#### 1.2.2. Conventional methods [1-4]

No special reactive compensation devices were used in the early ac power systems, because the generators were situated close to the loads. As the network became more

widespread synchronous motors, small synchronous compensators and static shunt capacitors were adopted for reactive compensation. In the transmission system, larger synchronous compensators (or synchronous condensers) were installed. The synchronous compensators produce high capacitive output currents even at the low system voltages and do not generate harmonics that resonate with the grid. However, they are vulnerable to rotating instability, have slow response with low short circuit impedance, and have high maintenance cost.

Along with the development of more efficient and economic capacitors, there has been a phenomenal growth in the use of shunt capacitors as a means of furnishing reactive power, particularly within distribution systems. With the introduction of the extra-high voltage (EHV) lines, large banks of mechanically switched or fixed capacitors/reactors have been important compensation devices to maintain the supply voltage and increase the steady state power of the line by 'reactive power compensation'. At regular intervals along the transmission line, the reactors are installed in shunt along with the large capacitors in series or parallel. However, with the fixed capacitor configuration using mechanical switches, continuous control of reactive power cannot be achieved. Also the switches have slow response time, are bulky, expensive and require maintenance.

#### 1.2.3. Static VAr Compensators (SVCs) [1-4]

The development of high power solid-state devices such as thyristors, opened up a new era of control techniques in power transmission systems. Using these solid-state switches, shunt, series or shunt and series connected systems were employed in power

systems for reactive power compensation. More detailed explanation of these methods is given in [1-4].

Figure 1.1. (a) Conventional SVC System, and its (b) V-I characteristic.

A 'Static VAr compensator' (SVC) is a member of the Flexible AC Transmission Systems (FACTs) family which uses solid-state power electronic devices to control the power flow on power grids. A SVC regulates voltage at its terminal by controlling the amount of reactive power injected into or absorbed from the power system. When the system voltage is low, SVC operates in capacitive mode and generates reactive power. Whereas, when the system voltage is high, SVC operates in the inductive mode and absorbs reactive power to maintain the system voltage at the desired level.

The SVCs were first developed in the late 1960s to prevent annoying voltage flicker caused by large industrial fluctuating loads, such as electric arc furnaces, which cause rapid changes in the reactive power and also introduce phase unbalance. Since then, they have been extensively used in the power transmission networks for the dynamic compensation of the electric power to achieve better utilization of existing generation and transmission facilities and to provide the voltage support. Thyristor controlled reactors (TCRs) and thyristor switched capacitors (TSCs) have gained significant market share due to their relatively fast speed of operation low maintenance requirements and low cost.

Conventional SVCs employ large banks of shunt connected fixed capacitors, TSRs and TSCs to provide the desired controlled shunt reactive power compensation (Figure 1.1a). In such installations, ac capacitors are used as the VAr source, and shunt connected phase controlled reactors are used to absorb VArs. The net reactive power is the difference between the two. A coupling transformer matches the SVC to the transmission line voltage. In some installations two transformers are used with an increased pulse number to reduce harmonic distortion and to provide improved dynamic response [5].

SVC possesses certain disadvantages such as,

- Higher harmonic generation,

- Lower dynamic range,

- Limitations of operations with weak ac system, and

- As it acts as a variable susceptance, it is sensitive to the transmission system harmonic resonance (Figure 1.1b).

# 1.2.4. Advanced Static VAr Compensators (ASVCs) or Static Synchronous Compensators (STATCOM) [1, 2, 4-8]

With the development of new-generation, high-performance, high-power forced-commutated semiconductor switches such as gate turn-off thyristors (GTOs) and insulated gate bipolar junction transistors (IGBTs), the possibility of generating or absorbing controllable reactive power with various power electronics switching converters has long been recognised, and several candidate schemes have been implemented in laboratory models. These converters do not require large capacitor or phase controlled reactor banks to produce reactive power. They operate as alternating voltage or current sources (i.e. voltage-sourced inverter, VSI and current-sourced inverter, CSI) and produce reactive power essentially by circulating energy between the phases of the ac system. The inverters (or converters) for the transmission line application, require semiconductor power switches with the high voltage and current ratings and moreover, the switches must be capable of turning off in response to a gating command. The CSI implementation requires power switches with symmetrical bidirectional voltage blocking capability, while VSI requires only unidirectional voltage blocking.

The voltage sourced inverter or converter (VSI or VSC) based shunt-connected SVC system is known as an advanced SVC (ASVC) or more popularly a static synchronous compensator (STATCOM). The capability of the STATCOM is analogous to a rotating synchronous compensator, and can be used in the power systems, for the dynamic compensation, increasing the transient stability and providing the voltage

support. The basic principle of operation of the STATCOM is briefly explained next along with its significant advantages as compared to conventional shunt connected SVC.

## (a) Principle of operation of STATCOM (or ASVC) [1, 2, 4-8]

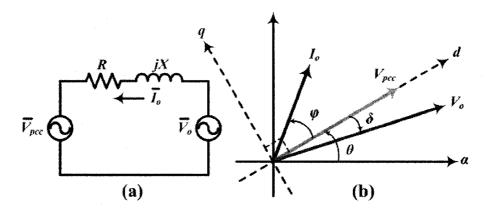

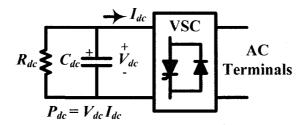

The major elements of a STATCOM are a VSC, a dc capacitor ( $C_{dc}$ ) and a transformer to match the inverter to the line voltage. In this STATCOM application, a four quadrant VSC converts a dc voltage at its input terminals into 3-phase set of output voltages synchronized with and connected to the ac line through a small buffer or tie reactance, which is the leakage reactance of a transformer. The basic principle of operation of a STATCOM is illustrated in Figure 1.2.

Figure 1.2. (a) Single line diagram of the STATCOM system, (b) Simplified equivalent circuit of a STATCOM connected to the AC system, and (c) Phasor diagrams.

As shown in Figure 1.2b, a simplified representation of the ac system is a Thevenin equivalent of voltage at the point of common coupling (PCC),  $V_{pcc}$  behind a reactance Xs. A STATCOM VSC can be considered to generate a 'back-emf' represented by its

fundamental component of the converter output voltage,  $V_o$  connected via transformer leakage reactance,  $X_{tr}$  to the ac system at the PCC.

By using a suitable closed-loop control system,  $V_o$  is controlled to be in phase with  $V_{pcc}$  and therefore the current,  $I_o$  flowing between the PCC and STATCOM is ideally purely reactive, which is given by:

$$I_o = \frac{V_{pcc} - V_o}{j(X_s + X_{tr})} \tag{1.1}$$

The back-emf ( $V_o$ ) is directly related to the dc side voltage of the STATCOM, which can be controlled by the closed loop control system to enable the STATCOM to draw leading or lagging reactive current ( $I_o$ ) from the ac line. When  $V_o$  is higher than  $V_{pcc}$ , leading  $I_o$  is drawn from the ac line (or reactive power is supplied to the line) and when  $V_o$  is lower than  $V_{pcc}$ , lagging  $I_o$  is drawn from the ac line (or reactive power is absorbed from the line) (Figure 1.2c). In this respect, the operation of the STATCOM is similar to that of a synchronous condenser. The transient response of STATCOM, however, is significantly better.

As explained earlier, ideally the line current is purely reactive therefore, no real power is required. In practice, as the semiconductor switches in the converter are not loss less, some real power is required to compensate for the converter losses. These losses are dissipated in the resistor ( $R_{dc}$ ) in parallel with  $C_{dc}$ . Because of these internal losses in the STATCOM converter, the dc capacitor voltage would diminish. However, these losses may be supplied from the ac line by adjusting the output voltage of the STATCOM converter to lag the line voltage by a very small angle (usually in the range of 1° to 3°). By compensating the converter losses in this way, continuous real power is not required from the dc source and no separate power supply is needed. The dc capacitor is only

required to maintain smooth dc voltage while carrying the ripple current drawn by the converter. Usually, the converter reactive current is controlled by increasing or decreasing the magnitude of the STATCOM output voltage, which in turn can be achieved by increasing or decreasing the magnitude of the dc voltage by adjusting the phase angle of the STATCOM output voltage. So in addition to the losses, some real power flows in or out of the dc capacitor, as required.

The reactive and active power exchange between the STATCOM and the ac system can be controlled independently of each other, and any combination of real power generation or absorption with VAr generation (supply or –Q) or absorption (+Q) is achievable, if the STATCOM is equipped with an energy storage device of suitable capacity for example, a battery.

Figure 1.3. Phasor diagrams for power exchanges in a STATCOM.

Figure 1.3 illustrates the phasor diagrams of the power system voltage at the point of common coupling ( $v_{pcc}$ ), the STATCOM output current ( $i_o$ ) and out voltage ( $v_o$ ) in all four quadrants of the PQ plane. As stated, for a STATCOM,  $2^{nd}$  and  $3^{rd}$  quadrant operation (i.e. supply of active power) is possible only with a separate dc source (i.e. battery) on its dc side. With this capability, extremely effective control strategies for modulation of the reactive and active output power can be devised to improve transient and dynamic stability limits.

## (b) V-I characteristic of STATCOM [1, 2, 4-8]

A typical V-I characteristic of a STATCOM is depicted in Figure 1.4. As can be seen, the STATCOM can supply both capacitive and inductive compensation and is able to control its output current over the rated maximum capacitive or inductive range independently and irrespective of the amount of the ac system voltage. In practice, the minimum value of the voltage at which the STATCOM can produce the rated output is dependent on the tie or buffer reactance of the coupling transformer (typically 0.2 pu). Figure 1.4 also illustrates that the STATCOM has an increased transient rating in both the capacitive and inductive operating regions. The maximum attainable transient overcurrent in the capacitive region is determined by the maximum current turn-off capability of the converter switches. However, in the inductive region, the converter switches are naturally commutated and therefore the transient current rating is limited by the maximum allowable junction temperature of the converter switches.

Figure 1.4. V-I characteristic of STATCOM.

## (c) Conventional STATCOM circuit using 3-phase VSC [1, 2, 4-8]

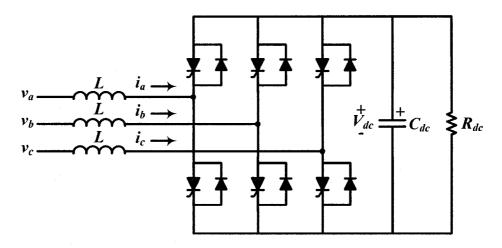

As stated earlier, the basic building block of the STATCOM is a 3-phase VSC which consists of six self commutated semiconductor switches (i.e. here GTOs) with antiparallel freewheeling diodes (Figure 1.5). With a dc voltage source (i.e. a charged capacitors), VSC can produce a balanced set of three quasi-square voltage waveforms of a given frequency by connecting the dc source sequentially to the three output terminals via the appropriate VSC switches. As the quasi-square output voltage waveform produces unacceptable current harmonics when connected to a line, a single 3-phase VSC bridge arrangement cannot be used as a STATCOM [5-7]. Therefore, a STATCOM uses many such VSC appropriately phase shifted, with their outputs combined electromagnetically to produce nearly sinusoidal resultant voltage waveform. This arrangement also results in increased STATCOM rating.

Figure 1.5. Conventional 3-phase 6-pulse VSC based STATCOM circuit.

#### (d) Advantages of STATCOM over SVC [1, 2, 5]

The ASVC or STATCOM has many advantages over the conventional SVC which are summarized as follows:

- Continuous and precise power control.

- Improved performance with a larger dynamic range.

- Increased transient stability & improved damping.

- Improved performance and improvement in the obtainable VAr output at low operating voltages. A STATCOM is capable of generating 1 pu of reactive current at line voltage down to the pu value of the tie reactance and hence (Figure 1.4). This ability to support the line is better than that obtained with conventional SVC because the current in the capacitors falls in proportion to the voltage (Figure 1.1b).

- The switches used in the STATCOM are well protected against the over voltages by the clamping action of the dc capacitor.

- The VAr output inherently adjusts to compensate for voltage variations.

- Because the current carrying capacity of the VSC switches (e.g. GTO) is high in

the naturally commutated mode, the switches may be utilized to a higher

proportion of their current rating when an over voltage transient is experienced

and lagging reactive power is required.

- Lower harmonic generation.

- Reduction in size and weight, due to the reduction in the passive component count and the size of the remaining passive components.

- Insensitivity to transmission system harmonic resonance as it acts as a voltage source behind a reactance.

- Reduction in the cost as compared to the conventional SVC, has been realized in production as the technology of the high power switches became matured.

# (e) Limitations of conventional 3-phase VSC based STATCOM [1, 2, 5, 6, 8, 10]

As stated earlier, a simple 3-phase VSC arrangement is not suitable as STATCOM circuit because of its poor harmonic performance and limited rating [1, 5, 10]. For high-power high-voltage applications, the total VAr rating could be increased by connecting the switches either in series or parallel; however this would not improve harmonic performance and introduces problems associated with voltage and/or current sharing.

Increased VAr rating can also be achieved by using multiple 3-phase bridges and phase-shifting transformers [1, 5, 6]. The 3-phase bridges can be connected in parallel on the dc side and the converters may incorporate series-connected GTOs and diodes to achieve higher ratings. The converter transformers are usually arranged to make bridges appear in series when viewed from the ac side [5, 6]. By arranging the phase shift

between the bridge transformer windings (i.e. using zigzag transformer), selected harmonics can be cancelled to give a multi-pulse arrangement (e.g. 24 or 48-pulse) under balanced conditions. With this method, it is not practicable to connect the series-connected transformer primaries directly to the high voltage power system, and a further fully rated step-down transformer is required for this purpose. For example, the 48-pulse STATCOM arrangement consists of eight VSCs connected together through eight zigzag transformers using the harmonic cancellation technique. These transformers,

- Are the most expensive equipment in the system;

- Produce about 50% of the total losses of the system;

- Occupy up to 40% of the total system's space, which is an expensive large area;

- Cause difficulties in control due to dc magnetizing and inrush current problems resulting from saturation of the transformers in transient states; and

- Are prone to failures.

Pulse width modulation (PWM) can also be applied to cancel selected harmonics. However, increasing the number of switching operations of the converter switches per cycle increases the switching and snubber losses, increases high frequency harmonics and reduces the fundamental VAr rating.

### 1.2.5. Multilevel converters and their problems [1, 8]

To solve the above mentioned problems associated with the conventional 3-phase VSC based STATCOM arrangement, to increase the VAr rating and to reduce the harmonics, a 'multilevel' converter is used; which produces a 'multi-stepped' output voltage waveform. These multilevel converters eliminate the transformers required in the

conventional 3-phase 6-pulse VSC based STATCOM; however they encounter new problems as explained next.

In recent years, a relatively new type of converter - multilevel voltage source converter - has attracted many researchers' attention. Multilevel converters operate at high voltage and reduce harmonics by their inherent structures without transformers, a benefit that many contributors have been trying to exploit for high-voltage, high-power applications especially for flexible ac transmission system (FACTS) controllers. Several multilevel converter topologies have been developed to demonstrate their flexibility in such applications.

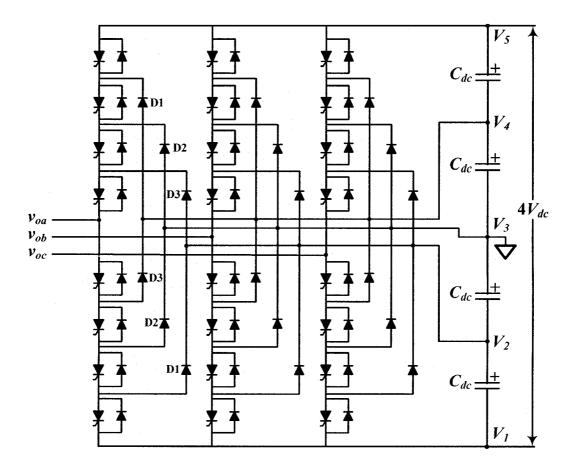

## (a) Diode clamp multilevel converter [1, 8, 10]

Figure 1.6 shows the structure of a 5-level diode-clamp converter. In this circuit the single energy storage capacitor of the conventional 3-phase VSC bridge circuit (Figure 1.5) is replaced by several capacitors stacked directly in series, and the basic switch per bridge arm (i.e. one GTO plus one anti-parallel diode of Figure 1.5) is changed to several switches in series coupled to the capacitor stack via auxiliary/clamping diodes. A stack of M capacitors produces (M +1) level symmetrical voltage waveform per phase, which gives increased VAr rating and a better approximation to a sine wave than the basic 3-phase VSC bridge. This converter can reach good performance without transformers [8]. For the 5-level converter, D1, D2, and D3 need to block  $V_{dc}$ ,  $2V_{dc}$  and  $3V_{dc}$  respectively, assuming each dc capacitor has the same dc voltage,  $V_{dc}$ . When diodes are selected to have the same voltage rating as the main switching devices, D2 and D3 comprise of two and three auxiliary diodes in series, respectively, to withstand the voltage. Therefore, the number of the additional auxiliary/clamping diodes is equal to (M - 1) x (M - 2) x 3 for an

M-level converter. Therefore, the main disadvantage with this circuit is that the total number of auxiliary diodes increases rapidly as the number of levels increase. For example, if M = 51 (for direct connection to 69 kV power lines), then the number of the auxiliary diodes will be 7350. Consequently, in practice a maximum of 9-levels (eight capacitors) is probably the economic limit. This gives a relatively low maximum 3-phase bridge rating of the order of  $\pm 20$ MVAr.

Figure 1.6. 3-phase 5-level diode clamp converter.

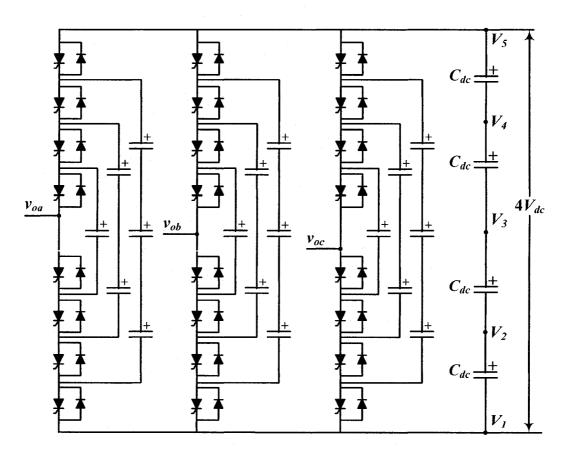

# (b) Flying-capacitor multilevel converter [1, 8, 10]

The multilevel flying-capacitor converter is supposed to be able to solve the problems of voltage unbalance and excessive diode count of the diode clamped converter.

Figure 1.7 shows the configuration of a 5-level flying-capacitor converter. In this converter, however, a large number of flying capacitors are needed. The required number of flying capacitors for an M-level converter is equal to  $(M-1) \times (M-2) \times 3/2 + (M-1)$ , provided that the voltage rating of each capacitor used is the same as the main power switches. With the assumption of the same capacitor voltage rating, an M-level diode clamped converter requires only (M-1) capacitors. Therefore, the flying capacitor converter requires large capacitance compared with the conventional 3-phase VSC bridge. In addition, control is very complicated, and higher switching frequency is required to balance each capacitor voltage.

Figure 1.7. 3-phase 5-level flying capacitor converter.

#### (c) Chain Link Converter (CLC) [1, 10-15]

A relatively new multilevel converter configuration has been developed by connecting a number of VSCs in series to form a chain; this configuration is known as a Chain link converter (CLC). A CLC based STATCOM known as Chain Link STATCOM (CLS), is proposed here. It has significant advantages compared with the other aforementioned known arrangements of the STATCOM. These include good harmonic performance, fast response, low losses and low cost. Moreover, the packaging and physical layout is much easier due to its modular structure. This arrangement of the STATCOM is relatively new and not well understood due to its limited number of applications for commercial use. The first and so far only, CLS application has been in service in the National Grid Company, East Claydon substation, UK.

This special type of STATCOM eliminates the excessively large number of,

- Bulky transformers required by conventional multipulse converters,

- Clamping diodes required by multilevel diode-clamped converters, and

- Flying capacitors required by multilevel flying-capacitor converters.

Also, some of its important features are:

- It switches each device only once per line cycle and generates a multi-stepped staircase voltage waveform approaching a pure sinusoidal output voltage by increasing the number of levels.

- Since the converter structure itself consists of a chain connection of many 1-phase, full-bridge VSC units and each bridge is fed with a separate dc source, ideally it does not require voltage balance (sharing) circuits or voltage matching of the switching devices.

Packaging and layout is much easier because of the simplicity of structure and lower component count and hence it is much more suitable to high-voltage, highpower applications than the conventional converters.

The basic principles of operation, along with the main features and advantages & disadvantages of the CLS circuit, are explained in Chapter 2.

# 1.3. EMTP-RV: OVERVIEW [1]

EMTP-RV is an acronym of the "Electro-Magnetic Transient Program - Restructured Version", which is the circuit-based power system simulation software used for the simulation study of the CLS system in this thesis. EMTP-RV is the end result of the "EMTP Restructuring project" undertaken by the Development Coordination Group (DCG) in 1998 for modernizing the EMTP96 software. EMTP-RV is the enhanced computational engine and EMTPWorks is its new graphical user interface (GUI).

This package is a sophisticated computer program for the simulation of electromagnetic, electromechanical and control systems transients in multiphase electric power systems. It features a wide variety of modeling capabilities encompassing electromagnetic and electromechanical oscillations ranging in duration from microseconds to seconds. Examples of its use include switching and lightning surge analysis, insulation coordination, shaft torsional oscillations, ferroresonance and power electronics applications in power systems.

#### 1.4. LITERATURE REVIEW

As the thesis is mainly concentrated on the shunt connected VSC based ASVCs (i.e. STATCOM) used as the FACTS controllers [2], a brief literature review on this topic is presented below.

In late 1970's, L. Gyugyi proposed the controlled reactive power compensation using conventional thyristor based shunt connected SVCs to increase the utilization of the existing transmission systems, to stabilize the power system, to improve the damping and to regulate the steady state value of the voltage and introduced several possible approaches including VSC, CSC and unrestricted frequency converter (UFC) using fully controlled power devices to generate and absorb reactive power without requiring large banks of capacitors or phase controlled reactors [2, 4]. N. Hingorani first defined the concept of FACTS in 1988 as high power electronics and flexible ac transmission system [2]. C.W. Edwards, K.E. Mattern, E.J. Stacy, P.R. Nannery and J. Gubernick proposed the prototype VSC using GTO thyristors as power devices, for evaluation in 1988 [5]. C. Schauder and H. Mehta developed a mathematical model of a VSC with direct and indirect controllers by using Park's transformation in 1991 [22]. Based on a Ph d project, D.R. Trainer, S.B. Tennakoon and R.E. Morrison presented the analysis of the 6-switch and 12-switch voltage-sourced GTO SVC circuits and derived the equations to describe the performance of each circuit in 1995. Under the EPRI sponsored FACTS program, C. Schauder, M. Gernhardt, E. Stacey, T. Lemark, L. Gyugyi, T.W. Cease and A. Edris developed the first world's largest prototype STATCOM of rating ±100 MVAr, which was installed in the Tennessee Valley Authority (TVA) Sullivan substation [7]. After the introduction of the multilevel converters-a new breed of power converters in 1996 by J.S. Lai and F.Z. Peng [8], in 1998, J.D. Ainsworth, M. Davis, P.J. Fitz, K.E. Owen and D.R. Trainer introduced a chain link converter based SVC with significant advantages over the multipulse conventional & multilevel converters [1, 10]. Several papers have been published mentioning the successful commissioning of as yet only one prototype

installation of the CLC based STATCOM of rating ±75 MVAr in the National Grid Company, East Claydon Substation, UK [11-15]. Only a few papers have been published that explained the basic principle of operation of the similar topology named as cascaded converters and investigated its application for the voltage support in the transmission line [20, 21, 23, 24] along with its gating strategy using phase shifted triangular carrier based PWM [16, 18]. Several articles on the conventional STATCOM have been published to investigate the controller function and to increase the efficiency of the converter's power circuit in order to reduce the losses and improve the quality of the output voltage [1-3, 25-27]. Moreover, many installations of the conventional STATCOM applications exist [1-3]. Much research has been done after developing the basic theory of a shunt connected VSC based FACTS controller [1-3]. A Chain Link STATCOM (CLS) is relatively new topology and less published research is available on it with only one prototype installation [1, 10]. Much more research is required on the CLS to fully exploit its advantages for its applications in power systems.

### 1.5. SCOPE AND CONTRIBUTION OF THIS THESIS

As mentioned in the preceding section, there are only a few publications [10, 20, 21, 23, 24] on the CLS and moreover, the information therein is insufficient for further research to exploit the advantages and applications of the CLS. Therefore, this thesis mainly investigates the theory of the CLS and develops its static & dynamic models, control philosophies and the simulation models for its application to support the voltage in the power system by carrying out the simulation in EMTP-RV.

• A basic principle of operation of a 7-level CLS using a 1-phase, full bridge, 3-level VSC as its basic building block is explained first. For the first time, an

SPWM gating technique utilizing multilevel triangular carrier signals and only one modulating signal (per phase), is proposed for the CLS along with the harmonic analysis of the multi-stepped CLS output voltage using the Double Fourier Series (DFS) method. In contrast with the fixed angle switching method (in which the switching angles are obtained by solving transcendental equations governing the modulating signals and carrier signals) used in the NGC's CLS application [1, 10], this SPWM gating strategy is simpler to use and easier to analyse using Double Fourier Series (DFS) method without any need of knowing the switching angles. Moreover, using the proposed SPWM gating strategy, each CLS switch is turned on/off only once per cycle of the line frequency which also minimizes the switching losses.

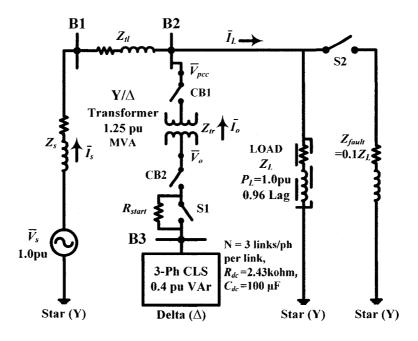

- EMTP-RV simulation model of the CLS system is proposed using its basic building blocks for the power and gating circuits. Approximate static and dynamic models of the CLS system are developed using *dq*-transformations and evaluated to verify the stability of the CLS system.

- A novel control technique called the Rotated Gate Signal Patterns (RGSP), is proposed to balance the dc capacitor voltages of the CLS. A step-by-step start-up procedure for the CLS system is also proposed to bring its reactive power output to a certain level in a short time, while maintaining all the switching devices within their ratings.

- A 3-phase 3-link 4 MVA, 15 kV delta connected CLS is modeled in EMTP-RV to support the voltage at the PCC. Considering only the phase angle of the CLS output voltage as the control input (i.e. selecting constant modulation index), a

closed-loop control strategy is proposed using two cascaded controllers (i.e. outer or ac voltage controller and inner or reactive current controller) and their approximate first-order transfer functions are derived. The dynamic performance of the proposed CLS with the controllers is studied and also verified by simulations in EMTP-RV. Several simulation tests are carried out to validate the operation of the CLS to regulate the power system voltage at the PCC by reactive power compensation, and the results are presented.

### 1.6. THESIS OUTLINE

The outline of the thesis is as follows:

Chapter 2 explains the theory of the CLS including its basic principle of operation, gating strategy and harmonic analysis of its output voltage using DFS method. It also depicts important features of the CLS along with its advantages and limitations. The basic layout and key design features of the only existing application of the CLS, at the NGC's East Claydon Substation, is also explained in this chapter.

In Chapter 3, the EMTP-RV model of the CLS system is developed using its basic building blocks viz. a switch model, VSC link model and SPWM circuit model. Approximate, steady-state and dynamic models of the CLS system are also derived using dq-transformations and the stability of the CLS system is verified using the Routh-Hurwitz criterion.

The objective of the Chapter 4 is to validate the EMTP-RV models developed in Chapter 2 by preliminary simulation in the open-loop control mode. For this, a 1-phase 3-link (or 7-level) version of the CLS is chosen for simulation in EMTP-RV. An open-loop control philosophy is also explained in this chapter, using modulation index and voltage

angle as control inputs. A novel control technique named Rotated Gate Signal Pattern (RGSP) to balance the link dc capacitor voltages of the CLS, is also described here along with the CLS start-up procedure. Both of these techniques are validated by simulation in EMTP-RV. The 1-phase CLS is simulated in EMTP-RV and its preliminary steady- and transient-state performance results are presented to validate its power & gating circuits and to evaluate its performance in open-loop control mode.

In Chapter 5, a closed-loop control strategy is developed using only the phase angle as a control input and keeping modulation index constant. Two cascaded controllers (outer or ac voltage controller and inner or reactive current controller) are designed from their approximate first-order transfer functions. Their dynamic performance is studied and verified using Bode plots and evaluating the system step response.

Several simulation tests are carried out with EMTP-RV in Chapter 6, to validate the operation of the CLS system (along with its controllers) to regulate the power system voltage and the simulation results showing its steady- and transient-state responses are presented.

Final concluding remarks are given in Chapter 7 along with the future direction of the research presented in this thesis.

# 1.7. SUMMARY

This chapter is summarised as follows:

- Brief explanation and comparison of the reactive power compensation techniques

using only shunt connected FACTs controllers were explained along with their

advantages and limitations.

- A CLC (or CLS) is a relatively new topology of the multilevel converters which has not had much published research information available.

- Brief overview of the objective of this thesis and its main contribution along with the thesis outline, was also provided.

# **CHAPTER-2**

# **CHAIN LINK STATCOM: THEORY**

### 2.1. Introduction

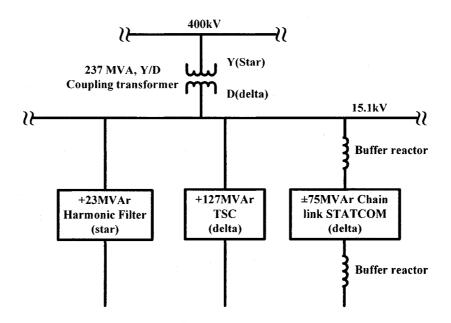

A chain link STATCOM (CLS) is recently introduced topology of the multilevel converter based STATCOM. As yet, only one application exists in the National Grid Company's (NGC's) East Claydon substation in the United Kingdom. This CLS rating is  $\pm$  75MVAr and it forms a part of the total 225MVAr SVC System. The basic circuit arrangement, operating principle and gating strategy used for switching this special type of STATCOM are explained in this chapter. Double Fourier series - a method of harmonic analysis of the multi-stepped waveforms of the CLS output voltage - is also explained here. This chapter also provides the main features of the CLS viz. ratings, losses, harmonic performance, redundancy, advantages and disadvantages and its topology in the NGC, UK.

### 2.2. Basic circuit arrangement & principle of operation

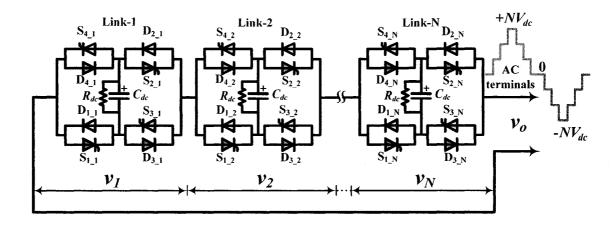

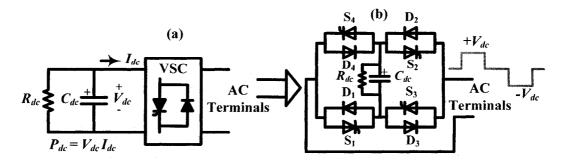

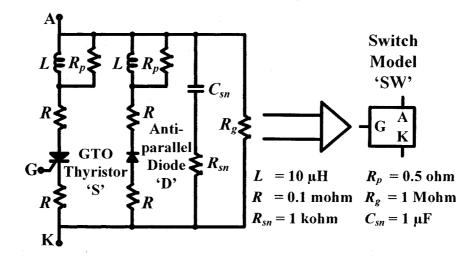

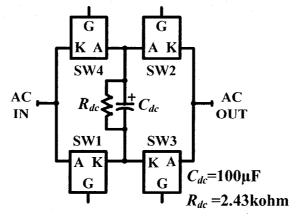

A CLS comprises of a number of GTO converter 'links' (or chain links) connected in series on their ac side to form a separate 'chain' per phase (Figure 2.1). (Note: Here, the choice of the GTO as a switch is arbitrary. Any other high power electronic switch, for example IGBT, may also be used instead of the GTO switch.) Each 'link' is a 1-phase, 3-level, full bridge, VSC comprised of four GTO-diode pairs as switches and an independent self-controlled dc capacitor ( $C_{dc}$ ) for energy storage (Figure 2.2). In this arrangement, the dc capacitors are floating with the dc voltage,  $V_{dc}$  on each of

Figure 2.1. General circuit arrangement of a 1-phase CLS with 'N' links.

them. Consequently, no real power needs to be supplied, other than the converter losses which are represented by the parallel resistor,  $R_{dc}$ .

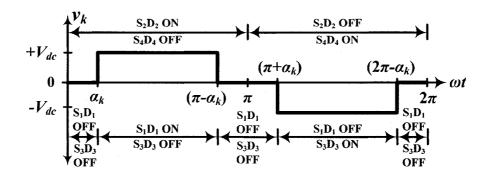

Each GTO, with its anti-parallel diode, forms a two-way switch. At any instant, the switches can be connected to the positive or negative terminal of its associated dc capacitor. Therefore, each link is either in 'contributing' state or 'non-contributing' state. In contributing state, diagonally placed GTO-diode pairs  $S_1$ - $D_1$  and  $S_2$ - $D_2$  conduct so that the link may contribute a voltage of  $+V_{dc}$  to the output voltage  $(v_o)$  (phase to neutral voltage for the 3-phase connection), or  $S_3$ - $D_3$  and  $S_4$ - $D_4$  conduct to contribute a voltage of  $-V_{dc}$ . In the non-contributing state, GTO-diode pairs  $S_2$ - $D_2$  or  $S_4$ - $D_4$  conduct, and the link does not contribute any voltage (i.e. zero voltage) to the output. By switching each GTO-diode pair "on/off" once per cycle of the fundamental frequency, a 3-level quasi-square

Figure 2.2. (a) Block diagram and (b) Simplified circuit diagram of a 1-phase VSC link.

Figure 2.3. 3-level output voltage  $(v_k)$  of a 1-phase VSC link.

output voltage waveform is synthesized for each link (Table 2.1 & Figure 2.3). Therefore, with N links in series (where N is a positive integer), the CLS output voltage contains (2N+1) voltage levels (Figure 2.4) that can give a good approximation to a sine wave.

It is important to note from Table 2.1 that for a CLS having more than one link in series per phase, to provide the closed circuit path among the series connected links per phase, during each positive half cycle, it is essential to simultaneously turn on the switches  $S_2$ - $D_2$  of all the links at instants  $(2n\pi)$  & turn off them at instants  $[(2n+1)\pi]$ .

Table 2.1. Switching sequence of any link-k per cycle of the fundamental frequency.

| Fundamental<br>Link output | Period in radians                         | Output<br>Voltage<br>of Link-k<br>(v <sub>k</sub> ) | Switch Operating sequence for link-k |           |                                |                                |

|----------------------------|-------------------------------------------|-----------------------------------------------------|--------------------------------------|-----------|--------------------------------|--------------------------------|

| voltage<br>waveform        |                                           |                                                     | $S_1-D_1$                            | $S_2-D_2$ | S <sub>3</sub> -D <sub>3</sub> | S <sub>4</sub> -D <sub>4</sub> |

| Positive cycle             | 0 to $\alpha_k$                           | 0                                                   | 0                                    | 1         | 0                              | 0                              |

|                            | $\alpha_k$ to $(\pi - \alpha_k)$          | $+V_{dc}$                                           | 1                                    | 1         | 0                              | 0                              |

|                            | $(\pi - \alpha_k)$ to $\pi$               | 0                                                   | 0                                    | 1         | 0                              | 0                              |

| Negative cycle             | $\pi$ to $(\pi + a_k)$                    | 0                                                   | 0                                    | 0         | 0                              | 1                              |

|                            | $(\pi + \alpha_k)$ to $(2\pi - \alpha_k)$ | -V <sub>dc</sub>                                    | 0                                    | 0         | 1                              | 1                              |

|                            | $(2\pi - \alpha_k)$ to $2\pi$             | 0                                                   | 0                                    | 0         | 0                              | 1                              |

Where, 1 - ON, 0 - OFF and k = 1, 2, 3, .....N.

Figure 2.4. (2N+1) level output phase voltage waveform of a CLS with 'N' links per phase.

Similarly, during each negative half cycle, it is essential to simultaneously turn on the switches  $S_4$ - $D_4$  of all the links at instants  $[(2n+1)\pi]$  & turn off them at instants  $(2n\pi)$ , where  $n = 0,1,2,....\infty$ . Otherwise there will be no flow of the current until all links come into conduction.

The total fundamental frequency output voltage of the CLS ( $v_o$ ) is thus the sum of the individual link ac voltages (Figure 2.4), and similarly for the total VAr rating of the CLS. The ac voltage rating and hence the dc capacitor voltage rating of each link, depends on the total compensation voltage required, the number of converters, and the sharing of the total capacitor voltage among individual links.

With purely reactive loading, the GTOs and the anti-parallel free-wheeling diodes, each carry a quarter wave segment of the fundamental current. When the CLS is supplying VArs to increase the line voltage or compensate for reactive loads, the GTOs must be capable of interrupting the current at its peak. Moreover, when the CLS is absorbing VArs to decrease the line voltage or compensate the capacitive loading, the GTOs are naturally commutated as the current passes through zero.

## 2.3. GATING STRATEGY

#### **2.3.1.** General

For a CLS, the main challenge is to drive its switches by providing gating signals such that each link produces a 3-level output voltage  $(v_k)$  by turning each GTO-diode switch "on/off" once per cycle of the fundamental frequency, to synthesize the multilevel output voltage per phase  $(v_o)$  in a close approximation to the sinusoidal waveform with controllable magnitude and phase angle. This is achieved by a popular control technique known as: "Sinusoidal Pulse Width Modulation (SPWM) method". Its popularity is due to its simplicity and to the good results it guarantees in all the operating conditions, including over modulation [18].

### 2.3.2. SPWM technique for a CLS.

A good approximation of the sinusoidal voltage waveform in a CLS can be produced by a set of triangular signals and a purely sinusoidal modulating signal using a modulation technique known as Sinusoidal Pulse Width Modulation (SPWM). The principle of switching is similar to that of the 1-phase, 2-level converter [16].

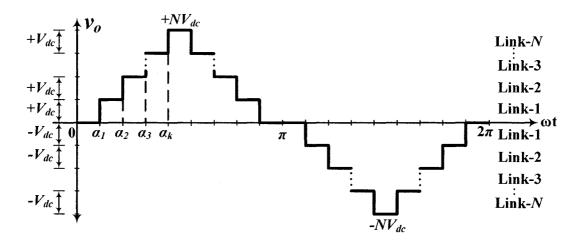

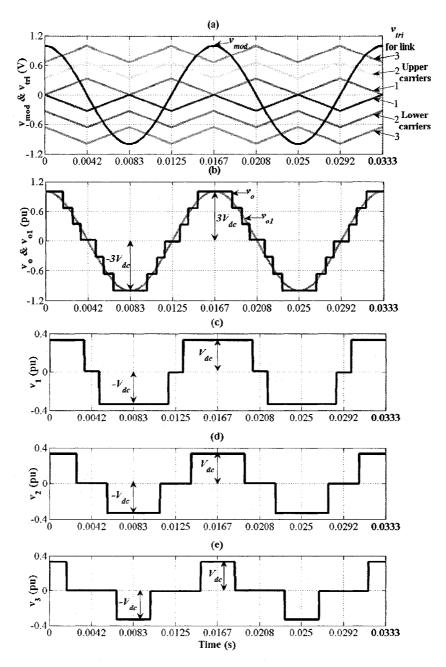

In the SPWM technique used for a CLS, there are two triangular carriers per link and one modulating signal for all the links. Therefore, the CLS with N-links, a total of 2N triangular carrier signals are required. The frequency of the triangular carriers ( $f_c$ ) is selected as 'twice' the fundamental (or power system) frequency ( $f_o$ ) so that each GTO-diode switches "on/off" only once per cycle of the fundamental frequency. The frequency of the modulating signal ( $f_m$ ) is chosen as the fundamental frequency.

i.e.

$$f_c = 2f_o$$

and  $f_m = f_o$  where,  $f_o = 60 \text{ Hz}$  (2.1)

Figure 2.5. (a) SPWM technique with six triangular carrier bands for 3-links, (b) SPWM output voltage of the CLS, and its fundamental frequency component, (c), (d) and (e) SPWM output voltage of the link-1, -2 and -3 respectively.

The intersection points of the triangular carrier signals and the modulating signal determine the switching instants  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ ,... $\alpha_k$  (where,  $\alpha_1 < \alpha_2 < \alpha_3$ ... $< \alpha_k$ ) (Figure 2.4). The harmonic analysis of the modulated waveform is done by the Double Fourier Series (DFS) method [19].

Figure 2.5 shows the SPWM waveforms used for the CLS with 3-links. The upper carrier signal switches the GTO-diode pairs  $S_1$ - $D_1$  and  $S_2$ - $D_2$  to contribute +  $V_{dc}$  to the output voltage ( $v_o$ ). The lower carrier signals switches the GTO-diode pairs  $S_3$ - $D_3$  and  $S_4$ - $D_4$  to contribute - $V_{dc}$ . When the carrier does not intersect the modulating signal, the link is in a non-contributing state.

For the CLS the amplitude modulation index  $(m_a)$  is defined as the ratio of the peak value of the sinusoidal modulating signal, to the sum of the peak-to-peak values, of all the upper (or lower) carriers:

$$m_a = \frac{\hat{V}_{\text{mod}}}{\sum_{l}^{N} \hat{V}_{tri}} \tag{2.2}$$

For the proposed CLS with 3-links, the sum of the peak-to-peak values of all the three upper (or lower) carriers is arbitrarily chosen as 1, as shown in Figure 2.5a (i.e.  $m_a = |v_{mod}| = \hat{V}_{mod}$ ). Thus, when  $m_a = 1$ , the peak of the modulating signal is 1 and when  $m_a < 1$ , the modulating signal may intersect only some of the carrier signals. Without loss of generality, this is also true for the CLS with N links. The number of links contributing to the full output voltage waveform is given as  $\langle Nm_a \rangle$ , which is the smallest integer greater than or equal to ' $Nm_a$ ' [19]. For example if  $\langle Nm_a \rangle = \langle 1.3 \rangle = 2$ , i.e. the number of links in contributing state = 2 and for  $\langle Nm_a \rangle = \langle 3.0 \rangle = 3$ , i.e., the number of links in contributing state = 3.

Assuming that the voltages on all the dc capacitors are equal, Figure 2.5b shows the output voltage waveform of the chain link converter with 3-links. With all the links in the contributing state, the individual link voltages are still 3-level waveforms, but having different pulse widths; they are combined to give an effective 7-level waveform of the

output voltage. Here link-1 is chosen to have the longest contribution time, link-2 a slightly shorter and link-3 to have the shortest contribution time. This principle can be extended, without loss of generality, to a converter with *N* links.

# 2.4. HARMONIC ANALYSIS OF THE CLS OUTPUT VOLTAGE [19]

The converter voltage is the sum of the voltages of all the links contributing to the full output voltage waveform. Therefore, from [19] the modulated output voltage of the CLS is given by:

$$v_{oh} = V_{dc} N m_o \cos(\omega_o t) + \sum_{m=1}^{\infty} \sum_{n=\pm 1}^{\infty} C_{mn} \cos((2m+n)\omega_o t)$$

(2.3)

Where,

$$C_{mn} = \frac{2V_{dc}(-1)^{\frac{n-1}{2}}}{m\pi} J_n(mN\pi m_a)$$

if m is even

$$= -\frac{4V_{dc}Nm_a}{n\pi} x \sum_{k=1}^{\langle Nm_a \rangle} \int_{\theta_{k-1}}^{\theta_k} (-1)^{k-1} \cos(m N \pi m_a \cos \lambda) \sin(n\lambda) \sin \lambda \, d\lambda$$

if m is odd

$\theta_k = \cos^{-1}(k/Nm_a)$  for  $k = 1, 2, 3, ..., (<Nm_a> -1)$ , and  $\theta_{<Nma>} = 0$ . Where,  $<Nm_a>$  is the number of links contributing to the output voltage. This is the expression for a waveform with  $<Nm_a>$  contributing links. The first term is of fundamental frequency and its magnitude is proportional to the amplitude modulation index  $m_a$ . The terms in the double summation are of angular frequency  $2\omega_o$ , multiples of  $2\omega_o$  and their sideband frequencies.

Instead of being a single term, the fundamental component of  $v_{oh}$  is made up of an infinite number of terms [19]: the first term of (2.3) and the terms in the double summation, where  $(2m+n) = \pm 1$  i.e. for all m from 1 to infinity. For simplicity of the

calculations and analysis, the terms in double summation from (2.3) can be neglected for the CLS with N - links per phase. Therefore, assuming the output voltage of the CLS,  $v_o \approx v_{ol}$ .

i.e.

$$v_o \approx V_{dc} N m_a \cos(\omega_o t)$$

(2.4)

As shown in Figure 2.5, for N=3 and  $m_a=1.0$ ,  $v_o\approx 3V_{dc}\cos{(\omega_o\,t)}$  and the peak magnitude of the output voltage,  $\hat{V}_o=3\,V_{dc}$ . Detailed harmonic analysis and derivation of (2.3) is given in [19].

# 2.5. CLS: IMPORTANT FEATURES [1, 10]

### 2.5.1. General

The CLS has many good features and advantages over conventional STATCOMs and SVCs. Consequently, it possesses enormous potential to be used in power system applications. Therefore, although the validation of these features and advantages of the CLS is not in the scope, it is essential to briefly discuss them here for the completeness of the thesis. Some of these features have already been validated by simulation studies and experiments on the pilot project in [1, 10].

#### 2.5.2. Ratings

The chain link rating is fixed by the capabilities of the GTOs & diodes employed. The commercial devices available readily, have a peak voltage & peak turn-off current capability of 4.5kV and 4kA respectively. In practice, the steady state voltage and current rating of the link has to be lower than these values to withstand the transients introduced during device switching and to give adequate safety margins for the stresses encountered during faults and disturbances. Each phase (or chain) of the 3-phase CLS is identical and

for each phase (or chain) the power circuits of individual chain links are independent of each other and also identical (i.e. same GTO-diode & dc capacitor ratings). Therefore, the voltage rating and hence the VAr rating of the CLS can be increased simply by the addition of more chain links in series per phase (or chain). With this method, the current rating remains unaltered.

### **2.5.3.** Losses

In all types of STATCOM the total losses mainly comprise of the losses in the transformer(s) and the power electronics equipment. The latter includes the losses associated with the GTO conduction, switching and its snubber circuit. In the CLS the switching losses are minimized by requiring only one switching operation per GTO per cycle of the fundamental frequency, and further the snubber circuit losses can be minimized by using a low loss design. Therefore the CLS offers a low loss design (less than 0.7% of the STATCOM VAr rating at 1 pu lagging and 1 pu leading current) [1, 10].

### 2.5.4. Redundancy

Since all the links are identical in the CLS, redundancy against the failure of any chain link is incorporated by adding an extra link per phase. Then, in the event of a GTO/link failure, the affected chain link operates continuously in the short circuit (bypass) mode, until the next scheduled maintenance outage.

### 2.5.5. Steady state characteristics

The static characteristic of a CLS is shown in Figure 1.4. Therefore, it possesses significant advantages in terms of performance over the conventional SVCs, as shown in Section 1.2.4.

### 2.5.6. Harmonic performance

A CLS with N links per phase can produce the output voltage waveform with N steps (or transitions) per quarter cycle of the fundamental frequency. Therefore, in principle it is possible to eliminate N harmonic voltages from the output voltage waveform by an appropriate choice of GTO switching angles [23]. However, this methodology is not in the scope of this thesis.

In actual practice the effects of the capacitor ripple limit the possible number of perfectly cancelled (zeroed) harmonics to somewhat less than the theoretical number. By increasing the number of links per phase, for installations of higher rating, the number of voltage steps in the converter output voltage waveform increases, and this gives further improvements in the harmonic performance.

## 2.5.7. Advantages of a CLS [1, 10]

The CLS has many advantages compared to other GTO based STATCOM circuits and conventional thyristor based SVCs [1, 10]. These are listed below:

- A CLS requires the least number of components to achieve the same number of steps in the output voltage waveform compared to the other known multilevel converter topologies viz. diode-clamped and flying capacitors converters [8]. Although it has the normal anti-parallel diodes across each GTO switch, it does not require extra auxiliary diodes associated with the multilevel capacitor stack circuit.

- The voltage and hence VAr rating of a CLS can be increased by simply adding more number of links in series per phase.

- Since each phase of a 3-phase CLS can be operated independently of one another, it offers the potential for balancing ac system phases.

- A CLS gives a low loss design by switching each GTO on/off only once per cycle

of the fundamental frequency. Furthermore, the snubber circuit losses can be

minimized by using low loss techniques and employing snubber energy recovery

circuits [9].

- A CLS has built-in redundancy against a failure of any link.

- As chain links in a CLS switch in sequence, the maximum instantaneous voltage

excursion is reduced depending upon the rating of the GTO (e.g. The STATCOM

used in the NGC's East Claydon substation, this voltage excursion is

approximately of 2kV for the 4.5kV peak voltage rated GTO) and hence the radio

interference is minimized.

- A CLS eliminates the use of expensive zigzag transformer and requires only one coupling transformer of the conventional design to step down the transmission voltage to the rated STATCOM connection voltage.