#### **Distributed Architecture for Resource Reservation Protocol**

### **Traffic Engineering (RSVP-TE)**

Saloni Neri

A Thesis

in

The Department

of

Electrical & Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical & Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

September 2007

© Saloni Neri, 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-52315-5 Our file Notre référence ISBN: 978-0-494-52315-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### Abstract

# Distributed Architecture for Resource Reservation Protocol Traffic Engineering (RSVP-TE)

The explosive growth of the Internet saw a corresponding expansion of information exchange dwarfing the very modest designs of early networking elements. With increasing dependence on this exciting medium the number of users has increased manifold. The exponential growth in the services that needed to be supported has spurred traffic volumes, resulting in the need for huge bandwidth and faster communication. Network infrastructures had to keep pace with these rapid developments but were unfortunately saddled with severe bottlenecks that the only solution was costly upgrades.

Routers, the mainstay of the Internet had to cope with a wide range of protocols. They have undergone several design modifications over the decades. A router essentially must perform two fundamental tasks-compute best routes and forward data packets. The evolution of routers is often described in terms of three generations of architectures. From the first generation with single CPUs and multiple interface cards with a shared bus, the routers evolved to the third generation with a switch fabric.

Reservation signaling protocols have become an indispensable part of the Internet service. Resource reservation protocols were originally designed to signal end hosts and network routers to provide quality of service (QoS) to individual real-time flows.

Recently, Internet Service Providers (ISPs) have been using the same signaling

mechanisms to set up provider-level Virtual Private Networks (VPNs) in the form of MPLS Label Switched Path (LSP). Traditional IP router architectures cannot scale to meet these demands, forcing architects to explore alternative designs. However, due to rapid growth of the Internet, the architecture of the third generation routers are not able to meet the expected amount of traffic (i.e., multiple terabits or petabits per second). This development results in emergence of next generation routers with large switching capacity and high speed interfaces.

The traditional centralized software model, where the control card is solely responsible for all routing and management operations is not able to efficiently utilize the new hardware platform architecture of line cards. Distributed architecture is one of the promising trends allowing routers to improve their robustness, scalability and resiliency. In this thesis path calculation and memory resources are proposed to be available on both control and line card in order to perform routing and forwarding tasks.

We investigate the ability to reallocate components of the current MPLS/RSVP-TE architecture on to the line cards in order to share the load between the control card and line card. This allows significant improvement in scalability, resiliency and robustness of the system. New mechanisms for message exchange, synchronization, table and session management, and storage are developed. Performance evaluations in terms of CPU consumption, memory requirements, load balancing and bandwidth utilization for both centralized and the proposed distributed software architectures indicate that the processing time and memory utilization are significantly reduced.

# Acknowledgement

I would like to take this opportunity to thank my mentors, advisors and supervisors, Dr. Anjali Agarwal and Dr. Brigitte Jaumard, to whom I am truly indebted for their continuous guidance and financial support in carrying out this research. Their assistance has always been generous and timely. They not only enlightened me on researching this exciting topic but also gave me the strength to be persistent in accomplishing my goals. But above all is what I have academically gained from my association with them.

I gratefully acknowledge the support of KimKhoa Nguyen for his advice, and guidance throughout this research project.

I would further like to express my appreciation to the examiners for their comments for improving my thesis. I would also like to thank Faculty of Electrical and Computer Engineering for their outstanding teaching and guidance.

I would also like to thank former Hyperchip, Inc., for providing me with financial support.

Thanks to my fellow students at University of Concordia, Akanksh Vashisth, Pavel Sinha and Alya Zaidi for making the long work hours fun.

A special whole hearted thanks to my friend Nikhil Mehta for supporting my dream and for believing in me all the way through.

Finally, I dedicate this dissertation to my parents Joe and Ruma Neri for their unconditional love and support. They are and will always be my inspiration and source of pride and strength.

I hope I have made them proud!

Saloni neri

# **Table of Contents**

| List of | Figur  | es x                                                                  |

|---------|--------|-----------------------------------------------------------------------|

| List of | Table  | esxii                                                                 |

| List of | Abbr   | eviationsxiii                                                         |

| СНАР    | TER 1  | l1                                                                    |

| l In    | troduc | ction                                                                 |

| 1.1     | Key    | y Functions of a Router4                                              |

| 1.2     | Evo    | olution of Router Architectures                                       |

| 1.2     | 2.1    | First Generation Routers: Single Central Processor and a Shared Bus 6 |

| 1.2     | 2.2    | Second Generation Routers: Route Caching                              |

| 1.2     | 2.3    | Third Generation Routers: Switch-based                                |

| 1.2     | 2.4    | Next Generation Routers                                               |

| 1.2     | 2.5    | Forwarding and Routing Mechanisms of Next Generation Routers 11       |

| 1.3     | Mo     | tivation for a Distributed MPLS/RSVP-TE Architecture                  |

| 1.5     | The    | esis Organization                                                     |

| CHAP'   | ΓER 2  | 2                                                                     |

| 2 Ba    | ckgro  | ound Information17                                                    |

| 2.1     | Ove    | erview of MPLS                                                        |

| 2.2     | Ove    | erview of RSVP-TE Protocol                                            |

| 2.3     | Ove    | erview of RTM25                                                       |

| C  | CHAPTER 32 |                                                                      | 28 |

|----|------------|----------------------------------------------------------------------|----|

| 3  | Lite       | erature Review                                                       | 28 |

|    | 3.1        | Distributed Software Architecture                                    | 29 |

|    | 3.2        | Industrial Next Generation Routers and Prototype                     | 31 |

|    | 3.2        | Juniper Next Generation Router                                       | 31 |

|    | 3.2        | 2 Nexabit NX64000 Router                                             | 34 |

|    | 3.2.       | 3 Cisco Next Generation Router                                       | 34 |

|    | 3.2.       | 4 Hyperchip Prototype                                                | 35 |

|    | 3.2.       | 5 Tiny Tera Prototype                                                | 37 |

| C. | НАРТ       | ER 4                                                                 | 38 |

| 4  | Cer        | ntralized and Distributed Architectures for RTM with RSVP-TE         | 38 |

|    | 4.1        | Centralized RTM Architecture                                         | 38 |

|    | 4.2        | Partially Distributed RSVP-TE Architecture with Centralized RTM      | 41 |

|    | 4.3        | Fully Distributed RSVP-TE Architecture with Distributed RTM          | 44 |

|    | 4.4        | Summary                                                              | 46 |

| C) | НАРТ       | ER 5                                                                 | 47 |

| 5  | Ele        | ments for a Distributed and a Scalable Architecture for MPLS/RSVP-TE | 47 |

|    | 5.1        | A General Framework for Distributed Software Architecture            | 47 |

|    | 5.2        | Table Management                                                     | 50 |

|    | 5.3        | Message Processing                                                   | 53 |

|    | 5.4        | RSVP-TE Data Base Distribution                                       | 55 |

| 5.5     | Resource Reservation with QoS Module                          | 56          |

|---------|---------------------------------------------------------------|-------------|

| 5.6     | Summary                                                       | 58          |

| CHAP.   | TER 6                                                         | 59          |

| 6 A     | New Distributed & Scalable MPLS/RSVP-TE Architecture          | 59          |

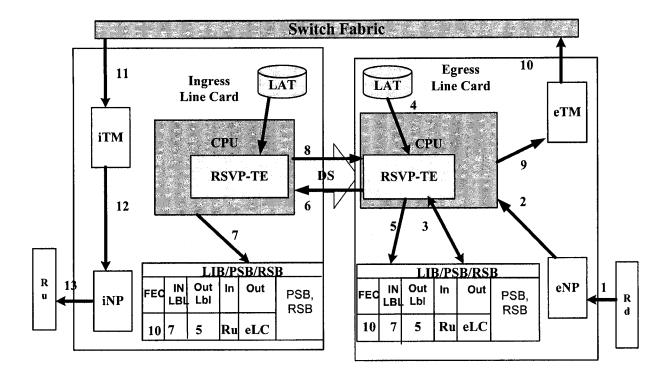

| 6.1     | Definition of Ingress and Egress Line Card                    | 59          |

| 6.2     | Detailed description of a RSVP-TE Protocol Message Processing | 60          |

| 6.2     | 2.1 Downstream Processing of Path Message Requests            | 61          |

| (       | 6.2.1.1 Processing a Path Message at LER                      | 62          |

| (       | 6.2.1.2 Processing a Path Message at LSR (Transit Router)     | 65          |

| 6.2     | 2.2 Upstream Processing of Resv Message Requests              | 68          |

| (       | 6.2.2.1 Processing a Resv Message at LER                      | 69          |

| (       | 6.2.2.2 Processing a Resv Message at LSR (Transit Router)     | 69          |

| 6.3     | Summary                                                       | 72          |

| CHAPT   | ΓER 7                                                         | 73          |

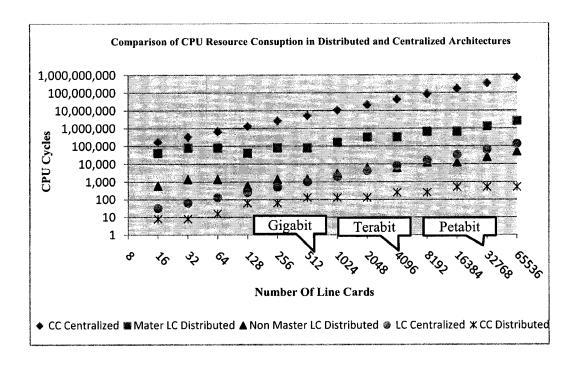

| 7 Per   | rformance Analysis of MPLS/RSVP-TE Messages (Distributed vs.  | Centralized |

| Archite | ectures)                                                      | 73          |

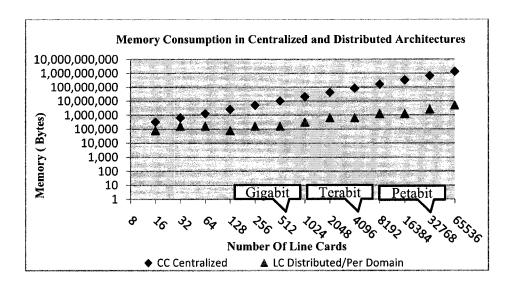

| 7.1     | CPU Cycles and Memory Consumption                             | 73          |

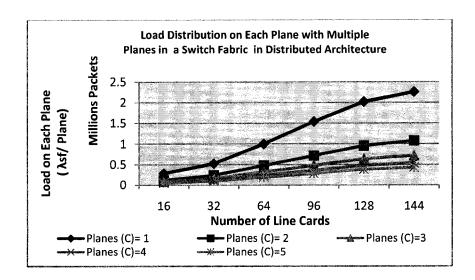

| 7.2     | Load Balancing with Multi-Plane Switch Fabric                 | 86          |

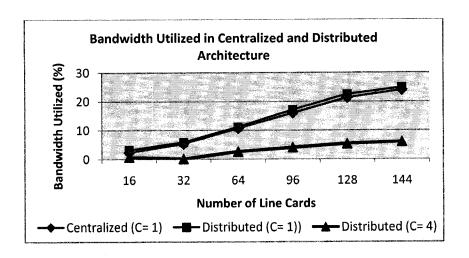

| 7.3     | Bandwidth Utilization                                         | 95          |

| 7.4     | Advantages of a Distributed/Scalable Architecture             | 97          |

| CHAPTER 8 |                               |     |

|-----------|-------------------------------|-----|

| 8 C       | onclusion and Recommendations | 100 |

| 8.1       | Conclusion                    | 100 |

| 8.2       | Future Work                   | 101 |

| Refere    | ences                         | 103 |

# **List of Figures**

| Figure 1.1 | First Generation Router with Single Central Processor and a Shared Bus 7 |

|------------|--------------------------------------------------------------------------|

| Figure 1.2 | Second Generation Router with Route Cache Architecture                   |

| Figure 1.3 | Third Generation Router with Switch Based Architecture                   |

| Figure 1.4 | Components of a Typical LC and CC                                        |

| Figure 1.5 | Architecture of Next Generation Router                                   |

| Figure 2.1 | MPLS Architecture                                                        |

| Figure 2.2 | Path and Resv Messages                                                   |

| Figure 2.3 | MPLS/RSVP-TE for Next Generation Routers [30]                            |

| Figure 2.4 | Inter-communication of RTM with Routing Protocols                        |

| Figure 3.1 | M-Series Router Architecture                                             |

| Figure 3.2 | T-Series Router Entities                                                 |

| Figure 3.3 | Hyperchip Architecture                                                   |

| Figure 3.4 | Architecture of Tiny Tera                                                |

| Figure 4.1 | Current RTM Architecture: Distributed on Protocol Basis                  |

| Figure 4.2 | Distributed MPLS Architecture with a Centralized RTM                     |

| Figure 4.3 | Distribution of LC-RTMs                                                  |

| Figure 5.1 | RSVP-TE Components on the LC                                             |

| Figure 5.2 | FEC-TO-NHLFE (FTN) Table Structure                                       |

| Figure 5.3 | ILM Table Structure                                                      |

| Figure 5.4 | Distributing RSVP-TE Data Base in LCs                                    |

| Figure 5.5 | Resource Reservation for a Distributed RSVP-TE                    | 57 |

|------------|-------------------------------------------------------------------|----|

| Figure 6.1 | Ingress LC and Egress LC                                          | 60 |

| Figure 6.2 | Downstream Processing of Path Message                             | 62 |

| Figure 6.3 | Processing RSVP-TE Path Message on LER                            | 63 |

| Figure 6.4 | Path Message Processing on LSR                                    | 68 |

| Figure 6.5 | Processing Resv Message (Upstream On demand Mode)                 | 69 |

| Figure 6.6 | Processing RSVP-TE Resv Message on LSR                            | 70 |

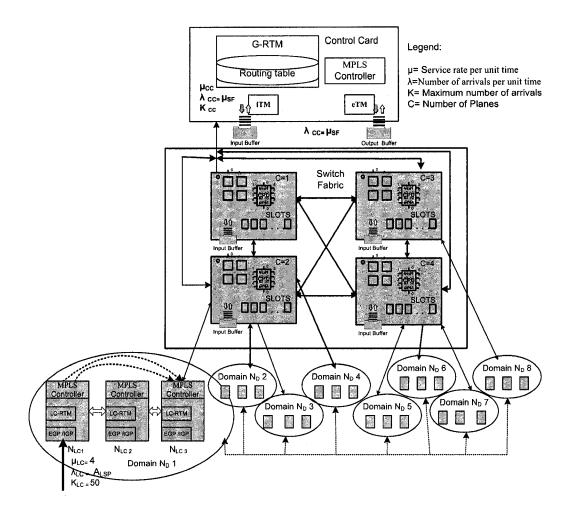

| Figure 7.1 | Centralized Architecture with Multiple Planes in a Switch Fabric  | 75 |

| Figure 7.2 | Distributed Architecture with Multiple Planes in a Switch Fabric  | 80 |

| Figure 7.3 | CPU Resource Consumption                                          | 85 |

| Figure 7.4 | Memory Consumption                                                | 86 |

| Figure 7.5 | Load Distribution in Distributed Architecture                     | 94 |

| Figure 7.6 | Bandwidth Utilization in Centralized and Distributed Architecture | 97 |

# **List of Tables**

| Table 7-1  | CPU Resource Consumption                                           | . 83 |

|------------|--------------------------------------------------------------------|------|

| Table 7-2  | Memory Consumption for Centralized and Distributed Architecture    | . 84 |

| Table 7-3  | Wait Time Calculations in Centralized Architecture                 | . 91 |

| Table 7-4  | Wait Time Calculations in Distributed Architecture                 | . 93 |

| Table 7-5: | Qualitative Comparison between Centralized and Distributed RSVP-TE |      |

| Archi      | tectures                                                           | . 99 |

#### List of Abbreviations

ATM Asynchronous Transfer Mode

BGP Border Gateway Protocol

CC Control Card

eNP Egress Network Processor eTM Egress Traffic Manager CLI Command-Line Interface

FEC Forwarding Equivalence Class

FIT Forwarding Information Table

FTN FEC-To-NHLFE

ILM Incoming Label MappingiNP Ingress Network ProcessoriTM Ingress Traffic Manager

IP Internet Protocol

LAT Label Allocation Table

LDP Label Distribution Protocol

LC Line Card

LER Label Edge Router

LIB Label Information Base

L-ROUTE Local Route Base

LSP Label Switch Path

LSR Label Switch Router

MPLS Multi-Protocol Label Switching

NHLFE Next Hop Label Forwarding Entry

OSPF Open Shortest Path First

QoS Quality of Service

RSVP Resource ReSerVation Protocol

RSVP-TE RSVP Traffic Engineering RTM Routing Table Manager

TCP Transmission Control Protocol

UDP User Datagram Protocol

# Chapter 1

### 1 Introduction

The explosive growth of the Internet has led to an increase in the number of users who have diverse demands for more reliable and differentiated services. Both large and small Internet Service Providers (ISPs) constantly face the challenges of adapting their networks to accommodate new services and meeting more diverse customer requirements. New services appear, which may require modifications of existing protocols, entirely new protocols, or modifications of the ways in which packets are processed in routers. Examples of such new services are video conference, IPTV and the transition to Internet Protocol version 6 (IPv6). In many situations, software updates are not enough to achieve this goal. Meanwhile, due to extremely high costs, physically replacing or upgrading network infrastructure constantly is not feasible, either.

The traditional way to build routers has been to use a monolithic architecture [1] [2], where line cards (LCs) are connected to a backplane, and where a CPU-based controller is used to run routing software, to handle network management software and other types of control software.

The LCs and the forwarding functionality are normally referred to as the forwarding plane, while the controller and its functionality are referred to as the control plane.

The continuously growing need for new services and protocols also affects the control plane of the router [3]. The control plane is traditionally a design where a variety of large software functions are integrated into an operating system in a monolithic fashion. This means that adding new services to a router is often a complex task from the control plane point of view. Protocols such as BGP [5], OSPF [6], ISIS [7], MPLS [8], RSVP-TE [10], together with other functions needed in a router, constitute large amounts of complex software. This may consequently result in high demands on control processing. Thus, it is hard to add new functionality in the control plane and at the same time maintain a high degree of reliability and efficient execution of the software.

The monolithic structure of these traditional routers is an architectural limitation when it comes to meeting future requirements. In order to satisfy these requirements, a modular design is required. With modular design, routing software components can run independently on the same or separate CPUs and interact with each other regardless of their respective physical location. This approach produces a robust network that is not vendor specific and that can use modules developed by different manufacturers.

MPLS is the protocol framework on which the attention of a network service provider is focused as it provides a solution to scalability and enables significant flexibility in routing. MPLS is capable of providing controllable quality of service (QoS) features. It is meant to primarily

prioritize Internet traffic and improve bandwidth utilization. When packets enter a MPLS-based network, Label Edge Routers (LERs) give them a label identifier based on its Forward Equivalence Class (FEC). Once this classification is complete and mapped, different packets are assigned to the corresponding Labeled Switch Paths (LSPs), where Label Switch Routers (LSRs) place outgoing labels on the packets. MPLS employs RSVP-TE, an extension of the Resource Reservation Protocol, for establishing LSPs [10].

RSVP-TE is a receiver-oriented protocol, meaning that label allocation and bandwidth reservation are driven by the receiver node. RSVP-TE allows the establishment of LSPs, taking into consideration network constraint parameters such as available bandwidth and explicit hops. The two main message types used are a Path Message (used to establish a path from the source to the destination) and Resv Message (used to reserve the resources that will be used in an LSP). Path Message is first sent downstream to the destination. Once Path Message is successfully sent and received, Resv Message is sent upstream to the source and an LSP is established to send data to the destination [8][10].

In the current generation of routers, the RSVP-TE module is neither distributed nor scalable. There are several limitations of the centralized architecture on the ever-increasing number of interconnections between routers. It requires routers to have more CPU cycles, more powerful accompanying hardware resources, and an increased memory size to contain all available routing information. Until recently, the only valid solution to support the increasing Internet traffic was to periodically upgrade the router control card (CC), on which the RSVP-TE module is running, or to replace the whole router with a new one having more powerful hardware resources (e.g.,

CPUs and increased memory size), demanding some service interruptions. An alternate solution is to implement distributed and scalable routers. Taking advantages of the hardware revolution, a more cost-effective approach to deal with the ever-increasing traffic in the networks has been proposed, where a next generation router with large-capacity switching of multiple terabit or even petabit is deployed in the core network [3][18].

In this chapter we intend to review the evolution of routers and give a brief overview of key functions of a router. In the following chapters we focus on a distributed and scalable architecture for MPLS/RSVP-TE routing protocol. We investigate the ability to reallocate components of MPLS/RSVP-TE on to the LCs in order to share the load between the CC and the LC.

#### 1.1 Key Functions of a Router

Broadly speaking, a router must perform two fundamental tasks which are described below.

• Compute best routes: The first function is to compute best routes that the data packets would use to traverse through the network to their destinations. The route computation has to take into account various policies and network constraints [13]. For example, the best route can be required to maximize network efficiencies, to minimize bandwidth usage costs and deliver the fastest possible response times to users. In the current generation routers, the route computation is accomplished by a route processor or universally known as a routing engine. Based on the information exchanged between neighbouring routers using routing protocols, the routing process constructs a view of the network topology and computes the

best paths. A routing engine is essentially the "brain" of the router and is responsible for communication with neighbours. This communication enables the route processor to build a route database, or routing table, that allows the forwarding engine to send packets across optimal paths through the network are located. Such communication is achieved by the routing protocols [17]. The routing protocols communicate information about which networks each router can reach and how far away those networks are. These messages are called routing updates. All routing protocols can be classified as Interior Gateway Protocols (IGPs) or External Gateway Protocols (EGPs) [13].

- o IGPs run inside an autonomous system (AS) and perform so called intra-domain routing functions. Widely used IGP protocols include Routing Information Protocol (RIP) [14], Open Shortest Path First (OSPF) [6] and Intermediate System-to-Intermediate System (IS-IS) [7].

- EGPs run between ASs. The currently most used EGP is Border Gateway Protocol (BGP)

In a core router, the BGP module has to handle a very large number of routes (e.g., some hundreds of thousands of routes) and ASs (e.g., tens of thousands of ASs) [15].

- Forward data packets: The second function of the router is to forward data packets received across the network. Forwarding relies on the best route information computed by the route processor. The forwarding function is achieved by forwarding engines. The forwarding engine consults a Forwarding Information Table (FIT) which contains a complete set of forwarding information for all destinations learned by the routing protocols or by the list of static routes. Based on the destination address field of the IP packet header,

the forwarding engine looks up the FIT to find the next hop to forward the packet. As traffic loads grow, the processing resources required for FIT lookups increase.

#### 1.2 Evolution of Router Architectures

The Internet has been in function since the 1970s, and IP routers have gone through several design modifications over the decades. The evolution of routers is often described in terms of three generations of architectures. The different generation of routers [16] [21] [35] [44] will be described briefly below. The latest generation of routers, could be thought of as the next generation routers or distributed routers, which will be described in detail in the next chapters.

#### 1.2.1 First Generation Routers: Single Central Processor and a Shared Bus

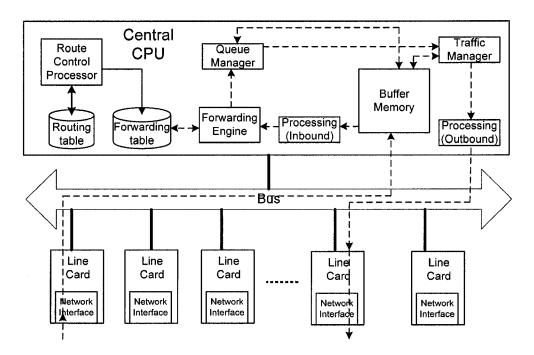

The first generation of IP routers was basically made of a single central processor and multiple interface cards interconnected through a shared bus. The CPU runs a commodity real-time operating system and implements the functional modules, including the forwarding engine, the queue manager, the traffic manager, and some parts of the network interface, especially Layer 2/Layer 3 processing logic in software. Figure 1.1 shows the architecture of the first generation routers. An incoming packet at a LC (called ingress line card) [16] is forwarded to the buffer memory through the shared bus. The central CPU extracts the headers of the packet and uses the forwarding table to determine the outgoing LC (called egress interface) and port. The packet is subsequently prioritized by the queue manager and shaped by the traffic manager. Finally, the packet is transferred from memory to the appropriate output port in the egress LC [17].

The performance of these routers depends on the throughput of the shared bus and on the speed of the central processor; therefore they are not able to scale to meet today's bandwidth requirements [17].

Figure 1.1 First Generation Router with Single Central Processor and a Shared Bus

#### 1.2.2 Second Generation Routers: Route Caching

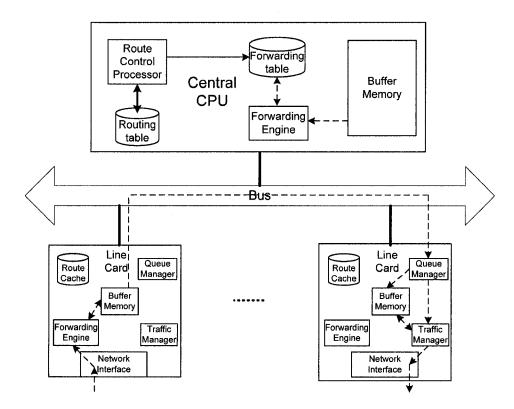

The second generation router architecture was designed with more intelligence. The router has a central CPU maintaining a central forwarding table and the LCs contain a local cache which is a subset of the master forwarding table based on the routes that were recently used as shown in Figure 1.2. When a LC receives a data packet, it first looks up the local cache for the next hop to forward the packet. If no entry is available in the cache, the LC sends a request to the central CPU [16].

The advantage of this architecture is the increased throughput because of the forwarding cache. However, the shared bus is still a potential bottleneck because it does not allow more than one data packet to go across at the same time. Due to these drawbacks, this architecture can neither scale to high capacity links nor provide complex traffic pattern-independent throughput [17].

Figure 1.2 Second Generation Router with Route Cache Architecture

#### 1.2.3 Third Generation Routers: Switch-based

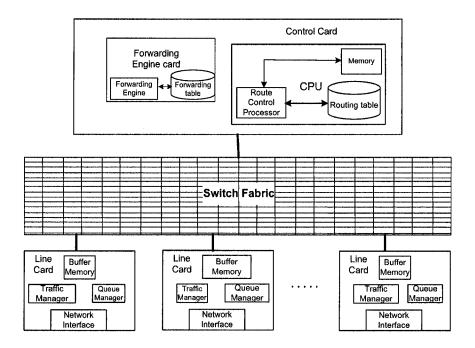

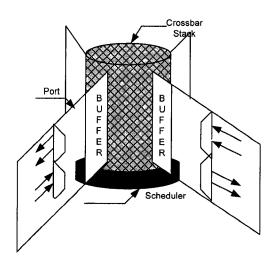

The third generation or the current generation router was introduced to solve bottlenecks of the second generation. The shared bus was replaced by a switch fabric which allows multiple packets to be simultaneously transferred across, hence increasing the performance as shown in Figure 1.3 [16]. The switch fabric is basically a crossbar connecting multiple cards together thus providing large bandwidth for transmitting packets among LCs [3][21].

Figure 1.3 Third Generation Router with Switch Based Architecture

There are three main bottlenecks which can potentially be experienced in a first and second generation router: processing capacity, memory bandwidth, and internal bus bandwidth. Hence the switching architecture has been deployed in the third generation routers in order to replace the internal bus. However, due to rapid growth of the Internet, the architecture is not able to meet the expected amount of traffic (i.e., multiple terabits or petabits per second). The third generation routers are not scalable to support a large number of LCs. These issues led to the next generation routers, which we will be describe in the next section.

#### 1.2.4 Next Generation Routers

The architecture of the next generation routers is essentially switch-based, with a switching capacity of petabits per second, satisfying different QoS requirements [4]. First commercial

terabit routers that appeared in the market were Avici's TSR [18][20], Juniper T1600 [12] and Nexabit [42]. Some prototypes have also been introduced like HyperChip's PBR1280 [19] and Tiny Tera [43]. Next generation routers have the following advanced features:

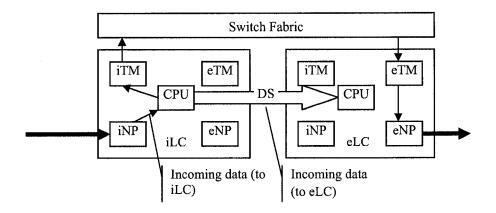

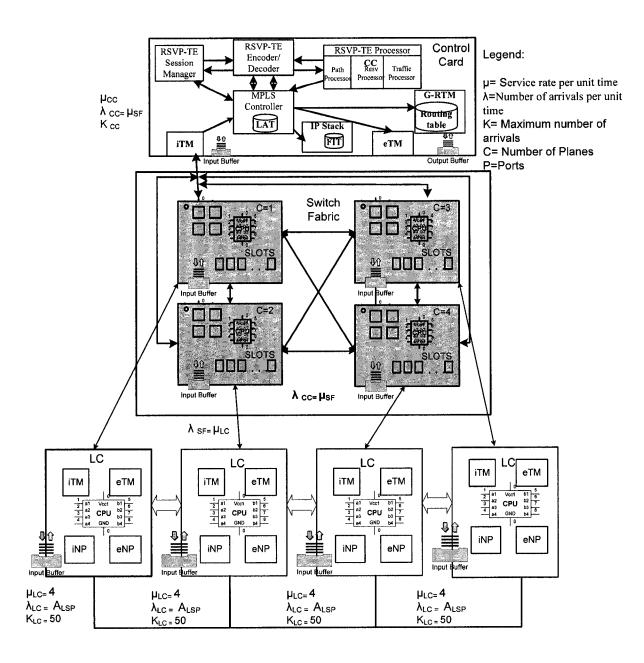

#### **Line Cards**

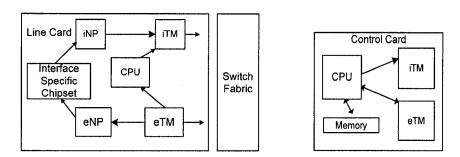

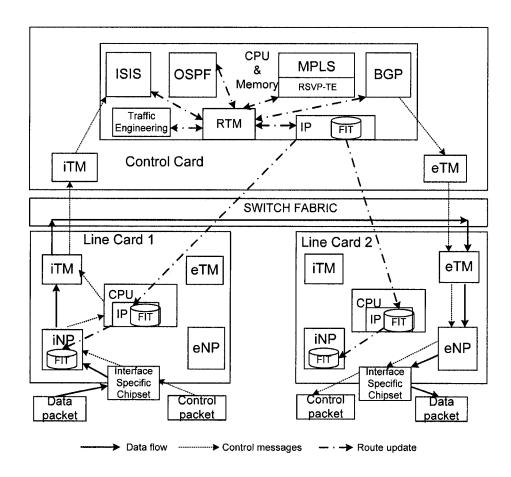

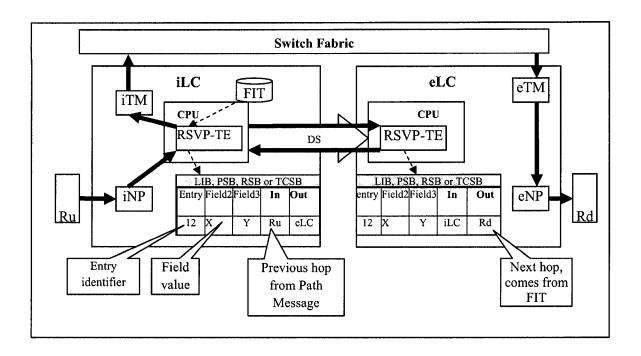

The Line Card (LC) provides one or more interfaces to external devices (such as other routers) and connects these interfaces to the switch fabric, as shown in Figure 1.4. The ingress Traffic Manager (iTM) receives frames from the ingress Network Processor (iNP) with the respective destination addresses, and queue numbers. The iTM's main role is to forward these frames to the switch fabric as well as to provide balanced traffic distribution among the switch fabric planes. The egress Traffic Manager's (eTM) role in the LC is to receive packets from the switch fabric planes directly connected to its LC, to perform frame re-assembly and to perform frame sequencing of re-assembled frames. Once these operations are completed, frames are either sent to the local CPU or forwarded to the egress Network Processor (eNP) for additional forwarding treatment and per-egress-port output queuing depending on the destination of the internal frame being re-assembled. Nowadays, a network processor can handle flows at OC-48 or OC-192 line rate or even faster [3].

Figure 1.4 Components of a Typical LC and CC

#### **Control Card**

The control card (CC) architecture is very similar to the one of a LC. The basic difference between both cards lies in the processing power and storage capabilities of CC being far superior, and there are no line interfaces. The CC has one ingress Traffic Manager (iTM) chip and one egress Traffic Manager (eTM) chip as shown in Figure 1.4. These chips provide an interface between the local processor and the switch fabric planes. The iTM and eTM chips are exactly the same as the ones used in the LCs.

#### Switch Fabric

The router's cards are interconnected by a scalable switch fabric. The switch fabric is distributed into identical and independent switching planes. In our research, we assume using a switch fabric model provided by Hyperchip [19] [22] which consists of multiple planes. In such a model, each switching plane has bandwidth to handle a full OC-48 port or equivalent. A switch fabric port, which is equivalent to one frontal interface chassis slot, connects a LC or a CC to one of the four planes. Each switching plane is made of identical switching cards, so called matrix cards.

#### 1.2.5 Forwarding and Routing Mechanisms of Next Generation Routers

Forwarding and routing mechanisms in a next generation router are illustrated in Figure 1.5. Data packets come in by the iNP of the ingress LC which contains a FIT table that is used to determine the path to the destination. Packet classification is also done by the iNP. Packets are then forwarded through the iTM where traffic engineering policies are applied. They then travel through the switch fabric to the egress LC. The eTM and eNP of the egress LC forward the

packet to the next hop in towards the destination. Control packets, on the other hand, are filtered by the iNP of the ingress LC and forwarded directly to the CC or the CPU of the LC where they will be processed by the routing protocol modules. The iTM and eTM chipsets located on the CC are responsible for managing flows of control packets. Control packets may also be sent out to external routers in the network through appropriate LCs.

Figure 1.5 Architecture of Next Generation Router

As we can see from Figure 1.5, routing engine handles a set of routing protocols like IS-IS, OSPF, BGP and MPLS that run together and interchange information such as routes or labels. The advantage of such an architecture is the ease of management since all the routing protocols run together on the same CC. The synchronization and message exchange mechanisms are also

quite simple to implement. However, the main issue of such legacy systems is their monolithic code base with all forwarding and routing processes competing for the same CPU and memory resources. Consequently, as the demanding packet forwarding process consumes almost all the CPU capacity, the other functions are left starving for CPU cycles. Clearly this type of routers can only be used for small and medium size networks.

Thus we investigate the ability to relocate RSVP-TE signaling protocol [10] on to the LC. This approach will let routers to have more CPU cycles, more powerful accompanying hardware resources, and an increased memory size to contain all available routing information.

#### 1.3 Motivation for a Distributed MPLS/RSVP-TE Architecture

One of the primary requirements for next generation routers is to obtain the advantages of the additional resource available on LCs. In general, next generation routers have to exchange control messages with hundreds of peers. Keeping pace with the growing requirement of bandwidth, a large number of LCs needs to be added to the router platform. This imposes several challenges to the operation of routing protocols. Current generation routers provide terabit throughput, while next generation routers, assuming a distributed architecture, will reach petabit throughput per set of thousand LCs.

Routing protocols like BGP [5], OSPF [6] and ISIS [7] should be distributed on the LCs in order to take advantages of the next generation distributed router platform to provide additional processing and memory resources on LCs. In the similar manner signaling protocols such as LDP [26] and RSVP-TE should also be distributed on the line cards. No research has been done on routing protocols. However work is in progress in [45] to distribute the LDP protocol. In this thesis we investigate the ability of distributing MPLS/RSVP-TE module on the LCs.

In addition, the model proposed in this thesis has the following advantages:

- **Performance:** parallel processing is enabled in the proposed architecture and waiting queue can therefore be avoided. LCs are able to process the routes separately without having to wait for reply from the CC.

- Scalability: Scalability is improved since some of the control tasks, particularly the signaling, are processed by LCs. The CC processes only the most complicated tasks, the tasks that need human interactions or the tasks used to inter-operate different LCs [23].

- Resiliency: If the CC is responsible for all control tasks, the system will completely shutdown if the CC fails. The distributed architecture proposed allows the LCs to maintain connections with the peer routers [25]. The CC restarts only when it fails. The fully distributed architecture we propose for signaling protocols such as RSVP-TE is able to self restore without the help of the CC.

- Availability: The time to recover from failures is reduced. Since complete restart is not required, problems pertaining to the CC will not slow down process on LCs.

#### 1.4 Contributions of this Thesis

We consider the next-generation router architecture as a starting point for a distributed framework. In this thesis we consider that the RTM is distributed on the LCs to serve RSVP-TE signaling protocol to increase the scalability and to reduce the load of the CC.

The major contributions of this thesis are as follows:

• A Novel Scalable and Distributed Architecture for MPLS/RSVP-TE: The system design of a distributed architecture for MPLS/RSVP-TE is proposed with respect to the RFC's

specifications. Different distributed solutions are explored in order to eliminate centralized scheduling and bottlenecks on the CC.

- Synchronization Mechanisms: Various synchronization mechanisms are used to process

RSVP-TE downstream and upstream signaling messages. Synchronization between LCs,

synchronization between routing tables and MPLS tables, distributed label provision,

distributed table access and update have also been dicussed.

- **Performance Evaluation:** Mathematical models have been designed for the proposed MPLS/RSVP-TE with respect to the number of CPU cycles, memory requirements, load balancing and bandwidth utilization. These models imply that the processing time can be significantly reduced via the distribution of workload and reduce potential bottlenecks experienced on the CC when the number of requests increase.

While we kept the resiliency issues in mind, we did not investigate it further in this thesis and left it for future research.

#### 1.5 Thesis Organization

This thesis consists of eight chapters including necessary background, motivation and the objectives of the research effort in Chapter 1. Chapter 2 provides an overview of MPLS and RSVP-TE protocols. In addition it provides an overview of the Routing Table Manager, which is the most important module of a router. Chapter 3 provides related information and previous research done by other researchers in the same area. It includes a review of recent literature on software architecture for distributed routers. It also includes the new generation routers in the industry. Chapter 4 discusses the benefits of distributed Routing Table Manager on the LCs and

motivations of using this approach in the research proposal. Chapter 5 covers the efficient elements needed for a distributed and scalable RSVP-TE architecture. Chapter 6 describes each element in detail for a distributed and scalable architecture. Chapter 7 gives the performance evaluation in terms of CPU consumption, memory usage and bandwidth utilization in centralized and distributed architecture. Finally, Chapter 8 provides conclusions and summary of the research effort as well as the recommendations for future research.

# Chapter 2

## 2 Background Information

Resource reservation protocols were originally designed to signal end hosts and network routers to provide quality of service to individual real-time flows. More recently, Internet Service Providers (ISPs) have been using the same signaling mechanisms to set up provider-level Virtual Private Networks (VPNs) in the form of MPLS Label Switched Path (LSP).

In core routers, the Routing Table Manager (RTM) [13] module plays an important role by managing all best routes coming from various sources. Possible sources are the different routing protocols, such as Open Shortest Path First (OSPF) [6], Intermediate System to Intermediate System (IS-IS) [7], Border Gateway Protocol (BGP) [5], and RSVP-TE [10]. This chapter provides an overview of MPLS/RSVP-TE and the RTM.

#### 2.1 Overview of MPLS

In a MPLS [8] network, packets are forwarded hop-by-hop based on a fixed-length label. This label, called Label Switched Path (LSP), determines the route that the packet will take to the destination. Thus, the routing process is done only in edge routers, so called Label Edge Router

(LER), then the packet is simply switched over transit routers, so called Label Switch Router (LSR); in consequence, the forwarding speed is improved. In traditional IP based networks, all packets from a given source to a given destination travel on a best route determined by a routing protocol. Hence the additional services such as VPN are not enabled. In addition, nodes on the best route can become critical points due to the overload, while other nodes in the network can be inefficiently utilized. Based on labels, MPLS provides flow management, traffic engineering, quality of service (QoS), VPNs (Virtual Private Networks) and Any Transport over MPLS (AToM).

A MPLS label is a 20-bit identifier, added to the MPLS data packets to forward them over a network. Packets share the same forwarding criteria, so called forwarding equivalence class (FEC), e.g., that experience the same delay, and carry the same label. Therefore, a LSP is a combination of a FEC and a label. In order to define the LSPs among routers in a network, signaling protocols like LDP [26] [25] and RSVP-TE [10] are deployed.

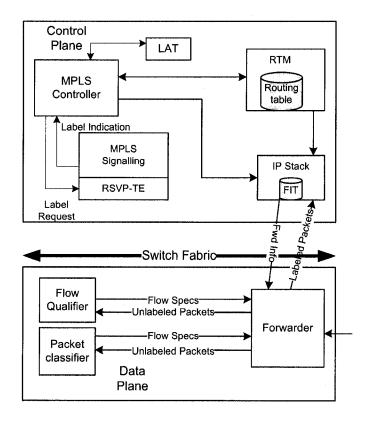

In a next generation router, MPLS architecture is divided into two main architectural blocks as shown in Figure 2.1 [30].

- Control plane: Performs functions of identify reachability to destination prefixes.

Therefore the control plane contains all the Layer 3 routing information. In addition, all protocol functions that are responsible for the exchange of labels between neighboring routers and RSVP-TE module.

- Data plane: Performs the functions relating to forwarding data packets. These packets can be either Layer 3 IP packets or labeled IP packets. The information in the data plane, such as

label values are derived from the control plane. Information exchange between neighboring routers creates mappings of IP destination prefixes to labels in the control plane, which is used to forward data plane labeled packets.

Figure 2.1 MPLS Architecture

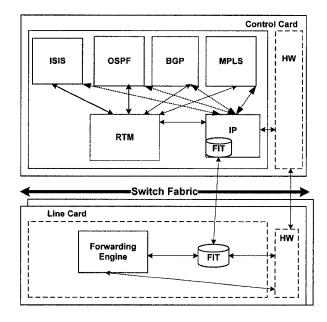

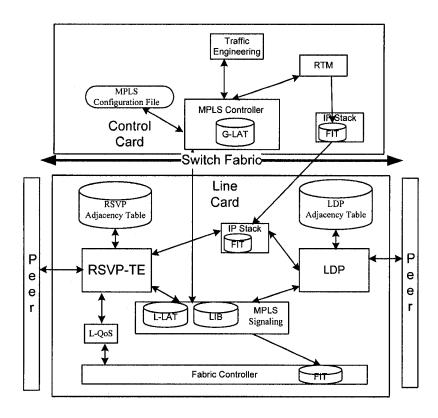

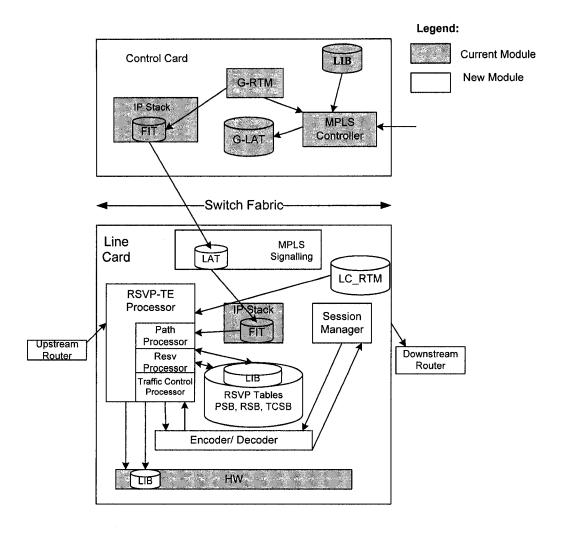

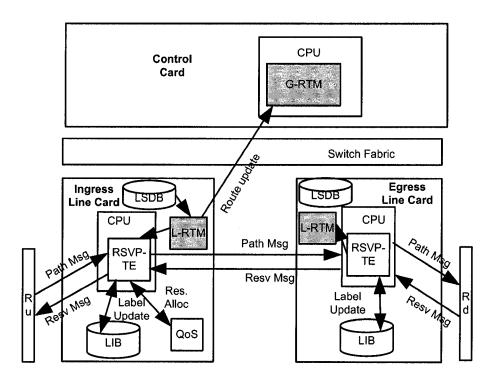

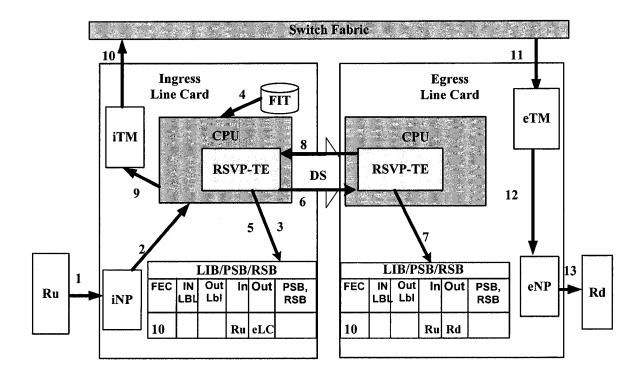

In recent router products including next generation routers, the MPLS and the RSVP-TE module are neither distributed nor scalable. These routers handle all RSVP-TE processes on the CC. Indeed, there are no MPLS and RSVP-TE module running on any LC. The centralized architecture of a MPLS module consists of the following modules as shown in Figure 2.3 [30].

• eTM, eNP (Forwarder): Is responsible for classifying and processing unlabeled packets, making MPLS forwarding decision for labeled packets and forwarding outgoing packet.

- iTM, iNP (Flow Qualifier): Is in charge of qualifying unlabeled packets, associating the unlabeled packets with a FEC.

- iTM, iNP (Packet Classifier): Is similar to Flow Qualifier and can be used alternatively. The difference is that Packet Classifier, filters packets according to the Traffic Engineering which can be specified by user, while Flow Qualifier, gets filter information from the FIT.

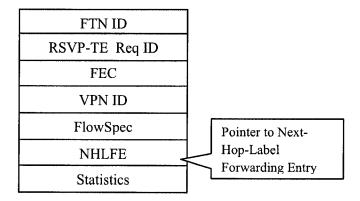

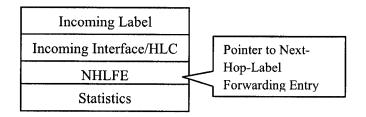

- FIT (Forwarding Information Table): Used for forwarding MPLS data packets. FIT is controlled and updated by MPLS Controller.

- Label Allocation Table (LAT): Used by MPLS Controller to manage label spaces and to keep track of all allocated labels.

- Label Information Base (LIB): Used to forward data packets. The LIB contains information for labeling a data packet, changing the current label, or removing label when the packet reaches the destination.

- MPLS controller: Is the heart of the MPLS system. It is responsible for managing FIT, using LAT to manage label space and to track all allocated and ready-to-use labels, and interacting with MPLS signaling module to establish LSPs.

#### 2.2 Overview of RSVP-TE Protocol

RSVP-TE extends RSVP by supporting additional objects allowing the establishment of explicitly routed label switched paths using RSVP as a signaling protocol. The result is the instantiation of label-switched tunnels that can be automatically routed away from network failures, congestion, and bottlenecks.

#### **Description of RSVP-TE Messages**

RSVP-TE defines seven signaling messages. This section gives a brief overview of the seven signaling messages: Path, Resv, PathErr, ResvErr, PathTear, ResvTear, and ResvConf used by the RSVP-TE protocol [9] [10] [11].

#### • Path Message and Resv Message

- o **Path Message** is sent by each sender along the unicast or multicast routes provided by the routing protocol(s). A Path Message is used to store the path state in each node. The path state is used to route reservation-request messages in the reverse direction.

- Resv Message is sent by each receiver host toward the senders. This message follows in

the reverse directions the routes that the data packets use, all the way to the sender hosts.

A reservation-request message must be delivered to the sender hosts so that the hosts can

set up appropriate traffic-control parameters for the first hop.

RSVP-TE takes a "soft state" approach to manage the reservation state in routers and hosts. RSVP soft state is created and periodically refreshed by Path and Resv Messages. The state is deleted if no matching Refresh Message arrive before the expiration of a "cleanup timeout" interval. State may also be deleted by an explicit "teardown" message, described in the next section. At the expiration of each "refresh timeout" period and after a state change, RSVP-TE scans its state to build and forward Path and Resv Refresh Message to succeeding hops.

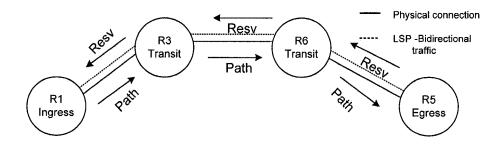

Figure 2.2 shows the flow of Path and Resy Message from router R1 to R5.

Figure 2.2 Path and Resv Messages

#### • Tear messages (Path Tear and Resv Tear)

RSVP-TE "teardown" messages remove path or reservation state immediately. There are two types of RSVP-TE teardown messages, PathTear and ResvTear. A teardown request may be initiated either by an application in an end system (sender or receiver), or by a router as the result of state timeout or service preemption. Once initiated, a teardown request must be forwarded hop-by-hop without delay. A teardown message deletes the specified state in the node where it is received.

- A PathTear Message travels towards all receivers downstream from its point of initiation and deletes path state, as well as all dependent reservation state, along the way.

- A **ResvTear** Message deletes reservation state and travels towards all senders upstream from its point of initiation. A PathTear and ResvTear Messages may be conceptualized as a reversed-sense Path Message (Resv Message, respectively).

#### • Error Messages (Path Error and Resv Error)

There are two Error Messages PathErr and ResvErr that are described below.

- o **PathErr** (path error) messages report errors in processing Path Messages. They travel upstream towards senders and are routed hop-by-hop using the path state. At each hop, the IP destination address is the unicast address of a previous hop. PathErr messages do not modify the state of any node through which they pass; they are only reported to the sender application.

- ResvErr (reservation error) messages report errors in processing Resv message. ResvErr messages travel downstream towards the appropriate receivers, routed hop-by-hop using the reservation state. Information carried in error messages are admission failure, bandwidth unavailable, Service not supported, bad flow specification and ambiguous path.

#### Confirmation Message (ResvConf)

Reservation-request acknowledgment messages are sent as the result of the appearance of a reservation-confirmation object in a reservation-request message. This acknowledgment message contains a copy of the reservation confirmation. A reservation-request acknowledgment message is forwarded to the receiver hop by hop (to accommodate the hop-by-hop integrity-check mechanism).

Detailed on processing of these messages is explained in Chapter 6. Essentially to establish a LSP path across an ingress and egress interface we require five basic signaling messages, Path, Resv, PathErr, ResvErr, Resv ResvConf Message. Therefore we consider only these five signaling messages in our thesis.

The modules required for processing these messages are shown in Figure 2.3 and are explained below.

Figure 2.3 MPLS/RSVP-TE for Next Generation Routers [30]

**MPLS Controller.** With respect to the RSVP-TE process, the MPLS Controller is responsible for:

- Initiating, accepting, rejecting or closing an RSVP-TE session.

- Requesting label mappings and resource reservations from other LSRs by sending appropriate requests to the RSVP-TE process.

- Processing label-related and resource reservation-related notifications received from other

LSRs by the RSVP-TE process, and sending information back.

**RSVP-TE Processor.** It is responsible for processing RSVP-TE messages coming from both the local API (MPLS Controller) and the underlying IP stack. The RSVP-TE processor includes:

• The RSVP-TE Path Processor (PSB), which is responsible for the Path direction processing.

- The RSVP-TE Resv Processor (RSB), which is responsible for the Resv direction processing.

- The RSVP-TE Traffic Controller (TCSB), which is responsible for Traffic Control related operations, including:

- o Creating/modifying/deleting Traffic Control State blocks.

- o Summarizing reservations committed for different senders.

- Interacting (via the MPLS Controller) with the Traffic Control mechanisms implemented in the Layer 2 Interface module.

## **RSVP-TE Session Manager.** It is responsible for:

- Creating outgoing and incoming RSVP-TE sessions.

- Notifying the MPLS Controller about newly available RSVP-TE sessions.

- Removing RSVP-TE sessions that have no PSBs, RSBs, and TCSBs attached.

#### **RSVP-TE Encoder/Decoder.** It is responsible for:

- Encoding RSVP-TE requests generated by the MPLS Controller into RSVP-TE messages and passing them to the underlying IP stack.

- Decoding incoming RSVP-TE messages and passing appropriate notifications to the Session

Manager for soft-state management and to the MPLS Controller.

#### 2.3 Overview of RTM

The Routing Table Manager (RTM) [13] is not a routing protocol in itself, but rather a link between the routing protocols. It gathers information from different sources such as the static routes configured by the system user and the dynamic routes. Based on all the route information from different routing protocols, RTM module will determine the Forwarding Information Table (FIT) that will contain the overall best routes.

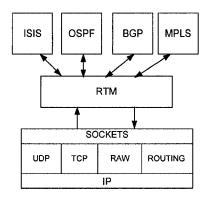

The main functionalities of RTM are to retrieve all configured static routes, to compute the overall best route for any known subnets or host destinations, and then to generate the FIT table used by the IP stack and the hardware components responsible for forwarding IP packets, as shown in Figure 2.4. It dynamically updates the IP stack with the latest revision of the FIT table, and keeps it up-to-date whenever changes occur. This is achieved through an interface called routing sockets [13].

The RTM module is also responsible for ensuring route redistribution from one routing protocol to another. In addition, it also filters route information being redistributed.

# The RTM also manages:

- Routing tables generated by underlying unicast and multicast protocols,

- Static routes,

- Routing tables on a per VPN basis,

- Best-effort and QoS based routing tables,

- Asynchronous notification to users about changes to the routing tables,

- Intra-domain and inter-domain next hop and explicit route resolution (for OSPF and BGP respectively) by looking up the routing tables,

- Support for LSP hierarchies (i.e., mapping from IP to MPLS, transit LSPs within MPLS domains, and mapping from MPLS to IP)

In general, the RTM can also be responsible for traffic engineering constraint-based path calculations. However, in a distributed architecture where routing and signaling protocols run entirely on the LCs, this task can be achieved by appropriate routing and signaling modules.

Figure 2.4 Inter-communication of RTM with Routing Protocols

In the next chapter we discuss the previous research conducted on MPLS/RSVP-TE centralized routers. Limitations of the centralized architecture have been discussed. It also discusses the advantages of the industrial next generation routers.

# Chapter 3

# 3 Literature Review

Previous research on router architectures spans over several research areas, such as classification/lookups, internal switch architectures, software modularization and packet forwarding extensions, resource management and QoS [4]. Many of these areas are of interest to our research on distributed router architectures, and a broad understanding of these areas is useful for the distribution of RSVP-TE protocol and the overall system design included in our work.

We have taken into consideration the research done in the chosen field to make a closer description of the state of the art in the areas that are most related to the topic of distributed router architectures and distributed RSVP-TE module. There is an explanation given about how the previous work in these areas is related to the proposed architecture.

In this chapter we describe the distributed routers modules and explain their basic characteristics. Industrial next generation high-speed distributed routers [39] like Juniper [29], Nexabit [42],

Cisco [38] and Avici [18], operating with packet forwarding rates on the order of gigabits or even terabits per second are also discussed.

The continuously growing need for new services and protocols also affects the control plane of routers. Adding new services to a router often is a complex task from the control plane point of view. The number of protocols that has to be supported by a router is already significant [33]. These protocols, together with other functions needed in a router, constitute large amounts of complex software. This may consequently result in high demands on the control processor. Thus, it is hard to add new functionality in the control plane and meanwhile maintain a high degree of reliability and efficient execution of the software. Our intention is to take this decentralization further and study how a router can be distributed for allowing physical separation of control and forwarding functions into multiple modules.

For example, in 2005, HyperChip Router [24] was introduced with a new core router model which may support a very large number of LCs and control card (e.g., 64,000) and provide a very high throughput up to 1280 Gbps. The software architecture for next generation routers should therefore be distributed and highly scalable.

#### 3.1 Distributed Software Architecture

When it comes to the overall system design of a distributed router, the architecture suggested within the IETF ForCES working group [34] will serve as a starting point. The ForCES architecture is defined in terms of exchange of information between control elements (CEs) and forwarding elements (FEs). A group of CEs and FEs together forms a network element (NE).

The ForCES protocol is used to associate the CEs and FEs. It updates the FEs with configuration information from the CEs, queries for information by the CEs or sends asynchronous event notifications to CEs. Using the ForCES protocol, the CEs may also configure the processing functions on the FEs [35] [36].

Control functions of a router have been redefined based on the ForCES architecture, in order to share the processing tasks between the CC and the LCs. In [27] authors present a Distributed Control Plane architecture where message processing, particularly HELLO Message processing, is handled by the LC. With this new approach failures can be detected faster and Shortest Path First (SPF) calculations can be run as frequently as required without affecting the load on the control plane processor.

The current ForCES architecture does not consider the general purpose CPU and memory on LCs which are available on the next generation routers. Moving some control functions to the LCs will lead to reprogramming the network processor (NP). This is costly and if there is an error in running the code of the control function may shutdown the forwarding function.

Second, distributing the MPLS/RSVP-TE routing protocol functions on to the LCs would increase the scalability of the system. Since the network processor on LCs is not able to host many control functions due to its specific architecture, using the general purpose CPU and memory available on the LCs can help to improve the processing performance of the next generation routers.

ForCES architecture has not currently been adopted by the industry due to it's architectural limitations. In contrast, industrial routers are a step ahead mainly with regards to the fact that they overcome the limitations posed by the ForCES architecture.

Based on a general distributed software framework, MPLS/LDP [26] is distributed on the line cards in order to fully exploit the hardware platforms of the next generation routers [25]. The proposed distributed MPLS/LDP architecture moves the signaling and table management to the line cards, with additional mechanisms for resiliency and task sharing at the line card level in order to increase the scalability of distributed router architecture. The main contribution for this research is presented in [45].

The next section describes the advancement in industrial routers with high-speed interfaces (e.g., 10 or 40 Gb/s) and large switching capacity (e.g., multipetabit) [2].

# 3.2 Industrial Next Generation Routers and Prototype

This section provides a survey of the terabit and gigabit capacity routers available in the market [44]. Comparative analysis of all the major products classifies them into various categories based on architecture design as well as performance. Current Next generation routers by leading vendors like Avici [18], Juniper [12], Nexabit [42] and Cisco [38] claim to support up to several OC-192 interfaces as well as multi-terabit switching capacity. Other prototypes like Hyperchip [24] and Tiny Tera [43] have also been introduced.

#### 3.2.1 Juniper Next Generation Router

Juniper's next-generation routing architecture provides the solid, reliable, high-performance foundation upon which today's real-time, critical networking applications can be delivered. In August 1998, Juniper networks began shipping the M-series Internet router. This was the first Internet- scale router built to offer uncompromising packet forwarding performance. All

M-series Internet router family are designed to meet demands of the new public network by delivering high reliability and scalability [28].

In April 2002, Juniper Networks began shipping the T640 Internet routers. The T640 delivers breakthrough OC-48/STM-16 and OC-192/STM-64 interface density in a multi-chassis capable system [28].

#### Architectural framework of M-series and T-series router:

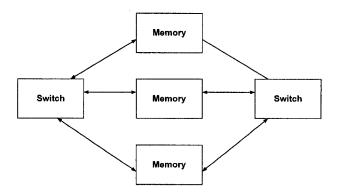

The M-series router architecture successfully provides the performance and control that carries need to support their transition from OC-12/STM-4 to OC-48/STM-16 [28]. Figure 3.1 illustrates the architecture of an M-series router; each input interface is logically connected to a switch which distributes the cells of a packet into a centralized shared memory system. The cells are written into memory once, read from memory once, and sent through a switch to the proper output interface for transmission to the network.

Figure 3.1 M-Series Router Architecture

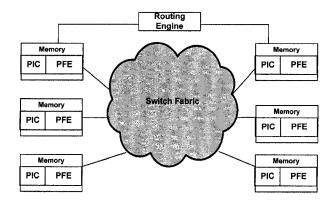

Figure 3.2 illustrates the architecture of a T-series router. A T-series router uses a distributed architecture with packet buffering at the ingress Packet Forwarding Engine (PFE) before the switch fabric as well as packet buffering at the egress PFE before the output port.

A single chassis or multi-chassis T-series system consist of four components PICs, PFEs, the switch fabric and one or more routing engine.

- **Physical Interface Card**: The PICs connect a T-series router to the network and perform both physical and link layer packet processing.

- Packet Forwarding Engine: Each PFE performs routing table lookups, and packet filtering, forwarding packets to the correct output interface and manages output queues.

- Switch Fabric: It provides connectivity between the PFEs.

- **Routing Engine**: The routing engine executes the JUNOS software and creates the routing tables which are downloaded to each PFE.

Figure 3.2 T-Series Router Entities

T-series router deliver industry-leading scalability, they provide the required scalability while maintaining feature and software continuity across all router platforms. T640 Internet Routing Node supports 32 OC-192c/STM-64 ports in a half-rack chassis, and offers eight 40 gigabits-persecond (Gbps) slots thus satisfying ever-increasing traffic in the networks.

#### 3.2.2 Nexabit NX64000 Router

The NX64000 innovative switch fabric delivers 6.4 Tbps switch capacity per chassis. The NX64000 supports up to 192 OC-3, 96 OC-12, 64 OC-48 and 16 OC-192 lines [42]. The NX64000 allows Service Providers to even scale to higher speed like OC-768 and OC-3072 and port densities can also be increased further by interconnecting multiple chassis [41].

The NX64000 implements a distributed programmable hardware forwarding engine on each line-card. This approach facilitates wire-speed route lookup for full, 32-bit network prefixes-even at OC-192 rates. The distributed model enables support for 128 independent forwarding tables on each line-card. Each forwarding engine is capable of storing over one million entries.

The industry-leading routers deliver a powerful solution for carriers to achieve substantial technology breakthroughs in packet forwarding performance, bandwidth density, IP service delivery and system reliability. Not only do the next generation routers deliver industry-leading scalability, they provide the required scalability while still maintaining feature and software across all router platform.

## 3.2.3 Cisco Next Generation Router

The Cisco® XR 12000 Series routers accelerate the service provider evolution toward IP Next-Generation Networks [38]. Cisco XR 12000 Series provides intelligent routing solutions that scale from 2.5 to 10-Gbps capacity per slot, enabling next-generation IP/Multiprotocol Label Switching (MPLS) networks [37].

## **Cisco XR 12000 Architecture Components**

The Cisco XR 12000 architecture consists of four basic building blocks:

- Cisco IOS XR Software Cisco IOS XR Software takes full advantage of the distributed intelligence and hardware capacities on LCs and Cisco XR 12000 and 12000 Series Performance Route Processor-2 (PRP-2) technology on the Cisco XR 12000 Router.

- Cisco XR 12000 multi- gigabit switch fabric The switch fabric is the high-speed interconnect between all router components, including the route processor and the Cisco intelligent programmable interface processors (Cisco ISE LCs).

- Cisco XR 12000 intelligent programmable interface processors The Cisco intelligent

programmable interface processors (Cisco LCs) terminate the physical interface and provide

the forwarding decisions, payload processing, payload accounting, policy management, and

security.

- Cisco XR 12000 Series Control Plane Route Processor The Cisco XR 12000 Series

Control Plane Processor provides chassis management, route protocol processing, and external management.

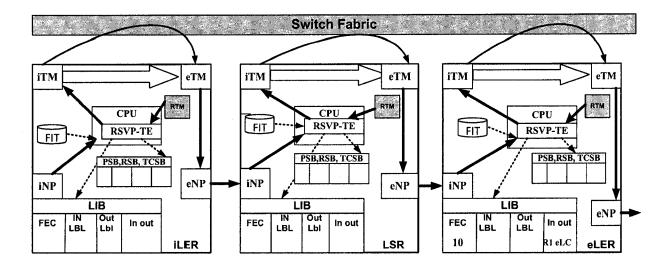

## 3.2.4 Hyperchip Prototype

The Hyperchip PBR-1280 Core IP System solves the problems of legacy routers to create a simple, low-cost IP core that provides the bandwidth quality needed not only for advanced IP services, but for traditional Voice and Frame Relay services as well. The PBR-1280 core IP system is fully compatible with legacy routers, allowing carriers to evolve their networks to reduce costs while preserving existing network architectures [19] [24].

PBR-1280 consists of a CC and a set of LCs connected via a switch fabric as shown in Figure 3.3. LCs contain very high speed interfaces (i.e., 10Gbps).

- One controller card that hosts all routing protocols. There can be an additional CC used for backup and redundancy.

- A given number of LCs which perform:

- o IP forwarding and/or MPLS label switching at hardware level, and

- o IP forwarding at software level for exceptional packets (e.g., control packets).

In this architecture there is a forwarding information table (FIT) on each LC. The RTM located on the CC receives the best routes learnt by routing protocols. Overall best routes are selected and then recorded to the FIT of the IP stack. The FIT on each LC is downloaded from the FIT on the CC via the switch fabric.

Figure 3.3 Hyperchip Architecture

# 3.2.5 Tiny Tera Prototype

Tiny Tera is a Stanford University research project, the goal of which is to design a small, 1 Tbps packet switch using normal CMOS technology [43]. The system is suited for an ATM switch or Internet core router. The current version has 32 ports each operating at a 10 Gbps (Sonet OC-192 rate) speed.

Figure 3.4 Architecture of Tiny Tera

In the next chapter we describe the distributed architecture for the Routing Table Manager (RTM) which is essentially one of the most important component of a router.

# Chapter 4

# 4 Centralized and Distributed Architectures for RTM with RSVP-TE

This chapter gives a brief overview of the Routing Table Manager. The first requirement for a RTM distributed architecture came from RSVP-TE. RSVP-TE needs also to be distributed on LCs in order to increase the scalability and resiliency and to reduce the load of the CC. If RSVP-TE needs to compute the paths over network based on user-specific requirements, such as QoS. This is done with the help of routing protocols, like OSPF or BGP, through the RTM. Therefore, a distributed architecture for RTM is required to serve the RSVP-TE distributed architecture. In addition, the distributed architectures of RTMs may save the CPU resource and memory on the CC which are used to compute the best routes. Section 4.1 describes the centralized architecture for RTM. Section 4.2 describes a brief overview of partially distributed RSVP-TE with centralized RTM and limitation of this architecture. Section4.3 describes the distributed architecture for RTM with distributed RSVP-TE.

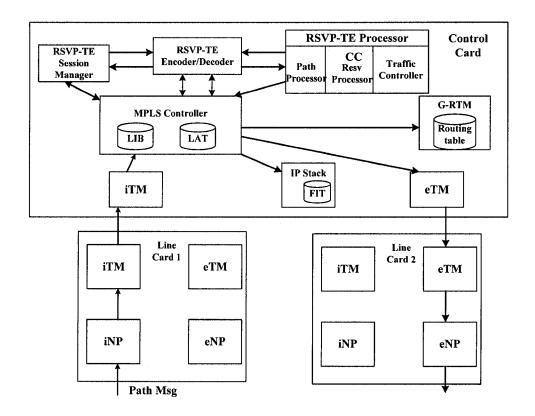

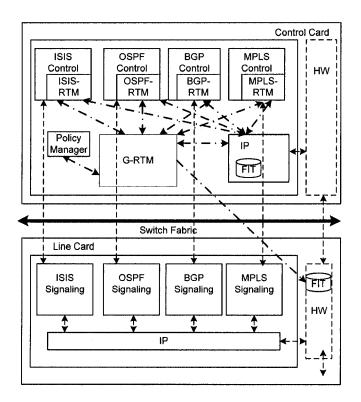

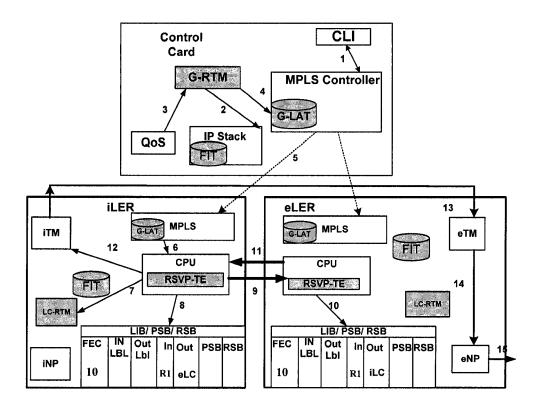

#### 4.1 Centralized RTM Architecture

The current RTM architecture [25] used for next generation routers, consists of a Global RTM (G-RTM) module that manages the routing table for the whole system and several smaller RTMs, each devoted to a given protocol and therefore denoted by IGP-RTM or EGP-RTM, i.e.,

for each protocol. Each IGP/EGP-RTM is responsible for managing routes computed by a specific routing protocol (i.e. OSPF, BGP, MPLS), as shown in Figure 4.1. The G-RTM is a stand-alone process located on any CC in the system. It interfaces only with the IGP/EGP-RTMs and IP. It receives all the routes learned by the different IGP/EGP-RTMs and performs the selection of the overall best routes. Then it updates IP and the IGP/EGP-RTMs and finally performs route redistribution between protocols. The G-RTM also manages the configuration of static routes configured by users (through an external routing policy module) or traffic engineering based routes. The interface configuration and up/down status are handled by the G-RTM and broadcast to the routing protocol modules through the IGP/EGP-RTMs.

Each IGP/EGP-RTM is physically linked with a given protocol and gives the impressions to the protocol that it is a complete RTM. It contains all best routes of the protocol and the overall best routes of the system computed by the G-RTM used to update the protocol. It offers the same API, and keeps all pertinent information to the protocol for fast access and sustained performance.

Such architecture allows the routing protocols to have a flexible access to the routing tables managed by the G-RTM without being queued. The architecture does not require much modification on routing protocol modules and G-RTM regarding the traditional architecture. Each IGP/EGP RTM manages only a subset of the routing table that is related to a specific routing protocol. When a routing protocol receives a route update notification message through the corresponding signaling component on a LC, the control component located on the CC recomputes the best routes and updates its local IGP/EGP-RTM. The G-RTM is also notified through the link with the IGP/EGP-RTM. The overall best routes of the system are selected

among those provided by different protocols. The route update is advertised by the G-RTM to other routing protocols in order to notify the neighbors. Finally, the overall best routes are updated to the FIT on the LCs through the connection with the G-RTM.

Figure 4.1 Current RTM Architecture: Distributed on Protocol Basis

The architecture does not reduce the number of messages sent to the CC, in other words, the congestion still remains. However, the resiliency and scalability are improved at the CC level because the routing protocol can still use the IGP/EGP-RTMs when the G-RTM temporary fails. The lookup operation is faster because each IGP/EGP-RTM contains only a portion of the global routing table. The main advantage of this scheme is the simplicity since not much modification is needed. Therefore, it can be suitable for the short-term migration from the current to the next

generation routers, where only the CC needs to be upgraded. However, there are some critical issues:

- Although the IGP/EGP-RTMs are distributed on a per protocol basis, they are basically independent processes running on the same CC. This leads to quite heavy resource consumption and to some overloading of the CC as the number of routes increases.

- Additional computing and memory resource on the LCs are not efficiently exploited to run the best route computations or to perform the route management tasks.

- The routing protocols will be distributed on the LCs in order to improve the scalability and fully exploit the available memory and CPU resource of the LCs [25], the IGP/EGP-RTM modules need also to be migrated to the LCs.

- It is not very efficient to perform the FIT update operations at the CC level by G-RTM as the FITs are hosted by the LCs.

In order to deal with these issues, in the following sections, new architectures for RTM will be proposed. We aim at a full distribution of RTMs on LCs where each LC has a RTM instance being responsible for the local routing protocols.

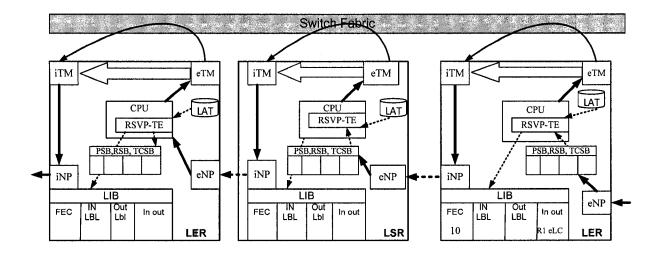

# 4.2 Partially Distributed RSVP-TE Architecture with Centralized RTM

Routing protocols, such as OSPF [6], IS-IS [7] or BGP [5] require path computations in order to produce best routes. The RSVP-TE protocol presented in the previous chapter is a signaling protocol for MPLS networks that performs simply the message exchanges between LSRs to establish the LSPs. RSVP-TE can be used alternatively as another signaling protocol for MPLS network that provides additional traffic engineering features. In traffic engineering we are

concerned with establishing LSPs that do not necessarily follow the IP best routes from the ingress to the egress computed by normal routing protocols like OSPF or IS-IS. This allows data to be sent by alternative routes to reduce bottle-necks and congestion, to increase the utilization of network-resources, and to avoid planned faults. The Resource Reservation Protocol (RSVP) was originally designed as a signaling for the Integrated Services (IntServ) model, wherein a host requests a specific QoS from the network for a particular flow. RSVP-TE is an extension of RSVP that has been adapted to support the traffic engineering within the MPLS network.

Signaling protocols run on LCs and can be used alternatively by the MPLS signaling module to establish the LSPs with the peer routers. Their concurrent access to the LIB table is controlled to avoid the data inconsistency. The labels provided by the L-LAT are given to RSVP-TE and LDP [26] according to their requirements. In Figure 4.2, there is only one RTM running on the CC that contains all the routes of the system and manages the interfaces of the routing protocols. Therefore, all path computation requests from RSVP-TE must go to the CC. The distributed MPLS architecture is therefore not deployed efficiently. In addition, the CC can be overloaded by the large number of requests when the number of LCs increases.

This issue can be dealt with a distributed RTM, where each LC has a RTM instance. The distributed RTM on each LC may contain the available routes of the routers, or all the routes out of the best routes that are directly related to the local LC. The RSVP-TE path computation request may therefore address the local RTM running on the same LC instead of the CC. Based on its routing table, the local RTM is able to call appropriate routing protocol to compute the connections to next-hop routes which satisfy user QoS requirements.

With a distributed RTM architecture, a RSVP-TE process will be able to consult the local routing database in order to obtain routes. Routing protocols determine where packets get forwarded; RSVP-TE is only concerned with the QoS of those forwarded packets. RSVP-TE sessions are launched according to user requests from application level. A host uses the RSVP-TE protocol to request specific qualities of services from a network for particular application data streams or flows. Routers use RSVP-TE to deliver QoS requests to all nodes along the paths of the flows and to establish and maintain a state to provide the requested services. RSVP-TE requests generally result in resources being reserved at each node in the data path.

Figure 4.2 Distributed MPLS Architecture with a Centralized RTM

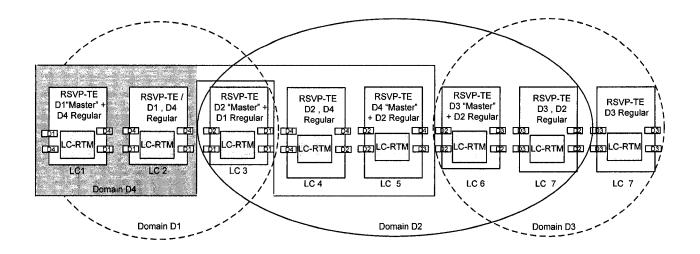

## 4.3 Fully Distributed RSVP-TE Architecture with Distributed RTM

The requirement of distributing RTM on line cards arise from the requirements of distributing signaling protocols such as LDP [26] and RSVP-TE. This section investigates the ability to distribute RTM on to the line cards [45].

A highly scalable router connects all ports on each LC to only one routing domain. In this context, proposed distributed architecture for RTM maintains a "master" for each cluster of LCs and each cluster is called a domain as shown in Figure 4.3. For example, domain D4 consists of line cards LC1, LC2, LC4 and LC5 and the master line card for this domain is LC5. The master LC instead performs the overall selection and management of the best routes from all routing protocols in its domain. This allows the master to be able to perform constrained shortest path first (CSPF) calculation on user-specific parameters (e.g., administrative weights) according to special requests (e.g., from RSVP). CSPF computation request (i.e., sent by a RSVP-TE module) from any LC in a domain will be forwarded to the master LC of that domain. The master LC-RTM performs the CSPF computation based on its database and on the IGP topology of the domain.

In this scheme, routes are managed at the LC level by LC-RTM process running on each LC. The LC-RTM handles the overall best routes of the domain supplied by the master. If a LC is assigned as master for a domain, its LC-RTM contains all available routes of the domain. The FIT on each LC is updated by the local LC-RTM. The LC-RTM of each LC has interfaces with local routing protocols modules so that route notifications can be sent from a given protocol to another one in order to advertise neighbors.

Figure 4.3 Distribution of LC-RTMs

# **Advantages**

The main advantage of distributing RTM on the LC is that route information is handled on a master LC for each domain. Route information is available for RSVP-TE protocols without having to go up to G-RTM. In this case, CSPF computation is conducted at the level of the master LC.

## **Disadvantages**

Large memory resource is required at the master LC in order to contain all available routes in the domain. In addition, the CSPF computation for every LSP in the domain requires message exchanges with the master: this result in an increase of the traffic among the LCs associated with the same domain.

# 4.4 Summary