# Abstract Property Verifier based on Multiway Decision Graphs

# Kamran Hussain

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science (Electrical & Computer Engineering)

at

Concordia University Montréal, Québec, Canada

September 2007

© Kamran Hussain, 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-40883-4 Our file Notre référence ISBN: 978-0-494-40883-4

### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### ABSTRACT

Abstract Property Verifier based on Multiway Decision Graphs

#### Kamran Hussain

Symbolic model-checking tools encounter state-explosion problem when verifying designs with large data paths. Multiway Decision Graph (MDG) model-checker uses abstract data representation and applies abstract operations to address the state explosion problem. The MDG verification tool, also known as Abstract Verifier, takes as input the specification (written as properties) and the description of the design, and then proves or disproves if the design satisfies these properties. The original specification language of the Abstract Verifier was called  $L_{mdg}$  that provides temporal operators and abstract data types to formalize properties. Meanwhile, the Property Specification Language (PSL) has changed the verification world by introducing very rich temporal operators but without abstract data types. In this thesis, we propose a new specification language called Abstract Property Language (APL), for the MDG model-checker. This language replaces the  $L_{mdg}$  specification language by introducing new operators borrowed from PSL to improve its expressiveness. We provide the formal definition of this language in BackusNaur form (BNF) and provide its formal semantics based on the computational model of the Abstract Verifier. APL is associated with a front-end translator that accepts APL specifications and builds verification-ready models to be handled directly inside the MDG model-checker. Finally, we have validated our APL language and the translator tool on the verification of several test benches including Look-Aside Interface (LA-1) design.

$To\ My\ Father\ -\ Tasadduq\ Hussain$

### ACKNOWLEDGEMENTS

First of all, I would like to thank the almighty God for giving me all the blessings throughout my life and for the opportunity to make this thesis possible.

It gives me great pleasure to thank all those who have helped me in my research work. The first person I would like to sincerely thank is my supervisor, Dr. Otmane Ait-Mohamed. Without his guidance, his expert advice, his support and continual encouragements, this thesis would not have been possible. I express my heartfelt gratitude to him. I sincerely thank Dr. Sofiene Tahar, who along with my supervisor have created one of the best research groups in this field. To all my fellow researchers in Hardware Verification Group (HVG) at Concordia University, I thank you for your friendship, your thoughtful discussions and productive feedbacks. Most importantly, I thank you all, the entire HVG family, for standing next to me when my father passed away. Without your encouragements and support, I would not have been able to continue my research work.

Last but not least, I thank my family and relatives, here and overseas, for their constant moral support and their prayers. Your support was invaluable in completing this thesis.

# TABLE OF CONTENTS

| LI | ST O | F TAB  | LES                          | ix  |

|----|------|--------|------------------------------|-----|

| LI | ST O | F FIG  | URES                         | х   |

| LI | ST O | F ACR  | ONYMS                        | xii |

| 1  | Intr | roduct | ion                          | 1   |

|    | 1.1  | Thesis | S Contribution               | 5   |

|    | 1.2  | Thesis | S Outline                    | 7   |

|    | 1.3  | Relate | ed Work                      | 8   |

| 2  | Bac  | kgrou  | nd                           | 10  |

|    | 2.1  | Temp   | oral Logic and Specification | 10  |

|    |      | 2.1.1  | Linear Time Logic            | 11  |

|    |      | 2.1.2  | Computation Tree Logic       | 13  |

|    |      | 2.1.3  | Full Branching-Time Logic    | 14  |

|    |      | 2.1.4  | Categories of specification  | 15  |

|    | 2.2  | Multi  |                              | 15  |

|    |      | 2.2.1  | Abstract State Machine       | 17  |

|    |      | 2.2.2  | Structure of MDG             | 17  |

|    |      | 2.2.3  | Verification Algorithms      | 19  |

|    | 2.3  | Abstra | act Verifier                 | 20  |

|    |      | 2.3.1  |                              | 21  |

|    |      | 2.3.2  |                              | 29  |

|    |      | 2.3.3  | Model-Checking in MDG        | 31  |

|    | 2.4  | Const  | ruction of Translators       | 33  |

|    |      | 2.4.1  |                              | 34  |

|    |      | 2.4.2  |                              | 35  |

|    |      | 2 4 3  |                              | 36  |

|   |     | 2.4.4                | Code Generator                          | 36 |

|---|-----|----------------------|-----------------------------------------|----|

| 3 | Lar | iguage               | Description                             | 38 |

|   | 3.1 | PSL a                | and its subset in APL                   | 39 |

|   |     | 3.1.1                | Boolean Layer                           | 39 |

|   |     | 3.1.2                | Temporal Layer                          | 40 |

|   |     | 3.1.3                | Verification Layer                      | 43 |

|   |     | 3.1.4                | Modeling Layer                          | 44 |

|   | 3.2 | $L_{mdg}$ $\epsilon$ | and its subset in APL                   | 44 |

|   | 3.3 | Abstra               | act Property Language(APL)              | 47 |

|   |     | 3.3.1                | Syntax of Abstract Property Language    | 47 |

|   |     | 3.3.2                | Semantics of Abstract Property Language | 49 |

|   |     | 3.3.3                | APL Language Restrictions               | 51 |

| 4 | Ger | neratin              | g Composite Model                       | 53 |

|   | 4.1 | Tool S               | Specification                           | 54 |

|   |     | 4.1.1                | Platform and interface                  | 56 |

|   |     | 4.1.2                | Output filenames                        | 56 |

|   |     | 4.1.3                | Processing files                        | 57 |

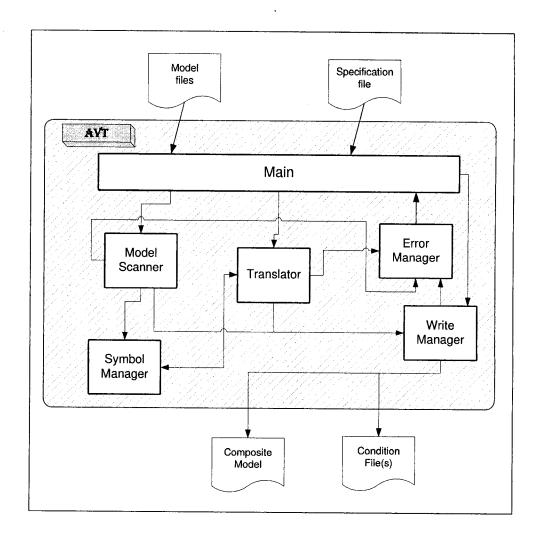

|   | 4.2 | AVT A                | Architecture                            | 57 |

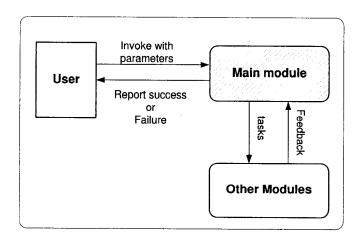

|   |     | 4.2.1                | Main Module                             | 59 |

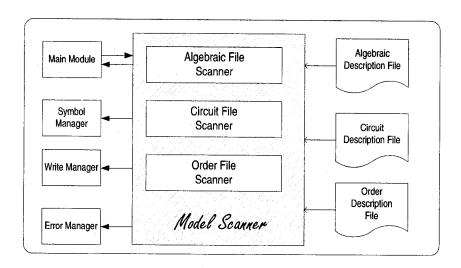

|   |     | 4.2.2                | Model Scanner                           | 60 |

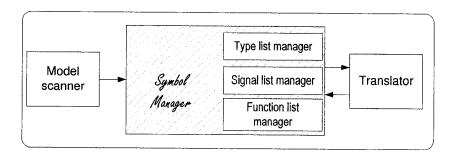

|   |     | 4.2.3                | Symbol Manager                          | 62 |

|   |     | 4.2.4                | Translator Module                       | 65 |

|   |     | 4.2.5                | Write Manager                           | 65 |

|   |     | 4.2.6                | Error Manager                           | 66 |

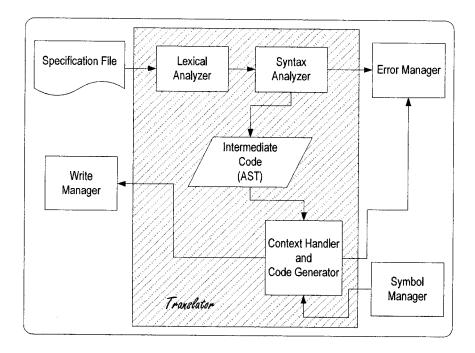

|   | 4.3 | Transl               | ator                                    | 67 |

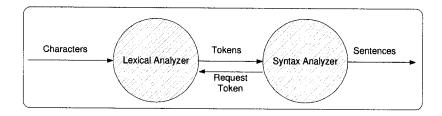

|   |     | 4.3.1                | Lexical Analyzer                        | 68 |

|   |     | 432                  | Syntax Analyzer                         | 71 |

|    |       | 4.3.3  | Annotated AST Generation:                      |    | 74 |

|----|-------|--------|------------------------------------------------|----|----|

|    |       | 4.3.4  | Context Handling and Code Generation           | 8  | 80 |

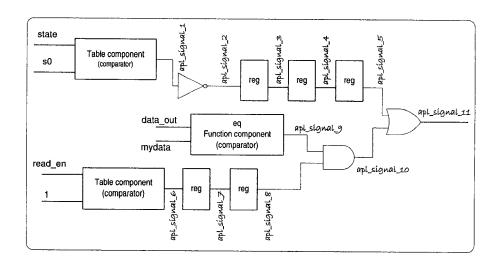

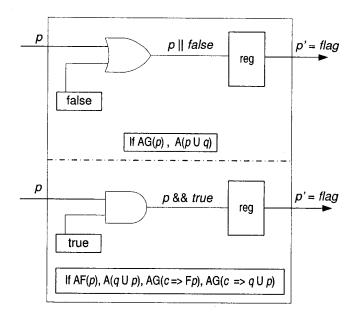

|    |       | 4.3.5  | Flag Circuit Generation                        | ;  | 86 |

| 5  | Exp   | erime  | ntal Results                                   | 8  | 39 |

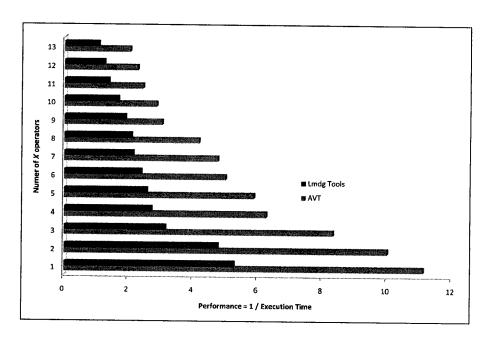

|    | 5.1   | Perfor | mance Comparison                               | 8  | 89 |

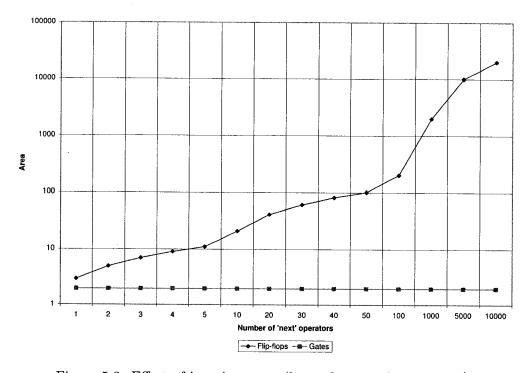

|    | 5.2   | Area l | Evaluation of the Generated Circuit            | 9  | 92 |

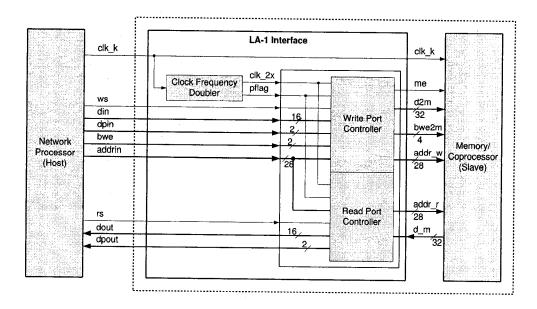

|    | 5.3   | Applie | cation: Verification of the LA-1 Interface     | !  | 94 |

|    |       | 5.3.1  | Specification                                  | !  | 96 |

|    |       | 5.3.2  | MDG Model-checking Results                     | :  | 96 |

| 6  | Con   | clusio | n and Future Work                              | ę  | 98 |

| A  |       |        |                                                | 10 | )1 |

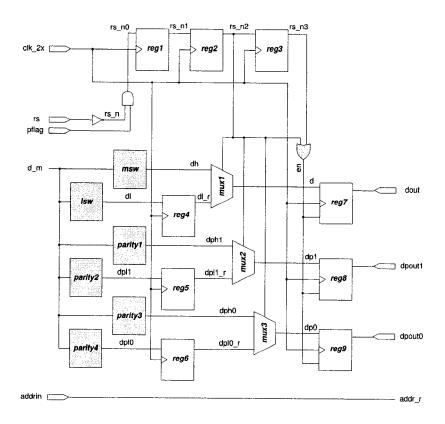

|    | A.1   | Read-  | -port of Look-Aside Interface in MDG-HDL       | 10 | )1 |

|    |       | A.1.1  | Algebraic Description                          | 10 | )1 |

|    |       | A.1.2  | Circuit Description                            | 10 | )2 |

|    |       | A.1.3  | Order Description                              | 10 | )4 |

|    | A.2   | Genera | ated monitor circuit for LA-1 in MDG-HDL       | 10 | )5 |

|    |       | A.2.1  | Example Specification                          | 10 | )5 |

|    |       | A.2.2  | Monitor Circuit in Circuit Description File    | 10 | )6 |

|    | A.3   | Modifi | ied Order Description File                     | 10 | )9 |

|    | A.4   | Modifi | ied Algebraic Specification File               | 13 | 11 |

|    | A.5   | Gener  | rated Condition file for the MDG model-checker | 1  | l1 |

| p; | hlico | ranhy  |                                                | 11 | 9  |

# LIST OF TABLES

| 1.1 | Raising the abstraction level                      | 4  |

|-----|----------------------------------------------------|----|

| 3.1 | Logical Operators considered for APL               | 40 |

| 3.2 | Example property violating simple subset rules     | 41 |

| 3.3 | LTL operators in PSL                               | 41 |

| 3.4 | next operators considered for APL                  | 42 |

| 3.5 | SERE operators considered for APL                  | 43 |

| 3.6 | Operator Synonyms                                  | 46 |

| 3.7 | $L_{mdg}$ and APL Lexical Rules                    | 47 |

| 3.8 | Property templates                                 | 51 |

| 3.9 | APL restrictions                                   | 52 |

| 4.1 | Condition file naming strategy.                    | 56 |

| 4.2 | Data collected from algebraic file                 | 61 |

| 4.3 | Flag output according to property templates        | 66 |

| 4.4 | Token List                                         | 70 |

| 4.5 | Boolean expression mapping                         | 77 |

| 4.6 | Temporal expression mapping                        | 78 |

| 5.1 | Performance of AVT compared to $L_{mdg}$ -Tools    | 90 |

| 5.2 | Area Evaluation.                                   | 93 |

| 5.3 | Read-port specification in APL                     | 97 |

| 5.4 | Verification results for Read-port specifications. | 97 |

# LIST OF FIGURES

| 1.1  | Model-checking method                                         |

|------|---------------------------------------------------------------|

| 1.2  | $L_{mdg}$ Tools: front-end of the Abstract Verifier           |

| 1.3  | Proposed front-end of MDG methodology                         |

| 2.1  | Model Structure                                               |

| 2.2  | LTL formulae and time                                         |

| 2.3  | CTL formulae and time                                         |

| 2.4  | BDDs to MDGs                                                  |

| 2.5  | MDG Verification                                              |

| 2.6  | OR gate in MDG and its corresponding MDG-HDL description $28$ |

| 2.7  | MDG-HDL description of a Comparator                           |

| 2.8  | An abstract counter                                           |

| 2.9  | Model-Checking in MDG                                         |

| 2.10 | Basic structure of a compiler                                 |

| 2.11 | AST for a+b+c                                                 |

| 2.12 | AST to target code                                            |

| 3.1  | MDG Model-Checking Algorithms                                 |

| 4.1  | Composite model with flag output                              |

| 4.2  | Top view of the generator tool                                |

| 4.3  | Structure of AVT                                              |

| 4.4  | Main Module                                                   |

| 4.5  | Model scanner                                                 |

| 4.6  | Symbol Manager                                                |

| 4.7  | Top view of the Translator module                             |

| 4.8  | Translator                                                    |

| 4.9  | Syntax flow                                            | 68 |

|------|--------------------------------------------------------|----|

| 4.10 | Syntax Tree                                            | 71 |

| 4.11 | AST for function expressions                           | 76 |

| 4.12 | AST for compare expressions                            | 77 |

| 4.13 | AST for boolean expressions                            | 78 |

| 4.14 | AST for temporal expression examples                   | 79 |

| 4.15 | AST for LET expression                                 | 80 |

| 4.16 | Annotated AST                                          | 82 |

| 4.17 | Circuit representing property                          | 86 |

| 4.18 | Completion of Monitor Circuit                          | 87 |

| 4.19 | The Flag Circuit                                       | 87 |

| 5.1  | Performance Comparison                                 | 91 |

| 5.2  | Effect of 'next' on area (logarithmic scale on Y-axis) | 92 |

| 5.3  | Look-Aside Interface (LA1)                             | 95 |

| 5 4  | Read-port representation in MDC-HDL                    | 06 |

## LIST OF ACRONYMS

ABV Assertion-Based Verification

AP Atomic Proposition

APL Abstract Property Language

ASM Abstract State Machine

BDD Binary Decision Diagram

BNF Backus-Naur Form

CFG Context-Free Grammar

CTL Computation Tree Logic

DAG Directed Acyclic Graph

DF Directed Formula

DFA Deterministic Finite Automata

FL Foundation Language

FPGA Field-Programmable Gate Array

FSM Finite State Machine

LA-1 Look-Aside Interface

LTL Linear Temporal Logic

MDG Multiway Decision Graph

NFA Non-deterministic Finite Automata

OBE Optional Branching Extension

PSL Property Specification Language

RE Regular Expression

RTL Register Transfer Level

SERE Sequence Extended Regular Expression

SV SystemVerilog

SVA System Verilog Assertion

YACC Yet another compiler-compiler

# Chapter 1

# Introduction

A major challenge in digital system design is ensuring correctness of the design at the earliest phase possible. Encountering design errors in manufactured products have lofty economic consequences. The impact is more severe in digital designs of critical applications. Given the number of devices and number of gates per IC chip growing radically, verification engineers must find a way to provide adequate verification coverage without drastic increase in verification time and cost.

Simulation-based methods are standard practice in the industrial community for hardware verification. However, they cannot offer complete coverage because the number of test cases grows significantly with the complexity of the design. Recently, formal verification methods have become an important complement because of their ability to find errors early in the design cycles through exhaustive exploration of all possible behavior.

In formal verification, the goal is to mathematically establish that the *system* under verification satisfies its specification. There are three main aspects when using formal verification techniques: the implementation of the system, its corresponding specification (or reference model) and the relationship between the implementation and the specification (or reference model). Among the three, it is the relationship that needs to be ascertained. The system representation can be at any level of

abstraction. Its specification, refers to the properties, can be given by behavioral descriptions, abstract structural description, temporal logic formulae, and so forth. Formal verification methods are usually categorized into three major techniques: theorem proving, equivalence checking and model-checking.

Theorem proving is generally an interactive approach where the implementation and the specification are stated in formal logic. The correctness is obtained by mathematically proving their relationship, equivalence or implication. The logic is characterized by a proof system that defines a set of axioms and a set of inference rules. Inference rules are applied until the desired theorem is proven. Theorem proving requires expertise and significant efforts on the part of the user in developing specifications of each component and in guiding the theorem prover through a large set of lemmas. As a result, this technique has limited practice in the industry, and it is mainly used for verifying critical parts of systems. The most popular theorem proving tools are Boyer-Moore Theorem Prover Nqthm [32], the Cambridge HOL system [27] and PVS [33].

Equivalence checking is a method to prove that two design representations of the same system are functionally equivalent. The two representations are usually at two different levels of abstraction. One common scenario of equivalence checking can be comparing a circuit's gate-netlist description with its RTL description. It is usually divided into two classes: Combinational equivalence checking and Sequential equivalence checking. In combinational equivalence checking, the circuits to be compared are converted into canonical representations of boolean functions, usually BDDs [14] which are then structurally compared to conclude the relationship. For example, MDG [1], an academic tool, and Synopsys Formality [3], a commercial tool, offer combination equivalence checking. On the other hand, in sequential equivalence checking, the two designs are represented using state-encoding. The equivalence is then proven by building the product finite state machine and checking whether the

output is invariant for any initial states of the product machine. It can verify equivalence between RTL and behavioral models because it only considers the behaviors of the models. However, due to state-space limitations, it cannot check large designs. MDG and VIS [4] are examples of tools that can perform sequential equivalence checking.

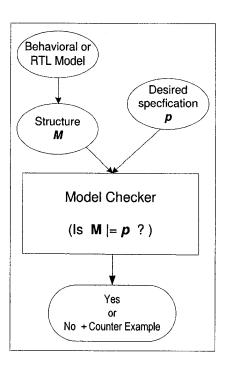

Figure 1.1: Model-checking method

Model-checking techniques are attractive verification method because of their high automation. Like equivalence checking, model-checking is historically a decision graph based method. It uses state space algorithms on finite-state models to check if the desired specification is satisfied. Specifications are expressed in a propositional temporal logic. An algorithm is employed to automatically explore the state-space and ascertain if the specification is verified by the state-transition graph. A top view of this method is depicted in Figure 1.1. Depending on success or failure, a model-checking tool gives the answer yes or no respectively. When the verification

fails, a counter example is provided that helps the user in tracing the source of the error. This counter example is also known as the *failure trace*.

Model-checking algorithms have been explored since early eighties and significant results have been published [26]. The introduction of Bryant's Binary Decision Diagrams (BDD's) [14] piloted a breakthrough in the size of a transition system that can be verified. Since then, a number of researchers have explored BDD-based symbolic technique and have published results [28] [30] [31]. The drawback of this method is that they usually suffer from the state-explosion problem when verifying designs with large data paths.

A new class of decision graph, called Multiway Decision Graphs (MDGs), was proposed as a solution to the state-space explosion problem by Cerny et al. in 1997 [15]. In MDG based model-checking approach, data signals are denoted by abstract variables, and data operators are represented by un-interpreted function symbols. As a result, a verification based on abstract-implicit-state-enumeration can be carried out independently of data path width, substantially lessening the state explosion problem. Table 1.1 shows the abstraction level of MDG compared to traditional methods. A model-checking methodology is typically comprised of three major parts: a specification language, a system modeling language and a set of algorithms to perform model-checking. In existing MDG methodology, these are  $L_{mdg}$  [37], MDG-HDL [38] and MDG model-checker [15] [35] respectively.

Table 1.1: Raising the abstraction level

| Conventional method             | Multiway Decision Graph                    |

|---------------------------------|--------------------------------------------|

| ROBDD [14]                      | MDG                                        |

| Finite State Machine            | Abstract State Machine                     |

| Implicit state enumeration [28] | Abstract state implicit enumeration of ASM |

| CTL based model-checking        | Based on first-order abstract CTL*         |

In our work, we explore  $L_{mdg}$  property specification language that facilitates

the formal representation of desired specification in MDG based model-checking methodology. We also investigate how the written specifications are processed in MDG based model-checking.

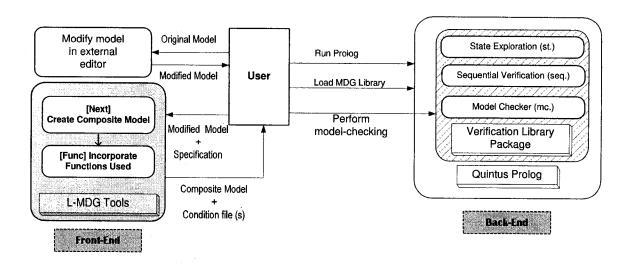

## 1.1 Thesis Contribution

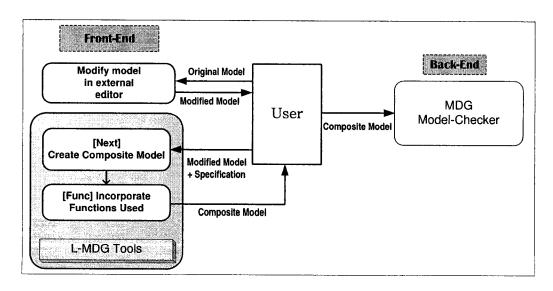

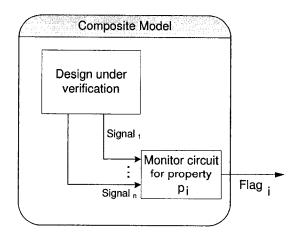

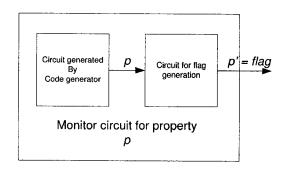

The existing MDG model-checking process requires two sets of tools: a back-end model-checker and a front-end comprised of  $L_{mdg}$  tools [37]. The front-end is a set of tools that provides a mechanism to process the desired specification written in terms of properties. The existing  $L_{mdg}$  specification language, used as specification language in MDG model-checking to write properties, is based on the first-order abstract CTL\* class of temporal logic [36]. In order to create the verification-ready model, the property formulae are processed to construct additional circuitry that is added to the original model. The result is a composite model (Figure 1.2) in MDG-HDL. The composite model is fed to the back-end model-checker to formally verify if the specification holds.

Figure 1.2:  $L_{mdg}$  Tools: front-end of the Abstract Verifier

After investigating the language description of  $L_{mdg}$  and the implementation of its tools, we have concluded that both can be improved without affecting the model-checking algorithms offered by the MDG model-checker [35]. The apparent issues are following:

- The front-end parsing process requires modifying the syntax of original model in an external editor. This is due to lexical restrictions in  $L_{mdg}$  language.

- An extra file specifying all the functions used in specification is needed. This is parsed by the *Func* tool (Figure 1.2).

- Concrete functions (cross-terms) used in specification cannot be handled [12].

- More than one tool is needed to build the composite model.

- The generated composite model needs to be manually fixed (edited) in order to comply with the rules of MDG-HDL [12].

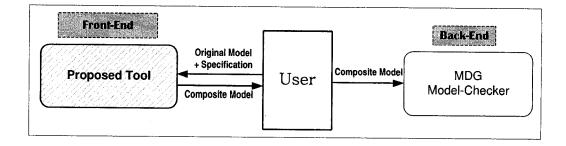

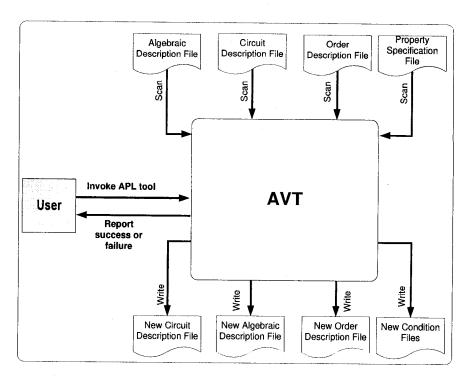

Figure 1.3: Proposed front-end of MDG methodology

Our goal is to develop a new front-end (Figure 1.3), where a single tool will accept the original model with its specifications written in an improved language and will efficiently create the verification-ready composite model. Thus, the proposed improvements are:

• Remove  $L_{mdg}$  language restrictions, thereby creating a new language.

- Support expressions of  $L_{mdg}$  but use appropriate standardized operators from PSL [6]. Also add PSL expressions to improve expressive-power.

- Develop a single tool (Figure 1.3) that can process specifications and generate respective composite models.

- Improve performance of the front-end specification processing.

# 1.2 Thesis Outline

This thesis is made up of six chapters. It is organized as follows:

- In Chapter 2, we give brief background information on topics that are required to comprehend materials presented in Chapters 3 and 4.

- In Chapter 3, the description of Abstract Property Language (APL) is provided along with its syntax and semantics. Here, we also present the subsets of L<sub>mdg</sub> [36] and PSL [6] considered in constructing APL.

- In Chapter 4, the requirement, the specification and the design of the proposed tool (Figure 1.3) are presented in details. Major part of the tool is a translator that translates APL specification to MDG-HDL. We provide the lexical and syntactic rules used in this translator as regular expressions and in BNF respectively.

- In Chapter 5, experimental results are presented. It includes performance analysis and analysis of generated circuit area. It also presents model-checking results of the Read-port of Look-Aside Interface [20].

- Finally we conclude in Chapter 6 with a brief discussion on future work.

### 1.3 Related Work

As related work to ours, we cite the work of Eric Gascard [16]. He presented a process of generating deterministic finite automata from a given PSL SERE expression [6]. The work describes a tool which generates a VHDL description of a monitor checking circuit from a PSL SERE formula. This is achieved by creating a parser for PSL language. The syntax tree produced by the PSL parser is then given to the automata construction module. The VHDL monitors are directly translated from the expressions. These monitors are later synthesized on FPGA (Field-Programmable Gate Array).

Marc Boulé and Zeljko Zilic described a way to generate hardware assertion checkers to be used in an emulation environment [25]. To use assertions in hardware emulation, they have introduced a checker generator tool, called MBAC, that can transform PSL assertion units into Verilog modules. The transformation includes boolean layer, temporal layer and assert directive of the verification layer. The Verilog modules are synthesized on FPGA. The assertion signals are externally monitored by the verification engineer.

Morin-Allory and Borrione showed a unique method of synthesizing monitors from PSL assertions [24]. In their work, primitive monitor blocks are built for each foundation language operator of PSL. Generic monitors are built for operators that can have different number of operands. These monitors are written in synthesizable subset of VHDL. Construction of complex monitors are done by interconnecting primitive monitors. They have proved the correctness of the monitors using PVS theorem prover [33]. To do this, each monitor is converted to its respective finite state machine (FSM) and translated into PVS input formalism.

Abarbanel et al. gave birth to FoCs (Formal Checkers), an automatic generation of simulation checkers [34]. It takes PSL assertions and translates them into HDL Checkers, which in turn are integrated into the simulation environment. These Checkers monitor the simulation results on a cycle-by-cycle basis for violation of the

properties. Each Checker implements a state machine that enters and asserts an error state if the respective property fails to hold in a simulation run. The language of the checkers can be VHDL or Verilog. The tool first translates a given assertion into non-deterministic finite state automaton (NFA). The obtained NFA is converted into a deterministic finite state automaton (DFA). Finally, HDL form of the checker is generated from the DFA. The translation process is based on the work of Ilan Beer [23].

The major difference between the work presented in this thesis and the works presented in the above paragraphs is the target application. The above mentioned related works are presented with application to either simulation or emulation based verification environment in mind. The research closely related to ours is the work done by Ying et al. [36], in creating  $L_{mdg}$  language and its processing tools, called  $L_{mdg}$ -Tools. In this case the targeted application is MDG based model-checking. In our work, we present a new language based on  $L_{mdg}$ , with added operators from PSL, and present an improved tool to perform the processing of specifications written in terms of properties. Given a model of a hardware design in MDG-HDL and its respective specification in terms of properties, the outcome of both  $L_{mdg}$ -Tools and our proposed tool is a verification-ready composite model. This model is combination of the original model and the generated monitor (checker) circuit, representing the specification, in MDG-HDL.

# Chapter 2

# Background

In this chapter, we provide a brief background on following topics:

- Classification of temporal logic and specification.

- Multiway Decision Graphs (MDGs).

- Abstract Verifier or MDG verification tool.

- Construction of Translators.

# 2.1 Temporal Logic and Specification

In model-checking methods, desired specifications are usually written in propositional temporal logic formulae [9]. This allows the user to write propositions with respect to time. The model of time is represented either in linear time (LTL) [29] or branching time (CTL) [26]. CTL\* is a logic that combines the expressive power of LTL and CTL. It is also known as full branching-time logic.

### 2.1.1 Linear Time Logic

In linear time logic, the structure of time is a totally ordered set (S, <), isomorphic to the set of natural numbers (N, <) [17]:

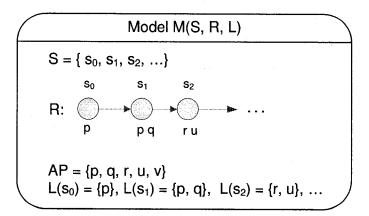

If AP is a set of atomic propositions, a linear time structure is defined as M(S, R, L), where:

- S: a set of states.

- $R \subseteq S \times S$ : transition relation function with  $\forall_{s \in S} \exists_{s' \in S}$ .  $(s,s') \in R$ .

- $L: S \to 2^{AP}$  is a labeling of each state with the set of atomic propositions true in that state.

If R is a function, i.e. for every state there exists exactly one successor state, then we obtain a *linear* structure. Following is an example (Figure 2.1):

Figure 2.1: Model Structure

In propositional linear temporal logic (PLTL), one can use propositional logic as building block and apply temporal operators to specify properties. The *syntax* of it is defined as a least set of formulae generated by the following rules [17]:

1. Each atomic proposition is a formula;

- 2. If p and q are formulae then  $\neg p$  and  $p \land q$  are formulae;

- 3. If p and q are formulae then pUq and Xp are formulae.

Semantics of a formula p of PLTL with respect to a linear-time structure M(S, x, L), where x is the transition relation, is defined below. Here, we write  $M, x \models p$  iff  $p \in L(s_0)$  for atomic proposition p to mean that in structure M formula p is true on timeline (path) x;  $x^i$  denotes the suffix path  $s_i$ ,  $s_{i+1}$ ,  $s_{i+2}$ , and so forth.

- 1.  $M, x \models p \text{ iff } p \in L(s_0)$ .

- 2.  $M, x \models \neg p \text{ iff not } M, x \models p$ .

- 3.  $M, x \models p \land q \text{ iff } M, x \models p \text{ and } M, x \models q$ .

- 4.  $M, x \models Xp \text{ iff } M, x^1 \models p$ .

- 5.  $M, x \models p \cup q \text{ iff } \exists j(M, x^j \models q, \text{ and } \forall_{0 \le i \le j}(M, x^i \models p)).$

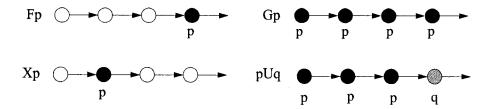

A PLTL formula p is satisfiable iff there exists a linear-time structure M := (S, x, L) such that  $M, x \models p$ , and any such structure defines a model of p. Following are some examples (Figure 2.2):

Figure 2.2: LTL formulae and time.

### 2.1.2 Computation Tree Logic

Computation tree logic (CTL) was first proposed by Clarke and Emerson [18]. It is based on branching time temporal logic (BTTL). Here, the time is modeled as a branching tree-like structure where each moment may have many different successor moments. Along each path, the timeline is isomorphic to the natural number. To specify a property in CTL, we simply apply the path operators along with temporal operators to the propositional building blocks. There are two strict restrictions in CTL:

- 1. The LTL operators F, G, X and U are immediately preceded by a path quantifier.

- 2. Time operators cannot be combined directly with the propositional connectives.

The syntax of CTL are governed by the following rules:

- 1. Every proposition is a CTL formula;

- 2. If p and q are CTL formula, then so are  $\neg p$ ,  $(p \land q)$ , AXp, EXp, A(pUq), E(pUq).

The remaining operations can be derived from the above rules. The truth of a formula is determined on a given state and not on a branch of the time structure. The structure resembles an infinite computation tree. A temporal formula p is satisfied by a model M with transitions T, if it is true for all the initial states  $s_0$  of the model. The semantics of CTL formula is given below:

- 1.  $M, s_0 \models p \text{ iff } p \in L(s_0)$ .

- 2.  $M, s_0 \models \neg p \text{ iff not } M, s_0 \models p.$

- 3.  $M, s_0 \models p \land q \text{ iff } M, s_0 \models p \text{ and } M, s_0 \models q.$

- 4.  $M, s_0 \models AXp$  iff for all states  $s_0'$  with  $(s_0, s_0') \in T$ ,  $M, s_0' \models p$ .

- 5.  $M, s_0 \models \text{EX}p$  iff for some state  $s_0^{'}$  with  $(s_0, s_0^{'}) \in T$ ,  $M, s_0^{'} \models p$ .

- 6.  $M, s_0 \models A[pUq]$  iff for all paths  $(s_0, s_1, ...)$ , there exists a  $j \geq 0$  with  $M, s^j \models q$ , and  $M, s^i \models p$  holds  $\forall_{0 \leq i < j}$ .

- 7.  $M, s_0 \models \mathbb{E}[pUq]$  iff for some path  $(s_0, s_1, \dots)$ , there exists a  $j \geq 0$  with  $M, s^j \models q$ , and  $M, s^i \models p$  holds  $\forall_{0 \leq i \leq j}$ .

Figure 2.3 shows intuitive meanings of some CTL formulae.

Figure 2.3: CTL formulae and time.

# 2.1.3 Full Branching-Time Logic

This class of logic formula combines the branching-time and linear-time operators. In CTL\*, a path quantifier can be a prefix to an assertion composed of arbitrary combination of the temporal operators: F, G, X and U. Like CTL, the tree is formed by designating a initial state  $s_0$  in model M, and then unwinding the structure into

an infinite tree with  $s_0$  as the root. The semantics of the path quantifiers and temporal operators remain the same.

# 2.1.4 Categories of specification

The specifications are written as properties of the system. They are categorized as follows:

- 1. Safety property: ensures that nothing 'bad' will ever happen. Depicted as  $\models$  Gp, where p is true at the time.

- 2. Liveness property: ensures that something 'good' will eventually happen. Depicted as  $\models Fp$ , where p will eventually be true at some point in the future.

- 3. Precedence property: ensures precedence order of events. Depicted as  $\models p Uq$ , where q is true in present time or p is true until q becomes true.

Among the three, safety property is the most used when writing specifications of a design under verification.

# 2.2 Multiway Decision Graphs

The underlying formal system of MDGs is a subset of many-sorted first-order logic improved with a distinction between abstract sorts and concrete sort. Concrete sorts have finite enumerations, while abstract sorts do not. The enumeration of a concrete sort  $\alpha$  is a set of distinct constants of sort  $\alpha$ . The constants occurring in enumerations are referred to as individual constants and the other constants as generic constants. They could be viewed as 0-ary function symbols. The distinction between abstract and concrete sorts leads to a distinction between three kinds of function symbols.

The vocabulary of many-sorted first-order logic consists of sorts, constants, variables, and function symbols or (operators). A function symbol is defined as follows: Let f be a function symbol of type  $\alpha_1 \times \alpha_2 \times \cdots \times \alpha_n \to \alpha_{n+1}$ .

- 1. If  $\alpha_{n+1}$  is an abstract sort, then f is an abstract function symbol.

- 2. If  $\alpha_1$ ...  $\alpha_{n+1}$  are concrete, then f is a concrete function symbol.

- 3. If  $\alpha_{n+1}$  is concrete while at least one of the  $\alpha_1$ ...  $\alpha_n$  is abstract, then f is referred to as *cross-operator*.

Concrete function symbols must have explicit definition. Abstract function symbols and cross-operators are *uninterpreted*.

An *interpretation* is a mapping  $\Psi$  that assigns a denotation to each sort, constant and function symbol, such that:

- 1. The denotation  $\Psi(\alpha)$  of an abstract sort  $\alpha$  is a non-empty set.

- 2. If  $\alpha$  is a concrete sort with enumeration  $a_1, a_2, \dots, a_n$  then  $\Psi(\alpha) = \Psi(a_1), \Psi(a_2), \dots, \Psi(a_n)$  and  $\Psi(a_i) \neq \Psi(a_j)$  for  $1 \leq i < j \leq n$ .

- 3. If c is a generic constant of sort  $\alpha$ , then  $\Psi(c) \in \Psi(\alpha)$ .

- 4. If f is a function symbol of type  $\alpha_1 \times \alpha_2 \times \cdots \times \alpha_n \to \alpha_{n+1}$  then  $\Psi(f)$  is a function from cartesian product  $\Psi(\alpha_1) \times \cdots \Psi(\alpha_n)$  into the set  $\Psi(\alpha_{n+1})$ .

If X is set of variables then a variable assignment with domain X, compatible with an interpretation  $\Psi$ , is a function  $\varphi$  that maps every variable  $x \in X$  of sort  $\alpha$  to an element  $\varphi(x)$  of  $\Psi(\alpha)$ . We write  $\Phi_X^{\Psi}$  for the set  $\Psi$ -compatible assignments to the variables in X.  $\Psi, \varphi \models P$  if P denotes truth under an interpretation  $\Psi$  and a  $\Psi$ -compatible variable assignment  $\varphi$  to the variables that occur free in P.  $\models P$  if a formulae P denotes truth under every interpretation  $\Psi$  and every  $\Psi$ -compatible variable assignment to the variables that occur free in P.

#### 2.2.1 Abstract State Machine

In MDGs, a state machine is described using finite sets of input, state and output variables, which are pair-wise disjoint. The behavior of a state machine is defined by its transition/output relations including a set of reset states. An abstract description of the state machine, called Abstract State Machine (ASM) [19], is obtained by letting some data input, state or output variables be of abstract sort(s), and the datapath operations be uninterpreted function symbols. As ROBDDs are used to represent sets of states and transition/output relations for finite state machines (FSM), MDGs are used to compactly encode sets of (abstract) states and transition/output relations for ASMs. This technique replaces the *implicit enumeration* technique [28] with the *implicit abstract enumeration* [15].

### 2.2.2 Structure of MDG

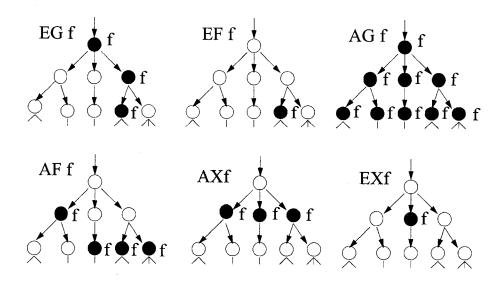

MDGs can be viewed as a generalization of BDDs. With BDDs, we can represent formulae written in boolean logic with leaf nodes labeled with boolean values. But it can also be viewed as representing an assertion, with the leaf nodes labeled by propositions. This idea can be generalized to accommodate abstract types. For example, let G represent the graph of the boolean formula  $(\neg x \land F_0) \lor (x \land F_1)$ , where,  $F_0$  and  $F_1$  are the boolean formulas represented by the sub-graphs  $G_0$  and  $G_1$  respectively. In many sorted first-order logic, the graph G can be viewed as representing a formula:

$$((x=0) \wedge F_0) \vee (x=1) \wedge F_1).$$

Three possible generalizations of G and the corresponding formulas are shown in Figure 2.4.  $F_0$ ,  $F_1$  and  $F_2$  are first-order formulas represented by the sub-graphs  $G_0$ ,  $G_1$  and  $G_2$  respectively. Sorts and functions are annotated in the graphs.

1. From G to G':  $x \in \{0,1\} \rightarrow x \in \{0,2,3\}$ , and Graph G' represents the

formula:

$$((x = 0) \land F_0) \lor ((x = 2) \land F_1) \lor ((x = 3) \land F_2).$$

2. From G to G'':  $x \in \{0,1\} \to x \in \{a,y,f(a,y)\}$ , and Graph G'' represents the formula:

$$((x = a) \land F_0) \lor ((x = y) \land F_1) \lor ((x = f(a, y)) \land F_2).$$

3. From G to G''':  $x \in \{0,1\} \to g(x) \in \{0,2,3\}$ , and Graph G''' represents the formula:

$$((g(x) = 0) \land F_0) \lor ((g(x) = 2) \land F_1) \lor ((g(x) = 3) \land F_2).$$

Figure 2.4: BDDs to MDGs.

The above generalized decision graph G', G'' and G''' are examples of Multiway Decision Graphs (MDGs).

## 2.2.3 Verification Algorithms

The MDG software package includes algorithms for disjunction, relational product, pruning-by-subsumption (PbyS), and reachability analysis. Except for PbyS, the operations are a generalization of first-order terms of algorithms on ROBDD, with some restrictions on the appearance of abstract variables in the arguments. In the reachability analysis procedure, starting from the initial set of states, the set of states reached in one transition is computed by the relational product operation. The frontier set of states is obtained by removing the already visited states from the set of newly reached states using the pruning-by-subsumption (PbyS) operation. If the frontier set of states is empty, then the reachability analysis procedure terminates, since there are no more unexplored states. Otherwise the newly reached states are merged (using disjunction) with the already visited states and the procedure continues where the next iteration with the states in the frontier set as the initial set of states. A facility to carry out simple rewriting of terms that appear in the MDGs is also included. This allows algorithms to provide a partial interpretation of an uninterpreted function symbol. A detailed description of the operations and algorithms can be found in [15]. The following sub-sections describe the important verification methods provided by the MDG tools.

#### Combinational Equivalence Checking

The MDGs representing the input-output relation of each circuit are computed using the relational product of the MDGs of the components of the circuits. Then taking advantage of the canonicity of MDGs, it is verified whether the two MDG graphs are isomorphic. Using this technique, we can verify the equivalence of two combinational circuits.

### Sequential Equivalence Checking

The behavioral equivalence of two sequential circuits can be verified by checking that the circuits produce the same sequence of outputs for every sequence of inputs. This is achieved by forming a circuit from two circuits by feeding the same inputs to both and verifying an invariant asserting the equality of the corresponding outputs in all reachable states.

### **Model Checking**

MDG model checker provides both safety and liveness property checking facilities using the implicit abstract enumeration of an abstract state machine. In MDG model-checking, the design is represented in MDG-HDL and the properties to be verified are expressed by formulae in  $L_{mdg}$ . The ASM model of  $L_{mdg}$  and the RTL model is composed along with a simplified invariant. The simplified invariant is checked on the composite machine using the implicit abstract enumeration of the ASM.

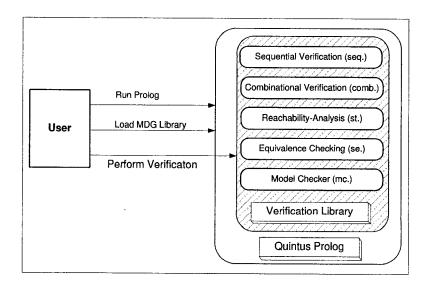

### 2.3 Abstract Verifier

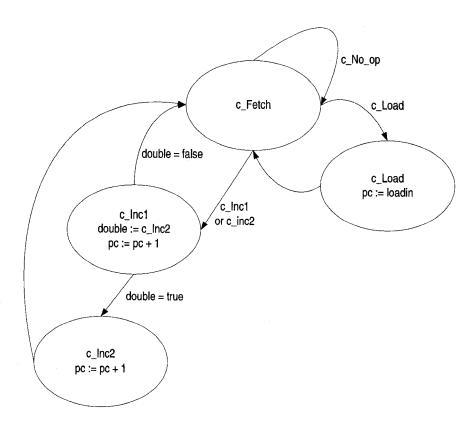

Abstract Verifier, also known as MDG Verification Tool, consists of set of tools. These include a composite model generator in  $L_{mdg}$  tools (Figure 2.9) at the frontend and a collection of services that are implemented as a library package under Quintus Prolog [2] at the back-end. The package includes a reachability-analysis procedure, applications for combinational and sequential hardware verification at RT level [39], and model-checking applications for a subset of first-order abstract CTL\* [36].

Figure 2.5: MDG Verification

A user needs to represent the model under verification in MDG-HDL according to its language specification [38]. He then needs to load the MDG library (Figure 2.5) in Prolog to run applications available in the library package. If model-checking needs to be performed,  $L_{mdg}$  set of tools must be used to get a composite model. The user must modify the original model using any text editor and write its specification in  $L_{mdg}$  language in accordance with the restrictions provided in MDG Model Checker User's Manual [35]. In the following subsections, we provide instructions on how to represent models in MDG-HDL and the process of MDG based model-checking.

### 2.3.1 MDG-HDL

MDGs describe circuits at the RT level as a collection of components interconnected by nets that carry signals. Each signal can be an abstract variable or a concrete variable. The input language for MDG based applications is MDG-HDL. It allows the use of abstract variables for representing data signals and uninterpreted function symbols for representing data operations. MDG-HDL mainly supports structural description. In order to represent a design, a user must create three files: an algebraic description file, a circuit description file and an order description file. To perform model-checking, he also needs to feed the model-checker with the property file. In the following subsections, we provide brief discussion on each step.

#### Algebraic Description File

In this file the user defines custom signal types (sorts), function types and generic constants used in the hardware description. The built-in types are given in common.pl in MDG package library [38]. If rewrite-rules are needed to interpret the function symbols, they are also specified in this file.

- Sorts: Sorts can be one of the two types: abstract or concrete.

- 1. abs\_sort(Sort). declares Sort as an abstract sort.

- Example: abs\_sort(wordn). declares wordn is an abstract sort.

- 2. conc\_sort(Sort, [list\_of\_values]). declares Sort as a concrete sort having list of constant values as its enumeration.

- Example: conc\_sort(bool,[1,0]). Here, bool is a concrete sort whose enumeration is given in the list [1,0], where 1 and 0 are treated as individual constants.

- Functions: There are two types of functions in MDG-HDL: abstract function symbol and cross function symbol.

function(Func\_symbol, Args\_sorts, Target\_sort) - declares a function type. Func\_symbol is the function symbol. It can be an abstract function symbol or a cross-operator. Args\_sorts is a list of types of the arguments and Target\_sort is the type of the function return.

- 1. Example: function(add, [wordn, wordn], wordn). Here, add is uninterpreted but could mean addition. It is a function that takes two arguments, whose sorts are wordn, and returns a result of sort wordn. In this case, wordn must be abstract sort and add is an abstract function symbol.

- 2. Example: function(leq, [wordn, wordn], bool). leq is a function which is uninterpreted. It intends to mean less then or equal. The function has two arguments of abstract sort wordn and returns a result of boolean sort bool. Here, leq is called a cross-function symbol (or cross-operator or cross-op).

- Generic constants: The generic constants are declared the following way:

- gen\_const(Gen\_const, Sort) declares a generic constant Gen\_const

having the type Sort.

- Example: gen\_const(min,wordn). Here, min is a generic constant of sort wordn.

- Re-writing rules: The re-writing rules are written using two keywords: rr and xtrr.

- rr(C<sub>s</sub>, LHS, RHS) is a conditional rewrite rule: C<sub>s</sub> ⇒ LHS → RHS.

Here, LHS (left hand side) and RHS (right hand side) are terms. C<sub>s</sub> is a list of conditions. A condition can be a pair (Xt<sub>t</sub>, C) composed of a cross-term and an individual constant, or it is simply a term which is a goal of the predicate.

- Example:  $\operatorname{rr}([(eq(X,Y),0),(iszero(X),1)],iszero(Y),0)$ . It means if (eq(X,Y)=0) and (iszero(X)=1) then iszero(Y) equals 0. Here, [(eq(X,Y),0),(iszero(X),1)] is the condition list.

- 2.  $xtrr(C_s, LHS, RHS)$  is a conditional rewrite rule for cross-terms:

$C_s \Rightarrow LHS \rightarrow RHS$ . LHS must be a cross-term and RHS must be an individual constant.  $C_s$  may contain arithmetic expressions, but must not contain cross-term and individual constant pairs.

- Example 1: xtrr([], eq(X, X), 1).

It represents the rewrite rule: X=Y ⇒ eq(X, Y) → 1. The condition X=Y (syntactic equivalence) is implicitly expressed in the rule. The condition list is thus empty.

- Example 2:  $\mathsf{xtrr}([square(X,Y)], sq(X,Y), 1)$ .  $\mathsf{square}(X,Y)$ :- Y is  $X^*$  X. It represents the rewrite rule:  $X^2 = Y \Rightarrow sq(X,Y) \to 1$ . The condition  $X^2 = Y$  is an arithmetic expression. It is evaluated by a *Prolog predicate*: square(X,Y):- Y is X \* X.

#### Circuit Description File

A circuit can be described as a structural description, a behavioral ASM description, or a mixture of structural and behavioral descriptions. A structural description is usually a net-list of components (predefined in MDG-HDL) connected by signals. A behavioral description is the transition/output relations of an ASM given by table construct. Following are the basic constructs:

- 1. Signal declaration: Each signal must be declared only once in the following format:

- Format: signal(name, type). Here, name is the name of the signal and type is the sort of the signal.

- Example: signal(mySig, bool). declares a signal mySig with type bool.

- 2. Component declaration: Components are the basic building blocks in MDG-HDL.

- Format: component(name, definition) declares a component name that is defined by definition.

- Examples: Following are some definitions of components from the set of predefined components in MDG-HDL:

- (a) NOT gate: not(input(Input: bool), output(Output: bool))

- (b) Two-input and-gate: and(input(Input1: bool,Input2: bool), output(Output: bool)).

- (c) Register with control signal: reg(control(Control:bool), input(Input:Sort),

output(Output: Sort)).

- (d) Uninterpreted function block: transform(inputs(Inputs:[ $Sort_1$ ,  $Sort_2$ , ...,  $Sort_n$ ]), function(Func\_symbol), output(Output:Sort)).

- 3. Table declaration: Tables are considered as components. It is similar to a truth table, but it allows first-order terms in the rows. In the list of rows, the first row is a list containing variables and cross-terms. The last element of the list must be a (concrete or abstract) variable. All the other variables in the list must be concrete variables. Starting from the second row, each row is a list of values that the corresponding variables or cross-terms can take. The last element in the value list could be a first-order term, which means an assignment to the output variable. The other elements in the list must be either don't-cares (represented by '\*') or individual constants in the enumeration of their corresponding variable sort. The last element a row may be a term which serves as the default value.

- Format: table(rows).

- Example: component(myTable, table([[myInput,myOutput], [1, 0] | 1])).

It specifies a NOT gate, where myOutput has value 0 if myInput has value 1; myOutput has value 1 if myInput is not 1.

- 4. State variable initialization: User needs to assign starting point for state variables.

- Format: init\_val(Stvar, InitVal). assigns InitVal to Stvar.

- Example:init\_val(myState, s0). assigns s0 as the starting state to myState variable.

- 5. State variable generalization: For abstract state variables, the initial states should be generalized.

- Format: init\_var(InitVal, Sort). declares InitVal as a generalized state variable sort to be used in initializations.

- Example: init\_val(pc,init\_pc). init\_var(init\_pc,wordn).

- 6. Next state declarations: For sequential circuit, the user should provide the mapping between state variables and next-state variables.

- Format: st\_nxst(Stvar, NextStvar) declares that NextStvar is the next-state variable of a state variable Stvar.

- Example: st\_nxst(myStateVar, n\_myStateVar).

- 7. State partition declaration: It is a 3-level nested list. The inner most list gives a list of next-state variables. The transition relation MDG, containing all the variables in the list, forms an individual transition relation. The middle level list specifies a default partition block.

- Format: next\_state\_partition(Partitions).

- Example: next\_state\_partition([[[n\_a]],[[n\_b]],[[n\_c]]]).

- 8. Output partition declaration: It declares Outputs as a list of outputs of the circuit.

- Format: outputs(Outputs).

- Example: outputs([myOutput]).

- 9. Partition strategy declaration:

- Format: par\_strategy(OrdMethod, ParMethod). declares OrdMethod as the ordering strategy for individual relations and ParMethod as the partitioning strategy.

- Example: par\_strategy(auto, auto).

Complete details of the MDG-HDL language can be found in its user manual [38].

#### Order Description File

Like ROBDDs, the MDGs require a total order over all the nodes in the graph. This order is manually provided by the user using order\_main(Symbols) function where Symbols is a list of variables and cross-operators. We say that symbol a comes before symbol b if a is at the left side of b in the list. In MDG, a will appear above b. We may also write it as a < b.

Example: order\_main([r,x,c\_A,n\_c\_A,rm\_A,n\_rm\_A,rM\_A,n\_rM\_A,leq]). For node ordering of abstract variables and cross-operators, MDGs have some requirements:

- 1. If a variable a will appear as a secondary variable in an edge label of node b, then a < b.

- 2. If a variable a will appear as a secondary variable in a cross-term having cross-op f, then a < f.

- 3. The state variables and next state variables must be in a correspondent order.

- 4. If using rewriting rule  $rr(C_s)$ , LHS, RHS, the cross-operators in  $C_s$  must come before the terms in LHS in the graph structure. For example, for rule: rr([(eq(X,Y), 0), (iszero(X), 1)], iszero(Y), 0), cross-operator eq should come before iszero.

#### **Modeling Examples**

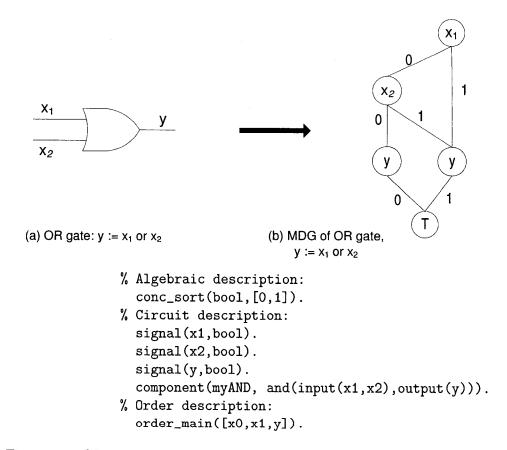

For logic gates, the input and output signals are always of concrete sort with boolean values. Abstract sort is pre-defined in the MDG library package. Cross operators are used when feedback of a datapath is used as part of control. If not, a function symbol is used. Both, however, are uninterpreted. A simple logic-gate design is given as an example below containing concrete sorts. The Figures 2.6 and 2.7 show MDG-HDL representations of an OR-gate and a comparator respectively. More details can be found in the user manual of MDG-Tools [38].

Figure 2.6: OR gate in MDG and its corresponding MDG-HDL description.

Figure 2.7: MDG-HDL description of a Comparator

## 2.3.2 Specification Language for MDG Model-Checking

The property language of MDG model-checking methodology,  $L_{mdg}$ , is tailored to fit the powerful model-checking algorithms available in MDG. It is based on abstract CTL\* [36]. The formulae are divided into two categories: state formulae and path formulae. State formulae give specification on certain states in the system and path formulae elaborate on them with respect to time using temporal operators. Its semantics can be found in the user manual of MDG model-checker [35].

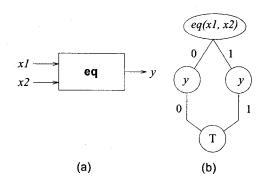

**Example:** Here, we present some properties written in  $L_{mdg}$  specification language. Given the model of Figure 2.8 represented in MDG-HDL, the specification

can be written as follows:

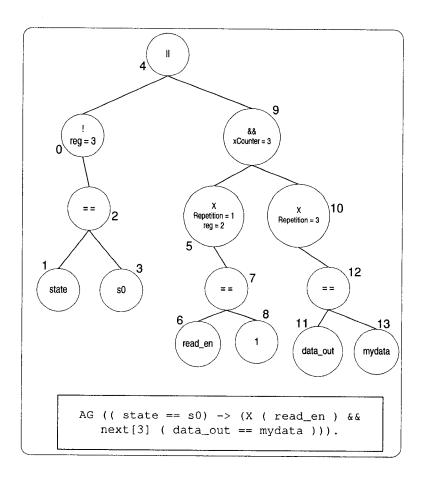

- 1. AG ( state = c\_Fetch & input = c\_Inc2) -> X(state = c\_Inc1));

If state is c\_Fetch and input is c\_Inc2, then in the next transition state is c\_Inc2.

- 2. AG ((state = c\_Fetch & input = c\_Load) -> XX(state = c\_Fetch));

If state is c\_Fetch and input is c\_Load, then in two transition steps state is c\_Fetch.

- 3. AG((state = c\_Fetch & input = c\_Inc2) ->

(LET(pc = v1) IN (XXX(pc = finc(finc(v1)))));

If state is c\_Fetch and input is c\_Inc2, then in three transition steps the value of pc will be incremented two times. Here, the value of pc in the present state is stored in v1. The comparison is made between the value of pc after three transition steps and incrementing the old value of pc twice.

Figure 2.8: An abstract counter

$L_{mdg}$  language is discussed in detail in the next chapter.

## 2.3.3 Model-Checking in MDG

To perform model-checking based on MDG, following steps are taken:

- 1. Represent the design under verification in MDG-HDL.

- 2. Perform state exploration to make sure that no error exists. The state exploration service in MDG software package detects and reports all syntax and semantic errors before performing reachability analysis.

- 3. Edit the model according to restrictions given in the manual [35].

- 4. Write the specification according to the manual.

- 5. Run the  $L_{mdg}$  tools to generate the composite model and the condition file(s).

- 6. Run model-checker to verify the model.

To verify subsequent specifications, user needs to repeat steps 4 to 6 in the above list. The user shall creates a few additional files in order to use MDG model-checker, part of MDG verification tool implemented as a library package under Quintus Prolog [2]:

- 1. A make pl file that tell *prolog* application where the MDG library package is. After running *prolog*, a user loads the make file.

- 2. A circuit.pl file that provides the MDG applications the filenames of the models and their locations. This file can be automatically generated as well.

Figure 2.9: Model-Checking in MDG

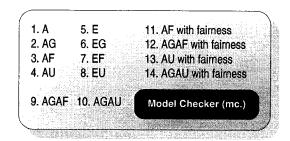

Figure 2.9 shows the modules involved in the model-checking process. When a user runs the sequential verification application, it loads all the necessary algorithms that are required to run the model-checker. A user must do it before running the model-checker application. When the model-checker application is run, the user must select a property template from the following list:

- 1. A 2. AG

- 3. AF 4. AU

- 7. EF 8. EU

5. E

- 9. AGAF 10. AGAU

- 11 .AF with fairness 12. AGAF with fairness

6. EG

13 .AU with fairness 14. AGAU with fairness

Based on the chosen template, user must specify the filenames of the composite model and the condition files. The model checker than runs the algorithm and produces a result: yes or no. This informs the user if the specification is satisfied or not.

## 2.4 Construction of Translators

In this thesis, the proposed tool shall have a component that can perform a translation between Abstract Property Language (APL) to MDG-HDL. Thus, in this section, we provide the basic construction technique of such module that can perform the required operation. We follow the procedure of compiler construction for this purpose.

In its most general form - a compiler is a program that accepts as input a program text in certain language and produces as output a program text in another language [11]. This conversion process is called translation. The input language of this process is denoted as the source language, and the output language is denoted as the target language.

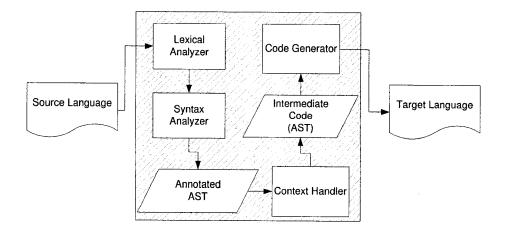

Figure 2.10: Basic structure of a compiler.

Figure 2.10 shows the basic structure of a compiler. The components are: Lexical Analyzer, Syntax Analyzer, Semantic Analyzer and Code Generation. A code optimizing module is usually present in compiler constructions. Since it is not used in building the proposed tool, we have omitted the module.

## 2.4.1 Lexical Analyzer

A lexical analyzer or lexer takes an arbitrary input stream and tokenizes it into lexical tokens. In this thesis, the lexical analyzer is built using a tool called Flex [22]. Flex automatically generates a lexical analyzer given its lexical specifications. The specifications are set of patterns written using regular expressions that are matched against the input. Each time one of the pattern is matched, corresponding action code is executed. In such a case, the *action* returns appropriate token to the syntax analyzer. Attributes of the tokens are also saved along with the tokens.

#### Example:

- 1. Pattern: id  $[a-z][a-zA-Z0-9_]*$

- 2. Action: Return the token ID and store its attributes.

When pattern of id is matched, its attributes are saved and token ID is provided to the syntax analyzer.

## 2.4.2 Syntax Analyzer

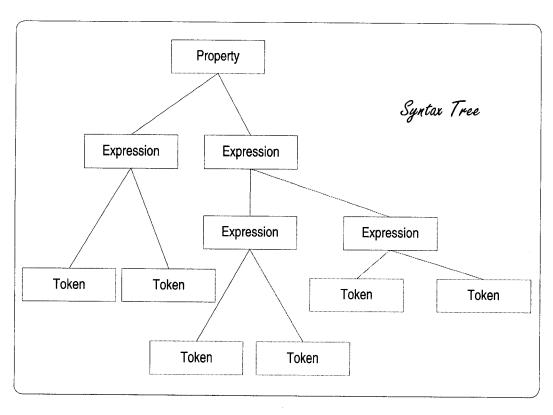

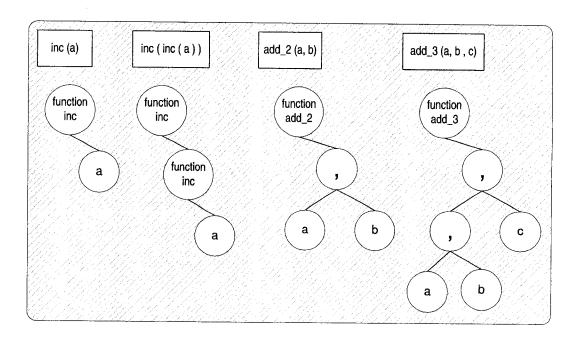

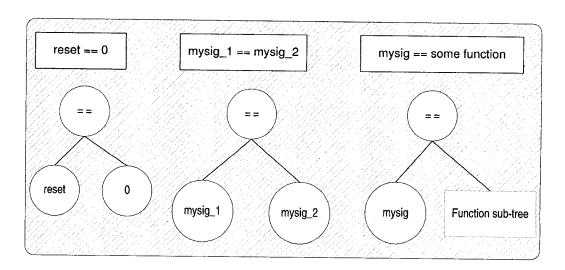

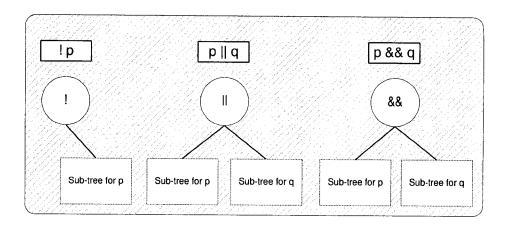

A syntax analyzer determines if its input is syntactically correct given a set of syntax rules and also determines its structure. The syntax rules are given as grammar of the language. The structure is usually an abstract syntax tree (AST). AST is also known as parse-tree. The AST accurately shows how the segments of program text are to be viewed in terms of the specified grammar. In this thesis, Bison [21] is used to build the syntax analyzer. In Bison, a user specifies the grammar in Backus-Naur Form (BNF) and provides corresponding actions per production rule in order to build the AST. User also needs to specify the association types of the operators and their precedence. When an AST is built, the nodes are annotated with its attributes. It is then called an annotated AST. In this thesis, AST means annotated AST.

#### Example:

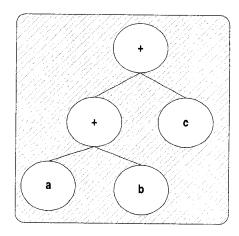

The grammar given below presents a grammar of an expression that can be an identifier, or it can be a *plus* operation between two expressions. Figure 2.11 shows an example AST of the expression a + b + c, where the *plus* operator is left associative.

#### • Grammar:

- 1. expression: expression + expression

- 2. | id;

#### • Actions:

1. For the first line: create a node in the AST with corresponding value of plus and the expressions as its children.

2. For the second line: create a node in the AST with associated value of *id* with two NULL children. Here the *id* is a leaf node.

Figure 2.11: AST for a+b+c.

#### 2.4.3 Context Handler

Based on the attributes of tokens and the context of use, this process checks the semantics of program text. It is also known as *semantic analyzer*. For example, a plus can be an arithmetic operation or a logical OR. Based on the semantic, its usage should be analyzed. In this case, the operands should be either logical or numeric. During semantic analysis phase, optimization information is collected, and later it is used in the code generation.

### 2.4.4 Code Generator

A code generator produces statements in target language through a process called code generation. It is a process of systematic replacement of nodes and sub-trees of the AST by target code segments. This process preserves the semantics. The AST is re-written to produce a linear sequence of instructions based on the target

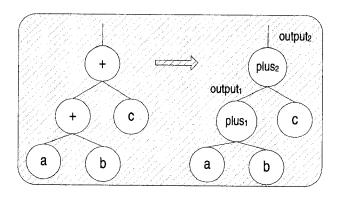

language. For example, if we consider the AST given on Figure 2.11, as representing some statement in the source language and consider a target language supporting procedure  $plus(input_1, input_2, output)$ , we can do the following:

- 1. a+b generating a target statement:  $plus(a, b, output_1)$ .

- 2. (a+b) + c generating a target statement:  $plus(output_1, c, output_2)$ .

Figure 2.12: AST to target code.

Figure 2.12 shows one of the ways it can be done. Here,  $plus_1$  can be replaced with  $output_1$  and  $plus_2$  with  $output_2$ . In this thesis, simple traversal algorithms are used to generate the target text from AST. The details of which are given in Chapter 4.

# Chapter 3

# Language Description

The purpose of using formal logic to define hardware specification is to avoid ambiguities associated with descriptions in natural languages. Defining specification in formal logic also facilitates automation of verification processes. In model-checking based verification, specification languages, as expected, are based on temporal logic. They allow verification engineers to specify how the behavior of a system should progress over time. This is possible in temporal logic without explicit introduction of time. Abstract property language (APL) described in this chapter is such a language.

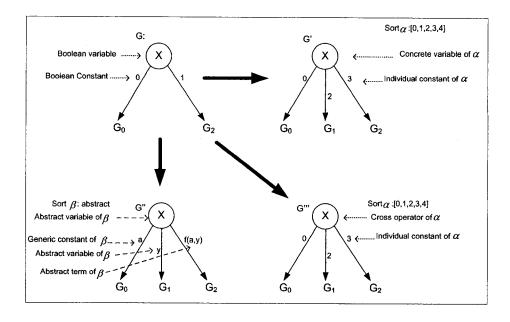

Figure 3.1: MDG Model-Checking Algorithms.

In this chapter, we provide detail description of the proposed language. We introduce Property Specification Language (PSL) and  $L_{mdg}$  specification language

and then define subsets of the two languages that are considered in constructing APL. When we define these subsets, we must keep in mind the model-checking algorithms implemented in the *MDG model-checking* package.

The package supports 14 different formats of temporal logic (Figure 3.1). There are also four algorithms dealing with fairness formulae that allow users to put constraints on the environment of the design. In this thesis, we only focus on properties based on the first 10 algorithms given in Figure 3.1.

## 3.1 PSL and its subset in APL

Property Specification Language (PSL) has recently become an IEEE standard in 2005 [6]. With its crisp syntax and comprehensive formal semantics, it is becoming the primary choice among assertion languages intended for hardware verification. In this section, we present a brief introduction to PSL and its subset relevant to APL.

The PSL language structure is based on four layers: Boolean Layer, Temporal Layer, Verification Layer and Modeling Layer.

## 3.1.1 Boolean Layer

This layer consists of expressions with valuations true or false. The boolean operators in this layer are from the respective underlying HDL flavor. For APL, the underlying layer is MDG-HDL. It is a structural language where boolean operations are represented by logic components and not by boolean expressions. However, for its specification language, we are free to choose boolean expressions to represent logical operations, as the composite model shall be generated by the proposed tool. We choose the logical operators given in Table 3.1 to be used in APL. The primary reason for considering these operators is that most users are accustomed to using them in this syntax.

Table 3.1: Logical Operators considered for APL

| Operator          | Logical Operation | HDL Flavor                       |

|-------------------|-------------------|----------------------------------|

| !                 | NOT               | Verilog, SystemVerilog , SystemC |

|                   | OR                | Verilog, SystemVerilog , SystemC |

| &&                | AND               | Verilog, SystemVerilog , SystemC |

| $\rightarrow$     | IMPLICATION       | Verilog, SystemVerilog , SystemC |

| $\leftrightarrow$ | EQUIVALENCE       | Verilog, SystemVerilog , SystemC |

Bit and bit-vectors can be suitably represented by creating concrete signals in MDG-HDL. Union operator cannot be considered because non-deterministic assignments of concretes are not applicable in MDG. The supported expressions and operators are constrained by the rules of simple subset of PSL [6].

## 3.1.2 Temporal Layer

This layer consists of temporal properties that allow us to represent relationships between boolean expressions over time structure. Since PSL is mostly used in simulation environment, it offers weak and strong temporal operators. Weak operators allow assertions to pass if simulation traces (finite) end prematurely and nothing else fails. In such cases, use of strong operators results in failed assertions. By definition, in formal verification we are dealing with 'infinite traces'. In MDG based model-checking algorithms, operators are treated as strong by default. Therefore, we do not distinguish operators based on the type. In PSL, LTL and SERE style temporal properties together are known as Foundation Language (FL). In all styles of temporal properties in PSL, we follow the rules of simple subset [6], briefly discussed in this section. We shall then discuss Foundation Language and CTL based Optional Branching Extension styles of PSL.

#### Simple Subset

In simple subset of PSL, the time is seen as flowing from *left to right* through the property. The intuitive meaning of it is that if we need to evaluate an atomic entity at cycle  $\Delta$ , then valuation of any entity to the right of it, in the property, should not need to occur before  $\Delta$ . An example of an invalid property is given in Table 3.2. In the invalid property, c and d need to be asserted before we assert b. Details of the rules are given in the language reference manual [6].

Table 3.2: Example property violating simple subset rules

| Property                                        | Valid (?) |

|-------------------------------------------------|-----------|

| $AG ((a \&\& XX(b)) \rightarrow (c \&\& X(d)))$ | No        |

| $AG((p \&\& XX(q)) \rightarrow (XXX(r)))$       | Yes       |

### Foundation Language (FL)

LTL style support all the temporal operators of LTL. Table 3.3 shows LTL operators and corresponding PSL synonyms [10]. Here, items 2, 4 and 5 have strong operators. As mentioned before, we shall not make distinction on types of temporal operator. In APL, all temporal operators shall be treated as *strong* [10].

Table 3.3: LTL operators in PSL

| No. | LTL        | PSL synonym   |

|-----|------------|---------------|

| 1   | Gp         | always p      |

| 2   | Fp         | eventually! p |

| 3   | Хp         | next p        |

| 4   | X! p       | next! p       |

| 5   | $p \cup q$ | p until! q    |

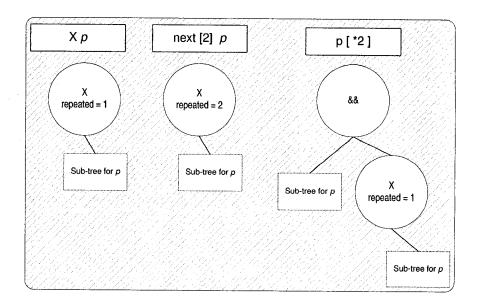

In addition, PSL offers expressive classes of 'next', 'until' and 'before' operators. Table 3.4 gives two variations of next that are considered for APL. The reason for considering them is their ease of use and applicability in our property templates. For instance, if a property requires to reason about a state after 32 cycles, it is much simpler to write next[32] than writing X thirty two times. The complete set of LTL operators can be found in the PSL LRM [6].

Table 3.4: next operators considered for APL

| Property      | LTL Equivant   | Description                          |

|---------------|----------------|--------------------------------------|

| next! p       | Xp             | p holds in the next cycle            |

| next! [* n] p | XX (n-times) p | $p$ holds in the $n^{th}$ next cycle |

The other member of the Foundation Language is SERE style. SERE, sequence extended regular expression, was created so that users can write temporal properties as easily as they write regular expressions. In this style, the time sequence events are delimited by a concatenation operator. A set of expressive SERE operators are provided in this style to easily specify how long or when a boolean entity should be asserted. Most are very useful in simulation environment. Complete details of SERE operators and expressions can be found in PSL's LRM [6]. For now we only consider the concatenation operator and one of the repetition operators. Table 3.5 gives their details. More operators can be considered for APL if time permits. Given the underlying abstraction in MDG methodology, we will use the name abstract SEREs when they are used in APL.

Table 3.5: SERE operators considered for APL

| Operator | Name                            | Example  | Description                                                                              |

|----------|---------------------------------|----------|------------------------------------------------------------------------------------------|

| ;        | Concatenation operator          | req; ack | ack is asserted one cycle after req is asserted.                                         |

| [* n]    | Consecutive repetition operator | p[*3]; q | p is asserted for three consecutive cycles and then $q$ is asserted in the fourth cycle. |

Since clock is always implicit in MDG methodology, we do not consider any clock related expressions. The SERE expressions used in APL are thereby unclocked. Based on the strict set of algorithms we have, we shall not consider few other useful operators: suffix, fusion, disjunction, within, etc. Endpoint declarations and built-in functions are not applicable for the very same reason. Syntax and semantics of foundation language are given in the language reference manual of PSL [6].

### Optional Branching Extension (OBE)

For branching-time temporal logic based formal verification, PSL offers *Optional Branching Extension* (OBE). It is based on CTL. Since our MDG model checker is based on first-order abstract CTL\*, we support all OBE operators, with their applicability governed by their corresponding verification algorithms (See Figure 3.1). Restriction on *until* operator still applies based on simple subset rules of PSL.

## 3.1.3 Verification Layer

This layer consists of directives to the verification tool indicating what to do with the property in concern. There are five classes of directives: assert, assume, restrict, cover and fairness. In MDG model-checking algorithms all properties are asserted, and thus assert is the implicit directive. The fairness constraints can be employed by using fairness algorithms available in the  $L_{mdg}$  package.

## 3.1.4 Modeling Layer

This layer helps model behavior of design inputs and allows declaring and providing behavior to auxiliary signals and variables. In MDG model-checking methodology, the properties are written in first-order abstract CTL\*, and the syntax is vastly different then its HDL flavor. In MDG-HDL, the logic gates are represented structurally using components. The written properties are parsed and embedded as additional circuit to the original model as checkers. The signals and components needed to represent these additional circuits are automatically generated.

## 3.2 $L_{mdg}$ and its subset in APL

$L_{mdg}$  is constructed based on first-order temporal logic. It is a subset of abstract CTL\* [36]. The syntax and semantics of it have already been clearly defined and established [37]. Our goal is to improve the existing specification language,  $L_{mdg}$ , and its parser implementation. Therefore, we must consider the  $L_{mdg}$  language in its entirety for APL. Only a few lexical rules for operands are changed, and some operators are replaced by their synonyms. However, the semantics remain as defined. Let us revisit the syntax of  $L_{mdg}$ .

With a given description of an *abstract state machine* (ASM) and a set of ordinary variables (used as storage in properties), the formulae are divided into two categories: *state* formulae and *path* formulae.

#### State Formulae

- 1.  $t_1 = t_2$  is a state formula, if  $t_1$  is an ASM variable and  $t_2$  is either an ASM variable, or a constant, or an ordinary variable.

- 2. If p, q are state formulae, then so are:

- (a)  $p \in (NOT p)$ ,

- (b) p & q (p AND q),

- (c) p + q (p OR q) and

- (d)  $p \rightarrow q$  (p IMPLIES q).

- 3. LET (v = t) in p is a *state* formula, if v is an ordinary (storage) variable, t is an ASM variable and p is a *state* formula.

- 4. If p is a path formula, then Ap (for all path) and Ep (there exist a path) are state formulae.

#### Path Formulae

- 1. Each state formula is a path formula.

- 2. If p, q are path formulae, then so are

- (a)  $p \in (NOT p)$ ,

- (b) p & q (p AND q),

- (c) p + q (p OR q),

- (d)  $p \rightarrow q$  (p IMPLIES q),

- (e) Xp (next p),

- (f) Gp (always p),

- (g) Fp (eventually p) and

- (h) pUq (p until q).

- 3. LET (v = t) in p is a path formula, if v is an ordinary (storage) variable, t is an ASM variable and p is a path formula.

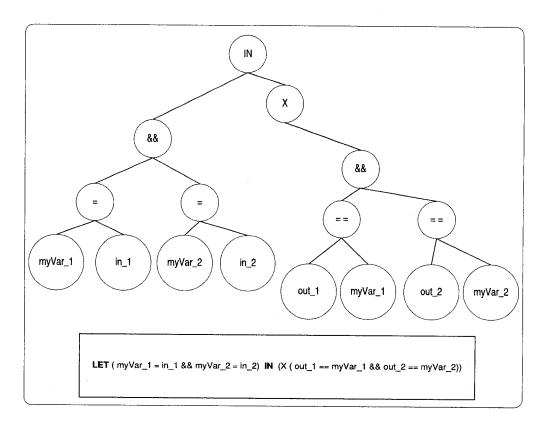

Here, LET  $(v_1=t_1 \& ... \& (v_n=t_n) \text{ IN } p \text{ is a shorthand for LET } (v_1=t_1) \text{ IN } (\text{LET} (v_2=t_2) ... (\text{LET } (v_n=t_n) \text{ IN } p ))...)$

The proposed changes to incorporate into APL are following: