# FORMAL SEMANTICS AND VERIFICATION OF USE CASE MAPS

#### JAMELEDDINE HASSINE

A THESIS

IN

THE DEPARTMENT

OF

COMPUTER SCIENCE AND SOFTWARE ENGINEERING

Presented in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy

Concordia University

Montréal, Québec, Canada

April 2008 © Jameleddine Hassine, 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-37746-8 Our file Notre référence ISBN: 978-0-494-37746-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

| By:      | Mr. Jameleddine Hassine                                                                    |                      |

|----------|--------------------------------------------------------------------------------------------|----------------------|

| Entitled | : Formal Semantics and Verification of Use Case Ma                                         | ps                   |

| and sub  | mitted in partial fulfillment of the requirements for the degree of                        |                      |

|          | Doctor of Philosophy (Computer Science)                                                    |                      |

| •        | s with the regulations of this University and meets the accepted stands<br>ty and quality. | ards with respect to |

| Signed b | by the final examining committee:                                                          |                      |

|          |                                                                                            | _ Chair              |

| _        |                                                                                            | External Examiner    |

| -        |                                                                                            | Examiner             |

| -        |                                                                                            | Examiner             |

| =        |                                                                                            |                      |

| -        |                                                                                            |                      |

| -        |                                                                                            | _ Co-supervisor      |

| Annrow   | be                                                                                         |                      |

| Approve  | Chair of Department or Graduate Program Director                                           |                      |

|          | 20                                                                                         |                      |

|          | Dr. Nabil Esmail, Dean                                                                     |                      |

|          | Faculty of Engineering and Comput                                                          | ter Science          |

### Abstract

Formal Semantics and Verification of Use Case Maps Jameleddine Hassine, Ph.D. Concordia University, 2008

Common to most software development processes is that system functionalities are defined early in the life cycle in terms of informal requirements and visual models. As requirement descriptions evolve, they quickly become error-prone and difficult to understand leading to prolonged detrimental effects on reliability, cost, and safety of a software system that are very costly to fix in later phases of the software development process. Thus, the development of techniques and tools to support requirement specification development, understanding, validation, verification, maintenance and reuse becomes an important issue.

This thesis proposes a novel methodology named Early Stages V&V (Early Stages Validation & Verification), which combines the semi-formal scenario-based Use Case Maps language with formal techniques to help comprehend, validate and verify requirements. UCM models allow the description of functional requirements and high-level designs at early stages of the development process. Use Case Maps is being standardized as part of the User Requirements Notation (URN), the most recent addition to ITU-Ts family of languages. In the first part of the thesis, we propose a concise and rigorous formal semantics for Use Case Maps based on Abstract State Machines (ASM) formalism. The resulting semantics are embedded in an ASM-UCM simulation engine and are expressed in AsmL, an advanced ASM-based executable specification language, which is used to validate UCM models through simulation.

Timing issues are often overlooked during the initial system design and treated as separate behavioral issues and therefore described in separate models. In the second part of the thesis, we extend the Use Case Maps language to cover timing constraints. A potential timed version of UCM (called *Timed UCM*) is formalized using Clocked Transition Systems (CTS) and Timed Automata (TA). The proposed semantics can be applied to comprehend, analyze, validate and verify (using model checking) timed UCM models. In addition, we have proposed a novel UCM-based property pattern system that combines qualitative, real-time and architectural properties into a single graphical representation. The resulting pattern system is mapped to popular temporal logics CTL, TCTL and ArTCTL (Architectural real-time temporal logic), which is an extension to TCTL introduced in this research that provides temporal logics with architectural scopes.

In order to achieve an efficient validation and verification of UCM models and to assess the impact of a specification change (e.g. as a result of a bug fixing or a feature upgrade), we extend the application of the well-known technique of program slicing to Use Case Maps language.

An ongoing example of a simple telephone system is used to illustrate these concepts. The thesis validates the  $Early\ Stage\ V&V$  methodology by implementing it and applying it to two case studies: IP Multicast Protocol and an Online Store application.

## Acknowledgments

First and foremost, I would like to express my most sincere gratitude to my supervisors, Professor Juergen Rilling and Professor Rachida Dssouli, without whose insightful guidance and invaluable help this thesis would not be possible. They have given me enormous freedom to pursue my own interests and provided me with guidance and steadfast encouragement to ensure that my efforts are rewarded. I really appreciate the time and energy they had dedicated to my thesis work. I feel fortunate to be under their supervision.

I would like to give great thanks to professor Daniel Amyot, School of Information Technology and Engineering at the University of Ottawa, who also played an important role in my research work. I am grateful for his guidance throughout this research. As my thesis reader, his insightful suggestions were invaluable in the production of this work.

I also extend my thanks to my committee, Dr. Abdeslam En-Nouaary, Dr. Dhrubajyoti Goswami, Dr. Hon F. Li, and Dr. Abdellatif Obaid (From UQAM), my external examiner, for gracefully accepting to review and comment this work.

Finally, words cannot express the thanks I owe to my parents and my wife for their encouragement and support.

# Contents

| Li | st of          | Figures                                                                          | Ж          |

|----|----------------|----------------------------------------------------------------------------------|------------|

| Li | List of Tables |                                                                                  |            |

| 1  | Intr           | roduction                                                                        | 1          |

|    | 1.1            | Motivation                                                                       | ]          |

|    | 1.2            | Research Hypothesis                                                              | $\epsilon$ |

|    | 1.3            | Thesis Approach                                                                  | 8          |

|    | 1.4            | Thesis Contributions                                                             | 8          |

|    |                | 1.4.1 Contribution 1: Early Stages V&V methodology                               | 8          |

|    |                | 1.4.2 Contribution 2: Classification of Timed Scenario Languages                 | 10         |

|    |                | 1.4.3 Contribution 3: Use Case Maps as a Property Description Language           | 10         |

|    |                | 1.4.4 Contribution 4: Illustrative Experiments of Early Stages V&V methodology . | 10         |

|    | 1.5            | Issues not Addressed in this Thesis                                              | 10         |

|    | 1.6            | Thesis Outline                                                                   | 10         |

| 2  | Bas            | sic Definitions and Notations                                                    | 12         |

|    | 2.1            | Introduction to Use Case Maps                                                    | 12         |

|    |                | 2.1.1 Philosophy of UCMs                                                         | 12         |

|    |                | 2.1.2 UCM Basic Notation                                                         | 13         |

|    |                | 2.1.3 UCM Component Notation                                                     | 16         |

|    |                | 2.1.4 Running Example: A simple Telephone System                                 | 18         |

|    |                | 2.1.5 Use Case Maps Properties                                                   | 20         |

|    |                | 2.1.6 Use Case Maps Semantics                                                    | 21         |

|    |                | 2.1.7 UCM Tools                                                                  | 24         |

|    | 2.2            | Introduction to Abstract State Machines                                          | 26         |

|    |                | 2.2.1 ASM Thesis                                                                 | 26         |

|    |                | 2.2.2 ASM Program                                                                | 28         |

|    |                | 2.2.3 Multi-Agent ASMs                                                           | 30         |

|    |                | 2.2.4 ASM Properties                                                             | 31         |

|    |                | 2.2.5 ASM Tools                                                                  | 31         |

|    | 2.3            | Chapter Summary                                                                  | 35         |

| 3 | Stat | te of the Art                                              |

|---|------|------------------------------------------------------------|

|   | 3.1  | Scenario Notations                                         |

|   | 3.2  | Scenarios Integration                                      |

|   | 3.3  | Classifications of Scenario Notations                      |

|   | 3.4  | Formal Semantics                                           |

|   | 3.5  | Formal Description Techniques                              |

|   |      | 3.5.1 LOTOS                                                |

|   |      | 3.5.2 SDL                                                  |

|   | 3.6  | UCM Validation: SPEC-Value Approach                        |

|   |      | 3.6.1 Testing Approach in SPEC-VALUE                       |

|   |      | 3.6.2 UCM-Oriented Testing Patterns                        |

|   | 3.7  | Chapter Summary                                            |

| 4 | An   | ASM Operational Semantics for Use Case Maps 50             |

|   | 4.1  | ASM-based UCM Formal Syntax                                |

|   |      | 4.1.1 Use Case Maps Formal Syntax                          |

|   |      | 4.1.2 ASM Signature of UCM Constructs                      |

|   | 4.2  | ASM-based UCM Formal Semantics                             |

|   |      | 4.2.1 Multi Agent ASM-based Solution                       |

|   |      | 4.2.2 Single Agent Non Deterministic Interleaving Solution |

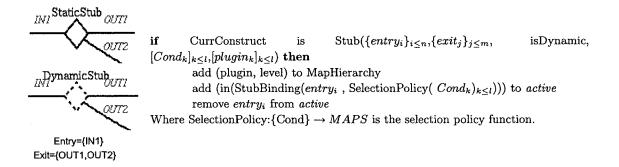

|   | 4.3  | ASM-UCM Simulation Engine                                  |

|   |      | 4.3.1 UCM Specification                                    |

|   |      | 4.3.2 Data Structures                                      |

|   |      | 4.3.3 ASM Program                                          |

|   | 4.4  | General Discussion                                         |

|   |      | 4.4.1 Interpretation vs. Compilation                       |

|   |      | 4.4.2 Language Evolution                                   |

|   |      | 4.4.3 Semantic Variations                                  |

|   |      | 4.4.4 Extraction of Information                            |

|   | 4.5  | AsmL Specification of the Simple Telephony System 67       |

|   | 4.6  | Chapter Summary                                            |

| 5 | Ear  | rly Stages Validation Approach 71                          |

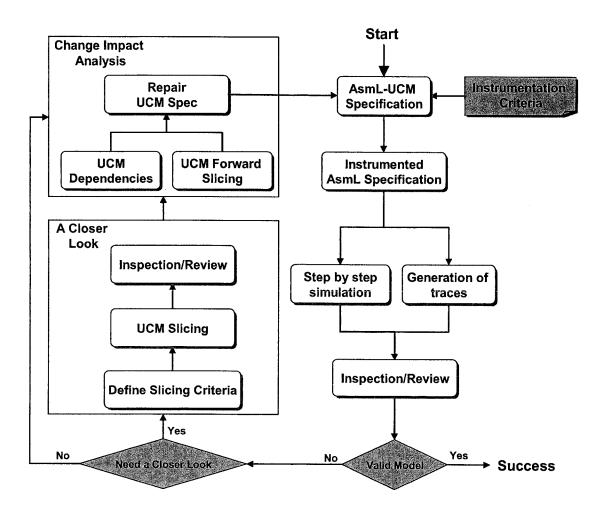

| • | 5.1  | High Level Validation Approach                             |

|   |      | 5.1.1 Instrumenting the ASM-UCM simulation engine          |

|   |      | 5.1.2 Simulation and Generation of Traces                  |

|   |      | 5.1.3 Inspection of Traces                                 |

|   |      | 5.1.4 Fixing Errors and/or Design Improvement              |

|   | 5.2  | Slicing Use Case Maps Requirement Specifications           |

|   |      | 5.2.1 Traditional Program Slicing                          |

|   |      | 5.2.2 Related Work: Model Based Slicing                    |

|   |     | 5.2.3  | UCM Slices                                            | 77                                |

|---|-----|--------|-------------------------------------------------------|-----------------------------------|

|   |     | 5.2.4  | UCM Slicing Criteria                                  | 78                                |

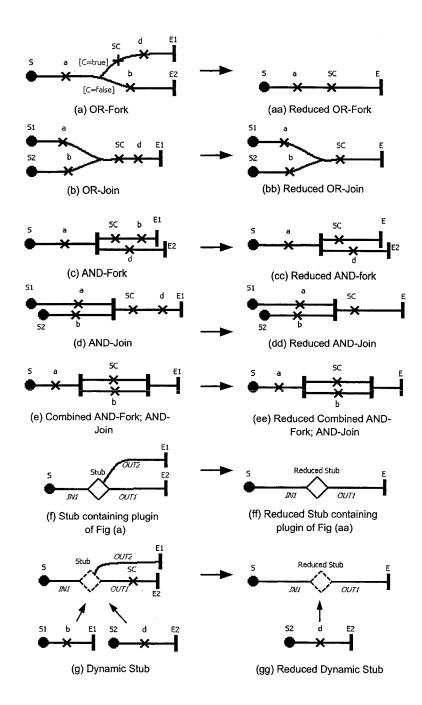

|   |     | 5.2.5  | Slicing UCM Constructs                                | 79                                |

|   |     | 5.2.6  | UCM Backward Slicing                                  | 79                                |

|   |     | 5.2.7  | Solving the Reachability Expression                   | 82                                |

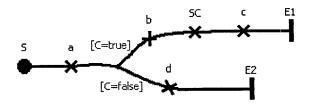

|   |     | 5.2.8  | UCM Data Flow                                         | 82                                |

|   |     | 5.2.9  | UCM Forward Slicing                                   | 84                                |

|   | 5.3 | Chang  | e Impact Analysis                                     | 84                                |

|   |     | 5.3.1  | UCM Scenario Dependencies                             | 85                                |

|   |     | 5.3.2  | Ripple Effect Analysis                                | 87                                |

|   |     | 5.3.3  | Related Work: Model Based Change Impact Analysis      | 88                                |

|   | 5.4 | Applyi | ing the Validation Approach                           | 89                                |

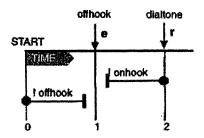

|   |     | 5.4.1  | Simple Telephone System Traces                        | 89                                |

|   |     | 5.4.2  | CND Feature upgrade: A Closer Look                    | 91                                |

|   |     | 5.4.3  | Simple Telephone System: Change Impact Analysis       | 92                                |

|   | 5.5 | Chapte | er Summary                                            | 93                                |

| c | m:  | 1 0    |                                                       |                                   |

| 6 |     |        | enario Languages                                      | 94                                |

|   | 6.1 |        | ation Criteria                                        | 94                                |

|   |     | 6.1.1  | Timed Action/Event Enabling                           | 94                                |

|   |     | 6.1.2  | Instantaneous (atomic) vs. Durational Actions         | 95                                |

|   |     | 6.1.3  | Relative vs. Absolute Time                            | 95                                |

|   |     | 6.1.4  | System Clocks: Local vs. Global, Physical vs. Logical | 95                                |

|   |     | 6.1.5  | Urgency                                               | 96                                |

|   |     | 6.1.6  | Time Domain                                           | 97                                |

|   |     | 6.1.7  | Time Representation/Measurement                       | 98                                |

|   |     | 6.1.8  | Timed Constructs/Constraints                          | 98                                |

|   |     | 6.1.9  | Formal vs. Semi-formal Semantics                      | 98                                |

|   |     |        | Time Analysis and Verification                        | 98                                |

|   | 6.2 |        | Specification Executability and tool support          | 99                                |

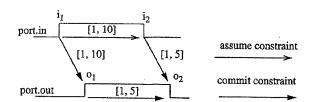

|   | 0.2 | 6.2.1  | of Selected Timed Scenarios Languages                 | 99                                |

|   |     | 6.2.2  | Time-Enriched LSCs                                    | 99                                |

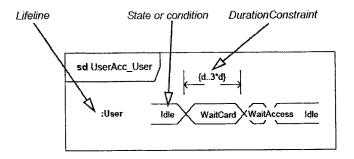

|   |     | 6.2.3  | Timed Annotations in UML                              | <ul><li>103</li><li>104</li></ul> |

|   |     | 6.2.4  | Time in SDL                                           |                                   |

|   |     | 6.2.5  | Real-time Object Oriented Modeling (ROOM)             | <ul><li>114</li><li>116</li></ul> |

|   |     | 6.2.6  | Visual Timed Event Scenarios(VTS)                     | 116                               |

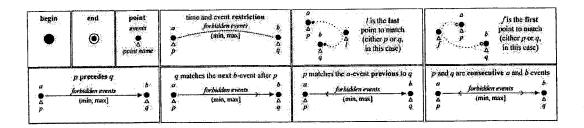

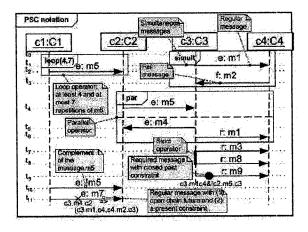

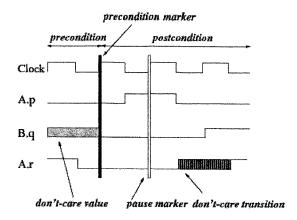

|   |     | 6.2.7  | Property Sequence Chart (PSC)                         | 117                               |

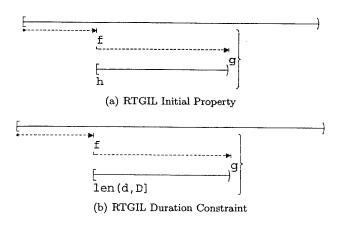

|   |     | 6.2.8  | Real-time Graphical Interval Logic (RTGIL)            | 117                               |

|   |     | 6.2.9  | Timeline Notation                                     | 119                               |

|   |     |        | Regular Timing Diagrams (RTD)                         | 110                               |

|   |     |        |                                                       |                                   |

|   |     |        | Action Diagrams (Timing Diagrams)                                          |     |

|---|-----|--------|----------------------------------------------------------------------------|-----|

|   |     |        | Timed Behavior Trees                                                       |     |

|   |     | 6.2.13 | Somé's Scenarios                                                           | 121 |

|   | 6.3 | Summ   | ary of Evaluation of the Selected Timed Scenarios Languages                | 122 |

|   | 6.4 | Chapte | er Summary                                                                 | 129 |

| 7 | Tim | ed Use | e Case Maps                                                                | 130 |

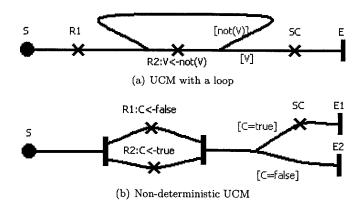

|   | 7.1 | Modeli | ing Time in UCMs: Decision points                                          | 131 |

|   | 7.2 | Syntax | c of Timed Use Case Maps                                                   | 133 |

|   | 7.3 | Forma  | l Semantics of Timed UCM Models in Terms of CTS                            | 135 |

|   |     | 7.3.1  | Clocked Transition Systems                                                 | 135 |

|   |     | 7.3.2  | CTS-based Semantics of Timed UCM                                           | 136 |

|   |     | 7.3.3  | CTS Transition Relation                                                    | 137 |

|   |     | 7.3.4  | Concurrency Model and Time Evolution                                       | 139 |

|   |     | 7.3.5  | Step Semantics for Interleaving Model                                      | 140 |

|   |     | 7.3.6  | Step Semantics for True Concurrency Model                                  | 142 |

|   |     | 7.3.7  | Example of CTS run                                                         | 145 |

|   | 7.4 | Forma  | l Semantics of Timed UCM Models in Terms of ASM                            | 146 |

|   |     | 7.4.1  | An AsmL Implementation of Timed UCM Semantics                              | 147 |

|   |     | 7.4.2  | Applying AsmL Semantics to the Simplified Telephone System (timed version) | 148 |

|   | 7.5 | Forma  | l Semantics of Timed UCM Models in Terms of Timed Automata                 | 153 |

|   |     | 7.5.1  | Timed Automata                                                             | 153 |

|   |     | 7.5.2  | Timed Automaton Formal Syntax and Semantics                                | 152 |

|   |     | 7.5.3  | Timed Automaton Clock Region                                               | 153 |

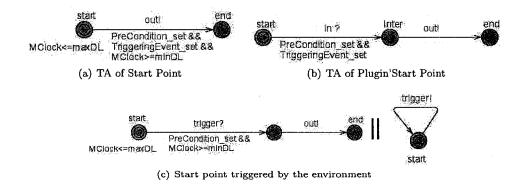

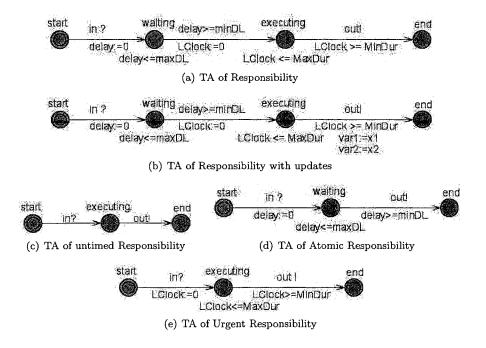

|   |     | 7.5.4  | TA-based Semantics of Timed UCM Constructs                                 | 155 |

|   |     | 7.5.5  | Applying TA-based Semantics to the Simple Telephony System                 | 158 |

|   |     | 7.5.6  | Limitations                                                                | 161 |

|   | 7.6 | Chapt  | er Summary                                                                 | 161 |

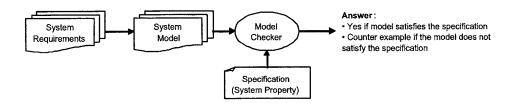

| 8 | Mo  | del Ch | ecking Timed UCM Specifications                                            | 163 |

|   | 8.1 | Model  | Checking                                                                   | 163 |

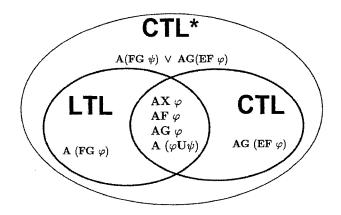

|   |     | 8.1.1  | Temporal Logics                                                            | 164 |

|   |     | 8.1.2  | Real-time Temporal Logic                                                   | 168 |

|   |     | 8.1.3  | State Space Explosion                                                      | 169 |

|   |     | 8.1.4  | Model Checking Tools                                                       | 170 |

|   |     | 8.1.5  | The Model Checker UPPAAL                                                   | 172 |

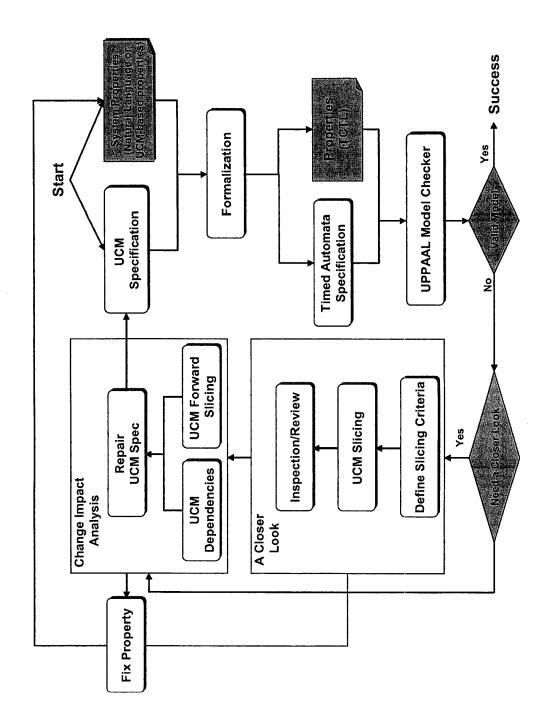

|   | 8.2 | Early  | Stages Verification Approach                                               | 178 |

|   | 8.3 | Optim  | izing TA Specifications                                                    | 180 |

|   |     | 8.3.1  | Sequential vs. Parallel Control Flows                                      | 180 |

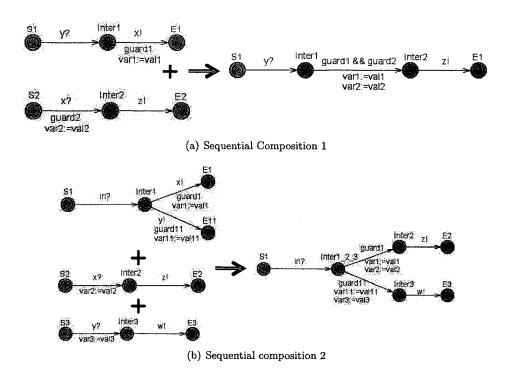

|   |     | 8.3.2  | Sequential Composition of Timed Automata                                   | 180 |

|   | Q 1 | Marin  | and Progress in HPPAAT                                                     | 100 |

|    | 8.5                                         | Applying Early Stages Verification Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 182                                                                                                   |

|----|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

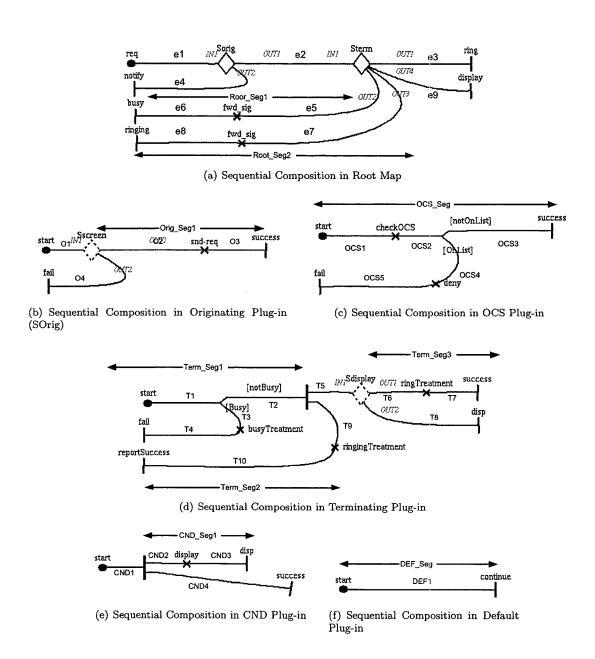

|    |                                             | 8.5.1 Simple Telephone System Decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 182                                                                                                   |

|    |                                             | 8.5.2 Simple Telephone System: Network of Timed Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 184                                                                                                   |

|    |                                             | 8.5.3 Simple Telephone System: Property Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 189                                                                                                   |

|    | 8.6                                         | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 190                                                                                                   |

| 9  | Use                                         | Case Maps as A Property Specification Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 192                                                                                                   |

|    | 9.1                                         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 192                                                                                                   |

|    | 9.2                                         | Specification Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 194                                                                                                   |

|    |                                             | 9.2.1 Untimed Specification Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 194                                                                                                   |

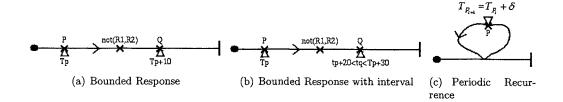

|    |                                             | 9.2.2 Timed Specification Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 195                                                                                                   |

|    | 9.3                                         | Use Case Maps Property Pattern System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 197                                                                                                   |

|    |                                             | 9.3.1 Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 197                                                                                                   |

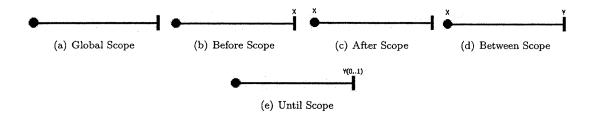

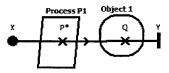

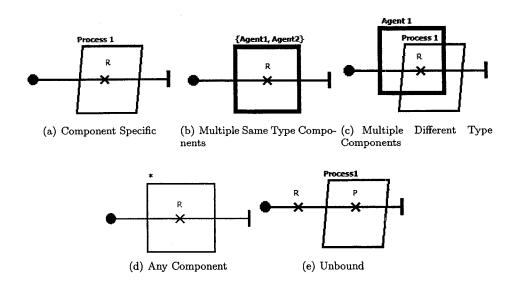

|    |                                             | 9.3.2 Specification Pattern Scopes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 200                                                                                                   |

|    | 9.4                                         | Architectural Real-time Temporal Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 204                                                                                                   |

|    |                                             | 9.4.1 Architectural TCTL (ArTCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 205                                                                                                   |

|    | 9.5                                         | Applying Property Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 206                                                                                                   |

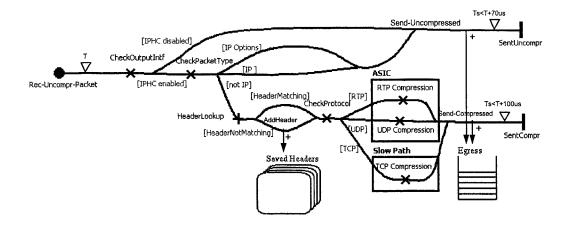

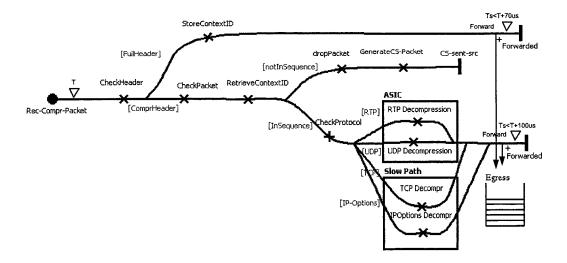

|    |                                             | 9.5.1 Case Study: IP Header Compression Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 206                                                                                                   |

|    |                                             | 9.5.2 IPHC System Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 209                                                                                                   |

|    | 9.6                                         | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 210                                                                                                   |

|    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 10 | Exp                                         | periments with Early Stages Validation and Verification Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 212                                                                                                   |

| 10 |                                             | Periments with Early Stages Validation and Verification Methodology  Case Study 1: IP Multicast Routing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>212</b> 212                                                                                        |

| 10 |                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 10 |                                             | Case Study 1: IP Multicast Routing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 212                                                                                                   |

| 10 |                                             | Case Study 1: IP Multicast Routing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 212<br>212                                                                                            |

| 10 |                                             | Case Study 1: IP Multicast Routing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul><li>212</li><li>212</li><li>214</li></ul>                                                         |

| 10 |                                             | Case Study 1: IP Multicast Routing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul><li>212</li><li>212</li><li>214</li><li>218</li></ul>                                             |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>212</li> <li>212</li> <li>214</li> <li>218</li> <li>221</li> <li>224</li> <li>230</li> </ul> |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification                                                                                                                                                                                                                                                                                       | <ul> <li>212</li> <li>212</li> <li>214</li> <li>218</li> <li>221</li> <li>224</li> <li>230</li> </ul> |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store                                                                                                                                                                                                                                        | <ul> <li>212</li> <li>212</li> <li>214</li> <li>218</li> <li>221</li> <li>224</li> <li>230</li> </ul> |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation                                                                                                                                                                                              | 212<br>214<br>218<br>221<br>224<br>230<br>230                                                         |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation  10.2.4 UPPAAL Specification and Property Verification                                                                                                                                       | 212<br>214<br>218<br>221<br>224<br>230<br>230<br>233                                                  |

| 10 | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation                                                                                                                                                                                              | 212<br>212<br>214<br>218<br>221<br>224<br>230<br>230<br>233<br>236                                    |

|    | 10.1                                        | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation  10.2.4 UPPAAL Specification and Property Verification                                                                                                                                       | 212<br>214<br>218<br>221<br>224<br>230<br>230<br>233<br>236<br>240                                    |

|    | 10.1<br>10.2<br>10.3<br>Con<br>11.1         | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation  10.2.4 UPPAAL Specification and Property Verification  Lessons Learned  aclusions and Future Work  Hypothesis and Contributions of the Thesis                                               | 212<br>214<br>218<br>221<br>224<br>230<br>230<br>233<br>236<br>240<br>245                             |

|    | 10.1<br>10.2<br>10.3<br>Con<br>11.1<br>11.2 | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation  10.2.4 UPPAAL Specification and Property Verification  Lessons Learned  aclusions and Future Work  Hypothesis and Contributions of the Thesis  Integrating Early Stages V&V with SPEC-VALUE | 212<br>214<br>218<br>221<br>224<br>230<br>230<br>233<br>236<br>240<br>245                             |

|    | 10.1<br>10.2<br>10.3<br>Con<br>11.1<br>11.2 | Case Study 1: IP Multicast Routing Protocol  10.1.1 Introduction to IP Multicast  10.1.2 IP Multicast: UCM Scenarios Specifications  10.1.3 AsmL Specification of IP Multicast Protocol  10.1.4 IP Multicast Protocol Scenarios Generation  10.1.5 UPPAAL Specification and Property Verification  Case Study 2: Online Store  10.2.1 Online Store: System Overview and UCM Specification  10.2.2 AsmL Specification of the Online Store  10.2.3 Online Store Scenarios Generation  10.2.4 UPPAAL Specification and Property Verification  Lessons Learned  aclusions and Future Work  Hypothesis and Contributions of the Thesis                                               | 212<br>214<br>218<br>221<br>224<br>230<br>230<br>233<br>236<br>240<br>245<br><b>247</b>               |

# List of Figures

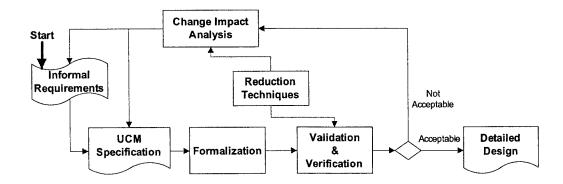

| 1.1  | Early Stages Validation and Verification Approach                            | 8  |

|------|------------------------------------------------------------------------------|----|

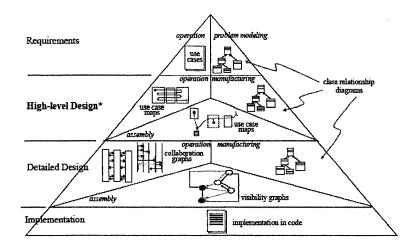

| 2.1  | A Suite of Design Models [BC96]                                              | 13 |

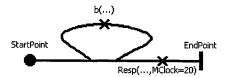

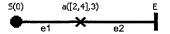

| 2.2  | A Simple UCM [MAB+01]                                                        | 13 |

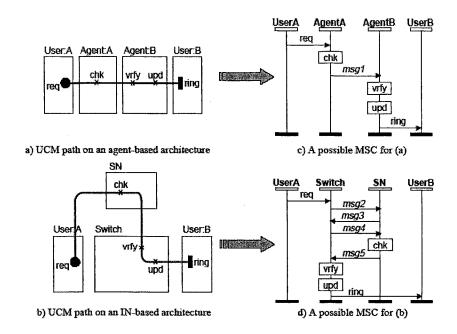

| 2.3  | UCM Path Bound to Two Different Architectures, and Potential MSCs [MAB+01] . | 14 |

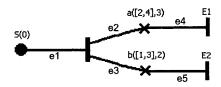

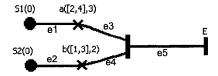

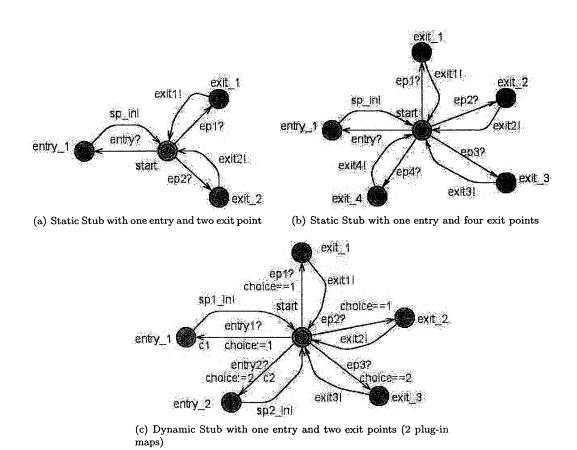

| 2.4  | Structuring Scenarios                                                        | 15 |

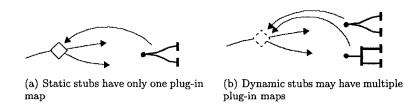

| 2.5  | Stubs and Plug-in Maps                                                       | 15 |

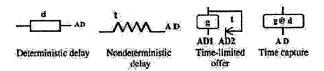

| 2.6  | UCM Timed Notation                                                           | 16 |

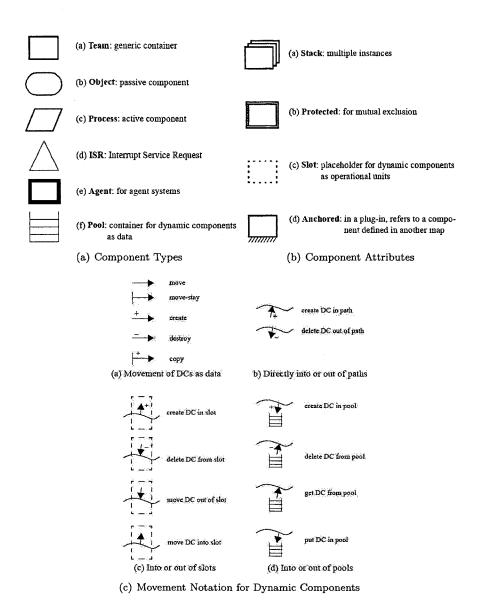

| 2.7  | Component Types, Attributes and Movement Notation [Amy01b]                   | 17 |

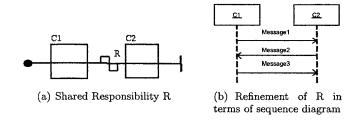

| 2.8  | Shared Responsibility and One Possible Refinement                            | 18 |

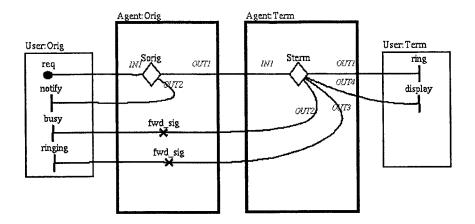

| 2.9  | Simple Telephone System Root Map                                             | 19 |

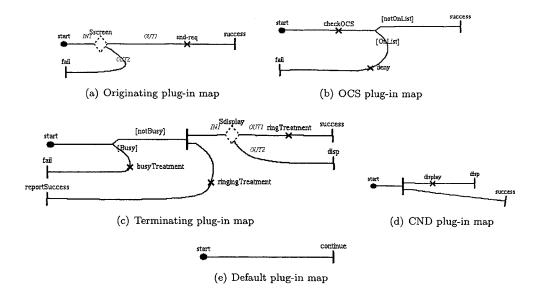

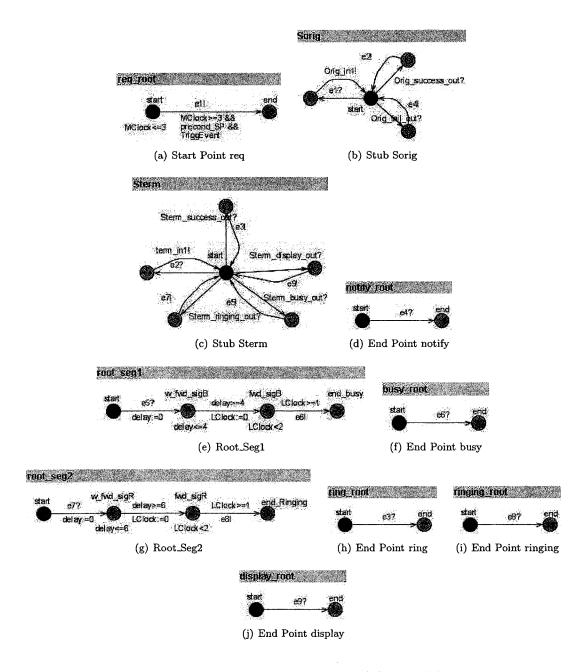

| 2.10 | Simple Telephone System Plug-in Maps                                         | 20 |

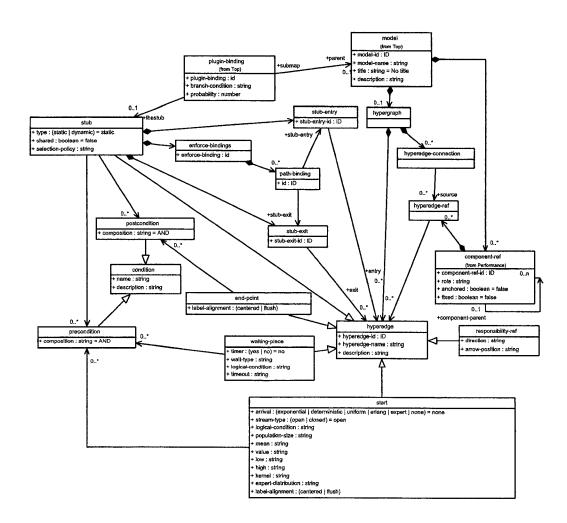

| 2.11 | UCM Path Meta-Model [Zen05, Jia05]                                           | 22 |

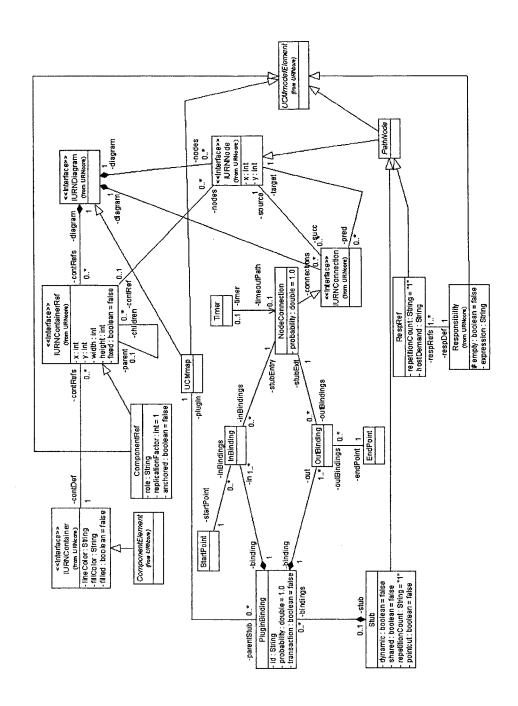

| 2.12 | UCM Path Meta-Model [jUC07]                                                  | 23 |

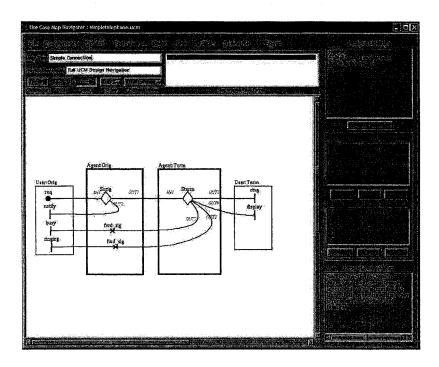

| 2.13 | UCMNav GUI                                                                   | 24 |

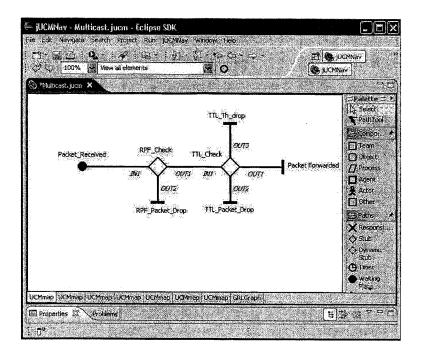

| 2.14 | jUCMNav GUI                                                                  | 26 |

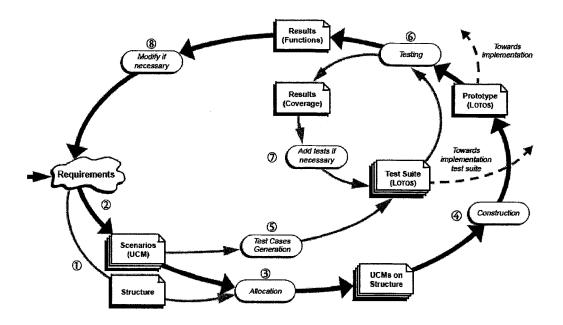

| 3.1  | Specification-Validation Approach with LOTOS and UCMs (SPEC-VALUE) [Amy01a]  | 48 |

| 4.1  | A UCM decomposition into five agents                                         | 53 |

| 4.2  | Multi Agent Solution: Rule of Start Point                                    | 54 |

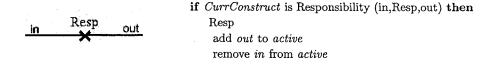

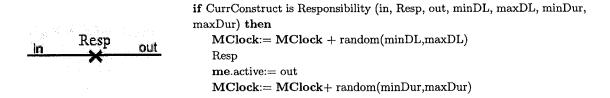

| 4.3  | Multi Agent Solution: Rule of Responsibility                                 | 54 |

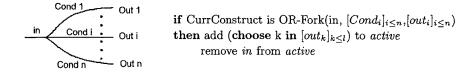

| 4.4  | Multi Agent Solution: Rule of OR-Fork                                        | 54 |

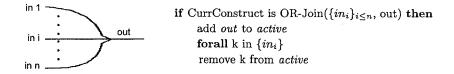

| 4.5  | Multi Agent Solution: Rule of OR-Join                                        | 55 |

| 4.6  | Multi Agent Solution: Rule of AND-Fork                                       | 55 |

| 4.7  | Multi Agent Solution: Rule of AND-Join                                       | 55 |

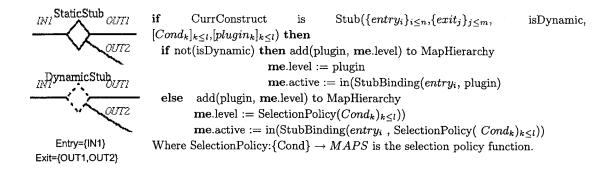

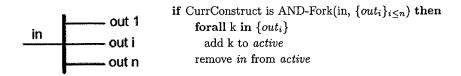

| 4.8  | Multi Agent Solution: Rule of Stub                                           | 56 |

| 4.9  | Multi Agent Solution: Rule of End Point                                      | 56 |

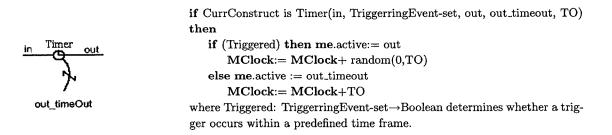

| 4.10 | Multi Agent Solution: Rule of Timer                                          | 57 |

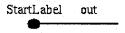

| 4.11 | Single Agent Solution: Rule of Start Point                                   | 57 |

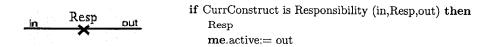

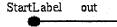

|      | Single Agent Solution: Rule of Responsibility                                | 58 |

| 4.13 | Single Agent Solution: Rule of OR-Fork                                       | 58 |

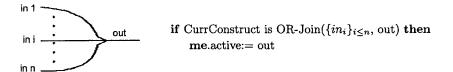

|      | Single Agent Solution: Rule of OR-Join                                       | 58 |

| 4.15 | Single Agent Solution: Rule of AND-Fork                                      | 59 |

| 4.16 | Single Agent Solution: Rule of AND-Join                   | 59  |

|------|-----------------------------------------------------------|-----|

| 4.17 | Single Agent Solution: Rule of Stub                       | 59  |

| 4.18 | Single Agent Solution: Rule of End Point                  | 60  |

| 4.19 | Single Agent Solution: Rule of Timer                      | 60  |

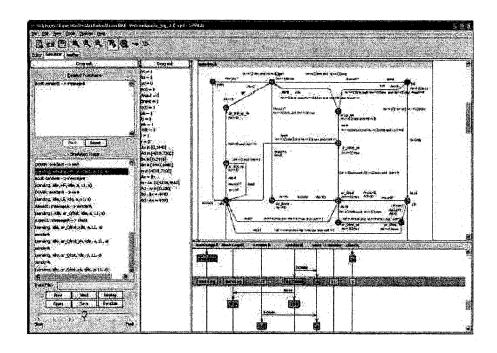

| 4.20 | ASM-UCM Simulation Engine Architecture                    | 61  |

| 4.21 | Multi-Agent Solution: ASM-UCM program                     | 65  |

| 4.22 | Single-Agent Solution: ASM-UCM program                    | 66  |

| 4.23 | AsmL Default Plug-in Map                                  | 68  |

| 4.24 | AsmL: OCS Plug-in Map                                     | 68  |

| 4.25 | AsmL: Stub SOrig                                          | 68  |

| 4.26 | AsmL: Stub Sterm                                          | 69  |

| 4.27 | AsmL implementation of the Root Map                       | 69  |

| 5.1  | Early Stages Validation Approach                          | 72  |

| 5.2  | UCM Constructs and its Reduced Form                       | 80  |

| 5.3  | Responsibilities Updating Boolean Variables               | 83  |

| 5.4  | UCM Data Flow: Special Cases                              | 84  |

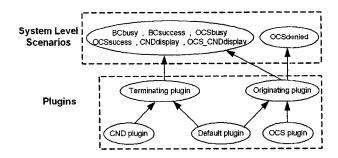

| 5.5  | System Scenarios Definitions                              | 86  |

| 5.6  | Scenario Containment Dependency                           | 87  |

| 5.7  | Temporal Dependencies                                     | 87  |

| 5.8  | CND Trace (with busy = False)                             | 89  |

| 5.9  | CND Trace (with busy = True)                              | 89  |

| 5.10 | CND-OCS Trace (with InOCSList = False)                    | 90  |

| 5.11 | CND-OCS Trace (with InOCSList = True)                     | 90  |

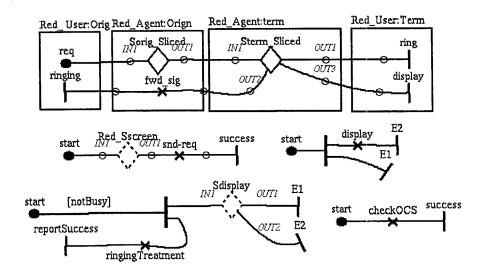

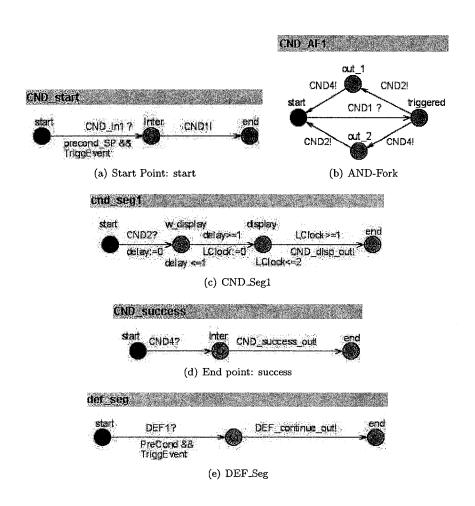

| 5.12 | Simple Telephony System Slice with Respect to SC: display | 91  |

| 5.13 | Reachability Expression for Responsibility display        | 91  |

| 5.14 | Telephony System Slice for SC=AND-Fork                    | 92  |

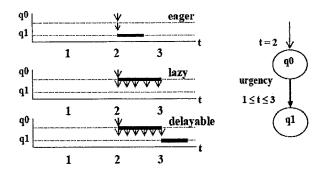

| 6.1  | Transition Urgencies [Sin04]                              | 97  |

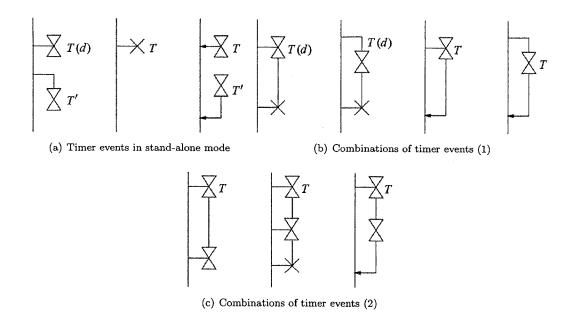

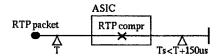

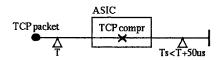

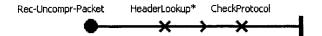

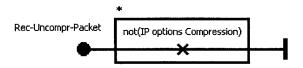

| 6.2  | · · · · · · · · · · · · · · · · · · ·                     | 100 |

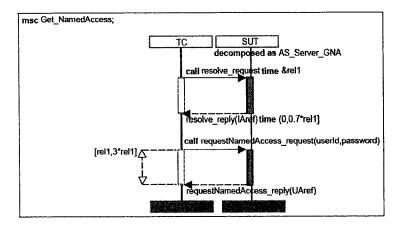

| 6.3  | • •                                                       | 101 |

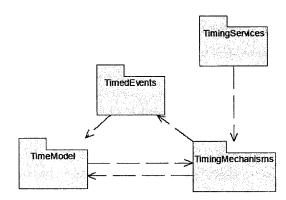

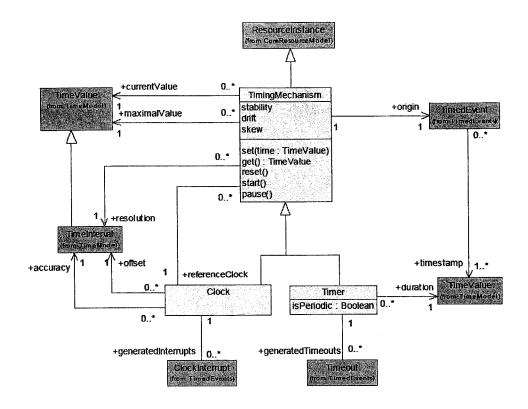

| 6.4  | The Modules of the Time Domain Model [OMG02]              | 107 |

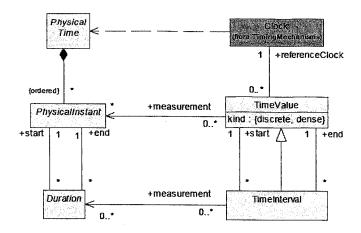

| 6.5  | - , , , ,                                                 | 108 |

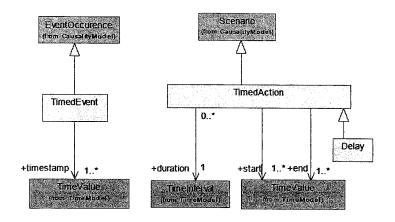

| 6.6  | Timing Mechanisms In UML/SPT [OMG02]                      | 109 |

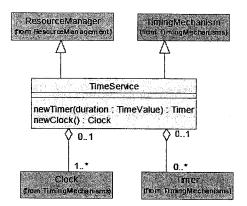

| 6.7  | Timed Action and Timed Event Concepts [OMG02]             | 110 |

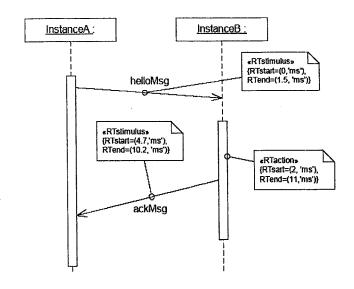

| 6.8  | Timing Service Concepts [OMG02]                           | 110 |

| 6.9  | Time Annotations in Sequence Diagrams [OMG02]             | 111 |

| 6.10 | TURTLE Temporal Operators                                 | 113 |

| 6.11 | Timing Diagram Example [OMG05]                            | 115 |

| 6.12 | VTS Graphical Notation [ABKO04]                           | 117 |

| 6.13 | Property Sequence Chart [AIP06]                           | 117 |

| 6.14 | RTGIL Examples [MRK <sup>+</sup> 97]                      | 118 |

| 6.15 | Timeline example [SHE01]                                     | 119 |

|------|--------------------------------------------------------------|-----|

| 6.16 | Synchronous Regular Timing Diagram [AEKN01]                  | 120 |

| 6.17 | Example of Action Diagram [KC98]                             | 120 |

| 6.18 | Timed BT Node [LKR07]                                        | 121 |

| 7.1  | Absolute Time Constraint in Presence of UCM Loop             | 132 |

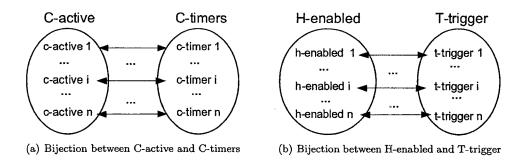

| 7.2  | Bijections Functions within V                                | 137 |

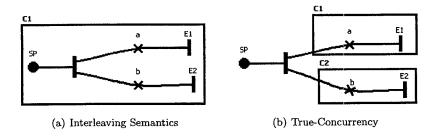

| 7.3  | Concurrency Semantics                                        | 139 |

| 7.4  | Urgent Responsibility                                        | 142 |

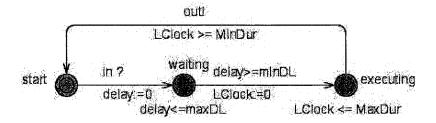

| 7.5  | Delayed Responsibility                                       | 142 |

| 7.6  | Parallel Flows                                               | 143 |

| 7.7  | Synchronization of Flows                                     | 143 |

| 7.8  | Parallel Flow Execution in True Concurrency Mode             | 146 |

| 7.9  | ASM Rule of Timed Start Point                                | 146 |

| 7.10 | ASM Rule of Timed Responsibility                             | 147 |

| 7.11 | ASM Rule of Timer                                            | 147 |

| 7.12 | Timed UCMConstruct Data Structure                            | 147 |

| 7.13 | Timed ASM-UCM Program                                        | 149 |

| 7.14 | Timed Trace                                                  | 150 |

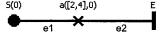

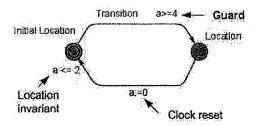

| 7.15 | Example of a Timed Automaton                                 | 152 |

| 7.16 | Clock Region Example                                         | 154 |

| 7.17 | TA Templates for Start Points                                | 155 |

| 7.18 | TA Templates for Responsibilities                            | 156 |

| 7.19 | TA Templates of UCM Constructs                               | 157 |

| 7.20 | TA Templates for Stubs of the Simple Telephone System        | 159 |

| 7.21 | UPPAAL Textual Implementation of the Simple Telephone System | 160 |

| 7.22 | Responsibility that Supports Loops                           | 161 |

| 8.1  | The Model Checking Approach                                  | 164 |

| 8.2  | Basic CTL Operators                                          | 166 |

| 8.3  | Expressiveness of the Three Temporal Logics                  | 168 |

| 8.4  | The Simulator in the UPPAAL GUI                              | 172 |

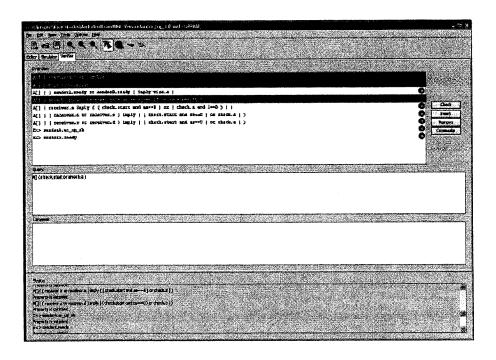

| 8.5  | The Verifier in the UPPAAL GUI                               | 173 |

| 8.6  | The Symbolic State Space Exploration Algorithm               | 175 |

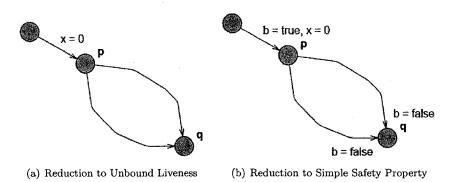

| 8.7  | Reduction to Unbound Liveness                                | 176 |

| 8.8  | Reduction to Reachability with Test Automaton                | 176 |

| 8.9  | Early Stages Verification Approach                           | 179 |

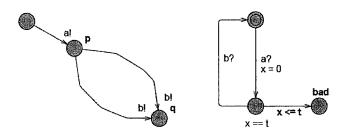

| 8.10 | UCM Parallel Flows Decomposition                             | 180 |

| 8.11 | TA Sequential Composition                                    | 181 |

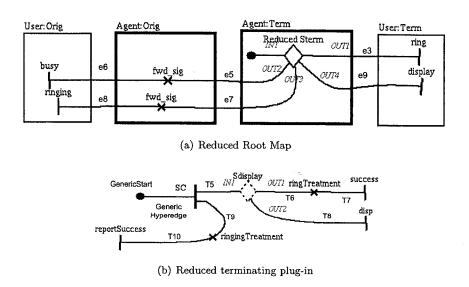

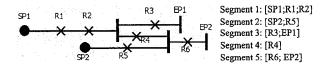

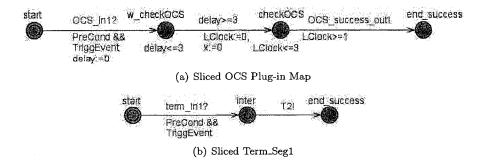

| 8.12 | Sequential Composition of Simple Telephone System            | 183 |

| 8.13 | UPPAAL Implementation of the Root Map                        | 185 |

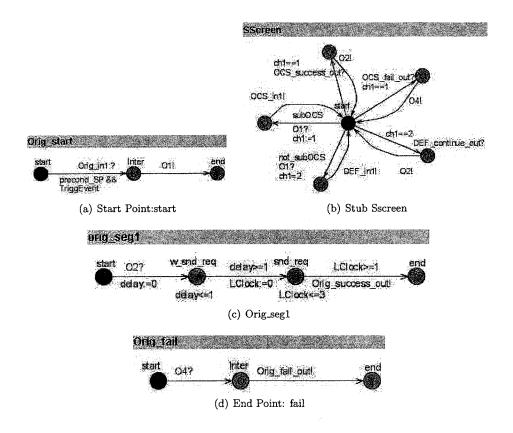

| 8.14 | UPPAAL Implementation of Originating Plug-in                 | 186 |

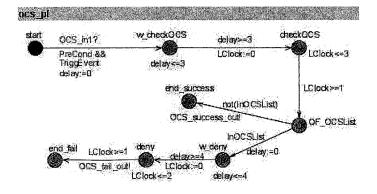

| 8.15 UPPAAL Implementation of OCS Plug-in                                     | 186           |

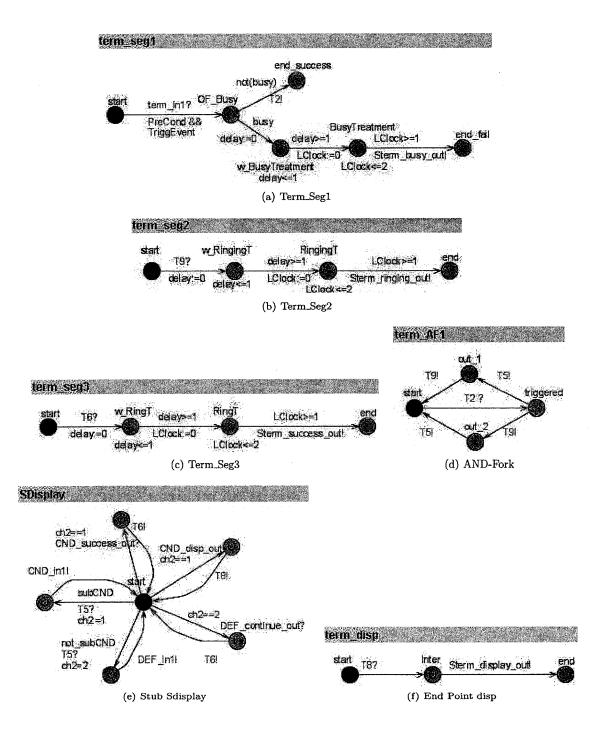

|-------------------------------------------------------------------------------|---------------|

| 8.16 UPPAAL Implementation of the Terminating Plug-in $\ \ldots$ .            | 187           |

| 8.17 UPPAAL Implementation of CND and DEFAULT Plug-in Ma                      | ps 188        |

| 8.18 Sliced UPPAAL Implementation of OCS and Terminating Plus                 | g-in Maps 190 |

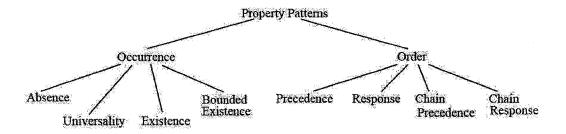

| 9.1 Pattern Hierarchy by Dwyer et al. [DAC99] $\ \ldots \ \ldots \ \ldots$    | 193           |

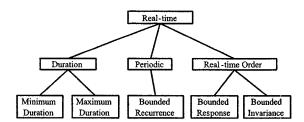

| 9.2 Real-Time Specification Patterns by Konrad et al                          | 195           |

| 9.3 Timed Automaton for Time-bounded Existence                                | 196           |

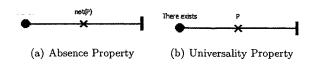

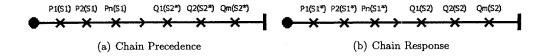

| 9.4 Absence and Universality                                                  | 198           |

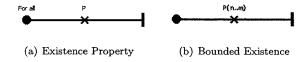

| 9.5 Existence and Bounded Existence                                           | 198           |

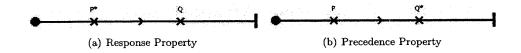

| 9.6 Response and Precedence $\dots$                                           | 199           |

| 9.7 Chain Precedence and Chain Response                                       | 199           |

| 9.8 Separated Responses                                                       | 200           |

| 9.9 Temporal Scopes                                                           | 200           |

| 9.10 Examples of Timing Requirements $\dots \dots \dots$ .                    | 202           |

| 9.11 Three Scopes: Occurrence, Temporal and Architecture                      | 202           |

| 9.12 Architectural Scopes                                                     | 203           |

| 9.13 Architectural Containment Dependency                                     | 204           |

| 9.14 PPP and IPCP Negotiation                                                 | 207           |

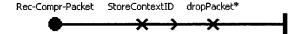

| 9.15 IPHC: Compression Scenario $\ \ldots \ \ldots \ \ldots \ \ldots$         | 208           |

| 9.16 IPHC: Decompression Scenario $\hdots$                                    | 208           |

| 9.17 Bounded Existence Property Satisfying IPHC Design                        | 209           |

| 9.18 Bounded Existence Property Violating IPHC Design $\ \ldots \ \ldots$     | 209           |

| 9.19 Response Property Satisfying IPHC Design                                 | 210           |

| 9.20 Absence Property Satisfying IPHC Design                                  | 210           |

| 9.21 Precedence Property Violating IPHC Design $\ \ldots \ \ldots \ \ldots$   | 210           |

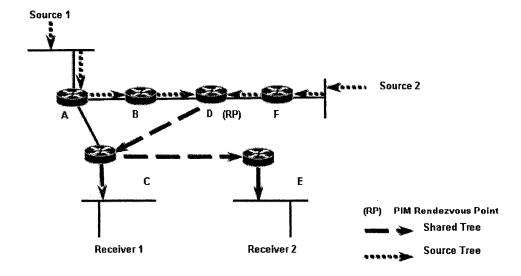

| 10.1 Example of a Multicast Enabled Network [Inc04] $\ \ldots \ \ldots$       | 213           |

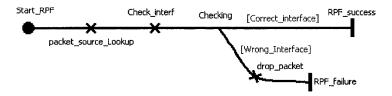

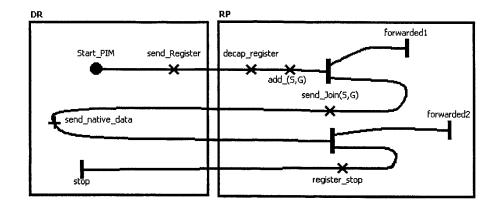

| 10.2 RPF Check Plug-in Map                                                    | 214           |

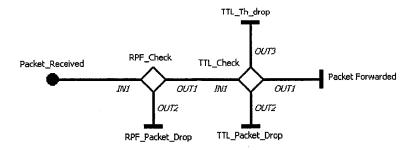

| 10.3 Multicast Forwarding                                                     | 215           |

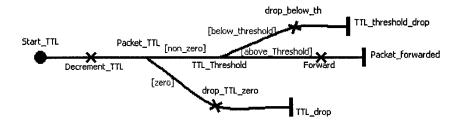

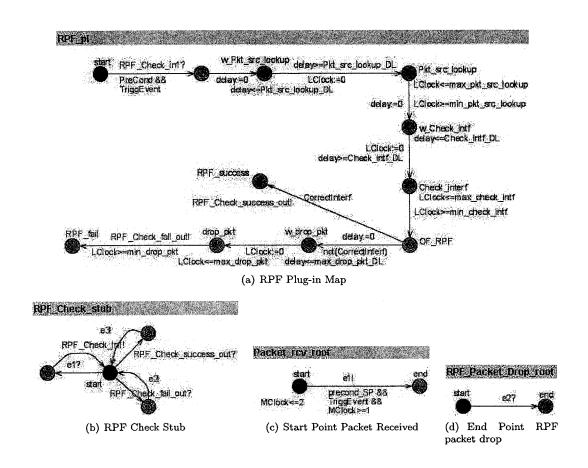

| 10.4 TTL Check Plug-in Map                                                    |               |

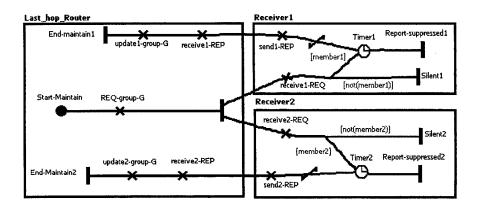

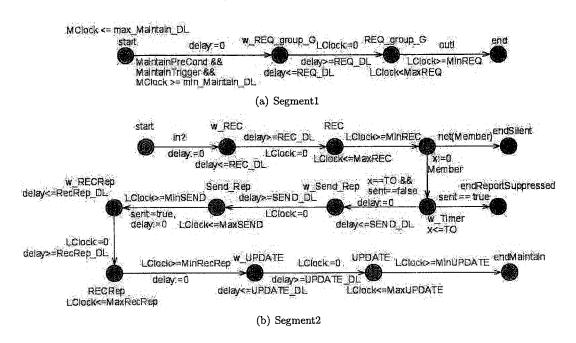

| 10.5 IP Multicast Group Membership Maintenance                                |               |

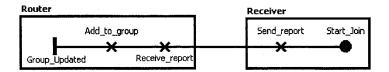

| 10.6 Join IP Multicast Group                                                  | 216           |

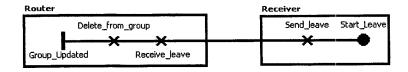

| 10.7 Leave IP Multicast Group                                                 | 217           |

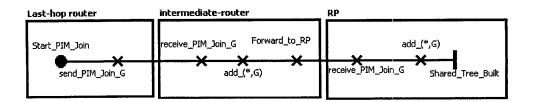

| 10.8 PIM-SM Join                                                              | 217           |

| 10.9 PIM-SM Sender Registration                                               | 218           |

| $10.10 \mathrm{AsmL}$ Implementation of the Multicast Forwarding Scenario .   | 219           |

| $10.11 \mathrm{AsmL}$ Implementation of the Group Maintenance Scenario        |               |

| $10.12 \mathrm{AsmL}$ Implementation of PIM-SM Sender Registration            |               |

| 10.13<br>Multicast Forwarding Scenario Generated Traces $\ \ldots \ \ldots$ . |               |

| 10.14Multicast Forwarding Generated Traces                                    |               |

| 10.15PIM-SM Sender Registration Trace                                         |               |

| 10.16UPPAAL Implementation of IP Multicast Forwarding Scenario          |

|-------------------------------------------------------------------------|

| 10.17UPPAAL Implementation of IP Multicast Forwarding Scenario(2)       |

| 10.18Timed Automata of IP Multicast Group Membership Maintenance        |

| 10.19UPPAAL Implementation of PIM-SM Sender Registration Scenario       |

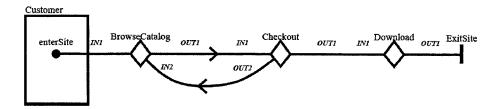

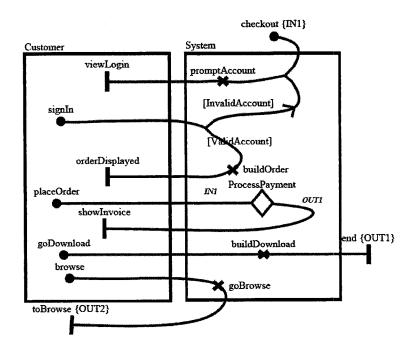

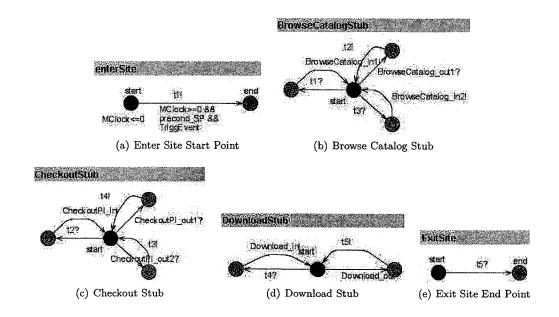

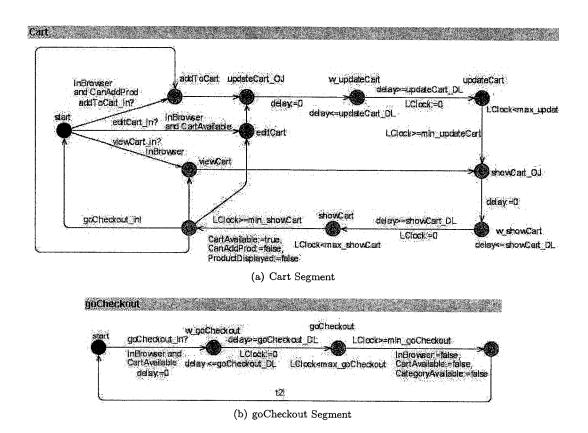

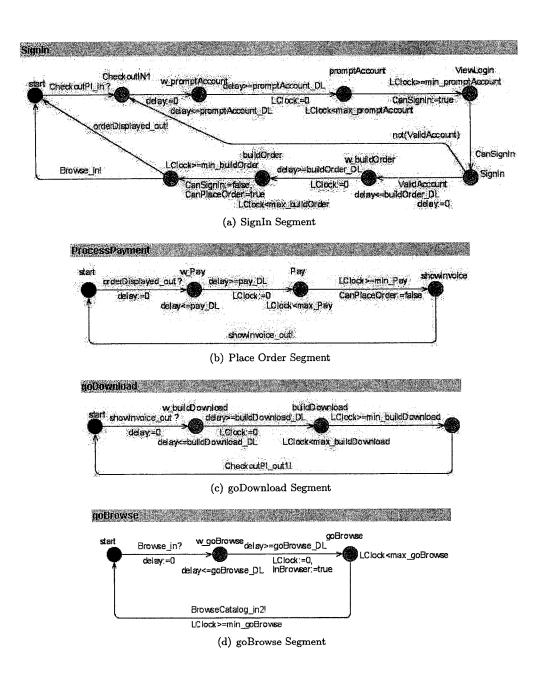

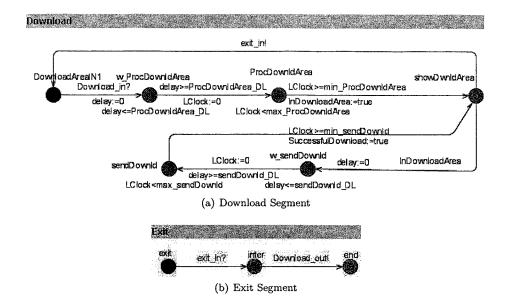

| 10.20Root Map for the Widgets.com Online Store [ARW05]                  |

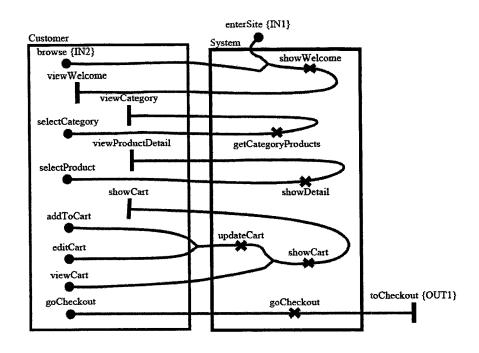

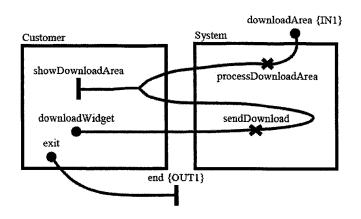

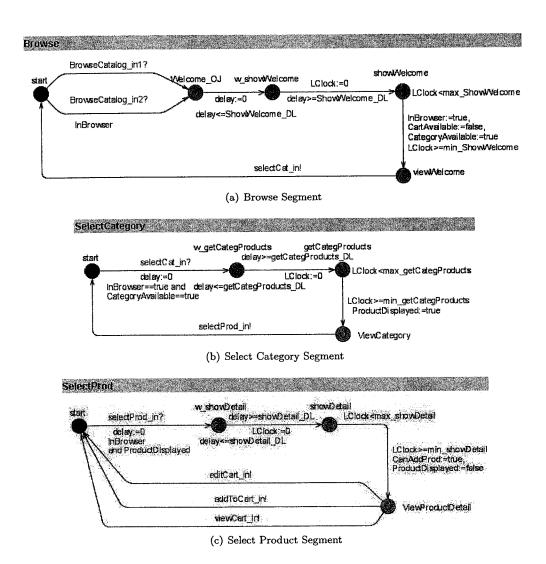

| 10.21Plug-in for BrowseCatalog Stub [ARW05]                             |

| 10.22Plug-in for Checkout Stub [ARW05]                                  |

| 10.23Plug-in for Download Stub [ARW05]                                  |

| 10.24AsmL Implementation: Online Store Global Variables                 |

| 10.25AsmL Implementation: Browse Catalog Plug-in                        |

| 10.26AsmL Implementation: Checkout Plug-in Map                          |

| 10.27AsmL Implementation: Payment Plug-in                               |

| 10.28AsmL Implementation: Download Plug-in Map                          |

| 10.29AsmL Implementation: Online Store Root Map                         |

| 10.30Online Store: Trace 1                                              |

| 10.31Online Store: Trace 2                                              |

| 10.32Online Store: Trace 3                                              |

| 10.33UPPAAL Implementation of Root map for Widgets.com Online Store 240 |

| 10.34UPPAAL Implementation of BrowseCatalog Plug-in                     |

| 10.35UPPAAL Implementation of BrowseCatalog Plug-in(2)                  |

| 10.36UPPAAL Implementation of Checkout Plug-in                          |

| 10.37UPPAAL Implementation of Download Plug-in 244                      |

# List of Tables

| 1.1  | Relative Cost of Error Repair in Different Development Stages [Dav93]                   | 4  |

|------|-----------------------------------------------------------------------------------------|----|

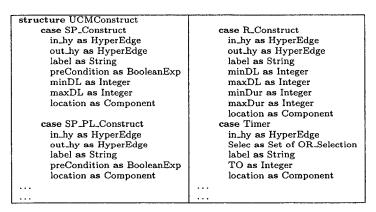

| 4.1  | UCMConstruct Data Structure                                                             | 2  |

| 4.2  | Common Data Structures                                                                  | 2  |

| 4.3  | Multi-Agent Data Structures                                                             | 3  |

| 4.4  | Single-Agent Data Structures                                                            | 3  |

| 4.5  | AsmL Access Functions                                                                   | 4  |

| 4.6  | Edges, Components and Global Variables                                                  | 8  |

| 5.1  | Example of Program Slicing                                                              | 5  |

| 5.2  | Backward Slicing Algorithm                                                              | ;1 |

| 5.3  | Forward Slicing Algorithm                                                               | 5  |

| 6.1  | Survey Summary (1)                                                                      | !3 |

| 6.2  | Survey Summary (2)                                                                      | 4  |

| 6.3  | Survey Summary (3)                                                                      | :5 |

| 6.4  | Survey Summary (4)                                                                      | 26 |

| 6.5  | Survey Summary (5)                                                                      | ?7 |

| 6.6  | Survey Summary (6)                                                                      | 28 |

| 7.1  | Urgent Responsibility Execution                                                         | 12 |

| 7.2  | Delayed Responsibility Execution                                                        | 13 |

| 7.3  | Parallel Flow Execution                                                                 | 13 |

| 7.4  | Run of Synchronized Flows                                                               | 4  |

| 10.1 | Online Store: Global Boolean Variables [ARW05]                                          | 2  |

| 10.2 | Online Store: Start Point Preconditions for Browsecatalog Plug-in [ARW05] 23            | 2  |

| 10.3 | Online Store: Variables Modified by Responsibilities in BrowseCatalog Plug-in [ARW05]23 | :3 |

## Chapter 1

## Introduction

The hardest single part of building a software system is deciding what to build. No other part of the conceptual work is as difficult as establishing the detailed technical requirements, including all the interfaces to people, to machines, and to other software systems. No part of the work so cripples the resulting systems if done wrong. No other part is more difficult to rectify later. Jr. Frederick P. Brooks [FPB87]

#### 1.1 Motivation

There is a general consensus on the importance of good Requirements Engineering (RE) for achieving high quality software. The modeling and analysis of requirements have been the main challenges during the development of complex systems. Requirements describe the needs or desired functionalities of a product, i.e. what the system should do. Requirement has many definitions, each emphasizing an aspect of requirements engineering [ZJ97]. Analysts categorize requirements into the following types (for a more refined description, see [Poh96]):

- System. These requirements describe the type of system, such as hardware or software. They may describe requirements concerning the development process (cost-effective, timely) or development aspects of the resulting product (reusable, maintainable, platform independent).

- Functional and non-functional. These requirements describe the form of service. Functional requirements are associated with specific functions, tasks or behaviors the system must support. They describe a service relation between inputs and outputs. Non-functional requirements do not define a service, but instead describe constraints on various attributes of the service provision, such as efficiency and reliability. Non-functional requirements are sometimes called system qualities.

- **Abstraction level.** Analysts describe requirements at different levels of abstraction. By specializing or refining abstract requirements, or by generalizing detailed requirements, they define a requirements abstraction hierarchy.

- Representation. One requirement can have several representations. It may begin as an informal sketch, become a natural language document, and end up as a more formal representation (e.g., temporal logic [Pnu77, MP92])

The process of defining requirements is called requirement engineering. It constitutes the first phase of any development process and it covers all the activities involved in discovering, documenting and maintaining a set of requirements for a computer-based system [SS97]. A requirement engineering process is expected to include four activities: requirements elicitation where the customers' needs are identified through consultation with all stakeholders; requirements analysis which, based on the customer's context and constraints, checks and solves potential conflicts, overlaps, omissions and inconsistencies; requirements specification that describes formally or informally the behavior of the system to be developed; and requirements validation which involves verifying if a specification is complete and clear enough for the development team to understand exactly what it needs to build.

Although several approaches have been suggested to address these tasks, requirements engineering is still facing many challenges. Among many others, we cite:

- Lack of requirement languages for eliciting and describing requirements according to their nature (e.g. functional, non-functional), and their level of abstraction. Existing frameworks tend to be overloaded with linguistic constructs and irrelevant details.

- There is a gap between requirement engineering research and formal methods research. Traditionally, requirement languages suffer from a lack of formal semantics. Hence, this represents a barrier towards the adaptation of rich set of analysis methodologies offered by formal methods.

- Lack of automated analysis and validation support to detect possible ambiguities, inconsistencies or undesirable interactions.

- Lack of specialized support: Several aspects of the requirements engineering process need specialized support for requirements evolution and refinement.

#### Scenario-based Models