# The Verification of MDG Algorithms in the HOL Theorem Prover

Sa'ed Rasmi H. Abed

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University

Montréal, Québec, Canada

June 2008

© Sa'ed Rasmi H. Abed, 2008

#### Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada

#### Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-42548-0 Our file Notre référence ISBN: 978-0-494-42548-0

## NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### ABSTRACT

The Verification of MDG Algorithms in the HOL Theorem Prover

Sa'ed Rasmi H. Abed, Ph. D.

Concordia University, 2008

Formal verification of digital systems is achieved, today, using one of two main approaches: states exploration (mainly model checking and equivalence checking) or deductive reasoning (theorem proving). Indeed, the combination of the two approaches, states exploration and deductive reasoning promises to overcome the limitation and to enhance the capabilities of each. Our research is motivated by this goal. In this thesis, we provide the entire necessary infrastructure (data structure + algorithms) to define high level states exploration in the HOL theorem prover named as MDG-HOL platform. While related work has tackled the same problem by representing primitive Binary Decision Diagram (BDD) operations as inference rules added to the core of the theorem prover, we have based our approach on the Multiway Decision Graphs (MDGs). MDG generalizes ROBDD to represent and manipulate a subset of first-order logic formulae. With MDGs, a data value is represented by a single variable of an abstract type and operations on data are represented in terms of uninterpreted function. Considering MDGs instead of BDDs will raise the abstraction level of what can be verified using a state exploration within a theorem prover. The MDGs embedding is based on the logical formulation of an MDG as a Directed Formulae (DF). The DF syntax is defined as HOL built-in data types. We formalize the basic MDG operations using this syntax within HOL following a deep embedding approach. Such approach ensures the consistency of our embedding. Then, we derive the correctness

proof for each MDG basic operator.

Based on this platform, the MDG reachability analysis is defined in HOL as a conversion that uses the MDG theory within HOL. Then, we demonstrate the effectiveness of our platform by considering four case studies. Our obtained results show that this verification framework offers a considerable gain in terms of automation without sacrificing CPU time and memory usage compared to automatic model checker tools.

Finally, we propose a reduction technique to improve MDGs model checking based on the MDG-HOL platform. The idea is to prune the transition relation of the circuits using pre-proved theorems and lemmas from the specification given at system level. We also use the consistency of the specifications to verify if the reduced model is faithful to the original one. We provide two case studies, the first one is the reduction using SAT-MDG of an Island Tunnel Controller and the second one is the MDG-HOL assume-guarantee reduction of the Look-Aside Interface. The obtained results of our approach offers a considerable gain in terms of heuristics and reduction techniques correctness as to commercial model checking; however a small penalty is paid in terms of CPU time and memory usage. To My Family

,

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my supervisor, Dr. Otmane Ait Mohamed, whose expertise, understanding, and patience, added considerably to my graduate experience. I am deeply grateful for his support and encouragement throughout my Ph.D. studies.

I would like to thank the other members of my committee, Dr. Sofiène Tahar, Dr. Rachida Dssouli, and Dr. Asim J. Al-Khalili for the assistance they provided at all levels of the research project. Finally, I would like to thank Dr. El-Mostapha Aboulhamid from Montreal University for taking time out from his busy schedule to serve as my external examiner.

Very special thanks go out to my colleagues in the Hardware Verification Group (HVG), without their help, motivation and encouragement I would not have reached this point in my research. I have spent three years and half in the HVG labs and will never forget the great moments, and achievements we had together during these years. Also, I would like to thank Dr. Ghiath Al Sammane, a post doctoral in our (HVG) group, for many discussions and helpful suggestions, which are invaluable to this thesis.

Last but not least, I would like to reserve my deepest thanks for my parents, sisters and brother, for their support and encouragement. My wife, who has been with me in every moment of my PhD tenure, is my source of strength and without her support this thesis would never have started much less finished. I would like to mention my children, Bara', Baha and Lina, for bringing joy and fun in my life and for their sacrifices and patience. I can never thank them enough.

# TABLE OF CONTENTS

| ĹΙ | LIST OF TABLES  |                                                                  |   |

|----|-----------------|------------------------------------------------------------------|---|

| LI | LIST OF FIGURES |                                                                  |   |

| LI | ST O            | PF ACRONYMS                                                      | 7 |

|    | _               |                                                                  |   |

| 1  | Intr            | roduction 1                                                      | • |

|    | 1.1             | Formal Verification Techniques                                   | ł |

|    |                 | 1.1.1 Theorem Proving                                            | ; |

|    |                 | 1.1.2 Model Checking                                             | 7 |

|    |                 | Binary Decision Diagrams                                         | ) |

|    |                 | SAT Based Methods                                                | ) |

|    | 1.2             | Related Work                                                     | L |

|    |                 | 1.2.1 Hybrid Approach                                            | L |

|    |                 | 1.2.2 Deep Embedding Approach                                    | 5 |

|    |                 | Embedding of Model Checking Algorithms in Theorem Provers . $16$ | ; |

|    |                 | Correctness Proof of Model Checking Algorithms                   | 3 |

|    | 1.3             | Proposed Methodology                                             | L |

|    | 1.4             | Thesis Contributions                                             | ł |

|    | 1.5             | Thesis Organization                                              | 5 |

| 0  | ъ               | 1                                                                | - |

| 2  | Pre             | liminaries 27                                                    |   |

|    | 2.1             | The HOL Theorem Prover                                           | , |

|    | 2.2             | Multiway Decision Graphs                                         | - |

|    |                 | 2.2.1 Formal Logic                                               | L |

|    |                 | 2.2.2 Abstract State Machines                                    | } |

|   |     | 2.2.3 Structure                             | 4 |

|---|-----|---------------------------------------------|---|

|   |     | 2.2.4 The MDG-Tool                          | 3 |

|   |     | 2.2.5 MDGs Model Checking                   | 7 |

| 3 | For | malization of MDG Syntax 39                 | • |

|   | 3.1 | Transition Relation: Graph or Formula       | 9 |

|   | 3.2 | Embedding Directed Formulae in HOL 41       | 1 |

|   | 3.3 | Well-formedness Conditions                  | 7 |

|   | 3.4 | MIN-MAX Example                             | 1 |

| 4 | For | malization of MDG Operations 55             | 5 |

|   | 4.1 | The Conjunction Operation                   | 5 |

|   |     | 4.1.1 The Conjunction Constraints:          | 3 |

|   |     | 4.1.2 The Conjunction Embedding:            | 3 |

|   | 4.2 | The Relational Product (RelP) Operation     | 3 |

|   |     | 4.2.1 The RelP Constraints:                 | 1 |

|   |     | 4.2.2 The RelP Embedding:                   | 5 |

|   | 4.3 | The Disjunction Operation                   | 3 |

|   |     | 4.3.1 The Disjunction Constraints:          | 7 |

|   |     | 4.3.2 The Disjunction Embedding:            | 3 |

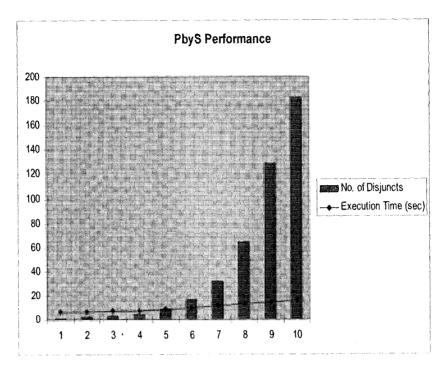

|   | 4.4 | The Pruning by Subsumption (PbyS) Operation | L |

|   |     | 4.4.1 The PbyS Constraints:                 | 2 |

|   |     | 4.4.2 The PbyS Embedding:                   | 2 |

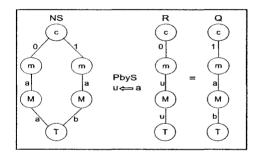

|   |     | 4.4.3 The PbyS Performance:                 | 5 |

|   | 4.5 | The Correctness Proof                       | 3 |

|   | 4.6 | Embedding and Proof Discussion              | ) |

| <b>5</b> | For | maliza   | tion of MDG Reachability Analysis                  | 81  |

|----------|-----|----------|----------------------------------------------------|-----|

|          | 5.1 | Reach    | ability Analysis Algorithm                         | 81  |

|          | 5.2 | Forma    | alization of Reachability Analysis                 | 83  |

|          | 5.3 | Exam     | ple: The MIN-MAX revisited                         | 86  |

|          | 5.4 | The M    | 1DG-HOL Platform                                   | 87  |

| 6        | Ap  | olicatio | ons and Case Studies                               | 91  |

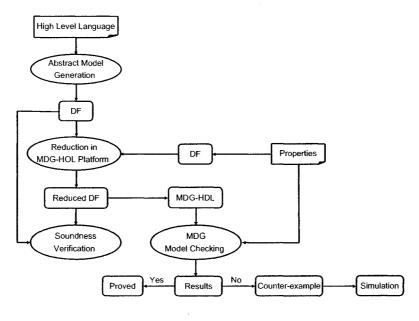

|          | 6.1 | Model    | l Reduction Techniques                             | 93  |

|          | 6.2 | SAT-N    | MDG Reduction Verification                         | 95  |

|          |     | 6.2.1    | Boolean Satisfiability                             | 95  |

|          |     | 6.2.2    | Combining SAT and MDG Methodology                  | 97  |

|          |     | 6.2.3    | Abstracting CNF from DF                            | 97  |

|          |     | 6.2.4    | Extracting Variables from Properties               | 99  |

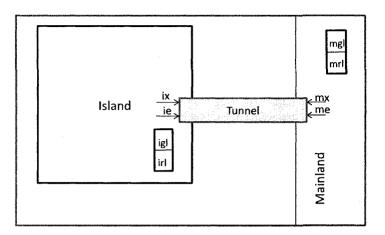

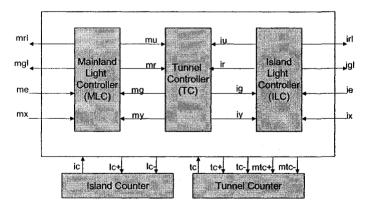

|          |     | 6.2.5    | Island Tunnel Controller (ITC)                     | 100 |

|          |     |          | System Description                                 | 100 |

|          |     |          | Verification                                       | 102 |

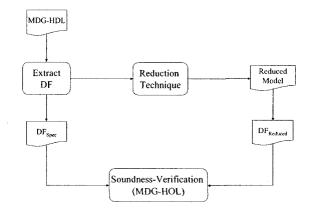

|          | 6.3 | The A    | Assume-Guarantee Reduction Verification in MDG-HOL | 103 |

|          |     | 6.3.1    | The Assume-Guarantee Reduction Methodology         | 103 |

|          |     | 6.3.2    | Generation of Directed Formulae                    | 105 |

|          |     |          | From High Level Language                           | 105 |

|          |     |          | From the Properties                                | 108 |

|          |     | 6.3.3    | Verification of the Reduction Soundness            | 108 |

|          |     |          | The Reduction-Soundness Algorithm                  | 110 |

|          |     |          | Correctness of the Algorithm                       | 111 |

|          |     |          | The False Negative                                 | 112 |

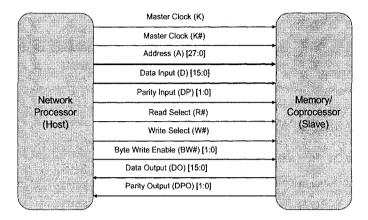

|          |     |          | The RAM Example                                    | 113 |

|   | 6.3.4                                                                             | Case Studies                   | . 114                            |

|---|-----------------------------------------------------------------------------------|--------------------------------|----------------------------------|

|   |                                                                                   | Look-Aside Interface (LA-1)    | . 114                            |

|   |                                                                                   | Island Tunnel Controller (ITC) | . 119                            |

| 7 | Conclusio                                                                         | ons and Future Work            | 122                              |

|   | 7.1 Summ                                                                          | nary                           | . 122                            |

|   | 7.2 Futur                                                                         | re Research Directions         | . 124                            |

| B | ibliography                                                                       | Ÿ                              | 127                              |

| ٨ |                                                                                   |                                |                                  |

| A | The MDC                                                                           | G-HOL Platform                 | 139                              |

| А |                                                                                   | G-HOL Platform<br>MDG Syntax   |                                  |

| A | A.1 The M                                                                         | MDG Syntax                     | . 139                            |

| A | A.1 The M<br>A.2 The C                                                            | MDG Syntax                     | . 139<br>. 142                   |

| A | <ul><li>A.1 The I</li><li>A.2 The I</li><li>A.3 The I</li></ul>                   | MDG Syntax                     | . 139<br>. 142<br>. 145          |

| A | <ul><li>A.1 The I</li><li>A.2 The I</li><li>A.3 The I</li><li>A.4 The I</li></ul> | MDG Syntax                     | . 139<br>. 142<br>. 145<br>. 146 |

# LIST OF TABLES

| 1.1 | Deductive theorem proving vs. state exploration method          |

|-----|-----------------------------------------------------------------|

| 1.2 | Raising the Abstraction Level                                   |

| 2.1 | Terms of the HOL Logic                                          |

| 3.1 | Well-Formedness (WF) Inference Rules                            |

| 4.1 | The PbyS Performance                                            |

| 5.1 | MDG-HOL Benchmarks                                              |

| 5.2 | FormalCheck Benchmarks                                          |

| 6.1 | Comparing the Original MDGs Model Checking Results with the Re- |

|     | duced MC and Soundness Verification Results                     |

| 6.2 | Comparing the Original MDGs Model Checking Results with the Re- |

|     | duced MC and Soundness Verification Results                     |

| 6.3 | Comparing the Original MDGs Model Checking Results with the Re- |

|     | duced MC and Soundness Verification Results                     |

# LIST OF FIGURES

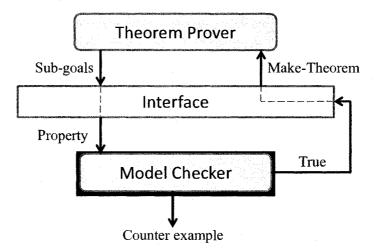

| 1.1 | Theorem Proving and Model Checking Interface         | 12  |

|-----|------------------------------------------------------|-----|

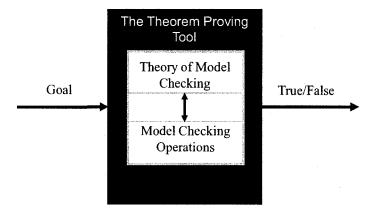

| 1.2 | Embedding Model Checking inside Theorem Proving Tool | 15  |

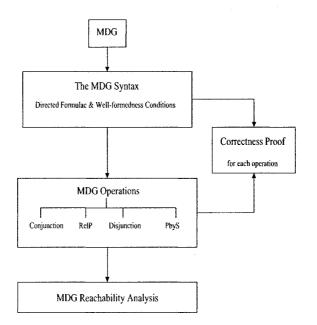

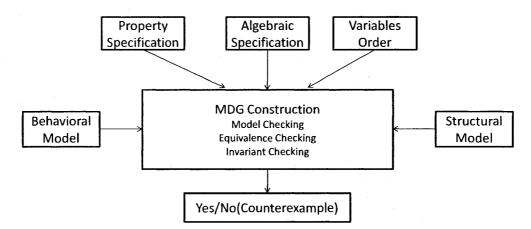

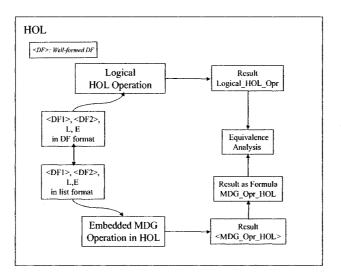

| 1.3 | Overview of the Embedding Methodology in HOL         | 22  |

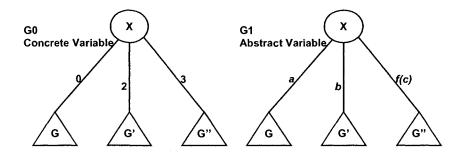

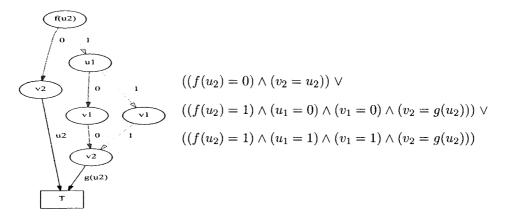

| 2.1 | Example of Multiway Decision Graphs Structure        | 35  |

| 2.2 | 2 The Structure of the MDGs-tool                     | 36  |

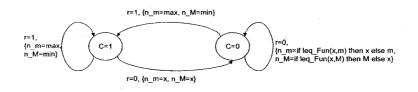

| 3.1 | MIN-MAX State Machine                                | 51  |

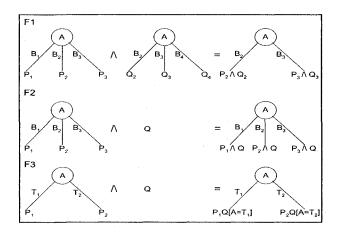

| 4.1 | The conjunction operation                            | 56  |

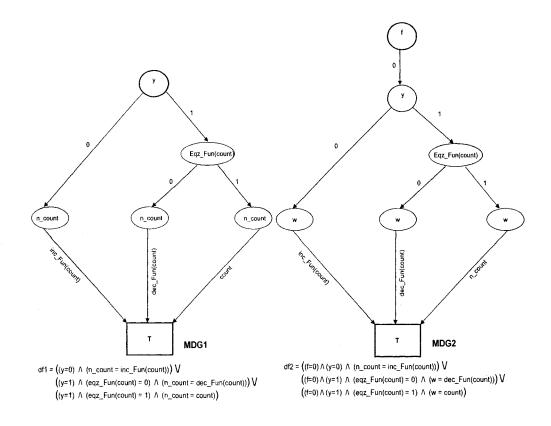

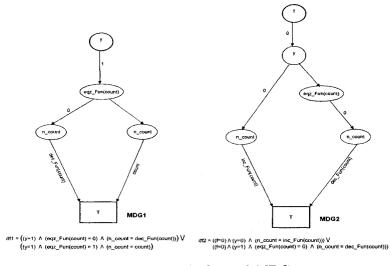

| 4.2 | 2 MDG1 and MDG2                                      | 63  |

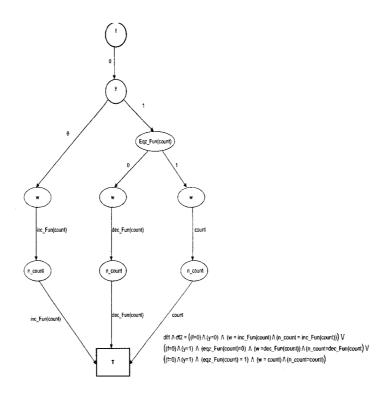

| 4.3 | MDG1 CONJ MDG2                                       | 64  |

| 4.4 | MDG1 RelP MDG2                                       | 66  |

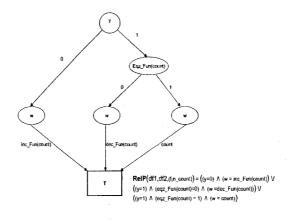

| 4.5 | The disjunction operation                            | 66  |

| 4.6 | MDG1 and MDG2                                        | 70  |

| 4.7 | MDG1 DISJ MDG2                                       | 70  |

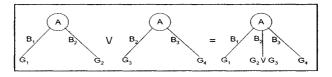

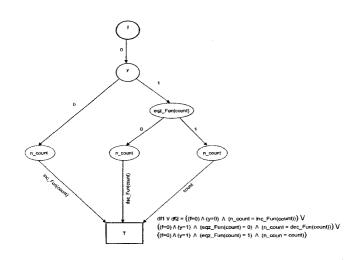

| 4.8 | 3 The PbyS operation                                 | 71  |

| 4.9 | The PbyS Performance                                 | 77  |

| 4.1 | 0 Correctness Methodology                            | 78  |

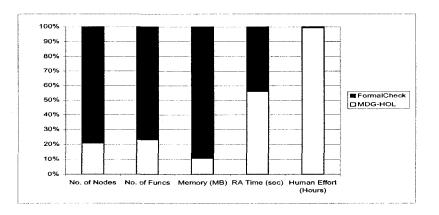

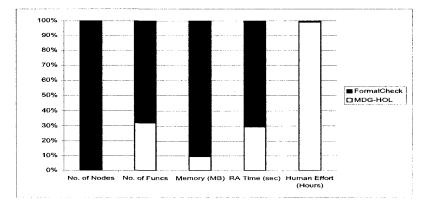

| 5.1 | MDG-HOL and FormalCheck Small Benchmarks             | 89  |

| 5.2 | MDG-HOL and FormalCheck Big Benchmarks               | 89  |

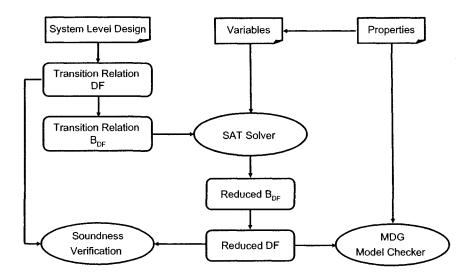

| 6.1 | Overview of the Methodology                          | 98  |

| 6.2 | 2 The Island Controller                              | 101 |

| 6.3 | Island Tunnel Controller Structure                   | 101 |

| 6.4 | Overview of the Reduction Methodology              | . 104 |

|-----|----------------------------------------------------|-------|

| 6.5 | Overview of the Soundness-Verification Methodology | . 108 |

| 6.6 | Look-Aside Interface                               | . 116 |

| 6.7 | Look-Aside Interface Design                        | . 117 |

# LIST OF ACRONYMS

.

....

~ - -

$\sim$

| Computer Aided Design                   |

|-----------------------------------------|

| Abstract State Machine                  |

| Binary Decision Diagram                 |

| Reduced Ordered Binary Decision Diagram |

| Satisfiability Checking                 |

| Directed Formulae                       |

| Directed Acyclic Graph                  |

| Finite State Machine                    |

| Hardware Description Language           |

| Multiway Decision Graph                 |

| Model Checking                          |

| Bounded Model Checking                  |

| Symbolic Trajectory Evaluation          |

| Linear time Temporal Logic              |

| Computational Tree Logic                |

| Higher-Order Logic                      |

| Automatic Theorem Prover                |

| Logic of Computable Function            |

| Meta Language                           |

| Functional Language                     |

| Conjunctive Normal Form                 |

| Quantified Boolean Formulae             |

| Register Transfer Level                 |

|                                         |

| LHS  | Left Hand Side               |

|------|------------------------------|

| RHS  | Right Hand Side              |

| VLSI | Very Large Scale Integration |

| ITC  | Island Tunnel Controller     |

| LA-1 | Look-Aside Interface         |

| RelP | Relational Product           |

| PbyS | Pruning by Subsumption       |

# Chapter 1

# Introduction

With the increasing complexity of the design of digital systems and the size of the circuits in VLSI technology, the role of design verification has gained a lot of importance. Serious design errors and bugs take a lot of time and effort to be detected and corrected especially when they are discovered late in the verification process. This will increase the total cost of the chip. In order to overcome these limitations, *formal verification techniques* arose as a complement to simulation for detecting errors as early as possible, thus ensuring the correctness of the design.

Formal techniques are the application of applied mathematics in order to prove that the design implementation satisfies its specifications, and entail reasoning in some formal logic. In general, *formal verification* of digital systems is achieved, today, using one of two main approaches: states exploration [49] (mainly model checking and equivalence checking) or deductive reasoning (theorem proving). It is accepted that both approaches have complementary strengths and weaknesses.

State exploration approaches use states space traversal algorithms on finite-state models to check if the implementation satisfies its specification. They are focused mostly on automatic decision procedures for solving the verification problem. In case the verification fails, the user can track with the counter example produced as to why it failed.

Model checking is an automatic approach for verifying finite-state systems and mainly used in hardware and protocol verification. The circuit is described as a state machine with a transition to describe the circuit behavior. The specifications are described as properties that the machine should satisfy. Furthermore, they can produce a counterexample when the property does not hold, which can be very important for correcting the corresponding error in the implementation under verification or in the specification itself. Traditionally, model checkers used explicit representations of the state transition graph, for all but the smallest state machines. However, model checking suffers from the state explosion problem [19]: the number of the explored states grows exponentially in the size of the system description.

Equivalence checking is used to prove functional equivalence of two design representation modeled at the same or different levels of abstraction. It can be divided into combinational equivalence checking and sequential equivalence checking. Combinational equivalence checking is based on the canonical representations of Boolean functions or Binary Decision Diagrams (BDDs). Equivalence checking verifies for all input sequences that an implementation has the same outputs as the specification, both modeled as Finite State Machines (FSM). Sequential equivalence checking is used to verify the equivalence between two sequential designs at each state. Sequential equivalence checking consider only the behavior of two designs while ignoring their implementation details such as register mapping. It can verify the equivalence between Register Transfer Level (RTL) and netlist or RTL and the behavioral model which is very important in design verification. The disadvantage of sequential equivalence checking is that it cannot handle large design because it enumerates state space explosion problem very fast.

In deductive reasoning approach, the correctness of a design is formulated as a theorem in a mathematical logic and the proof is checked using a general-purpose theorem-prover. Based on first-order and high-order logic, these theorem provers are known for their abilities to express relationships over unbounded data structures. Therefore, theorem proving tools are not sensitive to the state explosion problem when used to reason formally about such data and relationships. Unfortunately, if the property fails to hold, deductive methods do not give a counterexample. Furthermore, this frequent situation requires skilled manual guidance for verification and human insight for debugging. Yet theorem provers, today, provide feedback, but only expert user can track the proof trace and determine whether the fault lies within the system, the property being verified, or within the failed proof tactic.

There has been a great deal of work over the past decade to combine the two approaches to gain the strengths of both, and alleviate the weaknesses. Successful combinations of this kind have been achieved in [2, 44, 46, 48, 57, 75, 78]. The strengths and weaknesses of model checking and deductive theorem proving, as discussed above, are summarized in Table 1.1.

| Method      | State exploration method         | Deductive method | Hybrid method    |

|-------------|----------------------------------|------------------|------------------|

| Automation  | completely automatic             | interactive      | semi-automatic   |

| Domain size | finite system                    | infinite system  | finite system    |

|             | (large)                          | (complex)        | (very large)     |

| Debugging   | generates                        | expert based     | rarely generates |

|             | $\operatorname{counter-example}$ |                  | counter-example  |

Table 1.1: Deductive theorem proving vs. state exploration method

The combination of the two approaches can be performed either by adding a

layer of deduction theorems and rules on top of the model checking tool (hybrid approach) or by embedding model checking algorithms inside theorem provers (deep embedding approach). Our research is motivated by using the deep embedding approach to blend the best of model checker and theorem prover.

The structure of the rest of this chapter is as follows: In Section 1.1, we briefly introduce the formal verification techniques. Section 1.2 surveys the literature and presents the related work. An overview of the research and the contribution of this thesis is explained in Sections 1.3 and 1.4, respectively. Finally, the outline of the thesis is presented in Section 1.5.

### **1.1** Formal Verification Techniques

Formal verification problem consists of mathematically establishing that an implementation behaves according to a given set of requirements or specification. To classify the various approaches, we first look at the three main aspects of the verification process: the system under investigation (implementation), the set of requirements to obey (specification) and the formal verification tool to verify the process (relationship between implementation and specification).

The implementation refers to the description of the design that is to be verified. It can be described at different levels of abstraction which results in different verification methods. Another important issue with the implementation is the class of the system or circuit to be verified, i.e., whether it is combinational/sequential, synchronous/asynchronous, pipelined or parameterized hardware. These variations may require different approaches. The specification refers to the property with respect to which the correctness is to be determined. In practice, one needs to model both the implementation and the specification in the tool, and then uses one of the formal verification algorithms of the tool to check the correctness of the system or in some cases give a trace of error (counter-example).

Formal techniques have long been developed within the computing research community as they provide sound mathematical foundation for the specification, implementation and verification of computer system. Thus, formal verification is proposed as a method to help certify hardware and software, and consequently, to increase confidence in new designs. A correctness proof cannot guarantee that the real device will never malfunction; the design of the device may be proved correct, but the hardware actually built can still behave in a way unintended by the designer. Wrong specification can play a major rule in this, because it has been verified that the system will function as specified, but it has not been verified that it will work correctly. Defects in physical fabrication can cause this problem too. In formal verification a model of the design is verified, not the real physical implementation. Therefore, a fault in the modeling process can give false negatives (errors in the design which do not exist). Although sometimes, the fault covers some real errors.

Formal verification approaches can be generally divided into two main categories: theorem proving methods and state exploration methods such as model checkers as described in the following subsections.

#### **1.1.1** Theorem Proving

Theorem proving is an approach where the specification and the implementation are usually expressed in first-order or higher-order logic. Their relationship is formed as a theorem to be proved within the logic system. This logic is a set of axioms and a set of inference rules. Steps in the proof appeal to the axioms and rules, and possibly derived definitions and intermediate lemmas. The axioms are usually "elementary" in the sense that they capture the basic properties of the logic's operators [32].

Theorem proving utilizes the proof inference technique. The problem itself is transformed into a sequent, a working representation for the theorem proving problem. Then a sequent holds if the formula f holds in any model:

$$\models f$$

A proof system is collection of *inference rules* of the form:

(name)

$$\frac{P_1 \dots P_n}{C}$$

where C is a conclusion sequent, and  $P_i$ 's are premisses sequents. The meaning of an inference rule is, if all the premisses are derivable, then the conclusion is guaranteed to hold. Some inference rules may have no premisses, in which case their conclusion automatically holds. Such rules are also called *axioms*, and they are the only means to complete the proof derivation.

Traditionally, the logic used in theorem proving is the classical First- or Higher-Order logic (FOL and HOL respectively). Some other kinds of logics are also used, but since all of them can be expressed in the higher-order logic, the latter is used much more often as a general property language.

Theorem proving methods have been in use in hardware and software verification for a number of years in various research projects. Some of the well-known theorem provers are HOL (Higher-Order Logic), ISABELLE, PVS (Prototype Verification System), Coq and ACL2 [23, 36, 42, 47, 66]. These systems are distinguished by, among other aspects, the underlying mathematical logic, the way automatic decision procedures are integrated into the system, and the user interface. Even though they are powerful, they require expertise in using a theorem prover. User is expected to know the whole design leading to a white box verification approach. It is not fully automated and requires a large amount of time to verify the system. Another shortcoming is the inability to produce counter-examples in the event of a failed proof, because the user does not know whether the required property is not derivable or whether the person conducting the derivation is not ingenious enough. The advantage of the deductive verification approach is that it can handle very complex systems because the logics of theorem provers are more expressive. In the next chapter, we will overview the HOL theorem proving system, which we intend to use in this thesis.

### 1.1.2 Model Checking

Model checking is a state exploration based verification technique developed in the 1980s by Clarke and Emerson [19] and independently by Quielle and Sifakis [68]. In model checking, a state of the system under consideration is a snapshot of the system at certain time, given by the set of the variables values of that system at that time. The system is then modeled as a set of states together with a set of transitions between states that describe how the system moves from one state to another in response to internal or external stimulus. Model checking tools are then used to verify that desired properties (expressed in some temporal logic) hold in the system.

Model checker has two important advantages. First, once the correct design of the system and the required properties has been fed in, the verification process is fully automatic. Second, in the event of a property not holding, the verification process is able to produce a counter-example (i.e. an instance of the behavior of the system that violates the property) which is extremely useful in helping the human designers pinpoint and fix the flaw. On the other hand, model checkers are unable to handle very large designs due to the state space explosion problem [19]. Another drawback is the problematic description of specifications as properties, this description sometimes

7

may not give full system coverage.

Model checkers such as SPIN [40], COSPAN [51], SMV [54], and MDG [88] take as input, essentially, a finite-state system and temporal property in some variety or subset of Computation Tree Logic (CTL\*), and automatically check that the system satisfies the property. Moreover, the model is often restricted to a finite-state transition system, for which finite-state model checking is known to be decidable. The design or model is formalized in terms of a state machine (*Transition System*), or a Kripke structure:

$$M = (P, S, I, R, L)$$

where M is a state machine (model) with a transition to describe the circuit behavior, P is a set of atomic propositions, S is a finite set of states,  $I \subseteq S$  is a set of initial states,  $R \subseteq SxS$  is a transition relation that must be total (i.e. for every  $s \in S$  there exists  $s' \in S$  such that  $(s' \in R)$ ), and  $L : S \to 2^P$  maps each state to the set of atomic propositions true in that state. The property  $\phi$  is formalized as a logical formula that the machine should satisfy. The verification problem is stated as checking the formula  $\phi$  in the model M:

#### $M\vDash\phi$

If the model M is represented explicitly as a transition relation, then the size of the model is limited to the number of states that can be stored in the computer memory, which are a few million states with the current technology. To increase the size of the model, more efficient state representations can be used to manipulate these formulae using BDDs or SAT solving techniques.

#### **Binary Decision Diagrams**

Binary Decision Diagrams (BDDs) [13] are data structures used as a compact representation for the Boolean function which improves the capacity of the model checker. BDDs have several useful properties. Many common functions have small BDDs in addition to the fact that the BDDs are easy to manipulate. Also a function can be evaluated in linear time in the number of variables and also can be existentially or universally quantified (Boolean) variables in time quadratic in the size of the BDD. Moreover, the order in which the variables appear can be fixed and hence the BDD is a canonical representation for the Boolean function.

BDDs are used to overcome the capacity limitation of the model checkers, different representations of ROBDDs (Reduced Order Binary Decision Diagrams) [14] are used to manipulate the state transition relations as diagrams and this allows model checkers to verify larger systems. Still, most model checkers face the state space explosion problems [19] even using Symbolic Model Checking. To be able to apply model checking to larger designs, state reduction techniques are used that exploit some features of the model, the properties, or the problem domain to reduce the state space to a tractable size. Examples include partitioned transition relation, dynamic variable reordering, cone of influence reduction, abstraction, problem-specific techniques, e.g. when the original design is rewritten in a simpler way, omitting the irrelevant details, but preserving the important behavior for the property being verified.

In this thesis, we intend to use the Multiway Decision Graphs (MDGs), a new class of decision graph. MDG was proposed as a solution to the state space explosion problem [21]. In MDGs based model checking approach, data signals are denoted by abstract variables, and data operators are represented by uninterpreted function symbols. As a result, a verification based on abstract-implicit-state-enumeration can be carried out independently of datapath width, substantially lessening the state explosion problem. Table 1.2 shows the abstraction level of MDG corresponding to traditional methods.

| Conventional Method        | Multiway Decision Graphs                   |

|----------------------------|--------------------------------------------|

| ROBDD [14]                 | MDGs [21]                                  |

| Finite State Machine (FSM) | Abstract State Machine (ASM)               |

| Implicit state enumeration | Abstract state implicit enumeration of ASM |

| CTL based model-checking   | Based on first-order abstract CTL*         |

Table 1.2: Raising the Abstraction Level

#### SAT Based Methods

An alternative for decision graphs is to represent the transition relation in CNF and use Satisfiability Checking (SAT) [26, 81] with several properties that make them attractive compared to BDDs. SAT solvers can decide satisfiability of very large Boolean formulae in reasonable time, but they are not canonical and require additional efforts to check for equivalence of formulas. As a result, various researchers have developed routines for performing Bounded Model Checking (BMC) [3, 11, 30] using SAT. The common theme is to convert the problem of interest into a SAT problem, by devising the appropriate propositional Boolean formula, and to utilize other noncanonical representations of state sets. However, they all exploit the known ability of SAT solvers to find a single satisfying solution when it exists. Moreover, SAT solver technology has improved significantly in recent years with a number of sophisticated packages now available. Well known state-of-the-art SAT solvers include CHAFF [59], GRASP [52] and SATO [89]. Since state sets can be represented as Boolean formulae, and since most model checking techniques manipulate state sets, SAT solvers have enormously boosted their speed and applicability.

## 1.2 Related Work

Model checking is automatic while theorem proving is not. On the other hand, theorem proving can handle complex systems while model checking can not. Today, there exist a number of integration tools of theorem proving and model checking. The motivation is to achieve the benefits of both tools and to make the verification simpler and more effective. In this section, we explore two approaches of linking proof systems to external automated verification tools. The approaches can be divided in two kinds:

- Hybrid approach: adding a layer of deduction theorems and rules on top of Decision Diagrams tool, i.e. combining theorem provers with other powerful model checking tool.

- 2. Deep embedding approach: adding Decision Diagrams algorithms to theorem provers.

We first review the most related work to every approach and then, we contrast between them according to their efficiency, complexity and feasibility.

### 1.2.1 Hybrid Approach

The hybrid approach implements a tool linking model checking and theorem proving. During the verification procedure, the user deals mainly with the theorem proving tool. Verification using hybrid approach proceeds as shown in Figure 1.1. The user starts by providing the theorem proving with the design (specification or implementation), the property and the goal to be proven. If the goal fits the required pattern, the theorem proving tool generates the required model checking files (sub-goals). The latter are sent to the model checking tool for verification. If the property holds, a theorem is created (Make-Theorem). Otherwise, the proof is performed interactively.

Figure 1.1: Theorem Proving and Model Checking Interface

The linkage between both tools is carried out using scripting languages (translators) to be able to automatically verify small subgoals generated by the theorem prover from a large system. The disadvantage of this approach lies in achieving an efficient and correct translation from theorem prover logic to a model checker and from model checker to theorem prover (import the result or give a counter-example). Successful combinations of this kind have been achieved in [46, 48, 57, 75, 78].

Rajan et al. [74, 75] described an approach where a BDD-based model checker for the propositional  $\mu$ -calculus has been used as a decision procedure within the framework of PVS. An extension of the  $\mu$ -calculus, which consists of Quantified Boolean Formulae (QFB), is defined using PVS higher-order logic. The temporal operators are then defined using the  $\mu$ -calculus. These temporal operators apply to arbitrary state spaces. In the case where the state type is constructed in a hereditarily finite manner,  $\mu$ -calculus expressions are translated into input acceptable by a  $\mu$ -calculus model checker. This model checker can then be used as a decision procedure to prove certain subgoals. The model checker accepts the translated input from  $\mu$ -calculus expression. The generated subgoals are verified by the model checker and the results are used in the proof process of PVS.

Schneider et al. [46] used higher order hardware formulae to express the safety and liveness properties hierarchically. They proposed an approach of invoking model checking within HOL where properties are translated from HOL to temporal logic. A new class of higher-order formulae was presented, which allows a unified description of hardware structure and behavior at different levels of abstraction. Datapath oriented verification goals involving abstract data types can be expressed by these formula as well as control dominated verification goals with irregular structure. To ease the proofs of the goals in HOL, a translation procedure was presented which converts the goals into several Computational Tree Logic (CTL) model checking problems, which are then solved outside HOL.

Schneider and Hoffmann [78] linked the SMV model checker to HOL using PROSPER. It provides an open proof architecture for the integration of different verification tools in a uniform higher-order logic environment. They embedded the linear time temporal logic (LTL) in HOL and translated LTL formulae into  $\omega$ -Automata, a form that can be reasoned about within SMV. The translation is completely implemented by means of HOL rules. HOL terms are exported to SMV through the PROSPER plug-in interface. On successful model checking, the results are returned to HOL and turned to theorems. This integration tool allows SMV to be used as a HOL decision procedure. The deep embedding of the SMV specification language in HOL allows LTL specifications to be manipulated in HOL.

In [67], Pisini and Tahar proposed a hybrid approach for formal hardware verification which uses the strengths of the HOL theorem prover and the advantages of the automated tool MDG which supports equivalence and model checking. They developed a linkage tool between HOL and MDG which uses the specification and implementation of a circuit written in HOL to automatically generates all required MDG files. The implementation of the methodology is achieved by building a linkage tool using Moscow ML to translate from HOL to MDG. It then calls the MDG equivalence checking procedure and reports the MDG verification results back to HOL.

The MDG-HOL system [48] is a hybrid system which links the HOL interactive proof system and the MDG automated hardware verification system. It supports a hierarchical verification approach and fits the use of MDG verification naturally within the HOL framework for a compositional hierarchical verification. The HOL system is used to manage the proof. The MDG system is called to verify the submodules of a design. When the MDG-HOL system is used to verify a design, the design is modeled as a hierarchy structure with modules divided into submodules.

An extension of the above work was presented in [57] to link HOL and the MDG model checker. They described a hybrid tool that links the HOL theorem prover and the MDG model checker. For this purpose, they developed an interface which reads a HOL goal, generates the required MDG files, calls the MDG model checker, and generates the HOL theorem on successful verification. The interface between the two tools is implemented using ML.

### 1.2.2 Deep Embedding Approach

In this approach, the emphasis is to establish a secure platform for new verification algorithms. The performance penalty will be compensated by the secure infrastructure. The approach implements a model checking inside a theorem proving tool. As shown in Figure 1.2, the design and the property are fed to the model checking to check if the property holds and create a theorem. Otherwise, the proof cannot be performed.

Figure 1.2: Embedding Model Checking inside Theorem Proving Tool

The result of the model checker is correct by construction, since both of the theory and the implementation are proved correct in the theorem prover. Thus a high assurance of soundness is guaranteed because more work is backed up by mechanized fully-expansive proof. The price for the extra proof and flexibility is in increased development effort. This approach differs from the hybrid approach in the way the verification is performed. In fact, we do not use an external checking tool, instead we deeply embed the model checker algorithms inside the theorem prover. Thus the criteria of correctness by construction, efficiency, flexibility and expressiveness can be met. Successful works have been achieved in [7, 34, 35, 37, 44, 56].

The "deep embedding" approach [69] introduce the model checker syntax as a

new higher order logic type and then define the operations and algorithms based on this syntax within the theorem prover. This contrasts within a "shallow embedding" where the syntax is not formally represented in the logic, only in the meta-language. In general, a deep embedding allows one to reason about the language itself rather than just the semantics of programs in the language.

We consider two categories of related work: the first category regarding embedding of model checking algorithms in theorem provers. The second category regarding correctness proof of the model checker algorithms.

#### Embedding of Model Checking Algorithms in Theorem Provers

Model checkers [54] are usually built on top of BDDs [13], or some other set of efficiently implemented algorithms for representing and manipulating Boolean formulae. The closest work, in approach to our own is that of Joyce and Seger [79], Gordon [34, 35] and later Amjad [7].

Voss system [79], an implementation of Symbolic Trajectory Evaluation (STE), was implemented in a lazy Functional Language (FL). In [44] Voss was interfaced to HOL and the verification using a combination of deduction and STE was demonstrated. The HOL-Voss system integrates HOL88 deduction with BDD computations. The BDD tools are programmed in FL as a built-in datatype. The assertion language of Voss was formalized in HOL and a HOL tactic, which can make an external calls to the Voss system, checks wether an assertion is true. Then the proved assertion was returned as a HOL theorem. The early experiments with HOL-Voss suggested that a lighter theorem prover component was sufficient, since all that was needed is a way to combine results obtained from STE. A system based on this idea, called Voss-ThmTac, was later developed by Aagaard *et al.* [2]; combination of the ThmTac theorem prover with the Voss system. Then the development of HOL-Voss evolved into a new system called Forte [1]. More recently, with industrial take-up at Intel, Forte [55] has become one of the most mature formal verification environments based on tool integration.

Gordon integrated the BDD based verification system BuDDy (BDD package implemented in C) into HOL by implementing BDD-based verification algorithms inside HOL, the embedding is built on top of provided primitives. The aim of using BuDDy is to get near the performance of C-based model checker, whilst remaining fully expansive, though with a radically extended set of inference rules [35].

In [37], Harrison implemented BDDs inside the HOL system without making use of external oracle. The BDD algorithms were used by a tautology-checker. However, the performance was about thousand times slower than with a BDD engine implemented in C. Harrison argued that by re-implementing some of HOL's primitive rules, the performance could be improved by around ten times.

Amjad [7] demonstrated how BDD based symbolic model checking algorithms for the propositional  $\mu$ -calculus ( $L_{\mu}$ ) can be embedded in HOL theorem prover. This approach allows results returned from the model checker to be treated as theorems in HOL. By representing primitive BDD operations as inference rules added to the core of the theorem prover, the execution of a model checker for a given property is modeled as a formal derivation tree rooted at the required property. These inference rules are hooked to a high performance BDD engine [35] which is external to the theorem prover. Thus, the HOL logic is extended with these extra primitives. Empirical evidence suggests that the efficiency loss in this approach is within reasonable bounds. The approach still leaves results reliant on the soundness of the underlying BDD tools. A high assurance of soundness is obtained at the expenses of some efficiency. Thus the security of the theorem prover is compromised only to the extent that the BDD engine or the BDD inference rules may be unsound.

Our work, deals with embedding MDGs [21] rather than BDDs. In fact, while BDDs are widely used in state-exploration methods, they can only represent Boolean formulae. By contrast, MDGs represent a subset of first-order terms allowing the abstract representation of data and hence raising the level of abstraction. Another major difference is that it implements the related inference rules for BDD operators in the core of HOL as a plugged in code, whereas we implement the MDG operations inside HOL itself.

Mhamdi and Tahar [56] follow a similar approach to the BuDDy work [35]. The work builds on the MDG-HOL [48] project, but uses a tightly integrated system with the MDG primitives written in ML rather than two tools communicating as in MDG-HOL system. In their work, the syntax is partially embedded and the conditions for well-formedness must be respected by the user. By contrast, we provide a complete embedding of the MDG syntax and the conditions could be checked automatically in HOL.

#### **Correctness Proof of Model Checking Algorithms**

Verification of BDD algorithms has been a subject of active research using different proof assistants such that HOL, PVS, Coq, and ACL2 [23, 36, 42, 47]. A common goal of these papers is to extend the prover with a certified BDD package to enhance the BDD performance, while still inside a formal proof system. Moreover, there is a general consensus in the formal verification community that correctness proofs should be checked, partly or wholly, by computers. Some efforts have been made to verify model checkers and theorem provers. In [71], the authors successfully carried out the verification task of the RAVEN model checker. RAVEN is a real-time model checker which uses time-extended finite state machines (interval structure) to represent the system and a timed version of CTL (CCTL) to describe its properties. The specification and the correctness proof were carried out using an interactive specification and verification system KIV.

In [62], the author showed a mechanism of how certifying model checker can be constructed. The idea is that, a model checker can produce a deductive proof on either success or failure. The proof acts as a certificate of the result, since it can be checked independently. A certifying model checker thus provides a bridge from the model-theoretic to the proof-theoretic approach to verification. The author developed a deductive proof system for verifying branching time properties expressed in the  $\mu$ calculus, and showed it to be sound and relatively complete. Then, a proof generation in this system from a model checking run is presented. This is done by storing and analyzing sets of states that are generated by the fixpoint computations performed during model checking.

Krstic and Matthews [50] provided a technique for proving correctness of high performance BDD packages. In their work, they adopted an abstraction method called monadic interpretation for verifying an abstraction of the BDD programs with the primitives specified axiomatically. The method is suitable for higher order logic theorem provers such as Isabelle/HOL. The monadic interpreter translates source programs of input type A and output type B into function of type  $A \Rightarrow MB$  in the target functional language, where the type constructors M is a suitable monad that encapsulate the notion of computation used by the source language to describe BDD programs. At this level, they modeled the BDD programs as a function in higher order logic in the style of monadic interpreters. Then the correctness proof was carried out on the BDD abstract model.

Wright [86] described an embedding of higher order proof theory within the logic of the HOL theorem proving system. Types, terms and inferences were represented as new types in the logic of the HOL system, and notions of proof and provability were defined. Using this formalization, it was possible to reason about the correctness of derived inference rules and about the relations between different notions of proofs: a Boolean term is provable if and only if there exists a proof for it. The formalization is also intended him to make it possible to reason about programs that handle proofs as their data (e.g., proof checker).

Harrison [38] answered a question concerning the correctness of the theorem prover itself. The author verified formally that the abstract HOL logic is correct and that the OCaml code does correctly implement this logic. The verification is conducted with respect to a set-theoretic semantics within the HOL Light itself.

The authors in [85] implemented and proved the correctness of BDD algorithms using Coq. One of their goals was to extract a certified algorithm manipulating BDDs in Caml (the implementation language of Coq). BDDs were represented as DAGs and maps were used to model a state of the memory in which all the BDDs are stored. The authors used reflection to prove a given property P applied to some term t where the program is described and proved in Coq. This means that writing a program  $\pi$ that takes t as an input and returns true exactly when P(t) holds. Then, to show  $\pi$ is correct with respect to P they needed to be sure that whenever  $\pi(t)$  returns true P(t) holds and this is done inside the Coq proof assistant itself (i.e. the proof of Phas been replaced by the computation of  $\pi$  and reflect this by allowing the system to accept meta-level computation as actual proof).

Another concept to prove the program correctness using Hoare logic as described

by Ortner and Schirmer [64]. The principle of this logic is to annotate the program with pre- and post-conditions and to observe the changes made by each statement of the program. Ortner and Schirmer modeled the graph structure of the BDD as a kind of heap and presented the verification of BDD normalization. They follow the original algorithm presented by Bryant in [13]: transforming an ordered BDD into a reduced, ordered and shared BDD. The work is based on Schirmer's research on the Verification Condition Generator (VCG) to generate the proof obligations for Hoare Logic. The proofs are carried out in the theorem prover Isabelle/HOL.

Haiyan et al. [87] verified formally the linkage between a simplified version of MDG tool and the HOL theorem prover. The verification is based on the importing of MDG results to HOL theorems. Then, they combined translator correctness theorems with the linkage theorems in order to allow low level MDG verification results to be imported into HOL in terms of the semantics of MDG-HDL. The work was concerned with ways of increasing trust in the linked systems.

Our work follows the verification of the Boolean manipulating package, but using MDG instead. We provided a complete formalization of the MDG logic and its wellformedness conditions as DFs in HOL mechanically. Based on this infrastructure we formalized the basic MDG operations in HOL following a deep embedding approach and proved their correctness. Our work focuses more on how one can raise the level of assurance by embedding and proving formally the correctness of those operators in HOL to use them as an infrastructure for MDG model checker.

### 1.3 Proposed Methodology

The intention of our research is to provide a secure platform that combines an automatic high level MDGs model checking tool within the HOL theorem prover. While related work has tackled the same problem by representing primitive Binary Decision Diagrams (BDD) operations [13] as inference rules added to the core of the theorem prover [35], we have based our approach on the Multiway Decision Graphs (MDGs) [21]. MDG generalizes ROBDD to represent and manipulate a subset of first-order logic formulae which is more suitable for defining model checking inside a theorem prover. With MDGs, a data value is represented by a single variable of an abstract type and operations on data are represented in terms of uninterpreted functions. Considering MDG instead of BDD will rise the abstraction level of what can be verified using a state exploration within a theorem prover. Furthermore, an MDG structure in HOL allows better proof automation for larger datapaths systems.

In this thesis, we provide the entire necessary infrastructure (data structure + algorithms) to define a high level state exploration in the HOL theorem prover named as MDG-HOL platform.

Figure 1.3: Overview of the Embedding Methodology in HOL

Firstly, as shown in Figure 1.3, we define the MDG structure inside the HOL theorem prover to be able to construct and manipulate MDGs as formulae in HOL. This step implies a formal logic representation for the *MDG Syntax*. This representation is based on the Directed Formulae DF: an alternative vision for MDG in terms of logic and set theory [6]. Secondly, a HOL tactic is defined to check the satisfaction of the well-formedness conditions of any directed formula. This step is important to guarantee the canonical representation of the MDG as a DF. Then, the definition of each MDG operations is defined and a correctness proof is derived within HOL.

Based on this platform, the MDG reachability analysis is defined in HOL as a conversion that uses the MDG theory within HOL. Then, we demonstrate the effectiveness of our platform by considering four case studies. Our obtained results show that this verification framework offers a considerable gain in terms of automation without sacrificing CPU time and memory usage compared to automatic model checker tools.

Finally, we propose a reduction technique to improve MDGs model checking based on the MDG-HOL platform. The idea is to prune the transition relation of the circuits using pre-proved theorems and lemmas from the specification given at system level. We also use the consistency of the specifications to verify if the reduced model is faithful to the original one. We provide two case studies, the first one is the reduction using SAT-MDG of an Island Tunnel Controllerand the second one is the MDG-HOL assume-guarantee reduction of the Look-Aside Interface. The performance penalty in the case of SAT-MDG reduction verification is acceptable as compared with commercial model checking tools. In the case of assume guarantee in MDG-HOL, the reduction strategy results still satisfactory in terms of heuristics and reduction techniques correctness, however a small penalty is paid in terms of time and memory.

### **1.4** Thesis Contributions

The objective of our research is to explore a way of increasing the degree of trust of the MDG system by embedding the MDG system in HOL. In light of the above related work review, proposed methodology, and discussions, we believe the contributions of the thesis can be specified as follows:

- We have provided a secure platform (data structure + algorithms) of MDG system in HOL. This step consists of the following phases:

- 1. Embedding of the MDG formal logic underlying the abstract state machines in HOL.

- 2. Defining the notion of well formed HOL terms. These terms could be represented canonically by MDGs.

- 3. Embedding the MDG algorithms (conjunction, relational product (RelP), disjunction, and pruning by subsumption (PbyS)) following deep embedding approach. Also, we have two kinds of theorems: one theorem regarding the correctness proof of each MDG operation, and the other one for preserving the well-formedness of the operation results.

- The MDG based reachability analysis is then defined in HOL as a conversion that uses the MDG-HOL platform and a fixpoint theorem is then proven for some particular circuits.

- We have evaluated the performance of the MDG-HOL platform using a set of benchmarks to ensure the applicability of our approach.

- We have proposed a reduction methodology to improve the MDGs model checking as well as to verify the soundness of model checking reduction techniques.

• We have provided two case studies, the first one is the reduction using the SAT-MDG technique of the Island Tunnel Controller (ITC), and the second one is the MDG-HOL assume-guarantee reduction technique of the Look-Aside Interface (LA-1).

In summary, we have created a new formal theory for MDGs (data structure + operations) inside the HOL theorem prover which provides us with several theoretical advantages without too high performance penalty. We used this theory or platform to verify the soundness of model checking reduction techniques. We thus hope that this work will be of interest to the research community and also be of use to industrial practitioners.

## **1.5** Thesis Organization

The rest of the thesis is organized as follows:

- In Chapter 2, we review the basics of the HOL theorem prover. We also introduce the basic concepts of Multiway Decision Graphs (MDGs).

- Chapter 3 presents the formal logic underlying MDGs as well as well-formedness conditions and its embedding inside HOL.

- In Chapter 4, we formalize the MDG basic operations and prove the correctness of each operation.

- In Chapter 5 , we show the formalization of the MDG reachability analysis and the proposed conversion for proving a fixpoint. We also consider four case studies to measure the performance of the MDG-HOL platform.

- Chapter 6 considers the applications and case studies for the proposed reduction techniques.

- Chapter 7 concludes the thesis and indicates the future work.

## Chapter 2

# Preliminaries

In this chapter, we give a brief description to the HOL theorem prover as well as to the Multiway Decision Graphs (MDGs) system. The intent is to familiarize the reader with the main concepts and notations that are used in the rest of the thesis. Section 2.1 starts by a basic description of higher-order logic concepts. Then, we describe the syntax and semantics of the particular logical system supported by HOL notation, as well as the proof methods supported by the HOL theorem prover.

Section 2.2 describes the underlying formal logic of MDGs, the MDGs structure, the Abstract State Machine (ASM), the MDG tool and the MDG model checker.

## 2.1 The HOL Theorem Prover

The HOL system is an LCF [33] (Logic of Computable Functions) style proof system. Originally intended for hardware verification, HOL uses higher-order logic to model and verify variety of applications in different areas; serving as a general purpose proof system. We cite for example: reasoning about security, verification of faulttolerant computers, compiler verification, program refinement calculus, software and algorithms verification, modeling, and automation theory.

HOL provides a wide range of proof commands, including rewriting tools and decision procedures. The system is user-programmable which allows proof tools to be developed for specific applications; without compromising reliability [36].

The set of types, type operator, constants, and axioms available in HOL are organized in the form of theories. There are many theories, which are arranged in a hierarchy, have been added to axiomatize lists, products, sums, numbers, primitive recursion, and arithmetic. On top of these, users are allowed to introduce applicationdependent theories by adding relevant types, constants, axioms, and definitions.

The HOL system supports higher order logic with three main expressions:

- Variables can range over functions and predicates.

- The logic is typed.

- There is no separate syntactic category of formulae.

The HOL syntax contains syntactic categories of types and terms whose elements are intended to denote respectively certain sets and elements of sets. The types of the HOL logic are expressions that denote sets (in the universe  $\mathcal{U}$ ). There are four kind of types in HOL logic. Type variables stand for arbitrary sets in the universe, they are part of the meta-language and are used to range over object language types. Atomic types denote fixed sets in the universe. For example, the standard atomic types *bool* denotes the distinguished two-element set 2. Compound types have the form  $(\sigma_1, \dots, \sigma_n)op$ , where  $\sigma_1, \dots, \sigma_n$  are the argument types and op is a type operator of arity n. Type operators denote operations for constructing sets. Function types denote the set of all (total) functions from the set denoted by its domain to the set denoted by its range [32]. The terms of the HOL logic are expressions that denote elements of the sets denoted by types. There are four kinds of terms in HOL logic. The variables are sequences of letters or digits beginning with a letter. The constants have the same syntax as variables, but stand for fixed values. The function applications or combinations have the general form  $t_1(t_2)$  where  $t_1$  is called the operator and  $t_2$  is the operand. The result of such a function application can itself be a function. The lambda terms  $(\lambda$ -terms) or abstractions denote for functions. Such a term has the form  $\lambda x.t$  (where t is a term) and denotes the function f defined by f(x) = t. The syntax and semantics of the particular logical system supported by HOL notation used in this paper is summarized in Table 2.1. Note that the cons infix operator (::) is used to represent an enumerated list (hd :: tl) and the (t) notation is used to instantiate the value of the term t as shown in the bottom of the table.

| Kind of term              | HOL notation               | Standard notation          | Description                |  |

|---------------------------|----------------------------|----------------------------|----------------------------|--|

| Truth                     | Т                          | Т                          | true                       |  |

| Falsity                   | F                          | Ţ                          | false                      |  |

| Negation                  | t                          | $\neg t$                   | not t                      |  |

| Disjunction               | $t_1 \backslash / t_2$     | $t_1 \lor t_2$             | $t_1 \text{ or } t_2$      |  |

| Conjunction               | $t_1/\backslash t_2$       | $t_1 \wedge t_2$           | $t_1$ and $t_2$            |  |

| Implication               | $t_1 ==> t_2$              | $t_1 \Longrightarrow t_2$  | $t_1$ implies $t_2$        |  |

| Equality                  | $t_1 = t_2$                | $t_1 and t_2$              | $t_1$ equal $t_2$          |  |

| $\forall$ -quantification | !x.t                       | $\forall x.t$              | for all x:t                |  |

| $\exists$ -quantification | ?x.t                       | $\exists x.t$              | for some x:t               |  |

| $\epsilon$ -term          | @x.t                       | $\epsilon x.t$             | an x such that:t           |  |

| Conditional               | if t then $t_1$ else $t_2$ | $(t \rightarrow t_1, t_2)$ | if t then $t_1$ else $t_2$ |  |

| List Type                 | h::t                       | [h;t]                      | [hd;tl]                    |  |

| Antiquotations            | Ĩ                          | ł                          | Evaluates to the           |  |

|                           |                            |                            | ML value of $t$            |  |

Table 2.1: Terms of the HOL Logic

The basic interface to the system is a Standard Meta Language (SML) interpreter. SML [65] is both the implementation language of the system and the Meta Language in which proofs are written. The HOL system supports two main different proof methods: forward and backward proofs in a natural-deduction style calculus.

In forward proof, the steps of a proof are implemented by applying inference rules chosen by the user, and HOL checks that the steps are safe. All derived inference rules are built on top of a small number of primitive inference rules. This approach has some limitations since it is hard to know where to state the proof and, for large proofs, to determine which sequence of rules to apply. The results are strong and the user can have great confidence since the most primitive rules are used to prove a theorem.

In backward proof, the user sets the desired theorem as a goal. Small programs written in SML called tactics and tacticals are applied to break the goal into a list of subgoals. Tactics and tacticals are repeatedly applied to the subgoals until they can be resolved. In practice, forward proof is often used within backward proof to convert each goal's assumptions into a suitable form.

Theorems in the HOL system are represented by values of the ML abstract type **thm**. There is no way to construct a theorem except by carrying out a proof based on the primitive inference rules and axioms. HOL system has many built-in inference rules and ultimately all theorems are proved in terms of the axioms and basic inferences of the calculus. By applying a set of primitive inference rules, a theorem can be created. Once a theorem is proved, it can be used in further proofs without recomputation of its own proof. In this way, the ML type system protects the HOL logic from arbitrary construction of a theorem, so that every computed value of the type-representing theorem is a theorem. The user can have a great deal of confidence in the results of the system. The applications of the HOL system can be found in hardware verification, reasoning about security, verification of fault-tolerant computers, and reasoning about real-time systems. It is also used in compiler verification, program refinement calculus, software and algorithms verification, modeling, and automation theory.

HOL also has a rudimentary library facility which enable theories to be shared. This provides a file structure and documentation format for self contained HOL developments. Many basic reasoners are given as libraries such as **mesonLib**, **bossLib**, and **simpLib**. These libraries integrate rewriting, conversion and decision procedures to free the user from performing low-level proof.

### 2.2 Multiway Decision Graphs

### 2.2.1 Formal Logic

The formal logic underlying MDG is many-sorted First Order Logic (FOL). The vocabulary consists of *sorts, constants, variables, and function symbols* or (*operators*). Constants and variables have sorts. An n-ary function symbol (n > 0) has a type  $\alpha_1 \times \alpha_2 \times \cdots \times \alpha_n \to \alpha_{n+1}$ , where  $\alpha_1 \cdots \alpha_{n+1}$  are sorts. Two kinds of sorts are distinguished: concrete and abstract:

- Concrete sort: is equipped with finite enumerations, lists of individual constants. Concrete sorts are used to represent control signals.

- Abstract sort: has no enumeration available. A signal of an abstract sort represents a data signal.

The enumeration of a concrete sort  $\alpha$  is a set of distinct constants of sort  $\alpha$ . We refer to constants occurring in enumerations as *individual constants*, and to other constants as generic constants. An individual constant can appear in the enumeration of more than one sort  $\alpha$ , and is said to be of sort  $\alpha$  for each of them. Variables and generic constants, on the other hand, have unique sorts.

The terms and their types (sorts) are defined inductively as follows: a constant or a variable of sort  $\alpha$ ; and if f is a function symbol of type  $\alpha_1 \times \alpha_2 \times \cdots \times \alpha_n \rightarrow \alpha_{n+1}$ , where  $\alpha_1 \cdots \alpha_{n+1}$ ,  $n \ge 1$ , and  $A_1, \cdots, A_n$  are terms of types  $\alpha_1 \cdots \alpha_{n+1}$ , then  $f(A_1 \cdots A_{n+1})$  is a term of type  $\alpha_{n+1}$ . A term consisting of a single occurrence of an individual constant has multiple types (the sorts of the constant) but every other term has a unique type.

We say that a term, variable or constant is concrete (resp. abstract) to indicate that it is of concrete (resp. abstract) sort. A term is *concretely reduced* iff it contains: (i) the individual constants; (ii) the abstract generic constants; (iii) the abstract variable; and (iv) the terms of the form  $f(A_1 \cdots A_{n+1})$  where f is an abstract symbol and  $A_1, \cdots, A_n$  are concretely-reduced terms. Thus, the concretely-reduced terms are those that have no concrete sub terms other than individual constants. A term of the form  $f(A_1 \cdots A_{n+1})$  where f is a cross-operator and  $A_1, \cdots, A_n$  are concretely-reduced terms is called *cross-term*. An *equation* is an expression  $A_1, \cdots, A_n$  where  $A_1$  and  $A_n$ are terms of same type  $\alpha$ . Atomic formulae are the equations, plus **T** (truth), and **F** (falsity). Formulae are built from the atomic formulae in the usual way using logical connectives and quantifiers.

An *interpretation* is a mapping  $\Psi$  that assigns a denotation to each sort, constant and function symbol such that:

- 1. The denotation  $\Psi(\alpha)$  of an abstract sort  $\alpha$  is a non-empty set.

- 2. If  $\alpha$  is a concrete sort with enumeration  $a_1, a_2, \dots, a_n$  then

$$\Psi(\alpha) = \Psi(a_1), \Psi(a_2), \dots, \Psi(a_n) \text{ and } \Psi(a_i) \neq \Psi(a_i) \text{ for } 1 \leq i \prec j \leq n.$$

3. If c is a generic constant of sort  $\alpha$ , then  $\Psi(c) \in \Psi(\alpha)$ . If f is a function symbol of type  $\alpha_1 \times \alpha_2 \times \cdots \times \alpha_n \to \alpha_{n+1}$  then  $\Psi(f)$  is a function from cartesian product  $\Psi(\alpha_1) \times \cdots \Psi(\alpha_n)$  into the set  $\Psi(\alpha_{n+1})$ .

Let X be a set of variables, a variable assignment with domain X compatible with an interpretation  $\Psi$  is a function  $\varphi$  that maps every variable  $x \in X$  of sort  $\alpha$ to an element  $\varphi(x)$  of  $\Psi(\alpha)$ . We write  $\Phi_X^{\Psi}$  for the set  $\Psi$ -compatible assignments to the variables in  $X, \Psi, \varphi \models P$  if P denotes truth under an interpretation  $\Psi$  and a  $\Psi$ -compatible variable assignment  $\varphi$  to the variables that occur free in P, and  $\models P$ if a formula P denotes truth under every interpretation  $\Psi$  and every  $\Psi$ -compatible variable assignment to the variables that occur free in P. Two formulae P and Q are logically equivalent iff  $\models P \Leftrightarrow Q$ .

#### 2.2.2 Abstract State Machines

Abstract description of State Machines (ASMs) is a model used for describing hardware designs at the Register Transfer Level (RTL). It was introduced by Corella et al. [21, 91]. In MDGs, a state machine is described using finite sets of input, state and output variables, which are pair-wise disjoint. The behavior of a state machine is defined by its transition/output relations including a set of reset states. Using ASMs, a data value can be represented by a single variable of abstract type, rather than by a vector of Boolean variables, and a datapath operation is represented by an uninterpreted function symbol. As ROBDDs are used to represent sets of states and transition/output relations for finite state machines (FSM), MDGs are used to compactly encode sets of (abstract) states and transition/output relations for ASMs. This technique replaces the implicit enumeration technique [22] with the implicit abstract enumeration [21, 91].

#### 2.2.3 Structure

MDGs are graph representation of a class of quantifier-free and negation-free firstorder many sorted formulae. It subsumes the class of Bryant's (ROBDDs) [13] while accommodating abstract data and uninterpreted function symbols. It can be seen as a Directed Acyclic Graph (DAG) with one root, whose leaves are labeled by formulae of the logic True (T)[21], such that:

- Every leaf node is labeled by the formula T, except if the graph G has a single node, which may be labeled T or F.

- 2. The internal nodes are labeled by terms, and the edges issuing from an internal node v are labeled by terms of the same sort as the label of v.