# REDUCTION OF LOW-ORDER HARMONICS AND NEW TOPOLOGIES OF CURRENT SOURCE CONVERTERS

Maged Fouad Fahmy Naguib Barsom

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of

**Doctor of philosophy**

Concordia University

Montréal, Québec, Canada

March 2010

© Maged Fouad Fahmy Naguib Barsom, 2010

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-67334-8 Our file Notre référence ISBN: 978-0-494-67334-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### **AVIS:**

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **ABSTRACT**

#### REDUCTION OF LOW-ORDER HARMONICS AND NEW TOPOLOGIES OF

#### **CURRENT SOURCE CONVERTERS**

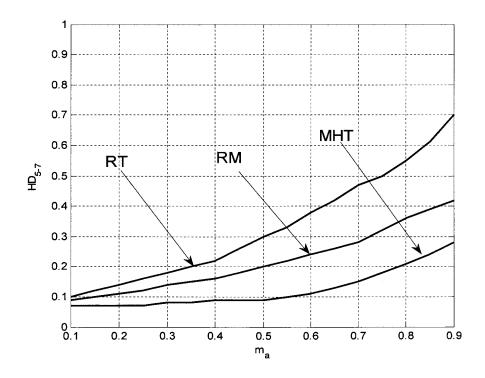

#### Maged Fouad Fahmy Naguib Barsom

Two CSCs related issues are investigated. The first is the reductions of Low Order Harmonics (LOH) in Low Switching Frequency (LSF) CSCs. High power CSCs operate with LSF. This is not an ideal scenario for Space Vector Modulation (SVM), resulting in non-characteristics LOH, 5<sup>th</sup> and 7<sup>th</sup> (HD<sub>5-7</sub>). Researchers have attempted to reduce these harmonics by creating new sequences of space vectors (states) or different sampling techniques. New approaches based on the fact that HD<sub>5-7</sub> is affected by states ON times calculation process are proposed. Results show that by using a new technique called Record Middle (RM), one can obtain a smaller HD<sub>5-7</sub>. Also, results for calculating states ON times as the reference vector rotates by new SVM equations show that one can get a significant reduction in HD<sub>5-7</sub>. Another alternative effective with large overlap periods is minimizing LOHs in LSF-SVM-CSCs with Minimum Harmonic Tracking (MHT) technique. Fuzzy logic dependent states ON times calculation give fixed states ON times adjustment during steady state and fast response. Those techniques allowed the usage of reduced size ac-side filters with high cut-off frequencies.

The second issue is on new hybrid current source converters (HCSCs). Three SCRs and four IGBTs HCSC has similar characteristics, less capital cost and less power losses compared to the 6-switches CSC. Two types of modulation are proposed. The first is Hard Switching Space Vector Modulation technique (HS-SVM). HS-SVM is

presenting low maximum modulation index (m<sub>a.max</sub>), resulting in LOH distortion and requiring multiple mandatory switching inside a cycle. The second modulation technique achieves line-commutation or soft switching (SS) of the SCRs whenever possible, thus being called Soft Switching Space Vector Modulation technique (SS-SVM). SS-SVM increases the m<sub>a.max</sub> while reducing LOH, the switching frequency and switching losses. Comparisons between the 6-switches CSC and the HCSCs are provided. Cost analysis showing the importance of HCSCs is carried out. A case study is presented to show that the HCSC is economically viable in medium and high power ranges. Besides having lower capital cost, the HCSC can operate with lower power losses than 6-switches CSC.

### **ACKNOWLEDGMENTS**

The author would like to express his sincere gratitude to his supervisor, Dr. Luiz A.C. Lopes for his invaluable guidance, advice and friendship throughout the course of this study. Dr. Lopes improved my ability in describing concepts, writing skills and selecting research topics.

The author would also like to thank Mr. Joe Wood and all colleagues in the P. D. Ziogas Power Electronics Laboratory. Smart suggestions from and helpful discussions with Reinaldo, Ninad, Saeed, Neil, Yong, Peng and Ghulam are unforgettable.

Last but not least, the author is very grateful towards his wife Mary, his children Mina and Marina and his parents Fouad and Margret whose constant support made it possible to finish the thesis.

## TABLE OF CONTENT

| TABLE OF CONTENT                                                      | vi    |

|-----------------------------------------------------------------------|-------|

| List of Figures                                                       | X     |

| LIST OF TABLES                                                        | xvi   |

| LIST OF ACRONYMS                                                      | xvii  |

| LIST OF PRINCIPAL SYMBOLS                                             | XX    |

| PUBLICATIONS                                                          | xxv   |

| PART-1.                                                               | 1     |

| REDUCING LOW ORDER HARMONICS IN CURRENT SOURCE CONVERT                | ERS.1 |

| Chapter 1                                                             | 1     |

| 1. SPACE VECTOR MODULATION FOR CURRENT SOURCE CONVERTER               | 1     |

| 1.1. Introduction                                                     | 1     |

| 1.2. CSC modulation techniques                                        | 4     |

| 1.2.1. Common modulation techniques for CSCs                          | 4     |

| 1.2.2. Fundamentals of SVM- CSCs                                      | 4     |

| 1.2.3. Implementation of SVM for 6-switches CSC                       | 7     |

| 1.2.4. Calculations of traditional SVM-CSC states ON time             | 12    |

| 1.3. Thesis outline                                                   | 20    |

| 1.4. Conclusion                                                       | 22    |

| CHAPTER 2                                                             | 23    |

| 2. Using states on-times calculations to Reduce LOH in 6-switches CSC | 2 23  |

| 2.1. Introduction                                                     | 23    |

| 2.2. Middle states ON times calculation procedure                     | 23    |

| 2.3. Performance comparison between SAs, SAm and RM                   | 32    |

| 2.4. Conclusion.                                                      | 39    |

| CHAPTER 3                                                             | 41    |

| 3. New SVM equations to reduce LOH in LSF-CSC                         | 41    |

| 3.1. Introduction                                                     | 41    |

| 3.2. Sequence one                                                     | 42    |

| 3.2.1. Calculation of states ON time using SQ1-EQ                     | 42    |

| 3.2.2. Calculation of states ON times using SQ1-CF                    | 46    |

|    | 3.2.  | 3.    | Performance of SQ1-EQ and SQ1-CF                                       | 48   |

|----|-------|-------|------------------------------------------------------------------------|------|

|    | 3.3.  | Seq   | uence two                                                              | 55   |

|    | 3.3.  | 1.    | Calculation of states ON time using SQ2-EQ                             | 55   |

|    | 3.3.  | 2.    | Calculation of states ON times using SQ2-CF                            |      |

|    | 3.3.  | 3.    | Performance of SQ2-EQ and SQ2-CF                                       | 58   |

|    | 3.4.  | Seq   | uence three                                                            | 61   |

|    | 3.4   | .1.   | Calculation of states ON time using SQ3-EQ                             | 61   |

|    | 3.4   | .2.   | Calculation of states ON times using SQ3-CF                            | 63   |

|    | 3.4   | .3.   | Performance of SQ3-EQ and SQ3-CF                                       | 64   |

|    | 3.5.  | Exp   | erimental results                                                      | . 67 |

|    | 3.6.  | Con   | clusion                                                                | . 70 |

| C  | HAPTE | R 4   |                                                                        | . 71 |

| 4. | Mn    | NIMIZ | ZING LOH IN LSF-SVM-CSC WITH MHT TECHNIQUE                             | . 71 |

|    | 4.1.  | Intro | oduction                                                               | . 71 |

|    | 4.2.  | Dire  | ect states ON times calculations with LOH                              |      |

|    | 4.2   | .1.   | Middle states ON times calculations                                    | . 72 |

|    | 4.2   | .2.   | States ON times calculations during transition point                   | . 73 |

|    | 4.2   |       | Performance comparison between direct techniques                       |      |

|    | 4.3.  | One   | e variable MHT technique                                               | . 76 |

|    | 4.3   | .1.   | Tracking technique concept                                             |      |

|    | 4.3   | .2.   | One variable MHT for CSC ac-side current                               |      |

|    | 4.3   |       | One variable MHT for filtered CSC ac-side current                      |      |

|    | 4.4.  | The   | overlap period effect on HD <sub>5-7</sub>                             |      |

|    | 4.4   | .1.   | One variable MHT for CSC filtered ac-side current with overlap period. | . 92 |

|    | 4.4   |       | Two variable MHT for CSC filtered ac-side current with overlap period. |      |

|    | 4.5.  | Exp   | perimental Investigation and Challenges                                | . 98 |

|    | 4.6.  |       | nclusion                                                               |      |

| C  |       |       |                                                                        |      |

| 5. | . HA  |       | NICS REDUCTION IN CSC USING FUZZY LOGIC                                |      |

|    | 5.1.  |       | oduction                                                               |      |

|    | 5.2.  |       | posed Fuzzy logic technique                                            |      |

|    | 5.3.  |       | monics reduction in CSC ac-side current                                |      |

|    | 5.4.  | Har   | monics reduction in the grid current                                   |      |

|    | 5.5   | Cor   | relusion                                                               | 111  |

| PART-  | 2                                                        | 112 |

|--------|----------------------------------------------------------|-----|

|        | VECTOR MODULATED HYBRID BI-DIRECTIONAL CURREN            |     |

| CONVE  | ERTERS                                                   | 112 |

| Снарте | ER 6                                                     | 112 |

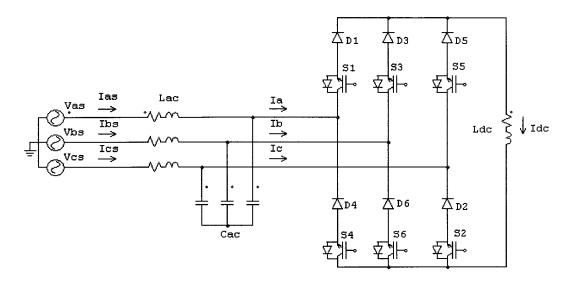

| 6. Pr  | OPOSAL OF TWO NEW HYBRID CSCs TOPOLOGIES                 | 112 |

| 6.1.   | Introduction                                             | 112 |

| 6.2.   | Previously proposed HCSCs                                | 115 |

| 6.3.   | Proposed HCSC topologies                                 |     |

| 6.4.   | Commutation in HCSC topologies                           |     |

| 6.5.   | Experimental verification of the commutation in HCSC     | 123 |

| 6.6.   | Conclusion                                               | 127 |

| Снарте | ER 7                                                     | 128 |

| 7. HA  | ARD-SWITCHING SVM FOR HCSC                               | 128 |

| 7.1.   | 6-switches SVM-CSC used for comparison                   | 128 |

| 7.2.   | HS-SVM principles for the Three SCRs and four IGBTs HCSC | 130 |

| 7.3.   | HS-SVM principles for the Six SCRs and two IGBTs HCSC    | 133 |

| 7.4.   | Average switching frequency of the semiconductors        | 135 |

| 7.5.   | Limitations on the modulation index (m <sub>a</sub> )    |     |

| 7.6.   | Experimental setup                                       | 139 |

| 7.7.   | Simulation and Experimental Results                      | 141 |

| 7.8.   | PF control for HCSC with HS-SVM                          | 144 |

| 7.9.   | Conclusion                                               | 147 |

| Снартн | ER 8                                                     | 149 |

| 8. Sc  | OFT-SWITCHING SVM FOR HCSC                               | 149 |

| 8.1.   | Introduction                                             | 149 |

| 8.2.   | SS-SVM principles for the three SCRs and four IGBTs HCSC | 150 |

| 8.3.   | Average switching frequency of the Semiconductors        | 162 |

| 8.4.   | Limitations on the modulation index (m <sub>a</sub> )    | 163 |

| 8.5.   | Simulation and experimental results                      | 164 |

| 8.6.   | Conclusion                                               | 170 |

| Снарти | ER 9                                                     | 171 |

| 9. Co  | OST ANALYSIS                                             | 171 |

| 9.1.   | Introduction                                             | 171 |

| 9.2.   | General economical formula                               | 172 |

| 9.3.   | Power Losses categories                                  | 173 |

| 9.4. Conduction power losses                           | 175 |

|--------------------------------------------------------|-----|

| 9.5. Commutation (switching) power losses              | 178 |

| 9.5.1. Average calculations for switching power losses | 180 |

| 9.5.2. Switching power losses with simulation results  | 182 |

| 9.6. Conclusion                                        | 191 |

| 10. Conclusions                                        | 193 |

| 10.1. Summary                                          | 193 |

| 10.1.1. Part one                                       | 193 |

| 10.1.2. Part two                                       | 195 |

| 10.2. Future work                                      | 197 |

| 10.2.1. Part one                                       | 197 |

| 10.2.1. Part two                                       | 198 |

| References                                             | 199 |

## **LIST OF FIGURES**

| Fig. 1- 1:- 6-switches IGBT based Voltage Source Converter (VSC)                                                                | 2   |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 1-2:-6-switches GTOs-based current source converter (CSC)                                                                  | 3   |

| Fig. 1-3: Definition of the sectors (0 - 5), states (I <sub>1</sub> - I <sub>9</sub> ), and the switches which are ON           | ſ   |

| in each state when $N_{CS} = 6$ in 6-switches SVM-CSC.                                                                          | 6   |

| Fig. 1-4:-SIMULINK blocks generating SVM sector number and a pulse per SVM cycl                                                 | le  |

|                                                                                                                                 | 9   |

| Fig. 1-5:-Three continuous states ON times, $t_i$ , $t_{i+1}$ and $t_z/2$ for one SVM sector when m                             | a   |

| $= 0.5 \text{ and } N_{CS} = 6.$ 1                                                                                              | . 1 |

| Fig. 1-6:-SIMULINK blocks designed to compute continuous states ON times                                                        | . 1 |

| Fig. 1-7:-Sequences with the best harmonics spectrum from literature review                                                     |     |

| Fig. 1-8:- SIMULINK blocks convert generates states signal with SQ1-SAs                                                         | . 5 |

| Fig. 1-9:-States ON times calculation procedure for t <sub>i</sub> , t <sub>i+1</sub> and t <sub>z</sub> in each SVM cycle in   |     |

| one SVM sector when SAs is used.                                                                                                | . 5 |

| Fig. 1- 10: Percentage average active states ON times for SVM sector with SAs m <sub>a</sub> =0.5                               | 5.  |

| 1                                                                                                                               | 7   |

| Fig. 1-11: ON times of an active state with SAs when $N_{CS} = 6$ and $m_a = 1$                                                 | 7   |

| Fig. 1-12:- SIMULINK blocks designed to calculate ON times for states if SAm is used                                            | d.  |

| 1                                                                                                                               | 8   |

| Fig. 1- 13: States ON times calculation procedure for t <sub>i</sub> , t <sub>i+1</sub> and t <sub>z</sub> in each SVM cycle in | n   |

| one SVM sector when SAm is used                                                                                                 | 9   |

| Fig. 1- 14: Percentage average active states ON times for SVM sector with SAm m <sub>a</sub> =0                                 | .5  |

| 2                                                                                                                               | 20  |

| Fig. 1- 15:- ON time of an active state with SAm when $N_{CS} = 6$ and $m_a = 1$                                                | 20  |

|                                                                                                                                 |     |

| Fig. 2-1:- RM technique states ON times calculations process                                                                    | 25  |

| Fig. 2- 2 :- State I <sub>i</sub> ON time calculation when SQ1-RM is used                                                       |     |

| Fig. 2- 3: States $I_{i+1}$ and $I_z$ ON time calculation when SQ1-RM is used                                                   |     |

| Fig. 2- 4: State I <sub>z</sub> ON time calculation when SQ2-RM is used                                                         |     |

| Fig. 2- 5: States $I_i$ and $I_{i+1}$ ON time calculation when SQ2-RM is used                                                   |     |

| · · · · · · · · · · · · · · · ·                                                                                                 |     |

| Fig. 2- 6: State I <sub>i</sub> ON time calculation when SQ3-RM is used                           |

|---------------------------------------------------------------------------------------------------|

| Fig. 2-7: State $I_{i+1}$ and $I_z$ ON time calculation when SQ3-RM is used                       |

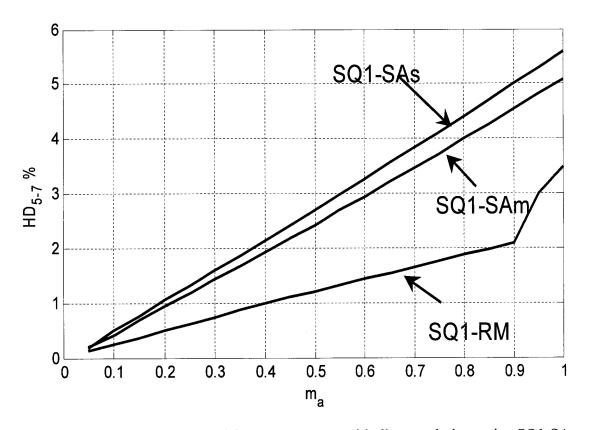

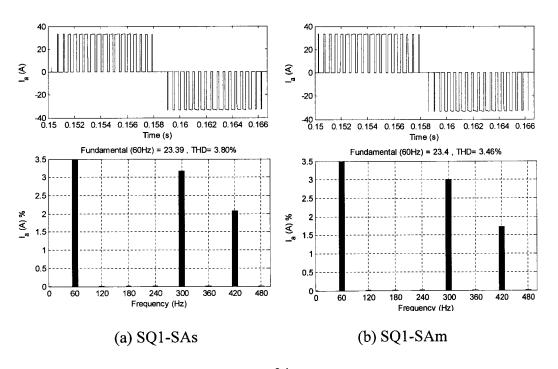

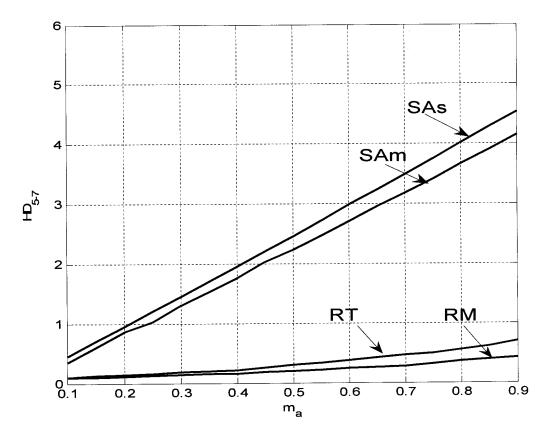

| Fig. 2-8: Index HD <sub>5-7</sub> measured for sequence one with direct techniques, i.e. SQ1-SAs, |

| SQ1-SAm and SQ1-RM                                                                                |

| Fig. 2- 9: Index HD <sub>5-7</sub> in the SVM-CSC ac-side current for different states ON times   |

| calculation techniques with SQ1 when $m_a = 0.7$                                                  |

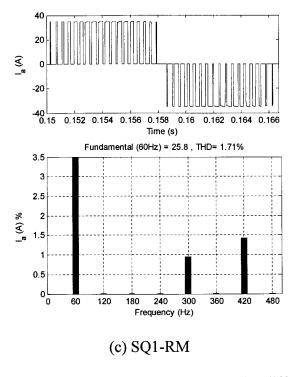

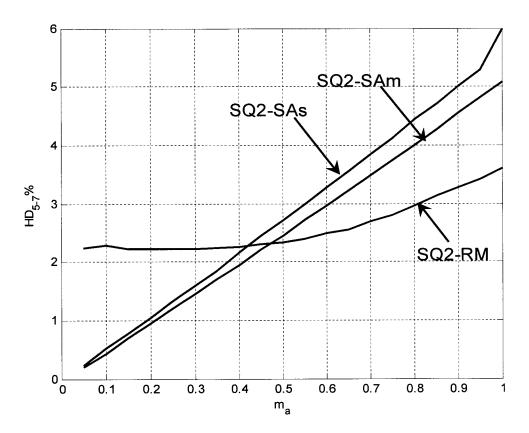

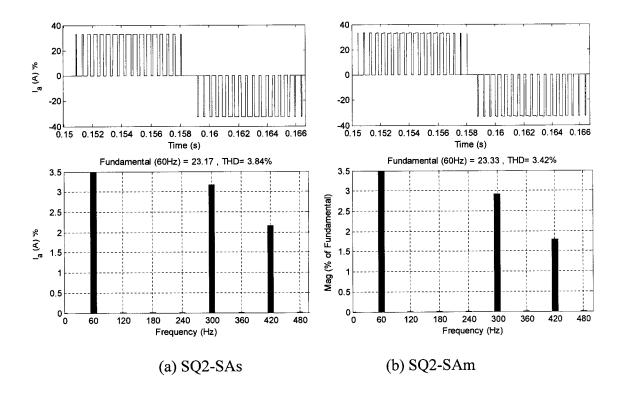

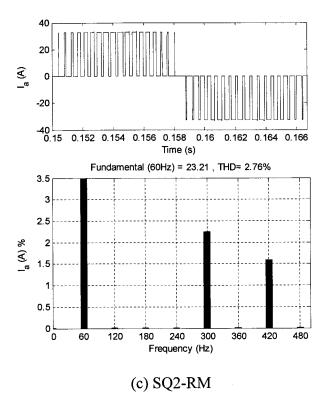

| Fig. 2- $10$ :- Index HD <sub>5-7</sub> measured for SQ2-SAs, SQ2-SAm and SQ2-RM36                |

| Fig. 2- 11: Index HD <sub>5-7</sub> in the CSC ac-side current for different states ON times      |

| calculation techniques with SQ2 when $m_a = 0.7$                                                  |

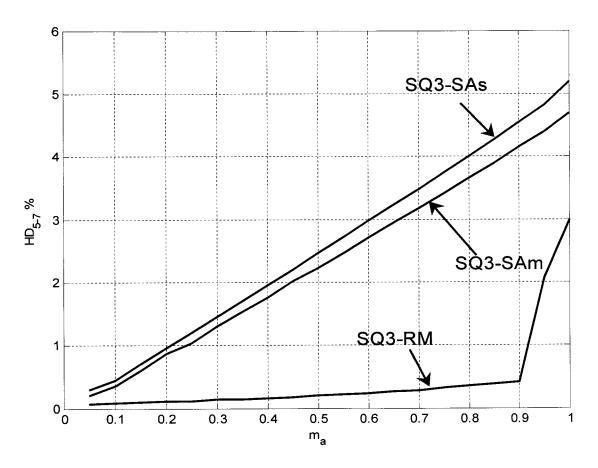

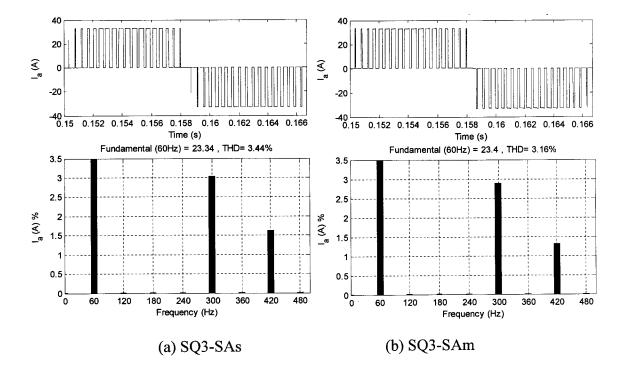

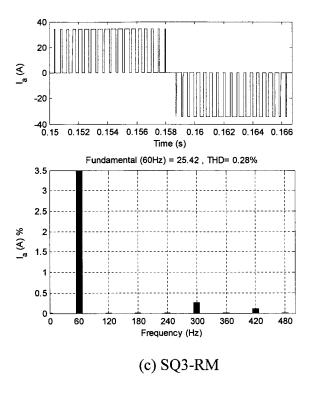

| Fig. 2- 12 :- Index $HD_{5-7}$ measured for SQ3-SAs, SQ3-SAm and SQ3-RM                           |

| Fig. 2- 13: Index HD <sub>5-7</sub> in the CSC ac-side current for different states ON times      |

| calculation techniques with SQ3 when $m_a = 0.7$                                                  |

|                                                                                                   |

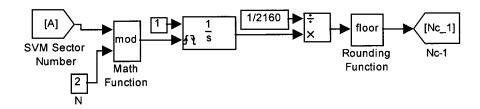

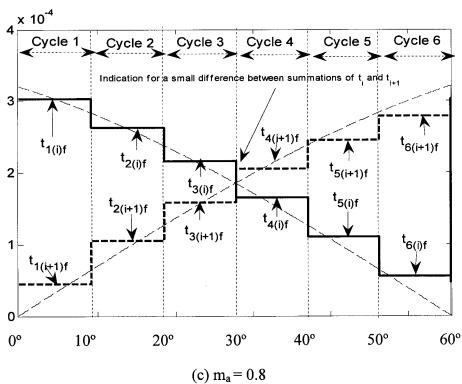

| Fig. 3- 1 :- SIMULINK blocks deciding SVM cycle number                                            |

| Fig. 3- 2 :- SIMULINK blocks used in calculating states ON times for SQ1-EQ 44                    |

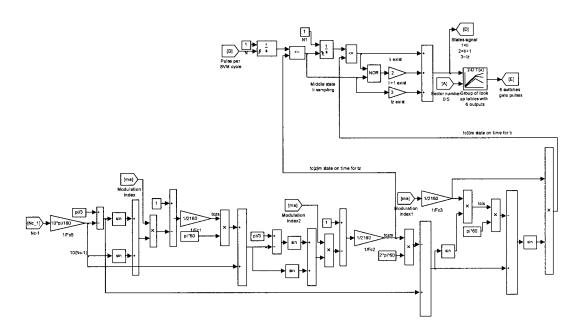

| Fig. 3- 3:- Graphical presentation for SQ1-EQ in the 3 <sup>rd</sup> cycle of 6                   |

| Fig. 3-4:- SIMULINK blocks used in calculating states ON times for SQ1-CF47                       |

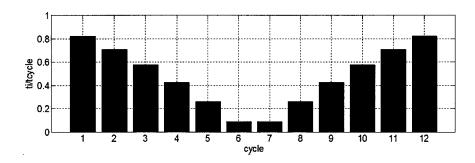

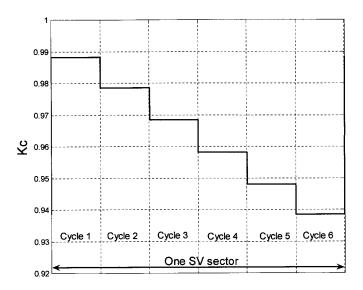

| Fig. 3- 5 :- $K_c$ in one SVM sector cycles with SQ1-CF and $m_a = 0.7$                           |

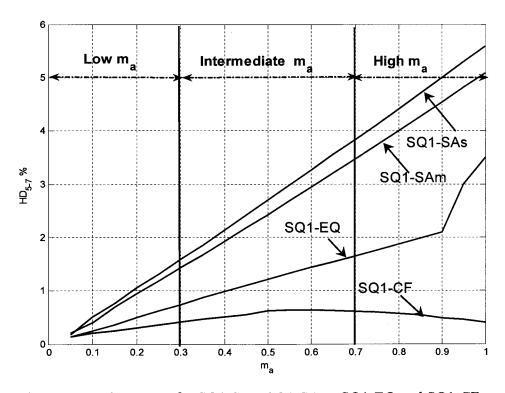

| Fig. 3- 6:- Index HD <sub>5-7</sub> for SQ1-SAs, SQ1-SAm, SQ1-EQ and SQ1-CF49                     |

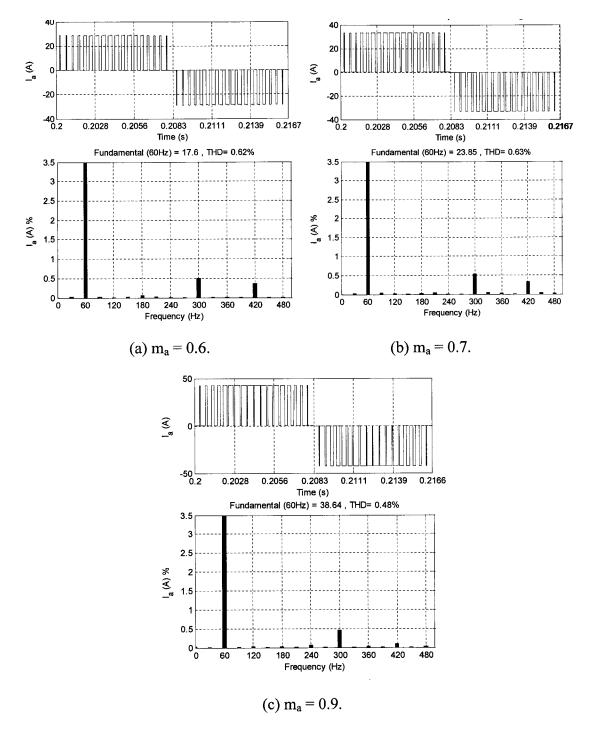

| Fig. 3- 7 :- Index $HD_{5-7}$ in the CSC ac-side current with SQ1-CF at different $m_a$ 's 50     |

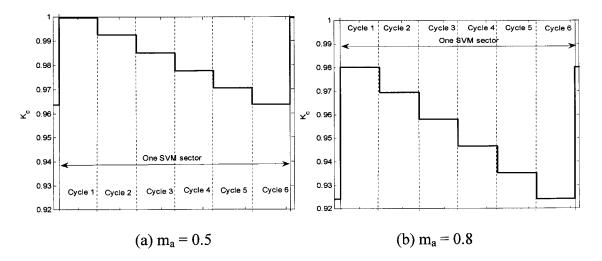

| Fig. 3- 8 :- $K_c$ in one SVM sector cycles when SQ1-CF is used with different $m_a$ 's 52        |

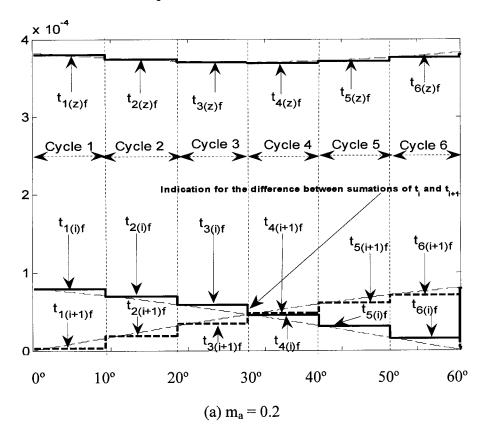

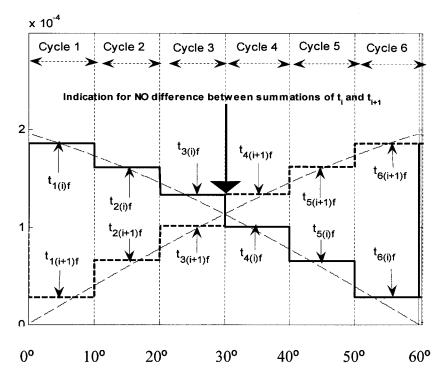

| Fig. 3- 9: States ON times in one SVM sector cycles for SQ1-CF                                    |

| Fig. 3- 10:- SIMULINK blocks used in deciding states ON times for SQ2-EQ 56                       |

| Fig. 3- 11: Graphical presentation for SQ2-EQ in the 3 <sup>rd</sup> cycle of 6                   |

| Fig. 3- 12:- SIMULINK blocks used in calculate states ON times for SQ2-CF 58                      |

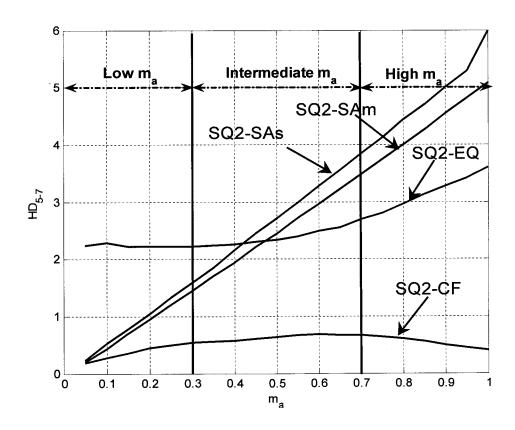

| Fig. 3- 13:- Index HD <sub>5-7</sub> for SQ2-SAs, SQ2-SAm, SQ2-EQ and SQ2-CF                      |

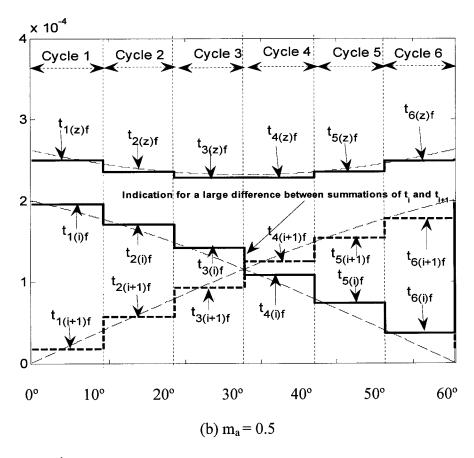

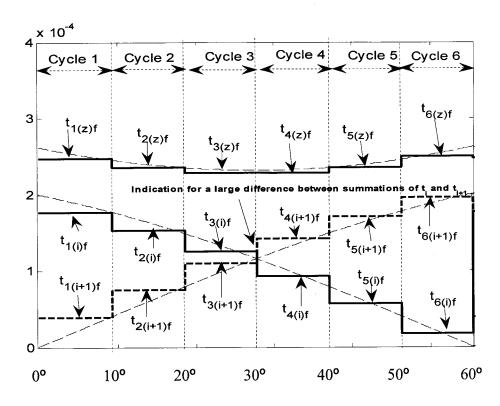

| Fig. 3- 14:- States ON times in one SVM sector cycles for SQ2-CF when $m_a = 0.560$               |

| Fig. 3- 15: Index $HD_{5-7}$ in the CSC ac-side current for SQ2-CF when $m_a = 0.7$               |

| Fig. 3- 16: States ON times when SQ3-EQ is used and $m_a = 0.7$                                   |

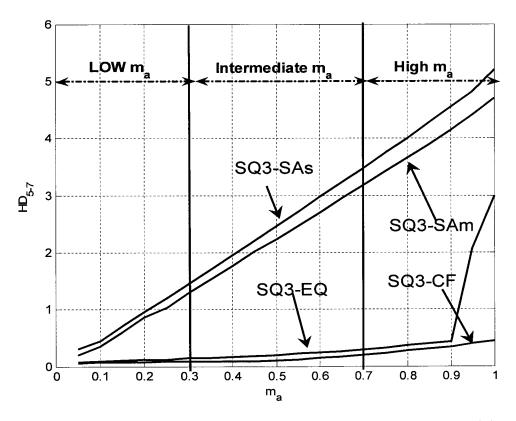

| Fig. 3- 17: Index HD <sub>5-7</sub> calculated for SQ3 using the SAs, SAm, EQ and CF65            |

| Fig. 3- 18:- K <sub>c</sub> values in one SVM sector cycles for SQ3-CF                            |

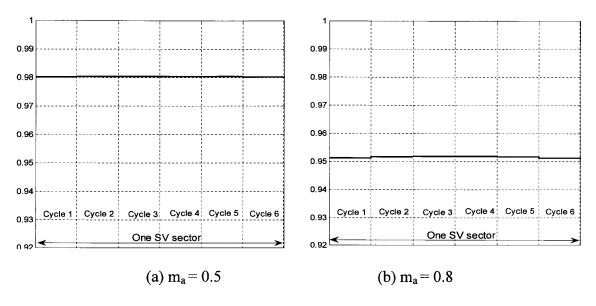

| Fig. 3- 19: Symmetry assessment in SQ3-CF when m <sub>a</sub> =0.5                                       |

|----------------------------------------------------------------------------------------------------------|

| Fig. 3- 20: Index $HD_{5-7}$ in the CSC ac-side current for SQ3-CF when $m_a = 0.767$                    |

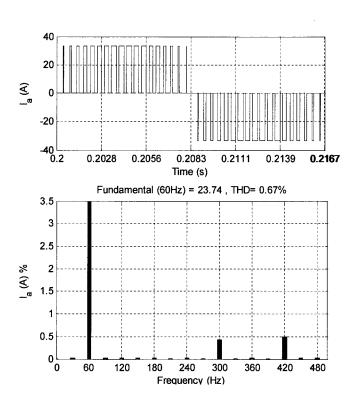

| Fig. 3-21 :- Ac-side CSC current when SQ1-SAs is used with $m_a$ = 0.7 and $f_{grid}$ = 6 Hz.69          |

| Fig. 3- 22 :- Ac-side CSC current when SQ1- CF is used with $m_a$ = 0.7 and $f_{grid}$ = 6 Hz. 69        |

|                                                                                                          |

| Fig. 4-1: RM technique states ON time calculations in the $3^{rd}$ SVM cycle, $m_a = 0.773$              |

| Fig. 4- 2 :- RT for one SVM cycle, $3^{rd}$ cycle of 6 cycles when $m_a = 0.7$                           |

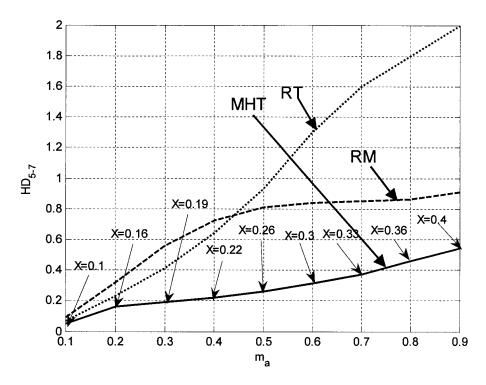

| Fig. 4-3: Index HD <sub>5-7</sub> for direct techniques of SQ3, i.e. SAs, SAm, RM and RT 75              |

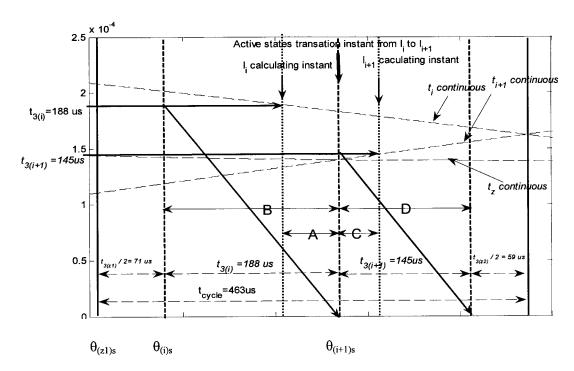

| Fig. 4-4: Variable X definition using A, B, C and D in the $3^{rd}$ SVM cycle when $m_a =$               |

| 0.7  and  X = 0.3                                                                                        |

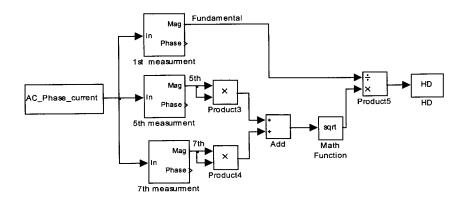

| Fig. 4- 5 :- SIMULINK model used to measure HD <sub>5-7</sub>                                            |

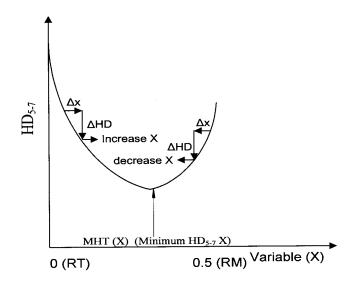

| Fig. 4- 6: Minimum Harmonics Tracking (MHT) concept                                                      |

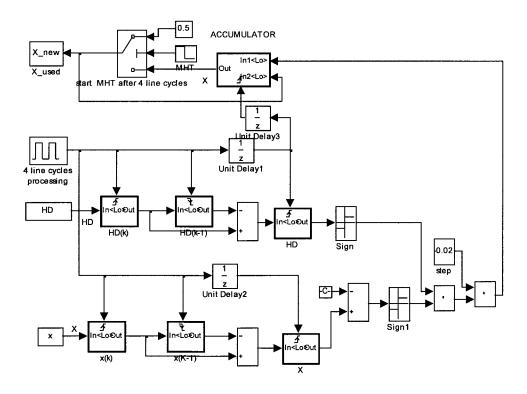

| Fig. 4- 7 :- SIMULINK model for MHT technique                                                            |

| Fig. 4- 8 :- SIMULINK model used to calculate states ON times using $X_1$ and $X_2$ 80                   |

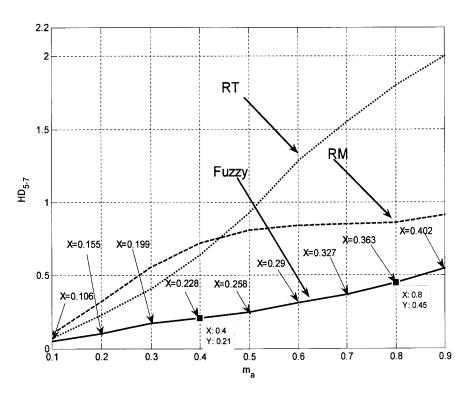

| Fig. 4- 9:- Index HD <sub>5-7</sub> for RT, RM and MHT techniques                                        |

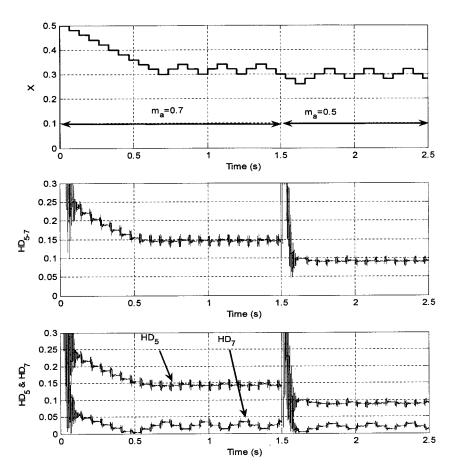

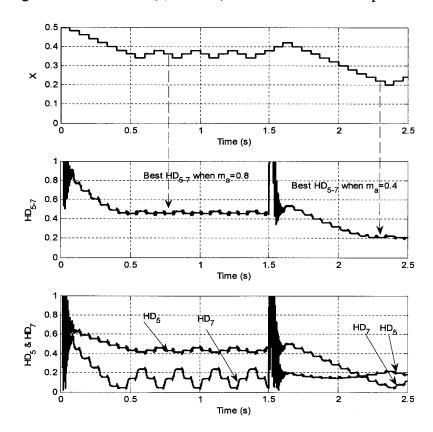

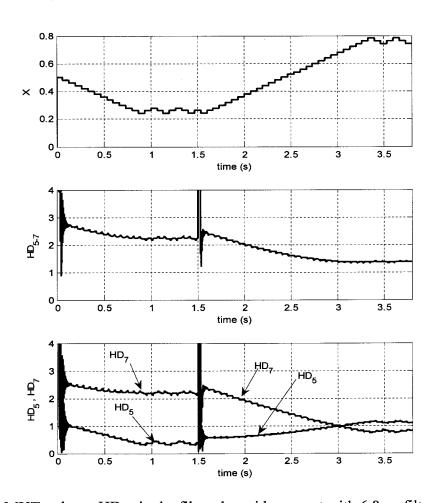

| Fig. 4- 10 :- MHT technique reduces $HD_{57}$ in CSC ac-side current when $m_a\!=\!0.7$ for 1.5s         |

| then $m_a = 0.5$ for 1s                                                                                  |

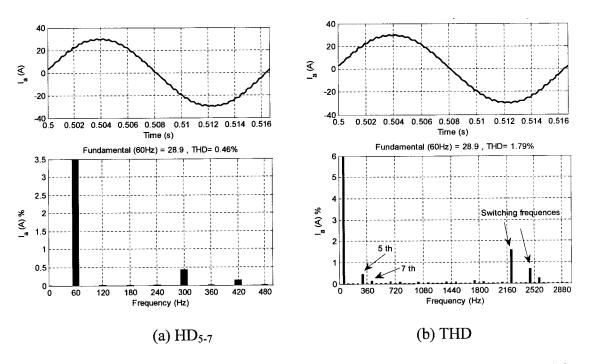

| Fig. 4- 11 :- Index $HD_{5-7}$ in the CSC ac-side current with MHT technique and $m_a = 0.7.82$          |

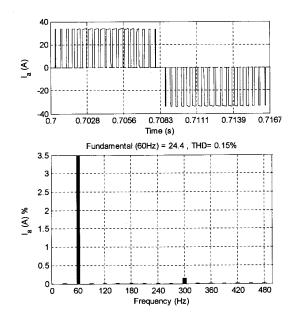

| Fig. 4- 12:- The effect of ac-side filter on 5th, 7th and switching frequencies harmonics.84             |

| Fig. 4- 13 :- THD in CSC filtered ac-side current with SQ1-SAs, 9 pu filter and $m_a = 0.7$ .            |

|                                                                                                          |

| Fig. 4- 14 :- THD in CSC filtered ac-side current with SQ1-SAs, 5.93pu filter and $m_a\!\!=\!\!0.7$      |

|                                                                                                          |

| Fig. 4- 15 :- THD in CSC filtered ac-side current with SQ1-SAs, 3 pu filter and $m_a\!=\!0.7$ .          |

|                                                                                                          |

| Fig. 4- 16: MHT technique reduces index $\mathrm{HD}_{5-7}$ in filtered ac-side current when $m_a$ = 0.7 |

| for 1.5s then $m_a = 0.5$ for 1s                                                                         |

| Fig. 4- 17:- THD in CSC filtered ac-side current with MHT, $5.93$ pu filter and $m_a = 0.7$ .            |

|                                                                                                          |

| Fig. 4- 18: Index HD <sub>5-7</sub> for RM, RT and MHT with 6.8pu ac-side filter                         |

| Fig. 4- 19: MHT technique reduces HD <sub>5-7</sub> in the filtered ac-side current                      |

| Fig. 4- 20 :- Index HD <sub>5-7</sub> and THD with MHT and 6.8pu ac-side filter at $m_a = 0.8$              | 90    |

|-------------------------------------------------------------------------------------------------------------|-------|

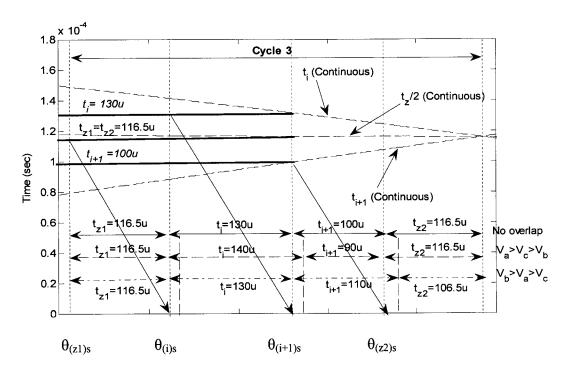

| Fig. 4-21: Overlap period effect on RT technique for one SVM cycle (3 <sup>rd</sup> cycle) in               |       |

| SVM sector one when $m_a = 0.5$ .                                                                           | 92    |

| Fig. 4- 22 :- MHT reduces $HD_{5-7}$ in the filtered ac-side current with 6.8 pu filter, 5 $\mu s$          |       |

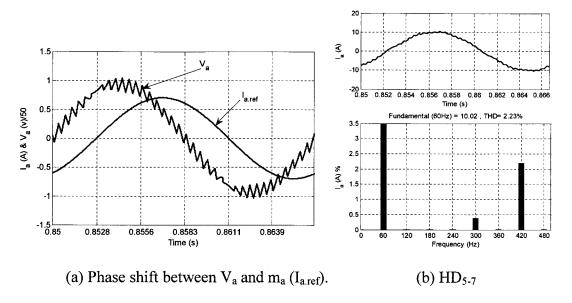

| overlap period and $m_a = 0.7$ , PF = 0.5 (lagging) for 1.5s then PF = 0.866 (leading)                      | 94    |

| Fig. 4- 23 :- Investigation for single variable MHT when PF = 0.5 (lagging) and $m_a$ =                     | 0.7.  |

|                                                                                                             | 95    |

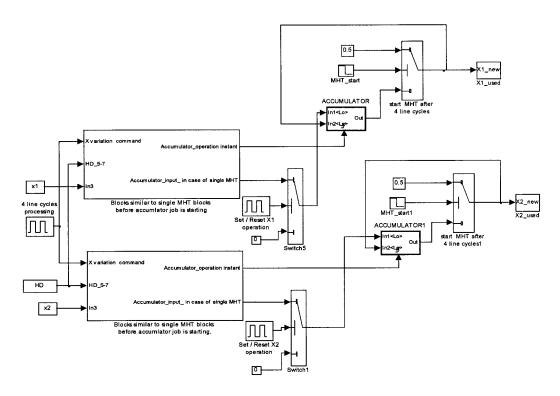

| Fig. 4- 24 :- SIMULINK model for two variables MHT                                                          | 96    |

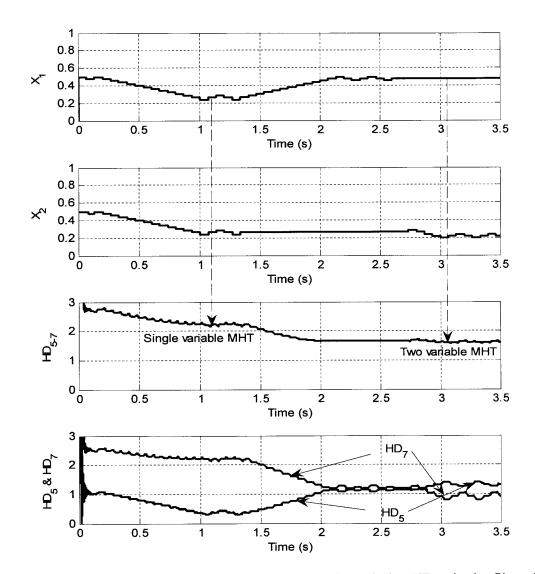

| Fig. 4- 25: Two variables MHT technique reduces index HD <sub>5-7</sub> in the filtered ac-side             | е     |

| current with 6.8pu filter and 5 $\mu$ s overlap period, $m_a$ = 0.7 and PF = 0.5 (leading)                  | 97    |

| Fig. 4- 26 :- Index $HD_{5-7}$ in the CSC ac-side current with two variables MHT, 5 $\mu s$                 |       |

| overlap period, 6.8 pu filter cut off frequency, $m_a = 0.7$ and PF = 0.5 (leading)                         | 98    |

| Fig. 4- 27: Experimental HD <sub>5</sub> and HD <sub>7</sub> in the filtered CSC ac-side current with 6.8 I | ou    |

| filter when $m_a = 0.7$ and PF = 0.866 (leading).                                                           | 99    |

|                                                                                                             |       |

| Fig. 5-1: SIMULINK blocks calculate states ON times using Fuzzy logic                                       | . 104 |

| Fig. 5- 2 :- Internal construction of Fuzzy logic.                                                          | . 105 |

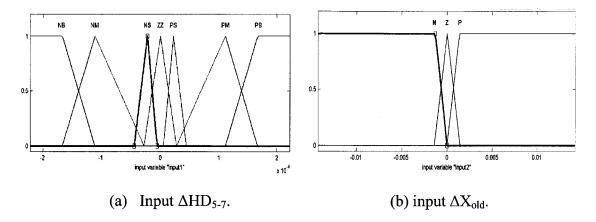

| Fig. 5- 3 :- Input membership functions for the Fuzzy model                                                 | . 105 |

| Fig. 5- 4 :- Output $\Delta X_{new}$ membership functions for the Fuzzy model                               | . 105 |

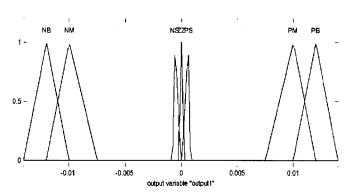

| Fig. 5- 5 :- Surface for the Fuzzy logic.                                                                   | . 105 |

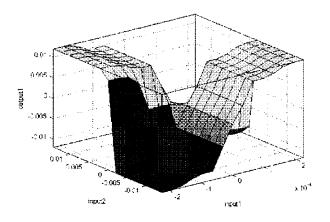

| Fig. 5- 6: Fuzzy logic reduces HD <sub>5-7</sub> in CSC ac-side current                                     | . 108 |

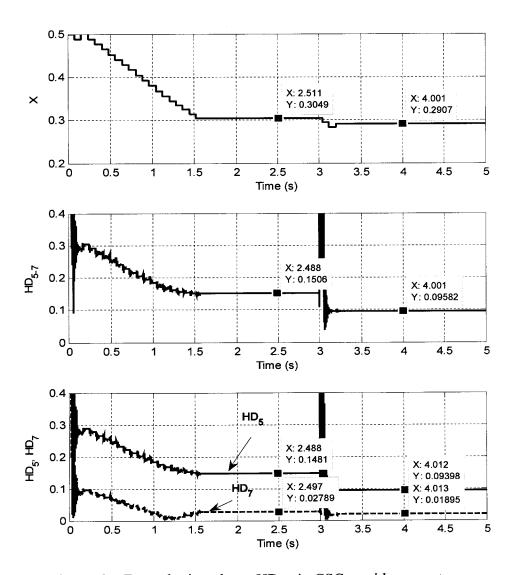

| Fig. 5-7:- HD <sub>5-7</sub> for RM, RT and Fuzzy logic with 6.8pu CSC ac-side filter                       | . 109 |

| Fig. 5-8: Fuzzy logic technique reduces HD <sub>5-7</sub> in the filtered ac-side current with 6.           | 8pu   |

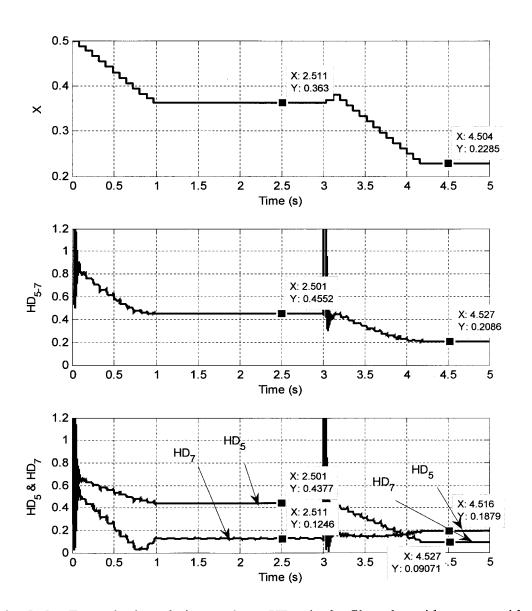

| filter when $m_a = 0.8$ for the first 3s then $m_a = 0.4$ for the last 2s                                   | . 110 |

|                                                                                                             |       |

| Fig. 6- 1 :- Six SCRs based CSC.                                                                            | . 113 |

| Fig. 6- 2 :- Six IGBTs based CSC                                                                            | . 115 |

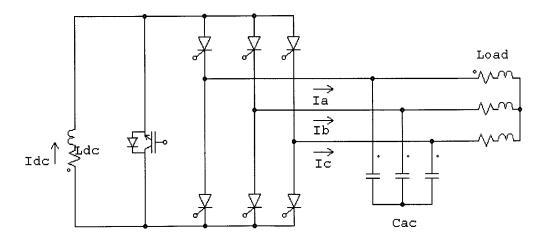

| Fig. 6-3:- HCSC with six SCRs, four IGBTs and seven diodes                                                  | . 117 |

| Fig. 6- 4: Six SCRs one switch hybrid unidirectional CSR                                                    | . 117 |

| Fig. 6- 5: Six SCRs one switch hybrid unidirectional CSI                                                    | . 118 |

| Fig. 6-6: Hybrid bi-directional CSC (HCSC) with an SCR bridge and two IGBTs                                 | . 119 |

|                                                                                                             |       |

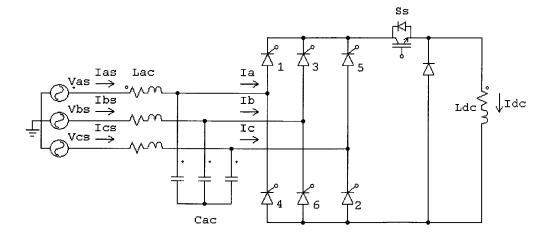

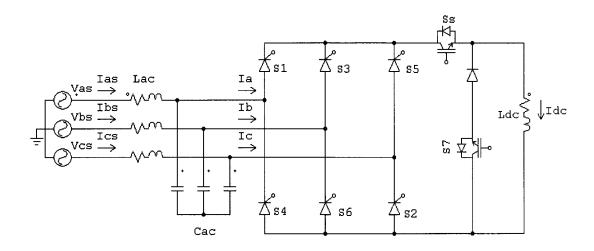

| Fig. 6-7: Hybrid bi-directional CSC (HCSC) with three SCRs and four IGBTs 121                                           |

|-------------------------------------------------------------------------------------------------------------------------|

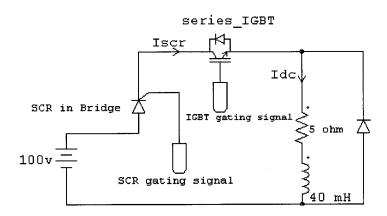

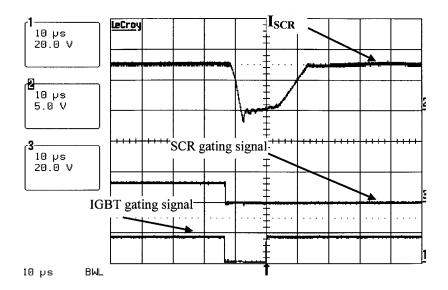

| Fig. 6-8: Experimental test verifies the active commutation feasibility                                                 |

| Fig. 6- 9:- IGBT and SCR gate signals in the active commutation feasibility test 125                                    |

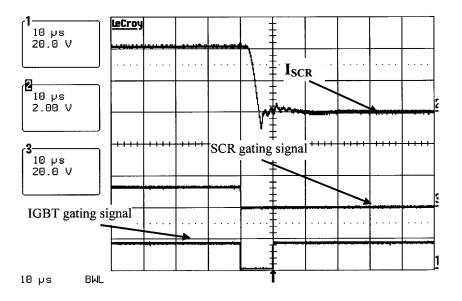

| Fig. 6- 10 :- Successful commutation in the active commutation test, $I_{dc} = 8A$ , $t_x = 10 \mu s$ .                 |

|                                                                                                                         |

| Fig. 6- 11:- Commutation failure in the active commutation test, $I_{dc} = 15 \text{ A}$ , $t_x = 15.5 \mu\text{s}$ .   |

|                                                                                                                         |

|                                                                                                                         |

| Fig. 7-1: Traditional CSC states sequence used in part two of the thesis                                                |

| Fig. 7-2: Definition of the sectors (0 to 5), states (I <sub>1</sub> to I <sub>9</sub> ), and the switches which are    |

| ON in each state in traditional 6-switches SVM-CSC                                                                      |

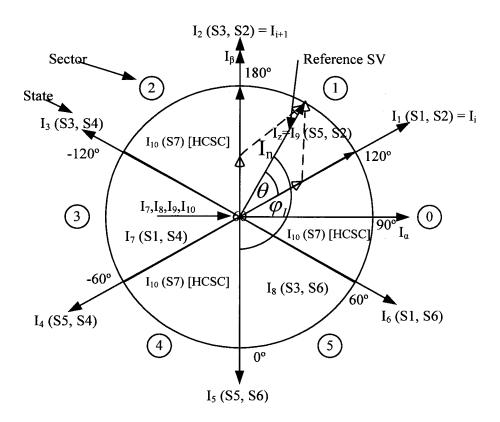

| Fig. 7-3: Definition of the sectors (0 to 5), states (I <sub>1</sub> to I <sub>10</sub> ), ON switches in each state    |

| and the reference current vector for three SCRs and four IGBTs HCSC topology 131                                        |

| Fig. 7- 4:- Sequence of states for operation with active commutation (HS-SVM) 133                                       |

| Fig. 7-5: Definition of the sectors (0 to 5), states (I <sub>1</sub> to I <sub>7</sub> ), switches on in each state and |

| the reference current vector for six SCRs and two IGBTs HCSC topology                                                   |

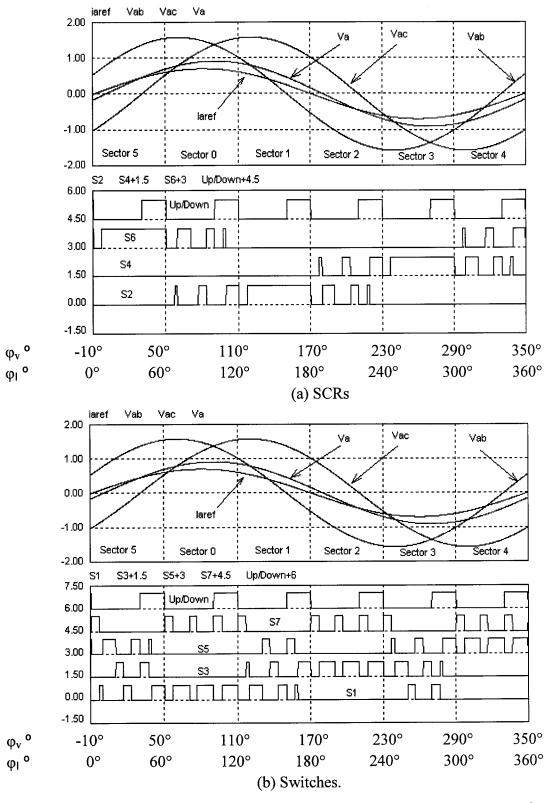

| Fig. 7- 6 :- Gating pattern for upper IGBTs in 6-switches SVM-CSC when $m_a \!\!=\! 0.7~136$                            |

| Fig. 7-7 :- SCRs gating pattern in HCSC with HS-SVM when $m_a = 0.7$ and $N_{CS} = 3137$                                |

| Fig. 7- 8 :- IGBTs gating pattern in HCSC with HS-SVM when $m_a = 0.7$ and $N_{CS} = 3.137$                             |

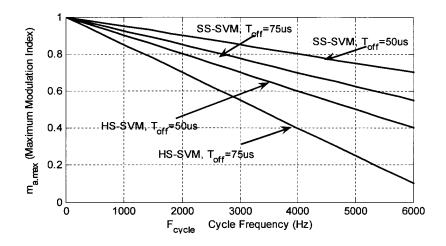

| Fig. 7- 9 :- $m_{a.max}$ for HCSC as a function of $f_{cycle}$ at different SCR turn off time $(t_q)$ 139               |

| Fig. 7- 10:- Semiconductors and their drives in Three SCR four IGBTs HCSC 140                                           |

| Fig. 7- 11 :- Complete view for Three SCR four IGBTs HCSC                                                               |

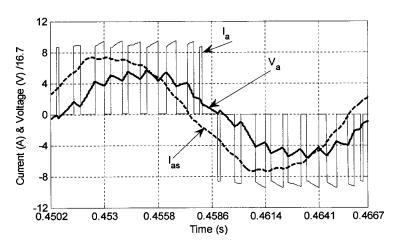

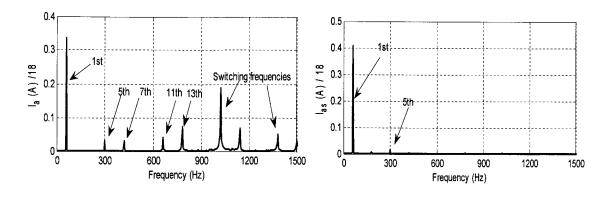

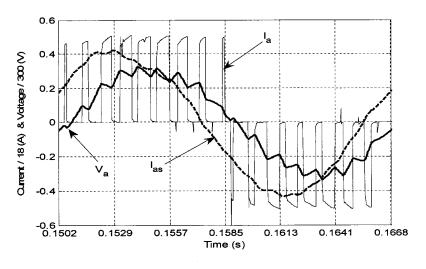

| Fig. 7- 12 :- Simulation results for HCSC with HS-SVM, $m_a$ = 0.7, $N_{CS}$ = 3 and $V_a$ , $I_a$ in                   |

| phase                                                                                                                   |

| Fig. 7- 13 :- Experimental results for HCSC with HS-SVM, $m_a$ = 0.7, $N_{CS}$ = 3 and $V_a$ , $I_a$                    |

| in phase                                                                                                                |

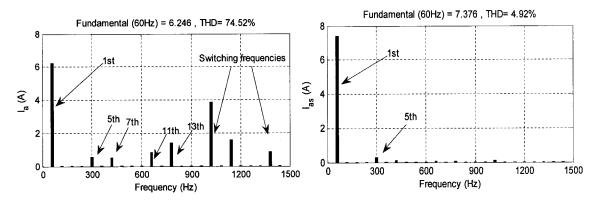

| Fig. 7- 14 :- Simulation results for SVM-CSC, $m_a$ = 0.7, $N_{CS}$ = 3 and $V_a$ , $I_a$ in phase 144                  |

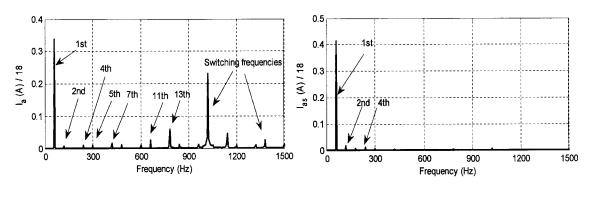

| Fig. 7- 15 :- Simulation results for HCSC with HS-SVM for $m_a$ = 0.7, $N_{CS}$ = 3 144                                 |

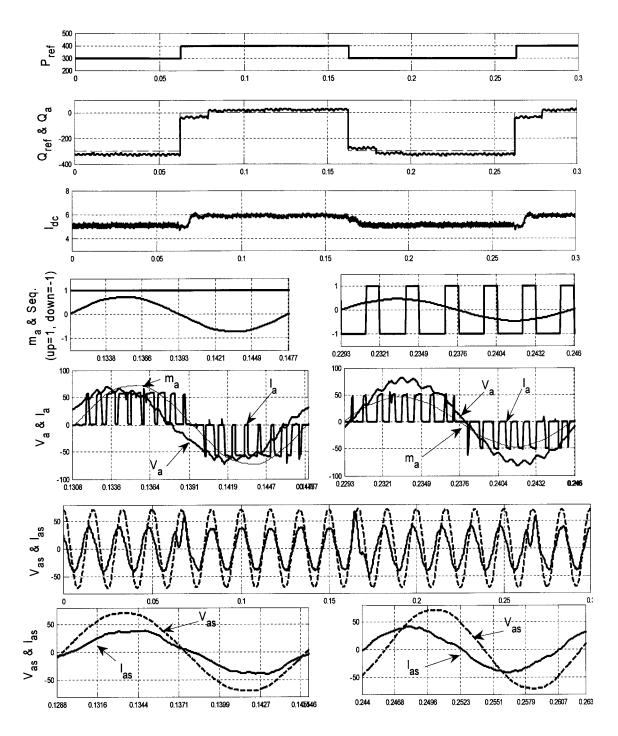

| Fig. 7- 16: The effect of P <sub>ref</sub> and Q <sub>ref</sub> variations in HCSC with HS-SVM                          |

|                                                                                                                         |

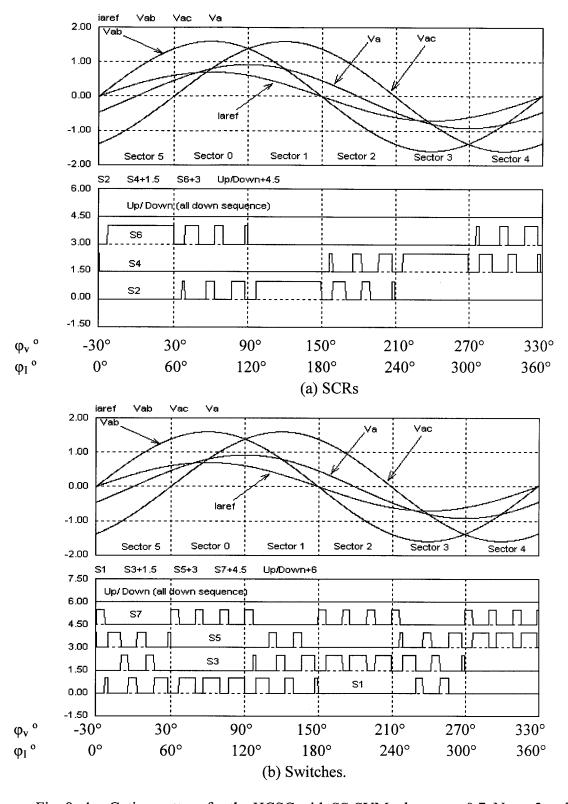

| Fig. 8-1: Sequences of states required for line-commutation (soft switching)                                            |

| Fig. 8-2: Input voltage relationships and current complex plane for the HCSC with                                           |

|-----------------------------------------------------------------------------------------------------------------------------|

| PF=cos 10°, leading                                                                                                         |

| Fig. 8-3: Gating pattern for the HCSC with SS-SVM when $m_a = 0.7$ , $N_{CS} = 3$ and                                       |

| PF=cos 10°, leading                                                                                                         |

| Fig. 8-4: Gating pattern for the HCSC with SS-SVM when $m_a = 0.7$ , $N_{CS} = 3$ and                                       |

| PF=cos 30°, leading                                                                                                         |

| Fig. 8-5: - m <sub>a.max</sub> VS f <sub>cycle</sub> at different t <sub>off.min</sub> for HS-SVM and SS-SVM techniques 164 |

| Fig. 8-6: Simulation results for HCSC with SS-SVM for $m_a = 0.7$ , $N_{CS} = 3$ and                                        |

| PF=cos10°, leading                                                                                                          |

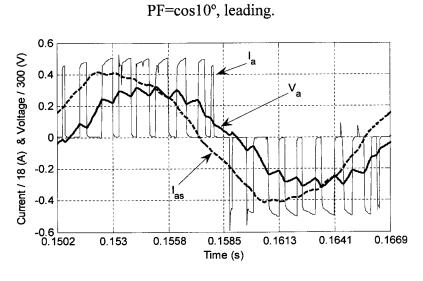

| Fig. 8-7: Experimental results for HCSC with SS-SVM for $m_a$ = 0.7, $N_{CS}$ = 3 and                                       |

| PF=cos 10°, leading                                                                                                         |

| Fig. 8-8: Experimental results for commutation failure with down sequence in all SVM                                        |

| cycles for HCSC with SS-SVM for $m_a$ = 0.7, $N_{CS}$ = 3 and PF = $\cos 10^{\circ}$ , leading 167                          |

| Fig. 8- 9: The effect of P <sub>ref</sub> and Q <sub>ref</sub> variations in HCSC with SS-SVM                               |

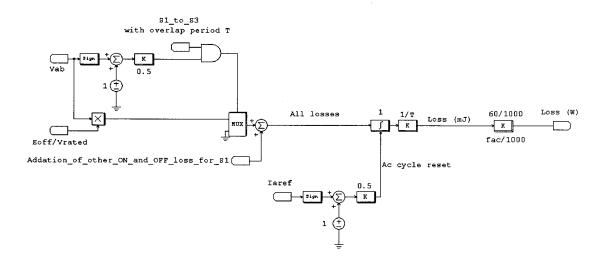

| Fig. 9- 1 :-Simulation procedure to calculate S1 switching power loss                                                       |

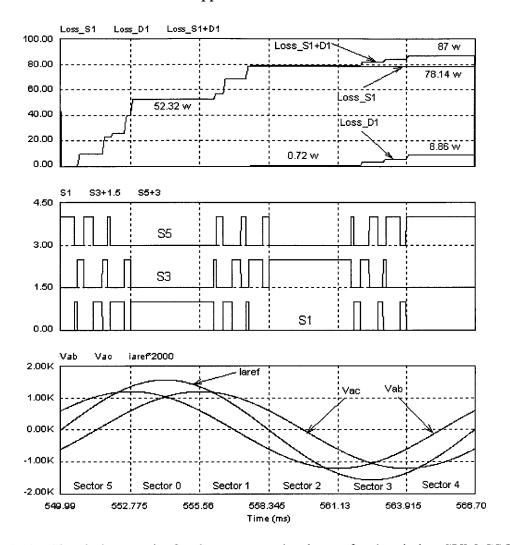

| Fig. 9- 2:- Simulation results for the commutation losses for 6-switches SVM-CSC 185                                        |

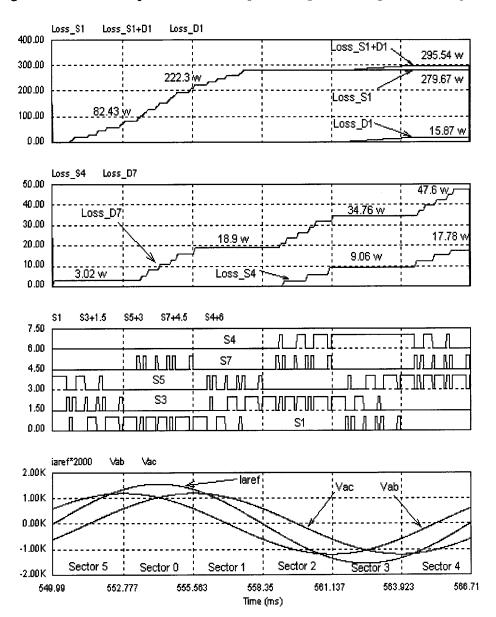

| Fig. 9- 3:- Simulation results for commutation losses for HCSC with HS-SVM 188                                              |

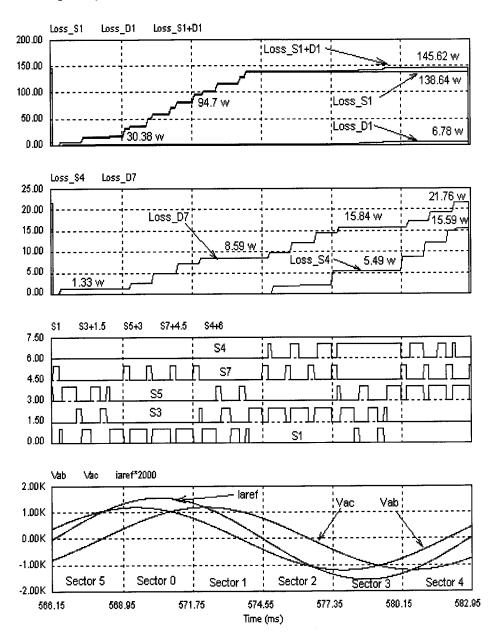

| Fig. 9- 4:- Simulation results for the commutation losses for HCSC with SS-SVM 190                                          |

## **LIST OF TABLES**

| Table 1-1:- States realizations and switches switching functions in CSC 7          |

|------------------------------------------------------------------------------------|

| TABLE 1-2:- SECTORS DIVISION IN SVM-CSC                                            |

| Table 1-3:- ON switches in each state in SVM-CSC                                   |

|                                                                                    |

| Table 5-1:- Rule base for the Fuzzy model                                          |

|                                                                                    |

| Table 6- 1 :- Experimental relation between the SCR current ( $I_{dc}$ ) and the   |

| MINIMUM TURN OFF TIME $(t_x)$                                                      |

|                                                                                    |

| Table 7-1:- States realizations and switching functions of three SCRs four         |

| IGBTs HCSC                                                                         |

| Table 7- $2$ :- States, realizations and switching functions of six SCRs two IGBTs |

| HCSC                                                                               |

|                                                                                    |

| Table 8- $1:$ - AC side voltage relations and required states sequences in SS-     |

| SVM                                                                                |

|                                                                                    |

| Table 9-1:- Capital cost comparison between 6-switches CSC and HCSC 172            |

| Table 9-2:- Datasheet information for SCR, diode and IGBT used in HCSC $174$       |

| TABLE 9-3:- CONDUCTION POWER LOSSES FOR EACH SCR, DIODE, IGBT AND FOR THE          |

| WHOLE TOPOLOGY                                                                     |

| TABLE 9-4:—LOSSES FOR SEMICONDUCTORS USED IN THE 6-SWITCH CSC AND HCSC 191         |

#### LIST OF ACRONYMS

A (Unit) Ampere

ac Alternating Current

ASCI Auto Sequential Commutated current source Inverter

CF Correction Factor

CSC Current Source Converter

CCM Continuous Conduction Mode

CMOS Complementary Metal Oxide Semiconductor

CSR Current Source Rectifier

CSI Current Source Inverter

db Decibel

dc Direct Current

dq Direct and Quadratic component

DSP Digital Signal Processor

dSPACE Digital Signal Processor with real-time hardware, I/O interfaces

connected via RTI blocks integrated into MATLAB/Simulink

DS-1103 A type of Digital signal processor with rapid control prototyping

EQ EQuation

F Farad (capacitor measuring unit)

f Frequency

OPAL-RT A company for Open Scalable Real-Time simulation and control devices

OP-5000 An electronic card use fast processor for rapid control prototyping

GTO Gate Turns Off

H Henry (Inductor measurement unit)

HCSC Hybrid Current Source Converter

HS-SVM Hard Switching Space Vector Modulation

Hz Hertz

HVDC High Voltage Direct Current

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

IGCT Integrated Gate Commutated Thyristor

LEM Type of voltage and current measurement device (transducer)

LOH Low Order Harmonics

LSF Low Switching Frequency

MOSFET Metal Oxide Silicon Field Effect Transistor

MHT Minimum Harmonics Tracking

pu Per unit

PCC Point of Common Coupling

PWM Pulse Width Modulation

P Active power

PLL Phase Locked Loop

PF Power Factor

Q Reactive power

RM Record Middle

RT Record Transition

RTI Real Time Interface

SAs Start SAmpling

SAm Middle SAmpling

SCR Silicon Controlled Rectifier

SHE Selective Harmonics Elimination

SMES Super Magnetic Energy Storage

SPWM Sinusoidal Pulse Width Modulation

SQ1 SeQuence one

SQ2 SeQuence two

SQ3 SeQuence three

SS Soft Switching

SS-SVM Soft Switching Space Vector Modulation

STATCOM STATic synchronous COMpensator

SV Space Vector

SVM Space Vector Modulation

THD Total Harmonic Distortion

UPF Unity Power Factor

V Voltage

VAR Variable Reactive Power

VSC Voltage Source Converter

VSR Voltage Source Rectifier

VSI Voltage Source Inverter

t time (s)

W Watt (Active power measurement unit)

$\Omega$  Ohm (Resistor measurement unit)

## LIST OF PRINCIPAL SYMBOLS

| abc/αβ              | Conversion from three axis stationary frame to two axis stationary frame.              |

|---------------------|----------------------------------------------------------------------------------------|

| abc/dq              | Conversion from three axis stationary frame to two axis rotating frame.                |

| A                   | The distances between t <sub>i</sub> calculating and active states transition instants |

| В                   | I <sub>i</sub> ON time                                                                 |

| C                   | The distance between $t_{i+1}$ calculating and active states transition instants       |

| $C_{ac}$            | Ac side Capacitance                                                                    |

| C                   | SVM Cycle number                                                                       |

| D                   | I <sub>i+1</sub> ON time                                                               |

| $f_{\text{ac}}$     | Alternating current ac-side cycle frequency                                            |

| $f_{ m cycle}$      | SVM cycle frequency                                                                    |

| HD <sub>5-7</sub>   | Index for 5 <sup>th</sup> and 7 <sup>th</sup> non-characteristics harmonics components |

| HD <sub>5</sub>     | Index for 5 <sup>th</sup> non-characteristics harmonics components                     |

| HD <sub>7</sub>     | Index for 7 <sup>th</sup> non-characteristics harmonics components                     |

| $I_a$               | pulsated current appears in the HCSC terminals for phase A                             |

| I <sub>as</sub>     | Grid current for phase A at the point of common coupling                               |

| $I_{(abc)cap}$      | Three phases ac-side capacitor current                                                 |

| I <sub>(abc)s</sub> | Three phases ac-side source currents at PCC                                            |

| I <sub>(abc)</sub>  | Three phases currents in converter ac-side, not include the ac-side filter             |

| $I_{dc}$            | Dc-side current                                                                        |

| $I_{(dq)}$          | Current in HCSC ac-side terminal with two rotating axis frame.                         |

| $I_{(dq)s}$         | Ac-side currents in PCC with two rotating axis frame.                                  |

| $\overline{I_{da}}, \overline{I_{qa}}$    | dq frame values for the required currents from HCSC in capacitor       |  |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

|                                           | terminals after changing to adequate SS-SVM concept.                   |  |  |  |  |  |

| $\overline{I_{db}}$ , $\overline{I_{qb}}$ | dq frame values for the required currents from HCSC in capacitor       |  |  |  |  |  |

|                                           | terminals before changing to adequate SS-SVM concept.                  |  |  |  |  |  |

| $I_{(\alpha\beta)cap}$                    | Ac-side filer capacitor current in HCSC with two stationary axis frame |  |  |  |  |  |

| $I_{(\alpha\beta)s\_ref}$                 | The required current from HCSC in the capacitor terminals with two     |  |  |  |  |  |

|                                           | stationary axis frame                                                  |  |  |  |  |  |

| $I_{(\alpha\beta)s}$                      | Ac-side currents in PCC with two stationary axis frame.                |  |  |  |  |  |

| $i_a$ , $i_b$ and $i_c$                   | Instantaneous ac-side currents for phases A, B and C                   |  |  |  |  |  |

| $I_n$                                     | Reference current vector in SVM                                        |  |  |  |  |  |

| $I_1$ - $I_{10}$                          | States space vectors in SVM-CSC                                        |  |  |  |  |  |

| $I_i \ and \ I_{i+1}$                     | Active state vectors                                                   |  |  |  |  |  |

| $I_z$                                     | Zero state vector                                                      |  |  |  |  |  |

| $I_{(1^{st})}$                            | Fundamental component for the current                                  |  |  |  |  |  |

| $I_{(5^{th})}$                            | Fifth order harmonics component for the current                        |  |  |  |  |  |

| I <sub>(7<sup>th</sup>)</sub>             | Seventh order harmonics component for the current                      |  |  |  |  |  |

| k                                         | Safety factor required to grantee safe commutation in HCSC             |  |  |  |  |  |

| K <sub>c</sub>                            | Correction factor required to reduce HD <sub>5-7</sub> in CF technique |  |  |  |  |  |

| $L_{ac}$                                  | Ac side inductance                                                     |  |  |  |  |  |

| $m_a$                                     | Modulation index                                                       |  |  |  |  |  |

| $m_{a.max}$                               | Maximum modulation index                                               |  |  |  |  |  |

| n                                         | Number of SVM cycle $n = 1, 23 N_{CS}$ .                               |  |  |  |  |  |

| $N_{\rm C}$                               | SVM cycle Number                                                       |  |  |  |  |  |

|                                           |                                                                        |  |  |  |  |  |

N<sub>CS</sub> Number of cycles per sector

P<sub>ref</sub> Reference active power

R<sub>ac</sub> Ac side filter resistance

Q<sub>ref</sub> Reference reactive power

Q<sub>a</sub> Available reactive power in SS-SVM.

t<sub>ac</sub> Alternating Current ac-side cycle time

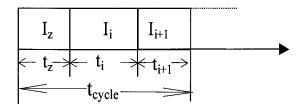

t<sub>cycle</sub> SVM cycle time

$t_i$  and  $t_{i+1}$  Active states ON times

t<sub>sector</sub> SVM sectors time

$t_i$  (N<sub>C</sub>) State  $I_i$  ON times in SVM cycle N<sub>C</sub>

$t_{i+1}$  (N<sub>C</sub>) State  $I_{i+1}$  ON time in SVM cycle N<sub>C</sub>

t<sub>z</sub> Zero state ON time

t<sub>z1</sub> First half zero state ON time in SQ3

t<sub>z2</sub> Second half zero state ON time in SQ3

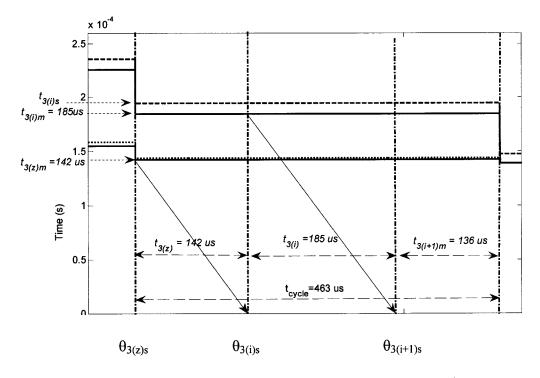

$t_{x(y)}$  State 'I<sub>y</sub>' ON times in SVM cycle 'x'

$t_{x(y)m}$  State 'I<sub>y</sub>' ON time in SVM cycle 'x' calculated using continuous t<sub>y</sub> in the

middle of state 'I<sub>y</sub>'

$t_{x(y)s}$  State 'I<sub>y</sub>' ON time in SVM cycle 'x' calculated using continuous t<sub>y</sub> in the

starting of state 'I<sub>y</sub>'

$t_{x(y)f}$  Final state 'I<sub>y</sub>' ON time in SVM cycle 'x' when CF is used

t<sub>z.min</sub> Minimum zero state time interval to guarantee the safe commutation of

the SCRs in HCSC

t<sub>q</sub> Data sheets turn off time for SCRs

| $t_{ m off.min}$ | Minimum turn-off time of an SCR that is actively commutated by       |

|------------------|----------------------------------------------------------------------|

|                  | diverting its current and without being reverse biased.              |

| $t_{\rm off}$    | Turn-off time of an SCR                                              |

| T                | Total pulses cycle in the HCSC feasibility experimental test         |

| $t_{on}$         | SCR gate excitation period in the HCSC feasibility experimental test |

$t_{x}$  Required time to recover SCR in the HCSC feasibility experimental test,

during this period SCR and IGBT have no gate signals.

X<sub>old</sub> Input of Fuzzy logic effecting LOH

X<sub>new</sub> Output of Fuzzy logic required to reduce LOH

V<sub>a</sub> or V<sub>A</sub> Ac-side capacitor voltage for phase A

V<sub>(abc)s</sub> Three phases ac-side source voltages

V<sub>(abc)</sub> Three phases ac-side capacitor voltage

V<sub>dc</sub> direct current in the experimental test circuit

$V_{(\alpha\beta)s}$  Ac-side source voltages in two stationary axis frame

$V_{(\alpha\beta)}$  Ac-side capacitor voltages in two stationary axis frame

$\phi_I$  Space vector angle for the SVM reference current

$\phi_V$  Space vector angle for the ac-side capacitor voltage

$\theta$  The angle of the reference current vector in a given SVM sector

$\omega$  Angular frequency (Space vector rotation speed)

$\theta_{off}$  Offset angle required to satisfy middle sampling (SAm)

$\theta_{x(y)m}$  The SVM sector angle at SVM cycle 'x' in the middle of state 'I<sub>y</sub>'

$\theta_{x(y)s}$  The SVM sector angle at SVM cycle 'x' in the beginning of state 'I<sub>y</sub>'

| $\alpha_{\text{max}}$ | The biggest firing angle of the SCRs without commutation failure in        |

|-----------------------|----------------------------------------------------------------------------|

|                       | phase control applications                                                 |

| $\angle \vec{V}$      | The capacitor voltage rotating frame angle                                 |

| $ec{\mathcal{I}}$     | The required HCSC rotating current SVM angle                               |

| $\delta_{a(n)}$       | An array of angles with n length, one of those is required between current |

|                       | and voltages vectors in SS-SVM                                             |

| $\delta_{b}$          | The angle between Va and Ia before adjusted to satisfy SS-SVM concept.     |

| $\delta_a$            | The angle between Va and Ia after adjusted to satisfy SS-SVM concept.      |

| α                     | The angle between grid capacitor voltage and grid voltage vectors.         |

## **PUBLICATIONS**

## **Journals**

- [1] L.A.C. Lopes and M.F. Naguib, "Space vector modulated hybrid bi-directional current source converter", accepted, in October 2009, to be published in *IEEE Transaction on Power Electronics*.

- [2] M.F. Naguib and L.A.C. Lopes, "Harmonics reduction in current source converters using Fuzzy logic", *IEEE Transaction on Power Electronics*, vol. 25, issue. 1, January 2010, pp. 158 167

- [3] L.A.C. Lopes and M.F. Naguib, "Space vector modulation for low switching frequency current source converters with reduced low order non-characteristic harmonics", *IEEE Transaction on Power Electronics*, vol. 24, issue. 4, pp.903 910, April. 2009.

- [4] M.F. Naguib and L.A.C. Lopes, "Minimize low order harmonics in low switching frequency space vector modulated current source converters with minimum harmonic tracking technique", *IEEE Transaction on Power Electronics*, vol. 24, issue. 4, pp.881 893, April. 2009.

## **Conferences**

- [5] M.F. Naguib and L.A.C. Lopes, "The effect of states ON time calculations and states sequence in low order harmonics of space vector modulated current source converter", in proc. IEEE, EPEC'09, 22 23 October 2009.

- [6] M.F. Naguib and L.A.C. Lopes "Soft switching of a hybrid current source converter ", in proc. IEEE, PESC'08, 15 19 June 2008, pp. 4177 4183.

- [7] M.F. Naguib and L.A.C. Lopes, "Harmonics reduction in low switching frequency space vector modulated current source rectifier ", in proc. IEEE, PESC'08, 15 19 June 2008, pp. 1443 1440.

- [8] M.F. Naguib and L.A.C. Lopes, "A Hybrid bi-directional current source converter with two force commutated switches and controlled with space vector modulation"; in proc. IEEE, CCECE'08, 4 7 May 2008, pp. 173 178.

- [9] M.F. Naguib and L.A.C. Lopes, "Analysis of a hybrid current source converter with bi-directional power flow capability," in proc. IEEE, EPC'07, 25 26 October 2007. pp. 128 133.

#### PART-1.

## REDUCING LOW ORDER HARMONICS IN CURRENT SOURCE CONVERTERS

## **CHAPTER 1**

## 1. SPACE VECTOR MODULATION FOR CURRENT SOURCE CONVERTER

#### 1.1. Introduction

Controllable Power Electronics switching devices are roughly divided into two types, SCRs and force-commutated switches. SCRs are usually employed in high power applications, above the power ratings of force-commutated switches. An SCR turns on when forward biased with short gating pulses and turns off when its current becomes zero. It cannot be turned off via a gate signal, which limits its operation in PWM techniques. Low and medium power applications can be achieved using MOSFETs and IGBTs, respectively, where around 5 kHz switching frequency is used. For high power levels applications GTOs or IGCTs are used with switching frequency around 2 k Hz, giving long switching times and high power losses [1].

Ac - dc power converter topologies are usually classified into two categories. The first category is Voltage Source Converters (VSC), which is more common and widely used [1] - [5]. Traditional three phase VSC is shown in Fig. 1- 1 when connected as rectifier. In VSC the load is usually connected in parallel with a dc-side capacitor. VSC is used as a rectifier and (or) an inverter in motor drives, reactive power compensation and energy storage systems. VSC with PWM was for long time the traditional way to transfer power between ac-side and dc-side using six forced commutation switches and low harmonic distortion [1] - [5]. VSC based on IGBTs, GTOs or MOSFETs has shown intrinsic weakness for high power applications due to substantial switching losses and high dv/dt of the PWM operation, leading to hazardous over voltages [2]. Many researchers have focused on VSC design, applications, modulation techniques, harmonic spectrum and control [2] - [5].

Fig. 1-1:-6-switches IGBT based Voltage Source Converter (VSC).

The second category is current source converters (CSC) [6]. CSC topologies are found in many applications. Such as, superconducting magnet energy storage systems (SMES) [7], reactive power compensation STATCOM [8] - [10], high voltage dc transmissions HVDC [11]. And, in a number of industrial processes like high-power adjustable-speed drives, where four-quadrant operation, near sinusoidal motor terminal voltages, supply voltage variations immunity and inherent short-circuit protection are required [6], [12] - [15].

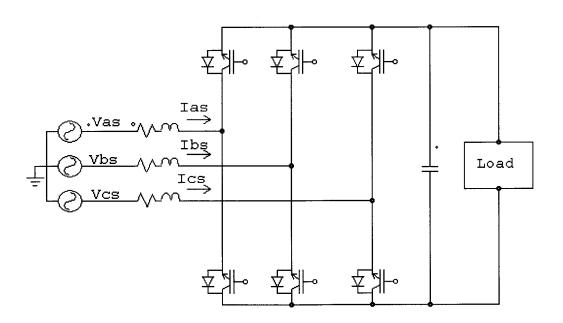

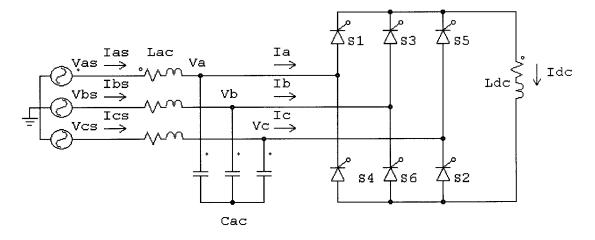

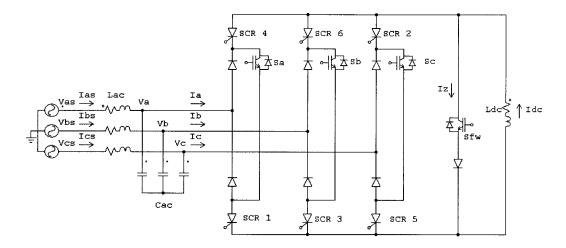

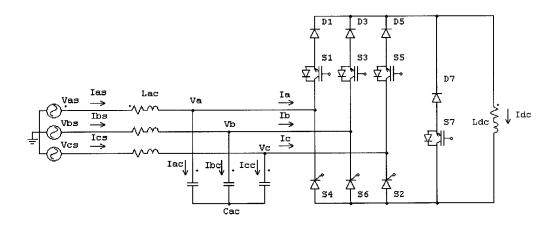

Traditional GTOs based CSC is shown in Fig. 1- 2 when connected as rectifier. Less research deals with CSC in general [1]. The power circuit of the CSC is simpler and more robust than the VSC due to no freewheeling diodes with unidirectional current flow [6]. In principle, CSC presents a higher reliability than VSC due to the inherent over current protection and the fact that large dc-side capacitors present shorter life spans than large inductors [2]. Non-characteristic harmonics in LSF-CSC are higher than in LSF-VSC [16], [17]. And, both CSC and VSC can be used in both rectifier and inverter modes of operation [1], [3], [5], [6].

Fig. 1-2:-6-switches GTOs-based current source converter (CSC).

## 1.2. CSC MODULATION TECHNIQUES

#### 1.2.1. COMMON MODULATION TECHNIQUES FOR CSCS

A number of PWM techniques have been used for generating the gating signals of CSCs [6]. The popular Sinusoidal Pulse width modulation (SPWM) technique results in frequent switching and power losses when applied to CSC, not suitable for high power applications [18], [19].

In high power applications, selective harmonic elimination (SHE) has been used as an off-line technique to eliminate certain harmonics in the ac-side current [20] - [23]. SHE concept can be extended to multilevel CSC [24], [25]. Certain procedures should be used for the ac-side filter design in this case [26]. SHE has been used for CSC with around 500 Hz switching frequency, where a limited number for the SHE chopping angles are calculated off-line [21]. For 1 kHz - 3 kHz, SHE chopping angles are increased which complicating the calculation of those angles.

Space Vector Modulation (SVM) offers an elegant way of generating the gating signals of CSCs on line with reduced switching frequency and increased gain [27] - [33]. Besides, specific gating requirements of CSCs can be readily incorporated in the pattern generation schemes, thus SVM is more suitable for CSC [6]. A comparative study between SPWM and SVM modulation techniques for CSC was presented in [27].

#### 1.2.2. Fundamentals of SVM- CSCs

Fig. 1- 2 shows 6-switches (S1- S6) GTO-based CSC. For ideal CSC two GTOs should be ON at any instant, one and only one GTO from upper switches group S1, S3 and S5, and one and only one GTO from lower switches group S2, S4 and S6. That

permits a predefined current path for the dc-side current. In real CSC a commutation (overlap) period is essential to ensure that there is no danger of having no path for the dc link current, to avoid overvoltage [6]. In CSCs both of L<sub>ac</sub> and C<sub>ac</sub> define the cut-off frequency of the 2<sup>nd</sup> order ac-side filter, which is usually designed for attenuating the characteristic switching current harmonics that appear in the ac-side current. A brief description in CSC ac-side filter effect on harmonic spectrum was presented in [33].

The reference current vector of a three-phase CSC is given by (1-1).

$$I_{n} = \frac{2}{3} (i_{a} + i_{b} e^{2\pi/3} + i_{c} e^{-2\pi/3}) = I_{\alpha} + jI_{\beta} = |I_{n}| \angle \phi_{I}$$

(1-1)

Where  $i_a$ ,  $i_b$ ,  $i_c$  are the instantaneous CSC ac-side currents.

A number of SVM techniques have been proposed to minimize the magnitude of the harmonic distortion caused by 5<sup>th</sup> and 7<sup>th</sup> non-characteristics harmonics components (HD<sub>5-7</sub>) in CSCs operating with LSF [6], [27] - [33]. Those SVM techniques include three main procedures. First, they use the nearest active states in a given sector to synthesize the reference space vector (SV). Second, they select the SVM cycle frequency (f<sub>cycle</sub>) to be a multiple of six of the grid frequency (f<sub>ac</sub>) for synchronized SVM, meaning that each SVM sector is started with one of the SVM cycles. Finally, they choose a certain sequence of states in SVM cycles.

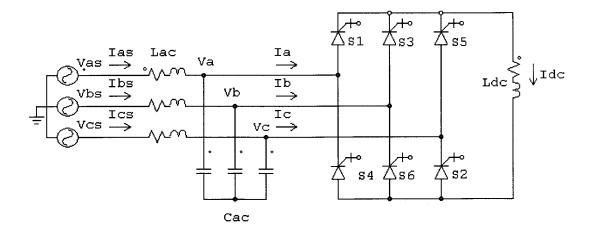

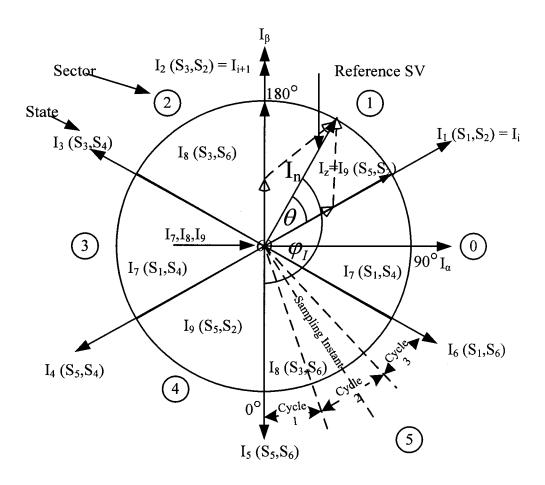

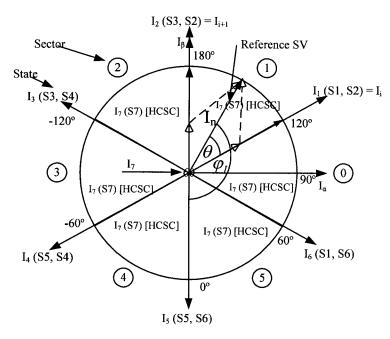

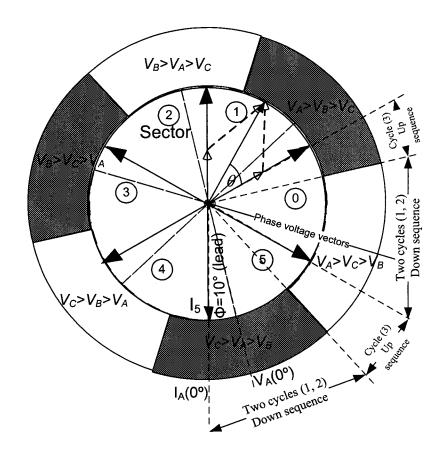

Fig. 1- 3 shows the six sectors complex plane for 6-switches CSC with the reference current vector  $(I_n)$ , six active states  $(I_1-I_6)$  and three zero states across three CSC legs  $(I_7-I_9)$ . Also it presents CSC switches that are ON in each state. Table 1- 1 presents the switches that are ON in each of the nine states and the direction of the ac currents in each phase.

Fig. 1- 3:- Definition of the sectors (0 - 5), states ( $I_1$ -  $I_9$ ), and the switches which are ON in each state when  $N_{CS} = 6$  in 6-switches SVM-CSC.

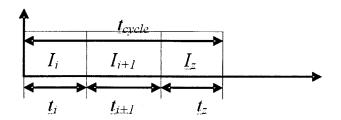

The CSC modulated by SVM operates with two active states vectors ( $I_i$  and  $I_{i+1}$ ) and one zero state vector ( $I_z$ ). The angle of the reference vector  $\phi_I$  defines the sector of operation in the complex plane. The reference current vector is synthesized by using a sequence of two active and one zero states with

$$I_n t_{cycle} = I_i t_i + I_{i+1} t_{i+1} + I_z t_z$$

(1-2)

Where,  $t_{cycle}$  is the SVM cycle period of a given sequence of states.  $t_{cycle}$  is the inverse of  $f_{cycle}$  which depends on the frequency of the fundamental current component at the ac-side ( $f_{ac}$ ) and on the number of SVM cycles per sector ( $N_{CS}$ ) as given by (1-3).

$$f_{cycle} = 6 N_{cs} f_{ac}$$

(1-3)

In synchronized SVM each SVM sector should starts with a new SVM cycle and  $N_{CS}$  should be an integer [6]. In Fig. 1- 3,  $N_{CS}$  = 6 was selected, each SVM sector is divided into six SVM cycle. That is applied to SVM sector five in Fig. 1- 3, which give  $f_{cycle}$ =2160 Hz, using (1- 3). In this case, the dominant harmonics appears at  $(6\times N_{CS}\pm 1)$  pu and GTOs switching frequency is  $0.5\times f_{cycle}$ =1080 Hz which is suitable for GTOs and the main advantage of using SVM over SPWM technique.

TABLE 1-1:- STATES REALIZATIONS AND SWITCHES SWITCHING FUNCTIONS IN CSC

| State | Lower Switch | Upper Switch | $(I_a/i_{dc})$ | $(I_b/i_{dc})$ | $(I_c/i_{dc})$ |

|-------|--------------|--------------|----------------|----------------|----------------|

| 1     | S2           | S1           | 1              | 0              | -1             |

| 2     | S2           | S3           | 0              | 1              | -1             |

| 3     | S4           | S3           | -1             | 1              | 0              |

| 4     | S4           | S5           | -1             | 0              | 1              |

| 5     | S6           | S5           | 0              | -1             | 1              |

| 6     | S6           | S1           | 1              | -1             | 0              |

| 7     | S4           | S1           | 0              | 0              | 0              |

| 8     | S6           | S3           | 0              | 0              | 0              |

| 9     | S2           | S5           | 0              | 0              | 0              |

#### 1.2.3. IMPLEMENTATION OF SVM FOR 6-SWITCHES CSC

SVM had many implementation approaches. SVM for CSC concepts was presented in [6], [27] - [33]. SVM was achieved using different software [34], [35]. There

the procedures to divide the ac-side cycle into SVM sectors, divide SVM sectors to SVM cycles and calculates states ON times implementing SVM cycle were not described. In this thesis SVM for CSC is implemented using MATLAB-SIMULINK and PSIM. SIMULINK is used more often in this thesis while PSIM is used to introduce certain ideas. During research, the results from PSIM and SIMULINK were compared to check results. Thus, SIMULINK blocks used in this thesis to implement the gating signals for SVM-CSC are presented step by step.

The feedback command in closed loop or the desired operating condition in open loop applications of CSCs defines two variables. The first is the modulation index value  $(m_a)$  and the second is the modulation index angle  $(\varphi_I)$ . They are used to implement CSC switches gating pattern. Possible forms for the input variables ( $m_a$  and  $\varphi_I$ ) are in (1-1). If the grid cycle frequency is 60 Hz ( $f_{ac}$  = 60 Hz), the ac-side cycle time period is  $t_{ac}$  = 1/60 = 16.67ms, the current SV covers 360° electrical in 16.67ms. There is 6-switches in the CSC topology and 6 active switching schemes in SVM-CSC, so the ac-side current line cycle is divided into six SVM sectors. Each SV sector time is  $t_{\text{sector}}=16.67/6=2.78\text{ms}$ . That leads each SVM sector to cover 60° electrical. Fig. 1- 3 illustrates one ac-side current line cycle (360°) which is divided into six SVM sectors (60°). Surrounding the period where phase A current is maximum positive (90° in ac sinusoidal waveform signal) the upper switch for phase A (S1) of CSC is used. In the first SVM sector (sector 0) S1 is common in  $60^{\circ} \le \varphi_1 \le 120^{\circ}$ . Surrounding the period where the phase A current is maximum negative (270° in ac sinusoidal waveform signal) the lower switch for phase A (S4) of CSC is used. In the fourth SVM sector (sector 3) S4 is common in 240° ≤  $\phi_I \leq 300^{\circ}$ . The same can be said for phases B and C.

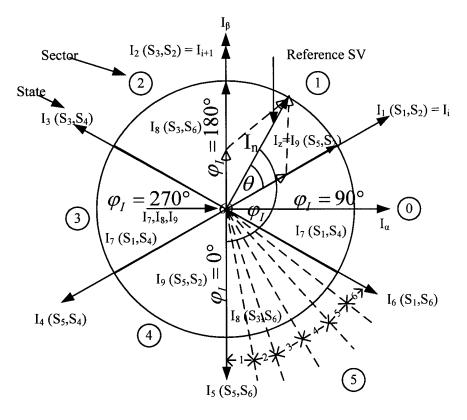

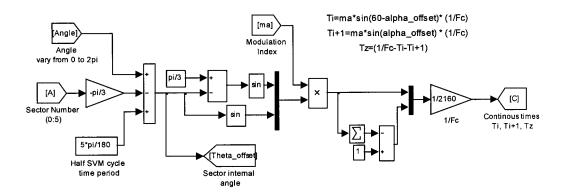

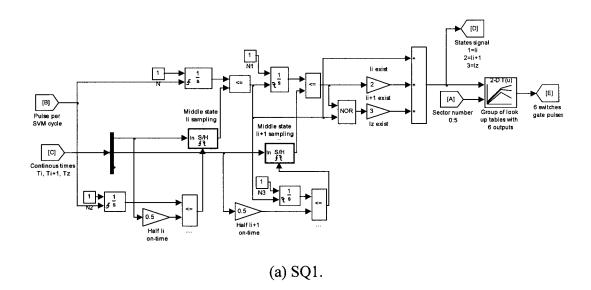

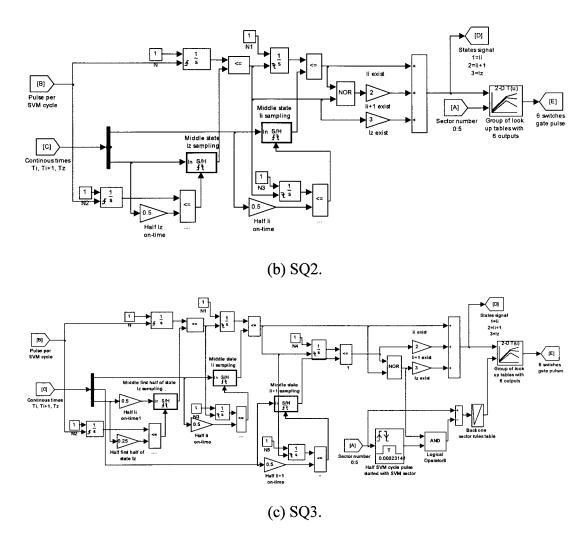

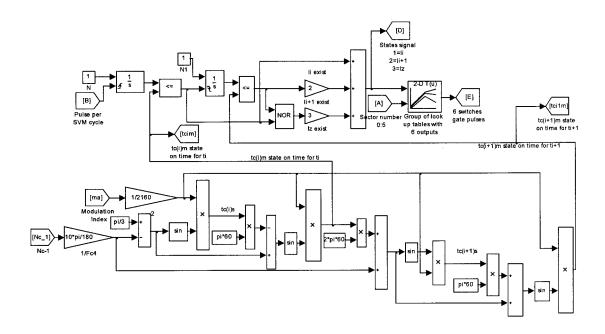

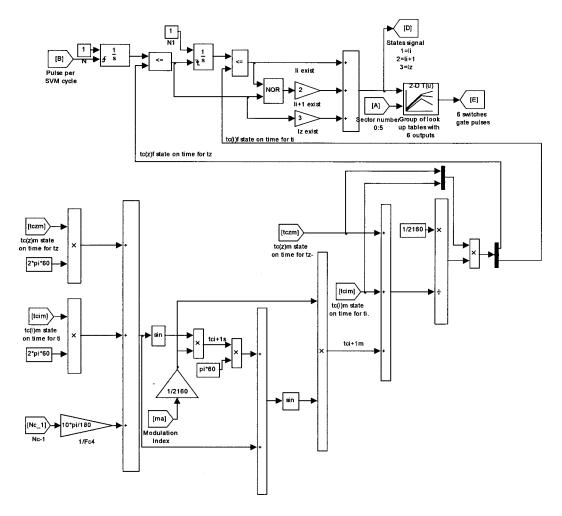

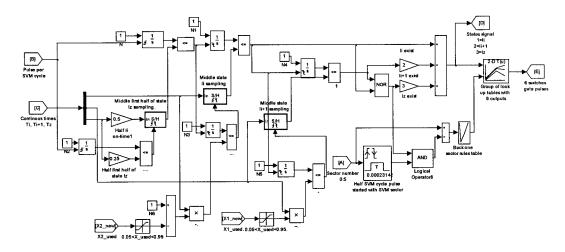

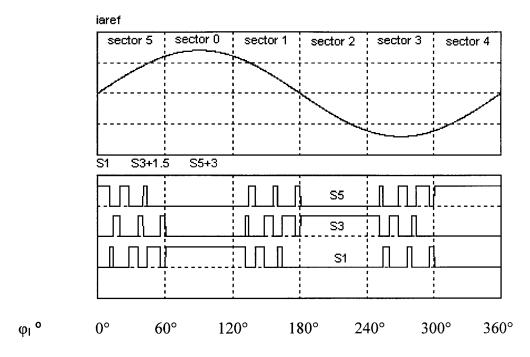

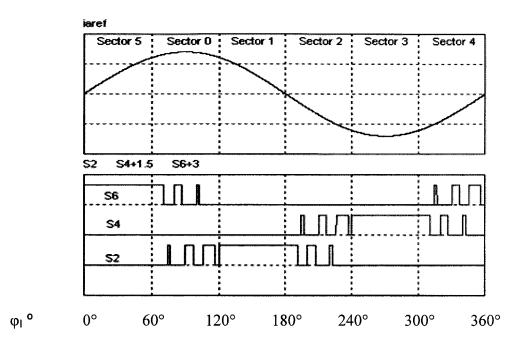

Table 1- 2 and Fig. 1- 3 illustrate the divisions of the SVM sectors. Each SVM sector is divided into  $N_{CS} = 6$  cycle. Fig. 1- 4 illustrates how the ac-side line cycle is divided into six SVM sectors, and how a pulse in the beginning of each SVM cycle using SIMULINK Blocks is generated. There the input  $\phi_I$  {[Angle]} is the angle of the required fundamental currents in the converter ac-side. The first output {[A]} represents the number of SVM sector at certain instant varying from zero to six. And, the second output {[B]} is generating a pulse in the beginning of each SVM cycle.

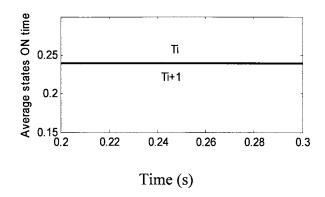

Fig. 1-4:-SIMULINK blocks generating SVM sector number and a pulse per SVM cycle

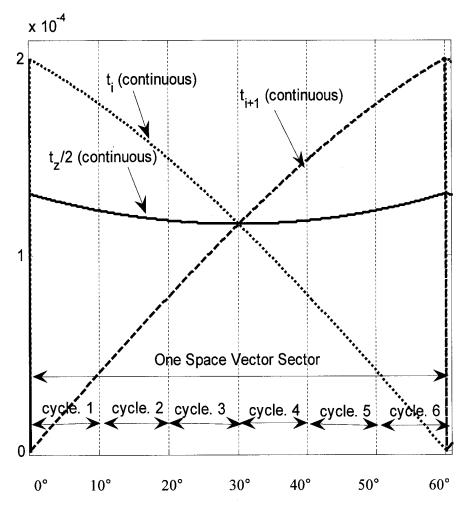

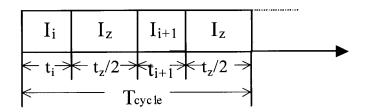

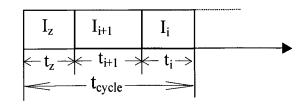

The continuous states ON times for three states  $(t_i, t_{i+1} \text{ and } t_z)$  are calculated according to equations (1-4), (1-5) and (1-6), respectively as a function  $m_a = \|I_n\|$ , such that  $(0 \le m_a \le 1)$ , and  $\theta$  is the angle of  $I_n$  in a given sector  $(0^\circ \le \theta \le 60^\circ)$ . Fig. 1-5 illustrates the three continuous states ON times for one SVM sector when  $m_a = 0.5$ . There the SVM sector divided into six SVM cycles when  $N_{CS} = 6$ .

$$t_{i} = t_{cycle} m_{a} \sin\left(\frac{\pi}{3} - \theta\right) \tag{1-4}$$

$$t_{i+1} = t_{cvcle} m_a \sin(\theta)$$

(1-5)

$$t_z = t_{cycle} - t_i - t_{i+1}$$

(1-6)

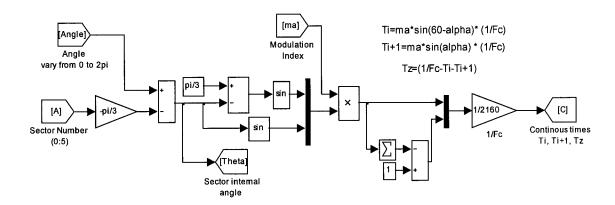

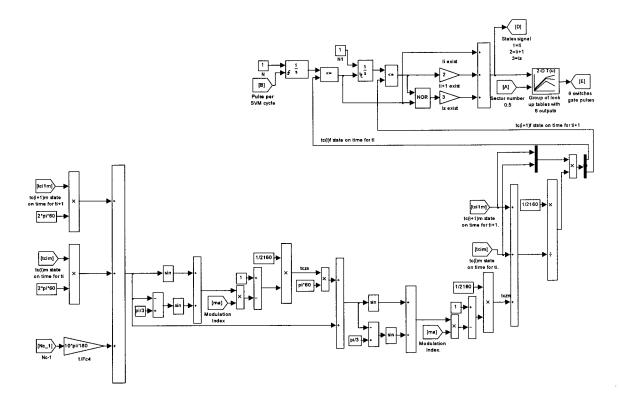

Fig. 1- 6 represents the SIMULINK blocks used to find the continous states ON times. There  $\phi_I$  {[Angle]} and sector number {[A]} are used to decide  $\theta$  {[Theta]}, which can be used along with  $m_a$  {[ma]}to decide continous states ON times {[C]} for  $t_i$ ,  $t_{i+1}$  and  $t_z$  using equations (1-4), (1-5) and (1-6), respectively.

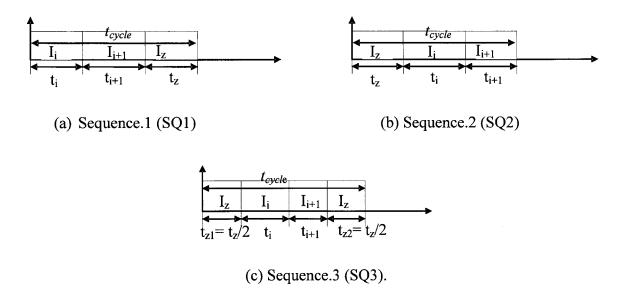

Both active states should be placed one after the other to minimize HD<sub>5-7</sub> during sector transitions in SVM-CSC, which generates three sequences of states shown in Fig. 1-7. States sequences for SVM-CSC were investigated in [33]. In Fig. 1-7, sequences with good harmonics spectrums are shown.

TABLE 1-2:- SECTORS DIVISION IN SVM-CSC

| Sector | Common<br>Switch | Non-common Switches | Start angle | Middle<br>angle | End angle |

|--------|------------------|---------------------|-------------|-----------------|-----------|

| 0      | S1               | S6 - S2             | 60          | 90              | 120       |

| 1      | S2               | S1 - S3             | 120         | 150             | 180       |

| 2      | S3               | S2- S4              | 180         | 210             | 240       |

| 3      | S4               | S3 - S5             | 240         | 270             | 300       |

| 4      | S5               | S4 - S6             | 300         | 330             | 360/0     |

| 5      | S6               | S5 - S1             | 0           | 30              | 60        |

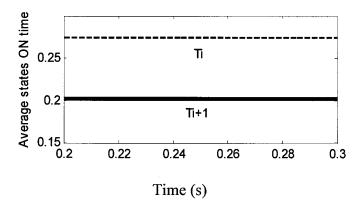

Fig. 1- 5 :-Three continuous states ON times,  $t_i$ ,  $t_{i+1}$  and  $t_z/2$  for one SVM sector when  $m_a = 0.5 \text{ and } N_{CS} = 6.$

Fig. 1-6:-SIMULINK blocks designed to compute continuous states ON times.

Fig. 1-7:-Sequences with the best harmonics spectrum from literature review.

#### 1.2.4. CALCULATIONS OF TRADITIONAL SVM-CSC STATES ON TIME

As an example of SVM-CSC operation from Fig. 1- 3 and Fig. 1- 7, if SQ1 is used for sector one, in the beginning of each SVM cycle  $I_i$  comes first and implemented with  $I_1$  (S1 and S2), the dc-side current flows from phase A to phase C. That is followed  $I_{i+1}$  which is implemented with  $I_2$  (S3 and S2), the dc-side current flows from phase A to phase B. The last state is  $I_z$ , there freewheeling the dc-side current take place, in sector one freewheeling should be across S2, which is common in both active states in sector one using  $I_9$  (S2 and S5), that reduce the switching losses. While if SQ3 is used, each cycle is started by the first half of state  $I_z$  ON time ( $I_z = I_z = I_z$

SVM with high switching frequency results in low LOH distortion in the CSC acside current [35]. However, in high power levels where the switches can only operate at

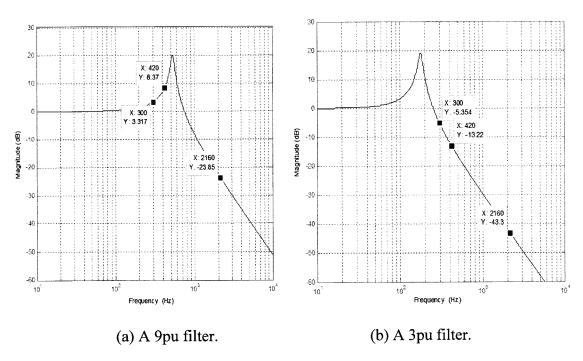

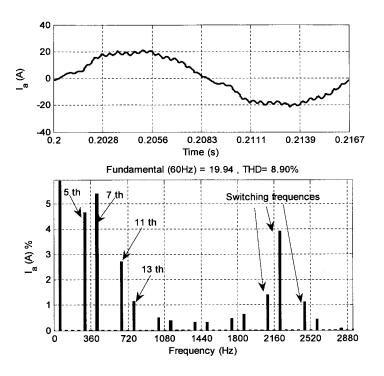

low switching frequencies (LSF) the magnitude of the non-characteristic  $5^{th}$  and  $7^{th}$  harmonics (HD<sub>5-7</sub>) presents a serious burden on the design of the low pass input filter of CSCs which typically presents low damping [6]. To reduce LOH in LSF-SVM-CSC an active damping method was proposed to reduce the ac-side line current Total Harmonics Distortion (THD) in [36], [37]. There the reduction of LOH was done with resonance while the source of those harmonics in the SVM-CSC was not introduced. Also, suppression of resonance oscillation resulting from LOH was presented in [37] - [39]. These LOH components propagate through the current control loop and distorting the acside current in SVM-CSC. In practice, SVM-CSCs have been implemented with  $f_{cycle} > 5$  k Hz and a bulky  $2^{nd}$  order ac-side filter with 3pu cut off-frequency [40] - [43].

The use of hybrid states sequence scheme where a different sequences are used according to position and value of the reference vector in SVM scheme have been reported with minor reductions in the LOH distortion for VSCs in [44]. The problem of LOH in high power LSF-SVM-CSCs can be mitigated with multi-level topologies by phase shifting the gating signals of CSC levels in an appropriate way [7], [45]. Also, LOH was reduced using Multimodal CSC with modified SVM approach in [11]. To reduce the HD<sub>5-7</sub> injected into grid in the PCC large resistors are used in series with acside filter capacitors and/or inductors in [37], [46].

The harmonic distortion at the input line current for grid-connected CSC is strictly regulated by guidelines such as the IEEE Standard 519, where smaller than 5% total harmonics distortion (THD) is recommended [47]. Traditional SVM-CSC can barely reach this value with certain types of ac-side filters [33]. Besides, resonance in the CSC ac-side usually amplifies LOH, which was damped in [36] - [39]. The geometric-wall-

model on CSC using duality considerations to VSC to determine the spectra of the pulsed output currents occurring in a CSC was presented in [48].

Another venue for investigation, which was not investigated in previous research, is the way ON times of states are calculated in LSF-SVM-CSC, which is the main focus here. In the conventional SVM techniques, the states ON times are calculated at the same time in the beginning of the SVM cycle and held to be used later in that SVM cycle according to the states sequence [33]. This way is defined as Start Sampling (SAs) in this thesis. This results in an unbalanced use of the states. That is for even  $N_{CS}$ ,

$$t_i(N_c) \neq t_i(N_{cs} - N_c + 1)$$

(1-7)

Where  $N_C$  is the cycle number ( $N_C = 1, 2 ... N_{CS}$ ).

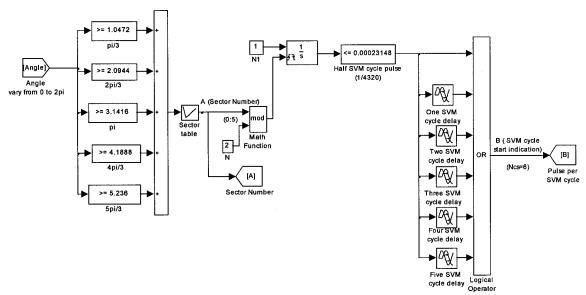

Fig. 1- 8 is presenting the SIMULINK blocks used to convert continuous states ON times  $\{[C]\}$  to a sequence of states  $\{[D]\}$  when SQ1 and SAs are used. There, sampling is done in the begging of the SVM cycle, that is why it called SQ1-SAs. When states sequence or states ON times calculation technique is changed to be different than SQ1-SAs, then Fig. 1- 8 is changed. The output  $\{[D]\}$  should be one when  $I_i$  is selected, two when  $I_{i+1}$  is selected and three when  $I_z$  is selected. Both of SVM sector number  $\{[A]\}$  and states signal  $\{[D]\}$  are used as an input of a group of look up tables designed to decide the selected switches in 6-switches SVM-CSC according to Table 1- 3.

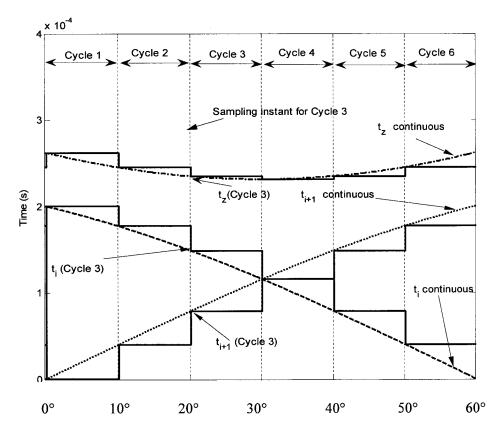

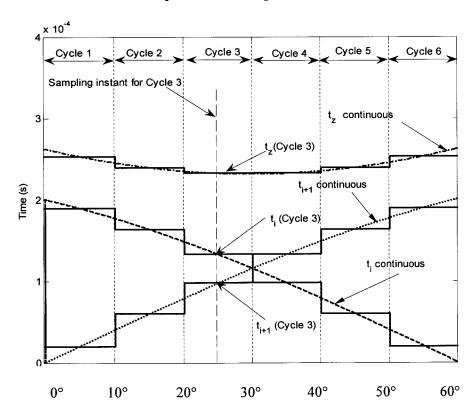

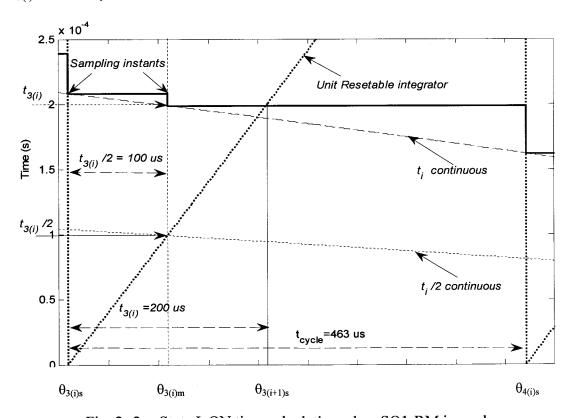

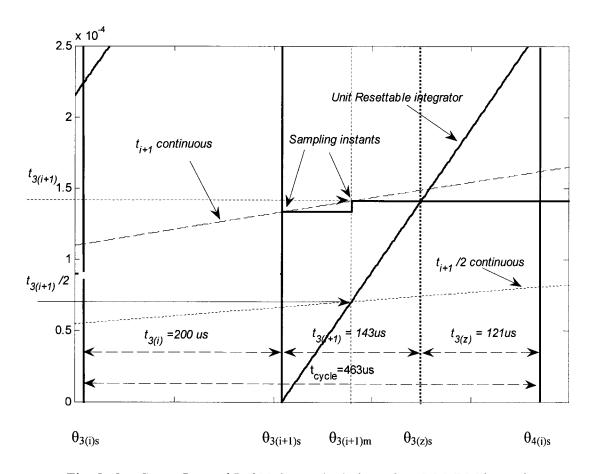

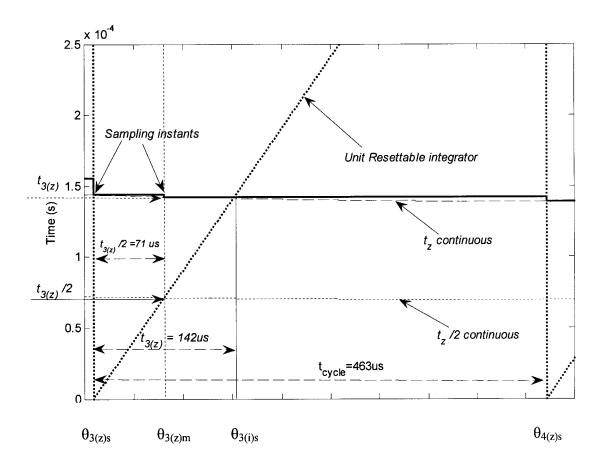

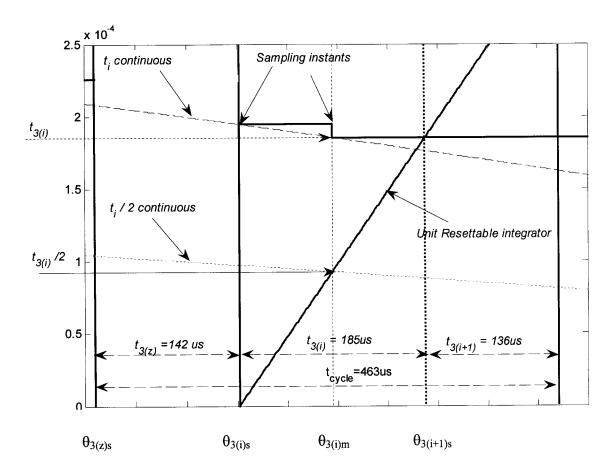

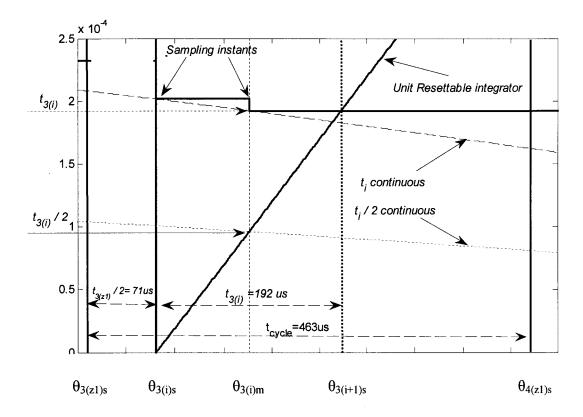

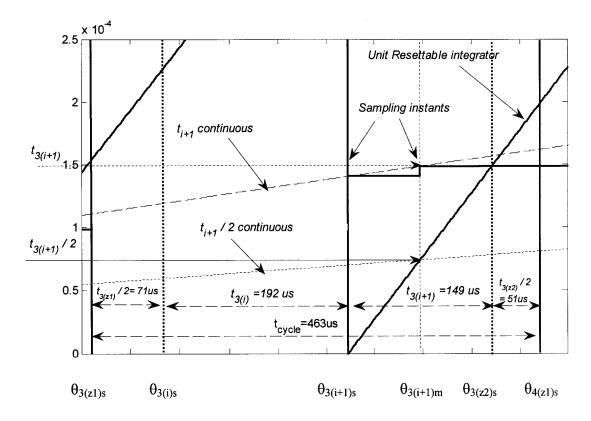

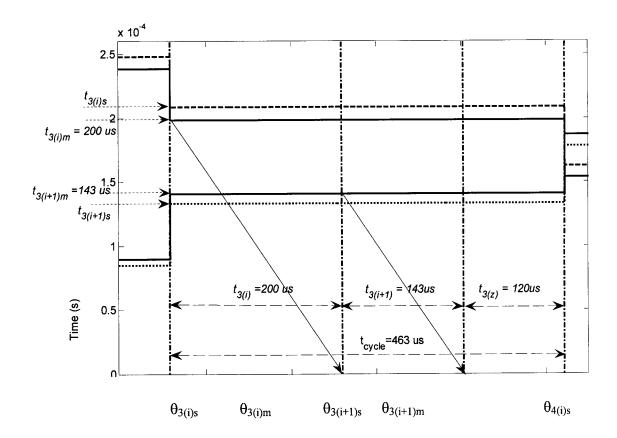

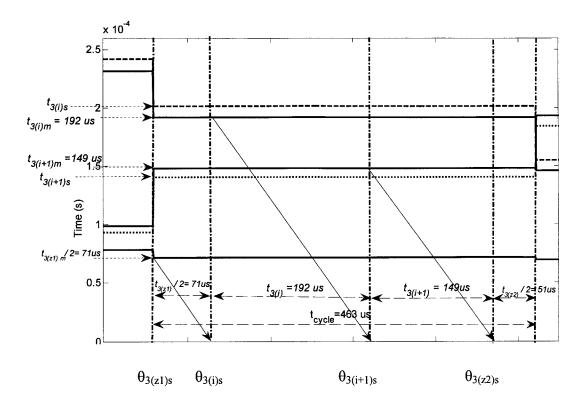

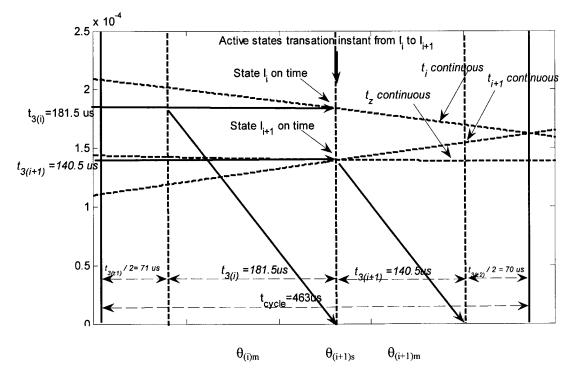

In the horizontal axis of Fig. 1- 9, SVM sector angles  $(0^{\circ} \le \theta \le 60^{\circ})$  are shown. There are six SVM sectors per ac-side line cycle  $(360^{\circ})$ . Since  $\theta = \omega t$ , the horizontal axes in Fig. 1- 9 represents angle  $(\theta)$  as well as time (t), the SVM sector time is divided into six SVM cycles. The vertical axis is the time in seconds used for calculating the states ON times inside SVM cycles. Fig. 1- 9 shows the continuous times for three states  $t_i$ ,  $t_{i+1}$

and  $t_z$  calculated from (1-4), (1-5) and (1-6), respectively as dotted curves. It also shows  $t_i$ ,  $t_{i+1}$  and  $t_z$  calculated using Start Sampling (SAs) technique as solid curves, those values which changes in the beginning of each SVM cycle are used by SAs to represent states ON times inside SVM cycles independent on SVM sequence of states.

Fig. 1-8: SIMULINK blocks convert generates states signal with SQ1-SAs.

Fig. 1- 9 :-States ON times calculation procedure for  $t_i$ ,  $t_{i+1}$  and  $t_z$  in each SVM cycle in one SVM sector when SAs is used.

TABLE 1-3:- ON SWITCHES IN EACH STATE IN SVM-CSC.

| Sector Number | State Signal   | Upper Switch | Lower Switch |

|---------------|----------------|--------------|--------------|

| 0             | $I_i$          | S1           | S6           |

|               | $I_{i+1}$      | S1           | S2           |

|               | $I_z$          | S1           | S4           |

| 1             | I <sub>i</sub> | S1           | S2           |

|               | $I_{i+1}$      | S3           | S2           |

|               | Iz             | S5           | S2           |

| 2             | $I_i$          | S3           | S2           |

|               | $I_{i+1}$      | S3           | S4           |

|               | $I_z$          | S3           | S6           |

| 3             | I <sub>i</sub> | S3           | S4           |

|               | $I_{i+1}$      | S5           | S4           |

|               | $I_z$          | S1           | S4           |

| 4             | $I_i$          | S5           | S4           |

|               | $I_{i+1}$      | S5           | S6           |

|               | $I_z$          | S5           | S2           |

| 5             | I <sub>i</sub> | S5           | S6           |

|               | $I_{i+1}$      | S1           | S6           |

|               | Iz             | S3           | S6           |

SAs presented in Fig. 1- 9 do not give an ideal SVM in LSF applications. The difference between the dotted curves and SAs solid curves for states is zero in the beginning of SVM cycles and maximum at their ends. With long SVM cycle in LSFs applications, the difference between dotted and solid curves is large. That gives inaccurate calculations for states appearing near the end of SVM cycles. However, with LSF the synthesis of the SVM is concluded several degrees after calculated, leading to an

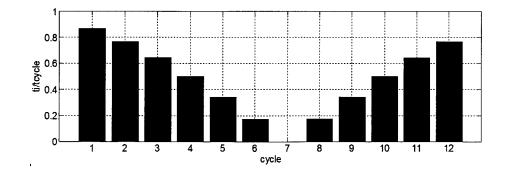

unbalance in the use of the active states in all sectors, i.e. the first active state  $I_i$  will be used more than the second active state  $I_{i+1}$ . Average times of  $t_i$ 's  $> t_{i+1}$ 's when SAs is used, that is seen in Fig. 1- 10. The state representing  $I_{i+1}$  in the recent sector will represent  $I_i$  in the next sector, which is shown in Fig. 1- 3. Fig. 1- 11 shows the ON times for one (the common) active state in two sectors follows each other when SAs is used, each of the 12 cycles of the 2 sectors (120°). There the use of a state is unbalanced for SAs, the ON time is the largest for the cycle 1 and zero for cycle 7, there is no symmetry. Since there are six sectors in the complex plane,  $HD_{5-7}$  should appear in the ac-side current. In SAs technique, independent on  $m_a$  and states sequence, the average error in the SVM sector is positive for  $t_i$  and is negative for  $t_{i+1}$  during an entire SVM sector.

Fig. 1- 10: Percentage average active states ON times for SVM sector with SAs m<sub>a</sub>=0.5.

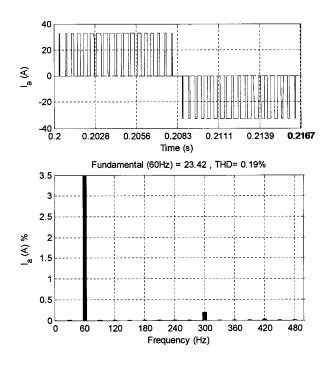

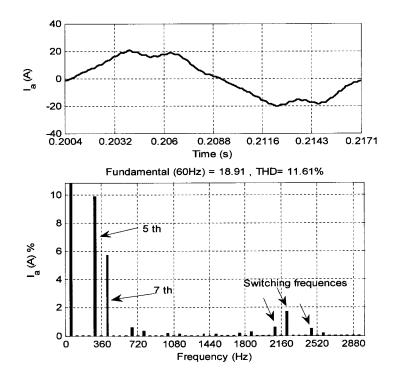

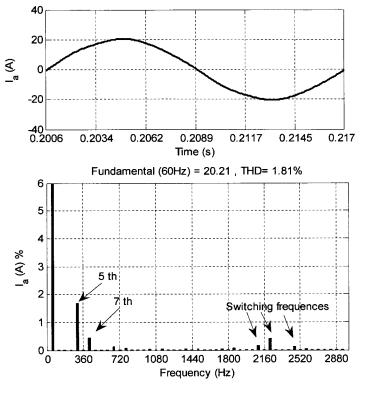

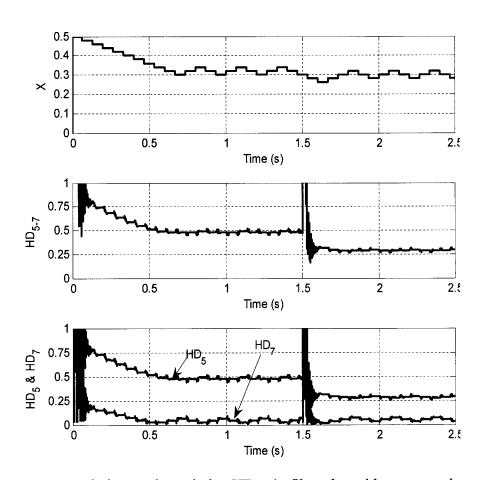

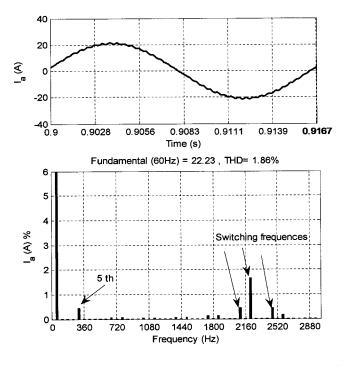

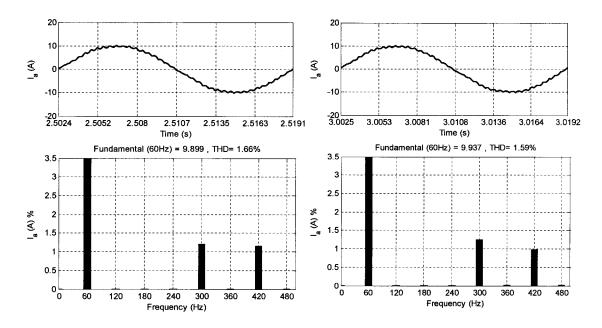

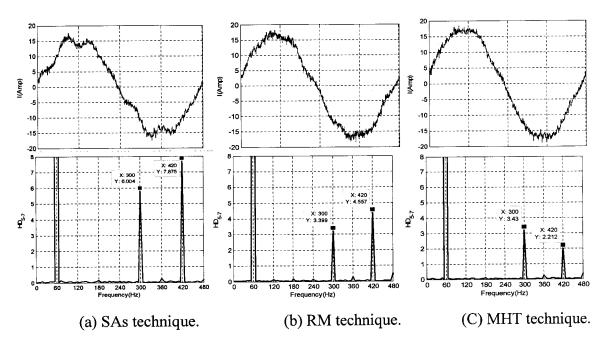

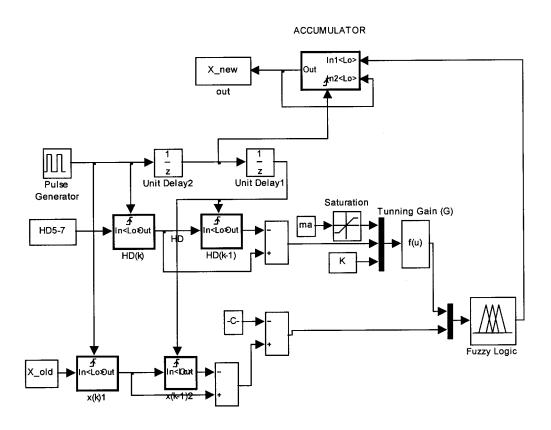

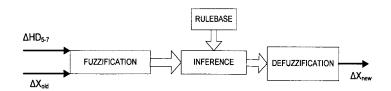

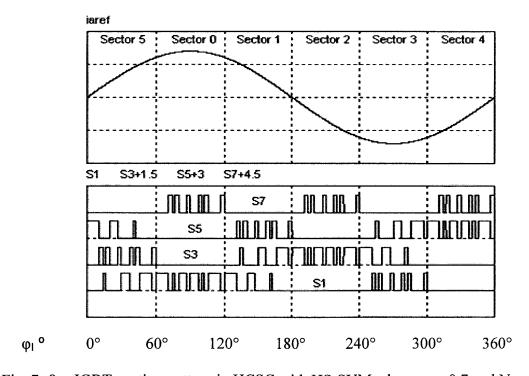

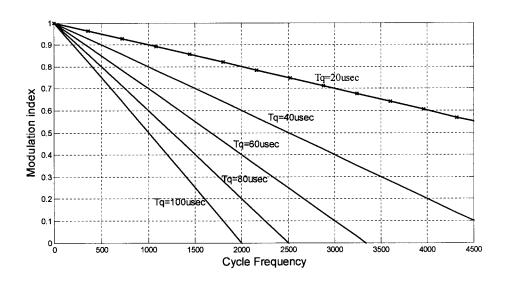

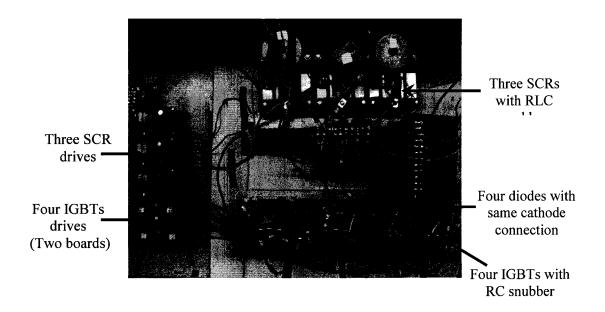

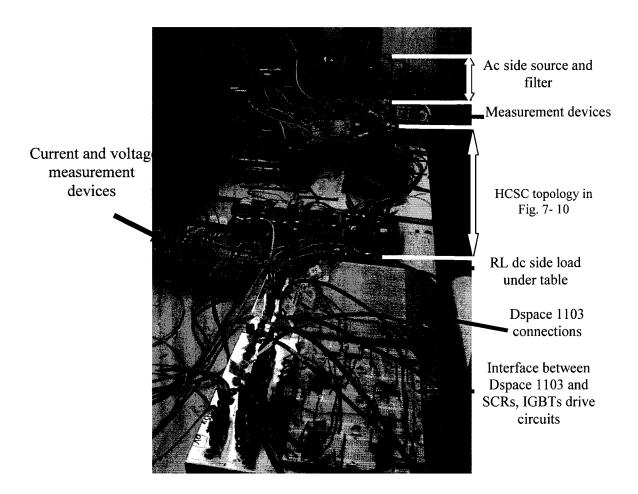

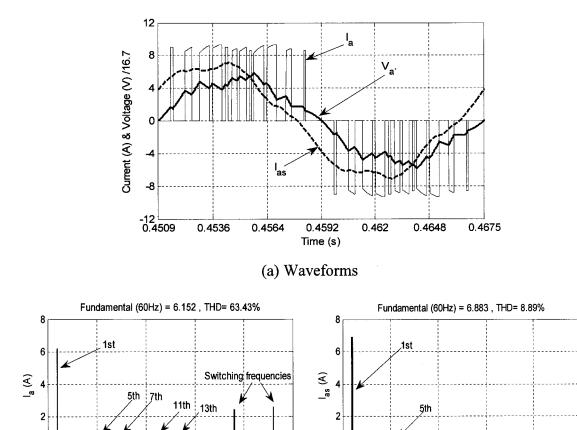

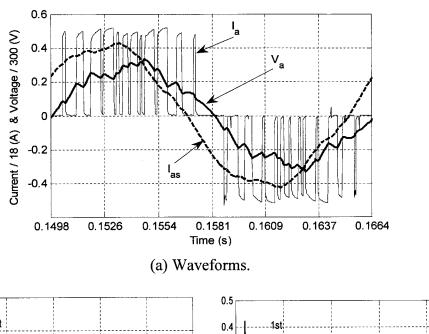

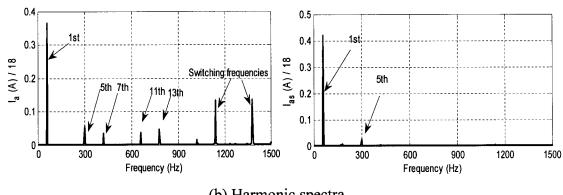

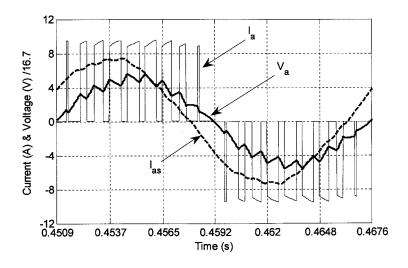

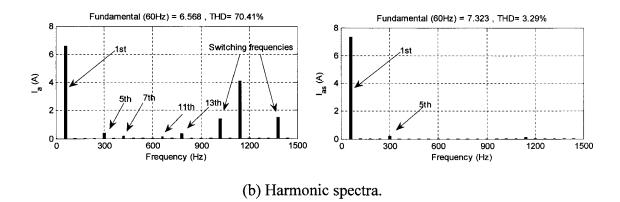

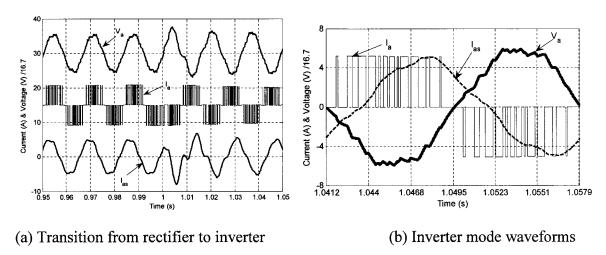

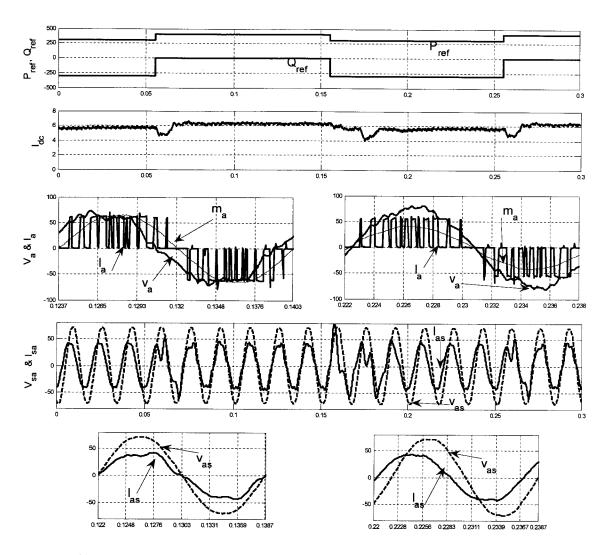

Fig. 1-11:- ON times of an active state with SAs when  $N_{CS} = 6$  and  $m_a = 1$ .