# Hybrid Prototyping of Multicore Embedded Systems

EHSAN SABOORI

A THESIS IN THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY CONCORDIA UNIVERSITY MONTREAL, QUEBEC, CANADA

> JULY 2016 © Ehsan Saboori, 2016

### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

By:Mr. Ehsan SabooriEntitled:Hybrid Prototyping of Multicore Embedded Systems

and submitted in partial fulfilment of the requirements for the degree of

#### Doctor of Philosophy (Electrical and Computer Engineering)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|            |                                      | _ Chair             |

|------------|--------------------------------------|---------------------|

|            | Dr. Wahid S. Ghaly                   |                     |

|            |                                      | External Examiner   |

|            | Dr. Amirali Baniasadi                |                     |

|            |                                      | External to Program |

|            | Dr. Lingyu Wang                      |                     |

|            |                                      | Examiner            |

|            | Dr. Otmane Ait Mohamed               |                     |

|            |                                      | Examiner            |

|            | Dr. Yan Liu                          |                     |

|            |                                      | Supervisor          |

|            | Dr. Samar Abdi                       |                     |

|            |                                      |                     |

| Approved   | 1 by:                                |                     |

|            | Dr. Wei-Ping Zhu, Graduate Program D | irector             |

| July 22, 2 | 2016                                 |                     |

|            | Dr. Amir Asif, Dean                  |                     |

|            | Faculty of Engineering and Comp      | outer Science       |

### Abstract

#### Hybrid Prototyping of Multicore Embedded Systems

Ehsan Saboori, Ph.D. Concordia University, 2016

Multicore platforms are becoming increasingly pervasive in modern embedded systems. System level modeling techniques have enabled creation of fast software models of multicore platforms, commonly known as Virtual Prototypes, for early functional validation of embedded software, before the hardware is available. On the other hand, for accurate performance validation, the complete multicore platform can be implemented as a physical prototype on FPGA. Both virtual platforms and FPGA prototypes have their respective pros and cons. Virtual platforms have the advantage of high speed functional simulation and, typically, scale well with the number of cores. However, the accuracy of performance estimation is sacrificed. FPGA prototypes provide cycle-accurate performance estimation, because the software executes directly on an FPGA implementation of the target cores. However, it takes a significant amount of time to design, implement and test the inter-core communication architecture on the FPGA.

In this thesis we propose to design a novel system-level modeling framework, called Hybrid Prototyping. Our goal is to provide the benefits of both virtual platforms and FPGA prototypes. It aims to provide early, fast, and scalable models, similar to virtual platforms, along with the cycle-accuracy of FPGA prototypes. Using hybrid prototyping, embedded software designers will be able to create concurrent applications and accurately analyze the performance implication of their optimizations before the chip is delivered. At the same time, multicore architects will be able to modify the platform model without having to do full system prototyping. Therefore, hybrid prototyping will enable early and reliable multicore embedded system design, resulting in huge productivity gains for both embedded software designers and multicore chip architects.

### Acknowledgments

I would like to take this opportunity to thank all the people who have contributed to the fruition of this thesis. First of all, I would like to thank my advisor, Professor Samar Abdi for excellent guidance during my PhD studies. He has taught me how to think about problems, how to approach the solution and when to commit to a solution. I will forever be indebted for the time and the effort he has spent in my education. I would also like to thank many friends in ECE, including Shafigh Parsazad, Richard Lee, Partha Ravishankar, Paul Leons, Ali Barzegar, Karim Al-Khalek and Aryan Yaghoubian for their great company and all their help.

This thesis would not have been possible without the unflinching support of my wonderful wife, Golnaz. She celebrated my success and lifted my spirits whenever I faced rejection. She is by far the single most important reason why I maintained my emotional balance through the ups and downs of graduate life.

Finally, I would like to thank my parents, to whom this thesis is dedicated. My dear mother and father who have made many personal sacrifices to provide me the best possible education and a healthy atmosphere at home. It is impossible to put down in words their contribution to my personal growth. I would also like to thank my brother, sister and their families for always cheering me on.

# Contents

|          | List of Figures |                                               |      |

|----------|-----------------|-----------------------------------------------|------|

|          | List of Tables  |                                               |      |

|          | Code Listings   |                                               |      |

|          | Public          | cations and Workshops                         | xii  |

|          | Glossa          | ary                                           | xiii |

| 1        | Introd          | luction                                       | 1    |

|          | 1.1             | Motivation                                    | 1    |

|          | 1.2             | Literature Review                             | 3    |

|          |                 | 1.2.1 Virtual Prototyping                     |      |

|          |                 | 1.2.2 FPGA Prototyping                        |      |

|          | 1.3             | General Problem Statement                     | 10   |

|          | 1.4             | Thesis Contribution                           | 12   |

|          | 1.5             | Thesis Outline                                | 14   |

| <b>2</b> | Hybri           | d Prototyping Methodology                     | 15   |

|          | 2.1             | Methodology                                   | 17   |

|          | 2.2             | Modeling Framework                            |      |

|          | 2.3             | Summary                                       |      |

| 3        | Multi           | core Emulation Kernel                         | 23   |

|          | 3.4             | Hardware Timer Controller                     |      |

|          | 3.5             | Event                                         | 25   |

|          | 3.6             | Shared Resources                              |      |

|          | 3.7             | Emulated Core Scheduler                       |      |

|          | 3.8             | Summary                                       |      |

| 4        | Hardv           | ware Model Layer                              | 35   |

|          | 4.1             | Emulated Cores                                |      |

|          | 4.2             | Communication Models                          |      |

|          |                 | 4.2.1 Statically Scheduled MPSoCs             | 39   |

|          |                 | 4.2.2 SMP Architecture                        | 45   |

|          |                 | 4.2.3 Interrupt to Processor                  |      |

|          | 4.3             | Hardware Interrupt Handling                   |      |

|          | 4.4             | Multi-Clock Domains                           |      |

|          | 4.5             | Memory Hierarchy                              |      |

|          |                 | 4.5.1 Dynamically Reconfigurable Active Cache | 54   |

|         | 4.5.2 DRAC Design                                                                                                          | 55                                                                                                                                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 4.5.3 Bridge/Cache Arbitrator & Bus Bridge                                                                                 | 55                                                                                                                                                                                                                                                                                                              |

|         | 4.5.4 Cache Module                                                                                                         | 56                                                                                                                                                                                                                                                                                                              |

|         | 4.5.5 Swap Module                                                                                                          | 57                                                                                                                                                                                                                                                                                                              |

|         | õ                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         | 0                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 4.6     | Summary                                                                                                                    |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| -       |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 5.3     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 5.4     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 5.5     | Message Queue                                                                                                              |                                                                                                                                                                                                                                                                                                                 |

| 5.6     | Idle Task                                                                                                                  |                                                                                                                                                                                                                                                                                                                 |

| 5.7     | Dynamic Scheduling Example                                                                                                 | 74                                                                                                                                                                                                                                                                                                              |

| 5.8     | Summary                                                                                                                    |                                                                                                                                                                                                                                                                                                                 |

| Evalu   | ation                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |

| 6.1     | Use cases                                                                                                                  |                                                                                                                                                                                                                                                                                                                 |

|         | 6.1.1 MP3 Decoder                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         | 6.1.2 Jpeg Encoder                                                                                                         |                                                                                                                                                                                                                                                                                                                 |

|         | 6.1.3 Packet Forwarding Application                                                                                        | 83                                                                                                                                                                                                                                                                                                              |

| 6.2     | Experimental Results                                                                                                       |                                                                                                                                                                                                                                                                                                                 |

|         | 6.2.1 Accuracy                                                                                                             |                                                                                                                                                                                                                                                                                                                 |

|         | -                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|         | -                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

| 6.3     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|         | 1                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 0.4     | · · ·                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |

| 0.4     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|         | 5                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         | · · · · · ·                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

|         | 1                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         | 0                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 6.5     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| Concl   | usions and future work                                                                                                     |                                                                                                                                                                                                                                                                                                                 |

| 7.1     |                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| bliogra | phy                                                                                                                        | 117                                                                                                                                                                                                                                                                                                             |

|         | Softw.<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>Evalu<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Concl<br>7.1 | 4.5.3       Bridge/Cache Arbitrator & Bus Bridge         4.5.4       Cache Module         4.5.5       Swap Module         4.5.6       Timing Model         4.5.7       DRAM Modeling         4.5.8       Cache Modeling Limitation in Hybrid Prototyping         4.6       Summary         Software Model layer |

#### vii

# List of Figures

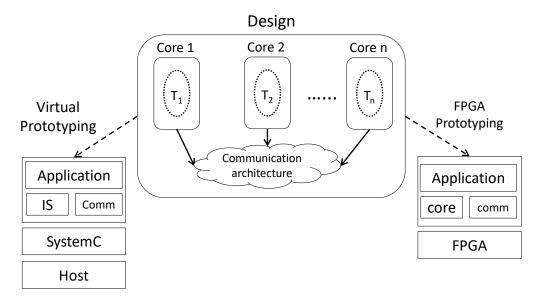

| Figure | 1: Virtual Prototyping vs. FPGA Prototyping                                                                         | 4    |

|--------|---------------------------------------------------------------------------------------------------------------------|------|

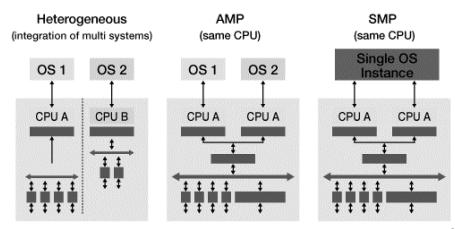

| Figure | 2: SMP vs. AMP configurations of multicore designs [40]                                                             | 16   |

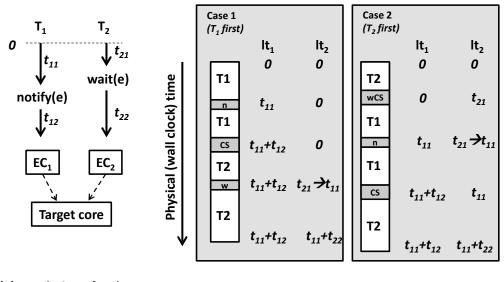

| Figure | <b>3:</b> Simple example of simulation with a hybrid prototype                                                      | 18   |

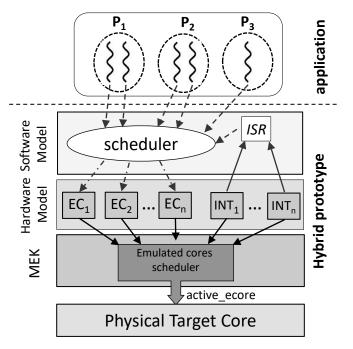

| Figure | 4: The hybrid prototyping framework                                                                                 | 20   |

| Figure | 5: The MEK structure in the                                                                                         | 23   |

| Figure | 6: The busy/idle time                                                                                               | 27   |

| Figure | 7: Simulation of two tasks on two emulated cores with hybrid prototyping                                            | 28   |

| Figure | 8: Possible emulation schedules                                                                                     | 29   |

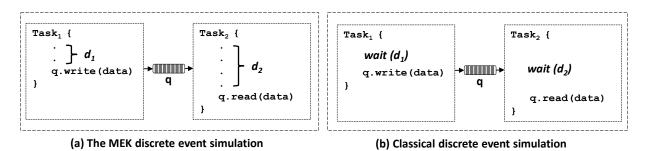

| Figure | 9: Classical vs the MEK discrete event simulation                                                                   | 32   |

| Figure | 10: Classical vs MEK discrete event simulation                                                                      | 32   |

| Figure | 11: Hardware model layer structure                                                                                  | 35   |

| Figure | 12: Emulated core life-cycle state diagram                                                                          | 37   |

| Figure | 13: Communication models in the hybrid prototyping                                                                  | 39   |

| Figure | 14: Simple example of using communication model by two emulated cores in the hybrid prototyping                     | . 42 |

| Figure | <b>15:</b> Simple example of using communication model by two tasks                                                 | 43   |

| Figure | 16: Simple example of using communication model by two tasks                                                        | 43   |

| Figure | 17: Multi-clock domain simulation example                                                                           | 50   |

| Figure | 18: A multicore design with its equivalent hybrid prototype                                                         | 53   |

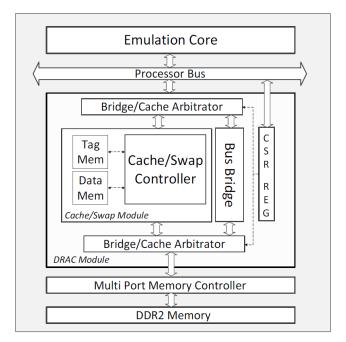

| Figure | 19: Top level design of DRAC                                                                                        | 55   |

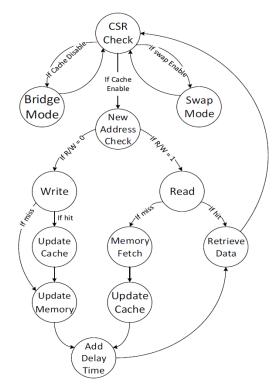

| Figure | 20: Finite State Machine of cache controller                                                                        | 56   |

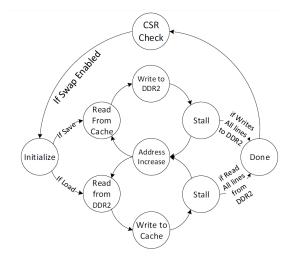

| Figure | <b>21:</b> FSM of swap controller (Swap Mode)                                                                       | 58   |

| Figure | 22: Software model layer structure                                                                                  | 65   |

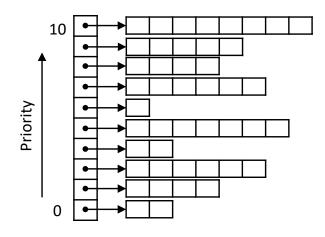

| Figure | 23: Threads ready queue                                                                                             | 67   |

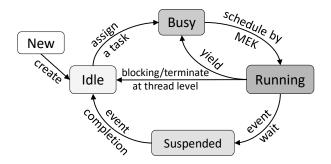

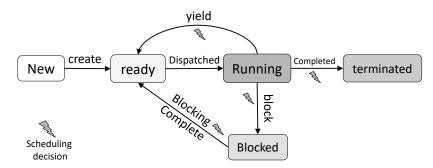

| Figure | 24: Thread life cycle in the software model scheduler                                                               | 68   |

| _      | <ul> <li>25: Simple example of dynamic scheduling on two emulated cores with a hardware interrupt</li></ul>         | 74   |

| Figure | 26: Timing estimation example with two threads running on a design with two emulated cores and a hardware interrupt | 77   |

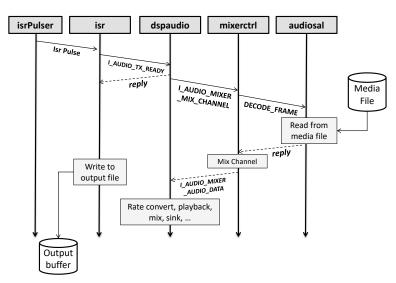

| Figure | 27: The MP3 decoder application                                                                                     |      |

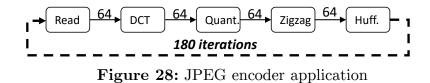

| Figure | 28: | JPEG encoder application                                                                                                                       | . 82 |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|------|

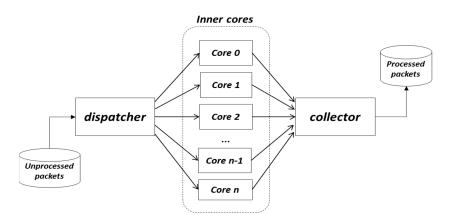

| Figure | 29: | Simple Packet forwarding application                                                                                                           | . 83 |

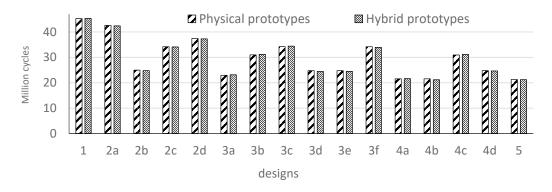

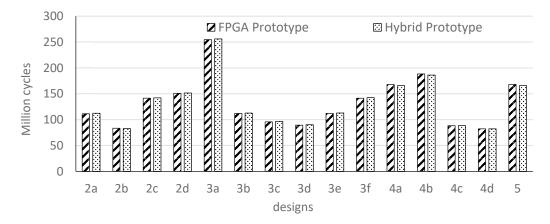

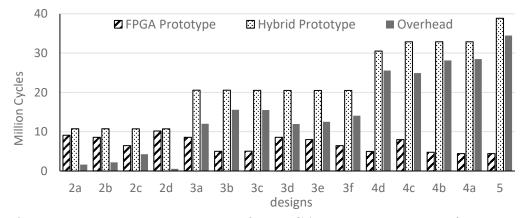

| Figure | 30: | The busy times for FPGA, hybrid and Virtual prototypes for the JPEG encoder                                                                    | . 84 |

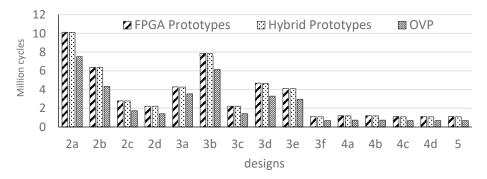

| Figure | 31: | The execution time reported by FPGA and hybrid prototypes for the JPEG encoder                                                                 | . 85 |

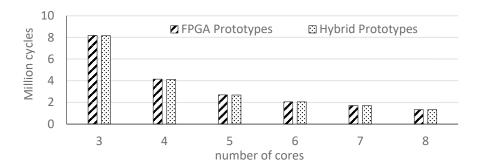

| Figure | 32: | Packet forwarding application execution time for all designs with up to 8 cores                                                                | . 89 |

| Figure | 33: | The execution times for FPGA and hybrid prototypes for the JPEG encoder<br>with multiple clock domains                                         | . 90 |

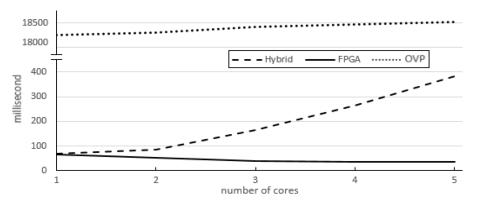

| Figure | 34: | Prototyping speed comparison between FPGA, hybrid and OVP prototypes<br>for the JPEG encoder                                                   | . 92 |

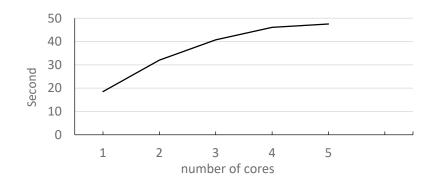

| Figure | 35: | The simulation times for FPGA and hybrid design for the JPEG encoder application                                                               | . 93 |

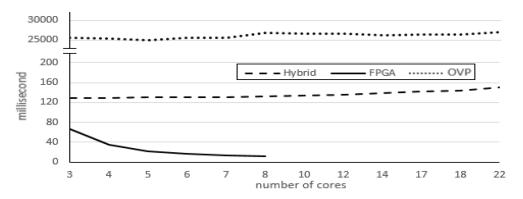

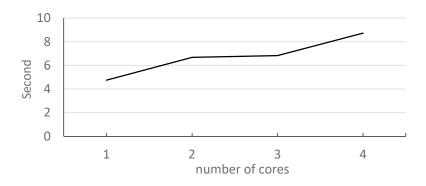

| Figure | 36: | Prototyping speed comparison between FPGA, hybrid and OVP prototypes<br>for Packet forwarding application                                      | . 93 |

| Figure | 37: | Simulation time (second) reported by the hybrid prototype with dynamic scheduling with different number of cores for JPEG encoder              | . 95 |

| Figure | 38: | Simulation time (second) reported by the hybrid prototype with dynamic scheduling with different number of cores for MP3 decoder               | . 95 |

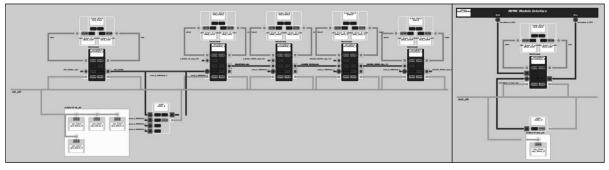

| Figure | 39: | Hybrid prototype vs. FPGA prototype hyper-terminal output                                                                                      | . 97 |

| Figure | 40: | Hybrid prototype vs. FPGA prototype hardware design for MP3 decoder application                                                                | . 97 |

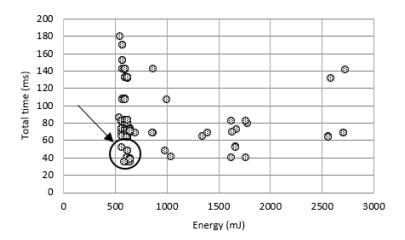

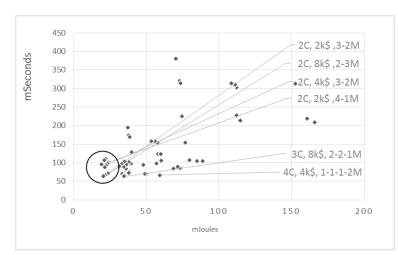

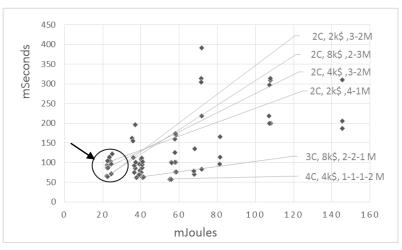

| Figure | 41: | Design Space Exploration                                                                                                                       | . 98 |

| Figure | 42: | Scatter chart for design exploration with two different clock domains                                                                          | 103  |

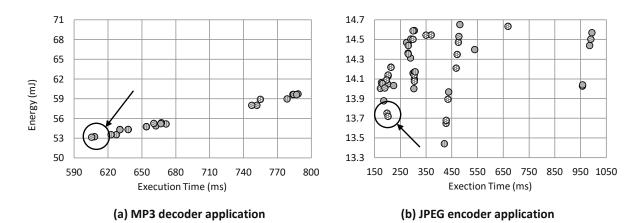

| Figure | 43: | Speed vs. Energy consumption for different SMP designs with multi-clock domains and different threads' priorities for the JPEG encoder and MP3 | 104  |

| ъ.     |     | decoder applications                                                                                                                           |      |

| -      |     | Simulation speed of hybrid prototypes with DRAC                                                                                                |      |

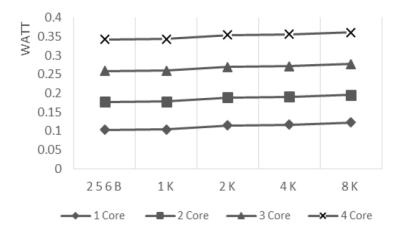

| -      |     | Power consumption for different L1 cache sizes                                                                                                 |      |

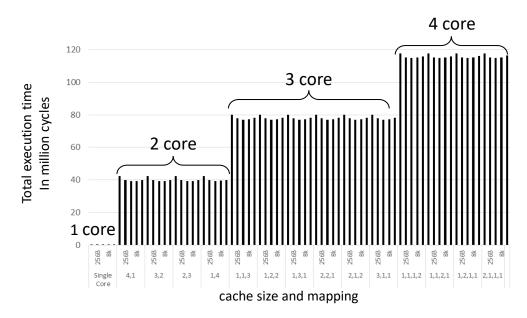

| -      |     | Design exploration using full FPGA prototype                                                                                                   |      |

| Figure | 47: | Design exploration using hybrid prototype                                                                                                      | 111  |

# List of Tables

| Table 1: Effect of concurrent writes to DRAM                                                |

|---------------------------------------------------------------------------------------------|

| Table 2: Multiple write factor for different number of cores                                |

| Table 3: Threads and emulated cores trace                                                   |

| Table 4: Task mappings for the JPEG encoder multicore designs       82                      |

| Table 5: The JPEG encoder execution time in CPU cycles for all possible design              |

| Table 6: The MP3 decoder execution time                                                     |

| Table 7: Packet forwarding application execution time for all designs with up to 8 cores 88 |

| Table 8: MP3 decoder results with multiple clock domains       89                           |

| Table 9: The JPEG encoder all possible design results with multiple clock domains 91        |

| Table 10: The busy power consumption for different clock domains                            |

| Table 11: Number of all possible design with multiple clock domains                         |

| Table 12: Estimation accuracy of standalone DRAC                                            |

| Table 13: Estimation accuracy of DRAC-based hybrid prototype                                |

| Table 14: Swap time consumption for different L1 sizes                                      |

| Table 15: Resource usage of hybrid vs FPGA prototype         109                            |

# Code Listings

| Listing 1: Timer class                                  | 24 |

|---------------------------------------------------------|----|

| Listing 2: Control time                                 | 24 |

| Listing 3: Event class                                  | 25 |

| Listing 4: Event's wait pseudo code                     | 26 |

| Listing 5: Event's notify pseudo code                   | 27 |

| Listing 6: Shared resource write pseudo code            | 31 |

| Listing 7: Shared resource read pseudo code             | 31 |

| Listing 8: Hardware description with hybrid prototyping | 36 |

| Listing 9: FSL class                                    | 39 |

| Listing 10: FSL's blocking write method                 | 40 |

| Listing 11: FSL's blocking read method                  | 41 |

| Listing 12: Signal's wait method pseudo code            | 46 |

| Listing 13: Signal's signal method pseudo code          | 47 |

| Listing 14: Simple interrupt thread pseudo code         | 48 |

| Listing 15: Thread class in the software model          | 67 |

| Listing 16: Message queue send method pseudo code       | 71 |

| Listing 17: Message queue receive method pseudo code    | 72 |

| Listing 18: Idle thread pseudo code                     | 73 |

## **Publications and Workshops**

- Ehsan Saboori, Samar Abdi, "Fast and cycle-accurate simulation of multi-threaded applications on SMP architectures using hybrid prototyping", International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Pittsburgh, USA, 2016

- Ehsan Saboori, Samar Abdi, "Rapid design space exploration of multi-clock domain MPSoCs with Hybrid Prototyping", Electrical & Computer Engineering (CCECE), 2016

29th IEEE Canadian Conference on, Vancouver, BC, 2016

- 3. A. Barzegar, E. Saboori and S. Abdi, "DRAC: a dynamically reconfigurable active L1 cache model for hybrid prototyping of multicore embedded systems," 2014 25nd IEEE International Symposium on Rapid System Prototyping, New Delhi, 2014, pp. 86-92.

- Ehsan Saboori, Samar Abdi, "Hybrid Prototyping of Multicore Embedded Systems", qualified presentation at TEXPO, student competition and exhibition, Ottawa, Canada, Oct, 2014

- 5. S. Abdi, E. Saboori, "Hybrid Prototyping of Many-core Embedded Systems," Many-Core Embedded Systems Workshop (MCES), Montreal, Canada, October, 2013.

- E. Saboori, S. Abdi, "Hybrid Prototyping of MPSoCs," In Proceedings of the International Forum on MPSoC and Embedded Multicore, Otsu City, Japan, June, 2013 (invited paper).

- Saboori, Ehsan; Abdi, Samar, "Hybrid Prototyping of multicore embedded systems," Design, Automation & Test in Europe Conference & Exhibition (DATE), 2013, vol., no., pp.1627,1630, 18-22 March 2013

- The source code is available at: https://github.com/ehsab/hybrid\_prototyping

## Glossary

| DES                 | Design Space Exploration                              |

|---------------------|-------------------------------------------------------|

| DRAC                | Dynamically Reconfigurable Active Cache               |

| FPGA                | Field Programmable Gate Arrays                        |

| FPGA Prototyping    | Using FPGAs as a platform for SoC development and     |

|                     | verification                                          |

| Hybrid Prototyping  | The proposed prototyping framework in this thesis     |

| ISS                 | Instruction Set Simulator                             |

| MEK                 | Multicore Emulation Kernel                            |

| MPSoC               | Multi Processors System on Chip                       |

| RTL                 | Register-Transfer Level                               |

| RTOS                | Real-time Operating System                            |

| SMP                 | Symmetric Multiprocessing                             |

| $\mathbf{SoC}$      | System on Chip                                        |

| Thread Scheduling   | deciding which thread runs at a certain point in time |

| Virtual Prototyping | Software-based modelling for SoC development and      |

|                     | verification                                          |

# Chapter 1

### Introduction

#### 1.1 Motivation

Multicore platforms are becoming increasingly pervasive in modern embedded systems because of the potential computation speedups resulting from concurrent application execution on independent cores. However, both the multicore hardware platform and the embedded software that runs on it must be carefully designed for functional correctness and optimal performance. System level modeling techniques have enabled creation of fast models of multicore platforms, commonly known as virtual platforms, for early functional validation of embedded software. Virtual platforms enable early functional validation of embedded software, before the chip is delivered. For accurate performance validation, the complete multicore platform can be prototyped on *F*ield *P*rogrammable *G*ate *A*rrays (FPGA). The FPGA prototype serves as a cycle-accurate hardware model of the chip and can be used for embedded software design using incircuit emulation tools.

Both virtual and FPGA prototypes have their respective pros and cons. Virtual prototypes have the advantage of high speed functional simulation and, typically, scale

well with the number of cores. However, the accuracy of performance estimation is sacrificed because the processor simulation models used are very abstract. Cycleaccurate models may be used in virtual prototypes, but they drastically slow down simulation speed, thereby defeating the purpose of fast and early software validation. FPGA prototypes provide cycle-accurate performance estimation because the software executes directly on an FPGA implementation of the target cores. However, it takes a significant amount of time to design, implement and test the inter-core communication architecture on the FPGA. Furthermore, if several cores are being used, the amount of reconfigurable logic required for implementing the cores, the communication fabric, and the on-chip memory for the full multicore system becomes too large to fit on a single FPGA. Using multiple FPGA chips adds another dimension of complexity to implementing the prototype. Therefore, the scalability and design time of full system FPGA prototypes are serious issues.

In this thesis, we present a new technique called Hybrid Prototyping framework that offers the scalability benefits of virtual prototypes, as well as the cycle-accuracy of FPGA prototypes. The system provides a high-speed model of a multicore platform that will enable embedded software designers to accurately analyze and debug their applications before the hardware is available. Application designers can also use these models to influence the multicore architecture design early in the design process. The fundamental idea of hybrid prototyping is to create an emulation kernel in software that executes on a single target core. The target core is physically implemented in FPGA. The emulation kernel simulates the execution of concurrent tasks on independent emulated cores by dynamically scheduling the tasks on the physical target core. The emulation kernel manages the state of the individual emulated cores and the logical times until which they have been simulated.

#### 1.2 Literature Review

Pre-silicon performance validation of multicore embedded systems is a serious challenge. Both virtual prototyping and FPGA-based physical prototyping have been a topic of intense research with the growing adoption of multicore architectures and the corresponding need to provide early simulation models to embedded software designers.

Virtual prototype is a set of functional models of System on Chip (SoC) hardware such as processors, peripherals and buses, in software form. Processor model is often implemented using *Instruction Set Simulator* (ISS) which provides binary compatibility with embedded processor (called Target) instruction set. ISS converts target instruction set to the instruction set of the general-purpose computer by running the simulation (called Host) to allow execution of un-modified embedded software. Bus and peripheral are typically modeled using a high-level language such as ANSI C or SystemC with focusing on pin-accurate software visible interfaces such as register, bus protocol and peripheral functionality.

FPGA-based prototyping is another widely-used pre-silicon SoC evaluation method using FPGA as the platform. FPGA can be used to implement any logic function that an *Application-Specific Integrated Circuit* (ASIC) chip could perform, which makes it a good platform for rapid system prototyping. In FPGA-based prototype the application and the system software for a design is executed directly on FPGA. Figure 1 shows virtual prototyping vs. FPGA prototyping.

Figure 1: Virtual Prototyping vs. FPGA Prototyping

Conventional technologies such as virtual prototyping and FPGA prototyping have several limitations. Virtual prototypes, based on host-compiled ISS, can provide high simulation speed, but at the expense of limited or no timing accuracy. FPGA prototypes, based on instantiation and integration of processor cores in FPGA, provide cycle accuracy, but with the disadvantage of high development cost and lack of scalability. In addition, there is no flexibility of abstracting the inter-core communication in FPGA prototypes, since it is fixed in hardware. Furthermore, software debugging on multiple processors in FPGA can be quite challenging.

#### 1.2.1 Virtual Prototyping

In recent years multicore virtualization has become an important research subject in computer architecture and embedded systems fields. Virtual prototyping involves the use of highly abstracted target architecture model. Many tools and frameworks have been developed for virtual prototyping. The SimpleScalar [1] tool set provides an infrastructure for simulation and architectural modeling. This tool is an interpreter which executes all program instructions and can model a variety of platforms ranging from simple unpipelined processors to detailed dynamically scheduled microarchitectures with multiple-level memory hierarchies. Quick EMUlator (QEMU) [2] is an open source machine emulator which relies on dynamic binary translation. It allows applications compiled for one architecture to be run on another. The proposed system provides performance estimation for Design Space Exploration (DSE). Mambo [3] is a full-system simulator for modeling PowerPC-based systems. It provides building blocks for creating simulators that range from purely functional to timing-accurate. ASIM [4] is a decoupled simulation framework. This framework provides modularity which helps break down the performance-modeling problem into individual pieces that can be modeled separately, while its reusability allows using a software component repeatedly in different contexts. PTLsim [5] is a cycle accurate full system x86-64 microprocessor simulator and virtual machine. This framework provides cycle accurate simulation with sacrificing the speed.

These frameworks not only enable earlier software development but also can give a feedback where the hardware needs to be adapted or to be changed prior the implementation. The enabler for virtual prototyping is a virtual platform, which is an executable model of the target core architecture, including processors, memories, buses and peripheral [6]. Virtual prototyping can provide flexibility, scalability and ease of debugging for the designer, but one most compromise either simulation speed or accuracy. Virtual prototypes cannot provide highly accurate results due to abstract software implementation of models. Conversely, if accurate models are used in virtual prototyping, the simulation slows down significantly.

Software cycle-accurate simulation has been the primary tool to allow collaborative hardware and software [7]. Cycle-accurate *R*egister-*T*ransfer *L*evel (RTL) simulations accurately model hardware behaviors down to register transfer level, suitable for hardware verification and profiling. They provide very accurate timing with sacrificing the simulation time. ModelSim [8], Synopsys VCS [9] and Cadence Incisive Enterprise Simulator [10] are some example of these kind of simulators. Simics [11] is a full-system functional simulators. It provides the level of accuracy necessary to execute fairly complex binaries on the simulated machine. GEMS [12], timing multiprocessor simulator, and SimWattch simulation tool [13], used for microprocessor performance and power estimation, are built on top of the Simics library. Such simulators can be used for large designs with range of single-digit hertz which is not reasonable for regular software code to be run on it [6].

Amongst the software-based methods, the most successful developments have been virtual platform technologies based on binary translation, as commercialized by Windriver [14], Coware [15], and Xilinx XVP [16]. In most virtual platforms, hostcompiled ISS have replaced or complemented traditional cycle-accurate microarchitecture simulators [17] [18]. HISCS [19] is a technique for generation of fast instruction-set simulators that combines the benefit of both compiled and interpretive simulation. A major challenge in this technique is the compilation time overhead that makes usage of compiler optimizations impractical, especially for large applications. DynamoSim [20] is a suite of techniques inspired by recent advances in dynamic compilers to construct a hybrid simulation framework. In this framework any instruction can be interpreted and only frequently executed instructions are translated on-the-fly into native code for direct execution. SoClib [21] is an open platform for virtual prototyping of *M*ulti-*P*rocessors *S*ystem on *C*hip (MPSoC). Its core is based on a library of SystemC [22] simulation models to facilitate architecture exploration of MPSoC. Open Virtual Platform (OVP) [23] is an open source virtual platform which uses OVPsim to simulate different designs. OVPsim is an instruction accurate simulator which provides infrastructure for describing platforms with one or more processors containing shared memory and busses in arbitrary topologies and peripheral models [24]. Wang et al. [25] have shown OVP and its interoperability with the existing Transaction-Level Modeling (TLM) based SystemC platforms shows that OVP is faster than other existing solutions. Such simulators can provide significant speedups (reaching simulation speeds of several hundred MIPS), but often focus on functionality and speed at the expense of limited or no timing accuracy.

Host-compiled software simulation technique is based on source level static delay annotation in the application [26] [27]. The delays are derived by analyzing the execution of applications on an abstract model of the core. Although source-level annotation techniques promise high simulation speed, they require the full application source, including sources of libraries. These techniques also use an abstract core model, leading to estimation inaccuracies.

Another popular method to simulate a multiprocessor system is to integrate multiple ISSs into a SystemC based simulation backbone. MPARM [7] is well known academic simulation platforms based on this solution. Such simulators are able to execute target binary and provide cycle-accurate simulation. However, they are extremely slow and very complicated [28].

7

#### 1.2.2 FPGA Prototyping

FPGAs are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing. This feature distinguishes FPGAs from ASICs, which are custom manufactured for specific design tasks. FPGAs has become a natural choice for building system prototypes of ASIC and SoC designs. It allows hardware designers to develop and test their systems, and it provides software developers early access to a fully functioning hardware platform.

FPGA Prototyping is a technique to verify the functionality and performance by implementing the design on a FPGA. FAST [29] is a methodology that enables a single FPGA to accelerate the performance of cycle-accurate computer system simulators modeling modem, realistic SoCs and embedded systems. ProtoFlex [30] simulation architecture is an FPGA-based, full-system functional simulator for a symmetric multiprocessor server, hosted on a single FPGA and achieves a significant speedup over comparable software simulation. Chiou et al. improve FAST simulator by supporting work in parallelized computer system simulators [31]. Taeweon et al. [32] show the possibility of using FPGA in architecture research to enhance the simulation time. They introduce a new hardware/software co-simulation method that performs execution-driven microarchitecture simulation. Based on an off-the-shelf Pentium-III system that communicates with an FPGA via the Front-Side Bus. RAMP gold [33] is a FPGA-based architecture simulator for multiprocessors provides a high-throughput, cycle-accurate full-system simulator that runs on a single Xilinx Virtex-5 FPGA board, and which simulates a 64-core shared-memory target machine capable of booting real operating systems.

FPGA prototypes are highly accurate and fast. So, designers do not have to rely only on software simulations to verify a design. The application and system software for a design is executed directly on FPGA prototype to ensure that it is functionally correct before implementation. In contrast to virtual prototyping, FPGA prototyping does not provide scalability and flexibility is too costly. It is impractical for designers to implement different hardware platform on FPGA, given the vast amount of design choices.

FPGA prototyping can be much more complicated for multicore architectures because FPGA logic on a chip is limited. Prototyping multicore may require multiple FPGA chips, which can compromise the accuracy of the FPGA prototype. In addition, debugging can be cumbersome and time consuming on FPGA prototypes. ChipScope [34] and SignalTAP [35] are standard debugging tools offered by FPGA vendors. However, they are difficult to use with multicore. Several prototyping frameworks using FPGA have been proposed. RAMP [36] provides the prototyping platform for implementing the full-system under test on FPGA. This platform puts together a large array of FPGAs in order to support the instantiation and integration of hundreds of cores [37] [36]. Unfortunately, the cost and design time of such full system prototypes is very high [30]. In addition, there is no flexibility of abstracting the inter-core communication in RAMP, since it is fixed in hardware by the inter-FPGA communication architecture.

Another FPGA-based modeling approach implements the SystemC simulation kernel in FPGA to support standard hardware I/O during simulation [38]. Yet, another type of FPGA-assisted simulation, called virtual in-circuit emulation, runs software-on-host and application-specific hardware on FPGA to avoid slow RTL simulation in software [39]. The above techniques are incremental improvements to cycle-accurate simulation and have not been shown to scale to large multicore designs.

#### **1.3 General Problem Statement**

The objective of this work is to design a novel system-level modeling framework, called hybrid prototyping that can provide the benefits of both virtual platforms and FPGA prototypes. Virtual prototypes have the advantage of scalability and high speed functional simulation by sacrificing the accuracy of performance estimation. Using cycle-accurate models are drastically slow down simulation speed. FPGA prototypes provide cycle-accurate performance. However, the scalability and design time of full system FPGA prototypes are serious issues.

The proposed framework targets the typical Symmetric MultiProcessing (SMP) architecture consisting of multiple cores, each with a dedicated L1 cache and shared off-chip main memory. It also introduces emulation kernel and the modeling of dynamic Real-Time Operating System (RTOS) scheduler as well as hardware interrupts on top of the emulation kernel, in order to support the simulation of unmodified multi-threaded applications. The L1 caches of the cores are emulated by a dynamically reconfigurable on-chip memory module to support dynamic thread scheduling in SMP designs. In order to meet the above objective, we need to address some key technical challenges in hybrid prototyping design. First, the core, the emulation kernel and the cache model must all fit on one FPGA chip for optimal performance. Second, the emulation kernel and the cache model must be highly optimized for performance so that the core-context switching overhead is minimized. Finally, the emulation system must be completely transparent to the user, similar to virtual platforms.

Hybrid prototyping aims to provide early, fast, and scalable models similar to virtual prototypes along with the cycle-accuracy of FPGA prototypes. Using hybrid prototyping, embedded software designers can create concurrent applications and accurately analyze the performance implication of their optimizations before implementation. At the same time, hardware architects can modify the platform model without having to do full FPGA prototyping. Therefore, hybrid prototyping will enable early and reliable multicore embedded system design, resulting in huge productivity gains for both embedded software designers and multicore chip architects.

#### 1.4 Thesis Contribution

The main contributions of this thesis are presented as follows:

- 1. Multicore Emulation Kernel (MEK). The fundamental idea of hybrid prototyping is to create multicore emulation kernel that executes on a single target core, which is physically implemented in FPGA. The MEK emulates the execution of concurrent tasks on independent cores by dynamically scheduling them on the physical target core. It provides simulation primitives and the modeling of intercore communication. The emulation kernel, MEK, implements primitives for the management of discrete events and logical times for the tasks. It also provides simulation primitives and services to instantiate emulated cores and modeling of inter-core communication for SMP architecture. SMP is a system that has multiple, identical processors all sharing memory and devices.

- 2. Multi-clock domains MPSoCs. Most embedded processors support several operating frequencies, which allows us to create a mixture of cores, each running at a different operating point. So, a multicore embedded system might have multiple clock domains. Hybrid prototyping can be applied to realistic multi-clock MPSoC designs.

- 3. Simulation of Hardware peripherals (interrupts). An important aspect of RTOS design is the mechanism for servicing the interrupt-driven devices such as hardware peripherals. Hybrid prototyping is extended to simulate interrupts issued by external hardware.

- 4. **Memory hierarchy simulation.** Caches are widely used in embedded system to increase efficiency. So it is important to consider memory hierarchy in hybrid prototyping. A novel dynamically reconfigurable active L1 cache (instruction and

data) model called DRAC proposed for hybrid prototyping. It is an on-chip hardware peripheral connected to the local bus of the core. DRAC is responsible for swapping the cache context when the MEK switches simulation context from one emulated core to another. Utilizing DRAC model, embedded designers are able to analyze, verify, and optimize their multicore design with cache design without the need for full system prototyping.

- 5. SMP designs with dynamic RTOS scheduler model. In SMP designs, the number of threads that can run concurrently (simultaneously) is limited by the number of processors. Since each processor can execute only one thread at a time, with multiple processors, multiple threads can execute simultaneously. A single kernel manages all cores simultaneously. The hybrid prototyping supports SMP architectures and introduces the modeling of dynamic RTOS scheduler on top of the emulation kernel, in order to support the simulation of unmodified multi-threaded applications. Therefore, in the hybrid prototyping, the RTOS scheduler can dynamically schedule any thread on any emulated core to achieve full utilization of all emulated cores.

- 6. Automatic/Semi-Automatic Design Space Exploration. Using hybrid prototypes, multicore embedded system designers can create concurrent applications and accurately analyze the power and performance implication of their optimizations before the hardware is available. As such, the hybrid prototyping is capable of fast and early multicore design space exploration. It can provide huge productivity gains for multicore chip architects as they can optimize the hardware architecture without having to do full system prototyping.

#### 1.5 Thesis Outline

The remainder of this thesis is organized as follows. In Chapter 2 the hybrid prototyping methodology is presented. We start with describing the main idea behind the hybrid prototyping technique followed by explaining its different layers. In chapter 3, we describe the MEK and primitives provided by this layer. Chapter 4 explains the hardware model layer and its primitives. Memory hierarchy and cache model supported by the hybrid prototyping are also discussed in details. Chapter 5 covers software model layer including thread management and RTOS model scheduler. Chapter 6 includes the experimental results for evaluating the hybrid prototyping in terms of accuracy, speed and scalability. Finally, conclusions and suggestions for future work are provided in Chapter 7.

# Chapter 2

### Hybrid Prototyping Methodology

Multicore platforms deliver greater computing power through concurrency, offer greater system density, and run at lower clock speeds than uniprocessor chips resulting lower power consumption and thermal dissipation. Multiprocessing includes several operating modes such as SMP and Asymmetric MultiProcessing (AMP). An AMP system has multiple cores (may be either heterogeneous or homogeneous multicore). A separate operating system or a separate copy of the same operating system, manages each core. Typically, each application's process is locked to a single core. It provides an execution environment similar to that of uniprocessor systems. It allows simple migration of legacy code and facilitates management of each core independently. However, it can result in underutilization of processor cores. For instance, if one core becomes busy, applications running on that core cannot, in most cases, migrate to a core that has more CPU cycles available. Though such dynamic migration is possible, it typically involves complex check pointing of the application's state and can result in a service interruption while the application is stopped on one core and restarted on another. SMP is a computer architecture that provides fast performance by using two or more homogeneous processors to complete individual processes simultaneously under a single operating system. Unlike asymmetrical processing, any idle processor can be assigned any task, and additional processors can be added to improve performance and handle increased loads. Specific applications can benefit the most if the code allows multithreading. SMP systems can easily move tasks between processors to balance the workload efficiently. Figure 2 shows different configurations of a multicore design.

Figure 2: SMP vs. AMP configurations of multicore designs [40]

Hybrid Prototyping [41] is a modeling framework that aims to provide early, fast, and cycle-accurate models of SMP designs which are widely used in modern embedded and networking SoCs. The fundamental idea is to simulate a design with multiple processor cores by creating a *M*ulticore *E*mulation *K*ernel (MEK) in software on top of a single physical instance of the processor. The MEK switches between cores and manages the logical simulation times of the individual processor cores. Since the application executes on exactly the same core as it is targeted for, the simulation is cycle-accurate. As a result, we can achieve fast and cycle-accurate simulation of multicores, thereby overcoming the accuracy concerns of virtual prototyping and the scalability issues of FPGA prototyping. Using hybrid prototypes, multicore system designers can create concurrent applications and accurately analyze the power and performance implication of their optimizations before the hardware is available.

#### 2.1 Methodology

Hybrid prototyping time-multiplexes several emulated cores on a single physical target core. The principal idea is to simulate a design with multiple processor cores by creating an emulation kernel in software on top of a single physical instance of the processor core. Since the application executes on exactly the same core as it is targeted for, the simulation is cycle-accurate. The core and the additional simulation infrastructure can fit on a single FPGA chip, making it very cost effective in contrast to full system prototyping in FPGA. It supports the execution of any multi-tasking ANSI C/C++ application.

Since the application executes on exactly the same core as it is targeted for, the estimation accuracy is 100%, in contrast to binary translation. As opposed to sourcelevel annotation techniques, there is no need for availability of source code or knowledge of the core datapath, since the application binary runs directly on the target core. Finally, the at-speed execution of application tasks in our technique provides significant speedup over cycle-accurate software simulation.

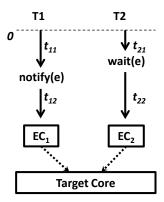

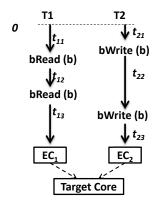

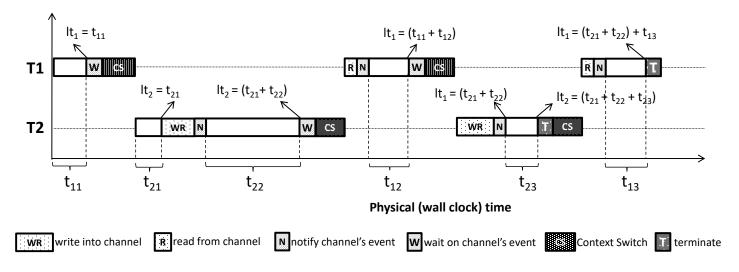

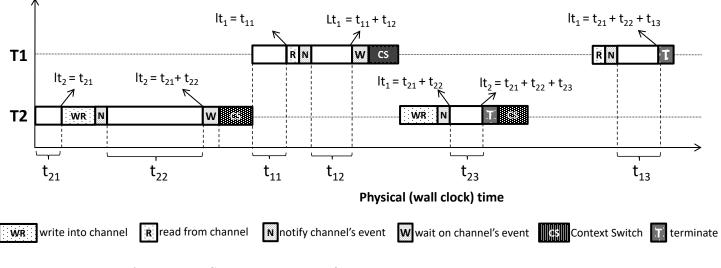

Figure 3 uses a simple example to illustrate the concept of multi-core simulation on a hybrid prototype. We assume that the design consists of multiple cores, communicating using inter-core communication primitives, such as simplex channels. The synchronization in the channels between the threads (mapped to different cores) is modeled using events. We assume a classical discrete event model, in which an event is consumed by a waiting thread, or lost if no thread is waiting at the logical time of notification.

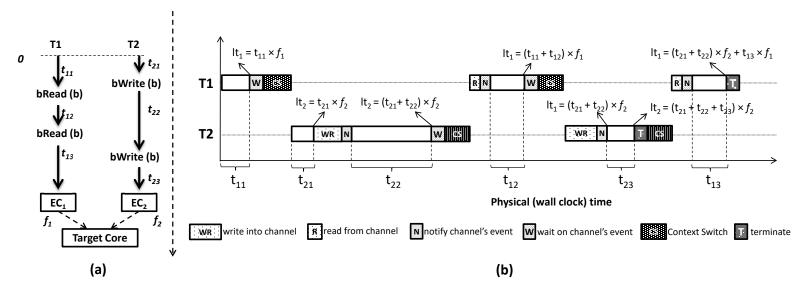

## (a) Emulation of tasks on (b) Possible emulation schedules two different cores

**Figure 3:** Simple example of simulation with a hybrid prototype

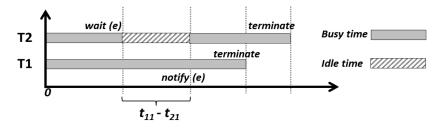

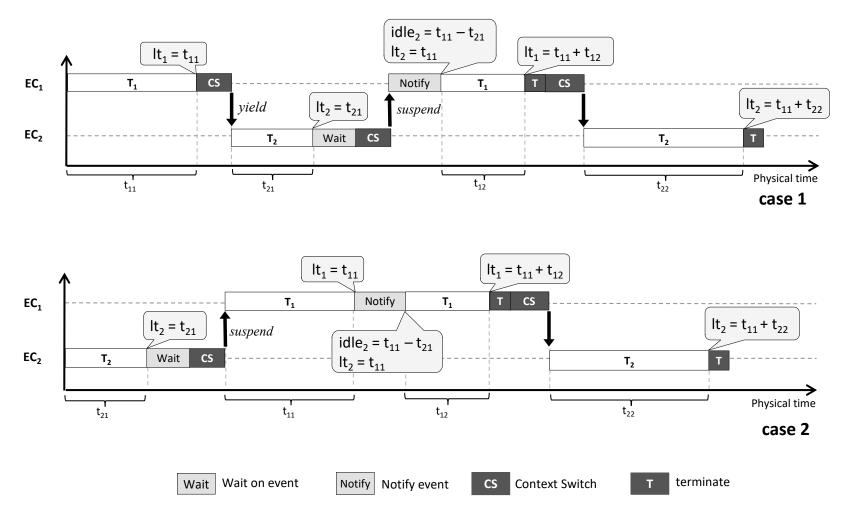

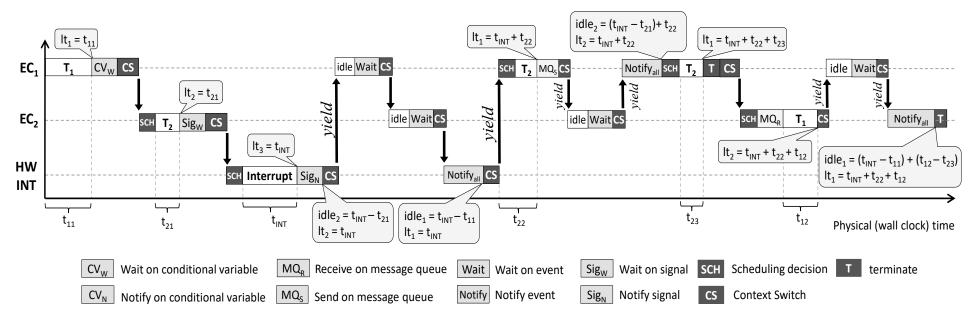

Figure 3(a) shows the design with two cores, each executing a single thread. Thread T<sub>1</sub> executes on core EC<sub>1</sub> for time t<sub>11</sub> and notifies a global event e. After notification, it executes for another t<sub>12</sub> units and terminates. Thread T<sub>2</sub> executes on core EC<sub>2</sub> (of the same type as EC<sub>1</sub>) for time t<sub>21</sub> (< t<sub>11</sub>) and waits for the global event e. After e is notified (by T<sub>1</sub>), it executes for another t<sub>22</sub> units and terminates. Both tasks are assumed to start at the same time. The cores, EC<sub>1</sub> and EC<sub>2</sub>, are simulated on the target core, which is of the same type as EC<sub>1</sub> and EC<sub>2</sub>, and hosts the MEK.

Figure 3(b) shows two possible simulation schedules on the target core. A thread may be in four possible states: RUNNING, READY, BLOCKED or TERMINATED. The MEK maintains the logical times,  $lt_1$  and  $lt_2$ , of the two emulated cores EC<sub>1</sub> and EC<sub>2</sub>, respectively. The logical time for an emulated core is the time until which the core has been simulated since the beginning of system simulation. At logical time 0, the MEK may pick either EC<sub>1</sub> or EC<sub>2</sub> to simulate first. If the MEK schedules EC<sub>1</sub> to be simulated first, it runs T<sub>1</sub> on EC<sub>1</sub> until *e* is notified. The MEK saves the event's notification and its logical timestamp t<sub>11</sub>. Since event notification is non-blocking in a discrete event model, the MEK allows  $T_1$  to execute until it is terminated. Once  $T_1$  is terminated, the MEK does a context switch (CS) and runs  $T_2$  from its logical time 0 until it reaches *wait(e)* at logical time  $t_{21}$ . At this point the MEK checks for any notifications of *e* that were made after logical time  $t_{21}$ . Indeed, since  $t_{11}>t_{21}$ , the MEK finds that *e* was notified by  $T_1$  before  $T_2$  started waiting for it. As such the MEK updates the logical time of EC<sub>2</sub> to  $t_{11}$  to model  $T_2$  being blocked on the wait from  $t_{21}$ to  $t_{11}$ . Finally,  $T_2$  is resumed and runs to completion.

If the MEK schedules EC<sub>2</sub> to be simulated first (Case 2), it runs T<sub>2</sub> on EC<sub>2</sub> from EC<sub>2</sub>'s logical time 0 until it reaches wait(e) at EC<sub>2</sub>'s logical time t<sub>21</sub>. Since no notifications of e are found, the MEK stores the wait on event e with timestamp equal to t<sub>21</sub> and blocks T<sub>2</sub>. It then does a core context switch from EC<sub>2</sub> to EC<sub>1</sub>. To emulate EC<sub>1</sub>, the MEK runs T<sub>1</sub> from EC<sub>1</sub>'s logical time 0 until the notification of e at EC<sub>1</sub>'s logical time t<sub>11</sub>. Upon notification, the MEK checks if there are any pending waits on event e at or before logical time t<sub>11</sub>. Indeed, task T<sub>2</sub> is blocked since EC<sub>2</sub>'s logical time t<sub>21</sub> (< t<sub>11</sub>) on e. Therefore, the MEK unblocks T<sub>2</sub> and updates EC<sub>2</sub>'s logical time to t<sub>11</sub> in order to account for the blocking time. The MEK continues simulating EC<sub>1</sub> until termination of T<sub>2</sub>.

#### 2.2 Modeling Framework

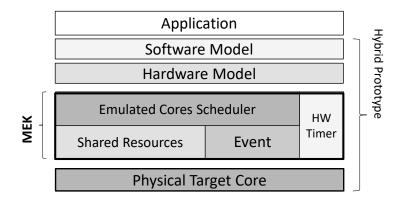

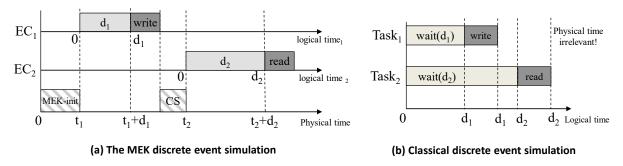

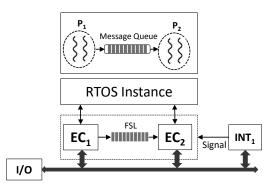

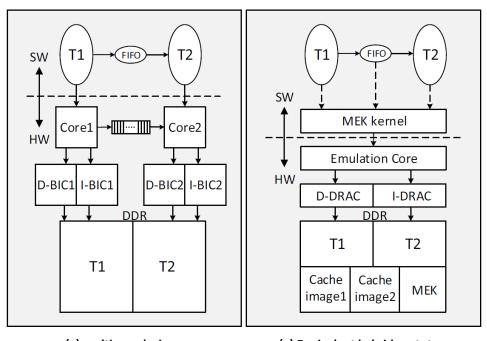

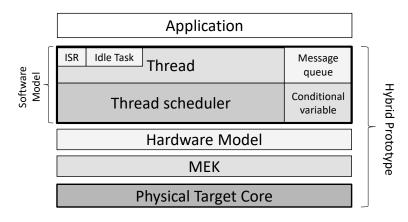

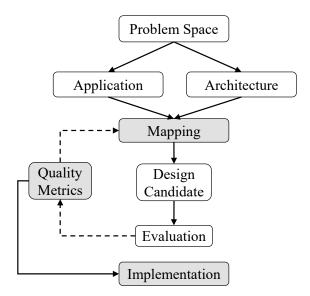

Figure 4 illustrates the modeling framework of the hybrid prototyping. A hybrid prototype is a combination of software and hardware components. The hardware component is the target core which is physically implemented in FPGA. And the software component consists of three layers: the MEK, software and hardware models.

Figure 4: The hybrid prototyping framework

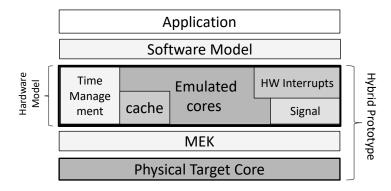

The MEK implements primitives for the management of discrete events and logical times of the emulated cores. It provides services to instantiate emulated cores and communication channels. This layer consists of discrete event model, shared resource (SR), hardware timer and emulated cores scheduler. The MEK defines primitives for event management using basic notify/wait concept. The context switching between emulated cores during simulation is done by the emulated core scheduler. It stores the context (stack, registers and state) of the running thread and loading the context of

the next ready thread. Timer primitives is also defined to provide a simple API to control the execution time.

The hardware layer models emulated SMP cores that are responsible for executing the user application threads, memory hierarchy and hardware interrupt sources. It provides services to allocate/deallocate a thread to a specific emulated core. The hardware design such as the number of processors, hardware interrupts, processors frequencies, Fast Simplex Link (FSL) (for modeling of simplex channels for point-topoint communication between the emulated cores) and etc. are implemented as an API on top of the MEK primitives in this layer

The software model layer implements OS primitives for scheduling and communication on top of the hardware model. It provides models of priority-based preemptive scheduler - which is responsible for scheduling threads on the emulated cores -, *I*nter-*P*rocess *C*ommunication (IPC) services, and *I*nterrupt *S*ervice *R*outines (ISR). The software model is the layer of the system which interacts directly with the user application. It defines thread management primitives (e.g. pthread\_create, sleep, etc.), message queue, conditional variables and other essential services needed by the user application.

The hybrid prototyping simulates the execution of concurrent tasks on independent cores by dynamically scheduling the processes on the emulated cores. As it is shown in Figure 4, only one thread can be run on the physical processor at a time.

#### 2.3 Summary

In this chapter we introduced the hybrid prototyping methodology and the idea behind it. We then explained the modeling framework and described different layers of the hybrid prototype. Hybrid prototype consists of three layers: software model layer which is responsible for thread scheduling, hardware model layer which is providing primitives for instantiating the emulated cores and the MEK which defines primitives for the management of discrete events and provides timer API required for managing the logical times for the emulated cores. In the next chapter we will talk about the MEK and its role in the hybrid prototyping.

# Chapter 3

### **Multicore Emulation Kernel**

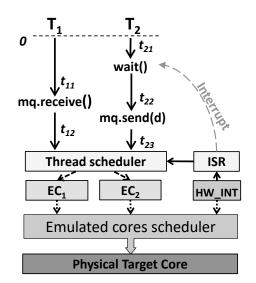

Figure 5 shows the MEK structure. The MEK provides simulation primitives for the management of events and shared resources. The most important part of the MEK is the emulated cores scheduler which is responsible to switch context between emulated cores. The timer primitive is also defined to provide a simple API to control the execution time.

Figure 5: The MEK structure in the

# 3.4 Hardware Timer Controller

The MEK uses a hardware timer (XPS Timer [16]) controller to measure the execution time in CPU cycles. The hardware timer driver provides a simple API to control the timer. The XPS Timer is organized as two identical timer modules. Each timer module has an associated load register that is used to hold the value for the counter. The MEK defines timer class to provide a simple API to control the execution time. Listing 1 shows the timer class which is providing essential methods to work with both timer modules in the hardware timer.

```

Class Timer{

public:

Timer(u16 deviceId);

void start(u16 timerId);

void stop(u16 timerId);

u32 getValue(u16 timerId);

private:

XTmrCtr XPS_Timer;

int controlTime;

}

```

#### Listing 1: Timer class

For measuring the execution time of a block of code, the MEK starts the timer before the block by calling *start* method. At the end of the block, the MEK calls *stop* method to stop the timer and reads the timer's value by calling *getValue* method. To have accurate time measurement, the MEK must account for control time, which is the CPU time consumed for starting and stopping the timer, without any operations between them. The Listing 2 shows calculates the control time.

```

u32 get_control_time() {

start(0);

stop(0);

return XTmrCtr_GetValue(&XPS_Timer, 0);

}

```

#### Listing 2: Control time

## 3.5 Event

We have implemented a classical discrete event model, where an event is consumed by a waiting thread, or is lost if no thread is waiting at the logical time of notification. Each event maintains a waitlist which is sorted by the logical time of wait calls. The item type in the list is a pair of id and timestamp. As the name implies, the waitlist is the list of all emulated cores that their running threads are waiting on the event. Listing 3 shows the event class in the MEK.

```

class Event {

public:

Event();

~Event();

void wait();

void notify();

private:

Boost::List< pair<int,int> >* waitList;

void insertWait(int id, int timeStamp);

}

```

Listing 3: Event class

The MEK defines notify/wait methods for event management. Listing 4 shows the pseudo code for event's wait method. Each kernel call is surrounded by KERNEL\_CALL\_START and KERNEL\_CALL\_END functions. The first function, stops the timer to mark the end of user code and the start of execution of the kernel call. It also uses the timer value to update the logical time of the running emulated core. While the second function starts the timer before the kernel call returns to the user core. Wait operation puts the emulated core in suspended state (line 2), adds the wait to the event's waitlist (line 3) and gives the control of the physical processor to the emulated core on the top of the busy queue (next busy emulated core) (line 4). *Active\_ecore* is the emulated core which is actually running on the physical processor and consume CPU cycles.

```

void event::wait() {

1: KERNEL_CALL_START();

2: suspend(active_ecore);

3: this->waitlist.insert(active_ecore);

4: run_next_ready_ecore();

5: KERNEL_CALL_END();

}

```

#### Listing 4: Event's wait pseudo code