# Validation and Enhancement of a Three-level Inverter for Applications in Real-time Simulations

# **Deepak Chetia**

A Thesis

In the Department of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science

(Electrical & Computer Engineering) at

Concordia University

Montreal, Quebec, Canada.

April, 2018 © Deepak CHETIA

#### **CONCORDIA UNIVERSITY**

#### SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Deepak Chetia

Entitled: Validation and Enhancement of a Three-level Inverter for Applications in Real-time Simulations

And submitted in partial fulfillment of the requirements for the degree of

#### **Master of Applied Science**

Complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|     |                  | Chair                                |

|-----|------------------|--------------------------------------|

|     | Dr. R. Raut      |                                      |

|     | Dr. W. Lucia     | Examiner, External<br>To the Program |

| _   |                  | Examiner                             |

|     | Dr. P. Pillay    |                                      |

|     |                  | Supervisor                           |

|     | Dr. A.K. Rathore |                                      |

|     |                  | Co-Supervisor                        |

|     | Dr. D. Nasrallah |                                      |

|     |                  |                                      |

| 1 1 |                  |                                      |

Approved by: \_

Dr. W. E. Lynch, Chair Department of Electrical and Computer Engineering

20

Dr. Amir Asif, Dean Faculty of Engineering and Computer Science

#### ABSTRACT

The motivation of this thesis is to perform a hardware validation of a three-level inverter in real-time simulation. Real-time simulators enable faster design and prototyping of controllers without the need of building hardware based test benches. But, it is also essential that the virtual models behave the way they were supposed to, and produce equivalent output as the physical setups. Power electronic systems often have very fast switching devices, which are an inhibiting factor for real-time simulation, as the simulator must have the capability to produce high resolution samples of the gate pulses of these fast acting devices. A virtual model for the three-level inverter is available already for real-time simulation. This model had been tested with the outcome of other non-real-time solvers such as the one from Simscape Power System's Simulink, but not alongside with a physical inverter. Hence, a physical inverter was operated along with its virtual model in a real-time simulator to verify the model.

Real-time simulators use different approaches to model power electronic systems and also make them suitable for such simulations. One such approach is to solve for the nodal voltages and currents using fixed admittance matrices derived from the network. This fixed matrix contains a switch conductance parameter derived from a discrete time model of an ideal switch. The choice of this parameter is very crucial in determining the accuracy of the real-time simulations. A number of ways are used to optimize this parameter, but optimizing a proper value is always a challenge.

This work is dedicated to my father...

#### ACKNOWLEDGEMENT

I would like to express my gratitude to my supervisor, Prof. Akshay Kumar Rathore for his immense support and motivation in my MASc studies. His inputs and attention to detail motivated me a lot while completing my thesis; he has been an inspiration throughout my studies. He was always present to help me out with any impasse that I faced during my work. I also thank him for his initiative to involve me in the NSERC CRD project co-sponsored by OPAL-RT.

I would also like to thank my co-supervisor Danielle Nasrallah, for sharing her expertises with me, her inputs were very crucial for the completion of this thesis. She has been involved in the project at every step and has given a lot of her time and effort, without her assistance it would have been impossible for me to proceed with the project.

I would like to thank my family, especially my mother and my fiancée for their sacrifices they have been making in the pursuance of my endeavors.

My work would have been incomplete without the help from my colleagues M.H. Afshin, Mohamed Omer, Karin Feistel, Luccas Kunzler and Gabriel Broday. M.H. Afshin and Karin assisted me a lot in reviewing my work and provided with very helpful constructive criticism. I also thank Ahmed Kotb and K.S Amitkumar for their help to make me understand about OPAL-RT systems. I thank everyone in the PEER group of Concordia University, for all the assistance and the amicable environment they provided during the course of my studies. Thanks are also due to OPAL-RT and National Science and Engineering Research Council of Canada, for supporting me with financial assistance.

# **TABLE OF CONTENTS**

| LIST OF TABLES                                                | xiii |

|---------------------------------------------------------------|------|

| LIST OF FIGURES                                               | xv   |

| LIST OF ACRONYMS                                              | xxi  |

| INTRODUCTION                                                  |      |

| Chapter 1. Literature Review                                  |      |

| 1.1 Simulation of power electronic circuits                   |      |

| 1.2 Real-time Simulation                                      |      |

| 1.3 Selection of the real-time simulator                      |      |

| 1.4 CPU and FPGA Based Simulation                             |      |

| 1.5 Discrete Time Switch Model in Real-time Simulation        |      |

| 1.6 Validation of Power Electronic Circuits                   |      |

| 1.7 Multilevel Inverters                                      |      |

| 1.8 Conclusion                                                |      |

| Chapter 2. Switch Model in Real-Time Simulation               |      |

| 2.1 Switch Model in Real-time Simulation:                     |      |

| 2.2 Real-time Simulation of Power Electronic Converters:      |      |

| 2.3 The need of Fixed Admittance Matrix Nodal Method:         |      |

| 2.4 Limitations of Pejovic Switch Model                       |      |

| 2.5 Conclusion                                                |      |

| Chapter 3. Real-Time Simulation of a Three-Level NPC Inverter |      |

| 3.1 Introduction to Multilevel Inverters                      |      |

| Diode Clamped Multilevel Inverter:                            |      |

| Flying Capacitor Multilevel Inverter:                         |      |

| Cascaded Inverter with Separate DC Sources:                                   | 42 |

|-------------------------------------------------------------------------------|----|

| 3.2 Working of the Three-level NPC Inverter                                   |    |

| 3.2.1 Allowed Switching States                                                | 49 |

| 3.2.2 Classification of Modulation Techniques Available For 3 Level Inverters | 50 |

| 3.2.3 Sinusoidal PWM (SPWM) for a Three-level Inverter:                       | 51 |

| 3.2.4 Advantages and Applications of Three-level Inverter                     | 54 |

| 3.3 Modelling of a Three-level Inverter in Real-time Simulation               | 56 |

| 3.3.1 The RT Lab Environment                                                  | 57 |

| 3.3.2 Gating Pulse Generation in RT Lab                                       | 63 |

| 3.3.3 Experimental Setup                                                      | 64 |

| 3.4 Expressions for Instantaneous Voltages                                    | 67 |

| 3.5 Validation of a Virtual Inverter with a Physical Three-level NPC Inverter | 69 |

| 3.5.1 Inverter Operation at Unity Power Factor                                |    |

| 3.5.2 Inverter Operation at 0.95 Power Factor                                 |    |

| 3.5.3 Inverter Operation at 0.9 Power Factor                                  |    |

| 3.5.4 Measurements:                                                           |    |

| 3.6 Inverter Operation with Unbalanced Load                                   |    |

| 3.7 Inverter Operation with an Unbalanced Load and Reduced DC link voltage    |    |

| 3.8 Conclusion                                                                |    |

| Chapter 4. Optimization of G <sub>S</sub> Parameter used in FAMNM for RTS     | 85 |

| 4.1 Need of G <sub>s</sub> Optimization                                       |    |

| 4.2 Getting Gs as a Ratio of Switches' Currents and Voltages                  |    |

| 4.2.1 A Buck Converter with an Open Circuited Freewheeling Diode              |    |

| 4.2.2 A Boost Converter with a Short Circuited Freewheeling Diode             |    |

| 4.2.3 A Three-phase Three-level Inverter with Unbalanced Load                 |    |

| 4.3 Getting Gs by Reducing the Distance between Eigenvalues of Ideal Switches and Pe     | jovic |

|------------------------------------------------------------------------------------------|-------|

| Switches.                                                                                | . 100 |

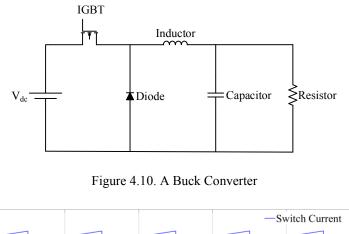

| 4.3.1 Buck Converter with Ideal Switch S1 ON and S2 OFF                                  | . 104 |

| 4.3.2 Buck Converter with Ideal Switch S1 OFF and S2 ON                                  | . 105 |

| 4.3.3 Buck Converter with Ideal Switch S1 and S2 ON                                      | . 107 |

| 4.3.4 Buck Converter with Ideal Switch S1 and S2 OFF                                     | . 108 |

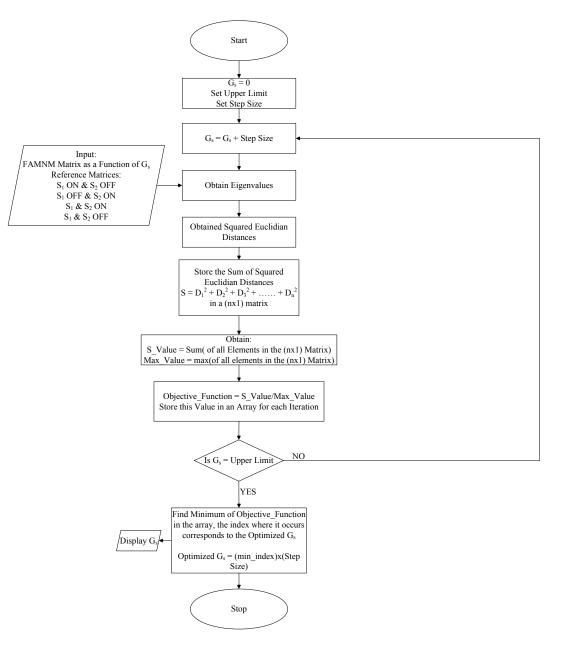

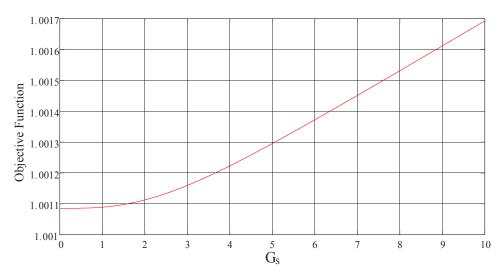

| 4.3.5 Algorithm for Implementing the Proposed G <sub>s</sub> Optimization Method         | . 110 |

| 4.3.6 Validation of the Buck Converter                                                   | . 112 |

| 4.4 Conclusion                                                                           | . 116 |

| Chapter 5. Evaluation of Efficiency of the Three-Level Inverter using Offline Simulation | . 117 |

| 5.1 Introduction                                                                         | . 117 |

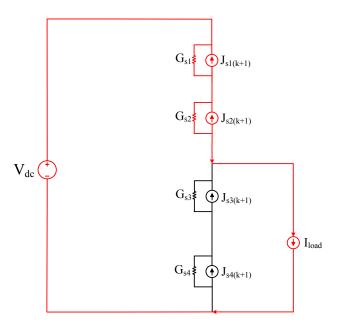

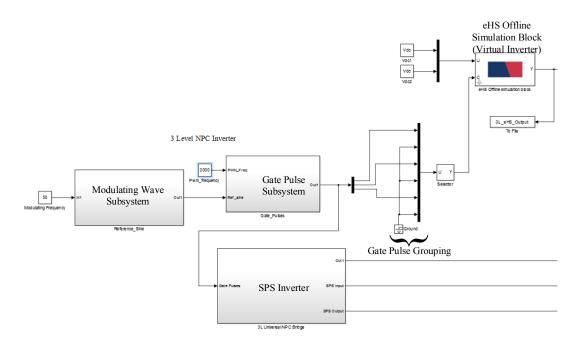

| 5.2 Verification Model for Offline eHS Simulation                                        | . 117 |

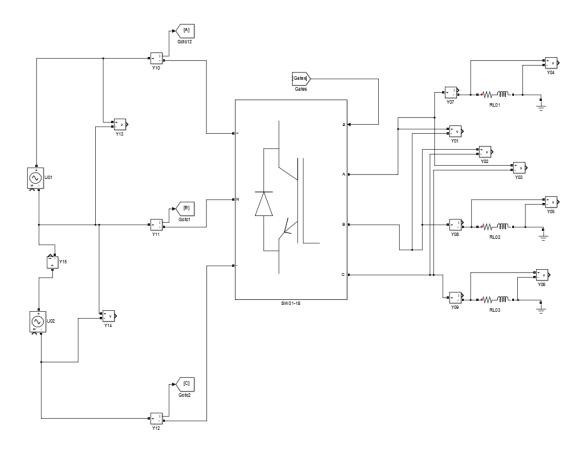

| 5.3 SPS Circuit with the Universal Bridge                                                | . 118 |

| 5.4 eHS Offline Block                                                                    | . 119 |

| 5.4 Conclusion                                                                           | . 122 |

| Chapter 6. Conclusion and Future Work                                                    | . 123 |

| Conclusion                                                                               | . 123 |

| Contributions of the Thesis                                                              | . 124 |

| Future Work                                                                              | . 124 |

| BIBLIOGRAPHY                                                                             | . 127 |

# LIST OF TABLES

| Table 1. Table of the Switch State and Boolean Value                                    |          |

|-----------------------------------------------------------------------------------------|----------|

| Table 2. Voltage Blocked by the Top Throw Switch                                        | 44       |

| Table 3. Voltage Blocked by the Middle Throw Switch                                     |          |

| Table 4. Voltage Blocked by the Bottom Throw Switch                                     |          |

| Table 5. Complementary Behavior of the Switches                                         | 49       |

| Table 6. Switch States and Instantaneous Switch Voltages                                | 49       |

| Table 7. Allowed Switching States                                                       | 50       |

| Table 8. Switching States to be avoided                                                 | 50       |

| Table 9. Naming Convention of the Elements in the Reference Model                       | 61       |

| Table 10. Naming Convention of the IGBT's in the Reference Model                        |          |

| Table 11. Details of Some of the Components in the 3 L NPC Inverter                     | 67       |

| Table 12. Instantaneous Pole Voltages                                                   |          |

| Table 13. Details of the Load Connected for Different Power Factors                     | 69       |

| Table 14. Parameters Set for the Virtual and the Physical Inverter                      | 69       |

| Table 15. Output of the Real Inverter Measured Using a Voltmeter and a Clamp-meter      |          |

| Table 16. Output of the Virtual Inverter Measured Using a Digital Storage Oscilloscope  |          |

| Table 17. Results of the Real-time Simulation Compared with Different Solvers           |          |

| Table 18. Oscilloscope Settings                                                         |          |

| Table 19. Details of the Real-time Simulator                                            |          |

| Table 20. Inverter Parameters for Inverter Operation with Unbalanced Load               |          |

| Table 21. Comparison of the Results (RMS output) of RTS of the 3 L NPC Inver            | ter with |

| Unbalanced Load                                                                         |          |

| Table 22. Inverter Parameter for Inverter Operation with Unbalanced Load and Redu       | iced DC  |

| Link Voltage                                                                            |          |

| Table 23. Comparison of the Results (RMS output) of RTS of the 3 L NPC Inver            | ter with |

| Unbalanced Load                                                                         |          |

| Table 24. Circuit Parameters of the Buck Converter                                      |          |

| Table 26. Output Parameters of the Normal Buck Converter                                |          |

| Table 27. Output Comparison of the Boost Converter with Different G <sub>s</sub> values |          |

| Table 30. $G_s$ Matrix for the Inverter with a 0.001 $\Omega$ Line to Line Fault        | 100      |

| Table 31. Output of the Inverter from eHS and SPS                                 | 100 |

|-----------------------------------------------------------------------------------|-----|

| Table 32. Eigenvalues of the Buck Converter with $S_1$ ON and $S_2$ OFF           | 105 |

| Table 33. Eigenvalues of the Buck Converter with $S_1$ OFF and $S_2$ ON           | 107 |

| Table 34. Eigenvalues of the Buck Converter with $S_1$ OFF and $S_2$ ON           | 108 |

| Table 35. Eigenvalues of the Buck Converter with $S_1$ OFF and $S_2$ ON           | 110 |

| Table 36. Eigenvalues for all the Switch Combinations                             | 112 |

| Table 37. Output of the Buck Converter from SPS and eHS                           | 113 |

| Table 38. Output of the Buck Converter With Shorted Diode                         | 114 |

| Table 40. Output of the SPS and eHS Inverter at 0.9 PF Load                       | 121 |

| Table 41. Comparison of the SPS and eHS Inverters connected to an Unbalanced Load | 122 |

|                                                                                   |     |

### **LIST OF FIGURES**

| Figure 1.1. Timing Diagram when Computation Time is less than Simulation Time Step          | o (non-  |

|---------------------------------------------------------------------------------------------|----------|

| real-time)                                                                                  | 27       |

| Figure 1.2. Timing Diagram when Computation Time is greater than Simulation Time Step       | p (non-  |

| real-time)                                                                                  | 27       |

| Figure 1.3. Timing Diagram during Real-time Simulation                                      | 27       |

| Figure 1.4. Computer chipset architecture prevalent before Sandy Bridge microarchi          | tecture  |

| introduced in 2011                                                                          | 29       |

| Figure 1.5. Modern computer chipset using Nehalem microarchitecture                         | 29       |

| Figure 1.6. CPU Based Simulation                                                            | 30       |

| Figure 1.7. FPGA Based Simulation                                                           | 31       |

| Figure 2.1. Ideal Switch                                                                    | 35       |

| Figure 2.2. Discrete Switch Model of an (i) ON Ideal Switch and (ii) OFF Ideal Switch       | 36       |

| Figure 3.1. Circuit Diagram of a Three-phase Three-level NPC Inverter                       | 42       |

| Figure 3.2. State of the Switch with Pole Connected to the Top DC Bus                       | 45       |

| Figure 3.3. Equivalent Electronic Switch for Throw T <sub>1</sub>                           | 46       |

| Figure 3.4. State of the Switch with Pole Connected to the Midpoint of the DC Bus           | 46       |

| Figure 3.5. Equivalent Electronic Switch for Throw T <sub>2</sub>                           | 46       |

| Figure 3.6. State of the Switch with Pole Connected to the Top DC Bus                       | 47       |

| Figure 3.7. Electronic Switch for Throw T <sub>3</sub>                                      | 47       |

| Figure 3.8. (i) Derived configuration and (ii) 3L TNPC topology                             | 48       |

| Figure 3.9. Single Leg of a NPC Inverter                                                    | 48       |

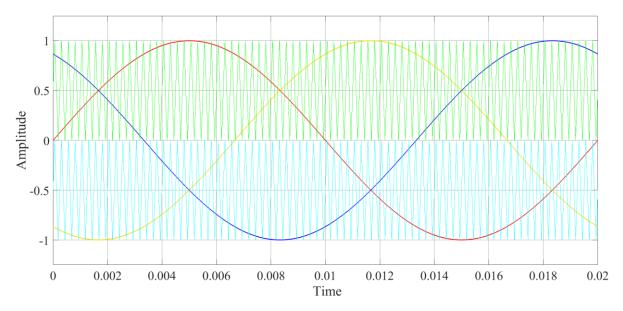

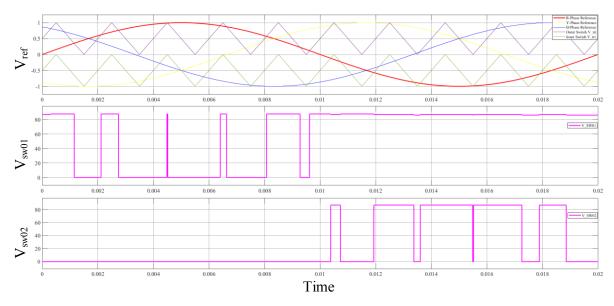

| Figure 3.10. Two Carrier Sinusoidal Modulation                                              | 52       |

| Figure 3.11. Switching of the Top Outer and the Inner Switches of the First Leg of the Inve | erter 53 |

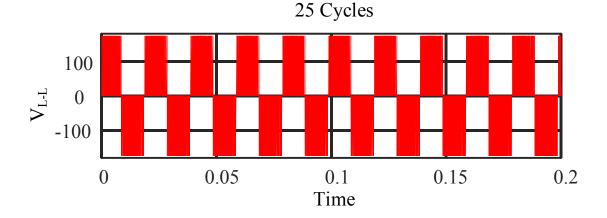

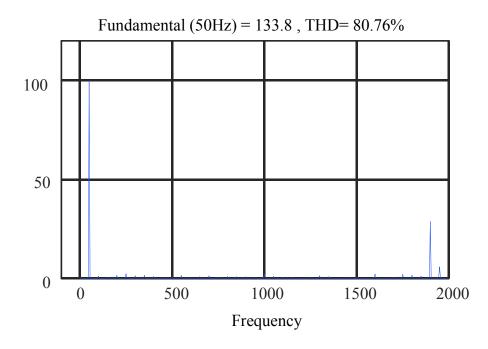

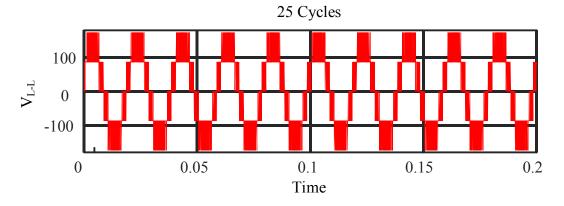

| Figure 3.12. Line Voltage of a Two-level Inverter                                           | 54       |

| Figure 3.13. THD of a Two-level Inverter                                                    | 55       |

| Figure 3.14. Line to Line Voltage of a Three-level Inverter                                 | 55       |

| Figure 3.15. THD of a Three-level Inverter                                                  | 56       |

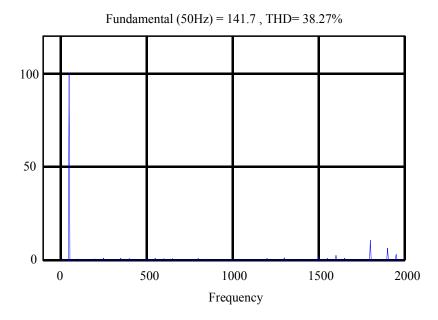

| Figure 3.16. The RT Lab Window                                                              | 58       |

| Figure 3.17. The Master and Console Subsystems in RT Lab                                    | 59       |

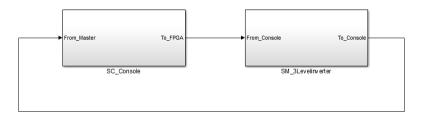

| Figure 3.18. The OpComm Block in RT Lab                                                     | 59       |

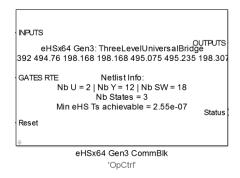

| Figure 3.19. The eHS Solver Block                                                                                       | . 60 |

|-------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.20. The Console Window Available during Real-time Simulation                                                   | . 61 |

| Figure 3.21. The Parameter Setting Window of the eHS Solver Block                                                       | . 62 |

| Figure 3.22. Parameter Window of the eHS Solver Block Showing the Netlist Details Extrac                                | ted  |

| by the Solver                                                                                                           | . 62 |

| Figure 3.23. Window Showing the Gate Settings for the eHS Solver                                                        | . 62 |

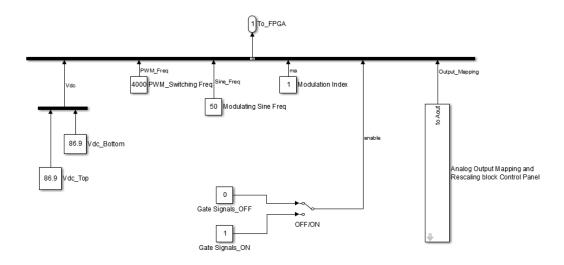

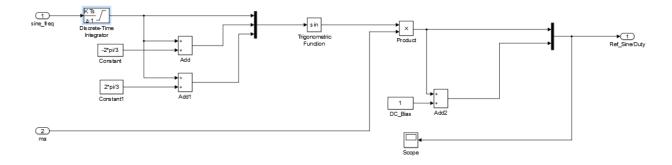

| Figure 3.24. Reference Sine Generation in RT Lab                                                                        | . 63 |

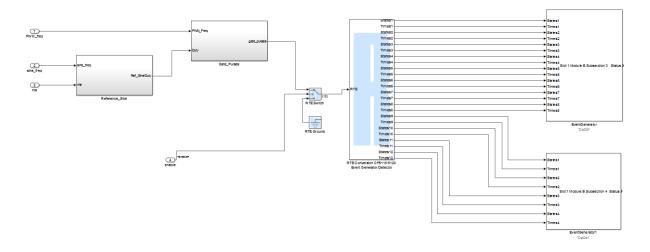

| Figure 3.25. Routing of the Gate Pulses to the Digital Output Boards                                                    | . 64 |

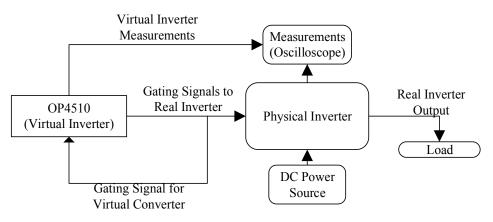

| Figure 3.26. Block Diagram of the Setup for the RTS of a Three-level Inverter                                           | . 64 |

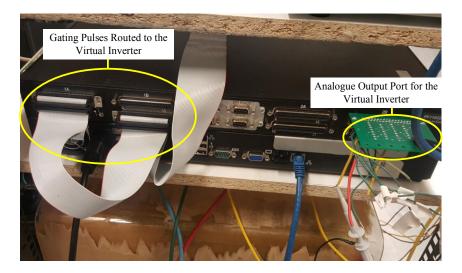

| Figure 3.27. Rear Side of the OPAL-RT OP4510 Simulator Showing the Digital Input/out                                    | tput |

| Ports and the Analogue Port                                                                                             | . 65 |

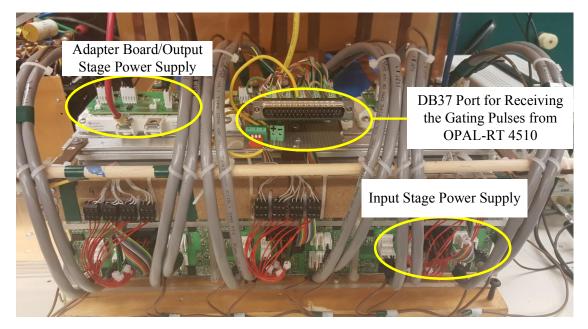

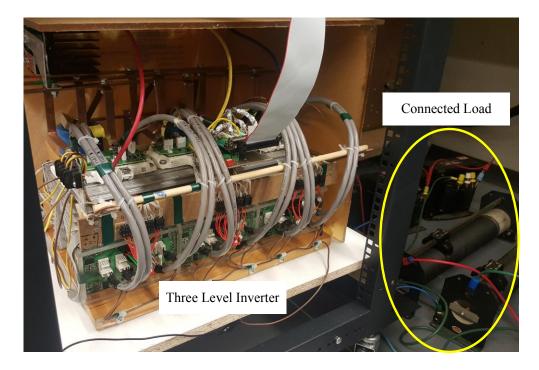

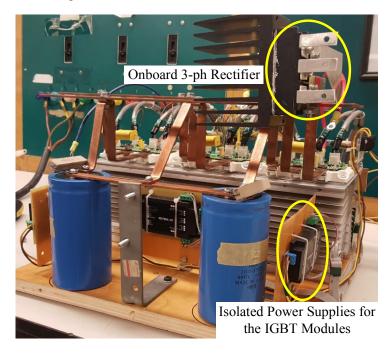

| Figure 3.28. Front Side of the Three-level Inverter                                                                     | . 65 |

| Figure 3.29. The Connected RL Load to the Inverter                                                                      | . 66 |

| Figure 3.30. Rear Side of the Three-level Inverter                                                                      | . 66 |

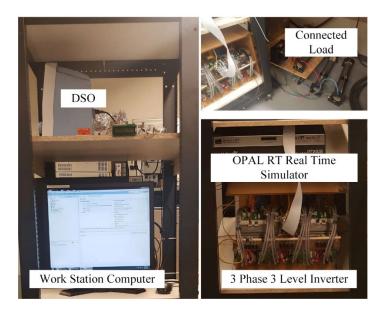

| Figure 3.31. Setup for the Validation of Three-level Inverter                                                           | . 67 |

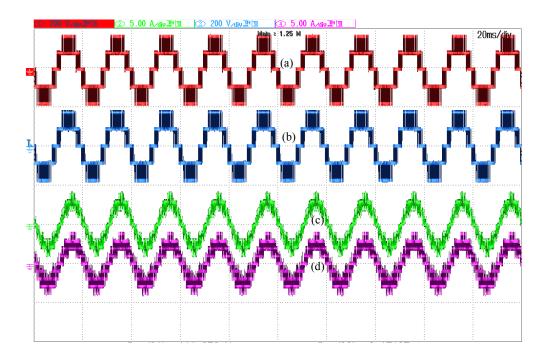

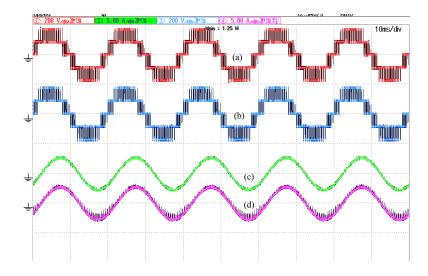

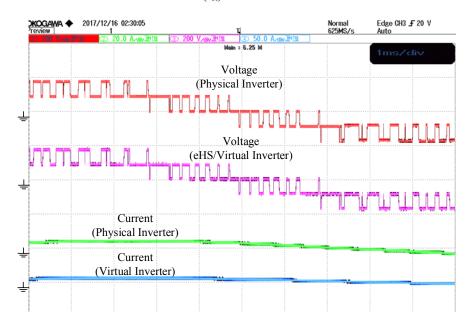

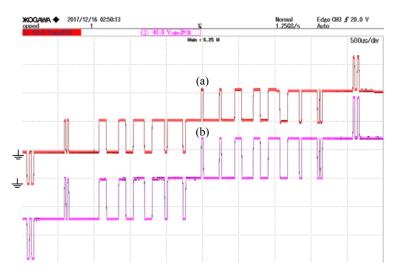

| Figure 3.32. Test Results from RTS of 3 L NPC Inverter with Unity Power Factor Load; (a) L                              | ine  |

| Voltage ( $V_{RY}$ ) of the Physical Inverter; (b) Line Voltage ( $V_{RY}$ ) of the Virtual Inverter; (c) L             | line |

| Current (I <sub>R</sub> ) of the Physical Inverter; (d) Line Current (I <sub>R</sub> ) of Virtual Inverter              | . 70 |

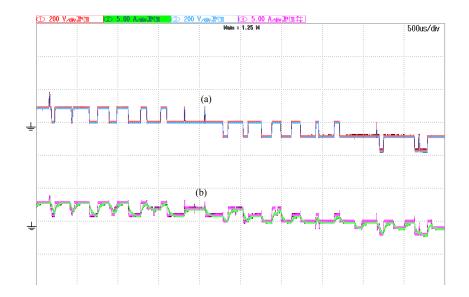

| Figure 3.33. Close Up View of Superimposed Results from RTS of 3 L NPC Inverter with Ur                                 | nity |

| Power Factor Load; (a) Line Voltage $(V_{RY})$ of the Physical and Virtual Inverter; (b) L                              | line |

| Current (I <sub>R</sub> ) of the Physical and Virtual Inverter                                                          | . 71 |

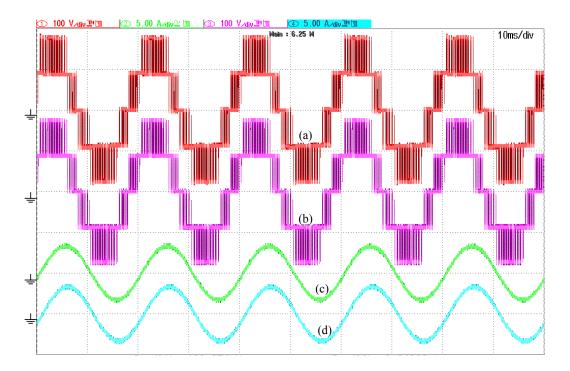

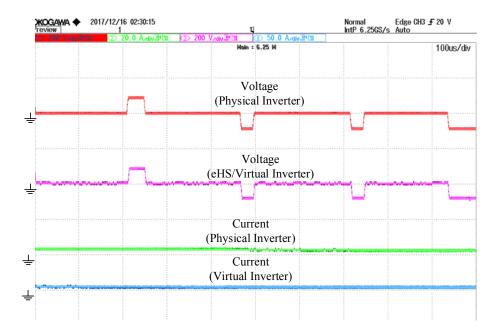

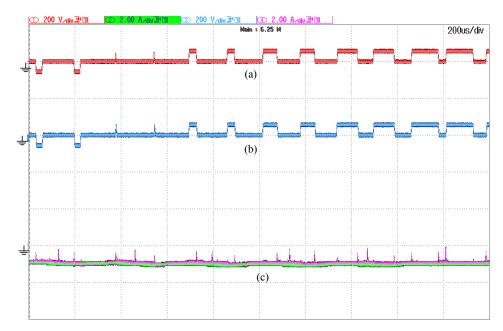

| Figure 3.34. Test Results from RTS of 3 L NPC Inverter with 0.95 Power Factor Load; (a) L                               | ine  |

| Voltage (V <sub>RY</sub> ) of the Physical Inverter; (b) Line Voltage (V <sub>RY</sub> ) of the Virtual Inverter; (c) L | line |

| Current (I <sub>R</sub> ) of the Physical Inverter; (d) Line Current (I <sub>R</sub> ) of Virtual Inverter              | . 71 |

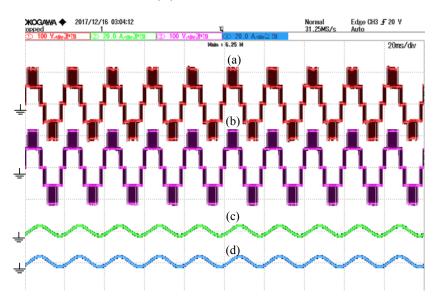

| Figure 3.35. Test Results from RTS of 3 L NPC Inverter with 0.9 Power Factor Load; (a) L                                | line |

| Voltage ( $V_{RY}$ ) of the Physical Inverter; (b) Line Voltage ( $V_{RY}$ ) of the Virtual Inverter; (c) L             | line |

| Current (I <sub>R</sub> ) of the Physical Inverter; (d) Line Current (I <sub>R</sub> ) of Virtual Inverter              | . 72 |

| Figure 3.36. Close-up Superimposed View of Results from RTS of 3 L NPC Inverter with                                    | 0.9  |

| Power Factor Load; (a) Line Voltage $(V_{RY})$ of the Physical and Virtual Inverter; (b) Line Curr                      | rent |

| (I <sub>R</sub> ) of the Physical and Virtual Inverter                                                                  | . 73 |

| Figure 3.37. Test Results from RTS of 3 L NPC Inverter with an Unbalanced Load; (a) Line                                      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Voltage ( $V_{RB}$ ) of the Physical Inverter; (b) Line Voltage ( $V_{RB}$ ) of the Virtual Inverter; (c) Line                |  |  |

| Current ( $I_R$ ) of the Physical Inverter; (d) Line Current ( $I_R$ ) of Virtual Inverter                                    |  |  |

|                                                                                                                               |  |  |

| Figure 3.38. Zoomed Waveforms of the Line Voltages and Currents (R-Phase)                                                     |  |  |

| Figure 3.39. Greater Zoomed Waveforms of the Line Voltages and Currents                                                       |  |  |

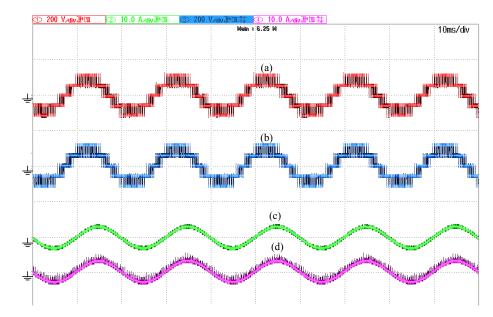

| Figure 3.40. Test Results from RTS of 3 L NPC Inverter Feeding an Unbalanced Load; (a) Line                                   |  |  |

| Voltage ( $V_{RY}$ ) of the Physical Inverter; (b) Line Voltage ( $V_{RY}$ ) of the Virtual Inverter; (c) Line                |  |  |

| Current $(I_R)$ of the Physical Inverter; (d) Line Current $(I_R)$ of Virtual Inverter                                        |  |  |

| Figure 3.41. Test Results from RTS of 3 L NPC Inverter Feeding an Unbalanced Load; (a) Line                                   |  |  |

| Voltage $(V_{RY})$ of the Physical Inverter; (b) Line Voltage $(V_{RY})$ of the Virtual Inverter; (c) Line                    |  |  |

| Current (I <sub>B</sub> ) of the Physical Inverter; (d) Line Current (I <sub>B</sub> ) of Virtual Inverter for $G_{s1}$ =     |  |  |

| $0.0086536$ and $G_{s2} = 0.0043268$                                                                                          |  |  |

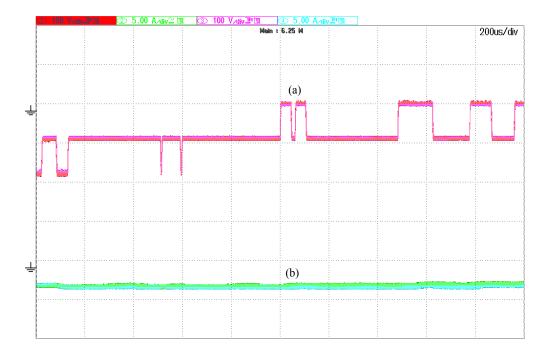

| Figure 3.42. Zoomed in Waveform of the Line Voltage, $V_{RY}$ (a) Physical Inverter and (b) Virtual                           |  |  |

| Inverter                                                                                                                      |  |  |

| Figure 3.43. Zoomed in Waveforms of Line Voltages $(V_{RY})$ of (a) Physical Inverter, (b) Virtual                            |  |  |

| Inverter (c) Line Current $(I_R)$ of the both the Inverters                                                                   |  |  |

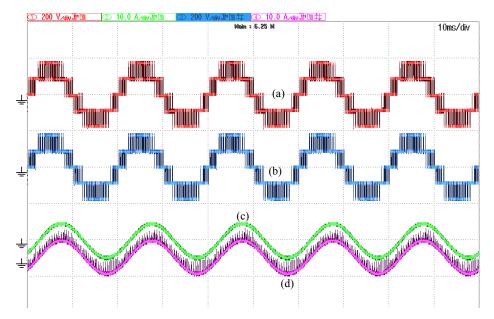

| Figure 3.44. Line Voltage (V <sub>YB</sub> ): (a) Physical Inverter and (b) Virtual Inverter; Line Current (I <sub>Y</sub> ): |  |  |

| (c) Physical Inverter and (d) Virtual Inverter                                                                                |  |  |

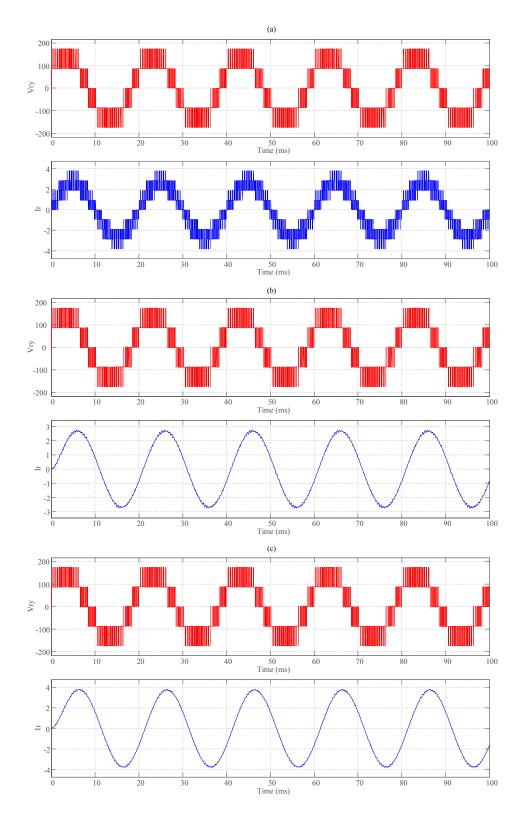

| Figure 3.45. SPS output of Line-Line Voltages $(V_{RY})$ and Line Current $(I_R)$ (a) At Unity Power                          |  |  |

| Factor, (b) At 0.95 Power Factor and (c) At 0.9 Power Factor                                                                  |  |  |

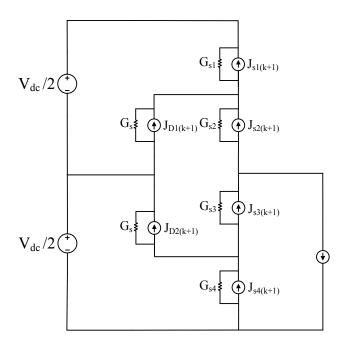

| Figure 4.1. Three-level Inverter Leg with Discrete Switches                                                                   |  |  |

| Figure 4.2. Power Flow in the Inverter Leg with S <sub>1</sub> and S <sub>2</sub> ON                                          |  |  |

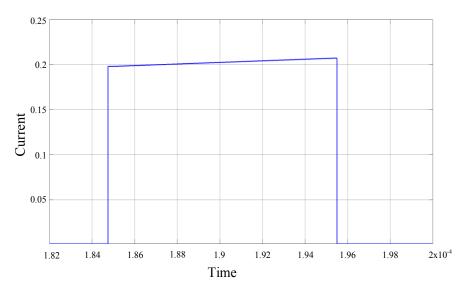

| Figure 4.3. Current in Switch 1 (top outer switch)                                                                            |  |  |

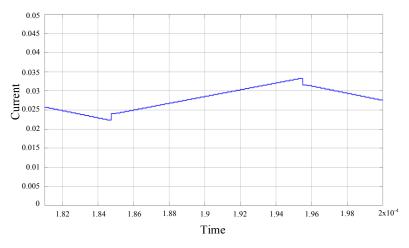

| Figure 4.4. Current in Switch 2 (top inner switch)                                                                            |  |  |

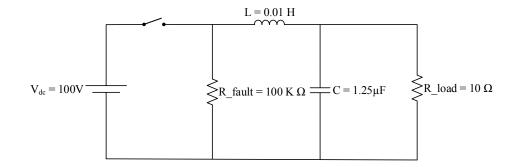

| Figure 4.5. Buck Converter Circuit with an Open Circuited Diode                                                               |  |  |

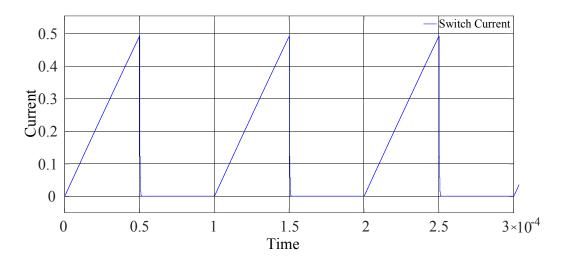

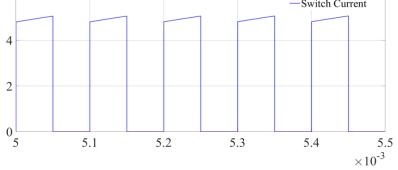

| Figure 4.6. Switch Current in the Buck Converter                                                                              |  |  |

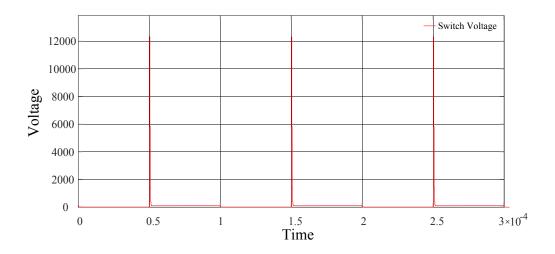

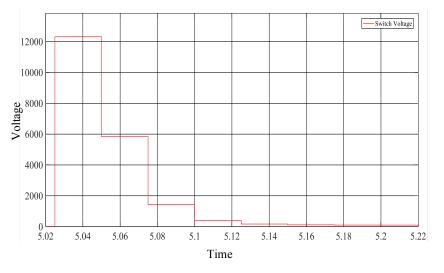

| Figure 4.7. Switch Voltage in the Buck Converter                                                                              |  |  |

| Figure 4.8. Zoomed Switch Voltage in the Buck Converter                                                                       |  |  |

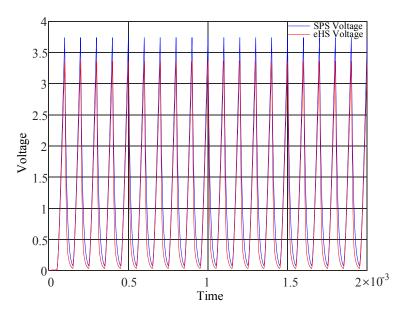

| Figure 4.9. Output of the Buck Converter from the SPS and eHS Solvers                                                         |  |  |

| Figure 4.10. A Buck Converter                                                                                                 |  |  |

| Figure 4.11. Switch Current of a Normal Buck Converter                                                                        |  |  |

| Figure 4.12. Output of the Normal Buck Converter with $G_s = 0.0414$                           | 96     |

|------------------------------------------------------------------------------------------------|--------|

| Figure 4.13. Output of the Normal Buck Converter with $G_s = 0.05$ (Returned by eHS Opti       | mized  |

| Tool)                                                                                          | 97     |

| Figure 4.14. Boost Converter with a Shorted Diode                                              | 98     |

| Figure 4.15. Output of the Boost Converter Using $G_s = 0.458$                                 | 98     |

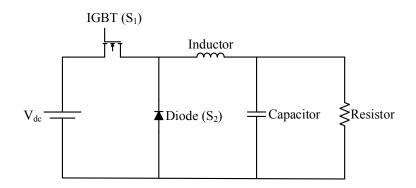

| Figure 4.16. The Buck Converter                                                                | 101    |

| Figure 4.17. The Buck Converter with Discrete Switches                                         | 101    |

| Figure 4.18. The FAMNM Matrix Obtained from the MNA equations                                  | 102    |

| Figure 4.19. Plot of the Eigenvalues Obtained by Varying G <sub>s</sub> in the FAMNM Matrix    | 103    |

| Figure 4.20. Buck Converter with S1 ON and S2 OFF                                              | 104    |

| Figure 4.21. Admittance Matrix of the Buck Converter with S1 ON and S2 OFF                     | 105    |

| Figure 4.22. Buck Converter with S1 OFF and S2 ON                                              | 106    |

| Figure 4.23. Admittance Matrix of the Buck Converter for S1 OFF and S2 ON                      | 107    |

| Figure 4.24. Buck Converter with S1 and S2 ON                                                  | 107    |

| Figure 4.25. Admittance Matrix of the Buck Converter for S <sub>1</sub> and S <sub>2</sub> ON  | 108    |

| Figure 4.26. Buck Converter with S <sub>1</sub> and S <sub>2</sub> OFF                         | 109    |

| Figure 4.27. Admittance Matrix of the Buck Converter for S <sub>1</sub> and S <sub>2</sub> OFF | 110    |

| Figure 4.28. Flow Chart of the Algorithm for Optimizing G <sub>s</sub>                         | 111    |

| Figure 4.29. Plot of the Objective Function                                                    | 112    |

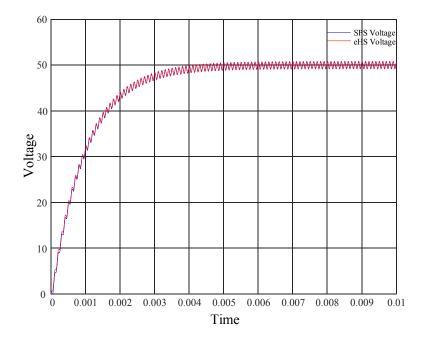

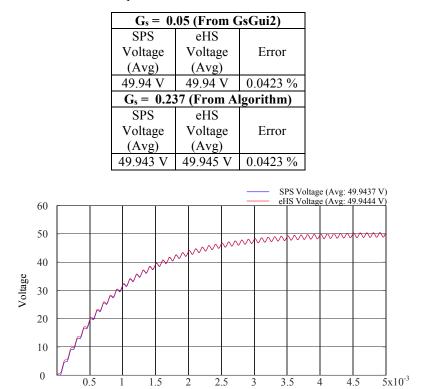

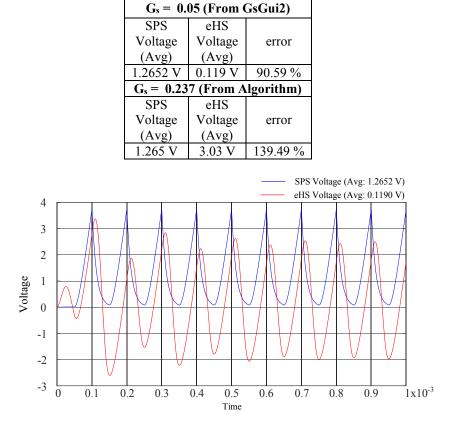

| Figure 4.30. SPS and eHS Output for $Gs = 0.05$ (from GsGui2) in the Normal Buck Cor           | werter |

|                                                                                                | 113    |

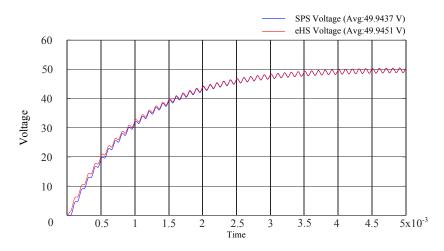

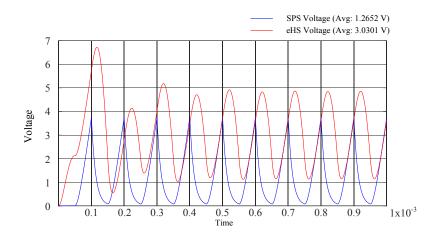

| Figure 4.31. SPS and eHS Output for $Gs = 0.237$ (from the algorithm) in the Normal            | Buck   |

| Converter                                                                                      | 113    |

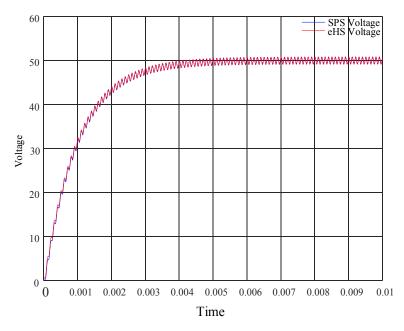

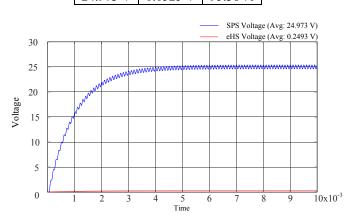

| Figure 4.32. SPS and eHS Output for $G_s = 0.05$ (from GsGui2) in the Buck Converte            | r with |

| Shorted Diode                                                                                  | 114    |

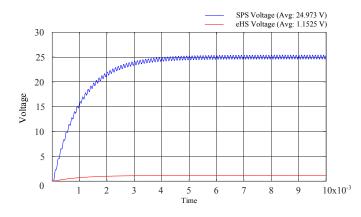

| Figure 4.33. SPS and eHS Output for $G_s = 0.237$ (from Algorithm)                             | 114    |

| Figure 4.34. SPS and eHS Output for $G_s = 0.05$ (from GsGui2) in the Buck Converter with      | Open   |

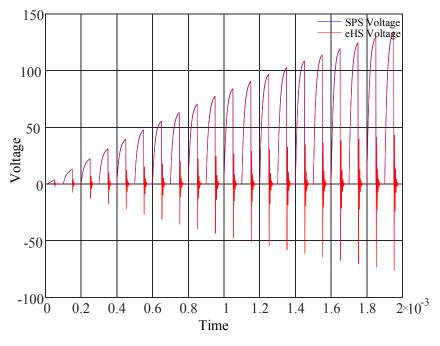

| Diode                                                                                          | 115    |

| Figure 4.35. SPS and eHS Output for $Gs = 0.237$ (from Algorithm) in the Buck Converte         | r with |

| Open Diode                                                                                     | 116    |

| Figure 5.1. The eHS Offline Circuit for the Three-Level Inverter                               | 117    |

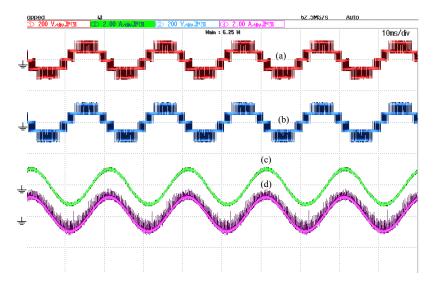

| Figure 5.2. The SPS Bridge of the Three-Level Inverter                                | . 118 |

|---------------------------------------------------------------------------------------|-------|

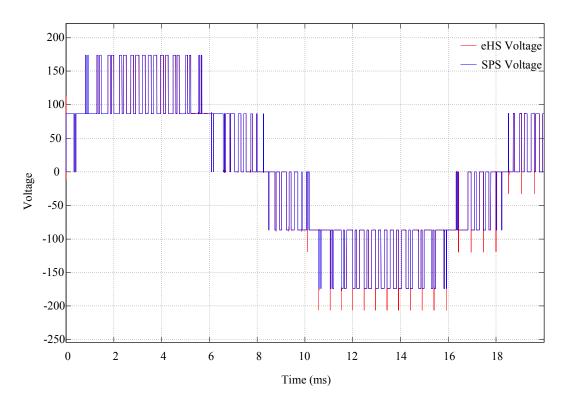

| Figure 5.3. The eHS and SPS Inverter Line Voltage Output Using Gs from GsGui2         | . 120 |

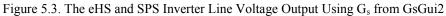

| Figure 5.4. The eHS and SPS Inverter Line-Line Voltage Output Using Modified Gs Calcu | lated |

| from RMS Components                                                                   | . 120 |

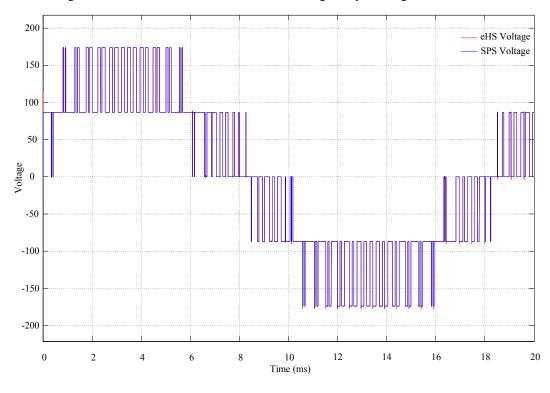

| Figure 5.5. The eHS and SPS Inverter Line-Line Voltage Output, when connected t       | o an  |

| Unbalanced Load                                                                       | . 121 |

### LIST OF ACRONYMS

- KVL Kirchhoff's Voltage Law

- KCL Kirchhoff's Current Law

- AC Alternating Current

- DC Direct Current

- PF Power Factor

- RMS Root mean square

- PWM Pulse Width Modulation

- SPWM Sinusoidal Pulse width modulation

- MNA Modified Nodal Analysis

- FAMNM Fixed Admittance Modified Nodal Analysis Method

- RTS Real-time Simulation

- CPU Central Processing Unit

- FPGA Field-Programmable Gate Array

- DAC Digital to Analogue Converter

- I/O Input/output

- RCP Rapid Control Prototyping

- HIL Hardware in the Loop

- SIL Software in the Loop

- PHIL Power Hardware in the Loop

| DSP     | Digital Signal Processor          |

|---------|-----------------------------------|

| SPS     | Simscape Power Systems            |

| eHS     | Electric Hardware Solver          |

| MLI     | Multilevel Inverter               |

| RTE     | Real-time Events                  |

| NPC     | Neutral Point Clamped             |

| 3 L NPC | Three-level Neutral Point Clamped |

| IGBT    | Insulated Gate Bipolar Transistor |

| HMI     | Human Machine Interface           |

#### INTRODUCTION

The real-time simulation of power electronic systems provides a lot of flexibility in the design and testing process. It also does not require a physical test bench to finalize the design; this can lead to a great reduction in the designing and testing costs. Moreover, the same real-time simulator can be used for the realization of converters with multiple topologies; the tests are repeatable without loss of credibility in the results, as the behavior of the simulator does not change with repetition. The real-time simulations of power electronic converters have some challenges and the primary one being the high switching frequency of the devices. The high switching frequency requires the use of very low sampling times (in the order of nanoseconds) to provide high resolution samples of the switching pulses.

The discrete switch model and the usage of a fixed admittance matrix proposed by Pejovic and Maksimovic in 1994, allows the solution of the system equations within the small time step. The switch conductance parameter, G<sub>s</sub> used in the discrete switch model remains constant during a simulation but, it is critical to obtain an optimized value before the start of the simulation. An improper G<sub>s</sub> would lead to inaccurate simulation results, moreover, this parameter can be dependent upon other factors such as the topology of the converter, connected load etc. which makes the synthesis of an optimized G<sub>s</sub> even more difficult. And although optimization tools such as GsGui2 are available for selecting Gs some scenarios may still need the manual tuning of this parameter. GsGui2 is tool that provides a good-enough value of Gs based on converter's ratings and topology. It is available in the eFPGAsim installer. A two-level inverter had been validated successfully against a physical setup in an earlier work. However, in the presence of faults the Gs values from GsGui2 along with the Loss Compensation Algorithm (LCA) did not work properly, which prompted the use of trial and error methodology to find proper G<sub>s</sub> values. In this thesis, interpretations from the two-level inverter shall be generalized to a three-level inverter and an optimization technique using eigenvalues shall also be explored. This thesis has been divided into six chapters, the first chapter carries out a literature review about trends in realtime simulation, and it also provides an insight to the related work done and provides a glimpse of the work that shall be done in this thesis. The second chapter introduces the switch model that will be used in this work along with the benefits and drawbacks. The third chapter describes the

validation of a three-level inverter in real-time simulation with a physical converter. Chapter four describes methodologies to optimize the critical switch conductance parameter and to enable real-time simulation of circuits with faulty conditions. Chapter five analyses the three-level inverter using the offline simulation block of eHS. Chapter six is the conclusion of the thesis and states the future work that may be done in its continuation.

### **Chapter 1. Literature Review**

#### 1.1 Simulation of power electronic circuits

To simulate a power electronic circuit or any electrical circuit, there are a few procedures that are required to be followed. At first, a mathematical model of the circuit under test is built, and then solvers are chosen to solve those equations [1]. After a proper model is chosen, the mathematical equations for the model can be developed by using either Maxwell's cyclic current, widely known as Kirchhoff's Voltage Law (KVL), nodal analysis or Kirchhoff's Current Law (KCL) or the relatively newer approach called Modified Nodal Analysis (MNA) [2]. Nodal analysis had some advantages over mesh analysis, one being reduced number of equations compared to mesh analysis. But there were difficulties in the use of the classical nodal analysis, particularly in computer simulation; certain elements such as voltage sources, dependent sources, transformers etc. could not be included in the analysis unless some conversion was done to some extent, but on conversion, there was always loss of information about the model [3]. MNA was proposed by Chung-Wen Ho in 1975, to resolve the limitations of the classical nodal analysis. MNA can considerably reduce computation time for solving the network matrices and is easier to implement on a computer, thus making it more suitable for simulation of electrical circuits. Realtime Simulation (RTS) of power electronic circuits demand even faster computation and a slightly different version of MNA called the Fixed Admittance Modified Nodal Analysis Method (FAMNM) [4]-[6] came into use. This method allowed the system equations to be solved in very small time steps as required by RTS of fast switching power electronic converters.

#### **1.2 Real-time Simulation**

A real-time simulation is a type of computer simulation, where a computer model runs at the same pace and produces similar output as the physical system it represents. The virtual representation of physical system i.e. a virtual model runs at the same speed, and for the same time as the physical system. They may share common input variables and come out with comparable output. One good example for a RTS can be operation of the Fuel Injection System of a modern day computer controlled car engine, the onboard computer (Engine Control Unit) calculates the duration of operation and the interval between each operation based upon the

throttle input, camshaft position, dwell time, inputs from Oxygen Sensors, inputs from NOx sensors etc. all of which are measured in real-time.

A computer does all the computations using an operating system which eventually does all of its calculations in the form of 0's and 1's. All the differential equations, state equations or any mathematical functions representing a physical system will converted to a discrete system of 0's and 1's; these will be solved by the computer simulation software using their own solvers. The solvers use different numerical methods to do the computations and each may take different amount of time and produce results with different accuracy.

To work with RTS, the simulation associated would be for discrete time with a constant step size. Variable time-step simulation is not suitable for RTS and hence the time is incremented in equal step sizes called *Simulation Time Steps* and the simulation itself is often called *Fixed Time Simulation*.

As mentioned earlier, the differential equations and the mathematical functions representing the model are solved to perform the input/output (I/O) operations and to obtain the output of the model. However during a 'discrete non real-time simulation' the actual time required to solve the aforementioned equations and functions may be more or less than the simulation time step. But in case of real-time simulation it is necessary that (apart from the precise modeling of the physical system) all the computations are done within the simulation time step, only then the model under test can accurately represent the functioning and perform all the I/O operations as its equivalent real or physical system.

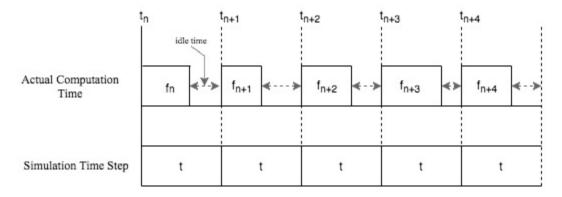

If the computations are not complete within the simulation time step the real-time simulation results are not accurate, which is also referred to as an '*overrun*' and the simulation ceases to be real-time. If the computations are done before the simulation time step is complete, then the remaining time, called the '*idle-time*' [7] is simply lost in case of RTS. This in contrast to the accelerated simulations where the remaining time would be utilized to perform the computations of the subsequent time step. Figure 1.1 to Figure 1.3 distinguishes between the characteristics of a real-time and non-real-time simulations.

|                            | <sup>t</sup> n | t <sub>n+</sub>  | 1                | t <sub>n+2</sub> |                  | t <sub>n+3</sub> | t <sub>n+4</sub> |

|----------------------------|----------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Actual Computation<br>Time | fn             | f <sub>n+1</sub> | f <sub>n+2</sub> | f <sub>n+3</sub> | f <sub>n+4</sub> |                  |                  |

|                            |                |                  |                  |                  |                  |                  |                  |

| Simulation Time Step       | t              |                  | t                |                  | t                | t                | ť                |

Figure 1.1. Timing Diagram when Computation Time is less than Simulation Time Step (non-real-time)

|                            | t <sub>n</sub> | t <sub>n+1</sub> | t <sub>n+2</sub> | t <sub>n+3</sub> | t <sub>n+4</sub> |

|----------------------------|----------------|------------------|------------------|------------------|------------------|

| Actual Computation<br>Time | fn             | fn               | H+1              | f <sub>n+2</sub> | f <sub>n+3</sub> |

| Simulation Time Step       | t              | t                | t                | t                | t                |

Figure 1.2. Timing Diagram when Computation Time is greater than Simulation Time Step (non-real-time)

Figure 1.3. Timing Diagram during Real-time Simulation

#### 1.3 Selection of the real-time simulator

As suggested in [7]-[11] selection of real-time simulators can be done based upon the applications to which they are intended for and can be categorized as:

#### Rapid Control Prototyping (RCP):

In a Rapid Control Prototyping a physical setup is always used and the controller is implemented in a real-time simulator. The presence of a virtual controller enables it to be configured with more flexibility and be debugged easily. Since the modelling and testing of the controller becomes easy and fast, the prototype model of the controller can be developed sooner to a final robust product.

#### Hardware in the Loop (HIL):

In Hardware in the Loop a virtual model is run on a real-time simulator, this virtual model emulates and behaves like a physical test bench; the virtual model is then controlled by a physical controller. In a variation of HIL, another real-time simulator can function as a physical controller and feed the virtual model in a separate simulator. This configuration is very beneficial because the controller can be tested even without a physical setup, the tests are very repeatable and can be done without any fear of damage, in contrast to a real hardware based setup. The work in this literature uses Hardware in the Loop (HIL) simulation.

#### Software in the Loop (SIL):

Software in the Loop is possible as the simulators grow more and more powerful. This allows the controller and the virtual plant model to be implemented in the same real-time simulator. Here, no physical input/outputs are used and that ensures that the fidelity of the signals is maintained. Moreover, the simulations can now run only in the virtual mode and there are no constraints in following the time clock of the real world. Simulation can now take their own time and if resources are available simulations can run faster than the real world time while maintaining the integrity of the results.

#### 1.4 CPU and FPGA Based Simulation

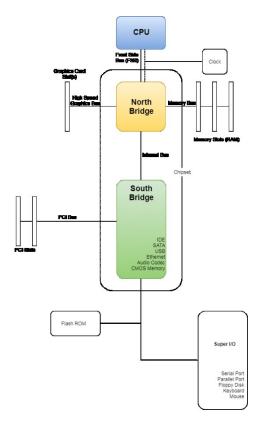

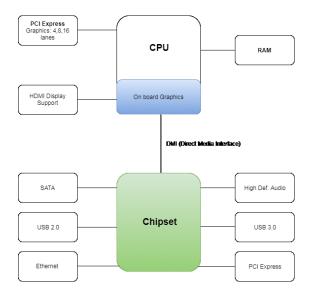

The computer architecture has changed a lot in the last two decades, the advent of multiple cores, increase in parallel processing capabilities, decrease in the I/O latencies, faster working memories and improved hardware interfaces have made the modern computer quite suitable for real-time simulations. Figure 1.4 shows an Intel chipset architecture widely used until 2011 [12], Figure 1.5 shows an architecture used currently in most modern computers [13].

Figure 1.4. Computer chipset architecture prevalent before Sandy Bridge microarchitecture introduced in 2011

Figure 1.5. Modern computer chipset using Nehalem microarchitecture

However, even though the CPU of a modern computer has a very high clock frequency, the sequential nature of the operating system and the latencies still present at the I/O communications, allows it to have a minimal sampling time of about 5-10 $\mu$ s. This sampling time

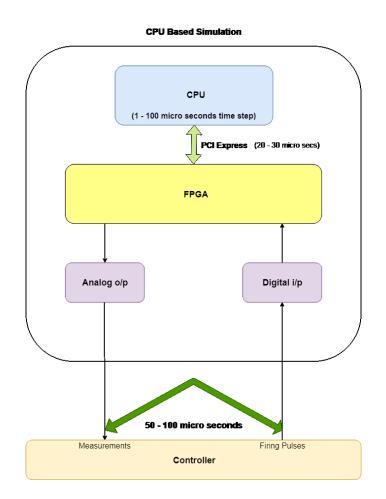

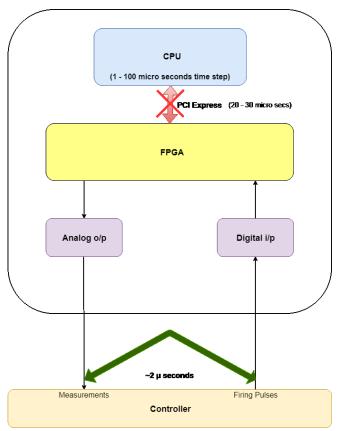

is often enough for the real-time simulation of systems with slower dynamics such as a motor, but for fast systems like the high frequency switches in the power electronic systems, this sampling rate is inadequate. So, a methodology was developed wherein the models requiring very low sampling times are simulated in Field Programmable Gate Arrays (FPGAs) [14] - [16], the highly parallel structure of the FPGA allowed very high sampling rates with simulation time steps as low as 250ns. Figure 1.6 shows a CPU based simulation and Figure 1.7 shows a FPGA based simulation.

Figure 1.6. CPU Based Simulation

Figure 1.7. FPGA Based Simulation

#### 1.5 Discrete Time Switch Model in Real-time Simulation

There are a number of models for representing a switch in order to make it suitable for computer simulations. Some simulators model the switch as a small resistance when it is ON and a large resistance when it is OFF [5], the value of the ON and OFF resistances are updated at every step of the iteration in the numerical method used for the simulation [5]. The trouble with this approach is that for a large network with a number of switches, huge amount of computational resources may be consumed for updating the resistance parameters at every step of the simulation. To cope with that, some real-time solvers achieve a precomputation of these matrices and store them in memory. Then, at every time-step, the corresponding matrix is used to solve the circuit. That is the case with ARTEMIS and Simscape Power Systems (SPS) SPS/SSM solvers. Due to memory limitations the number of switches will be limited consequently. In [17] a model with a RC circuit is proposed for an open circuit and an inductor for a short circuit, this representation removes the need of a system matrix inversion when the switch state changes

from ON to OFF or OFF to ON. Another model proposed in [18], represents the switch as a resistance across a capacitance, when the switch turns ON this resistance goes low and goes high when it is turned OFF.

In the switch model mentioned in [5] an ideal switch is modelled as a conductance in parallel with a current source. This conductance will not change with the iteration steps and the current source shall provide details of the state of the switch. The work in this thesis shall consider this model for real-time simulation.

#### **1.6 Validation of Power Electronic Circuits**

Validation of power electronic systems is necessary to ensure that a virtual model behaves like a real physical system to the extent possible. Real-time simulation of fast switching power electronic converters using a FPGA based Electric Hardware Solver (eHS) [8] is discussed in [16]. The design flow for the solver as well as validation results of the RTS of a number of power electronic converters are also covered. The results were validated by comparing the output of the eHS with those from the variable step Ode 23tb (stiff) solver in Simulink. This thesis will also utilize this Simulink solver as the benchmark. Some of the shortcomings of this method of simulating fast switching devices have also been discussed. Notwithstanding the shortcomings, the technique of performing real-time simulation of power electronic systems in FPGAs has a lot of potential. [7]

#### **1.7 Multilevel Inverters**

An introduction to the different topologies and working principles of multilevel converters are covered in [19], [20]. A more detailed overview about Neutral Point Converter (NPC) based inverters along with the modulation techniques is provided in [21]. Different modulation schemes for a three-level inverter are introduced in [22]. A comprehensive working of the three-level NPC inverter is discussed in [23] and [24], this will also be covered in detail in the Chapter 3 along with a step by step procedure in the hardware validation of the same. The results obtained from the simulation of a three-phase three-level inverter in SimScape Power Systems (SPS), a FPGA based eHS and the physical converter shall be compared. Furthermore, few

techniques for optimizing the switch conductance for the Pejovic discrete time switch model shall be discussed in more details in Chapter 4.

#### **1.8 Conclusion**

A brief introduction to circuit simulation and real-time simulation of power electronic converters is provided in this chapter. The chapter introduces some of the current trends in real-time simulation and also familiarizes the reader with the basics of RTS. The chapter also introduces some switch models which are often used in the RTS of electrical systems. Certain constraints in the RTS of power electronic systems are also discussed, this chapter also reckons with related work done by other researchers and gives a glimpse of the work that shall be done to complete this thesis.

### **Chapter 2. Switch Model in Real-Time Simulation**

#### 2.1 Switch Model in Real-time Simulation:

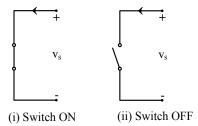

An ideal switch has been shown in Figure 2.1, it is a single pole switch with a single throw. The switch offers just two states either ON or OFF, the truth table is provided in Table 1.

Figure 2.1. Ideal Switch

Table 1. Table of the Switch State and Boolean Value

| Switch State | <b>Boolean Value</b> |  |  |  |

|--------------|----------------------|--|--|--|

| ON           | 1                    |  |  |  |

| OFF          | 0                    |  |  |  |

In an ideal switch, the change of state happens without any delay, moreover for controlled switches, which depend upon an external signal for the change of state to happen, a function can also be assigned that would govern the operation of the switch. This function is referred to as a switching function [5]. However, this function is not relevant to uncontrolled switches such as diodes, as their operation would not be dependent upon any control element outside the switch. In addition to this, the switch state can also be a function of the switch voltage or current.

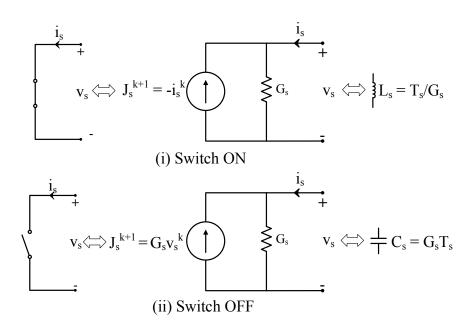

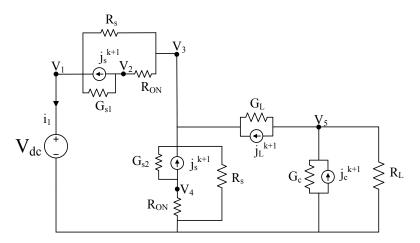

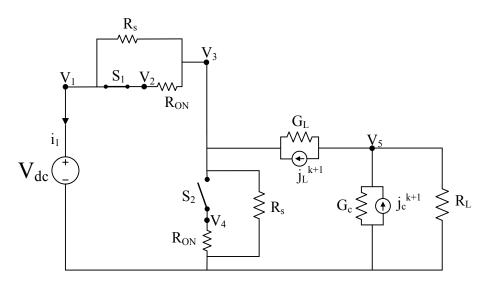

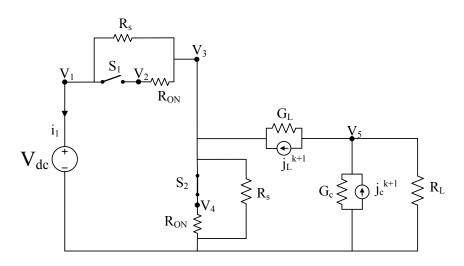

To enable computer simulation of an ideal switch, an approximate discrete time switch model was developed. The model contains a conductance parameter, also known as Switch Conductance ( $G_s$ ) in parallel to a current source as shown in Figure 2. 2. This representation of the discrete switch does resemble the equivalent circuit of a voltage controlled nonlinear resistor. When modified nodal analysis of the network containing the switches is done, the resultant system matrix will contain this  $G_s$  parameter. In a given simulation step the solution of the nodal equations would provide the output of the network and the  $G_s$  is updated after the iteration is over, inversion of the system matrix is done at every simulation step with an updated  $G_s$  value.

But this requires a lot of computational resource and time. To hasten the speed and increase efficiency of the simulation the switch conductance parameter ( $G_s$ ) is kept constant, this implies that the system matrix would also contain the constant  $G_s$  value, which shall not be updated in the subsequent iterations. And since  $G_s$  is no longer updated in every simulation step, the system matrix inversion required for solving the network need not be done for every iteration and thus, can be done away with by just doing it once at the initialization of the simulation. This step is crucial considering that during RTS, the simulator must arrive with the solutions of the network within a given time step and failing to do so would result in an "overrun" or produce unreliable results.

Figure 2.2. Discrete Switch Model of an (i) ON Ideal Switch and (ii) OFF Ideal Switch

As the G<sub>s</sub> would remain constant and bear no burden in identifying the switch state, it is the current source,  $j_s^{k+}$ , l that indicates the state of the switch. It is to be reckoned that this  $j_s^{k+1}$ , is not a part of the system matrix that was discussed a little while earlier. In contrast to the model of the ideal switch, the current source,  $j_s^{k+1}$  in the discrete switch model is dependent upon the current and voltage parameters obtained in the previous iteration. If the present simulation step is k+1 and previous step is k, the state of the current source is given by (2.1):

$$j_{s}^{k+1} = \begin{cases} -i_{s}^{k+1}, \text{ when switch is ON} \\ G_{s}v_{s}^{k+1}, \text{ when switch is OFF} \end{cases}$$

(2.1)

But for the computation of  $j_s^{k+l}$ , it is necessary that it should be dependent upon known parameters or signals and in this case, the values of current and voltage from the previous simulation step are known. If a simulation step ( $T_s = t^{k+l} - t^k$ ) is chosen such that current and voltage in the present simulation step is approximately the same as that of the previous step, i.e.  $i_s^{k+l} \cong i_s^k$  and  $v_s^{k+l} \cong v_s$ , then the state of the current source can be re-written as:

$$j_{s}^{k+1} = \begin{cases} -i_{s}^{k}, \text{ when switch is ON} \\ G_{s}v_{s}^{k}, \text{ when switch is OFF} \end{cases}$$

(2.2)

Now, the computation of  $j_s^{k+1}$  is possible since it is dependent upon known values of current and voltages obtained from an earlier simulation step. This however, leads to an approximation in the discrete switch model representation of an ideal switch.

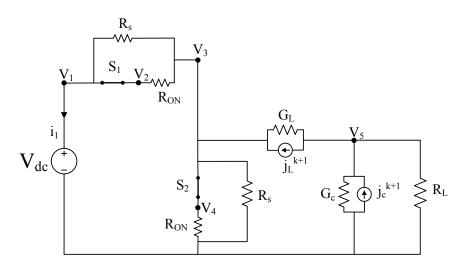

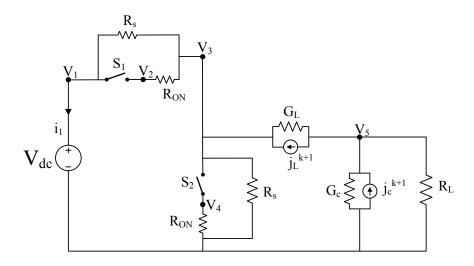

Moreover, the discrete switch model is also similar to the discrete time model of an inductor or a capacitor, but the switch conductance  $G_s$ , shall be replaced by  $G_L$  (in case of inductor) and  $G_c$  (in case of capacitor). The equivalent current sources shall be represented by  $j_L$  and  $j_c$ respectively. Comparing all the discrete time models (switch, inductor and capacitor) it can be inferred that switch state can be indicated by a small inductance when turned ON and a small capacitance when turned OFF. Since the switch conductance has to be kept constant throughout the simulation the following equality is achieved:

$$G_s = G_L = G_c = \frac{C_s}{T_s} = \frac{T_s}{L_s}$$

(2.3)

#### 2.2 Real-time Simulation of Power Electronic Converters:

In case of Power Hardware in the Loop (PHIL) with power electronic converters, it becomes necessary to use fixed-step non iterative solvers. This is because the power converter may comprise of many switches and whose switching frequencies can be high in comparison to the sampling frequency of a real-time simulator. Moreover, the differential equations that represent the power electronic system are often very large and thereby difficult to simulate within a small time step. [25] Mentions a suitable time step in the range of 25-30µs for a 1 KHz PWM frequency, i.e. the simulations have to be completed within the 25-30µs range.

The typical sampling time available from Central Processing Units (CPUs) is in the range of 5-10µs and 5-10ns when FPGA is used. The CPU however, allows the computation of complex algorithms and solvers, whose compilation can be done in minutes in contrast to FPGAs, which only allows the implementation of much simpler ones. The compilation time taken by the FPGAs to get one 'bit stream' which configures the I/O ports can be in hours. Thus a combination of both CPU and FPGA technologies are used to achieve the real-time simulation of a power electronic system, high resolution samples of gate switching of a power electronic converter can be captured by the fast sampling FPGA and the averaged information can be provided to the CPU side for interpretation and make the results available to the user. [16], [25].

The minimum time step possible in a CPU without any I/O or external dependencies can be in the range of 1-100µs (7µs in case of OPAL-RT OP4510). Because of sequential operations involved in the processing in a CPU, sampling time is still high despite of the CPU's very high clock frequencies (>3 GHz for modern CPU's), improved parallel processing capabilities and lower I/O latencies. In contrast to the CPU, a FPGA has a clock frequency in the range of a few hundreds of MHz, but by means of parallel processing with logic blocks, very low sampling time can be achieved (5 - 400ns) which again can provide very high resolution samples of the gating pulses (50 - 100KHz). The total latency including I/Os in case of FPGA can also be as low as 2.5µs. This high speed capability allows the user to simulate on board switching device protections, such as  $V_{ce}$  short circuit protections. Very high sampling frequencies can also be achieved in FPGAs because the I/O ports are placed very close to the FPGA and the latencies are very low, moreover, the ADC/DAC's can be modelled on the FPGA itself. [16], [25], [26]

#### 2.3 The need of Fixed Admittance Matrix Nodal Method:

As discussed in the earlier sections, an approximate discrete time model is used to represent an ideal switch for the purpose of simulation. A small inductance indicates the ON-State and a small capacitance indicates the OFF-State of the switch. The discrete switch model can be further represented by an equivalent conductance ( $G_s$ ) in parallel to a current source ( $j_s^{k+1}$ ). Some simulators use this model to represent an ideal switch, however the parameter  $G_s$  is updated in each iteration which is again burdensome to the computational resources and cannot be used in RTS of switches, meant for fast switching power electronic converters. Thus, another approach was formulated which enables the parameter,  $G_s$  to be kept fixed and the value of the current source  $(j_s^{k+1})$ , also referred to a 'history term', is changed in accordance to the state of the switch. Modified nodal analysis can be used to formulate the circuit elements. The current source is not a part of the system admittance matrix, and is contained in the vector of the unknown independent sources. The fixed admittance matrix obtained from MNA, with a constant  $G_s$  is the basis of the FAMNM. This approach with the fixed admittance matrix, inverts the system matrix, say 'A' only once at the start of the simulation. This inverted matrix 'A<sup>-1</sup>' is then multiplied with the vector 'y' containing the known sources which also includes the current sources or the memory elements of the discrete switch model [5]. If 'x' is the vector containing the nodal voltages and currents then during a current simulation step 'k+1' the network or the circuit can be solved as (2.4):

$$x^{k+1} = A^{-1} y^{k+1} \tag{2.4}$$

#### 2.4 Limitations of Pejovic Switch Model

There are a few limitations of the Pejovic switch model which can cause simulation inaccuracies, they are:

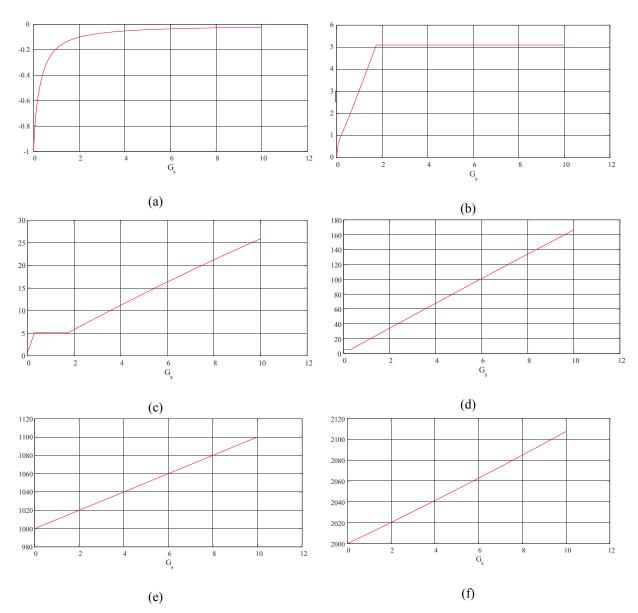

Artificial losses during switch commutation: In the discrete time switch model an ideal switch can be modelled as an inductor when it is ON, and a capacitor when it is OFF. If there is a change of state of the switch in between the simulation steps k and k+1 from ON to OFF, the inductor is replaced by a capacitor. The energy stored in the inductor when the switch was ON is  $0.5L_s(i_s^{k-1})^2$ , where  $L_s$  is the inductance when the switch is modelled as an inductor, and  $i_s^{k-1}$  is the current flowing through the switch in an earlier simulation step. But, when the switch turns OFF, say at  $k+1^{th}$  simulation step the switch is now modelled as a capacitor and the state of the memory element is  $j_s^{k+1} = G_s V_s^k$ , where  $V_s^k$  is the switch voltage in the  $k^{th}$  simulation step i.e. when the switch was still ON, hence  $V_s^k = 0$ . The energy now stored in the capacitor is  $0.5C_s(V_s^k)$ ,<sup>2</sup> which is equal to zero, so during the state change from ON to OFF an energized inductor was replaced by a capacitor without any charge and hence, the energy that was stored in the inductor is lost; this is also true when the reverse happens when the switch state changes from OFF to ON. These artificial losses during the state changes can cause errors in the simulation results [26]. Need of proper optimization: It is important to properly optimize the value of  $G_s$ , a small value would mean that for a given time step ( $T_s$ ) equivalent inductance ( $L_s = T_s/G_s$ ) is large and capacitance ( $C_s = T_sG_s$ ) is small. A large  $L_s$  will act as a high reactance when a high switching frequency is applied and so will a low  $C_s$ ; this high reactance will allow lesser power to flow through the switch. Similarly when a high  $G_s$  value is used, more power can flow through the switch. Thus,  $G_s$  can influence the power flow in the circuit and an improper selection can produce an erroneous output, moreover, when a circuit is more complex with a greater number of switches, predicting a proper  $G_s$  becomes more difficult. [26]

#### 2.5 Conclusion

A discrete time switch model is introduced in this chapter. This model shall be used in the real-time simulation of power electronic converters throughout this thesis. There are other approaches and different switch models as well; however, this model is one of the most widely used. The chapter also discusses about the FAMNM approach and its need in RTS. Finally some limitations of the discrete switch model are elaborated.

# **Chapter 3. Real-Time Simulation of a Three-Level NPC Inverter**

## **3.1 Introduction to Multilevel Inverters**

Multilevel Inverter (MLI) topologies can be broadly classified into three categories [19], [20], [23]:

- 1. Diode Clamped Multilevel Inverter

- 2. Flying Capacitor Multilevel Inverter

- 3. Cascaded Inverter with Separate DC Sources

## **Diode Clamped Multilevel Inverter:**

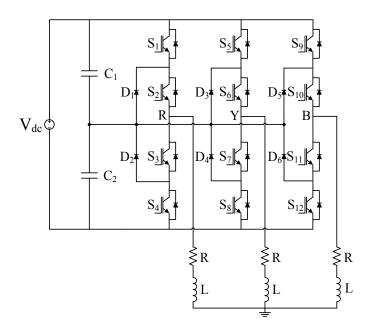

The diode clamped inverter was first proposed by Nabae Et Al in 1981, this topology consists of a DC bus whose voltage levels are subdivided into smaller ones by means of capacitors. The maximum number of voltage levels so obtained are n+1, where n is the number of capacitors. The point where the capacitors meet is clamped by diodes and hence the name diode clamped multilevel inverter. The point where the first two top switches connect, is joined by the cathode of the first clamping diode and the anode of the diode is connected to the meeting point of the first two capacitors; this is done for the remaining clamping diodes of the higher side (i.e. for all the switches connected above the DC bus midpoint). The first clamping diode of the lower side (i.e. for all the switches connected in between the first two switches just below the DC bus midpoint and the cathode is connected to the corresponding elements. The output pole voltage levels so obtained are:  $0, +/-V_{dc}/n, +/-2V_{dc}/n, +/-3V_{dc}/n, \dots$  (n - 1) $V_{dc}/n$

As the number of levels increase the output waveform would have lesser harmonic distortion in the output voltage and current. Figure 3.1 shows a three-level diode clamped inverter.

Figure 3.1. Circuit Diagram of a Three-phase Three-level NPC Inverter

## **Flying Capacitor Multilevel Inverter:**

The flying capacitor or the capacitor clamped inverter is quite similar to the diode clamped inverter but the clamping diodes are replaced by capacitors. The capacitor voltages can be regulated to control the output voltages. The switches can be controlled to charge or discharge the clamping capacitors and thereby the output voltage can be balanced. The switching states available in this topology is higher when compared to diode clamped inverter, the capacitors can also have different ratings depending upon their position in the legs. The inverter also allows control of active and reactive power flow but the requirement of large number of capacitors can make the inverter very bulky and expensive. The control of the inverter is more complex compared to NPC, the switch utilization and efficiency is poorer. [20]

## **Cascaded Inverter with Separate DC Sources:**

In a cascaded multilevel inverter, cells of single phase full bridge inverter are arranged in a cascaded manner to obtain a multilevel phase leg to produce the desired staircase AC voltage waveform. A single phase full bridge inverter produces a three-level voltage output i.e. if the source voltage is  $V_{dc}$  the output from one cell would be  $+V_{dc}$ , 0 &  $-V_{dc}$ . More levels are obtained by stacking these cells together in series, this uniformity makes this topology easy to design and

fabricate. This topology also uses the least number of power components among other MLI's but the need of isolated and separate DC power sources is a major shortcoming. [20]

#### 3.2 Working of the Three-level NPC Inverter

The three-level inverter is the lowest number of voltage levels achieved amongst multilevel inverters. A three-level inverter produces three voltage levels by connecting the AC output either to  $+0.5 V_{dc}$ ,  $-0.5V_{dc}$  or  $0 V_{dc}$ . This is in contrast to a two-level inverter where the output voltage is produced by connecting the AC side just to the  $+0.5V_{dc}$  and  $-0.5V_{dc}$  of the DC link. Owing to the availability of a third voltage level, the output voltage waveform so obtained is closer to the sinusoidal waveform desired [24], [28]. This results in a significant reduction in the Total Harmonic Distortion (THD) levels of current and lesser filtering requirements as well as lower losses in the filter. For the same THD specifications the switches can be operated at lower frequency thus resulting in lower switching losses.

The diode clamped multilevel inverter can be again classified into two sub-categories:

- 1. Three-Level NPC (also NPC 1), see Figure 3.9

- 2. Three-Level TNPC (also NPC 2), see Figure 3.8

In a two-level inverter the DC bus midpoint '0 V' may or may not be available physically, this midpoint is available halfway between the DC buses usually formed by a voltage divider with two capacitors connected in series. The operation in a leg of a two-level inverter can be realized with the functioning of a single pole switch with two throws. The switch can connect to the positive DC bus or the negative DC bus and there is no intermediate state in between. The voltage between the pole and the midpoint is half of that of the DC voltage, i.e. for a DC bus voltage of V<sub>dc</sub> then the pole voltage would be  $V_{dc} / 2$ . So, when a pole say 'R', can have either  $V_{RO} = +V_{dc} / 2$  when it is connected to the top positive bus or  $V_{RO} = -V_{dc} / 2$ , when connected to the bottom DC bus. This availability of the two voltages with opposite polarity at the pole of the switch gives it the name of two-level inverter.

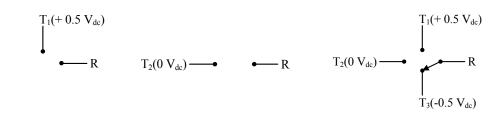

For a three-level inverter however, the DC neutral or the DC bus midpoint is available for connection. This can be evaluated by considering one leg of the three-level inverter and applying a similar analogy to that of a two-level inverter, but with a single pole three throw switch instead of two throws in between a DC bus. Understanding the switch realization of the three-level

inverter as discussed in [28] can be very useful in the real-time simulation work that will be done in the coming sections. The three throw switch can now connect to the top DC bus, the DC midpoint and the bottom DC bus. The voltage between the pole and the DC bus would again be half the DC bus voltage. For a DC bus voltage  $V_{dc}$ , the pole voltage with respect to the DC bus midpoint would be  $V_{dc}$  / 2. So when a pole 'R' is connected to the top DC bus the pole voltage  $V_{RO} = + V_{dc}$  / 2, when it is connected to DC bus midpoint, the pole voltage  $V_{RO} = 0$  and finally when the pole is connected to the bottom DC bus the pole voltage  $V_{RO} = - V_{dc}$  / 2. The availability of these three voltage levels at the pole gives it the name three-level inverter. [24], [28]

There are some additional requirements that the switches have to meet and enable the threelevel inverter to function properly. The switches should be able to let the current flow both ways and all the while should also be able to maintain the load voltage, notwithstanding the direction of current [28]-[30]. Moreover, for a three-phase inverter three such legs shall be required and each leg shall produce output voltages which are electrically apart by 120°.

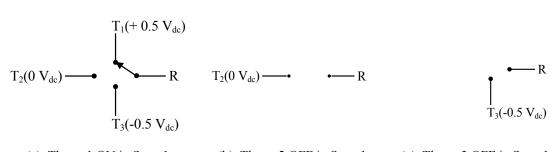

To get the switch realization in a single leg of a three-level inverter, a single pole switch with three throws is chosen with a pole 'R' and throws 'T<sub>1</sub>', 'T<sub>2</sub>' and 'T<sub>3</sub>' and the following three states are possible:

#### State 1: When the pole is connected to the top bus i.e. 'R' connected to T<sub>1</sub>

The current should be able to flow from 'R' to  $T_1$  and vice versa, the pole is not connected to the other throws and the switches which establish this must allow the aforementioned flow of current and block the voltages between the open throws. Table 2 below provides the details of state of the switches between the pole and the throws, and the blocking voltages to be endured.

| Switch (between pole and throw) | State  | Voltage to be blocked |

|---------------------------------|--------|-----------------------|

| R - T <sub>1</sub>              | Closed | 0                     |

| R - T <sub>2</sub>              | Open   | 0.5 V <sub>dc</sub>   |

| R - T <sub>3</sub>              | Open   | $V_{dc}$              |

Table 2. Voltage Blocked by the Top Throw Switch

State 2: When the pole is connected to the DC bus midpoint i.e. 'R' connected to T<sub>2</sub>

The current should be able to flow from 'R' to  $T_2$  and vice versa, the pole is yet again not connected to the remaining two poles. Table 3 below provides the details of the state of the switches between the pole and the throws and the blocking voltages to be endured in State 2.

| Switch (between pole and throw) | State  | Voltage to be blocked |

|---------------------------------|--------|-----------------------|

| R - T <sub>1</sub>              | Open   | 0.5 V <sub>dc</sub>   |

| <b>R</b> - T <sub>2</sub>       | Closed | 0                     |

| R - T <sub>3</sub>              | Open   | 0.5V <sub>dc</sub>    |

Table 3. Voltage Blocked by the Middle Throw Switch

# State 3: When the pole is connected to the bottom DC bus i.e. 'R' connected to T<sub>3</sub>

The current should be able to flow from 'R' to  $T_3$  and vice versa, the remaining two poles are not connected. Table 4 below provides the details of the state of the switches between the pole and the throws and the blocking voltages to be endured in State 3.

| Switch (between pole and throw) | State  | Voltage to be blocked |

|---------------------------------|--------|-----------------------|

| R - T <sub>1</sub>              | Open   | $V_{dc}$              |

| R - T <sub>2</sub>              | Open   | $0.5 \; V_{dc}$       |

| R - T <sub>3</sub>              | Closed | 0                     |

Table 4. Voltage Blocked by the Bottom Throw Switch

Combining all the three states obtained earlier and obtaining the equivalent electronic switches for State 1 as shown in Figure 3.2.

(a). Throw 1 ON in State 1 (b). Throw 2 OFF in State 1 (c). Throw 3 OFF in State 1

Figure 3.2. State of the Switch with Pole Connected to the Top DC Bus

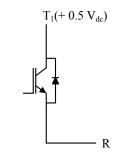

So the equivalent electronic switch for throw  $T_1$  must allow bidirectional current flow through it and must block a maximum voltage of  $V_{dc}$ . The switch that can be established shall be a transistor with an antiparallel diode rated at  $V_{dc}$  as shown in Figure 3.3.

Figure 3.3. Equivalent Electronic Switch for Throw T<sub>1</sub>

Combining all the three states obtained earlier and obtaining the equivalent electronic switches for State 2 as shown in Figure 3.4.

(a). Throw  $T_1$  OFF in State 2 (b). Throw  $T_2$  ON in State 2 (c). Throw  $T_3$  OFF in State 2

Figure 3.4. State of the Switch with Pole Connected to the Midpoint of the DC Bus

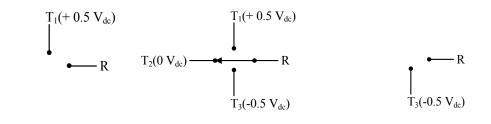

The equivalent electronic switch for throw  $T_2$  must allow bidirectional current flow through it and must block a maximum voltage of  $0.5V_{dc}$ . The switch that can be established shall be a four quadrant switch comprising of two antiparallel transistors with series diodes rated at  $0.5V_{dc}$  as shown in Figure 3.5.

Figure 3.5. Equivalent Electronic Switch for Throw T<sub>2</sub>

Combining all the three states obtained earlier and obtaining the equivalent electronic switches for State 3 as shown in Figure 3.6.

(a). Throw 1 OFF in State 3

(b). Throw 2 OFF in State 3

(c). Throw 3 ON in State 3

Figure 3.6. State of the Switch with Pole Connected to the Top DC Bus

The equivalent electronic switch for throw  $T_3$  must allow bidirectional current flow through it and must block a maximum voltage of  $V_{dc}$ . The switch that can be established shall be a transistor with an antiparallel diode rated at  $V_{dc}$  as shown in Figure 3.7.

Figure 3.7. Electronic Switch for Throw T<sub>3</sub>

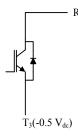

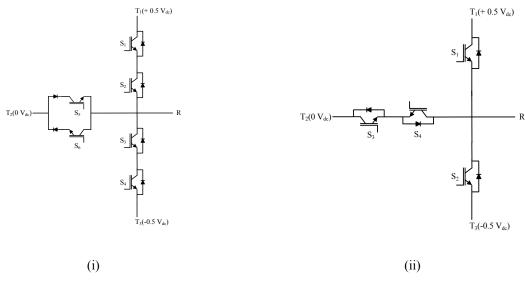

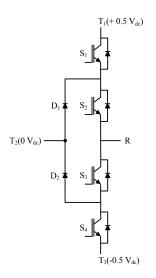

The derived configuration combining all the equivalent switches is close to the three-level TNPC topology, this configuration however, has switches with different blocking voltages, and this can be further modified to have a topology where the switches have similar blocking voltages as shown in Figure 3.8 (i), the 3L TNPC topology is shown in Figure 3.8 (i). The basis for this derivation is that, when the pole 'R' is connected to the throw 'T<sub>1</sub>' the two switches S<sub>1</sub> & S<sub>2</sub> have to be turned ON together, but when the throw has to be disconnected either S<sub>1</sub> or S<sub>2</sub> can be turned OFF. At this state, the switches between 'R' and throw 'T<sub>2</sub>' has to block a voltage of  $0.5V_{dc}$ , similarly the switches S<sub>3</sub> and S<sub>4</sub> block the DC bus voltage V<sub>dc</sub> together. The blocking voltage for each switch in this configuration is 0.5 V<sub>dc</sub>.

Figure 3.8. (i) Derived configuration and (ii) 3L TNPC topology

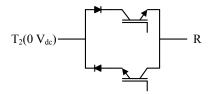

Another redundancy would remain in the circuit, which can be seen when  $S_1 \& S_2$  are ON (i.e when Pole 'R' is connected to throw 'T<sub>1</sub>'), the voltage between pole 'R' and throw 'T<sub>2</sub>' is blocked by the diode in series of  $S_5$ . This scenario can be repeated if the pole 'R' is connected to the throw 'T<sub>3</sub>', where again only the diode in series with  $S_5$  will block the voltage. Moreover, to isolate throw T<sub>1</sub> from the pole,  $S_2$  can be opened instead of both  $S_1$  and  $S_2$ , similarly T<sub>2</sub> can be isolated just by opening  $S_3$ . Thus the circuit can be reduced further, and  $S_5$ ,  $S_6$  can be removed. The following circuit in Figure 3.9 achieves the final reduction in the redundancy and works the same as the earlier circuit.

Figure 3.9. Single Leg of a NPC Inverter

From the switch status given in Table 5, it can be seen that the switches  $S_1 \& S_3$  are never ON together, again  $S_2 \& S_4$  are never ON together so the combinations  $S_1 \& S_2$ ,  $S_3 \& S_4$  are always complementary. It is also observed that for every pole and throws connection  $S_2$  and  $S_3$  switches are involved, meaning that they are ON for a longer duration than  $S_1$  and  $S_4$ , which would also imply that there are more losses in  $S_2$  and  $S_3$ . [28]

| Connection (Pole and Throw) | Switch Status (ON)                 | Switch Status (OFF)                 |

|-----------------------------|------------------------------------|-------------------------------------|

| Pole 'R' to 'T1'            | S <sub>1</sub> & S <sub>2</sub> ON | S <sub>3</sub> & S <sub>4</sub> OFF |

| Pole 'R' to 'T2'            | S <sub>2</sub> & S <sub>3</sub> ON | S1 & S4 OFF                         |

| Pole 'R' to 'T3'            | S <sub>3</sub> & S <sub>4</sub> ON | S1 & S2 OFF                         |

Table 5. Complementary Behavior of the Switches

| $S_1$ | $S_2$ | <b>S</b> <sub>3</sub> | <b>S</b> 4 | Pole Voltage (VRO)              |

|-------|-------|-----------------------|------------|---------------------------------|

| 1     | 1     | 0                     | 0          | +0.5 V <sub>dc</sub>            |

| 0     | 1     | 1                     | 0          | $0 V_{dc}$                      |

| 0     | 0     | 1                     | 1          | -0.5V <sub>dc</sub>             |

| 0     | 0     | 0                     | 0          | 0 V <sub>dc</sub><br>(unloaded) |