# Analysis and Design of High Efficiency Grid-to-Vehicle (G2V) Plug-in Chargers for Local e-Transportation

#### Abhinandan Dixit

A Thesis

In the Department

Of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada.

August 2020

# CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

| This is to certif                | ify that the thesis prepared                                                  |                                |

|----------------------------------|-------------------------------------------------------------------------------|--------------------------------|

| By:                              | Abhinandan Dixit                                                              |                                |

| Entitled:                        | Analysis and Design of High Efficiency Grid-to-Veh for Local e-Transportation | ticle (G2V) Plug-in Chargers   |

| and submitted                    | in partial fulfillment of the requirements for the degree                     | ee of                          |

|                                  | Master of Applied Science                                                     |                                |

| Complies with originality and    | the regulations of this University and meets the accel quality.               | pted standards with respect to |

| Signed by the                    | final examining committee:                                                    |                                |

|                                  | Dr. Sébastien Le Beux                                                         | Chair                          |

|                                  | Dr. Ilamparithi T.Chelvan                                                     | External Examiner              |

|                                  | Di. Ramparam 1. Cheivan                                                       | Examiner                       |

|                                  | Dr. Sébastien Le Beux                                                         |                                |

|                                  | Dr. Akshay Kumar Rathore                                                      | Supervisor                     |

| Approved by:                     | Dr. Yousef R. Shayan, Chair Department of Electrical and Computer Engineering | _                              |

| August 21st, 20<br>Date of Defen |                                                                               |                                |

#### **ABSTRACT**

Analysis and Design of High Efficiency Grid-to-Vehicle (G2V) Plug-in Chargers for Local e-Transportation

Abhinandan Dixit, MASc.

Concordia University, 2020

Electric transportation worldwide has witnessed a tremendous increase in the use of electric vehicles (EV's) due to increased awareness of environmental issues. Road EV's compromise a broad spectrum of vehicles right from two-wheelers three-wheelers (rickshaws/Auto/Trio), cars and electric buses. E-Rickshaw has gained popularity in the Asian market post-2010 because of their symbolic resemblance with traditional auto-rickshaw. The fast growth of the market is principally pushed by the low ownership cost of electric three-wheelers, falling battery prices, and favorable government policies and support. These EVs run on low-cost 48 V, 120 Ah lead acid battery packs having low depth-of-discharge (DOD). Hence, frequent battery charging becomes essential for such EVs. Conventional battery chargers available in the market utilize flyback converter based topologies in order to charge such battery packs. On one hand such battery chargers are easy to implement, these topologies fail to achieve unity power factor (UPF) operation leading to high total harmonic distortion (THD) and poor input power quality at the input. Thus active power factor correction (PFC) becomes a vital constituent in AC-DC converters. By understanding the constraints posed by continuous current mode (CCM) based battery chargers, the proposed converters are designed to operate in discontinuous current mode (DCM) because of its evident benefits such as inherent PFC, zero current turn-on and zero diode reverse recovery losses. By omitting sensors at the input and utilizing only the output sensors, regulated voltage or current can be obtained which makes the system cost-effective and improves its reliability and robustness to high frequency noise.

This thesis presents both isolated and non-isolated battery charger for local e-transportation EVs utilizing 48 V lead acid battery pack. At first, a non-isolated single-stage interleaved buck-boost float charger is proposed by considering the advantages such as reduced current stresses, minimum

number of semiconductor devices and absence of bulky high frequency transformer. DCM operation of the proposed converter ensure UPF operation for variable input voltage and utilizing just a single sensor makes this charger configuration economical and easy to implement. However, such a configuration had high current stress on the semiconductor devices leading to increased thermal requirement and reduced efficiency at light loads. Thus addressing these problems, a high efficiency two-stage battery charger is proposed. The battery charger uses an interleaved DCM buck-boost converter in order to achieve PFC at variable input voltage, whereas the second stage is an unregulated half-bridge LLC resonant converter which provides isolation as well as softswitching for the primary switches. Synchronous rectification (SR) along with only capacitive filter is used on center tapped transformer secondary to improve converter efficiency. Due to DCM of the front-end AC-DC converter achieves zero current turn-on of the switches and DC-DC converter switches achieve zero voltage turn-on because of the LLC resonant. The proposed battery charger implements constant current (CC) and constant voltage (CV) method of charging using simple PI controllers, thus making it suitable for commercial use. Small signal models for both the battery charger configurations are developed using the current injected equivalent circuit approach and a detailed controller design is illustrated. Simulation results using PSIM11.1 software and experimental results from proof-of-concept laboratory hardware prototypes are provided in order to validate the reported analysis and design which demonstrates their performance.

#### Acknowledgment

Foremost, I would like to express my sincere to my erudite supervisor, *Prof. Akshay Kumar Rathore* for his patience, guidance, motivation, enthusiasm and constant support throughout my Masters. I am thankful for his priceless suggestions and assistance that helped me in my research work and gave me deep insights in the field of power electronics. I have learned a lot from his scientific knowledge, critical thinking, simplicity, and punctuality, which are key factors of any success

The completion of this thesis also includes scholarly inputs and help from my colleagues in the Power Electronics and Energy Research (PEER) Group. I would like to express my gratitude to *Dr. Sivanagaraju and Karan* for their support in building experimental set-up and for the fruitful research discussions. My special thanks to *Swati, Gayathri, Ronak, Akhilraj, Dwaipayan, Venkata, Koyelia, and Dr. Amit* for their friendship and constant moral support. I would also like to thank my undergraduate supervisor *Dr. Prabhakar M* for sparking interest in me in the field of power electronics.

I would like to gratefully acknowledge Concordia University (CU) for their world-class research facility and financial support, which pave way for a successful career.

I would like to thank my parents (*Mrs. Anjali Dixit and Mr. H R Dixit*) for showing me the path to pursue Masters. I would also like to thank my family members *Prashansa*, *Prafulla*, *Pravina*, *Mishka*, *R C Dixit*, *and Vijaya Dixit* for their continuous blessings, love and support.

In the end, I would also like to acknowledge my friends who made my Masters (MASc.) life colourful and enjoyable.

## **Table of Contents**

| List of Tables                                         | VIII |

|--------------------------------------------------------|------|

| List of Figures                                        | IX   |

| List of Abbreviations                                  | XII  |

| List of Symbol                                         | XIV  |

| CHAPTER 1: Introduction                                | 1    |

| 1.1 Introduction                                       | 1    |

| 1.2 Literature Review                                  | 2    |

| 1.2.1 Types of Battery Chargers                        | 2    |

| 1.2.2 Battery Charger Architectures.                   | 3    |

| 1.2.2.1 AC-DC Converters                               | 5    |

| 1.2.2.2 DC-DC Converter Architecture                   | 10   |

| 1.3 Research Objective                                 | 12   |

| 1.4 Thesis Outline                                     | 13   |

| 1.6 Conclusion                                         | 13   |

| CHAPTER 2: DCM Based Non-Isolated PFC AC Float Charger | 15   |

| 2.1 Introduction                                       | 15   |

| 2.2 Topological Selection Proposed Converter           | 15   |

| 2.3 Steady State Analysis                              | 19   |

| 2.4 Converter Design                                   | 21   |

| 2.4.1 Average Output Current.                          | 21   |

| 2.4.2 Input Current.                                   | 22   |

| 2.4.3 DCM Operation and Critical Conduction Parameter  | 23   |

| 2.4.4 Design of Inductor.                              | 24   |

| 2.4.5 Design of Output Capacitor                       | 24   |

| 2.4.6 Design of Input Filter                           | 26   |

| 2.5 Converter Small Signal Model                       | 26   |

| 2.6 Results and Discussion                             | 28   |

| 2.6.1 Simulation Results                                             | 28 |

|----------------------------------------------------------------------|----|

| 2.6.2 Experimental Results.                                          | 33 |

| 2.7 Conclusion                                                       | 36 |

| CHAPTER 3: A Dual-Sensor based High Efficiency Two-stage Battery Cha | U  |

| e-Transportation                                                     | 37 |

| 3.1 Introduction                                                     | 37 |

| 3.2 Proposed Converter                                               | 37 |

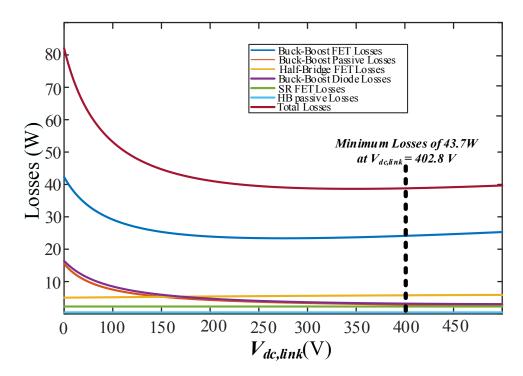

| 3.3 Optimal DC-Link Selection                                        | 40 |

| 3.3.1 Front-end Loss Analysis.                                       | 40 |

| 3.3.2 Back-end Loss Analysis.                                        | 46 |

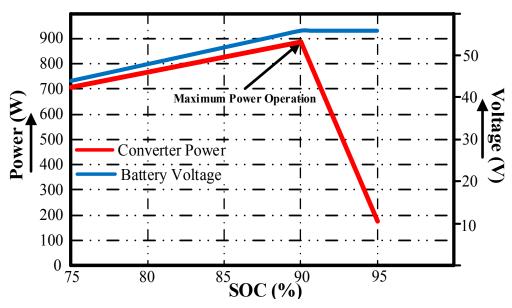

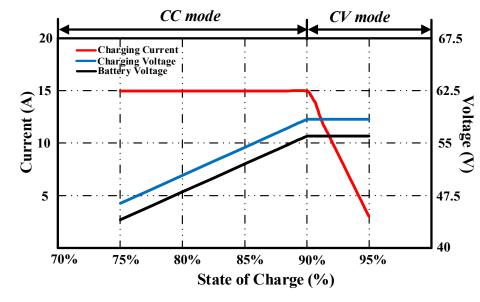

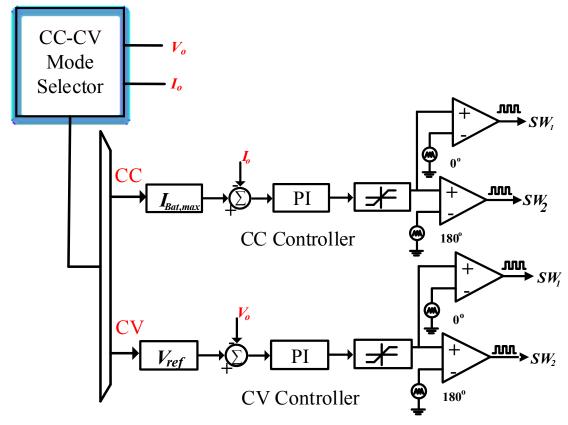

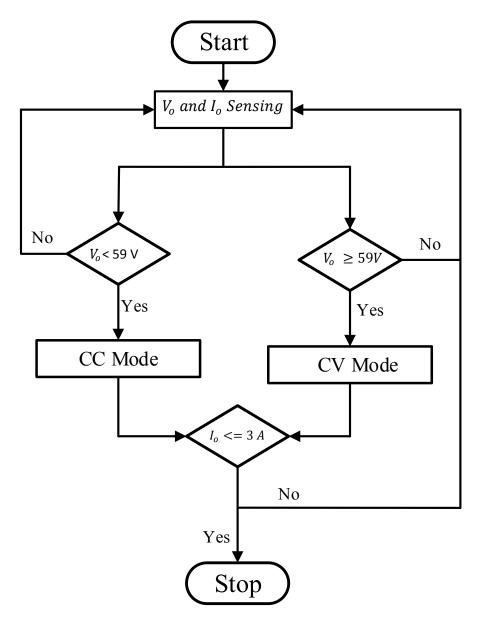

| 3.3.3 Battery Charging Profile                                       | 51 |

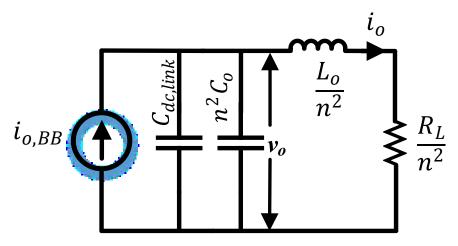

| 3.4 Small Signal Model of Proposed Converter Charger                 | 56 |

| 3.5 Results and Discussion                                           | 58 |

| 3.5.1 Simulation Results                                             | 58 |

| 3.5.2 Experimental Results.                                          | 62 |

| 3.6 Conclusion                                                       | 68 |

| CHAPTER 4: Conclusion and Future Work                                | 69 |

| 4.1 Contributions of Thesis                                          | 69 |

| 4.2 Comparison between proposed Battery Charger Configurations       | 71 |

| 4.3 Future Scope                                                     | 73 |

| 4.3.1 Design and Development of EMI/EMC Filter                       | 73 |

| 4.3.2 Non-Linear Control for better dynamic performance              | 73 |

| 4.3.3 Bridgeless AC-DC converter as active front-end                 | 74 |

| 4.3.4 Current-fed converter as back-end                              | 74 |

| Bibliography                                                         | 75 |

| List of Publications                                                 | 83 |

# List of Tables

| Table 2.1: | Design Specifications.                                                                                                                                                  | 28 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2: | Component Specification.                                                                                                                                                | 31 |

| Table 2.3: | Comparison between proposed and other topologies                                                                                                                        | 35 |

| Table 3.1: | Design Specifications.                                                                                                                                                  | 54 |

| Table 3.2: | Actual parameters and for loss analysis                                                                                                                                 | 55 |

| Table 3.3: | Comparison of analytically calculated and simulated average and rms current values of active and passive devices at rated condition of 1 kW. V_in=110 V, D=0.56, L=75µH | 62 |

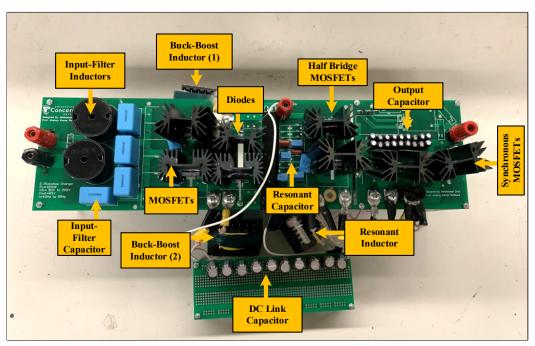

| Table 3.4: | Hardware Component specifications                                                                                                                                       | 63 |

| Table 3.5: | Comparison between the proposed topology and other topology for battery charging                                                                                        | 66 |

| Table 4.1  | Comparison between Proposed Battery Charger Configurations                                                                                                              | 71 |

# List of Figures

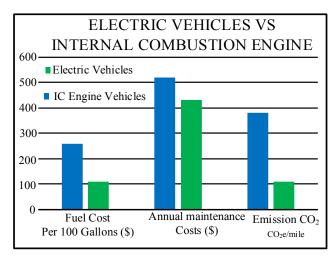

| Fig. | 1.1.  | Comparison between EV and IC engine                                                                                                                                                                                                                     | 2  |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

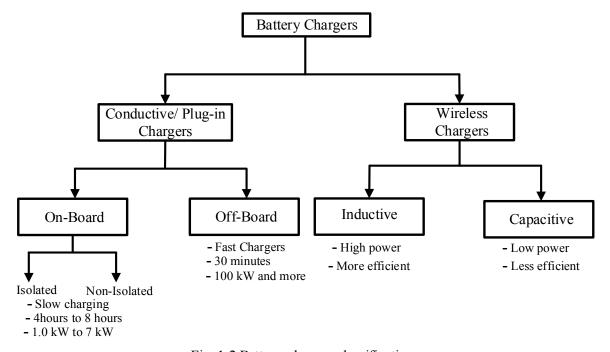

| Fig. | 1.2.  | Battery Charger Classification.                                                                                                                                                                                                                         | 2  |

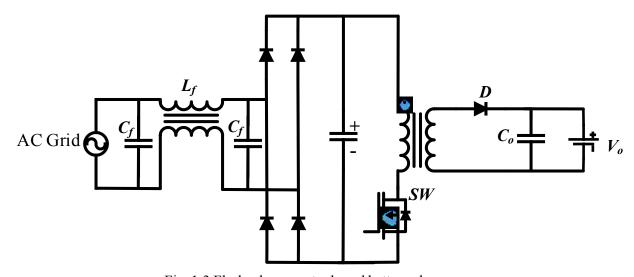

| Fig. | 1.3.  | Fly-back converter based battery charger                                                                                                                                                                                                                | 3  |

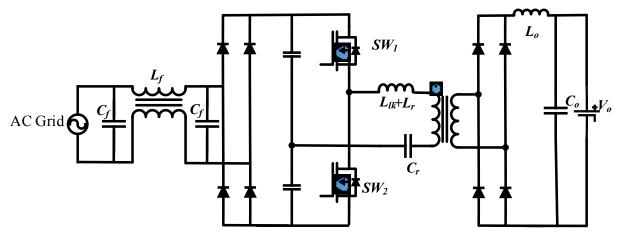

| Fig. | 1.4.  | Half-bridge series resonant converter based battery charger                                                                                                                                                                                             | 4  |

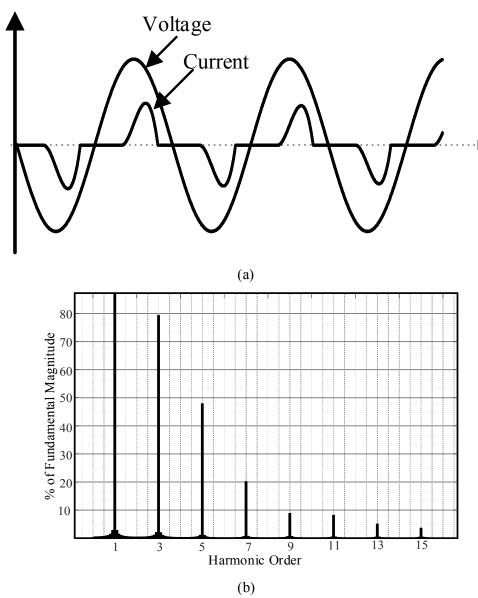

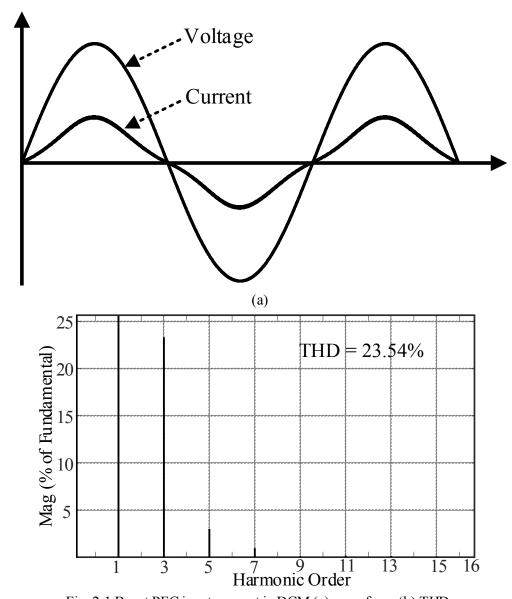

| Fig. | 1.5.  | (a) Diode bridge voltage and current waveform. (b) Input current THD                                                                                                                                                                                    | 5  |

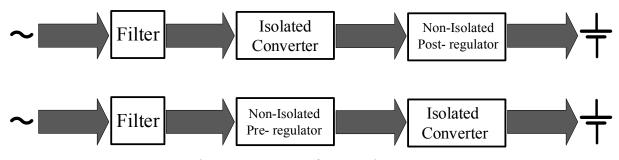

| Fig. | 1.6.  | Two types of proposed concept                                                                                                                                                                                                                           | 6  |

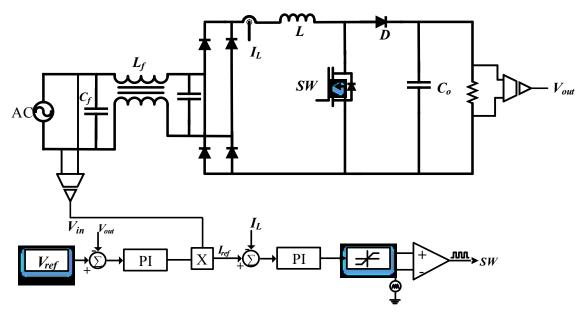

| Fig. | 1.7.  | Boost converter as pre-regulator in CCM                                                                                                                                                                                                                 | 7  |

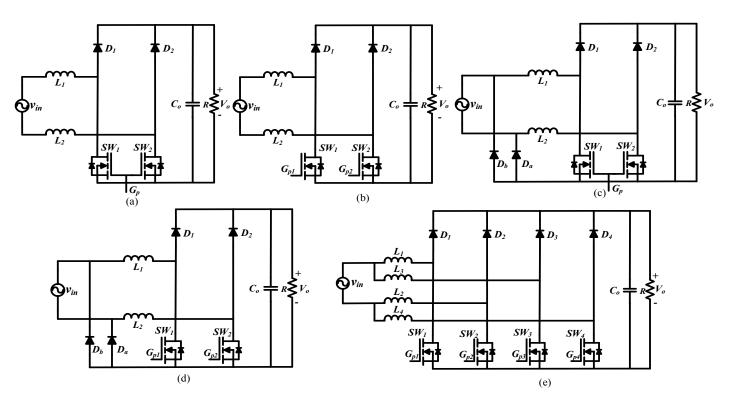

| Fig. | 1.8.  | Schematics of state-of-the-art topologies (a) bridgeless boost PFC; (b) dual boost PFC; (c) semi-bridgeless PFC; (d) phase-shifted semi-bridgeless PFC; (e) bridgeless interleaved boost PFC converter                                                  | 8  |

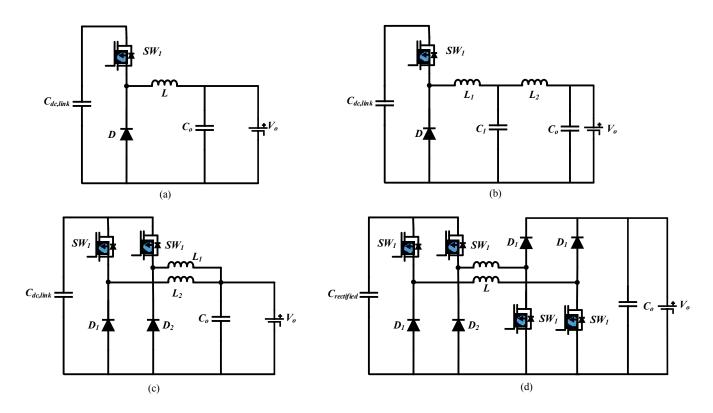

| Fig. | 1.9.  | Non-isolated DC-DC state-of-the-art topologies (a) Buck; (b) buck with output filter; (c) interleaved buck; (d) non-inverting buck-boost                                                                                                                | 10 |

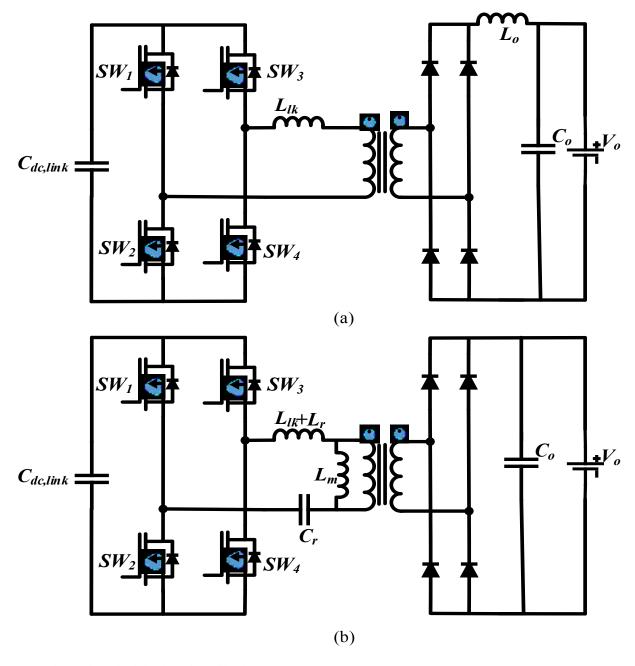

| Fig. | 1.10. | (a)Phase shifted full-bridge. (b) full bridge LLC resonant converter                                                                                                                                                                                    | 11 |

| Fig. | 2.1.  | Boost PFC input current in DCM (a) waveform (b) THD                                                                                                                                                                                                     | 16 |

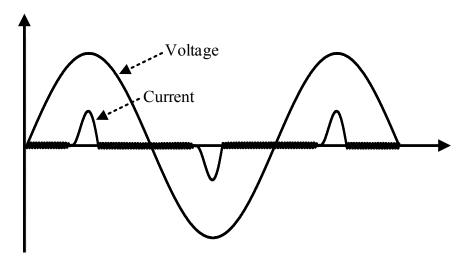

| Fig. | 2.2.  | Input current and voltage waveform for buck converter in DCM                                                                                                                                                                                            | 17 |

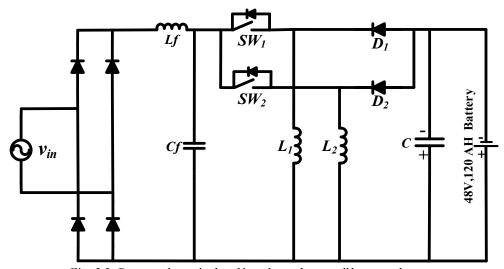

| Fig. | 2.3.  | Proposed non-isolated interleaved two-cell battery charger                                                                                                                                                                                              | 18 |

| Fig. | 2.4.  | Steady-state waveforms of two-cell converter                                                                                                                                                                                                            | 19 |

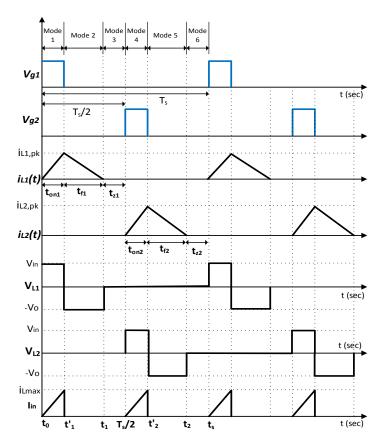

| Fig. | 2.5.  | (a)CIECA for small signal modelling. (b) Control diagram for proposed converter                                                                                                                                                                         | 27 |

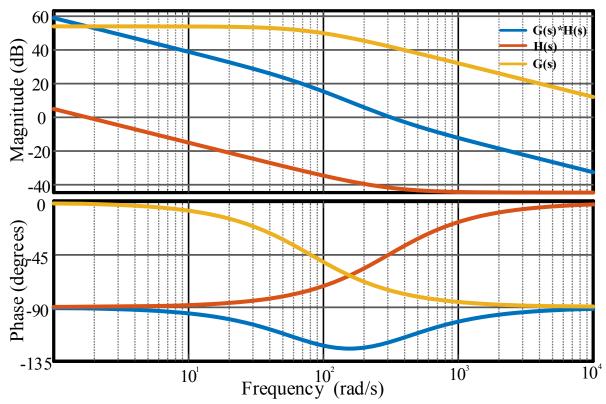

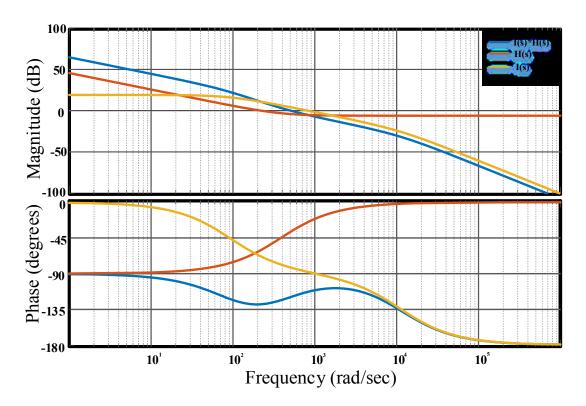

| Fig. | 2.6.  | Bode plot with plant G(s), controller H(s) and open loop transfer function G(s)*H(s)                                                                                                                                                                    | 29 |

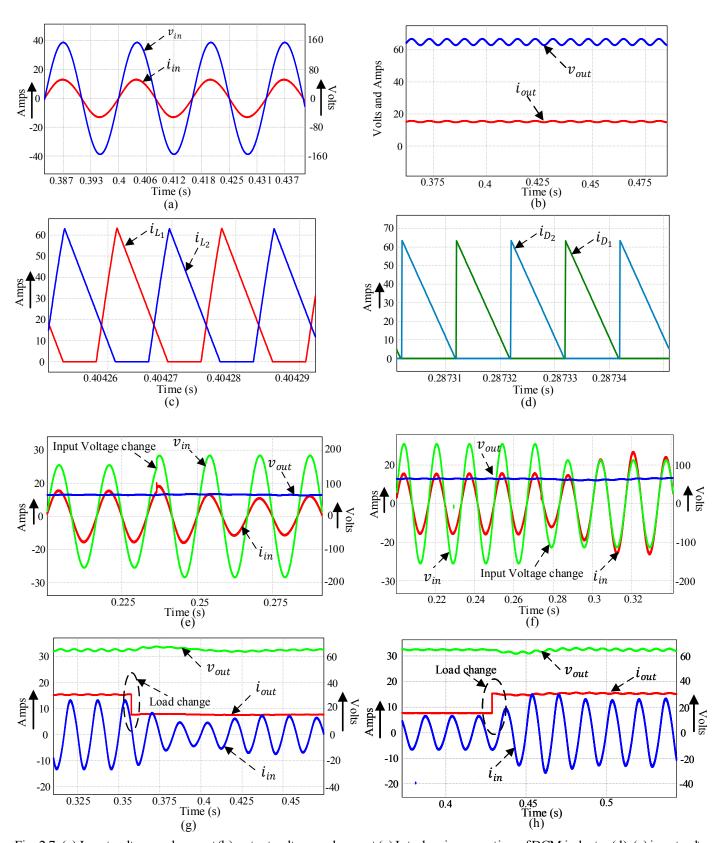

| Fig. | 2.7.  | Simulation Results (a) Input voltage and current (b) output voltage and current (c) Interleaving operation of DCM inductor (d) (e) input voltage swell (f) input voltage dip (g) load change from 500 W to 1.0 kW (h) load change from 500 W to 1.0 kW. | 30 |

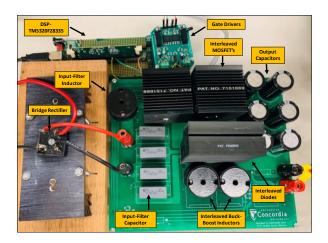

| Fig. | 2.8.  | Hardware Prototype                                                                                                                                                                                                                                      | 31 |

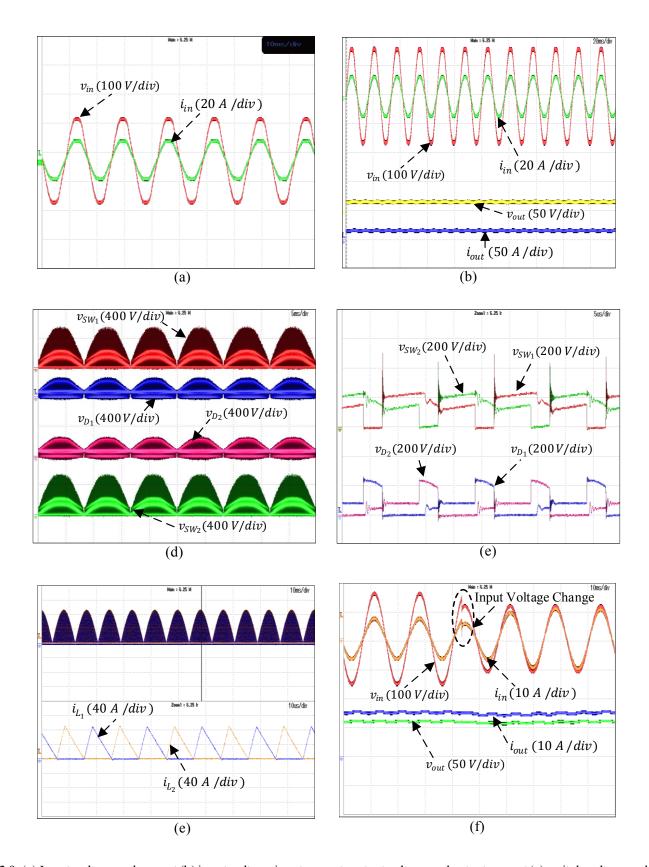

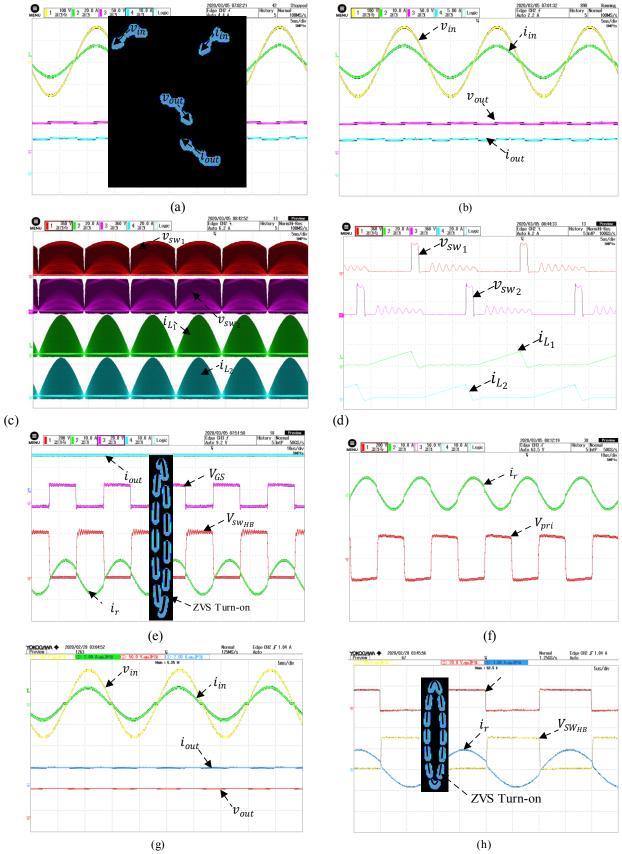

| Fig. 2.9.  | Experimental Results (a) Input voltage and current (b) input voltage, input current ,output voltage and output current (c) switch voltage and diode voltage profile (d) Switch voltage and diode voltage stresses (e) Interleaving operation of DCM inductors (f) input voltage dip. |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

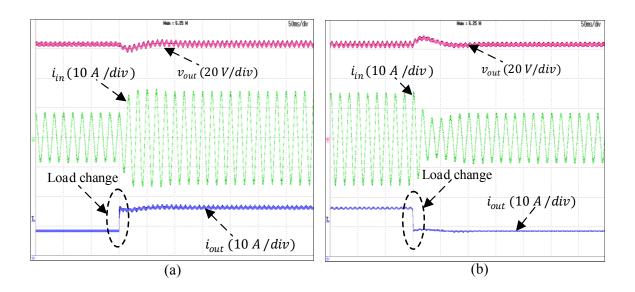

| Fig. 2.10. | (a) Load change from 500W to 1.0 kW. (b) Load change from 1.0 kW to 500W                                                                                                                                                                                                             |

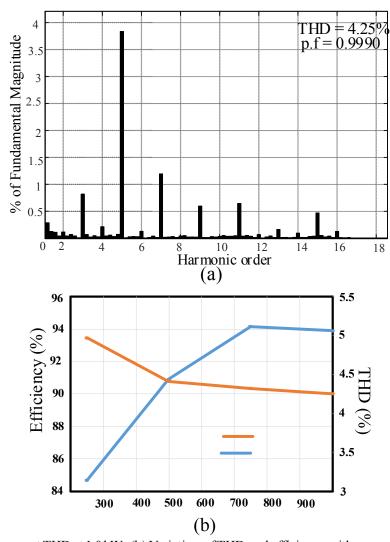

| Fig. 2.11. | (a) Input current THD at 1.0 kW. (b) Variation of THD and efficiency with power                                                                                                                                                                                                      |

| Fig. 2.12. | Volumetric distribution of interleaved converter                                                                                                                                                                                                                                     |

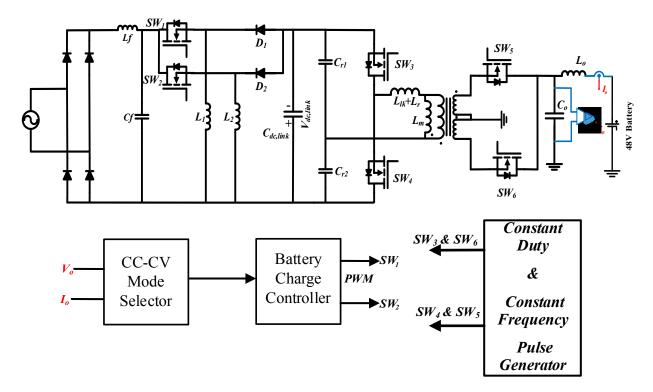

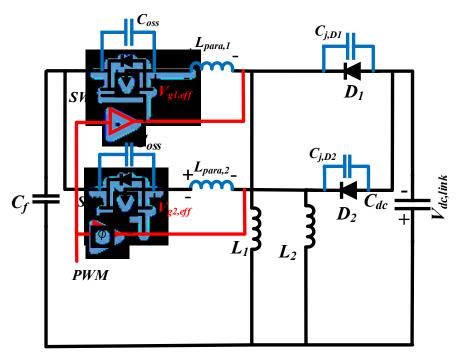

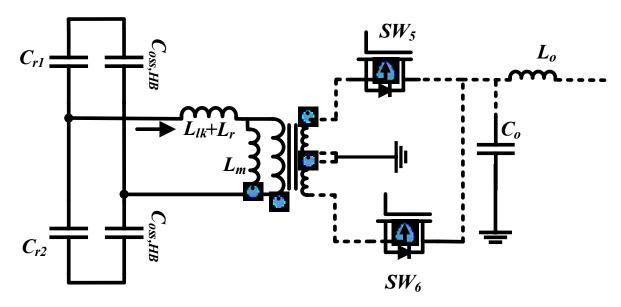

| Fig. 3.1.  | The proposed three-phase interleaved buck-boost derived PFC converter                                                                                                                                                                                                                |

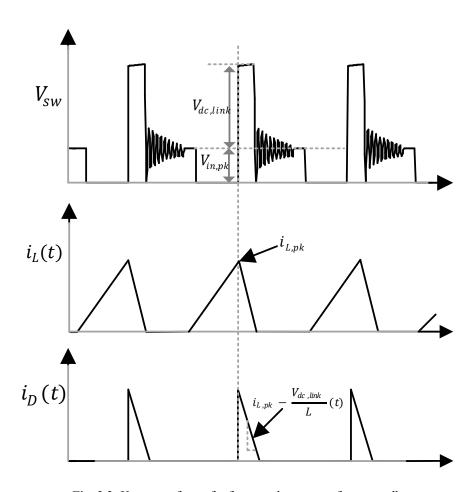

| Fig. 3.2.  | Key waveforms for front-end converter for one-cell                                                                                                                                                                                                                                   |

| Fig. 3.3.  | Schematic of front-end converter using CSI consideration                                                                                                                                                                                                                             |

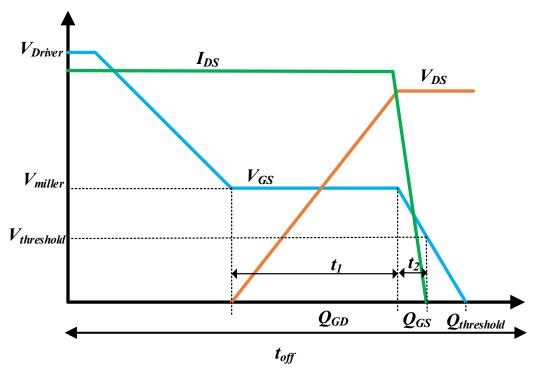

| Fig. 3.4.  | Waveform at device turn-off                                                                                                                                                                                                                                                          |

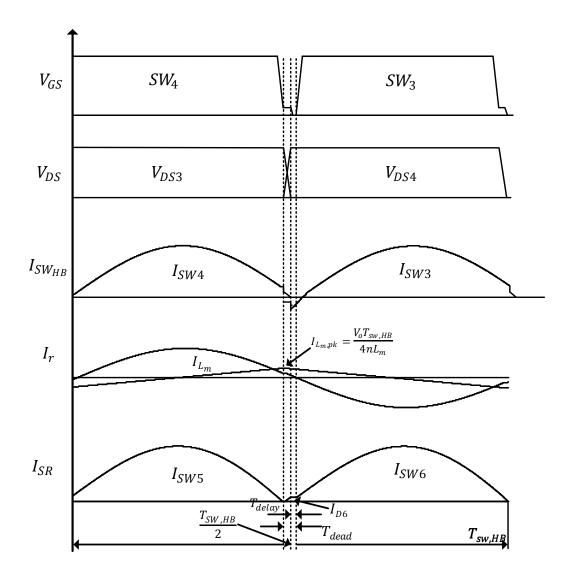

| Fig. 3.5.  | Switching waveforms for Unregulated LLC converter                                                                                                                                                                                                                                    |

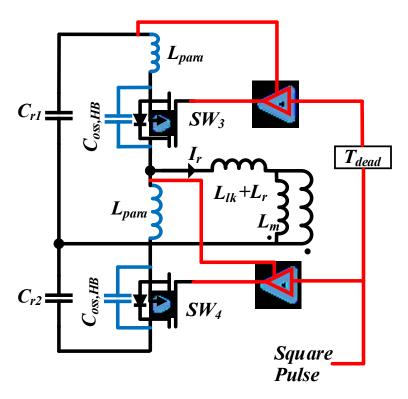

| Fig. 3.6.  | Schematic of back-end converter using CSI consideration                                                                                                                                                                                                                              |

| Fig. 3.7.  | The Equivalent circuit of back-end during dead-time                                                                                                                                                                                                                                  |

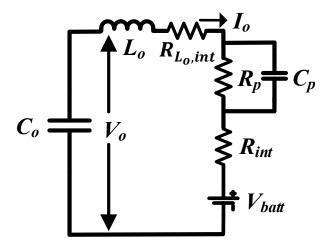

| Fig. 3.8.  | Battery Equivalent circuit when connected to battery charger                                                                                                                                                                                                                         |

| Fig. 3.9.  | Variation of converter power and battery voltage with respect to SOC                                                                                                                                                                                                                 |

| Fig. 3.10. | Charging profile of lead acid battery pack                                                                                                                                                                                                                                           |

| Fig. 3.11. | Calculated Losses according to various DC-Link Voltages                                                                                                                                                                                                                              |

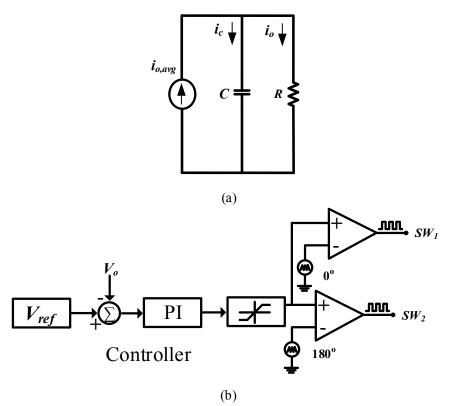

| Fig. 3.12. | CIECA Equivalent Model                                                                                                                                                                                                                                                               |

| Fig. 3.13. | CC-CV Charge Controller                                                                                                                                                                                                                                                              |

| Fig. 3.14. | CC-CV mode selector algorithm                                                                                                                                                                                                                                                        |

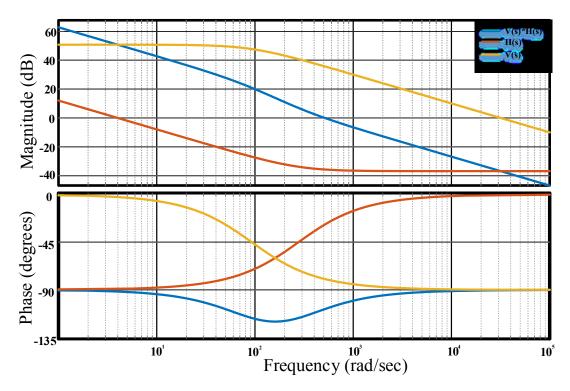

| Fig. 3.15. | Frequency response of plant $I(s)$ , controller $H(s)$ and open loop $I(s)*H(s)$ .                                                                                                                                                                                                   |

| Fig. 3.16. | Frequency response of plant $V(s)$ , controller $H(s)$ and open loop $V(s)*H(s)$                                                                                                                                                                                                     |

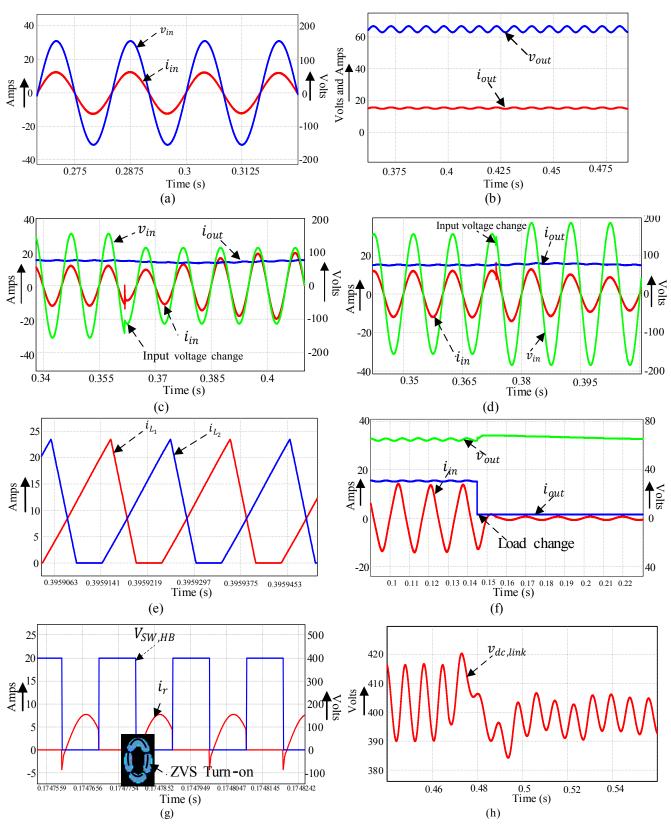

| Fig. 3.17. | Simulation results (a) input voltage and current. (b) output voltage and current. (c) input voltage change from 110 V to 80 V. (d) input voltage change from 110 V to 130 V. (e) inductor current. (f) load change from 100% to 10%. (g) ZVS turn-on of half-bridge switch. (h) DC-link voltage variation during load change                                                                                                                                                                                                                                                                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.18. | Hardware prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

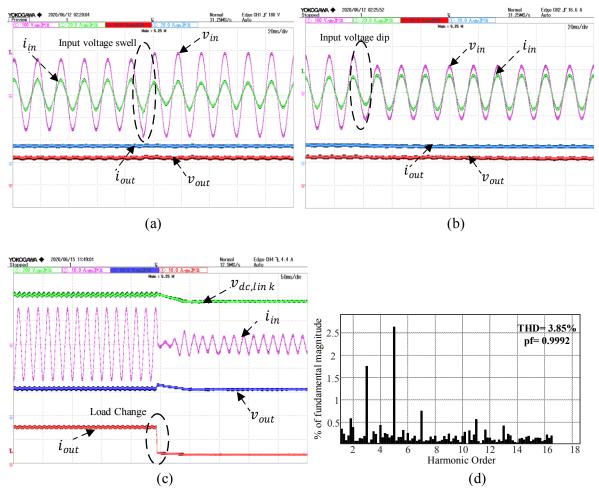

| Fig. 3.19. | Experimental results (a) input voltage 100 V/div , input current 20 A/div, output voltage 50 V/div and output current 10 A/div. (b) input voltage 100 V/div , input current 10 A/div, output voltage 50 V/div and output current 5 A/div. (c) & (d) switch voltage 360 V/div, inductor current 20 A/div (e) & (f) switch voltage 200 V/div, gate 20 V/div, resonant current 10 A/div (g) input voltage 100 V/div , input current 2 A/div, output voltage 50 V/div and output current 2 A/div. () ZVS turn-on of half-bridge switch. (h) switch voltage 200 V/div, gate 20 V/div, resonant current 1 |

| Fig. 3.20  | A/div.  (a) input voltage 100 V/div, input current 20 A/div, output voltage 50 V/div and output current 10 A/div. (b) input voltage 100 V/div, input current 20 A/div, output voltage 50 V/div and output current 10 A/div. input voltage dip (c) dc-link voltage 100 V/div, input current 10 A/div, output voltage 50 V/div and output current 10 A/div. (d) input current FFT at 1.0 kW.                                                                                                                                                                                                          |

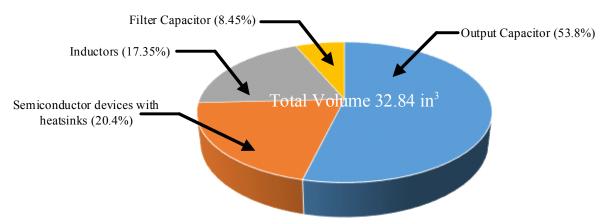

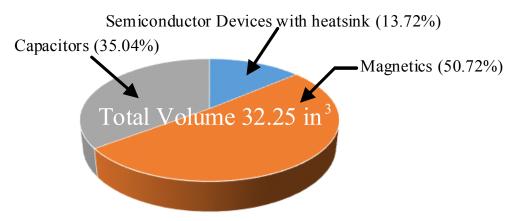

| Fig. 3.21  | Volumetric distribution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

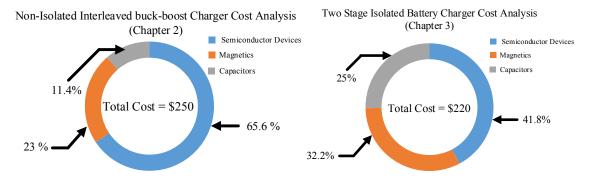

| Fiσ 4 1    | Cost Analysis of proposed charger configurations, scaled to 3 3kW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### List of Abbreviations

EVs Electric Vehicles

PHEV Plug-in Hybrid Electric Vehicle

OBCs On-board Battery Charger

BMS Battery Management System

PFC Power Factor Correction (or Corrected)

THD Total Harmonic Distortion

EMI Electromagnetic Interference

CCM Continuous Conduction Mode

DCM Discontinuous Conduction Mode

AC Alternating Current

DC Direct Current

LLC Inductor-Inductor-Capacitor

ZVS Zero Voltage Switching

ZCS Zero Current Switching

UPF Unity Power Factor

kW Kilo-Watt

CC Constant Current

CV Constant Voltage

MOSFET Metal Oxide Semiconductor Field-Effect

Transistor

CIECA Current Injected Equivalent Circuit Approach

RMS Root Mean Square

ms Millisecond

PF Power Factor

FFT Fast Fourier Transform

G2V Grid to Vehicle

V2G Vehicle to Grid

SOC State-of-Charge

DOD Depth-of-Discharge

ATV All Terrain Vehicles

IC Internal Combustion

RCD Resistor Capacitor Diode

LC Inductor Capacitor

PLL Phase-locked-loop

CSI Common Source Inductance

# List of Symbols

$v_{in} = V_{in,pk} \sin(\omega t)$ Line input voltage  $i_{in} = i_{in,pk} \sin(\omega t)$ Line input current  $L_1 = L_2 = L$ DCM buck-boost inductor  $i_{Lk,pk_{k=1,2}}$ Peak inductor current Average output current in one switching cycle  $i_{o.ava}$  $K_{crit}$ Critical Conduction Parameter  $R_{crit}$ Critical Load Resistance  $K_{cond}$ Conduction Parameter  $C = C_0$ Output capacitor  $f_c$ Cut-off frequency  $L_f, C_f$ Filter inductor and capacitor  $L_o$ Output inductor  $P_o$ Output power  $I_{o,BB} = I_{o,avg}$ Buck-boost average output current  $V_{dc,link}$ DC-link voltage D Duty cycle  $V_{o}$ Converter output voltage Switching time period of buck-boost or half-bridge  $T_{SW_{kB,k=H,B}}$ converter 1:n:n Transformer turns ratio Μ Buck-boost converter gain  $R_{D,bridge}$ Diode bridge resistance for one leg  $V_{f,d}$ Forward voltage for diode bridge  $L_{vara}$ Parasitic inductance  $V_{q,eff}$ Effective gate voltage  $V_{a,off}$ Turn-off gate voltage Miller Plateau Voltage  $V_{miller}$  $C_{i,D}$ Diode junction capacitance  $DT_{S}$ Switch On-Time

Duty Cycle

D

$I_{sw,rms}$  Switch rms current

$I_{d,rms,avg}$  Diode rms and average current

$I_{g_k,off,k=1,2,...}$  Gate current during turn off

$C_{oss,kB,k=H,B}$  MOSFET Output capacitance

$v_{sw}$  Switch Voltage stress

$I_{SW_{BB},rms}$  Buck-boost switch RMS current

$R_{DS,on,kB,k=H,B,SR}$  Switch drain-to-source on resistance

$P_{c.limit}$  Inductor core loss limit,  $mW/cm^3$

$V_e$  Effective core volume,  $cm^3$

$I_{d,rms}$  Diode RMS current

*I<sub>d.rms</sub>* Diode average current

$V_f$  Buck-boost diode forward voltage

$R_d$  Buck-boost diode resistance

$I_{C_{dc.link},rms}$  DC-link capacitor rms current

$R_{Cdc,linkESR}$  DC-link capacitor ESR

$R_L$  Load resistance

$i_r(t)$  Resonant current

$i_{L_m}$  Magnetizing current

$L_m$  Transformer magnetizing inductance

$T_{dead}$  Dead-time for back-end switches

$L_r$  Resonant inductor

$L_{lk}$  Transformer leakage inductance

$C_{r_1} = C_{r_2}$  Resonant capacitor

$I_{SW_k,rms;k=BE,SR}$  Back-end switch current

$R_{DCR}$  DC winding resistance

*I<sub>L,rms</sub>* Buck-boost inductor RMS current

$I_{C_o,rms}$  Output capacitor ripple current

$R_{C_{o,ESR}}$  Output capacitor equivalent series resistance

$R_P$  Self-discharge resistance

R<sub>int</sub> Battery internal resistance

V<sub>batt</sub> Battery voltage

$R_{g,switch}$  MOSFET switch resistance

$R_{g,driver}$  Gate driver resistance

## Chapter 1: Introduction

#### 1.1 Introduction

With growing environmental concerns and increased emissions the world is moving towards electrification in every industrial sector. The automotive industry is one of them to observe a rapid growth where the internal combustion (IC) engines are being replaced by the electric motors. Electric motors are a viable option because of their higher efficiency and robustness. Fig. 1.1 shows a comparison between the classical IC engine vehicle and electric vehicles (EVs) [1]. It is observed that EVs are a realistic solution to offer reduced maintenance cost, better fuel economy, and limits CO<sub>2</sub> emissions as compared to the classical IC engines. Electrification of not only the private vehicles but also of the local transport vehicles has seen a major boom recently. One of the major parts of local transport is an inverter which is supplied from a battery pack to propel the electric motor and the vehicle. EVs can be classified into three major categories as two-wheelers, threewheelers, and four-wheelers. Two-wheelers are used mostly in personal transportation and currently for delivery service, whereas three-wheelers are used for short range local mobility, along with four-wheelers that are mainly used as personal and passenger vehicles for higher range. Three wheeler vehicles have become popular in Asian market because of its cheap price and high robustness. In Thailand and India these three wheelers are commonly known as tuk-tuk or erickshaws [2] and have evolved from IC engine vehicles to full-electric vehicles. Small fourwheeler such as golf carts and all terrain vehicles (ATVs) have also gone full electric to reduce the size and increase efficiency. These vehicles are comparatively cheaper as they are hauled by 850 W motors which are powered by low voltage battery packs of 48 V, 120 Ah lead-acid batteries. As the depth-of-discharge for these lead-acid battery packs is only 20% battery packs require to be charged often [3]. Thus a charger becomes a fundamental component for these vehicles. Charging these battery packs without compromising with the IEEE standards of low total harmonic distortion (THD) is an essential requirement.

Fig. 1.1 Comparison between EV and IC engines.

#### 1.2 Literature Review

In this Section, a detailed overview of various types of battery charging methods and conventional charging topologies is presented.

#### 1.2.1 Types of Battery Chargers

Fig. 1.2 shows the classification of battery chargers. Battery chargers can be broadly classified into two categories i.e. plug-in chargers and wireless chargers. Wireless chargers are

Fig. 1.2 Battery charger classification.

comparatively lesser in use due to lower efficiency and complex design. Plug-in chargers are one the most popular and are currently in practice because of their higher efficiency and simpler design. Off-board chargers are usually fast chargers and require a dedicated power system to charge batteries at high power whereas on-board chargers are relatively slow chargers and can be used when plugged in AC mains. On-board chargers are further classified into isolated and nonisolated topologies. As there is no such requirement in standards for safety of EVs as specified in SAEJ1772 (from the North American standard for electrical connectors for EVs maintained by the Society of Automotive Engineers). Furthermore, there is no electrical reason that the battery should be isolated from ac input power, because its ground is generally floating with the body ground of the vehicle [11]. Non-isolated topologies have low component count and thus achieve higher efficiencies as compared to isolated topologies [4]. Isolated topologies can be further segregated into single-stage and two-stage topologies. Several single-stage isolated topologies have been reported in the literature but deal with poor efficiency due to the transformer leakage inductance [5]. Other topologies present complex control algorithms to implement power factor correction (PFC) which increase the computational burden on the microcontroller [6]. Two-stage non-isolated configurations have also been reported [6] but such topologies increase switch count and system losses.

#### 1.2.2 Battery Charger Architectures

Several battery charger topologies for charging high-voltage battery packs (450 V-650 V) and low voltage battery packs (48 V-72 V) have been proposed in the literature [7], [8]. High voltage

Fig. 1.3 Fly-back converter based battery charger.

Fig. 1.4 Half-bridge series resonant converter based battery charger.

lithium-ion battery packs are used for sophisticated EVs like Tesla and Toyota and lead-acid based low voltage battery packs are used for e-rickshaws, golf carts, airport movers and fork-lifts. Battery chargers employed for such low-voltage battery packs are not refined in order to cut down the cost of such systems. One of the most common topologies used for charging such battery packs is shown in Fig. 1.3 [9]. One of the main drawbacks of using such topologies is the effect of leakage inductance on the switch voltage. During turn-off of the switch SW, the leakage inductance of the high-frequency transformer is discharged and hence gives a voltage spike across the switch. External RCD snubber is connected to dissipate this energy and to clamp the switch voltage leading to, losses [10]. Moreover, connecting diode at the secondary for the low voltage battery charging application induces high conduction and turn-on losses for the diode leading to reduced efficiency. Though the topology is simple and easy to implement, it lacks the basic requirement of achieving unity power factor (UPF) for various line voltages. Such topology presents poor power factor and THD as no active current wave shaping unit is present [9]. An improved version for a low voltage battery charger that is available in the market and is shown in Fig. 1.4. It is seen that though losses due to leakage inductance do not occur due to soft switching achieved because series resonant tank, poor efficiency due to the output diode bridge rectifier losses is one of the main issues. Also such battery charger configuration lacks PFC unit, which induces odd harmonics in the grid leading to poor power quality. The presence of an LC filter at the transformer secondary induces duty cycle loss on transformer primary voltage. As the output of the inductor does not allow a sudden change in current, secondary diodes are shorted that leads to duty cycle loss and rectifier snubber losses

[11]. It is observed that such a PFC unit becomes essential for chargers in order to improve power quality at the input and enhance converter performance.

The above-mentioned charger configurations come in the category of float chargers [7] [8]. Such chargers are easy to implement in terms of control with one control loop to control the charging battery. Float chargers require current limiting resistors at the output and use a single sensor, making them a less complicated solution for battery charging.

#### 1.2.2.1 AC-DC Converters

Fig. 1.5 (a) Diode bridge voltage and current waveform. (b) Input current THD.

AC-DC converters are an essential part of the battery chargers in order to convert AC voltage to stiff DC. Diode rectification is one of the most common ways which is implemented in current chargers but draws discontinuous peaky current. Input current waveform and FFT analysis with diode rectification-based chargers is shown in Fig. 1.5(a) and Fig. 1.5(b). It is seen that odd harmonics are injected in the grid leading to poor input current THD and reduced power quality. Such battery chargers require a bulky passive filter to filter out these harmonics leading to increased weight and size. As per IEC-6000-3-2 [12], the input current THD limit should be below 5% for automobile battery chargers.

The PFC control objectives can be defined as follows:

- 1.) Sinusoidal input current is in-phase with the input voltage over a range of frequencies.

- 2.) Low input current THD over entire range of power.

- 3.) Stiff Regulated DC output voltage.

Thus an active PFC becomes an essential need for battery charging application in order to meet the above mention control objectives. In order to reduce the cost and the weight single-stage, isolated, and non-isolated charger configurations have been developed [13]. Such chargers don't require a dedicated second stage for charging, which reduces cost and improves efficiency. Isolated single-stage topologies present poor efficiencies because of losses due to leakage inductance. Huge voltage spikes at turn-off reduce reliability and require an RCD snubber which reduces the efficiency drastically [14]-[27]. Secondary converters and control schemes are developed in order to improve the efficiencies of such topologies [28]. On the other hand, non-isolated topologies possess no such problems owing to the absence of high-frequency transformer, thus presenting higher efficiencies. But deal with the problem of an increased number of semiconductor count and sensors, which increases the cost greatly. Two-stage battery charging topologies have been popular

Fig. 1.6 Two types of proposed concept.

Fig. 1.7 Boost converter as pre-regulator in CCM

in industries and have one stage dedicated to PFC regulation and the second stage for battery charging control [29]. As shown in Fig. 1.6 such battery charger can have two configurations:

- 1. Post-regulator type

- 2. Pre-Regulator type

In a post-regulator configuration, an isolated converter is used to provide isolation from AC mains and a non-isolated converter to shape the input current and control the battery charging process. Such a battery charging configuration has been reported in [30] but presents comparatively less efficiency as the primary side switches have high conduction losses. Moreover such a topology is not suited for charging low voltage battery packs as the current wave-shaping unit has high conduction and switching losses. On the other hand, a pre-regulator configuration [31]-[35] has the non-isolated converter is used to shape the input current in order to achieve UPF and an isolated converter to control the battery charging process. This configuration is more reliable and is used in current battery chargers.

The most commonly used pre-regulator topology for such an implementation is the use of boost converter because of its simple structure and grounded FET as shown in Fig. 1.7 [35]. Boost inductors are operated in CCM and control is designed in order to shape this inductor current sinusoidal. Inductor current can be shaped in three ways mainly peak current control, average current control, and hysteresis control. These control techniques require sensing of input current

for wave shaping and input voltage in order to synchronize with the grid. Fig. 1.7 shows the circuit and control of a boost converter for active PFC. To implement such control it requires two control loops; the outer loop to regulate the output voltage and inner loop to shape input current by maintaining UPF. Such control strategies have been extended to various topologies like SEPIC converter but deal with issues like increased component count leading to higher losses. Interleaved boost converter has also been presented [32] [33] to reduce the size of the input filter and reduce current stress through the switches. CCM based converters can be extended to various bridgeless topologies as shown in Fig. 1.8 [36]. The input diode bridge is eliminated in order to reduce losses due to the diode forward voltage drop and achieve higher efficiency. Such converters require a bulky isolated transformer for input voltage and current sensing in order to implement phase-locked loop (PLL) for grid synchronization, which increases the cost and weight of the system significantly. It is observed that in a total of three sensors or in some cases four are used to achieve control goals. Moreover, sophisticated microcontrollers are required in order to sample high-frequency data, leading to reduced reliability and converter robustness. In the prospect of control and cost, such converters present high complexity as it requires to determine the phase angle for

Fig. 1.8 Schematics of state-of-the-art topologies (a) bridgeless boost PFC; (b) dual boost PFC; (c) semi-bridgeless PFC; (d) phase-shifted semi-bridgeless PFC; (e) bridgeless interleaved boost PFC converter.

implementation of PLL. Failure of PLL can lead to non-sinusoidal input currents, leading to poor THD and efficiency. As the front-end converter is operated in CCM, it presents right half plane zero (RHZ) during transient operations leading to instability. Thus the controller designed for such implementation should be robust and reliable in order to meet the control objectives and maintain stability. This increases the computation burden on the microprocessor, which indirectly affects the converter performance and start-up.

Reduction in sensors and control complexity has several benefits and can be listed as follows:

- 1) System weight reduction.

- 2) Reduction in cost.

- 3) Improved system reliability.

- 4) Reduced control burden on microcontroller

- 5) High frequency noise robustness.

In order to reduce sensors several algorithms has been reported in literature for estimating the input current and voltages. Such approaches are complex in nature and require rigorous computation burdening the microcontroller, making it difficult for practical application.

In a converter, the number of sensors by default can be reduced by operating it in DCM. In DCM, the average value of the input current in a switching cycle is determined by the input voltage at that instant, therefore the average input current naturally follows the input voltage, which means the DCM operation inherently fulfills the PFC, the first control objective. The second objective of PFC control can be achieved by using a single voltage control loop. To conclude, the DCM operation by default eliminates requirement of the input voltage and input current sensing and therefore, only one output voltage sensor is required. Further the DCM operation inherently realizes the zero-current switching (ZCS) of the converter switches and the zero reverse recovery losses in the converter diodes [10]. Since a small inductor is required for converter DCM operation, it reduces the converter total weight and improves power density. But, the drawback of DCM operation is the high current stress of the semiconductor devices, however the higher current rating semiconductor devices are commercially available at reasonable price. Therefore, by considering all the benefits of DCM, the DCM operated converters are considered in this research work.

Fig. 1.9 Non-isolated DC-DC state-of-the-art topologies (a) Buck; (b) buck with output filter; (c) interleaved buck; (d) non-inverting buck-boost.

#### 1.2.2.2 DC-DC Converter Architecture

The nominal traction battery pack for various categories of EVs ranges from 48 V to 650 V and, for that reason, the most employed DC/DC converter for the battery current regulation (BCR) stage consists of a unidirectional buck converter in order to reduce the voltage from the DC-link to the voltage level of the battery as shown in Fig 1.9. Sometimes an LC output filter is added to reduce the filtering components as in Fig. 1.9 (b). In addition, the interleaving technique can be applied to these topologies [6] [32] as depicted in Fig. 1.9 (c) and Fig. 1.9 (d). In particular, a diode rectifier followed by two interleaved noninverting buck-boost converters is proposed in [4] to design a single-stage battery charger. Other topologies include a high-frequency switched transformer to provide galvanic isolation between the grid and the battery [31]-[35].

In this sense, it is preferable to use high-frequency switched transformers in terms of size and weight than line-frequency transformers [31]. Two of the most widely used topologies are the phase-shifted full-bridge DC-DC converter [32] and the full-bridge LLC resonant converter [35] [36] as shown in Fig. 1.10. Such topologies have been well in use in current chargers but face issues regarding battery charger control. Phase-shift control presents complex switching states and

circulating currents in order to achieve zero voltage switching (ZVS) of primary switches. Such modulation technique tends to lose ZVS at light load leading to low efficiency at partial loads. LC filter connected at the output induces duty cycle loss and rectifier diode ringing due to secondary diode bridge short-circuit during polarity reversal [32]. On the other hand, LLC converters do not present such problems but require complex variable frequency modulation and microcontroller with a high clock rate to control the charging the battery voltage and current. Sophisticated small

Fig. 1.10 (a) Phase shifted full-bridge. (b) full bridge LLC resonant converter.

#### signal modelling is required in order to design a robust control for such charging application.

Moreover, the use of full-bridge topology for the LLC converter does not hold valid until unless the charger has bidirectional flow. Unidirectional battery chargers with full-bridge configuration present high conduction and switching losses due to increased semiconductor devices. LLC converter also has an issue of output voltage increase during light-load conditions [6]. Thus keeping the above points proper hardware topology needs to be selected for optimal performance for power conversion.

#### 1.3 Research Objectives

The fundamental objective of this thesis is to propose battery charging topologies (both isolated and non-isolated) to replace currently used battery chargers with reduced sensing and control requirement by fulfilling the current THD requirements with active PFC for low voltage battery EVs. In particular AC-DC and DC-DC converters are studied and analyzed with a focus on minimizing the total number of components, improving power quality, and improving the overall operating efficiency and power density. The proposed converters are designed for the DCM operation in order to simplify the control circuit and to reduce the number of sensors which consequently increases the converter reliability, and robustness. Further, the design and performance of the converter are tested for input voltage change and load perturbations.

The objectives of this thesis are:

- 1) Simplified control and easy implementation

- 2) Reduced number of sensors

- 3) Higher reliability

- 4) Improved power quality (THD < 5%)

- 5) Improved efficiency

- 6) UPF operation for input voltage variation

To accomplish these objectives, and to replace the conventional diode rectifier active PFC rectification, this thesis proposes two battery charging topologies which have been briefly described in the thesis outline in the next section 1.4 and in detail in Chapter 2 and 3 respectively.

#### 1.4 Thesis Outline

The objectives of the thesis are realized in Chapter 2 and 3 and the thesis outline is:

In Chapter 2, a non-isolated single-stage interleaved buck-boost converter based battery charger configuration is studied with the inductors operating in DCM. The proposed charger configuration uses the simple concept of float charging in order to reduce weight due to the bulky transformer. The steady-state DCM operation, converter design, DCM condition, small-signal model, and closed-loop controller design have been reported. The analysis and design are validated with simulation results from PSIM11.1 software and further verified with the experimental results from a 1.0 kW hardware prototype developed in the lab.

In Chapter 3, a low cost two-stage isolated battery charger has been proposed. The battery charger configuration uses an interleaved buck-boost converter operated in DCM boost mode as a first stage and a half-bridge LLC converter is used in order to provide high-frequency isolation as the see second stage. The loss analysis of each stage is done in order to obtain optimal DC-link voltage for the optimal performance of the converter. Small signal analysis for constant current (CC) and constant voltage (CV) mode is done in order to improve battery charger performance. The analysis and design are validated with simulation results from PSIM11.1 software and further verified with the experimental results from a 1.0 kW proof-of-concept hardware prototype developed in the lab. The proposed charger uses only two sensors and simple control architecture which is easy to implement. The results show high efficiency and low THD as per the requirement

#### 1.5 Conclusion

This Chapter discusses the current trends in the automotive market intending to incorporate more EVs in the fleet of ever-growing EVs. Due to higher efficiency, better fuel economy and reliability have led to an increase in EV sales annually. The current EV industry faces challenges in the area of battery charging for the low voltage battery packs for golf-cart and e-rickshaws.

A comprehensive review of the currently used diode bridge base AC-DC converters that are available in the market and their limitations to meet the power quality requirements have been discussed. Their inability to meet the THD standards as per [12] poses challenges to current battery charging configurations. The literature study reveals the current trends in the battery charger configurations, which include both isolated and non-isolated topologies. Complications regarding

that these topologies offer poor efficiency and extra footprints. Types of two-stage battery charger topologies are discussed 3 front-end and back-end architectures for such configurations. The literature study revealed that the CCM operated converter requires at least three sensors and two control loops which increase the computational burden on microcontrollers. Reduction in the number of sensors has various merits such as a reduction in cost, reduction in control complexity, increased reliability, and robustness to high frequency.

Given this DCM based battery charger configurations (isolated and non-isolated) are studied in order to reduce cost and achieve higher efficiency and contribute to novel power electronic solutions for EV battery charging application. The next chapter deals with design and development of a DCM single stage non-isolated battery charger for low voltage battery driven EVs.

# Chapter 2: DCM Based Non-Isolated Battery Charger

#### 2.1 Introduction

Typically the low power (slow) battery chargers for the low voltage battery packs (48 V) do not employ any active PFC unit for wave shaping. A two-stage battery chargers can be implemented for such low voltage battery packs where a non-isolated converter performs PFC followed by a DC-DC converter for isolation at second stage. This is one of the simplest approach with two power processing stages that leads to higher conduction losses and complex control. Moreover two-stage converters require additional semiconductor devices and bulky dc-link capacitors which increases and compromise the system reliability. Single stage converter is an appealing choice as the power is processed only once with reduced semiconductor devices. Single-stage isolated topologies have also been presented [5], [22] but offer poor efficiency because of losses associated with the leakage inductance of the transformer and require RCD snubber and overrated devices. Non-isolated battery chargers present comparatively higher efficiency, as they have reduced number of components and reduces system weight. As such converters are operated in CCM and have multiple of sensors and control requirement [37]. With the focus on reducing total number of components and sensors, a non-isolated interleaved buck-boost converter operated in DCM has been presented that addresses these concerns.

### 2.2 Topological Selection and Proposed Converter

CCM based PFC converters have been in implementation but the concept of DCM cannot be implemented to all the basic topologies. Boost converter and buck converter cannot be implemented in DCM for power factor correction for the following reason. The input current for a boost converter can be given as

$$i_{in}(t) = \begin{cases} \frac{v_{in}(t)}{L}t, & 0 < t \le t_{on} \\ \frac{(v_{in}(t) - V_{o})}{L}t, & t_{on} < t < T_{s} \end{cases}$$

(2.1)

By performing FFT of the (2.1) using (2.2), one can get,

$$i_{in}(t) = \frac{a_0}{2} + \sum_{h=1}^{\infty} (a_h \cos(h\omega_{sw}t) + b_h \sin(h\omega_{sw}t))$$

(2.2)

$$a_h = \frac{V_0}{h\omega_{SW}L} \left( Dsin(2\pi hD) + \frac{1}{2h\pi} \cos(2\pi hD) - \frac{1}{2h\pi} \right)$$

(2.3)

$$b_h = \frac{V_0}{h\omega_{sw}L} \left( 1 - D\cos(2\pi hD) + \frac{\sin(2\pi hD)}{2\pi h} \right) - \frac{V_{in}}{h\omega_{sw}L}$$

(2.4)

From (2.3) and (2.4), it is observed that lower order odd harmonics are present, which leads to poor input current THD. Fig 2.1 shows the input current waveform and FFT analysis for a boost

Fig. 2.1 Boost PFC input current in DCM (a) waveform (b) THD.

PFC converter operating in DCM. It is seen that higher amplitude low order harmonics are injected (2.3), (2.4) in input current leading to poor THD. Such a waveform is obtained due to its boost structure as the boost inductor is connected to the input throughout the switching cycle. Thus any non-linearity from the output is transferred to the input leading to peaky input current waveform. As a consequence, DCM boost and boost derived configurations require a large filter at the input side to filter out lower order harmonics, which in turn reduces the power density of the system. Several methodologies have been proposed for improving the current quality in DCM boost converter by reducing the lower order harmonic content. However, such approaches are complex in nature and require extra sensing without having a significant impact on the harmonic content [38]-[42]. Therefore, DCM based boost topologies are not feasible for such PFC application. On the other hand, buck or buck derived topologies cannot be implemented PFC, which can be understood by performing FFT analysis of input current expression expressed as

$$i_{in}(t) = \begin{cases} \frac{(v_{in}(t) - V_o)}{L}t, & 0 < t \le t_{on} \\ 0, & t_{on} < t < T_s \end{cases}$$

(2.5)

Using (2.1),

$$a_h = \frac{(v_{in}(t) - V_0)}{h\omega_{sw}L} \left( Dsin(2\pi hD) + \frac{1}{2h\pi} cos(2\pi hD) - \frac{1}{2h\pi} \right)$$

(2.6)

$$b_h = \frac{(v_{in}(t) - V_o)}{h\omega_{sw}L} \left(\frac{\sin(2\pi hD)}{2h\pi} - D\cos(2\pi hD)\right)$$

(2.7)

Fig. 2.2 Input current and voltage waveform for buck converter in DCM.

Even though this topology does not present odd harmonics at the input as seen from (2.6) (2.7), unlike boost converter, power transfer doesn't take place for  $v_{in}(t) < V_o$ , as duty cycle saturates at its maximum limit, leading to poor power factor as seen from Fig. 2.2.

A DCM buck-boost becomes advantageous as the input inductor is either connected to the input or the output, thus harmonics from the output are not reflected across the input side thus achieving a good THD and UPF operation. Moreover, it has less passive components' count as compared to the conventional Sepic or Cuk converter making it a cost effective option for charging.

Fig. 2.3. Proposed non-isolated interleaved two-cell battery charger

Fig. 2.3, shows an interleaved PFC buck-boost converter for the low voltage battery charging. It is the fusion of a full-bridge diode rectifier and two-cells (switch, inductor and diode). Both the cells operate on a similar switching frequency and the switching signals are 180° phase shifted. By interleaving operation of two-cells, not only the current stress is reduced through the devices but also the input filter size is also reduced, which leads to increased power density of the converter. The proposed configuration uses the simple concept of float charging to charge the battery. It uses a simple charging method by just pushing current equal to the maximum current limit of the lead acid battery. As the battery voltage increases gradually this current falls and charging is turned off. Such battery charging method is a cost effective solution as it reduces the sensor count and complexity.

Fig.2.4. Steady-state waveforms of two-cell converter.

#### 2.3 Stready State Analysis

Steady-state operation of the two-cell buck-boost for one high frequency switching cycle is shown in Fig. 2.4. With following assumptions [49], [50] and the same analysis can be done for single-cell converter.

- a) All the components are ideal and lossless.

- b) Within one switching cycle, input and output voltages are constant.

- c) The output capacitor is bulky enough to maintain output voltage constant.

- d) Duty cycle is fixed for one power level.

# *Mode I:* $0 < t < t'_1$

In this mode switch  $SW_I$  is turned on with gating pulse  $V_{g_1}$ ,  $L_I$  charges and stores energy whereas capacitor C supplies the load. No energy is stored in  $L_2$ . Inductor current  $i_{L1}$  is given by

$$i_{L1}(t) = \frac{v_{in}(t)}{L_1} \tag{2.8}$$

$Mode II: t_1' < t < t_1$

Switch  $SW_I$  is turned off and inductor current  $i_{L1}$  freewheels through diode  $D_I$ . Capacitor C filters out the ripple current and supplies pure DC current to the battery. Inductor current  $i_{L1}$  for this stage is given by

$$i_{L1}(t) = i_{L1,pk} - \frac{V_o}{L_1} t_1 \tag{2.9}$$

*Mode III:*-  $t_1 < t < \frac{T_s}{2}$

This is the DCM condition where energy stored in  $L_1$  becomes zero and the capacitor supplies the load. At the end of this interval, half of the high frequency cycle is over. This time duration is given by

$$t_{z1} = \frac{T_s}{2} - t_{on1} - t_{f1} \tag{2.10}$$

*Mode IV:*  $T_s/2 < t < t_2'$

Switch  $SW_2$  is turned ON in this mode, inductor  $L_2$  charges, and stores energy. Capacitor C supplies the load and whereas energy stored in  $L_1$  is zero. Inductor current  $i_{L_2}(t)$  is given by

$$i_{L2}(t) = \frac{v_{in}(t)}{L_2} \tag{2.11}$$

*Mode V:*-  $t_2' < t < t_2$

Gating pulse from switch  $SW_2$  is removed. Inductor  $L_2$  discharges through the load and diode  $D_2$ , thus supplies power to the load  $i_{L2}(t)$  is given by

$$i_{L2}(t) = i_{L2,pk} - \frac{V_0}{L_2} \tag{2.12}$$

$Mode\ VI:-t_2 < t < T_s$

This is the same as *Mode III*, and the DCM period is given

$$t_{z2} = T_s - t_{on2} - t_{f2} (2.13)$$

# 2.4 Converter Design

In this section, the expressions for converter average output current and input current, and the DCM condition are derived. Further, the design equations for each passive component of converter are developed.

#### 2.4.1 Average output current

The average load current in one switching cycle  $i_{o,avg}$  is nothing but the average current of both diodes  $D_1$  and  $D_2$  i.e. the sum of area under the  $i_{L1}$  curve and  $i_{L2}$  curve during interval  $t_{f1}$  and  $t_{f2}$  respectively. Substituting  $t = t_{f1}$  and  $t = t_{f2}$  we get,

$$i_{o,avg} = \frac{1}{2} t_{f1} i_{L1,pk} + \frac{1}{2} t_{f2} i_{L2,pk}$$

(2.14)

where,

$$t_{f1} = \frac{i_{L1,pk}}{V_o} L_1 \tag{2.15}$$

$$t_{f2} = \frac{i_{L2,pk}}{V_0} L_2 \tag{2.16}$$

$$i_{L1,pk} = \frac{v_{in}(t)}{L_1} D_{1,on} T_s \tag{2.17}$$

$$i_{L2,pk} = \frac{v_{in}(t)}{L_2} D_{2,on} T_s \tag{2.18}$$

Thus the average output over one switching cycle can be given as

$$i_{o,avg} = \frac{1}{2} \left( \frac{i_{L1,pk}^2}{V_o} L_1 + \frac{i_{L2,pk}^2}{V_o} L_2 \right)$$

(2.19)

$$=\frac{v_{in}^{2}(t)T_{s}}{V_{o}}\left(\frac{D_{1,on}^{2}L_{2}+D_{2,on}^{2}L_{1}}{L_{1}L_{2}}\right)$$

(2.20)

The average output current  $I_{o,avg}$  over a line period is calculated by integration of the switching cycle average output current and can be given as

$$I_{o,avg} = \frac{1}{2\pi} \int_0^{2\pi} i_{o,avg} d\omega t$$

(2.21)

$$I_{o,avg} = \frac{V_{in,pk}^2 T_s}{4V_o} \left( \frac{D_{1,on}^2 L_2 + D_{2,on}^2 L_1}{L_1 L_2} \right)$$

(2.22)

where  $D_{1,on} = D_{2,on} = D$ , D = duty cycle.

# 2.4.2 Input current

Assuming the lossless circuit, i.e., 100% efficiency, the input power of is equal to the output power

$$v_{in}i_{in} = v_o i_{o,avg} \tag{2.23}$$

Substituting (2.20) in (2.23)

$$v_{in}i_{in} = \frac{v_{in}^2(t)T_s}{2} \left( \frac{D_{1,on}^2 L_2 + D_{2,on}^2 L_1}{L_1 L_2} \right)$$

(2.24)

$$i_{in} = \frac{v_{in}(t)T_s}{2} \left( \frac{D_{1,on}^2 L_2 + D_{2,on}^2 L_1}{L_1 L_2} \right) = \frac{V_{in,pk}T_s}{2} \left( \frac{D_{1,on}^2 L_2 + D_{2,on}^2 L_1}{L_1 L_2} \right) \sin(\omega t)$$

(2.25)

$$i_{in} = I_{in,pk} \sin(\omega t) \tag{2.26}$$

where,

$$I_{in,pk} = \frac{V_{in,pk}T_s}{2} \left( \frac{D_{1,on}^2 L_2 + D_{2,on}^2 L_1}{L_1 L_2} \right)$$

(2.27)

Since the duty cycle of the converter is constant in DCM, the relation given by (2.26) indicates the UPF operation of the converter and the input current is sinusoidal with peak current  $I_{in,pk}$  given by (2.27). The higher switching order harmonics present in the input currents will be filtered out by the input inductors and result in low input current THD.

#### 2.4.3 DCM operation and critical conduction parameter

Following inequalities must hold for DCM operation Fig. 2.4

$$I_o < \Delta i_{L1} + \Delta i_{L2} \tag{2.28}$$

$$I_o < \frac{V_{in.pk}T_s}{2V_o} \left( \frac{D_{1,on}L_2 + D_{2,on}L_1}{L_1 L_2} \right)$$

(2.29)

where,

$$I_o = \frac{DV_{in,pk}}{(1-D)*R} \tag{2.30}$$

$$K_{crit} > \frac{4L_1L_2}{RT_s(L_1 + L_2)} \tag{2.31}$$

To maintain DCM for all cases, the critical conduction parameter is given as  $K_{crit}$

$$K_{crit}(D) = 1 - D \tag{2.32}$$

This can also be expressed in terms of critical load resistance  $R_{crit}$ . Thus equation can be expressed as

$$R_{crit} > \frac{4L_1L_2}{D_{crit}T_s(L_1 + L_2)} \tag{2.33}$$

Critical duty cycle  $D_{crit}$  is calculated in order to maintain DCM for all cases. To maintain DCM at all times

$$t_{on1} + t_{f1} + t_{on2} + t_{f2} < T_s (2.34)$$

$$D\left(1 + \frac{1}{M}\sin(\omega t)\right) < 1\tag{2.35}$$

where

$$M = \frac{V_o}{V_{in,pk}}$$

Average output current is given by

$$I_{o,avg} = \frac{V_o}{R} \tag{2.36}$$

$$D = M\sqrt{K_{cond}} \tag{2.37}$$

where  $K_{cond}$  is the conduction parameter for is interleaved buck-boost and is defined in equation (2.37). The critical value of  $K_{cond}$  to keep the converter in DCM is

$$K_{crit} = \frac{1}{2(M+1)^2} \tag{2.38}$$

### 2.4.4 Design of inductor

To ensure PFC, the inductor needs to be in DCM for worst-case input voltage as input current will be maximum for that case. The inductor can be computed as follows,

$$L < \frac{V_{in,pk}^2 D^2 T_s}{2P_0} \tag{2.39}$$

A value below this critical inductor value should be selected in order ensure DCM operation. Due to

# 2.4.5 Design of output capacitor

In PFC converters, the output capacitor is designed to filter the harmonic components occurring at twice the line frequency. Thus, the variation in the power (input and output) discharges through the output filter capacitor and is expressed as

$$P_c(t) = P_{ac}(t) - P_o(t) (2.40)$$

$$V_o i_c = V_{in,pk} I_{in,pk} cos2\omega t - V_o I_o$$

(2.41)

Considering efficiency equal to 100%,

$$i_c(t) = \frac{V_{in,pk}I_{in,pk}}{V_o}cos2\omega t = I_ocos2\omega t$$

(2.42)

The output voltage ripple equation is given by,

$$V_{o,ripple}(t) \approx \frac{1}{C} \int i_c(t)dt$$

(2.43)

By putting (2.21) into equation (2.22),

$$V_{o,ripple}(t) \approx \frac{1}{C} \int i_c(t)dt$$

(2.44)

$$C = \frac{I_o}{2\omega V_{o\,rinnle}} \tag{2.45}$$

# 2.4.6 Design of input filter

Input current in an interleaved DCM buck-boost converter is defined as

$$i_{in}(t) = \begin{cases} \frac{v_{in}(t)}{L}, & 0 < t \le t_{on} \\ 0, & t_{on} < t \le T_{s} \end{cases}$$

(2.46)

On performing FFT of input current using (2.2), we get

$$a_0 = \frac{v_{in}(t)}{L} D^2 T_s \tag{2.47}$$

$$a_{h} = \frac{v_{in}(t)}{2\pi h f_{sw} L} \left( D sin(2\pi h D) + \frac{1}{2h\pi} cos(2\pi h D) - \frac{1}{2h\pi} \right)$$

(2.48)

$$b_h = \frac{v_{in}(t)}{2\pi h f_{sw} L} \left( \frac{\sin(2\pi hD)}{2h\pi} - D\cos(2\pi hD) \right)$$

(2.49)

Equation (2.47) indicates the fundamental component of the input current and (2.47), (2.49) indicates the switching order harmonics present, which needs to be filtered out. Upon comparing (2.3) and (2.4) with (2.48) and (2.49), it is noted that unlike conventional boost converter the proposed converter does not inject higher lower order amplitude harmonics in the input and thus requires a small filter. By designing a low-pass LC filter with a cutoff frequency much lower than the switching frequency, the harmonic currents can be filtered out.

The criteria to design low-pass LC Filter is as follows:

1) Selection of cut-off frequency  $f_c$  given by

$$f_c = \frac{1}{2\pi} \sqrt{\frac{1}{L_f C_f}}$$

(2.50)

2) Minimization of filter reactive power consumption for 60 Hz at 1.0 kW. The reactive power is minimum when filter characteristic impedance is equal to the converter impedance i.e.

$$Z_{ch} = \sqrt{\frac{L_f}{C_f}} = Z_{in} \tag{2.51}$$

where  $Z_{ch}$  is the characteristic impedance and  $Z_{in}$  is the input impedance at rated load and is given by

$$Z_{in} = \frac{2L}{D^2 T_s} \tag{2.52}$$

Using (2.51) and (2.52), the low-pass filter parameters  $L_f$  and  $C_f$  can be obtained as

$$L_f = \frac{Z_{ch}}{2\pi f_c} \tag{2.53}$$

$$L_{f} = \frac{Z_{ch}}{2\pi f_{c}}$$

$$C_{f} = \frac{1}{2\pi Z_{ch} f_{c}}$$

(2.53)

#### Converter small signal model 2.5

The small-signal model of the proposed converter is obtained by using current injected equivalent circuit approach (CIECA) [51], [52] [53]. In this approach, the non-linear part of the circuit is

Fig. 2.5. (a) CIECA for small signal modelling. (b) Control diagram for proposed converter

linearized by injecting the average output current in a switching cycle  $(i_{o,avg})$  produced by the non-linear part into the linear part. From Fig. 2.5(a), we know that

$$\hat{\imath}_{o,avg} = \left(sC + \frac{1}{R}\right)\hat{v}_o \tag{2.55}$$

Applying perturbations to (2.22) around the steady state operating point and making the small signal approximation gives

$$\hat{i}_{o,avg} = \frac{V_{in,pk}^2 D T_s}{L V_o} \hat{d} + \frac{V_{in,pk} D^2 T_s}{L V_o} \hat{v}_{in,pk} - \frac{i_{o,avg}}{V_o} \hat{v}_o$$

(2.56)

On equating (2.55) and (2.56) and substituting  $\hat{v}_{in,pk} = 0$ ,

$$G(s) = \frac{v_o(s)}{d(s)} = \frac{2V_o}{M\sqrt{K_{cond}}(sRC + 2)}$$

(2.57)

DSP TMS320F28335 is used as a digital control platform to implement the converter control. Hall Effect sensor LV 25-P is used to sense the output voltage across the load. The sensed voltage and

Table 2.1: Design Specifications.

| Parameters                                  | Value                                  |

|---------------------------------------------|----------------------------------------|

| Source Voltage, Vs (rms)                    | $110V \pm 25\%, 60 \text{ Hz}$         |

| Output Voltage, Vo                          | 65V                                    |

| Output Power, Po                            | 1 kW                                   |

| Output voltage ripple, $V_o$ , ripple $(t)$ | 5% of output voltage (V <sub>o</sub> ) |

| Switching frequency, f <sub>s</sub>         | 50 kHz                                 |

reference voltage are compared, and the error is fed to the PI Controller which generates the control signal  $d_{con}$ . This  $d_{con}$  is fed into a comparator with sawtooth signal shifted by  $180^o$  in order to generate pulses for interleaving operation Fig. 2.5(b).

#### 2.6 Results and Discussion

This section presents the simulation and experimental results of the proposed converter along with a comparison with other state-of-art topologies.

#### 2.6.1 Simulation Results

This sub-section presents the simulation results of the proposed battery charger on PSIM 11.1 software. The converter is designed with the specifications mentioned in Table 2.1, and the designed parameters are given in Table 2.3. The input LC low-pass filter is designed for a cut-off frequency of 5 kHz. The control-to-output transfer function is obtained by using (2.53) and is given by (2.58)

$$G(s) = \frac{498.82}{0.0124s + 1} \tag{2.58}$$

As the transfer function is a single pole system, a simple PI controller  $\left(K_p + \frac{K_i}{s}\right)$  given by (2.59) is used to control the output voltage as shown in Fig. 2.5(b). As the output capacitor sees a voltage ripple of twice the line frequency, a PI controller with bandwidth lower than the 120Hz is selected with a phase margin of 60°. The controller is tuned using sisotool in Matlab and the controller is designed at a gain crossover frequency of 314.4 rad/sec.

Fig. 2.6. Bode plot with plant G(s), controller H(s) and open loop transfer function G(s)\*H(s)

Fig. 2.6 shows the frequency response of plant transfer function G(s), controller transfer function H(s) and open loop transfer function G(s)\*H(s). The open loop transfer function has an infinite dc gain which indicates the system reference tracking with zero steady state error, and the system robustness for input and load disturbances. The open loop phase margin of  $60^{\circ}$  indicates enough damping of the system and the -20 dB slope at zero gain crossover frequency indicates system robustness towards the high frequency noise rejection. The sensed voltage is compared with the reference voltage and error is fed into the PI controller. The PI controller generates the duty cycle to control switch  $SW_1$  and  $SW_2$ . A limiter is connected in order to limit the duty cycle during startup and overload conditions.

With the designed controller, a closed-loop simulation for the proposed converter is performed in PSIM11 software, and the results are depicted in Fig. 2.7. Fig. 2.7 (a) shows the input voltage and current waveform of the proposed battery charger. Input current is perfectly sinusoidal and in phase with the input voltage thus confirming UPF operation of proposed configuration. Fig. 2.7 (b) shows the output voltage and current of the single stage charger at rated power of 1.0 kW. The output

$Fig.\ 2.7.\ (a)\ Input\ voltage\ and\ current\ (b)\ output\ voltage\ and\ current\ (c)\ Interleaving\ operation\ of\ DCM\ inductor\ (d)\ (e)\ input\ voltage\ swell\ (f)\ input\ voltage\ dip\ (g)\ load\ change\ from\ 500\ W\ to\ 1.0\ kW\ (h)\ load\ change\ from\ 500\ W\ to\ 1.0\ kW\ .$

voltage is constant and settled at a reference value of 65 V. Interleaving and DCM operation of the buck-boost converter is shown in Fig. 2.7 (c). Inductor currents are discontinuous thus validating the design. Fig. 2.7(d) shows the diode current waveform of the interleaved converter. It is observed as the diode current is zero in every switching cycle, zero reverse recovery losses occur in such converters which boosts up the efficiency. Fig. 2.7 (e) and Fig. 2.7 (f) show the converter response to input voltage variation from 110V to 80 V and 110V to 130 V respectively. Output voltage is maintained nearly constant with a small fall and rise during voltage dip and voltage swell conditions. The output voltage remains stable and closely tracks the reference voltage which confirms the controller design. Input current is maintained sinusoidal and in-phase with input voltage throughout its operation. The output voltage and input current of the converter when subjected to a load step change from 50% to 100% and 100% to 50% of the rated power are shown in Fig. 2.7(g) and Fig. 2.7(h). It is observed that the output voltage is closely tracking the reference voltage and settled within the settling time of 30ms, which confirms the robustness of the

Fig. 2.8 Hardware Prototype.

Table 2.2: Component Specification

| Components       | Two Cell Specifications          |

|------------------|----------------------------------|

| MOSFET           | UJ3C065030K3S, SIC               |

| Diode            | RURG80100                        |

| Input filter     | $110\mu H$ ,1140-221K-           |

| inductor         | RC/2                             |

| Input filter Cap | $0.22\mu F * 4,480 \text{ VAC},$ |

|                  | R76QR32204030J                   |