# ON THE IMPROVING OF APPROXIMATE COMPUTING QUALITY ASSURANCE

Alain F.M. Aoun

A THESIS IN THE DEPARTMENT OF COMPUTER AND ELECTRICAL ENGINEERING

Presented in Partial Fulfillment of the Requirements For the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

> May 2021 ⓒ Alain F.M. Aoun, 2021

#### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

#### By: Alain F.M. Aoun Entitled: On the Improving of Approximate Computing Quality Assurance

and submitted in partial fulfillment of the requirements for the degree of

#### Master of Applied Science

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining commitee:

| Abdessamad Ben Hamza |

|----------------------|

| Otmane Ait Mohamed   |

| Sofiène Tahar        |

Approved \_\_\_\_\_\_

Dr. Yousef R. Shayan, Chair of the ECE Department

May 5, 2021

Dr. Mourad Debbabi, Dean, Faculty of Engineering and Computer Science

### Abstract

### On the Improving of Approximate Computing Quality Assurance

#### Alain F.M. Aoun Concordia University 2021

Approximate computing (AC) has been predominantly recommended for implementation in error-tolerant applications as it offers a reduced resource usage, e.g., area and power, for a trade-off in output quality. However, AC implementation has not been adopted in commercial designs yet as it is still falling short in providing a good enough quality. Thus, continued research in the field in the field of improving quality of AC designs is indispensable. In this direction, a recent study exploited the use of machine learning (ML) to improve output quality. Nonetheless, the idea of quality assurance in AC designs could be improved in many aspects.

In the work we present in this thesis, we propose a few practical methods to improve an ML-based quality assurance methodology, which consist of an ML-model that select the most suitable design from a library of AC circuits. For instance, we extend the library of AC designs used for the ML-based approach with larger data path circuits. Larger designs, however, result in an exponential growth of complexity. Thus we propose the use of data pre-processing in order to reduce this hurdle by prioritizing designs based on their physical properties.

Another direction of improving AC circuits designs in general, and the ML-based model in particular is design space exploration (DSE). We therefore propose a novel DSE that drastically reduces the design space based on the aimed targets for area, latency and power of the AC circuit. Moreover, even with a narrowed design space, the number of AC designs to be assessed for their quality could be enormous. Thus, as part of this thesis, we propose a DSE that uses an intricate mathematical modeling for designs to assess their quality.

In another effort in improving quality assurance for AC design, we introduce a highly reliable model that uses a minimal overhead. This work is achieved by using redundant AC modules to form an approximate quadruple modular redundancy (AQMR) design. The proposed AQMR is superior to the exact triple modular redundancy (TMR) by offering a better reliability on top of the resource savings resulting from the implementation of AC. In loving memory of my Godfather, my guardian angel, my uncle, To my father, my mother, my sister and brothers.

# Acknowledgments

First, I would like to thank my supervisor, Prof. Sofiène Tahar, for his valuable feedback, support, and encouragement throughout my master thesis. He was always available to share his experience and knowledge which helped in keeping my study on-track. Moreover, during my study under his supervision, I learned a lot about research which helped me improving my abilities in this field. In summary, I can say that I am beholden for his valuable time and effort that he has spent helping me achieving this milestone. Also, I am grateful for the extremely valuable feedback that Dr. Osman Hasan has offered throughout my research. Moreover, I am beholden to Dr. Mahmoud Masadeh, who was more than a colleague at the Hardware Verification Group (HVG) but also inspirational throughout my work, and was always available when needed, to provide support and brainstorm ideas.

I am also deeply grateful for Prof. Abdallah Kassem who was my supervisor at Notre Dame University for my undergraduate studies. Through his endless support and feedback, I acquired a lot of knowledge that was the essence for my Master's study. Moreover, I would like to thank him for introducing me to Prof. Sofiène Tahar, which I consider was one of the best things that ever happened to me.

I would also like to express my gratitude for Dr. Abdessamad Ben Hamza and Dr Otmane Ait Mohamed for serving on my advisory thesis committee and taking the time from their busy schedules to read and evaluate my thesis.

I am very thankful for my friends and colleagues at HVG, specially Yassmeen El-Derhalli, Hassnaa El-Derhalli, Saif Najmeddin, Mohamed Abdelhamid and Mohamed Wagdy Abdelghany, whom made me feel welcomed by a family upon joining HVG. Their company, guidance and the help offered when needed was generously overwhelming.

Finally, I would like to express my deepest gratitude for my family, i.e., my mother, my father, my sister and brothers, for their endless love and support throughout my

life, and specifically through this journey. Their embracement made the hard days and chaos of the year 2020 much easier. Last but by no mean the least, I would like to thanks my friends in Montreal whom I call my second family. My sincere gratefulness to my friends from the families of Khalifeh, Saliba and El Kadiri for their honest and great love.

# Table of Content

| $\mathbf{Li}$          | st of          | Figur  | es                                                    | x    |

|------------------------|----------------|--------|-------------------------------------------------------|------|

| $\mathbf{Li}$          | st of          | Table  | s                                                     | xii  |

| $\mathbf{L}\mathbf{i}$ | st of          | Acro   | nyms                                                  | xiii |

| 1                      | Intr           | oduct  | ion                                                   | 1    |

|                        | 1.1            | Conte  | ext                                                   | 1    |

|                        | 1.2            | Motiv  | ration                                                | 2    |

|                        | 1.3            | Sate-o | of-the-Art                                            | 3    |

|                        |                | 1.3.1  | Approximate Circuits                                  | 4    |

|                        |                | 1.3.2  | ML-based Quality Assurance for AC Design              | 5    |

|                        |                | 1.3.3  | Design Space Exploration for AC                       | 6    |

|                        |                | 1.3.4  | Error Models of Approximate Design                    | 7    |

|                        |                | 1.3.5  | Boolean Calculus Modeling                             | 8    |

|                        |                | 1.3.6  | Modular Redundancy to Improve Reliability             | 8    |

|                        | 1.4            | Probl  | em Statements                                         | 10   |

|                        | 1.5            | Prope  | sed Methodology                                       | 10   |

|                        | 1.6            | Thesis | s Contributions                                       | 13   |

|                        | 1.7            | Thesis | s Organization                                        | 14   |

| <b>2</b>               | $\mathbf{Ext}$ | ended  | Implementation of ML-Based Quality Assurance          | 15   |

|                        | 2.1            | Intro  | luction                                               | 15   |

|                        | 2.2            | Challe | enges Extending the ML-based Quality Assurance for AC | 17   |

|                        | 2.3            | Prope  | sed Solution                                          | 18   |

|                        | 2.4            | Exper  | imental Results                                       | 20   |

|                        |                | 2.4.1  | Simulating Extended Model                             | 20   |

|                        |                | 2.4.2  | Quantazing & Reducing Training Data                   | 20   |

|          |        | 2.4.3   | Building the ML-Based Design Selector                     | 22 |

|----------|--------|---------|-----------------------------------------------------------|----|

|          |        | 2.4.4   | Quality Check                                             | 24 |

|          | 2.5    | Summ    | nary                                                      | 27 |

| 3        | Des    | ign Sp  | ace Exploration for Approximate Circuits                  | 29 |

|          | 3.1    | Introd  | luction                                                   | 29 |

|          | 3.2    | Design  | n Space Reduction                                         | 32 |

|          |        | 3.2.1   | Position-Independent Constraint                           | 33 |

|          |        | 3.2.2   | Position-Dependent Constraint                             | 33 |

|          | 3.3    | Mathe   | ematical Modeling                                         | 35 |

|          |        | 3.3.1   | Decimal to Binary                                         | 36 |

|          |        | 3.3.2   | Logic Operators Equivalence                               | 38 |

|          | 3.4    | Exper   | imental Results                                           | 38 |

|          |        | 3.4.1   | Applying the Proposed DSE on a 16-bit Array Multiplier    | 39 |

|          |        | 3.4.2   | Extending the Proposed DSE to other AC Designs $\ldots$ . | 42 |

|          | 3.5    | Summ    | nary                                                      | 46 |

| 4        | Apj    | oroxim  | nate Quadruple Module Redundancy                          | 47 |

|          | 4.1    | Introd  | luction                                                   | 47 |

|          | 4.2    | Propo   | sed System Architecture                                   | 49 |

|          | 4.3    | Exper   | imental Results                                           | 51 |

|          |        | 4.3.1   | Area and Power Assessment                                 | 51 |

|          |        | 4.3.2   | Accuracy Assessment                                       | 51 |

|          |        | 4.3.3   | Reliability Assessment                                    | 54 |

|          | 4.4    | Summ    | nary                                                      | 56 |

| <b>5</b> | Cor    | nclusio | ns and Future Work                                        | 57 |

|          | 5.1    | Concl   | usions                                                    | 57 |

|          | 5.2    | Future  | e Work                                                    | 58 |

| Bi       | ibliog | graphy  |                                                           | 60 |

| Bi       | iogra  | phy     |                                                           | 67 |

# List of Figures

| 1.1 | ML-Based Quality Assurance for AC Design                                 | 6  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | DSE for ACusing AUGER Tool [22]                                          | 7  |

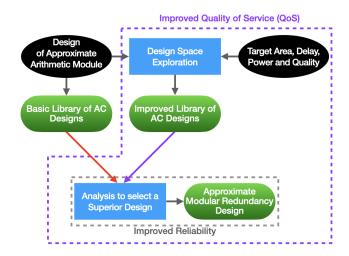

| 1.3 | General Overview of the Proposed Thesis Methodology                      | 12 |

| 2.1 | Structure of an 8-bit Array Multiplier                                   | 15 |

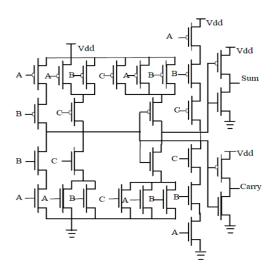

| 2.2 | Schematic of Conventional Mirror Full Adders [17] $\ldots \ldots \ldots$ | 16 |

| 2.3 | Structure of Design 3                                                    | 17 |

| 2.4 | Improved ML-Based Quality Assurance                                      | 19 |

| 2.5 | The Structure of the Constructed DT-Model                                | 23 |

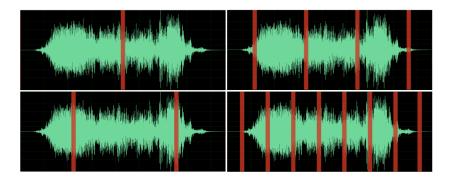

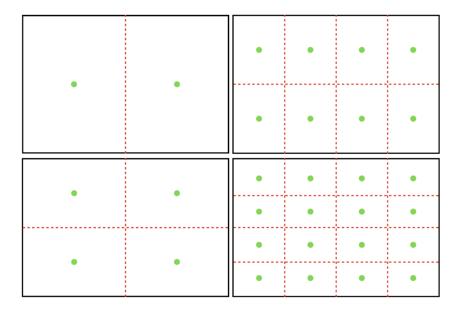

| 2.6 | Pattern used to Sample Audio Files                                       | 25 |

| 2.7 | Pattern used to Sample Images                                            | 25 |

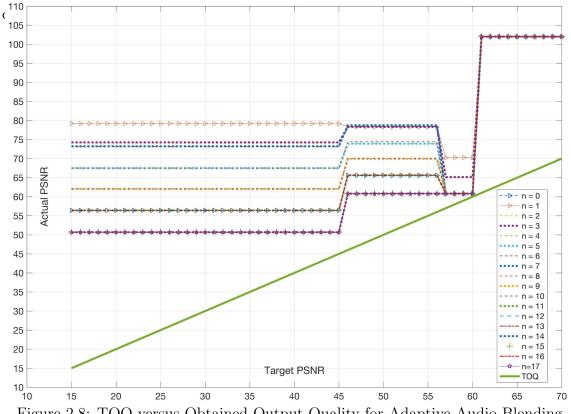

| 2.8 | TOQ versus Obtained Output Quality for Adaptive Audio Blending           | 26 |

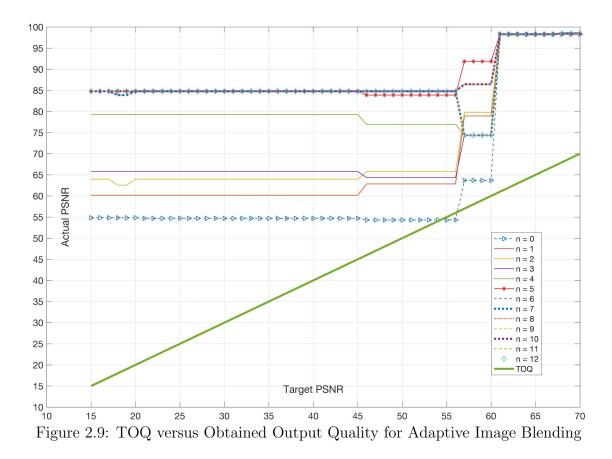

| 2.9 | TOQ versus Obtained Output Quality for Adaptive Image Blending           | 27 |

| 3.1 | Architecture of a 16-bit Array Multiplier                                | 30 |

| 3.2 | Proposed Design Space Exploration for AC Design                          | 31 |

| 3.3 | Frequency of Delay for 1 Million Randomly Generated Configurations       | 35 |

| 3.4 | Graphical Representation of the proposed $h(x)$                          | 37 |

| 3.5 | Configuration of Array Multiplier Consisting of Multiple types of Ap-    |    |

|     | prox. FAs                                                                | 42 |

| 3.6 | Structure of a Basic 16-bit Multiply and Accumulate Unit $[24]$          | 43 |

| 3.7 | Approximate Divider [20]                                                 | 44 |

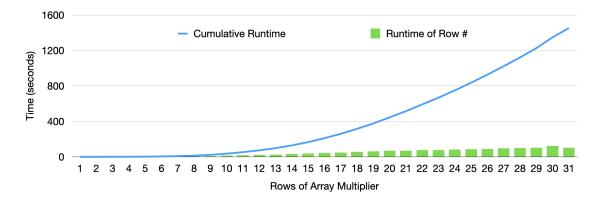

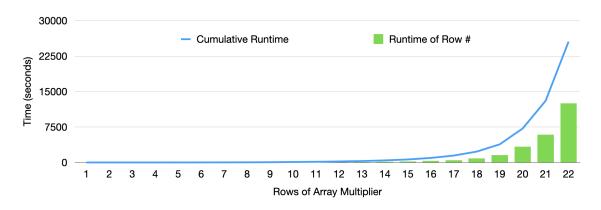

| 3.8 | Runtime to Generate Output Equations for a 32-bit Array Multiplier       | 45 |

| 3.9 | Runtime to Generate Some of the Output Equations for a 64-bit Array      |    |

|     | Multiplier                                                               | 45 |

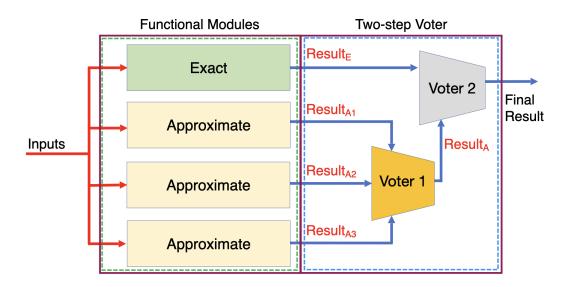

| 4.1 | Integrating Modular Redundancy for Improved AC Quality of Service        | 48 |

| 4.2 | Architecture of Approximate Quadruple Modular Redundancy                 | 50 |

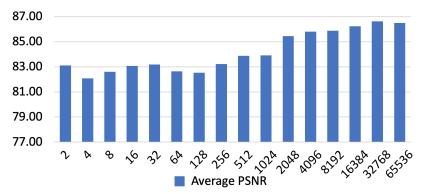

| 4.3 | Average PSNR in $dB$ for Different Numbers of Clusters $\ldots \ldots$   | 53 |

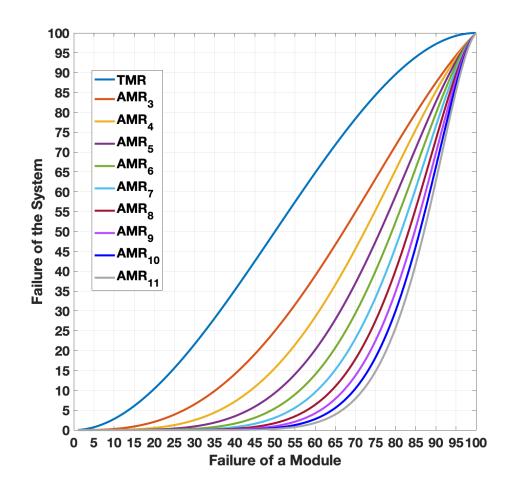

| 4.4 | Relative Probability of System Failure vs Component Failure for Dif- |    |

|-----|----------------------------------------------------------------------|----|

|     | ferent Module Redundancy Circuits                                    | 55 |

# List of Tables

| 1 | Library of 20 Static Approximate Designs based on Degree and Type                                                                           |    |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | $[27] \ldots \ldots$ | 16 |

| 2 | Design Characteristics of the Approximate Library, i.e., Power, Area,                                                                       |    |

|   | Delay and Power-Area-Delay Product (PADP)                                                                                                   | 21 |

| 3 | The Number of Training Entries of each Approximate Design After                                                                             |    |

|   | Pre-processing                                                                                                                              | 22 |

| 4 | Decimal to Binary Conversion for $X = 19$                                                                                                   | 37 |

| 5 | Logic-Arithmetic Equivalence                                                                                                                | 38 |

| 6 | Synthesis of used FAs                                                                                                                       | 39 |

| 7 | Simulation-Based Quality Assessment of Chosen Designs                                                                                       | 41 |

| 8 | The Percentage $(\%)$ of Fault Detection if the Exact Module is Faulty                                                                      | 52 |

| 9 | The Percentage (%) of Fault Detection if the Approximate Module is                                                                          |    |

|   | Faulty                                                                                                                                      | 53 |

# List of Acronyms

| $\operatorname{AC}$                                  | Approximate Computing                                                                                                                                                                  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMA                                                  | Approximate Mirror Adder                                                                                                                                                               |

| ANN                                                  | Artificial Neural Netowrk                                                                                                                                                              |

| AQMR                                                 | Approximate Quadruple Modular Redundancy                                                                                                                                               |

| ATMR                                                 | Approximate Triple Modular Redundancy                                                                                                                                                  |

| AUGER                                                | Apprximate Units Generator                                                                                                                                                             |

| BDD                                                  | Binary Decision Diagram                                                                                                                                                                |

| BER                                                  | Bit-Error Rate                                                                                                                                                                         |

| DMR                                                  | Dual Modular Redundancy                                                                                                                                                                |

| DSE                                                  | Design Space Exploration                                                                                                                                                               |

| DT                                                   | Decision Tree                                                                                                                                                                          |

| ED                                                   | Error Distance                                                                                                                                                                         |

| FA                                                   | Full Adder                                                                                                                                                                             |

| GA                                                   | Genetic Algorithm                                                                                                                                                                      |

| НА                                                   | Half Adder                                                                                                                                                                             |

|                                                      |                                                                                                                                                                                        |

| HDL                                                  | Hardware Description Language                                                                                                                                                          |

| HDL<br>HPC                                           | Hardware Description Language<br>High Performance Computer                                                                                                                             |

|                                                      | - • •                                                                                                                                                                                  |

| HPC                                                  | High Performance Computer                                                                                                                                                              |

| HPC<br>IoT                                           | High Performance Computer<br>Internet of Things                                                                                                                                        |

| HPC<br>IoT<br>k-NN                                   | High Performance Computer<br>Internet of Things<br>k-nearest neighbors                                                                                                                 |

| HPC<br>IoT<br>k-NN<br>LR                             | High Performance Computer<br>Internet of Things<br>k-nearest neighbors<br>Linear Regression                                                                                            |

| HPC<br>IoT<br>k-NN<br>LR<br>LSB                      | High Performance Computer<br>Internet of Things<br>k-nearest neighbors<br>Linear Regression<br>Least Significant Bit                                                                   |

| HPC<br>IoT<br>k-NN<br>LR<br>LSB<br>LUT               | High Performance Computer<br>Internet of Things<br>k-nearest neighbors<br>Linear Regression<br>Least Significant Bit<br>Lookup Table                                                   |

| HPC<br>IoT<br>k-NN<br>LR<br>LSB<br>LUT<br>MAC        | High Performance Computer<br>Internet of Things<br>k-nearest neighbors<br>Linear Regression<br>Least Significant Bit<br>Lookup Table<br>Multiply and Accumulate                        |

| HPC<br>IoT<br>k-NN<br>LR<br>LSB<br>LUT<br>MAC<br>MED | High Performance Computer<br>Internet of Things<br>k-nearest neighbors<br>Linear Regression<br>Least Significant Bit<br>Lookup Table<br>Multiply and Accumulate<br>Mean Error Distance |

| NN   | Neural Netowrk               |

|------|------------------------------|

| PADP | Power-Area-Delay Product     |

| PC   | Personal Computer            |

| PEA  | Probabilistic Error Analysis |

| PSNR | Peak to Signal Noise Ratio   |

| QMR  | Quadruple Modular Redundancy |

| QoS  | Quality of Service           |

| RF   | Random Forest                |

| RGB  | Red Green Blue               |

| SEU  | Single-Event Upset           |

| SOP  | Sum of Product               |

| TMR  | Triple Modular Redundancy    |

| TOQ  | Target Output Quality        |

|      |                              |

### Chapter 1

## Introduction

In this chapter, we first present the context and motivation behind this thesis followed by a review for the state-of-the-art and the problem statement. We conclude the chapter by outlining the main contributions and the organization of the thesis.

#### 1.1 Context

The discovery of transistors in the 20th century and their implementation in computers changed the life on earth forever. Computers nowadays are integrated in day to day activities, e.g., communication and transportation. This deep integration has been achievable by reducing feature size, which enabled the fit of more transistors on a given die. However, this advancement has seen a slower pace in the last few years and computer architecture design has shifted from solely fitting more transistors to architecture modifications, such as the superscalar architecture and multicore processors, etc. These variations in the computer architecture allowed computers to cope with most of the current demands. Nonetheless, improving some of these advanced implementations have or will soon reach its saturation and computers might struggle in the near future to deliver the computation required with the booming of Internet of Things (IoT) and cloud based services. Furthermore, recent chip famine caused by COVID-19 pandemic and its impact on many industries, e.g., automotive [1] and phones [50], demonstrate the vulnerability of chip manufacturing and indicate that a drastic resource optimization, e.g., transistors used to perform a given process, must take place. The work in this thesis offers a solution to this dilemma by offering a reduced resource usage, i.e., area and power, while preserving an acceptable quality of service (QoS), i.e., output quality and reliability.

#### 1.2 Motivation

Approximate Computing (AC), which is well known as best-effort computing, is a nascent computing paradigm that is suitable for error-tolerant applications, e.g., search engines [38], multimedia [38] and big-data analysis [42], which do not require an accurate result. These applications exhibit *intrinsic error-resilience* due to the following factors [53]: (i) iterating and noisy input data; (ii) absence of golden or sole output; (iii) imprecise sense of humans; and (iv) implementing algorithms with self-healing and error attenuation patterns. Based on these concepts, AC could be the essence in delivering the computation power required in the future as it offers a significantly reduced usage of resources.

Diverse approximation techniques in the levels of software and hardware have been investigated by industry and academia, such as IBM [42], Intel [37] and Microsoft [10]. AC in hardware results in a reduced area, delay and power requirements by compromising the accuracy of computation. Such reductions can be achieved by reducing transistor count, e.g., altering logic gates [17], voltage over scaling [41] or bit-wise truncation [20]. The development of circuits aiming to deliver approximate adders, multipliers, dividers have been researched, yet this development has not matured since the perfect trade off, i.e., Golden Goal, in the four dimensions of AC design, i.e., area, delay, power and quality, is not achieved so far. Moreover, for circuits designed with AC in mind, the error persists during the operational-life. Such error in the circuit is classified as hard-error [46]. Nonetheless, many of the proposed approximate designs offer promising results in quality assurance and if improved, an implementation in end-user devices could take place. Thus, future development of AC circuits should be driven by:

1- Implications of Approximation: Some modifications that result in the design of an AC circuit could be a little advantageous in some dimensions of AC design, while being very diminishing in the remaining aspects, e.g., improved latency with deteriorated output quality. Hence, the design of approximate circuits is a delicate process that must be carefully practiced. 2- Assessing Quality: Output quality assessment and verification of approximate circuits are open challenges with the quality mainly relying on excessive simulation. With larger circuits, an exponential growth in time complexity, e.g., possible inputs combinations of a 16-bit multiplier are 64K times larger compared to the combinations of an 8-bit multiplier. Reduction in simulation time relies on randomly generating a limited set of test cases, which could result in misrepresentation of the actual quality.

3- Design Space Exploration (DSE): Most of the proposed designs have been studied in limited configurations. Furthermore, many variations can take place in these designs, which can generate a large set of undiscovered possibilities. With such large set of possibilities, the chances of finding a configuration that is near the golden goal in the four dimensions of an approximation computing design can be considered reasonable.

**4-** Approximate Failure: An approximate circuit should be designed with the notion of fail-small, fail-rare or fail-moderate where the approximated output should not result in a high loss of quality. Thus, the output-reliability must be studied carefully.

Multiple approximate circuit designs have been proposed in the literature, yet their usage for quality assurance has not matured so far. In the scope of this thesis, we propose to improve an existing quality assurance method, along with a new implementation of AC for quality assurance. In addition, we propose a design space exploration for approximate circuits.

#### 1.3 Sate-of-the-Art

In this section, we review most relevant literature in the area of quality assurance and design space exploration, which are closely related to the objective of this thesis. The literature will discuss the need for AC designs and some of the different techniques discovered so far. Moreover, this section will review state-of-the-art methods for improving quality assurance of AC designs in particular machine learning based quality assurance and design space exploration. Nonetheless, when dealing with AC designs, the main issue is quality assessment. In this area, we will review recent approaches for mathematical modeling of circuits, which can help assessing quality.

#### **1.3.1** Approximate Circuits

Due to the massive explosion in new data, i.e., big-data, for the sake of improving daily services, e.g., smart-cars, search engines etc., powerful computing machines are falling short in delivering all computations needed. Thus, creating the idea of rethinking computer architecture, in order to deliver low power consumption, small footprint, yet powerful computing machines [28] [30] [42]. Moreover, many applications are considered error-tolerant where there is no golden or single correct output, e.g., search engines. Therefore, AC is good trade-off, that can satisfy these requirements. Furthermore, AC can be achieved at the hardware or software level.

Research in approximate sub-blocks, e.g., full adders (FAs), is considered a hot topic in AC circuit design, as their implementation can go beyond the application of adders. For instance, the work in [43] used approximated FAs proposed in [17] to design an array multiplier. Another implementation of approximated FAs is building multiply and accumulate (MAC) circuits as proposed in [29]. Furthermore, research in this area is important, as multiple sub-blocks can be combined together to form a larger functional unit. This would generate a large design space to be explored, since variation at the sub-block level will create different design structure.

For this reason, various approximate hardware designs, specially functional units for arithmetic modules including adders [4] [17] [58], dividers [12] [20] [23] [36] and multipliers [19] [39] [43] [59] [61] [60], have been explored for their practical role in multiple applications. These applications are sporadically tested in computation intensive yet error-tolerant applications, which are susceptible to an approximation.

The approximation of functional units can be done at different levels of abstraction, i.e., transistor, gate, register transfer and application. Transistor-level approximation offers the uppermost versatility, since it is the bottom-line of circuit design. Variations at this level will twist most aspects of the design parameters. The work proposed in [17] is a good example of transistor-level approximation in order to build approximate FA. A similar approximation is accomplished on the gate level by Z. Yang et.al in [58]. Nonetheless, a lower level of abstraction does not guarantee an outstanding improvement in the four dimensions of AC design simultaneously [28]. The work in [28] shows that a good starting point should be a behavioral study for smaller sub-blocks. Such step can be considered as a vital assessment when designing AC circuits, since smaller sub-blocks, e.g., FA, can be used to build larger circuits.

#### 1.3.2 ML-based Quality Assurance for AC Design

The error in AC designs depends on the applied inputs [25]. This could be taken care of if the error is known at early design stages. The solution could take one of the following recently exploited forms: 1) adapting the architecture of approximate components in form of error-compensation input aware [31]; 2) partial reconfiguration as a switch among multiple AC circuits as proposed by [30] or [32]. These solutions rely on machine learning (ML) for quality assurance. ML is a computer algorithm that builds a model by learning properties of a provided training data. The trained data generates an ML-model which is then used to predict the outcome of a given input. ML is a hot topic where algorithms are constantly improved to support a wider range of models, e.g., decision tree (DT), artificial neural network (ANN) and k-nearest neighbors (k-NN) [21]. ML-algorithms are used in different types of applications, e.g., speech recognition and media description [8]. Using ML has been widely used for quality assurance for big-data where the aim is retrieving relevant information to assure quality [47]. Similarly, the work in [30] [32] exploited the use of ML-algorithms for quality assurance in AC designs.

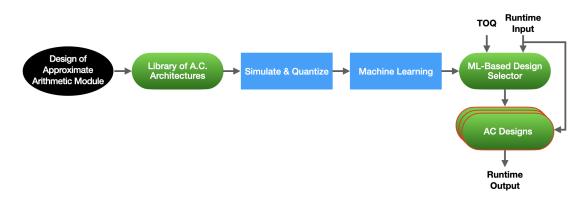

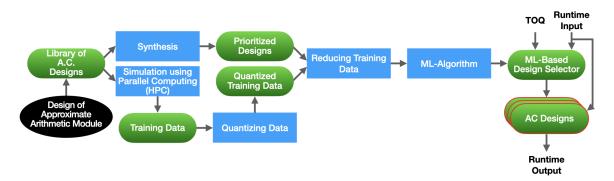

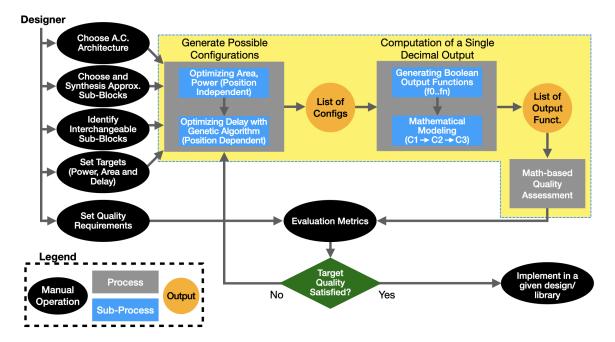

The foundation of the work done in [30] [32] is to have a knob-like setting that selects the most suitable design based on a provided target output quality (TOQ). As shown in Figure 1.1 the proposed model is constructed by first designing various approximate arithmetic modules, which will form a library of approximate designs. Output quality of all models in the library is then assessed using excessive simulation. Afterwards, error metrics, e.g., error distance (ED) and peak signal to noise ratio (PSNR), are quantized for every *n*-consecutive input entries. The quantized data is then used as a training data for the ML-algorithm, which will generate a ML-predictor. The ML-predictor will be provided with the TOQ and input data in run-time, which will select the most suitable design from a library of designs.

The proposed ML-based quality assurance approaches for AC design could be improved in many directions, and one of them is a design space exploration (DSE), which can improve the library of approximate designs.

Figure 1.1: ML-Based Quality Assurance for AC Design

#### 1.3.3 Design Space Exploration for AC

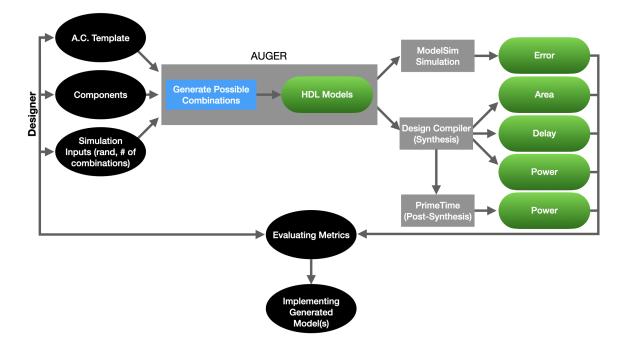

Given that the structure of approximate circuits can have multiple configurations, design space exploration (DSE) can become useful as it offers an automated generation of possible configurations. For this purpose, some tool have been developed such as Approximate Units Generator (AUGER) [22] and Automatic Design Space Exploration and Circuit Building (autoAx) [40], which generates approximate adders, multipliers, and dividers using a sub-components library [22]. Figure 1.2 depicts how the AUGER tool allows the designer to provide design specifications, such as bitwidth of the arithmetic unit, least significant bits (LSB) to be approximated, the sub-blocks type and the number of random samples to be used to measure probabilities of error distances (EDs). The tool generates hardware description language (HDL) model based on the provided requirements. The generated model is forwarded to synthesis tool for area, delay and power assessment. In addition, a post-synthesis is performed in order to have a more accurate power valuation. Finally, Figure 1.2 shows that the designer will manually assess the output quality and check the area, delay and power usage of the generated structures and choose the design satisfying the requirements. Nonetheless, a DSE is needed for AC designs, and the implementation of AUGER uses the simulation of random inputs for quality assessment. However, a small number of random inputs may not reflect the actual quality of an AC design, while a large set of samples could be time consuming for large designs.

Figure 1.2: DSE for ACusing AUGER Tool [22]

#### 1.3.4 Error Models of Approximate Design

Probabilistic error analysis (PEA) for approximate circuit designs is commonly used to measure its quality. The foundation of this approach is the assumption of equiprobability of inputs being logic 0 or 1. This equiprobability is then carried to study the probability of output bits. An excellent example of quality measurement using a probabilistic form is proposed in [35], where the authors describe a technique to build larger approximate arithmetic units recursively from an energy-efficient smaller component. The probability of error for sub-components is evaluated first. Using a recursive procedure, this probabilistic behavior is later generalized to a larger arithmetic unit. However, applying the proposed PEA in [35] to large designs, e.g., 32-bit multiplier, can be delicate. Moreover, another disadvantage of PEA is the fact that the output assessment relies on bit-error which can have irrelevant indication in some cases. For example, if an exact computation resulted in  $(16)_{10}$  while its approximated version resulted in  $(15)_{10}$ , the bit-error would indicate a 0% accuracy while the arithmetic error distance (ED) is 1. Furthermore, the bit-error could indicate a high accuracy while ED is large, e.g.  $(15)_{10}$  and  $(7)_{10}$ . These extreme cases show that looking at the bit-error may point in the wrong directions and/or may not indicate an absolute behavior of the quality. Nonetheless, the usage of mathematical notions to asses output quality of AC designs is a deviation in the right direction.

#### 1.3.5 Boolean Calculus Modeling

Calculus modeling for circuits is an alternative approach to model logic circuits, which can be applied on AC designs in order to asses their quality. This approach has been researched in the 20th century [26]. This exploration focused on canonical Boolean vector representation. This work earned the name of "Digital Calculus" since it merges Boolean calculus and binary vector Boolean calculus. Moreover, the authors developed the differential and primitives of the proposed equations. This work was poorly adopted since it lacks wide support by commercial tools for this type of equations and thus can be burdensome to deal with. Nonetheless, a calculus modeling for circuits can eliminate the need for excessive simulation, since quality assessment can be examined using mathematical equations. Hence, an alternative approach which relies on mathematical approaches that are supported by commercial tools is crucial.

#### **1.3.6** Modular Redundancy to Improve Reliability

Modern micro-architectural trends and scaling feature size, reduce the susceptibility of logic circuits to external noise such as radiation or internal noise such as variations in applied voltages [48]. Such events can result in lifetime damages (hard errors) [46], or temporary faults (soft errors) [54]. In both cases, the system can be deemed as malfunctioning. Therefore, error mitigation techniques, such as fault tolerance at both software and hardware levels are proposed in order to improve quality of service (QoS). However, the use of these techniques can significantly affect embedded systems and microprocessors as more resources are required, e.g., area and power.

Error-mitigation can be done in hardware in the fashion of components redundancy, such as double modular redundancy (DMR) and triple modular redundancy (TMR) [5]. However, error-correction modules will add a significant overhead in terms of resources, i.e., area, performance and power. To overtake this issue, selective or partial redundancy is proposed in [54]. This technique will protect sensitive components and thus reducing the overhead. Towards achieving a similar goal, the usage of AC has been researched in [44]. AC designs are attractive since they are fast and offer a low resources usage.

TMR is one of the most used technique, which consists of triplicating the module and adding a voter which will mask error, if one of the three units is faulty. The downside of TMR, is the 200% increase in area and a similar rate in power. To reduce overhead, approximate TMR (ATMR) [45] is presented for use at the hardware level. This work targets loop-based applications where approximation is achieved by using duplicate circuits that will be used for fewer iterations. Another work of ATMR is presented in [16] with the usage of an exact unit along with two approximate units. The realization of the approximate units is achieved by first finding a subset architecture for the exact unit to build the first approximate unit, followed by a subset of the approximate unit to generate the second approximate circuit. A good example that illustrates the realization of this work is an exact unit that computes  $Exact = (A \times B) + C$ , while the approximate units compute  $App_1 = (A \times B)$  and  $App_2 = A$ . This approach would allow to mitigate errors in a given sub-space. A similar approach to [45] has been explored in [49], which uses binary decision diagrams (BDDs) [11] to represent all the functions under consideration when forming the approximate circuits. Another approach of integrating AC to improve reliability is proposed in [7], with the goal here to build three different approximated versions of the exact unit to be used in parallel. Similar approach is used in [6] with the assumption that the usage of three different approximate units would generate an exact computation using a majority voter in the absence of errors, with the possibility of erroneous computation in the presence of a fault. To achieve a better quality, the usage of four different approximate units is proposed in [14] with the aim to improve the probability of achieving a better quality in the absence of faults. Even though the integration of AC has advantages in terms of reducing area and power, it has seen a limited adoption as it lacks quality assurance since all previously proposed models are either application specific, e.g., loop based applications, or designed with the assumption of achieving exact computation in the absence of faults.

#### **1.4** Problem Statements

Developed AC circuits proved to be powerful in reducing area, delay and power. However, the best trade-off to achieve the golden goal in the four dimensions of AC design is not achieved. The list below represents a series of researched work that can be considered as assets of accomplishing this goal, yet with their respective draw-back(s) such achievement is paralyzed:

1- ML-Based Quality Assurance [27]: This work, offers a noticeable improvement in quality. However, its scalability is questionable, e.g., 16-bit multipliers library instead of 8-bit, since the simulation time for an *n*-bit multiplier is almost  $2^n$  times larger compared to *m*-bit multiplier (where  $n = 2 \times m$ ). Another challenge is handling the large set of data to be classified.

2- Design Space Exploration (DSE): One way of improving AC designs is by performing a DSE. Nonetheless, previous methods of DSE for AC designs do not consider all possibilities in the design space. Nonetheless, a proper DSE must consider all possible configurations.

**3-** Quality Assessment: Output quality assessment is a vital process to any research in the field of AC. However, using excessive simulation can take an infinite amount of time. Alternatively, a mathematical approach is proposed in [35] which grants a small overhead. Nonetheless, this method suffers from inaccuracy in some cases and can become complex. Thus, research for a different quality assessment method that has a minimal overhead while offering a solid determination of quality is needed.

#### 1.5 Proposed Methodology

As discussed in the previous sections, AC designs have been proposed and tested in limited numbers of configurations. Furthermore, the usage of AC proved saving benefits in area, delay and power, in exchange for reduced output quality. Moreover, the main method used today to assess quality of AC designs is excessive simulation. Such method consumes a good amount of time and may not be feasible for large designs. In this thesis, we aim to improve the quality of service (QoS) with the use of AC circuits.

Towards achieving this goal, we study a state-of-the-art model [32], which is an ML-based design select towards the delivery of quality assurance. The study focuses

on finding the limits of the proposed model in terms of extending to larger designs. In addition, a careful examination for further quality improvement is performed. Based on these studies, we propose a methodology that overcomes the challenges by using data pre-processing to reduce the training data. Furthermore, if a design space exploration (DSE) is conducted, the library of approximate designs might be improved and maybe reduced. Therefore, these changes would benefit the quality of the proposed design.

Nonetheless, the state-of-the-art DSE generates designs in a limited number of configurations and relies on excessive simulation to assert quality. To overcome these disadvantages, we propose a novel DSE that aims to study all possible scenarios, yet robustly eliminating configurations and thus narrowing the design space. The elimination is done based on the designer's targets for area, delay and power. Moreover, the proposed DSE offers a new mathematical modeling that can be deployed on commercial tools, e.g., Matlab [34]. The modeling will then be used to assess the output quality of the candidate designs from the reduced design space.

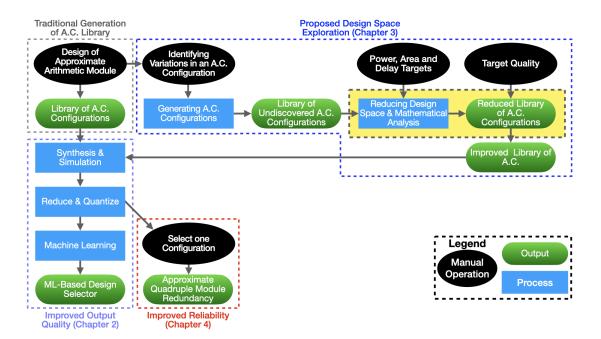

Finally, we propose a highly reliable approximate design to improve quality assurance using AC. This design uses the concept of modular redundancy in order to improve the reliability of logic circuits. The design is an approximate quadruple modular redundancy (AQMR) and consists of three approximate modules and one exact module. Figure 1.3 illustrate a general overview of the proposed methodology for improving AC quality assurance. The methodology consists of black boxes describing manual operations that the designer must perform by hand, blue boxes represent implemented computer based processes, while the green boxes are physical outputs of the individual processes. As the figure shows, the overall methodology consists of four main classes, with the manual, i.e., traditional, generation of AC designs being the base for all the remaining work. The other three components are: 1) ML-based output quality assurance which aims at improving the output quality 2) DSE which will result in an improved library of AC designs; and 3) quadruple modular redundancy (AQMR) which improves reliability yet offers a minimal overhead by using AC. These three components complement each other in the direction of improving quality assurance, i.e., QoS, with the use of AC. For instance, the the ML-based design selector could be enhanced further if an improved library of AC designs is generated by a DSE. The improvement can take place in some or all of the four dimensions of AC

Figure 1.3: General Overview of the Proposed Thesis Methodology

design, based on the designer' inputs to the DSE. Similarly, the AQMR could benefit in a similar manner by using data resulting from any of the processes for improving output quality to select the most suitable design. For instance, in Figure 1.3, AQMR is applied after data reduction and quantization.

The output quality improvement is based ML-based design selector proposed in the literature [27]. To achieve this improvement, the library of designs is first synthesized and simulated for a complete quality analysis. Thereafter, the data generated by the simulation is quantized and reduced. The reduction is based on the synthesis of the designs, which will prioritize designs in the library. Thereafter, reduced and quantized data is used as a training data for the ML-algorithm, which will generate a ML-based design selector. The generated selector will be used in runtime to predict the most suitable design delivering the aimed output quality.

The DSE is a crucial in improving the library of AC configurations. The proposed DSE consists of first identifying the variations in the proposed designs. These variations will generate a large number of undiscovered configurations. Thereafter, the library is reduced based on the targets of area, delay and power provided by the designer. This will generate a smaller library of undiscovered AC configurations. Finally, the quality of configurations in the reduced library are assessed, with designs satisfying target quality carried to form an improved library of AC configurations.

Finally, the improvement in AC design reliability will be achieved with the use of modular redundancy. As Figure 1.3 depicts, the process that consists of selecting one configuration of an AC design that is known to have a good metrics in the four dimensions of AC. The design is then used to built the proposed AQMR.

#### **1.6** Thesis Contributions

In this thesis, the work presented focuses on improving quality assurance when using AC circuits. The contributions of the thesis can be summarized as follows:

- Extending ML-based quality assurance model proposed in [32] from 8-bit to 16-bit. Moreover, the work improves the output quality by giving a priority to specific designs. To provide a relevant priority, the designs are synthesized using Xilinx Vivado [57] with the design resulting in the least power-area-delay-product (PAPD) given the highest priority [Bio-Cf2].

- A novel DSE that drastically reduces design space based on the designer's requirements, i.e., resource usage and output quality. The design space reduction is accomplished in two steps, i.e., area & power optimization and delay optimization. In addition, the presented DSE uses a calculus- based mathematical modeling for logic circuits which will revoke the use of excessive simulation and replace it with a pure mathematical examination of output quality. The use of this modeling remarkably reduces the time needed for quality assessment.

- Improving the quality of circuits by delivering higher reliability with the use of approximate circuits. This improvement is achieved by using modular redundancy. Moreover, unlike previous implementations of approximate modular redundancy, the proposed model adapt to the characteristics of AC circuits and uses a two steps voter. One of the voters is a new magnitude-based voter [Bio-Cf1].

#### 1.7 Thesis Organization

The rest of this thesis is organized as follows: in Chapter 2, the challenges of extending a previously proposed ML-based quality assurance is presented. Subsequently, we proposes a solution that reduces the training data with the aim of reducing complexity of constructing the ML-predictor which also reduces the complexity of the design in runtime. Moreover, this reduction results in an improved output quality. Finally, the currently known limits of this methodology are discussed.

In Chapter 3, we propose design space exploration by first describing the methodology used to reduce design space. Consequently, a detailed explanation of the mathematical modeling is proposed, which includes the reasoning that led to the creation of the equivalences. Lastly, a practical experiment is conducted to validate the proposed methodology.

In Chapter 4, a new approach to implement AC circuits in modular redundancy is proposed. Thereafter, a detailed assessment for resource usage, accuracy and reliability are presented. Lastly, Chapter 5 summarizes the thesis and the outlines potential future research directions.

### Chapter 2

# Extended Implementation of ML-Based Quality Assurance

This chapter represents a detailed description of the challenges in extending the work in [32], which uses 8-bit multipliers. While 8-bit designs can be used as a proof of concept; however, extensions to larger designs, e.g., 16-bit functional units, are required. This chapter also represents a possible solution for these hurdles and the outcome of the proposed solution.

#### 2.1 Introduction

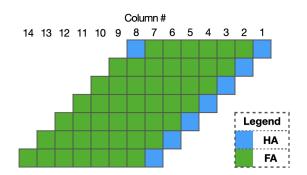

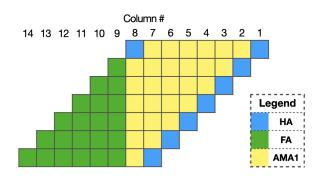

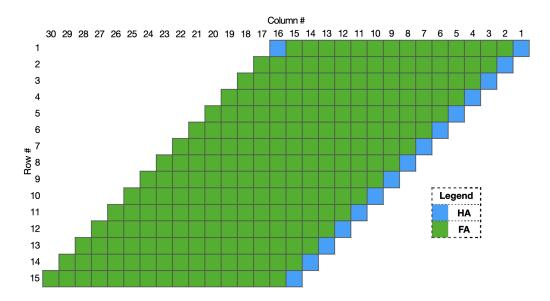

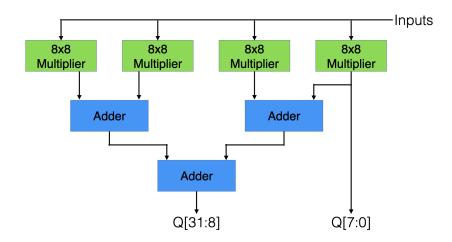

The proposed model in [32] uses 8-bit array multipliers with variations to its structure to form multiple approximated configurations. Figure 2.1 shows the structure of an 8-bit array multiplier which consists of full adders (FAs) and half adders (HAs).

Figure 2.1: Structure of an 8-bit Array Multiplier

Figure 2.2: Schematic of Conventional Mirror Full Adders [17]

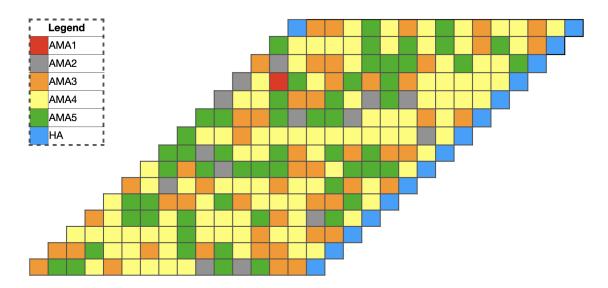

The work in [32] opted for the use of four degrees of approximation: D1, D2, D3 and D4. The chosen degrees are the number of columns in which the exact FAs are replaced with approximated ones. The selected four degrees are: 1) half of the columns, 2) half minus one column, 3) half plus one column, and 4) all columns approximated. Moreover, the authors of [32] used five well known approximate FAs proposed in [17] denoted as AMA1, AMA2, AMA3, AMA4, and AMA5, to form five types of approximate array multiplier. These five approximate FAs resulted from modifications in the exact mirror FA which is shown in Figure 2.2. The work in [17] is based on removing one set of transistors at a time to form a new approximate mirror adder (AMA). This iterative reduction of transistor count leads to a minimum count of two transistors in AMA5, i.e., two buffers. Thus, the library is composed of 20 designs, i.e., four degrees and five types, as shown in Table 1. Furthermore, the structure of *Design 3* can be seen in Figure 2.3.

| Appro   | oximate | Degree    |           |           |           |  |

|---------|---------|-----------|-----------|-----------|-----------|--|

| Designs |         | D1        | D2        | D3        | D4        |  |

|         | AMA1    | Design 1  | Design 2  | Design 3  | Design 4  |  |

|         | AMA2    | Design 5  | Design 6  | Design 7  | Design 8  |  |

| Type    | AMA3    | Design 9  | Design 10 | Design 11 | Design 12 |  |

|         | AMA4    | Design 13 | Design 14 | Design 15 | Design 16 |  |

|         | AMA5    | Design 17 | Design 18 | Design 19 | Design 20 |  |

Table 1: Library of 20 Static Approximate Designs based on *Degree* and *Type* [27]

Figure 2.3: Structure of Design 3

As proposed in [32], the modified array multipliers are used to generate a library of AC designs. Moreover, with the help of machine learning (ML), an ML-based design selector is developed in order to choose the most suitable design in runtime, which will deliver the aimed output quality. In the context of extending the models proposed in [32], we chose the implementation of 16-bit array multipliers, with the same type of FAs, and a similar approach in the degrees of approximation, which is based on four levels of column-driven approximation. Lastly, the extended implementation uses the same error metric, namely PSNR, as used in [32].

### 2.2 Challenges Extending the ML-based Quality Assurance for AC

Extending the ML-based quality assurance model proposed in [32] to larger designs comes with its challenges. Thus, in this section, we will discuss in details the main challenges, which are:

1- Simulation Time: Simulation time and possible outcomes for larger circuit have a ratio of more than 1:1. This is due to the fact that larger circuits have more components that require more simulation time. For instance, if the 8-bit and 16-bit array multipliers are to be compared, the 16-bit model is four times bigger in terms of FAs usage. This overhead alone would imply that the 16-bit simulation would require roughly four times the time to compute a single combination of inputs. On top of that, the 16-bit multiplier has more possible inputs (64K times more). Considering these two facts, it is obvious that the simulation time will be much higher for larger citcuits.

**2-** Classifying Diverse and Large Training Data: Machine learning is a computer algorithm that learns to act based on a set of training data. In the proposed model by [32],

the provided training data is composed of quantized inputs and their corresponding errors. However, when expanding to larger models, i.e., larger input-width, classification can become more challenging. For instance, for 20 approximate 16-bit multipliers, if simulation data is quantized for every 16 consecutive inputs, i.e., clusters of size  $16 \times 16$ , the number of entries for the training data is:  $\frac{20 \times (2^{16} \times 2^{16})}{16 \times 16} = 335,544,320$ . Moreover, with each entry containing a set of three data, i.e., two-inputs and corresponding error, the size of the training data to be classified by the ML-algorithm is almost 1 billion. Errors can be similar in magnitude, and thus the job can be easy for the classifier. However, the fact that errors can vary in magnitude, cannot be omitted. Thus, with the growth and possible variance of the training data, the classifier can easily fail to classify the training data, and hence aborting the process of building a ML-based design selector.

#### 2.3 Proposed Solution

For ML-algorithms, classifying large and diverse training data is a delicate process, since the computation power can be beneficial, yet not a sufficient factor to build an ML-based predictor. Furthermore, with the exponential growth of data entries mentioned earlier, larger circuits will provoke much more data. To surmount this challenge, the usage of data pre-processing can be a viable solution, which is often neglected, yet it represents a significant step in the data mining process [15]. The authors of [32] applied a class of pre-processing (quantizing); however, this pre-processing is not sufficient to handle the simulation of large circuits. Moreover, modifying the proposed pre-processing by enlarging the array of data to be quantized could potentially result in a loss of accuracy in the training data and hence might compromise the proposed quality assurance model. Nonetheless, applying other techniques can aid in reducing data, yet without the loss of indispensable data. For this reason, the reduction of entries based on given priority is proposed. A valuable priority for the AC circuits can be the Power-Area-Delay Product (PADP), with the design offering the lowest PADP, would have the highest priority. Subsequently, with accordance to this priority, training data entries are eliminated on the basis of the existence of designs with the same or better accuracy and a higher priority, i.e., lower PADP. Additionally, input instances with high accuracy, e.g.,  $PSNR \ge 70 dB$ , are excluded if there exists another instance with high accuracy. Finally, input entries with very low quality, e.g.,  $PSNR \leq 15 dB$ , which are considered worthless in real applications are also eliminated. This data pre-processing, would keep training data of circuits with lower PADP, yet offering a better, similar, or high enough quality compared to circuits with higher PADP. This data-processing resulted in a light-weight training data, as it will be demonstrated in the next section.

Figure 2.4 depicts the flow of the proposed methodology when extending the work proposed in [32] to larger models. The methodology consists of first designing a library of AC designs. These designs are synthesized on the RTL level and prioritized based on their PADP. Moreover, the models are simulated in parallel computing using high performance computation (HPC) to generate training data, with this data being quantized based on consecutive entries to produce quantized training data. Afterwards, based on the synthesis-based priority, the quantized training data is reduced, and then sent to the ML-algorithm in order to be classified. The MLalgorithm will generate a design selector which will predict the appropriate design based on a given TOQ and the runtime inputs. Finally, it must be noted that the proposed reduction of training data set may result in a different behavior of the MLbased design selector. Nonetheless, this modification is accepted since the aim here is to develop an ML-based design selector that will select the most suitable design satisfying the TOQ and not the classification of generated data from a data analysis point of view.

Figure 2.4: Improved ML-Based Quality Assurance

#### 2.4 Experimental Results

In this section, we conduct experiments in order to demonstrate the performance gains from applying the methodology proposed in the previous section. The attained benefits in each stage, are explained in the following subsections.

#### 2.4.1 Simulating Extended Model

The excessive simulation to evaluate the accuracy of 20 designs of 16-bit array multipliers was conducted on high-performance computing (HPC) server [52]. This HPC offers 32 physical cores, 512GB of RAM per node and a total of 24 nodes. The runtime gained access to the full power of this machine, by utilizing all 32-cores available per node. Furthermore, with the HPC server offering multiple computational nodes, different models were simulated simultaneously each on a given node, which drastically reduced the overall runtime. Moreover, the simulation of each model took between 8 to 10 hours, reduced from 24 days if they were simulated using a PC. Furthermore, the overall runtime was less than 2 days compared to 1 year and 4 months if it had to be conducted on a PC. This speed-up was achievable due to the availability of multiple nodes, thus running multiple simulations in parallel. Moreover, it must be noted that the extension to 32-bit can be deemed impractical since its projection simulation time would be in the range of  $3.4 \times 10^{10}$  to  $4.3 \times 10^{10}$  hours when using a similar HPC.

#### 2.4.2 Quantazing & Reducing Training Data

Next, as shown in Figure 2.4, the training data resulting from the excessive simulation is first quantized, which reduced the data from  $8.5 \times 10^{10}$  down to  $3.35 \times 10^{8}$ . Afterwards, the 20 designs are synthesized using Xilinx Vivado [57]. We conducted the synthesis with an XC7VX330T FPGA from the Xilinx Virtex-7 family [56]. Table 2 shows the synthesis results, i.e. area, power, delay. The power considered in this study is the FPGA dynamic power and measured in mW, while the area is measured by two factors represented in the number of slices and lookup tables (LUTs) used by each of the designs. Finally, the delay is measured in ns and represents the time required by the slowest output bit. The PADP is computed by multiplying the sum of the two columns of area, i.e., Slice and LUT, by the dynamic power and delay.

Moreover, as proposed in the previous section, each design was given a priority, where the design with the lowest PADP has the highest priority while the design with the highest PADP has the lowest priority. As shown in Table 2 the design resulting in the lowest PADP (Type = AMA4, Degree = D4), is provided the highest priority which is 1. Furthermore, the benefit of AC circuits can be noticeable, since the circuits with priority 1, has 0.18% the PADP of the exact multiplier. Moreover, the design with least priority (Type = AMA2, Degree = D1), i.e., approximate circuits with highest PADP, resulted in a PADP that is 55.63% the value of the exact multiplier design.

| Design | Degree | Dynamic<br>Power(mW) | Area<br>(Slice) | Area<br>(LUT) | <b>Delay</b> (ns) | PADP    | Priority |

|--------|--------|----------------------|-----------------|---------------|-------------------|---------|----------|

| AMA1   | D1     | 290                  | 166             | 552           | 18.297            | 3809.80 | 19       |

| AMA1   | D2     | 259                  | 165             | 536           | 18.472            | 3353.76 | 17       |

| AMA1   | D3     | 230                  | 151             | 487           | 13.620            | 1998.6  | 11       |

| AMA1   | D4     | 52                   | 53              | 115           | 7.547             | 65.93   | 3        |

| AMA2   | D1     | 318                  | 165             | 504           | 18.479            | 3931.26 | 20       |

| AMA2   | D2     | 300                  | 153             | 483           | 18.690            | 3560.45 | 18       |

| AMA2   | D3     | 289                  | 148             | 473           | 18.329            | 3289.49 | 15       |

| AMA2   | D4     | 98                   | 80              | 207           | 8.221             | 231.22  | 5        |

| AMA3   | D1     | 309                  | 156             | 451           | 17.796            | 3337.87 | 16       |

| AMA3   | D2     | 292                  | 147             | 467           | 18.876            | 3204.95 | 14       |

| AMA3   | D3     | 271                  | 133             | 415           | 17.134            | 2544.54 | 13       |

| AMA3   | D4     | 93                   | 38              | 63            | 7.330             | 68.85   | 4        |

| AMA4   | D1     | 268                  | 143             | 439           | 15.109            | 2356.64 | 12       |

| AMA4   | D2     | 249                  | 128             | 423           | 14.434            | 1980.33 | 10       |

| AMA4   | D3     | 222                  | 128             | 413           | 14.366            | 1725.39 | 8        |

| AMA4   | D4     | 32                   | 27              | 34            | 6.787             | 13.25   | 1        |

| AMA5   | D1     | 287                  | 128             | 413           | 14.366            | 1725.39 | 8        |

| AMA5   | D2     | 270                  | 99              | 312           | 13.989            | 1552.36 | 7        |

| AMA5   | D3     | 241                  | 93              | 255           | 13.343            | 1119.05 | 6        |

| AMA5   | D4     | 74                   | 23              | 24            | 6.046             | 21.03   | 2        |

| Exact  | -      | 473                  | 183             | 603           | 19.008            | 7066.76 | -        |

Table 2: Design Characteristics of the Approximate Library, i.e., Power, Area, Delay and Power-Area-Delay Product (PADP)

Consequently, for every distinctive applied input, training data is reduced based on the set priority. The implementation of the proposed data reduction proposed in the methodology shown in Figure 2.4 is summarized in the list below along with the data excluded with each of the three reductions: **1-** Reducing entries based on output quality and priority: 73.11% of data instances are excluded.

**2-** Entries with high accuracy, e.g., PSNR  $\geq 70$ , yet a design with higher priority, i.e., lower PADP, offering similar or higher accuracy: additional 9.96% of the data is eliminated.

**3-** Entries with very low accuracy, e.g., PSNR  $\leq 15$ : additional 7.29% of the data is reduced.

In total, 90.36% of the data is eliminated resulting in approximately  $3.24 \times 10^7$  instances, down from  $3.35 \times 10^8$ . Table 3 shows the remaining number of training entries for each of the 20 designs after pre-processing, i.e., quantizing then reducing, data. From Table 3, it can be noticed that the design with (Type = AMA5, Degree=D4), i.e., *Design 19* in Table 8 has the most number of entries after data pre-processing. This design is given a priority of 6 as shown in Table 2 and thus has one of the lowest PADP. Moreover, it can be noticed that designs with low priority, e.g., priorities 15 to 20, have minimal to zero entries after data pre-processing as shown in Table 3. Finally, it must be noted that this data pre-processing eliminated 7 designs, i.e., zero training entries, from the library of AC designs, since other designs offer similar or better quality with better PADP.

Table 3: The Number of Training Entries of each Approximate Design After Preprocessing

|         | AMA1 | AMA2      | AMA3      | AMA4      | AMA5            |

|---------|------|-----------|-----------|-----------|-----------------|

| Degree1 | 264  | 12,677    | 7         | 441,404   | 1,859,393       |

| Degree2 | 0    | 0         | 0         | 29,437    | 315,541         |

| Degree3 | 0    | 0         | 0         | 75,752    | 16,761,883      |

| Degree4 | 0    | 1,315,321 | 1,493,624 | 4,987,277 | $2,\!230,\!190$ |

#### 2.4.3 Building the ML-Based Design Selector

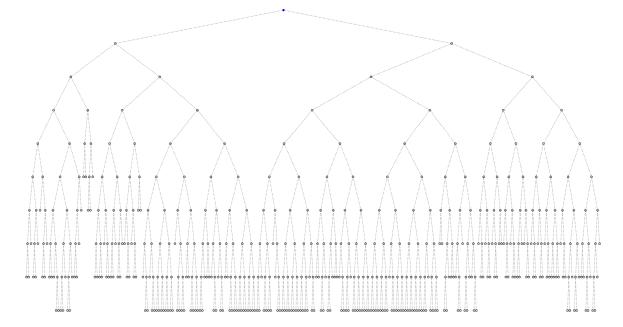

Based on the proposed methodology of Figure 2.4, the quantized and reduced training data was sent to the ML-algorithm, in order to build an ML-predictor, that would select the design that is projected to meet the TOQ. The research conducted in [30] found out that the usage of decision tree (DT) as ML-algorithm proved superiority compared to linear regression (LR), random forest (RF) and neural network (NN) for the ML-based quality assurance model. Furthermore, over-fitting of training data is needed since all possible combinations have been generated when simulating the designs. Thus, an ML-algorithm that delivers an over-fitting of training data is needed. Therefore DT has been chosen and the best algorithm for the ML-based design selector. The DT-modeling was constructed using Classification Learner Toolbox in Matlab [33]. The generated DT-predictor that will select the appropriate design is depicted in Figure 2.5, with an accuracy of 83.9%. Moreover, the data was simplified in order to create a lightweight ML-predictor, and indeed this goal was achieved, since predictions can be achieved with a minimum of 5 nodes, and a maximum of 9 nodes. Moreover, it is remarkable that when data pre-processing is applied, many designs were excluded, either for having 0 entries, or a small contribution as shown in Table 3. However, with such enormous unbalanced contribution for different designs, it must be noted that the ML-algorithm tend to disregard training data entries with small contribution, unless a true-fit predictor is set. Nonetheless, a true-fit predictor would result in unnecessary overhead by the predictor, since the ML-model will have further nodes and quality improvement that could be intangible.

Figure 2.5: The Structure of the Constructed DT-Model

#### 2.4.4 Quality Check

In order to assess the design quality, we now test the generated model that uses the DT-predictor shown in Figure 2.5. For the experimental results, we have chosen multimedia blending applications based on multiplication as they are known to be error-tolerant. The two multimedia services chosen are audio and image, with  $2 \times 10^9$ and  $12 \times 10^6$  unique inputs, for each of the two applications, respectively. The experimental work is executed with a variation in the TOQ, i.e., PSNR, and a variation in the numbers of samples used, which are provided to the DT-predictor. The number of samples vary from 1 sample, to the maximum number of  $2^n$  samples. For each run, the predictor is used once, since the samples are averaged, and thereby, the prediction is based on this value. To proceed with the multimedia processing, one should understand the physical nature of each of the applications, and its digital representation. Thus below, the physical behavior is explained, along with their corresponding digital construction:

1- Characteristics of Audio Files: Sounds can be stored as digital audio in a series of bitstreams, with each bit representing the physical wave length, i.e., amplitude. With the use of 16-bits per sample, the amplitude is represented in a more accurate representation, as a wider range is covered  $\pm 2^8$ . The database of WAV sound files available in [9], is a good resource for researchers, conducting experiments in the field of audio-processing.

2- Characteristics of Image Files: Similar to audio, images are constructed of the mix in three channels, i.e., Red, Green and Blue (RGB). The 16-bit representation for images, means that each pixel can take one of  $2^{48}$  unique combination of colors, since each of the three channels has a set of  $2^{16}$  unique colors, i.e.,  $2^{16}$  different red colors. A library of raw images found in [2] is used in order to have access to 16-bit images.

The simulation is conducted with a target PSNR ranging from 15 dB up to 70 dB. Furthermore, since the ML-selector requires runtime inputs to predict the appropriate design, switching designs for every computation would defeat the purpose of using AC. Thus, in order to reduce the overhead of switching among designs, the images and audio files are sampled with the runtime input being the average of the samples. The samples are taken in the form of  $2^n$  with n varying from 0 up to 12 and 17 for image and audio processing, respectively. The patterns used to collect  $2^n$  samples from audio files and images are shown in Figures 2.6 and 2.7, respectively. As these figures depict, the space is divided after every iteration with the samples taken from the middle of each of the sub-spaces resulting from the division.

Figure 2.6: Pattern used to Sample Audio Files

Figure 2.7: Pattern used to Sample Images

Multiple runs of audio and image processing are conducted, and the output quality is monitored. Afterwards, the average quality based on the number of samples taken is computed. Figure 2.8 shows the quality obtained for audio processing when the various  $2^n$  samples are collected with n varying from 0 to 17. Figure 2.9 shows similar data for image sampling when collecting  $2^0$  to  $2^{12}$  samples, i.e., n varying from 0 to 12. Moreover, both figures provide the target output quality (TOQ) provided to the ML-predictor. As shown in Figure 2.8, the audio blending resulted in a measured quality that is better or equal to the chosen TOQ. On the other side, we can notice from Figure 2.9 that the actual quality was better than the chosen TOQ for most of the cases. Furthermore, the simulation shows that additional numbers of samples does not always imply an improvement in quality. Thus, the number of samples to be taken must be carefully selected in order to minimize the overhead of sampling. Finally, it must be noted that the reduction of training data we proposed in this chapter improved the output quality. This can be noticed in Figures 2.8 and 2.9 since the actual quality is higher than the TOQ, while the work in [32] resulted in an actual

Figure 2.8: TOQ versus Obtained Output Quality for Adaptive Audio Blending

### 2.5 Summary

In this chapter, we studied the extension of previously proposed ML-based quality assurance [32]. Such extension is hard when dealing with larger designs, e.g., 16-bit multiplier instead of 8-bit. Nonetheless, the proposed methodology in Figure 2.4 uses an HPC server [52] to reduce simulation time and introduce, a new reduction to the training data. Using this proposed methodology, the ML-based model was successfully extended to support 16-bit multipliers. Moreover, the extension to 16-bit model was achievable, however with today's computation power, simulating a 32-bit models or larger is unpractical as it would require an indefinite amount of time. Moreover, it is remarkable that the data pre-processing proposed in this chapter resulted in extensive reduction of training data. This reduction resulted in a simple DT-predictor which has a small overhead along with an improved output quality.

Nonetheless, the output quality of the ML-based quality assurance could be enhanced, if the library of AC designs used is improved. A viable approach to improve the library is an implementation of a DSE. Such study could also result in a design that has an improved metrics in the four dimensions of AC design. If such design is found, it could be a good solution for circuits where ML-based quality assurance results in undesirable overhead, e.g., IoT. Moreover, extension to larger designs, e.g., 32-bit multiplier, could be feasible if the time to assess the quality is reduced. Towards this goal, in the next chapter we propose a methodology of a DSE for AC designs that allows such achievements.

# Chapter 3

# Design Space Exploration for Approximate Circuits

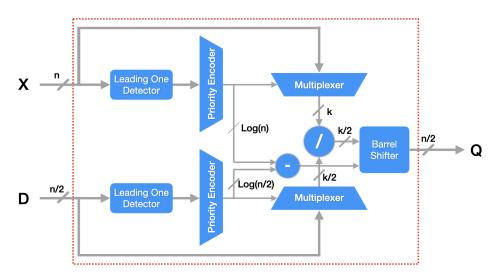

In this chapter, a methodology for design space exploration (DSE) for AC circuits is proposed. The methodology is based on a new mathematical modeling for circuits, which allows for a faster assessment of logical circuits.

### 3.1 Introduction

Research of AC circuits has been concentrated on modifications at the architecture level. Furthermore, the reported AC architectures such as the work in [32] [43] have been explored in a small number of structural configurations. Some of the reasons why the proposed designs are studied in a limited number of configurations are: 1) common fallacies of circuit approximation; and 2) time required to asses large set of configurations. In order to illustrate some of the common fallacies and interpret the proposed DSE for AC, array multipliers are used in this chapter.

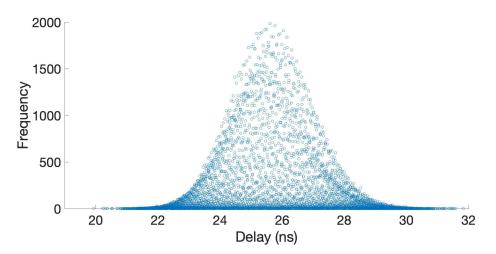

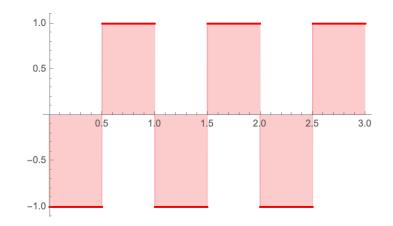

One common fallacy is an effort to approximate least significant bits (LSBs) only. For instance, in order to approximate the array multiplier shown in Figure 3.1, techniques have been based on swapping exact sub-blocks in the right columns with approximated ones, e.g., replacing exact full adders (FAs) in column 1 to column 15 with approximated FAs. A good example of this approach's adoption is AUGER tool [22] and the work in [32]. The objective of this approach is the desire to approximate LSBs only, which will result in a negligible impact on the output quality. Nonetheless,

Figure 3.1: Architecture of a 16-bit Array Multiplier