### Low-Power Class-D Amplifier for Industrial Applications

Nueraimaiti Aimaier

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

**Presented in Partial Fulfillment of the Requirements**

for the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

**Concordia University**

Montréal, Québec, Canada

February 2025

© Nueraimaiti Aimaier, 2025

### CONCORDIA UNIVERSITY

#### School of Graduate Studies

This is to certify that the thesis prepared

By: Mr. Nueraimaiti Aimaier

Entitled: Low-Power Class-D Amplifier for Industrial Applications

and submitted in partial fulfillment of the requirements for the degree of

### **Doctor of Philosophy (Electrical and Computer Engineering)**

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

### Signed by the Final Examining Committee:

|             |                             | Chair                |

|-------------|-----------------------------|----------------------|

|             | Dr. Farah Hafeez            |                      |

|             |                             | External Examiner    |

|             | Dr. Gerry Moschopoulos      |                      |

|             |                             | Arms-Length Examiner |

|             | Dr. Handy Fortin Blanchette |                      |

|             |                             | Examiner             |

|             | Dr. Luiz A. C. Lopes        |                      |

|             |                             | Examiner             |

|             | Dr. Rabin Raut              |                      |

|             |                             | Supervisor           |

|             | Dr. Glenn Cowan             |                      |

|             |                             | Co-Supervisor        |

|             | Dr. Nicolas Constantin      |                      |

|             |                             |                      |

| Approved by |                             |                      |

Dr. Yousef R. Shayan, Chair Department of Electrical and Computer Engineering

\_ 2025

Mourad Debbabi, Dean Faculty of Engineering and Computer Science

### Abstract

#### Low-Power Class-D Amplifier for Industrial Applications

Nueraimaiti Aimaier, Ph.D.

**Concordia University, 2025**

This dissertation investigates the design and development of fully differential switching (class-D) amplifiers optimized for high efficiency, linearity, and compact integration, tailored to low-power applications such as industrial servo valves, hall effect sensors, and low-power actuators. These loads, commonly employed in automotive and other critical power systems, require differential sine wave inputs at frequencies ranging from several kilohertz to 10 kHz. Traditional linear amplifiers (Class A, B, and AB) are constrained by low efficiency and significant thermal management requirements, while switching amplifiers, despite their inherent efficiency advantages, pose challenges in mitigating nonlinearities and distortions.

The first major contribution is the development of a low-power Selective Harmonic Elimination Pulse-Width Modulation (SHEPWM)-based full-bridge inverter, featuring a novel FPGA hardware implementation. Unlike conventional SHEPWM systems focused on high-power, fixed-frequency applications (50 Hz–60 Hz), this work extends SHEPWM to low-power systems operating at high fundamental output frequencies (4 kHz–10 kHz). A unique FPGA-based architecture enables real-time configurability of output amplitude and frequency, offering flexibility without excessive computational or storage demands. Experimental results demonstrate harmonic elimination up to the 34<sup>th</sup> order, achieving total harmonic distortion (THD) below 5.1% and efficiency improvements of up to 17.3% compared to natural PWM (NPWM). By integrating this design into a compact system-in-package (SiP) utilizing Gallium-Nitride (GaN) power transistors, the inverter minimizes the printed circuit board (PCB) footprint compared to conventional discrete implementations. This

integration offers a robust and versatile solution for next-generation low-power industry applications.

The second contribution is the design and analysis of a Double Integral Sliding Mode Control (DISMC)-based class-D amplifier. Theoretical work forms the foundation of this research, involving a rigorous analysis of reaching and stability conditions to derive optimal controller gains. The proposed controller employs a double-loop strategy that uses the integrals of inductor current and output voltage tracking errors to ensure robust tracking and stability under varying operating conditions. The theoretical findings are validated through extensive simulation and experimental studies, demonstrating the DISMC's superior disturbance rejection, enhanced transient response, and reliability compared to conventional proportional-integral (PI) controllers.

By combining innovative control techniques such as SHEPWM and DISMC with compact and efficient hardware designs, this research advances the state-of-the-art in switching amplifier technology. The outcomes offer practical solutions for compact, high-performance systems, addressing critical requirements in modern industrial applications while paving the way for future advancements in power electronics.

### Acknowledgments

First and foremost, I would like to express my deepest gratitude to my supervisor, Professor Glenn Cowan, for offering me an opportunity that has profoundly changed my life. His unwavering belief in me, coupled with his support, guidance, and encouragement, has been instrumental in shaping this dissertation. I am truly fortunate to have had the privilege of working under his mentorship.

I am also profoundly thankful to my co-supervisor, Professor Nicolas Constantin, for his remarkable vision and technical advice throughout my Ph.D. His mentorship has not only contributed significantly to the direction of my research, but his support in granting me access to research offices and labs at École de Technologie Supérieure (ETS) greatly facilitated the progress of my work. For these reasons, I am deeply indebted to him.

Special thanks go to Professor Yves Blaquière, who patiently taught me digital design. Coming from an analog IC background, his expertise in digital IC and FPGA design had a profound impact on my Ph.D. research. His kindness, patience, and vast knowledge were always there to support me whenever I needed guidance. I consider him the most kind, patient, and knowledgeable professor I have ever had the privilege of learning from, and I am truly grateful for his invaluable contributions to my work.

I am immensely grateful to my project team members, whose contributions were instrumental in the success of this work. Nam Ly, for designing the gate driver IC and for his help with the design of the host PCB and System-in-Package (SiP) for my first project. Abdul Hafiz Alameh, for his dedication to the SiP layout and production. Tan Pham, for assembling the SiP and host PCB. Ha Nguyen, for debugging the SiP and developing the MATLAB GUI. Gabriel Nobert, for his invaluable advice on digital design, assistance with FPGA, and support in testing readback circuitries. Hamid Sadrimanesh, for his efforts in testing the readback circuits and his advice on hardware debugging. Mathieu Gratuze, for his constant support with lab work and equipment at ETS. Their collaboration and technical expertise played a critical role in advancing my research, and I am truly grateful for their contributions.

I would also like to extend my deepest gratitude to the technicians and fellow students at the Department of Electrical Engineering at both ETS and Concordia University. Their continuous help and support, whether in the lab, in discussions, or in day-to-day problem-solving, made a significant difference in the progress of my research. Without their assistance, I would not have been able to achieve this milestone.

Finally, I owe an immeasurable debt of gratitude to my wife, Salamet Semet, who has stood by my side throughout this entire journey. We came to Canada together with our first child, and she is now raising our three children while supporting me wholeheartedly. Despite the profound hardship of being unable to contact her parents, my in-laws, for the past seven years—having not even heard their voices—she has remained positive and resilient. Her strength and unwavering support have been my foundation throughout this Ph.D., and without her, none of this would have been possible.

Lastly, I would like to thank everyone who, in one way or another, contributed to the completion of this thesis. This milestone is not only mine but a reflection of the collective effort of those who have supported me along the way.

### Dedication

I dedicate this dissertation to my parents, Omar Osman and Aynur Abdurehim, who raised me with unwavering love and support. Despite coming from a small, remote town in the far west of the Uyghur region, they encouraged me to pursue the best education possible. Their belief in me extended even further when they supported my journey to Canada to pursue my Ph.D., fully aware that it might be the last time we would see each other. I hold on to the hope that, despite the political challenges we face, I will be able to reunite with them within their lifetime.

## Contents

| Li | st of l | Figures                                                                          | X    |

|----|---------|----------------------------------------------------------------------------------|------|

| Li | st of ] | Fables                                                                           | xiv  |

| Li | st of S | Symbols x                                                                        | viii |

| 1  | Intr    | oduction                                                                         | 1    |

|    | 1.1     | Motivation                                                                       | 2    |

|    | 1.2     | Focus of This Work                                                               | 5    |

|    |         | 1.2.1 Problem Statement                                                          | 6    |

|    |         | 1.2.2 Research Objectives                                                        | 7    |

|    | 1.3     | Fundamentals of Class-D Amplifiers                                               | 8    |

|    | 1.4     | Thesis Outline and Publications                                                  | 12   |

| 2  | Lite    | rature Review                                                                    | 15   |

|    | 2.1     | Class-D Amplifier (CDA) Power Dissipation Sources                                | 15   |

|    | 2.2     | Class-D Amplifier Architectures and Modulation Techniques                        | 21   |

|    |         | 2.2.1 Class-D Amplifier Structures                                               | 21   |

|    |         | 2.2.2 Class-D Amplifier Modulation Techniques                                    | 25   |

|    | 2.3     | Background of Selective Harmonic Eliminated Pulse Width Modulation (SHEPWM)      |      |

|    |         | Technique                                                                        | 28   |

|    | 2.4     | State-of-the-Art of Selective Harmonic Eliminated Pulse Width Modulation (SHEPWM | 1)   |

|    |         | Technique                                                                        | 31   |

|    | 2.5                                                        | Background of Sliding Mode Controller (SMC) Technique                             | 33  |

|----|------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|

|    | 2.6                                                        | State-of-the-Art of Sliding Mode Controller (SMC) Technique in Class-D Amplifiers | 39  |

| 3  | SHI                                                        | EPWM Inverter with a Compact SiP Implementation                                   | 42  |

|    | 3.1                                                        | Design of SHEPWM Full-Bridge Inverter                                             | 43  |

|    |                                                            | 3.1.1 Proposed SHEPWM FPGA Architecture                                           | 47  |

|    |                                                            | 3.1.2 On-the-Fly Configuration of AC Output Signals                               | 53  |

|    |                                                            | 3.1.3 SHEPWM Inverter System Implementation                                       | 54  |

|    | 3.2                                                        | Simulation and Experimental Results of Designed SHEPWM Inverter                   | 57  |

|    | 3.3                                                        | Conclusions                                                                       | 67  |

| 4  | Disc                                                       | erete DISMC for a Class-D Amplifier                                               | 73  |

|    | 4.1                                                        | Design of the DISMC                                                               | 74  |

|    |                                                            | 4.1.1 Modeling the Class-D Amplifier Output Stage                                 | 74  |

|    |                                                            | 4.1.2 Design of a Discrete Double Integral Sliding Mode Controller for Class-D    |     |

|    |                                                            | Amplifier                                                                         | 76  |

|    |                                                            | 4.1.3 System Level Design of the DISMC Class-D Amplifier                          | 86  |

|    | 4.2                                                        | Simulation and Experimental Results of Designed DISMC                             | 92  |

|    | 4.3                                                        | Conclusions                                                                       | 105 |

| 5  | Con                                                        | clusions and Future Work                                                          | 107 |

|    | 5.1                                                        | Conclusions                                                                       | 107 |

|    | 5.2                                                        | Recommendations for Future Work                                                   | 109 |

| Aj | Appendix ADISMC Class-D Amplifier Printed Circuit Board112 |                                                                                   |     |

| Bi | bliog                                                      | raphy                                                                             | 121 |

# **List of Figures**

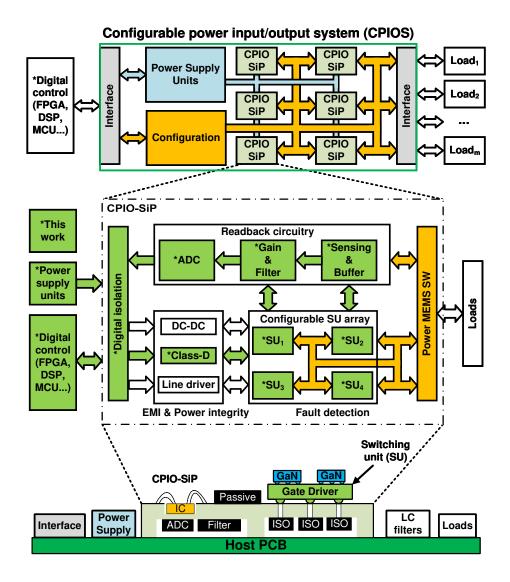

| Figure 1.1  | The block diagram of CPIOS                                                    | 3  |

|-------------|-------------------------------------------------------------------------------|----|

| Figure 1.2  | class-D amplifier open-loop block diagram                                     | 10 |

| Figure 1.3  | Full-bridge output stage operation                                            | 10 |

| Figure 1.4  | Full-bridge switching waveform                                                | 11 |

| Figure 2.1  | Circuit diagram of the half-bridge class-D amplifier for power loss analysis. | 16 |

| Figure 2.2  | The diagram of switching node voltage and inductor current waveform and       |    |

| power       | loss.                                                                         | 17 |

| Figure 2.3  | Timing diagram of switching waveform when indcutor current flows into a       |    |

| half-b      | ridge (Ma, van der Zee, and Nauta (2015))                                     | 20 |

| Figure 2.4  | Efficiency diagram of a CDA versus output power, illustrating the dominant    |    |

| loss ir     | the output power region                                                       | 20 |

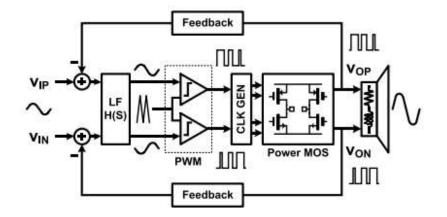

| Figure 2.5  | Analog class-D amplifier block diagram (WC. Wang and Lin (2016))              | 22 |

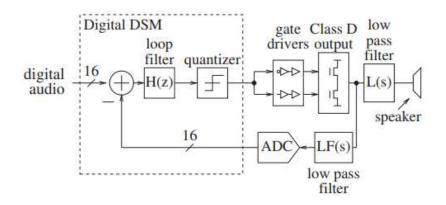

| Figure 2.6  | Digital class-D amplifier block diagram (McKenzie and Ng (2018))              | 23 |

| Figure 2.7  | Digital class-D amplifier block diagram (Berkhout and Dooper (2010))          | 23 |

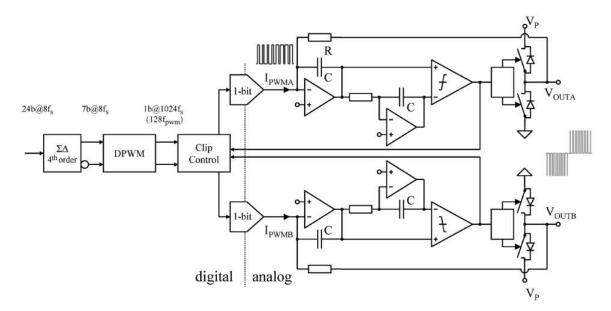

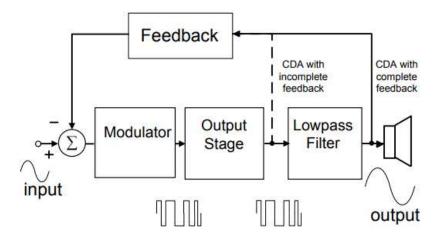

| Figure 2.8  | Two different feedback types in CDA (W. Yu, Shu, and Chang (2009))            | 25 |

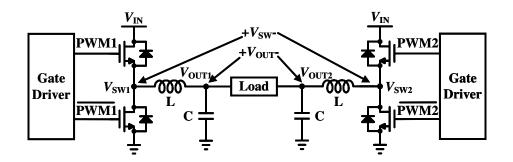

| Figure 2.9  | Schematic of a full-bridge inverter output stage                              | 29 |

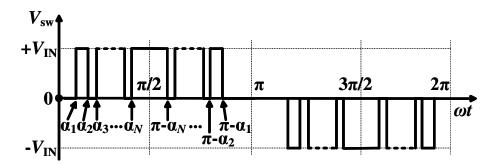

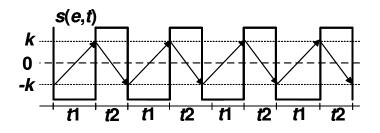

| Figure 2.10 | A three-level odd-symmetrical SHEPWM waveform.                                | 29 |

| Figure 2.11 | A half-bridge two-state operation.                                            | 34 |

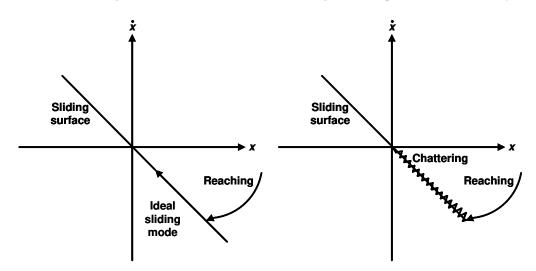

| Figure 2.12 | Sliding mode illustration.                                                    | 36 |

| Figure 2.13 | A diagram illustrating the reaching mode condition of the SMC                 | 37 |

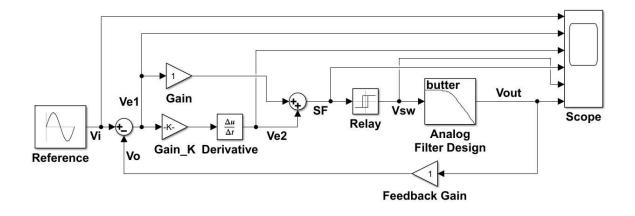

| Figure 2.14 | Simulink schematic of a reference tracking system using SMC.                  | 38 |

| Figure 2.15 S           | Simulink simulation of the reference tracking system using SMC                                   | 38 |

|-------------------------|--------------------------------------------------------------------------------------------------|----|

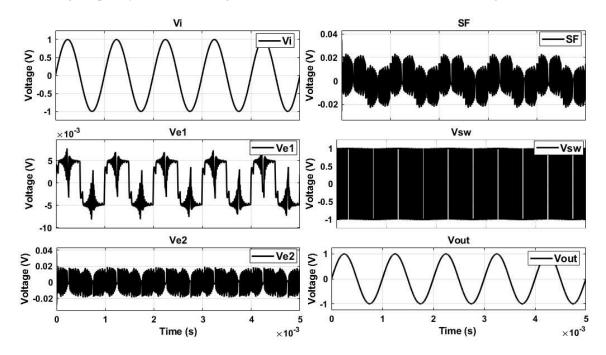

| Figure 3.1              | THD of second-order filtered output for various switching angle counts at                        |    |

| fundame                 | ental output frequencies of 5 kHz and 4 kHz                                                      | 47 |

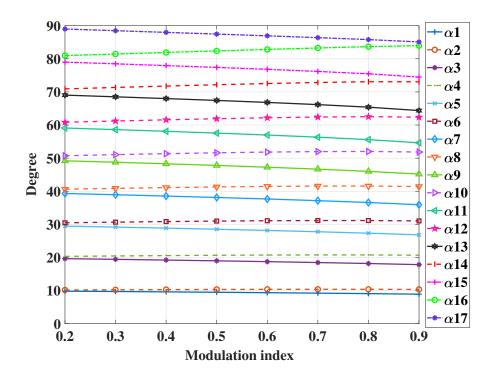

| Figure 3.2              | The 17 optimal switching angles per quarter-cycle for different modulation                       |    |

| indices.                |                                                                                                  | 49 |

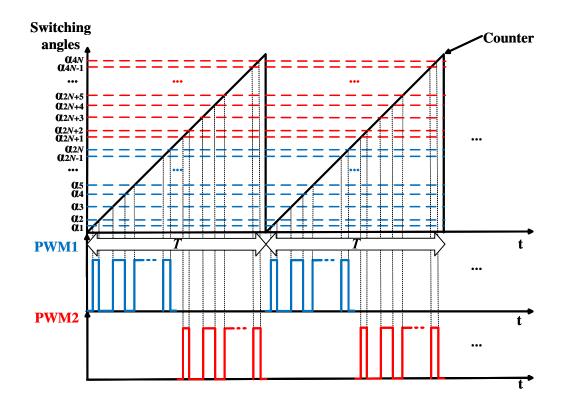

| Figure 3.3 C            | Generating the SHEPWM pulses using a counter-based methodology                                   | 50 |

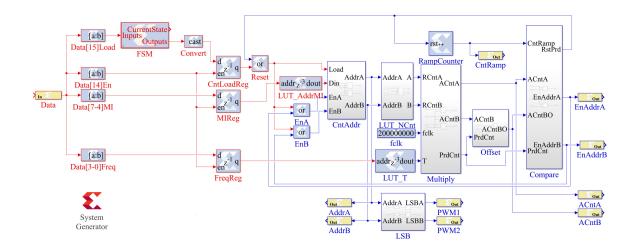

| Figure 3.4 7            | The designed SHEPWM core in Xilinx System Generator.                                             | 51 |

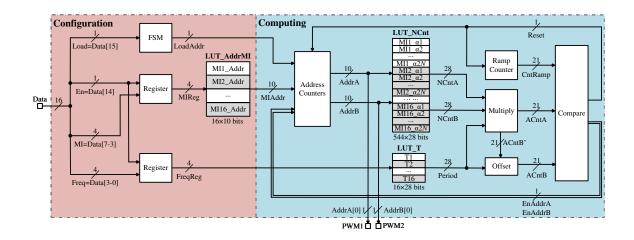

| Figure 3.5              | The SHEPWM architecture on the FPGA with $M=16$ MIs and $N_{\rm f}=16$                           |    |

| frequen                 | cies, employing $N = 17$ switching angles                                                        | 52 |

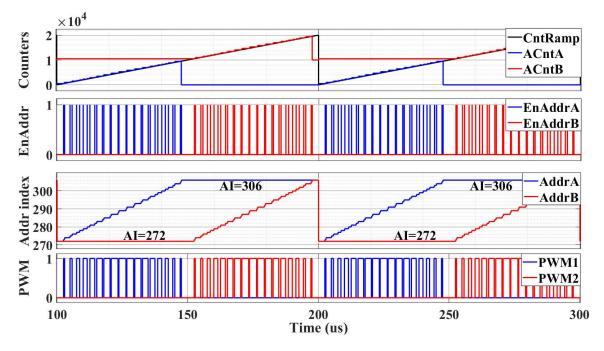

| Figure 3.6 S            | SHEPWM simulation showing critical FPGA signals in Figure 3.5                                    | 53 |

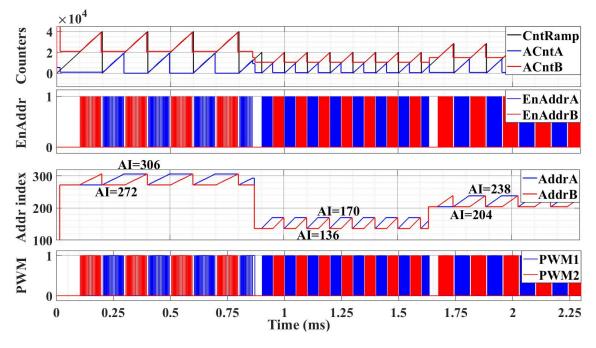

| Figure 3.7 F            | FPGA signals during on-the-fly configuration.                                                    | 54 |

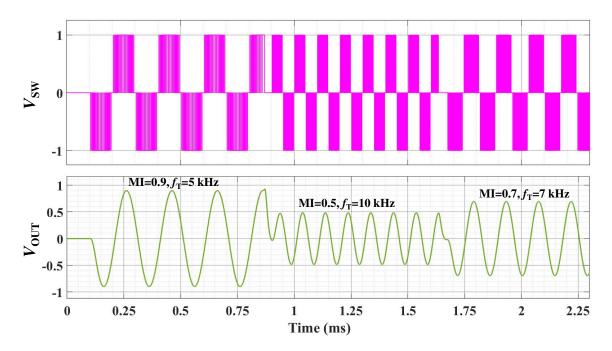

| Figure 3.8 7            | The effect of on-the-fly configuration on the amplitude and frequency of the                     |    |

| inverter                | output waveform                                                                                  | 55 |

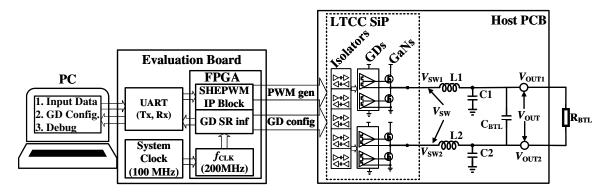

| Figure 3.9 7            | The architecture of the SHEPWM inverter.                                                         | 55 |

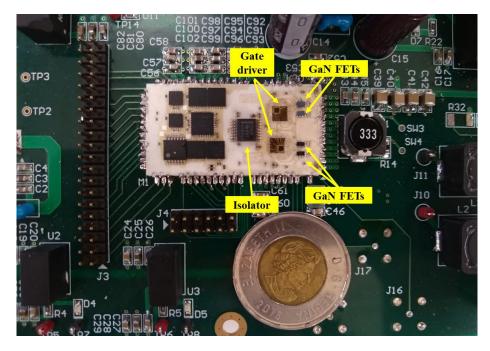

| Figure 3.10 I           | TCC SiP with a Canadian two-dollar coin (diameter=28mm) as a reference.                          | 56 |

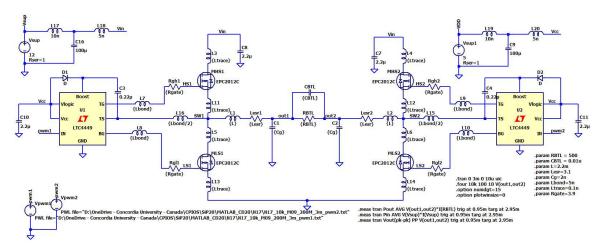

| Figure 3.11 S           | SHEPWM inverter output stage schematic in LTspice                                                | 57 |

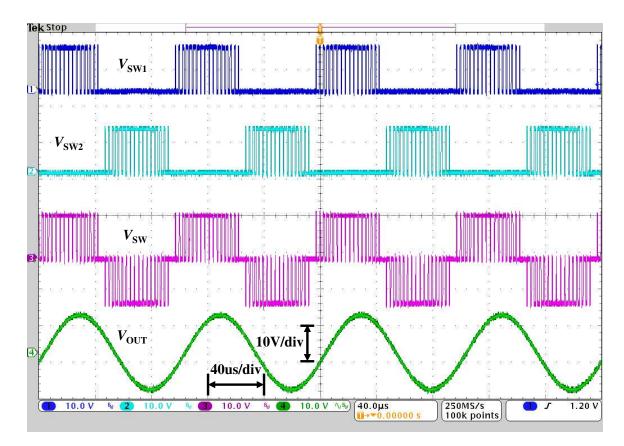

| Figure 3.12 S           | Singled-ended switching node voltages ( $V_{\rm SW1}$ and $V_{\rm SW2}$ ), differential switch-  |    |

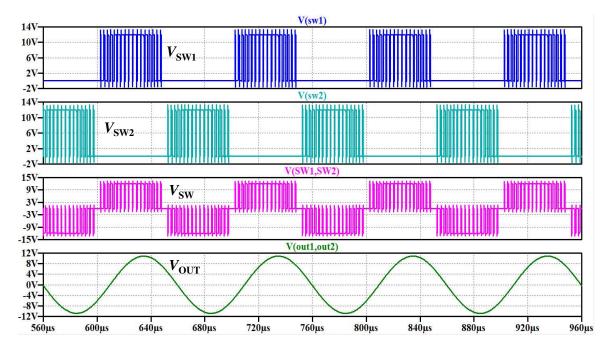

| ing node                | e ( $V_{\rm SW}$ ) and output voltage ( $V_{\rm OUT}$ ) waveforms from LTspice simulations.      | 58 |

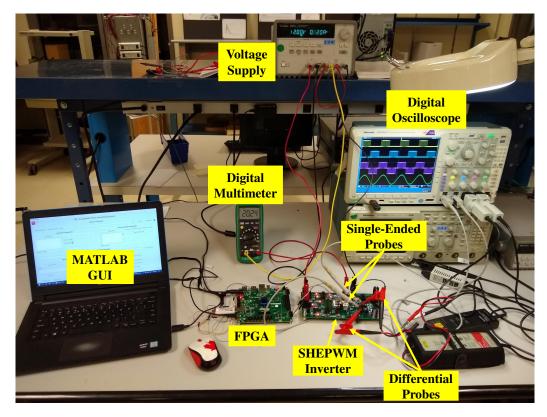

| Figure 3.13 S           | SHEPWM inverter experimental test setup                                                          | 60 |

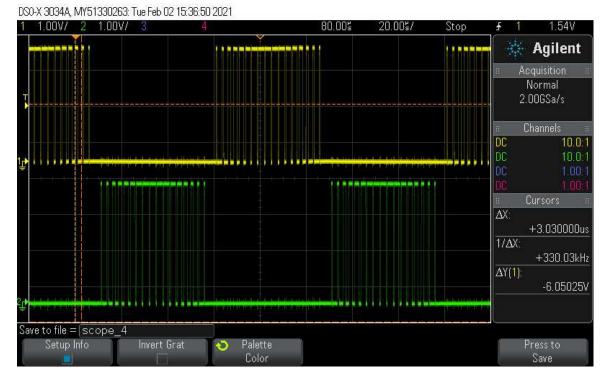

| Figure 3.14 S           | SHEPWM signals from FPGA for MI = 0.9 and $f_{\rm T}$ = 10 kHz                                   | 61 |

| Figure 3.15 M           | Measured single-ended switching node voltages ( $V_{\rm SW1}$ and $V_{\rm SW2}$ ), differen-     |    |

| tial swit               | the sching node ( $V_{\rm SW}$ ) and output voltage ( $V_{\rm OUT}$ ) waveforms for MI = 0.9 and |    |

| $f_{\mathrm{T}}\!=\!10$ | kHz                                                                                              | 62 |

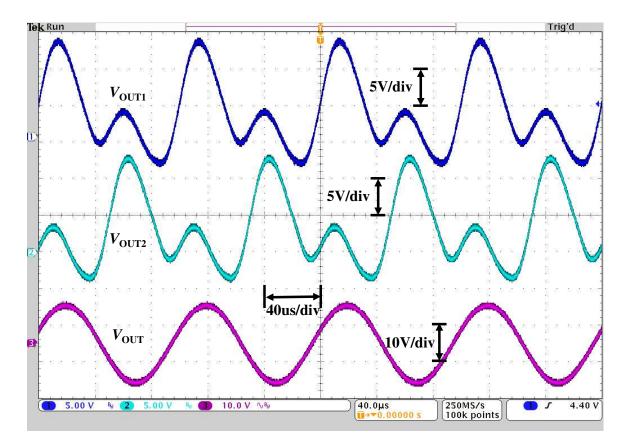

| Figure 3.16 M           | Measured inverter single-ended ( $V_{OUT1}$ and $V_{OUT2}$ ) and differential ( $V_{OUT}$ )      |    |

| output s                | ignals for MI=0.9 and $f_{\rm T}$ =10 kHz                                                        | 63 |

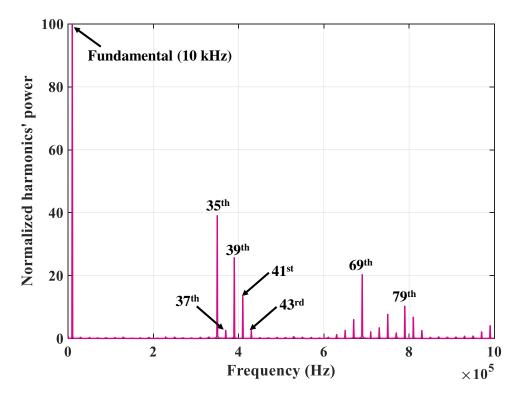

| Figure 3.17 S           | Spectrum of the measured differential switching node voltage ( $V_{\rm SW}$ )                    | 64 |

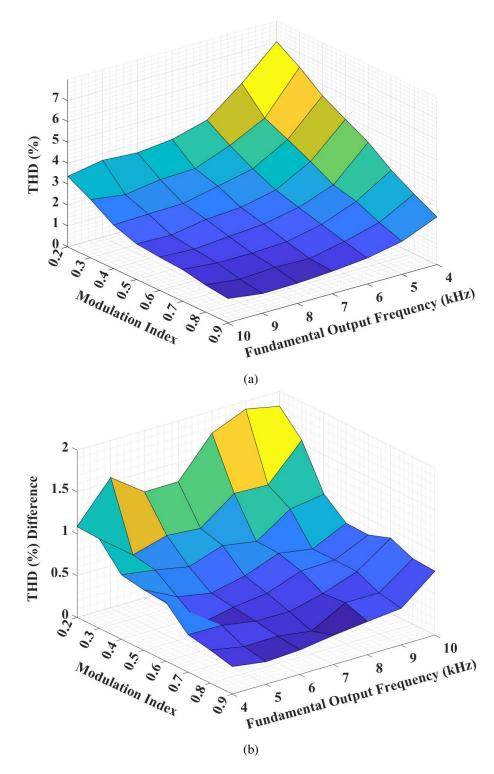

| Figure 3.18 (           | (a) Measured THD versus different modulation indices and output frequen-                         |    |

| cies, (b)               | THD difference between simulation and measurement.                                               | 69 |

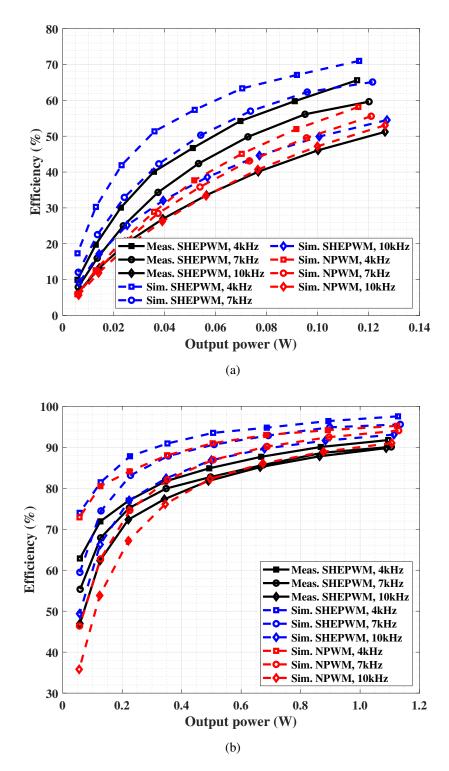

| Figure 3.19 Power efficiency comparisons of the SHEPWM and NPWM inverters for the          |    |

|--------------------------------------------------------------------------------------------|----|

| same output THD (a) $P_{\text{out}}=0.12 \text{ W}$ , (b) $P_{\text{out}}=1.2 \text{ W}$ . | 70 |

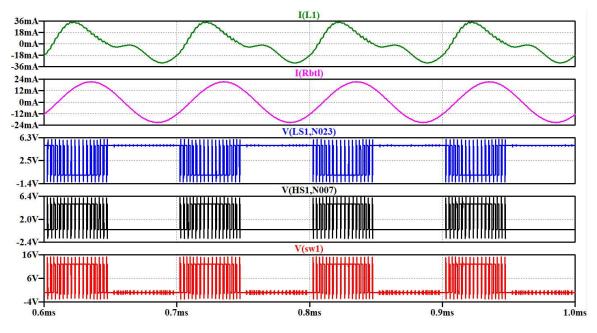

| Figure 3.20 SHEPWM inverter waveform showing one branch inductor and load current,         |    |

| high and low side gate-source voltages, and switching node voltage                         | 71 |

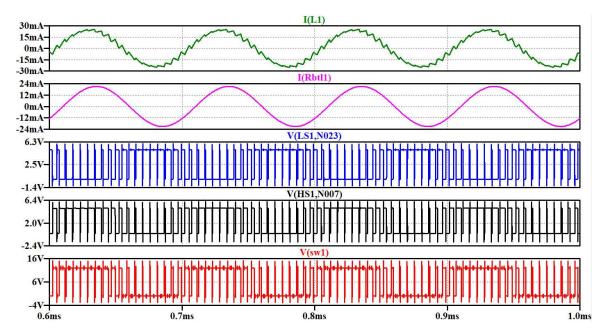

| Figure 3.21 NPWM inverter waveform showing one branch inductor and load current,           |    |

| high and low side gate-source voltages, and switching node voltage                         | 71 |

| Figure 3.22 NPWM inverter in light load: negative inductor current contributing to the     |    |

| rising of switching node voltage during dead-time                                          | 72 |

| Figure 3.23 NPWM inverter in heavy load: negative inductor current contributing to the     |    |

| rising of switching node voltage during dead-time                                          | 72 |

| Figure 4.1 Schematic of a full-bridge inverter output stage                                | 75 |

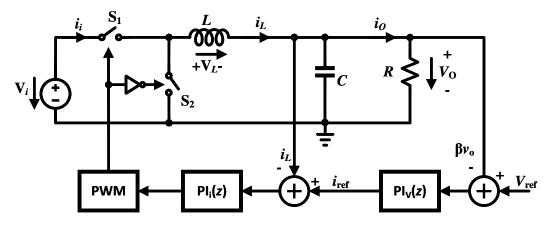

| Figure 4.2 Discrete-time DISMC block diagram for a full-bridge CDA                         | 86 |

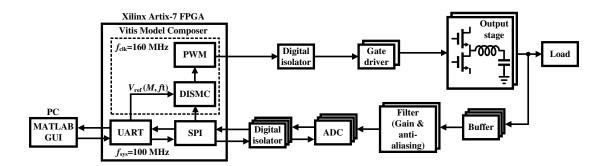

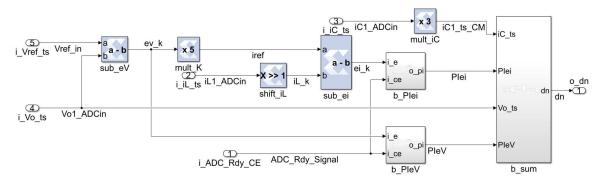

| Figure 4.3 The system architecture of the designed class-D amplifier                       | 86 |

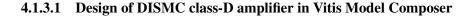

| Figure 4.4 The full-bridge class-D amplifier design in Vitis Model Composer (System        |    |

| Generator)                                                                                 | 87 |

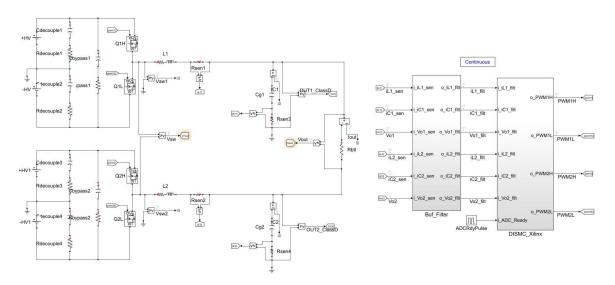

| Figure 4.5 The top level DISMC showing I/Os                                                | 89 |

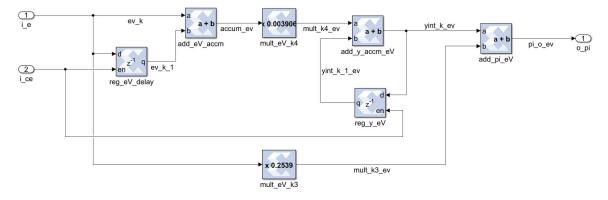

| Figure 4.6 The implementation of DISMC in Xilinx blocksets in Vitis Model Composer         | 89 |

| Figure 4.7 The implementation of proportional-integral in DISMC                            | 90 |

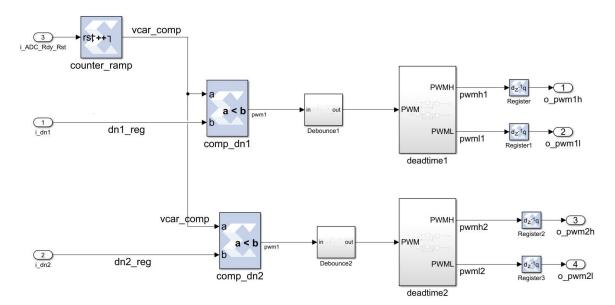

| Figure 4.8 The digital pulse width modulation block                                        | 90 |

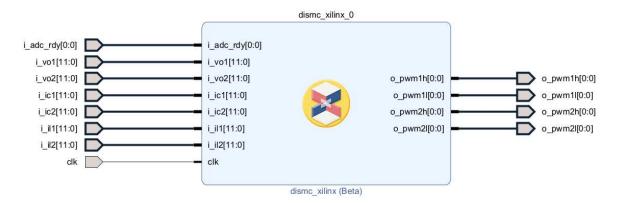

| Figure 4.9 The DISMC IP in Vivado imported from Xilinx Vitis Model Composer                | 91 |

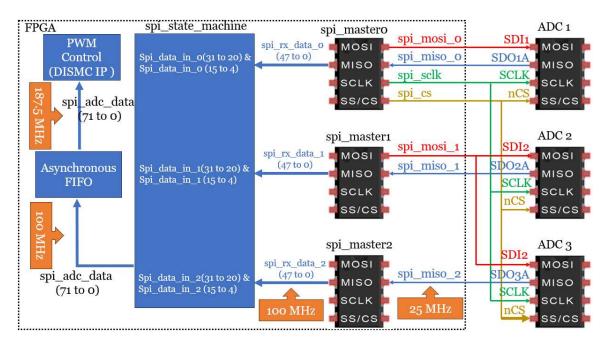

| Figure 4.10 The FPGA block diagrams and its interaction to ADCs                            | 92 |

| Figure 4.11 Steady-state operation of DISMC, ISMC, and PI controllers compared to a        |    |

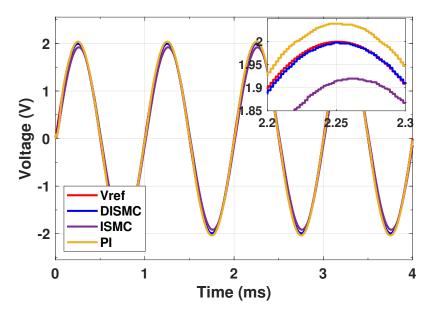

| reference signal.                                                                          | 93 |

| Figure 4.12 Steady-state operation of DISMC, ISMC, and PI controllers compared to a        |    |

| reference signal                                                                           | 94 |

| Figure 4.13 (a) Load current transient from 0.1 A to 1 A and back to 0.1 A. (b) Load       |    |

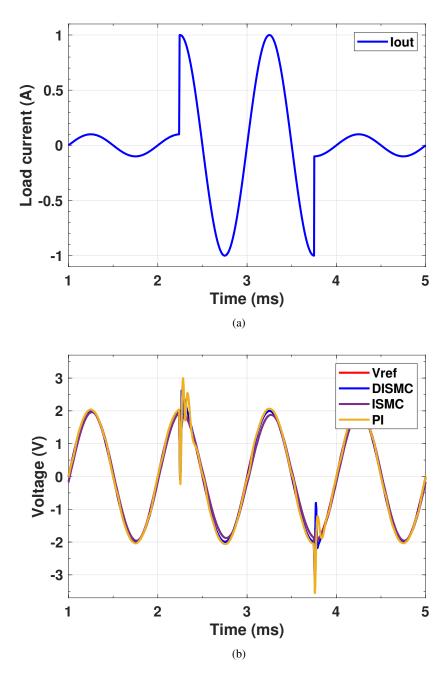

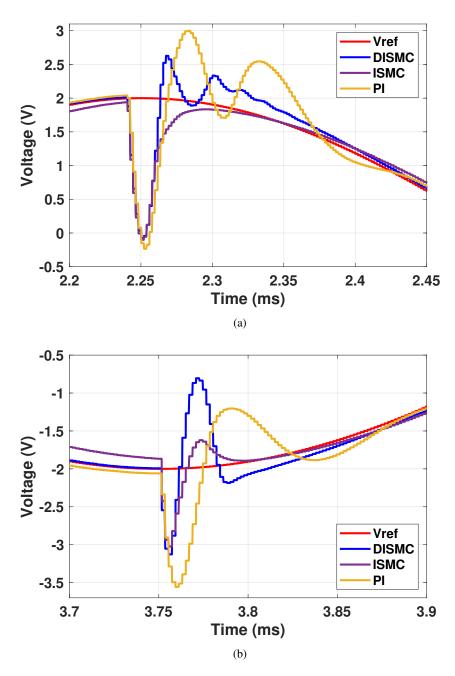

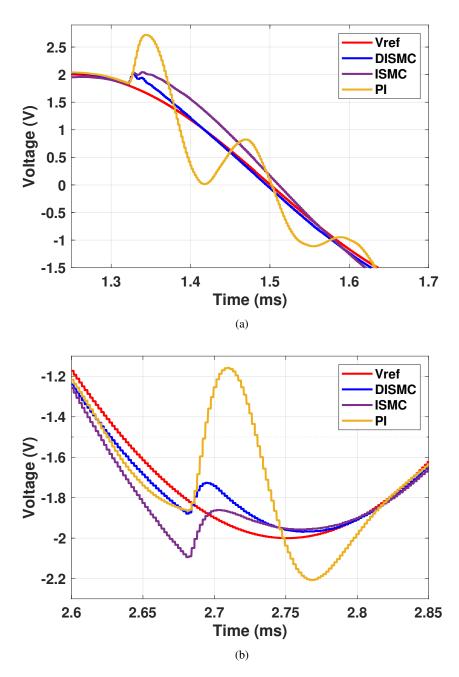

| transient response of DISMC, ISMC, and PI controllers.                                     | 96 |

| Figure 4.14 (a) Enlarged load transient response from light load to heavy load. (b) En-    |    |

| larged load transient response from heavy load to light load.                              | 97 |

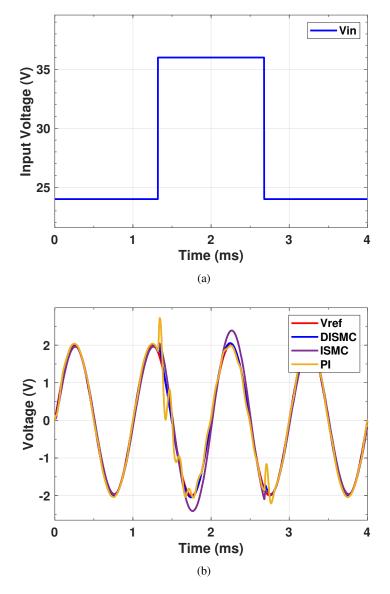

| Figure 4.15 (a) Input voltage transient from 24 V to 36 V and back to 24 V. (b) Line     |     |

|------------------------------------------------------------------------------------------|-----|

| transient response of DISMC, ISMC and PI controllers at light load of 0.1 A              | 98  |

| Figure 4.16 (a) Enlarged line transient response from 24 V to 36 V. (b) Enlarged line    |     |

| transient response from 36 V to 24 V.                                                    | 99  |

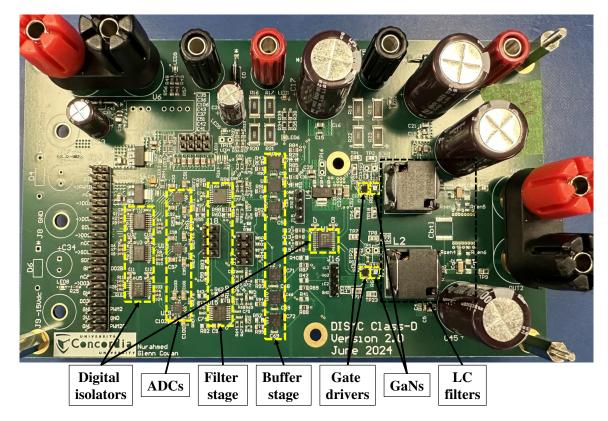

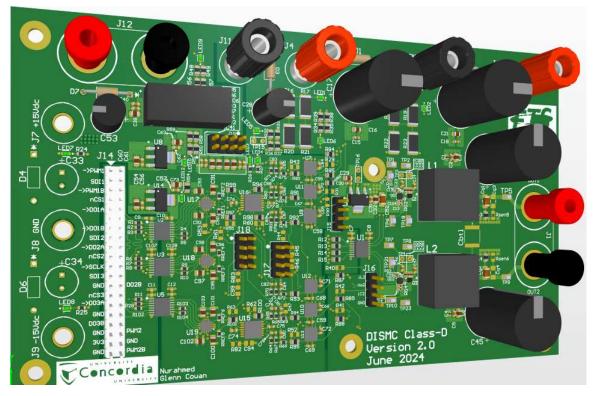

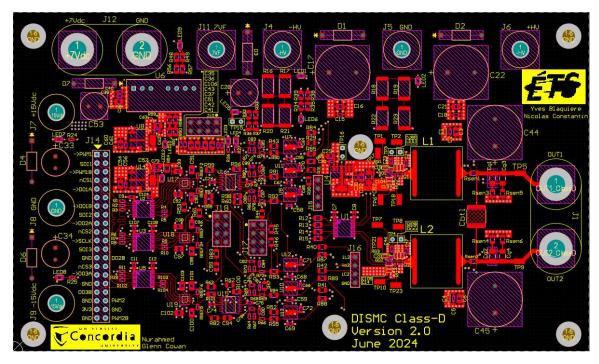

| Figure 4.17 The prototype of DISMC class-D amplifier                                     | 100 |

| Figure 4.18 Test setup for the DISMC class-D amplifier                                   | 101 |

| Figure 4.19 Experimental results of steady state operation of 1 kHz output               | 102 |

| Figure 4.20 Experimental results of steady state operation of 10 kHz output              | 102 |

| Figure 4.21 Experimental results of steady state operation showing both branches switch- |     |

| ing nodes and differential output voltage waveform. (a) When output voltage is           |     |

| positive (b) when output voltage is negative                                             | 103 |

| Figure 4.22 Experimental results of dynamic response under step load changes. (a) Light  |     |

| load jumps to high load, (a) DISMC (b) PI, Heavy load jumps to light load, (c)           |     |

| DISMC (d) PI.                                                                            | 104 |

| Figure 4.23 Measured THD versus modulation index                                         | 106 |

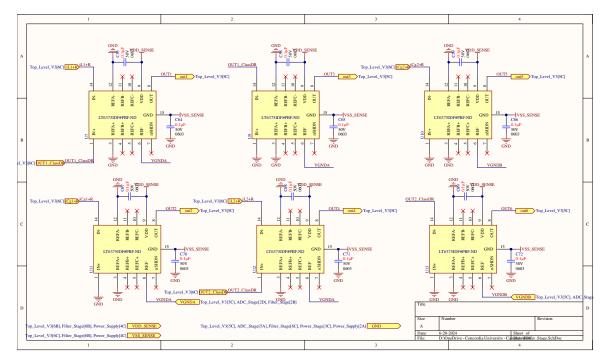

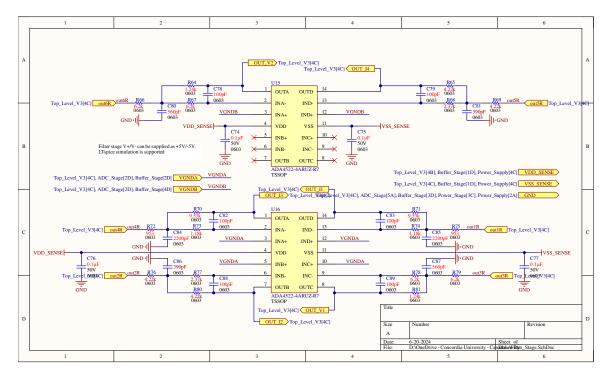

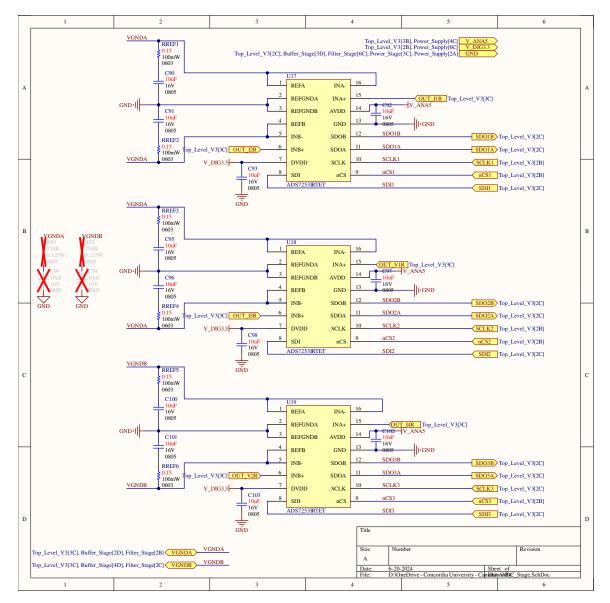

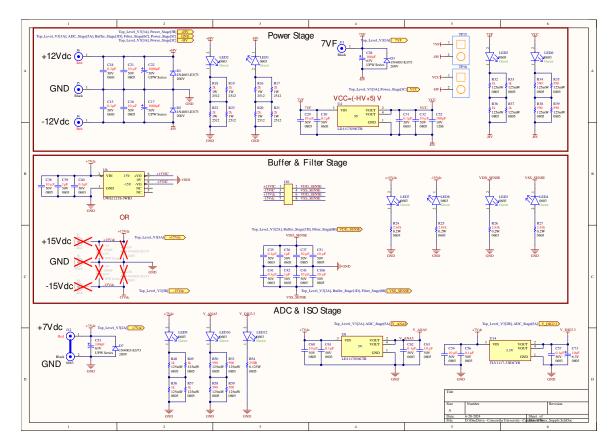

| Figure A.1 Top level schematic                                                           | 112 |

| Figure A.2 Power stage including gate drivers, power GaNFETs and LC filters              | 113 |

| Figure A.3 Buffer stage                                                                  | 114 |

| Figure A.4 Filter stage                                                                  | 114 |

| Figure A.5 Analog to digital converters                                                  | 115 |

| Figure A.6 Power supplies                                                                | 116 |

| Figure A.7 3D view of the DISMC Class-D PCB                                              | 117 |

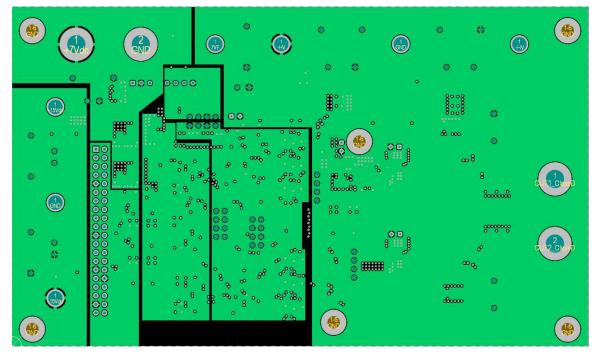

| Figure A.8 Layer 1 of the PCB - components placement and signal traces on top            | 117 |

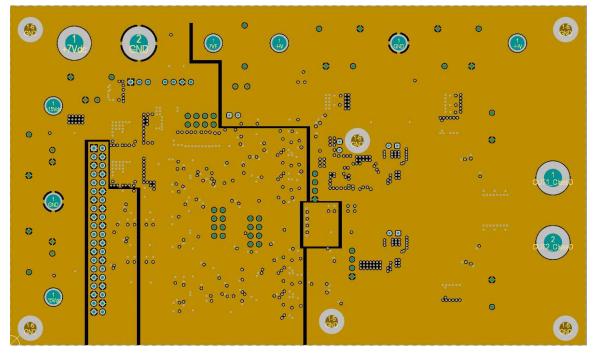

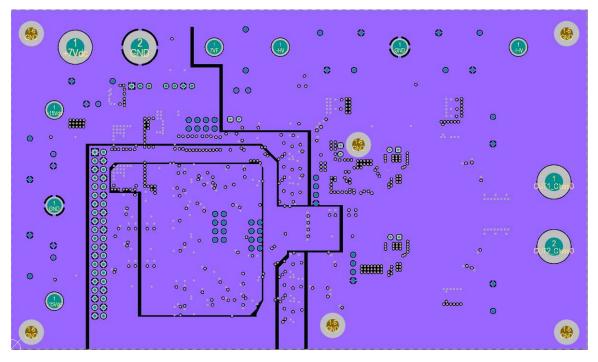

| Figure A.9 Layer 2 of the PCB - ground planes                                            | 118 |

| Figure A.10 Layer 3 of the PCB - power planes                                            | 118 |

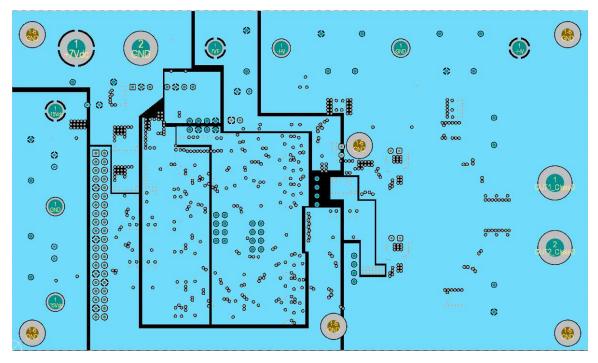

| Figure A.11 Layer 4 of the PCB - power planes                                            | 119 |

| Figure A.12 Layer 5 of the PCB - ground planes                                           | 119 |

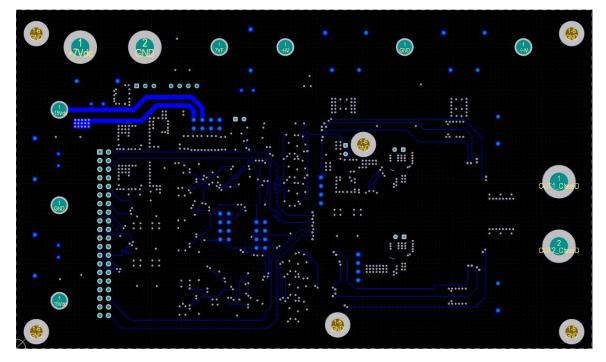

| Figure A.13 Layer 6 of the PCB - signal traces on bottom                                 | 120 |

## **List of Tables**

### Table 3.1 INITIAL GUESSED AND CALCULATED OPTIMAL SWITCHING AN-

| 48  | ES IN DEGREES FOR DIFFERENT MODULATION INDICES (MI)            | GLE       |

|-----|----------------------------------------------------------------|-----------|

| 50  | Lookup Table (LUT) size of the FPGA architecture in Figure 3.5 | Table 3.2 |

| 51  | Lookup Table (LUT) size of the SHEPWM experiment in this work  | Table 3.3 |

|     | SWITCHING ANGLE RESOLUTION IN DEGREES FOR DIFFERENT            | Table 3.4 |

| 51  | NDAMENTAL OUTPUT FREQUENCY                                     | FUN       |

| 59  | SHEPWM INVERTER TEST CONDITIONS                                | Table 3.5 |

|     | POWER OF THE HARMONICS OF THE DIFFERENTIAL SWITCHING           | Table 3.6 |

| 65  | DE VOLTAGE ( $V_{\rm SW}$ )                                    | NOE       |

| 67  | COMPARISON TO OTHER WORKS                                      | Table 3.7 |

| 84  | SYSTEM PARAMETERS                                              | Table 4.1 |

| 84  | CALCULATED COEFFICIENTS                                        | Table 4.2 |

| 100 | COMPONENT PART NUMBERS                                         | Table 4.3 |

### **List of Abbreviations**

- **3D** Three-Dimensional.

- AC Alternating Current.

- ADC Analog-to-Digital Converter.

- **BOM** Bill of Materials.

- BRAM Block Random Access Memory.

- CDA Class-D Amplifier.

- **CPIO** Configurable Power Input/Output.

- **CPIOS** Configurable Power Input/Output System.

- DC Direct Current.

- **DISMC** Double Integral Sliding Mode Control.

- **DSP** Digital Signal Processing.

- EMI Electromagnetic Inteference.

- ESR Equivalent Series Resistance.

- FET Field Effect Transistor.

- FPGA Field Programmable Gate Array.

- FSM Finite State Machine.

- GaN Gallium-Nitride.

- GD Gate Driver.

- GUI Graphic User Interface.

- HDL Hardware Description Language.

- IC Integrated Circuit.

- **ISMC** Integral Sliding Mode Control.

- KCL Kirchhoff's Current Law.

- KVL Kirchhoff's Voltage Law.

- LPF Low-Pass Filter.

- LSB Least-Significant Bit.

- LTCC Low-Temperature Co-fired Ceramics.

- LUT Look-up Table.

- MCU Micro-Controller Unit.

- MEMS Micro-Electro-Mechanical-System.

- MI Modulation Index.

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor.

- NPWM Natural Pulse Width Modulation.

- PC Personal Computer.

- PCB Printed Circuit Board.

PDM Pulse Density Modulation.

- PGND Power Ground.

- PI Proportional-Integral.

PSRR Power Supply Rejection Ratio.

- **PSU** Power Supply Unit.

- **PWM** Pulse Width Modulation.

- RMS Root Mean Square.

SHEPWM Selective Harmonic Eliminated Pulse Width Modulation.

- SiP System-In-Package.

- SMC Sliding Mode Control.

- SMPS Switch Mode Power Supply.

- SNR Signal-to-Noise Ratio.

- **SPI** Serial Peripheral Interface.

- SU Switching Unit.

- SW Switch.

- SysGen System Generator.

- THD Total Harmonic Distortion.

- THD+N Total Harmonic Distortion plus Noise.

- UART Universal Asynchronous Receiver/Transmitter.

- VHDL VHSIC Hardware Description Language.

# **List of Symbols**

| $lpha_k$            | $k^{th}$ switching angle in SHEPWM                     |

|---------------------|--------------------------------------------------------|

| β                   | Scaling factor for the output voltage                  |

| $\boldsymbol{A}$    | Coefficient vector of state variables                  |

| В                   | Coefficient vector of control law                      |

| C                   | m-dimentional coefficient vector of switching fucntion |

| x                   | State variables vector                                 |

| $\Delta \alpha$     | Switching angle resoultion                             |

| η                   | Power efficiency of the converter                      |

| $\hat{v}_{car}$     | Peak amplitude of a carrier signal                     |

| ω                   | Angular frequency in radian/second                     |

| $\omega_{ m LC}$    | Cut-off frequency of LC filter in radian/second        |

| $\omega_n$          | Natural frequency                                      |

| $	riangle I_{ m L}$ | Inductor peak-to-peak current                          |

| ζ                   | Damping ratio                                          |

| $a_0$               | DC component of a Fourier series                       |

$a_n$  Coefficient of the  $n^{th}$  order harmonic of the cosine term in a Fourier series

- $b_n$  Coefficient of the  $n^{th}$  order harmonic of the sine term in Fourier series

- C Capacitor of the output filter

- $C_{\rm DS-H}$  Drain-source capacitance of a high-side transistor

- $C_{\rm DS-L}$  Drain-source capacitance of a low-side transistor

- $C_{\rm GD-H}$  Gate-drain capacitance of a high-side transistor

- $C_{\rm GD-L}$  Gate-drain capacitance of a low-side transistor

- $C_{\text{GS-H}}$  Gate-source capacitance of a high-side transistor

- $C_{\rm GS-L}$  Gate-source capacitance of a low-side transistor

- $C_{\text{OSS-H}}$  Output capacitance of a high-side transistor

- $C_{\rm OSS-L}$  Output capacitance of a low-side transistor

- C<sub>BTL</sub> Bridge-tied capacitor

- $C_{\text{bus}}$  Bus capacitor

- $C_{\text{par}}$  Parasitic output capacitance at the switching-node

- D Duty cycle

- $f_{\rm CLK}$  Clock frequency

- $f_{\rm LC}$  Cut-off frequency of LC filter

- $f_{\rm SW}$  Switching frequency of the converter

- $f_{\rm T}$  Fundamental output frequency

- $I_{\text{AVERAGE}}$  Inductor average current

- $I_{\rm C(RMS)}$  Capacitor RMS current

- *I*<sub>C</sub> Capacitor current

- $I_{\rm DD}$  Input current for a controller

- $I_{\rm IN}$  Input current for a power stage

- *I*<sub>L</sub> Inductor current

- *I*<sub>out</sub> Output current

- $I_{\rm PEAK}$  Inductor peak (max) current

- IVALLEY Inductor valley (min) current

- *I*<sub>DS</sub> Drain-source current

- $I_{\text{IN(AVE)}}$  Average input current of the inverter

- $I_{OUT(RMS)}$  RMS value of the dofferential output current signal

- $i_{\rm ref}$  Reference current

- $I_m$  Peak amplitude of steady-state output current

- $I_{\rm RR}$  Reverse recovery current in a diode

- $K_{ii}$  Integral gain of the current control

- $K_{iv}$  Integral gain of the voltage control

- $K_{pi}$  Proportional gain of the current control

- $K_{pv}$  Proportional gain of the voltage control

- *L* Inductor of the output filter

- *M* The number of modualtion index number

- $M_{\rm HS}$  High-side power transistor

- $M_{\rm LS}$  Low-side power transistor

- *N* The total number of switching angle numbers in SHEPWM

- *n* Harmonic order

- $N_{\rm f}$  The number of fundamental output frequency

- $P_{\rm CAP(ESR)}$  Conduction loss in a capacitor

$P_{\rm COSS}$  Output capacitance loss in the MOSFET

- *P*<sub>ctrl</sub> Controller operation loss

- $P_{\rm D}$  Dead-time loss

- $P_{\rm G}$  Gate charge loss

- $P_{L(DCR)}$  Conduction loss in an inductor

- $P_{\rm ON-H}$  Conduction loss for high-side transistor

- $P_{\rm ON-L}$  Conduction loss for low-side transistor

- $P_{\rm SW-H}$  Switching loss for high-side transistor

- $P_{\rm SW-L}$  Switching loss for low-side transistor

- P<sub>DIODE</sub> Reverse recovery loss in a diode

- R Load resistor

- $R_{\rm DCR}$  DC resistance of an inductor

- $R_{\rm ESR}$  Equivalent series resistance of a capacitor

- $R_{\rm ON-H}$  Turn-on resistance of a high-side transistor

- $R_{\rm ON-L}$  Turn-on resistance of a low-side transistor

- $R_{\rm BTL}$  Bridge-tied load

- $R_{\text{DS(ON)}}$  Drain-source turn on resistance of a transistor

- $R_{\text{PATH}}$  Path resistance from converter input supply to output node

- S Sliding surface

- s(x) Switching function of state variables

- *T* Fundamental period of sinewave output signal

- t Time

- $t_{\rm Df}$  Dead-time in falling

- $t_{\rm Dr}$  Dead-time in rising

- $t_{\rm f-H}$  Fall time of a high-side transistor

- $t_{\rm f-L}$  Fall time of a low-side transistor

- $t_{\rm OFF}$  Transistor turn-off time

- $t_{\rm ON}$  Transistor turn-on time

- $t_{\rm r-H}$  Rise time of a high-side transistor

- $t_{r-L}$  Rise time of a low-side transistor

#### t<sub>d</sub> Dead-time

- $T_s$  Sampling period

- $t_{\rm RR}$  Reverse recovery time in a diode

- *u* Control law

- $u_{eq}$  Equivalent control law

- $V_{\rm DD}$  Input supply voltage for the controller and/or gate driver

- *V*<sub>D</sub> Body-diode voltage of a power transistor

- *v*<sub>C</sub> Capacitor voltage

- V<sub>DS</sub> Drain-source voltage

- $V_{\rm HS}$  Gate voltage of high-side transistor

- $V_{\rm IN}$  Input supply voltage to a power stage

- $V_{\rm LS}$  Gate voltage of low-side transistor

- V<sub>L</sub> Inductor voltage

V<sub>OUT(RMS)</sub> RMS value of the differential output voltage signal

- V<sub>PWM</sub> PWM input signal of a gate driver

- V<sub>ref</sub> Reference voltage

- $V_{\text{signal}}$  Input signal of an amplifier

- $V_{\rm SW}$  Switching node voltage

- $v_c$  Control signal

- $V_m$  Peak amplitude of steady-state output voltage

### Chapter 1

### Introduction

Low-power loads, such as industrial servo valves, hall effect sensors, and low-power actuators, often operate using a differential output sine wave, and are commonly used in industries such as automotive and other critical power systems. The typical operating frequency of these loads ranges from several kHz to 10 kHz. The choice of amplifier architecture plays a critical role in achieving both high efficiency and linearity. Traditional amplifiers, such as Class A, B, and AB, suffer from limited efficiency, requiring bulky heat sinks that increase the size and weight of the overall power delivery system.

Switching amplifiers, by contrast, offer significantly higher efficiency, eliminating the need for large heat sinks and relaxing thermal design constraints. However, their inherently nonlinear operation, caused by the switching of power transistors between on and off states, introduces unwanted distortions at the amplifier output if not carefully designed. Although switching amplifiers are more efficient than their linear counterparts, this does not guarantee consistently high efficiency across all operating ranges. Switching losses are intrinsic to these amplifiers, and a trade-off must be made between switching and conduction losses.

Digital control of switching amplifiers benefits from process scaling and the ease of configurability, whereas analog circuits are limited by reduced supply voltages and decreased linearity. However, since the loads are inherently analog, there is still a need for sensing amplifiers, signal conditioning, and the conversion of analog signals into the digital domain. Integrating both the power stage and readback circuitry can occupy significant board space, leading to increased system size and cost.

In this research, we focus on designing fully differential switching amplifiers that deliver high efficiency to the load while improving linearity and accuracy, all within a compact board size. Gallium-Nitride (GaN) power transistors are employed in the power stage due to their small footprint and fast switching capabilities. Two control and modulation techniques are explored: Selective Harmonic Eliminated Pulse Width Modulation (SHEPWM), aimed at reducing the switching activity of the power transistors to achieve superior efficiency in low-power operating ranges, and Double Integral Sliding Mode Control (DISMC), known for its robustness and high accuracy, utilizing a double-loop control strategy. The goal is to achieve superior performance in both efficiency and linearity, while also minimizing the overall system size through the integration of power stages and readback circuitry into a system-in-package (SiP). Furthermore, the digital control is implemented on an Field Programmable Gate Array (FPGA) platform, offering versatility by allowing easy adjustments to control parameters. This flexibility enables fine-tuning of the system to achieve optimal performance under varying operating conditions, making it adaptable to different application requirements.

#### **1.1** Motivation

Recent advances in microelectronic fabrication have enabled the development of smaller and lighter power electronics boards. However, reducing system volume and replacing bulky power electronic components with reconfigurable units is essential to further minimize overall size and effectively distribute power to various loads operating under different conditions. In automotive and other industrial applications where safety is critical, designing redundancy is crucial to ensure continuous operation despite potential component failures. Such a system can be described as a Configurable Power Input/Output System (CPIOS), as illustrated in Figure 1.1. The main components of the CPIOS include:

An array of Configurable Power Input/Output (CPIO) units, which can be integrated into a SiP to reduce size and weight.

Figure 1.1: The block diagram of CPIOS

- 2. Power Supply Units (PSUs) that regulate the power of the CPIO-SiP.

- 3. A configuration system that interconnects the CPIO-SiP units, determining which units operate and replacing any that fail.

- 4. An interface to a digital control unit such as a FPGA, Digital Signal Processing (DSP) board, or Micro-Controller Unit (MCU), which controls the system.

- 5. An interface to the load, connecting the CPIO-SiP array to various loads.

With such a CPIOS system, different power topologies such as Direct Current (DC)-DC buckboost converters, Class-D Amplifiers (CDAs), and line drivers within CPIO can be controlled with a digital control unit to drive different loads. Additionally, redundancy of the CPIO-SiP is ensured, allowing for control and configuration to decide which unit to operate and to replace any failed CPIO system, thus ensuring continued operation of the CPIOS.

The major component of the CPIOS is the CPIO design. The CPIO consists of:

- 1. Configurable Switching Units (SUs) array. Each SU includes a gate driver and power devices such as GaN. Given that the SU is the most critical part, it is essential to design for redundancy and ensure continuous operation of the system.

- 2. Readback circuitry, which includes sensing and buffer circuits, filters to remove high-frequency noise and provide gain for the desired signal, and Analog-to-Digital Converters (ADCs) to convert the measured output signals to digital signals.

- 3. Digital isolation, which isolates the FPGA from the entire CPIO system.

- 4. Power Micro-Electro-Mechanical-System (MEMS) Switchs (SWs), which serve as the configuration interface between the SUs and the loads. The continuous operation of the system is achieved by the MEMS SWs in case of failures in the critical SUs.

- 5. Other components specific to different control systems, such as DC-DC converters, CDAs, and line drivers.

- 6. A fault detection system, which performs early diagnostic detection of system failures or aging components to enable early failure detection.

- 7. Research on Electromagnetic Inteference (EMI) and power integrity among the subsystems, aiming to reduce interferences between subsystems, such as noisy high-power SUs and other sensitive low-power analog circuits in the readback subsystem. This also ensures efficient power delivery from the source to the destination, maintaining the power integrity of the system.

### **1.2 Focus of This Work**

This work focuses on elaborating the methods and techniques for designing the CPIO. The research primarily investigates the design of the SUs, readback circuits, and control algorithms. The CPIO can be integrated into a SiP to reduce the footprint size and weight of the electronic board. However, this integration largely depends on the current available SiP technology and the selection of components to be integrated. In terms of electronic design, the major components of the CPIO remain largely unchanged.

To deliver efficient power to the load, Switch Mode Power Supplies (SMPS) are advantageous due to their highly efficient operation and the elimination of heat sinks compared to class-A, B, and AB amplifiers. This enables the reduction of the PCB area and thermal budget of the electronic system. CDAs are a type of SMPS that can deliver arbitrary voltage/current waveforms to the load, unlike DC-DC converters which regulate the output voltage/current to a constant value. In this work, most of the loads require a sine wave output voltage/current, while a few require a DC output. The CDA in a full-bridge topology is chosen to deliver differential output voltages/currents efficiently to the load.

This work is a collaboration between researchers in different fields to achieve the final goal of CPIOS. The research areas in this work include the blocks of SU, sensing and buffer circuits, gain and filter stages, ADCs, digital isolation, and control algorithms for the CDA, which are highlighted with an asterisk (\*) in Figure 1.1.

The differential output power delivered from the CDA is primarily intended for low-power loads. The major power-consuming blocks in the CPIO are the SUs, or power stages. For low output power, switching losses in power stages dominate over conduction losses. Therefore, one of the challenges of this research is to decrease the switching frequency of the CDA without sacrificing THD. To address this, the SHEPWM technique is investigated in this work. SHEPWM is particularly attractive because it significantly reduces the switching frequency of Pulse Width Modulation (PWM) while canceling lower-order harmonics, thereby improving efficiency. This makes SHEPWM an ideal choice for applications requiring high efficiency and low harmonic distortion, aligning with the objectives of this research. In addition to SHEPWM, this work explores the application of Sliding Mode Control (SMC) to address the challenges associated with precise control of the CDA. The gain of a CDA is directly influenced by the input supply voltage, which can degrade output accuracy in the presence of ripples or noise. Traditional feedback mechanisms typically compensate after the power stage for simplicity, but this research investigates feedback after the LC filter to directly improve the accuracy of the output voltage/current at the load. SMC is particularly well-suited for this purpose due to its robustness against parameter variations and external disturbances. By leveraging SMC, this work aims to enhance the load/line regulation, achieve precise regulation of output voltage/current, and ensure stable operation under varying conditions. Together, these attributes make SMC a powerful tool for improving the performance and reliability of the CDA.

#### **1.2.1** Problem Statement

Efficiently delivering differential output power to low-power loads using CDA presents several challenges, particularly in applications requiring high efficiency, low distortion, and compact design. Unlike high-power electronics, low-power systems demand innovative solutions to address issues such as switching losses, dynamic load conditions, and precise control of output voltage/current. Furthermore, the integration of advanced control techniques, such as SHEPWM and SMC, into low-power CDA design introduces additional complexities.

The key challenges identified in this research are as follows:

- P1: Existing implementations of SHEPWM are primarily designed for high-power electronics, characterized by fixed filter sizes, fixed output frequencies, and minimal load variation. A detailed review of these implementations is provided in Section 2.4. However, adapting SHEPWM for low-power applications with diverse operating conditions and dynamic load variations remains an unexplored research area.

- **P2**: Minimizing the PCB footprint size is critical for low-power systems. Power stages and digital isolators occupy significant board area, necessitating exploration of new SiP technologies to integrate these components and reduce the overall footprint.

- P3: Discrete implementation of DISMC for CDA applications remains largely unexplored.

Challenges such as phase delay introduced by the LC filter and the high-frequency switching dynamics need to be addressed.

• **P4**: While double-loop DISMC has been successfully implemented in DC-DC converters, its application to CDA systems is complicated by the time-varying nature of the reference signal. Stability analysis for such systems remains an open research problem.

By addressing these challenges, this research aims to advance the design of CDA systems for low-power applications, leveraging the unique capabilities of SHEPWM and SMC to achieve high efficiency, precise control, and compact integration.

#### **1.2.2 Research Objectives**

The primary objective of this research is to design a full-bridge CDA that efficiently delivers differential output power to the load while addressing the identified challenges. This involves tailoring advanced techniques such as SHEPWM and SMC to meet the unique requirements of low-power applications.

To address the challenges outlined in Section 1.2.1, the following specific research objectives are defined:

- **O1**: Investigate and adapt the SHEPWM technique to reduce the switching frequency of the CDA without compromising THD for low-power applications. Develop a unique FPGA-based architecture to implement SHEPWM, enabling on-the-fly configuration of inverter outputs to dynamically adjust to varying load conditions. (Addresses problem statement **P1**)

- **O2**: Develop a tailored SHEPWM approach to accommodate a wide range of operation and variable load conditions in low-power systems. Simultaneously, explore a new SiP technologies to minimize the PCB footprint by integrating power stages and digital isolators, thereby reducing the overall size of the CDA. (Addresses problem statement **P2**)

- **O3**: Conduct an in-depth investigation into the development of a discrete DISMC framework for CDA systems. This research aims to address the fundamental challenges posed by phase

delays inherent in the system dynamics, ensuring robust and precise control under varying operational conditions. (Addresses problem statement **P3**)

• **O4**: Explore the application of double-loop DISMC to CDA systems, considering the timevarying nature of the reference signal, and perform stability analysis to ensure reliable operation. (Addresses problem statement **P4**)

By achieving these objectives, this research aims to advance the state of the art in low-power CDA design, enabling high efficiency, precise control, and compact integration.

### **1.3 Fundamentals of Class-D Amplifiers**

CDAs, first introduced in 1958, have seen a significant rise in popularity in recent years Gaalaas (2006). Also known as switching amplifiers or digital amplifiers, CDAs represent a notable advancement in amplifier technology, particularly due to their high efficiency and compact design. Unlike traditional linear amplifiers (class A, B, and AB), which operate transistors in their linear region and consequently suffer from substantial power losses and heat dissipation, CDAs use a different approach to amplification. Even a well-designed class AB amplifier experiences significant power dissipation because its midrange output voltages are generally far from either the positive or negative supply rails. This results in large drain-source voltage drops, producing substantial instantaneous power dissipation.

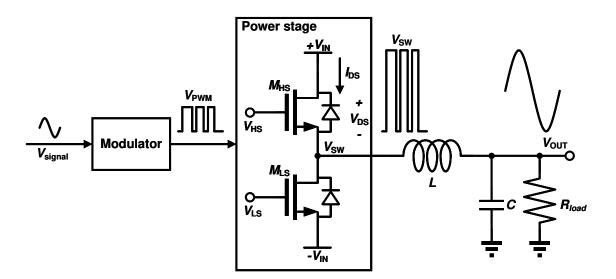

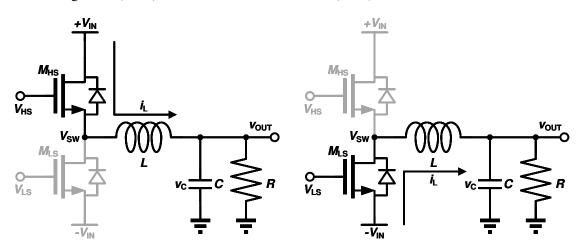

In contrast, CDAs employ a topology that significantly reduces power dissipation. Figure 1.2 illustrates the basic CDA open-loop block diagram. The input signal ( $V_{signal}$ ) is modulated to generate small voltage pulses ( $V_{PWM}$ ). Among various modulation techniques, PWM is the most common. The output power stage of a class-D amplifier switches between the positive ( $+V_{IN}$ ) and negative ( $-V_{IN}$ ) power supplies to produce a train of large voltage pulses at the switching node,  $V_{SW}$ . This power stage, also known as a half-bridge, contains two output transistors: a high-side transistor ( $M_{HS}$ ) and a low-side transistor ( $M_{LS}$ ).

The PWM signal ( $V_{PWM}$ ) cannot directly drive the half-bridge power transistors due to their large size. Therefore, a gate driver circuit is typically used to drive the gate terminals of the power

transistors. The gate voltages ( $V_{\text{HS}}$  and  $V_{\text{LS}}$ ) for the high-side and low-side power transistors are turned on in a complementary manner to avoid cross-conduction, a function usually managed by the gate driver. Sometimes, the controller generates complementary PWM signals if the gate driver lacks a dead-time generation block.

This switching mechanism is efficient because the output transistors carry zero current when not switching and maintain a low drain-source voltage ( $V_{DS}$ ) when conducting current. As a result, the product of current ( $I_{DS}$ ) and voltage ( $V_{DS}$ ) is minimized, leading to significantly lower power dissipation compared to linear amplifiers. By driving the transistors either fully on or fully off, CDAs minimize the time spent in high-power dissipation states, thereby achieving greater efficiency.

The amplified switching node voltage  $(V_{SW})$  is then filtered by an LC filter to reconstruct the original input signal ( $V_{signal}$ ). The LC filter effectively removes the high-frequency switching components, allowing the desired low-frequency signal to pass through, thereby recreating a clean and amplified version of the original input signal at the output.

The primary advantage of CDAs is their high efficiency, which results in significantly lower power and heat dissipation compared to other amplifier classes. Consequently, the heat sinks typically required for other amplifiers can be greatly reduced or even eliminated. However, one drawback of CDAs is that their output signal is a square wave at full power, which must be filtered before being applied to the load. This necessitates the use of an LC filter, which occupies Printed Circuit Board (PCB) space and increases the Bill of Materials (BOM). Additionally, CDAs generate switching noise due to the rapid switching of power transistors and the presence of parasitic inductances and capacitances. This noise can increase EMI radiation and degrade the power integrity of other sensitive analog circuits.

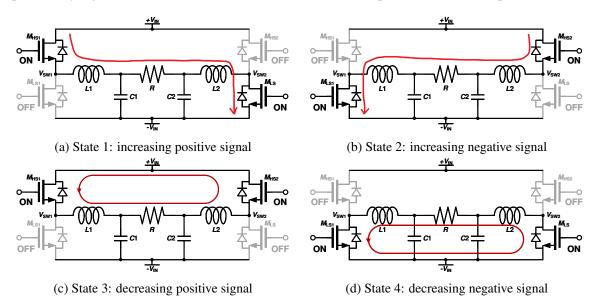

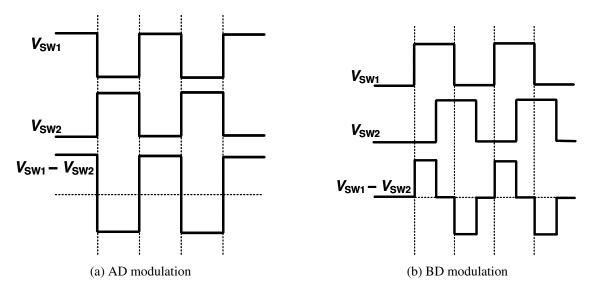

For PWM, the two popular modulation schemes are AD and BD modulation, where D stands for Class-D, and A and B denote the order in which they were invented. Figures 1.3a and 1.3b show how the H-bridge operates with an AD modulation scheme, which essentially has two states. The high-side and low-side transistors in each half-bridge are switched alternately. When the highside transistor is ON, the low-side is OFF, and vice versa. The switching node voltage  $V_{SW2}$  is a complement of  $V_{SW1}$ . The differential switching node voltage produces a two-level switching waveform as shown in Figure 1.4a.

Figure 1.2: class-D amplifier open-loop block diagram

In BD modulation, there are four states as shown in Figure 1 (a), (b), (c), and (d) depending on the input signal conditions: increasing positive signal, increasing negative signal, decreasing positive signal, and decreasingly negative signal. The differential switching node voltage produces a three-level switching waveform as shown in Figure 1.4b. Both half-bridges operate in a complementary fashion, which helps to balance the output and reduce common-mode noise. By using complementary signals, BD modulation minimizes the EMI and improves overall noise performance.

Figure 1.3: Full-bridge output stage operation

Figure 1.4: Full-bridge switching waveform

Class-D modulators can be implemented in various ways. Here we introduces some fundamental concepts. The most common modulation technique is PWM. In PWM, the input signal is compared to a triangular or ramp waveform running at a fixed carrier frequency, generating a stream of pulses at the carrier frequency. Within each carrier period, the duty cycle of the PWM pulse is proportional to the amplitude of the input signal.

Another modulation technique is Pulse Density Modulation (PDM), where the number of pulses in a given time window is proportional to the average value of the input signal. Unlike PWM, PDM has "quantized" pulse widths that are multiples of the modulator clock period. One-bit sigma-delta modulation is a form of PDM. Sigma-delta modulation spreads high-frequency energy over a wide range of frequencies rather than concentrating it at multiples of a carrier frequency as PWM does. This distribution can offer an EMI advantage.

Recently, self-oscillating amplifiers have been developed. These amplifiers include a feedback loop that determines the switching frequency of the modulator, rather than relying on an external clock. High-frequency energy in self-oscillating amplifiers is often more evenly distributed than in PWM. The feedback loop enables excellent performance, but because the loop is self-oscillating, it is challenging to synchronize with other switching circuits or connect to digital sources without first converting the digital signal to analog.

To effectively compare the performance of the CDA, it is crucial to understand its performance

metrics. These metrics can be categorized into three main groups: time domain measurements, frequency domain measurements, and power measurements.

- Time Domain Measurements: These include both steady-state operation and dynamic performance. Dynamic performance encompasses line and load transitions, as well as the quantified ability for line and load regulation.

- 2. Frequency Domain Measurements: This category includes THD, Total Harmonic Distortion plus Noise (THD+N), Signal-to-Noise Ratio (SNR), and PSRR.

- 3. Power Measurements: The primary metric in this group is power efficiency.

Each of these metrics provides valuable insights into the performance and suitability of a CDA for various applications.

### **1.4 Thesis Outline and Publications**

The first chapter of this thesis provides the motivation, scope, and objectives of the research. Additionally, this chapter introduces the fundamental concepts of CDA operation, offering a foundation for understanding the advanced techniques discussed in subsequent chapters.

Chapter 2 presents a comprehensive review of the existing literature related to CDAs, focusing on several key areas. In Section 2.1, the various sources of power dissipation in CDAs are reviewed, highlighting their impact on efficiency. The CDA architectures and modulation techniques discussed in the literature are reviewed in Section 2.2. Section 2.3 provides the necessary background information on the SHEPWM technique, followed by a review of the latest advancements and current state of the art in SHEPWM techniques in Section 2.4. Section 2.5 presents the fundamental principles of SMC, providing the necessary background for its application in CDAs. Section 2.6 reviews research and developments in SMC techniques, focusing on their implementation in power electronics.

Chapter 3 details the design, simulation, and experimental results of the SHEPWM inverter. Section 3.1 describes the design methodology and implementation of the SHEPWM inverter. The simulation and experimental results are presented and discussed in Section 3.2, providing a thorough analysis of the inverter's performance. The chapter concludes with Section 3.3, which summarizes the findings and offers recommendations for improvement. This chapter led to one conference paper and one journal paper as the first author, along with two conference papers as the second author. The key contributions of this chapter include bridging the gap in utilizing the SHEPWM technique, which has primarily been applied in high-power grid applications, to its implementation in a low-power inverter where higher frequencies can also be employed with high efficiency. Furthermore, the on-the-fly configuration of the SHEPWM inverter output is achievable with the unique SHEPWM architecture introduced in this chapter. Additionally, the SHEPWM inverter is implemented in a compact 3-D LTCC SiP technology, demonstrating that size reduction compared to traditional boards is feasible.

Chapter 4 focuses on the design and evaluation of the DISMC for CDAs. Section 4.1 explains the design approach and methodology used to implement the DISMC. The performance of the DISMC CDA is evaluated through simulation and experimental results in Section 4.2, followed by a detailed discussion. The chapter concludes with Section 4.3, providing a summary of the findings and their implications for future research. This chapter led to one conference paper and is expected to result in one journal paper. The key contributions of this chapter include not only the theoretical contribution of defining the stability condition and determining the controller gain but also the experimental demonstration that DISMC can be implemented in CDA, where the reference signal is time-varying, complicating the stability analysis of the controller compared to DC-DC converters, where the reference is constant. Furthermore, it shows that DISMC outperforms traditional proportional-integral (PI) controllers in terms of handling large signal variations, such as line and load regulations.

The final chapter, Chapter 5, provides a comprehensive summary of the research conducted, highlighting key contributions and findings. It includes recommendations for future work and potential areas for further investigation.

The papers are listed below in chronological order.

• N. Ly, N. Aimaier, A. H. Alameh, Y. Blaquière, G. Cowan, and N. G. Constantin, "A High Voltage Multi-Purpose On-the-fly Reconfigurable Half-Bridge Gate Driver for GaN

HEMTs in 0.18-μm HV SOI CMOS Technology," 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS), Montreal, QC, Canada, 2020, pp. 178–181, doi: 10.1109/NEWCAS49341.2020.9159781.

- N. Aimaier, N. Ly, G. Nobert, Y. Blaquière, N. Constantin, and G. Cowan, "SHEPWM Class-D Amplifier with a Reconfigurable Gate Driver Integrated Circuit," *2021 IEEE International Symposium on Circuits and Systems (ISCAS)*, Daegu, Korea, 2021, pp. 1–5, doi: 10.1109/IS-CAS51556.2021.9401689.

- V. H. Nguyen, N. Aimaier, et al., "A Reconfigurable Power System-in-Package Module using GaN HEMTs and IC Bare Dies on LTCC Substrate: Design - Implementation - Experiment and Future Directions," 2022 20th IEEE International New Circuits and Systems Conference (NEWCAS), Quebec City, QC, Canada, 2022, pp. 188–192, doi: 10.1109/NEW-CAS52662.2022.9842234.

- N. Aimaier, N. Constantin, and G. Cowan, "A Pulsewidth Modulation Based Double Integral Sliding Mode Controller for Class-D Amplifiers," 2023 IEEE 14th International Conference on Power Electronics and Drive Systems (PEDS), Montreal, QC, Canada, 2023, pp. 1–5, doi: 10.1109/PEDS57185.2023.10246506.

- N. Aimaier, Y. Blaquière, N. G. Constantin, and G. E. R. Cowan, "An FPGA-Based On-the-Fly Reconfigurable Low-Power SHEPWM Inverter With a Compact SiP Implementation," *IEEE Transactions on Power Electronics*, vol. 39, no. 5, pp. 5942–5953, May 2024, doi: 10.1109/TPEL.2024.3364534.

- N. Aimaier, Y. Blaquière, N. G. Constantin and G. E. R. Cowan, "A PWM-Based Discrete Double Integral Sliding Mode Current Controller Design for a Class-D Amplifier," submitted to *IEEE Journal of Emerging and Selected Topics in Power Electronics*.

## **Chapter 2**

# **Literature Review**

In this chapter, a review of the most recent literature has been conducted. Given the focus on designing a low-power full-bridge CDA, it is imperative to delve into the mechanisms responsible for power losses within the CDA. Section 2.1 thoroughly examines all power losses within the CDA. An overview of CDA architectures and their implementations, along with a brief description of existing modulation techniques, is provided in Section 2.2. Subsequently, in Section 2.3, the chapter delves into the background of SHEPWM, which plays a crucial role in reducing switching losses. Then, the current state-of-the-art SHEPWM techniques are reviewed. Additionally, the background of a robust non-linear controller with a feedback loop, specifically SMC, is discussed in Section 2.5, with an emphasis on its current advancements and different derivatives in the realm of converters. Finally, Section 2.6 offers insights into the state-of-the-art techniques employed in power converters, including SMPS and CDA fields.

#### 2.1 Class-D Amplifier (CDA) Power Dissipation Sources

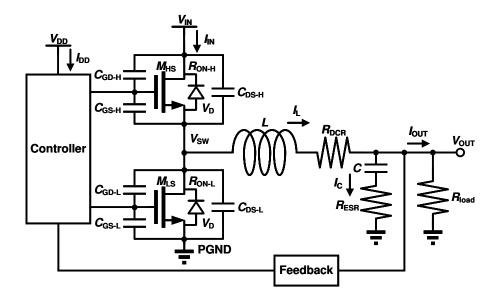

In this section, a power loss estimation for the half-bridge converter is reviewed. Figure 2.1 depicts the circuit diagram of a half-bridge CDA, including parasitic capacitances and resistors. The switching node voltage and inductor current waveform are given in Figure 2.2.

Figure 2.1: Circuit diagram of the half-bridge class-D amplifier for power loss analysis.

The calculation of power loss for the half-bridge CDA is as follows:

• Conduction loss:

$$(1) P_{\rm ON-H} = I_{\rm OUT}^2 \times R_{\rm ON-H} \times D$$

$$(2) P_{\rm ON-L} = I_{\rm OUT}^2 \times R_{\rm ON-H} \times (1-D)$$

$$(2)$$

where  $I_{OUT}$  is the output current,  $R_{ON-H}$  and  $R_{ON-L}$  are the turn-on resistance of a high-side and low-side transistors, D represents the duty cycle, denoting the duration of the high-side power Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) turn-on time, while (1 - D) corresponds to the turn-off time.

• Switching loss:

$$(3) (4) P_{\rm SW-H} = \frac{1}{2} \times V_{\rm IN} \times I_{\rm OUT} \times (t_{\rm r-H} + t_{\rm f-H}) \times f_{\rm SW}$$

$$(3)$$

where  $t_{\rm r-H}$  and  $t_{\rm f-H}$  are the rise and fall time of the high-side transistor,  $f_{\rm SW}$  is the switching

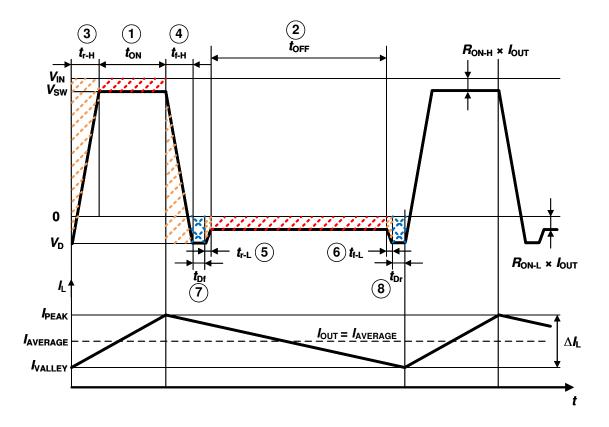

Figure 2.2: The diagram of switching node voltage and inductor current waveform and power loss.

frequency of the converter,  $V_D$  is the voltage drop of the body diode,  $t_{r-L}$  and  $t_{f-L}$  are the rise and fall time of the low-side transistor.

• Dead-time loss:

$$(7) \otimes P_{\rm D} = V_{\rm D} \times I_{\rm OUT} \times (t_{\rm Dr} + t_{\rm Df}) \times f_{\rm SW}$$

(5)

where  $t_{\rm Dr}$  and  $t_{\rm Df}$  are the dead-time in rising and falling.

• Controller operation loss:

$$P_{\rm ctrl} = V_{\rm DD} \times I_{\rm DD} \tag{6}$$

where  $V_{\rm DD}$  and  $I_{\rm DD}$  are the controller operating voltage and current.

• Gate charge loss:

$$P_{\rm G} = (C_{\rm GS-H} + C_{\rm GS-L}) \times V_{\rm DD}^2 \times f_{\rm SW}$$

(7)

where  $C_{GS-H}$  and  $C_{GS-L}$  are the gate-source capacitance of the high and low side transistors.

• Output capacitance loss in the MOSFET:

$$P_{\rm COSS} = \frac{1}{2} \times (C_{\rm OSS-H} + C_{\rm OSS-L}) \times V_{\rm IN}^2 \times f_{\rm SW}$$

(8)

where

$$C_{\rm OSS-H} = C_{\rm DS-H} + C_{\rm GD-H} \tag{9}$$

$$C_{\rm OSS-L} = C_{\rm DS-L} + C_{\rm GD-L} \tag{10}$$

where  $C_{\text{DS}-\text{H}}$  and  $C_{\text{DS}-\text{L}}$  are the drain-source capacitance of the high and low side transistors,  $C_{\text{GD}-\text{H}}$  and  $C_{\text{GD}-\text{L}}$  are the gate-drain capacitance of the high and low side transistors.

• Conduction loss in inductor:

$$P_{\rm L(DCR)} = I_{\rm OUT}^2 \times R_{\rm DCR} \tag{11}$$

where  $R_{\rm DCR}$  is the DC resistance of the inductor.

• Conduction loss in capacitor:

$$P_{\rm CAP(ESR)} = I_{\rm C(RMS)}^2 \times R_{\rm ESR}$$

(12)

where  $I_{C(RMS)}$  is the capacitor Root Mean Square (RMS) current,  $R_{ESR}$  is the Equivalent Series Resistance (ESR) of the capacitor.

• Reverse recovery loss:

$$P_{\text{DIODE}} = \frac{1}{2} \times V_{\text{IN}} \times I_{\text{RR}} \times t_{\text{RR}} \times f_{\text{SW}}$$

(13)

where  $I_{RR}$  is the peak value of body-diode reverse recovery current, and  $t_{RR}$  is the body-diode reverse recovery time.

Additionally, it's worth noting that power losses arising from factors such as ripple current in the inductor and magnetic core losses are also present. However, these losses, while related to switching frequency, are of relatively minor significance and have been excluded from the discussion due to their negligible impact on the overall assessment.

In a half-bridge CDA, the total power loss is the sum of all the aforementioned losses. Among these, conduction loss and switching loss of the power transistors are predominant. Typically, losses proportional to the output current  $I_{OUT}$  are categorized as conduction losses, while losses proportional to the switching frequency  $f_{SW}$  are categorized as switching losses. From the above power loss equations, in low-power CDA designs where the output current is small, switching losses dominate over conduction losses. Therefore, it is crucial to reduce the switching frequency of the CDA. However, this reduction compromises the THD.

In contrast, when increasing the output power, conduction losses start to rise and eventually surpass switching losses. In this scenario, increasing the switching frequency becomes desirable to achieve better THD. As the output current increases, so does the power delivered to the load. Consequently, the efficiency of the CDA can remain high since the turn-on resistance and other parasitic resistances from the input voltage to the output voltage path are relatively small.

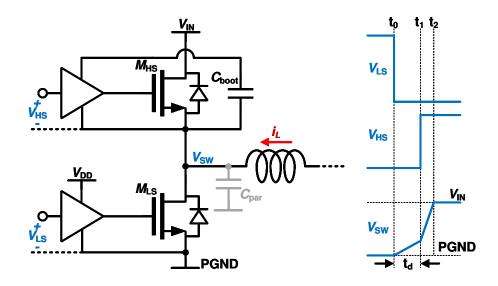

It is worth noting that in the full-bridge topology, the inductor current flows both into and out of one side of the half-bridge. When the inductor current flows out of the half-bridge, the switching mechanism is hard-switching, where the switching node voltage  $V_{SW}$  is solely pulled up by turning on the high-side power transistor, consuming power. However, when the inductor current flows into the half-bridge, as shown in Figure 2.3, it contributes partially to the rise of  $V_{SW}$  during the dead-time ( $t_d$ ) by charging the parasitic output capacitance ( $C_{par}$ ) in the switching node before the high-side transistor turns on. During this period (from  $t_0$  to  $t_1$  in the figure), no power is consumed. Once the dead-time is over, the rest of the rise in  $V_{SW}$  (from  $t_1$  to  $t_2$ ) is contributed by turning on the high-side power transistor, which is faster but also consumes power.

Figure 2.3: Timing diagram of switching waveform when indcutor current flows into a half-bridge (Ma et al. (2015))

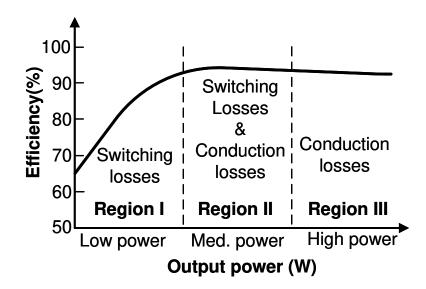

Figure 2.4: Efficiency diagram of a CDA versus output power, illustrating the dominant loss in the output power region.

Figure 2.4 illustrates the efficiency diagram of a CDA versus the output power, highlighting the dominant loss in different output power regions. Region I, II, and III represent low-power, medium-power, and high-power operation regions of the CDA, respectively. In Region I, switching losses dominate; in Region II, both switching and conduction losses are significant; and in Region III,

conduction losses surpass switching losses. Depending on the specific application and the CDA's operating power region, one can target specific losses for optimization to achieve better efficiency in that region.

#### 2.2 Class-D Amplifier Architectures and Modulation Techniques

This literature review examines the principal components and control strategies of CDA systems, focusing on architectural structures, modulation techniques, and feedback topologies. By analyzing the main developments and methodologies in CDA design, this review provides a thorough overview of the current approaches in the field, evaluating the benefits and drawbacks of different architectural choices and control mechanisms.

First, existing CDA structures will be reviewed with an emphasis on architectural configurations. In this examination, three primary categories—fully analog CDA, fully digital CDA, and mixed-signal CDA architectures—will be considered, each presenting distinct advantages and design challenges in achieving optimal efficiency, linearity, and fidelity in class-D amplification.

Second, modulation techniques employed in class-D amplifier design will be reviewed, as these play a critical role in shaping the amplifier's performance and suitability for various applications. Depending on the specific requirements—such as efficiency, linearity, or spectral characteristics—different modulation strategies are applied. This review will examine the most commonly used techniques in the literature, highlighting their distinct features, advantages, and limitations. By comparing methods such as PWM, SHEPWM, and Delta-Sigma Modulation, this section will provide insights into the modulation choices available for optimizing CDA performance across a range of operational contexts.

#### 2.2.1 Class-D Amplifier Structures

Most CDAs are for audio applications, therefore numerous publications are available for audio CDAs. Very few published CDAs are for industrial or automotive applications. But generally, their structures can be classed into three different categories. In the first category are CDAs that are designed using analog circuits. Choi et al. (2012); Kovačević, Pešić-Brdjanin, and Galić (2018);

W.-C. Wang and Lin (2016) reported such CDAs and their input signals are analog signals (Figure 2.5). Input analog signals are summed with feedback signals and create error signals which will be compared with ramped signals. The PWM signals are generated at the output of comparators and non-overlapping PWM signals are derived which will drive the power MOSFETs. Such an analog CDA's modulation technique uses an analog modulator.

Figure 2.5: Analog class-D amplifier block diagram (W.-C. Wang and Lin (2016))

The second category is CDAs that are designed in digital circuits. Chang and Wu (2016); Kuo and Liou (2019); McKenzie and Ng (2018); M. Wang, Jiang, Song, and Brooks (2010) reported such CDAs and they use a digital PWM modulator (Figure 2.6). The input signals are available in digital audio form. The digital CDA uses an ADC in its feedback loop because CDA's output is an analog signal while the input is a digital signal. The operation principle is the same as an analog CDA where the input signal is summed with the feedback signal and the error signal is accumulated by the loop filter. The error signal from the loop filter is quantized using a digital comparator and the generated PWM signal drives the power stage.

Figure 2.6: Digital class-D amplifier block diagram (McKenzie and Ng (2018))

The third category is CDAs that are designed in mixed-signal circuits. Berkhout and Dooper (2010); Guanziroli, Bassoli, Crippa, Devecchi, and Nicollini (2012) reported such CDAs. Their input signals are in digital form and use a digital PWM modulator (Figure 2.7). However, the feedback path and loop filter are implemented in analog circuits and analog PWM is generated to drive the power stage.

Figure 2.7: Digital class-D amplifier block diagram (Berkhout and Dooper (2010))

Depending on the applications and requirements of the system, the CDA's structures discussed above have their advantages and disadvantages. Analog CDA is used in applications where input signals are available as analog signals, and its feedback system does not require complex ADC.

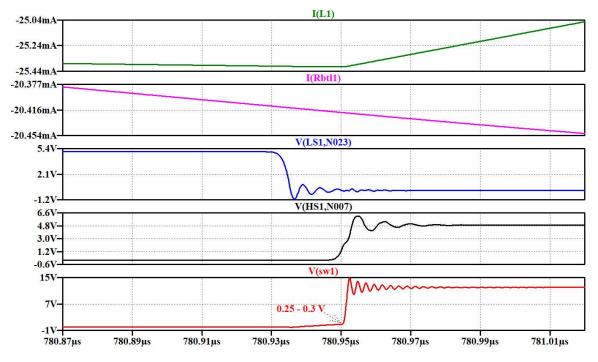

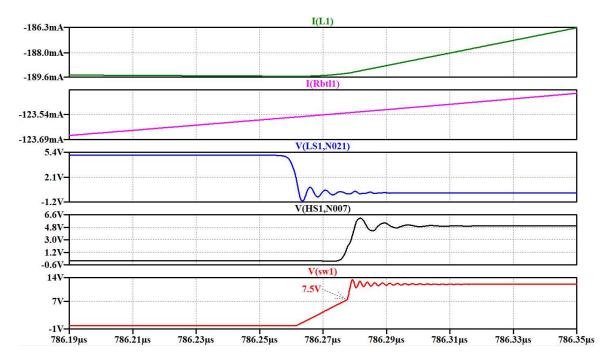

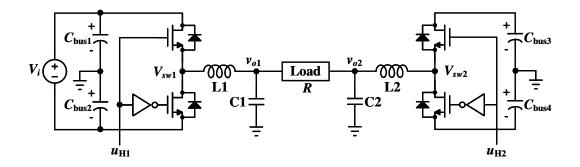

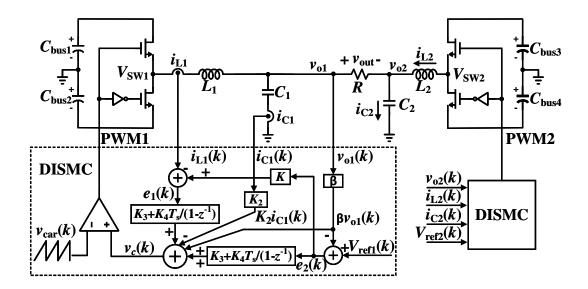

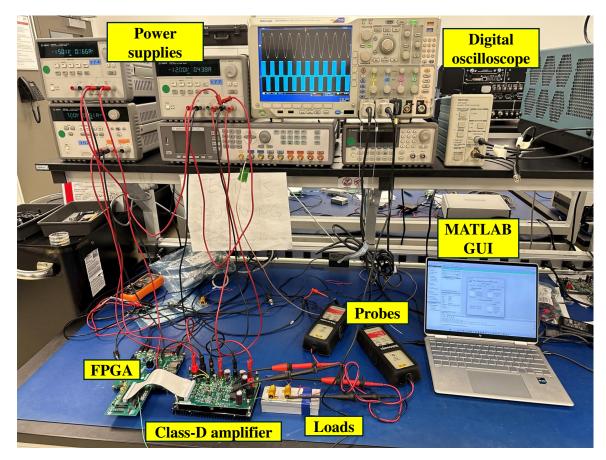

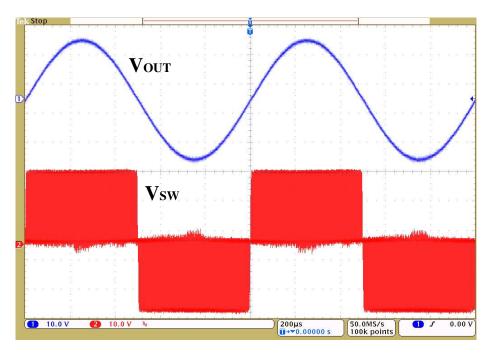

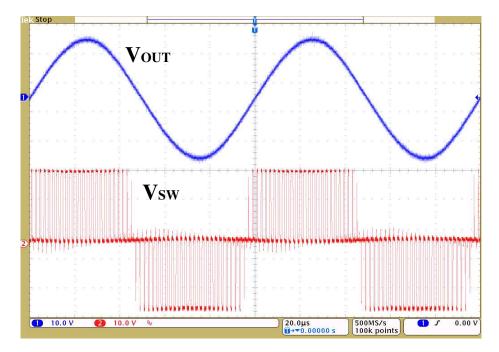

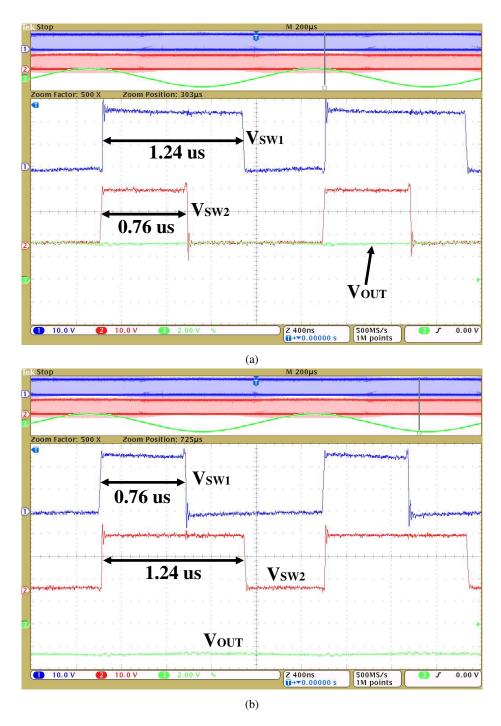

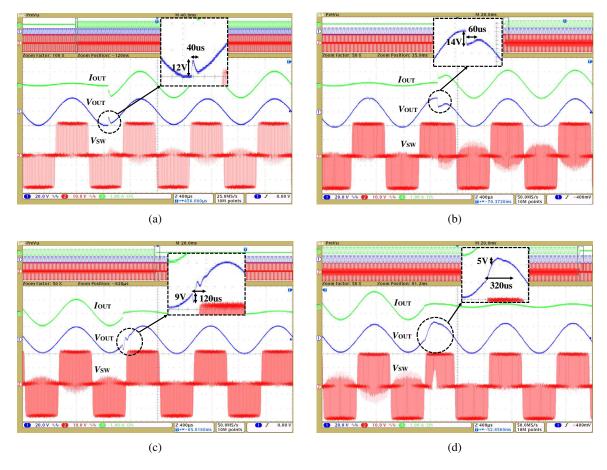

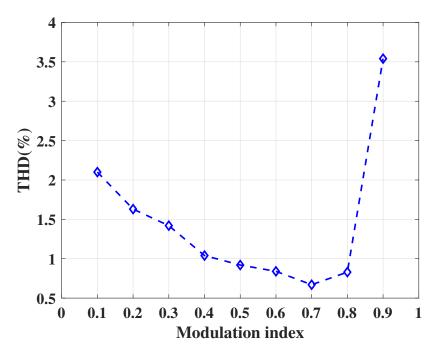

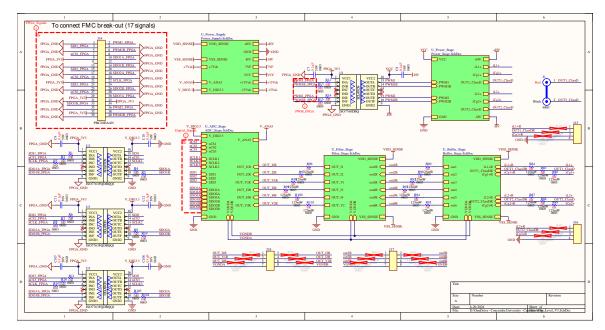

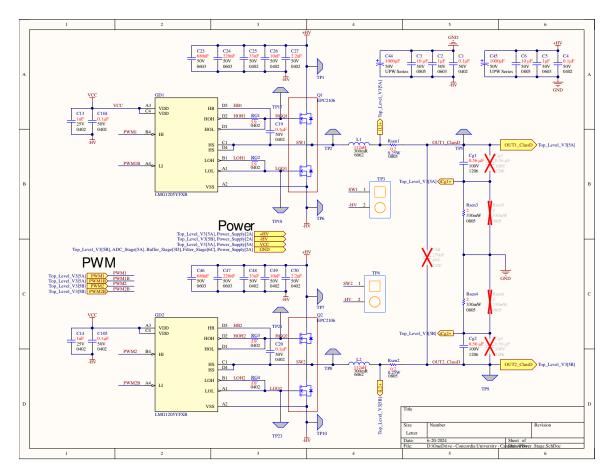

Most of the input signals are available in digital form due to the increasing demand for digital electronics and it is easy to store audios in digital format. So, most of the CDA's front-end uses a digital modulator for easy processing of the input signals. Pure digital CDAs, however, still require ADC in its feedback. The mixed-signal CDAs combine the advantages of both analog and digital CDAs, use digital PWM modulator in front-end, and analog circuits are used for the backend. Such a structure gets rid of ADC and complex signal processing in the feedback loop. Most of the existing power stage topologies use full-bridge differential output. This power topology generates two or three-level PWM at the output depending on the modulation technique it uses. As discussed before, multilevel inverters that use more than three-level topologies have advantages over fewer-level topologies in reducing the THD and filter size. There are very few publications in CDAs that use multilevel topologies whereas most of the multilevel topologies are reported in DC-DC converters. This is because the duty cycle of CDA's PWM is always changing but DC-DC converters' PWM duty cycle is fixed. This makes the signal processing of multilevel CDA even more complex. Høyerby, Jakobsen, Midtgaard, and Hansen (2016) reports state-of-the-art multilevel CDA. Its general structure is the same as an analog CDA, where it uses a fourth-order analog loop filter to get rid of an ADC in the feedback loop.