#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# A Visual Performance Debugger for Concordia Parallel Programming Environment

Jing Zhang

**A Thesis**

in

**The Department**

of

**Computer Science**

Presented in Partial Fulfillment of the Requirements For the Degree of Master of Computer Science Concordia University Montreal, Quebec, Canada

March 2000

© Jing Zhang, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa CN K1A 0N4 Canada

Your file Vatre référence

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-47859-9

## **ABSTRACT**

## A Visual Performance Debugger for Concordia Parallel Programming Environment

#### Jing Zhang

This thesis presents the design and implementation of the Visual Performance Debugger for the Concordia Parallel Programming Environment (CPPE), a simulator for parallel programming environment. The purpose of this visual performance debugger is to provide a rich set of correctness and performance debugging tools for CPPE to make CPPE a real flexible and efficient system for parallel program development.

The challenge in the design of the performance debugger is the comprehensive recognition of the interaction of performance affecting factors and their impact on parallel applications running on a parallel system. We intend to provide the user with the tool set that can gather performance data regarding different performance affecting factors at different level of details to facilitate the performance analysis and fine-tuning. To this end, a comprehensive survey of performance affecting factors for parallel programming is conducted. Based on this recognition, we have designed and implemented a rich set of correctness and performance debugging tools that can significantly help the user in their parallel programming exercise for correctness debugging and performance tune. We provide a visual environment for this performance debugger in order to achieve these goals more easily.

## Acknowledgements

I would like to express my cordial gratitude to Dr. Lixin Tao at the end of my study.

Since I have been working in companies throughout most of my studying terms, Dr. Tao has given me the most support in my study and the maximum flexibility in the schedule.

Almost all my consultation and discussion with Dr. Tao happened after working hours or during the weekends. This thesis will not be completed without Dr. Tao's compassionate support, advice and encouragement.

My thanks also go to the CPPE team: Dr. Lixin Tao, the team leader: Hassan Hosseini and Ai Kong (CPCC), Hoang Uyen Trang Nguyen and Thien Bui (CPSS), which provided the good basis for the contributions of this thesis.

I am grateful to the professors and administrative stuffs in the department of Computer Science, especially Dr. Butler Gregry, who gave the lectures in Software Engineering and Software Design Methodology, Dr. H.F. Li, who taught an excellent course in Computer Architecture and offered me the guidance in graduate study, Mr. Stan, who gave me so much help in the use of computer system and system programming, and Ms. Halina Monkiewicz, her friendliness and administrative support have made my student's life much easier and pleasant.

I also have a very supportive family that backs me up. My wife supported me with her unconditional love, sharing and inspiration throughout my study. I am also grateful to my parents for their encouragement and help.

# **Table of Contents**

| List of F      | igures x                                            |

|----------------|-----------------------------------------------------|

| List of T      | Tables xii                                          |

| 1 Intro        | duction1                                            |

| 1.1 <b>M</b> o | otivations2                                         |

| 1.2 Ge         | neral Structure of CPPE4                            |

| 1.3 Co         | ntributions of This Thesis                          |

| 1.3.1          | Correctness Debugging Tools6                        |

| 1.3.2          | Performance Debugging Tools6                        |

| 1.3.3          | Graphical User Interface                            |

| 1.4 The        | esis Outline                                        |

| 2 Litera       | ature Survey9                                       |

| 2.1 Sou        | rces of Performance Degradation                     |

| 2.1.1          | Performance Affecting Factors in Communication      |

| 2.1.2          | Performance Affecting Factors in Parallel Computing |

| 2.1.3          | Parallel Algorithms and Performance                 |

| 2.1.4          | Summary                                             |

| 2.2 Para       | allel Computer Simulators and Performance Debugging |

| 2.2.1          | Direct Execution Simulation System                  |

| 2.2.2          | Direct Execution with Code Augmentation             |

| 2.2.3          | Functional Simulation System                        |

|    | 2.2.4   | CPSS Simulation Technique                          | . 28       |

|----|---------|----------------------------------------------------|------------|

|    | 2.3 G   | raphic User Interface                              | . 29       |

| 3  | The     | CPSS System Architecture and Debugging Environment | 31         |

|    | 3.1 De  | esign Objectives                                   | .31        |

|    | 3.2 CI  | PSS High-Level Design and Debugging Environment    | .33        |

|    | 3.2.1   | The General Structure of the CPSS                  | 33         |

|    | 3.2.2   | The Code Execution Module                          | 36         |

|    | 3.2.3   | The Network Module                                 | 38         |

| 2  | 3.3 Hi  | gh-Level Design of Debugging Tools                 | 39         |

|    | 3.3.1   | Correctness Debugging                              | 39         |

|    | 3.3.2   | Performance Debugging                              | 42         |

|    | 3.3.3   | Graphical User Interface                           | 45         |

| 4  | The I   | Design of the Debugging Monitor4                   | 16         |

| 4  | l.1 Co  | rrectness Debugging Tools                          | 46         |

|    | 4.1.1   | Setting and Clearing Source Breakpoints            | <b>47</b>  |

|    | 4.1.2   | Stepping Through a Process                         | 51         |

|    | 4.1.3   | Viewing Source Code and vCode                      | 54         |

|    | 4.1.4   | Tracing Variables5                                 | 56         |

|    | 4.1.5   | Examining Status of Process                        | <b>'</b> 6 |

|    | 4.1.6   | Examining Memory Contents                          | 9          |

| 4. | .2 Peri | formance Debugging Tools8                          | 0          |

|    | 4.2.1   | Setting Time Breakpoint: Alarm8                    | i          |

|    | 4.2.2   | Setting Network Architectures                      | 2          |

| 4.2.3     | Vary Processor Speed                          | 89  |

|-----------|-----------------------------------------------|-----|

| 4.2.4     | Program Mapping                               | 90  |

| 4.2.5     | Performance Statistics                        | 102 |

| 5 Graph   | hical User Interface                          | 111 |

| 5.1 Des   | sign Objectives                               | 111 |

| 5.2 App   | proaches to Realize the Design Objectives     | 112 |

| 5.2.1     | Unified CPPE Development Environment          | 112 |

| 5.2.2     | User Friendliness                             | 114 |

| 5.2.3     | Easy Configuration and Multi-Platform Support | 115 |

| 5.3 GUI   | I for UNIX Platform                           | 115 |

| 5.3.1     | Main Function                                 | 115 |

| 5.3.2     | Main Frame                                    | 117 |

| 5.3.3     | Configuration                                 | 119 |

| 5.3.4     | Data Structures                               | 119 |

| 5.4 GUI   | for Windows Platform                          | 122 |

| 5.4.1     | Main Frame                                    | 122 |

| 5.4.2     | Configuration                                 | 123 |

| 5.4.3     | Data Structures                               | 124 |

| 6 Examp   | ole Applications of Debugging Tools           | 128 |

| 6.1 Virtu | ual-to-physical Mapping And Performance       | 131 |

| 6.2 Topo  | ology And Performance                         | 132 |

| 6.3 Com   | munication Parameters And Performance         | 132 |

| 7 Conclus | sion and Future Work                          | 124 |

| Appen  | dix A CPPE User's Manual For UNIX Platform137    | , |

|--------|--------------------------------------------------|---|

| 1 (    | Configuration137                                 | , |

| 1.1    | Environment Files                                | , |

| 1.2    | Environment Variables                            |   |

| 1.3    | Start The CPPE Program                           | ı |

| 1.4    | Configuration Setup139                           |   |

| 2 C    | CPPE Functionality140                            |   |

| 2.1    | Create Application Program Source File           |   |

| 2.2    | Compile Application Program Source File          |   |

| 2.3    | Execution And Debugging                          |   |

| 2.4    | Network Architectures and Mapping                |   |

| 2.5    | Program Performance Statistics                   |   |

| Append | dix B CPPE User's Manual For Windows Platform158 |   |

| l C    | onfiguration158                                  |   |

| 1.1    | Configuration File                               |   |

| 1.2    | Environment variables                            |   |

| 1.3    | Configuration Setup                              |   |

| 2 C    | PPE Functionality160                             |   |

| 2.1    | Create Application Program Source File           |   |

| 2.2    | Compile Application Program Source File          |   |

| 2.3    | Execution And Debugging                          |   |

| 2.4    | Network Architecture And Mapping                 |   |

| 2.5    | Program Performance Statistics                   |   |

| Bibliography <sub>1</sub> | 17  | 7 |

|---------------------------|-----|---|

|                           | . / | • |

# **List of Figures**

| Figure 1: General structure of the CPPE                                             | 5   |

|-------------------------------------------------------------------------------------|-----|

| Figure 2: Model of the multicomputer architecture                                   | ç   |

| Figure 3 : CPSS structure and operations.                                           | 35  |

| Figure 4: Data structure of Breakpoint table in C                                   | 50  |

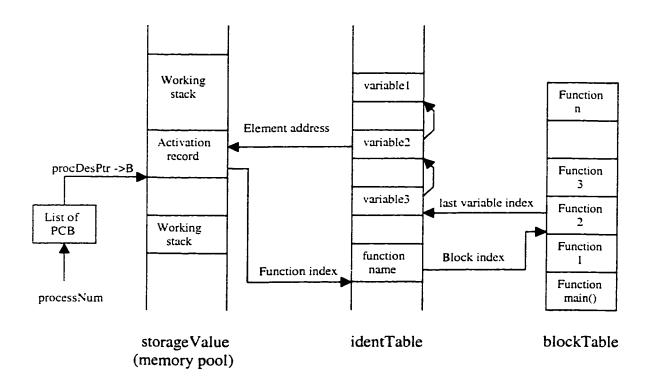

| Figure 5: Memory management of process stacks                                       | 58  |

| Figure 6 : Data structures of memory pool in C                                      | 60  |

| Figure 7: The process of retrieving the value of a variable                         | 61  |

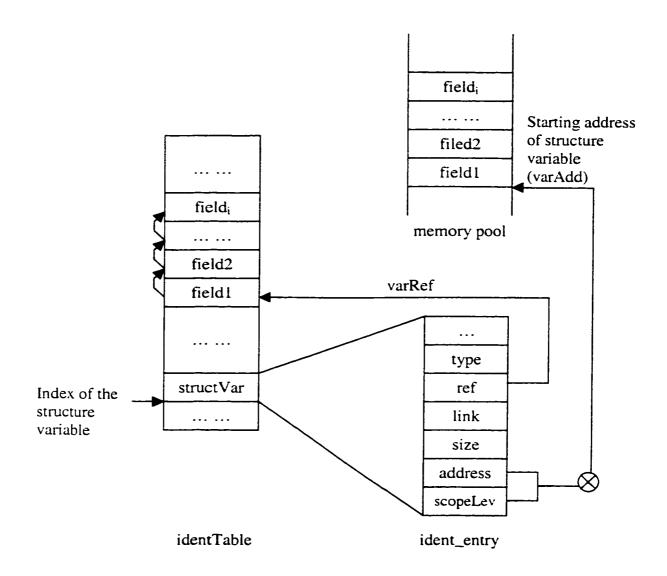

| Figure 8: The process of retrieving the value of a structure variable               | 66  |

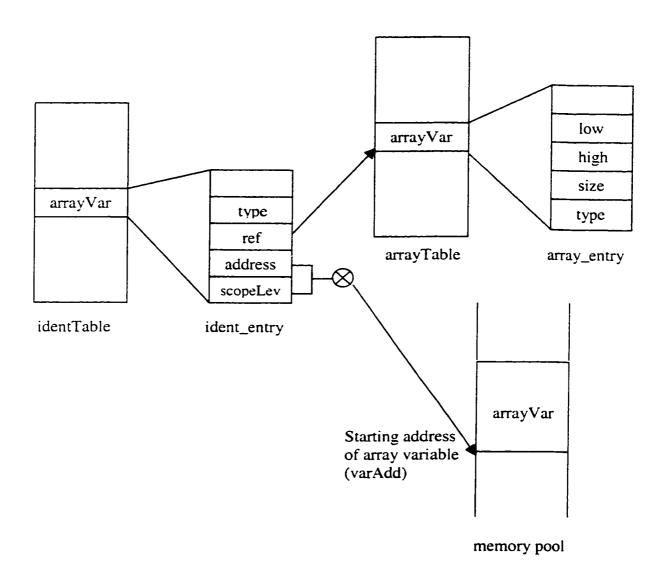

| Figure 9: The process of retrieving the value of an array variable                  | 69  |

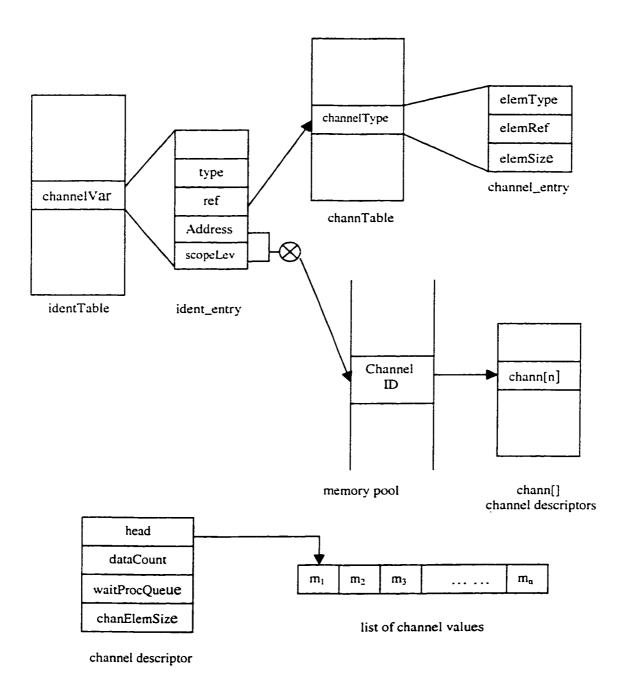

| Figure 10: Data structure of Channel variable in C                                  | 72  |

| Figure 11: Retrieve messages from a Channel variable                                | 73  |

| Figure 12: Data structures in C for Trace function                                  | 75  |

| Figure 13: Data structure of Process Control Block in C                             | 78  |

| Figure 14: Mapping of a process to a virtual processor then to a physical processor | 92  |

| Figure 15: Algorithm for Identity mapping in C                                      | 94  |

| Figure 16: Algorithm for Random mapping in C                                        | 95  |

| Figure 17: Algorithm for Default mapping in C                                       | 96  |

| Figure 18: Algorithm for Ring-to-Line Mapping in C                                  | 97  |

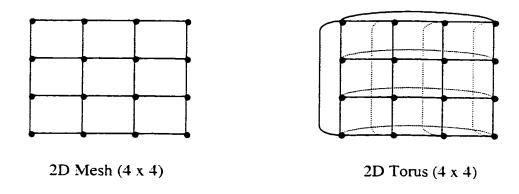

| Figure 19: Mesh and Torus topology                                                  | .98 |

| Figure 20 :Algorithm for Torus-to-Mesh mapping in C                                 | 100 |

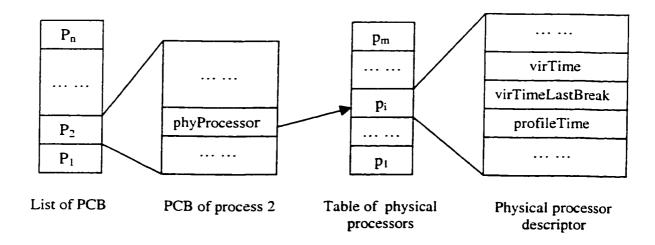

| Figure 21: Data structure related to Physical Processor Descriptor                  | 107 |

| Figure 22 : Performance profile of a parallel program       | 108 |

|-------------------------------------------------------------|-----|

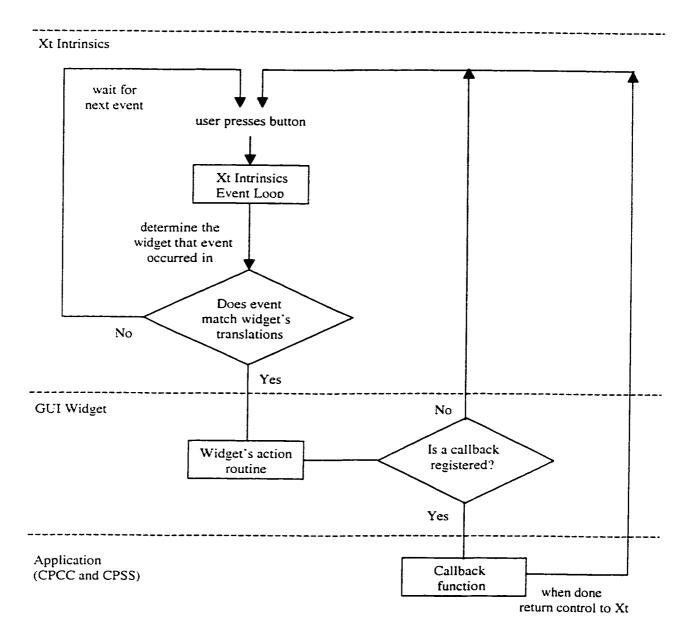

| Figure 23: Event handling of a MOTIF application            | 117 |

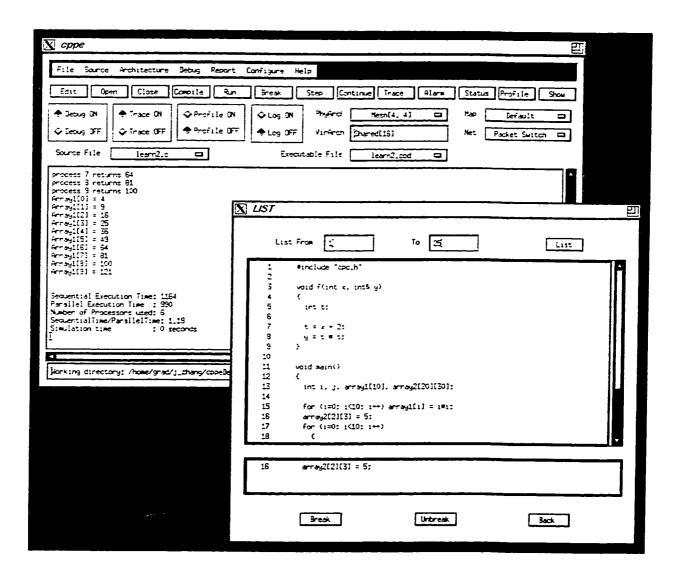

| Figure 24 : CPPE GUI on UNIX workstation platform           | 118 |

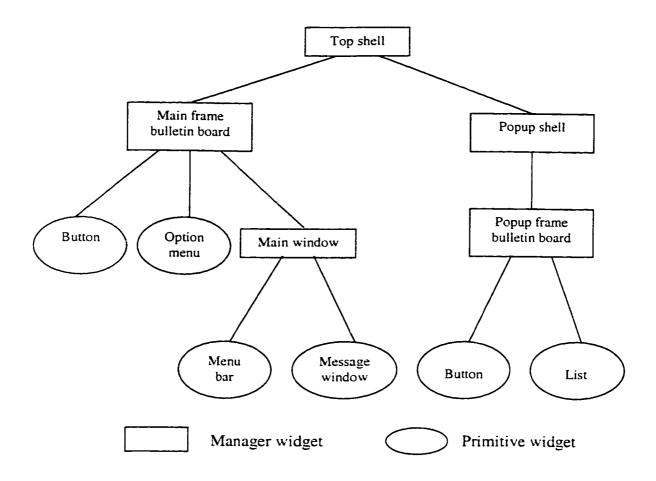

| Figure 25 : Application widget hierarchy in CPPE GUI        | 120 |

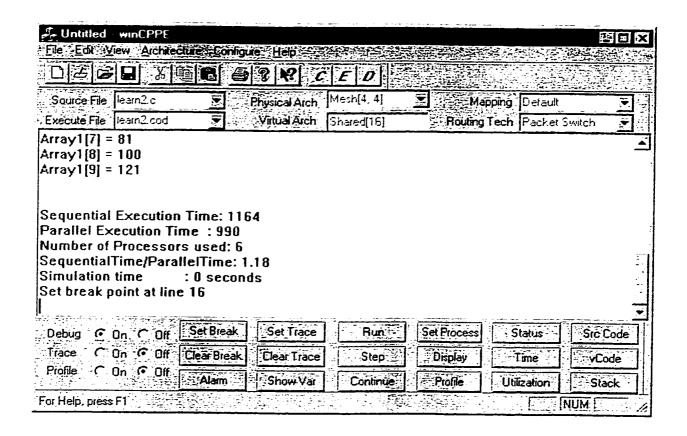

| Figure 26: Main frame of CPPE on Windows platform           | 123 |

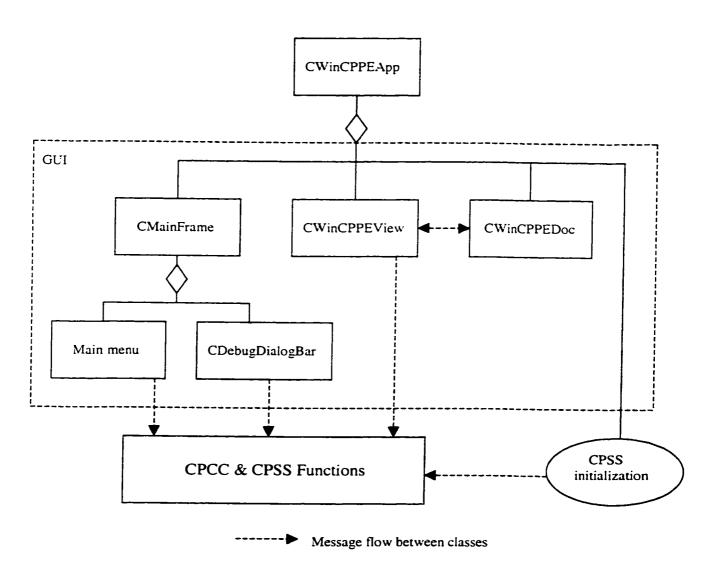

| Figure 27: Major classes and their relationship in CPPE GUI | 124 |

| Figure 28: Matrix multiplication on an 8x8 torus            | 131 |

## **List of Tables**

| Table 1: vCode's that have variable reference                                | 76  |

|------------------------------------------------------------------------------|-----|

| Table 2: Process-to-physical-processor mapping                               | 93  |

| Table 3 : Ring-to-Line mapping                                               | 97  |

| Table 4: Performance statistics for virtual-to-physical-architecture mapping | 131 |

| Table 5: Performance statistics for topologies                               | 132 |

| Table 6: Performance statistics for packet size                              | 133 |

## Chapter 1

## Introduction

Computing power has always been an issue in research and industry. Despite the tremendous growth of processor speed over years, there is still a wide range of important computational problems in science and engineering that require much greater computer speed. Parallel programming has shown its potential to meet the demands for high computing power. However, parallel programming is difficult and error-prone, not only because parallel processes are difficult to trace and debug, but also due to the fact that the performance of parallel program is influenced by many hardware and software factors, such as algorithm design, system architecture, routing technique, and networking speed. To make matter even complicated, some algorithms may be more suitable for a particular architecture than others. The performance of a particular parallel program often has to be evaluated through trial and error.

In order to evaluate and improve the performance of parallel application effectively, simulation techniques have been studied in the hope to provide the necessary environment and software tools. CPPE (Concordia Parallel Programming Environment) is one of the simulated parallel systems being studied and developed in our group, aimed to provide users with flexible and efficient software tools for developing parallel programs, evaluating and optimizing performance of parallel applications.

As part of the CPPE project, the objective of the research associated with this thesis is to study the performance affecting factors in parallel computing, design and implement a visual performance debugger for CPPE. The visual performance debugger will provide a rich set of correctness and performance debugging tools to make CPPE a flexible and efficient system for parallel program development.

In this chapter, we first discuss the motivations and objectives of this research.

Then we present the contributions of this thesis. At the end we give a thesis outline.

#### 1.1 Motivations

Parallel computers can be classified into two categories: shared-memory multi-processor and message-passing multicomputer. With the advancement of hardware technology, high-speed networks and efficient routing techniques have made message-passing multicomputer the developing trend for parallel computing, because it is more scalable due to the distributed nature of local memories.

On a parallel computer architecture, there are many factors that can affect the performance of a parallel program. Users often have to write a parallel program and run it on an actual parallel system to verify the correctness and observe the performance of the program through trial and error. However, The trial and error approach on a real machine is inefficient because of the following reasons:

Real parallel computers are expensive resources that are available to only a restricted number of users. Testing and debugging tools supported on real parallel computer are currently very limited.

- 2. Real parallel computers are non-deterministic in nature in terms of the network performance and the probability of error. The probability for some bugs to occur may be one over ten thousand. It is vary hard to test, debug and tune a parallel program on a real parallel computer machine.

- 3. The performance of a parallel program is affected by system size and system topology. The performance of an application may be good on small-sized systems but degrade tremendously as system size increases. An algorithm may be efficient on a particular system topology but perform badly on another topology. To achieve high performance, the designer should study the scalability and communication complexity of parallel algorithms. However, topologies and sizes supported by a real multi-computer are restricted within small ranges. This limitation does not allow for studies of scalability and communication complexity of parallel algorithms.

Because of the limitations of the real machines, many studies of parallel algorithms have been conducted on an analytical basis – the analytical modeling. Performance aspects of a parallel program under specific conditions may be estimated using mathematical formulation. However, this approach is suitable only for simple applications and small computer systems. Parallel computer systems and their applications are sufficiently complex to make analytical modeling very difficult and inaccurate.

Because of the difficulty of using real parallel computers and analytical modeling, the simulation approach has been studied by several research groups. CPPE is one of the projects of that kind. CPPE provides a parallel system simulator called CPSS (Concordia

Parallel System Simulator) which runs sequential software on a uniprocessor to emulate program execution on a real parallel computer. Its objective is to provide a parallel programming environment that allows users to study impacts of system and software factors on program performance and locate performance bottlenecks in the program.

The simulator CPSS is supposed to accurately mimic the behavior of the real parallel machine and yield correct program outputs as if the program has been executed on the real machine. In addition, it should provide users with adequate and useful simulator tools and models for evaluating parallel architectures and the performance of parallel programs on these architectures. Users should be able to use these tools to observe the effects of all the affecting factors on their application so as to detect system bottleneck and thus optimize performance of the applications, which is referred to as performance debugging.

The objective of this thesis is to give a comprehensive review of performance affecting factors of parallel computing, design and implement a visual performance debugger for CPPE, which allows users to study the impacts of system architectures and software algorithms on the program performance.

#### 1.2 General Structure of CPPE

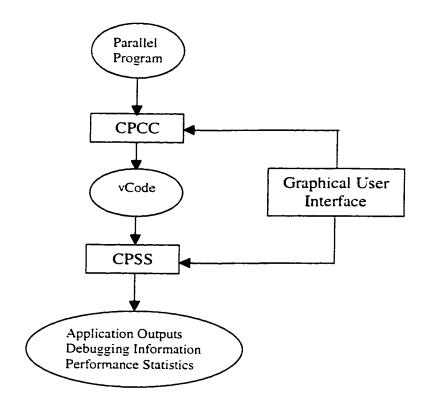

This thesis is part of the research project Concordia Parallel Programming Environment (CPPE). CPPE consists of two major modules (Figure 1):

Concordia Parallel C Compiler (CPCC): The CPCC accepts parallel programs written

in the CPC (Concordia Parallel C) language and generates virtual machine code

(vCode) which will be the input to the CPSS.

Concordia Parallel System Simulator (CPSS): The CPSS reads in the intermediate

code produced by the CPCC, simulates execution of the application, yields programs

outputs.

Figure 1: General structure of the CPPE

As a major component of the CPPE, CPSS in turn is made of three main components:

1. Code Execution Module (CEM): The CEM is the processing element of a simulated parallel system. It executes the vCode produced by the CPCC.

- 2. Network Module: The roll of the network module is to allocate network resources to messages, route and deliver messages, and detect deadlock in the network.

- 3. Performance Debugger: The performance debugger provides a set of software tools to facilitate program testing and debugging.

The scope of this thesis is to design and implement the Performance Debugger of CPSS and provide a graphic user interface (GUI) for the CPPE. Together we call the software Visual Performance Debugger.

#### 1.3 Contributions of This Thesis

The visual performance debugger includes three major components: correctness debugging tools, performance debugging tools and graphical user interface.

## 1.3.1 Correctness Debugging Tools

The design concepts of correctness debugging tools are borrowed from sequential programming environment [27]. We concentrate on the most useful debugging tools existing in other sequential debuggers, plus the specific debugging tools necessary for parallel programming environment.

## 1.3.2 Performance Debugging Tools

The performance debugging tools are meant to provide the performance data and statistics for parallel execution at various levels of details in order to help the user locate performance bottleneck and fine-tune the program. The design of performance debugging

tools is based on the comprehensive study of performance affecting factors of parallel computing. This study enables us to define the most informative and useful performance data and statistics so that we can design corresponding tools to provide such information.

One of the distinguish characteristics of our performance debugger is the ability to support virtual architecture programming and run-time mapping. The user writes an application using the virtual architecture most natural to the application. At run-time the virtual architecture will be mapped to the available physical architecture based on the user-specified virtual-to-physical mapping pattern. For programs with multiple parallel phases, the user can specify a mapping pattern at the beginning of each parallel phase.

### 1.3.3 Graphical User Interface

The visual performance debugger has a graphic user interface (GUI) which provides a user-friendly developing environment, making the use of debugging tools and the analysis of execution results easy. We provide graphic user interface for versions running on both UNIX and Windows platforms.

The efficiency of our visual performance debugger is tested by actually running some parallel application programs and then analyzing the performance data and statistics gathered from the performance debugging tools. Our simulation results show a good match with the theoretical analysis of the performance under different software and network environment.

## 1.4 Thesis Outline

In chapter 2, we give a comprehensive review of the performance affecting

factors of parallel computing in both parallel computing and network communication.

Chapter 3 gives an overview of CPSS and debugging environment in CPSS, identifies and rationalizes the design of debugging tools in CPSS. Chapter 4 details the design of correctness and performance debugging tools. Chapter 5 describes the design and data structures of graphic user interface. Chapter 6 are some actual parallel program execution and performance statistics using the performance debugging tools built in this thesis.

Chapter 7 provides a summary of the thesis and suggestions for future work. Appendix A provides a user manual of CPPE for UNIX platform. Appendix B provides a user manual of CPPE for Windows platform

## Chapter 2

## **Literature Survey**

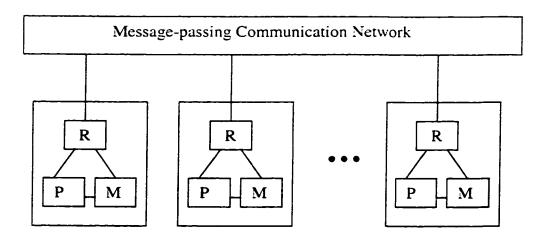

The general structure of a multicomputer system can be illustrated in Figure 2. Each processor has its own local memory and processing unit so that it can compute in a self-sufficient manner, using the data stored in its own local memory. Each processor also has a function unit called router so that every processor can send and receive data from any other processor, using the message-passing communication network. The advantage of multicomputer structure over the multiprocessor include better utilization of memory access locality and support of scalable parallel systems.

Figure 2: Model of the multicomputer architecture

However, the advantage of multicomputer does not come without cost. The cost is the data communication between different processors. There is another type of cost

concerning the use of the parallel computer system. From a parallel program designer's perspective, parallel computer system makes the parallel programs more difficult to develop, debug and fine-tune the performance. Therefore, a set of user-friendly debugging tools are indispensable in a parallel development system.

CPSS is a simulator of parallel development system which is intended to provide accurate simulation of both computation and communication activities, at the same time, with a flexible and user-friendly environment for correctness and performance debugging of parallel program development. In order to identify and design the debugging tools which are helpful to the users, we should first understand the computation and communication behavior in a parallel system and identify the performance affecting factors in the computation and communication process.

In this chapter, we first present a literature review on performance affecting factors of parallel applications in the perspectives of both parallel computing and communication. Then we present a review of existing code execution simulation techniques and their debugging functionality.

## 2.1 Sources of Performance Degradation

In order to design effective performance debugging tools for monitoring program performance, first we need to find out the major practical sources of performance degradation of parallel programs when running on real multiprocessors or multicomputers. Some performance affecting factors are typical for multiprocessors, some are typical for multicomputers, while some factors exist for both multiprocessors and multicomputers. The performance of parallel programs are affected by the

combination of software and hardware characteristics. Therefore, without effective performance monitoring tools, it would be hard to predict the final performance output.

#### 2.1.1 Performance Affecting Factors in Communication

In a multicomputer, each processor has its own private physical memory for storing and retrieving data during computation. Each processor also has one or more direct connections to other processors, through which data can be transmitted. If processors have no direct connection, they will communicate through intermediate processors that forward the data. The overall pattern of the direct connections between processors is called the multicomputer topology.

#### **Topology and Performance**

There is a wide variety of different types of communication topologies that can be used in parallel systems. The goal of these topologies is to try to reduce the cost and complexity of the network, while rapid communication between processors is achieved. Ideally, the communication cost will be reduced to minimum if there is a direct connection between each pair of processors. However, it is generally not possible in a large multicomputer system to provide a connection between every pair of processors, because this would need n<sup>2</sup> number of connections for n processors. This is not only too expensive, but also practically unachievable for a large multicomputer system. Also, there is a trade-off between cost and performance. In order to maintain a reasonable cost/performance rate and allow the system to be easily scaled up to a large number of processors, different topologies have been developed for multicomputers.

There are two important parameters that characterize each topology: the connectivity, which is the number of direct connections per processor, and the diameter, which is the maximum number of intermediate connections required for distant processors to communicate. The connectivity of a topology is an important affecting factor of network cost, while the diameter is an important affecting factor in the performance of the network. Simpler topologies usually have lower connectivity and therefore a higher diameter. The more complex topologies usually have higher connectivity and therefore a lower diameter. The fact is, we can not make a simple association between performance and topology. The performance is usually affected by a combination of topology and other factors such as parallel algorithm [21][22], message routing technique [15], network speed, data and program mapping [24], and operating system [25]. This fact justifies the existence of different topologies and the requirement for efficient performance monitoring tools.

The multicomputer topology is determined by its underlying interconnection network. CPSS is able to simulate all the widely used network topologies including line, ring, mesh, torus, hypercube and full-connected [23]. Through the performance debugger, user can specify different topologies before simulation without recompile of the simulator software and the user application program. This provides a flexible performance debugging environment.

#### **Communication Delay**

The overhead caused by communication delay is typical in multicomputers where the processors interact with each other through message-passing communication. In a

multicomputer, each processor has a separate local memory module for storing its data and program code. In order for all the processors to work together on a single computational problem they must communicate and exchange data during execution.

Processor communication is accomplished by message-passing via processor-to-processor communication link. The basic unit of communication from a programmer's point of view is a *message*, which consists of many bits of data. There are time delays by each message transmission because of the following reasons [26]:

- Transmission time: The communication link has a certain maximum bandwidth. The transmission time is significant compared with the processor speed. In addition to the actual physical transmission of the data bits, the communication module also needs to perform other functions to ensure that data is sent and received correctly. If error does occur, the message may need to be retransmitted.

- Processing time: The communication module needs to perform some computation for every message. The computation includes error detection using the checksum, routing decision based on the source and destination processor IDs.

- Waiting time: The waiting time results from the delay due to congestion in the communication network. Some algorithm may incur considerable amount of message passing, causing heavy network traffic so that messages build up and are delayed.

The actual cost of message transmission can also be affected by the network topology and communication parameters such as packet size, flit size, number of virtual channels per link, and buffer size of the virtual channel [13][14][35][36]. Significant

efforts have been made in both network design and program algorithm design. The ultimate goal is to minimizing the frequency of communication and the distance traveled by each message, and to minimize the communication cost under specific network architecture. However, again because of the complexity of parallel programming, it is hard to accomplish the goal without efficient performance monitoring tools.

The performance debugger developed for CPPE enables user to configure network architecture by redefining the communication parameters and costs without recompile of the simulator software and application programs. Performance statistics enables user to easily obtain the program performance under different network architectures.

## 2.1.2 Performance Affecting Factors in Parallel Computing

#### Memory Contention And synchronization Delay

Memory contention is typically a problem when there is shared memory such as in multiprocessors. Processor execution is delayed while waiting to gain access to the shared memory that is currently being used by another processor. When global variables are shared by a large number of processors involved in a parallel computing, memory contention can cause significant performance degradation.

When parallel processes synchronize, one processor may be forced to wait until certain condition is satisfied. So some processes may be idle for a considerable amount of time that causes performance bottlenecks and a reduction of overall speedup.

Because of the memory contention and synchronization delay, the overall performance of parallel computing could be affected to a variety of extents. Users need to

obtain the overall performance data and statistics in order to fine-tune the parallel algorithms.

#### **Excessive Sequential Execution and Process Creation Cost**

In any parallel program, there are always portions that are purely sequential code. Certain types of centralized operations, such as initializations, are executed sequentially in one processor before any parallel processes are created. In some algorithm, the sequential code may significantly limit the overall speedup that can be achieved from parallel execution.

The creation of parallel processes requires a certain amount of execution time. If the created processes are relatively short in duration, the process creation overhead may not be compensated by the savings of time due to parallelism. That means, parallel program may not necessarily speed up the execution in some algorithms.

Both scenarios hide the efficiency of parallel computing. In order to realize the actual gain from a certain pattern of parallel computing, we need to provide the performance data for any fragment of program execution in addition to the overall performance monitoring. Typically user may want to obtain speedup data for a pure parallel computing fragment without the counting of cost for sequential computing fragment and parallel process creation.

#### Load Imbalance

In some parallel programs, computing tasks are generated dynamically in an

unpredictable manner and must be assigned to processors as they are generated. The result is the possibility that some processors may be idle while others have more computing load than they can handle.

Load imbalance is most likely caused by the difference between the optimal computing architecture for a particular algorithm and the available physical parallel architecture. In order to evaluate the efficiency of a particular parallel algorithm on different physical architectures, we need to provide the user with the ability to map a virtual architecture which is optimal to the parallel algorithm to different physical architectures and study the performance under these virtual-to-physical mapping styles.

#### 2.1.3 Parallel Algorithms and Performance

There has been a considerable amount of research in the field of parallel algorithm design for a wide range of practical problems [28, 29, 30]. The most common parallel algorithms include data parallelism, synchronous iteration, replicated workers and pipeline computation. For parallel application programmers, such research help them to fully utilize the enormous computing potential of parallel computers. For us, it helps us to be aware of the different parallel algorithms and their pros and cons for different network architectures, so we can design meaningful test cases to evaluate our system design and demonstrate the usage of our performance debugging tools. By comparing the actual performance output gathered from the performance debugger with the anticipated performance based on the analysis of parallel algorithms and network architecture, we can not only evaluate the efficiency of the performance debugging tools, but also evaluate the correctness and efficiency of the CPSS network simulation system.

## 2.1.4 Summary

In this section, we summarized the major performance affecting factors in parallel programming. There is no simple formula to calculate the relative weight of each factor contributing to the overall performance, because the performance of parallel programs are affected by a combination of many software and hardware characteristics of the multiprocessors or multicomputers. Effective performance monitoring tools are required for performance debugging.

# 2.2 Parallel Computer Simulators and Performance Debugging

Several simulation systems for parallel computers have been developed [1][2][3][4][5]. Existing simulation techniques can be classified into three categories: direct execution, direct execution with code augmentation and functional simulation. In this session, we provide a review on these three types of simulation systems concerning the relationship between the simulation mechanism and their debugging functionality.

## 2.2.1 Direct Execution Simulation System

In direct execution simulation systems, a parallel program is first compiled into object code which is in the assembly language of the host computer. During compile, the compiler identifies two kinds of instructions for the purpose of simulation: local instructions and non-local instructions. An instruction is local if it has effects only on the

local processor, such as accessing variables residing in the local memory. Non-local instructions such as sending messages to a remote processor, in contrast, impact another part of the system such as a remote processor. In the process of simulation, local instructions will be executed directly by host processes and timed with the host's machine clock, while non-local instructions will be simulated via a procedure call which interprets the instruction at the functional level.

Direct execution technique is generally faster compared with the functional simulation technique, because local instructions are executed directly instead of being interpreted. However, it suffers from a major drawback: difficult debugging in terms of feasibility and accuracy.

In terms of feasibility, local instructions are directly executed by the host and the simulating engine does not have much control on the execution of local instructions. Thus it is very difficult to establish the connection between user application code and the low-level simulation activities. Such connection is essential for in-session debugging and fine-tuning an application. (In-session debugging refers to the debugging interaction between users and the program during execution of the program. Examples of in-session debugging are stepping through the program, setting breakpoint, and variable tracing after breakpoints).

In terms of accuracy, direct execution suffers an even more drawback of low accuracy because of the following reasons:

Because the simulation is timed with the host's clock, which is usually the

workstation clock with coarse granularity. Therefore, the timing is not accurate

because execution time of an instruction is often truncated to the nearest milliseconds.

Within a millisecond, the target parallel computer may have executed thousands of instructions or sent hundreds of messages.

With direct execution technique, monitoring code is often needed because the

difficulty of in-session debugging. Such code fragments would not be executed on the

target machine. Because there is no way to distinguish monitoring code from the

application code, the direct execution technique also times the monitoring code and

this will affect the overall execution time, making the simulation even less accurate.

Because of the difficulty of debugging, debugging tools provided by directexecution simulators are very limited and based primarily on monitoring code added to

the application and the simulation engine. In general, direct-execution simulator is not

suitable to accurately simulate both computation and communication activities of a target

parallel computer and to provide a user-friendly debugging environment.

An example simulator using direct execution technique is the CARE simulator [6][7] which simulates the execution of LISP code.

## 2.2.2 Direct Execution with Code Augmentation

This approach enhances the pure direct execution technique by adding cycle counts of local instructions to the object code during the compilation phase. The cycle counts of an instruction is the time the target system would take to execute that instruction. Cycle counts of object code will be accumulated during simulation as if the code were being executed on the target parallel computer. The simulation of local instructions is no longer

timed with the host's clock but accumulated using cycle counts added to the object code.

This results in a more accurate simulation than the pure direct execution technique.

Like the pure direct execution technique, code-augmented direct execution is generally faster than functional simulation since local instructions are executed directly rather than being interpreted. On the other hand, code-augmented direct execution offers more accuracy to simulation results than pure direct execution.

However, the problem of difficult debugging still exists. In fact, correctness and performance debugging in direct-execution simulators (both pure and code-augmented) relies heavily on the instrumented software technique due to the difficulty of in-session debugging. In the instrumented software approach, additional code is inserted into the simulation engine and the application to monitor the simulation. Adding monitoring code to the simulation engine does not cause any side-effect except that the added code may slow down the simulation. However, adding monitoring code to cycle-counted code (i.e. local instruction blocks) can be problematic. A simple addition will change the behavior of the simulation since the monitoring code is also included in the cycle counting. Conditional compilation flags or macros can be used to exclude the cost of the added monitoring code [2]. However, even with conditional compilation flags or macros, the addition may change the behavior of the application. This is because the additional code may affect the surrounding code indirectly. For example, if the additional code uses several registers, the surrounding code may spill more registers than the previous version (which contains no monitor code). This would increase the cost and thus could change the behavior of the system. The more debugging or statistics traces are required, the more perturbed the simulation can be.

Example simulators using direct execution with code augmentation technique are Ptoteus [2], Tango [3][8], EPPP [4][9], and PARSE [5].

#### **Proteus**

Proteus [2] is developed at MIT in 1991, using code augmentation to count the cycles required by the target machine to execute local instructions. The application program is first compiled into the host's assembly language. A code-augmenting program will then add cycle counts to local instructions of the object code. The compiled code is first divided into basic blocks of local instructions. A basic block is the smallest block of code delimited by a non-local instruction or an instruction where the execution can branch (e.g. a jump, a function call). Each instruction of a basic block is then matched with a cycle count by looking up a table. The cycle counts of all the instructions in that basic block are then summed and an instruction updating a global cycle counter is added at the end of the block. The cost of each basic block is thus a fixed number and determined at compile time.

Proteus' debugging capability depends heavily on the use of sequential dbx tools. The user is also allowed to add monitoring code into the simulation engine and the application. During program execution, monitoring code produces data and event traces, and logs the traces into an output file. When the program execution is completed, a graph generator is used to interpret the trace file data and present the results of the simulation.

Although the Proteus simulator is fast, it suffers from several drawbacks regarding its debugging functionality:

- Although the simulation results are improved compared with pure direct execution

because of the use of cycle counts, the timing results may still not be accurate because

the cost of each block is determined at compile time and is a fixed number. In reality,

the cost of an instruction depends on other run-time factors such as operands (or

cache hits if the target machine is a shared-memory architecture).

- The simulator can simulate accurately only a limited set of architectures whose instruction set is similar to that of the host. If the instruction set of the target machine is quite different from that of the host, the assignment of a cycle count to a local assembly instruction is no longer accurate.

- The simulator is not flexible from the user's point of view. When the architecture is changed, the engine parameters must be modified. The engine then needs to be recompiled and linked with the user application. This is not convenient, for example, for experimenting with different network topologies or program mapping. The experiment would require to run the same program on different architectures of varied sizes. The simulator must be modified, re-compiled and linked with the application code every time the topology or system size is changed.

- Debugging capability relies mainly on software instrumentation. In-session debugging facility is very limited and depends on sequential *dbx* tools.

#### Tango

Tango simulator was built at Stanford University in 1990 [3][8]. Tango and Proteus are quite similar, however, Tango simulates only shared-memory architectures. It was

implemented for studying shared-memory behaviors, shared-memory synchronization and concurrency abstractions and for architectural evaluation [3].

Like Proteus, Tango may produce inaccurate simulation results due to fixed costs of local instruction blocks calculated at compile time. Tango does not support any insession debugging tools. Debugging and statistics data are provided using the instrumented software approach. Many kinds of trace file are generated. System events are recorded in trace files. Program outputs are logged in an output file. There are also a process summary file and an event trace file. This is not a user-friendly debugging environment for parallel applications. Debugging tools are not adequately provided for code development or performance fine-tuning.

#### **EPPP Project**

The EPPP (Environment for Portable Parallel Programming) simulator [4][9] is in fact an extended version of Proteus. In this simulator, the augmentation phase is enhanced to accurately simulate a particular target architecture whose instruction set differs from that of the host. An application program will first be compiled and optimized as it would be on the target system. The intermediate code just produced will then be augmented with cycle counts. A second pass on the augmented intermediate code will generate assembly code for execution on the host.

The above enhancement requires the compiler to be modified specifically for each different target architecture. This is a major task calling for much time and effort.

Therefore, the target architectures of the EPPP simulator have been so far limited to only

very few systems [4]. Like Tango, no in-session debugging tools are available in the EPPP.

#### **PARSE**

Unlike Proteus or Tango which uses a separate program to augment the compiled code, PARSE [5] has code augmentation implemented directly in the compilation phase. The GNU C/C++ compiler was modified to augment parallel code when its basic block profiling flag is enabled.

This simulator is aimed at analyzing communication architectures and communication performance of parallel applications. Thus a high level of accuracy of code execution simulation is not of special interest to the simulator. For example, PARSE assumes that each instruction takes one clock cycle to execute and that memory accesses do not take additional cycles.

Concerning the debugging facilities, no tools are provided for correctness debugging of parallel programs. Performance debugging is available to analyze communication performance. However it is not user-friendly. The user specifies the monitoring of various events performed within the communication network through a configuration file. The simulator will generate a trace file containing a time sorted list of all requested events. Detailed communication statistics can then be determined by examining these traces using data analysis tools.

## Summary

Direct execution (both pure and with code augmentation) is fast but associated with two severe drawbacks:

- In-session debugging is very hard due to the nature of direct execution. Debugging and statistics rely heavily on the instrumented software approach. The accuracy of simulation results then depends on how much the monitoring code perturbs the system and application behaviors. The more traces/data required, the less accurate simulation results would be. This approach is thus not suitable for code developing or fine-tuning application performance.

- Simulation results are not accurate if the host's instruction set differs from that of the target. The inaccuracy also results from the fact that cycle counts of local blocks are accumulated at compile-time. In reality, execution time of an instruction depends on many run-time factors.

## 2.2.3 Functional Simulation System

In functional simulation systems, a parallel program is first translated into intermediate code of a virtual parallel machine (target machine). The set of intermediate code instructions is definable and can be different from the host's assembly language. Each instruction of the intermediate code is usually expressed as a host macro/procedure whose size depends on the complexity of the instruction and the desired level of simulation accuracy. At run time, the intermediate code instructions are interpreted at the functional level as if they were being executed on the target machine.

Functional simulation generally takes more simulation time than the direct execution approach. However, it is a very attractive technique for performance debugging due to its high accuracy and flexibility:

- In terms of accuracy, it is very accurate due to the interpretation of intermediate instructions as if they were executed on the target machine. Monitoring code can be added to the simulating code without affecting simulation outcomes, because monitoring code can be distinguished from the application code and its execution time will not be accumulated into the total execution time. Cycle counts of intermediate instructions are accumulated at actual run-time (whereas direct execution simulators compute execution time of local blocks in advance at compile time).

- In terms of flexibility, code interpretation permits the simulator to have complete control over program execution. This allows to establish the connection between user program code and the intermediate instructions. The user can thus set breakpoints, examine traced variables, or step through the program in a particular process. The user can also view status of processes, processors and messages at any point during program execution. Monitoring code can be added to the simulating code without affecting simulation outcomes, because execution time of monitoring code is not accumulated.

A typical simulator using functional simulation technique is Multi-Pascal simulator [1][10].

#### Multi-Pascal Simulator

This simulator simulates both shared-memory and message-passing architectures. User programs are first compiled into intermediate code. Each intermediate code instruction is associated with a fixed cost which is the cycle count of that instruction on the target machine. At run time, intermediate code instructions are interpreted and their cycle counts are accumulated to give the total execution cost at the end of execution.

Multi-Pascal simulator provides a rich set of debugging tools, which benefits from the advantages of functional simulation technique. However, it still has some limitations which prevent it from being an ideal performance debugger.

- In Multi-Pascal simulator, cycle counts of intermediate instructions are hard-coded into the interpreting code of the instructions and not well-defined, therefore simulation results may not be accurate.

- The simulator does not support the concept of virtual architecture. The user needs to declare the physical architecture and specify the process-to-processor mapping in their application programs. There is no run-time mapping. Moreover, the user is forced to organize the program to match the available physical architecture which may not be a natural structure to the application. This limitation makes study of program performance under different architectures inconvenient.

- The simulator assumes an underlying packet-switching network. There is no dynamic network simulation. Communication overheads of message passing are calculated

based on one communication model. Again this makes the study of program performance under different network conditions inconvenient.

The simulator does not support file I/O. It is only intended for small applications.

## 2.2.4 CPSS Simulation Technique

CPSS uses the functional simulation technique to simulate the execution of a parallel program on a multicomputer or multiprocessor system. Application programs are written in CPC language which enhances the C language with parallel features to express process creation/termination and message-passing. Similar to Multi-Pascal simulator, the CPSS also provides a rich set of debugging tools. In addition, it has some improvement over the Multi-Pascal simulator which makes it an ideal performance debugger for studying parallel programming:

- Every intermediate code instruction is associated with a configurable cost which can be adjusted to match a specific target machine, which makes the simulation outcomes more accurate.

- Most of the computation and communication parameters are configurable. Values of the configurable parameters can be changed within the same simulation session as often as needed.

- CPSS supports virtual architecture programming and run-time process-to-processor

mapping to improve programmability of message-passing applications. The user can

write an application using the virtual architecture most natural to the application. At

run-time the virtual architecture will be mapped to the available physical architecture. Moreover, the same source program can be mapped to different physical architectures without any changes to the source code. This makes the performance study under different physical architectures easy.

- CPSS contains a dynamic network simulator. It can simulate both packet switching and wormhole routing. CPSS can offer very accurate message routing and communication performance statistics for both routing models. Since wormhole routing technique is very popular on modern parallel computer systems, such as Intel Paragon [31], nCUBE6400 [32], and Ametek2010 [33], a parallel computer simulator that supports wormhole-routed networks has the practical value for performance study of parallel applications.

- CPPE has a graphical user interface that eases the use of the rich set of debugging tools and the analysis of debugging information and program output.

## 2.3 Graphic User Interface

Graphic user interface has been designed for some of the parallel simulators to help the programmers to visualize and analyze program outputs and problematic performance statistics. METRICS [16] and Procsimity [17] are implemented using Tcl/Tk, which is an interpreted language. Applications witten in Tcl/Tk require an interpreter at run time and thus are slower. ParaGraph [18] is implemented using the X Window System. It is quite fast since it does not use any toolkit, but it does not take advantage of the latest developments in graphical user interface technology. U/IMX [19] is a toolkit for

developing graphic user interface based on X Window System. It has powerful capability to create GUI for existing application programs. However it is less flexible to integrate the graphic interface with a complex application program, such as CPSS. Java Abstract Window Toolkit [20] is another GUI development toolkit. Applications implemented in Java are portable across many platforms without modification. Again, Java is an interpreted language and thus applications written in Java are slow.

Our GUI for CPPE is developed using Motif toolkit [11] for the UNIX workstation platform and MS-MFC (microsoft foundation classes) [12] for the Windows PC platform. Motif is a set of guidelines that specifies how a user interface for graphical computers should look and feel. The term of Motif describes how an application appears on the screen (the look) and how the user interacts with it (the feel). Motif toolkit is developed by the Open Software Foundation (OSF) [34]. Compared with X window programming. Motif toolkit provides a higher level interface functionality and thus enables user to produce completely Motif-compliant applications in a relatively short amount of time. Compared with other X window toolkit, such as U/IMX, Motif toolkit provides the lower level programming functionality and thus provides the high flexibility to integrate application programs with the user interface. MS-MFC has become the most popular tools in writing Windows program. It provides a comprehensive set of classes for developing GUI objects and applications. Since it was written by the company that writes the Windows operating system, MFC is continuously updated to incorporate the latest changes to Windows itself.

## Chapter 3

# The CPSS System Architecture and Debugging Environment

In this chapter, we first describe our objectives for the design of CPPE performance debugger. Then we present an overview of the system architecture and high level design of CPSS, which provides the background information and creates the foundation for identifying the debugging environment and designing the performance debugger in CPSS. Then we present the high level design of the CPSS performance debugger.

## 3.1 Design Objectives

The final goal of the debugging system is to enable the user to interact with the underlying simulation system in order to better understand the behavior of parallel programs for correctness and performance tuning. To realize this goal, the most important objectives in the design of the debugging system are as follows.

Correctness debugging: We should provide end-users with convenient debugging tools and useful information in order to debug and test applications, as in the case of sequential debugging environment. After all, this is the main advantage of using a simulator rather than a real parallel computer machine which provides a very limited set of debugging tools. Compared with conventional sequential debugging tools, the

challenge for designing the parallel debugging tools is that the tools should be able to trace individual parallel process during execution.

- Performance debugging: We should provide end-users with a set of performance monitoring tools which will provide computation and communication statistics of parallel application execution to facilitate the study of parallel architectures, network characteristics, parallel algorithms, program mapping and their effect on performance. Global statistics of an application (such as total execution time, speedup, total computation time and total communication time) allow the user to tune the applications to a desired performance. Run-time data or trace (such as process creation/termination information, message sending/receiving information) could be very useful in studying a particular aspect of the application, which can not be captured by global statistics.

- User friendliness: It should be easy to learn and use the simulator debugging tools.

The functionality of each tool should be well defined and informative so that users can easily apply these tools in their programming exercises.

To meet the objectives of performance debugging, the following criteria should be followed in the designing of performance debugging tools:

• Informative: The information provided by the debugging tools should well address the functionality of corresponding performance affecting factors of parallel processing in the areas of both computing and network communication. From the performance statistics and run-time data, user should be able to well understand the

behavior of the parallel programs in terms of the relationship between performance and the changing of performance affecting factors.

- Accurate: The performance results obtained from the debugging tools should reflect accurately the behaviors of the parallel computer system. The results should be based on behaviors of realistic computation and communication models, yet making a good trade-off between simulation accuracy and simulation time.

- Repeatable: The results obtained from the debugging tools should be repeatable.

Repeatability is essential to provide a stable debugging environment that is not available on a real parallel computer machine. Real parallel computers are nondeterministic in nature and, rarely provides any form of repeatability. Some bugs may not occur frequently enough for observation. Repeatability does not mean that the simulator can produce only one of the many possible executions of a nondeterministic application: the simulator should also be able to simulate multiple executions of an application when it is required to mimic the nondeterministic nature of real parallel computer systems and of parallel applications.

## 3.2 CPSS High-Level Design and Debugging Environment

This section gives an overview of CPSS high-level design, which provides the foundation for the design of debugging system in CPPE regarding the necessity and feasibility.

#### 3.2.1 The General Structure of the CPSS

The CPSS (Concordia Parallel System Simulator) is an integrated part of the CPPE (Concordia Parallel Programming Environment). CPPE consists of two components: the CPCC and the CPSS.

The core of the CPCC (Concordia Parallel C Compiler) is a compiler. After reading a parallel program written in CPC (Concordia Parallel C) language, the CPCC builds a complete abstract syntax tree to perform syntax and semantics analysis, and produces object code for a generic virtual machine. Such object code is called *vCode* in CPPE. The vCode instruction set is defined based on an analysis of common operations of parallel computer systems. To produce vCode, the compilation process makes use of the virtual architecture and does not call for a physical architecture. The advantage of this design is that the CPC parallel program does not need to be re-compiled every time the underlying target architecture is changed.

The vCode produced by the CPCC will be input to the CPSS. Other inputs to the CPSS are parameters and commands from the user. For example, the user can specify the physical topology on which the program will run and the virtual-to-physical topology mapping. The CPSS then executes the vCode, using the parameters and commands entered by the user. The outputs from the CPSS are the application outputs, performance statistics, and debugging information.

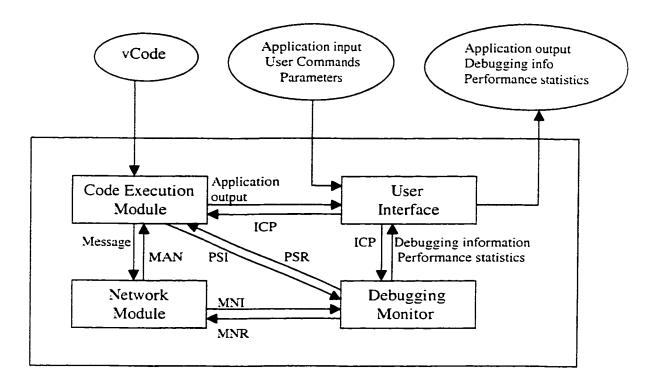

The CPSS consists of two major components: the code execution module and the network module. The code execution module models the processing elements of the parallel computer system: it executes the parallel code specified by the parallel program. The network module is to manage the inter-processor communication via message

passing. There are two other utility modules interacting with the code execution module and network module in CPSS: they are the debugging monitor and the user interface.

The interactions between the components in CPSS are illustrated in Figure 3.

MAN: Message Arrival Notification MNR: Message/Network Request MNI: Message/Network Information

ICP: Input/Commands/Parameters

PSR: Process/Processor Status Request

PSI: Process/Processor Status Information

Figure 3 : CPSS structure and operations

The debugging monitor and interface not only closely interact with the two major components of CPSS during execution, their implementation is also dependent on the high-level design of these two components. In order to understand the design of the debugging monitor, we will first have an overview of the high-level design of code execution module and the network module.

## 3.2.2 The Code Execution Module

The Code Execution Module (CEM) plays the role of processing element of a parallel computer system: it executes the parallel code specified by the parallel program. There are three key issues that influent the design of the debugging monitor: simulation at the functional level, sequential execution model and the way timing system is implemented. CPSS uses the functional simulation technique which uses sequential execution model to emulate the parallel execution and interprets the parallel object code instructions at the functional level. This technique offers the most accurate results among the existing simulation techniques. In addition, this technique provides a good basis for performance debugging:

• Functional simulation: CEM interprets the intermediate parallel code at the functional level as if they were executed on the target machine. Each instruction of the target machine is usually expressed as a host macro or procedure whose size depends on the complexity of the instruction and the desired level of simulation accuracy. This technique permits the simulator to have complete control over program execution. It allows to establish the connection between user program statements and intermediate instructions. Thus the user can set breakpoints, examine trace variables, or stepthrough the program fragment of a particular process. Monitor code can be added to the simulating code without affecting the execution outcomes, because the CEM is able to distinguish between application code and monitor code and the execution time for monitoring code is not accumulated.

- By using functional simulation technique, we can parameterize system measurements

(e.g. system clock cycle, execution time of object code instructions, network packet

size, link buffer size, network delay, message and packet startup overheads).

Performance statistics are based on these parameterized measurements.

- The sequential simulation is deterministic in nature. Therefore repetition of execution of a parallel program will always produce the same results and performance under the same system parameters. This provides a stable environment to study the performance of parallel programs at different levels of detail and from different perspectives.

- Timing system: CPSS does not use the machine clock for performance timing. There is a global clock for the simulated parallel computer system which is updated periodically by the CEM. Each process has a local clock that keeps track of the present time of this process. In the CPSS, parallelism is simulated by time slicing: each application process is given a quantum to run and processes are scheduled in a round-robin fashion. During each quantum, the job scheduler traverses the list of physical processors and schedules one process on a processor at a time for execution. The local clock of the scheduled process is updated after each instruction is executed. The user can define the cost to execute an instruction based on the complexity of the instruction. A process runs until its time quantum expires or it is put to sleep by some event. The job scheduler then schedules a process on the next processor for execution. When every processor has finished its quantum, the global clock is advanced to the

next quantum. By using this timing system, CPSS can provide accurate and repeatable performance statistics for performance debugging.

## 3.2.3 The Network Module

The Network Module is responsible for inter-process communication via message passing. It is under control of the network manager. The network manager allocates network resources to messages to be sent, routes messages and delivers them to destination processors, and detects and resolves deadlock, if any.

The following design issues of the network module is crucial for accurately simulating the communication behavior, yet providing feasibility for performance evaluation for parallel applications:

- By using the functional simulation technique and the same global clock mentioned in the CEM design, it can effectively simulate the network behavior and communication cost such as message startup overhead, routing overhead and congestion delay. New messages which are being initialized for routing are queued at a new message list. The waiting time at this list simulates message startup overheads. When the startup overhead time of a new message expires, the message will be removed from the list and appended to a list of active messages. In each quantum, all active packets that are not blocked are advanced by one link, and it simulates the movement of packets by advancing their ID numbers.

- Most of the network and communication parameters are well defined with appropriate data structures. User can configure most of the network parameters such as packet

size, flit size, routing scheme, link bandwidth, communication delay, network topologies and virtual-to-physical mapping without recompile of the simulator software and application programs, which provides a flexible performance debugging environment.

## 3.3 High-Level Design of Debugging Tools

Practical sources of performance degradation reviewed in Chapter 2 require the simulation system to provide the efficient and flexible debugging tools for parallel program development and performance fine-tune. The system architecture of CPSS provides a good debugging environment which is inherited from the functional simulation technique and the timing system employed in the design of the two major components (Code Execution Module and Network Module) in CPSS, as we reviewed in last section. We now identify the major debugging tools which will be implemented in CPSS and describe the high-level design of these debugging tools.

## 3.3.1 Correctness Debugging

Since parallel object code instructions are interpreted at the functional level, it is convenient to insert debugging code inside the interpretation code as much as we need to implement the necessary debugging functions. Unlike the case of direct simulation technique, the debugging code can be distinguished from the application code so that the amount of inserted debugging code does not affect the simulation results in terms of execution cost.

We identified and implemented the following functionality within CPSS for correctness debugging, with the design concepts borrowed from sequential programming environment:

- Set and clear instruction breakpoints: users can set breakpoints in the source program to automatically interrupt the program execution. Users can also clear breakpoints.

- Set and clear trace variables: users can set a trace flag on variables. Whenever the variable is referenced during execution, the program execution is suspended so that user can inspect the execution status. Users can also clear the trace flags.

- View the value of a variable: users can view the value of a variable in an active process when execution is suspended.

- Step through a process: users can suspend a program and then let the execution continue line by line or by a specified number of lines.

- Set a particular process to be the current process for debugging. The user may then use the above tools to debug the current process.

- View the program source code (written in the CPC language). Users can specify the range of the source code to be displayed.

- View the vCode corresponding to specified range of the source code.

- View the status of the processes. Information about each process includes

- the processor on which this process is run

- the process status (e.g., ready, running, blocked, etc.)

- the stack of the process

- the function that is currently executed by this process

- the line in the source code that is currently executed by this process.

The main data structures related to correctness debugging are:

- Source code breakpoint table: CPSS maintains a global break table that stores all

breakpoints set by user at run time. When executing in debugging mode, the code

execution engine checks the line number of an instruction in the global break table

before executing it.

- Trace variable table: CPSS maintains a global trace table that stores all traced variables set by user at run time. Since CEM references variables by their addresses in the memory pool, traced variables are stored in the trace table with their memory addresses. When a vCode references a variable, CEM will check whether the referenced variable is in the trace table.

- Source code and vCode table: Source code table stores the application source code.

and vCode table stores the compiled virtual machine code. CEM executes the vCode in the vCode table, with the index of the vCode table servers as the program count (PC).

- Source-to-vCode table: each source code is usually compiled into several vCode

instructions for execution. The source-to-vCode table src2codTable will associate the

source line number with the vCode line number so that we can trace the program

execution. The first vCode line number of each corresponding source code line will be stored in this table.

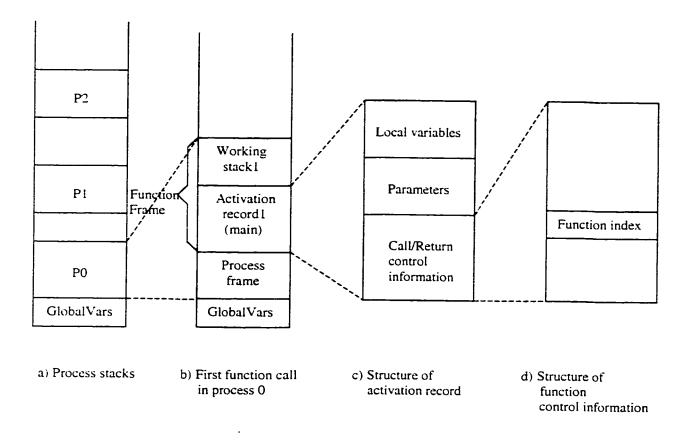

• Memory pool: Memory blocks will be allocated from the memory pool and distributed to running processes for program execution. Memory pools is implemented as a fixed-size array, with the index of the array serves as the memory address. Variables are accessed by their addresses in the memory pool.

## 3.3.2 Performance Debugging

Based on the review on the sources of performance degradation in Chapter 2, we not only need to provide the overall performance profile of a parallel program execution, but also to provide the functionality to study the performance of any portion of the parallel program. To study the communication overhead of parallel computing, we need to simulate a variety of network topologies and be able to easily configure the communication parameters. To study the optimal program mapping from virtual architecture to physical architecture, we need to provide the user with the ability to specify certain patterns of virtual-to-physical-architecture mapping.

We identified the following performance statistics for performance debugging and implemented corresponding functionality within CPSS to provide these information: