#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

|  | · |   |

|--|---|---|

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   | · |

|  | · |   |

|  |   |   |

|  |   |   |

# A LINE AND LOAD INDEPENDENT ZERO VOLTAGE SWITCHING DC/DC FULL BRIDGE CONVERTER TOPOLOGY

Wen Kang

A Thesis

In

The Department

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

December 2000

© Wen Kang, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our fale Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-59307-X

#### **ABSTRACT**

# A line and load independent zero voltage switching dc/dc full bridge converter topology

#### Wen Kang

Full bridge dc/dc converter topology is extensively applied in medium to high power conversion. In a power level up to 3 kW, the full bridge converter now employs MOSFET switches. High efficiency, high power density, high reliability and low EMI are some of the most desirable features in these applications, particularly for computer and telecom systems.

To achieve these features, soft switching techniques are normally employed. However, the conventional soft switching full bridge converter topologies would either lose the soft switching at some operating conditions, or become rather complex in design and implementation for a few kilo watts applications.

This thesis presents and analyzes an improved zero voltage switching dc/dc full bridge converter topology. The proposed topology employs asymmetrical auxiliary circuits that consist of only a few passive components. However, the advantage of the proposed topology is significant: it achieves soft switching independent of line and load conditions.

Detailed steady state and dynamic analyses are performed to understand the operating principle of the proposed topology and its performance. A dc blocking capacitor is essential to prevent the current sense transformer from saturation, and the study of this thesis shows that contrary to the conventional pulse width modulated full bridge converter, the peak current mode control can still be used along with the blocking capacitor in a phase shift full bridge converter. Design procedure for industrial application is presented. Experimental and simulation results of a prototype 500 W 350-400 Vdc to 55 Vdc converter operating at 100 kHz verify the analysis and design, and show an overall efficiency of greater than 97% at full load.

#### **ACKNOWLEDGMENT**

I would like to express my sincere gratitude to Dr. P. K. Jain for his encouragement, support and guidance during the course of this study.

I would also like to thank my colleagues at the P. D. Ziogas Power Electronics Lab at Concordia University, for their friendship, their always readiness to help, and for many valuable discussions we have shared. Special thanks to Nikhil Jain for his proof reading of this thesis.

Also acknowledged are the financial supports from Gouvernement du Quebec Ministere de l'Education and from Canada's Natural Science and Engineering Research Council (NSERC).

# **TABLE OF CONTENTS**

| List of Figures                                         | vi                  |

|---------------------------------------------------------|---------------------|

| List of Table                                           | x                   |

| List of Acronyms                                        | x                   |

| List of Principal Symbols                               | xi                  |

| Chapter 1 Introduction                                  |                     |

| 1.1 General Introduction                                | 1                   |

| 1.2 Review of Existing ZVS Full Bridge Topologies       | 2                   |

| 1.2.1 ZVS full bridge topologies with passive mechanism | 2                   |

| 1.2.2 ZVS full bridge topologies with active mechanism  | 5                   |

| 1.3 Objectives and Scope of the Study                   | 7                   |

| 1.4 Thesis Outline                                      | 7                   |

| Chapter 2 Proposed ZVS Converter Topology and the St    | eady State Analysis |

| 2.1 Introduction                                        | 9                   |

| 2.2 Circuit Description                                 | 9                   |

| 2.3 Steady State Analysis                               | 11                  |

| 2.3.1 Assumptions and some constants for the analysis   | 11                  |

| 2.3.2 Steady state analysis of each interval            | 15                  |

| 2.4 Simulation Results                                  | 22                  |

| 2.5 Experimental Results                                | 26                  |

| 2.6 Conclusions                                         | 29                  |

### Chapter 3 Dynamic Analysis

| 3.1 Introduction                                                                   | 30       |

|------------------------------------------------------------------------------------|----------|

| 3.2 Flux Imbalance Problems                                                        | 31       |

| 3.2.1 Use of current transformer                                                   | 31       |

| 3.2.2 DC voltage component in the output of the bridge legs                        | 31       |

| 3.3.3 Peak current mode control protects the power transformer but not the current | nt sense |

| transformer                                                                        | 32       |

| 3.3 Flux Balancing                                                                 | 33       |

| 3.3.1 Solution to the saturation problem of the current sense transformer          | 33       |

| 3.3.2 Analysis of the dc voltage component                                         | 35       |

| 3.3.3 Flux balancing by adding a series dc blocking capacitor                      | 37       |

| 3.4 Small Signal Model                                                             | 38       |

| 3.4.1 Modes of operation and the equivalent circuits                               | 38       |

| 3.4.2 State space equations                                                        | 40       |

| 3.4.3 Averaged state space equations                                               | 41       |

| 3.4.4 DC and AC models                                                             | 42       |

| 3.4.5 Small signal model                                                           | 43       |

| 3.5 Transfer function of the power circuit in the PCMC and loop compensation       | 43       |

| 3.5.1 PCMC verses VMC and ACMC                                                     | 43       |

| 3.5.2 Transfer function and control loops                                          | 45       |

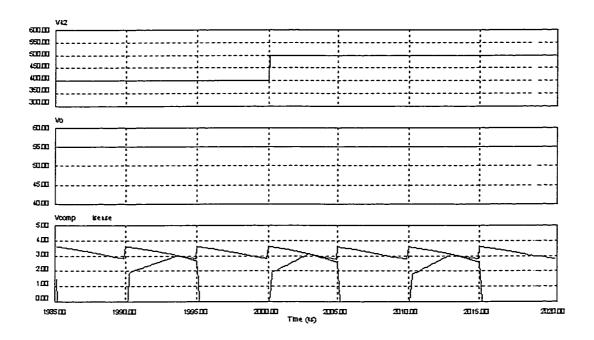

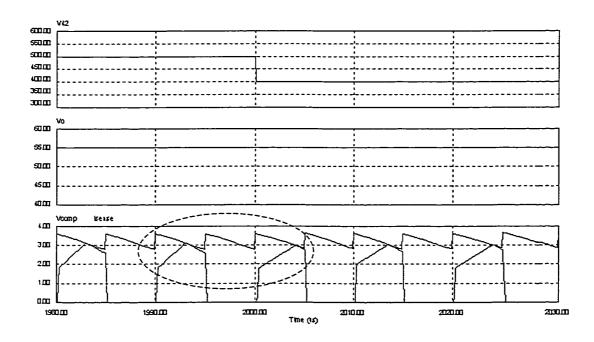

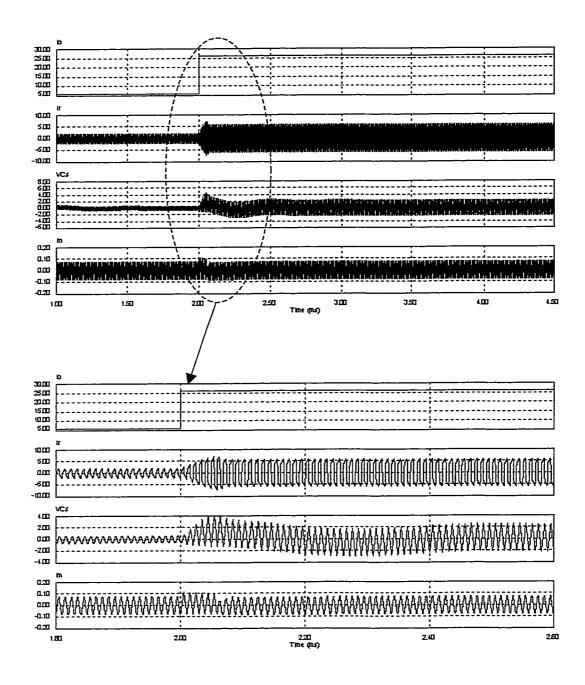

| 3.6 Simulation Results                                                             | 52       |

| 3.6.1 Flux balancing against asymmetrical gating pattern                           | 53       |

| 3.6.2 Other influences of the dc blocking capacitor                                | 56       |

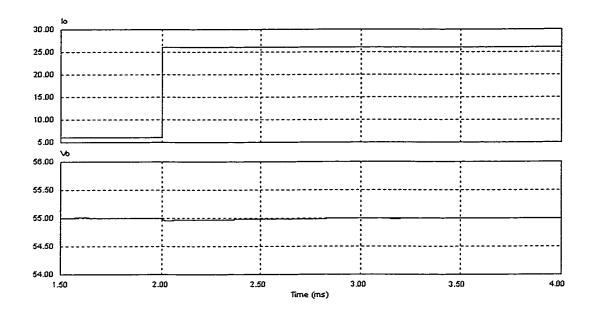

| 3.6.3 Step responses                                                                         | 59 |

|----------------------------------------------------------------------------------------------|----|

| 3.6.4 DC blocking series capacitor voltage under dynamic conditions                          | 69 |

| 3.7 Conclusions                                                                              | 66 |

| Chapter 4 Design Procedure                                                                   |    |

| 4.1 Introduction                                                                             | 67 |

| 4.2 Optimizing the design by employing asymmetrical auxiliary circuits                       | 68 |

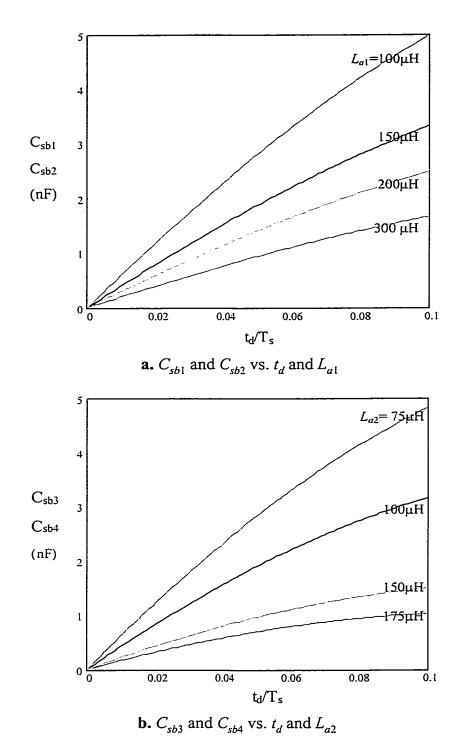

| 4.3 Design of the auxiliary circuits                                                         | 71 |

| 4.3.1 Assumptions                                                                            | 71 |

| 4.3.2 Selection of $L_{a1}$ , $L_{a2}$ , $C_{snb1}$ , $C_{snb2}$ , $C_{snb3}$ and $C_{snb4}$ | 71 |

| 4.3.3 Selection of $C_{a1}$ and $C_{a2}$                                                     | 73 |

| 4.3.4 Selection of $C_s$                                                                     | 74 |

| 4.4 A Design Example                                                                         | 74 |

| Chapter 5 Summary, Conclusions and Suggestions for Future Work                               |    |

| 5.1 Summary                                                                                  | 75 |

| 5.2 Conclusions.                                                                             | 76 |

| 5.3 Suggestions for future work                                                              | 78 |

| References                                                                                   | 79 |

# LIST OF FIGURES

| Fig.   | 1.1 | ZVS full bridge converter topologies using passive devices                             | 3   |

|--------|-----|----------------------------------------------------------------------------------------|-----|

| Fig.   | 1.2 | Soft switching full bridge converter IGBT topology using active auxiliary circuits     | 6   |

| Fig.   | 1.3 | ZVS full bridge converter MOSFET topology using active auxiliary circuits              | 6   |

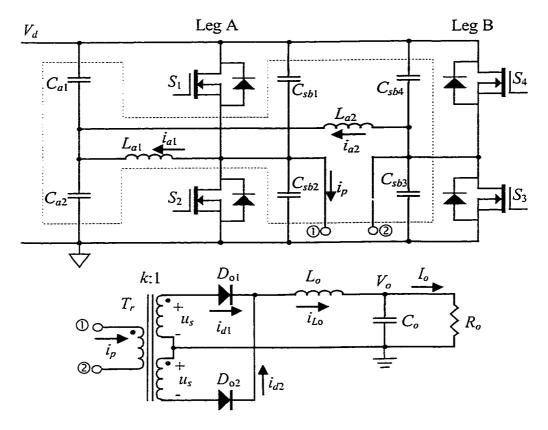

| Fig.   | 2.1 | The proposed ZVS full bridge converter topology                                        | .10 |

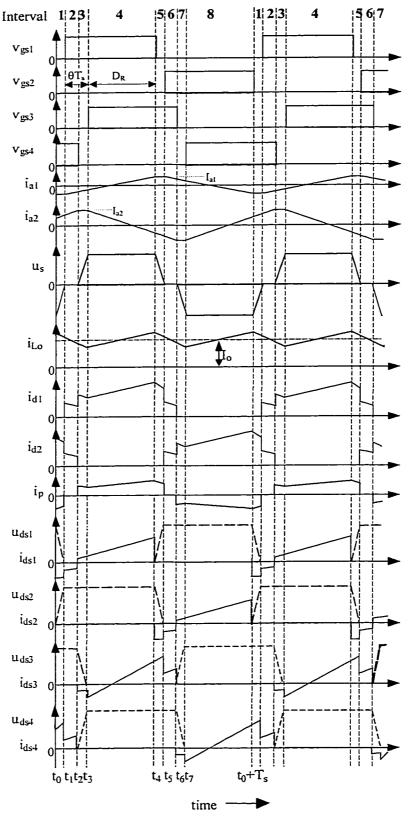

| Fig.   | 2.2 | Key waveforms of the proposed converter topology                                       | .13 |

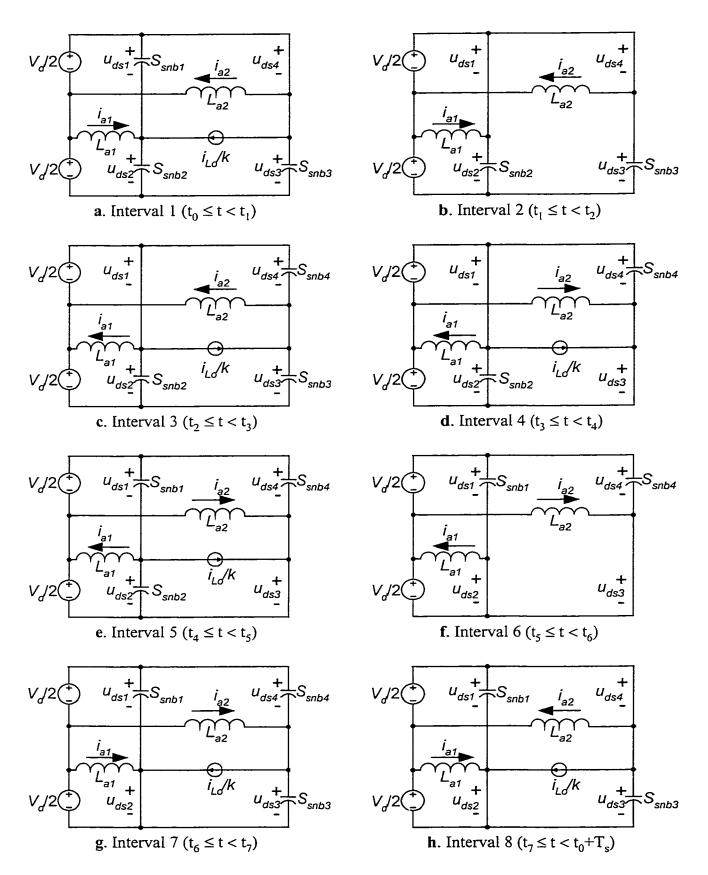

| Fig.   | 2.3 | Equivalent circuits in different intervals.                                            | 17  |

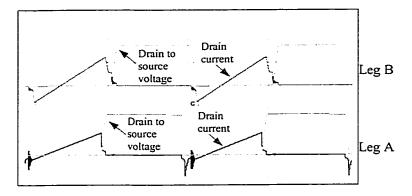

| Fig.   | 2.4 | The current and voltage waveforms of switches on both legs of the bridge at full load  |     |

|        |     | condition                                                                              | 23  |

| Fig. 2 | 2.5 | The current and voltage waveforms of switches on both legs of the bridge at light load |     |

|        |     | condition                                                                              | 24  |

| Fig. 2 | 2.6 | The current and voltage waveforms of switches on both legs under extreme operating     |     |

|        |     | conditions                                                                             | 25  |

| Fig. 2 | 2.7 | The gating and drain-to-source voltage waveforms of the switches under full load       |     |

|        |     | condition                                                                              | 26  |

| Fig. 2 | 2.8 | The gating and drain-to-source voltage waveforms of switches under light load          |     |

|        |     | condition.                                                                             | 27  |

| Fig. 2 | 2.9 | The overall efficiency as a function of output power                                   | 28  |

| Fig. 1 | 3.1 | ZVS full bridge converter with dc blocking capacitor $C_s$                             | 33  |

| Fig. 3 | 3.2 | Timing sequence of the asymmetrical gating pattern                                     | 34  |

| Fig. 2 | 3.3 | Equivalent circuits in three different modes each switching cycle.                     | 38  |

| Fig 1  | 3 4 | The block diagram of the peak current mode control feedback loops                      | 44  |

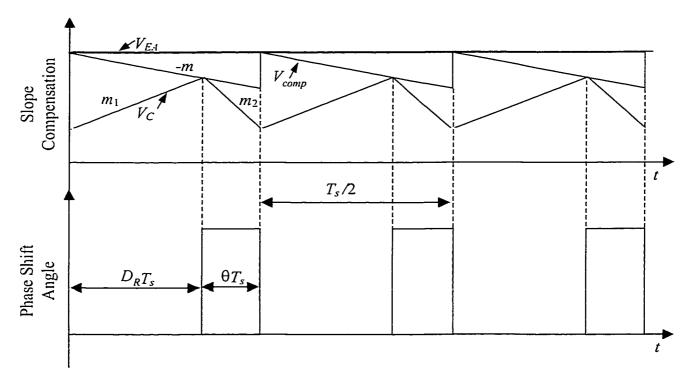

| Fig. 3.5 Generating the phase shift angle in PCMC.                                                | 45 |

|---------------------------------------------------------------------------------------------------|----|

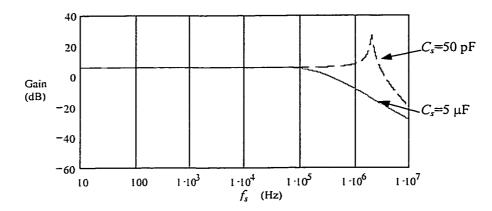

| Fig. 3.6 Effects of $C_s$ on the closed current loop gain.                                        | 49 |

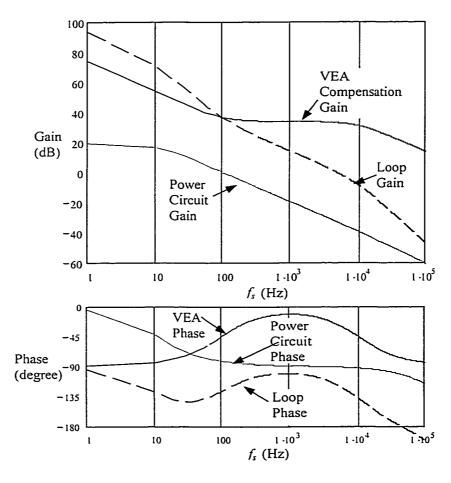

| Fig. 3.7 The Bode Plot of the power circuit in PCMC and proposed compensation                     | 49 |

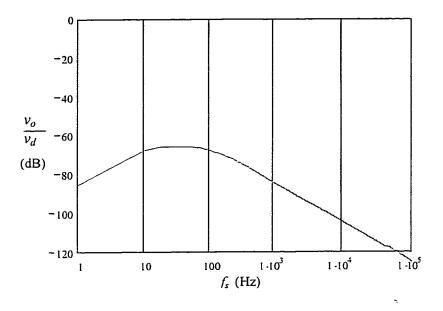

| Fig. 3.8 The Bode Plot of the transfer function from the input to the output.                     | 50 |

| Fig. 3.9 A Type-II compensation around the error voltage amplifier                                | 50 |

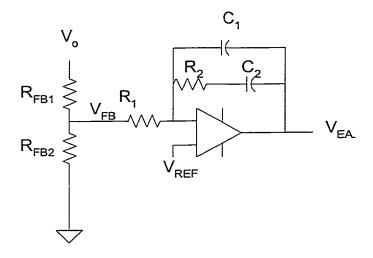

| Fig. 3.10 Circuit schematic for simulation using PSIM                                             | 52 |

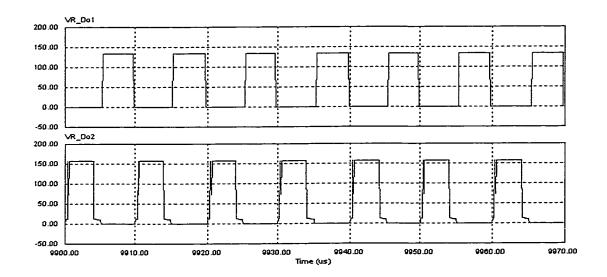

| Fig. 3.11 Asymmetrical gating and the output voltage of the two bridge legs                       | 54 |

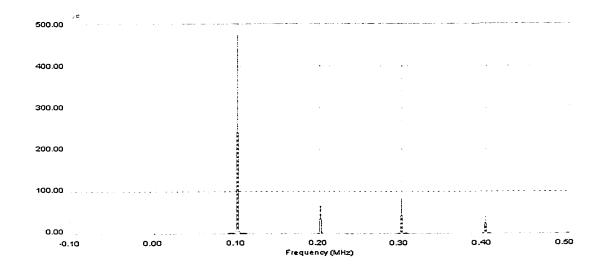

| Fig. 3.12 Spectrum of the bridge output voltage $V_{AB}$ shown in Fig. 3.11                       | 54 |

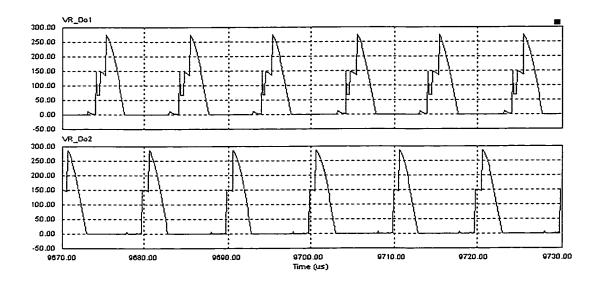

| Fig. 3.13 The effects of the dc blocking capacitor $C_s$                                          | 55 |

| Fig. 3.14 Spectrum of the bridge output voltage seen by the transformers after the dc blocking    | 5  |

| capacitor $C_s$                                                                                   | 55 |

| Fig. 3.15 Influences of the value of the dc blocking capacitor on the reverse voltage stress of t | he |

| rectifier diodes                                                                                  | 57 |

| Fig. 3.16 Influences of the dc blocking capacitor on secondary currents                           | 58 |

| Fig. 3.17 Influences of the dc blocking capacitor on ZVS switching                                | 58 |

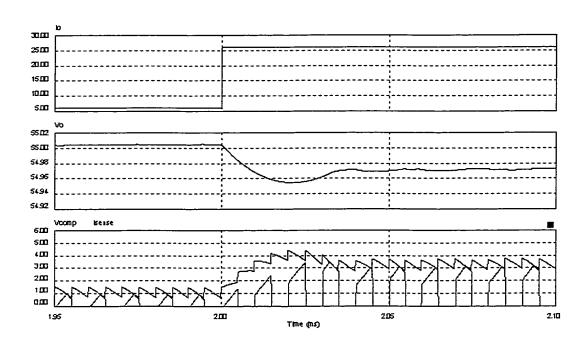

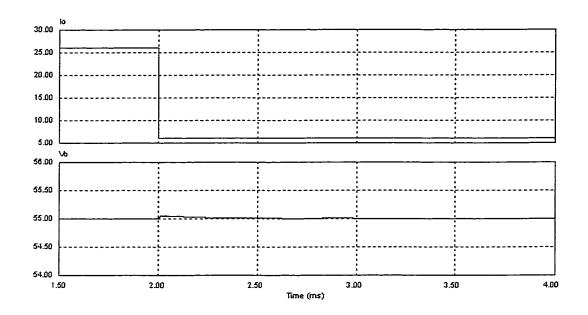

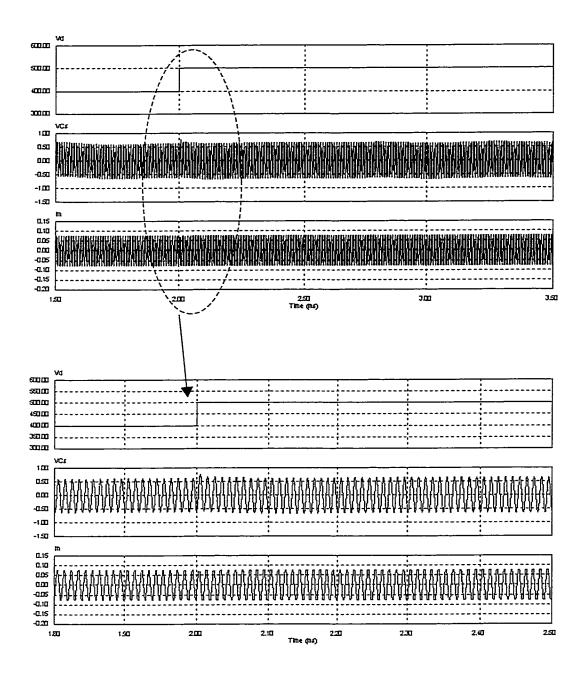

| Fig. 3.18 Input voltage step responses.                                                           | 60 |

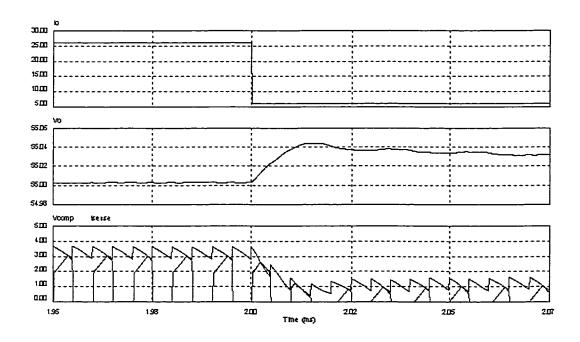

| Fig. 3.19 Converter responses to load current stepping up, and the control signal variations      | 61 |

| Fig. 3.20 Converter responses to load current stepping down, and the control signal variations.   | 62 |

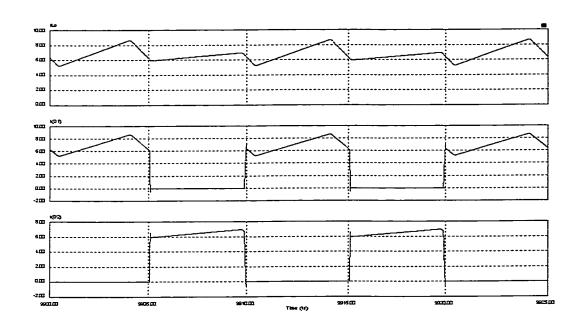

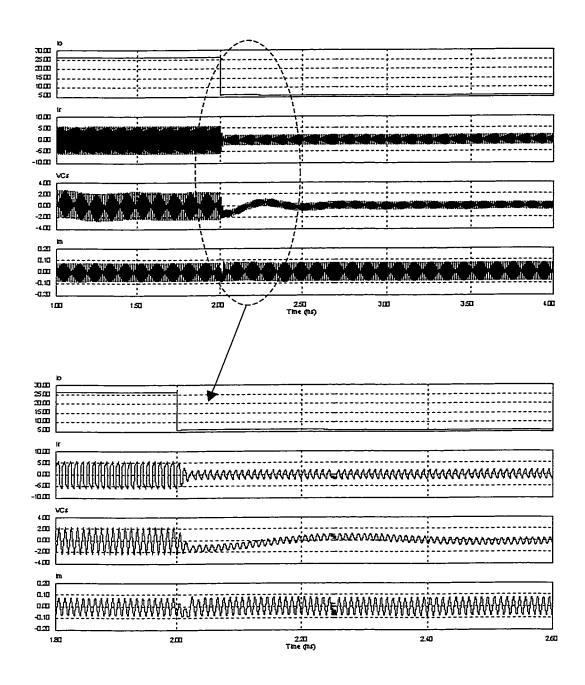

| Fig. 3.21 Magnetizing current and dc blocking capacitor voltage under load step down              | 63 |

| Fig. 3.22 Magnetizing current and dc blocking capacitor voltage under load up step                | 64 |

| Fig. 3.23 Magnetizing current and dc blocking capacitor voltage under input voltage up step       | 65 |

| Fig. 4. 1 The example design curves for selecting the auxiliary inductors and the permitted       |    |

| maximum snubber capacitors                                                                        | 72 |

| Fig. A.24 The block diagram of the voltage mode control feedback loop. | 81 |

|------------------------------------------------------------------------|----|

| Fig. A.25 Generating the phase shift angle in VMC                      | 82 |

# LIST OF TABLES

| Table 2.1 Principal Parameters of the Simulation Circuit | 22 |

|----------------------------------------------------------|----|

| Table 3.2 The Asymmetrical Gating Patterns               | 53 |

| Table 4.3 An Example Circuit                             | 74 |

#### **LIST OF ACRONYMS**

AC Alternative Current

ACMC Averaged Current Mode Control

CCM Continuous Conduction Mode

DC Direct Current

DCM Discontinuous Conduction Mode

EMI Electromagnetic Interference

ESL Equivalent Series Inductor

ESR Equivalent Series Resistor

FB Feedback

IGBT Isolated Gate Bipolar Transistor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PCMC Peak Current Mode Control

PWM Pulse Width Modulation

rms, RMS Root Mean Square value

VMC Voltage Mode Control

ZCS Zero Current Switching

ZVS Zero Voltage Switching

#### LIST OF PRINCIPAL SYMBOLS

$\Delta_{+}$  and  $\Delta_{-}$  positive and negative voltage pulse width, respectively

θ phase shift angle expressed in fraction of a switching cycle period

$C_{a1}$  and  $C_{a2}$  auxiliary circuit input voltage splitter capacitors

C<sub>a</sub> output filter capacitor

$C_s$  dc component blocking series capacitor

$C_{sh1}$ ,  $C_{sh2}$ ,  $C_{sh3}$ , and  $C_{sh4}$  snubber capacitors for each of the four switches, respectively

$D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  individual duty ratio of the four switches, respectively

$D_{o1}$  and  $D_{o2}$  two output rectifier diodes of the full bridge converter

$D_R$  duty ratio of the output rectifier diodes

$d_1, d_2, d_3$  and  $d_4$  individual switching dead time of the four switches respectively

$f_s$  switching frequency

$I_{La1}$  and  $I_{La2}$  peak value of the current through the two auxiliary inductors  $L_{a1}$

and  $L_{a2}$ , respectively

$I_{Lopeak}$  and  $I_{Lovalley}$  peak and valley values of the current through the output inductor

$L_o$ , respectively

I<sub>o</sub> nominal output current

$i_{ds1}$ ,  $i_{ds2}$   $i_{ds3}$  and  $i_{ds4}$  instantaneous drain current of the four switches, respectively

$i_p$  instantaneous primary current of the power transformer

k turns ratio of the power transformer primary to secondary windings

$L_{a1}$  and  $L_{a2}$  auxiliary circuit inductors

$L_o$  output filter inductor

$P_o$  output power of the converter

$S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  four switches of the full bridge converter

s Laplace transform variable

$T_r$  power transformer

$T_s$  switching cycle period

t time variable

$t_d$  switching dead time

$u_{ds1}$ ,  $u_{ds2}$   $u_{ds3}$  and  $u_{ds4}$  instantaneous drain to source voltage of the four switches,

respectively

$V_d$  nominal input dc voltage

$V_{dc}$  dc bias voltage

$V_o$  nominal output voltage

$v_c$  instantaneous voltage of the dc blocking capacitor  $C_s$

$v_o$  instantaneous output voltage

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 General Introduction

Full-bridge dc/dc converters are extensively used in medium to high power level applications. For most of these applications, particularly those for the computer and telecommunication systems, the most desirable features of the converter are high efficiency, high power density, high reliability and low Electro-Magnetic Interference (EMI).

Unfortunately, the standard full bridge topology operates in hard switching, and the hard switching converter is unable to achieve high efficiency and high power density for the following reasons: in order to achieve high power density, the switching frequency is normally increased, because at increased frequencies, the converter can employ smaller sized power magnetics and capacitors, both of which are the largest devices of a power converter. However, as the switching frequency increases, the switching losses associated with the turning on and off of switches will become excessive. These losses greatly reduce the converter's overall efficiency, and high power density is not achievable due to the resultant high cooling requirements.

To solve these problems, soft switching techniques are normally used. Basically there are two types of the soft switching techniques: Zero Voltage Switching (ZVS) and Zero Current Switching (ZCS). Either of the techniques can greatly reduce and even completely eliminate the switching losses in the converter. However, it is well understood that ZVS is more advantageous for a MOSFET switch topology than the ZCS.

High power level full bridge converters usually use IGBT switches, due to IGBT's low

conduction losses and higher power capability. However, IGBT is not as fast as MOSFET, and its switching frequency can not be increased beyond 50 kHz even if softly switched. Contrary to IGBT, MOSFET is a resistive device when it is turned on, and the conduction losses are higher as compared to IGBT at high power levels. However, MOSFET is a faster device and is able to operate up to a few MHz.

As mentioned before, the approach to achieve high power density is to operate the converter at a higher switching frequency. For power levels up to 3 kW, the full-bridge converters now employ MOSFET switches. In most of these converters, ZVS is used to increase the overall efficiency and alleviate the thermal problems. However, in the following section, it will be seen that these converters lose ZVS under some operating conditions, causing potential thermal problems and lowering the reliability of the converter.

#### 1.2 Review of Existing ZVS Full Bridge Topologies

#### 1.2.1 ZVS full bridge topologies with passive mechanism

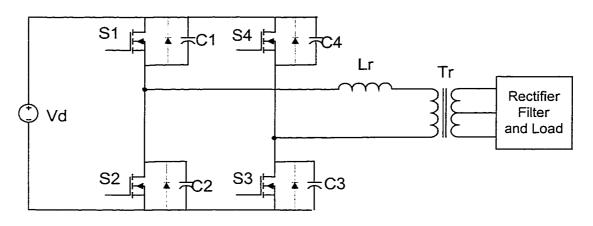

Fig. 1.1 shows two typical full bridge topologies that achieve ZVS with passive components [1-7]. In Fig. 1.1a, ZVS is achieved by placing an inductor in series with the power transformer, while in Fig. 1.1b it is achieved by placing an inductor in parallel with the power transformer. In both topologies, a snubber capacitor is placed across each switch. In a practical configuration, the series inductor may be the leakage inductor of the power transformer, the parallel inductor may be the magnetizing inductor of the power transformer, and the snubber capacitor may be the inherent drain-to-source capacitor of the MOSFET switch. Addition of only one component to the full bridge converter makes these topologies the simplest.

The basic operating principles to achieve ZVS in these two topologies are as follows.

(i) ZVS turn-off is achieved by holding the drain-to-source voltage of the MOSFET at zero or very low during the turn off transient. This is accomplished by the snubber capacitor. At turn-off, the snubber capacitor significantly slows down the rate of rise of the drain to source voltage of the pertinent switch. In this way, the overlap between the decreasing drain current and rising drain-to-source voltage of each switch is greatly reduced, or even completely eliminated, and so are the switching losses.

a. ZVS topology with series inductor

b. ZVS topology with parallel inductor

Fig. 1.1 ZVS full bridge converter topologies using passive devices.

(ii) ZVS turn-on is achieved by completely discharging the snubber capacitors of the switches before they are turned on. During the dead time of the gating of the bridge switches, the discharging of the snubber capacitors is made possible by the residual current in the series inductor in the topology of Fig. 1.1a, or the parallel inductor in the topology of Fig. 1.1b.

In comparison of these two topologies in Fig. 1.1, the one with the series inductor can achieve ZVS even when there is a short circuit (or over loading) across the load, while the other one that has the parallel inductor maintains ZVS operation even when there is an open circuit (or no load) across the output terminals. Both topologies are simple. However, both of them suffer from their own shortcomings.

The drawbacks of the topology with series inductor (Fig. 1.1a) are:

- Loss of ZVS at no load or light-load. This is because the complete discharge of snubber capacitors depends on the stored energy in inductor  $L_r$  and the energy is proportional to the square of the peak value of the primary current. When the load is light, the primary current is low, and consequently the stored inductor energy is also low. This energy is not sufficient to deplete the snubber capacitor in the dead time. Thus, ZVS is lost at turn-on.

- (ii) Reduction of the effective duty ratio because of the voltage drop on the series inductor.

This results in higher primary current and conduction losses of the switches.

- The drawbacks of the topology with parallel inductor (Fig. 1.1b) include the following.

- (i) Loss of ZVS under over load or short-circuit conditions. This is because, when the output terminals have a short circuit, the large load current, when it is reflected into the primary side, overrides the parallel inductor current and cancel its function to achieve ZVS.

- (ii) Increased conduction losses and reduced efficiency at light load. This is because the

circulating current flowing along the parallel inductor, switch and the input dc line is almost independent of the load level. At light load, the circulating current becomes significant compared to the load current, and this remarkably increases the total conduction losses at light load.

It is seen that, both topologies lose ZVS under certain operating conditions. The loss of ZVS results in the following problems: (i) increased size of heat sink due to switching losses, (ii) higher EMI due to high di/dt of the snubber discharging current when the switch is turned on, and (iii) reduced reliability due to reverse recovery current of the body diodes.

#### 1.2.2 Soft switching full bridge topologies with active mechanism

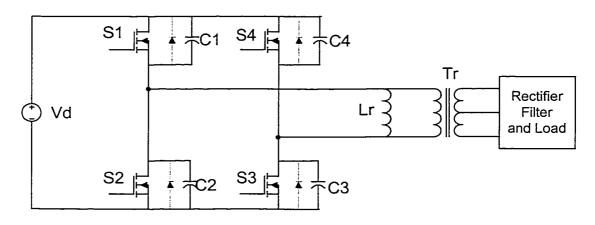

Fig. 1.2 shows a soft switching full bridge topology with active components [6-13]. It employs two symmetrical auxiliary circuits, each of which is controlled through an auxiliary bidirectional switch. In order to control the current through the auxiliary inductors, each bidirectional switch must be implemented by using two anti-paralleled unidirectional switches. By proper timing, the current building up in the auxiliary inductor discharges the snubber capacitor of the pertinent switch to achieve its ZVS turn-on, or overcomes the tail current of the pertinent switch to achieve ZCS turn-off. Soft switching can be achieved under all operating conditions, thereby overcoming the aforementioned drawbacks existing in the topologies shown in Fig. 1.1. Specifically, it achieves soft switching even under both extreme operating conditions, namely no load and output short circuit conditions, and there is no reduction of the effective duty ratio.

The topology in Fig. 1.2 is originally developed for high power full-bridge converters using IGBTs. For lower power level applications, when MOSFETs are used, the topology of Fig. 1.2 is directly converted into Fig. 1.3.

Fig. 1.2 Soft switching full bridge converter IGBT topology using active auxiliary circuits.

Fig. 1.3 ZVS full bridge converter MOSFET topology using active auxiliary circuits based on the original IGBT topology in Fig. 1.2.

As seen from Fig. 1.3, each unidirectional switch in the auxiliary circuit requires an additional fast speed diode in series with a MOSFET. The topology becomes rather complicated and costly for low power level applications. Simplified ZVS topologies shall be developed to overcome these problems.

#### 1.3 Objectives and Scope of the Study

The objectives of the study are as follows:

- (i) Presenting a simplified but improved ZVS full bridge topology,

- (ii) Characterizing the proposed topology for industrial applications,

- (iii) Generating the design procedure.

The scope of this thesis is limited within the following frame:

- (i) Steady state analysis,

- (ii) Averaged state space small signal analysis,

- (iii) Concept verification through simulations performed in Pspice and Psim, and

- (iv) Experimental results of the prototype converter.

#### 1.4 Thesis Outline

The thesis is organized in the following structure.

In Chapter 2, the proposed topology is presented, and the steady state analysis is performed to understand its steady states characteristics and properties. Simulation and experimental results are also presented as proofs of concept.

In Chapter 3, the proposed topology under dynamic conditions is analyzed, including the effects of the asymmetry in gating patterns of the full bridge switches, protection of the current

sense transformer from saturation, and the small signal model of the proposed topology. It also points out that with phase shift Pulse Width Modulation (PWM) technique, the Peak Current Mode Control (PCMC) can still be used along with the dc blocking capacitor that is employed to prevent the current sense transformer saturation. Compensation of the feedback loop to dynamically stabilize the converter is also discussed.

In Chapter 4, asymmetrical auxiliary circuits are suggested to optimize the converter performance, and a design procedure oriented for industrial applications is generated based on the analysis performed in the previous chapters. A design example is also given.

Conclusions of the thesis work are drawn in Chapter 5, followed by suggestions for future work.

#### **CHAPTER 2**

# PROPOSED ZVS CONVERTER TOPOLOGY AND

#### THE STEADY STATE ANALYSIS

#### 2.1 Introduction

An improved line and load independent ZVS full bridge converter topology is presented in this chapter. This topology is simply a combination of a conventional full bridge converter and an auxiliary circuit that consists of a few passive components. However, the advantages of the topology are remarkable: (i) it achieves ZVS independent of the line and load conditions, and the power circuit as well as its control is just that of the conventional full bridge converter, (ii) ZVS independent of line and load conditions results in smaller heatsinks for the switches and also the capability of operating the converter at high frequency, (iii) the design of the converter can follow the well understood and well developed procedure to facilitate industrial application.

To better understand the operating principle and performance characteristics of the proposed topology, and to provide reference in optimal design procedure in Chapter 4, a detailed steady state analysis is performed in this chapter.

In this chapter, the proposed topology is presented in Sec. 2.2. The steady state analysis is performed in Sec. 2.3. Simulation results are shown in Sec. 2.4, followed by the conclusions.

#### 2.2 Circuit description

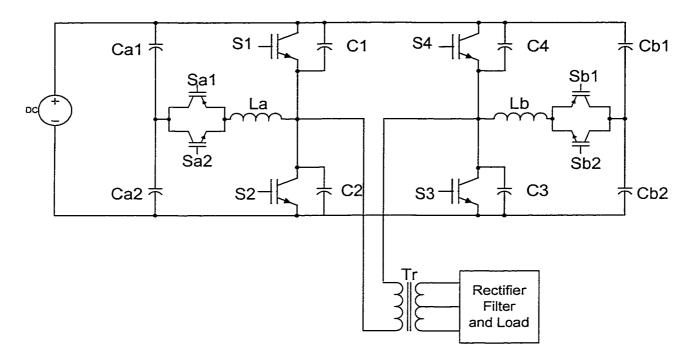

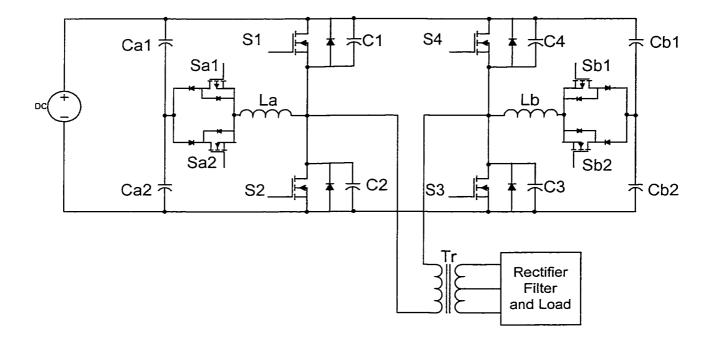

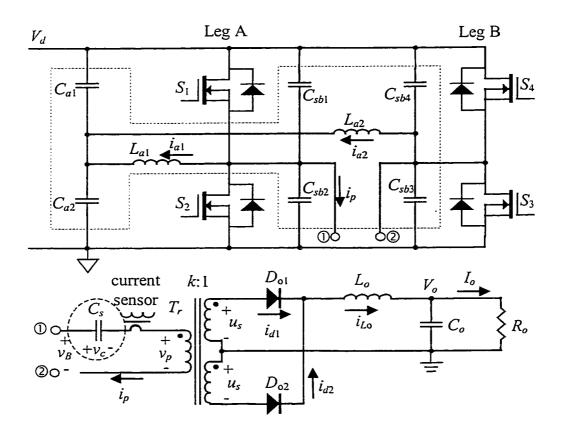

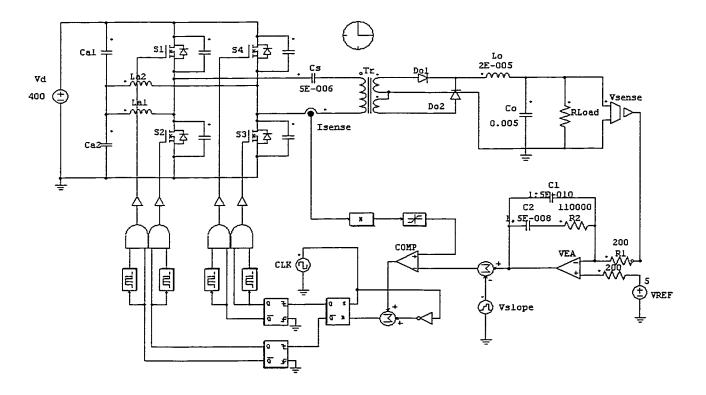

Fig. 2.1 shows the proposed ZVS full bridge converter topology. It consists of two functional sub-circuits. One sub-circuit is a conventional full bridge converter, which is referred to as the power circuit hereafter. The other is the auxiliary circuit shown in the shaded area.

Fig. 2.1 The proposed ZVS full bridge converter topology.

The power circuit employs the following devices: (i)  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ , four MOSFET switches, (ii)  $T_r$ , the power transformer with a turns ratio of k, (iii)  $D_{o1}$  and  $D_{o2}$ , two rectifier diodes, (iv)  $L_o$  and  $C_o$ , the output filter, and (v)  $R_o$ , the load.

The auxiliary circuit is comprised by eight passive devices, i.e., (i)  $C_{sb1}$ ,  $C_{sb2}$ ,  $C_{sb3}$ , and  $C_{sb4}$ , four drain-to-source snubber capacitors, each connected across one switch, (ii)  $C_{a1}$  and  $C_{a2}$ , a capacitor voltage divider, and (iii)  $L_{a1}$  and  $L_{a2}$ , two auxiliary inductors.

Phase shift PWM is used as the control technique to regulate the output voltage. The reasons for choosing the phase shift technique is to be able to use the PCMC which will be detailed in Chapter 3. For power transfer, the power circuit operates almost in the same way as does a conventional full bridge converter, and the auxiliary circuit hardly interferes with this

transfer. However, the auxiliary circuit does have significant influences on the switching transients of the switches: it simply removes the switching losses from all the switches during both turn-on and turn-off transients.

#### 2.3 Steady State Analysis

Since conventional phase shift full bridge converters have been extensively addressed in the literature, only the operation of the auxiliary circuit will be discussed in detail in this chapter.

In the following analysis, the time varying variables such as the current and voltage of the principal components and devices are determined. Based on these variables, the performance of the converter can be illustrated, and quantities such as the root mean square (rms), average or peak current and voltage of these components can be obtained. These quantities determine the ratings of the components and they will be used in the design procedure in Chapter 4.

In the analysis presented below, a closed form solution is obtained by solving a set of differential equations in each interval and by matching the boundary conditions at the boundary of the intervals. The initial conditions are a function of the operating frequency  $f_s$ , the input line voltage  $V_d$  and the output power  $P_o$ . They can be obtained by the iterative process such as Newton-Raphson method.

#### 2.3.1 Assumptions and some constants for the analysis

The following assumptions are made for the steady state analysis:

- (i) The steady state conditions have been established and the converter is running in the Continuous Conduction Mode (CCM) at the input dc voltage  $V_d$ , producing the nominal output voltage  $V_o$  and delivering the power of  $P_o$  to a constant load.

- (ii) The gating of switches on Leg A, namely  $S_1$  and  $S_2$ , is leading the gating of switches on

- Leg B, or  $S_3$  and  $S_4$ , by a phase shifted angle  $\theta$  (expressed as a fraction of a switching period), and  $\theta$  is determined by the control circuit to regulate the output voltage,

- (iii) the switching frequency is  $f_s$ ,

- (iv) all components and devices have ideal properties and characteristics, i.e.,

- (1)  $T_r$ : losses and leakage inductance are negligible, and the core does not saturate,

- (2)  $L_o$ ,  $L_{a1}$  and  $L_{a2}$ : all inductors are ideal inductors with zero losses, and their inductances are constant,

- (3)  $C_o$ ,  $C_{a1}$ ,  $C_{a2}$ ,  $C_{sb1}$ ,  $C_{sb2}$ ,  $C_{sb3}$ , and  $C_{sb4}$ : all capacitors are ideal capacitors, their equivalent series resistance (ESR) and equivalent series inductance (ESL) are negligible, and their capacitances are constant,

- (4)  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ : all switches are ideal, having negligible conduction losses, and zero parasite capacitances,

- (5)  $D_{o1}$  and  $D_{o2}$ : both diodes are ideal, having a forward voltage drop of 0 V and negligible reverse recovery time.

- (6) The magnetizing inductance of the power transformer is so great that the magnetizing current is negligible.

- (v) There is a very short dead time,  $t_d$ , between the ON states of the two switches on each leg of the bridge,

- (vi)  $C_{sb1}$  and  $C_{sb2}$  have equal capacitance value, and so do  $C_{sb3}$  and  $C_{sb4}$ ,

- (vii)  $C_{a1}$  and  $C_{a2}$  have equal capacitance value, and they are large enough to establish a constant and ripple free voltage during the steady state operation.

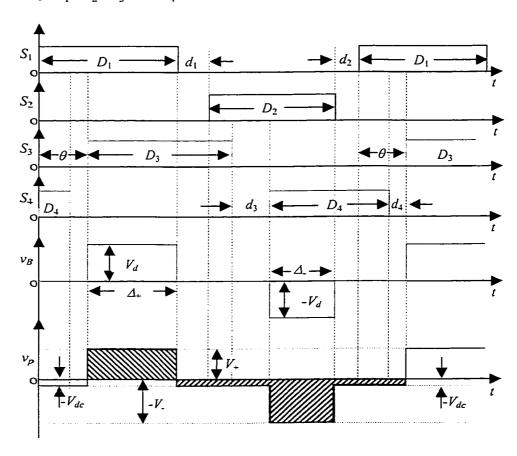

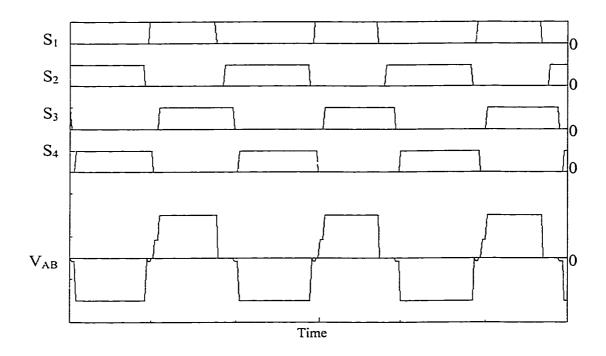

Under these assumptions, the operating principle is illustrated with key waveforms shown in Fig. 2.2. Each switching cycle can be divided into eight distinct intervals.

Fig. 2.2 Key waveforms of the proposed converter topology. The dead time and switching transient are exaggerated.

For convenience, the following constants used in the analysis are defined.

In steady state, the effective duty ratio  $D_R$  of each output diode is determined by

$$D_R = \frac{kV_o}{2V_d} \tag{2-1}$$

and it is also equal to

$$D_R = \frac{1}{2} - t_d f_s - \theta \tag{2-2}$$

where  $t_d$  is the switching dead time,  $f_s$  the switching frequency and  $\theta$  the phase shifted angle expressed as a fraction of one switching cycle.

For the power circuit, the current flowing through the output inductor has the saw-tooth waveform biased by the output dc current  $I_o$ . Defining  $I_{Lopeak}$  and  $I_{Lovalley}$  as the peak and valley values of this saw-tooth shaped current, respectively, then there are:

$$I_{Lopeak} = \frac{1}{2} \frac{(\frac{V_d}{k} - V_o)}{L_o} \frac{D_R}{f_s} + I_o = \frac{(V_d - kV_o)V_o}{4f_s V_d L_o} + I_o$$

(2-3)

$$I_{Lovalley} = -\frac{(V_d - kV_o)V_o}{4f_s V_d L_o} + I_o$$

(2-4)

For the auxiliary circuit,  $C_{a1}$  and  $C_{a2}$  act as a voltage divider, each holding half the input voltage  $V_d$ . When the two switches on each leg are switched alternately and symmetrically with little dead time in between, the auxiliary inductors  $L_{a1}$  and  $L_{a2}$  each see alternating positive and negative voltage for equal intervals. For example, when  $S_1$  is ON for the duration of half cycle minus  $t_d$ ,  $L_{a1}$  sees the voltage across  $C_{a1}$  that is  $V_d/2$ , and when  $S_2$  is ON, it sees the voltage across  $C_{a2}$  in opposite polarity that is  $V_d/2$ . Then the current through  $L_{a1}$  alternatively rises and

falls in linear mode. The magnitude of the total variation of this fluctuating current is determined by

$$\Delta I_{a1} = \frac{V_d}{2L_{a1}} \left( \frac{1}{2f_s} - t_d \right) \tag{2-5}$$

When both  $S_1$  and  $S_2$  are OFF, because the dead time is assumed very short, the current through  $L_{a1}$  can be considered constant during the dead time interval.

Similarly, the fluctuations in the current through  $L_{a2}$  are determined by

$$\Delta I_{a2} = \frac{V_d}{2L_{a2}} \left( \frac{1}{2f_s} - t_d \right) \tag{2-6}$$

It is noticed that  $C_{a1}$  and  $C_{a2}$  are in the auxiliary current loops. Because of the capacitors, the steady state auxiliary inductor currents have no dc components. Thus, these currents have a triangle waveform that is symmetrical about zero. Defining  $I_{a1}$  and  $I_{a2}$  as the peak values of the currents through  $L_{a1}$  and  $L_{a2}$  respectively, then they are:

$$I_{a1} = \frac{V_d}{4L_{a1}} \left(\frac{1}{2f_s} - t_d\right) \tag{2-7}$$

$$I_{a2} = \frac{V_d}{4L_{a2}} \left(\frac{1}{2f_s} - t_d\right) \tag{2-8}$$

#### 2.3.2 Steady state analysis of each interval

In the last interval of the previous cycle, both  $S_2$  and  $S_4$  were ON while both  $S_1$  and  $S_3$  OFF. The primary winding of  $T_r$  saw a constant voltage,  $-V_d$ , and  $D_{o1}$  was reverse biased and  $D_{o2}$  forward biased. Thus the output inductor current was reflected back the primary side via  $D_{o2}$  and  $T_r$ . The drain current of  $S_2$  was the sum of primary current and the auxiliary inductor current  $I_{a1}$ ,

and it reached its peak value at the end of the last cycle. This peak value is given by

$$I_1 = I_{a1} + \frac{I_{Lopeak}}{k} \tag{2-9}$$

#### A. Interval $1 (t_0 \le t < t_1)$

At the beginning of this interval,  $S_2$  is turned off and no other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.3a.

As  $S_2$  is OFF  $I_1$ , which is the total current flowing into Leg A, starts to charge  $C_{sb2}$  and discharge  $C_{sb1}$ . Consequently  $u_{ds1}$ , the drain-to-source voltage of  $S_1$ , is decreasing while  $u_{ds2}$  is increasing. At the same time,  $S_4$  remains ON and  $S_3$  OFF. Then  $T_r$  continues to see a negative voltage during this interval. This keeps  $D_{o1}$  reverse biased and  $D_{o2}$  forward biased. Under this condition, the output inductor current is reflected back into the primary side through  $D_{o2}$ , and the primary current is still flowing into Leg A.

Because this interval is usually very short, the inductor current  $i_{a1}$  and  $i_{Lo}$  can be considered constant. Then, the drain-to-source voltages of both switches on  $Leg\ A$  are governed by the following equations:

$$\begin{cases} -C_{snb1} \frac{du_{ds1}(t)}{dt} + C_{snb2} \frac{du_{ds2}(t)}{dt} = I_1 \\ u_{ds1}(t) + u_{ds2}(t) = V_d \end{cases}$$

(2-10)

Taking the initial conditions that  $u_{ds1}(t_0)=V_d$  and  $u_{ds2}(t_0)=0$ , and remembering  $C_{snb1}=C_{snb2}$ , then the solution of (2-10) is found to be the following:

Fig. 2.3 Equivalent circuits in different intervals.

$$u_{ds1}(t) = V_d - \frac{I_{a1} + I_{Lopeak}/k}{2C_{sb1}}(t - t_0)$$

(2-11)

$$u_{ds2}(t) = \frac{I_{a1} + I_{Lopeak}/k}{2C_{sh2}}(t - t_0)$$

(2-12)

It is seen from (2-12) that because of  $C_{sb2}$ ,  $u_{ds2}$  rises slowly, providing the ZVS condition for the switch to turn off. Thus, a nearly lossless turn-off is achieved on  $S_2$ .

Within this interval  $u_{ds1}$  falls to zero volts and  $u_{ds2}$  reaches  $V_d$ , then the body diode of  $S_1$  latches in to give  $i_{a1}$  a path to flow. This clamps  $u_{ds1}$  at zero in the rest of this interval, providing the ZVS condition for  $S_1$  to turn on.

It is also noticed that although the auxiliary current  $i_{a1}$  joins the load current to exert more current stress on  $S_2$  at its turn-off, the auxiliary current is enhanced by the load current in discharging the snubber of  $S_1$ , preparing the ZVS condition for  $S_1$ to turn on.

After  $u_{ds1}$  reaches zero, the primary winding of  $T_r$  will see a zero voltage as  $S_4$  is still ON. As required by  $L_o$ , both  $D_{o1}$  and  $D_{o2}$  start to share the output inductor current  $i_{Lo}$  in the freewheeling mode as in a conventional full bridge converter. Thus the primary current  $i_p$  stops flowing and only  $i_{a1}$  flows into  $Leg\ A$ . In the meantime, the current that flows through  $S_4$  only consists of  $i_{a2}$  which is the current of the auxiliary inductor  $L_{a2}$ . It is found that

$$i_{a2}(t) = \frac{V_d}{2L_{a2}}(t - t_0 - \frac{\theta}{f_s}) + I_{a2}$$

(2-13)

The duration of this interval is the switching dead time  $t_d$ , i.e.,

$$t_1 - t_0 = t_d (2-14)$$

#### B. Interval 2 $(t_1 \le t < t_2)$

At the beginning of this interval,  $S_1$  is turned on under ZVS condition. Thus a nearly lossless turn-on switching is achieved on  $S_1$ . No other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.3b.

As  $S_1$  is ON,  $L_{a1}$  sees a constant voltage established by  $C_{a1}$ . Then  $i_{a1}$  starts to increase linearly from its negative peak as governed by

$$i_{a1}(t) = \frac{V_d}{2L_{a1}}(t - t_1) - I_{a1}$$

(2-15)

As both  $S_1$  and  $S_4$  are ON, the primary winding of  $T_r$  still sees zero voltage. Thus both output rectifier diodes conducts to freewheel the output inductor current, and no current flows through the primary winding. Hence there is still the single current  $i_{a2}$  flowing through  $S_4$  as governed by (2-13).

The duration of this interval is determined by the phase shift angle that is required to regulate the output voltage as well as by the dead time:

$$t_2 - t_1 = \frac{\theta}{f_s} - t_d \tag{2-16}$$

and the phase shift angle expressed as a fraction of a switching cycle period, is approximately governed by

$$\theta = \frac{1}{2} - \frac{kV_o}{2V_d} - t_d f_s \tag{2-17}$$

#### C. Interval 3 $(t_2 \le t < t_3)$

At the beginning of this interval  $S_4$  is turned off. No other switching action takes place

during this interval. The equivalent circuit of this interval is shown in Fig. 2.3c.

When  $S_4$  is off,  $i_{a2}$  reaches its positive p-eak value  $I_{a2}$ . Similar to Interval 1, this current starts to charge  $C_{sb4}$  and discharge  $C_{sb3}$ . Thus i = sb4 starts to rise from zero while  $u_{sb3}$  decreases from  $V_d$ .

During this interval  $T_r$  starts to see a positive voltage because  $S_1$  is already ON. Thus  $D_{o1}$  is forward biased and  $D_{o2}$  reverse biased. The total output inductor current that is at its valley value now starts to flow through  $D_{o1}$ , forcing a primary current to flow. Therefore the current flowing out of Leg B is  $i_{a2}$  minus the reflected output inductor current during the discharging/charging interval.

As this interval is very short,  $i_{a2}$  is almost constant at its peak value  $I_{a2}$ . So is the output inductor current at its valley value as given in (2-4). Similar to Interval 1, it is found that

$$u_{ds3}(t) = V_d - \frac{I_{a2} - I_{Lovalley}/k}{2C_{sb3}}(t - t_2)$$

(2-18)

$$u_{ds4}(t) = \frac{I_{a2} - I_{Lovalley}/k}{2C_{sb4}}(t - t_2)$$

(2-19)

Owing to  $C_{sb4}$   $u_{sb4}$  can only rise slowly, providing the ZVS condition for  $S_4$  to turn off. Thus a nearly lossless turn-off is achieved on  $S_4$ .

Contrary to the switches on Leg A as seen from (2-18) and (2-19), the load current relieves  $S_4$ 's turn-off current stress from  $i_{a2}$ , but it also reduces the strength of  $i_{a2}$  in discharging the snubber capacitor of  $S_3$ . In order to prepare the ZVS condition for  $S_3$  to turn on,  $I_{a2}$  must be greater than the reflected load current. Otherwise ZVS turn-on would be lost in  $C_{sb3}$ . This shows the opposite effect of the load current on two different legs and this phenomenon shall be

observed in designing the auxiliary circuit.

The duration of this interval is determined by the dead time:

$$t_3 - t_2 = t_d \tag{2-20}$$

## D. Interval 4 $(t_3 \le t < t_p)$

At the beginning of this interval  $S_3$  is turned on under ZVS condition. Thus a nearly lossless turn-on is achieved for  $S_3$ . No other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.3d.

As  $S_3$  is ON,  $L_{a2}$  sees a constant negative voltage established by  $C_{a2}$ .  $i_{a2}$  starts to decrease linearly, as given by

$$i_{a2}(t) = -\frac{V_d}{2L_{a2}}(t - t_3) + I_{a2}$$

(2-21)

During this interval the drain currents of  $S_1$  and  $S_3$  are the combination of  $i_p$  with  $i_{a1}$  and  $i_{a2}$ , respectively. It is found that,

$$i_{ds1}(t) = \frac{V_d}{2L_{a1}}(t - t_1) - I_{a1} + \frac{1}{k} \left[ \frac{V_d - kV_o}{kL_o}(t - t_2) + I_o - \frac{(V_d - kV_o)V_o}{4f_sL_oV_d} \right]$$

(2-22)

$$i_{ds3}(t) = \frac{V_d}{2L_{a2}}(t - t_3) - I_{a2} + \frac{1}{k} \left[ \frac{V_d - kV_o}{kL_o}(t - t_2) + I_o - \frac{(V_d - kV_o)V_o}{4f_s L_o V_d} \right]$$

(2-23)

The duration of this interval is determined by the duty ratio that is required to regulate the output voltage:

$$t_4 - t_3 = \frac{D_R}{f_s} = \frac{kV_o}{2f_s V_d} \tag{2-24}$$

It is equivalent to

$$t_4 - t_3 = \frac{1}{2f_s} - t_d - \frac{\theta}{f_s} \tag{2-25}$$

## E. Intervals 5 through 8

The analysis of the circuit in the last four intervals of this switching cycle is similar to the first four intervals, except for the opposite switching activities on the switches. The equivalent circuit of this interval is shown in Fig. 2.3e though h. The analysis will not be repeated here.

After Interval 8, another switching cycle begins and operation of the circuit repeats the process from Intervals 1 through 8.

#### 2.4 Simulation Results

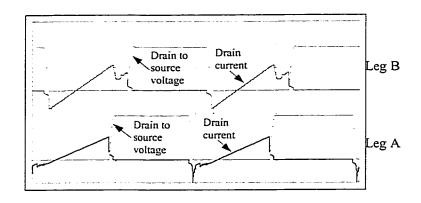

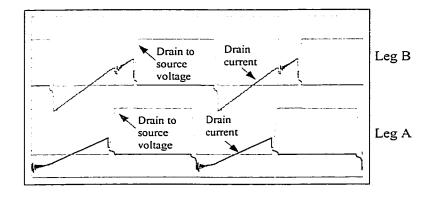

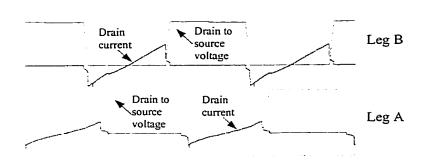

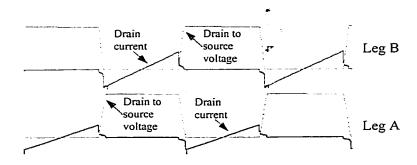

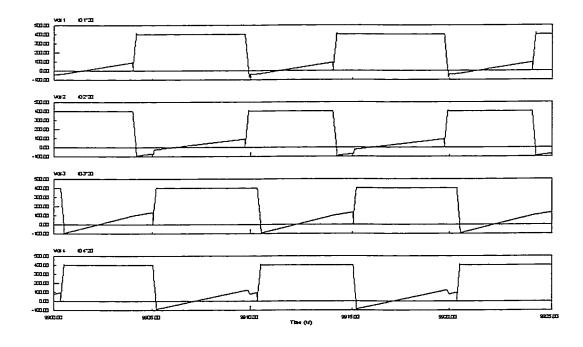

Simulation of the proposed converter topology is performed with the Pspice software. Table 2.1. shows the principal parameters of the circuit used in simulation. Since the drain-to-source voltage and drain current of the two switches on the same leg have exactly the same waveforms but out of phase, the waveforms of  $S_1$  on Leg A and  $S_3$  on Leg B are shown below instead of that of all four switches.

Fig. 2.4 shows the voltage and current waveforms of the switches under full load and different input voltage. It is seen that ZVS on each switch is achieved at both turn-on and turn-off under all these conditions.

Table 2.1 Principal Parameters of the Simulation Circuit

| parameter          | value  | parameter            | value   |

|--------------------|--------|----------------------|---------|

| k                  | 5.5:1  | $C_{sb3}, C_{sb4}$   | ln F    |

| t <sub>d</sub>     | 400 ns | L <sub>a1</sub>      | 200 μΗ  |

| $C_{a1}, C_{a2}$   | lμF    | L <sub>a2</sub>      | 100 μΗ  |

| $C_{sb1}, C_{sb2}$ | l nF   | $S_1, S_2, S_3, S_4$ | IRFP460 |

**a.** Low line full load:  $V_d = 350 \text{ V}$ .

**b.** Medium line full load:  $V_d = 380 \text{ V}$

c. High line full load:  $V_d = 400 \text{ V}$

Fig. 2.4 The current and voltage waveforms of switches on both legs of the bridge at full load condition.  $P_o$ =500W. Scale: voltage-200V/div., current-5A/div. time-5 $\mu$ s/div.

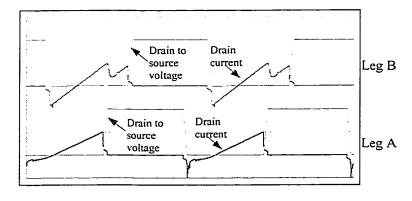

a. Low line light load:  $V_d = 350 \text{ V}$

**b.** Medium line light load:  $V_d$ =380 V

**c.** High line full light load:  $V_d$ =400 V

Fig. 2.5 The current and voltage waveforms of switches on both legs of the bridge at light load condition. Po=50W (10% rated load). Scale: voltage-200V/div., current-5A/div. time-5 $\mu$ s/div.

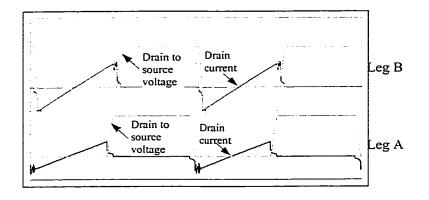

a. Simulation results under open circuit condition.  $V_d$ =380 V,  $P_o$ =0 W.

**b.** Simulation results under short circuit condition.  $V_d$ =380 V.

Fig. 2.6 The current and voltage waveforms of switches on both legs under extreme operating conditions.

Fig. 2.5 shows the voltage and current waveforms of the switches under 10% of the rated load and different input voltage conditions. It is seen that ZVS is also achieved on each switch at both turn-on and turn-off under all these conditions.

Fig. 2.6 shows the voltage and current waveforms of the switches under extreme operating conditions, i.e., the open or short circuit conditions. It can be concluded that ZVS is still achieved under these extreme conditions.

In summary, as seen from Fig. 2.4, Fig. 2.5 and Fig. 2.6, ZVS at turn-on and turn-off on each switch is achieved under all line and load conditions. All these prove the concepts of the

proposed topology, i.e., ZVS is achieved independent of line and load conditions.

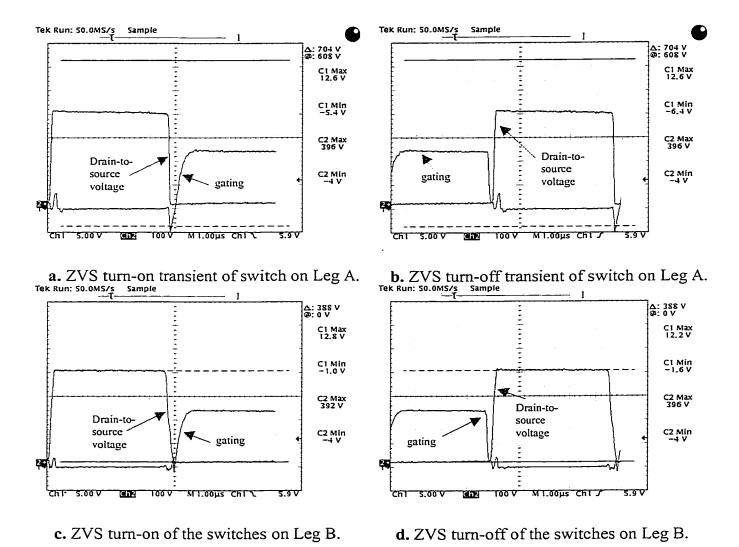

#### 2.5 Experimental Results

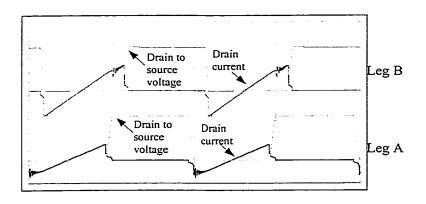

A 500 W, 300-400 V dc to 55 V dc prototype converter operating at 100 kHz was built to prove the concepts of the proposed topology. Listed in Table 2.1 are the principal parameters of the prototype converter.

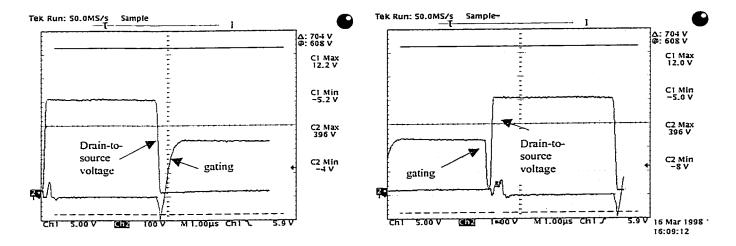

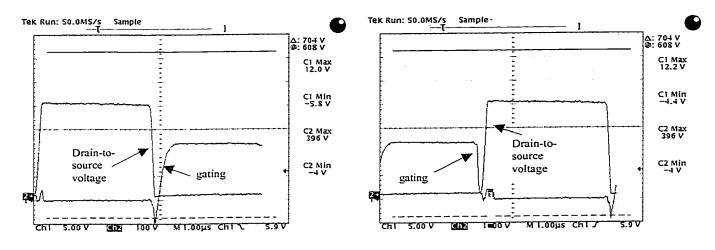

Fig. 2.7 The gating and drain-to-source voltage waveforms of the switches under full load condition.  $f_s$ =128 kHz,  $V_o$ =55 V,  $P_o$ =500 W,  $V_d$ =390 V.

Vertical scales: 100V/div. for the drain voltage, 10V/div. for the gating signal. Timing: 1µs/div.

- a. ZVS turn-on of the switches on Leg A.

- b. ZVS turn-off off the switches on Leg A.

- c. ZVS turn-on of the switches on Leg B.

- d. ZVS turn-off of the switches on Leg B.

Fig. 2.8 The gating and drain-to-source voltage waveforms of the switches under light load condition. f<sub>s</sub>=128 kHz, V<sub>o</sub>=55 V, P<sub>o</sub>=50 W, V<sub>dl</sub>=390 V.

Vertical scales: 100V/div. for the drain voltage, 5V/div. for the gatting signal. Timing: 1µs/div.

Fig. 2.7 shows the gating signal and the drain-to-source v-oltage of the under full load condition. The waveforms of only one switch from each leg are shown. The other switch has the same waveform with a 180° phase delay.

In Fig. 2.7 the drain current is not shown for the reason that putting the current probe to measure the current requires a long hook of wire inserted into the circuit, and the inductance of long wire hook will interfere with the normal operation and the wire hook can easily pick up

noises. Without detecting the drain current, it can still be concluded from Fig. 2.7 that each switch has ZVS switching at both turn-on and turn-off under all those conditions. Because, the gating signal comes after the drain to source voltage completely drops to zero, and it is withdrawn completely before the drain to source voltage starts to rise from zero.

Fig. 2.8 shows the gating signal and the drain to source voltage waveforms of the switches under 10 % of the rated load condition. Similarly, it can be concluded that ZVS is achieved on each switch under all those conditions.

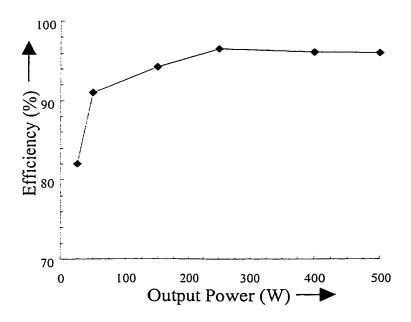

Fig. 2.9 shows the overall efficiency as a function of the output power. It is seen that, the efficiency is almost constant (>97%) over the range from 100% down to 50% rated load, but it will drop gradually below this range. This is because the conduction losses in the auxiliary circuit which are independent of the output load, become significant at reduced load.

Fig. 2.9 The overall efficiency as a function of output power. Operating conditions:  $f_s=128 \text{ kHz}$ ,  $V_o=55 \text{ V}$ ,  $V_d=390 \text{ V}$ .

## 2.6 Conclusions

The steady state analysis, simulation and experimental results have shown that the proposed ZVS full bridge dc/dc converter topology is advantageous in the following aspects:

- (i) It achieves ZVS independent of the line and load conditions, thereby overcoming the drawbacks in the existing soft switching full bridge converter topologies,

- (ii) It employs a simple auxiliary circuit that consists of passive components only; thus the control of the converter is not complicated,

- (iii) The power circuit is the same as a conventional full bridge converter. This makes the design and implementation of the proposed topology much easier.

In short, the proposed ZVS full bridge topology is an attractive solution for general applications of power level up to 3 kW.

•

## **CHAPTER 3**

## **DYNAMIC ANALYSIS**

#### 3.1 Introduction

The steady state analysis presented in the previous chapter assumed that the gating of the switches on each leg was in perfect symmetry. However, this symmetry is hardly true in reality. When the gating becomes asymmetrical, it will result in a dc voltage component in the output of the bridge legs, and this dc voltage may saturate the current sense transformer.

A simple solution to this problem is to insert a dc blocking capacitor between the bridge and the current sense transformer. However, a conventional opinion about the addition of this dc blocking capacitor is that PCMC is no longer applicable to the full bridge converter. In fact, this opinion is only true for the conventional PWM full bridge converter. This chapter will demonstrate that PCMC can still be used in the phase shift PWM full bridge converter.

To achieve the closed loop stability is another important issue. To reveal the dynamic properties of the proposed converter topology, the small signal model will be derived in this chapter using averaged state space equations.

Although the auxiliary circuit is critical in achieving ZVS of proposed topology, it just circulates the currents inside the auxiliary circuit and it hardly affects the power transfer of the converter. Thus, the auxiliary circuit has negligible influences on the dynamic properties of the power circuit, and it will be excluded from the discussion in the rest of this chapter.

In Sec. 3.2, the gating asymmetry and the flux imbalance in the current sense transformer will be addressed. In Sec. 3.3, the topology will be modified and analyzed, to overcome the gating asymmetry problem. The small signal model will be established in Sec. 3.4. The transfer

function for PCMC will be derived in Sec. 3.5 along with an example of the straightforward compensation to stabilize the closed loop. Simulation results will be presented in Sec. 3.6, followed by the conclusions.

#### 3.2 Flux Imbalance Problems

#### 3.2.1 Use of current transformer

Current transformer is usually used in the medium to high power level converters to replace the simple but lossy series resistor current sensor. In a current mode controlled converter, the current transformer serves efficiently as a current sensor that feeds back the sensed current information to the controller. In a voltage mode controlled converter, it is used for over current protection.

The current sense transformer is normally made from a small toroidal core. Because a toroidal core is unable to have an air gap, the current transformer can easily be saturated by a small dc voltage component. When saturation happens in the sensor, the control loop loses the feedback signal and the converter loses regulation that may destroy the precious loads it powers.

For the full bridge topology, the current sensor can be located either on the secondary side or on the primary side, and it is concluded in [19] that putting it on the primary side is advantageous mainly for smaller size and the input/output isolation. However, located on the primary side, it faces risks of saturation owing to the dc voltage in the output of the bridge legs.

#### 3.2.2 DC voltage component in the output of the bridge legs

In the proposed topology shown in Fig. 2.1, a dc voltage component may be present at the output of the bridge legs when the gating of the switches is not in perfect symmetry. This

asymmetry may be either static or dynamic. Although it is normally slight, the asymmetry is inevitable in any real converter because of the following major factors:

- (i) Random deviation of individual switches from each other in time response to gating signal due to product parameter spans;

- (ii) Unequal duty ratios and dead times between the switches on the two legs because of the manufacturing limitation of the control chips;

- (iii) Thermal effects on component parameters; and

- (iv) Sudden changes in the phase shift angle due to fast transients in the input voltage or output load.

When the dc voltage component exists, it could easily saturate the current sense transformer due to the aforementioned reasons.

## 3.2.3 PCMC protects the power transformer but not the current sense transformer

With PCMC, when flux imbalance in the power transformer occurs, no matter what the reason, the magnetizing current reflects this imbalance by showing a dc bias. Because the sensor sees the sum of the magnetizing current and the load current, this dc bias in the magnetizing current changes the arrival time of the peak of the sensed current. The arrival of the peak current commands the control circuit to adjust the phase shift angle. In this way the duration of magnetizing/demagnetizing period is adjusted such that the flux balance is re-established in the power transformer.

When the output of the bridge legs has a dc voltage component, the magnetizing current of the power transformer may have a dc bias. Unlike the small, non-air-gapped current censor transformer core, the power transformer usually has an air gapped core. This air gap stores the dc

magnetizing energy and keeps the core from saturation.

However, current sense transformer is still vulnerable to the dc voltage because it does not have an air gap to store any dc magnetizing energy.

## 3.3 Flux Balancing

## 3.3.1 Solution to the saturation problem of the current sense transformer

A direct solution to the saturation problem of the current sense transformer is to block this dc component by inserting a small capacitor in series with sensor and power transformers. This is illustrated in Fig. 3.1, where the dc blocking capacitor is labeled  $C_s$ . The capacitor  $C_s$  blocks the dc voltage component, thus eliminating the flux imbalance and preventing saturation.

Fig. 3.1 ZVS full bridge converter with dc blocking capacitor  $C_s$ .

However, the addition of the series dc blocking capacitor increases the reverse voltage stress on the output rectifier diodes. This problem comes from both the dc voltage and ripple voltages across the capacitor. Due to voltage superimposition, the dc voltage across the capacitor and its ripples will be alternatively added on top the input voltage in two consecutive half switching cycles. Then the power transformer will see the input voltage being increased by the voltage across the blocking capacitor. The increased voltage will be reflected into the secondary side, and it will increase the reverse voltage on the diodes in the rectification stage. To limit the voltage stress, a larger capacitor shall be used to suppress the ripple voltages. But a too large capacitor will be both expensive and bulky. A trade-off should be made to select the capacitor.

R. D. Middlebrook pointed out that in a conventional PWM full bridge converter PCMC can not be used along with the dc blocking capacitor. This can be explained as follows. Assume a positive dc voltage is built up across the blocking capacitor for whatever reasons, this voltage is deducted from the input voltage during the positive voltage pulse of one switching cycle. Thus the current slope is reduced and the peak current comes at a later time to expand the positive voltage pulse. Contrarily, the dc voltage across the blocking capacitor is added on top of the input voltage during the consecutive negative voltage pulse and it increases the current slope. Thus, the peak current comes at an earlier time and the negative voltage pulse is cut shorter. Because, during the rest of the cycle all switches are OFF and the capacitor sees an open circuit, there are residual charges left on the capacitor due to the unbalanced voltage pulses and this further increase the dc voltage across the capacitor. In the following cycle, the increased dc voltage will further expand the positive voltage pulse and decrease the negative voltage pulse. One cycle after another, the dc voltage across the capacitor increases continuously and it will eventually cut off the power flow from the input to the load.

However, in a phase shift PWM full bridge converter, the dc blocking capacitor will see the short circuit during the phase shift intervals. Because of the short circuit, any extra charges on the dc blocking capacitor will be discharged and the voltage across the capacitor will not run away from its equilibrium value after each cycle. Thus, PCMC can still be used along with the dc blocking capacitor. Detail analysis will be presented below.

## 3.3.2 Analysis of the dc voltage component

To be generic, the following assumptions are made:

(i) The duty ratios of the four switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  of the bridge in Fig. 2.1 are respectively  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$ ;

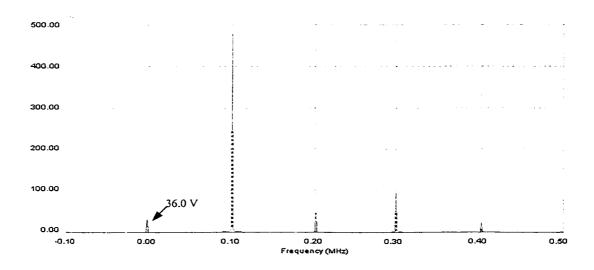

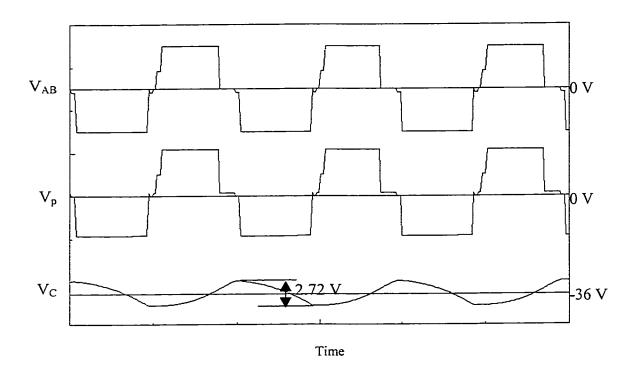

Fig. 3.2 Timing sequence of the asymmetrical gating pattern.  $v_B$  is the bridge output voltage,  $v_p$  is the voltage seen after the dc blocking capacitor.

- (ii) The dead time between the hind edge of  $D_1$  and front edge of  $D_2$  is  $d_1$ , and that between the hind edge of  $D_2$  and front edge of  $D_1$  is  $d_2$ ;

- (iii) The dead time between the hind edge of  $D_3$  and front edge of  $D_4$  is  $d_3$ , and that between the hind edge of  $D_4$  and front edge of  $D_3$  is  $d_4$ ;

- (iv) The phase shift angle, expressed as a fraction of a switching period, is  $\theta$ ; and

- (v) All dead times are very small as compared to the switching period,

Fig. 3.2 shows the time sequence of the asymmetrical gating signals and key waveforms.

Based on the above assumptions, there are the following relationships:

$$D_1 + d_1 + D_2 + d_2 = 1 (3-1)$$

$$D_3 + d_3 + D_4 + d_4 = 1 (3-2)$$

Therefore, the positive voltage pulse has a magnitude of  $V_d$ , and its pulse width as a fraction of a switching period is determined by

$$\Delta_{+} = D_1 - \theta \tag{3-3}$$

and the negative voltage pulse has a magnitude of  $-V_d$ , and its pulse width as a fraction of a switching period is determined by

$$\Delta_{-} = 1 - d_2 - (\theta + D_3 + d_3) \tag{3-4}$$

The dc voltage component of such periodical bipolar voltage pulses is determined by

$$V_{dc} = (\Delta_+ - \Delta_-)V_d \tag{3-5}$$

Substituting (3-3) and (3-4) into (3-5), and replacing the number "1" with (3-1) and (3-2), it yields

$$V_{dc} = \frac{D_1 - D_2 + D_3 - D_4 - d_1 + d_2 + d_3 - d_4}{2} V_d$$

(3-6)

In an ideal case the gating is in perfect symmetry, then there are  $D_1 = D_2 = D_3 = D_4$  and

$d_1=d_2=d_3=d_4$ . Thus, as seen from (3-6), there will be no dc voltage component in the output voltage of the bridge.

Unfortunately, the asymmetry of gating inevitably exists in reality because of the aforementioned factors. Therefore, as seen from (3-6), a dc voltage component may exist and it shall not be overlooked.

## 3.3.3 Flux balancing by adding a series dc blocking capacitor

As mentioned previously, if no corrective means is taken, the dc voltage given in (3-6) will appear across the series connected current sense transformer and power transformer, and eventually it will drive the current sensor into saturation, if it does not saturate the power transformer.

When a capacitor is put in series with the current sensor and power transformers, this capacitor will block the dc voltage component such that the transformers become blind to the dc voltage component, and this forces balanced flux excursion in the transformer cores.

When the dc blocking capacitor is used, as seen from Fig. 3.1, the positive and negative dc voltage pulses seen by the current sense transformer are governed respectively by

$$V_{+} = V_{d} - V_{dc} \tag{3-7}$$

$$V_{-} = -V_{d} - V_{dc} (3-8)$$

and they have the pulse widths determined by (3-3) and (3-4), respectively. During the silent intervals between these two pulses, the transformer sees a voltage of  $-V_{dc}$  for a total time of  $(1-\Delta_+-\Delta_-)$ . Hence volt-second products of the voltage pulses seen by the series connected transformers are:

## (i) Positive voltage pulse volt-second product:

$$V_{+} \cdot \Delta_{+} \cdot T_{s} = V_{d} \Delta_{+} T_{s} - V_{dc} \Delta_{+} T_{s} \tag{3-9}$$

(ii) Negative voltage pulse volt-second product:

$$V_{-} \cdot \Delta_{-} \cdot T_{s} = -V_{d} \Delta_{-} T_{s} - V_{dc} \Delta_{-} T_{s} \tag{3-10}$$

(iii) Silent intervals volt-second product:

$$-V_{dc} \cdot (1 - \Delta_{+} - \Delta_{-}) \cdot T_{s} = -V_{dc}T_{s} + V_{dc}\Delta_{+}T_{s} + V_{dc}\Delta_{-}T_{s}$$

(3-11)

where  $T_s$  is the period of a switch cycle.

The total volt-second product in one cycle is the sum of above three equations. Substituting (3-5) into the summation, it yields zero. This means a balanced volt-second product in one cycle. Because the sensor and power transformers are in series, then both of their magnetizing inductors have a balanced volt-second product, or balanced flux excursion. In other words, this achieves flux balancing in the current sense transformer and prevents it from possible saturation.

#### 3.4 Small Signal Model

## 3.4.1 Modes of operation and the equivalent circuits

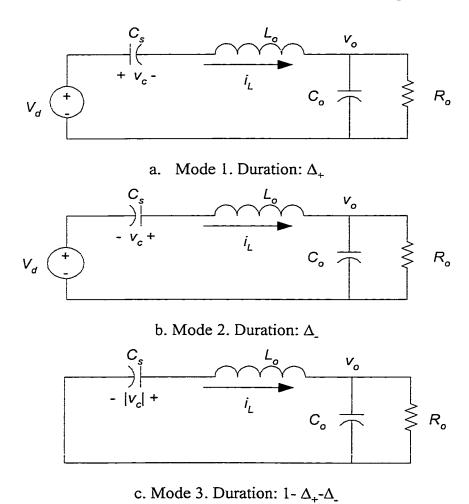

As stated previously, the circuit operation seen from the secondary side has three distinct modes when the converter is in CCM. Specifically in these three modes, the output stage sees respectively, (i) a positive input voltage when both  $S_1$  and  $S_3$  are ON and  $D_{o1}$  is conducting, (ii) a positive input voltage when both  $S_2$  and  $S_4$  are ON and  $D_{o2}$  is conducting, and (iii) a positive voltage across  $C_s$  in the rest of the switching cycle. In all three modes, the effects of the current sense transformer is ignored because it is equivalent to a negligible resistor due to the high turns ratio of the current transformer.

Fig. 3.3 shows equivalent output circuits of these three modes seen on the secondary side of the power transformer. When  $D_{o1}$  and  $D_{o2}$  conduct in Modes 1 and 2 respectively, the output inductor sees different end of  $C_s$ ; thus  $C_s$  flips its direction in Modes 1 and 2.

It is noticed that the equivalent circuit of Mode 3 uses the absolute voltage of  $C_s$ . It is because when the actual dc voltage across  $C_s$  is positive,  $D_{o1}$  will conduct in this mode, and when it is negative,  $D_{o2}$  will conduct. Thus the dc voltage across  $C_s$  seen by the output inductor is always positive in Mode 3.

A unity turns ratio k is assumed for convenience in the following discussion.

Fig. 3.3 Equivalent circuits in three different modes each switching cycle.

#### 3.4.2 State space equations

#### A. Mode I

In this mode both  $S_1$  and  $S_3$  are ON, and  $D_{o1}$  is conducting while  $D_{o2}$  is blocked. Thus the state space equations for this mode are as follows.

$$\begin{bmatrix}

\frac{di_L}{dt} \\

\frac{dv_o}{dt} \\

\frac{dv_c}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_o} & -\frac{1}{L_o} \\

\frac{1}{C_o} & -\frac{1}{R_oC_o} & 0 \\

\frac{1}{C_s} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_L \\ v_o \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L_o} \\ 0 \\ 0 \end{bmatrix} \cdot V_d$$

(3-12)

The duration of this mode is  $\Delta_+$  that is determined by (3-3).

#### B. Mode 2

In this mode both  $S_2$  and  $S_4$  are ON, and  $D_{o2}$  is conducting while  $D_{o1}$  is blocked. Thus the state space equations for this mode are defined by

$$\begin{bmatrix}

\frac{di_L}{dt} \\

\frac{dv_o}{dt} \\

\frac{dv_c}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_o} & \frac{1}{L_o} \\

\frac{1}{C_o} & -\frac{1}{R_o C_o} & 0 \\

-\frac{1}{C_s} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_L \\ v_o \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L_o} \\ 0 \\ 0 \end{bmatrix} \cdot V_d$$

(3-13)

The duration of this mode is  $\Delta$  that is determined by (3-4).

#### C. Mode 3

In this mode either  $S_1$  and  $S_4$ , or  $S_2$  and  $S_3$ , are both ON. Then the bridge output voltage is zero. Due to CCM either  $D_{o1}$  or  $D_{o2}$  (but not both if the dc voltage across  $C_s$  is not zero) must conduct to continue the output inductor current  $i_L$ , depending on the polarity of the voltage across  $C_s$ . Generally, the state space equations for this mode can be expressed as

$$\begin{bmatrix}

\frac{di_L}{dt} \\

\frac{dv_o}{dt} \\

\frac{d|v_c|}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_o} & \frac{1}{L_o} \\

\frac{1}{C_o} & -\frac{1}{R_o C_o} & 0 \\

-\frac{1}{C_c} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_L \\ v_o \\ |v_c| \end{bmatrix}$$

(3-14)

The duration of this mode is  $1-\Delta_{+}-\Delta_{-}$

## 3.4.3 Averaged state space equations

For each cycle, the averaged state space equations are obtained by weighted summing of (3-12) (3-13) and (3-14), i.e. by applying (3-12)  $\cdot \Delta_{+} + (3-13) \cdot \Delta_{-} + (3-14) \cdot (1-\Delta_{+} - \Delta_{-})$ . This yields:

$$\begin{bmatrix}

\frac{di_{L}}{dt} \\

\frac{dv_{o}}{dt} \\

\frac{dv_{c}}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_{o}} & \frac{1-2\Delta_{+}}{L_{o}} \\

\frac{1}{C_{o}} & -\frac{1}{R_{o}C_{o}} & 0 \\

\frac{2\Delta_{+}-1}{C_{s}} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_{L} \\ v_{o} \\ v_{c} \end{bmatrix} + \begin{bmatrix} \Delta_{+}+\Delta_{-} \\ 0 \\ 0 \end{bmatrix} \cdot V_{d} \qquad if \quad V_{dc} \ge 0$$

$$\begin{bmatrix}

\frac{di_{L}}{dt} \\

\frac{dv_{o}}{dt} \\

\frac{dv_{o}}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_{o}} & \frac{2\Delta_{-}-1}{L_{o}} \\

\frac{1}{C_{o}} & -\frac{1}{R_{o}C_{o}} & 0 \\

\frac{1-2\Delta_{-}}{C_{s}} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_{L} \\ v_{o} \\ v_{c} \end{bmatrix} + \begin{bmatrix} \Delta_{+}+\Delta_{-} \\ -\frac{1}{L_{o}} \\ 0 \\ 0 \end{bmatrix} \cdot V_{d} \qquad if \quad V_{dc} < 0$$

(3-15)

In the following only the case of  $V_{dc} \ge 0$  is discussed. The other case can be easily analyzed following a similar procedure and the results are similar.

Defining the following two constants

$$\alpha = 1 + D_1 - d_2 - D_3 - d_3 \tag{3-16}$$

$$\beta = 1 - 2D_1 \tag{3-17}$$

Substituting (3-3), (3-4) into (3-15), and using above two constants to simplify the results, it yields:

$$\begin{bmatrix}

\frac{di_L}{dt} \\

\frac{dv_o}{dt} \\

\frac{dv_c}{dt}

\end{bmatrix} = \begin{bmatrix}

0 & -\frac{1}{L_o} & \frac{\beta + 2\theta}{L_o} \\

\frac{1}{C_o} & -\frac{1}{R_o C_o} & 0 \\

-\frac{\beta + 2\theta}{C_s} & 0 & 0

\end{bmatrix} \cdot \begin{bmatrix} i_L \\ v_o \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{\alpha - 2\theta}{L_o} \\ 0 \\ 0 \end{bmatrix} \cdot V_d \tag{3-18}$$

#### 3.4.4 DC and AC models

Decomposing each variable into DC and AC components, i.e.,

$$\begin{cases} v_o \to V_o + \widetilde{v}_o \\ i_L \to I_L + \widetilde{i}_L \\ \theta \to \theta + \widetilde{\vartheta} \\ V_d \to V_d + \widetilde{v}_d \\ v_c \to V_{dc} + \widetilde{v}_c \end{cases}$$

(3-19)

Substituting (3-19) into (3-18), and rearranging the result, it yields:

$$\begin{cases}

L_o \frac{d\tilde{i}_L}{dt} = -(V_o + \tilde{v}_o) + (\alpha - 2\theta - 2\tilde{\vartheta})(V_d + \tilde{v}_d) + (\beta + 2\theta + 2\tilde{\vartheta})(V_{dc} + \tilde{v}_c) \\

C_o \frac{d\tilde{v}_o}{dt} = (I_L + \tilde{i}_L) - \frac{1}{R_o}(V_o + \tilde{v}_o) \\

C_s \frac{d\tilde{v}_c}{dt} = -(\beta + 2\theta + 2\tilde{\vartheta})(I_L + \tilde{i}_L)

\end{cases}$$

(3-20)

#### A. DC model

From (3-20), the DC model of the circuit is obtained as:

$$\begin{cases} V_o = (\alpha - 2\theta)V_d + (\beta + 2\theta)V_{dc} \\ I_L = \frac{V_o}{R_o} \end{cases}$$

(3-21)

#### B. AC model

Also from (3-20), the AC model is obtained as:

$$\begin{cases}

L_o \frac{d\widetilde{i}_L}{dt} = -\widetilde{v}_o + (\alpha - 2\theta)\widetilde{v}_d - 2(V_d - V_{dc})\widetilde{\vartheta} + (\beta + 2\theta)\widetilde{v}_c - 2(\widetilde{v}_d - \widetilde{v}_c)\widetilde{\vartheta} \\

C_o \frac{d\widetilde{v}_o}{dt} = \widetilde{i}_L - \frac{1}{R_o}\widetilde{v}_o

\end{cases}$$

$$C_s \frac{d\widetilde{v}_c}{dt} = -(\beta + 2\theta)\widetilde{i}_L - 2I_L\widetilde{\vartheta} - 2\widetilde{i}_L\widetilde{\vartheta}$$

(3-22)

## 3.4.5 Small signal model

Under small perturbations or seeking the small signal model, the second order terms in the AC model are ignored; thus the small signal model of the proposed converter topology is given as:

$$\begin{cases} L_o \frac{d\widetilde{i}_L}{dt} = -\widetilde{v}_o + (\alpha - 2\theta)\widetilde{v}_d - 2(V_d - V_{dc})\widetilde{\vartheta} + (\beta + 2\theta)\widetilde{v}_c \\ C_o \frac{d\widetilde{v}_o}{dt} = \widetilde{i}_L - \frac{1}{R_o}\widetilde{v}_o \end{cases}$$

$$(3-23)$$

$$C_s \frac{d\widetilde{v}_c}{dt} = -(\beta + 2\theta)\widetilde{i}_L - 2I_L\widetilde{\vartheta}$$

## 3.5 Transfer Function of the Power Circuit in the PCMC and Loop Compensation

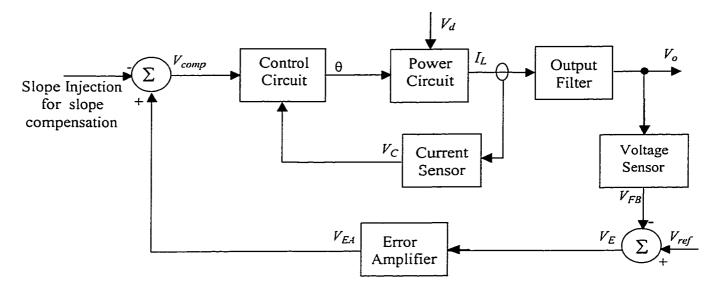

# 3.5.1 PCMC versus the Voltage Mode Control (VMC) and the Averaged Current Mode Control (ACMC)

PCMC is the most popular control technique for full bridge converter topology. In addition to its protection of the power transformer from saturation, PCMC inherently has the function of voltage feed forward control. For instance, as soon as the input voltage has a step up change the slope of the inductor current will be increased at once. The current sensor will directly detect the change of slope of the sensed current, and it sees that the peak of the current

comes at an earlier time. This commands the control circuit to increase the phase shift angle immediately. The increased phase shift angle reduces the effective duty ratio of the switches, cutting off the possible overflow of energy to the output and thus keeping the output voltage at the regulated point. Similarly, as the input voltage steps down, the control circuit directly detects the change via the sensed current and decreases the phase shift angle immediately. This increases the effective duty ratio to regulate the output voltage. In this way, the output regulation against the input voltage variations is fulfilled before the output voltage is actually affected.

Contrarily VMC does not have the voltage feed forward function, and the output regulation against the input voltage variations is comparatively slow. Because the controller can only detect the input variations after the output voltage has already been affected, and adjustment of the phase shift angle can only be made after the detection. Therefore it is concluded that current mode control is faster than VMC.