#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

|  |  | • |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# AN AC-AC INVERTER FOR HIGH FREQUENCY POWER DISTRIBUTION SYSTEM

Guo Wennan

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada

December 2000

© Guo Wennan, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-59305-3

#### **ABSTRACT**

#### AN AC-AC INVERTER FOR HIGH FREQUENCY POWER DISTRIBUTION SYSTEM

#### Guo Wennan

Future computer and telecommunication power distribution systems require the power source to be high frequency ac type and be combined with line current Power Factor Correction that satisfies IEC 1000-3-2 standard. In addition, low power applications require high efficiency, high power density and cost effectiveness. This thesis provides a solution to low power ac-ac inverter for the future computer and telecommunication power distribution systems, which complies with the above requirements.

The proposed high frequency ac-ac inverter operates under Zero Voltage Switching (ZVS) throughout the whole range of the line voltage and load. Hence, high efficiency can be realized under high switching frequency. A unified controller is introduced in the proposed ac-ac inverter to control the dc-ac stage and the PFC stage at the same time. The controller is simple and the DC bus voltage can be well limited for all line and load conditions. Hence, cost effectiveness can be realized.

In the thesis, two types of PFC stage converters (Boost and Buckboost) are presented to compare the performance of the ac-ac inverter. Principle of operation and steady state analysis of the proposed topology are given. Performance characteristics, design procedures and computer simulation results are presented to guide the design. Experimental results from a prototype of 100kHz, 30V<sub>ac</sub>/250W output, 90-265V<sub>ac</sub> input, are presented to confirm the analysis and performance of the proposed ac-ac inverter.

#### **ACKNOWLEDGEMENTS**

I wish to express my deep gratitude to my supervisor Dr. Praveen K. Jain for his invaluable guidance, advice and financial support throughout the course of this work. I would also like to thank Dr. Geza Joos for his sincere help during the course of my study.

I would like to thank my colleagues in the P. D. Ziogas Power Electronics Laboratory. Smart suggestions and witty comments from Humberto Pinheiro are unforgettable. Technical assistance from Joe Woods acclerated my experiment. Friendship and helpful discussions with Youhao Xi, Gerry, Mei, Simmi, Wen, Su Chen, Kalil, Dheeraj and Fariborz meant a lot during my study and research in the Power Electronics Lab.

Financial support received from the Natural Sciences and Engineering Research Council of Canada is also greatly appreciated.

Finally, I would like to express my thanks to my wife and my parents for their love, support and encouragement during these years.

# **TABLE OF CONTENTS**

| List of Figures                                            | ıx    |

|------------------------------------------------------------|-------|

| LIST OF TABLES                                             | XVI   |

| LIST OF ACRONYMS                                           | XVII  |

| LIST OF PRINCIPLE SYMBOLS                                  | XVIII |

| CHAPTER 1 INTRODUCTION                                     | 1     |

| 1.1 General                                                | 1     |

| 1.2 Problem Definition                                     | 2     |

| 1.2.1 Power Factor Correction                              | 2     |

| 1.2.2 Efficiency and Constant Frequency Resonant Technique | 6     |

| 1.3 Proposed Topology                                      | 8     |

| 1.4 Thesis Objective                                       | 9     |

| 1.5 Thesis Outline                                         | 9     |

| CHAPTER 2 BOOST IMPLEMENTED PFC                            | 11    |

| 2.1 Introduction                                           | 11    |

| 2.2 DESCRIPTION OF PROPOSED TOPOLOGY                       | 12    |

| 2.3 Principle of Operation                                 | 14    |

| 2.4 Steady State Analysis                                  | 19    |

| 2.4.1 Duty Cycle and DC Bus Voltage                        | 19    |

| 2.4.2 Peak Current of the Converter                        | 21    |

| 2.4.3 Boundary between DCM and CCM                                  | 23 |

|---------------------------------------------------------------------|----|

| 2.4.4 Input Current Power Factor                                    | 24 |

| 2.5 Performance Characteristics                                     | 24 |

| 2.5.1 Effect of Load on Performance                                 | 25 |

| 2.5.2 Effect of Transformer Turn Ratio on Performance               | 26 |

| 2.5.3 Effect of Input Inductor L <sub>in</sub> on Performance       | 27 |

| 2.5.4 Effect of Gate Signal Constant m on Performance               | 28 |

| 2.6 SIMULATION AND EXPERIMENTAL VERIFICATIONS                       | 31 |

| 2.6.1 Simulation Waveforms                                          | 31 |

| 2.6.2 Experimental Waveforms                                        | 35 |

| 2.6.3 Comparison of Experiment, Simulation and Theoretical Analysis | 38 |

| 2.7 CONCLUSION                                                      | 40 |

| CHAPTER 3 BUCKBOOST IMPLEMENTED PFC                                 | 41 |

| 3.1 Introduction                                                    | 41 |

| 3.2 Principle of Operation                                          | 42 |

| 3.3 Steady State Analysis                                           | 45 |

| 3.3.1 Duty Cycle and DC Bus Voltage                                 | 45 |

| 3.3.2 Peak Current of the Converter                                 | 48 |

| 3.3.3 Boundary between DCM and CCM                                  | 48 |

| 3.4 PERFORMANCE CHARACTERISTICS                                     | 49 |

| 3.4.1 Effect of Load on Performance                                 | 49 |

| 3.4.2 Effect of Transformer Turn Ratio on Performance               | 50 |

| 3.4.3 Effect of m on Performance                        | 52       |

|---------------------------------------------------------|----------|

| 3.5 SIMULATION AND EXPERIMENTAL VERIFICATION            | 55       |

| 3.5.1 Simulation Results                                | 55       |

| 3.5.2 Experimental Results                              | 57       |

| 3.6 CONCLUSION                                          | 59       |

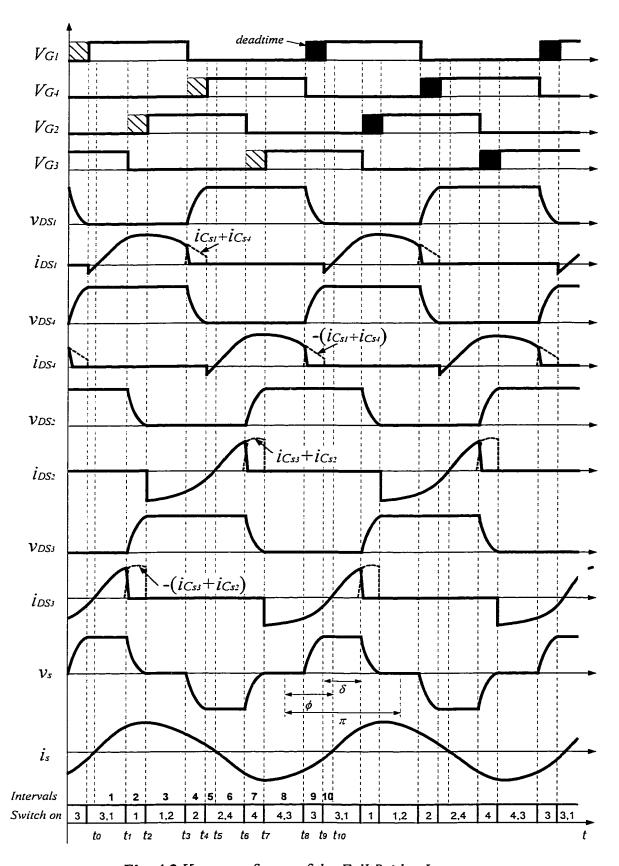

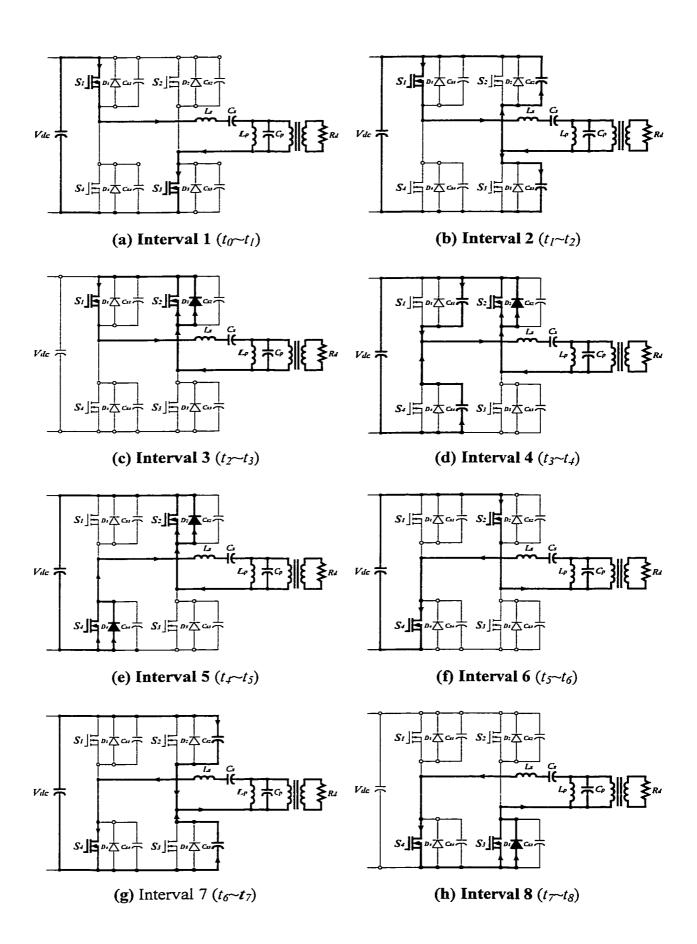

| CHAPTER 4 FULL BRIDGE ZVS RESONANT INVERTER             | 60       |

| 4.1 Introduction                                        | 60       |

| 4.2 PRINCIPLE OF OPERATION                              | 61       |

| 4.3 Modes of Operation                                  | 65       |

| 4.4 STEADY STATE ANALYSIS                               | 68       |

| 4.5 PERFORMANCE CHARACTERISTICS                         | 77       |

| 4.5.1 Minimum Phase-shift Angle                         | 77       |

| 4.5.2 Circulating Current                               | 78       |

| 4.5.3 Total Harmonic Distortion of the Output Voltage   | 79       |

| 4.5.4 The Effect of Transformer Location on Performance | 81       |

| 4.6 SIMULATION AND EXPERIMENTAL VERIFICATIONS           | 83       |

| 4.6.1 Simulation Waveforms                              | 83       |

| 4.6.2 Experimental Results                              | 86       |

| CHAPTER 5 DESIGN PROCEDURES AND EXAMPLES                | 89       |

| 5.1 DESIGN SPECIFICATIONS                               | 89       |

| 5.2 Design Procedure                                    | on<br>on |

| 5.2.1 Determination of Gate Signal Constant $m_2$ and Inductor $L_{in}$ | 90  |

|-------------------------------------------------------------------------|-----|

| 5.2.2 Determination of Key Constants $k_1$ , $k_2$ and $k_3$            | 91  |

| 5.2.3 Determination of Resonant Components:                             | 92  |

| 5.2.4 Rating of Resonant Components:                                    | 92  |

| 5.2.5 Current Rating of switches:                                       | 93  |

| 5.2.6 Determination of boost diode and switch                           | 93  |

| 5.2.7 Determination of boost inductor                                   | 94  |

| 5.2.8 Implementation of Control Circuits                                | 94  |

| 5.3 DESIGN EXAMPLES                                                     | 94  |

| CHAPTER 6 CONCLUSIONS                                                   | 96  |

| 6.1 SUMMARY                                                             | 96  |

| 6.2 Contributions                                                       | 97  |

| 6.3 Suggestions For Future Work                                         | 97  |

| REFERENCE                                                               | 98  |

| APPENDIX                                                                | 102 |

| A1. OUTPUT VOLTAGE OF RESONANT NETWORK                                  | 102 |

| A2. Transformer Design                                                  | 104 |

| A3. RESONANT INDUCTOR DESIGN                                            | 107 |

| A4 BOOST AND BUCKBOOST INDUCTOR DESIGN                                  | 113 |

# **LIST OF FIGURES**

| Fig. 1.1 Block Diagram of conventional Two-Stage PFC converters                                | 2                |

|------------------------------------------------------------------------------------------------|------------------|

| Fig. 1.2 Block diagram of Single-Stage PFC converters                                          | 3                |

| Fig. 1.3 DC bus voltage as a function of load for different line input voltage                 | 5                |

| Fig. 1.4 DC bus voltage as a function of load for universal line voltage                       | 6                |

| Fig. 1.5 Block diagram for proposed PFC high frequency ac-ac inverter                          | 8                |

| Fig. 2.1 Proposed high frequency ac-ac inverter with boost PFC                                 | 12               |

| Fig. 2.2 Gate signals generated by the <i>Unified Controller</i>                               | 14               |

| Fig. 2.3 Boost Converter after Diode Rectifier with equivalent load                            | 15               |

| Fig. 2.4 Equivalent circuit for interval one                                                   | 15               |

| Fig. 2.5 Equivalent circuits for interval two                                                  | 16               |

| Fig. 2.6 Equivalent circuits for interval three                                                | 16               |

| Fig. 2.7 Key waveforms of the Boost PFC stage                                                  | 17               |

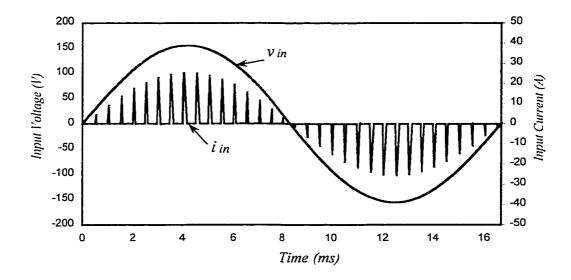

| Fig. 2.8 Simulated input line voltage and current with 2kHz switching frequency                | 18               |

| Fig. 2.9 Simulated low frequency harmonic spectrum of the input current                        | 18               |

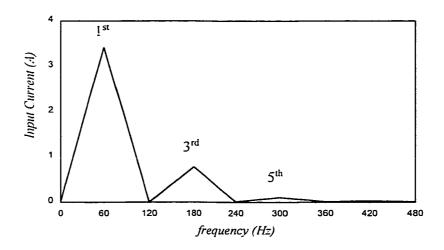

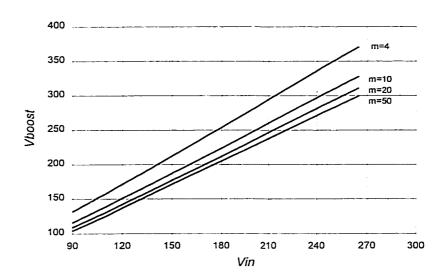

| Fig. 2.10 DC bus voltage versus input voltage for various loads (at $V_o=30V_{ac}$ , $f_{sw}=$ | 100 <i>KHz</i> , |

| $N=4, L_{in}=30uH, m=4)$                                                                       | 25               |

| Fig. 2.11 Duty cycle versus input voltage for various loads (at $V_o=30V_{ac}$ , $f_{sw}=100KHz$          |

|-----------------------------------------------------------------------------------------------------------|

| $N=4, L_{in}=30uH, m=4)$ 26                                                                               |

| Fig. 2.12 DC bus voltage versus input voltage for various transformer turn ratio (a                       |

| $V_o=30V_{ac}, f_{sw}=100KHz, R_d=3.6\Omega, L_{in}=30uH, m=4)$                                           |

| Fig. 2.13 Duty cycle versus input voltage for various transformer turn ratio (at $V_o=30V_{ac}$           |

| $f_{sw}=100KHz, R_d=3.6\Omega, L_{in}=30uH, m=4)$                                                         |

| Fig. 2.14 Maximum input peak current versus input voltage for various $L_{in}$ (at $V_o=30V_{ac}$         |

| $f_{sw}=100KHz, R_d=3.6\Omega, N=4, m=4)$ 28                                                              |

| Fig. 2.15 DC bus voltage versus input voltage for various $L_{in}$ (at $V_o=30V_{ac}$ , $f_{sw}=100KHz$ ) |

| $R_d = 3.6\Omega, N = 4, m = 4$ )                                                                         |

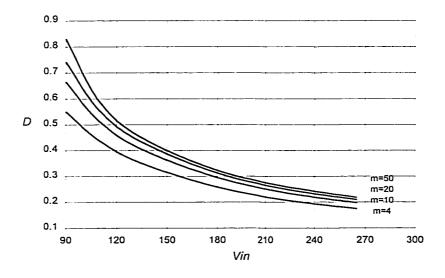

| Fig. 2.16 DC bus voltage versus input voltage for various $m$ at rated load (at $V_o=30V_{ac}$            |

| $f_{sw}$ =100KHz, $R_d$ =3.6 $\Omega$ , $L_{in}$ =30 $u$ H, $N$ =4)                                       |

| Fig. 2.17 Duty cycle versus input voltage for various $m$ at rated load (at $V_o=30V_{ac}$                |

| $f_{sw}$ =100KHz, $R_d$ =3.6 $\Omega$ , $L_{in}$ =30 $u$ H, $N$ =4)                                       |

| Fig. 2.18 DC bus voltage versus input voltage for various $m$ at 10% rated load (at                       |

| $V_o = 30V_{ac}, f_{sw} = 100KHz, R_d = 36\Omega, L_{in} = 30uH, N = 4$ )30                               |

| Fig. 2.19 Duty cycle versus input voltage for various $m$ at 10% rated load (at $V_o=30V_{ac}$            |

| $f_{sw}=100KHz, R_d=36\Omega, L_{in}=30uH, N=4)$                                                          |

| Fig. 2.20 Input Power Factor as a function of input voltage for various $m$ (at $V_o=30V_{ac}$            |

| $f_{sw}=100KHz, R_d=3.6\Omega, L_{in}=15uH, N=4)$                                                         |

| Fig. 2.21 (a) Simulation waveform of the boost inductor current; (b) Simulation waveform            |

|-----------------------------------------------------------------------------------------------------|

| of the filtered input current32                                                                     |

| Fig. 2.22 (a) Simulated high frequency harmonic spectrum of the boost inductor current;             |

| (b) Simulated high frequency harmonic spectrum of the filtered line current32                       |

| Fig. 2.23 (a) Simulated low frequency harmonic spectrum of the boost inductor current; (b)          |

| Simulated low frequency harmonic spectrum of the filtered line current33                            |

| Fig. 2.24 (a) Simulation waveform of the gate signal of the Boost Converter; (b)                    |

| Simulation waveform of the boost inductor current after zoom; (c) Simulation                        |

| waveform of the voltage across the boost switch; (d) Simulation waveform of the                     |

| voltage across the boost diode33                                                                    |

| Fig. 2.25 (a) Simulated frequency spectrum of input current times input voltage; (b)                |

| Simulated frequency spectrum of output put current times output voltage34                           |

| Fig. 2.26 Experimental waveform of the line current without the <i>Input Filter</i> (at $110V_{ac}$ |

| input, 250W output)                                                                                 |

| Fig. 2.27 Measured frequency harmonic spectrum of the unfiltered line current (at $110V_{ac}$       |

| input, 250W output)                                                                                 |

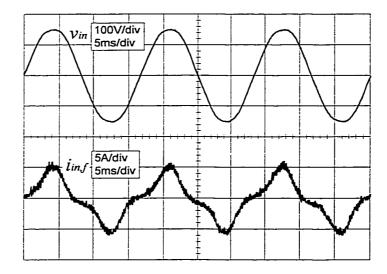

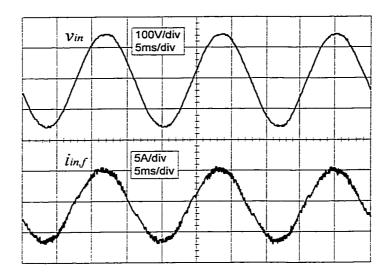

| Fig. 2.28 Experimental waveforms of the line voltage and the filtered line current (at              |

| 110V <sub>ac</sub> input, 250W output power)36                                                      |

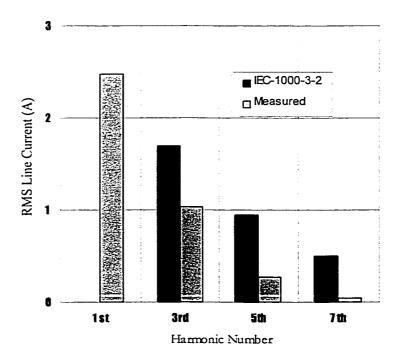

| Fig. 2.29 Measured harmonics of the unfiltered line current compared with IEC 1000-3-2              |

| limits36                                                                                            |

| Fig. 2.30 Measured DC bus voltage versus load for various line voltage                              |

| Fig. 2.31 Measured overall effi                     | iciency                                                              | 38                         |

|-----------------------------------------------------|----------------------------------------------------------------------|----------------------------|

| Fig. 2.32. Measured dc bus                          | voltage versus theoretical calculation at $110V_{ac}$ inpu           | ut and                     |

| 100% output power                                   |                                                                      | 39                         |

| Fig. 3.1 Proposed high frequen                      | ncy ac-ac inverter with buckboost PFC                                | 42                         |

| Fig. 3.2 Buckboost converter a                      | after Diode Rectifier with equivalent load                           | 43                         |

| Fig. 3.3 Equivalent circuits of                     | buckboost during interval one                                        | 43                         |

| Fig. 3.4 Equivalent circuits of                     | buckboost during interval two                                        | 44                         |

| Fig. 3.5 Equivalent circuits of                     | buckboost during interval three                                      | 44                         |

| Fig. 3.6 Key waveforms of the                       | Buckboost Converter                                                  | 45                         |

| Fig. 3.7 DC bus voltage versus                      | is input voltage for various loads (at $V_o=30V_{ac}$ , $f_{sw}=100$ | 0 <i>KHz</i> ,             |

| $N=3, L_{in}=20uH, m=2)$                            |                                                                      | 50                         |

| Fig. 3.8 Duty cycle versus inp                      | out voltage for various load (at $V_o=30V_{ac}$ , $f_{sw}=100KHz$ ,  | , <i>N</i> =3,             |

| $L_{in}=20uH, m=2)$                                 |                                                                      | 50                         |

| Fig. 3.9 DC bus voltage ver                         | rsus input voltage for various transformer turn rat                  | io (at                     |

| $V_o = 30 V_{ac}, f_{sw} = 100 KHz,$                | $R_d=3.6\Omega, L_{in}=20uH, m=2)$                                   | 51                         |

| Fig. 3.10 Duty cycle versus in                      | nput voltage for various transformer turn ratio (at $V_o$ =1         | 30 <i>V<sub>ac</sub></i> , |

| $f_{sw}=100KHz$ , $R_d=3.6\Omega$ , $R_d=3.6\Omega$ | <i>L<sub>in</sub></i> =20 <i>uH</i> , <i>m</i> =2)                   | 51                         |

| Fig. 3.11 DC bus voltage vers                       | sus input voltage for various $m$ at rated load (at $V_o$ =1         | $30V_{ac}$                 |

| $f_{sw}$ =100KHz, $R_d$ =3.6 $\Omega$ , $R_d$       | <i>L<sub>in</sub></i> =20 <i>uH</i> , <i>N</i> =3)                   | 52                         |

| Fig. 3.12 Duty cycle versus                         | input voltage for various $m$ at rated load (at $V_o$ =              | $30V_{ac}$ ,               |

| $f_{\text{cw}}=100KHz$ , $R=3.6\Omega$ .            | $L_{in}$ =20 <i>uH</i> , <i>N</i> =3)                                | 53                         |

| Fig. 3.13 DC bus voltage versus input voltage for various $m$ at 10% rated load (at                    |

|--------------------------------------------------------------------------------------------------------|

| $V_o=30V_{ac}, f_{sw}=100KHz, R_d=36\Omega, L_{in}=20uH, N=3)$                                         |

| Fig. 3.14 Duty cycle versus input voltage for various $m$ at 10% rated load (at $V_o=30V_{ac}$ ,       |

| $f_{sw}=100KHz, R_d=36\Omega, L_{in}=30uH, N=3)$                                                       |

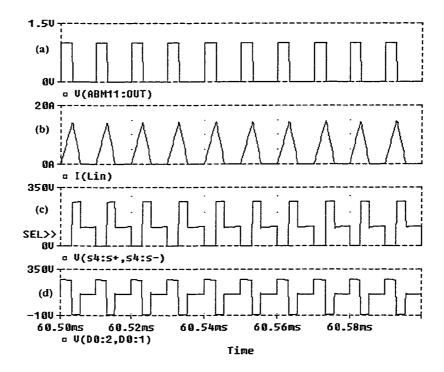

| Fig. 3.15 (a) Simulation waveform of the buckboost inductor current; (b) Simulation                    |

| waveform of the filtered input current55                                                               |

| Fig. 3.16 (a) Simulation waveform of the Buckboost Converter gate signal; (b) Simulation               |

| waveform of the buckboost inductor current after zoom; (c) Simulation waveform                         |

| of the voltage across the buckboost switch; (d) Simulation waveform of the voltage                     |

| across the buckboost diode56                                                                           |

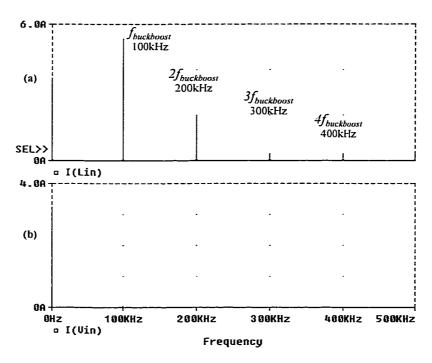

| Fig. 3.17 (a) Simulated high frequency harmonic spectrum of the buckboost inductor                     |

| current; (b) Simulated high frequency harmonic spectrum of the filtered line current56                 |

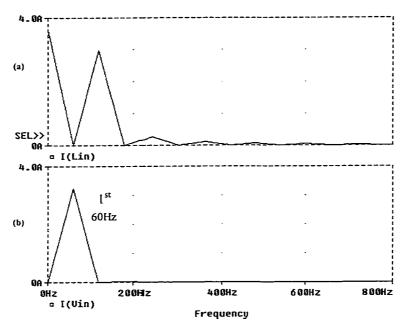

| Fig. 3.18 (a) Simulated low frequency harmonic spectrum of the buckboost inductor                      |

| current; (b) Simulated low frequency harmonic spectrum of the filtered line current57                  |

| Fig. 3.19 Measured harmonics of unfiltered line current                                                |

| Fig. 3.20 Experimental waveforms of line voltage and filtered line current (at 110V <sub>ac</sub> line |

| input and 250W output)58                                                                               |

| Fig. 4.1 Proposed high frequency full bridge inverter                                                  |

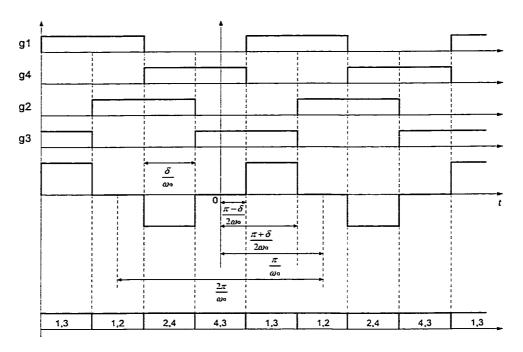

| Fig. 4.2 Key waveforms of the Full Bridge Inverter                                                     |

| Fig. 4.3 Current paths of the inverter during various intervals corresponding to the key               |

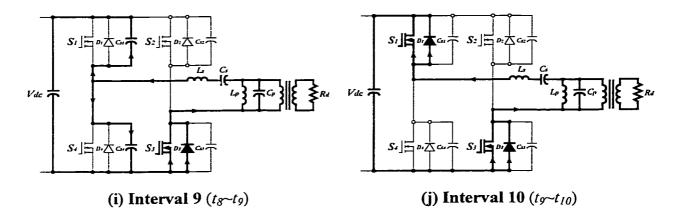

| waveforms given in Fig. 4.2                                                                            |

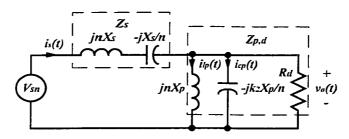

| Fig. 4.4 n <sup>th</sup> harmonic equivalent circuit (per unit) of the inverter                                   |

|-------------------------------------------------------------------------------------------------------------------|

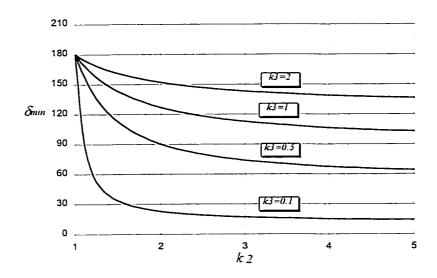

| Fig. 4.5 Minimum phase shift-angle $\delta_{min}$ (degree) versus $k_2$ for various $k_3$                         |

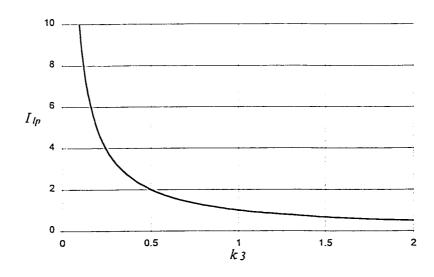

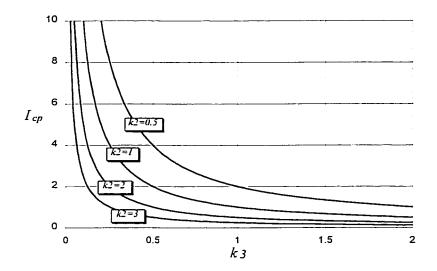

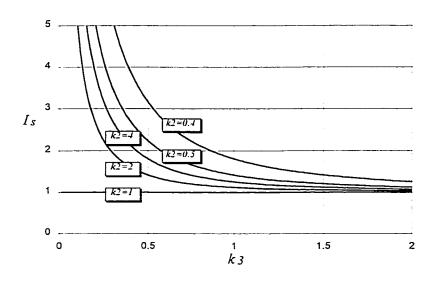

| Fig. 4.6 Circulating current (per unit) through parallel inductor $L_p$ versus $k_3$                              |

| Fig. 4.7 Circulating current (per unit) through capacitor $C_p$ versus $k_3$ for various $k_2$ 79                 |

| Fig. 4.8 Current (per unit) through series branch versus $k_3$ for various $k_2$                                  |

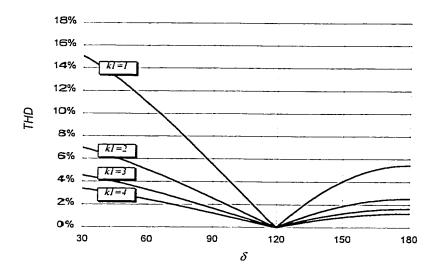

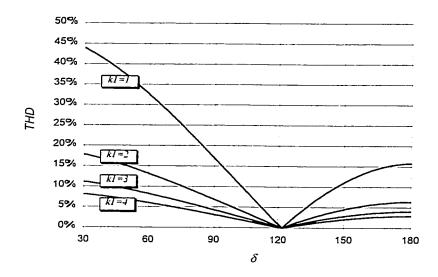

| Fig. 4.9 THD as function of phase-shift angle $\delta$ for various $k_l$ (at $k_2$ =1)80                          |

| Fig. 4.10 THD as function of phase shift-angle $\delta$ for various $k_1$ (at $k_2$ =2)80                         |

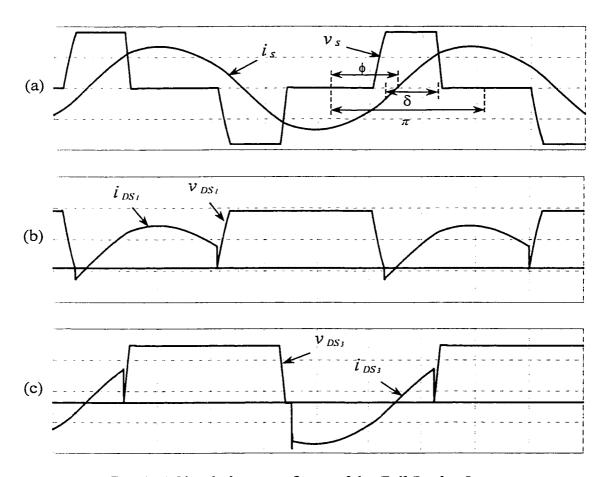

| Fig. 4.11 Simulation waveforms of the Full Bridge Inverter (a) Output voltage and current                         |

| of the Full Bridge Inverter; (b) Drain to source voltage and current of switch $S_l$ ; (c)                        |

| Drain to source voltage and current of switch $S_3$ 83                                                            |

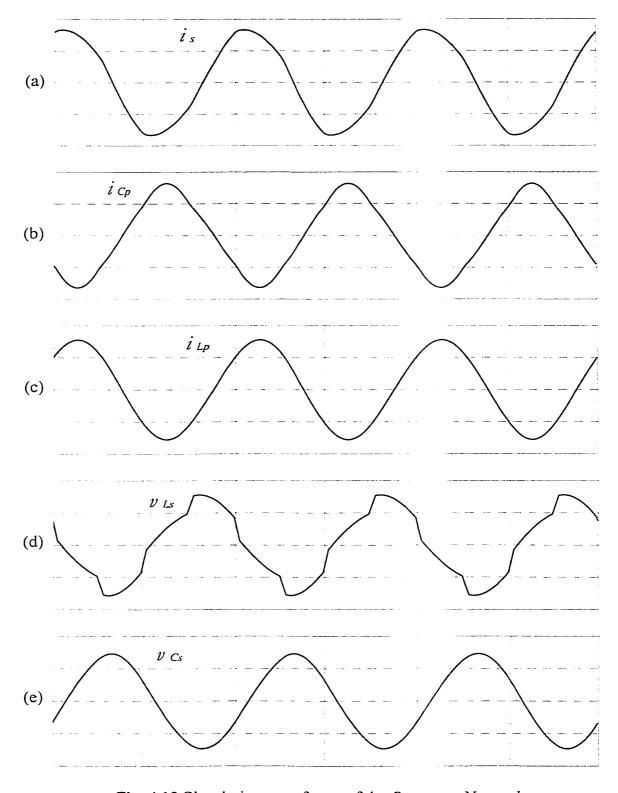

| Fig. 4.12 Simulation waveforms of the Resonant Network (a) Current through the series                             |

| branch; (b) Current through the parallel capacitor; (c) Current through the parallel                              |

| inductor; (d) Voltage across the series inductor; (e) Voltage across the series                                   |

| capacitor84                                                                                                       |

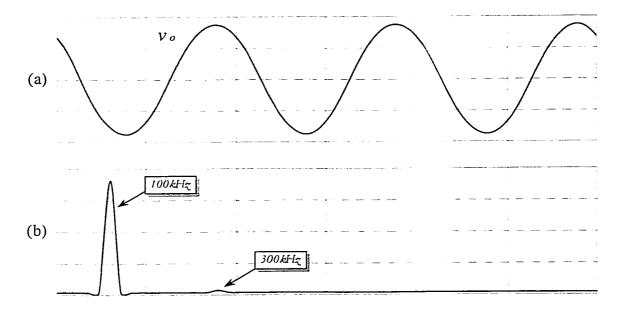

| Fig. 4.13 Simulation waveform of the output voltage (a) Waveform of the output voltage                            |

| $(30V_{ac} \text{ at } 100\text{kHz})$ ; (b) Frequency spectrum of the output voltage (THD=2%)85                  |

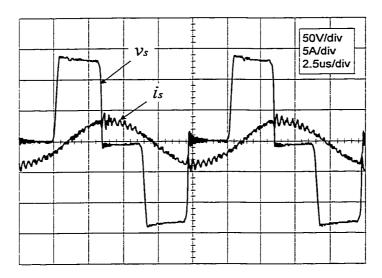

| Fig. 4.14 Experimental waveforms of the output voltage and current of the Full Bridge                             |

| Inverter (at 110V <sub>ac</sub> line input, P <sub>o</sub> =250W)86                                               |

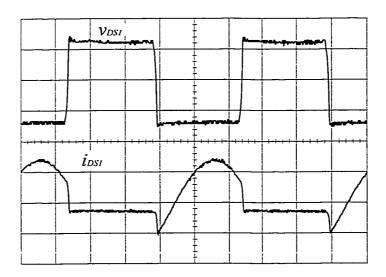

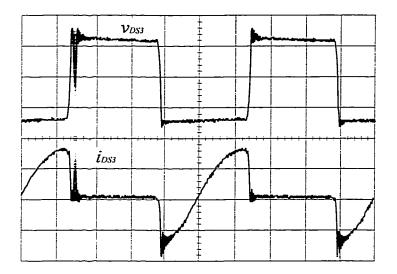

| Fig. 4.15 Experimental voltage and current waveforms switch 1                                                     |

| Fig. 4.16 Experimental voltage and current waveforms switch 3                                                     |

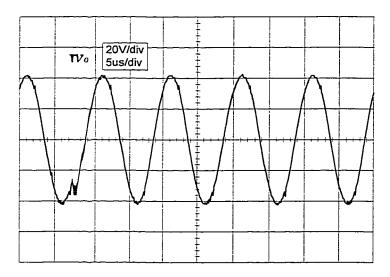

| Fig. 4.17 Experimental waveform of the output voltage (at 110V <sub>-</sub> , line input P <sub>2</sub> =250W) 87 |

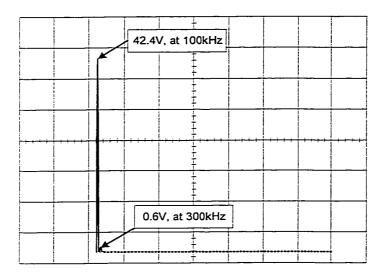

| Fig. 4.18 Measured harmonics of the output voltage, THD=1.4% (at $110V_{ac}$ line | input, |

|-----------------------------------------------------------------------------------|--------|

| P <sub>o</sub> =250W)                                                             | 88     |

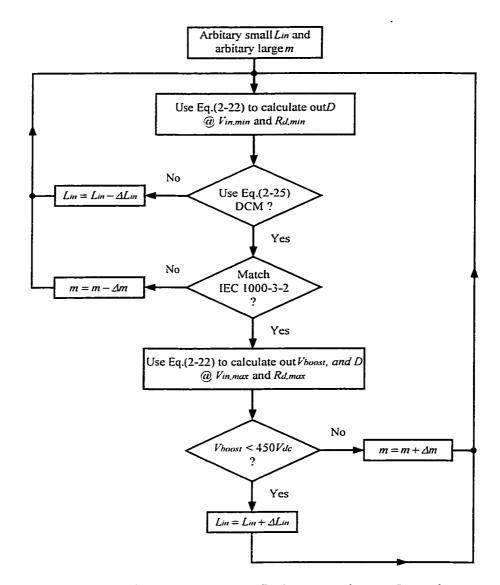

| Fig. 5.1 Design procedures to find out maximum $L_{in}$ and $m$                   | 91     |

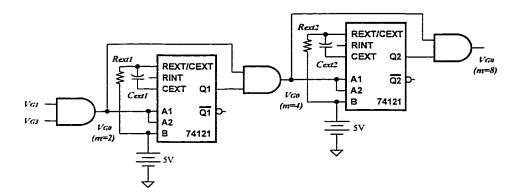

| Fig. 5.2 Logic circuits that generate $V_{G0}$ for different $m$                  | 94     |

# **LIST OF TABLES**

| Table   | 1.1 Relationship between the DC bus voltage and the load for different          |

|---------|---------------------------------------------------------------------------------|

|         | combinations of conduction mode4                                                |

| Table   | 2.1 Comparison of duty and DC bus voltage between theoretical calculation,      |

|         | simulation and experimental results39                                           |

| Table 3 | 3.1 Measured experimental data for various input voltages at 250W58             |

| Table   | 4.1 Values and ratings for resonant components (transformer before the Resonant |

|         | Network at $N=4$ , $k_1=6$ , $k_2=4$ , $k_3=0.2$ , $I_{o,rated}=8.33A$ )        |

| Table   | 4.2 Values and ratings for resonant components (transformer after the Resonant  |

|         | Network at $N=4$ , $k_1=6$ , $k_2=4$ , $k_3=0.2$ , $I_{o,rated}=8.33A$ )        |

| Table : | 5.1 Lists of Components (Boost Implementation)95                                |

| Table 5 | 5.2 Lists of Components for Buckboost Implementation95                          |

## LIST OF ACRONYMS

CCM Continuous Conduction Mode

DCM Discontinuous Conduction Mode

EMI Electromagnetic Interference

*PF* Power factor

*PFC* Power Factor Correction

THD Total Harmonics Distortion

AP Area Product

High Frequency Power Distribution System

#### LIST OF PRINCIPLE SYMBOLS

$\delta$  Phase shift angle

$\phi$  Phase lag angle

η Efficiency

$B_m$  Peak flux density (T)

$C_p$  Parallel branch capacitor of the Resonant Network (uF)

$C_s$  Series branch capacitor of the Resonant Network (uF)

$C_{sl}$  to  $C_{st}$  Snubber capacitors of the full bridge

Duty cycle of the full bridge

$D_{boost}$  Duty cycle of the boost converter

$D_{buckboost}$  Duty cycle of the buckboost converter

fboost Switching frequency of the Boost Converter (Hz)

f<sub>buckboost</sub> Switching frequency of the Buckboost Converter (Hz)

$f_L$  Line frequency (Hz)

f<sub>sw</sub> Switching frequency of the Full Bridge Inverter (Hz)

$I_{cp}$  rms value of the current through the parallel capacitor (A)

$i_{Lin}$  Current through input inductor (A)

$i_{Lin,peak,k}$   $k^{th}$  peak current through input inductor (A)

$i_{Lin,peak,k}$  Maximum peak current through input inductor (A)

$I_{lp}$  rms value of the current through the parallel inductor (A)

*I<sub>oB.boost</sub>* Boundary current between DCM and CCM of boost converter

I<sub>oB,buckboost</sub> Boundary current between DCM and CCM of buckboost converter

$I_s$  rms value of the current through the series branch (A)

$k_u$  Winding packing factor

lg Total length of air gap

$L_{in}$  PFC stage inductor (uH)

L<sub>p</sub> Parallel branch inductor of the Resonant Network (uH)

L<sub>s</sub> Series branch inductor of the Resonant Network (uH)

m Gate Signal Constant

N Main transformer turn ratio

$N_p$  Main transformer primary side turn number (turn)

$N_s$  Main transformer secondary side turn number (turn)

$R_{boost}$  Equivalent load of boost converter  $(\Omega)$

$R_{buckboost}$  Equivalent load of buckboost converter  $(\Omega)$

$R_d$  Final output load  $(\Omega)$

u<sub>0</sub> Magnetic field constant (H/m)

| $u_r$                  | Relative permeability of core                        |

|------------------------|------------------------------------------------------|

| $V_{boost}$            | DC bus voltage of boost implementation (V)           |

| V <sub>buckboost</sub> | DC bus voltage of buckboost implementation (V)       |

| $v_{in}$               | AC line input voltage (V)                            |

| $V_{in}$               | rms value of AC line input voltage (V)               |

| $V_o$                  | rms value of output voltage (V)                      |

| $V_{rec}$              | AC line input voltage after diode rectifier (V)      |

| $X_{cp}$               | Impedance of the Resonant Network parallel capacitor |

| $X_p$                  | Impedance of the Resonant Network parallel inductor  |

| $X_{s}$                | Impedance of the Resonant Network series branch      |

## **CHAPTER 1**

# INTRODUCTION

#### 1.1 GENERAL

Future computer and telecommunication power distribution systems may require power transfer between the power distribution system and electronic cards through magnetic coupling, which means that the power distribution system should be of ac type [1] [2] [3] [4] [5]. In addition, in order to reduce the size and weight of the power converter, the switching frequency of the ac source should be high. Furthermore, due to the pending European Standard, IEC 1000-3-2 [6], the Power Factor Correction (PFC) has gained more and more attention in recent years. Therefore, PFC inevitably becomes another issue that should be included in the design of the high frequency ac source for the future comuter and telecommunication power distribution systems.

This thesis tries to provide a solution to low power, high frequency ac-ac inverter that complies with the above-mentioned requirements.

#### 1.2 PROBLEM DEFINITION

The main challenges in the ac-ac inverter design is to provide a high input power factor with restricted DC bus voltage and low cost, and to supply a constant high frequency sinusoidal output voltage with high efficiency. Section 1.2.1 and 1.2.2 describe these issues in detail.

#### 1.2.1 Power Factor Correction

#### 1.2.1.1 Conventional Two-Stage Power Factor Correction

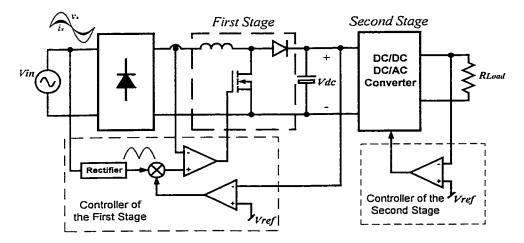

The block diagram of a conventional two-stage PFC converter is given in Fig. 1.1. The first stage is usually a boost, buckboost (or flyback) converter, which is introduced to correct the power factor and also supply DC voltage to the next stage as its input. The second stage can be a dc-dc or dc-ac converter. The two stages are independent from each other and have a controller of their own. The controller of the PFC stage has a current and voltage loop. It senses the line voltage waveform and forces the input current to track the sinusoidal line voltage to achieve unity input power factor.

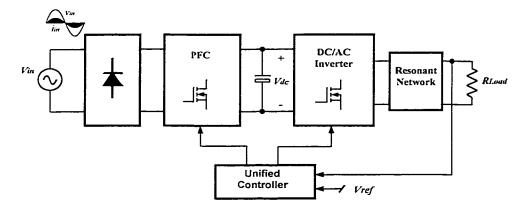

Fig. 1.1 Block Diagram of conventional Two-Stage PFC converters

The advantage of this topology is that it can provide almost unity power factor and a controllable constant DC bus voltage, which is independent from the second stage. However, it needs two separate controllers, which will increase the complexity and the cost of the converter. Since cost reduction is one of the main factor concerned in low power applications, the conventional two-stage PFC topology is not suitable for this design.

#### 1.2.1.2 Single-Stage Power Factor Correction

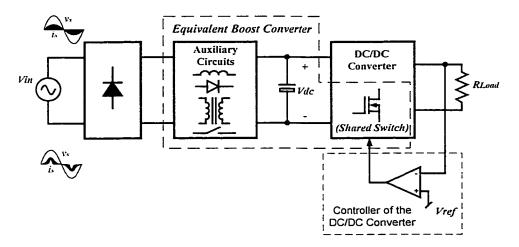

Single-Stage PFC techniques have been studied thoroughly in recent years. There are many approaches to it [7] [8] [9] [10], but normally those proposed topologies have some auxiliary circuits to implement PFC. Fig. 1.2 gives the conceptual structure of those single-stage PFC converters. However, no matter what the forms of the auxiliary circuits are, they are substantially a boost equivalent circuit followed by a dc-dc converter. The switch of the boost equivalent circuit is integrated in the dc-dc converter. Thus no separate switch is needed for the boost equivalent circuit. Since the boost equivalent circuit and the dc-dc converter are sharing the same switch or switches, they will receive the same control signal, yielding economical control circuitry [11].

Fig. 1.2 Block diagram of Single-Stage PFC converters

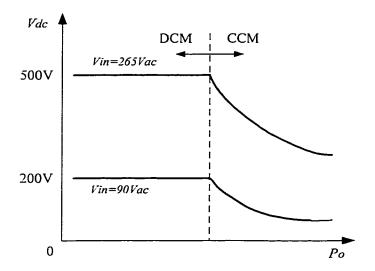

In order to keep the DC bus voltage within a relative low level in those topologies, the dc-dc converter and the boost equivalent circuit are normally designed to enter Discontinuous Conduction Mode (DCM) at low load. The dc-dc converter can be a forward [7], a full bridge [8] [9], or a flyback converter [10]. While both the dc-dc converter and the boost equivalent circuit are working in DCM, the output voltages of the dc-dc converter and the boost equivalent circuits are load dependent. However, when they are combined together, the influence of load on DC bus voltage is minimized. Therefore the DC bus voltage becomes load independent and a relatively low DC bus voltage can be realized. Table 1.1 gives the relationship between the DC bus voltage and the load for different combinations of conduction modes.

| Combinati                   | DC Bus Voltage V <sub>dc</sub>                     |                  |

|-----------------------------|----------------------------------------------------|------------------|

| Equivalent Boost<br>Circuit | DC-DC Converter<br>(Forward, Flyback, Full Bridge) |                  |

| CCM<br>(Load Independent)   | CCM<br>(Load Independent)                          | Load Independent |

| CCM<br>(Load Independent)   | DCM<br>(Load Dependent)                            | Load Dependent   |

| DCM<br>(Load Dependent)     | CCM<br>(Load Independent)                          | Load Dependent   |

| DCM<br>(Load Dependent)     | DCM<br>(Load Dependent)                            | Load Independent |

**Table 1.1** Relationship between the DC bus voltage and the load for different combinations of conduction mode

Fig. 1.3 shows the DC bus voltage as a function of load for universal line voltage. When either the boost equivalent circuit or the dc-dc converter is working in CCM, the DC bus voltage is increasing as the load is decreasing. When both the boost equivalent circuit

and the dc-dc converter are working in DCM, the DC bus voltage keeps constant regardless of the load changes.

Fig. 1.3 DC bus voltage as a function of load for different line input voltage

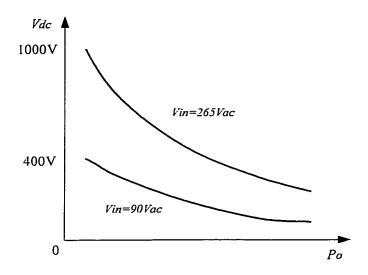

However, as will be analyzed later in Chapter 4, the output voltage of the proposed ac-ac inverter in this thesis is load independent. If the above single-stage PFC strategy is adopted, there is no *Conduction Mode Combination* to choose. Therefore when load is decreasing, and the boost equivalent circuit enters DCM, the DC bus voltage will increase accordingly. Theoretically, the DC bus voltage can be extremely high at low load. Fig. 1.4 gives the DC bus voltage as a function of load for this case.

Fig. 1.4 DC bus voltage as a function of load for universal line voltage

A major difficulty in designing a universal line input single-stage PFC converter is to limit the bulk capacitor voltage within  $450V_{dc}$ , which is the voltage limitation of commercially available capacitors. Some single-stage PFC ac/dc converter can achieve this design goal [10] by introducing additional dimensions, but what this thesis presents is a acac inverter which is different from above-mentioned dc-dc converters. There is no Conduction Mode Combination to choose and the above mentioned methods do not apply.

#### 1.2.2 Efficiency and Constant Frequency Resonant Technique

The ac-ac inverter for computer and telecommunication power distribution systems is required to supply high frequency sinusoidal voltage. The frequency of the output voltage must be constant, therefore the switching frequency is required to be fixed. High efficiency is also required by the inverter.

Convential hard switching toplologies are simple and easy to implement, but they are obviously not suitable for the high frequency ac-ac inverter due to their following drawbacks [12]:

- 1. The switches are subjected to high switching stress.

- 2. High switching power losses increase linearly with the switching frequency, hence high efficiency and small size of cooling devices become impossible.

- 3. Large *dv/dt* and *di/dt* caused by hard switching produces significant Electromagnetic Interference (EMI) [13].

Adding snubber circuits around the switches can reduce the switching stress and switching losses of the switches. However, the switching power losses are shifted from the switches to the snubber circuits, so there is no reduction in the overall switching power losses [12].

Zero-voltage switching techniques enable switches switch at a high frequeny with zero switching losses. Topologies presented in reference [14][15] operate under zero-voltage switching. However they are implemented under variable frequency control, which means the switching frequency is not fixed. Thus, a constant frequency output voltage can not be obtained from the ac-ac inverter.

Reference [16][17][18] present multiple elements resonant converter topologies, which have constant frequency operation. However they only reduce part of the switching losses and exhibit higher conduction losses. Thus, they can not provide a satisfatory efficiency for the high frequency ac-ac inverter.

#### 1.3 PROPOSED TOPOLOGY

Different types of PFC topologies have been discussed in section 1.2.1. The conventional two-stage PFC topology needs two separate controllers, which increases the complexity and cost. Typical single-stage PFC topologies [7] [8] [9] [10] are simple and cost effective, but will result in high DC bus voltage for the proposed ac-ac inverter [19].

Fig. 1.5 gives the block diagram of the proposed PFC high frequency inverter, in which a separate stage is introduced to correct power factor. A unified controller is introduced to control the PFC stage and the dc-ac stage at the same time. In the proposed topology, a separate PFC controller for the power factor stage is saved. In addition, the DC bus voltage can be well controlled to satisfy the limitations of commercial capacitors. The cost of the converter is therefore reduced.

Fig. 1.5 Block diagram for proposed PFC high frequency ac-ac inverter

The dc-ac inverter and the *Resonant Network* together can generate the required constant high frequency sinusoidal output voltage. Zero-voltage switching can be realized for all the switches throughout the whole switching cycle under all load variations. Thus, a high efficiency can be achieved. In addition, the output voltage of the ac-ac inverter

demonstrates very good load independent characteristics. Details will be given thoroughly in Chapter 4.

#### 1.4 THESIS OBJECTIVE

The objectives of this thesis are:

- Propose a high frequency low power ac-ac inverter with PFC.

- Realize ZVS for the dc-ac stage throughout the line voltage and load variations so that high efficiency can be achieved.

- Achieve high input power factor that satisfies IEC 1000-3-2 standards.

- Maintain a low DC bus voltage for universial line voltage and required load range.

- Develop steady state analysis and demontrate performance. Give design procedure and design example to guide the design process.

- Use simulation and experimental results to verify the theoretical analysis.

#### 1.5 THESIS OUTLINE

The content of this thesis are organized as follows:

Chapter 2 presents a *Boost Converter* implemented power factor corrected ac-ac inverter. Circuit description and principle of operation are given. Performance

characteristics are given to guide the design. Simulation and experimental results are given in the end.

Chapter 3 presents a *Buckboost Converter* implemented power factor corrected acac inverter. The structure of this chapter is similar to that of Chapter 2.

Chapter 4 gives the detailed analysis of the resonant dc-ac stage. Principle of operation, operation modes, and steady state analysis are given. Performance characteristics are presented to guide the design. Simulation and experimental results are given in the end to illustrate the achieved goal of the design.

Chapter 5 gives the design procedure and example of the proposed high frequency ac-ac inverter. Actually used components in the experiment are also listed in detail.

Chapter 6 gives the summary of the thesis. Suggestions for furure work on this topic are presented.

# **CHAPTER 2**

# **BOOST IMPLEMENTED PFC**

#### 2.1 Introduction

This chapter presents an ac-ac inverter with a PFC stage implemented by a boost converter [20]. A unified controller is introduced to control the two stages. The analyzed example operates at a fixed frequency of 100kHz with a rated output power of 250DW and a rated output voltage of 30V<sub>ac</sub>. In order to achieve a high input power factor, the boost converter is designed to work in Discontinuous Conduction Mode (DCM).

In the following sections, the description and analysis will be mainly focused on the *Boost Converter*. The detail analysis on the dc-ac stage will be given in Chapter 4. DC bus voltage, duty cycle, input power factor, and peak input current for different input voltages and loads are the main factors that will be analyzed in this chapter.

Circuits description and operation principles will be given in section 2.2 and 2.3 respectively. Steady state analysis is given in section 2.4. Performance characteristics are given in section 2.5 to guide the design. Simulation and experimental results are given in section 2.6 to verify the steady state analysis. Suggestions on the application of this proposed topology are also given at the end of this chapter.

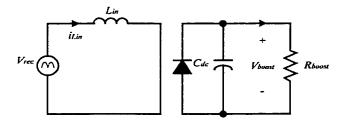

# 2.2 DESCRIPTION OF PROPOSED TOPOLOGY

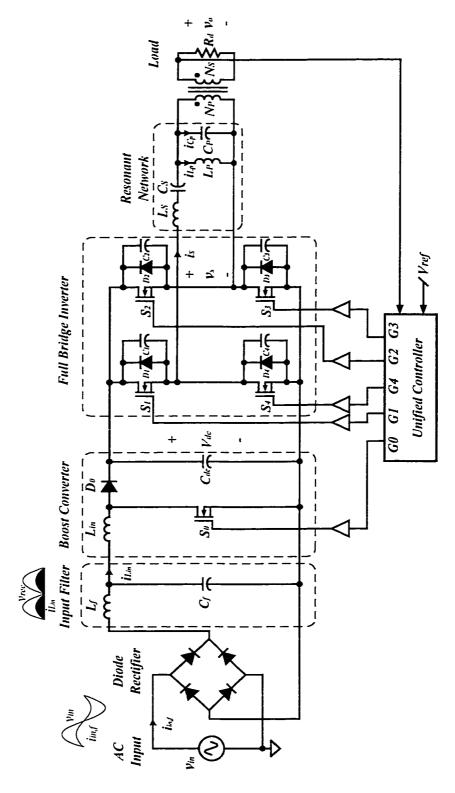

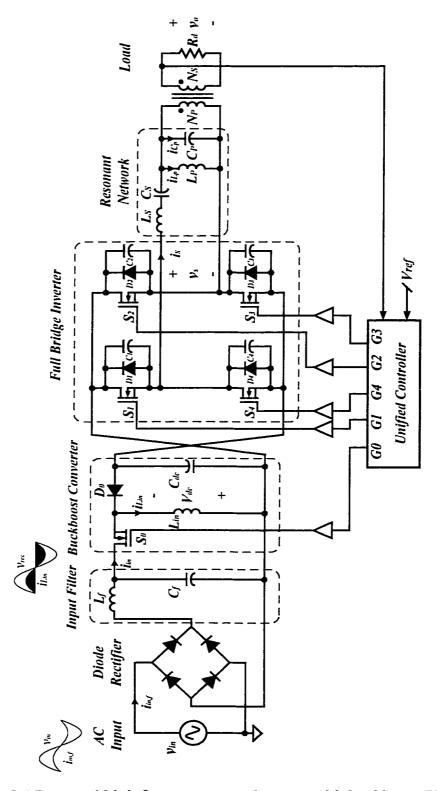

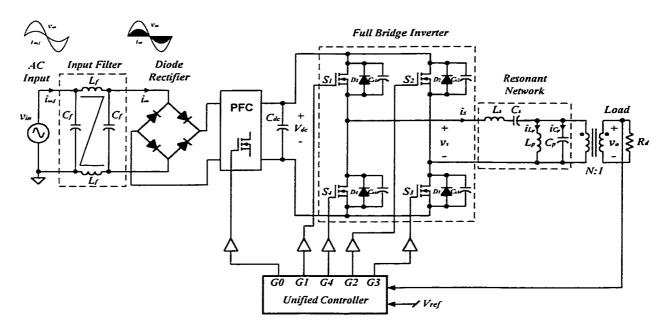

Fig. 2.1 Proposed high frequency ac-ac inverter with boost PFC

- Fig. 2.1 gives the proposed high frequency ac-ac inverter, which consists of the follow parts:

- *Input Filter*: It is made up of high frequency capacitors and inductors to filter out the high frequency harmonics contained in the line current.

- **Diode Rectifier**: The *Diode Rectifier* provides rectified ac input voltage to the *Boost Converter*.

- Boost Converter: The Boost Converter is designed to work in Discontinuous

Conduction Mode to correct the power factor and provide a DC bus voltage to

the Full Bridge Inverter simutaneously. Its input is from the Diode Rectifier and

its gate signal is generated by the Unified Controller.

- *Full Bridge Inverter*: The dc-ac stage adopts a full bridge topology with phase-shifted gating signal control pattern. It generates a high frequency quasi-square voltage waveform at its output.

- Resonant Network: The Resonant Network is made up of capacitors and inductors. It converts the quasi-square voltage waveform from the Full Bridge Inverter into a sinusoidal waveform. At the same time, it can let the Full Bridge inverter work under ZVS to reduce the switching losses.

- Unified Controller: The Unified Controller gets the feedback from the output voltage and generates phase shifted signal to the four switches of the Full Bridge Inverter as well as the gate signal for the Boost Converter at the same time.

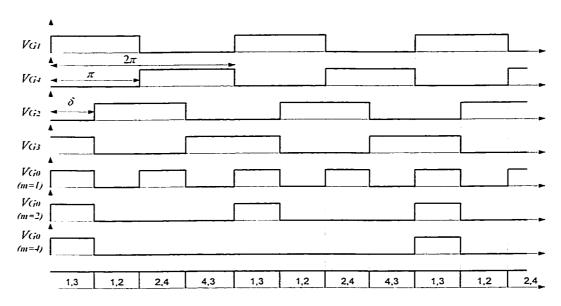

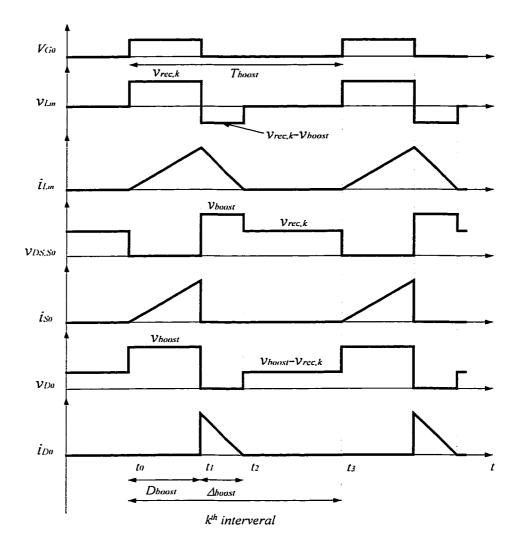

The gate signals of the proposed topology are illustrated in Fig. 2.2, where  $V_{GI}$ ,  $V_{G2}$ ,  $V_{G3}$ , and  $V_{G4}$  are the phase shifted gate signals to the *Full Bridge Inverter*.  $\delta$  is the phase shift angle.  $V_{G0}$  is the gate signal to the *Boost Converter*.  $V_{G0}$  is generated whenever  $S_I$  and  $S_3$ , or  $S_2$  and  $S_4$  are conducting at the same time, see  $V_{G0}$  (m=1) in Fig. 2.2. However, in order to reduce the DC bus voltage, we may not keep all the pulses shown in  $V_{G0}$  (m=1). We may keep only 1/m of them (m here is called *Gate Signal Constant*). For example, when m=1, we keep all the pulses, see  $V_{G0}$  (m=1). When m=2 or 4, we keep 1/2 or 1/4 of the pulses respectively, see  $V_{G0}$  (m=2) and  $V_{G0}$  (m=4).

Fig. 2.2 Gate signals generated by the Unified Controller

### 2.3 PRINCIPLE OF OPERATION

Fig. 2.3 gives the simplified circuits for the boost PFC stage, in which  $R_{boost}$  is the equivalent load for the Boost Converter. The only difference between this topology and the standard boost converter is that the input of this topology is a rectified sinusoidal voltage waveform instead of a DC voltage source. This difference makes PFC possible. In order to

have high power factor, the *Boost Converter* should be designed to work in Discontinuous Conduction Mode (DCM) [21].

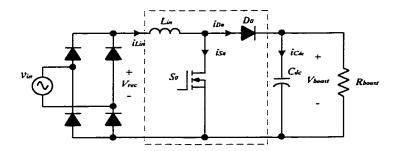

Fig. 2.3 Boost Converter after Diode Rectifier with equivalent load

There are three different operation switching intervals for the boost PFC stage during a single switching cycle. The first interval starts when the boost switch  $S_0$  is turned on. The rectified input voltage is therefore applied to the inductor  $L_{in}$  through the switch  $S_0$ . The bulk capacitor  $C_{dc}$  supplies the power to the output load. The equivalent circuit for this interval is given in Fig. 2.4. Key waveforms of this interval are shown in Fig. 2.7:  $t_0$ - $t_1$ .

Fig. 2.4 Equivalent circuit for interval one

The second interval begins with the turn-off of switch  $S_0$ . The input power and the energy stored in the inductor  $L_{in}$  is transferred to the buck capacitor  $C_{dc}$  through diode  $D_0$ . The equivalent circuit for this interval is given in Fig. 2.5. Key waveforms of this interval are shown in Fig. 2.7:  $t_1$ - $t_2$ .

Fig. 2.5 Equivalent circuits for interval two

In the third interval, switch  $S_0$  is still off, same as in interval two, but no current is circulating through inductor  $L_{in}$ . Diode  $D_0$  is reverse biased, which means no power is transferred from the input to the output. The bulk capacitor  $C_{dc}$  supplies the load alone. The equivalent circuit for this interval is given in Fig. 2.6. Key waveforms of this interval are shown in Fig. 2.7:  $t_2$ - $t_3$ .

Fig. 2.6 Equivalent circuits for interval three

Fig. 2.7 Key waveforms of the Boost PFC stage

From Fig. 2.7, we can see that the current through inductor  $L_{in}$  is a discontinuous triangular waveform. The peak of  $i_{Lin}$  forms a 60Hz line frequency sinusoidal envelop, which is forced by the rectified input voltage

[21]. Fig. 2.8 gives a simulation example for the line voltage and current waveforms. As we can see, the line current has a 60Hz sinusoidal envelop with many high frequency components, which can be filtered by the *Input Filter*. After being filtered, the line current can be nearly a sinusoidal waveform, which results in high input Power Factor

(PF) and low Total Harmonics Distortion (THD). The switching frequency of the simulation is chosen to be only 2kHz to have a clear picture of the line current.

Fig. 2.8 Simulated input line voltage and current with 2kHz switching frequency

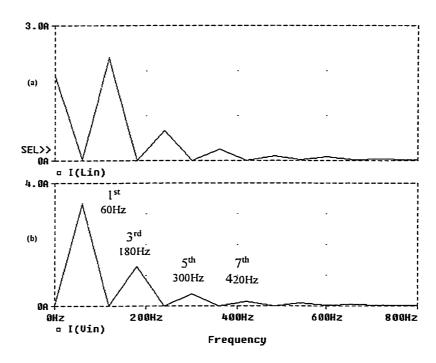

Fig. 2.9 gives the simulated spectrum of the line current at low frequency. High frequency harmonics is not given because the *Input Filter* can easily filter them out. However, the low frequency harmonics: 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup> are not easily eliminated, so the design is mainly focused on reducing the low frequency harmonics.

Fig. 2.9 Simulated low frequency harmonic spectrum of the input current

#### 2.4 STEADY STATE ANALYSIS

This section will only give the steady state analysis of the boost PFC stage. DC bus voltage, input power factor, and input peak current will be studied thoroughly. The steady state analysis of the *Full Bridge Inverter* will be given in Chapter 4.

### 2.4.1 Duty Cycle and DC Bus Voltage

Eq.(2-1) gives the equation for boost in DCM:

$$D_{boost} = \sqrt{2 \cdot \frac{V_{boost}}{V_{in}} \cdot \left(\frac{V_{boost}}{V_{in}} - 1\right) \cdot \frac{L_{in} \cdot f_{boost}}{R_{boost}}}$$

(2-1)

The gate signals for the Full Bridge Inverter and the Boost Converter have already been given in Fig. 2.2. " $\delta$ " is the phase shift angle. The duty cycle of the Full Bridge Inverter is defined as:

$$D = \frac{\delta}{\pi} \tag{2-2}$$

The transformer turn ratio of the Full Bridge Inverter is:

$$N = \frac{N_p}{N_s} \tag{2-3}$$

The relationship between the rms output voltage  $V_o$  and the DC input voltage  $V_{boost}$  of the Full Bridge Inverter is given in Eq.(2-4). The derivation of the equation will be given in section 4.4 and Appendix A1. The equation indicates that the output voltage of the Full Bridge Inverter is load independent.

$$V_o = \frac{1}{N} \cdot 0.9 \sin \frac{\delta}{2} \cdot V_{boost} \tag{2-4}$$

$$P_o = P_{boost} \cdot \eta \tag{2-5}$$

Hence,

$$\frac{V_{boost}^2}{R_{boost}} \cdot \eta = \frac{V_o^2}{R_d} \tag{2-6}$$

By substituting (2-4) into (2-6), we can get the expression for the equivalent load of the *Boost Converter*.

$$R_{boost} = \frac{V_{boost}^{2}}{V_{o}^{2}} \cdot R_{d} \cdot \eta = \frac{N^{2}}{\left(0.9 \sin \frac{\delta}{2}\right)^{2}} \cdot R_{d} \cdot \eta \tag{2-7}$$

From Fig. 2.2, we can get the duty cycle of the *Boost Converter*, where *m* is the *Gate Signal Constant*:

$$D_{boost} = \frac{1}{m} \cdot D \tag{2-8}$$

The switching frequency of the Boost Converter is:

$$f_{boost} = \frac{2f_{sw}}{m} \tag{2-9}$$

Substitute Eq.(2-2), (2-4), (2-7), (2-8) and (2-9) into Eq.(2-1), we get:

$$D = \sqrt{\frac{V_o}{V_m} \cdot \left(\frac{V_o}{V_m} - \frac{0.9 \sin \frac{D^{\bullet} \cdot \pi}{2}}{N}\right) \cdot \frac{4m \cdot L_{in} \cdot f_{sw}}{R_d \cdot \eta}}$$

(2-10)

For given input line voltage, output v•oltage and load, we can calculate out the duty cycle of the *Full Bridge Inverter* by solving Eq.(2-10).

Combine Eq.(2-2), (2-4) and (2-10), we get the DC bus voltage  $V_{boost}$ .

$$V_{hoost} = \frac{V_o^2 - V_{in}}{V_o^2 - \frac{V_{in}^2 \cdot D^2 \cdot Rd \cdot \eta}{4m \cdot L_{in} \cdot f_{sw}}}$$

(2-11)

As we have pointed out in section 1.22.1.2, the DC bus voltage is load dependent. It is determined by the value of inductor  $L_{in}$ , switching frequency  $f_{sw}$  and the *Gate Signal Constant m*. In order to limit the DC buse voltage within an acceptable range, those parameters need to be carefully designed. In section 2.5, characteristic curves will be given in detail to guide the design.

### 2.4.2 Peak Current of the Converter

Eq.(2-12) gives the expression of the \( \alpha \) line input voltage.

$$v_{in}(t) = \sqrt{2}V_{in}\sin(2\pi f_L \cdot t) \tag{2-12}$$

When the switch  $S_0$  is turned on (interval one), the voltage across the inductor  $L_{in}$  is the rectified ac input voltage, given in Eq.(2- $\mathbb{I}_3$ ):

$$v_{Lim} = v_{rec}(t) = \left| v_{im}(t) \right| = \left| \sqrt{2} V_{im} \sin(2\pi f_L \cdot t) \right|$$

(2-13)

Due to the high switching frequency  $f_{boost}$  of the *Boost Converter*, the rectified input voltage  $v_{rec}$  can be assumed constant within the  $k^{th}$  switching interval. The number of switching intervals during one line cycle is given in Eq.(2-14).

$$n = \frac{f_{hoost}}{f_L} \tag{2-14}$$

Thus, the up slop of the current through the inductor  $L_{in}$  during the  $k^{th}$  interval is:

$$\frac{di_{Lin.up.k}}{dt} = \frac{\left|\sqrt{2}V_{in}\sin(2\pi k/n)\right|}{L_{in}} \tag{2-15}$$

The peak current through the inductor  $L_{in}$  during the  $k^{th}$  interval is:

$$i_{Lin. peak, k} = \frac{\left| \sqrt{2V_{in}} \sin(2\pi k/n) \right|}{L_{in}} \cdot \frac{D_{boost}}{f_{boost}}$$

(2-16)

The maximum peak current through the inductor  $L_{in}$  during one line cycle is:

$$i_{Lin, peak, max} = \frac{\sqrt{2V_{in}}}{L_{in}} \cdot \frac{D_{boost}}{f_{boost}}$$

(2-17)

The maximum peak current through the switch  $S_0$ , diode  $D_0$  and diode rectifier are the same as the maximum peak current through the inductor  $L_{in}$ :

$$i_{So, peak, max} = i_{Do, peak, max} = i_{Lin, peak, max} = \frac{\sqrt{2V_{in}}}{L_{in}} \cdot \frac{D_{boost}}{f_{boost}}$$

(2-18)

Substitute Eq.(2-8) and (2-9) into Eq.(2-17), we get the maximum input peak current, where D is given in Eq.(2-10).

$$i_{Lin. peak, max} = \frac{\sqrt{2V_{in} \cdot D}}{2L_{in} \cdot f_{sw}}$$

(2-19)

When the switch  $S_0$  is off (interval two), the voltage across the inductor  $L_{in}$  becomes:

$$v_{Lin} = \left| \sqrt{2} V_{in} \sin \omega_{line} t \right| - V_{boost} \tag{2-20}$$

Thus, the down slop of the current through the inductor  $L_{in}$  during the  $k^{th}$  interval becomes:

$$\frac{di_{Lin,dw,k}}{dt} = \frac{\left|\sqrt{2}V_{in}\sin(2\pi k/n)\right| - V_{boost}}{L_{in}}$$

(2-21)

### 2.4.3 Boundary between DCM and CCM

The output current of the Boost Converter is:

$$I_{boost} = \frac{V_{boost}}{R_{boost}} = \frac{V_{boost}}{R_d \cdot \eta} \cdot \frac{\left(0.9 \sin \frac{D\pi}{2}\right)^2}{N^2}$$

(2-22)

The boundary of the output current of the Boost Converter is [12]:

$$I_{OB, hoost} = \frac{V_{hoost}}{2L_{in} \cdot f_{hoost}} \cdot D_{hoost} \cdot (1 - D_{hoost})^2$$

(2-23)

In order to let the *Boost Converter* work in DCM, the output current of it must be smaller than the boundary current.

$$I_{boost} < I_{OB, boost}$$

(2-24)

Substitute Eq. (2-8), (2-9), (2-22) and (2-23) into Eq.(2-24), we get the expression that judge the *Boost Converter* is in DCM or not.

$$\frac{\left(0.9\sin\frac{D\pi}{2}\right)^2}{D\cdot\left(1-\frac{1}{m}D\right)^2} < \frac{N^2\cdot Rd\cdot\eta}{4L_{in}\cdot f_{sw}}$$

(2-25)

### 2.4.4 Input Current Power Factor

The expression for the input current power factor is given in Eq.(2-26). The fundamental and harmonics can be measured from the spectrum, such as the one shown in Fig. 2.9.

$$PF = \frac{I_{s1}}{\sqrt{I_{s1}^2 + I_{s3}^2 + I_{s5}^2 + I_{s7}^2 + \cdots}}$$

(2-26)

### 2.5 PERFORMANCE CHARACTERISTICS

The performances of the PFC stage refers to the range of the DC bus voltage, the range of the duty cycle, the maximum unfiltered input peak current and the input power factor. In this section, performance characteristics will be given in detail corresponding to different load, transformer turn ratio, input inductor, and *Gate Signal Constant m*.

#### 2.5.1 Effect of Load on Performance

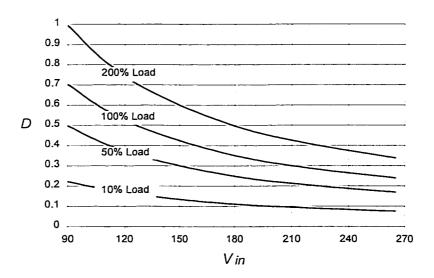

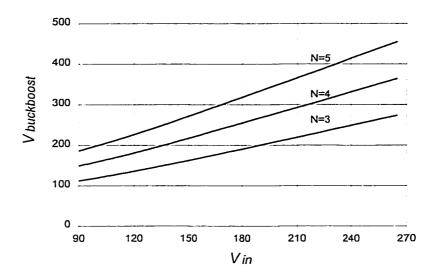

Fig. 2.10 gives the curves of the DC bus voltage versus input voltage for various load, which illustrates that the DC bus voltage is load dependent. When load is decreasing, the DC bus voltage is increasing. Theoretically the DC bus voltage can be infinite, which means the proposed inverter has to work within a certain range of load. Fig. 2.11 gives the characteristics of the duty cycle versus load. The lower the load is, the smaller the duty cycle will be.

Fig. 2.10 DC bus voltage versus input voltage for various loads (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ , N=4,  $L_{in}=30uH$ , m=4)

Fig. 2.11 Duty cycle versus input voltage for various loads (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ , N=4,  $L_{in}=30uH$ , m=4)

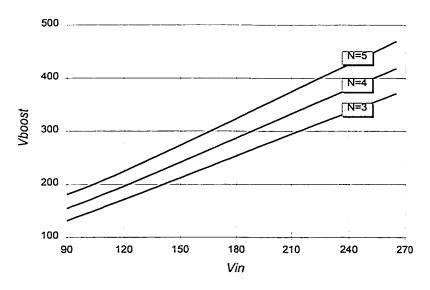

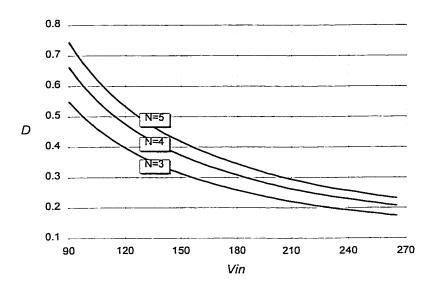

### 2.5.2 Effect of Transformer Turn Ratio on Performance

The transformer turn ratio of the *Full Bridge Inverter* will affect the DC bus voltage and the duty cycle. The larger the turn ratio is, the larger the DC bus voltage and the duty cycle will be, see Fig. 2.12 and Fig. 2.13.

Fig. 2.12 DC bus voltage versus input voltage for various transformer turn ratio (at  $V_o=30 V_{ac}$ ,  $f_{sw}=100 KHz$ ,  $R_d=3.6 \Omega$ ,  $L_{in}=30 uH$ , m=4)

Fig. 2.13 Duty cycle versus input voltage for various transformer turn ratio (at  $V_o=30 V_{ac}$ ,  $f_{sw}=100 KHz$ ,  $R_d=3.6 \Omega$ ,  $L_{in}=30 uH$ , m=4)

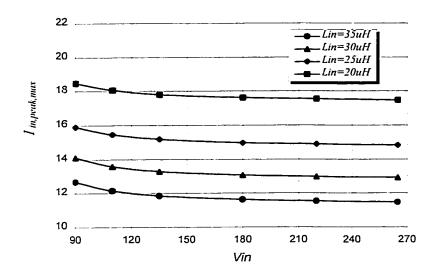

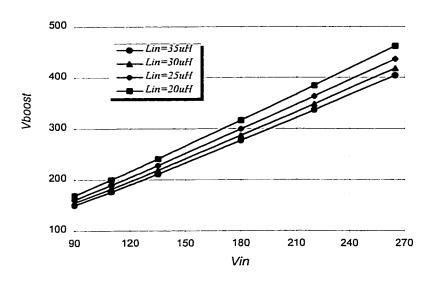

### 2.5.3 Effect of Input Inductor Lin on Performance

In order to have a high input power factor, we prefer the *Boost Converter* to work in DCM. Therefore, inductor  $L_{in}$  should be small enough to enable the *Boost Converter* to work in DCM. Fig. 2.14 gives the relationship between the maximum peak current and the inductor value (all simulated points for different  $L_{in}$  are in DCM). However,  $L_{in}$  can not be too small, otherwise the maximum input peak current will be too high, which will result in a high current stress on related components, hence would increase the cost accordingly. Therefore,  $L_{in}$  should be designed to its maximum value so that it reduces the switch stress and keeps DCM operation as well.

Fig. 2.15 shows that a smaller  $L_{in}$  will result in a higher DC bus voltage. However, the influence of  $L_{in}$  on the DC bus voltage is not very significant. Therefore, in the design,  $L_{in}$  is not expected to contribute much in reducing the DC bus voltage.

Fig. 2.14 Maximum input peak current versus input voltage for various  $L_{in}$  (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ , N=4, m=4)

Fig. 2.15 DC bus voltage versus input voltage for various  $L_{in}$  (at  $V_o$ =30 $V_{ac}$ ,  $f_{sw}$ =100KHz,  $R_d$ =3.6 $\Omega$ , N=4, m=4)

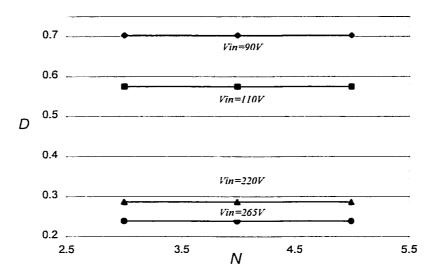

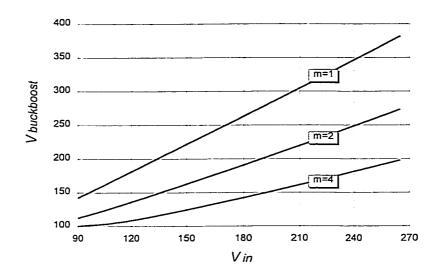

### 2.5.4 Effect of Gate Signal Constant m on Performance

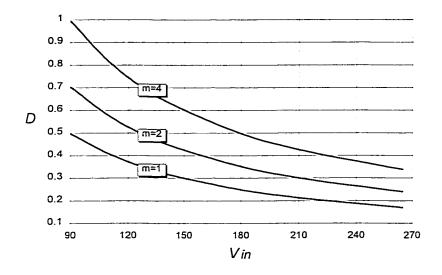

Fig. 2.16 to Fig. 2.19 illustrate the effects of gate signal constant m on the DC bus voltage and the duty cycle. Increasing m is the main means to reduce the DC bus voltage.

Moreover, if m is increased, the range of the duty cycle will be narrowed. A narrow range of the duty cycle is preferred in the design of the *Full Bridge Inverter*, which will be analyzed in Chapter 4.

Fig. 2.16 DC bus voltage versus input voltage for various m at rated load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=30uH$ , N=4)

Fig. 2.17 Duty cycle versus input voltage for various m at rated load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=30uH$ , N=4)

Fig. 2.18 DC bus voltage versus input voltage for various m at 10% rated load (at  $V_o$ =30 $V_{ac}$ ,  $f_{sw}$ =100KHz,  $R_d$ =36 $\Omega$ ,  $L_{in}$ =30uH, N=4)

Fig. 2.19 Duty cycle versus input voltage for various m at 10% rated load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=36\Omega$ ,  $L_{in}=30uH$ , N=4)

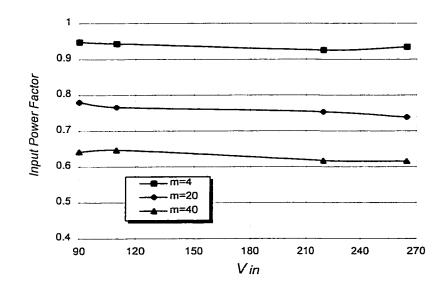

The DC bus voltage can be reduced significantly by increasing m. However, there is a trade off between the DC bus voltage and the input power factor. A larger m will result in a poor power factor, see Fig. 2.20. Therefore, in order to reduce the DC bus voltage and

keep a relative high power factor, a compromised has to be made while selecting the value of m.

Fig. 2.20 Input Power Factor as a function of input voltage for various m (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=15uH$ , N=4)

#### 2.6 SIMULATION AND EX PERIMENTAL VERIFICATIONS

Simulation and experimental waveforms are presented in this section to verify the steady state analysis. Collected data are also tabulated and plotted to compare with the theoretical predictions. The simulation and experiment circuits are based on the design example given in Chapter 5, which has a  $30V_{ac}$ , 100kHz output voltage, 250W output power, with  $90-265V_{ac}$  input voltage. The detailed specifications are given in section 5.1.

### 2.6.1 Simulation Waveforms

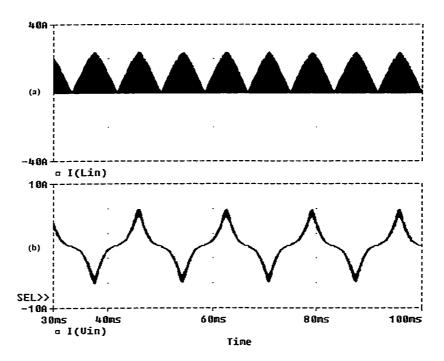

Fig. 2.21 to Fig. 2.25 give the simulation waveforms of the *Boost Converter* in the ac-ac inverter. The simulation is running at  $110V_{ac}$  input, 250W output power.

Fig. 2.21 (a) Simulation waveform of the boost inductor current; (b) Simulation waveform of the filtered input current

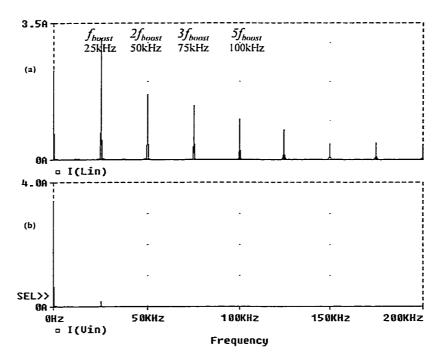

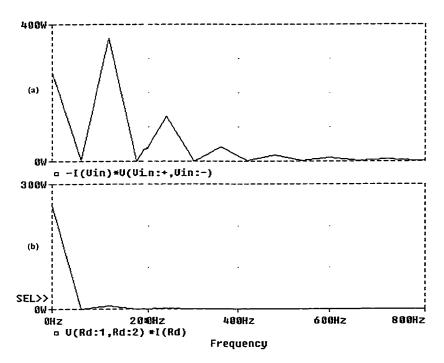

Fig. 2.22 (a) Simulated high frequency harmonic spectrum of the boost inductor current; (b) Simulated high frequency harmonic spectrum of the filtered line current

Fig. 2.23 (a) Simulated low frequency harmonic spectrum of the boost inductor current; (b) Simulated low frequency harmonic spectrum of the filtered line current

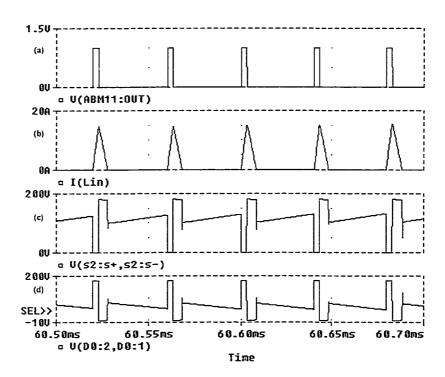

Fig. 2.24 (a) Simulation waveform of the gate signal of the Boost Converter;

- (b) Simulation waveform of the boost inductor current after zoom;

- (c) Simulation waveform of the voltage across the boost switch;

- (d) Simulation waveform of the voltage across the boost diode

Fig. 2.25 (a) Simulated frequency spectrum of input current times input voltage; (b) Simulated frequency spectrum of output put current times output voltage

Fig. 2.22 (a) verified the operation principle given in section 2.3. The discontinuous current through the boost inductor contains high frequency harmonics, which are at the frequency of  $f_{boost}$ ,  $2f_{boost}$ ,  $3f_{boost}$  and so on. However, the *Input Filter* can filter them out. Fig. 2.22 (b) shows that almost all the high frequency harmonics have been filtered out from the input current. The THD of the input current is smaller than 5%.

Fig. 2.23 (b) gives the low frequency harmonics of the input current. They satisfy the requirement of IEC-100-3-2. The measured input power factor is 0.904.

Fig. 2.24 verified the waveform prediction given in section Fig. 2.7. The dc component of the frequency spectrum given in Fig. 2.25 (a) and (b) shows that the input power equals to the output power, which means there is no substantial error in the proposed topology.

### 2.6.2 Experimental Waveforms

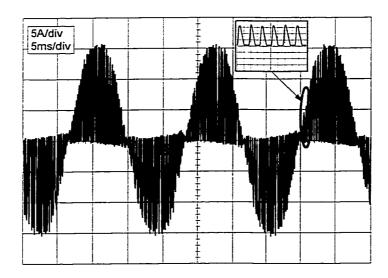

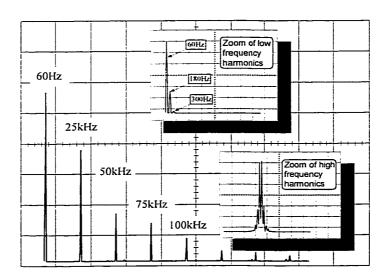

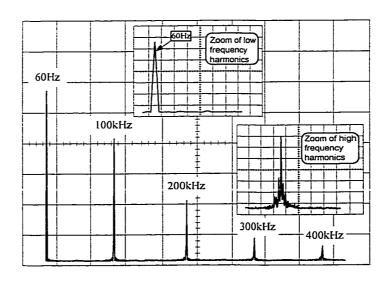

Fig. 2.26 gives the experimental waveform of the unfiltered input current, which shows that the *Boost Converter* is working in DCM. Fig. 2.27 gives the high frequency and low frequency harmonics of the input current. The recorded distribution of the high frequency harmonics verified the simulated frequency spectrum given in Fig. 2.22.

Fig. 2.26 Experimental waveform of the line current without the *Input Filter* (at 110V<sub>ac</sub> input, 250W output)

Fig. 2.27 Measured frequency harmonic spectrum of the unfiltered line current (at 110V<sub>ac</sub> input, 250W output)

Fig. 2.28 gives the experimental waveforms of the line voltage and the filtered line current. Fig. 2.29 gives the harmonic distribution and magnitude of the measured line current. It shows that the proposed topology satisfies the requirement of IEC-1 000-3-2.

Fig. 2.28 Experimental waveforms of the line voltage and the filtered line current (at 110V<sub>ac</sub> input, 250W output power)

Fig. 2.29 Measured harmonics of the unfiltered line current compared with IEC 1000-3-2 limits

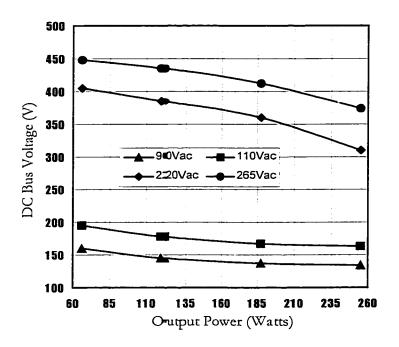

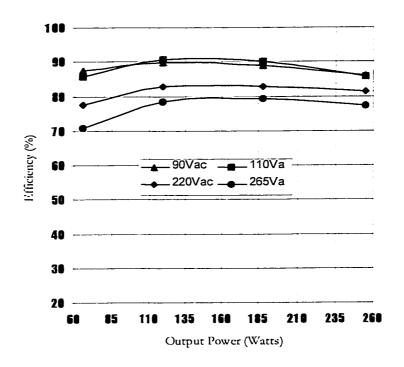

Fig. 2.30 plots the measured experimental DC bus voltage for all load and line voltage variations. It shows that the DC bus voltage can be limited within  $450V_{dc}$ . Fig. 2.31 plots the measured overall efficiency of the experimental prototype for all load and line voltage variations. The prototype has the highest efficiency of up to 90% at  $90-135V_{ac}$  input and 100-185W output.

Fig. 2.30 Measured DC bus voltage versus load for various line voltage

Fig. 2.31 Measured overall efficiency

# 2.6.3 Comparison of Experiment, Simulation and Theoretical Analysis

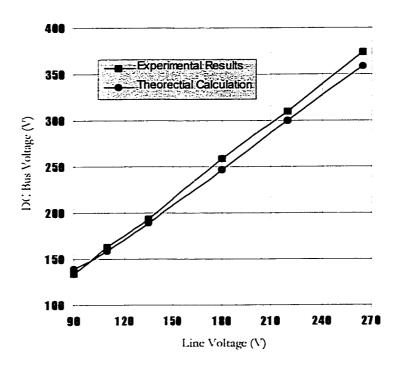

Fig. 2.32 gives the comparison of the DC bus voltage between experiment results and theoretical calculation, which shows that the theoretical prediction is very accurate.

Table 2.1 tabulates the value of duty cycle and DC bus voltage for theoretical calculation, simulation and experimental results. The comparison shows that the predictions are very close to simulation and experimental results.

Fig. 2.32. Measured dc bus voltage versus theoretical calculation at  $110V_{ac}$  input and 100% output power

| V <sub>in</sub> (V) | Duty Cycle  |            |            | DC bus voltage (V) |            |            |

|---------------------|-------------|------------|------------|--------------------|------------|------------|

|                     | Theoretical | Simulation | Experiment | Theoretical        | Simulation | Experiment |

| 90                  | 0.663       | 0.59       | 0.606      | 155                | 157        | 134        |

| 110                 | 0.524       | 0.49       | 0.483      | 182                | 188        | 163        |

| 135                 | 0.417       | 0.403      | 0.39       | 219                | 223        | 194        |

| 180                 | 0.308       | 0.30       | 0.283      | 287                | 295        | 259        |

| 220                 | 0.25        | 0.24       | 0.238      | 348                | 364        | 310        |

| 265                 | 0.207       | 0.22       | 0.198      | 418                | 432        | 374        |

**Table 2.1** Comparison of duty and DC bus voltage between theoretical calculation, simulation and experimental results

### 2.7 CONCLUSION

The proposed topology in this chapter can greatly reduce the DC bus voltage and keep a relative high input Power Factor. However, through theoretical analysis, simulation and experimental results show that the DC bus voltage is at the edge of  $450V_{dc}$  when the input voltage reaches its maximum  $265V_{ac}$ , and the load is reduced to its minimum. In addition, experimental results show that the prototype has the highest efficiency at 90- $135V_{ac}$  input. Therefore, the proposed inverter is suitable for  $90-265V_{ac}$  input and 250W output applications, and especially very attractive in  $90-135V_{ac}$  input and 250W output applications.

### **CHAPTER 3**

# **BUCKBOOST IMPLEMENTED PFC**

#### 3.1 Introduction

Chapter 2 has presented a boost converter to implement PFC. Its DC bus voltage is at the edge of  $450V_{dc}$  at high line voltage and minimum load. Therefore, a further reduction of the DC bus voltage is attempted in this chapter.

In this chapter, a buckboost converter is presented to substitute the boost converter in the PFC stage [22] [23]. Other circuits remain the same. The proposed topology can keep the DC bus voltage within  $450V_{dc}$  for universal line voltage. High power factor is maintained and the auxiliary control circuit is very simple.

The organization of this chapter is similar to that of Chapter 2. Principle of operation is given in section 3.2. Steady state analysis is given in section 3.3. Performance characteristics are given in section 3.4 to guide the design. Conclusions are made in section 3.6.

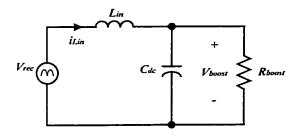

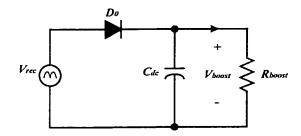

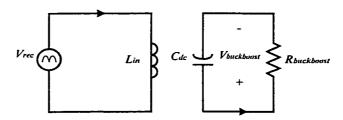

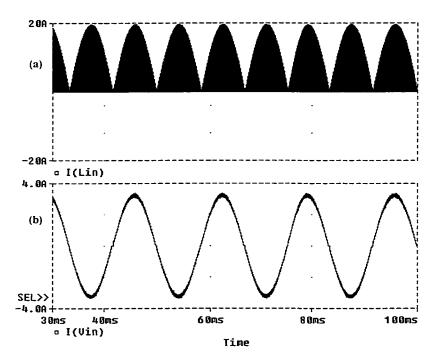

# 3.2 PRINCIPLE OF OPERATION

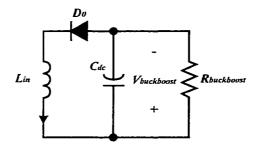

Fig. 3.1 Proposed high frequency ac-ac inverter with buckboost PFC

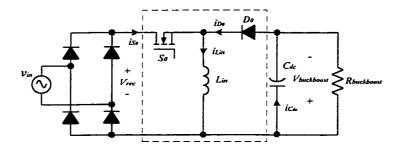

Fig. 3.2 gives the proposed inverter with buckboost PFC stage. The simplified circuit for the PFC stage is given in Fig. 3.2, in which  $R_{buckboost}$  is the equivalent load for the buckboost converter. In order to have high power factor, the *Buckboost Converter* is designed to work in DCM. Therefore, similar to the boost converter in Chapter 1, there are three different operation intervals for the buckboost PFC stage during a single switching cycle.

Fig. 3.2 Buckboost converter after Diode Rectifier with equivalent load

The first interval starts when the switch  $S_0$  is turned on. The rectified input voltage is therefore applied to the inductor  $L_{in}$  through the switch  $S_0$ . The bulk capacitor  $C_{dc}$  supplies the power to the output load. The equivalent circuit for this interval is given in Fig. 3.3. Key waveforms of this interval are shown in Fig. 3.6:  $t_0$ - $t_1$ .

Fig. 3.3 Equivalent circuits of buckboost during interval one

The second interval begins with the turn-off of switch  $S_0$ . The energy stored in the inductor  $L_{in}$  is transferred to the buck capacitor  $C_{dc}$  through diode  $D_0$ , see Fig. 3.4. Key waveforms of this interval are shown in Fig. 3.6:  $t_1$ - $t_2$ .

Fig. 3.4 Equivalent circuits of buckboost during interval two

In the third interval, switch  $S_0$  is still off, same as in interval two, but no current is circulating through inductor  $L_{in}$ . Diode  $D_0$  is reverse biased, which means no power is transferred from the input to the output. The bulk capacitor  $C_{dc}$  supplies the load alone, see Fig. 3.5. Key waveforms of this interval are shown in Fig. 3.6:  $t_2$ - $t_3$ .

Fig. 3.5 Equivalent circuits of buckboost during interval three

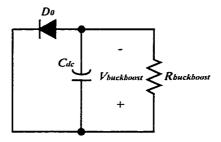

Fig. 3.6 Key waveforms of the Buckboost Converter

### 3.3 STEADY STATE ANALYSIS

# 3.3.1 Duty Cycle and DC B us Voltage

Eq.(3-1) gives the equation for buckboost in DCM, where  $R_{buckboost}$  is the equivalent load of the *Buckboost Converter*.

$$D_{buckboost} = \frac{V_{buckboost}}{V_{in}} \sqrt{\frac{2L_{in} \cdot f_{buckboost}}{R_{buckboost}}}$$

(3-1)

$$D = \frac{\delta}{\pi} \tag{3-2}$$

The turn ratio of Full Bridge Inverter is:

$$N = \frac{N_p}{N_s} \tag{3-3}$$

The relationship between rms output voltage  $V_o$  and DC input voltage  $V_{buckboost}$  of the Full Bridge Inverter is given in Eq.(3-4). The derivation of the equation will be given in section 4.4 and Appendix A1.

$$V_o = \frac{1}{N} \cdot 0.9 \cdot \sin \frac{\delta}{2} \cdot V_{huckhoost} \tag{3-4}$$

The power transferred by the Buckboost Converter equals to that of the output.

$$P_o = P_{buckoost} \cdot \eta \tag{3-5}$$

Hence,

$$\frac{V_{buckboost}^2}{R_{buckboost}} \cdot \eta = \frac{V_o^2}{R_d} \tag{3-6}$$

By substitute (3-4) into (3-6), we can get the expression of the equivalent load of the *Buckboost Converter*.

$$R_{buckhoost} = \frac{V_{buckhoost}^{2}}{V_{o}^{2}} \cdot R_{d} \cdot \eta = \frac{N^{2}}{\left(0.9 \sin \frac{\mathcal{S}}{2}\right)^{2}} \cdot R_{d} \cdot \eta \tag{3-7}$$

From Fig. 2.2, we get the duty cycle of the Buckboost Converter:

$$D_{buckboost} = \frac{1}{m} \cdot D \tag{3-8}$$

The switching frequency of the Buckboost Converter is:

$$f_{buckboost} = \frac{2f_{sw}}{m} \tag{3-9}$$

Substitute Eq.(3-2), (3-4), (3-7), (3-8) and (3-9) into (3-1), we get:

$$D = \frac{V_o}{V_{in}} \sqrt{\frac{4m \cdot L_{in} \cdot f_{sw}}{R_d \cdot \eta}}$$

(3-10)

For a given input and output voltage and load, we can calculate out the duty cycle of the *Full Bridge Inverter* by using Eq.(3-10). Combine Eq.(3-2), (3-4) and (3-10), we can get the DC bus voltage  $V_{buckboost}$ .

$$V_{buckboost} = \frac{NV_o}{0.9 \sin\left(\frac{V_o}{2V_{in}} \cdot \sqrt{\frac{4m \cdot L_{in} \cdot f_{sw}}{R_d \cdot \eta} \cdot \pi}\right)}$$

(3-11)

(3-11) indicates that the DC bus voltage is load dependent and determined by the value of inductor  $L_{in}$ , switching frequency  $f_{sw}$  and  $Gate\ Signal\ Constant\ m$ .

### 3.3.2 Peak Current of the Converter

The peak current through inductor  $L_{in}$  during the  $k^{th}$  interval is given in Eq.(3-12), where n is the number of intervals:

$$i_{Lin. peak, k} = \frac{\left| \sqrt{2V_{in}} \sin(2\pi k / n) \right|}{L_{in}} \cdot \frac{D_{buckboost}}{f_{buckboost}}$$

(3-12)

The maximum peak current through inductor  $L_{in}$  in one line cycle is:

$$i_{Lin, peak, max} = \frac{\sqrt{2V_{in}}}{L_{in}} \cdot \frac{D_{buckboost}}{f_{buckboost}}$$

(3-13)

Substitute Eq.(3-8), (3-9) into Eq.(3-13), we get the maximum input peak current.

$$i_{Lin, peak, \max} = \sqrt{2V_o} \cdot \sqrt{\frac{m}{L_{in} \cdot f_{sw} \cdot R_d \cdot \eta}}$$

(3-14)

### 3.3.3 Boundary between DCM and CCM

The output current of the Buckboost Converter can be expressed as:

$$I_{buckboost} = \frac{V_{buckboost}}{R_{buckboost}} = \frac{V_{buckboost}}{R_d \cdot \eta} \cdot \frac{\left(0.9 \sin \frac{\delta}{2}\right)^2}{N^2}$$

(3-15)

The boundary of the output current of the Buckboost Converter is given below [12]:

$$IOB, buckboost = \frac{V_{buckboost}}{2L_{in} \cdot f_{buckboost}} \cdot (1 - D_{buckboost})^2$$

(3-16)

In order to let the *Buckboost Converter* work in DCM, the output current of it must be smaller than the boundary current.

$$I_{buckhoost} < I_{OB, buckhoost}$$

(3-17)

Substitute Eq.(3-8), (3-9) and (3-15) into Eq.(3-17), we get the equation that judge the *Buckboost Converter* is in DCM or not.

$$\frac{\left(0.9\sin\frac{\delta}{2}\right)^2}{D\left(1-\frac{1}{m}D\right)^2} < \frac{m\cdot N^2\cdot R_d\cdot \eta}{4L_{in}\cdot f_{sw}} \tag{3-18}$$

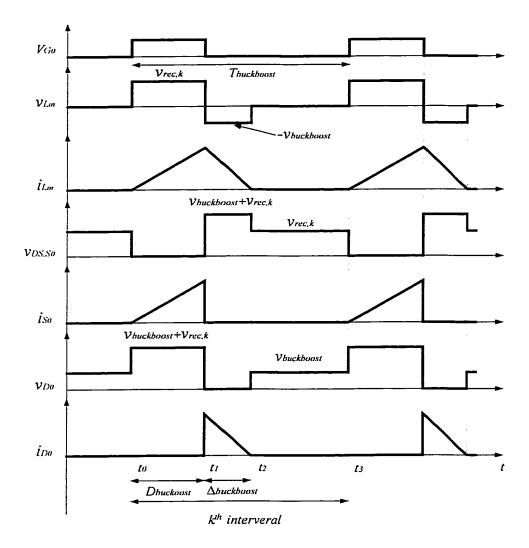

#### 3.4 Performance Characteristics

### 3.4.1 Effect of Load on Performance

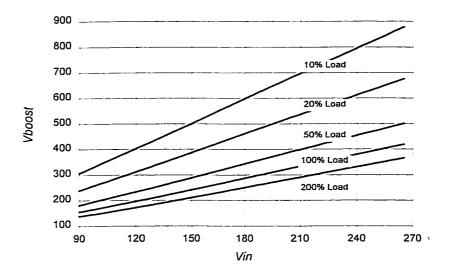

Similar to the *Boost Converter*, the DC bus voltage of the *Buckboost Converter* is load dependent. The DC bus voltage can be very high at light load. Fig. 3.7 and Fig. 3.8 give the characteristics of the DC bus voltage and the duty cycle versus load.

Fig. 3.7 DC bus voltage versus input voltage for various loads (at  $V_o$ =30 $V_{ac}$ ,  $f_{sw}$ =100KHz, N=3,  $L_{in}$ =20uH, m=2)

Fig. 3.8 Duty cycle versus input voltage for various load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ , N=3,  $L_{in}=20uH$ , m=2)

### 3.4.2 Effect of Transformer Turn Ratio on Performance

The effect of transformer turn ratio on the DC bus voltage is given in Fig. 3.9. Fig. 3.10 shows that the duty cycle is independent from the transformer turn ratio.

Fig. 3.9 DC bus voltage versus input voltage for various transformer turn ratio (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=20uH$ , m=2)

Fig. 3.10 Duty cycle versus input voltage for various transformer turn ratio (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=20uH$ , m=2)

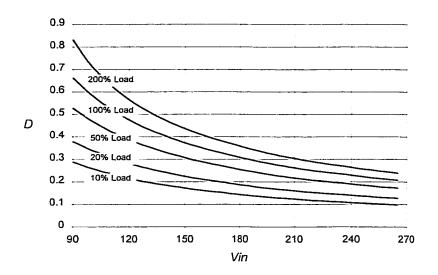

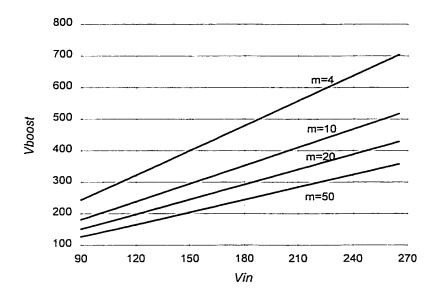

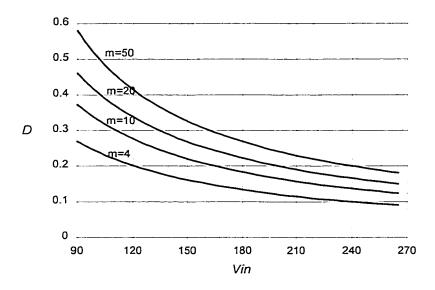

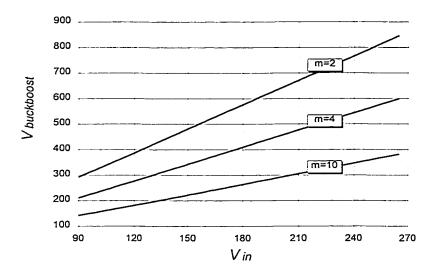

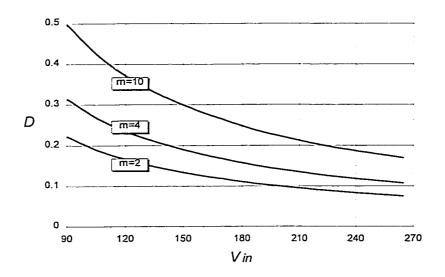

# 3.4.3 Effect of m on Performance

Fig. 3.11 to Fig. 3.14 illustrate the effect of *Gate Signal Constant m* on the DC bus voltage and the duty cycle. Increasing m is the main means to reduce the DC bus voltage at light load. However, for the *Buckboost* implemented PF corrected inverter, m can not be too large. Otherwise, at low line and heavy load, the DC bus voltage can not go high enough to maintain the required output voltage. In this design m is suggested to be 2 or 4.

Fig. 3.11 DC bus voltage versus input voltage for various m at rated load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=20uH$ , N=3)

Fig. 3.12 Duty cycle versus input voltage for various m at rated load (at  $V_o=30V_{ac}$ ,  $f_{sw}=100KHz$ ,  $R_d=3.6\Omega$ ,  $L_{in}=20uH$ , N=3)

Fig. 3.13 DC bus voltage versus input voltage for various m at 10% rated load (at  $V_o$ =30 $V_{ac}$ ,  $f_{sw}$ =100KHz,  $R_d$ =36 $\Omega$ ,  $L_{in}$ =20uH, N=3)

Fig. 3.14 Duty cycle versus input voltage for various m at 10% rated load (at  $V_o$ =30 $V_{ac}$ ,  $f_{sw}$ =100KHz,  $R_d$ =36 $\Omega$ ,  $L_{in}$ =30uH, N=3)

### 3.5 SIMULATION AND EXPERIMENTAL VERIFICATION