INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

**UMI**°

# AUTOMATED TEST GENERATION FROM FORMAL SPECIFICATIONS OF REAL-TIME REACTIVE SYSTEMS

MAO ZHENG

A THESIS

IN

THE DEPARTMENT

OF

COMPUTER SCIENCE

Presented in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy

Concordia University

Montréal, Québec, Canada

APRIL 2002 © MAO ZHENG, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-68212-9

#### **Abstract**

Automated Test Generation from Formal Specifications of Real-Time Reactive Systems

Mao Zheng, Ph.D. Concordia University, 2002

Real-time reactive systems are among the most difficult systems to design and implement because of their size and complex functional and timing requirements. They are often used in safety-critical contexts. Consequently, the correction of such systems must be assured before they are deployed. This thesis addresses the quality assurance of real-time reactive systems through rigorous testing methods. The thesis gives methods to generate test cases from the formal specifications of real-time reactive systems developed in TROMLAB framework.

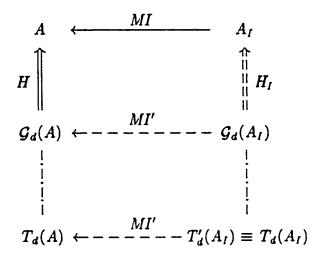

The scope of this thesis encompasses two major components. A Homomorphism Theorem is given that serves as a basis for automated test case generation from the grid automaton associated with the extended state machine formalism. A number of algorithms are also given for generating test cases for black-box testing of reactive class implementations, implementations of class refinements and system configurations. The testing methodologies are theoretically sound, yet being practical for automated test case generation.

To my parents.

### Acknowledgments

I would like to deeply thank my supervisor, Dr. V.S. Alagar. He guided me throughout my study at Concordia University and played a significant role in shaping my research career. His rigorous research attitude and professional shrewdness were fundamental to the success of this research work. Without his wisdom, his unfailing guidance, constant encouragement and insightful comments, this work would not have been possible. I am really fortunate to have had such a great supervisor to go through this long journey.

I am grateful to the TROMLAB research group for thought-provoking discussions.

I thank the faculty, staff and students of the Computer Science Department at Concordia University for providing me with a stimulating, and yet personal environment to work.

I gratefully acknowledge the financial support provided by my supervisor during my study at Concordia University. I also thank Concordia University for awarding me the Graduate Fellowships, International Tuition Fee Remission and Carolyn and Richard Renaud Teaching Assistantship.

On a personal level, I thank my parents and my brother for giving me all the best that anyone can ever ask for. Their love and support accompany me at all times.

I would also like to bring attention to Catherine and Richard who have brought significance to this accomplishment.

### Contents

| Li | st of | igures                                                    | ix |

|----|-------|-----------------------------------------------------------|----|

| Li | st of | ables                                                     | xi |

| 1  | Intr  | duction                                                   | 1  |

|    | 1.1   | Real-Time Reactive System                                 | 1  |

|    | 1.2   | Research Goals                                            | 2  |

|    | 1.3   | Major Contributions and Thesis Outline                    | 4  |

| 2  | TRO   | ILAB - Context of Testing                                 | 7  |

|    | 2.1   | ntroduction                                               | 7  |

|    | 2.2   | TROM Formalism                                            | 10 |

|    |       | 2.2.1 First Tier - Abstract Data Types                    | 11 |

|    |       | 2.2.2 Second Tier - Timed Reactive Object Model           | 11 |

|    |       | 2.2.3 Third Tier - System Configuration Specification     | 16 |

|    | 2.3   | Case Study                                                | 17 |

| 3  | For   | al Basis of Testing UML Models of Real-Time Reactive Sys- |    |

|    | tem   |                                                           | 22 |

|    | 3.1   | ntroduction                                               | 22 |

|    | 3.2   | RTUML Types and Domains                                   | 23 |

|    |       | 3.2.1 Time Semantics                                      | 26 |

|    |       | 3.2.2 Reactive Object Model in RTUML                      | 27 |

|    |       | 3.2.3 Reactive System Model                               | 35 |

|    | 3.3   | Automated Testing of RTUML Models                         | 38 |

| 4 | Rela | ated W  | Vork                                                      | 40 |

|---|------|---------|-----------------------------------------------------------|----|

|   | 4.1  | Introd  | luction                                                   | 40 |

|   | 4.2  | Untim   | ned System                                                | 40 |

|   | 4.3  | Timed   | l System                                                  | 42 |

|   | 4.4  | Comp    | arison With Our Work                                      | 45 |

| 5 | Uni  | t Testi | ing                                                       | 48 |

|   | 5.1  | Introd  | luction                                                   | 48 |

|   | 5.2  | Test A  | Adequacy Criteria                                         | 49 |

|   | 5.3  | Homo    | morphism                                                  | 50 |

|   |      | 5.3.1   | Clock Regions                                             | 50 |

|   |      | 5.3.2   | Definition of Grid Automaton                              | 53 |

|   |      | 5.3.3   | Homomorphism                                              | 55 |

|   |      | 5.3.4   | Homomorphism Theorem                                      | 56 |

|   | 5.4  | Unit 7  | Testing                                                   | 57 |

|   |      | 5.4.1   | Algorithm GA: Grid Automaton Construction                 | 57 |

|   |      | 5.4.2   | The complexity of the algorithm GA                        | 58 |

|   |      | 5.4.3   | Example                                                   | 59 |

|   |      | 5.4.4   | Algorithm TC: Generating Test Cases from a Grid Automaton | 59 |

| 6 | Tes  | ting D  | Perived Classes                                           | 63 |

|   | 6.1  | Introd  | duction                                                   | 63 |

|   | 6.2  | Conce   | ept of Inheritance in TROM                                | 64 |

|   | 6.3  | Behav   | vioral Inheritance                                        | 67 |

|   |      | 6.3.1   | Attribute Redefinition                                    | 68 |

|   |      | 6.3.2   | Transition Redefinition                                   | 69 |

|   |      | 6.3.3   | Time-constraint Redefinition                              | 69 |

|   |      | 6.3.4   | Example                                                   | 72 |

|   | 6.4  | Exten   | sional Inheritance                                        | 74 |

|   |      | 6.4.1   | State Redefinition                                        | 75 |

|   |      | 6.4.2   | Attribute Addition                                        | 76 |

|   |      | 6.4.3   | Event Addition, State Addition and Transition Addition    | 76 |

|   |      | 6.4.4   | Time-constraint Addition                                  | 76 |

|   |      | 6.4.5   | Example                                                   | 77 |

| 6.5 Polymorphic Inheritance |       |                                          | orphic Inheritance                                         | 81  |  |

|-----------------------------|-------|------------------------------------------|------------------------------------------------------------|-----|--|

|                             |       | 6.5.1                                    | Attribute Addition                                         | 81  |  |

|                             |       | 6.5.2                                    | Other Additions                                            | 81  |  |

|                             |       | 6.5.3                                    | Example                                                    | 82  |  |

|                             | 6.6   | Param                                    | neterized Events and General Inheritance                   | 86  |  |

|                             |       | 6.6.1                                    | Parameterized Events                                       | 86  |  |

|                             |       | 6.6.2                                    | General Inheritance                                        | 87  |  |

| 7                           | Sys   | tem Te                                   | esting - I                                                 | 95  |  |

|                             | 7.1   | Introd                                   | luction                                                    | 95  |  |

|                             | 7.2   | Pair T                                   | Testing: Testing a pair of Objects                         | 95  |  |

|                             |       | 7.2.1                                    | Algorithm for Constructing the Synchronous Product Machine | 96  |  |

|                             | 7.3   | Exam                                     | ple                                                        | 99  |  |

| 8                           | Sys   | tem T                                    | esting - II                                                | 101 |  |

|                             | 8.1   | Introd                                   | luction                                                    | 101 |  |

|                             | 8.2   | Synch                                    | ronous Product for a System                                | 102 |  |

|                             | 8.3   | Partition Algorithm                      |                                                            |     |  |

|                             | 8.4   | Test Cases for Components in a Partition |                                                            |     |  |

|                             |       | 8.4.1                                    | Grid-synchronous Product                                   | 107 |  |

|                             |       | 8.4.2                                    | Constructing Grid-synchronous Product                      | 109 |  |

|                             |       | 8.4.3                                    | Grid-synchronous Product Theorems                          | 113 |  |

|                             |       | 8.4.4                                    | Test Case Generation for a Component                       | 115 |  |

|                             | 8.5   | Test (                                   | Case Generation for System                                 | 115 |  |

| 9                           | Cor   | aclusio                                  | o <b>n</b>                                                 | 118 |  |

|                             | 9.1   | Test (                                   | Case Generation and Systematic Testing                     | 118 |  |

|                             | 9.2   | Sumn                                     | nary of Contributions and Future Work                      | 121 |  |

| В                           | iblio | graphy                                   | <i>r</i>                                                   | 124 |  |

## List of Figures

| 1  | TROMLAB Architecture                                      | 7  |

|----|-----------------------------------------------------------|----|

| 2  | Process Model for Developing Complex Reactive Systems     | 9  |

| 3  | Overview of TROM Methodology                              | 10 |

| 4  | LSL Trait for Set                                         | 12 |

| 5  | Anatomy of a Reactive Object                              | 13 |

| 6  | Template for Class Specification                          | 14 |

| 7  | Formal Specification of Class Arbiter                     | 15 |

| 8  | Template for System Configuration Specification           | 16 |

| 9  | Class Diagram for Train, Gate, and Controller Entities    | 18 |

| 10 | Formal Specification for GRC Controller                   | 19 |

| 11 | Statechart Diagram for Controller                         | 19 |

| 12 | Formal Specification for GRC Train                        | 20 |

| 13 | Statechart Diagram for Train                              | 20 |

| 14 | Formal Specification for GRC Gate                         | 20 |

| 15 | Statechart Diagram for Gate                               | 20 |

| 16 | Formal Specification for Train-Gate-Controller Subsystem  | 21 |

| 17 | Collaboration Diagram for 5 Train - 2 Gate - 2 Controller | 21 |

| 18 | RTUML and Automated Testing                               | 39 |

| 19 | Clock Regions                                             | 52 |

| 20 | Grid Automaton for a Time Constrained Transition          | 59 |

| 21 | Grid Automaton for Train                                  | 60 |

| 22 | Grid Automaton for Controller                             | 61 |

| 23 | Grid Automaton for Gate                                   | 61 |

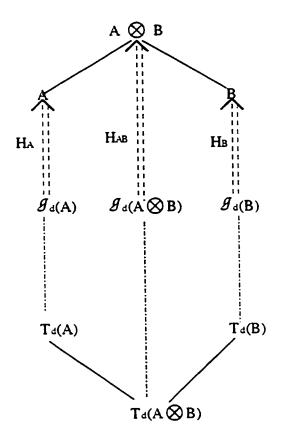

| 24 | The Principle of Inheritance                              | 66 |

| 25 | Class Specification of Channel                            | 72 |

| 26 | Class Specification of OrdChannel                         | 73 |

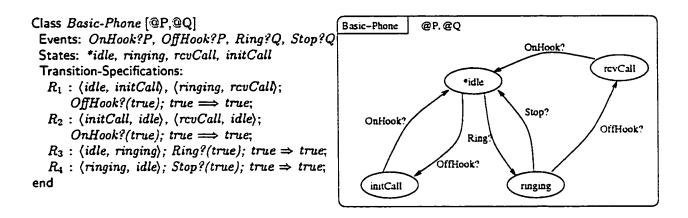

| 27         | Class Specification of Basic-Phone                | 78  |

|------------|---------------------------------------------------|-----|

| 28         | Class Specification of Answer-Phone: Enhancement  | 79  |

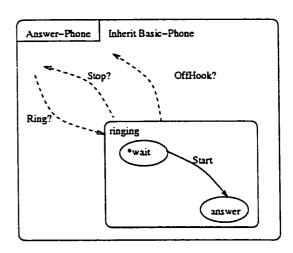

| 29         | Grid Automaton of ringing-machine                 | 79  |

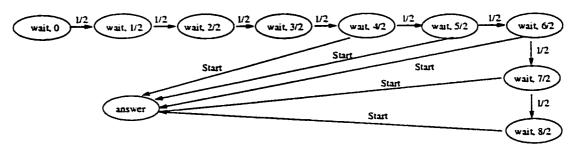

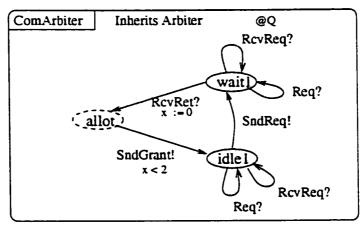

| <b>3</b> 0 | Class Specifications of the Communicating Arbiter | 83  |

| <b>3</b> 1 | Grid Automaton of Rem <sub>P</sub>                | 85  |

| 32         | Arbiter State Diagram                             | 88  |

| 33         | Formal Specification for GRC Arbiter-Simple       | 89  |

| 34         | Arbiter StateChart Diagram                        | 92  |

| 35         | Formal Specification for GRC Arbiter              | 93  |

| 36         | Formal specification for GRC Arbiter-Continued    | 94  |

| 37         | Temporal Predicates                               | 97  |

| 38         | Synchronous Product of Train and Controller       | 100 |

| 39         | Synchronous Product of Controller and Gate        | 100 |

| 40         | An Example of System Configuration                | 102 |

| 41         | $(Train \otimes Controller) \otimes Gate \dots$   | 103 |

| 42         | A General Architecture                            | 106 |

| 43         | The Architecture of Train-Gate-Controller System  | 106 |

| 44         | Principle of Grid-Synchronous Product             | 108 |

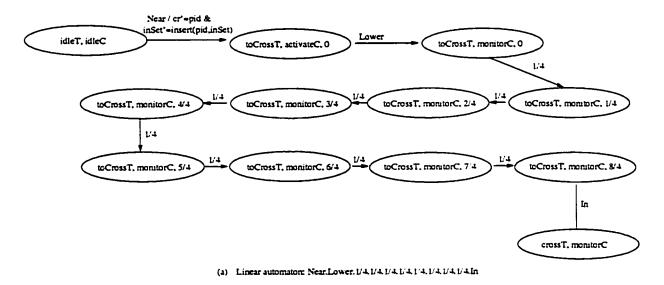

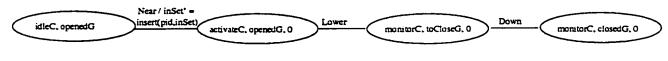

| 45         | Two Linear Automata                               | 112 |

| 46         | The Role of an Oracle                             | 120 |

### List of Tables

| 1 | Possible States of the Arbiter Class   | 90 |

|---|----------------------------------------|----|

| 2 | Definitions of the Temporal Predicates | 9€ |

### Chapter 1

### Introduction

### 1.1 Real-Time Reactive System

The term reactive was introduced by Harel and Pnueli [HP85] to designate systems that continuously interact with their environment through stimulus and response. The term reactive also distinguishes the stimulus and response synchronizations in reactive systems from those that are available in *interactive* and *transformational* systems. The real-time behavior of a reactive system is regulated by time and persists across some interval of time during which it responds to inputs as they occur. Two important properties characterize real-time reactive systems:

- stimulus synchronization: the process always reacts to a stimulus from its environment;

- response synchronization: the time elapsed between a stimulus and its response is acceptable to the relative dynamics of the environment, so that the environment is still receptive to the response.

A real-time system is a software system that maintains an ongoing and timely interaction with its environment. The behavior of a real-time reactive system encompasses concurrency, communication through sensors and actuators, and relations between input and output over time. Such systems often operate in *safety-critical* contexts, with applications in control systems for nuclear reactors, air traffic, rail-road crossings, telecommunications, and medicine. In safety-critical applications,

the consequences of failure are extremely high, usually with a threat to human life. Safety-critical systems are expected to perform as desired and should never fail.

Generally, the behavior of a reactive system is *infinite*: the process in a reactive system is usually continuously responding to the stimuli from its environment. The correct behavior of non-real time systems is founded on the *functional correctness* of the result. By contrast, real-time reactive systems require both the functional correctness of the result and its *timing correctness*. Hence, *safety* of such systems, which concerns prevention of risks to human life or property, relies on good analysis of the functional and timing properties of those systems. Nevertheless, real-time reactive systems are large and complex and consequently understanding or describing the behavior of such systems becomes very difficult.

In recent studies [RP95], formal methods have been applied to manage the complexity in modeling and implementing real-time reactive systems. Software-development techniques based on mathematics are called formal methods, and they are beginning to become both practical to apply and capable of providing substantial improvements in software quality. Two broad categories of techniques for assuring high-quality software are *formal verification* [Mut00] and *testing* [BG93, Heg89]. Although formal verification is based on a sounder theoretical foundation than testing, it is generally considered impractical to formally verify large complex software products. Therefore testing has remained the most commonly used technique for ensuring software quality.

#### 1.2 Research Goals

The goal of this research is the investigation of testing methods for real-time reactive systems founded on formal methods. Softwares that operate and control safety-critical applications must be thoroughly tested before the software is installed in the operational environment. This thesis proposes a testing methodology based on the formal software specification and gives algorithms for automated test case generation of real-time reactive systems. We provide a theoretical basis to justify the algorithms for test case generation and propose methods for efficiently implementing them.

The factors that contribute to the complexity of real-time reactive systems include largeness, concurrency, time constraints on stimuli and responses, complex sequencing of events, and an incomplete knowledge of the environment wherein it is supposed to be embedded. The complexity of the system permeates from requirement analysis to design, verification, implementation and testing. Time constraints, in addition to functionality, must be correctly carried through design refinements. The design must be verified for safety properties and validated for time-dependent functionalities. Verification deals with the specification of the system under consideration and aims to ensure that design specification satisfies predefined functional and timing requirements. A mechanical verification approach for reactive systems, proposed by Muthiayen and Alagar [MA99], complements the testing method discussed in this thesis.

The goal of testing is to uncover errors and improve the quality of software. An implementation of a system that has been formally verified for safety properties should still be tested. This is to guard against the errors due to resource constraints that might forbid the timed behavior at certain instances in the operational environment of the software. In this thesis, a black-box testing approach is investigated, limited to generating test cases from formal specifications. This approach is conformance-directed, therefore the intent is to provide a method for system developer to demonstrate conformance of the implementation to the design specification. Conformance-directed testing need not consider potential implementation faults in detail, but must establish that a test suite is sufficiently representative of the properties/features for a system. It is our view that black-box testing can adequately complement formal verification and validation effort in assuring an acceptable level of accuracy in an implementation.

Black-box testing relies on the quality of the specification of the system under test. If the specification is loose, the effectiveness of testing will be weak. Usually the results obtained from an implementation are compared with an oracle and the correctness of the implementation is certified only when they match in all test cases. When a good formal specification of the system is available, it can be used both as an oracle and a medium to generate test cases. The motivation for this research work comes from the following considerations:

• The correctness and safety requirements of real-time reactive systems must be assured in a safety-critical context. Test cases generated from a design that correctly incorporates the safety requirements are sufficient to certify the safety in an implementation.

- The object-oriented software development life cycle and its artifacts adopted by Timed Reactive Object Model (TROM) formalism [Ach95] are different from traditional real-time software development practices. Traditional software testing does not apply directly to object-oriented software.

- There is considerable value added to the entire development process when a rigorous testing is correctly combined with software development.

- There is an inherent limitation of formal verification for real-time reactive systems: methods based on model checking and theorem proving have exponential time complexity even when the model of time is discrete.

- Although specification-based testing methods for untimed systems have been studied in depth, not much work has been done for rigorous testing of timed systems. We take up the discussion on related work in Chapter 4.

### 1.3 Major Contributions and Thesis Outline

In this thesis, a methodology is given for testing real-time reactive systems developed in TROMLAB [AAM98] framework. The methodology includes methods for testing classes (unit testing), refinements of classes (inheritance testing), and system configurations (system testing). The methodology, although strictly follows TROM formalism, is adaptable for testing real-time reactive systems whose behavior can be abstracted as timed labeled transition systems.

Since the behavior of a real-time reactive system may be infinite, testing its behavior is a non-trivial problem. The significance of the research reported in this thesis lies in construction of a grid automaton with finite number of states and whose behavior can be homomorphically mapped to the infinite timed behavior of the labeled transition system that models the behavior of a reactive class. This construction provides the basis for an algorithm to generate test cases for unit testing.

Chapter 2 reviews TROMLAB, an environment for developing real-time reactive systems according to TROM formalism and gives the context of the research described in this thesis. Test case generation algorithms and a test driver for injecting test cases into a Java implementation are being integrated with the automatic code generation tool [Zha00]. Chapter 3 reviews TROM formalism and Real Time UML

(RTUML) [Mut00] to illustrate that UML models of reactive systems consistent with TROM formalism can be constructed. The motivation here is twofold: to introduce TROM formalism on which the testing methodology is founded, and to suggest that our testing methodology is applicable to UML models of reactive systems that have TROM as the semantic basis. Chapter 4 provides a survey of related work on testing real-time reactive systems with particular emphasis on black-box testing. Although a number of methods have been reported for testing object-oriented softwares, no efficient method has been reported yet for a rigorous testing of real-time reactive systems. Chapter 5 contains several major results:

- Test Adequacy: Two test adequacy criteria are given. These are used in test case generation algorithms.

- Homomorphism: A homomorphism theorem is stated as the basis for the construction of a finite state grid automaton.

- Algorithms: Algorithms are given for generating sufficient number of test cases for a reactive class.

Chapter 6 provides methods for incrementally generating test cases for inherited classes. Three forms of inheritance are defined in [Ach95]. Chapter 7 gives an algorithm for generating test cases for testing a system configured with two interacting objects that are instances of classes for which test cases have already been generated. The algorithm involves two steps:

- the synchronous product machine of the two instantiated objects is constructed, and

- test cases are generated from the grid automaton of the synchronous product machine.

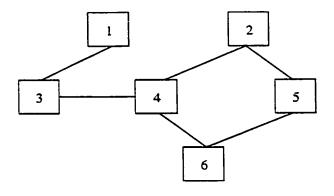

Chapter 8 discusses a method for minimizing the complexity of testing a real-time reactive system composed with  $n \ (n > 2)$  objects. The system configuration is decomposed into smaller components in such a way that

- each component, abstracted as a directed graph, is complete,

- the combined behavior of the components is equivalent to the behavior of the whole system.

An algorithm is given for generating test cases of the whole system as a composition of test cases generated for smaller components. The crucial step is in the utilization of the test cases generated for pairs of interacting objects in generating test cases for each component. Chapter 9 concludes the thesis with a discussion of future directions of research.

### Chapter 2

### TROMLAB - Context of Testing

#### 2.1 Introduction

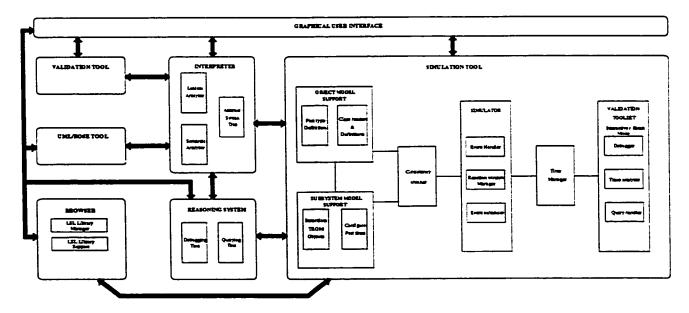

The research work reported in this thesis has been done in the context of TROM-LAB [AAM98], a formal framework for rigorous development of real-time reactive systems. The prototype TROMLAB environment, shown in Figure 1, has been constructed over the last six years and used as a testbed for real-time reactive systems development.

Figure 1: TROMLAB Architecture

The following components of TROMLAB are currently operational:

- Interpreter [Tao96] A parser, syntax checker and internal representation constructor:

- Simulator [Mut96] A tool that simulate a subsystem based on the internal representation and enables a systematic validation of the specified system;

- Browser [Nag99] A tool that help users navigate, query and access various system components for reuse during system development;

- UML-RT Support [Pop99] A translator to generate TROM specification from Real-time UML;

- Verification Assistant [Pom99] A tool to generate PVS theory from TROM specification for proving timing properties;

- Graphical User Interface [Sri99] A visual modeling and interaction facility for a developer using the TROMLAB environment;

- Reasoning System [Hai99] A tool to provide a means of debugging the system during animation by facilitating interactive queries of hypothetical nature on system behavior.

- Code Generator [Zha00] It automatically generate Java code from TROM specifications.

The testing tool built as part of this thesis will be integrated with the interpreter, the code generator, and the metrics tool being built by Ormandjieva [Orm02].

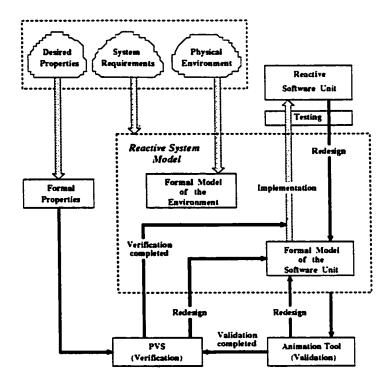

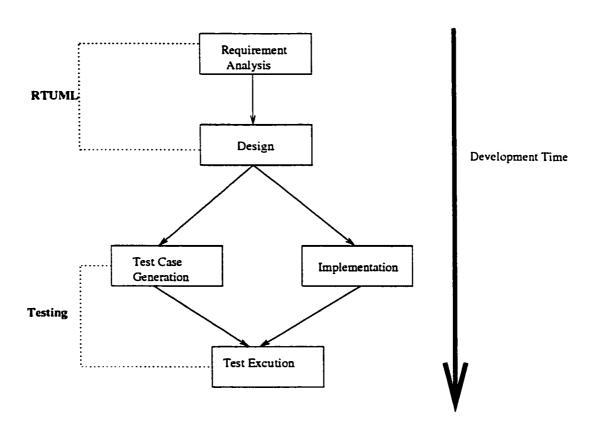

Software development activity in TROMLAB framework, assisted by the above tools, is carried out according to TROM formalism, integrated in the process model shown in Figure 2. The primary distinction between traditional process models and the process model of TROMLAB is in the integration of rigorous methods through the different stages of development. The Graphical User Interface provides complete transparency of the formalism to software developers in the framework.

The process model requires a formal model of the environment to be produced and integrated with system elements. Environment objects are abstracted and their interface to system elements are formally defined. System requirements which include functional and timing requirements are identified and their formal descriptions are produced. A reactive system model is composed from the software unit and the model

Figure 2: Process Model for Developing Complex Reactive Systems

of the environment. Integration of Rational Rose with initial stages of model building activities enables the construction of visual models of reactive systems.

The formal model of the reactive unit is not implemented until several iterations of design take place. Validation is done by animating the reactive system design. Simulation and reasoning are two techniques used to debug the design and predict its behavior. Simulation and reasoning tools use the formal model and hence is independent from any implementation constraints such as resource and process speed. This experimentation gives better insight into what the crucial properties of the design are and how these are directly related to the requirements. If flaws due to incorrect functions or inconsistent timing behavior are noticed during system simulation and reasoning, the process model allows an iterative inner cycle for redefining the formal model of the reactive unit and validating it.

System verification takes place at the next stage of the process model. Time critical properties, such as safety properties, are verified formally at this stage. The system design is mechanically translated to a set of PVS theories consisting of axioms describing the timed behavior of the system. The desired properties are formalized and are included as lemmas in PVS theories. A mechanized verification procedure

is discussed in [Mut00]. An iterative cycle enables redesigning the system when the design does not satisfy the desired properties.

Test suits are generated from the verified and validated design specification, and are independent from implementation decisions. In TROMLAB framework black-box testing is used to test the conformance of the code generated by [Zha00] with respect to the verified and validated design specifications. Thus, the generated code certified by the black-box testing can be trusted to conform to the initial requirements.

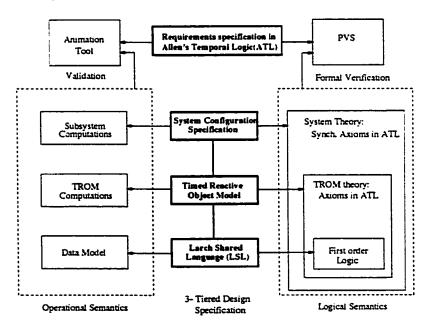

#### 2.2 TROM Formalism

In this section we review TROM formalism [Ach95] which is founded on merging object-oriented and real-time technologies. Our testing approach is modular to suit the TROM formalism's abstract three-tiered structure. Figure 3 shows the three-tiered structure of the TROM methodology. Abstract models from a lower tier can be included in upper tiers. The formalism is sufficiently expressive for modeling large real-time reactive systems.

Figure 3: Overview of TROM Methodology

#### 2.2.1 First Tier - Abstract Data Types

Abstract data types and theories can be specified in the first tier in Larch [GH93] style. For instance, the abstract data type Set is defined by the LSL (Larch Shared Language Trait) in Figure 4. The different sections of a trait define included traits, the signature for operations on the sort defined by the trait, the assertions constraining the operations, and the logical consequences that can be inferred from the assertions. In Figure 4, the *introduces* clause declares a set of operators, each with its signature (the sorts of its domain and range). The body of the trait contains, following the asserts clause, equations between terms containing operations and variables. The generated by clause states that all values of sort C can be represented by terms  $\{\}$  and insert. The operators listed in the partitioned by clause are sufficient to distinguish unequal set values. The implies section describes additional properties of sort C that follow from the assertions part. The theory of a trait is the set of all logical consequences of its assertions. It contains everything that logically follows from its assertions, but nothing else. All operators listed in the converts clause are defined for terms in their domains in the exceptions noted in the exempting clause.

The Larch language supports a family of *Interface Specification* languages. Each interface specification language is designed for a specific programming language. For instance Larch/C++ [GH93], the interface specification language for C++ programming language, can be used to specify how C++ class interfaces must be invoked by a client program. An implementation of a data type specification is thus linked to the interface specification. Based on LSL traits and Larch/C++ interface specifications Celer [AC95] and Protopsaltou [Pro96] have given black-box testing methods for data type implementation. The code generator implemented by Zhang [Zha00] uses a small Larch/Java interface specification language while mechanically generating Java code in TROMLAB framework. The test suit generation methods discussed in this thesis will assume that data type implementations have been tested by the above methods.

### 2.2.2 Second Tier - Timed Reactive Object Model

A TROM defines a Generic Reactive Class (GRC) parameterized with port types. A port type is an abstract interface defining the set of messages (events) that can be received or sent by an object of the class at a port of this type. The signature of a port-type P gives the set of events that can occur at the port-type P, denoted by  $\mathcal{E}^P$ ,

```

Set(E,C): trait

% Essential finite-set operators

includes Integer

introduces

\{\}: \to C

insert: E, C \rightarrow C

\_ \in \_ : E, C \rightarrow Bool

delete: E, C \rightarrow C

asserts

C generated by {}, insert

C partitioned by \in

\forall s: C, e, e_1, e_2: E

\overline{\phantom{a}}(e \in \{\})

e_1 \in insert(e_2, s) == e_1 = e_2 \lor e_1 \in s

delete(e_1, insert(e_2, s)) == if(e_1 = e_2) then s

else insert(e_2, delete(e_1, s))

implies

\forall e, e_1, e_2 : E, s : C

insert(e, s) \neq \{\}

insert(e, insert(e, s)) == insert(e, s)

insert(e_1, insert(e_2, s)) ==

insert(e_2, insert(e_1, s))

converts \in, delete

exempting \forall x : E

delete(x, \{\})

```

Figure 4: LSL Trait for Set

$\mathcal{E}^P = \mathcal{E}_{in}^P \bigcup \mathcal{E}_{out}^P$ , where  $\mathcal{E}_{in}^P$  is the set of input events,  $\mathcal{E}_{out}^P$  is the set of output events, and  $\mathcal{E}_{in}^P \bigcap \mathcal{E}_{out}^P = \emptyset$ . Message exchange can occur only between compatible ports. Two port type P and Q are *compatible* if

- $e? \in \mathcal{E}_{in}^P \Leftrightarrow e! \in \mathcal{E}_{out}^Q$

- $e! \in \mathcal{E}_{out}^P \Leftrightarrow e? \in \mathcal{E}_{in}^Q$

A GRC may include attributes of two kinds: (1) abstract data types imported from the first tier, and (2) port types. The attribute functions define the association of attributes to states. For each state, the attribute function defines a subset of attributes that are active in the state. For a computation associated with a transition entering a state, only the attributes associated with that state are modified and all other attributes will be read-only in that computation.

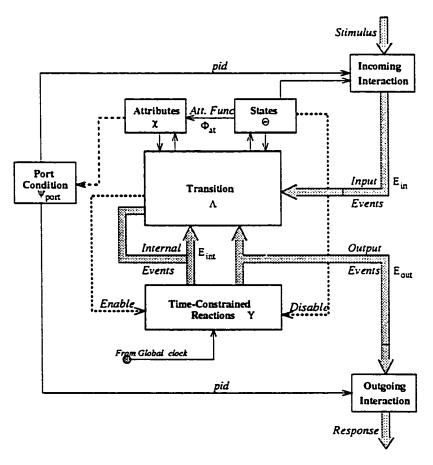

The semantic model of reactive objects belonging to a GRC is a timed labeled transition system, extended with hierarchical states, logical assertions involving clock variables and variables of included traits. A transition between two states is specified by a guard and an action. A guard is a conjunction of two predicates, one specifying the port-condition for the event labeling the transition, and the other specifying the enabling condition on the attributes in the pre-state of the transition. An action is specified as a predicate involving the attributes in the post-state of the transition. A clock may be initialized as part of an action, if the event labeling the transition triggers a future action. The guard of a constrained transition will include a predicate involving clock variables and time constants.

Figure 5: Anatomy of a Reactive Object

Figure 5 shows the behavior of a reactive object. The filled arrows in the figure indicate flow of events. An input event (?) is the result of an incoming interaction defined by the external stimulus, the current state of the object, and the port constrained by the port-condition. Every event occurrence causes a state transition

and may also involve a computation. A computation updates the object's state and attributes, shown by the arrow labeled 'Att. Func.'. The dotted arrow connecting the block of computation to that of time-constrained reaction signifies the enabling of a reaction due to a computation. Based on the reading of the clock, an outstanding reaction is fired by the object, thereby generating either an internal event or an external event. All generated output events (!) will result as a response at the port specified by the port-condition. A state update may also result in the disabling of an outstanding reaction. A formal definition of TROM and its semantics appear in [Mut00]. Figure 6 shows the template for a generic reactive class specification.

```

Class < name >

Events:

States:

Attributes:

Traits:

Attribute-Function:

Transition-Specifications:

Time-Constraints:

end

```

Figure 6: Template for Class Specification

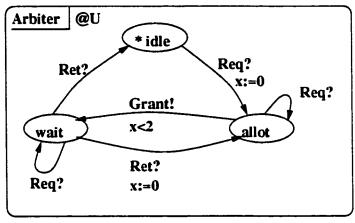

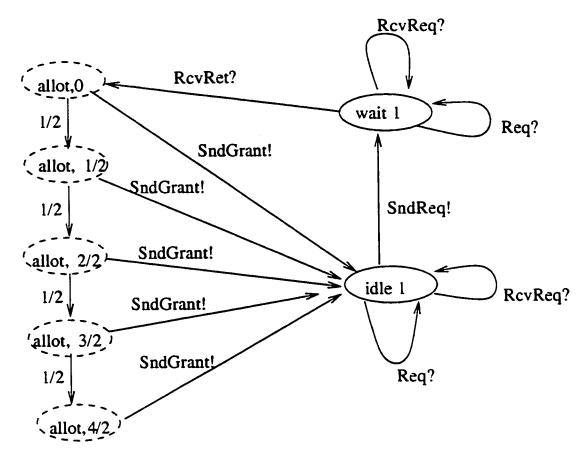

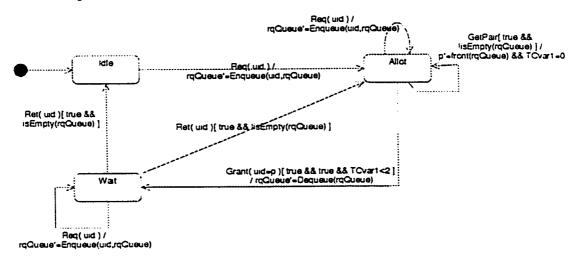

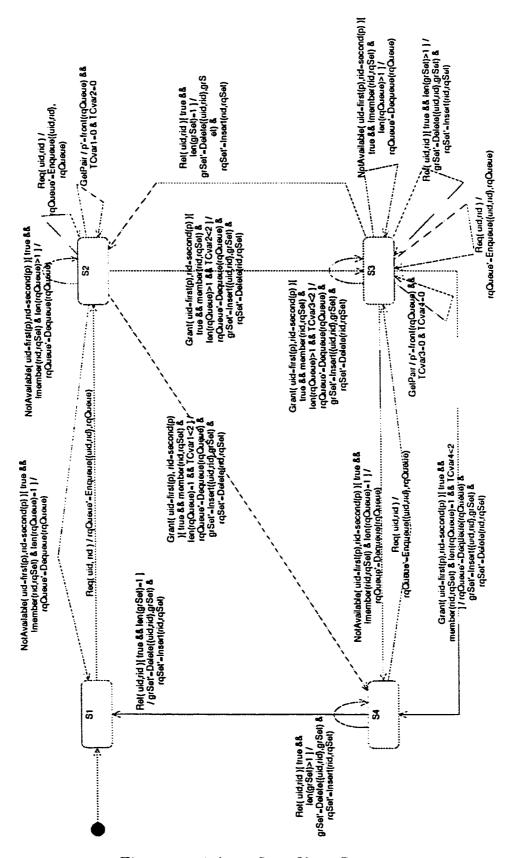

Figure 7 is an example of the formal specification of the TROM class Arbiter. An arbiter allocates shared resources to processes requesting them. It enqueues the requests for a resource received from processes and allocates the resource to the next process waiting in the queue. The specification uses the functions *insert* and *tail* from the trait Queue(@U, UQueue), imported by the Arbiter class, to add and delete requests made at a port of type @U. The attribute hold in class Arbiter denotes the most recent port at which the resource was granted. The output event Grant! is time constrained and must occur within 2 time units from the instant the input events Req? and Ret? have occurred.

The algorithms for testing the correctness of a class implementation are based on the semantics of TROM formalism. The two important requirements for conformance are the following:

• Every state in the design specification must be observable in the implementation: the attribute values and outstanding reactions in an implemented program

```

Class Arbiter [@U]

Events: Req?U, Grant!U, Ret?U

States: *idle, allot, wait

Attributes: rqQueue: UQueue; hold:@U

Traits: Queue/@U, UQueue/

Attribute-function:

allot \mapsto rqQueue; wait \mapsto rqQueue, hold;

Transition-Specifications:

R_1: (idle, allot); Req?(true);

true \Longrightarrow rqQueue' = insert(pid, \{\});

R_2: \langle allot, wait \rangle; Grant!(pid \in rqQueue);

true \Longrightarrow rqQueue' = tail(reQueue)) \land (hold' = pid);

R_3: \langle allot, allot \rangle, \langle wait, wait \rangle; Req?(not pid \in rqQueue);

true \Longrightarrow rqQueue' = insert(pid, rqQueue);

R_4: \langle wait, allot \rangle; Ret? (pid hold);

isEmpty(rqQueue) \implies equal(rqQueue', rqQueue);

R_5: (wait, idle); Ret? (pid = hold);

isEmpty(rqQueue) \Longrightarrow true;

Time-Constraints:

TC_1: (R_1, Grant, [0,2], \emptyset)

TC_2: (R_4, Grant, [0,2], \emptyset)

end

```

Figure 7: Formal Specification of Class Arbiter

must match the specification.

• Every transition in the state machine description of the design must have an implementation: the abstract computation specified in the action part must have a correct implementation.

#### 2.2.3 Third Tier - System Configuration Specification

A system configuration is the collaboration of a finite number of objects instantiated from the second tier. Objects collaborate through message passing. Only compatible ports of collaborating objects can exchange messages. The specification template shown in Figure 8 has three sections:

```

Subsystem < name >

Include:

Instantiate:

Configure:

end

```

Figure 8: Template for System Configuration Specification

Include Predefined subsystems are included in the Include section. Ports that are free in the included subsystems may be linked to ports of objects instantiated in the subsystem being defined.

Instantiate Reactive objects are instantiated from the GRCs defined in the second tier. An instantiation has the syntax (c: X[@P:3,@Q:2]). The effect of this declaration is the creation of object c having three ports  $p_1, p_2, p_3$  of type @P, and two ports  $q_1, q_2$  of type @Q from class X.

Configure Object collaboration is specified by defining links between compatible ports of instantiated objects and objects in the included subsystem. The syntax for defining a communication link between the port  $p_1$  (type P) of object P0 and the port P1 (type P3) of object P3 is P4. P5 of object P5 of object P6 is P7.

A formal operational semantics for system configurations is given in [Mut00]. The semantics is based on system traces, sequences of computational paths in the

synchronous product of the state machines associated with the objects in the system configuration. Our test algorithms generate test cases that are valid partial traces, inject them in an implementation and check whether the state information and time constrained reactions are timely, as specified.

### 2.3 Case Study

In this section, we introduce the railroad crossing problem, and will use it as a running example throughout this thesis to illustrate our testing methodology.

The railroad crossing problem has been considered as a bench mark example by researchers in real-time systems community [HM96]. A generalized version of this problem has been considered by Muthiayen and Alagar [MA99] to formally prove safety properties in their design. We take their verified design and generate test cases to test the correctness of code generated by Zhang [Zha00].

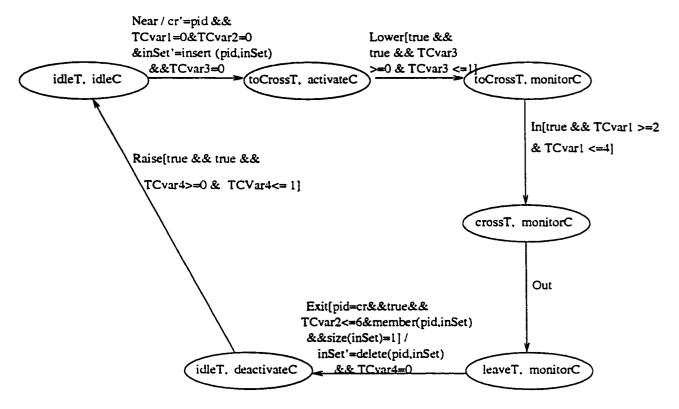

According to their design, several trains cross a gate independently and simultaneously using non-overlapping tracks. A train chooses the gate it intends to cross; there is a unique controller monitoring the operations of each gate. When a train approaches a gate, it sends a message to the corresponding controller, which then commands the gate to close. When the last train crossing a gate leaves the crossing, the controller commands the gate to open. The safe operation of the controller depends on the satisfaction of certain timing constraints, so that the gate is closed before a train enters the crossing, and the gate is opened after the last train leaves the crossing.

A train enters the crossing within an interval of 2 to 4 time units after having indicated its presence to the controller. The train informs the controller that it is leaving the crossing within 6 time units of sending the approaching message. The controller instructs the gate to close within 1 time unit of receiving an approaching message from the first train entering the crossing, and starts monitoring the gate. The controller continues to monitor the closed gate if it receives an approaching message from another train. The controller instructs the gate to open within 1 time unit of receiving a message from the last train to leave the crossing. The gate must close within 1 time unit of receiving instructions from the controller.

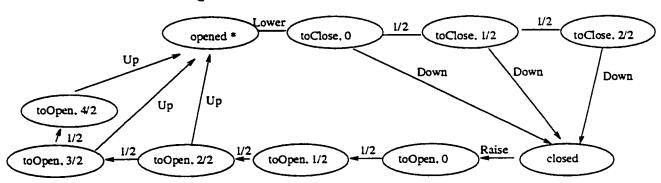

The gate must open within an interval of 1 to 2 time units of receiving instructions from the controller.

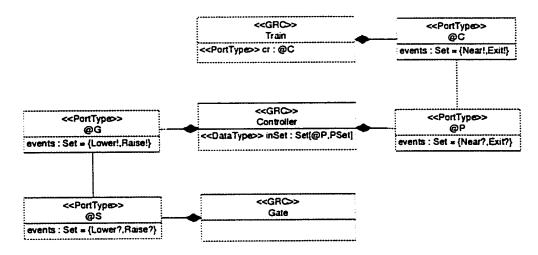

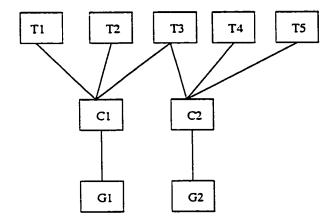

Figure 9: Class Diagram for Train, Gate, and Controller Entities

Figure 9 shows the class specification for the Train-Gate-Controller system. An input event is decorated with the suffix? and an output event is decorated with the suffix!. The port types for reactive classes and the events associated with the port types are shown. The associations between the Port Type classes indicate communication channels between instances of the GRC classes.

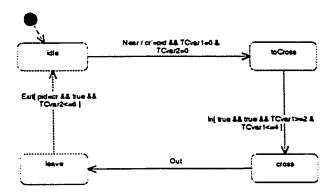

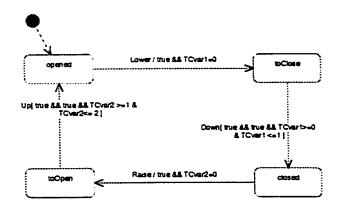

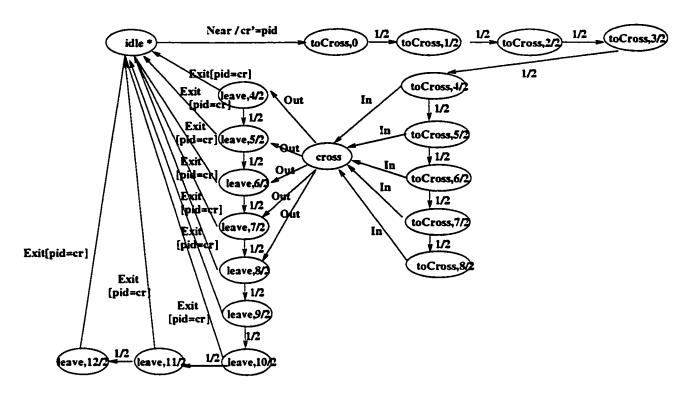

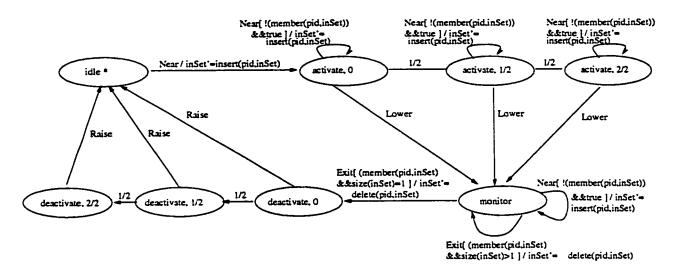

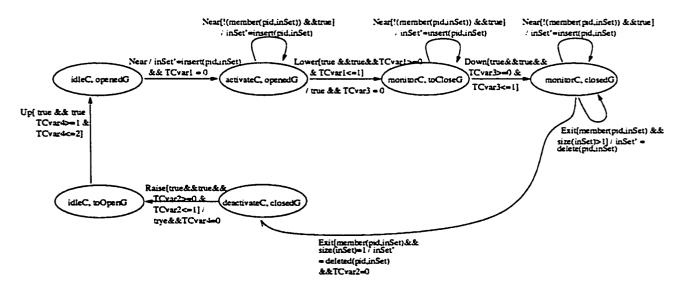

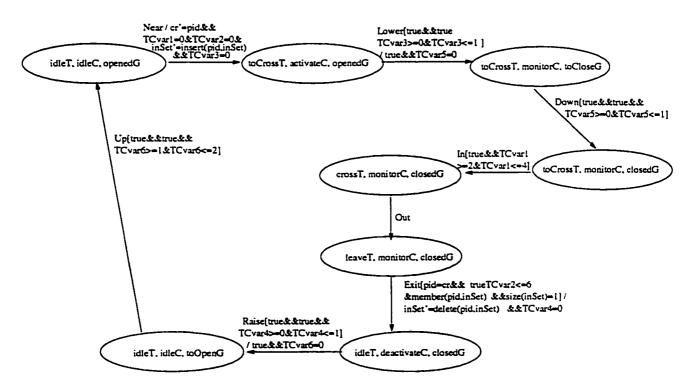

Figures 11, 13, 15 show the statechart diagrams for the controller, train and gate. Together, they specify the behavior of a Train-Gate-Controller system. When there is no train in the system, the train is in the idle state, the controller is in the idle state, and the gate is in the opened state. When a train wants to pass through a crossing, it sends the message to the controller, the train and controller change their states simultaneously. In the state activate, the controller may receive "Near" messages from other trains or it sends the message "lower" to the gate. In the latter case, the controller and gate change their states simultaneously. In the state monitor, the controller continues to receive "Near" messages from other trains or monitor the gate. The train which is in the crossing may send an "Exit" message to the controller before exiting the gate. Both the controller and the train synchronize on the event "Exit". The train leaves the gate within 6 unit of time from the instant originally sends the

```

Class Controller [@P, @Y]

Events: Lower!@Y, Near?@P, Raise!@Y, Exit?@P

States: *idle, activate, deactivate, monitor

Attributes: inSet:PSet

Traits: Set[@P,PSet]

Attribute—Function:

\{inSet\}; deactivate \rightarrow \{inSet\}; idle \rightarrow \{\};

activate →

{inSet};

Set-mantipet,ii

$$TC-ert-0

monitor →

Transition-Specifications:

R1: <activate,monitor>; Lower(true);

true => true;

R2: <activate,activate>; Near(NOT(member(pid,inSet)));

true => inSet' = insert(pid,inSet);

R3: <deactivate,idle>; Raise(true);

true => true:

R4: <monitor,deactivate>; Exit(member(pid,inSet));

size(inSet) = 1 => inSet' = delete(pid,inSet);

R5: <monitor,monitor>; Exit(member(pid.inSet));

size(inSet) > 1 => inSet' = delete(pid,inSet);

Esti member(pit.inSet) &&

size(inSet) = 1 ] / inSet =

elete(pit.inSet) && TCvar2 = 0

R6: <monitor,monitor>; Near(!(member(pid,inSet)));

true => inSet' = insert(pid,inSet);

R7: <idle,activate>; Near(true);

true => inSet' = insert(pid,inSet);

Time-Constraints:

TCvar1: R7, Lower, [0, 1], {}; TCvar2: R4, Raise, [0, 1], {};

Figure 11: Statechart Diagram for Con-

```

Near( '(member(pid,inSet)) && / inSet-ensert(pid,inSet)

eri true && true && TC/er1>=0 & TC/er1<=1 1

Near(!(member(pid,inSet)) && true [/inSet = insert(pid,inSet) ber(pd.nSet) &

Figure 10: Formal Specification for GRC Controller

end

message "Near" to the controller. The controller changes from monitor state only when all the train have exited from the gate. At that instant, it sends the message to the gate and returns to the idle state. The events "Down" and "Up" are time constrained internal events for the gate. The evaluation for the local clocks for the controller are the variables "TCvar1" and "TCvar2". Similarly, the timed constrained events for the controller and train are governed by their local clocks shown in the extended statechart diagrams. Figures 10, 12, 14 show the textual specifications corresponding to their extended statechart diagrams.

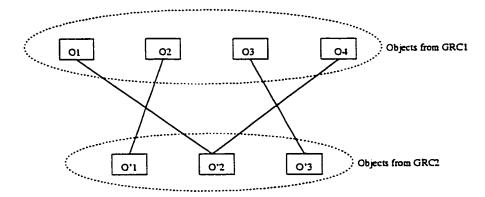

troller

Figure 17 shows the collaboration diagram for a system with 5 Trains, 2 Controllers, and 2 Gates. In this configuration, the object train3 is allowed to interact with both controllers, while the other train objects can only interact with one of the controllers. Hence the object train3 has two ports, one for each controller with which it will communicate. Each of the other trains have only one port. Each gate communicates with its associated controller through one port. Figure 16 shows the textual specification of the Train-Gate-Controller system shown in Figure 17.

```

Class Train [@R]

Events: Near!@R, Out, Exit!@R, In

States: *idle, cross, leave, toCross

Attributes: cr:@C

Traits:

Attribute-Function:

idle → {}; cross → {};

leave → {}; toCross → {cr};

Transition-Specifications:

R1: <idle,toCross>; Near(true); true=>cr'=pid;

R2: <cross,leave>; Out(true); true => true;

R3: <leave,idle>; Exit(pid = cr); true => true;

R4: <toCross,cross>; In(true); true => true;

Time-Constraints:

TCvar2: R1, Exit, [0, 6], {};

TCvar1: R1, In, [2, 4], {};

end

```

Figure 12: Formal Specification for GRC Train

Figure 13: Statechart Diagram for Train

```

Class Gate [③S]

Events: Lower? ⑤S, Down, Up, Raise? ⑥S

States: *opened, toClose, toOpen, closed

Attributes:

Traits:

Attribute-Function:

opened → {}; toClose → {};

toOpen → {}; closed → {};

Transition-Specifications:

R1: <opened, toClose>; Lower(true); true => true;

R2: <toClose, closed>; Down(true); true => true;

R3: <toOpen, opened>; Up(true); true => true;

R4: <closed, toOpen>; Raise(true); true => true;

Time-Constraints:

TCvarl: R1, Down, [0, 1], {};

TCvar2: R4, Up, [1, 2], {};

end

```

Figure 14: Formal Specification for GRC Gate

Figure 15: Statechart Diagram for Gate

```

SCS TrainGateController

Include:

Instantiate:

gate1::Gate[@S:1];

gate2::Gate[@S:1];

train1::Train[@C:1];

train2::Train[@C:1];

train3::Train[@C:2];

train4::Train[@C:1];

train5::Train[@C:1];

controller 1:: Controller [@P:3, @G:1];

controller2::Controller[@P:3, @G:1];

Configure:

controller1.@G1:@G <-> gate1.@S1:@S; controller2.@G2:@G <-> gate2.@S2:@S;

controller1.@P1:@P <-> train1.@C1:@C;

controller1.@P2:@P <-> train2.@C2:@C;

controller1.@P3:@P <-> train3.@C3:@C;

controller2.@P4:@P <-> train3.@C4:@C;

controller2.@P5:@P <-> train4.@C5:@C;

controller2.@P6:@P <-> train5.@C6:@C;

end

```

Figure 16: Formal Specification for Train-Gate-Controller Subsystem

Figure 17: Collaboration Diagram for 5 Train - 2 Gate - 2 Controller

### Chapter 3

# Formal Basis of Testing UML Models of Real-Time Reactive Systems

#### 3.1 Introduction

UML is widely used in industries to model untimed object-oriented systems. Selic [Sel99] has pointed out that UML has sufficient expressive power to model real-time systems, without requiring additional language constraints. Douglass [Dou98] has given a naive introduction to real-time modeling in UML. However, it is stated by Selic [Sel99] that Time, although defined in UML standards, is not given any semantics. Without semantics, time-constrained actions cannot be specified precisely. Given the general purpose modeling features of UML and the lack of formal semantics, it is possible to have several interpretations of one UML model even for untimed systems, thus giving rise to different implementations with different behaviors. Consequently, it is impossible to claim a conformance relation between a given UML model and its implementation. The goal of this chapter is to review RTUML, the language introduced by Muthiayen [Mut00] which has a formal syntax within UML language and formal semantics based on TROM formalism, and claim that our testing methodology is applicable to real-time UML models having TROM semantics.

### 3.2 RTUML Types and Domains

The basic types are GRCTypes, DataTypes, and PortTypes.

- GRC is the universal set of GRCTypes.

- $\mathcal{D}$  is the universal set of DataTypes.

- $\mathcal{P}$  is the universal set of PortTypes.

- $P_0$  is the null PortType.  $\mathcal{P}$  includes the null PortType  $P_0$ ,  $P_0 \in \mathcal{P}$ .  $P_0$  is a singleton set, containing the null port  $p_0$ ,  $P_0 = \{p_0\}$ .

The Event Domain formally defines the event set. Let  $\mathcal{E}$  be the universal set of events,  $\mathcal{E}_{internal}$  be the universal set of external events,  $\mathcal{E}_{internal}$  be the universal set of external events,  $\mathcal{E}_{input}$  be the universal set of input events, and  $\mathcal{E}_{output}$  be the universal set of output events. An input event corresponds to an external event suffixed with the symbol "?". We use "e?" to denote the input event obtained by suffixing the external event "e".

$$\mathcal{E}_{input} = \{e? \mid e \in \mathcal{E}_{external}\}$$

An *output* event corresponds to an *external* event suffixed with the symbol "!". We use "e!" to denote the *output* event obtained by suffixing the *external* event "e".

$$\mathcal{E}_{output} = \{e! \mid e \in \mathcal{E}_{external}\}$$

The following properties apply to the universal sets of events.

1. The universal sets of internal and external events are disjoint.

$$\mathcal{E}_{internal} \cap \mathcal{E}_{external} = \emptyset$$

2. The universal sets of internal and input events are disjoint.

$$\mathcal{E}_{internal} \cap \mathcal{E}_{input} = \emptyset$$

3. The universal sets of internal and output events are disjoint.

$$\mathcal{E}_{internal} \cap \mathcal{E}_{output} = \emptyset$$

4. The universal sets of input and output events are disjoint.

$$\mathcal{E}_{input} \cap \mathcal{E}_{output} = \emptyset$$

5. The universal set of events  $\mathcal{E}$  corresponds to the union of the universal sets of internal, input and output events.

$$\mathcal{E} = \mathcal{E}_{internal} \cup \mathcal{E}_{input} \cup \mathcal{E}_{output}$$

The following functions are defined on the Event domain.

• The bijective function  $\sigma_{in}$  converts a set of *input* events into a set of *external* events, by removing the suffix "?" from each *input* event.

$$\sigma_{in}: \mathbb{P}(\mathcal{E}_{input}) \to \mathbb{P}(\mathcal{E}_{external})$$

The function  $\sigma_{in}$  is defined as follows:

$$\forall E_{in} \in \mathbb{P}(\mathcal{E}_{input}) \bullet \sigma_{in}(E_{in}) = \{e \mid e? \in E_{in}\}$$

• The bijective function  $\sigma_{out}$  converts a set of output events into a set of external events, by removing the suffix "!" from each output event.

$$\sigma_{out}: \mathbb{P}(\mathcal{E}_{output}) \to \mathbb{P}(\mathcal{E}_{external})$$

The function  $\sigma_{out}$  is defined as follows:

$$\forall \ E_{out} \in \mathbb{P}(\mathcal{E}_{output}) \bullet \sigma_{out}(E_{out}) = \{e \mid e! \in E_{out}\}$$

The State Domain defines the set of states and their properties. Let S be the universal set of states,  $S_{simple}$  be the universal set of states, and  $S_{complex}$  be the universal set of complex states. The following properties apply to the universal sets of states.

1. The universal sets of simple and complex states are disjoint.

$$S_{simple} \cap S_{complex} = \emptyset$$

2. the universal set of states S corresponds to the union of the universal sets of simple and complex states.

$$S = S_{simple} \cup S_{complex}$$

The following functions are defined on the State domain.

\* A complex state contains a set of substates that are either simple or complex.

The function substates returns the set of substates of a state.

$$substates: S \to \mathbb{P}(S)$$

1. The function substates returns an empty set when applied to a simple state.

$$\forall s \in S_{simple} \bullet substates(s) = \emptyset$$

2. The set of substates of a complex state is nonempty.

$$\forall s \in S_{complex} \bullet substates(s) \neq \emptyset$$

\* A complex state has a unique *initial* state, which is a simple state. The total function *initial* identifies the initial state of a complex state.

$$initial: S_{complex} \rightarrow S_{simple}$$

1. The *initial* state of a complex state is a member of the *substates* of the *complex* state.

$$\forall s \in S_{complex} \bullet initial(s) \in substates(s)$$

2. The set of substates of a complex state contains at least 2 elements.

$$\forall s \in S_{complex} \bullet substates(s) \setminus \{initial(s)\} \neq \emptyset$$

\* The hierarchy function  ${\cal H}$  returns the set of all states in the hierarchy of a state.

$$\mathcal{H}: S \to \mathbb{P}(S)$$

1. The hierarchy function  $\mathcal{H}$  is recursively defined as follows.

$$\mathcal{H}(s) = \{s\} \cup \bigcup_{s \in substates(s)} \mathcal{H}(s)$$

### 3.2.1 Time Semantics

Time is defined as the set of nonnegative real numbers.

$$Time = \{t \mid t \in \mathbb{R}^{\geq 0}\}$$

TimeConstant is defined as the set of nonnegative rationals.

$$TimeConstant = \{m \mid m \in \mathbb{Q}^{\geq 0}\}$$

#### Clock Valuation

Time is fully encapsulated in a class. Clocks are locally defined and clock variables assume time values as measuring clock times.

• Clock Valuation v for a set C of clocks is a map that at any instant assigns a nonnegative real value to each clock.

$$v: C \to (\mathbb{R}^{\geq 0} \to \mathbb{R}^{\geq 0})$$

That is:  $v(C): \mathbb{R}^{\geq 0} \to \mathbb{R}^{\geq 0}$ , v(c)(x) is the valuation for a clock  $c, c \in C$  at instance  $x, x \in \mathbb{R}^{\geq 0}$

- For each  $x \in \mathbb{R}^{\geq 0}$ , and  $k \in \mathbb{Z}$ , we define k + x to be a k-shift of x.

- For any valuation v and for all clocks  $c \in C$ , the clock valuation has the following properties:

$$- v(c)(0) = 0$$

$$-v(c)(x) > v(c)(y)$$

, if  $x > y$ ,  $x, y \in \mathbb{R}^{\geq 0}$

$$- v(c)(k+x) = k + v(c)(x).$$

A time constraint is a predicate, involving clock valuation. If m is a time constant,  $m \in \mathbb{Q}^{\geq 0}$ , then  $v(c)(x) \leq m$ ,  $v(c)(x) \geq m$  are time constraints, where  $c \in C$ ,  $x \in \mathbb{R}^{\geq 0}$ . A time constraint may also involve conjunction, disjunction and negation. For instance, if  $m_1$ ,  $m_2$  are time constants, then  $v(c)(x) \geq m_1 \wedge v(c)(x) \leq m_2$  is a time constraint.

# 3.2.2 Reactive Object Model in RTUML

The reactive object model is one of GRCTypes, consisting of a generic reactive class with an associated statechart extended to capture timing constraints on transitions. This definition captures our notion of what a reactive object is.

#### Definition for GRCClass

A GRCClass is a 3-tuple  $\langle \mathcal{P}, \mathcal{X}, \Omega \rangle$ , with the following definition:

•  $\mathcal{P}$  is a set of PortTypes

$$\mathcal{P}: \mathbb{P}(\mathcal{P})$$

•  $\mathcal{X}$  is a set of *attributes*, where each attributes is either an instance of a PortType from the set  $\mathcal{P}$ , or an instance of a DataType from the universal set  $\mathcal{D}$ .

$$\mathcal{X} = \{x \mid x : \mathcal{P}\} \cup \{a \mid a : \mathcal{D}\}$$

•  $\Omega$  is a mapping from the set of PortTypes  $\mathcal{P}$  to the power set of the universal set of events  $\mathcal{E}$ , defining the set of allowed input and output events at instances of the PortType.

$$\Omega: \mathcal{P} \to \mathbb{P}(\mathcal{E})$$

The following properties apply to a GRC class  $\langle \mathcal{P}, \mathcal{X}, \Omega \rangle$ .

1. The sets of *input* and *output* events associated with a PortType, other than the null PortType  $P_0$ , correspond to disjoint sets of external events.

$$\forall P_i \in \mathcal{P} \bullet P_i \neq P_0 \rightarrow$$

$$\Omega(P_i) = E_{in_i} \cup E_{out_i} \wedge E_{in_i} \subseteq \mathcal{E}_{input} \wedge E_{out_i} \subseteq \mathcal{E}_{output} \wedge$$

$$\sigma_{in}(E_{in_i}) \cap \sigma_{out}(E_{out_i}) = \emptyset$$

2. The sets of events associated with two PortTypes of a GRC class are disjoint.

$$\forall P_i, P_i \in \mathcal{P} \bullet P_i \neq P_i \rightarrow \Omega(P_i) \cap \Omega(P_i) = \emptyset$$

3. The events associated with the null PortType  $P_0$  are internal events.

$$\forall P_i \in P \bullet P_i = P_0 \to \Omega(P_i) \subseteq \mathcal{E}_{internal}$$

4. The set of internal events  $\mathcal{E}_{internal}$  of a GRC class corresponds to the set of events associated with the null PortType  $P_0$ .

$$P_0 \in \mathcal{P} \to \mathcal{E}_{internal} = \Omega(P_0) \land P_0 \notin \mathcal{P} \to \mathcal{E}_{internal} = \emptyset$$

5. The events associated with a PortType  $P_i$  of a GRC class, excluding the null PortType  $P_0$ , are input and output events.

$$\forall P_i \in \mathcal{P} \bullet P_i \neq P_0 \to \Omega(P_i) \subseteq (\mathcal{E}_{input} \cup \mathcal{E}_{output})$$

6. The set of *input* and *output* events  $E_{io}$  of a GRCClass corresponds to the distributed union of the sets of events associated with the PortTypes of the GRCClass, excluding the *null PortType P*<sub>0</sub>.

$$E_{io} = \bigcup_{P_i \in \mathcal{P} \land P_i \neq P_0} \Omega(P_i)$$

#### Compatibility of PortTypes

Given two GRCClasses  $G_a$  and  $G_b$ , such that

$$G_a = \langle \mathcal{P}_a, \mathcal{X}_a, \Omega_a \rangle$$

, and

$$G_b = \langle \mathcal{P}_b, \mathcal{X}_b, \Omega_b \rangle$$

PortType  $P_{a_i}$  from the set  $\mathcal{P}_a$  and PortType  $P_{b_j}$  from the set  $\mathcal{P}_b$  are compatible iff the set of input events associated with PortType  $P_{a_i}$  is equal to the set of output events associated with PortType  $P_{b_j}$ , and the set of output events associated with PortType  $P_{a_i}$  is equal to the set of input events associated with PortType  $P_{b_j}$ . The comparison for equality events to the external events corresponding to the respective input and output events.

• The predicate *compatible* defines the compatibility of two PortTypes.

$$compatible: \mathcal{P} \times \mathcal{P} \rightarrow Bool$$

1. The predicate *compatible* has the following definition.

$$\forall P_{a_i} \in \mathcal{P}_a, P_{b_i} \in \mathcal{P}_b \bullet compatible(P_{a_i}, P_{b_j}) \leftrightarrow$$

$$\Omega_a(P_{a_i}) = E_{in_a} \cup E_{out_a} \wedge E_{in_a} \subseteq \mathcal{E}_{input} \wedge E_{out_a} \subseteq \mathcal{E}_{output} \wedge$$

$$\Omega_b(P_{b_j}) = E_{in_b} \cup E_{out_b} \wedge E_{in_b} \subseteq \mathcal{E}_{input} \wedge E_{out_b} \subseteq \mathcal{E}_{output} \wedge$$

$$\sigma_{in}(E_{in_a}) = \sigma_{out}(E_{out_b}) \wedge \sigma_{in}(E_{in_b}) = \sigma_{out}(E_{out_a})$$

#### Definition for Extended StateChart

An ExtendedStatechart is a 8-tuple  $\langle S, C, R, \Upsilon, \Psi, \Gamma, \Xi \rangle$ , with the following definition.

• S is a set of states.

$$S: \mathbb{P}(S)$$

1. The set S consists of *simple* and *complex* states. The set  $S_s$  denotes the subset of all simple states from the set S, and the set  $S_c$  denote the subset of all complex states from the set S.

$$S = S_s \cup S_c \wedge S_s \subseteq S_{simple} \wedge S_c \subseteq S_{complex}$$

2. The distinguished simple state  $s_0$  from the set S is the *initial* state of the statechart.

$$s_0 \in S_s$$

3. The initial state of a complex state from the set  $S_c$  is a simple state from the set  $S_s$ .

$$\forall s_c \in S_c \bullet initial(s_c) \in S_s$$

.

4. The set of substates of a complex state from the set  $S_c$  is a subset of the set S.

$$\forall s_c \in S_c \bullet substates(s_c) \subset S$$

5. The sets of substates of two complex states from the set  $S_c$  are disjoint.

$$\forall s_i, s_j \in S_c \bullet s_i \neq s_j \rightarrow substates(s_i) \cap substates(s_j) = \emptyset$$

- C is a set of logical clocks for defining time constraints on reactions to transitions.

- R is a set of transitions, where each transition is a 5-tuple  $\langle s, d, e, g, a \rangle$ , such that

- s is the source state; s is a member of the set S.

$$s \in S$$

- d is the destination state; d is a member of the set S.

$$d \in S$$

- e is the trigger event; e is a member of the universal set of events  $\mathcal E$

$$e \in \mathcal{E}$$

- g is a predicate representing the guard condition for the transition.

- a is a predicate representing the action resulting from the transition.

- 1. A valid transition satisfies one of the following four conditions.

- \* The destination state d is a state which is not a substate of another state.

$$d \in S \setminus \bigcup_{s_c \in S_c} substates(s_c)$$

\* The destination state d is the *initial* state of a complex state which is not a substate of another state.

$$\exists d_c \in S_c \setminus \bigcup_{s_c \in S_c} substates(s_c) \bullet d = initial(d_c)$$

\* There exists a complex state  $s_c$  such that the source state s is in the hierarchy of the state  $s_c$  and the destination state d is a substate of the state  $s_c$ .

$$\exists s_c \in S_c \bullet s \in \mathcal{H}(s_c) \land d \in substates(s_c)$$

\* There exists a complex state  $s_c$  such that the source state s is in the hierarchy of the state  $s_c$  and the destination state d is the *initial* state of a complex substate of the state  $s_c$ .

$$\exists s_c, d_c \in S_c \bullet s \in \mathcal{H}(s_c) \land d_c \in substates(s_c) \land d = initial(d_c)$$

2. If the source state s is a complex state, then the transition corresponds to a set of transition  $R_s$  such that the source state  $s_h$ , of each transition in the set  $R_s$ , is in the hierarchy of the state s.

$$s \in S_c \rightarrow \{\langle s_h, d, e, g, a \rangle | s_h \in \mathcal{H}(s)\} \subseteq R$$

3. If the destination state d is a complex state, then the transition corresponds to a transition whose destination state  $d_e$  is the initial state of the state d.

$$d \in S_c \rightarrow \{\langle s, d_e, e, g, a \rangle | d_e \in initial(d)\} \subseteq R$$

•  $\Upsilon$  is a total function that maps a clock from the set C to a transition from the set R, such that the clock is initialized to 0 when the transition occurs.

$$\Upsilon: C \to R$$

If  $\Upsilon(c) = r$ , then v(c)(0) = 0 for the transition r.

•  $\Phi$  is a function that maps a transition from the set R to a set of clocks from the set C, such that the timing constraint on the transition is specified in terms of the values of these clocks.

$$\Phi: R \to \mathbb{P}(C)$$

1. If the trigger event e of the transition  $r = \langle s, d, e, g, a \rangle$  is an *input* event, then the transition r is not time-constrained.

$$\forall r \in R \bullet r = \langle s, d, e, g, a \rangle \land e \in \mathcal{E}_{input} \to \Phi(r) = \emptyset$$

2. If the transition  $r = \langle s, d, e, g, a \rangle$  is time-constrained, then the trigger event e is either an *internal* or an *output* event.

$$\forall \ r \in R \bullet r = < s, d, e, g, a > \land \Phi(r) \neq \emptyset \rightarrow e \in (\mathcal{E}_{internal} \cup \mathcal{E}_{output})$$

3. If the transition  $r = \langle s, d, e, g, a \rangle$  is time-constrained, then the trigger event e corresponds to a reaction to transitions other than r from the set R, such that the corresponding clocks are initialized to 0 when those transition occur.

$$\forall \ r \in R \bullet \Phi(r) \neq \emptyset \rightarrow \forall \ c \in \Phi(r) \bullet \exists \ r_2 \in R \bullet \Upsilon(c) = r_2 \land r_2 \neq r \land v(c)(0) = 0$$

•  $\Psi$  is a partial function that gives the value of a clock from the set C when a transition from the set R occurs.

$$\Psi: C \times R \rightarrow Time$$

- \* The function  $\Psi$  is defined on the clock c and the transition r iff

- \* the clock c is initialized to 0 when the transition r occurs, or

- \* the transition r corresponds to a time-constrained reaction, such that the timing constraint is defined in terms of the clock c, or

- \* the destination state of the transition r is a disabling state for a time-constrained reaction, such that the timing constraint is defined in terms of the clock c.

$$\Psi(c,r) = \begin{cases} 0, & \text{if } \Upsilon(c) = r, \\ v(c)(x), & \text{where } 0 < v(c)(x) < \infty, & \text{if } c \in \Phi(r), \ x \in \mathbb{R}^{\geq 0} \\ \infty, & \text{if } r = < s, d, e, g, a > \land d \in \Xi(c) \end{cases}$$

•  $\Gamma$  is a partial function that gives the *lower* and *upper bounds* for the value of a clock from the set C, relative to the activation time of the time-constrained reaction, within which the corresponding transition from the set R can occur.

$$\Gamma: C \times R \rightarrow TimeConstant \times TimeConstant$$

\* The function  $\Psi$  is defined on the clock c and the transition r iff the transition r corresponds to a time-constrained reaction, such that the timing constraint is defined in terms of the clock c.

$$\Gamma(c,r) = < l, u > \quad \textit{iff} \quad c \in \Phi(r) \land (l \leq v(c)(x) \leq u)$$

where  $x \in \mathbb{R}^{\geq 0}$

•  $\Xi$  is a function that maps a clock c from the set C to the set of disabling states for the time-constrained reaction defined in terms of the clock c.

$$\Xi: C \to \mathbb{P}(s)$$

#### Definition for GRCType

A GRCType is a 2-tuple < G, B>, with the following definition.

• G is a GRCClass.

$$G = \langle \mathcal{P}, \mathcal{X}, \Omega \rangle$$

• B is an Extended Statechart.

$$B = \langle S, C, R, \Upsilon, \Phi, \Psi, \Gamma, \Xi \rangle$$

- A transition r from the set R, such that  $r = \langle s, d, e, g, a \rangle$ , satisfies the following properties.

- \* The trigger event e is associated with a PortType from the set of PortTypes P.

$$\exists P_i \in \mathcal{P} \bullet e \in \Omega(P_i)$$

\* The guard condition g is a conjunction of three predicates  $g_{port\_cond}, g_{enabling\_cond}$  and  $g_{time\_constraint}$ .

$$g = g_{port\_cond} \land g_{enabling\_cond} \land g_{time\_constraint}$$

\* The port condition  $g_{enabling\_cond}$  is a logical assertion on the values of attributes from the set  $\mathcal{X}$  and an instance  $p_j$  of a PortType  $P_i$  from the set P. The PortType  $P_i$  corresponds to the PortType with which event e is associated; the null PortType  $P_0$  for internal events. The instance  $p_j$  of PortType  $P_i$  corresponds to the port through which the message is channeled; the null port  $p_0$  for internal events.

$$g_{port\_cond}: \mathbb{P}(\mathcal{X}) \times P_i \rightarrow Bool$$

where

$$P_i \in \mathcal{P} \land e \in \Omega(P_i)$$

1. If the trigger event e an internal event, the port condition is true.

if

$$e \in \mathcal{E}_{internal}$$

, then  $g_{port\_cond} \stackrel{\triangle}{=} true$

- The enabling condition  $g_{enabling\_cond}$  is a logical assertion on the values of attributes from the set  $\mathcal{X}$ .

$$g_{enabling\_cond}: \mathbb{P}(\mathcal{X}) \to Bool$$

- The time constraint condition  $g_{time\_constraint}$  is a logical assertion on the values of clocks from the set C, that are used in specifying the timing constraint on transition  $\tau$ .

$$g_{time\_constraint}: \mathbb{P}(C) \rightarrow Bool$$

For instance, if  $x \in \delta$ ,  $g_{time\_constraint}(x) = true \mid false$

2. If there is no timing constraint r, the time constraint condition is true.

if

$$\Phi(r) = \emptyset$$

then  $g_{time\_constraint} \stackrel{\triangle}{=} true$

3. If the trigger event e is an input event, the time constraint is true.

If

$$e \in \mathcal{E}_{input}$$

then  $g_{time\_constraint} \stackrel{\triangle}{=} true$

\* The action a is a conjunction of two predicates apost\_cond and aclocking.

$$a = a_{post\_cond} \land a_{clock\_init}$$

- The post condition  $a_{post_{cond}}$  is a logical assertion on the values of attributes from the set  $\mathcal{X}$  after transition r is taken.

$$a_{post\_cond}: \mathbb{P}(\mathcal{X}) \to Bool$$

- The clock initialization expression a<sub>clock\_init</sub> initializes the value of a clock to 0 for each time-constrained reaction associated with transition r.

$$a_{clock\_init} \stackrel{\triangle}{=} \bigwedge_{c \in C \land \Upsilon(c) = r} \Psi(c, r) = 0$$

• For each state s from the set S, the disabling state expression e<sub>disabling\_state</sub> defines the time-constrained reactions that are disabled when a transition leading to the state s occurs. The disabling state expression e<sub>disabling\_state</sub> is defined as a predicate on clocks from the set C that are used for specifying the timing constraints on the reactions.

$$e_{disabling\_state}: \mathbb{P}(C) \rightarrow Bool$$

\* The disabling state expression  $e_{disabling\_state}$  sets the values of the clocks defining timing constraints on reactions that are disabled in state s to infinity( $\infty$ ).

$$e_{\textit{disabling\_state}} \stackrel{\triangle}{=} \bigwedge_{c \in C \land d \in \Xi(c) \land r \in R \land r = \langle s, d, e, g, a \rangle} \Psi(c, r) = \infty$$

#### **Operational Semantics**

The status of a TROM at any time t, is the tuple  $(s; \vec{a}; \mathcal{R})$ , where the current state  $\theta$  is a simple state of the TROM,  $\vec{a}$  is the assignment vector, and  $\mathcal{R}$  is the vector of outstanding reactions. A computational step of a TROM occurs when the object with status  $(s; \vec{a}; \mathcal{R})$ , receives a signal  $\langle e, p_i, t \rangle$  from its environment and there exists a transition specification that can change the status of the TROM. A computation  $\tau$  of a TROM object A is a sequence, possibly infinite, of alternating statuses and signals,  $\mathcal{OS}_0 \xrightarrow{\langle e_0, p_0, t_0 \rangle} \mathcal{OS}_1 \xrightarrow{\langle e_1, p_1, t_1 \rangle} \dots$

A computation of an extended statechart  $B = \langle S, C, R, \Upsilon, \Psi, \Gamma, \Xi \rangle$  can be written in terms of extended states, where an extended state is a pair  $\langle s, v \rangle$ ,  $s \in S$ , and v is a clock valuation at that state. For instance, let  $\mathcal{OS}_i = (s_i; \vec{a_i}; \mathcal{R}_i)$ ,  $\mathcal{OS}_{i+i} = (s_{i+1}; \vec{a_{i+1}}; \mathcal{R}_{i+1})$  are two successive statues of a TROM. The states change due to the occurrence of the signal  $\langle e_i, p_i, t_i \rangle$  at the state  $s_i$ . If this TROM receive its next signal  $\langle e_{i+1}, p_{i+1}, t_{i+1} \rangle$  in the state  $s_{i+1}$ , then  $v_{i+1} = v_i + t_{i+1} - t_i$ . That is, the local clocks run at the same rate as the global clock. Hence, one step of computation can be written as  $\langle s_i, v_i \rangle^{\langle e_i, p_i, t_i \rangle} \langle s_{i+1}, v_{i+1} \rangle$ .

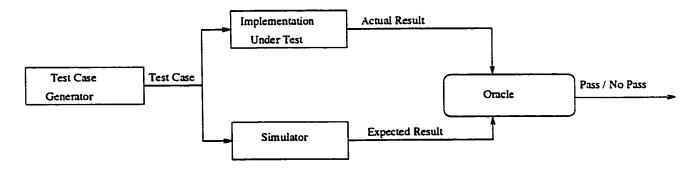

# 3.2.3 Reactive System Model