INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

**UMI**®

# CAPACITOR COMMUTATED CONVERTERS FOR HVDC TRANSMISSION SYSTEM

# Anup Mazumder

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements

for the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada

February, 2002

© Anup Mazumder, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-68443-1

### **Abstract**

# CAPACITOR COMMUTATED CONVERTERS FOR HVDC TRANSMISSION SYSTEM

### Anup Mazumder

The operation of HVDC systems using conventional Line Commutated Converters (LCCs) operating with weak AC systems becomes unreliable due to frequent commutation failures which can occur for any small disturbance in the AC networks. These commutation failures may eventually initiate other disturbances such as voltage or frequency instability in the AC networks.

Furthermore, each LCC station consumes huge amounts of reactive power (between 55-60% of the rated DC power) which is supplemented by large capacitor banks and the filters. This increases the converter station cost and may result in operational problems such as the development of low frequency resonance with the AC network.

Chances of commutation failure can be greatly reduced by using Capacitor Commutated Converters (CCCs). The commutation capacitor (CC) increases the commutation margin. Furthermore, with the recent developments in filter design, it is now possible to design a narrow bandpass filter (High Q) using far less capacitance. Hence, use of such filters can reduce the problem of low frequency resonance and provide better reactive power management. In this thesis, the performance of an HVDC system based on CCCs interact-

ing with weak AC networks is evaluated in terms of its dynamic/transient behaviour.

The thesis starts with a brief survey of the present state of the art in HVDC systems. This is followed by the descriptions of different subsystems of the CIGRE benchmark model. The basic control characteristics of HVDC systems are discussed and their implementations are described using block diagrams. Finally, different tests are carried out by applying varying faults and step changes in the control parameters.

PSCAD/EMTDC simulation package is used to model the CIGRE benchmark and its various control circuits.

The performance of the CCC is compared with conventional LCC using the same benchmark model. Finally, a modified version of CCC configuration, namely Hybrid Converter Combination (HCC) configuration is presented. This configuration uses a combination of both a traditional LCC and a CCC. Its viability is assessed in terms of technical suitability and lower overall cost.

### Acknowledgment

I express my sincere gratitude to Dr. V.K. Sood and Dr. K. Khorasani for their financial support, proper guidance and sharing knowledge and experience during the course of this work.

I acknowledge the untiring help offered by Mr. Wojciech Galuszka and Mr. Daniel Morrison of the System Administration.

I also acknowledge the help offered by Mr. Rohitha Jayasinghe and Mr. John E. Nordstrom of Manitoba HVDC Research Centre Inc.

I am indebted to my brothers and sisters for their moral support.

Finally, I thank my wife, Chandrika, for her continued inspiration throughout my study.

#### Dedicated to:

my mother, Smt. Nirmala Mazumder my father, (Late) Sukumar Mazumder and

my brother, (Late) Swarup Mazumder

# **Table of Contents**

|                |                                                                                                | Page No. |

|----------------|------------------------------------------------------------------------------------------------|----------|

| List of Figure | S                                                                                              | xi       |

| J              |                                                                                                |          |

| LIST OF Tables |                                                                                                | χv       |

| List of Abbre  | viations                                                                                       | xvi      |

| Chapter -1:    | Introduction                                                                                   | 1        |

| 1.1 Ba         | ackground to HVDC Systems                                                                      | 1        |

| 1.2 Pr         | oblem Definition                                                                               | 3        |

| 1.3 Li         | terature Survey on Capacitor Commutated Converters                                             | 4        |

| 1.3.1          | A Technical Assessment of Artificial Commutation of HVDC Converters with Series Capacitors [2] | 4        |

| 1.3.2          | Capacitor Commutated Converters for HVDC [4]                                                   | 5        |

| 1.3.3          | Capacitor Commutated Converter Circuit Configurations for DC Transmission [5]                  | 7        |

| 1.3.4          | Impact of Capacitor Commutated Converters in AC systems with multiple DC Infeed [6]            | 8        |

| 1.3.5          | Application of Capacitor Commutated Converters in multi-<br>infeed HVDC schemes [7]            | 9        |

| 1.3.6          | An AC Active Filter for use at Capacitor Commutated HVDC Converters [8]                        | 10       |

| 1.3.7          | Evaluation of Classical, CCC and TCSC Converter Schemes for                                    | 12       |

| 1.3     |        | redictive Firing Angle Calculation for Constant Effective  Margin Angle Control of CCC-HVDC [10] | 13  |

|---------|--------|--------------------------------------------------------------------------------------------------|-----|

| 1.4     |        | is Objectives                                                                                    | 14  |

| 1.5     |        | nology                                                                                           | 14  |

| 1.6     |        | is Outline                                                                                       | 15  |

|         |        |                                                                                                  | 16  |

| 1.7     | ines   | is Contributions                                                                                 | 10  |

| Chapter | -2 : H | VDC System and Control Strategy                                                                  | 17  |

|         |        |                                                                                                  |     |

| 2.1     | Intro  | oduction                                                                                         | 17  |

| 2.2     | CIG    | RE Benchmark-Based HVDC System                                                                   | 17  |

| 2.3     | Desc   | cription of Subsystems                                                                           | 19  |

| 2.      | 3.1    | AC Network                                                                                       | 19  |

| 2.      | 3.2    | AC Filter                                                                                        | 20  |

| 2.      | 3.3    | Shunt Capacitor Bank                                                                             | 20  |

| 2.      | 3.4 (  | Converter Transformer                                                                            | 21  |

| 2.      | .3.5   | Converter                                                                                        | 22  |

| 2.      | .3.6   | DC System                                                                                        | 23  |

| 2.4     |        | ristor Modeling                                                                                  | 24  |

|         | •      | Choice of Snubber Parameters                                                                     | 25  |

| 2.5     |        | lysis of Converter Bridge                                                                        | 26  |

|         |        |                                                                                                  |     |

| 2.6     | •      | oose of Control                                                                                  | 30  |

| 2       | .6.1   | Control Strategy                                                                                 | 30  |

| 2       | .6.2   | Control Characteristics                                                                          | 32  |

| 2       | 63     | Modified Control Characteristics                                                                 | 3.4 |

| 2.7       | Summary                                                                         | 35 |

|-----------|---------------------------------------------------------------------------------|----|

| Chapter - | 3 : Converter Configurations and Control Implementation                         | 36 |

| 3.1       | Introduction                                                                    | 36 |

| 3.2       | Commutation, Commutation Overlap Angle, Extinction Angle and Commutation Margin | 36 |

| 3.3       | Line Commutated Conveter (LCC) Configuration                                    | 37 |

| 3.4       | Capacitor Commutated Converter (CCC) Configuration                              | 39 |

| 3.5       | Commutation Overlap Angle for CCC Configuration                                 | 40 |

| 3.6       | Valve Stresses                                                                  | 41 |

| 3.7       | Size of Commutation Capacitor                                                   | 41 |

| 3.8       | Reactive Power Generation                                                       | 42 |

| 3.9       | Hybrid Converter Combination (HCC) Configuration                                | 42 |

| 3.10      | Implementation of Control                                                       | 43 |

| 3.        | 10.1 Control Loop in Rectifier                                                  | 44 |

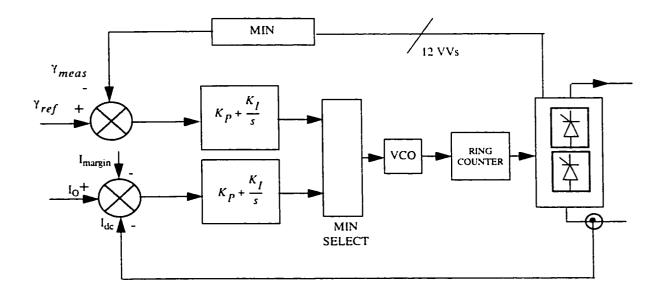

| 3.        | 10.2 Control Loop in Inverter for LCC and CCC Configurations                    | 46 |

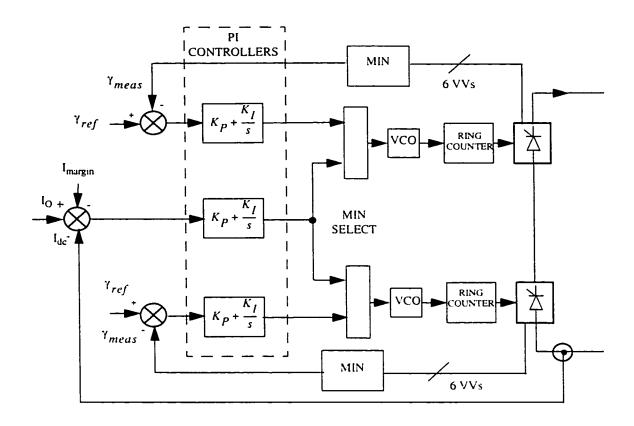

| 3.        | 10.3 Control Loop in Inverter for HCC Configuration                             | 47 |

| 3.11      | PI Controller                                                                   | 49 |

| 3.        | 11.1 PI Controller Design                                                       | 50 |

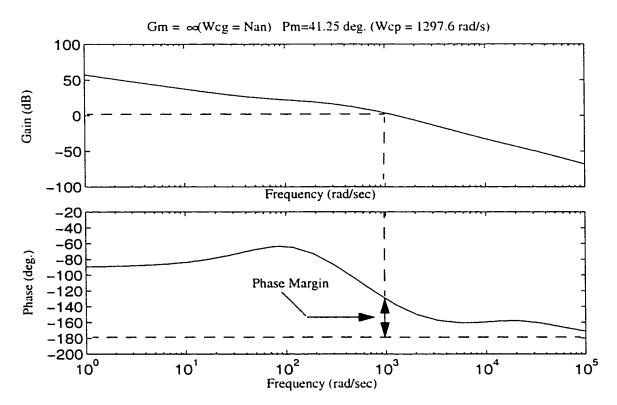

|           | 3.11.1.1 Rectifier Current Controller                                           | 50 |

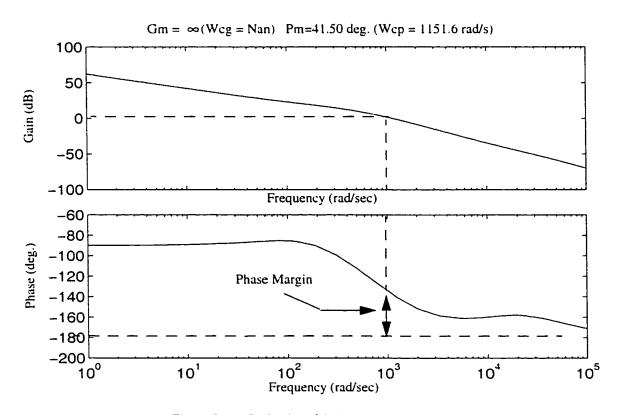

|           | 3.11.1.2 Inverter Current Controller                                            | 51 |

| 3.12      | Summary                                                                         | 53 |

Page No.

| Chapter -4 : Be | haviour of HVDC System under Transient Conditions      | 54  |

|-----------------|--------------------------------------------------------|-----|

| 4.1 Intro       | duction                                                | 54  |

| 4.2 Initia      | lization of the HVDC System                            | 54  |

| 4.3 Cont        | roller Tests                                           | 56  |

| 4.3.1 S         | tep Change in the Rectifier Current Order              | 56  |

| 4.3.2 S         | Step Change in the Inverter Current Order              | 59  |

| 4.3.3 S         | Step Change in the Inverter Gamma Order                | 62  |

| 4.4 Mod         | e Shift Test                                           | 66  |

| 4.5 Fault       | t Tests                                                | 69  |

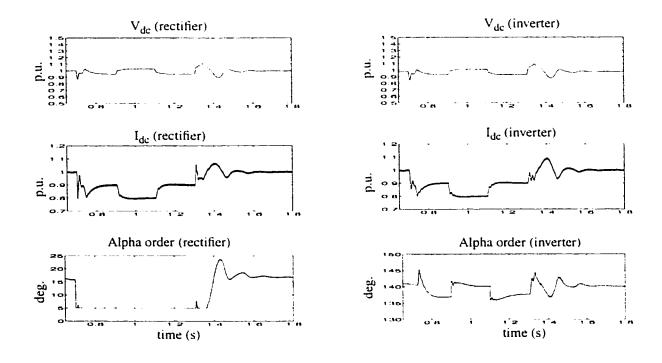

| 4.5.1 F         | Remote Three Phase Fault on AC Network of the Inverter | 69  |

| 4.5.2 F         | Remote SLG Fault on AC Network of the Inverter         | 74  |

| 4.5.3 I         | nverter side DC Line Fault                             | 78  |

| 4.6 Load        | d Rejection Over-voltage                               | 81  |

| 4.7 Sum         | mary                                                   | 84  |

| Chapter -5 : C  | onclusions                                             | 85  |

| References      |                                                        | 88  |

| Appendix -A     | Transformer Sizing and Filter Design                   | 92  |

| Appendix -B     | Background of HVDC Simulation Package/Tools [23]       | 101 |

| Appendix -C     | List of Publications                                   | 102 |

# **List of Figures**

| Figure No. |                                                                            | Page No. |

|------------|----------------------------------------------------------------------------|----------|

|            |                                                                            |          |

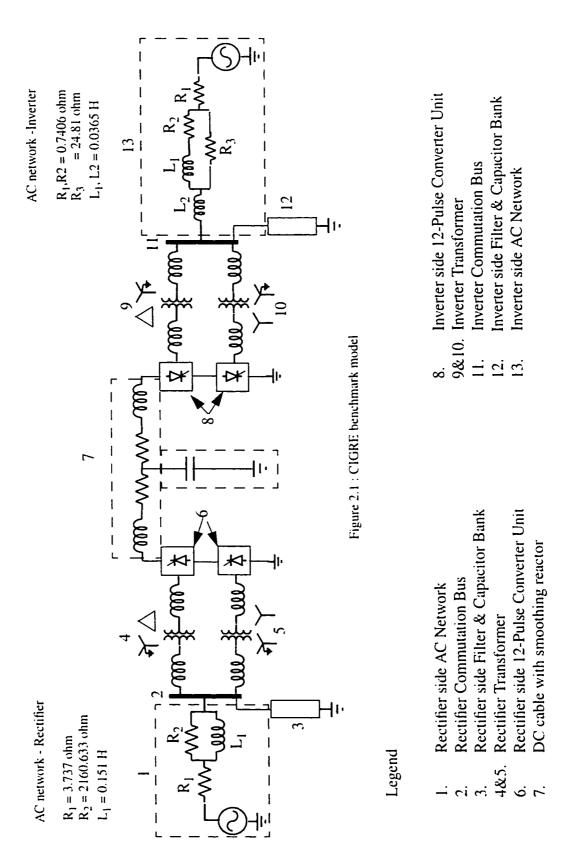

| 2.1        | CIGRE benchmark model                                                      | 18       |

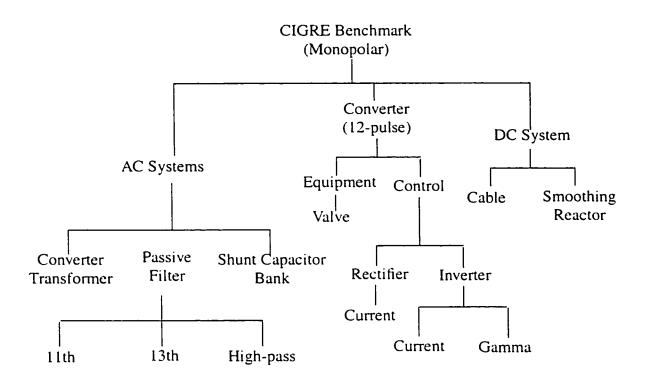

| 2.2        | Inverted tree showing subsystems of the CIGRE benchmark                    | 19       |

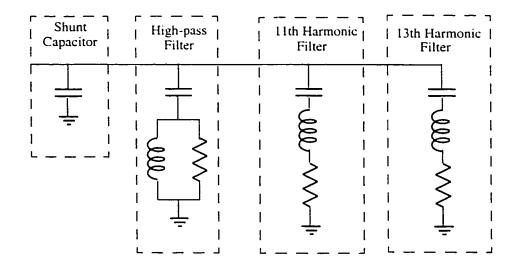

| 2.3        | AC filter bank                                                             | 21       |

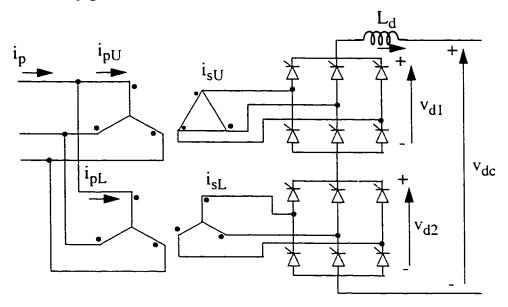

| 2.4        | 12-pulse converter arrangement                                             | 22       |

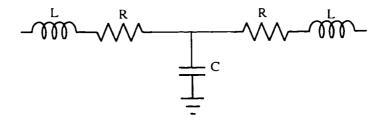

| 2.5        | T-equivalent circuit to represent the DC cable link with smoothing reactor | 24       |

| 2.6        | Equivalent circuit for the thyristor switch                                | 25       |

| 2.7a       | Variation of VV with R <sub>snubber</sub>                                  | 26       |

| 2.7b       | Variation of VV with C <sub>snubber</sub>                                  | 26       |

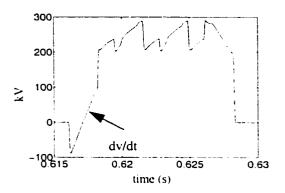

| 2.8a       | Valve voltage showing dv/dt                                                | 26       |

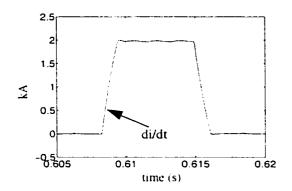

| 2.8b       | Valve current showing di/dt                                                | 26       |

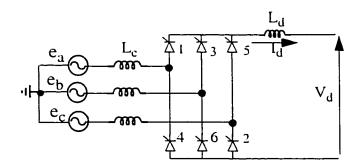

| 2.9        | 6-pulse bridge circuit                                                     | 27       |

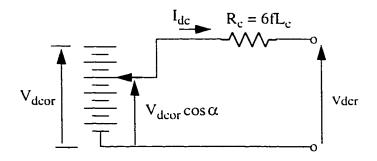

| 2.10       | Equivalent circuit of rectifier                                            | 29       |

| 2.11       | Equivalent circuit of inverter                                             | 29       |

| 2.12       | Equivalent circuit of two terminal HVDC system                             | 29       |

| 2.13       | Equivalent circuit of DC link                                              | . 31     |

| 2.14       | Choice of control strategy for DC link                                     | . 31     |

| 2.15       | Control characteristics                                                    | 32       |

| 2.16       | Modified control characteristics                                           | 34       |

| 3.1        | Line Commutated Converter (LCC) configuration                              | 38       |

| 3.2  | Commutation voltage and valve voltage for LCC configuration                                           | 38 |

|------|-------------------------------------------------------------------------------------------------------|----|

| 3.3  | Extinction angle and commutation overlap angle for LCC configuration                                  | 38 |

| 3.4  | Capacitor Commutated Converter (CCC) configuration                                                    | 39 |

| 3.5  | Commutation voltage and valve voltage for CCC configuration                                           | 40 |

| 3.6  | Extinction angle and commutation overlap angle for CCC configuration                                  | 40 |

| 3.7  | Comparison of valve stress for LCC and CCC configurations                                             | 41 |

| 3.8  | Variation of valve stress with CC size                                                                | 41 |

| 3.9  | Hybrid Converter Combination (HCC) configuration                                                      | 43 |

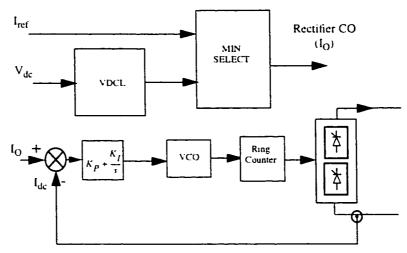

| 3.10 | Block diagram of the rectifier control loop for LCC, CCC and HCC configurations                       | 44 |

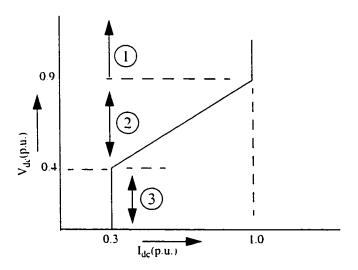

| 3.11 | VDCL characteristic                                                                                   | 45 |

| 3.12 | Block diagram of the inverter control loop for LCC and CCC configurations                             | 47 |

| 3.13 | Block diagram of the inverter control loop for HCC configuration                                      | 48 |

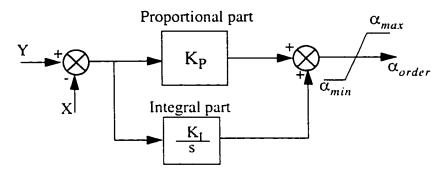

| 3.14 | Block diagram of the PI controller.                                                                   | 49 |

| 3.15 | Bode plot of the rectifier control system                                                             | 52 |

| 3.16 | Bode plot of the inverter control system                                                              | 52 |

|      |                                                                                                       |    |

| 4.1  | Characteristics on V <sub>dc</sub> -I <sub>dc</sub> plane to explain initialization of an HVDC system | 55 |

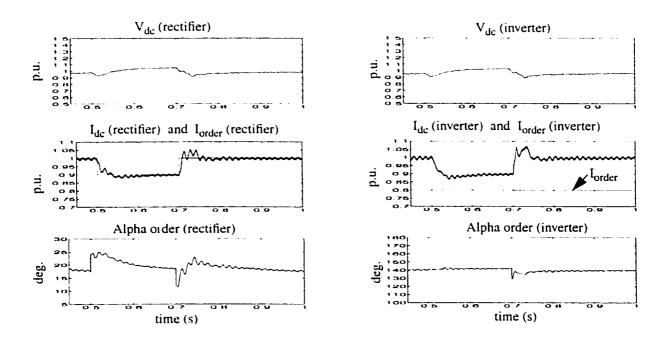

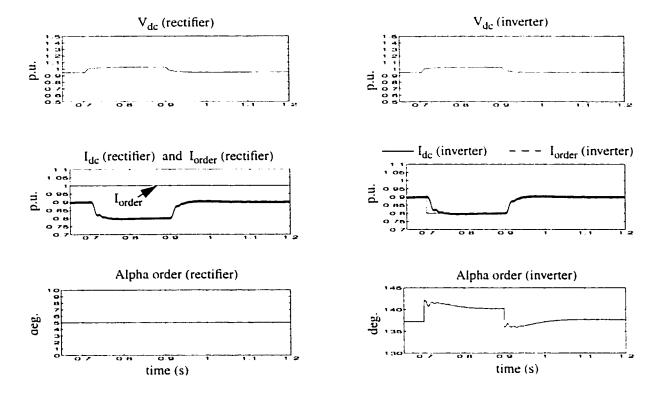

| 4.2  | 10% step change in the rectifier current order - LCC configuration                                    | 57 |

| 4.3  | 10% step change in the rectifier current order - CCC configuration                                    | 57 |

| 4.4  | 10% step change in the rectifier current order - HCC-UP configuration                                 | 58 |

| 4.5  | 10% step change in the rectifier current order - HCC-LO configuration                                 | 58 |

Figure No. Page No

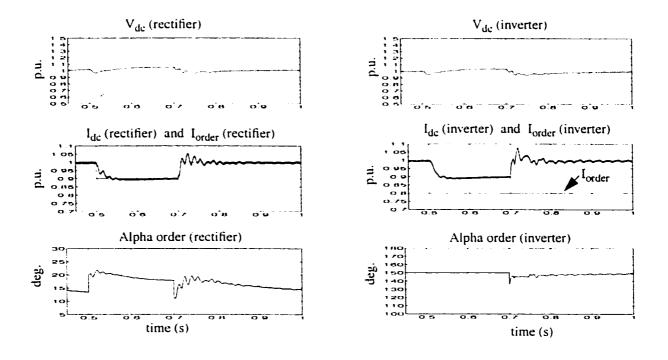

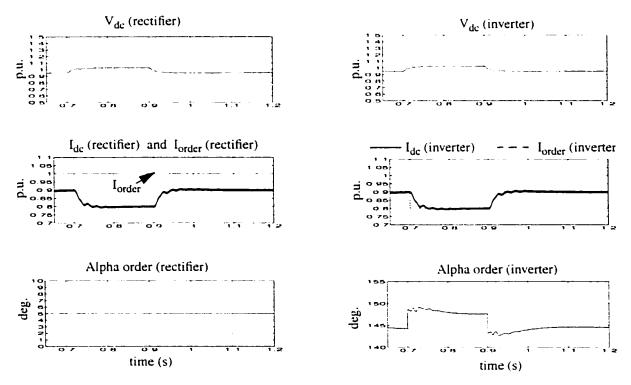

| 4.6  | 10% step change in the inverter current order - LCC configuration          | 60 |

|------|----------------------------------------------------------------------------|----|

| 4.7  | 10% step change in the inverter current order - CCC configuration          | 60 |

| 4.8  | 10% step change in the inverter current order - HCC-UP configuration       | 61 |

| 4.9  | 10% step change in the inverter current order - HCC-LO configuration       | 61 |

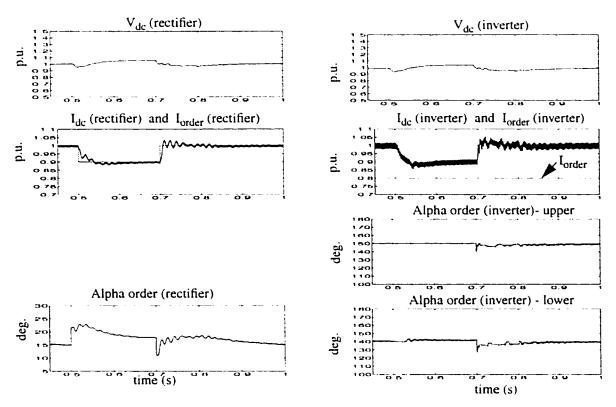

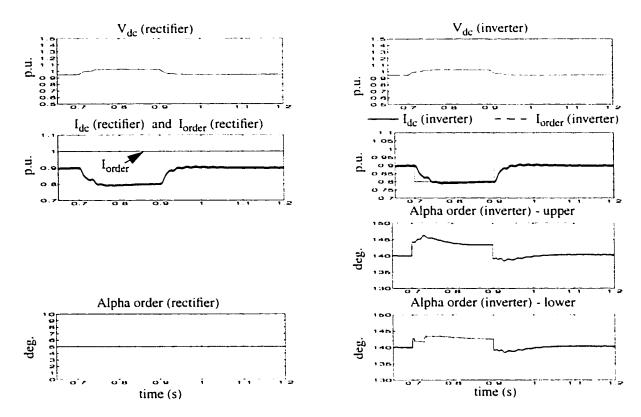

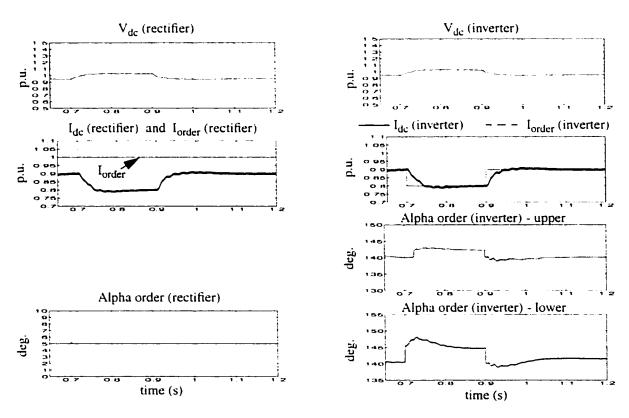

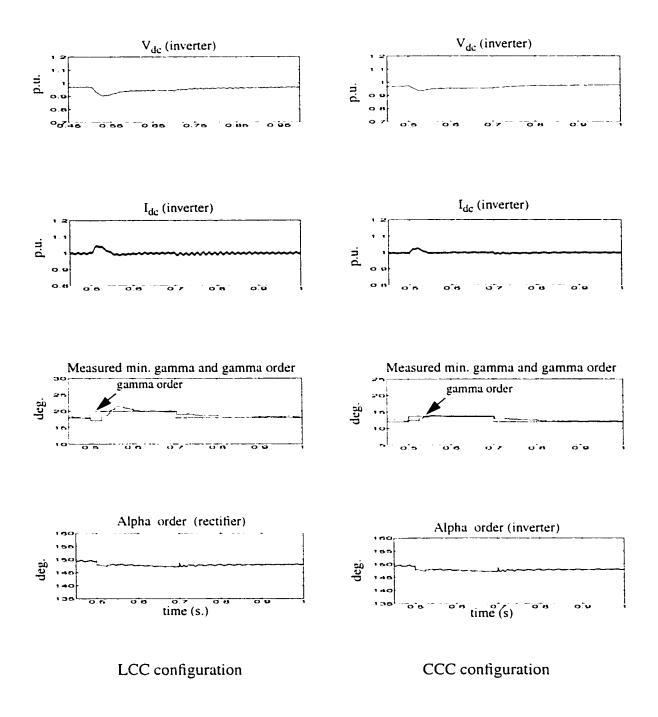

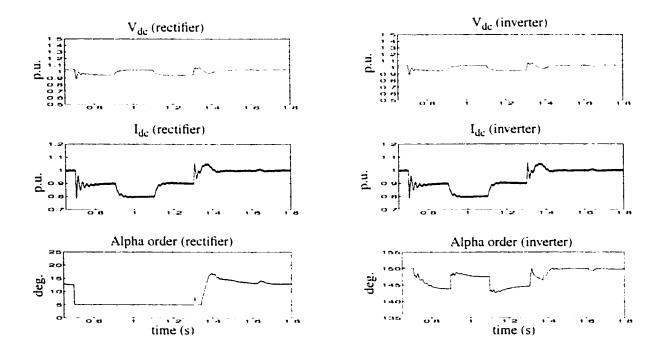

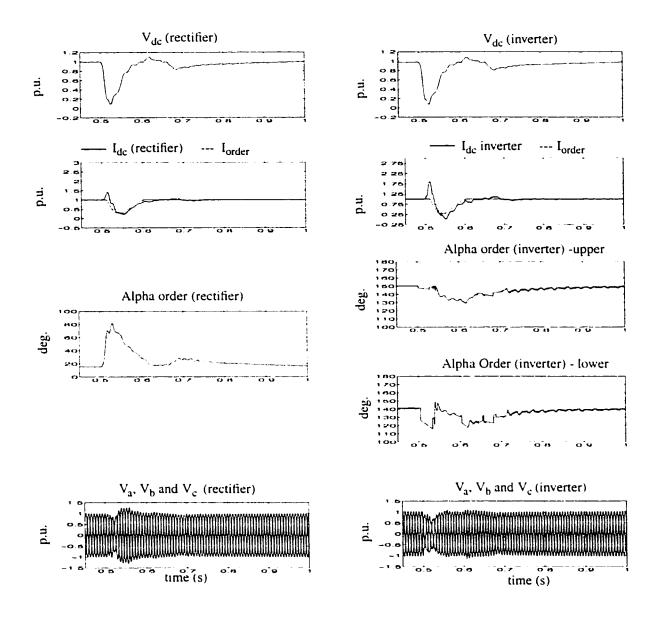

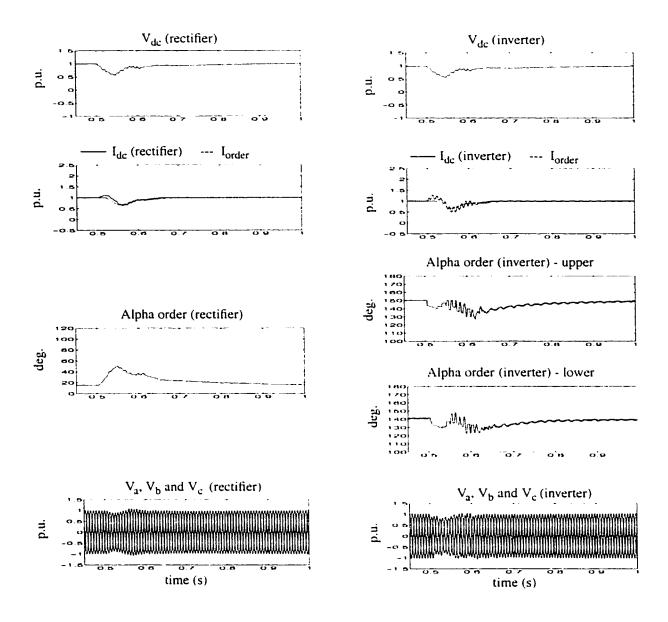

| 4.10 | 2 deg. step change in the inverter gamma order- LCC and CCC configurations | 63 |

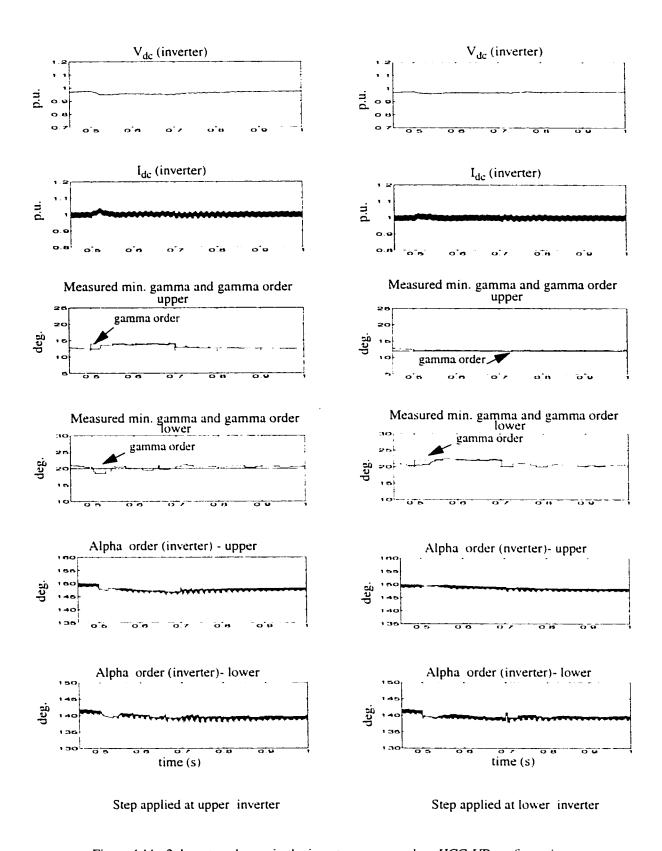

| 4.11 | 2 deg. step change in the inverter gamma order- HCC-UP configuration       | 64 |

| 4.12 | 2 deg. step change in the inverter gamma order- HCC-LO configuration       | 65 |

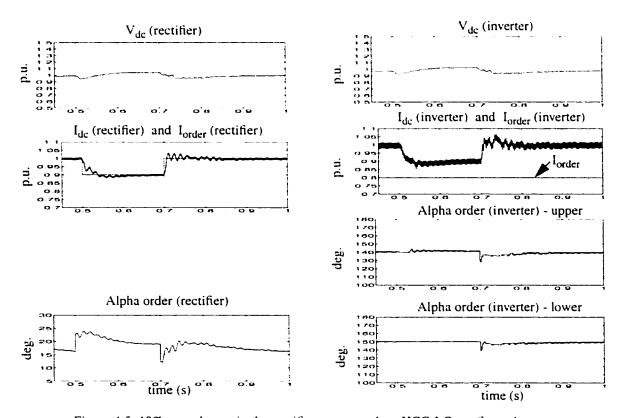

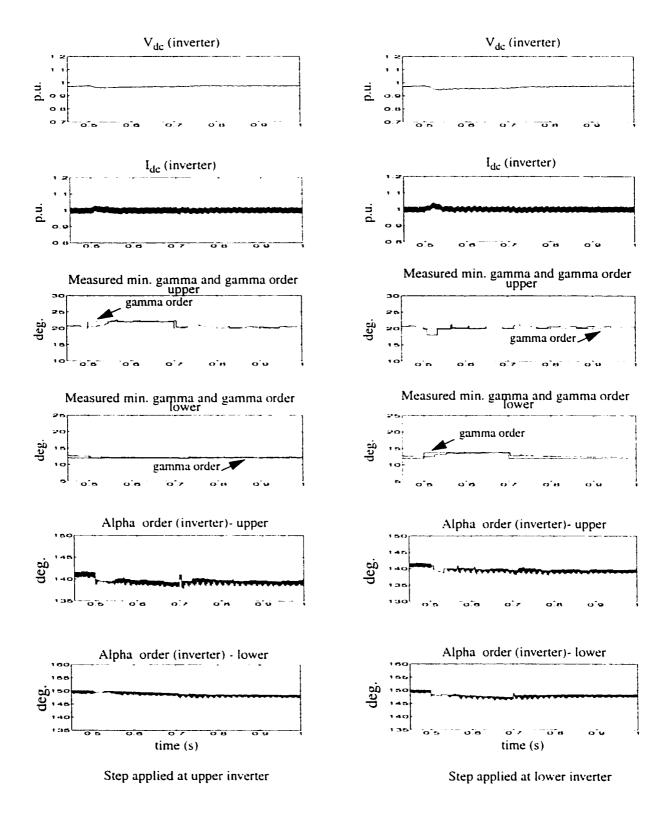

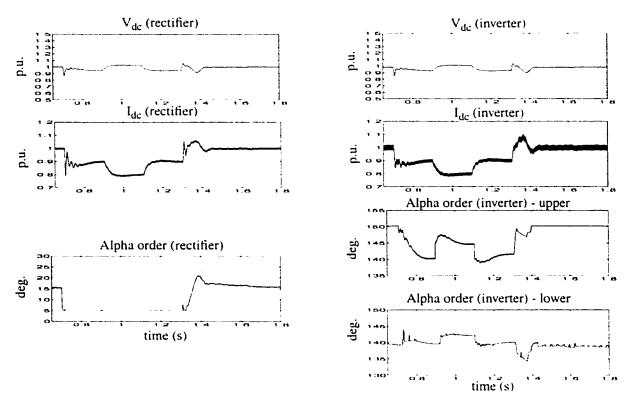

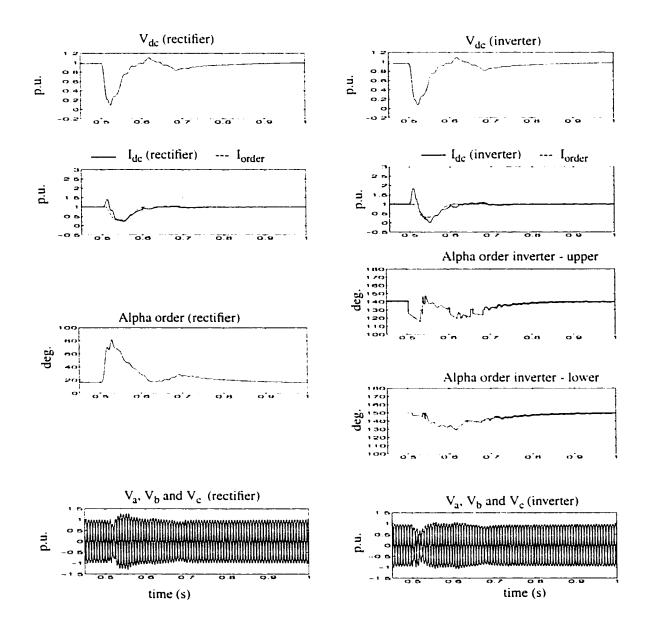

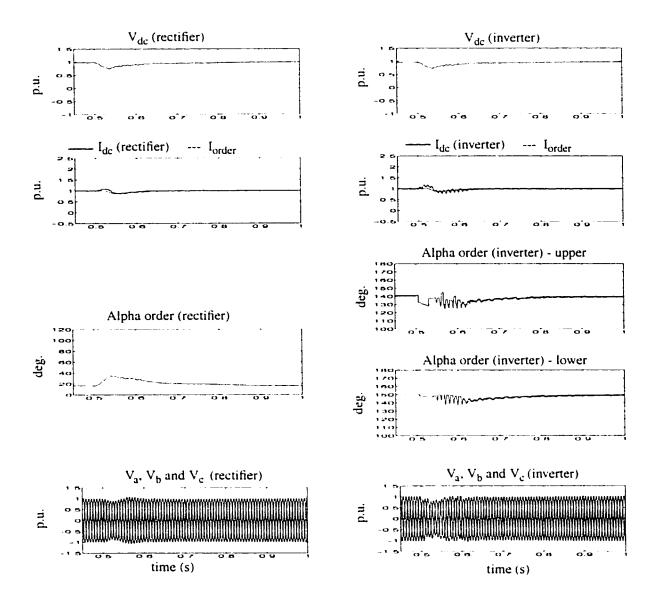

| 4.13 | Mode shift test - LCC configuration                                        | 67 |

| 4.14 | Mode shift test - CCC configuration                                        | 67 |

| 4.15 | Mode shift test - HCC-UP configuration                                     | 68 |

| 4.16 | Mode shift test - HCC-LO configuration                                     | 68 |

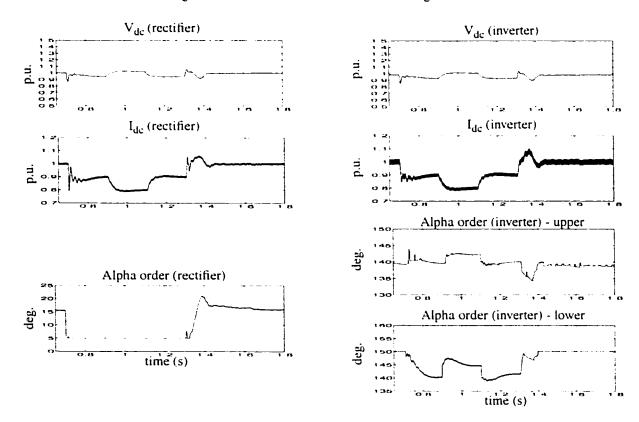

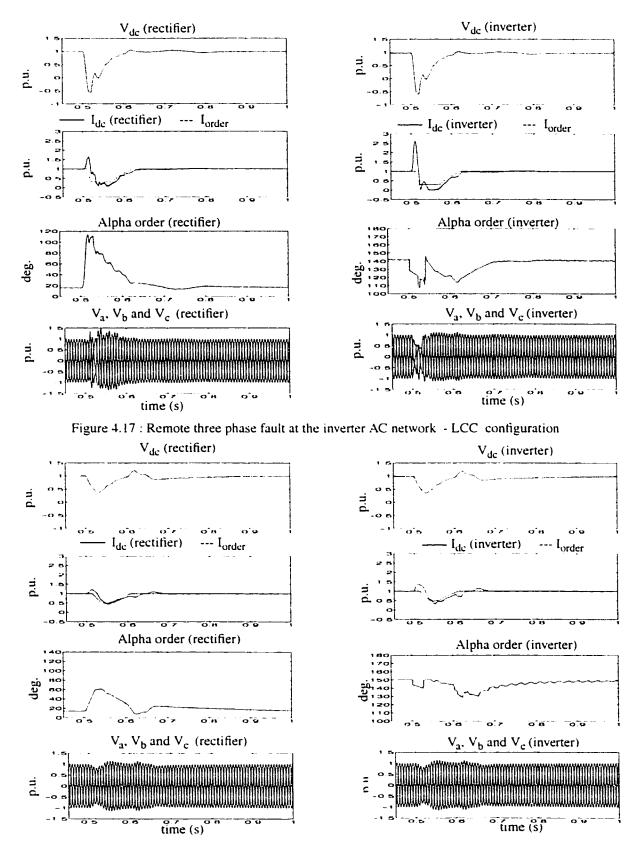

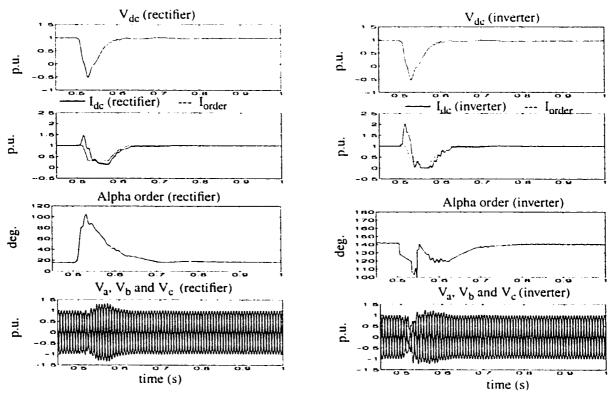

| 4.17 | Remote three phase fault at the inverter AC network - LCC configuration    | 71 |

| 4.18 | Remote three phase fault at the inverter AC network - CCC configuration    | 71 |

| 4.19 | Remote three phase fault at the inverter AC network - HCC-UP configuration | 72 |

| 4.20 | Remote three phase fault at the inverter AC network - HCC-LO configuration | 73 |

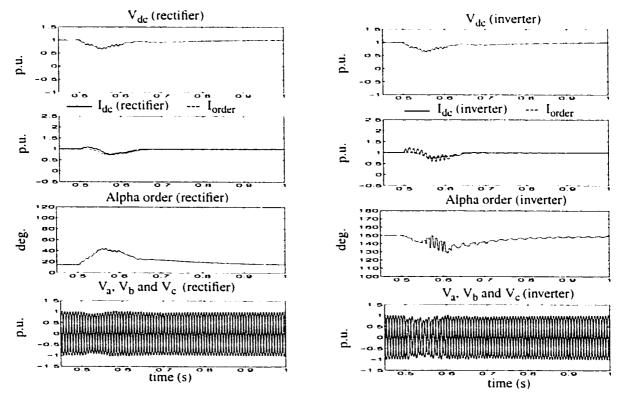

| 4.21 | Remote SLG fault at the inverter AC network - LCC configuration            | 75 |

| 4.22 | Remote SLG fault at the inverter AC network - CCC configuration            | 75 |

| 4.23 | Remote SLG fault at the inverter AC network - HCC-UP configuration         | 76 |

| 4.24 | Remote SLG fault at the inverter AC network - HCC-LO configuration         | 77 |

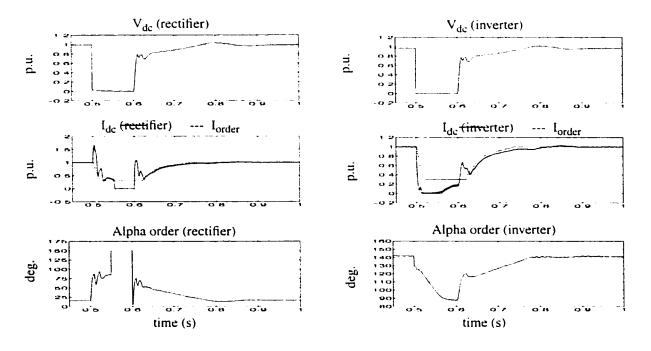

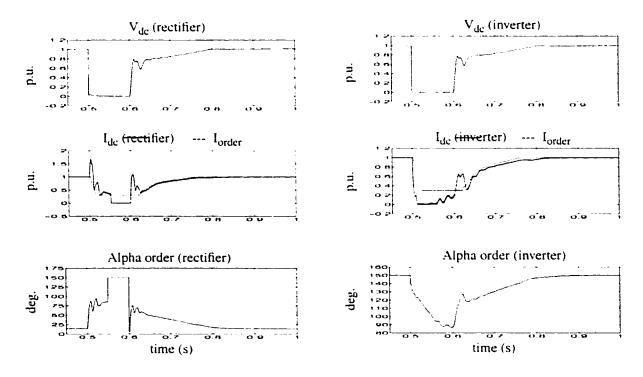

| 4.25 | Inverter side DC line fault - LCC configuration                            | 79 |

| Figure No.                                               | Page No. |

|----------------------------------------------------------|----------|

|                                                          |          |

| 4.26 Inverter side DC line fault - CCC configuration     | . 79     |

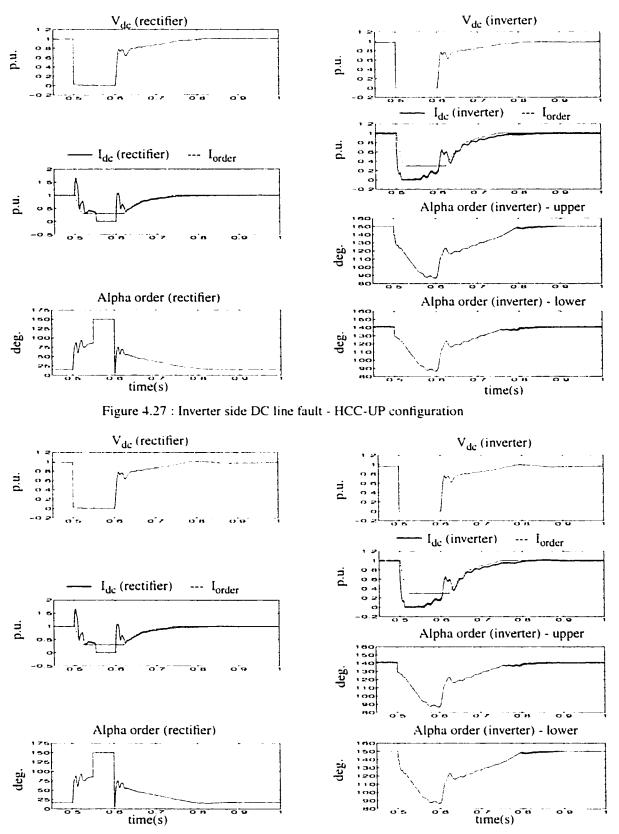

| 4.27 Inverter side DC line fault - HCC-UP configuration  | . 80     |

| 4.28 Inverter side DC line fault - HCC-LO configuration  | . 80     |

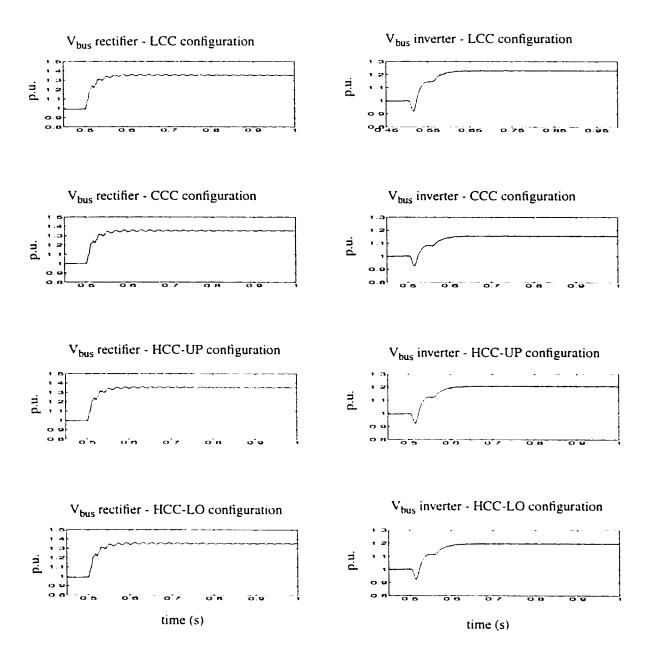

| 4.29 Load rejection over-voltage at the converter AC bus | 82       |

|                                                          |          |

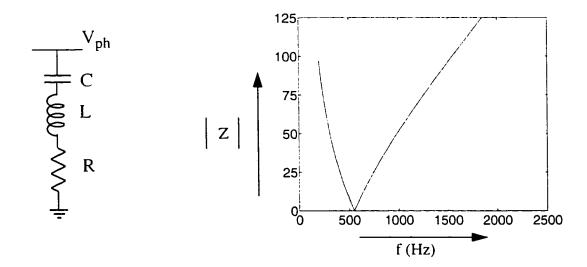

| A.1 R-L-C filter                                         | 96       |

| A.2 Frequency response of R-L-C filter                   | 96       |

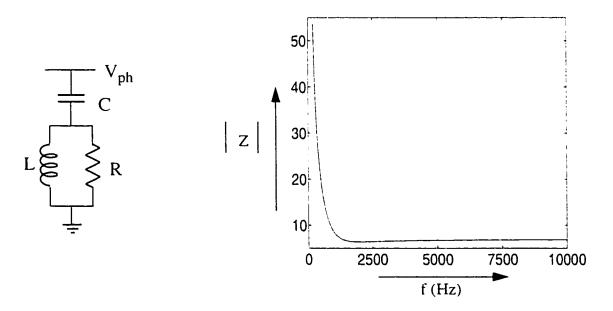

| A.3 High-pass filter                                     | 97       |

| A.4 Frequency response of high-pass filter               | . 97     |

### List of Tables

| Table No. |                                     | Page No |

|-----------|-------------------------------------|---------|

|           |                                     |         |

| Table 1:  | Controller Gains                    | 53      |

| Table 2:  | Comparative Results                 | 83      |

| Table 3:  | Signals Monitored                   | 99      |

| Table 4:  | Test Cases                          | 99      |

| Table 5:  | Details of Filter Parameters        | 100     |

| Table 6:  | Details of Characteristic Harmonics | 100     |

#### List of Abbreviations

AC - Alternating Current

DC - Direct Current

HVAC - High Voltage AC

HVDC - High Voltage DC

SC - Short Circuit

SCR - Short Circuit Ratio

CC - Commutation Capacitor

CCC - Capacitor Commutated Converter

CSCC - Controlled Series Capacitor Converter

TCSC - Thyristor Controlled Series Capacitor

PSCAD - Power System Computer Aided Design

EMTDC - Electromagnetic Transient DC

IGBT - Insulated Gate Bi-polar Transistor

VSC - Voltage Source Converter

CO - Current Order

CIGRE - The Conseil International des Grands Reseaux Electriques

EMTP - Electromagnetic Transient Programme

VDCL - Voltage Dependent Current Limiter

CEA - Constant Extinction Angle

LCC - Line Commutated Converter

HCC-UP - Hybrid Converter Combination with CC in the upper bridge

HCC-LO - Hybrid Converter Combination with CC in the lower bridge

VCO - Voltage Controlled Oscillator

PI - Proportional and Integral

AO - Alpha Order

AOr - Alpha Order rectifier

AOi - Alpha Order inverter

GO - Gamma Order

SLG - Single Line to Ground

VV - Valve Voltage

CM - Current Margin

# Chapter -1

#### Introduction

#### 1.1 Background to HVDC Systems

Since most power generating stations have been developed at remote sites from load centres, the need for bulk power transfer over long distance arises. It is practical and economical to transmit power at high voltage levels to minimize transmission line losses. Out of two available means of power transmission, such as HVAC and HVDC, the latter is advantageous for the following reasons:

- 1. The cost per unit length of transmission is cheaper for HVDC than for AC transmission.

- 2. A DC transmission tower has less visual profile (and lower environmental impact) than an equivalent AC transmission,

- 3. The break even distance for submarine cable transmission is much less than that of overhead transmission. AC power transmission through cable becomes impractical for distances more than 50 km but transmission of power by DC cable is feasible even for a distance of 600 km.

- 4. DC Link enables power transfer between two asynchronous systems.

- 5. Power control through a DC link is faster.

Conventional two terminal HVDC systems have been using line commutated converters at both ends. These converters rely on the AC network line voltage for commutation. Hence performance of the conventional converters are greatly affected by the AC network strength. Network strength of the AC system is measured by Short Circuit Ratio (SCR) which is defined as

A system is said to be weak if SCR is less than 3. A weak system is more sensitive to voltage fluctuations which causes problems in the HVDC transmission system, and special control methods may be needed to partially alleviate this problem.

In developing countries the demand for electricity is growing at a high rate due to industrial development. As a net effect, load centres keep growing larger. Power utilities are left with the choice of either adding capacity locally or importing power to load centres from remote sources. Capacity addition often implies a large investment and it may be coupled with environmental impacts. This increasing gap between supply and demand often results in making the existing power systems weaker with increasing demand. Consequently, it is now being envisaged that HVDC systems need to interact with AC networks with a SCR as low as 1.8.

Importing power to such a weak AC network using conventional converters is not a very reliable proposition because conventional converters suffer from frequent commutation failures. During commutation failure, power through the DC link becomes zero. This momentary interruption of power may have repercussions on AC networks at both ends. It

may cause voltage and frequency instability which may lead to a total shut down for a longer period of time. Also, frequent commutation failures can cause permanent damage to the valves.

Recent studies have focussed on the improvement of the commutation process by using series capacitors in the commutation circuit. This can reduce the chances of a commutation failure occurring.

#### 1.2 Problem Definition

HVDC systems have been using conventional converters which depend on the AC network voltage for commutation. The voltage condition of the network is a function of the network strength which is expressed by its short circuit ratio (SCR). Increasingly, due to growing gap between supply and demand, HVDC systems need to interact with AC networks having a very low value of SCR. As a result, line commutated converters experience more frequent commutation failures in new installations. Also, an HVDC system with a long DC cable link may face the same problem even when it interacts with a strong AC system. Besides, a conventional converter consumes reactive power of the order of 55-60% of the rated DC power. Large filters and capacitor banks used for the purpose of compensation increase the cost of the converter station and may result in operational problems such as the development of low frequency resonance with the AC network.

The concept of using a capacitor for commutation purposes was developed back in the 1950's, but no initiative towards its implementation was taken because of one or more of the following reasons.

- The AC systems were usually quite strong, i.e. SCR was not low

- Problems of resolving economically the extra voltage stresses across the converter valves did not exist

- Difficulty in management of reactive power. In the case of a CCC, total reactive power requirement being low (approximately 15% of the rated DC power), it is necessary to have filters only for the purposes of harmonic elimination and not for reactive power supply. The very nominal reactive power variation is manageable by switching a small capacitor bank. However, due to manufacturing constraints it was not possible to utilize filters with low values of capacitance at high Q-values. Such filters would easily go out of tune resulting in poor filtering. But recent developments in filter design have resulted in techniques for easily tuning high-Q filters using low values of capacitance [4]. Such filters can now be designed primarily for harmonic filtering.

#### 1.3 Literature Survey on Capacitor Commutated Converters

# 1.3.1 A Technical Assessment of Artificial Commutation of HVDC Converters with Series Capacitors [2]

The authors in [2] have discussed the principle of artificial commutation and how the operational range, in terms of firing angle, can be extended beyond normally attainable range. They have modeled a three phase full wave bridge configuration with series capacitors added in the commutation circuit. They have established the mathematical relationship(s) among commutation voltage, direct current, overlap angle, firing angle and voltage across the capacitor and provided the iterative solution using comprehensive computer programs. In converter operation, valves undergo varying stresses throughout the cycle.

The authors in [2] have presented the instantaneous value of the valve voltage for eight different periods over a complete cycle. Finally, they have presented a detailed comparison between natural and artificial commutation considering selected system ratings of  $V_{LL} = 1000 \text{ kV}$ ,  $I_{dc} = 1000 \text{ amps}$ ,  $X_L = 11.1 \text{ ohms}$  and f = 50 Hz and concluded that:

- For a given system, the range of permitted firing angles is determined by the values of the capacitor C and the direct current,

- Operating range can be increased by a reduction in the value of the capacitance at the expense of increase peak valve voltage,

- For a given set of conditions, the overlap angle reduces below that for natural commutation with high, but not proportionally higher, rate of change of current at the end of commutation, and

- Commutation failure is less likely to occur because of the tendency for the commutation margin to be increased for a decrease in AC system voltage or increase in direct current.

#### 1.3.2 Capacitor Commutated Converters for HVDC [4]

In [4], the authors have discussed the concept of Capacitor Commutated Converter (CCC) and how the introduction of the commutation capacitor (CC) can improve the performance of a conventional HVDC system by reducing the chances of commutation failure and reactive power consumption/demand of the converter stations.

Because of the additional commutation voltage, the operating range of the rectifier delay angle and the inverter extinction angle is increased. Consequently, the operation of the rectifier and the inverter can be achieved with smaller values of alpha and gamma respectively. The reactive power consumptions of both the converter stations are therefore reduced. Studies show that in case of the HVDC system with conventional converters, the reactive power requirement varies with the load. Therefore, the switching of shunt capacitor bank is necessary as the load varies. But in the case of an HVDC system with CCC, the reactive power requirement is limited to a very low (about 0.14 p.u.) value. The need for switching of the shunt capacitor bank can thereby be reduced or eliminated. Also, with extended operating range of alpha/gamma, the system has more flexibility of sharing the reactive power by the converter stations though the total reactive power remains same for any particular load.

Simulation results show that with constant load current and firing angle, commutation margin increases with decrease in AC bus voltage and vice versa. The authors in [4] have concluded that successful commutation is possible even when the AC bus voltage is close to zero. Transient analysis shows that CCC can successfully commutate with reduced AC bus voltage. Also, because of the presence of the commutation capacitor, peak fault current and its duration is less. Load rejection overvoltage performance of the CCC option is better than that of the conventional option. As the commutation voltage is current dependent, any sudden change in direct current may cause a momentary imbalance in the commutation voltage which may make a valve reach its critical commutation margin. The authors in [4] have discussed a control strategy to prevent this momentary voltage imbalance.

Even though CCC has higher power transfer capacity, it has certain drawbacks. The

voltage stress of the valves and the insulation level of the converter transformer are higher.

Also, because of smaller overlap angle the level of harmonic currents is higher.

Finally the authors in [4] have conducted cost analysis taking care of all practical aspects e.g. higher voltage stress on valve and higher insulation level of the transformer winding and the reduced size of the transformer and filter, and have concluded that HVDC transmission with CCC is economical as compared to the conventional option which consists of line commutated converters (LCC) only.

# 1.3.3 Capacitor Commutated Converter Circuit Configurations for DC Transmission [5]

The authors in [5] have identified commutation failure as the major problem of the conventional HVDC system specially while interacting with weak AC networks or strong AC networks with long DC cable link. They have described two different configurations of converters, namely, Capacitor Commutated Converter (CCC) and the Controlled Series Capacitor Converter (CSCC). In CCC, the commutating capacitor is placed between the transformer and the valves, whereas in the case of CSCC it is placed between the AC network and the converter transformer. A comparative simulation study has been carried out using PSCAD/EMTDC.

Since CCC and CSCC have improved performance with respect to Maximum Available Power (MAP), therefore stability limit as compared to the conventional configuration is improved. The Stability limit is increased to 1.44 p.u. and 1.34 p.u. for CCC and CSCC, respectively. The valve voltage stress is also increased. Both the configurations require

reduced reactive power, and hence the size of the shunt capacitor is reduced. Results show that reactive power requirement is only 15% of the rated power as compared to 55-60% in the case of the conventional option which consists of LCC only. Also, the magnitude of the harmonic currents is more for these two configurations because of reduced commutation overlap.

Transient analysis shows that both CCC and CSCC exhibit smooth recovery against the application of typical AC bus faults. Also, both can easily ride through disturbances such as a remote AC fault without any commutation failure.

The authors in [5] have overcome the ferroresonance problem which is encountered for a certain fixed value of the commutation capacitor. They have over come this problem by using Thyristor Controlled Series Capacitor (TCSC). Simulation result shows that ferroresonance problem has been fully eliminated when capacitor control is used.

Finally, it is concluded that both CCC and CSCC have improved immunity from commutation failure, lower load rejection and increased stability margin as compared to the conventional option. Hence, these two options can be considered suitable for use at the inverter end in a long DC cable system.

# 1.3.4 Impact of Capacitor Commutated Converters in AC Systems with multiple DC Infeed [6]

In [6], the authors have investigated the possibility of the degradation of the overall performance of HVDC systems consisting of several cable links (multiple infeed) between strong and weak AC networks at the rectifier and inverter end respectively.

They have considered the Norwegian Power Grid which has many pre-existing conventional DC links. With another one or two links in the planning stage, they have carried out studies to find out a suitable option such as conventional or CCC for the new links. In the simulation, all existing links are lumped and represented by a DC link with conventional converters at both ends. Similarly, all the new links are lumped and represented by a DC link with conventional converters at sending end and CCC at the receiving end. Three cases are studied:

- i) The existing link alone

- ii) The planned link alone

- iii) The combined system i.e. both existing link and the planned link together.

Special controls are used to prevent total collapse of the inverter DC voltage and for successful recovery of the system.

Various disturbances (i.e. three phase remote fault, step change in current order, load change and load rejection) are applied to the systems. Compiling all the results, they have concluded that in such a multi infeed system involving long submarine DC cables the over all performance would be better if any one of the links is chosen to have a CCC inverter.

# 1.3.5 Application of Capacitor Commutated Converters in multi-infeed HVDC schemes [7]

In [7], the authors have investigated the suitability of various inverter options in a multi- infeed HVDC system. The Norwegian Power Grid [6] is considered for the study. They have modeled the whole system with two HVDC links having conventional convert-

ers at the rectifier end interacting with two separate strong AC networks. At the inverter side, a common and weak AC network is considered. One of these two link, having a total capacity of 1600 MW, represents all existing links where as the other, having a total capacity of 1200 MW, represents all the links in the planning stage. Similar controls to [6] are adopted. Three distinct cases are studied:

- Case -I (Conventional) Both 1600 MW and 1200 MW links have conventional inverters,

- Case -II (Mixed) The 1600 MW link has conventional inverters and the 1200 MW link has CCC inverters, and

- Case -III (CCC) Both 1600 MW and 1200 MW links have CCC inverters.

Transient studies such as load rejection overvoltage, remote AC fault, fault at the AC bus of the inverter and step change to direct current order are carried out. Considering all the results, the authors have concluded that all options provide a level of performance that falls within generally acceptable limits but conventional alternative has in general the better performance.

They finally concluded that if load rejection overvoltage are not of critical importance then the conventional alternative has in general the better performance.

#### 1.3.6 An AC Active Filter for use at Capacitor Commutated HVDC Converters [8]

In [8], the authors have discussed the usefulness of an active filter for elimination of low order harmonics (11th and 13th) from the AC side of the HVDC system using a CCC.

In case of CCC or CSCC, filters are needed mainly for harmonic elimination and provide only a very small amount of reactive power support. Such filters with very low MVAR rating are more susceptible to de-tuning. In some cases, continuously tuned inductors are used to cope with this problem. The authors have described how the re-tuning of filters can be effectively realized by using an active filter developed by using a PWM technique.

The voltage of each phase is taken as a reference to the respective FFT block which determines the magnitude and phase of the targeted harmonics (here 11th and 13th) separately. The output of the FFT block is fed to a control system which re-calculates the real and imaginary parts of each harmonic voltage. A PI controller is used to control each part separately. At the output of the control system a combined waveform is obtained which is used as a voltage order for the PWM inverter. The output of the Voltage Source Converter (VSC) is applied to a transformer whose secondary injects the counter current into the converter bus to eliminate the low order characteristic harmonics.

Finally, taking an active filter into consideration, they have modeled a 1200 MW, 600 km long cable HVDC system having conventional rectifiers at one end and CCC inverters at the other end interacting with strong and weak AC system at the rectifier and inverter ends respectively. In the transient study, a three phase fault was applied at the inverter bus. The response of the DC bus voltage shows a smooth recovery. Also the controller is tested by using a 50% step in Current Order (CO) and the result shows that harmonic current is also reduced with the DC current order and the system responds quite well to the step change.

The authors in [8] have concluded that an active filter is a very attractive alternative to

passive/continuous tuned filter for CCC HVDC system application.

# 1.3.7 Evaluation of Classical, CCC and TCSC Converter Schemes for Long Cable Projects [9]

In [9], the authors have compared the features and simulated dynamic performance of series compensated and conventional HVDC converters with respect to long cable transmissions. Two series compensated converter technologies namely CCC and TCSC are included. In the CCC, the commutating capacitor is placed between the converter transformer and the valves whereas in the TCSC it is located between the AC network and the converter transformer. The conventional converters on the other hand, are connected directly to the converter transformers.

They pointed out that conventional technology is well established and can be best used between relatively strong AC networks where the need for AC filtering is moderate and reactive power balance is not a critical factor. Also, in classic HVDC converters, the basic problems involved were higher reactive power demand, higher sensitivity to inverter side AC network disturbances specially when a DC cable link is used.

The authors in [9] have carried out simulation studies with data of a planned project to transmit 2100 MW via an under-sea cable over a distance of 670 km. Comparison shows that the series compensated designs such as CCC and TCSC, improve the performance of HVDC transmissions connecting weak AC networks in terms of increased power flow and improved stability of the AC network, reduced load rejection over-voltages and consumed smaller amount of reactive power. Reduced reactive power means savings in capacitor

banks and breakers, and also the maintenance of the AC yard equipment is reduced.

With the above new converter designs, the HVDC technology for feeding weak networks is improved, and the choice among the three converter designs could be based on the type of AC network that will be fed by the HVDC transmission. Each design has its own advantages, but the properties of each design point to somewhat different applications.

Finally the authors in [9] concluded that

- The classic design is the cost effective solution for connecting relatively strong AC networks, where the demands of AC filtering are moderate and where there are only moderate demands on reactive power balance.

- The CCC design is a cost efficient solution for connecting weak AC networks, since a

high power transfer can be combined with a high stability margin in the inverter network. The stability does not have to rely on additional equipment, such as synchronous

condensers or additional series compensation.

- The TCSC design, in connection with an HVDC converter, is suitable for the same range of applications as those with the CCC, with performance compatible with the CCC design, but with reduced cost efficiency.

# 1.3.8 Predictive Firing Angle Calculation for Constant Effective Margin Angle Control of CCC - HVDC [10]

In [10], the authors proposed a predictive firing angle calculation method for Capacitor Commutated Converter (CCC). They have formulated the relations among various param-

eters for the commutation and post commutation periods. Because of the presence of the CCC, the relationship among  $\alpha$ ,  $\mu$ ,  $\gamma$ ,  $V_{ac}$  and  $I_{dc}$  are complex and an iterative method is used for the solution. Also, the convergence of the solution depends on the initial values of  $\alpha$  and  $\mu$  and they have found out various combination of  $\alpha$  and  $\mu$  for which convergence is possible.

Three cases are investigated for three different sizes of the commutation capacitor. They have incorporated this predictive angle calculation algorithm to the controller and tested the system by applying steps in direct current and AC bus voltage.

#### 1.4 Thesis Objectives

The objectives of this thesis are:

- To evaluate the performance of an HVDC system based on Capacitor Commutated Converters (CCC) in terms of its steady state and dynamic/transient behaviour, and

- To modify the CCC configuration and evaluate this modified version namely a Hybrid

Converter Combination (HCC), using both traditional line commutated converter and a

capacitor commutated converter to access its viability in terms of technical suitability

and lower cost.

#### 1.5 Methodology

An HVDC system based on the CIGRE HVDC benchmark is chosen for study [13]. The system consists of subsystems e.g. AC networks, converters, filters, converter trans-

formers and a DC link. The whole system is modeled by using the PSCAD/EMTDC simulation package [23]. Also, control and protection circuits are developed. This benchmark is used to study the performance of a system with Capacitor Commutated Converters (CCC). Using the capacitor commutated converter for one bridge and line commutated converter for the other bridge, a new configuration namely HCC, is developed and some modifications are proposed to achieve independent control of converters. The same benchmark model is used to study the performance of conventional and proposed hybrid configurations. Finally, a comparative study of the dynamic and steady state performances of these three systems is made.

#### 1.6 Thesis Outline

In chapter 2, background information to HVDC systems is presented. Each subsystem of the HVDC system is described briefly. Also, overall control and protection strategies are discussed.

In chapter 3, different converter configurations are presented, the effect of the capacitor in the commutation circuit and the control implementations are discussed

In chapter 4, behaviour of the HVDC system under transient conditions is discussed. Different fault conditions are applied. Also, controllers are tested by applying steps in current order/gamma order. Finally results are presented and analyzed.

In chapter 5, conclusions from this study and recommendations for further work are provided.

#### 1.7 Thesis Contributions

The dynamic performance of a modified converter configuration namely Hybrid Converter Combination (HCC) is studied and compared with two other configurations namely LCC and CCC. Study reveals that:

HCC option can be considered as a special case of CCC where one of the capacitor

banks is out of service due to some contigency. The ability to operate the station with

this contingency is an improvement in the security of the power supply.

# Chapter 2

#### **HVDC System and Control Strategy**

#### 2.1 Introduction

The main objective of this thesis is to evaluate the performance of an HVDC system using different converter configurations. Hence, an HVDC system model is required for this purpose. A benchmark model for the study of HVDC systems has been developed by CIGRE [13] (The Conseil International des Grands Reseaux Electriques), an international association based in France. Both manufacturers and users from all over the world have been using this benchmark model for testing and evaluating the performance of controllers for HVDC systems.

In this chapter, we consider the CIGRE benchmark-based HVDC system operating with weak AC networks and its control strategy.

#### 2.2 CIGRE Benchmark-Based HVDC System

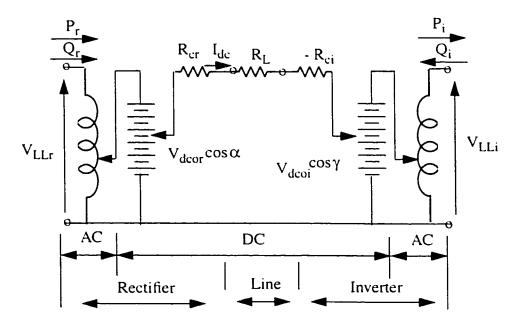

Figure 2.1 represents an HVDC system based on the CIGRE benchmark [13]. The values (e.g. ratings etc.) proposed are fictitious and do not represent any particular scheme. The system has been particularly selected to have an operationally difficult configuration. The original CIGRE benchmark is a 12-pulse bipolar system but in this study, a 12-pulse

monopolar configuration is considered. This reduces the computer simulation time and minimizes memory requirements. At each end, the DC link interacts with weak AC systems having a Short Circuit Ratio (SCR) of 2.5. The CIGRE benchmark is based on a fundamental frequency of the AC systems of 50 Hz. The inverted tree form (figure 2.2) shows different subsystems and control systems of the benchmark.

Figure 2.2: Inverted tree showing subsystems of the CIGRE benchmark

# 2.3 Description of Subsystems

The following subsections describe the operation of the various subsystems.

#### 2.3.1 AC Network

The HVDC system is connected to a 50 Hz AC network at each end. The AC network

is represented by the Thevenin equivalent of the whole system behind the AC bus. In this benchmark a weak AC network is considered for each end; the impedance angles of the AC systems (84° at the rectifier end and 75° at the inverter end) are chosen to provide the necessary damping to the systems. Also, source parameters are selected such that both the sending end and the receiving end AC systems have an impedance peak near 100 Hz (i.e. second harmonic). The purpose of such selection is to create stringent operational conditions for the controllers.

#### 2.3.2 AC Filter

The main purpose of the AC filters is to eliminate harmonics produced by the converters. Thus, unwanted harmonics are prevented from entering the AC system. The 12-pulse converter system generates characteristic harmonics of the order of 11th, 13th, 23rd, 25th, 35th, 37th and so on. In this simulation, passive tuned shunt R-L-C are used for removing lower order harmonics (i.e. 11th and 13th) and a high-pass filter is used for higher order harmonics (23rd and above). The design procedure and the frequency response of the filters are provided in the Appendix.

#### 2.3.3 Shunt Capacitor Bank

The filters also generate a fixed amount of reactive power at the fundamental frequency. The reactive power requirement of the converters varies with the load. Passive shunt filters are used to supply 70 - 80% of the total reactive power requirement of each converter station. The remaining reactive power is compensated for by the capacitor banks. In this simulation, capacitor banks are represented by a fixed capacitor. The

arrangement of filters and the capacitor banks are shown in figure 2.3. Calculations for capacitor sizing are shown in the Appendix.

Figure 2.3: AC filter bank

#### 2.3.4 Converter Transformer

In a 12-pulse converter system, two 6-pulse converter units are connected in series. Each 6-pulse converter unit is connected to the secondary of a converter transformer. The size and the voltage rating of each converter transformer is equal and their combination is suitable to handle the rated power at the rated voltage. Secondary (valve side) windings of one transformer are connected in STAR configuration and the other transformer windings in DELTA configuration to help cancel out some of the characteristic harmonics. The primary windings of each transformer are connected in STAR configuration with the neutral solidly grounded. Grounding provides a path for zero sequence currents caused by any asymmetrical fault in the AC system. The leakage reactance of the transformer is chosen as 18% (typical value) which is sufficient to limit the fault current through the valves. In

practice, it is always economical to design a single unit, three-phase transformer, but sometimes it becomes necessary to split the transformer into three single-phase units to facilitate transportation. In this simulation, a single unit of a three-phase transformer is considered. Converter transformers are provided with an On Line Tap Changer (OLTC), generally of the order of  $\pm 15\%$ . In the event of any variation in the AC system voltage, the operating delay angle of the converter shifts immediately and it is brought back again to the normal position by means of a comparatively slow acting OLTC. In this simulation no tap changer is considered because we are concerned only with transient phenomena. Calculations of transformer sizing are presented in the Appendix.

#### 2.3.5 Converter

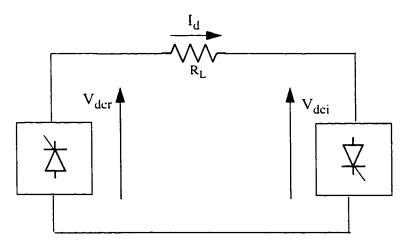

The converter unit does the conversion from AC to DC and vice versa. In the 12-pulse model used here, the primary windings of the converter transformers at both ends of the DC link are solidly grounded.

Figure 2.4: 12-pulse converter arrangement

Each 12-pulse converter unit consists of two 6-pulse converter bridges connected in series at the DC side. AC side of each converter bridge is connected to a separate converter transformer. Figure 2.4 shows a 12-pulse converter arrangement. The equivalent circuit of both the converters i.e. rectifier and the inverter, are shown in figures 2.10 and 2.11, respectively. The converter valves are protected against voltage surges by means of R-C snubber circuits and current surges by means of a smoothing reactor. The effect of snubber parameters on valve voltages are discussed in section 2.4.1

#### **2.3.6 DC** System

The DC system consists of DC cable, DC filters and smoothing reactor. In this simulation, a T-network is used to represent the DC cable. Since the inductance of the DC cable is very low, it is neglected in the simulation.

DC filters are used to eliminate higher order harmonics which may otherwise cause interference with nearby voice frequency communication circuits. For an HVDC system using a cable as a transmission link, this interference problem does not arise. Hence, DC filters are not used in this simulation with a cable.

A smoothing reactor is usually included in each pole of the converter station to satisfy the following requirements:

- Make the commutation process more robust by limiting the rate of change of direct current,

- 2. Form a DC filter in combination with the cable capacitance to smooth the direct cur-

rent so that a continuous current is maintained even at light load conditions.

Figure 2.5: T- equivalent circuit to represent the DC cable link with smoothing reactor

The equivalent circuit for the DC cable along with smoothing reactor is shown in figure 2.5

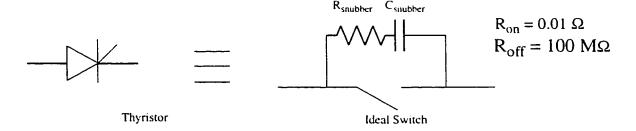

#### 2.4 Thyristor Modeling

In practice, a series combination of thyristors is used to achieve the required valve voltage handling capacity. Each thyristor is protected against a high rate of rise of voltage and current.

In PSCAD/EMTDC, a valve is modeled by an ideal switch having two distinct states i.e. ON and OFF. In the ON-state the valve is represented by a very small resistance (here it is  $0.01\Omega$ ) and in the OFF state it is represented by a very high resistance (here it is  $100~\mathrm{M}\Omega$ ). Also, there is a snubber circuit to protect the valve against a rapid rise in voltage. Large smoothing reactor protects the valves against rapid rise in current. The valve and its equivalent model are shown in figure 2.6

In this model, turn on and turn off time are not considered. But the model takes care of

Figure 2.6: Equivalent circuit for the thyristor switch

the Reverse Recovery time. In all simulations the value of Reverse Recovery time is taken as  $555\mu s$  which is equivalent to  $10^{\circ}$ .

#### 2.4.1 Choice of Snubber Parameters

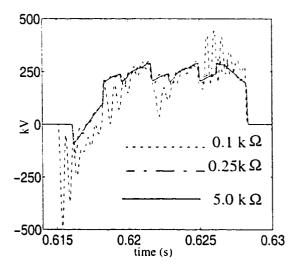

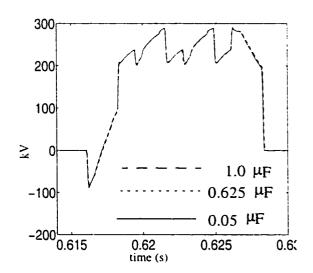

Snubber parameters i.e.  $R_{snubber}$  and  $C_{snubber}$  have an effect on the valve voltage. These parameters are not specified in the CIGRE benchmark. It is a fact that inappropriate values for  $R_{snubber}$  and  $C_{snubber}$  can lead to poor operation, over voltages and cause an erroneous measurement in delay angle specially when interacting with weak AC networks.

In figures 2.7a and 2.7b the effect of snubber resistance and capacitance are shown. It is evident from the figures that resistance has more impact on the valve voltage than the capacitor. The parameters  $R_{snubber}$  and  $C_{snubber}$  are adjusted until the satisfactory commutation voltage across the valve is obtained. In this simulation the value of  $R_{snubber}$  =5000 $\Omega$  and  $C_{snubber}$  = 0.05 $\mu$ F were selected for the snubber. However, it is to be noted that these values have no correlation with an actual snubber circuit used in practice.

Figure 2.7a: Variation of VV with R<sub>snubber</sub>

Figure 2.7b: Variation of VV with C<sub>snubber</sub>

Figure 2.8a: Valve voltage showing dv/dt

Figure 2.8b: Valve current showing di/dt

# 2.5 Analysis of Converter Bridge

Figure 2.9 shows a conventional 6-pulse converter bridge

The following assumptions are made for the analysis of the converter:

- Direct current I<sub>dc</sub> is constant.

- Valves are ideal switches, and

- AC system is strong (infinite).

Figure 2.9: 6-pulse bridge circuit

Due to the leakage reactance of the converter transformer, commutation from one valve to the next is not instantaneous. An overlap period is necessary and depending on the magnitude of the leakage reactance, either two, three or four valves may conduct at any one time.

The analysis of the bridge gives the following DC output voltages:

For a Rectifier:

$$V_{dcr} = V_{dcor} \cdot \cos \alpha - R_{cr} \cdot I_{dc} \tag{1}$$

where

$$V_{dcor} = \frac{3}{\pi} \cdot \sqrt{2} \cdot V_{LLr}$$

and

$$R_{cr} = \frac{3}{\pi} \cdot \omega \cdot L_{cr}$$

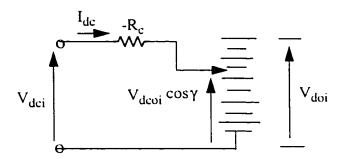

For an Inverter:

There are two options possible depending on the choice of the delay angle or extinction angle as the control variable

$$V_{dci} = V_{dcoi} \cdot \cos \beta + R_{ci} \cdot I_{dc}$$

(2)

$$V_{dci} = V_{dcoi} \cdot \cos \gamma - R_{ci} \cdot I_{dc}$$

(3)

where

$$V_{dcoi} = \frac{3}{\pi} \cdot \sqrt{2} \cdot V_{LLi}$$

and

$$R_{ci} = \frac{3}{\pi} \cdot \omega \cdot L_{ci}$$

with

$V_{LLr}/V_{LLi}$  = Line to Line voltage of the ac bus Rectifier/Inverter respectively

$V_{dcr}/V_{dci}$  = DC voltage at the Rectifier/Inverter respectively

$V_{dcor}/V_{dcoi}$  = Open circuit dc voltage at the Rectifier/Inverter respectively

$I_{dc}$  = Direct current in the DC link

$R_{cr}/R_{ci}$  = Equivalent commutation resistance at the rectifier/inverter respectively

$R_L$  = Resistance of the DC link

$L_{cr}/L_{ci}$  = Leakage inductance of the rectifier/inverter transformer respectively

$\alpha$  = Delay angle

$\beta$  = Advance angle at the inverter,  $(\beta = \pi - \alpha)$

$\gamma$  = Extinction angle at the inverter,  $(\gamma = \pi - \alpha - \mu)$

$\mu$  = Overlap angle

Figure 2.10: Equivalent circuit of rectifier

Figure 2.11: Equivalent circuit of inverter

Figure 2.12: Equivalent circuit of two terminal HVDC system

#### 2.6 Purpose of Control

The main purposes of the control strategy employed are to:

- 1. Limit maximum direct current to avoid valve damage

- 2. Keep the DC voltage level high to reduce power transmission loss

- 3. Maintaining a minimum extinction angle to avoid commutation failure

- 4. Maintaining a minimum firing angle to reduce reactive power consumption

#### 2.6.1 Control Strategy

An HVDC system can transport large amounts of power which can be accomplished under tightly controlled conditions. Both the direct current and voltage can be precisely controlled to effect the desired power transfer.

An equivalent circuit for the DC link is shown in figure 2.13. The direct current is given by

$$I_{dc} = \frac{V_{dcr} - V_{dci}}{R_{dc}} = \frac{V_{dcor} \cos \alpha - V_{dcoi} \cos \gamma}{R_{cr} + R_I - R_{ci}}$$

(4)

From equation (4), the control of  $I_{dc}$  can be achieved by:

- 1. Varying the Rectifier DC voltage

- 2. Varying the Inverter DC voltage

The rectifier side DC voltage can be controlled by two ways:

- Varying delay angle α (fast control)

- Varying AC side voltage by means of transformer tap changer (slow control)

Figure 2.13: Equivalent circuit of DC link

Similarly, Inverter side DC voltage can be controlled by two ways:

- Varying advance angle β (fast control)

- Varying AC side voltage by means of tap changer (slow control)

The DC power transmitted is given by

$$P_{dc} = V_{dc} \times I_{dc}$$

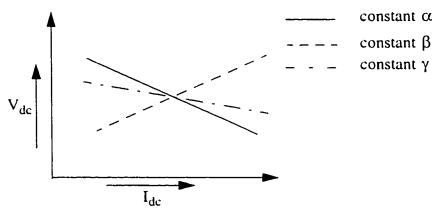

Three characteristics, as defined by equations (1) - (3), are shown in figure 2.14.

Figure 2.14: Choice of control strategy for DC link [15]

#### 2.6.2 Control Characteristics

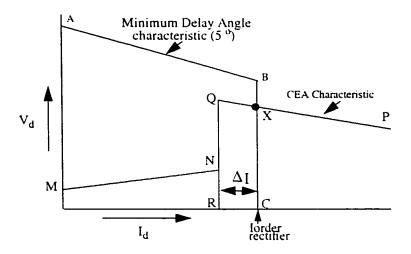

Under steady state conditions in a two terminal HVDC system, the inverter is assigned the task of controlling the DC voltage by maintaining a minimum Constant Extinction Angle (CEA) which causes the DC voltage  $V_{dc}$  to droop with increasing direct current  $I_{dc}$ . This is shown by the CEA characteristic PQ in figure 2.15. The weaker the AC system at the inverter, the steeper the droop.

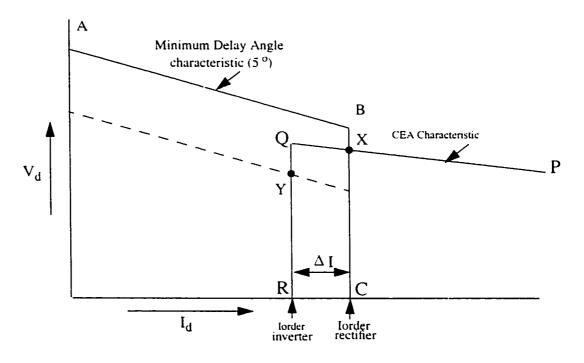

Figure 2.15: Control characteristics [15]

If the inverter is operating at a minimum constant  $\gamma$  characteristic, then the rectifier must control the direct current. In figure 2.15 the vertical line BC represents the rectifier constant current characteristic. The point X of intersection of these two characteristics (i.e.

line BC and line PQ) gives the operating point under steady state for the DC link. This operating point is reached by the action of the OLTC of the converter transformers at the inverter end.

The OLTC of the converter transformers at the rectifier end are controlled to adjust their tap settings so that the delay angle  $\alpha$  has a working range between  $10^{\circ}$  to  $20^{\circ}$  for maintaining the constant current setting  $I_{order}$ . The delay angle characteristic is shown by the line AB in Figure 2.15. If there is any voltage rise in the rectifier side AC bus, the immediate implication on the DC system will be the current increase. The delay angle will immediately be increased to maintain  $I_{dc}$  constant. Should the delay angle deviate from a set value, then the OLTC starts its action and reduces the voltage to bring back the delay angle to its normal operating point.

If there is a voltage dip, opposite action takes place. Rectifier current controller decreases the delay angle to maintain  $I_{dc}$  constant. But for a larger voltage dip, it is not possible to decrease the delay angle lower than the minimum limit (=5°), and the rectifier current controller loses its control over the current.

To counter act this situation, inverter side converter is also provided with a current controller. The constant current characteristic of the inverter is shown by the vertical line QR in figure 2.15. However, the current demanded by the inverter  $I_{di}$  is less than the current demanded by the rectifier  $I_{dr}$  by the current margin  $\Delta I$  which is typically about 0.1 p.u. The current margin is selected to be large enough to avoid any malfunction due to the presence of harmonics in the direct current.

Now, with the inverter current controller, if there is any voltage dip in the AC bus of the rectifier, the current will immediately reduce and the operating point moves from point X to point Y which is on the inverter constant current characteristic QR. At this point current is reduced to 0.9 p.u. of its previous value and the voltage control of the DC link will shift to the rectifier. However power transmission will largely be maintained near 90% of its original value.

If there is any small change in the AC network voltage at the inverter end, the system will behave accordingly, as described above.

#### 2.6.3 Modified Control Characteristics

The control strategy described above is used under steady state operation. However, following modifications are done to maintain power flow even under system disturbances.

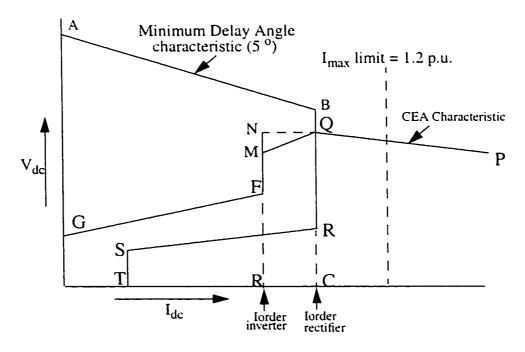

Figure 2.16: Modified control characteristics [15]

Figure 2.16 shows the modified control characteristics. Two new characteristics are included as a protective modification. This modification is made to limit the direct current reference as a function of the DC voltage. This modification assists the DC link to recover smoothly from faults. During disturbances when the AC voltage at the rectifier or the inverter is depressed, the current through the link is brought to a minimum value by means of the Voltage Dependent Current Limiter (VDCL). Line R-S-T and F-G represent the VDCL characteristics for the rectifier and inverter, respectively. The line F-G is also called the  $\alpha_{min}$ -in-inverter characteristic as it prevents the inverter from operating in the rectifier region by imposing an alpha-minimum-limit of about 110°.

When the inverter interacts with a weak AC system, the slope of the CEA control mode characteristic is quite steep and may cause multiple crossover points with the rectifier characteristic. To avoid this possibility, the inverter CEA characteristic is usually modified into either a constant beta characteristic (line QM) or a constant voltage characteristic (line QN) within the current error region.

#### 2.7 Summary

In this chapter, an HVDC system based on the CIGRE Benchmark is presented. Descriptions of various subsystems such as AC networks, filters, converters, converter transformers and DC cable are presented. Modeling of each subsystem is performed by using PSCAD/EMTDC simulation package. The control strategies employed are also discussed.

# Chapter 3

# **Converter Configurations and Control Implementation**

#### 3.1 Introduction

An HVDC system with a long DC cable is prone to commutation failures because the cable has a large capacitance which discharges whenever there is a voltage dip in the inverter side AC network. Each occurrence of a commutation failure stresses the valves for a certain period of time before the protective controller comes into action. Thus, frequent commutation failures can lead to system problems and possible damage of the valves. To overcome this problem different converter configurations have been suggested.

In this chapter, besides the conventional converter configuration, two other converter configurations are proposed. Certain important aspects of these converters such as commutation, commutation overlap angle, extinction angle and commutation margin are discussed. In addition block diagrams of the different control loops are also shown. Finally, a design procedure for selecting the parameters of the PI controllers is presented.

# 3.2 Commutation, Commutation Overlap Angle, Extinction Angle and Commutation Margin

In a 6-pulse bridge converter (figure 2.9), commutation means the transfer of current from one valve to another in the same row. This is achieved by successive triggering of valves in a sequential manner provided the incoming valve is forward biased and the trig-

gering pulse is applied.

If the commutation circuit is resistive, the transfer of current takes place instantly. But in practice the converter transformer has leakage reactance which acts as a commutation reactance and commutation is delayed. This delay in commutation is expressed by the Commutation Overlap Angle  $\mu$ . The value of this angle depends on the commutation reactance, the direct current and the commutation voltage.

Also, depending on the commutation overlap angle, 2 or 3 valves take part in the commutation. For an inverter, the outgoing valve must get sufficient time to regain its full blocking property. Hence, it must stop conduction well before the positive zero crossing of the AC bus voltage, otherwise commutation failure will occur. The time interval between the end of commutation and the instant of positive zero crossing of the AC bus voltage is known as the Extinction Angle  $\gamma$ .

Commutation margin [4] is the angle between the end of commutation and the positive zero crossing of the valve voltage. For the Line Commutated Converter (LCC) configuration, extinction angle and commutation margin are equal.

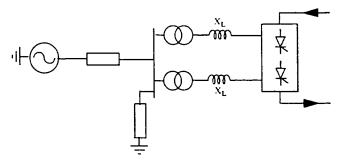

#### 3.3 Line Commutated Converter (LCC) Configuration

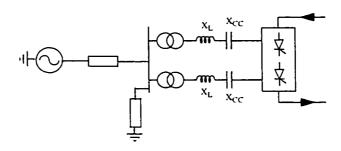

The single line diagram of a 12-pulse conventional converter for an HVDC system is shown in figure 3.1. The leakage reactance  $X_L$  of the converter transformer is also the commutation reactance for the LCC configuration.

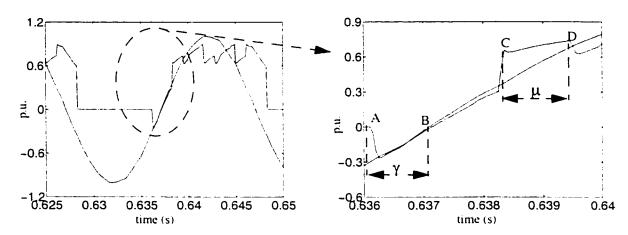

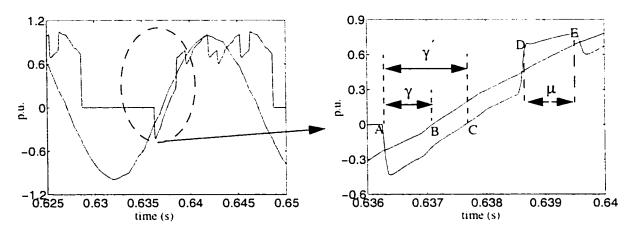

In figure 3.2, the steady-state valve-voltage and the commutation voltage that are obtained from the simulation are depicted. In figure 3.3, the extinction angle and the commutation overlap angle are shown in expanded form. Point A indicates the end of commu

Figure 3.1: Line Commutated Converter (LCC) configuration

tation and B indicates the instant of AC bus voltage and the valve voltage positive zero crossing. Hence, the extinction angle and the commutation margin is the same for the LCC

Figure 3.2: Commutation voltage and valve voltage for LCC configuration

Figure 3.3: Extinction angle and commutation overlap angle for LCC configuration

configuration. During this interval AB, the voltage across the outgoing valve is negative and the valve has to regain its full blocking property within the time period AB. It is important to note that if the outgoing valve fails to regain its full blocking property, it may start conducting again giving rise to a commutation failure. The time interval CD indicates the commutation overlap angle  $\mu$  which is approximately equal to  $20^{\circ}$ .

# 3.4 Capacitor Commutated Converter (CCC) Configuration

As already discussed in section 3.1, the DC cable poses a problem for the HVDC system because of its high discharge current. This problem is overcome by inserting a capacitor in each phase of the commutating circuit. Figure 3.4 shows the single line diagram of a 12-pulse Capacitor Commutated Converter (CCC) configuration.

Figure 3.4: Capacitor Commutated Converter (CCC) configuration

The basic arrangement is the same as that of the conventional configuration except for the presence of the commutation capacitor CC. The reactance of the commutation capacitor is represented by  $X_{CC}$ .

In figure 3.5 the steady-state valve-voltage and the AC bus voltage that are obtained from simulation are depicted. Figure 3.6 shows the extinction angle, commutation overlap angle and the commutation margin in detail. From this figure, it is evident that the commutation capacitance introduces a phase lag to the valve voltage and as a result the instant of positive zero crossing of the AC bus voltage and that of the valve voltage does not coincide. In figure 3.6, AB and AC indicate the extinction angle and the commutation margin, respectively. It is clearly observed that CCC configuration has a larger commutation margin.

gin, which means that the chances of a commutation failure are reduced as compared to the case of the LCC configuration.

Figure 3.5: Commutation voltage and valve voltage for CCC configuration

Figure 3.6: Extinction angle and commutation overlap angle for CCC configuration

Interpreted alternatively, this means that the CCC configuration has much more flexibility to operate the system with a lower value of gamma. In simulation studies for the CCC, the operating value of gamma is set at 12°.

# 3.5 Commutation Overlap Angle for CCC Configuration

The time interval DE in figure 3.6 indicates the overlap angle ( $\mu$ ) for the CCC configuration. It is less than the overlap angle for the LCC configuration as obtained from simulation and shown in figure 3.3. This establishes the fact that, because of the presence of the commutating capacitor the effective commutation reactance is reduced. Also, because of the lower commutation overlap angle, the magnitude of the harmonics is higher, but the order of harmonics is the same as that of the LCC configuration. Details of these harmonics are given in the Appendix.

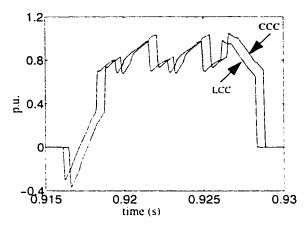

#### 3.6 Valve Stresses

In the case of the conventional converter, the secondary line voltage of the converter transformer appears across the valve. But in the case of the CCC configuration, the commutation capacitor provides an additional voltage ( $I_{dc} * X_{cc}$ ) to the valve. As a result, the voltage stress of the valve increases.

1.2

0.8  $C_4$   $C_4$

Figure 3.7: Comparison of valve stress for LCC and CCC configurations

Figure 3.8: Variation of valve stress with CC

Figure 3.7 shows the steady-state valve-voltages for the LCC and CCC configurations, as obtained from simulations. It is evident that the valve with the CCC configuration has higher peak stress than that with the LCC configuration.

# 3.7 Size of Commutation Capacitor

The valve voltage stresses are inversely proportional to the size of the commutation capacitor. In this study, we have limited the acceptable increase in voltage stress across the valve in the CCC configuration to be 10% greater than a comparable LCC configuration.

The commutation margin also varies inversely with the commutation capacitor size. The smaller the size of the commutation capacitor, the more the commutation margin and the better the performance with respect to commutation failures. Since the voltage stresses increase the cost of the valve directly, it becomes the limiting factor to decide the size of the commutation capacitor. The variation of the voltage stress of the valve with commutation capacitor size is shown in figure 3.8.

#### 3.8 Reactive Power Generation

Apart from increasing the commutation margin, the commutation capacitor also generates capacitive reactive power. Hence, the size of the shunt capacitor bank can be proportionately reduced to maintain the constant reactive power supplied to the bridge. Details of the shunt capacitor bank for different converter configurations are shown in the Appendix. Also, this reactive power generation increases with the increase of load. Hence the net reactive power variation with load is reduced. This is definitely an added advantage from the point of view of shunt capacitor switching to match load requirements.

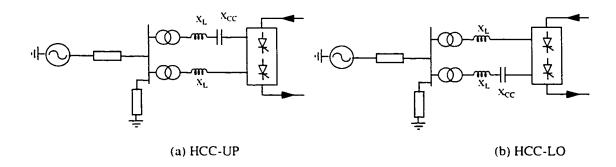

### 3.9 Hybrid Converter Combination (HCC) Cofiguration

Figure 3.9 shows the single line diagram of the Hybrid converter configuration. In this configuration, both conventional and capacitor commutated converters are used. Depending on the location of the commutation capacitor two different configurations are possible. The configuration with the commutation capacitor is placed in the upper converter is denoted by HCC-UP. The other in which the commutation capacitor is placed in the lower converter is denoted by HCC-LO. Ideally there should be no operational behaviour differ-

ence between these two configurations. But because of the different connections of the converter transformer i.e. STAR or DELTA, the net effect of the commutation capacitor may be different. Hence, each configuration is studied separately.

Figure 3.9: Hybrid Converter Combination (HCC) configuration

# 3.10 Implementation of Control

It is well known that proportional type of controllers have the limitation that it is often difficult to find a proper gain so that the steady-state and the transient responses satisfy their respective requirements [24]. In practice, single gain parameter is seldom sufficient to meet the design requirements on two performance criteria. It is, therefore, logical to perform other operations, in addition to the proportional control on the actuating signal.

Both Proportional plus Integral (PI) and Proportional plus Derivative (PD) controllers are fast in action but PI controller has an advantage over PD controller that it can reduce the steady state error of the system under consideration to zero. Besides, PD controller has the characteristic of a high-pass filter which tends to propagate noise and disturbances throughout the system.

Therefore, PI controllers are used to independently control the following three variables:

- 1. Rectifier current,

- 2. Inverter current, and

- 3. Inverter extinction angle, gamma