#### INFORMATION TO USERS

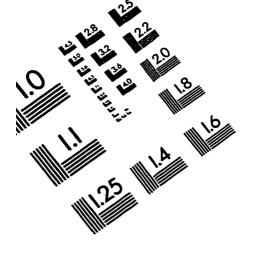

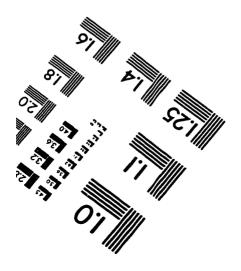

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

# TECHNIQUES FOR SPECIFICATION AND VALIDATION OF COMPLEX PROTOCOLS

THEODORE J. EWANCHYNA

A THESIS

IN

THE DEPARTMENT

OF

COMPUTER SCIENCE

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF MASTER OF COMPUTER SCIENCE

CONCORDIA UNIVERSITY

MONTRÉAL, QUÉBEC, CANADA

DECEMBER 1996 © THEODORE J. EWANCHYNA, 1997

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-26014-3

#### **Abstract**

### Techniques for Specification and Validation of Complex Protocols

Theodore J. Ewanchyna

Simple protocols can be described with natural language and pictures. This description is no longer adequate as protocols become more complex, or more people get involved. Formal Description Techniques (FDTs) have been developed to convey this information clearly and unambiguously (and as a basis for correctness verification) but FDT-based specifications tend to be long and hard to follow.

In order to help the user understand and use complex protocols, we have integrated informal graphical techniques with the current formal techniques. We have developed an approach for the generation of pictures directly from formal models.

# Acknowledgments

First, I would like to thank my supervisor for his intellectual and financial support.

I would especially like to thank Gustave Arroyo for his help in organizing and editing portions of this thesis.

I wish to acknowledge and thank the support staff in both the Computer Science and the Electrical and Computer Engineering departments of Concordia University and also the Computer Science staff at the Université de Montréal.

My thanks also to Dr. Holzmann, the creator of the PROMELA language and the SPIN tools, for the frequent correspondence over the years via e-mail.

Finally, I would like to acknowledge and thank my father, Wesley Ewanchyna for his help and support during the final and crucial phase of the writing of this thesis.

# **Contents**

| Li | ist of | Tables                                 | ,      |  |  |  |  |  |  |

|----|--------|----------------------------------------|--------|--|--|--|--|--|--|

| Li | ist of | Figures                                | X      |  |  |  |  |  |  |

| 1  | Intr   | ntroduction                            |        |  |  |  |  |  |  |

|    | 1.1    | Background                             | 1      |  |  |  |  |  |  |

|    |        | 1.1.1 FDTs                             | 1      |  |  |  |  |  |  |

|    |        | 1.1.2 Protocol Visualisation           | 2      |  |  |  |  |  |  |

|    |        | 1.1.3 Complex Protocols                | 4      |  |  |  |  |  |  |

|    | 1.2    | Scope of the Thesis                    | 6      |  |  |  |  |  |  |

| 2  | Prot   | Protocol Definition                    |        |  |  |  |  |  |  |

|    | 2.1    | Computer Protocols                     | 8      |  |  |  |  |  |  |

|    |        | 2.1.1 Five Essential Ingredients       | 9      |  |  |  |  |  |  |

|    | 2.2    | OSI Layers                             | 10     |  |  |  |  |  |  |

|    | 2.3    | Summary                                | 13     |  |  |  |  |  |  |

| 3  | Prot   | ocol Development Techniques            | 14     |  |  |  |  |  |  |

|    | 3.1    | Introduction and History               | 14     |  |  |  |  |  |  |

|    | 3.2    | Informal Methods                       | 14     |  |  |  |  |  |  |

|    |        | 3.2.1 Describing a Protocol Informally | 15     |  |  |  |  |  |  |

|    | 3.3    |                                        | 21     |  |  |  |  |  |  |

|    |        |                                        | 22     |  |  |  |  |  |  |

|    |        |                                        | 23     |  |  |  |  |  |  |

|    |        | 2.2.2. Chanded Con                     | <br>21 |  |  |  |  |  |  |

|   |     | 3.3.4    | Communicating Sequential Processes                          | 29 |

|---|-----|----------|-------------------------------------------------------------|----|

|   |     | 3.3.5    | Finite State Machines (FSMs)                                | 31 |

|   |     | 3.3.6    | Reactive Systems                                            | 32 |

|   |     | 3.3.7    | Concurrency                                                 | 34 |

|   | 3.4 | Valida   | tion and Verification                                       | 34 |

|   |     | 3.4.1    | Reachability Analysis                                       | 35 |

|   |     | 3.4.2    | Temporal Logic                                              | 36 |

|   |     | 3.4.3    | Classical Logic                                             | 37 |

|   | 3.5 | Concl    | usion                                                       | 39 |

| 4 | PRO | OMELA    | A, a PROtocol MEta-LAnguage                                 | 41 |

|   | 4.1 | Why F    | PROMELA?                                                    | 41 |

|   | 4.2 | The La   | anguage                                                     | 42 |

|   |     | 4.2.1    | C Extensions                                                | 42 |

|   |     | 4.2.2    | Model Specific Constructs                                   | 45 |

|   |     | 4.2.3    | Guarded Commands                                            | 45 |

|   |     | 4.2.4    | Timeout                                                     | 46 |

|   |     | 4.2.5    | Finite State Machines                                       | 47 |

|   |     | 4.2.6    | Execution Scheduling, Channels and other Aspects of PROMELA | 48 |

|   |     | 4.2.7    | Validation and Verification                                 | 49 |

|   | 4.3 | PROM     | TELA Tools                                                  | 56 |

|   |     | 4.3.1    | SPIN Usage                                                  | 56 |

|   |     | 4.3.2    | Simulation                                                  | 57 |

|   |     | 4.3.3    | Validation and Verification                                 | 59 |

|   | 4.4 | Conclu   | ısion                                                       | 60 |

| 5 | Gra | phics su | ipport                                                      | 62 |

|   | 5.1 | FDTs a   | and graphics                                                | 62 |

|   |     | 5.1.1    | Characteristics of Graphics                                 | 62 |

|   |     | 5.1.2    | Advantages of using graphics                                | 63 |

|   | 5.2 | Graphi   | ics Support Tools                                           | 64 |

|   |     | 5.2.1    | Dynamic and Static Graphic Information                      | 65 |

|   |     | 5.2.2    | Types of Graphic Representation                             | 65 |

|   |     | 5.2.3   | Languages and their Graphics Support  | 6         |

|---|-----|---------|---------------------------------------|-----------|

|   |     | 5.2.4   | Tcl/Tk                                | 7         |

|   | 5.3 | Our To  | ools                                  | 7         |

| 6 | Dra | wing Ti | ime Sequence Diagrams                 | 73        |

|   | 6.1 | Introd  | uction                                | 73        |

|   | 6.2 |         | round                                 | 74        |

|   | 6.3 |         | nating the Process                    | 75        |

|   |     | 6.3.1   | Input Formats                         | 75        |

|   |     | 6.3.2   | Output Formats                        | 76        |

|   |     | 6.3.3   | Generic Input Format                  | 77        |

|   |     | 6.3.4   | Discussion                            | 79        |

|   | 6.4 | tsd, th | e Tool                                | 79        |

|   |     | 6.4.1   | Calling Syntax                        | 80        |

|   |     | 6.4.2   | Layout                                | 81        |

|   |     | 6.4.3   | Main Program                          | 81        |

|   |     | 6.4.4   | TSD library program                   | 82        |

|   |     | 6.4.5   | The "tsd.h' File                      | 85        |

|   |     | 6.4.6   | Bug                                   | 85        |

| 7 | Dra | wing Fi | nite State Machines                   | 87        |

|   | 7.1 |         | uction                                | 87        |

|   | 7.2 |         | round                                 | 87        |

|   | 7.3 |         | SM Drawing Tools                      | 88        |

|   |     | 7.3.1   | Smaller Tools                         | 89        |

|   |     | 7.3.2   | fsm-make                              | 91        |

|   |     | 7.3.3   | Discussion of the code for "fsm-make" | 97        |

|   |     | 7.3.4   | pre-xdag                              | 99        |

|   |     | 7.3.5   | 3                                     | رو<br>02ا |

|   |     | 7.3.6   | 1 197 . 1                             | 02        |

|   | 7.4 |         | •                                     | 104       |

| 8  | Conclusions and Future Work |                                         |     |  |  |

|----|-----------------------------|-----------------------------------------|-----|--|--|

|    | 8.1                         | Conclusion                              | 106 |  |  |

|    | 8.2                         | Future Work                             | 106 |  |  |

| Re | eferen                      | ces                                     | 108 |  |  |

| Aı | ppend                       | ices                                    | 116 |  |  |

| A  | Spec                        | cification and Validation Approach      | 116 |  |  |

| В  | TSD Source Code             |                                         |     |  |  |

|    | <b>B.</b> 1                 | Main Program (text version)             | 119 |  |  |

|    | B.2                         | Main Program (X windows version)        | 120 |  |  |

|    | <b>B.3</b>                  | Library Program                         | 123 |  |  |

|    | B.4                         | Header Program                          | 134 |  |  |

| C  | FSM                         | I Source Code                           | 135 |  |  |

|    | <b>C</b> .1                 | Small Support Programs                  | 136 |  |  |

|    | C.2                         | Main Program (layout calculation)       | 139 |  |  |

|    | C.3                         | Main Program (draw graphic (X windows)) | 147 |  |  |

|    | C.4                         | Library Program                         | 149 |  |  |

# **List of Tables**

| 1 | PROMELA Keywords                                             | 43 |

|---|--------------------------------------------------------------|----|

| 2 | PROMELA Operators                                            |    |

| 3 | Miscellaneous PROMELA Syntax                                 |    |

| 4 | Spin Command Line Options                                    |    |

| 5 | C Compiler Command Line Options (for compiling the analyzer) |    |

| 6 | Verifier Command Line Options                                | 61 |

| 7 | List of FSM Tools                                            | 80 |

# **List of Figures**

| 1  | Design Methodology Overview                                  | 3  |

|----|--------------------------------------------------------------|----|

| 2  | Protocol Visualisation                                       | 5  |

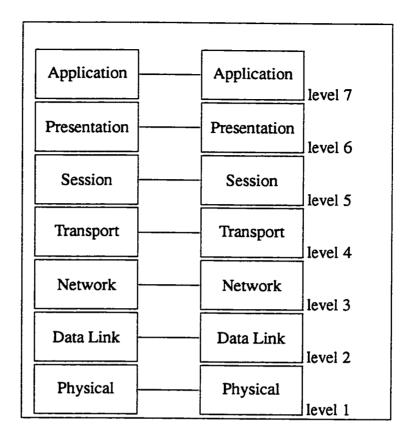

| 3  | OSI Layers                                                   | 10 |

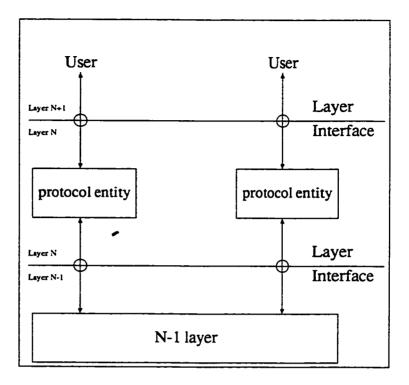

| 4  | The Protocol Model                                           | 12 |

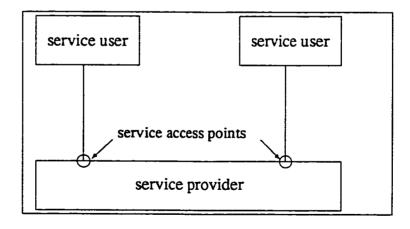

| 5  | The Service Model                                            | 12 |

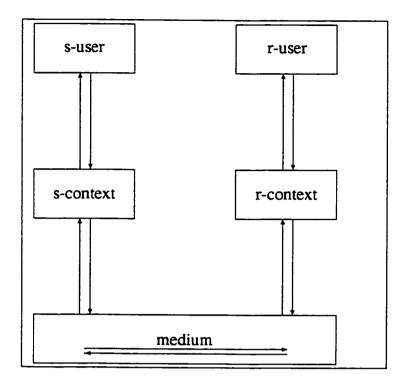

| 6  | The "classic" architecture model                             | 13 |

| 7  | Informal Architecture of XTP Communication Model             | 15 |

| 8  | Isolation of Contexts of the XTP Communication Model         | 16 |

| 9  | Internal Architecture of an XTP context                      | 16 |

| 10 | XTP Architecture of Contexts with data streams               | 17 |

| 11 | XTP 3.6 Context state machine                                | 18 |

| 12 | Fully Graceful Independent Close                             | 20 |

| 13 | XTP in action: FIRST and DATA packet exchanges               | 21 |

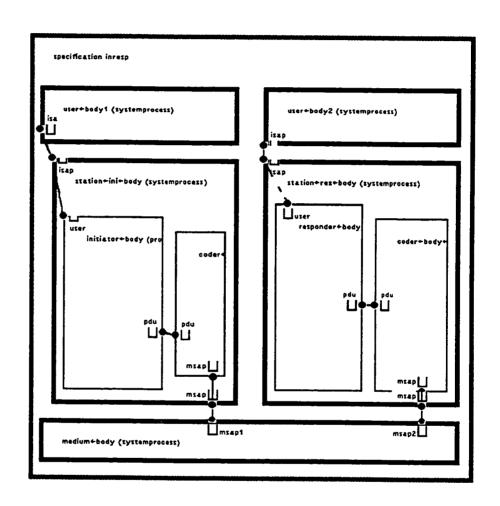

| 14 | InRes Protocol Architecture                                  | 66 |

| 15 | "End user"                                                   | 68 |

| 16 | ABP: Multiple State Machines within the Model's Architecture | 69 |

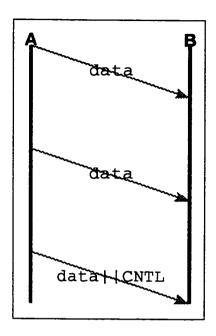

| 17 | Sample Input (SPIN 1.6)                                      | 74 |

| 18 | Sample Input (SPIN 2.3.3)                                    | 75 |

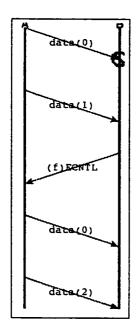

| 19 | 'Generic' Input for 'tsd'                                    | 76 |

| 20 | Sample Output from 'tsd'                                     | 76 |

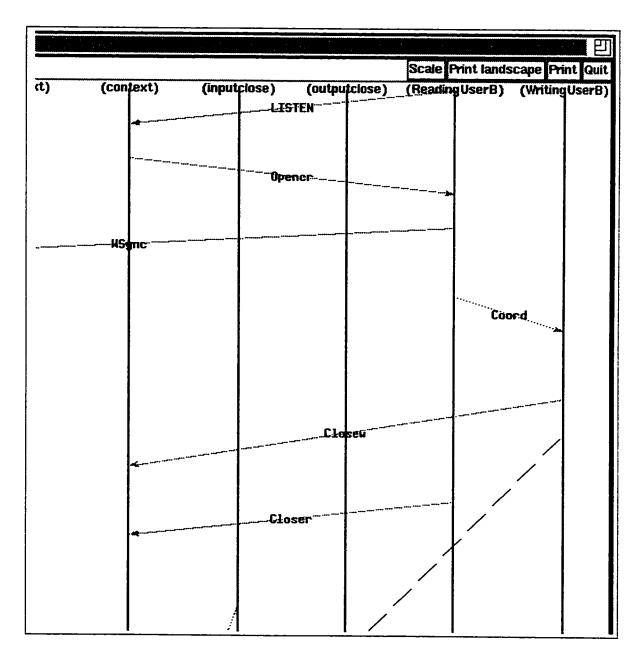

| 21 | Sample Output from 'xtsd'                                    | 77 |

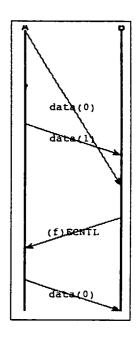

| 22 | "normal" FASTNAK mode                                        | 78 |

| 23 | FASTNAK on a non-FIFO network                                | 78 |

| 24 | xtsd interface                                               | 83 |

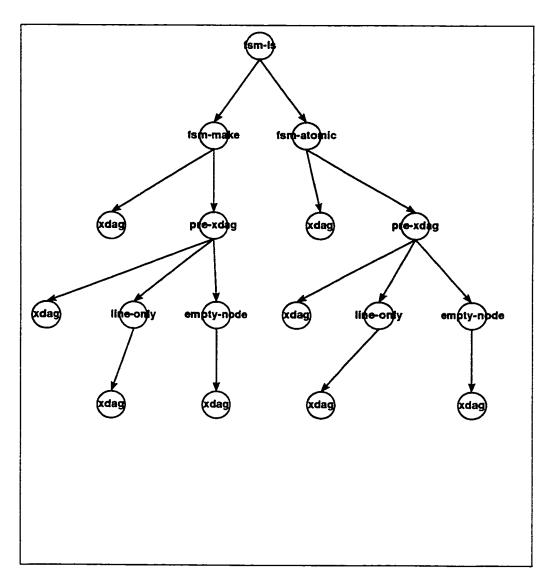

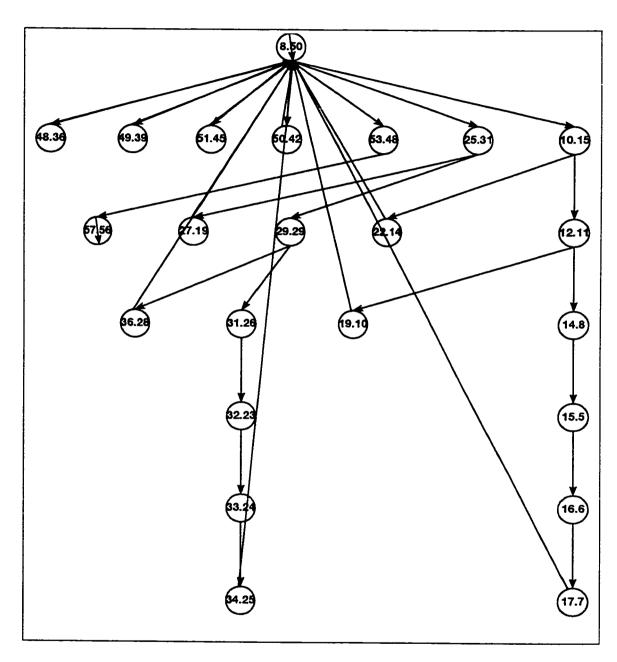

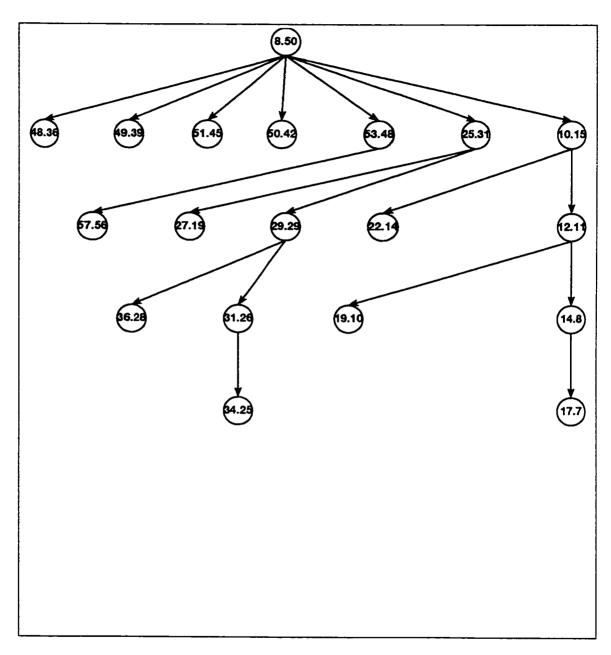

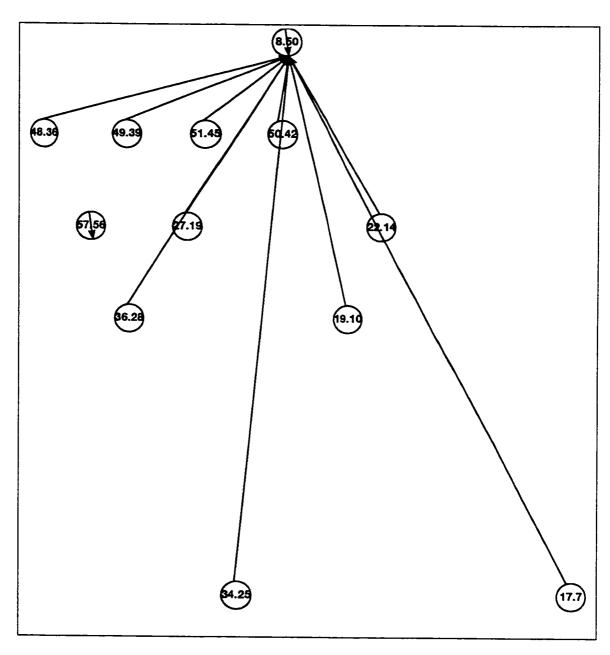

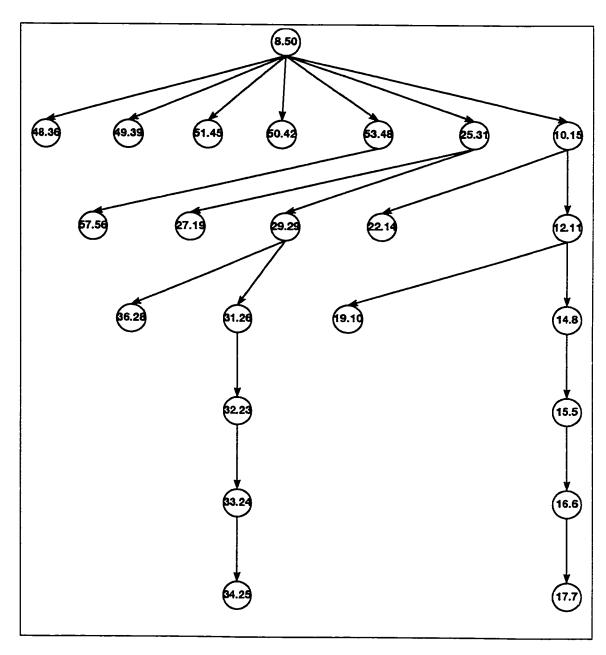

| 25 | Sample "pan -d"Output (spin 2.3.3)             | 88 |

|----|------------------------------------------------|----|

|    | FSM Design Methodology Overview                |    |

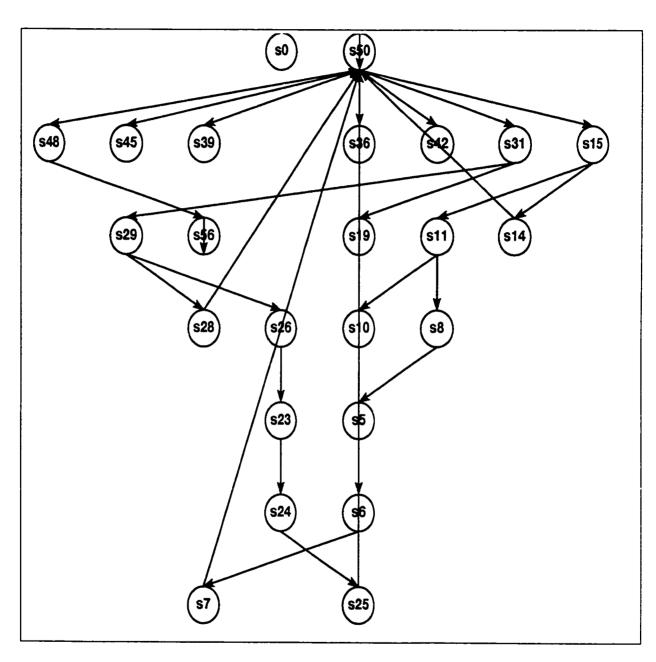

| 27 | Context Machine (Holzmann drawing algorithm)   |    |

| 28 | Context Machine                                |    |

| 29 | Context Machine (compacted "down" transitions) | 96 |

| 30 | "pre-xdag" Input Format                        |    |

|    | Context Machine ("up" transitions)             |    |

| 32 | Context Machine ("down" transitions)           |    |

| 33 | "xdag" Input Format                            |    |

# Chapter 1

### Introduction

### 1.1 Background

Computer protocols were first examined as an interesting problem in computer science with what became known as the "alternating bit protocol" [Lyn68]. A simple English and graphic description delineated the rules for two computers to follow in order to reliably transfer packets of information between them. But even this simple protocol description was found to be in error [BSW69] and, ominously, serves as a warning to other protocol designers: designing and describing protocols is deceptively complex—it looks easy to describe the mechanisms that make up what we call a protocol, but it is not! As modern protocols achieve levels of complexity many times the level of complexity of 'toy protocols' like ABP, the need for a more precise formulation becomes obvious.

#### 1.1.1 FDTs

Formal methods or formal description techniques (FDTs) are used to unambiguously describe how protocols work. The designer can use these techniques throughout the entire protocol design life cycle, from the initial design to the final validation and testing stages. As well, the protocol user (or implementer) can employ the formal description as the authorative definition of how the protocol works.

When employing FDTs, an unambiguous model of the protocol system is created using a formal language. Most formal languages were created to support the first design stage for protocols, the specification stage. An important aspect of using FDTs is that once a protocol

design is completed, it can be formally verified and validated. FDTs allow one to unambiguously describe protocols; but that is not enough, we must offer some assurance that the protocol is correct.

Unfortunately, when the design of a new protocol is complete, we usually have little trouble convincing ourselves that it is trivially correct. It can be unreasonably hard to prove those facts formally and to convince also others. [Hol93]

With formal techniques, a protocol description can be verified to be correct before it is implemented, that is, before it is put out into the field and used. Furthermore, most protocol descriptions are machine readable so that these descriptions can be shown automatically to be correct.

#### 1.1.2 Protocol Visualisation

Prior to using FDTs, protocol designers used natural language descriptions and pictures to explain how protocols work. Several factors led to designers adopting formal methods:

- as designers examined their 'success' with 'informal methods', they noticed inaccuracies and errors

- modern protocols became more complex

- designers' abilities to describe modern protocols using 'informal methods' could no longer keep up.

Despite the advantages of using FDTs, however, many protocol designers still do not use them. The few protocol designers that use FDTs do not use them throughout the *entire* protocol design life cycle. In fact, we can see two camps, the 'formalists' and the 'informalists'.

Some disadvantages of using FDTs are that training people to use them takes some extra time and FDT-based specifications tend to be large and hard to follow.

On the other hand, informal methods are intuitive so that they are relatively easy for human beings to use, as we are very good at recognising patterns and gleaning a great deal of information from illustrations.

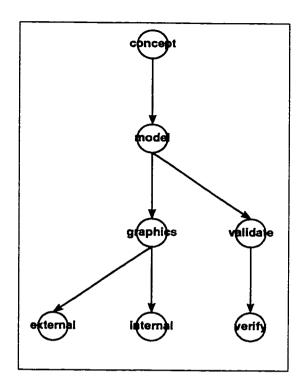

Figure 1: Design Methodology Overview

If formal methods are so superior to informal methods, why are not more people using them? As such, it may benefit us to re-examine what we hope to accomplish by building a formal model. We find that FDTs are most often used to:

- find problems in an existing informal specification

- prove the merit of FDTs by showing how easy it is to use FDTs

- as a basis for a proof step

- as a basis for other phases of protocol design steps.

We believe that we would be better off asking who is the specification (or model) being written for—humans or computers? The answer is for 'both'. An informal model is useful for humans and a formal model is potentially useful to humans but definitely must be 'formal' if it is to be used by computers.

We feel it would be beneficial to combine the two approaches: we propose using FDTs to create formal models; these can be validated and verified as is done already with FDTs

and can also be used as a basis for generating graphics of the system.

Figure 1 represents our design methodology. We see that we first start off with a concept; next, we express this concept as a model, preferably formally. Then we can validate and then verify the model. We can also produce graphics from it, wherein the graphics represent the model 'internally' and 'externally'.

Our design methodology allows both formal and informal description techniques. If we follow the 'right' path after the 'model' node, we represent the employment of standard FDTs. If we follow the 'left' path after 'model', the 'graphics' node represents the use of graphics from either an informal or formal model, so that this path also illustrates the ability to include an informal design approach independent of FDTs or in unison with their use.

New [New91, NA91, NA89a, NA89b] has done much work in the area of graphical representation of protocols, or what he calls "protocol visualization". He asserts that protocol design should incorporate graphical representation because this is 'natural' for us.

The most relevant portions of human cognitive and visual processing are the ability to automatically recognise proximity and connectivity between pictorial elements, the ability to automatically recognise inclusion of some pictorial elements within others, and the ability to automatically focus attention on changing elements of the visual field; all of these traits were encouraged by human evolution. [New91]

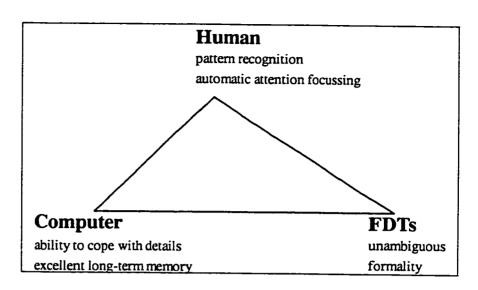

This author also argues that a three pronged approach that uses the respective strengths of computers, humans, and FDTs (or as he terms it 'specification') should be used. Figure 2 shows this approach graphically.

#### 1.1.3 Complex Protocols

The Xpress Transport protocol (XTP) is one complex protocol that was created specifically to address the demands of a new generation of networking and distributed computing needs that older protocols could no longer meet. Previous protocols, such as those in the OSI and TCP/IP protocol suites, were designed for environments running on Ethernet or telephone dialup lines, and their main applications were remote logins and file transfers.

<sup>&</sup>lt;sup>1</sup>This idea will be elaborated on in the next chapter.

Figure 2: Protocol Visualisation

With the advent of optical fiber technology and ATM networks, many new and previously unforeseen applications are now feasible and many old applications can be improved or even extended.

It follows that new protocols such as XTP would have to be developed in order to take advantage of new technologies. XTP was designed with these new technologies in mind. It has been optimised for the needs of the present day.

XTP is a large and complicated protocol and currently there is no complete, formal specification for it. The officially published description *informally* describes the protocol using natural language and pictures. Some implementation notes are provided but no formal description or analysis is available.

Much of the XTP definition concerns itself with describing 'mechanism' rather than 'policy'. As a protocol definition, this is expected but, without any background context it is hard for new XTP users to know how to use the protocol or for experienced XTP users to agree on how to use XTP's functionality. There is no 'service' description.

Many aspects of the XTP protocol are not very well defined – informally or formally, in either of the two base XTP documents: the XTP 3.6 definition document [Sil92] or the published text on XTP [SDW92]. We feel this situation to be unacceptable. Chesson, the inventor of XTP, in an accompanying letter to his protocol description, referring to the "imprecision in the protocol specification" writes:

The quantity of explanatory text is barely adequate, but the inclusion of an API<sup>2</sup> interface may be a first step toward portability of applications across XTP implementations. [Sil92]

and he looks forward to future drafts of the protocol, when this situation will be rectified:

Future revisions of XTP may include formal specification methods, such as state tables and language descriptions. ... An API fashioned in this manner may provide the long awaited service definition for XTP – a "bottom up" approach to service specification. [Sil92]

### 1.2 Scope of the Thesis

In this paper we investigate methods to describe complex protocols so that any ambiguities or imprecision can start to be cleared up in their descriptions. We apply the techniques of formal analysis to describe and validate our models in order to provide assurances that the model is both precise and correct. We also generate graphical descriptions as an aid to describe and understand the protocol. We use PROMELA as the protocol design and validation language.

The beginning chapters provides a look at the area of protocol engineering in general and then focusses on the use of the language PROMELA as a design tool for the specification, verification and validation of protocols. We look at finite state machines for specification, and at reachability analysis and temporal logic for validation and verification, respectively, then we compare the various techniques for formal methods. Although there are many techniques described in this chapter, only one, PROMELA, will be used to build protocol models.

Chapter 2 provides a description of what a protocol is. We use a definition by Holzmann to arrive at what he refers to as a 'complete' protocol description. The ISO OSI model is used to explain how a complex communications system is broken down into protocol description layers and the well defined interfaces that allow communication with those layers.

Chapter 3 provides a look at the techniques that have been developed to try and specify protocols. We start off describing informal desription techniques. Within this context we

<sup>&</sup>lt;sup>2</sup>API is an acronym for "application-protocol interface"

provide a classification system based on 'internal' and 'external' descriptions of protocol systems. After this we introduce the topic of formal techniques.

As with all large software systems there exists a software life cycle. Protocol engineering is an attempt to provide a more sound protocol design technique much as software engineering does for non-communicating software systems. We discuss some of the specification, validation and verification techniques that have been used to try and come to terms with the complex issues of defining protocol systems.

After this chapter, we discuss the language, PROMELA, which we feel incorporates the best aspects of the techniques of formal protocol design. The language is not only used in the first phase, the specification phase but also has allowances for validation, verification and even simulation. Thus PROMELA can be used for all the phases of the protocol design life cycle, except for the final, implementation phase.

Next, we discuss aspects of graphics support. Chapter 5 reiterates the advantages of using graphics in protocol design, but this time in the context of a formal design approach. We briefly look at some examples that have influenced us and then take a look at some tools we have created in order to bring graphics tools into the PROMELA world.

Chapter 6 looks at the graphical tool we designed to draw out time sequence diagrams. We provide background and motivation for wanting to come up with such a tool and then describe how the tool works. Time sequence diagrams provide an 'external' description of the modules of the protocol system.

In chapter 7 we provide a similar discussion for the graphical tool we designed to draw finite state machines. Finite state machines provide an 'internal' description of the modules of a protocol system.

The last chapter concludes the thesis and briefly examines other areas to explore.

# Chapter 2

### **Protocol Definition**

A protocol can be described as "the set of rules that two entities use in order to communicate with each other to accomplish a particular task". In order to show that the definition applies to many other things — other than computer 'protocols', this description is purposely as general as possible.

For example, when people engage in a telephone conversation they also follow a protocol: each person starts the connection with 'hello', talks for a while, and then says 'good-bye'. This, of course, abstracts the mechanics involved of dialling the telephone, taking the phone 'off hook', etc. See [BL93, BL91, SL93, FLS90a, FLS90b, FLS91], for several formal models of the telephone 'protocol' written in the formal specification language, LOTOS<sup>1</sup>.

### 2.1 Computer Protocols

In the world of data communications, computers communicate with one another by transmitting messages between themselves. In order to assure reliable communications some sort of acknowledgement for the sender from the receiver—'error control' and other mechanisms are introduced. The sum total of the different mechanisms used are what defines a 'protocol'.

<sup>&</sup>lt;sup>1</sup>The earlier papers discuss 'POTS' – plain old telephone system, while later papers build on this work and describe new telephone features like call waiting, etc. The problem of feature interaction, where newly introduced features interfere with already present ones, and different specification styles are mentioned when talking about these new features.

Equally important is for the protocol to be stated as a precise and unambiguous set of rules. Machines are not as flexible as humans. For example, where a human might 'hang up the phone' if no one is at the other end of the line a computer would not—unless it can recognize this situation and is specifically informed as to what to do. In other words computers may be fast but they are not all that smart. This then becomes the problem for protocol designers to overcome: how can we write a complete and unambiguous description so that computers can reliably transmit information between them.

#### **2.1.1** Five Essential Ingredients

In an attempt to describe how to go about this, Holzmann [Hol91] enumerates five essential ingredients for a complete protocol specification:

- 1. the service to be provided by the protocol

- 2. the assumptions about the protocol in which the protocol is to be used

- 3. the vocabulary of messages used to implement the protocol

- 4. the encoding (format) of each message in the vocabulary

- 5. the procedure rules guarding the consistency of message exchanges

The service refers to the outside interface that is presented to the protocol user, which includes the available ports and messages that can flow through those ports. The assumptions can be regarded as a requirement to specify the 'extraneous' entities of the protocol model. This would include the environment that the protocol is to be run in and the types of users the protocol would expect to interact with. The vocabulary concerns itself with the correct sequence of messages that may pass through interconnecting ports. Encoding (format) refers to the exact sequence of information that is contained in a message. This can vary, depending on the level of abstraction that the model represents. Often, only a portion of the 'actual' message is defined. The designer is concerned only with the fields that are relevant to the properties being tested in the model, so that unused fields need not be entered. The procedure rules are the definition of the protocol itself. This includes how each defined module in a system behaves—its full set of rules that explain how to act in each and every situation for each and every module.

Figure 3: OSI Layers

What this means is that a protocol consists not only of the 'protocol rules' but equally important: the service that that protocol provides, the assumptions or environment that the protocol operates in, and the specification of the format and order (vocabulary) that is correct for a proper transmission to take place. Finally, these messages come from 'above' and from 'below' the protocol module or layer.

### 2.2 OSI Layers

Network architecture design has driven the design of communications systems. The methodology is to divide the functionality needed for system interconnection into separate modules. The layers are divided up in terms of a particular functionality. Each layer provides services to the upper layer and requests services from the lower layer using interactions on well defined boundaries via a small number of 'service primitives'. Dividing a system up like this

allows the user to form different abstractions at each level, which helps to break up the task of describing such a large system into manageable tasks. In this way each layer defines a protocol that defines its interaction with its remote peer module; with this (layer and interaction) description being the 'heart' of the protocol.

To give historical and terminological perspective to the reader, we first look at the International Organisation for Standardisation's (ISO's) OSI model [DZ83, Hea93]. The OSI BRM [ISO7498] introduced the concepts of layering and abstraction into the computer communications world in order to tame the complexity inherent in communications systems. The current standard "OSI Basic Reference Model", (see figure 3), breaks up a system into layers [Lin83, Liu89].

Each layer has a well defined service interface, where the environment is defined via the interface directly above and below it (except for the lowest (physical) layer which has no 'lower' layer and the topmost (application) which has no 'higher' layer). As part of this definition, the format and ordering of messages that pass through these interfaces is also defined.

To illustrate this approach, refer again to figure 3. The 'physical' layer forms the basis of the model. The 'data link' layer uses the services as expressed by the behaviour characteristics of the physical layer to create a service that the next higher (network) layer can use. How the data link layer does this is what we call its protocol description.

Starting from the data link layer, each higher layer adds a little more functionality to the lowest layer of 'bare metal' wires. Each layer uses the 'services' of the layer immediately below it to provide a service that the next higher layer can use which.

This idea is expressed more generally in figure 4 [Lin83, Liu89] which shows how a layer N protocol uses the services of layer N-1 to offer a service to the layer N+1, or the 'user'. Figure 5 [Lin83] shows this same model from the viewpoint of the user layer N+1) where the layer N protocol is seen to be a 'black box'. The concern of the user is 'service', not how that service is provided. How the service is provided is what we are concerned with defining, in other words, it is the protocol.

So for any given layer, the lower layer becomes part of the environment that the current layer can use. The current layer's protocol is designed to work with the lower layer to provide a service that the next higher layer can then use. This process repeats itself until the highest layer is defined.

Figure 4: The Protocol Model

Figure 5: The Service Model

Figure 6: The "classic" architecture model

Figure 4 is often represented as shown in figure 6 when one wishes to describe the model's 'system architecture'. It should be clear how these last three figures relate to Holzmann's "five essential ingredients" of protocol specification as given in section 2.1.1.

### 2.3 Summary

It is a difficult job to define protocols clearly and correctly. Many techniques have been proposed in order to break the problem down into simpler sub-tasks. Abstraction and modularisation are used to break down the description of protocols into manageable units. The description techniques used to describe and design protocols are continually being refined as new approaches are discovered.

# Chapter 3

# **Protocol Development Techniques**

### 3.1 Introduction and History

The application of FDTs to protocols was spear-headed by the International Organisation for Standardisation (ISO) in the 1980's in order to insure a high degree of telecommunications software dependability and quality (see [Vis90] for an introduction to the subject). Prior to FDT usage, only natural language descriptions, diagrams and code walk-throughs were used to describe protocols, but this did not suffice to specify the exact requirements for large software systems, such as protocol software systems.

#### 3.2 Informal Methods

Protocols may quickly acquire a high degree of complexity, and informal descriptions fail to reflect this complexity, and may lead to mistakes in their implementation. On the other hand, formal descriptions are less likely to cause misunderstandings, and they may be automatically verified with the help of a computer.

For example, informal protocol design methods rely on the intuition and experience of the designer. Considering the complexity of protocol design this is a great compliment on the designer's abilities. However, not everyone has such great talent and even very experienced people can make mistakes <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Imagine writing complex Pascal or C code by hand without recourse to a compiler and expecting the code to be right the first time through. Now imagine writing a complex system with several threads of control, without a methodology to follow and without a compiler. This is essentially how protocol designers worked

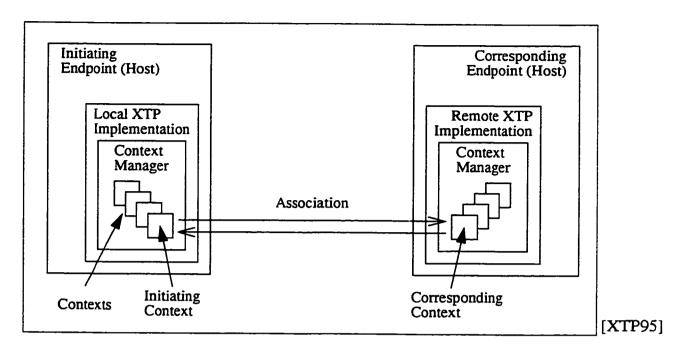

Figure 7: Informal Architecture of XTP Communication Model

#### 3.2.1 Describing a Protocol Informally

How would one go about describing a protocol informally? In the first place, the designer should try and convey a general overview of the protocol model. The participating system components and their inter-relationships should be described to show the modules and how they communicate with each other. Figure 7 shows an example of this overview for the XTP protocol architecture.

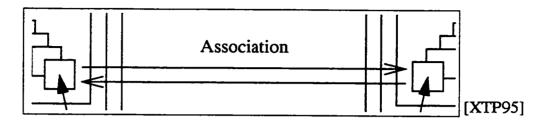

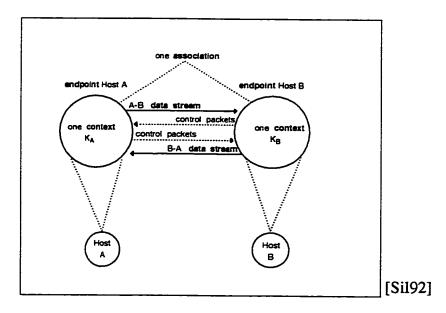

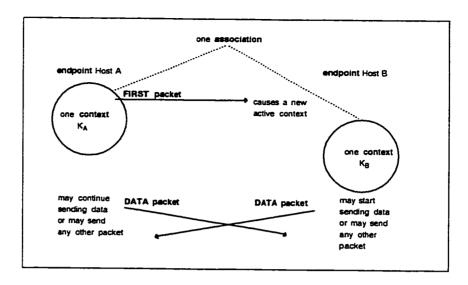

From this figure we see how a unicasting XTP 'association' can be built between two contexts (an initiating and its corresponding (listening) context and their corresponding two simplex data communications streams between them. Figure 8 is a closeup of this figure which we use to shift the reader's attention to this relationship. Each context exists on a different host which is running its own XTP protocol stack. As part of this implementation a 'context manager' is used to mediate the shunting of information to the proper context.

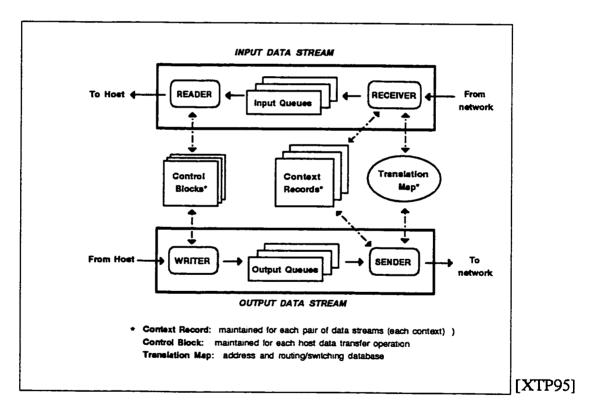

More detail and a better understanding is often provided by focussing on particular architectural components (see figures 7, 8, 9, and 10) and the designers of XTP have done just

before formal methods were adopted.

Figure 8: Isolation of Contexts of the XTP Communication Model

Figure 9: Internal Architecture of an XTP context

Figure 10: XTP Architecture of Contexts with data streams

that in order to help describe their protocol. Figures 7 and 8 informally show an 'association' between two 'contexts' and how they are connected together (we produced figure 9). Figure 9 shows the makeup of a single XTP context. Figure 10 is similar to figure 8, but by focussing on the channels, it attempts to illustrate the communications between two XTP contexts; it shows how the contexts communicate with each other and the types of packets they exchange.

In this way a protocol model is gradually fleshed out by a series of increasingly detailed descriptions and illustrations. However, we note that the architecture only provides a static description. Once the various details of the architecture are provided, it is the events that occur and their consequences to the protocol system that often give a more informative description of the protocol. This allows a dynamic view of the protocol and these cause and effect events (or actions) can be described as occurring 'internally' and 'externally'.

#### **Internal Description**

As we break down the protocol into modules and processes that implement specific functionalities we find that at certain times a process is ready to either instigate (or 'offer') or respond to certain events and therefore certain things can only happen at certain times. For

<sup>&</sup>lt;sup>2</sup>My terminology.

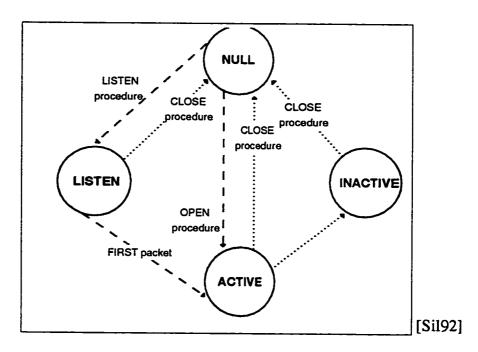

Figure 11: XTP 3.6 Context state machine

example, a module may send a message and then wait for a reply. There may be several possible scenarios that may occur after the message is sent, and all of them must be accounted for.

Internal descriptions show how the modules are affected on a per process level. Using an example where a process has sent a message and is awaiting a response: the process progresses to a wait state and will only change its "state" upon receipt of the returned message. A different message may force the process into a different "state" or if no message arrives, this, too may force a change of state.

At each stage in a process' lifetime, a list of responses that are acceptable to it and how the module responds to them and how it changes (by going through a series of stages) is described. Assuming only legal responses occur, for example, the sending module only enters a new stage upon receipt of one of those responses. On the global scale, the entire protocol is described as the sum of all its component modules' executions and interactions. The protocol goes through each of its component modules and enumerates their expected events.

These "stages" are termed "states" in finite state machine terminlogy.

Figure 11 illustrates the general stages an XTP context goes through in its lifetime. The

reader should note that the actions listed on the transition arrows show the result of an outside process' communications with it, so that the process chooses to go from the "null' state to either the "listen" or the "active" state, as a result of information not shown in the figure. Informal descriptions are often "incomplete".

It must be pointed out that the transition arrows are not like flow chart arrows. For example, the transition from the "listen" to the "active" state indicates the passive reception of a "FIRST" packet (not the sending of one), as would be depicted in a flow chart. State transitions occur because of a process instigating or responding to an action.

In figure 11 every context starts off in a "null" or "quiescent" state. The context has two choices: it can open as an initiator, in which case it proceeds directly to the "active" state, or it can open as a responder, in which case it goes to the "listen" state and only upon receiving an appropriate "FIRST" packet does the context then proceed to the "active" state. Once a context is in an "active" state, it proceeds to the "inactive" state (generally when a data transmission session is completed).

Every state except for "null" has a "CLOSE procedure" transition that leads back to the "null" state. When taken in the "inactive" state this transition represents a normal, uninterrupted cycle through the context's stages. Anywhere else, it represents an interruption in the normal data transmission session, usually due to some sort of unrecoverable error. Thus the finite state machine shows all possible behaviour without distinguishing between desired and undesired behaviours.

#### **External Description**

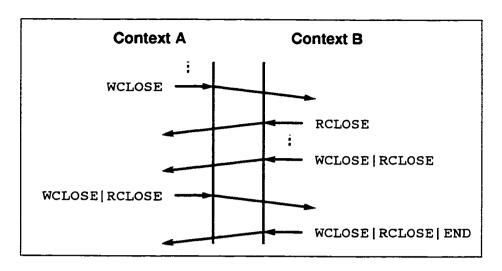

An "external" informal explanation shows the interactions between different modules that transmit messages to each other. Message sequence diagrams or time sequence diagrams [LL92b, LL92a, GR92c] are often used to explain the sequence of message exchanges between entities. These diagrams are used in most protocol descriptions. Directed arrows are drawn from the sender to the receiver of a given message. The module bodies are traditionally drawn along the x-axis and time is drawn along the y-axis starting from the top of the page (see figure 12).

There is an attempt to formalise this notation and turn it into a fourth FDT called **Message Sequence Charts** or MSCs. Grabowski and Rudolph [GR92c] gives a good introduction to the MSC language, including its history, modifications and enhancements, and

Figure 12: Fully Graceful Independent Close

the realisation that a clear semantics is not yet arrived at. An attempt to develop formal semantics for MSCs is given by Ladkin and Leue [LL92b], wherein the authors describe their work in turning MSCs into 'global state transition graphs' (GSTG) via "ne/sig graphs". They find that the MSC model, as defined, is under-specified because more than one GSTG can be drawn from a MSC specification. By looking at temporal logic and Büchi automata, however, they can give a formal semantics to MSC, by adding end states to the GSTGs that reflect the reliability properties of the communication (which is precisely what is underspecified by MSC notation) and correlate them with the accepted traces of the automata they wish to define [LL92a].

Sometimes a hybrid description approach is used. Figure 13 shows an example of the XTP protocol using a combination of an architecture diagram and a message sequence diagram in order to further convey some meaning about the protocol. This figure shows that a FIRST packet must be the first packet sent, how it creates an association, and how this must precede all DATA packet transmission.

Taken together the internal and external descriptions can give the user a good feel for how a protocol works and helps one to understand what types of problems the protocol solves and how it goes about solving them.

Often the specification is used by various people in different phases or stages of the protocol design life cycle: specification, verification, testing, implementation. Thus it must be

Figure 13: XTP in action: FIRST and DATA packet exchanges

clear, unambiguous, and sufficiently detailed. Only then can the specification give confidence that the protocol will be correct [Lin85]. As many potential interactions are unexpected and undesirable, FDTs help to spot problems in the specification early enough in the life cycle to ward off having to make expensive and difficult changes later on.

Without standard design techniques or standard formulations to specify and verify protocol designs, many problems arise. For example, each designer's techniques, style, and quirks have to be learned. Instead of making a 'black art' of protocol design (much as compiler design was in the 1960s [AU77]), we would like to develop or follow a methodology that others may actually use to correctly design complicated communications protocols.

Eventually, the notion of a formal description of a protocol is proposed. This technique is superior to informal methods because formal descriptions are precise to the point that now the code can be checked by machine [Mil90, Vis90, Liu89]. It is this approach which we feel holds the greatest promise and which we explore and build on in this thesis.

### 3.3 Formal Methods and Protocol Engineering

Protocol Engineering is the term used to describe the formal design methodology used throughout the entire protocol design life cycle—from the initial specification, to validation and testing, test case generation, and the generation of implementation code.

In order to accurately describe protocols, much work has been done in the field of formal description techniques (FDT). Most research has focussed on formally specifying, verifying and validating protocols (the first stages in protocol engineering) for logical correctness.

There is good reason for focussing on the earliest stages. Errors in the design stage have a nasty habit of showing up in the implementation stage, and when discovered, they are costly to fix.

#### 3.3.1 Benefits of Formal Methods

FDTs provide a mathematical underpinning to specifications which ensures their precision and tractability. They allow for the design of open systems that insure implementations that can inter-work. The specifications are also less ambiguous and are free from implementation bias. FDTs attempt to provide a precise statement of the requirements.

Through their use, FDTs are found to [Tur93]:

- provide a high level of dependability and quality

- specify exactly what is required

- discover errors, ambiguities, and inconsistencies

- impose clear structure on the problem domain

- help in the early stages, to define the requirements and program structure

- highlight deficiencies in the existing informal description.

FDTs can also support the use of computer tools that can help the designer<sup>3</sup>. Now the tedious task of looking for inconsistencies can be handled by a machine and the designer can

<sup>&</sup>lt;sup>3</sup>"It is not necessary to have computer tools to support FDTs since they can be used as intellectual tools." [Tur93]. This represents the strictly formalist point of view, wherein it is argued that model building and proof making should be done without any computer assistance. (For an extreme representation of this point of view see [Ste], where Dijkstra proposes teaching courses with programming languages which are not implemented on campus in order to discourage the use of computers in programming and to drive the point home that computer science is essentially a branch of formal mathematics.) We would reject this claim and say that computer tools are necessary; see Colin H. West in his foreword to [Hol91], where he says "Protocols have proved to be extremely difficult to understand without automated analysis tools".

focus on the more creative elements. Another advantage is that the 'bugs' can be eliminated at the earliest possible stage—before implementation coding has started.

In a major project, where several people are usually working together, descriptions must be formal and unambiguous. This means that the formal specification guides the design, not the interpretation of a diagram or natural language text fragment. It is important that all agree on one specification and the earlier they can do this the better.

### **3.3.2** Models

Models are often used to map from the human intuitive understanding of an application as expressed in natural language concepts to one based on more formal concepts. The term model is used in two senses (which should be clear from the context that it is used in). Specific specification languages are based on a conceptual model—process algebra or the finite state machine, for example. On the other hand, we build specific protocol system models in a particular specification language. Obviously this protocol system model will reflect, in the larger sense, whatever fundamental constructs are inherent in the specific specification language model. Models are chosen to represent the significant system properties that are required.

The purpose of a model is to precisely define specific properties or characteristics of a system under consideration to be built or analysed, and provides the foundation for verifying those properties ...thus ...one must select from a class of models which represent that property [Lam85]

Models should allow all valid implementations but they often represent a tradeoff between good analytical powers and good expressive power. In the remaining section, we look at some models which we find useful for describing protocols.

For example, all three ISO FDTs use the "labelled transition system" (LTS) concept which is defined (rather generally) as "systems whose transitions between states are labelled with associated actions" as a basic model [Tur93]. We use this model (finite state machines) as well as another model which delineates the difference between concurrent and sequential programs. The first subsections look at the beginning of the research into this area.

**Note:** The following two subsections make frequent reference to the language PROMELA, which will be discussed in the next chapter. PROMELA relies heavily on the concepts

which follow and, as such we felt that it would be appropriate to contrast the original concepts with how PROMELA interpretes them as we introduce the concepts.

### 3.3.3 Guarded Commands

In the mid-1970's, Dijkstra [Dij75] applied some new structuring techniques he considered suitable to describe a certain class of sequential algorithms. He noted that these algorithms all shared the common trait of 'concurrency'. In having rewritten these algorithms, he proposed using 'guarded commands' to support the programming concept of 'non-determinism'. He noted that using non-determinism to express these algorithms made them easier to understand as their inherent concurrency was brought out.

### **Definition**

The heart of the new structuring method is the guarded command. Structurally, a guarded command consists of two parts: a guard and a list of one or more commands.

guard

$$\rightarrow$$

command-list  $(x >= y) \rightarrow m := x$

Syntax Example

#### **Semantics**

The guard indicates a boolean condition which controls the executability of an attached list of commands. When the guard is passed (if the boolean condition is true), the command(s) following the guard are executed. In the example above, if x >= y then the command list (in this case, there is only one element in the list), m := x is executed.

### **Guarded Command Sets**

A single guarded command by itself does not differentiate this model from a sequential model of course. This paradigm is only useful when several guarded commands are grouped together to form a guarded command "set". With a guarded command set, the order that 'true' guarded commands in the set occur is not related to its choice of executability. So any

<sup>4&</sup>quot;set" as used in the mathematical sense

guarded command that evaluates to true may be executed; sequential order, as for mathematical sets, is irrelevant. When x == y, for example, both x >= y and x <= y are equally possible, regardless of their order in the set. This is discussed more fully further on.

guard0 -> command-list0

$$x >= y -> m := x$$

[] guard1 -> command-list1 []  $x <= y -> m := y$

Syntax Example

### Two Language Structuring Constructs

Using the guarded command set as a primitive language construct, two language structuring methods are used:

- ullet the alternative construct: if < guarded command set > fi, and

- the repetitive construct: do < guarded command set > od.

The Alternative Construct In an alternative construct, such as

```

if

x > y -> m := x

x < y -> m := y

fi

```

at least one guard must be true or the program will abort. In the above example, program abortion occurs if x and y have the same value. The consequence of this, of course, is that the model can never block.

The semantics of this construct are different in PROMELA: the model will block if all the guards evaluate to false, i.e., no guard is true. Thus an 'exit' condition must be explicit (see left hand side of the following figure). In the latest version of PROMELA, this condition can be expressed more simply with the *else* statement (see right hand side of the following figure):

```

example:

if

if

if

i: x > y -> m := x

i: x > y -> m := x

i: x < y -> m := x

i: x < y -> m := y

i: x == y -> skip

fi

PROMELA example

PROMELA version 2 example

```

Finally, as we have just seen, if more than one guard is true, a guarded command is chosen at random (or non-deterministically).

```

if

x >= y -> m := x

\[ x <= y -> m := y\]

fi

```

In the example, if x equals y both guards are true therefore either guard is non-deterministically chosen.

The alternative construct offers choices among alternatives, much like the CASE statement in Pascal or the SWITCH statement in C. It differs from C or Pascal, where, the first or most specific true choice is picked. Instead *any* 'true' or executable choice is randomly picked from the guarded command set.

The Repetitive Construct In a repetitive construct, a structure such as:

is used for looping. When all guards are false the loop exits (for PROMELA, again, an explicit 'exit' condition is required or else the model blocks). After a guarded command finishes execution, control is returned to the beginning of the loop, and the choice of the next guarded command to be executed is repeated. This continues until an exit condition occurs.

### **Applying the Constructs**

Concurrent algorithms are non-deterministic <sup>5</sup>, thus repeated execution of the **same** algorithm, will result in a different sequence of execution for each subsequent run whereas execution traces of sequential programs are always the same on subsequent runs.

**Proving Correctness and Algorithm Tracing** Sequential programs are routinely proven correct the same way as mathematical functions are proven correct. For example, using a given domain and range, any input from the domain will always give the same result in the range. The result should be consistent and the steps executed to obtain a given output should also be consistent. Sequential algorithms are in essence 'functions'.

Any algorithm's execution trace can be followed by noting the order of steps taken every time the algorithm is run. For a sequential algorithm this trace must always be the same. This is not true for a concurrent algorithm.

**Non-determinism** The effects of non-determinism are most clearly seen after examining the execution traces of algorithms using constructs based on guarded commands. They show that the computation sequence and even the final state are not necessarily uniquely determined from the inputs.

For example, given two values x and y, one can not say which statement will execute if x and y are equal, as in:

```

example:

```

```

x >= 0 -> x = x - 1

x >= 0 -> x = x - 2

od

```

**Re-writing Certain Classes of Algorithms** In looking at how to write or 'derive' programs in this new style one of the algorithms Dijkstra considered was the GCD or Euclid's algorithm.

The following example calculates the GCD or greatest common divisor of any two numbers a and b. To illustrate, we can pick any numbers, so 23 and 47 will suffice. Note that this

<sup>&</sup>lt;sup>5</sup>Other models do not equate concurrency with non-determinism. see [MP92]

example is essentially the same example that was used to introduce the repetitive construct. The result will always be the same (the greatest common divisor of a and b), but the order of execution or trace will not necessarily ever be the same for repeated runs. In other words, we do not know the order that these statements will execute.

The next two examples are different implementations of the same algorithm but written without guarded commands. Notice that *two* implementations for the same algorithm can be written. Also note that neither version is as clear and concise as the version above.

```

x = 23; y = 47

x = 23; y = 47

while x <> y do

while x <> y do

if x > y

while x > y do

then x := x - y

x := x - y od

else y := y - x

while y > x do

fi

do y := y - x od

od

bo

Version A

Version B

```

Dijkstra noted that several sequential versions exist to implement this algorithm, but each version has extraneous implementation details. Expressed using guarded commands, the algorithm is reduced to its bare essentials, hence making it easier to understand.

### Concurrency

Dijkstra speculated on the possibility of concurrent execution of some of his algorithms. For example, when more than one guard is true, in a single CPU machine, only one alternative in a "do" loop may be executed at a time. However, in a multi-CPU environment, each alternative could potentially be executed by a separate CPU.

# 3.3.4 Communicating Sequential Processes

Hoare used Dijkstra's basic language structuring methods of alternation and repetition constructs (based on guarded commands) less in terms of non-deterministic algorithm design but, to further explore concurrency.

For example, single CPU computers are designed with the assumption that programs will run with a single thread of control: the model based upon a deterministic execution of a single sequential program.

With multi-CPU computer platforms, this is no longer true and so it is possible to rewrite certain algorithms to take advantage of potential concurrency by running several threads of control (parrallelism) in the program. This is not to say that a single CPU can't run this new algorithm: several processes do run in a time sharing environment 'virtually' at the 'same time' (the process scheduler uses small time slice periods to run each process so that each user has the impression that their process is the only one running), but it is more forthright when systems are explicitly designed to allow several threads of control to operate at once, such as in multi-CPU systems, thereby bringing out the real issues of concurrency.

### **Process Concept**

This brings up new issues for the programmer to consider: processes are taken as fundamental or primitive language concepts and building blocks. Hoare, in fact, saw the process as an object, expressed only in terms of its behaviour as an 'executing device'. He explored how processes could communicate and synchronise with each other.

If several processes can run at the same time, a mechanism must be proposed to do this. Hoare described a 'primitive' for parallel execution of processes (based on Dijkstra's parbegin), the semantics of which imply that the relative execution speeds of any component processes are irrelevant and further that this parallel command is not finished until all its component processes are finished, that is, the parallel command must wait for the last process to finish.

With parallel execution, the issue of inter-process communication is raised. Processes have to communicate for purposes of synchronisation or for information exchange (the exchange of data via the sending and receiving of messages between processes). Hoare explored how the input and output between processes are addressed.

### **Message Passing**

In order for running processes to exchange information between themselves, Hoare proposed 'message passing'. We contrast this with how variables in sequential programs are traditionally updated—by some sort of assignment statement. He compared this mechanism with the needs of concurrently running processes and argued that, between processes, input and output is sufficiently different to warrant a conceptually different mechanism. He proposed two primitives: send and receive.

### **Definition**

The syntax for receive is: <fromProcess>?msg and for send: <toProcess>!msg.

### **Syntax**

These commands are composed of three parts. First, a receiver names its sending process and a sender names the receiving process. The symbol "?" for the action "receive" and "!" for "send" is placed next, and finally, the actual message exchanged is placed last. The message can be a single variable or a structured variable as long as these types match between the sender and receiver.

### **Semantics**

Hoare discussed using channels (port names) instead of processes as the first component in a send or receive command. He rejected this idea because he felt using processes was more readable. As well, the possibility of connecting more than 2 processes via a single channel added complexities that took away from the issues he wanted to deal with. PROMELA does use channel or port names and more than two PROMELA processes can use a single channel. In fact, the language allows any process to access both ends of the same channel.

Hoare defines his message exchanges in terms of synchronous communication. This

means that corresponding send and receive commands in different processes must be executed simultaneously. If one process arrives at its message exchange statement before the other, it must wait.

Asynchronous (buffered) communication is not a primitive notion for Hoare. To model asynchronous communication, as many processes as the buffering capability of the asynchronous channel to be simulated are used. Each buffer entry process alternates between reception from an upstream neighbour and sending to a downstream neighbour, so that the total number of component buffer entry processes defines the buffer size <sup>6</sup>.

For Hoare, the alternative construct does not require at least one guard to be true: if all guards are false the alternative command simply fails.

# **Issues for Communicating Protocols**

Hoare allows reception statements to be used as guards. This has dangerous consequences but largely represents exactly the types of systems we want to study when building communications protocol models. For example, if no sender completes an exchange where a reception is used as a guard, the possibility of 'deadlock' exists. This is an important issue to explore in any given model. This can be seen in the following scenario.

Using a repetition construct, with all guards being receptions, the only way for this loop to continue is to either wait for the first corresponding send to complete the exchange or wait for all source processes to terminate thereby terminating the loop. If neither of the two above events occur, the whole process stops, frozen in deadlock.

The issue of 'fairness' was also brought up: a choice can not be indefinitely not chosen and implementations rather than the programming language should guarantee fairness. Also, the programmer must show that the program terminates correctly. After considering parallelism and message exchange, Hoare concludes that input/output and concurrency should be primitives of any programming language.

# 3.3.5 Finite State Machines (FSMs)

The FSM is a fundamental model of computer science.

<sup>&</sup>lt;sup>6</sup>This synchronous buffer concept is also a fundemental premise in th LOTOS language [BB87]

"The FSM model provides the foundation for consistency and completeness properties linking inputs, outputs, state, and processing, and provides the link into program proof techniques". [Lam85]

Formally a FSM can be viewed as follows:

- set of inputs, X

- set of outputs, Y

- set of states, S

- an initial state,  $S_0$

- 2 functions that specify the result of inputs for all states at each state:

- a transformation function that specifies the resulting output

- a state transition function that specifies the resulting next state.

Its main limitations are that:

- 1. it serialises away all of the underlying concurrency ("clash states" are neglected)

- 2. the model is "flat": there is no inherent way of handling complexity

Figure 11 is an example of a FSM. These limitations are overcome by introducing "extensions"—essentially allowing variables and modules within the context of a programming language. FSMs that are used to describe communications systems are often extended by adding modules, variables, and send and receive primitives. Once a FSM system is designed, a trace is often used to describe the behaviour of these models.

# 3.3.6 Reactive Systems

Protocol models are part of a larger class of models called reactive systems.

Reactive systems are distinguished by the fact that they are always accepting input. Unlike sequential programs, they are highly interactive with their environment [MP92].

"The fact that the state of the system is changing while a process is viewing it is the fundamental problem in synchronising any kind of concurrent systems" [BBBC93].

As previously mentioned, sequential systems can be thought of as a function, where an input occurs, followed by its processing and finally its return. The fundamental concern of sequential programs is the input/output behaviour of the machine (the relation between the starting and terminating states).

Concurrent machines, whether shared memory multiprocessors (tightly coupled) or distributed systems (loosely coupled) are more complicated. With concurrent programs, two concurrent subprograms can interfere with one another. So one must look at the complete behaviour of the model: what the program does throughout its execution lifetime.

Formally, we can look at sequential programs as a special case of concurrent programs. First let us attempt to illustrate a representation of the execution of a sequential program:

$$\Sigma = s_0 \xrightarrow{\alpha_1} s_1 \xrightarrow{\alpha_2} s_2 \xrightarrow{\alpha_3} s_3 \cdots \xrightarrow{\alpha_n} s_n$$

where.

- s; are states

- $\alpha_i$  are atomic actions

- $\bullet$   $\Sigma$  is the sequence which is finite iff the sequence terminates.

This provides us with a simple trace that describes the behaviour of the system. Each state contains all the necessary information to determine its future behaviour. The sequence is termed "deterministic" if each state contains precise information about what its next move should be. The behaviour of the entire sequence is described as deterministic. Non-deterministic behaviour describes a situation where a given state has more than one choice.

Often, we wish to look at the set of all possible behaviours of a system due to its component actions. Actions are deemed atomic if an action, e.g. x = x + 1 proceeds uninterrupted from a current state where x = x to a next state where x = x + 1.

How the program is divided into atomic actions is irrelevant for sequential programs but is important for concurrent ones.

# 3.3.7 Concurrency

Different formalisms are used to describe this behaviour trace. We can describe this trace as a sequence of actions (space-time view) or a sequence of states (the interleaving view).

The space-time view describes its execution model in terms of actions. Although actions within a process are totally ordered, actions across processes can not be viewed as sequentially ordered. The space-time view assumes a partially ordered set of events determined by events per process totally ordered in time and cause must preced effect for inter-process actions. "This set of temporal orderings must be acyclic, so its transitive closure forms an irreflexive partial ordering" [Lam85].

The interleaving view reasons in terms of states. One constructs a global state-transition graph as per sequential models, in the sense that, if two actions occur at the same time, and they do not influence each other, we may pretend that they occur in either sequence. If we find that these actions do influence each other then we may say that the actions are NOT atomic so we may now increase the level of atomicity in the model. This, of course, requires that we lose precedence relations on a global level.

# 3.4 Validation and Verification

It is not enough to specify a system (although this can be a major task by itself). In order to be confident that the model reflects reality it must also be validated and verified.

Validation refers to checking general properties of the model in question. What we mean by the general properties are the characteristics that must be true regardless of the specific characteristics of any one protocol. Thus validation consists of checking for no deadlock, no unspecified receptions, no livelock, etc. [Lin85] defines validation as the properties that are apropos to all protocols and suggests that the following should be checked for:

- absence of deadlock

- completeness: ability to handle any condition that may occur

- absence of livelock: continual cycling of code that does nothing useful

- freedom from overflow

- stability

- proper termination.

Verification refers to checking the characteristics or properties that are unique to a protocol. [Lin85] defines verification as "checking the logical correctness of the protocol". For example, if any specific claims are made about the protocol, the proof that these claims are true is termed verification. In the language that we will use, specific PROMELA language primitives are available in order to do this.

# 3.4.1 Reachability Analysis

Reachability analysis is used to validate protocol models. The idea is conceptually simple and has been used for some time. Each single component module's behaviour is described via a FSM. In order to describe the behaviour of the entire system, each module and the interactions between them (as represented by the messages in transition for each channel) are used to yield a 'global' description. Reachability analysis attempts to build this complete system—essentially delineating all possible traces, which taken cumulatively, describes the global system behaviour.

The behaviour of the global machine can be represented by a finite graph, where every node represents a reachable system state and every transition represents the execution of a single statement in a single process [HGP92]. Once this graph is constructed a reachability analysis algorithm is used to traverse the graph in order to explore all the global system states.

The problem is that this methodology is often not practical because of the combinatorial explosion of the global state space, known as the 'state explosion problem'. As the complexity of the protocol increases, the number of states that have to be checked grows exponentially until it is too time or resource consuming to check the entire protocol model.

### **Graph Traversal Techniques**

Different reachability algorithms have been designed through the years in order to make the size of the problem space that can be covered by reachability analysis larger.

For example, one technique, the 'random walk validation' only analyses a small fraction of the reachable state space but it can detect a large fraction of the errors in a complex protocol, provided the errors themselves have limited complexity. The idea is based on the fact that in global FSMs there is much state duplication and any random walk down the many available traces will allow one to 'hit' most of the errors, if any. This method is described in [Wes89].

Different approaches to this problem are described by many other researchers. Holzmann [Hol85] and [Hol87] provide a good overview of these approaches. Holzmann [Hol90a] and [Hol90b] also provide many examples of algorithms for protocol verification. Holzmann [Hol88] introduces the bitstate approach, which is implemented in the SPIN tool. Holzmann et al. [HP89] discusses many of these issues for SDL. The authors also describe a way to pose correctness assertions directly in temporal logic, which curiously, has yet to show up in the SPIN tool.

[HGP92] describe three new reduction strategies for conventional reachability analysis. They describe implementations of partial order semantics rules that attempt to minimise the number of execution sequences that need to be explored for a full state space exploration. This has recently been implemented in the latest version of the SPIN tool [Hol95b]. They then go on to describe a method to minimise the amount of memory that is used to build a state space. They follow up on this last idea in [GHP92] where they maximise the number of global states that are cached in memory. They describe a method to avoid exponential increase of the run-time overhead caused by interleavings of a same partial ordering of statement executions leading to the same state.

As can be seen, the state explosion problem can not be avoided. Instead optimisations based on certain assumptions about the model are used to help design algorithms that make the analysis practical, yet still cover all the relevant states.

# 3.4.2 Temporal Logic

Logic is most often used to talk "about" a model in the protocols community. "The goal of reasoning about a program is to show that  $\models A$  is true for a desired property A."[Lam85] One uses linear time temporal logic [Pnu77, Hai82, MP92, Lam85], where actions are

ignored and only states used. Temporal logic uses several notions from classical propositional logic. Claims are expressed as assertions which are well formed formulas (wff) of classical logic and all new formulas are derived from temporal logic. [Got92, HG] provides a good introduction to temporal logic.

# 3.4.3 Classical Logic

Classical logic is defined as follows:

- P atomic predicates

- logical operators:

- or v.

- and  $\wedge$ ,

- negation -,

- $-\supset$  or  $\rightarrow$  for material implication

Formally a state is defined as a truth-valued function on the set of atomic predicates, which is written as  $s \models P$ , in order to describe the value of state s on predicate P.

Taking a more abstract view, we look at each state as being composed of many variables (including a program counter) and each state is determined by the sum total of the value of each predicate that it contains. Predicates are defined as all the variables taken singly or any logical combination of them.

From this we can build a model M:  $(S, \Sigma)$  where S is a set of states and  $\Sigma$  is a complete set of sequences of states (trace) satisfying property E starting at any possible state.