#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## Fast Symbol Synchronization Algorithms for On-Board Processing Satellites

Jeetendar Narsinghani

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

September 2002

© Jeetendar Narsinghani, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Valve référence

Our lite Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-72913-3

#### ABSTRACT

# Fast Symbol Synchronization Algorithms for On-Board Processing Satellites

#### Jeetendar Narsinghani

Satellite communications continue to undergo changes not only from advancing technology, but also from new service and regulatory activities. Therefore, advanced digital satellite communication systems using efficient on-board processing capabilities are required. Signal regeneration on-board the satellite makes it possible to use different multiple access schemes for the uplink and the downlink. The uplink and the downlink can be separately optimized for greater power efficiency and bandwidth utilization. A multiple access scheme using the frequency division multiple access (FDMA) for the uplink and time division multiplex (TDM) for the downlink has been considered for regenerative satellite communications. However, the feasibility of this approach depends on efficient means to directly interface the two multiple access formats on-board the satellite. The conversion from frequency to time division multiplex format requires the uplink signal to be demultiplexed and each individual carrier to be demodulated.

The main objective of this thesis is to present the existing symbol timing recovery structures, analyze them and prove the feasibility of the proposed technique which is less complex and that has fast-acquisition characteristics than the conventional techniques. Firstly, feed-forward symbol timing recovery technique based on the

spectral line estimation is presented, which requires relatively high over-sampling ratio and requires considerable amount of hardware resources for implementation. Secondly, feedback timing estimators are analyzed. These techniques have less complex structures compared to feed-forward structures but require more acquisition time. Feedback structures are well suited for continuous mode communications. Finally, a new algorithm for symbol timing recovery is presented in this thesis, which is based on decision-directed approach. The proposed algorithm has fast acquisition time, it has been shown through computer simulations that it is three times faster than the conventional feedback technique. In terms of VLSI implementation, the proposed symbol timing recovery circuit requires 3 adders for QPSK modulation format, where as Gardner's timing error detector needs 3 adders and 2 multipliers.

Dedicated to my uncle, Late Shri Tarachand Narsinghani.

#### **ACKNOWLEDGEMENTS**

I express my utmost gratitude to my supervisor, Dr. Mohammad Reza Soleymani, for originally proposing the research area and subsequently guiding me through the various stages of this research.

I would like to thank my friends, Rajesh, Sanjeev. Nikhil, Zahoor and many more whom I haven't mentioned for their invaluable support and encouragement.

I am also grateful for the constant support and love provided by my family.

Last but not the least, I would like to thank Leena for her patience and support.

## TABLE OF CONTENTS

| LI | ST O | F FIG  | URES                                                          | ,   |

|----|------|--------|---------------------------------------------------------------|-----|

| LI | ST O | F ABE  | BREVIATIONS AND SYMBOLS                                       | xiv |

| 1  | Inti | oduct  | ion                                                           | 1   |

|    | 1.1  | Backg  | ground                                                        | 1   |

|    | 1.2  | Contr  | ibution of Thesis                                             |     |

|    | 1.3  |        | nization of Thesis                                            |     |

| 2  | Clo  | ck Syr | nchronization Issues in Satellite Digital Receivers           | 5   |

|    | 2.1  | Introd | luction                                                       | ;   |

|    | 2.2  | Impor  | tance and need for Synchronization                            | 6   |

|    |      | 2.2.1  | Importance of Timing Estimation                               | 8   |

|    |      | 2.2.2  | Overview of existing schemes and strategies                   | ç   |

|    | 2.3  | The E  | Effect of Timing Offset on System Performance                 | 12  |

|    |      | 2.3.1  | Effects of Filtering in Digital Transmission                  | 12  |

|    |      | 2.3.2  | Probability of Error                                          | 16  |

|    | 2.4  | Symb   | ol Timing Estimators                                          | 20  |

|    |      | 2.4.1  | Feed-Forward Estimators                                       | 22  |

|    |      | 2.4.2  | Feedback Estimators                                           | 26  |

|    | 2.5  | Techn  | iques for Timing Correction/Adjustment                        | 29  |

|    |      | 2.5.1  | NCO Based Hybrid Method for Synchronous Sampling              | 29  |

|    |      | 2.5.2  | Ideal Sync Function Based Timing Correction                   | 3   |

|    |      | 2.5.3  | Polynomial based Interpolators with Non-Sync Sampling         | 32  |

|    |      | 2.5.4  | Coefficient Memory Implementation for Interpolation Filters . | 33  |

|    | 2.6  | Comp   | parison of NDA and DD Schemes                                 | 35  |

| 3 | Nor | -data Aided Feed-Forward Estimation                                 | 36 |

|---|-----|---------------------------------------------------------------------|----|

|   | 3.1 | Introduction                                                        | 36 |

|   | 3.2 | DFT Based STR                                                       | 36 |

|   | 3.3 | Theoretical Bounds on Performance                                   | 40 |

|   |     | 3.3.1 The Cramer-Rao Lower Bound for Block Based Estimators         | 40 |

|   |     | 3.3.2 Derivation of CRLB                                            | 41 |

|   | 3.4 | Performance of FFT based STR                                        | 42 |

|   | 3.5 | Implementation Issues and Considerations                            | 45 |

| 4 | Fee | dback Timing Error Detectors                                        | 47 |

|   | 4.1 | Introduction                                                        | 47 |

|   | 4.2 | Non-Decision Directed TED                                           | 48 |

|   | 4.3 | Decision Directed Timing Phase Detector                             | 49 |

|   | 4.4 | Theoretical Bounds for Performance                                  | 50 |

|   |     | 4.4.1 The CRLB for Feedback STR Structures                          | 50 |

|   | 4.5 | Performance Analysis                                                | 52 |

|   |     | 4.5.1 Acquisition Performance                                       | 52 |

|   |     | 4.5.2 Tracking performance                                          | 54 |

| 5 | Pro | posed TED using DD Feedback Technique and a Filter Inter-           |    |

|   | pol | ation Approach                                                      | 56 |

|   | 5.1 | Introduction                                                        | 56 |

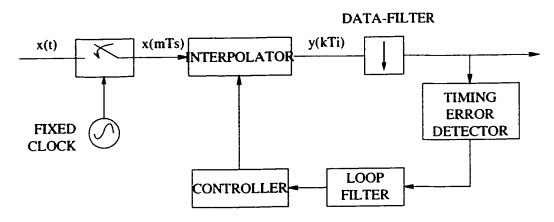

|   | 5.2 | Feedback Timing Control Loop Model                                  | 57 |

|   |     | 5.2.1 Feedback Loop                                                 | 57 |

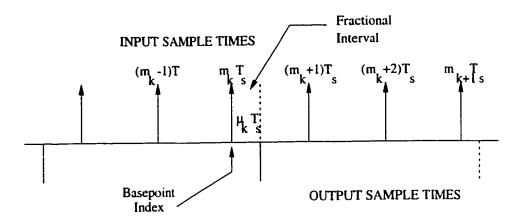

|   |     | 5.2.2 Interpolator Equation                                         | 58 |

|   | 5.3 | Proposed Timing Error Detector (TED)                                | 61 |

|   |     | 5.3.1 Algorithm                                                     | 62 |

|   | 5.4 | Using RRC Filter instead of Interpolator FIR Filter for Timing Cor- |    |

|   |     | rection                                                             | 64 |

|   | 5.5    | Perfor | mance                                          | 67 |

|---|--------|--------|------------------------------------------------|----|

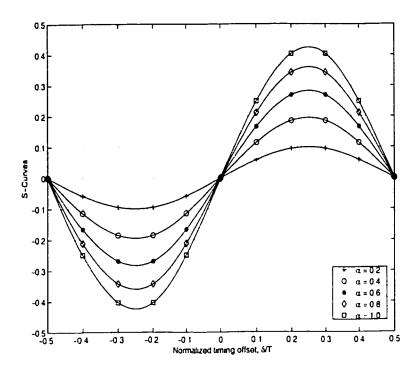

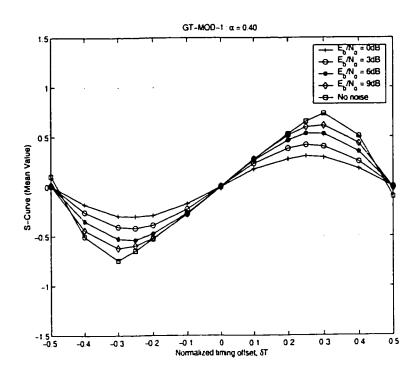

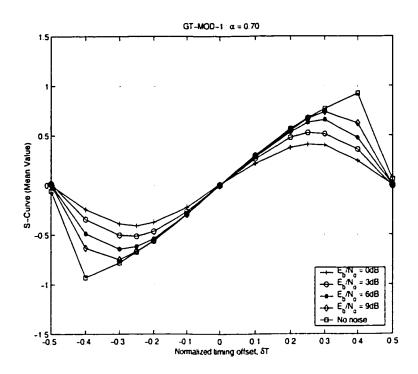

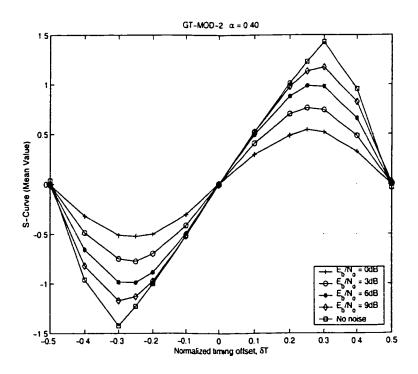

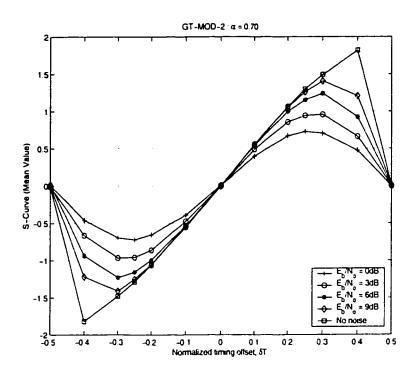

|   |        | 5.5.1  | S-Curve: Mean of the Estimated Timing Error    | 67 |

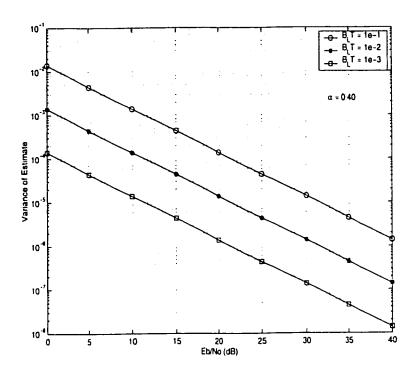

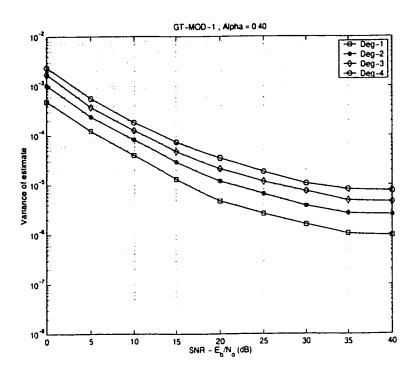

|   |        | 5.5.2  | Variance of Estimate (or Tracking Performance) | 70 |

|   |        | 5.5.3  | Acquisition Performance                        | 75 |

|   |        | 5.5.4  | Bit Error Rate                                 | 76 |

|   | 5.6    | Hardw  | vare Implementation Structures and Issues      | 83 |

|   |        | 5.6.1  | Clock Recovery Circuit                         | 86 |

|   |        | 5.6.2  | FIR Filter Implementation                      | 88 |

|   |        | 5.6.3  | Loop Filter                                    | 91 |

| 6 | Con    | clusio | ns and Suggestions for Further Research        | 93 |

|   | 6.1    | Summ   | ary and Conclusion                             | 93 |

|   | 6.2    | Sugges | stions for Further Research                    | 95 |

| В | ibliog | graphy |                                                | 96 |

## LIST OF FIGURES

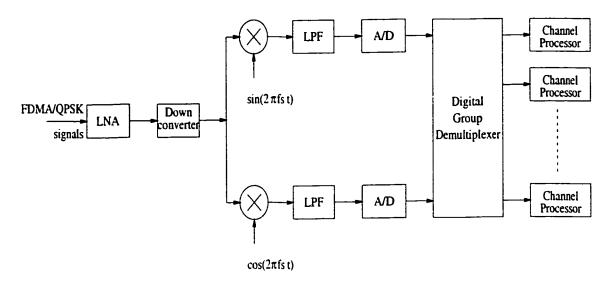

| 1.1  | Block diagram of group demodulator                               | 3  |

|------|------------------------------------------------------------------|----|

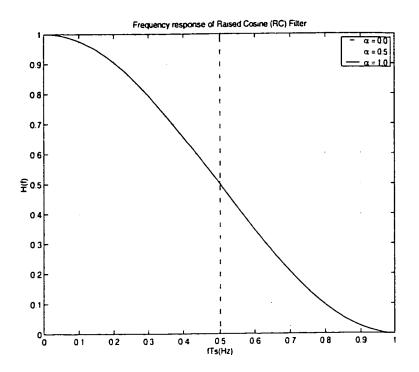

| 2.1  | Raised Cosine Filter Frequency Response                          | 14 |

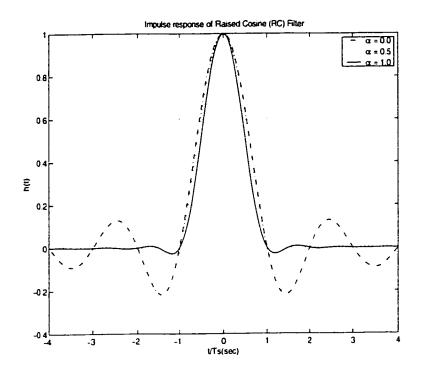

| 2.2  | Raised Cosine Filter Impulse Response                            | 15 |

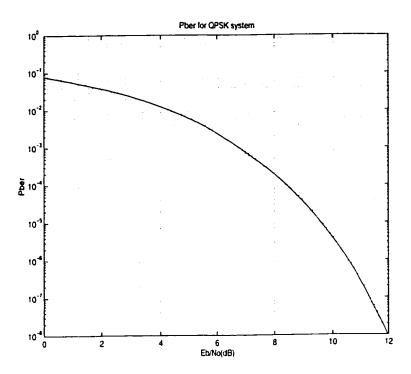

| 2.3  | Probability of Bit Error for QPSK System                         | 16 |

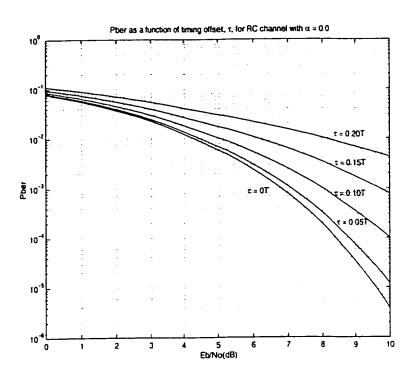

| 2.4  | BER as a function of timing offset, $\tau$ , for RC channel with |    |

|      | $\alpha = 0$                                                     | 18 |

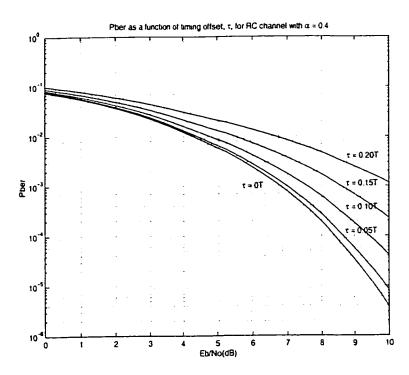

| 2.5  | BER as a function of timing offset, $\tau$ , for RC channel with |    |

|      | $\alpha = 0.4$                                                   | 18 |

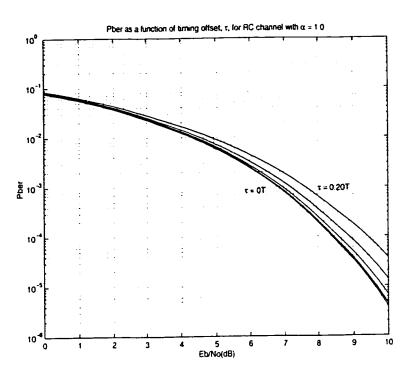

| 2.6  | BER as a function of timing offset, $\tau$ , for RC channel with |    |

|      | $\alpha = 1.0 \ldots$                                            | 19 |

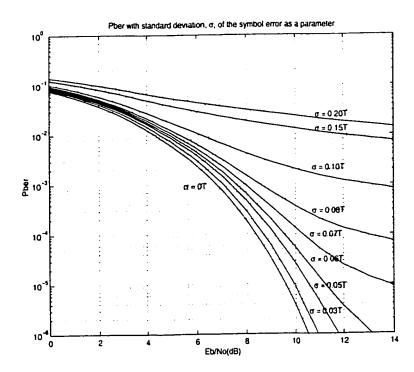

| 2.7  | BER as a function of standard deviation of timing offset as      |    |

|      | parameter                                                        | 19 |

| 2.8  | Feedback Configuration                                           |    |

| 2.9  | Feed-forward Configuration                                       | 21 |

| 2.10 | Synchronous Sampling                                             | 21 |

| 2.11 | Non-synchronous Sampling                                         | 22 |

| 2.12 | Block diagram of receiver with Mueller and Muller Synchro-       |    |

|      | nizer                                                            | 27 |

| 2.13 | Block diagram of a hybrid NCO                                    | 30 |

| 2.14 | Analog Implementation                                            | 32 |

| 2.15 | Digital Implementation                                           | 32 |

| 2.16 | Impulse responses for the Fractional Delay filters and the       |    |

|      | underlying continuous-time impulse response                      | 34 |

| 3.1  | Timing phase estimate using the spectral line method             | 3′ |

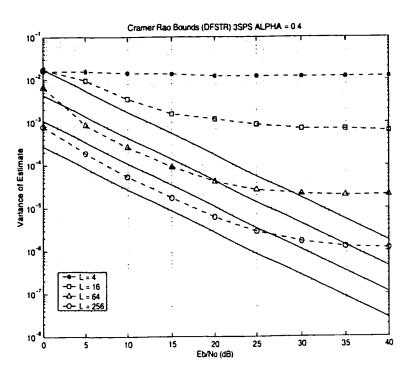

| 3.2  | Demonstration of TRC using spectral line                  | 38 |

|------|-----------------------------------------------------------|----|

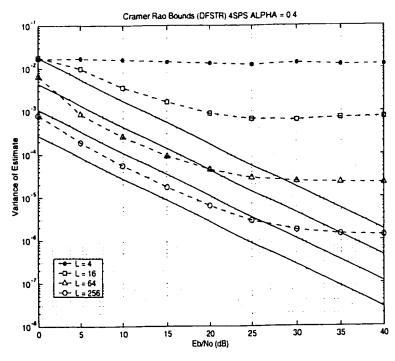

| 3.3  | CRLB for Oerder and Meyr scheme (varying L, 3SPS, and     |    |

|      | ALPHA = 0.4)                                              | 43 |

| 3.4  | CRLB for Oerder and Meyr scheme (varying L, 4SPS, and     |    |

|      | ALPHA = 0.4)                                              | 43 |

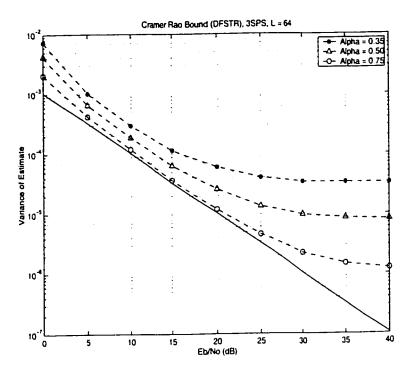

| 3.5  | CRLB for Oerder and Meyr scheme (varying roll-off values, |    |

|      | 3SPS, and $L = 64$ )                                      | 44 |

| 3.6  | CRLB for Oerder and Meyr scheme (varying roll-off values, |    |

|      | 3SPS, and $L = 256$ )                                     | 44 |

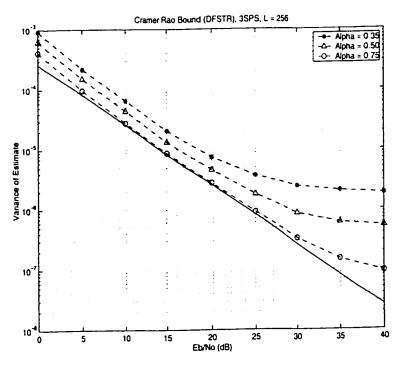

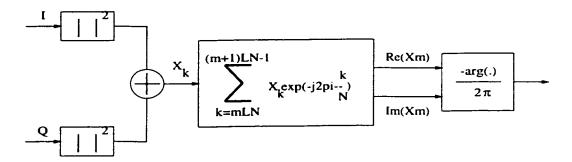

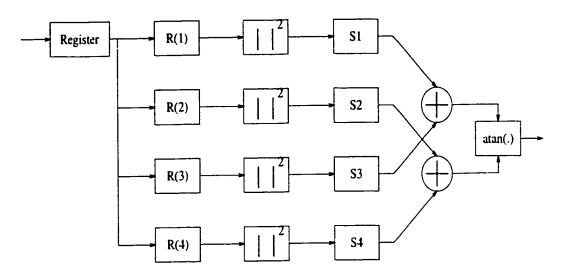

| 3.7  | Block Diagram of DFT based Timing Estimator               |    |

| 3.8  | Realization of the DFT based Timing Estimator             | 46 |

|      | Feedback Configuration                                    | 47 |

| 4.1  |                                                           |    |

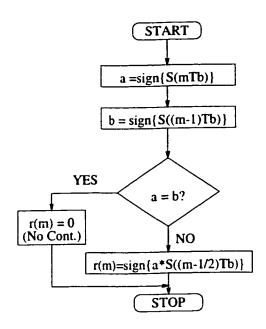

| 4.2  | Flow chart for determining the timing error signal        |    |

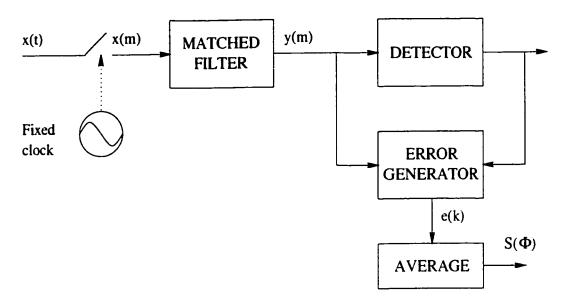

| 4.3  | Measuring the S-curve of the detector                     |    |

| 4.4  | S-Curves for Gardner's Timing Error Detector              |    |

| 4.5  | Effect of Loop Bandwidth on Variance of Estimate          | 54 |

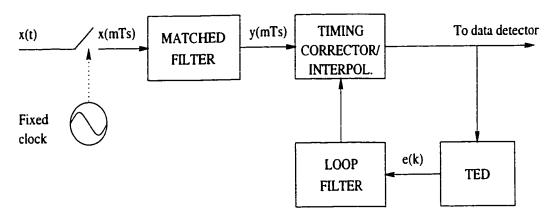

| 5.1  | Digital timing recovery feedback loop                     | 57 |

| 5.2  | Rate conversion with time-continuous filter               | 59 |

| 5.3  | Sample Time relations                                     |    |

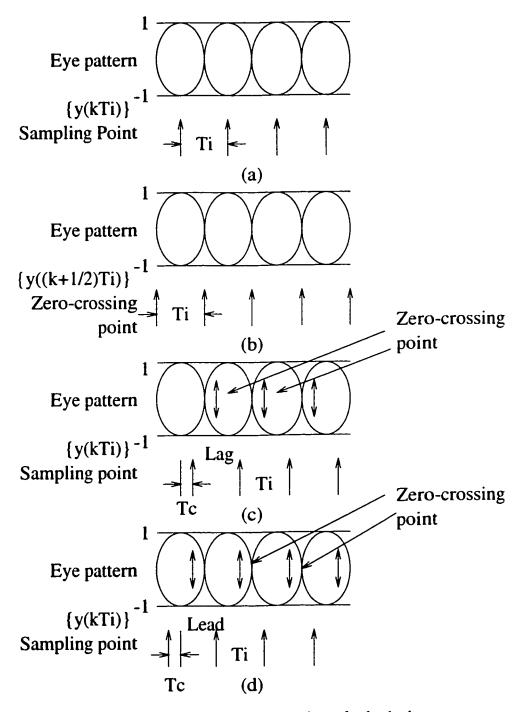

| 5.4  | Procedures for detecting clock timing error               | 63 |

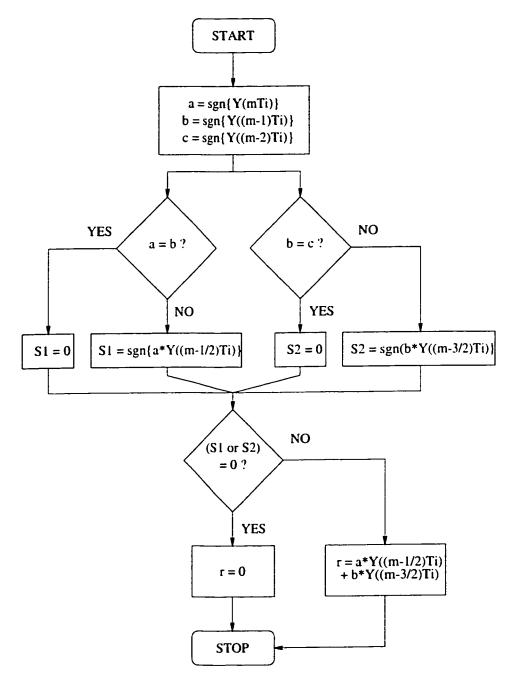

| 5.5  | Flow chart GT-MOD-1                                       | 65 |

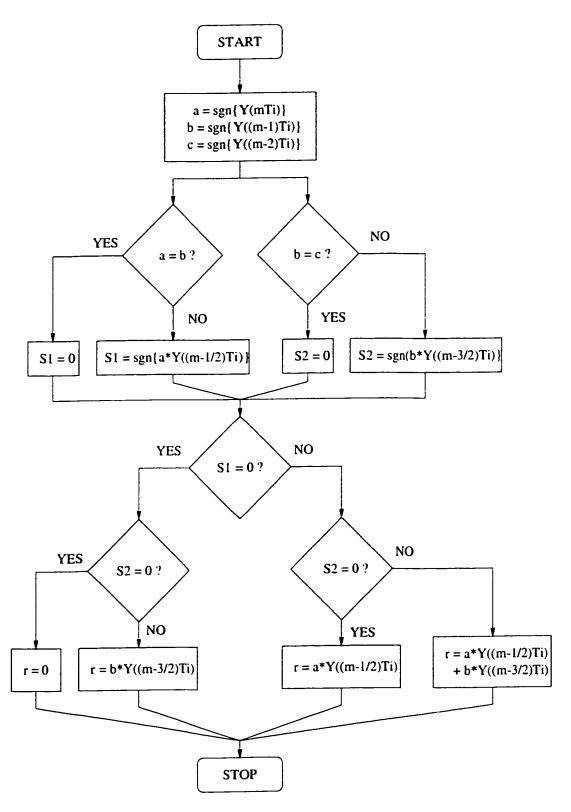

| 5.6  | Flow chart GT-MOD-2                                       |    |

| 5.7  | S-Curve for GT-MOD-1 for alpha = 0.40                     |    |

| 5.8  | S-Curve for GT-MOD-1 for alpha = 0.70                     | 69 |

| 5.9  | S-Curve for GT-MOD-2 for alpha = 0.40                     |    |

| 5.10 | S-Curve for GT-MOD-2 for alpha = 0.70                     | 70 |

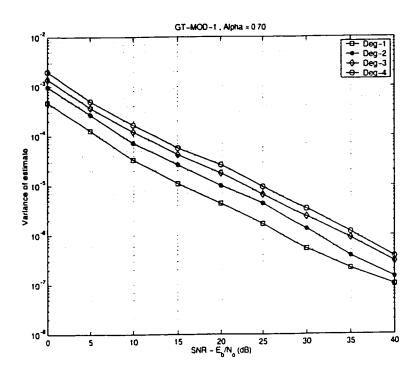

| 5 11 | Tracking performance for GT-MOD-1 for alpha = 0.40        | 71 |

| 5.12 | Tracking performance for GT-MOD-1 for alpha = $0.70 \dots$                        | 72 |

|------|-----------------------------------------------------------------------------------|----|

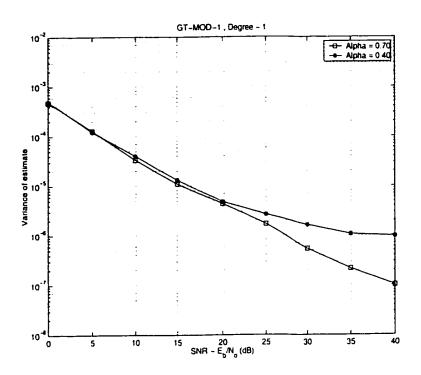

| 5.13 | Tracking performance for GT-MOD-1 (Degree $= 1) \dots$                            | 73 |

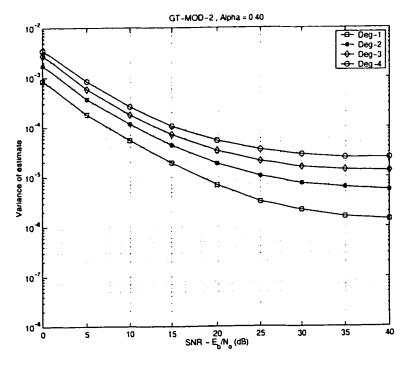

| 5.14 | Tracking performance for GT-MOD-2 for alpha = $0.40$                              | 73 |

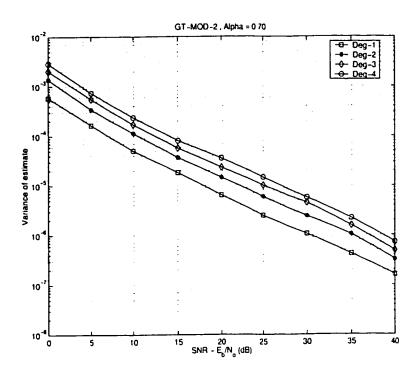

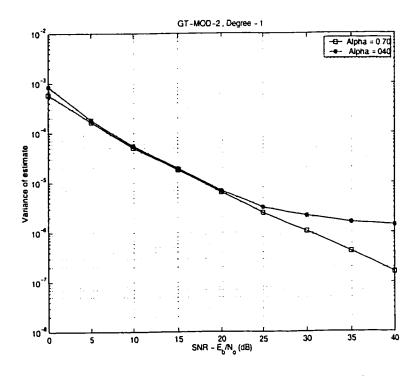

| 5.15 | Tracking performance for GT-MOD-2 for alpha = $0.70$                              | 74 |

| 5.16 | Tracking performance for GT-MOD-2 (Degree $= 1) \dots$                            | 74 |

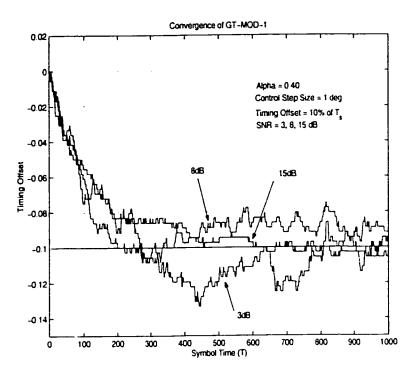

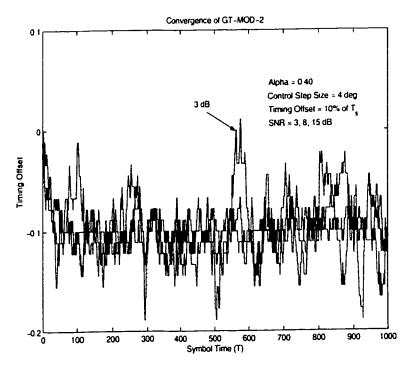

| 5.17 | Convergence of GT-MOD-1 for different SNRs (alpha $= 0.40$                        |    |

|      | and deg - 1)                                                                      | 76 |

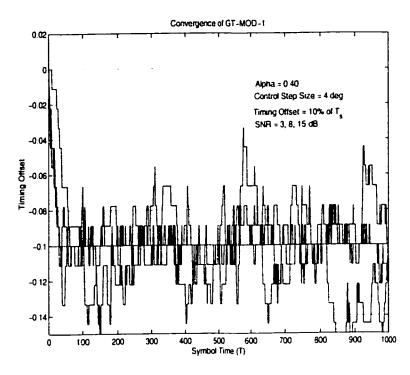

| 5.18 | Convergence of GT-MOD-1 for different SNRs (alpha $= 0.40$                        |    |

|      | and deg - 4)                                                                      | 77 |

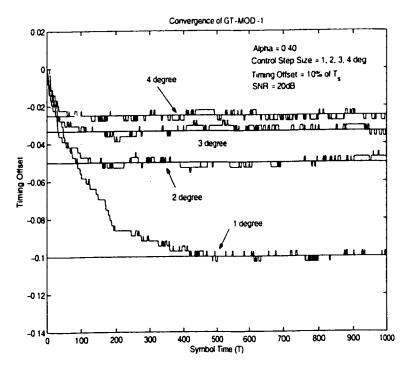

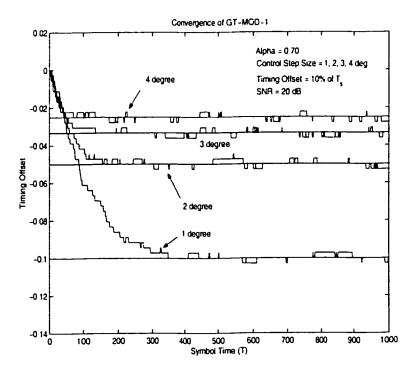

| 5.19 | Convergence of GT-MOD-1 for various control step size (al-                        |    |

|      | pha = 0.40)                                                                       | 77 |

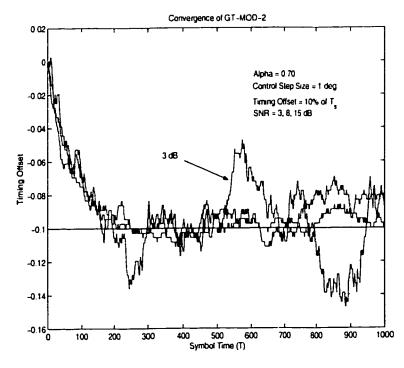

| 5.20 | Convergence of GT-MOD-1 for different SNRs (alpha = $0.70$                        |    |

|      | and deg - 1)                                                                      | 78 |

| 5.21 | Convergence of GT-MOD-1 for various control step size (al-                        |    |

|      | pha = 0.70)                                                                       | 78 |

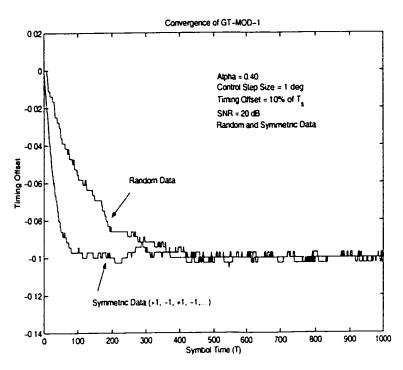

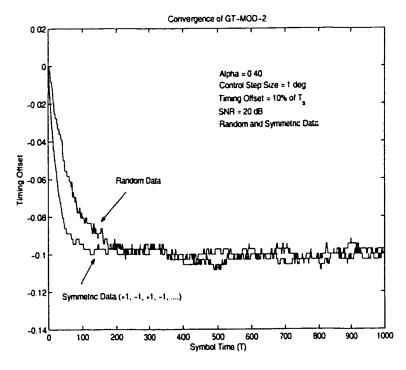

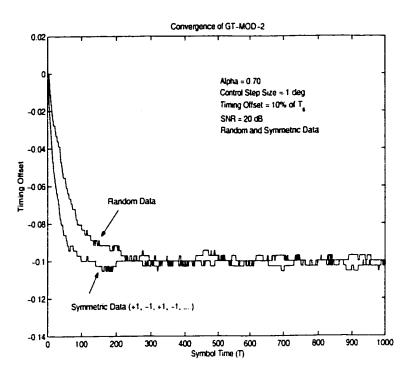

| 5.22 | Convergence of GT-MOD-1 for Random and Symmetric data                             |    |

|      | $(alpha = 0.40)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 79 |

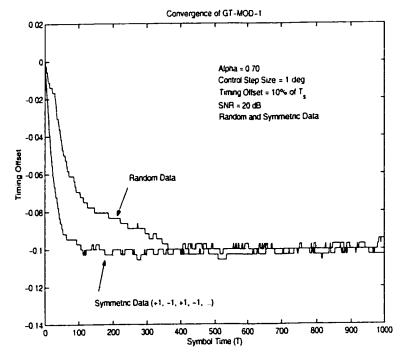

| 5.23 | Convergence of GT-MOD-1 for Random and Symmetric data                             |    |

|      | (alpha = $0.70$ )                                                                 | 79 |

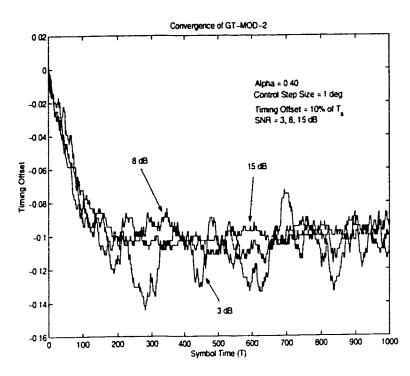

| 5.24 | Convergence of GT-MOD-2 for different SNRs (alpha $= 0.40$                        |    |

|      | and deg - 1)                                                                      | 80 |

| 5.25 | Convergence of GT-MOD-2 for different SNRs (alpha $= 0.40$                        |    |

|      | and deg - 4)                                                                      | 80 |

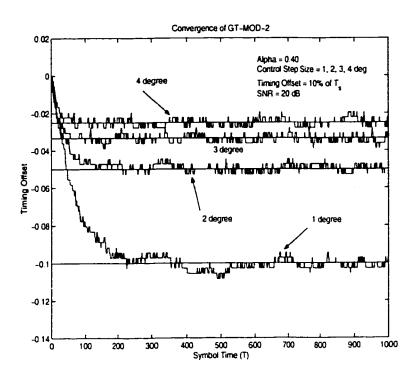

| 5.26 | Convergence of GT-MOD-2 for various control step size (al-                        |    |

|      | pha = 0.40)                                                                       | 81 |

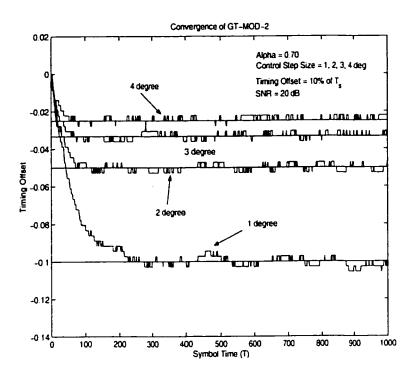

| 5.27 | Convergence of GT-MOD-2 for different SNRs (alpha $= 0.70$                        |    |

|      | and deg - 1)                                                                      | 81 |

| 5.28 | Convergence of GT-MOD-2 for various control step size (al-                                                                         |    |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $pha = 0.70) \dots \dots$    | 82 |

| 5.29 | Convergence of GT-MOD-2 for Random and Symmetric data                                                                              |    |

|      | $(alpha = 0.40) \dots \dots$ | 82 |

| 5.30 | Convergence of GT-MOD-2 for Random and Symmetric data                                                                              |    |

|      | (alpha = 0.70)                                                                                                                     | 83 |

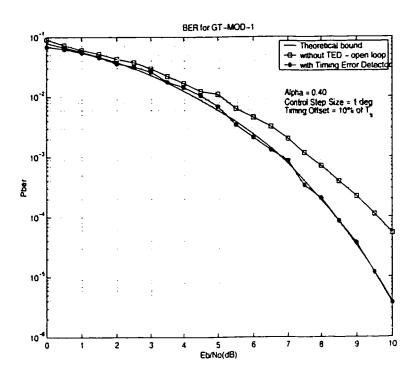

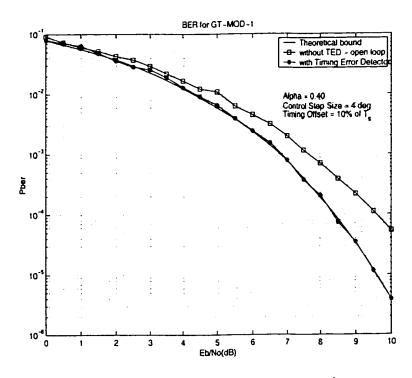

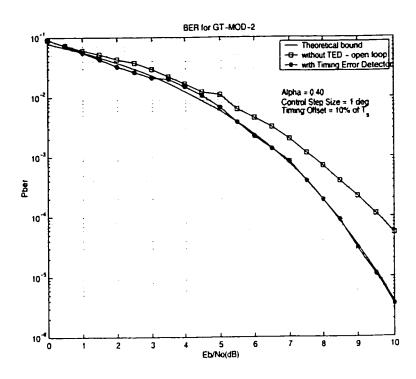

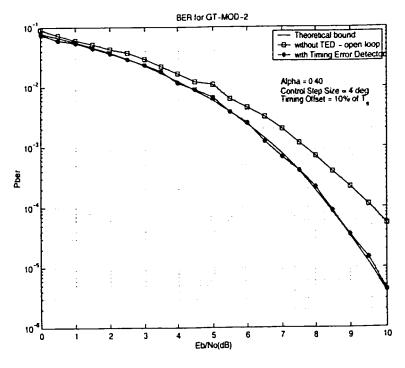

| 5.31 | Bit Error Rate for GT-MOD-1 (Degree - 1)                                                                                           | 84 |

| 5.32 | Bit Error Rate for GT-MOD-1 (Degree - 4)                                                                                           | 84 |

| 5.33 | Bit Error Rate for GT-MOD-2 (Degree - 1)                                                                                           | 85 |

| 5.34 | Bit Error Rate for GT-MOD-2 (Degree - 4)                                                                                           | 85 |

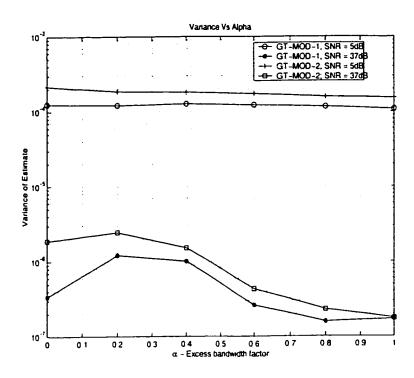

| 5.35 | Variance Vs Alpha for GT-MOD-1 and GT-MOD-2                                                                                        | 86 |

| 5.36 | Implementation structure for Gardner's TED                                                                                         | 87 |

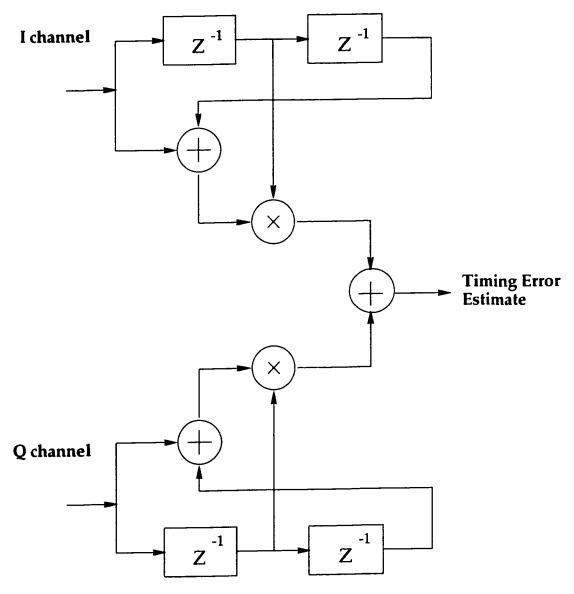

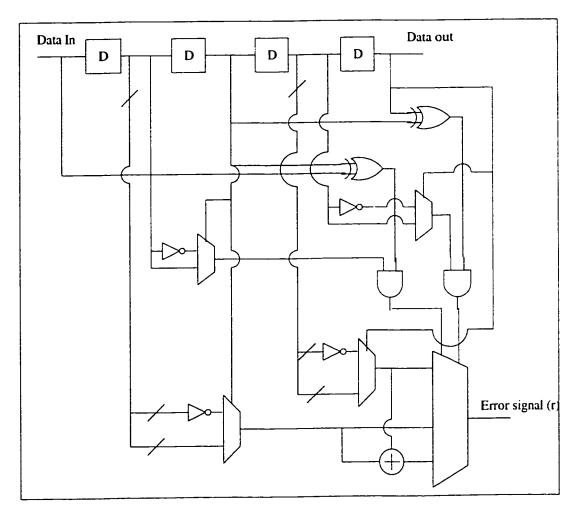

| 5.37 | Logic level circuit diagram for GT-MOD-2                                                                                           | 89 |

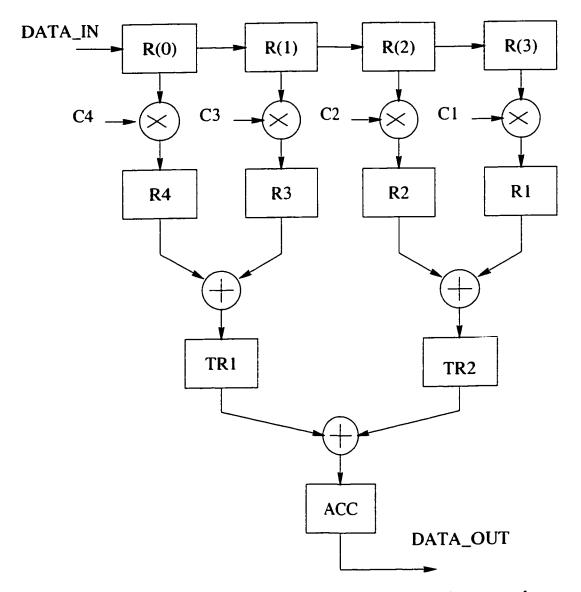

| 5.38 | FIR filter implementation using pipelined approach                                                                                 | 90 |

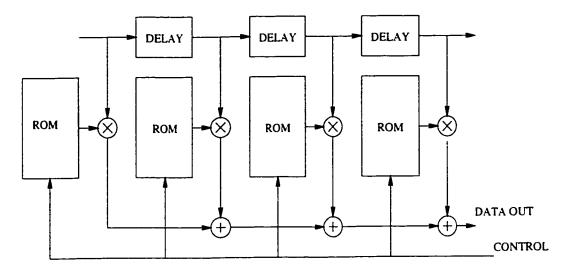

| 5.39 | Adaptive FIR filter implementation using ROM                                                                                       | 91 |

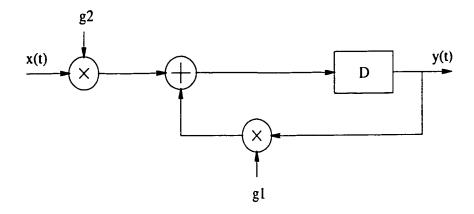

| 5.40 | Loop filter                                                                                                                        | 92 |

#### LIST OF ABBREVIATIONS AND SYMBOLS

AAF Anti-Aliasing Filter

ADC Analog to Digital Converter

ARC Adaptive Rate Conversion

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPF Band Pass Filter

BPSK Binary Phase Shift Keying

BW Bandwidth

CR Carrier Recovery

CRB Cramer Rao Bound

DA Data Aided

DAC Digital to Analog Converter

DD Decision Directed

DFT Discrete Fourier Transform

DSP Digital Signal Processing

FB Feedback

FDM Frequency Division Multiplex

FDMA Frequency Division Multiple Access

FF Feedforward

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

HPA High Power Amplifier

IIR Infinite Impulse Response

IL Implementation Loss

ISI Inter Symbol Interference

LPF Low Pass Filter

LUT Look-Up Table

M&M Mueller and Muller

MAP Maximum A Posteriori Probability

MCD Multicarrier Demodulation

ML Maximum Likelihood

MLE Maximum Likelihood Estimation

NCO Numerical Controlled Oscillator

NDA Non-Data Aided

OBP On-Board Processing

PAM Pulse Amplitude Modulation

PDF Probability Density Function

Pe Probability of BER

QPSK Quadrature Phase Shift Keying

RF Radio Frequency

ROM Read Only Memory

RRC Root Raised Cosine

SCPC Single Channel Per Carrier

SNR Signal to Noise Ratio

SRRC Square Root Raised Cosine

STR Symbol Timing Recovery

TDM Time Division Multiplex

TDMA Time Division Multiple Access

TED Timing Error Detector

TRC Timing Recovery Circuit

TWTA Traveling Wave Tube Amplifier

VCO Voltage Controlled Oscillator

VLSI Very Large Scale Integration

## Chapter 1

## Introduction

#### 1.1 Background

In this thesis various schemes for estimating the timing offset of a group demodulator, a representative subsystem which simultaneously demultiplexes 8 QPSK channels, each with a complex data rate of 0.772 M-samples per second is considered. Also, a technique which corrects the timing offset using an Adaptive Rate Conversion (ARC) filter is presented.

In an on-board processing (OBP) system, frequency-division multiple access using single channel per carrier (SCPC-FDMA) on the uplink and time-division multiplex (TDM) on the downlink is assumed. With SCPC-FDMA, each earth station in the satellite network transmits a radio frequency (RF) carrier to the satellite transponder. Each uplink carrier occupies a specific frequency band location within the uplink bandwidth. In addition, the data rate is typically constant, for all channels, so that each station has the same bandwidth and the network is uniform. With TDMA systems, each station transmits one data frame at a time which is globally synchronized in time to avoid collision. For both FDMA and TDMA the uplink signal is amplified by the satellite's traveling wave tube amplifier (TWTA) and retransmitted in the downlink beam. As compared to the TDMA method,

the SCPC-FDMA method on the uplink reduces the cost and complexity of the earth terminals considerably, because global synchronization is not needed. However, amplification of the multiple carriers by the TWTA operated at saturation on the downlink produces inter-modulation distortion, which significantly degrades individual channel performance. On the other hand, with TDMA since there is only one carrier at a time, the inter-modulation distortion is eliminated [1].

The SCPC-FDMA/TDM link combines the advantages of SCPC-FDMA on the uplink and benefits of a TDMA on the downlink. Thus, this method reduces the cost and complexity of the earth stations and allows the satellite amplifier to operate at saturation for maximum efficiency. It enables high power amplifier (HPA) power and antenna size at the terminal to be reduced [2]. Also, splitting of the satellite link into two distinct sections prevents noise and other interference to be accumulated and transferred from the uplink to the downlink, which improves performance.

The above discussions indicate the benefit of using FDMA on the uplink and TDMA on the downlink in a satellite communications system. The FDMA/TDMA configuration necessitates on-board signal regeneration in which the FDMA uplinks are frequency demultiplexed and then the individual carriers demodulated, routed and recombined into TDM signals for retransmission.

The digital signal processing (DSP) operation that simultaneously downconverts multiple FDM signals to baseband is referred to as a multicarrier demodulation and the device which accomplishes this is called a multicarrier demodulator (MCD). Multicarrier demodulation includes frequency demultiplexing of the FDM carriers and subsequent demodulation of each carrier to recover the individual channel data. Figure 1.1 depicts the block diagram for a group demodulator. It consists of two main blocks: a digital group demultiplexer and a bank of channel processors. The digital group demultiplexer separates out the individual channels in the received signal. The function of the channel processors is to regenerate each signal by performing timing and carrier recovery and making decisions on the QPSK signals.

Figure 1.1: Block diagram of group demodulator

Several approaches to demodulation (carrier and timing recovery) have been proposed. In this thesis various techniques for estimating the timing offset have been considered. The one most suitable for on-board processing has been studied and further improvement has been proposed to reduce the acquisition time.

#### 1.2 Contribution of Thesis

The main objective of this thesis is to propose new techniques for symbol timing recovery in on-board processing satellites. The key feature of the work is the development of symbol timing recovery methods which provide fast acquisition and considerable amount of jitter for continuous mode based communications systems. The major contributions of this thesis include the following:

- A review of the literature on symbol timing recovery is performed to highlight current areas of interest, namely symbol timing estimation algorithms for continuous mode communication systems.

- Performance evaluation of few timing estimation algorithms. Non-Data Aided

- Feed-forward and Non-Decision Directed Feedback estimators are two schemes

which have been simulated and performance evaluated using computer simulations.

- Proposed two new techniques for symbol timing recovery, which are based on Decision-Directed feedback approach.

- Evaluated the performance of the proposed technique using computer simulations and compared the performance to the existing schemes.

- A new study is made to replace the interpolating filter with matched filter on the receiver side, which reduces the hardware cost of the system.

- Made a comparison of various techniques for symbol timing recovery in feedback configuration in terms of performance and hardware cost.

- Finally, hardware structures are proposed for the implementation of the new algorithms and estimators.

## 1.3 Organization of Thesis

This thesis is organized in the following manner. Chapter 2 provides an overview of clock synchronization issues in satellite receivers. The effect of imperfect timing recovery on the system performance is presented. Various schemes for estimating and correcting timing offset are surveyed. Non-data aided feed-forward estimator for symbol synchronization is presented in chapter 3. Its performance is also evaluated. In chapter 4, feedback timing recovery circuits are presented. Chapter 5 gives the description of proposed symbol synchronization algorithms. Performance of the proposed scheme in terms of acquisition time, tracking (variance of estimate), bit error rate (BER) etc. are presented. Chapter 6 summarizes the thesis and provides recommendations for further research in this area.

## Chapter 2

## Clock Synchronization Issues in Satellite Digital Receivers

#### 2.1 Introduction

Satellite communications continue to undergo changes not only from advancing technology, but also from new service and regulatory activities. Therefore, advanced digital satellite communication systems using efficient modulation techniques and satellites with on-board signal processing capabilities are required. In particular, the on-board signal processing offers several advantages to satellite communication systems; an interesting feature is the separation of the uplinks and downlinks which permits their distinct and independent optimization. For mobile communication services, the use of uplink FDMA techniques with the inherent low-cost earth stations, and downlink TDMA techniques that can fully exploit the satellite transponder output power without inter-modulation, is a very interesting and attractive solution. The feasibility of this approach, however, depends on an efficient means of translating between the two formats on board the satellite. The complexity of the on-board system (including the VLSI design) and power consumption are obviously of primary concern. The on-board processing system receives an input FDMA signal and

supplies an output TDM signal; therefore it must be able to separate each radio channel, perform demodulation and correctly switch to the appropriate downlink channel. In this work, the concentration is on demodulation process with emphasis on clock synchronization circuit.

In this chapter, four major topics will be described. In Section 2.2, the importance and need for symbol synchronization will be discussed. Section 2.3 will the deal with effect of timing offset on the probability of error (Pe). It will be shown how the timing offset degrades the bit error rate. Also the effect of various parameters on the system performance will be presented. Section 2.4 deals with various symbol timing estimators which include both feed-forward and feedback estimators. In Section 2.5, various techniques for timing estimation/correction will be explained. This section addresses both types of receivers: synchronous and non-synchronous sampling receivers. In Section 2.6, a comparison is made between Non-Data Aided and Decision Directed schemes.

## 2.2 Importance and need for Synchronization

Synchronization is a critical function in Digital Communications; its failures may have catastrophic effects on the transmission system performance. In digital communications there is a hierarchy of synchronization problems to be considered. First, assuming a carrier-type system is involved, there is the problem of carrier synchronization which concerns the generation of a reference carrier with a phase closely matching that of the data signal. This reference carrier is used at the data receiver to perform a coherent demodulation operation, creating a baseband signal. Next comes the problem of synchronizing a receiver clock with the baseband data-symbol sequence. This is commonly called symbol synchronization [4].

In synchronous digital transmissions the information is conveyed by uniformly

spaced pulses and the received signal is completely known except for the data symbols and a group of variables referred to as reference parameters. Although the ultimate task of the receiver is to produce an accurate replica of the symbol sequence with no regard to reference parameters, it is only by exploiting knowledge of the latter that the detection process can properly be performed. In a baseband Pulse Amplitude Modulation (PAM) system the received waveform is first passed through a matched filter and then is sampled at the symbol rate. The optimum sampling times correspond to the maximum eye opening and are located at the "peaks" of the signal pulses. Clearly, the locations of the pulse peak must be accurately determined for reliable detection. A circuit that is able to predict such locations is called a timing synchronizer and is a vital part of any synchronous receiver [5].

Coherent demodulation is used with passband digital communications when optimum error performance is of paramount importance. This means the baseband data signal is derived making use of a local reference with same frequency and phase as the incoming carrier. This requires accurate frequency and phase measurements as phase errors introduce crosstalk between the in-phase and quadrature phase channels of the receiver and degrades the detection process. Such circuits are referred to as carrier synchronizers.

Carrier phase information is not always needed. In applications where simplicity and robustness of implementation are of more importance than achieving optimum performance, differential demodulation is an alternative to coherent detection. Differential demodulation of PSK signals is accomplished by the difference between the signal phases at two consecutive sampling times and making a decision on this difference.

From the above discussion it is evident that measuring reference parameters is a vital function in satellite communication systems. This function is called synchronization.

#### 2.2.1 Importance of Timing Estimation

Symbol Timing Recovery (STR) is a very important process in demodulation. Various options exists for the architecture of the STR process. The sampling process may take place using a feedback (FB) scheme where the signal is sampled after the matched filter. Alternatively, it may be sampled prior to, or directly after the frequency translation process. Each option has its own particular merits. Also, a feed-forward (FF) STR method could be used. This range of optional structures is discussed below. After the sample (symbol) timing has been established, phase and frequency correction is made. Again, a range of structures exists for implementation including both FF and FB schemes. If a feed-forward Carrier Recovery (CR) scheme is used, such as that described by Viterbi and Viterbi [6], then symbol timing must be established prior to the CR function. Consequently the STR process must operate on samples which have unknown carrier phase and frequency offset. In this situation the STR scheme chosen must be phase independent. Alternatively, a feedback CR scheme may be employed. If phase lock is achieved prior to the STR function a phase dependent STR scheme may be employed. The final process is that of data detection, where the received, matched filtered, and synchronized signal samples are produced to determine the values of the transmitted data symbols.

Without the STR function the phase and frequency at which the signal is sampled will generally be different to that optimum sampling. This situation will incur more symbol decision errors and potentially lost symbols due to cycle slipping. The task of the STR function is to sample the signal at or near the optimum location for all received symbols. This will ensure that the samples passed to the demodulation processes, including data detection, have the maximum available Signal to Noise Ratio (SNR) and hence a Bit Error Rate (BER) as close as possible to optimum. The increase in SNR above the minimum required to obtain a particular BER, is known as Implementation loss (IL). Considering that modern receivers are generally

required to have an implementation loss less than 1dB, the implementation associated with the symbol timing recovery function is often required to be less than 0.1dB.

## 2.2.2 Overview of existing schemes and strategies

Digital transmission of a signal can be classified into two basic categories; continuous-time and burst-mode transmission. A continuous time signal may be defined as one in which the signal is continuously transmitted/received i.e., the communication link operates from days to years without interruption. In contrast, burst mode signals are used in schemes designed to use short packets of information. Packet size may range from very short(for e.g., 32 or 64 symbols) to very large(for e.g., several thousands symbols). Typically, burst mode signals are used in TDMA and slow frequency hopping communications systems.

The information (i.e., signal) is transmitted in discrete form. The information coded using binary representation offers many advantages, such as higher bandwidth efficiency. Initially, timing synchronization information was transmitted on a separate channel. Golomb et al [7], in 1963 presented research work showing that optimum efficiency(that is the highest data throughput per used bandwidth) could be attained if all the transmitted energy was denoted to the transmission of the data signals, instead of splitting it between a data and a synchronization channel.

First symbol timing recovery methods extracted timing information from a discrete frequency component at the symbol rate using feed-forward structures. The frequency component is generally produced by feeding the baseband signal through a non-linearity and then filtering the unwanted frequency components using a bandpass filter (BPF) [8]. The output of the bandpass filter is a discrete component, corresponding to a sine wave, at a symbol rate. As the received signal is usually corrupted by the Additive White Gaussian Noise (AWGN), the use of the non-linearity introduces additional noise term due to the interaction of the signal with itself, and

with the input noise. Some constant fractional symbol delay is usually required after zero crossing edge to ensure that it is aligned with the symbol center. The delay is necessary because the previous processing functions introduce a delay which is not usually a multiple of the symbol period. The performance of such systems is highly dependent on the input SNR as the non-linearity produces unwanted signal components which increase the jitter of the timing estimate significantly at low SNRs. Additionally, this method has until recently been confined to analog implementation and hence has problems due to drift in the analog components in filtering, amplification and limiting stages.

In feedback systems, the received signal is processed by a timing phase detector which determines whether the current sample timing phase is advanced or retarded with respect to the symbol center. The output of the timing phase detector, that is the timing error, is then filtered to reduce the variance of the timing error. The filter usually incorporates an integrator which is used in the loop-back mode. The output of the loop-filter controls the frequency and phase of the sampling oscillator which is usually a Voltage Controlled Oscillator (VCO) or Numerically Controlled Oscillator (NCO) [4, 9, 10].

Earlier feedback symbol timing recovery loops were constructed using analog techniques with the familiar loop filter and VCOs. With the introduction of digital semiconductor devices, and the matured digital phase locked loop techniques, these methods are now implemented in a range of forms including hybrid analog/digital or fully digital hardware. Considering the disadvantages of analog implementations, and the increasing power of Digital Signal Processing (DSP) technologies, both feedforward and feedback methods are increasingly being implemented in fully digital forms.

Synchronization techniques are generally modeled using Maximum Likelihood Estimation (MLE) and Maximum A Posteriori Probability (MAP) [10] models. Techniques for analysis of the performance of STR schemes continued to advance

through the seventies. Many new techniques were published by Franks and Bubrouski [8] and by Mueller and Muller [9]. A good tutorial paper on Carrier and Bit synchronization was presented by Franks [4] in the special issue of IEEE transactions on communications on synchronization (1980).

The 80's saw a dawn of relatively powerful DSP integrated circuits, that allowed the implementation of systems completely digital. Gardner [11] proposed a new timing error detector for sampled data receivers. A technique for digitally implemented data receivers was proposed by Farhang-Boroujeny [12] in 1990. Lee et al [13], proposed a new STR algorithm based on the spectral line method and has better performance in narrowband.

Continuous signal based systems generally tend to use feedback STR methods. This is due to the tracking ability of the timing phase locked loop structure. Feedforward methods can also be used for STR in continuous systems, however, generally these schemes do not have the tracking ability of feedback methods and have higher jitter when the SNR is poor.

STR schemes using the feed-forward methodology have also been investigated. Basically the techniques available for feed-forward configuration are used for burst-mode transmission. The use of a burst mode transmission scheme increases the complexity of the demodulator relative to continuous mode systems. Such as, the accuracy of timing estimate depends on the burst length (i.e., number of symbols). There is a design constraint on the burst length, which limits the performance of the system. Shorter packets have high jitter, which results in increased BER. Burst-mode systems require fast acquisition so that the preamble length is reduced and hence maximize the user data throughput. Guard times are required at the beginning and at the end of the packet transmission to avoid packets overlapping with adjacent time slots.

The packets are generally constructed with a preamble of defined data. The preamble allows the STR scheme to ensure that the timing phase errors does not

exceed a predefined value with a specific probability. The use of preambles has two major disadvantages, namely: it reduces the available throughput of the system by introducing overheads and a trade-off is required between the acquisition time and steady state performance of the symbol timing and carrier phase.

Various techniques for estimating the timing phase in the burst-mode demodulators have been addressed in the past two decades. Meyr and Oerder [19] presented a technique for estimating the timing phase based on the FFT. It is the digital counterpart of the well-known continuous-time filter and square time recovery [8]. Thus keeping in mind the excessive computation power required by the STR structures in the feed-forward mode. Also the signal transmission has FDMA structure, techniques using feedback structure were preferred. This thesis proposed a number of new methods and solutions for continuous mode timing recovery and determines their performance through computer simulations and is shown that the proposed technique has better performance when compared to existing techniques.

# 2.3 The Effect of Timing Offset on System Performance

In this section, the effect of timing offset on the system performance is presented. Filtering is an importance aspect in digital transmission, the reason for selecting transmitter and receiver filter is given. And also the effect of Matched filtering is explained. In the next subsection, various parameters effecting the probability of BER are explained.

#### 2.3.1 Effects of Filtering in Digital Transmission

Filtering is an integral part of both, modulating and demodulating function. The obvious purpose of the transmit filter is to limit energy outside of a chosen bandwidth,

hence allowing the signal to be channelized and to provide a means of controlling the bandwidth efficiency. The purpose of the receive filter is to stop unwanted energy, both from adjacent channels and out of band noise, from entering the receiver.

The combination of the transmit and receive filter plays an important role in determining system performance, in terms of bit error rate, by affecting the received signal to noise ratio and the level of Inter-Symbol Interference (ISI).

It is well known [14, 15] that the matched filter receiver is the optimum solution for maximizing the received signal to noise ratio. The received filter is named matched filter, the reason being it is a time reversal and delayed version of the received pulse waveform.

The excess bandwidth factor (i.e., alpha) can be between 0 and 1, but commonly this will be 0.3 to 0.5 for 30% to 50% excess bandwidth. A class of filter called raised cosine filter is discussed in the following section.

#### 2.3.1.1 Raised Cosine Pulse Shaping

In order to obtain the level of performance for the matched filter demodulation, the ISI must be zero. Raised cosine pulses belong to such category [14, 16]. They contribute zero energy at symbol spaced sampling instants outside their own symbol epoch. These class of pulses satisfy the Nyquist pulse shaping criterion.

The frequency domain description of the Raised cosine family of pulses is given below:

$$H(f) = \begin{cases} Ts & for \quad 0 \le |f| \le \frac{1-\alpha}{2Ts} \\ \frac{Ts}{2} \left[ 1 + \cos\left(\frac{\pi Ts}{\alpha} \left[ |f| - \frac{1-\alpha}{2Ts} \right] \right) \right] & for \quad \frac{1-\alpha}{2Ts} \le |f| \le \frac{1+\alpha}{2Ts} \\ 0 & for \quad \frac{1+\alpha}{2Ts} \le |f| \end{cases}$$

(2.1)

where  $0 \le \alpha \le 1$  is the roll-off factor or excess-bandwidth factor which shapes the spectrum as illustrated in Figure 2.1. Note that H(f) is strictly band-limited.

Figure 2.1: Raised Cosine Filter Frequency Response

This, of course, implies that the impulse response h(t) is not time limited and extends to  $t = \infty$ . The impulse response is given by,

$$h(t) = \frac{\left[\frac{\sin\left(\pi \frac{t}{T_s}\right)}{\pi \frac{t}{T_s}}\right] \cos\left(\frac{\pi \alpha t}{T_s}\right)}{1 - \left(2\alpha \frac{t}{T_s}\right)^2}$$

(2.2)

It should be noted that these pulses are non-causal i.e.,

$$h(t) \neq 0; t < 0$$

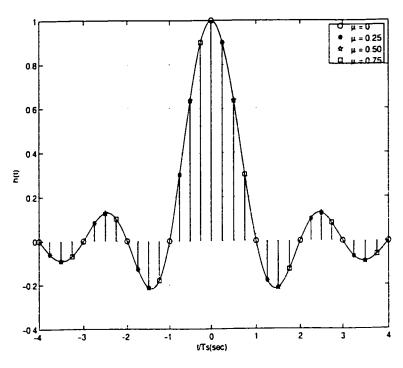

and is plotted in Figure 2.2. Note that the impulse response is exactly zero for integer multiples of  $T_s$ . Thus, when h(t) is used as a pulse shape for signaling at a rate  $1/T_s$  symbols/sec, intersymbol interference is not a problem. The RC pulse belongs to a general class of signals which satisfy the Nyquist Criterion for no ISI.

The choice of small  $\alpha$  corresponds to highest bandwidth efficiency, but makes the filtering function difficult to implement as the pulses decay slowly in time from

Figure 2.2: Raised Cosine Filter Impulse Response

the symbol center, as it is evident from Figure 2.2. It also proves that symbol synchronization is aided by larger value of excess bandwidth factor (this is proved in later chapters). In practise, an  $\alpha$  of 0.3 to 0.4 is used for satellite transmission as a compromise between implementation complexity, bandwidth efficiency and synchronization performance.

#### 2.3.1.2 Root Raised Cosine Pulse Shaping

In most communications applications, the RC pulse shape is divided into two parts, one for the transmitter and the other for the receiver. In this case, each side has what is called a *Square Root Raised Cosine Filter* forming a matched filter pair. The frequency response of this filter is the square root of Equation 2.1, while the impulse response is given by

Figure 2.3: Probability of Bit Error for QPSK System

$$h(t) = \frac{4\alpha}{\pi\sqrt{T_s}} \frac{\cos\left((1+\alpha)\pi\frac{t}{T_s}\right) + \frac{\sin\left((1-\alpha)\pi\frac{t}{T_s}\right)}{4\alpha\frac{t}{T_s}}}{1 - \left(4\alpha\frac{t}{T_s}\right)^2}$$

(2.3)

## 2.3.2 Probability of Error

Bit error rate is a measure of number of bits in error over a certain number of transmitted bits at a particular SNR. A typical BER for QPSK modulated system is shown in Figure 2.3.

The probability of bit error of the coherent QPSK receiver [15] is,

$$P_{E,QPSK} = \frac{1}{2} erfc \left( \sqrt{\frac{E_b}{N_o}} \right)$$

where

$$erfc(y) = \frac{2}{\sqrt{\pi}} \int_{y}^{\infty} \exp(-z^{2}) dz$$

for  $y > 0$

Figure 2.3 illustrates the theoretical limit on BER presuming a perfect synchronization. Synchronization mismatch causes this curve to deviate from its theoretical

limit, as will be illustrated.

The fundamental feature of a practical Timing Recovery Circuit (TRC) is that the separation between adjacent pulses is not exactly constant but varies slowly in a random manner. The variations are referred to as timing jitter and are a consequence of the random nature of the waveform at the TRC input. The average error probability is obtained by averaging  $P(e \mid \widehat{\tau})$  over  $\widehat{\tau}$ .

$$P(e) = \int_{-\infty}^{\infty} P(e \mid \widehat{\tau}) p(\widehat{\tau}) d\widehat{\tau}$$

(2.4)

where  $P(e \mid \hat{\tau})$  is the detector error probability on a fixed sampling epoch  $\hat{\tau}$ .

The derivation of the probability of error, Pe, of an optimum demodulator is generally derived assuming perfect STR (and CR).

The effect of static timing offset on the probability of error is shown in Figures 2.4 to 2.6 for a range of signal bandwidths. Figure 2.5 shows that for a channel roll-off factor,  $\alpha$ , of 0.4 and a BER of 10e-4, timing offsets of 5% and 10% will result in implementation losses of 0.33 and 0.80 dB respectively. A value of 0.4 is used for  $\alpha$  throughout this thesis as it provides a good trade off between matched filter implementation complexity and channel bandwidth and as such is commonly used. Where the channel bandwidth has distinct effects, results are given for a range of values of  $\alpha$ .

Figure 2.7 may be used to determine the standard deviation required to obtain a specified implementation loss at a nominal value of signal to noise ratio. However, if the signal to noise ratio varies, so will the timing estimate variance, and hence the implementation loss will also change. Consequently this method is only useful for constant SNRs. If a variable SNR is likely, or the effect of the timing offset variance is required over a range of SNRs, the effect of the SNR on the timing estimate variance can be taken into account. Effectively, this requires making the timing estimate pdf dependent on the SNR.

Figure 2.4: BER as a function of timing offset,  $\tau$ , for RC channel with  $\alpha$  = 0

Figure 2.5: BER as a function of timing offset,  $\tau$ , for RC channel with  $\alpha$  = 0.4

Figure 2.6: BER as a function of timing offset,  $\tau$ , for RC channel with  $\alpha = 1.0$

Figure 2.7: BER as a function of standard deviation of timing offset as parameter

Figure 2.8: Feedback Configuration

An interesting feature of the upper curves in Figures 2.4-2.7 is that they exhibit an irreducible error as  $E_b/N_o$  increases. The explanation is that timing errors generate intersymbol interference (ISI) which, in turn, produce decision errors even in the absence of noise [5].

# 2.4 Symbol Timing Estimators

Timing recovery basically consists of two distinct operations: (1) Estimation of the timing phase and (2) Application of the estimate to the sampling process. The former is referred to as timing measurement and the latter as timing correction (or adjustment). Timing correction serves to provide the decision with signal samples with minimum inter symbol interference [5].

Four types of algorithms exists for timing estimation and correction. They are:

- Feedback (FB) or Feed-forward (FF) structures,

- FB: correction before the detection of the error parameter.

- FF: correction after the estimation of the error parameter.

- Decision directed (DD) or Non-Data Aided (NDA) structures,

Figure 2.9: Feed-forward Configuration

Figure 2.10: Synchronous Sampling

- DD: use of data decisions to perform the detection.

- NDA: no use of data decisions to perform the detection.

In full digital implementation, the receiver clock is not synchronized to the transmitter clock. Figure 2.8 and 2.9 illustrate the feedback and feed-forward schemes.

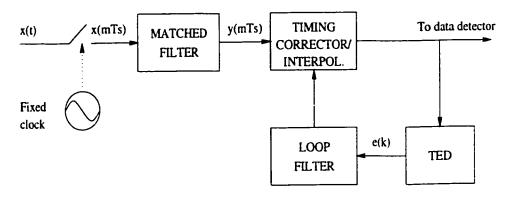

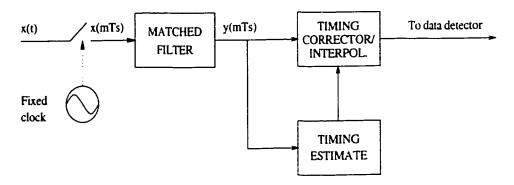

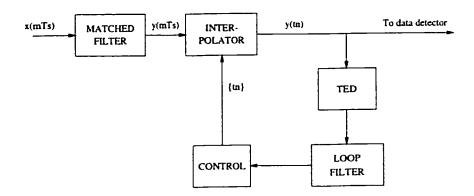

In feedback configuration, the timing corrector feeds a timing error detector (TED), whose purpose is to generate an error signal e(k) proportional to the difference between timing phase and it's estimate. The error signal is then used to recursively update the timing estimates. Feed-forward timing recovery configuration is shown in Figure 2.9.

The next prominent issue in synchronization is synchronized and non-synchronized sampling. In a fully digital implementation, sampling is not locked to the incoming

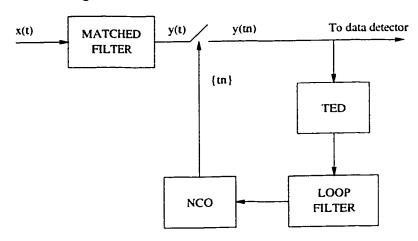

Figure 2.11: Non-synchronous Sampling

pulses. This is referred to as a non-synchronous sampling (Figure 2.11). On the other hand, sampling can be made synchronous by exploiting some error signal to adjust the timing phase of a numerically controlled oscillator (NCO) as shown in Figure 2.10.

#### 2.4.1 Feed-Forward Estimators

In this section various methods of estimating the symbol timing using a feed-forward approach are discussed. Traditionally, feed-forward methods have been based on non-linearity and filter schemes which extract the phase of a discrete frequency component, generated by the non-linearity at the symbol rate. The timing estimate obtained is thus used to correct the timing offset. This is done using the interpolation technique, which is addressed in Section 2.5.

In Section 2.4.1.1, a Non-Data Aided (NDA) Maximum Likelihood timing error estimator is explained. In the following Section (2.4.1.2), a scheme based on spectral line estimation is illustrated.

#### 2.4.1.1 NDA-ML based Algorithm

Let the transmitted symbol sequence be  $\{a_n\}$ , n=1, 2, ... In general, the  $a_n$ 's are complex numbers depending on the modulation type used such as QPSK. Then the

transmitted baseband waveform will take the form

$$x(t) = \sum_{n=-\infty}^{\infty} a_n g(t - nT)$$

(2.5)

where T and g(t) denote the symbol interval and the pulse shaping waveform, respectively. The received noisy signal can be written as

$$z(t) = x(t;\tau) + n(t) \tag{2.6}$$

where

$$x(t;\tau) = \sum_{n=-\infty}^{\infty} a_n g(t - nt - \tau)$$

(2.7)

and n(t) denotes the added white Gaussian noise with a double-sided spectral density of  $N_o$  W/Hz. And  $\tau$  is the timing offset due to propagation delays and other channel distortions.

The Maximum Likelihood (ML) estimate of the timing parameter  $\hat{\tau}$  is obtained by maximizing the apriori likelihood function  $L(\tau)$ , given by

$$L(\tau) = p(z(t)/\hat{\tau})$$

,  $z(t) \in T_o$  (2.8)

where  $T_o$  is the time interval over which the received signal z(t) is observed and is assumed to be much longer compared to the symbol interval T. The resulting likelihood function, with argument  $\hat{\tau}$  which can be regarded as a trial estimate of the parameter, is given by [8, 17, 18]

$$L(\tau) = \exp\left\{-\frac{1}{2N_o} \int_{T_o} [z(t) - x(t, \tau)]^2 dt\right\}$$

(2.9)

where  $N_o$  is used to denote the two-sided power spectral density of the noise (i.e., the variance of each of the quadrature Gaussian noise components with zero mean assumed).

The ML estimate is the value of  $\tau$  which minimizes the integral in Equation 2.9. This integral expresses the signal space distance between the received signal, z(t) and reference signal  $x(t,\tau)$  defined on the interval  $T_o$  [8]. Expanding the binomial term in Equation 2.9, we see that

$$\Lambda(\widehat{\tau}) = \ln L(\widehat{\tau}) = \frac{1}{N_o} \int_{T_o} z(t) x(t, \widehat{\tau}) dt + constant$$

(2.10)

since  $z^2(t)$  is independent of  $\widehat{\tau}$ , and the  $x^2(t,\widehat{\tau})$  term is simply the power of the transmitted signal and hence for signals with equal energy symbols its integral is  $\widehat{\tau}$ . Hence  $z^2(t)$  and  $x^2(t,\widehat{\tau})$  terms can be considered as constants independent of  $\tau$  and consequently the most likely timing offset  $\widehat{\tau}$  is the value which maximizes Equation 2.10, that is

$$\widehat{\tau} = \arg\max_{\widehat{\tau}} \left\{ \Lambda(\widehat{\tau}) \right\} = \arg\max \left\{ \frac{1}{N_o} \int_{T_o} z(t) x(t, \widehat{\tau}) dt \right\}$$

(2.11)

Note that the constant term is not included in above equation, as it has no impact on the maximization process.

The dependence of the likelihood function (Equation 2.11) on the data symbol valued may be removed by averaging the likelihood function over the data values [8, 18]. This is referred to as the non-data aided approach. Consider Equation 2.9,

$$L(\tau) \propto \exp\left\{-\frac{1}{2N_o} \int_{T_o} [z(t) - x(t, \tau)]^2 dt\right\}$$

(2.12)

Since the integral of the  $z^2(t)$  and  $x^2(t, \hat{\tau})$  terms is independent of  $\hat{\tau}$ , as described previously. Equation 2.12 can be rewritten considering the cross correlation terms only,

$$L(\widehat{\tau}) \propto \exp\left[\frac{1}{N_o} \int_{T_o} z(t) x(t, \widehat{\tau}) dt\right]$$

(2.13)

Substituting for z(t) from Equations 2.6 and 2.7, this expression is simplified after the necessary complex algebra and discarding constant multiplication factor involving the received signal z(t), is given by

$$L(\hat{\tau}) \propto \exp\left[\frac{1}{N_o} \sum_{n=0}^{L-1} a_n q_n(\hat{\tau})\right]$$

(2.14)

$q_n(t)$  is the output of the receiver matched filter and is given by

$$q_n(t) = \int_{-\infty}^{\infty} z(t)g(t - nT - \tau)dt$$

(2.15)

and L denotes the number of symbols that span the observation time interval  $T_o$ .

Equation 2.14 may be written as the product of L factors where each factor depends only on the random variable  $a_n$ , namely;

$$L(\widehat{\tau}) \propto \prod_{n=0}^{L-1} \exp\left(\frac{1}{N_o} a_n q_n(\widehat{\tau})\right)$$

(2.16)

In the case of binary PAM, the data terms can have the values +A and -A. If the data values are equally probable then to average (Equation 2.16) over the data values, the sum of the exponential terms is taken with respect to the data values. [8, 15].

$$L(\widehat{\tau}) \propto \prod_{n=0}^{L-1} \left( \frac{1}{2} \exp\left(\frac{A}{N_o} q_n(\widehat{\tau})\right) + \frac{1}{2} \exp\left(\frac{-A}{N_o} q_n(\widehat{\tau})\right) \right)$$

(2.17)

Taking natural logarithms, Equation 2.17 is given by

$$\Lambda(\hat{\tau}) \propto \sum_{n=0}^{L-1} \ln \cosh \left( \frac{A}{N_o} q_n(\hat{\tau}) \right)$$

(2.18)

As  $\ln \cosh(x)$  function is complex to implement, it is often approximated to  $x^2$  for small values of x and absolute value |x| when the argument x is larger.

#### 2.4.1.2 NDA-FFT (Oerder & Meyer) Algorithm

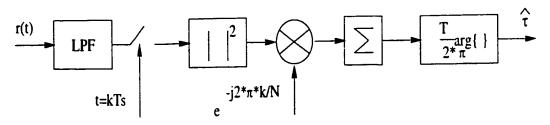

In the previous section (2.4.1.1), the unknown timing parameter is obtained by a maximum search. It is interesting to know that this maximum search could be circumvent. A commonly used *single shot* symbol timing estimator is the DFT estimator [19]. It is defined as

$$\widehat{\tau} = \frac{T_s}{2\pi} \arctan \left[ \frac{\sum_{n=0}^{LK-1} x^2 (nT_s - \tau) \sin(\frac{2\pi n}{K})}{\sum_{n=0}^{LK-1} x^2 (nT_s - \tau) \cos(\frac{2\pi n}{K})} \right]$$

(2.19)

where atan(.) returns a value over  $(-\pi, \pi)$ . The signal samples are squared to eliminate data dependency and generate a discrete frequency component at the symbol rate. At least four samples per symbol are required to generate the discrete frequency component at the symbol rate [19]. The phase of the discrete frequency component at the symbol rate is a measure of the timing offset from optimum and hence an estimate of the timing offset may be obtained by taking the DFT, of the squared signal, at the symbol rate. This results in the estimator (Equation 2.19) which is known as DFT-NDA. Derivation of this estimator and performance will be illustrated in chapter 3.

The tone filtering algorithm is seen to provide excellent overall performance in the estimation of the symbol timing offset as long as the timing offset is within  $\pm 45\%$  of the symbol time [18]. Its performance with this range and effectiveness in low signal to noise ratio is seen to be slightly better than the best of the ML-based algorithms. The ML-based techniques break after  $\pm 25\%$  of the symbol time. The tone filtering approach would in fact work well even at lower signal to noise ratios due to the processing gain of the DFT, which is a correlation-type computation in which the noise is decorrelated.

#### 2.4.2 Feedback Estimators

In the following sections, symbol timing recovery using feedback estimators is presented. Various techniques suitable for this configuration were studied and the one suitable from performance and implementation complexity point of view were chosen and analyzed.

In Section 2.4.2.1, the algorithm proposed by Mueller and Muller [9] is explained. Block diagram explaining its mode of operation is also presented. Second in the series is the timing error detector proposed by Floyd M. Gardner [11]. The one best suitable for this application is further investigated in chapter 5.

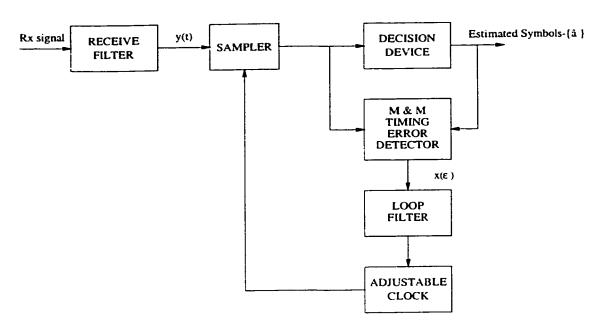

Figure 2.12: Block diagram of receiver with Mueller and Muller Synchronizer

#### 2.4.2.1 The Mueller and Muller (M & M) Synchronizer

The Mueller & Muller synchronizer [9] is a discrete-time error tracking synchronizer, which derives an indication about the delay difference between the received signal and the sampling clock from samples of the receive filter output signal  $y(t;\varepsilon)$  taken at the channel symbol rate 1/T. The M & M synchronizer is represented by the block diagram shown in Figure 2.12.

The timing error detector produces a sequence  $x_k(\varepsilon,\widehat{\varepsilon})$ , which is determined by

$$x_{k}(\varepsilon,\widehat{\varepsilon}) = \widehat{a}_{k-1}y(kT + \widehat{\varepsilon}T;\varepsilon) - \widehat{a}_{k}y(kT - T + \widehat{\varepsilon}T;\varepsilon)$$

(2.20)

where  $\widehat{a}_m$  denotes the receiver's decision about the  $m^{th}$  channel symbol  $a_m$ . As the timing error detector makes use of the receiver's decision, the M & M synchronizer is decision-directed.

The PAM signal  $y(t;\varepsilon)$  at the input of the synchronizer is given by

$$y(t;\varepsilon) = \sum_{m} a_{m}g(t - mT - \varepsilon T) + n(t)$$

(2.21)

where  $\{a_m\}$  is a stationary sequence of not necessarily binary data symbols, g(t) is the baseband pulse and n(t) is stationary noise.

The adjustment clock samples the signal  $y(t;\varepsilon)$  at the instants  $t_k$ , given by

$$t_k = kT + \widehat{\varepsilon}T \tag{2.22}$$

The resulting samples are denoted by  $y_k(\varepsilon, \hat{\varepsilon})$ ,

$$y_k(\varepsilon,\widehat{\varepsilon}) = y(kT + \widehat{\varepsilon}T;\varepsilon)$$

(2.23)

These samples are combined with the receiver's decision  $\{\widehat{a}_m\}$ , to form the following timing error detector output samples:

$$x_k(\varepsilon,\widehat{\varepsilon}) = \widehat{a}_{k-1}y_k(\varepsilon,\widehat{\varepsilon}) - \widehat{a}_k y_{k-1}(\varepsilon,\widehat{\varepsilon})$$

(2.24)

The Mueller and Muller synchronizer uses decision feedback to produce a timing error detector output. In the absence of data transitions, the useful timing error detector output equals zero; therefore, the transmissions of long strings of identical symbols must be avoided. The loop noise consists of two components: a component due to additive noise and a self-noise component due to the tails of the baseband pulse g(t). Self noise component is eliminated for a zero, steady-state timing error  $e_s$  when g(t) is a (time-shifted) Nyquist pulse, satisfying [20]

$$g(mT + \overline{\tau}) = 0 \quad for \quad m \neq 0 \tag{2.25}$$

where  $\bar{\tau}$  is defined by

$$g(T + \overline{\tau}) = g(-T + \overline{\tau}) \tag{2.26}$$

when this condition is fulfilled and  $e_s = 0$ , only additive noise contributes to the timing error detector. When this condition is fulfilled but  $e_s \neq 0$ , self-noise is present at the timing error detector output, and its contribution to the timing error variance is proportional to the normalized loop bandwidth  $(B_LT)$  [20].

#### 2.4.2.2 Non Decision-Directed Timing Error Detector

A second type of algorithm in the feedback systems explored was, the non-decision directed timing error detector by Floyd M. Gardner [11]. Compared to M & M algorithm, this timing error detector requires two samples per symbol to output a timing error signal. Gardner's algorithm is well suited for feedback systems. Gardner's detector needs only two samples of the signal for each data symbol. Moreover, one of the two samples serves as *symbol strobe*, i.e., the sample on which the symbol decision is made, while the other is a *mid-way* sample between two strobe samples. This algorithm is not decision directed, unlike M & M [9].

Gardner's detector is further studied and analyzed in chapter 3. A decision-directed version of this timing error detector proposed by Takahata et al [3] is also presented.

# 2.5 Techniques for Timing Correction/Adjustment

Timing correction serves to provide the decision device with signal samples (strobes) with minimum intersymbol interference. In synchronous analog or hybrid systems, timing adjustment is accomplished by shifting phase (delay) of a continuous timing wave. In asynchronous sampling systems, some other method of timing correction is needed. In digital receivers, the incoming signal is asynchronously sampled. That is, the sampling is not locked to the incoming pulses. In this section various methods for timing adjustment in synchronous and non-synchronous systems are studied.

#### 2.5.1 NCO Based Hybrid Method for Synchronous Sampling

Figure 2.10 shows the block diagram of a clock recovery circuit using synchronous sampling. In the sequel, first an overview of operation of a hybrid NCO is presented and then how an NCO can be used for timing adjustment in a feedback timing loop is demonstrated.

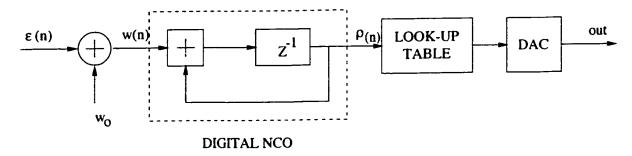

Figure 2.13: Block diagram of a hybrid NCO

#### 2.5.1.1 Hybrid NCO

The block diagram of a hybrid NCO [20] is shown in Figure 2.13. It consists of two parts: a digital loop comprising a delay and a mod1 adder (the so-called digital NCO), plus a look-up table and a digital-to-analog converter (DAC). These, together transform the NCO output into a continuous-time waveform. First let us concentrate on the digital NCO. Let w(n) be its input and  $\rho(n)$  its output. In the sequel w(n) and  $\rho(n)$  are viewed as numbers between 0 and 1. At each tick of a clock w(n) is added to  $\rho(n)$ . This results in the following difference equation:

$$\rho(n+1) = \rho(n) + w(n) \bmod 1 \tag{2.27}$$

As indicated in the Figure 2.13, w(n) is the sum of some constant  $w_o$  plus a zero-mean signal  $\varepsilon(n)$ . The constant establishes the "free running" period of the NCO whereas  $\varepsilon(n)$  allows us to change the period. To see how this comes about, suppose first that  $\varepsilon(n) = 0$ . In these conditions the NCO output will recycle every  $1/w_o$  ticks. Thus, calling  $T_c$  the clock period, the free running period will be  $T_c/w_o$ . If  $\varepsilon(n)$  is different from zero (but slowly varying in time), then the recycling period will be,

$$T_s(n) = \frac{T_c}{w_o + \epsilon(n)}$$

$$\simeq \frac{T_c}{w_o} \left[ 1 - \frac{\epsilon(n)}{w_o} \right]$$

(2.28)

assuming  $|\varepsilon(n)| \ll w_o$ .

Returning to the scheme in Figure 2.13, a look-up table maps  $\rho(n)$  into some function  $f[\rho(n)]$  which in turn, is transformed into a continuous-time function by the action of the DAC and some low-pass filter.

Now, how NCO can be used to do the timing correction is addressed; The hybrid NCO consists of a sine-table ROM, the *up-crossings* of the sine-wave (zero crossings with positive slope) are used to generate command pulses for the sampler. The goal is to steer the NCO so that its actual up-crossings occur at the exact sampling instants. Because of the presence of the hybrid NCO, the overall circuit cannot be implemented in full digital form.

#### 2.5.2 Ideal Sync Function Based Timing Correction

According to the sampling theorem [21], a bandlimited function can be reconstructed perfectly from its samples by means of a sync function, defined by

$$sinc(x) = \frac{sin(x)}{x} \tag{2.29}$$

In other words, if the sampling rate satisfies the relation

$$F_s \geq 2 \star BW(AAF)$$

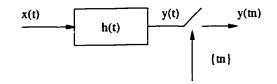

where, BW(AAF) is the bandwidth of the waveform from the anti-aliasing filter. In these conditions, the output sequel from the matched filter is sufficient to reconstruct the underlying continuous-time waveform through the interpolation formula,

$$y(t) = \sum_{m=-\infty}^{\infty} h_s(t - mT_s)y(mT_s)$$

(2.30)

where,  $h_s(t) = \frac{\sin(\pi t/T_s)}{\pi t/T_s}$

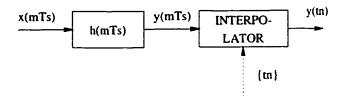

The representation of the above equation is illustrated in the Figures 2.14 and 2.15,

The Digital timing correction replaces its analog counterpart as shown in Figure 2.14. This type of ideal interpolation requires a transversal filter of infinite

Figure 2.14: Analog Implementation

Figure 2.15: Digital Implementation

length, whereas only a limited number of terms can be handled in practise. One way to realize such a filter is by truncating the ideal sync function, which will inevitably cause a certain amount of signal distortion.

The direct truncation is not usually used because of the Gibbs phenomenon which can be avoided by weighting the truncated sinc with some window function [22]. Thus instead of reconstructing the continuous-time signal by using DAC and an analog filter, a discrete interpolation filter can be used to achieve the same result.

# 2.5.3 Polynomial based Interpolators with Non-Sync Sampling

The polynomial based interpolators have achieved a lot of attention in the past decade. The linear and cubic Lagrange interpolation were first applied to the timing adjustment problem by Gardner and Lars Erup [23, 24]. Because these interpolation methods are polynomial-based they can be implemented using the Farrow structure [25].

A polynomial based interpolator calculates the filter coefficients online, given the fraction delay  $\mu$ . The underlying continuous-time impulse response  $h_a(t)$  is expressed in each interval  $T_s$  (Symbol duration) by means of a polynomial as follows,

$$h_a((\mu(l) - k)T_s) = \sum_{m=0}^{M} c_m(k)(\mu(l))^m$$

(2.31)

for k = -N/2 + 1, -N/2 + 2, ..., N/2 and  $\mu(l) \in [0, 1)$ . Here the  $c_m(k)$ 's denote the polynomial coefficients for  $h_a((\mu(l) - k)T_s)$  and M is the degree of polynomials. Thus, the polynomial-based interpolation filter can be implemented by filtering the input signal with M+1 parallel FIR filters of length N having the coefficient values of  $c_m(k)$  to obtain the output samples.

The main advantage of the Farrow structure is that the filter coefficients are fixed, and the only changeable parameter is the fractional interval  $\mu(l)$ . The second advantage to polynomial interpolation is the time resolution is determined by the number of bits used in specifying  $\mu(l)$ . An arbitrarily fine resolution can be obtained by employing a long-enough word length for  $\mu(l)$  and the filter coefficient [26, 27].

Cubic Lagrange or even Linear interpolation may be sufficient for the cases where the oversampling factor is high, e.g. >> 2. However, if the oversampling factor is small (< 2) the linear and cubic Lagrange interpolation are not good enough. The complexity of the Farrow structure can be reduced by increasing the sampling rate before the signal is passed through it.

# 2.5.4 Coefficient Memory Implementation for Interpolation Filters

Fractional delay FIR filters can also be used to implement the interpolation operation. This is done by using the so called coefficient memory implementation, where K different fractional delay FIR filters are designed having the fractional delay of  $\mu_k = \frac{k}{K}$  for k = 0, 1, ..., K - 1. Fractional delay,  $\mu_k$  is also referred to as control step size. Here K is a large integer which determines the resolution of  $\mu(l)$ . The coefficients of these filters are then stored into a memory, and, during the computation,

Figure 2.16: Impulse responses for the Fractional Delay filters and the underlying continuous-time impulse response

the desired delay can be obtained by choosing the corresponding filter coefficients from the memory [23, 24].

The impulse responses of these fractional delay filters are arranged as over-lapping polyphase components. The resulting polyphase-type impulse response then approaches the continuous-time response  $h_a(t)$  when  $K \to \infty$ . This is illustrated in Figure 2.16 for K=4. In this figure, the discrete-time impulse response consists of the over-lapping impulse response of the fractional delay FIR filters having the delay values of  $\mu=0,\ 0.25,\ 0.5$  and 0.75. The solid line illustrates the continuous-time response  $h_a(t)$  that is obtained when  $K\to\infty$ .

The approach presented in Section 2.5.3 demands multiple computations in exchange for reduced memory requirements and the need for calling coefficients from memory. But with the advent of high speed VLSI technology, the transfer of data (i.e. coefficients) is a trivial issue.

Filter operations include delays (i.e., memory), multiplications and additions.

Reductions in number of adders and multipliers is obtained at the cost of a facility needed for transfer of coefficients values from memory to the coefficient registers. One main drawback of memory based interpolators is that, at high data rates, time is a limiting factor. Only a small number of clock intervals would be available and so a large number of bits would have to be transfered in parallel.

# 2.6 Comparison of NDA and DD Schemes

- NDA implementation is substantially less complicated than DD implementation in an analog synchronizer since DD estimators require signal and/or data storage, which is usually awkward with analog circuits.

- In Digital synchronizers, NDA methods are slightly more complicated than DD methods.

- DD algorithms require less computation, for binary signals, since the NDA algorithms require multiplication of samples, whereas the DD algorithms only require 1-bit sign reversal.

- NDA can be better than DD only in one characteristic, that it might be superior in acquisition when decisions are unreliable and many are wrong.

- DD estimators give statistically better estimates than an NDA estimator in the range of  $E_b/N_o$  values of practical interest.

- NDA estimators have self-noise due to non-linearity used to remove the modulation.

- NDA estimator is very sensitive to frequency errors, thus leading to a systematic bias and to an increase in the mean square error of the reference parameters.

# Chapter 3

# Non-data Aided Feed-Forward Estimation

#### 3.1 Introduction

In the previous chapter (Section 2.4.1) two techniques for estimating the timing offset based on feed-forward structures were presented. Among the two approaches. NDA-ML and NDA-FFT, the scheme using the discrete Fourier transform has achieved a great deal of attention in the digital receivers. In this chapter analysis of the scheme are considered, performance bounds for such techniques are derived, the algorithm is simulated and compared to Cramer-Rao lower bounds and its implementation issues are discussed and presented.

#### 3.2 DFT Based STR

The DFT approach makes use of signal processing techniques for extracting a symbol rate spectral line from the received signal generated by non-linear operation [19]. Once the symbol rate spectral line is extracted, its phase scaled as will be explained below.

Figure 3.1: Timing phase estimate using the spectral line method

Referring back to Section 2.4.1 and rewriting Equation 2.6 and 2.7, we have

$$z(t) = \sum_{n = -\infty}^{\infty} a_n g_T(t - nT - \tau) + n(t)$$

(3.1)

where  $a_n$  are the symbols with mean power 1.  $g_T(t)$  is the transmission signal pulse, T is the symbol duration, n(t) is the channel noise which is assumed to be white and Gaussian with power density  $N_o$  and  $\tau$  is the slowly varying time delay. The timing estimator block diagram is shown in Figure 3.1

The symbol rate spectral line may be generated by a squaring operation on the magnitude of the baseband received signal samples from the matched filter output. The output of the matched filter  $g_R(t)$ ,  $r(t) = z(t) * g_R(t)$  is sampled at rate N/T. The sequence,

$$x(k) = \left| \sum_{n = -\infty}^{\infty} a_n g \left( \frac{kT}{N} - nT - \tau \right) + n \left( \frac{kT}{N} \right) \right|^2$$

(3.2)

represents the samples of the filtered and squared input signal and contains a spectral component at 1/T.

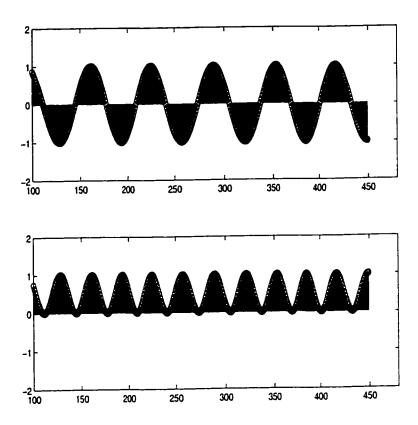

The above statement is asserted by considering a simple baseband BPSK signal. For this demo an alternative stream of  $\pm 1$  symbols is chosen. The signal is filtered using g(t), which is convolution of transmitted and received pulse shaping filter and is shown to be a Raised cosine filter. The output of the pulse shaping filter is squared and is illustrated in Figure 3.2. Once this waveform is squared, little dips are created at each rounded corners, which represent a bit transition. Thus, the squared waveform should have a fundamental harmonic at the symbol rate, with

Figure 3.2: Demonstration of TRC using spectral line