#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# An FPGA Implementation of RM-BTC Codec using Log-MAP Algorithm

Qing Li

A Thesis

in

the Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada

July 2002

©Qing Li, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Ceneda

Your file Votre référence

Our die Natre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-72910-9

#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# An FPGA Implementation of RM-BTC Codec using Log-MAP Algorithm

Qing Li

A Thesis

in

the Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada

July 2002

©Qing Li, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your ille Votre rétérance

Our ille Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-72910-9

## CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

| This is to co             | ertify that the thesis prepared                                                      |                                   |

|---------------------------|--------------------------------------------------------------------------------------|-----------------------------------|

| By:                       | Mr. Qing Li (4352475)                                                                |                                   |

| Entitled:                 | "A FPGA Implementation of RM-BTC Codec UAlgorithm"                                   | Jsing Log-MAP                     |

| and submit                | ted in partial fulfillment of the requirements fo                                    | r the degree of                   |

|                           | Master of Applied Science                                                            |                                   |

| complies v<br>standards v | vith the regulations of this University and with respect to originality and quality. | meets the accepted                |

| Signed by t               | he final examining committee:                                                        |                                   |

|                           | Dr. W-P. Zhu                                                                         | Chair                             |

|                           | Dr. C. Rozon                                                                         | Examiner, External to the Program |

|                           | () (1) - (1) /(c)<br>() r. Y. Shayan                                                 | Examiner                          |

|                           | M. R. Solymani<br>Dr. M.R. Solymani                                                  | Supervisor                        |

|                           | Dr. A.J. At-Khalili                                                                  | _ Supervisor                      |

| Approved b                | Dr. M.O. Ahmad Chair, Department of Electrical and Computer Engineering              | -                                 |

Dean, Faculty of Engineering and Computer Science

SEP 18 2002

#### **ABSTRACT**

## An FPGA Implementation of RM-BTC Codec using Log-MAP Algorithm

## Qing Li

Due to their powerful error correcting capability and superior coding gain, Turbo Codes are used in 3rd generation wireless and satellite communication systems. For these applications, efficient implementation of Turbo Codes, i. e., development of codec providing high throughput with small chip area and low power consumption is of growing importance.

In this thesis, Turbo Code using Reed-Muller code as its constitute code is implemented in VHDL and logic synthesis is executed. The Max-Log-MAP algorithm is used due to its significantly reduced complexity and negligible performance degradation from MAP algorithm. The implementation of codec mainly focuses on achieving the smaller chip area and lower power dissipation, and target to device Virtex-E FPGA. For this purpose, the system and module level optimization of codec architecture is carefully considered through the parallelism and pipeline, interleaving technique, function unit sharing and memory access. The quantization and finite accuracy are also discussed. The simulation in RTL level on a wide variety of test vectors is done, and results show that the encoder/decoder execute properly and correct functionality is realized. The synthesis reports show that chip utilization is reasonable and more resource remains for future improvement.

## Acknowledgments

I am so fortunate to have the opportunity to work on this interesting topic under the supervision of Dr. Asim A. Al-Khalili and Dr. M. Reza Soleymani. I want to express my sincere gratitude to both supervisors and truly appreciate their constructive guidance, valuable advice and helpful discussion throughout my thesis research. Their kind relationship with student make me could not ask more from them. Their financial support also provides me a more freedom to pursue my academic goal.

I am grateful to Usa Vilaipornsawai for her sharing with me knowledge of RM code and to whom I owe much of understanding of this topic. I want to thank all peoples who help and encourage me throughout my study in concordia university for their valuable solicitude and help.

Finally, I would like to express my heartfelt gratitude to my wife for her unconditional love and support. Without her understanding, it is impossible for me to continue my study and finish this research.

## **Table of Contents**

| List of Acronyms  1. Introduction  1.1 Introduction  1.2 Review of Error Correction Codes  1.3 Objective of thesis  1.4 Contribution  1.5 Overview  2. Block turbo codes  2.1 Basics of block turbo codes  2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm  2.5 Summary | viii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ix   |

| 1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | x    |

| 1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.2 Review of Error Correction Codes  1.3 Objective of thesis  1.4 Contribution  1.5 Overview  2. Block turbo codes  2.1 Basics of block turbo codes  2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                   | 1    |

| 1.3 Objective of thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 1.4 Contribution 1.5 Overview  2. Block turbo codes 2.1 Basics of block turbo codes 2.1.1 Linear block code 2.1.2 Block turbo codes 2.2 Reed-Muller turbo codes 2.2 Reed-Muller turbo codes 2.2.1 RM turbo encoder 2.2.2 RM turbo decoder 2.2.3 Interleaver  2.3 Minimal trellis construction of RM code 2.4 Trellis-based MAP algorithm                                                                                                                                            | 4    |

| 2. Block turbo codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8    |

| 2.1 Basics of block turbo codes  2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                     | 8    |

| 2.1 Basics of block turbo codes  2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                     | 9    |

| 2.1 Basics of block turbo codes  2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                     |      |

| 2.1.1 Linear block code  2.1.2 Block turbo codes  2.2 Reed-Muller turbo codes  2.2.1 RM turbo encoder  2.2.2 RM turbo decoder  2.2.3 Interleaver  2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                                                      | .11  |

| 2.1.2 Block turbo codes                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .11  |

| 2.2 Reed-Muller turbo codes                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .11  |

| 2.2.1 RM turbo encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .13  |

| 2.2.2 RM turbo decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .15  |

| 2.2.3 Interleaver                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .16  |

| 2.3 Minimal trellis construction of RM code  2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                                                                                                                                                                                                        | .19  |

| 2.4 Trellis-based MAP algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .23  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .24  |

| 2.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .27  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .31  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3. Algorithms for implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .32  |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .32  |

| 3.2 Max-Log-MAP algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .33  |

| 3.3 Max-Log-MAP algorithm with correction                                                                                                                                                                                                                                                                                                                                                                                                                                           | .35  |

| 3.4 Arithmetic units                               | 38 |

|----------------------------------------------------|----|

| 3.4.1 Pre-processing model                         |    |

| 3.4.2 Gamma calculation model                      |    |

| 3.4.3 Alpha/Beta calculation model                 |    |

| 3.4.4 Extrinsic information calculation model      |    |

| 3.4.5 Log-likelihood soft-output calculation model |    |

| 3.5 Summary                                        |    |

| 4. Design and implementation of RM-BTC             | 43 |

| 4.1 Review of turbo code implementation            |    |

| 4.2 Hardware choices and FPGA                      |    |

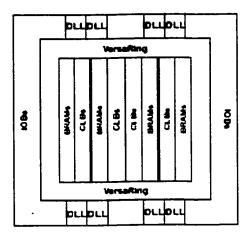

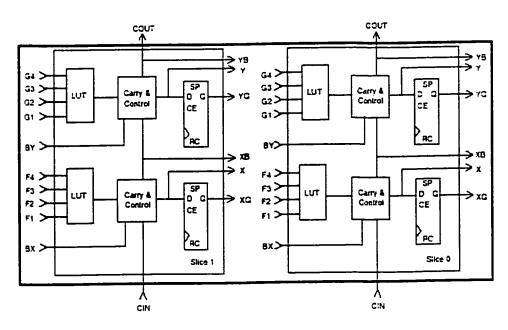

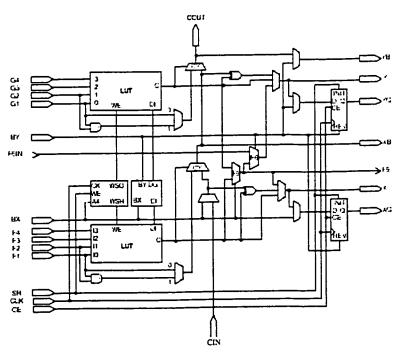

| 4.2.1 Virtex-E FPGA architecture                   |    |

| 4.2.2 Arithmetic function cores                    |    |

| 4.3 Design issues                                  |    |

| 4.3.1 Quantization and finite accuracy             |    |

| 4.3.2 Data- and hardware-sharing                   |    |

| 4.3.3 Parallelism and pipeline                     |    |

| 4.3.4 Iteration stop criterion                     |    |

| 4.3.5 (De)-interleaving technique                  |    |

| 4.4 Turbo encoder implementation                   |    |

| 4.4.1 Interface input/output                       |    |

| 4.4.2 Generator matrix and trellis                 |    |

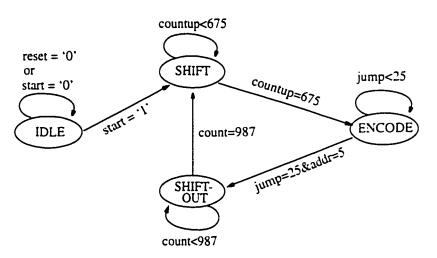

| 4.4.3 Finite state machine                         |    |

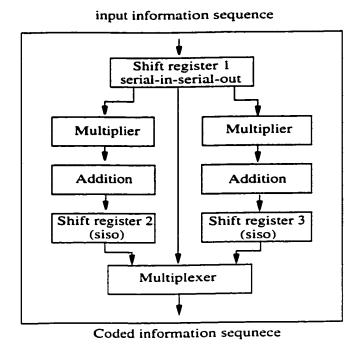

| 4.4.4 Encoder data path                            |    |

| 4.5 Turbo decoder implementation                   |    |

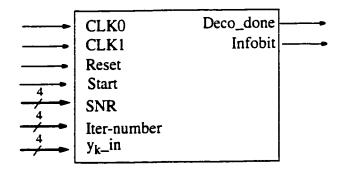

| 4.5.1 Interface input/output                       |    |

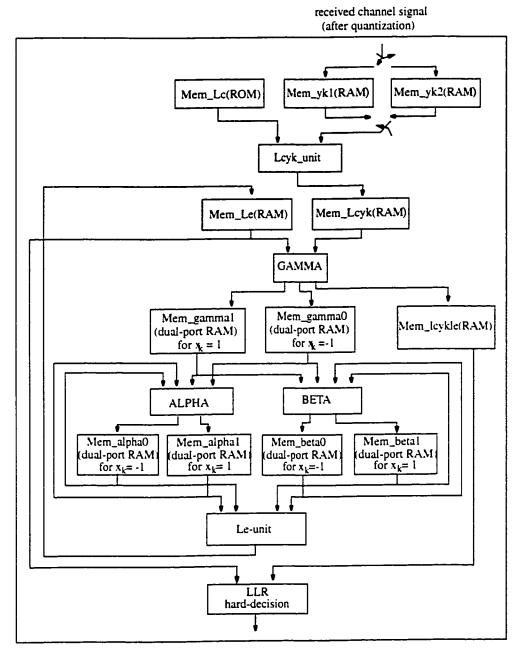

| 4.5.2 Finite state machine                         |    |

| 4.5.3 Pre-processing component                     |    |

| 4.5.4 Gamma unit                                   |    |

| 4.5.5 Alpha/Beta unit                              |    |

| 4 5 6 Extrinsic information unit                   |    |

| 4.5.7 LLR unit                              | 75 |

|---------------------------------------------|----|

| 4.6 Memory architecture                     |    |

| 4.7 Summary                                 |    |

| 5. Simulation and synthesis                 | 80 |

| 5.1 Test model                              |    |

| 5.2 Simulation                              |    |

| 5.3 Synthesis and comparison                |    |

| 5.4 Summary                                 |    |

| 6. Conclusion                               | 88 |

| 6.1 Summary                                 |    |

| 6.2 Practical limitation and solutions      |    |

| Bibliography                                |    |

| Appendix A Synthesis reports                | 98 |

| Appendix B Turbo encoder VHDL source codes  |    |

| Appendix C. Turbo decoder VHDL source codes |    |

## **List of Figures**

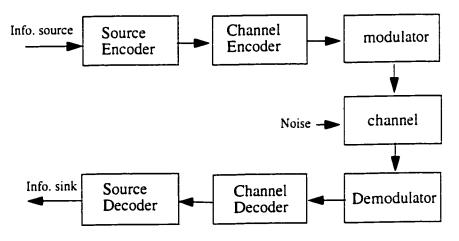

| Figure 1.1  | Typical digital communication block diagram            | 2  |

|-------------|--------------------------------------------------------|----|

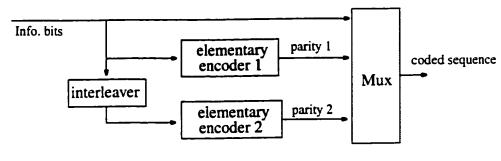

| Figure 2.1  | Block diagram of parallel turbo code                   | 14 |

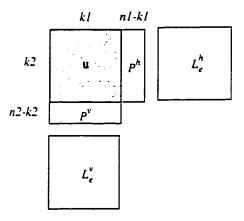

| Figure 2.2  | Re-ordered two dimensional RM turbo code               | 18 |

| Figure 2.3  | Soft-in-Soft-out decoder                               |    |

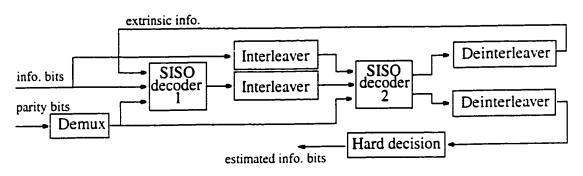

| Figure 2.4  | Iterative decoding procedure with initial $L^h(x) = 0$ | 21 |

| Figure 2.5  | One section of trellis structure of block code         | 28 |

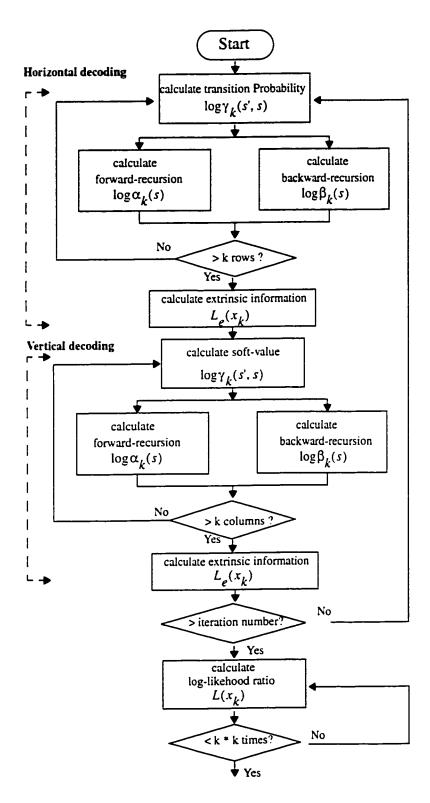

| Figure 3.1  | Log-MAP decoding flow chart diagram                    | 37 |

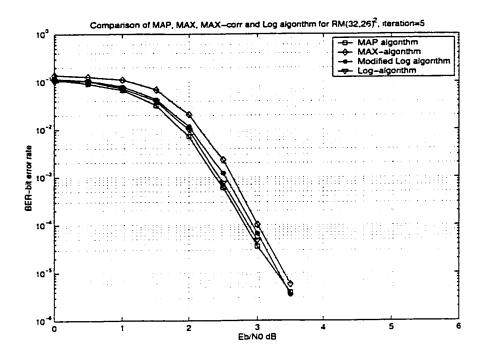

| Figure 3.2  | Comparison of different algorithm on performance       | 38 |

| Figure 4.1  | Virtex-E architecture overview                         | 48 |

| Figure 4.2  | A 2-slice Virtex-E CLB                                 | 49 |

| Figure 4.3  | A detailed view of Virtex-E slice                      | 49 |

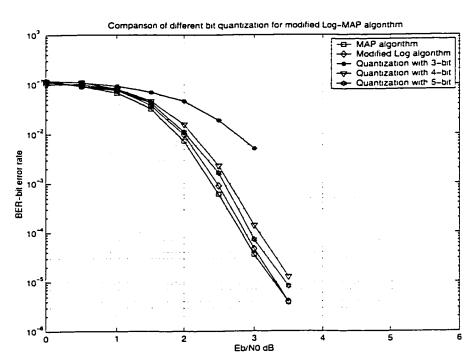

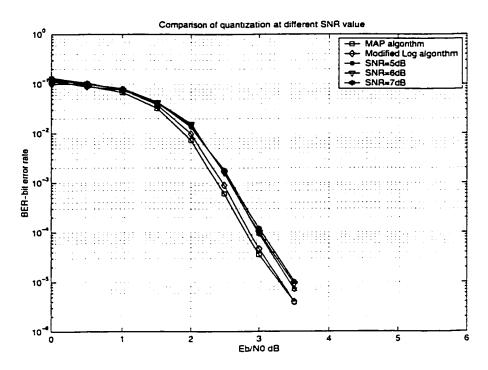

| Figure 4.4  | Different bit quantization effects on performance      | 52 |

| Figure 4.5  | 4-bit quantization on different SNR values             |    |

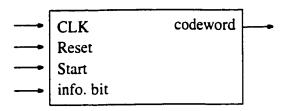

| Figure 4.6  | I/O interface of turbo encoder                         | 59 |

| Figure 4.7  | The illustrative trellis diagram of RM(32,26) code     | 61 |

| Figure 4.8  | Finite state machine of turbo encoder                  |    |

| Figure 4.9  | Data path of turbo encoder                             | 63 |

| Figure 4.10 | Data path architecture of Log-MAP turbo decoder        | 66 |

| •           | I/O interface of turbo decoder                         |    |

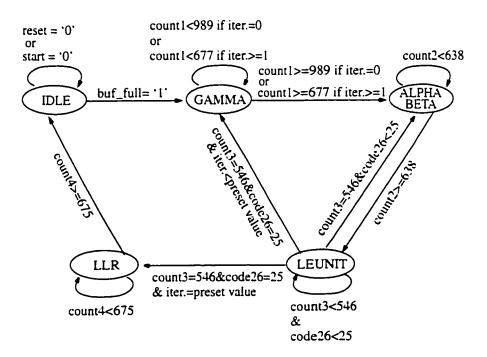

| Figure 4.12 | Finite state machine of turbo decoder                  | 69 |

| Figure 4.13 | Data path of branch metric calculation                 | 71 |

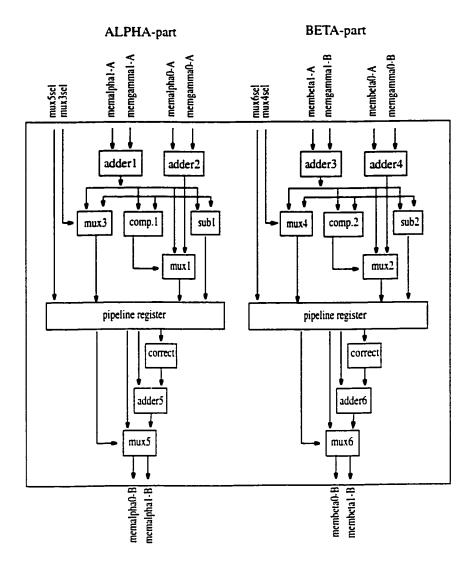

| Figure 4.14 | Data path of forward/backward recursion calculation    | 73 |

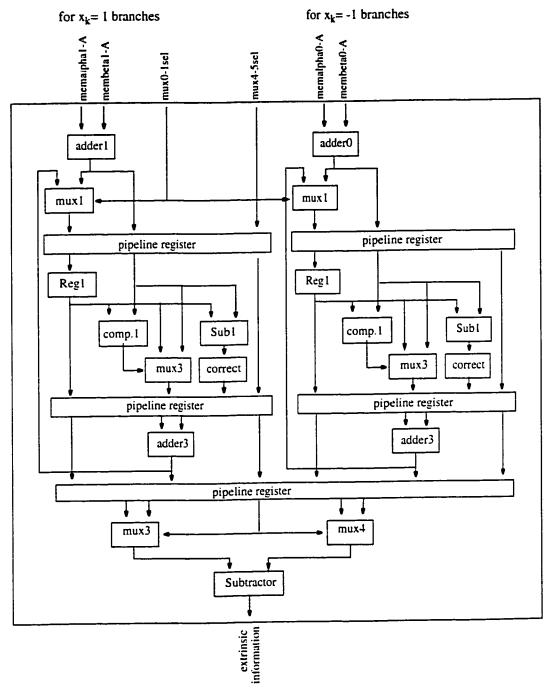

| Figure 4.15 | Data path of extrinsic inforamtion calculation         | 74 |

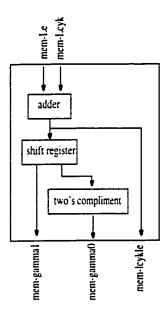

| Figure 4.16 | Data path of log-likelihood ratio calculation          | 75 |

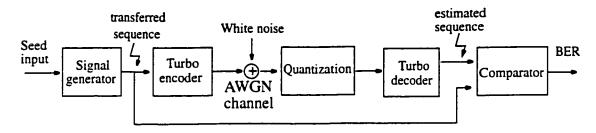

| Figure 5.1  | Block diagram of test model                            | 81 |

## **List of Tables**

| Table 4.1 Input/Output interface definition of turbo encoder           | 60 |

|------------------------------------------------------------------------|----|

| Table 4.2 Generator memory address and cell content                    | 61 |

| Table 4.3 Input/Output interface definition of turbo decoder           | 67 |

| Table 4.4 Lc values for E <sub>b</sub> /N <sub>0</sub> at rate R=0.684 | 70 |

| Table 4.5 Look-up table for correction term                            | 72 |

| Table 4.6 Memory description of turbo encoder and decoder              | 77 |

| Table 5.1 BER/Block versus SNR values                                  | 83 |

| Table 5.2 Design summary of turbo encoder                              | 85 |

| Table 5.3 Design summary of turbo decoder                              | 85 |

| Table 5.4 Comparison between implementations                           | 86 |

## **List of Acronyms**

ARQ automatic repeat request

ASIC application specific integrated circuit

AWGN additional white gaussian channel

BCH Bose-Chaudhuri-Hocquenghem code

BER bit error rate

BPSK binary phase shift key

BTC block turbo codes

CLB configurable logic block

CTC convolutional turbo codes

DSP digital signal processing

ECC error correction codes

FEC forward error correction

FIFO first in first out

FPGA field programmable gate array

FSM finite state machine

GRM programmable routing matrix

HCCC hybrid concatenated convolutional codes

IOB input/output block

LC logic cell

LUT look-up table

MAP maximum a posteriori probability

MSB most significant bit

PCCC parallel concatenated convolutional codes

RAM random access memory

RM-BTC Reed-Muller block turbo codes

ROM read only memory

SCCC serial concatenated convolutional codes

SISO soft in soft output

SNR signal to noise ratio

SOVA soft-output Viterbi algorithm

SRAM static random access memory

## Chapter 1

## Introduction

Increasing demand for information exchange is a characteristic of modern civilization, and the distance can't prevent people from communicating across the world. The past ten years have seen rapid growth in mobile communication and this is expected to continue. The information transmission should be done in such a way that the received information should be as close as possible to the transmitted information. Therefore, providing a high speed data transfer, reliable and cost-effective data communication system has drawn much attention in the past decades.

#### 1.1 Introduction

Since digital techniques offer many benefits in technical implementation and economic benefit, digital communication systems have become the main stream technology in communication systems. A typical digital communication system is shown in Figure 1.1[3]. The original signal source feeds into source encoder which efficiently compresses data with little or no redundancy; the binary output data stream from the source encoder, called the information sequence, is passed to the channel encoder, which introduces some controlled redundancy in binary information sequence. The added redundancy can be used at the receiver to overcome the effects of noise and interference encountered in the trans-

mission of the signal through the noisy channel. So the coded output from the channel encoder provides the error detecting and correcting capability to the channel decoder at the receiver end. The digital modulator maps the coded word into a set of waveforms that are suitable for transmission over the channel, where the data is usually corrupted by noise. At the receiving end, the demodulator processes the channel-corrupted waveforms and following detector will make a hard or soft decision based on decoding algorithm used. With the knowledge of the code used by the channel encoder, the channel decoder processes the quantized/unquantized output from the detector and outputs the estimated coded word whose errors have been detected and corrected. As a final step, source decoder attempts to reconstruct the original information sequence generated by the source.

Figure 1.1 Typical digital communication block diagram

The frequency of errors occurring in the decoded sequence is a measure of reliable information transfer. It is called bit error rate (BER). In general, it is related to the code characteristics, modulation type, transmitter power and the method of demodulation and decoding used, etc.. In this thesis, we focus on an algorithm and its implementation for channel coding, which minimizes the error bits in the decoded sequence.

The channel decoder can control errors in many ways[4]. For example, a bilateral exchange, called automatic repeat request (ARQ), can minimize the amount of wasted effort/bandwidth needed to control errors when both forward- and reverse-channel communications are reliable. However, in many cases, the reliable reverse channel is unavailable, and the system cannot tolerate the delay imposed by an ARQ system. So the forward error correction (FEC) is used mainly in protecting data against disturbance introduced by the physical channel.

Forward error correction adds redundancy to the data stream at the transmitter end so that the receiver can both detect and correct errors unilaterally. However, this requires expanded bandwidth to transfer the coded sequence including the original information and the error-correcting redundancy. Although increasing transmitted power and expanding bandwidth can reduce the error rate sufficiently, many applications are strictly power-limited and bandwidth-limited. Therefore, what engineers consider is to find a powerful forward error correcting coding scheme that balances the transmit power, bandwidth and data reliability.

While channel coding provides protection to transmitted information, it is also required to reduce the transmit power which is normally represented in terms of coding gain. The coded system requires less signal-to-noise ratio (SNR) than uncoded system to achieve the same bit error probability. This reduction expressed in decibel (dB) is called coding gain. A large coding gain means less transmit power. Therefore, a powerful coding scheme is to achieve as much coding gain as possible[3,5]. Nevertheless, the construction and selection of the coding type depend on some constraints and requirements such as channel environment, implementation complexity, as well as performance, speed and

bandwidth, etc.. That's why the development of error-correcting code (ECC) has been continuously improving for half century since the concept was proposed by Claude E Shanon.

## 1.2 Review of Error Correcting Codes

Claude E Shannon laid the foundation for modern digital communication with his ground breaking paper [6] in 1948. The two classical theorems in information theory are the source coding theorem and the channel coding theorem. The source coding theorem shows the smallest number of bits required to represent a given source without any loss; the channel coding theorem shows the maximum theoretical data rate with 'good' data code for reliable communications. The theorems show that if the data rate is less than the channel capacity, reliable information transmission can be achieved if one chooses proper encoding and decoding techniques.

There are two broad categories of codes used in communication system for error control coding, block codes and convolutional codes. In block codes, a block of n digits generated by the encoder in a particular time unit depends only on the block of k input message digits within that time unit. The larger the block length n, the smaller the probability of decoding error. In convolutional codes, a block of n digits generated by the encoder in a time unit depends not only on the block of n message digits within that time unit, but also on the preceding (N-I) blocks of message digits. Due to the difference between them, block codes are better suited for error detection and convolutional codes are mainly used for error correction. Recent studies have shown that convolutional codes perform as well or better than block codes in many error control applications [7-9].

Bose-Chaudhuri-Hocquenghem (BCH) codes, discovered by Bose, Chaudhuri[69] and Hocquenghem[70] in 1959, are among the most extensively used powerful error-correcting cyclic codes known. The important sub-class of BCH codes, Reed Solomn codes were proposed by Reed and Solomn in 1960[71]. It has a better performance at higher SNR region and copes well with burst error, whereas convolutional codes outperforms the Reed Solomn code at lower SNR region.

Burst errors often occur in storage media such as tapes and compact discs because of defects. Aforementioned codes concentrate on codes capable of correcting random errors. They are in general not efficient at correcting burst errors. In order to take advantages of each code, some new type of codes are introduced in coding schemes such as Interleaved, Product and Concatenated Codes. Because the large block lengths offer the small probability of decoding error, these codes are long block length codes that are derived from short block codes.

An interleaved code can correct a single burst of length  $A\tau$  or less if the original code can correct a single burst of length  $\tau$  or less, where A is degree of interleaving and  $\tau$  is burst of length. However, interleaving a code introduces delay (delayed interleaving) because transmission cannot begin until all A code words have arrived.

A product code is an  $(N_1N_2, K_1K_2)$  code in which each code word forms an  $N_1 \times N_2$  rectangular array such that each row is a code word from an  $(N_1, K_1)$  code  $C_1$  and each column is a code word from an  $(N_2, K_2)$  code  $C_2$ . Product code is capable of correcting burst errors of length  $\tau'$  or less, where  $\tau' = max(N_1\tau_2, N_2\tau_1)$  if  $C_1$  and  $C_2$  are capable of cor-

recting bursts of length  $\tau_1$  and  $\tau_2$ . Product codes were proposed by Elias and they can be extended to higher dimension.

Concatenated coding was introduced by Forney[2] as a practical technique for implementing a code with a very long block length and a large error-correcting capability. The principle is the application of two levels of coding, an inner and an outer code linked by an interleaver. The inner encoder, channel and the inner decoder are viewed as a super channel. The information is first encoded by outer encoder, for example Reed Solomn encoder, and then the output from outer encoder is fed into the inner encoder, for example convolutional encoder. The decoding process is in the reverse order: the received sequence with errors is decoded by inner decoder with hard or soft decision algorithm and then decoded by outer decoder to correct the residual errors.

Turbo codes, introduced by Berrou *et al.*[10], built from a particular concatenation of two recursive systematic convolutional codes linked by nonuniform interleaving, is the biggest breakthrough in recent error correction code [ECC] history[10,11]. For the AWGN channel, turbo codes perform to within 0.7 dB of Shannon's limit as opposed to 2 dB or more for other state-of-the-art techniques of similar complexity. Since 1993, turbo codes have become the hottest topic in ECC field. Soon after convolutional turbo codes (CTC) was proposed by Berrou *et al.* in 1993[10], the concept of turbo codes was extended to block turbo codes (BTC) in particular by Pyndiah *et. al*[12,13]. The difference between CTC and BTC is the component code used. Convolutional codes are used as component code in CTC whereas the block codes are used in BTC. Because of its excellent forward error correction capability and superior coding gain, the utilization of turbo codes has increased dramatically on AWGN channels, such as satellite, wireless and space commu-

nications which require high performance at very low SNR. In Chapter 2, the details of BTC will be discussed.

There are many decoding algorithms for different code constructions such as the efficient iterative algorithm proposed by Berlekamp for BCH codes[8]; the Viterbi algorithm for minimizing the probability of word error for convolutional codes[3]; the MAP algorithm proposed by Bahl et. al for minimizing the symbol (or bit) error probability by estimating the a posteriori probabilities of the states and transition of a Markov source through a discrete memoryless channel[14]. In this thesis, we are interested in the trellisbased MAP algorithm because the state transition and decoding process can be represented by a trellis diagram, and it is more efficient than other non-trellis algorithms.

Most algorithms can accept hard- or/and soft-input and perform hard- or/and soft-decision decoding. In the hard decision decoding, the input of the decoder is quantized into two levels; whereas in the soft decision, the input is quantized into more than two levels. Multi-level quantization or the real channel information input makes soft-input decoding to have more advantages over hard-input decoding due to more reliable information being available. The additional information provided by the soft decision in most instances can provide about 2 dB of additional coding gain and can significantly increase the usefulness of a particular code[1].

Based on the MAP algorithm in logarithmic domain[15,16], J. Hagenauer *et al.* gave a detailed analysis and mathematical formula about the iterative decoding of both block and convolutional turbo codes with MAP and its modified versions[17]. An alternative coding scheme with Reed-Muller code as component code was presented in [5]. The two papers [5, 17] are the basis of decoding algorithm used in this thesis.

## 1.3 Objective of thesis

Although turbo codes have outstanding performance, they are computational complex. Also there exists many technical difficulties in the implementation of a practical turbo-coded system. The main objective of this thesis is to design the hardware architecture and arithmetic function units of Reed-Muller block turbo codes (RM-BTC) Codec in RTL model, and aim at the implementation using Field Programmable Gate Array (FPGA), and produce a prototype. The second goal is to reduce the chip area as much as possible. The actual decoding speed and chip area obtained through synthesizing and mapping to Xilinx FPGA are taken as a reference for future improvement.

## 1.4 Contribution

This thesis is an engineering-intensive design work based on an existing decoding algorithm. It presents a practical implementation of a turbo-code codec on a Xilinx FPGA chip. The main contributions contains:

- Investigation and modification of the decoding algorithms suitable for hardware implementation.

- Behavioral simulation of the modified algorithm and quantization of variables.

- Hierarchical architecture design of codec and functional units and finite state

machine (FSM) for codec. Especially employing a single decoder for both horizontal and vertical decoding for the sake of saving chip area without performance degradation.

- Simulation and synthesis of proposed hardware implementation.

- Correct gate-level simulation of turbo encoder.

### 1.5 Overview of thesis

The focus of this thesis is on the implementation of turbo-coded codec. It is organized as follows:

Chapter 2 provides an introduction to block turbo codes related to this thesis. Besides the basic concepts of block turbo codes, the construction of Reed-Muller code and its minimal trellis diagram using Massey algorithm are given. After discussion of the soft-in-soft-out (SISO) decoder and parallel iterative decoding, trellis-based MAP algorithm for linear BTC is presented.

Chapter 3 studies the modified algorithm to be implemented based on trellis-based decoding. The Log-MAP and Max-Log-MAP as well as Lookup-table-based Log-MAP algorithms are discussed in detail. Decomposition of each arithmetic functional unit for forward recursion, backward recursion, branch probability as well as extrinsic information calculation is provided. Finally, the iterative decoding procedures are given as a guideline of FSM design.

Chapter 4 contains all aspects of design and implementation of RM-BTC codec. First, the review of turbo code implementation in the past is given; some issues such as quantization, fixed-point representation are also reviewed. Second, the aimed target implementation Xilinx Virtex-E FPGA architecture is provided. Finally, according to the modified algorithm and target device, the detailed designs of RM-BTC encoder and decoder are given, which include the overall architecture, finite state machine and data path components.

Chapter 5 covers the results of simulation and synthesis of the RM-BTC encoder and decoder. A variety of test information blocks are sent to the encoder and the decoder

output is compared with original information block under different SNRs. The hardware mapping results are given for encoder and decoder, respectively.

Chapter 6 summarizes the work presented in this thesis, and discusses several ideas for improving the current design in future work.

## Chapter 2

## **Block turbo codes**

In this chapter, we first discuss some basic concepts related to block turbo codes [3,18], which are relevant to this thesis. Then Reed-Muller code used in this thesis is discussed. Minimal trellis construction and trellis-based decoding of RM-BTC are discussed in detail.

#### 2.1 Basics of block turbo codes

#### 2.1.1 Linear block code

A block code C(n,k) consists of  $M = q^k$  code words of length  $n \ (k < n)$ , whose elements are selected from an alphabet of q elements of GF(q), the ratio k/n is defined to be the code rate which determines the amount of redundancy. Here we just consider the binary block code, i.e. q = 2. The  $2^k$  distinct code words are a subset of  $2^n$  binary sequence of length n, which are selected to transmit k-bit blocks of information.

An (n,k) block code is linear if component-wise modulo-q sum operation of any two code words is another code word. In our case, modulo-2 sum is used in obtaining another code word. Viewing from linear algebra, an (n,k) linear block code is a k-dimen-

sional subspace of the n-dimensional space of all the binary n-tuples. We can construct the linear block code with vector and matrix format.

The k-bit information vector  $\mathbf{M} = (m_0, m_1, m_2, ..., m_{k-1})$  would be encoded into block codeword C of length n,  $\mathbf{C} = (c_0, c_1, c_2, ..., c_{n-1})$ , the linear operation performed in a linear block encoder can be represented as

$$C = M \times G \tag{2.1}$$

where G is called the generator matrix, with a set of k linearly independent binary n-tuple as its row, arranged as a  $k \times n$  matrix.

Further, a linear systematic block code can be constructed when the generator matrix G can be reduced to the following special "systematic" form by a sequence of elementary row operations and column permutations,  $G=[I_k: P]$ , where  $I_k$  is a  $k \times k$  identity matrix and P is a  $k \times (n-k)$  matrix determining the parity check bits.

In the linear systematic block code, the first k bits of the codeword are identical to the information bits to be transmitted. This enables direct extraction of information bits at decoder from the codeword without attempting to recover information bits. As seen in the following formula, code word C is made up of two part: the information bits  $m_i$  and the parity check bits  $p_{ji}$ .

$$c_{i} = \begin{cases} m_{i} & 0 \le i \le k-1 \\ \sum_{j=0}^{k-1} p_{ji} \cdot m_{j} & k \le i \le n-1 \end{cases}$$

(2.2)

This form simplifies the decoding operation later. However, the position of information bits is not necessarily restricted to the first k bits of code words if the position of

information bits can be obtained through systematic-like G matrix. We still treat this form of code word as systematic-like code.

### 2.1.2 Block turbo codes

Today, concatenated coding schemes have proven to be attractive schemes for obtaining high coding gain with moderate decoding complexity. They aim to achieve the same performance as that of a single long and powerful error correcting code but with a lower complexity when associating two or more less powerful error correcting codes. Concatenated coding schemes can be divided into three categories: parallel, serial and hybrid concatenated coding[28]. In practice, the first two schemes are widely used because of the reasonable complexity of the decoders given a certain coding gain, especially the classic serial one with Reed-Solomn code as the outer code and convolutional code as inner code. Because the hybrid code introduces a considerable amount of delay, it is normally suitable for extremely high data rates where the resulting delay is tolerable.

Turbo codes exploit the similar idea of concatenated code to achieve a low error rate with less decoding complexity than that required for a single code of the corresponding performance. Turbo codes can be in form of two- or three-dimensional which consists of concatenation of two or three component codes separated by interleavers. Two-dimensional turbo codes normally consist of two elementary encoders, which construct turbo encoder and two soft-in-soft-out (SISO) decoders, which construct turbo decoder and interleaver/de-interleavers. According to how information bits are encoded and decoded, there are three kinds of turbo codes: parallel, serial and hybrid turbo codes (PCCC, SCCC and HCCC)[26]. Illustrated by some simulation results[26], SCCCs outperform PCCCs at

lows we take a two-dimensional turbo code to illustrate the basic concepts of parallel turbo code. The parallel turbo encoder and decoder are shown in Figure 2.1.

(a) Parallel turbo encoder

(b) Parallel turbo decoder

Figure 2.1 Block diagram of parallel turbo code

Although the term "turbo code" is used to refer to a wide variety of concatenated coding schemes, its initial version is solely a parallel concatenation of convolutional codes (PCCC) whose encoder is formed by parallel concatenation of two recursive systematic convolutional codes jointed by an interleaver. In parallel turbo encoder shown in Figure 2.1(a), two elementary encoders are connected in parallel by an interleaver. The information bits and its interleaved sequence are input to elementary encoders 1 and 2, respectively. Each encoder encodes the information bits and output the coded sequence consisting of the information and parity check bits. The information bits for the encoder 2

are not transmitted because it is same as that of the encoder 1. This is different from conventional concatenated codes. Therefore, turbo encoder output is made up of three parts: information bits, parity 1 and parity 2 bits, which will be transmitted over the physical channel. One advantage of the parallel scheme is that the two encoders can work clock-synchronously.

In the parallel turbo decoder shown in Figure 2.1(b), two soft-in-soft-out (SISO) decoders linked by an interleaver realize the iterative decoding of the received sequence. The soft output of the received information and parity 1 bits from the demodulator and extrinsic information from the SISO decoder 2 as *a priori* value are taken as the inputs of the SISO decoder 1; the soft output of the interleaved received information and parity 2 bits as well as interleaved extrinsic information from decoder 1 are taken as inputs to the SISO decoder 2. Similarly, the extrinsic information generated by decoder 2 are deinterleaved and feedback to decoder 1 for next iterative decoding. After a presetting iterative decoding process, the hard decision is made according to the sign of the deinterleaved soft output of the decoder 2, and the magnitude of soft output is the reliability of this decision.

#### 2.2 Reed-Muller turbo codes

The choice of the constituent code has a strong influence on the overall performance of turbo codes. Long block length (interleaver size) yield remarkable performance; however, in wireless applications, the block length is much smaller, on the order of a few hundred bits or less. The advantage of using a block code is that the memory requirements of the MAP decoding can be reduced significantly; also the decoding delay is set by the length of the block and does not depend on the transmission rate.

In our turbo code scheme, Reed-Muller codes are used as constituent code because they have modular structure for constructing longer codes with shorter ones. Their trellis can be easily constructed, further they can be decoded effectively with trellised-based decoding algorithms. In this section, we first present some basics of the Reed-Muller codes[19, 20], then discuss the construction of RM turbo codes. Finally the basics of RM turbo decoding is followed.

#### 2.2.1 RM turbo encoder

Reed-Muller codes are a class of linear codes over GF(2). They can be constructed by procedures for constructing a generator matrix. For a binary r-th order  $RM_{(r, m)}$  code of length  $n = 2^m$  with  $0 \le r \le m$ , there exists m  $2^m$ -tuple vectors  $\mathbf{v}_i$  over GF(2),  $1 \le i \le m$ . in the following form:

$$v_i = (\underbrace{\frac{0...0}{2^{i-1}}}, \underbrace{\frac{1...1}{2^{i-1}}}, \underbrace{\frac{0...0}{2^{i-1}}}, \underbrace{\frac{1...1}{2^{i-1}}})$$

(2.3)

that consists of  $2^{m-i+1}$  alternate all-zero and all-one  $2^{i-1}$ -tuples. Let  $\hat{a} = (a_1, a_2, ..., a_n)$  and  $\hat{b} = (b_1, b_2, ..., b_n)$ , and the product of a and b is defined as

$$\dot{\vec{a}} \cdot \dot{\vec{b}} = (a_1 \cdot b_1, a_2 \cdot b_2, \dots, a_n \cdot b_n) \tag{2.4}$$

For  $1 \le i_1 \le i_2 \le \dots \le i_l \le m$ , the product  $v_{i_1} \cdot v_{i_2} \cdot \dots \cdot v_{i_l}$  is said to have degree l. we also denote  $\vec{1}$  the all-one  $2^m$ -tuple,  $\vec{1} = (1,1,\dots,1)$ .

Now the generator matrix G of r-th order RM code, RM(r, m) of length  $2^m$  is generated by the following set of vectors:

$$G(r,m) = \begin{cases} \frac{1}{1}, v_1, v_2, ..., v_m, v_1 \cdot v_2, v_1 \cdot v_3, ..., v_{m-1} \cdot v_m, ... \\ up - to - products - of - degree - r \end{cases}$$

(2.5)

The RM(r, m) codes have the following parameters:

The code length  $n = 2^m$  and the dimension k of G matrix is

$$k_{r,m} = 1 + {m \choose 1} + {m \choose 2} + \dots + {m \choose r}$$

For convenience, from now on in this thesis, RM(n, k) form is used instead of  $RM_{(r,m)}$ .

In an example of RM(16, 11) code, the 2-th RM code of length 16 is generated by the following G matrix:

The above matrix is not in "systematic" form, so the code generated is not systematic code. In order to simplify the encoding and decoding, G matrix can be reduced by row operations and column permutations to a systematic-like form which clearly indicates the position of information and parity bits. Because turbo codes are linear block codes, the

encoding operation can be viewed as modulo-2 multiplication of information vectors with the generator matrix.

In this thesis, two dimensional  $RM(32,26)^2$  codes are used as constituent codes and parallel concatenated scheme is adopted. Therefore, two elementary encoders in Figure 2.1(a) are instantiated with two RM(32,26) encoders. The information block and its permuted version after block interleaver are encoded by two RM(32,26) encoders, namely horizontal and vertical encoder corresponding to elementary encoder 1 and 2, respectively. Because we only transmit the original information bits once, this turbo code has the following re-ordered pattern shown in Figure 2.2.

Figure 2.2 Re-ordered two dimensional RM turbo code

The horizontal encoder generates  $C_1$  ( $n_1,k_1$ ) and vertical one generates  $C_2$  ( $n_2,k_2$ ) linear systematic-like RM code, where  $n_i$  and  $k_i$  are code length and information length of code  $C_i$ , i = 1, 2. Horizontal parity bits  $P^h$  and vertical parity bits  $P^v$  are added by horizontal and vertical RM encoder accordingly based on the information data  $u = k_1 \times k_2$  and its interleaved version. This code has no parity bits on another parity part.

The Figure 2.3 has the ideal systematic form through re-ordering information and parity bits. When decoding, we need to perform the inverse operation to obtain the original code word order.

#### 2.2.2 RM turbo decoder

Before discussing the RM turbo decoder, we first present some basics of the loglikelihood algebra and SISO decoder as well as the iterative decoding principle[11,17].

Assume BPSK modulation and natural logarithm are used in the following discussion. Let a binary random variable X be in GF(2) with elements  $\{+1, -1\}$ . The log-likelihood ratio of x,  $L_X(x)$ , is defined as  $L_X(x) = \log \frac{P_X(x=1)}{P_X(x=-1)}$ , which will be denoted as the soft value. When an (n,k) systematic code is transmitted over a Gaussian channel, the log-likelihood ratio of bit x conditioned on the match filter output y is

$$L(x|y) = \log \frac{P_X(x=1|y)}{P_X(x=-1|y)}$$

$$= \log \left(\frac{p(y|x=1)}{p(y|x=-1)} \cdot \frac{P(x=1)}{P(x=-1)}\right)$$

$$= \log \frac{\exp\left(-\frac{E_s}{N_0}(y-a)^2\right)}{\exp\left(-\frac{E_s}{N_0}(y+a)^2\right)} + \log \frac{P(x=1)}{P(x=-1)}$$

$$= L_c \cdot y + L(x)$$

(2.7)

where  $L_c = 4 \cdot a \cdot \frac{E_s}{N_0}$  is called the reliability value of the channel, and a denotes

the fading amplitude whereas for Gaussian channel a = 1. The soft-output of the bit  $x_k$ ,

$L(\hat{x}_k)$  of the maximum a posteriori (MAP) decoder is defined as a posteriori log-likelihood ratio of bit  $x_k$  conditioned on the received sequence  $\hat{y}$  as follow

$$L(\hat{x}_{k}) = L(x_{k}|\hat{y})$$

$$= \log \frac{P_{X}(x_{k} = 1|\hat{y})}{P_{X}(x_{k} = -1|\hat{y})}$$

$$= \log \frac{p(\hat{y}|x_{k} = 1)}{p(\hat{y}|x_{k} = -1)} \cdot \frac{P(x_{k} = 1)}{P(x_{k} = -1)}$$

$$= \log \left(\frac{p(y_{k}|x_{k} = 1)}{p(y_{k}|x_{k} = -1)} \cdot \prod_{i=1, i \neq j}^{n} \frac{p(y_{i}|x_{k} = 1)}{p(y_{i}|x_{k} = -1)} \cdot \frac{P(x_{k} = 1)}{P(x_{k} = -1)}\right)$$

$$= \log \frac{p(y_{k}|x_{k} = 1)}{p(y_{k}|x_{k} = -1)} + \log \left(\prod_{i=1, i \neq j}^{n} \frac{p(y_{i}|x_{k} = 1)}{p(y_{i}|x_{k} = -1)}\right) + \log \frac{P(x_{k} = 1)}{P(x_{k} = -1)}$$

$$= L_{c} \cdot y_{k} + L_{e}(\hat{x_{k}}) + L(x_{k})$$

$$(2.8)$$

The above equation consists of three independent estimates for the log-likelihood ratio of the information bit  $x_k$ : channel value  $L_c \cdot y_k$  for all coded bits; the extrinsic information  $L_e(\hat{x_k})$  obtained from all the other code bits in the code sequence except  $x_k$ ; the a priori value  $L(x_k)$  which equals to zero for the first iteration under assumption of equally likely information bits.

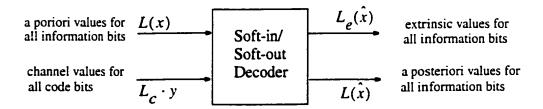

Soft-in-soft-out (SISO) decoder block diagram is shown in Figure 2.3. The log-likelihood input value L(x) feeds to SISO, which decodes received sequence y with MAP algorithm or SOVA algorithm and outputs the log-likelihood ratio of a posteriori  $L(\hat{x_k})$  and extrinsic values  $L_e(\hat{x})$  for all information bits.

Iterative decoding scheme is an important feature of turbo codes. Turbo codes use an iterative decoding algorithm where the BER performance improves after each iteration.

Figure 2.3 Soft-in-Soft-out decoder

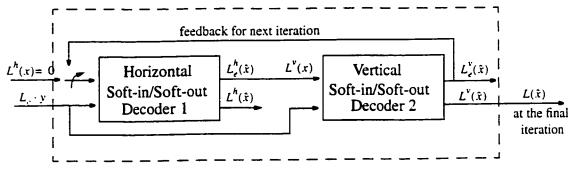

In order to optimize the global decoding performance of two concatenated decoder, named horizontal and vertical, the output extrinsic value of the vertical decoder is fedback to the horizontal decoder for further efficient utilization as a diversity effect, and this extrinsic information makes the horizontal decoder to obtain additional redundant information that may significantly improve its performance. However, this performance improvement is limited by the interleaver length and the code structure. The longer the interleaver, the more coding gain can be obtained from increasing the number of iterations. For a given interleaver length, the coding gain becomes negligible after a certain number of iterations. Reference [5] proves that when the block interleaver was used, the coding gain is saturated at 2nd, 4th and 5th iteration for  $RM(8,4)^2$ ,  $RM(16,11)^2$  and  $RM(32,26)^2$ , respectively.

The iterative feedback decoding scheme with two soft-in-soft-out decoders is shown in Figure 2.4. Its decoding procedure is as follows.

Figure 2.4 Iterative decoding procedure with initial  $L^h(x) = 0$

- 1. Assuming equally likely input information bits, so set the a priori  $L^h(x)$  to zero at first iteration.

- 2. Decoding of horizontal code  $C^h$  by using the corresponding  $L_c \cdot y$  of information part and horizontal parity check part. The horizontal extrinsic information  $L_e^h(\hat{x})$  of  $C^h$  on information bit x is:

$$L_e^h(\hat{x}) = L^h(\hat{x}) - L_c \cdot y - L^h(x)$$

$$= L^h(\hat{x}) - L_c \cdot y$$

(2.9)

3. Set  $L^v(x) = L_e^h(\hat{x})$ , i.e. the horizontal extrinsic information on information bit x is fed to the vertical decoder as the *a priori* value for decoding vertical code  $C^v$  while using the corresponding  $L_c \cdot y$  of the interleaved information part and vertical parity check part. The vertical extrinsic information  $L_e^v(\hat{x})$  of code  $C^v$  on information bit x is:

$$L_{\rho}^{\nu}(\hat{x}) = L^{\nu}(\hat{x}) - (L_{\rho} \cdot y) - L_{\rho}^{h}(\hat{x})$$

(2.10)

- 4. Set  $L^h(x) = L_e^v(\hat{x})$ , i.e. the vertical extrinsic information bit x is fed back to horizontal decoder as a priori value for decoding of horizontal code  $C^h$  in the next iteration.

- 5. After the last iteration, the soft output of turbo decoder on the information bit x is:

$$L(\hat{x}) = L_c \cdot y + L_e^h(\hat{x}) + L_e^v(\hat{x})$$

(2.11)

6. According to the sign of the soft output  $L(\hat{x})$ , the hard decision is made to obtain the estimated transmitted information bits.

In this thesis, RM turbo decoder takes parallel concatenated form of turbo codes shown in Figure 2.1(b). The component decoder uses SISO decoder with modified Log-MAP algorithm based on the minimal trellis diagram. Interleaver will take block interleaving techniques which is discussed in the next section.

#### 2.2.3 Interleaver

Another key feature of turbo codes is the interleaver. It plays an important role in achieving good performance of turbo codes. There are four major interleaving structures widely used in conjunction with error-correcting schemes: block interleaver, convolutional interleaver, random interleaver and code matched interleaver[18,28].

The interleaver in a turbo code scrambles the bits in each block of data before it enters the second encoder, so that the inputs to the two encoders are not correlated. For the burst error channel, this process spreads out the burst error. After correction of some of errors in the first component decoder, some of the remaining errors become correctable in the second decoder. Therefore, by de-coupling the inputs to the two encoders, the interleaver provides a good codeword weight distribution, which improves the decoder performance.

Turbo codes have a feedback path for extrinsic information to be used in the next iteration, and iterative decoding algorithm is used. Therefore, the decoding performance of turbo decoder depends on the structure and the size of the interleaver. For a given set of component codes, the turbo code with a longer interleaver has a better performance. However, longer interleaver introduces long delays which are not desirable in low data rate. That's why turbo codes are particularly attractive to higher data rate application.

A block interleaver formats the input sequence in a matrix of  $m \times n$ , in which the input sequence is written into matrix row-wise and read out column-wise. It is a simple interleaving method with sound performance. For our RM-BTC, the delay of block interleaver is fixed.

#### 2.3 Minimal trellis construction of RM code

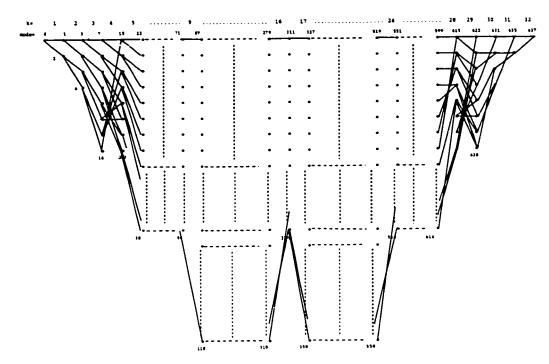

A trellis is a compact method of representing all of the  $q^k$  codeword of a linear code. A path from the root to a terminal node is referred to as a path through the trellis, and each distinct codeword corresponds to a distinct path in the trellis. Thus the total number of paths in the trellis is  $N_p = q^k$ . It has been found that an arbitrary linear  $(n, k, d_{min})$  block code over GF(q),  $q \ge 2$ , can be represented by its trellis diagram which contains  $N_c = n+1$  columns and  $N_s \le q^{min\{k, n-k\}}$  states[21]. In RM(32, 26) block code, we have the following state profile corresponding to 33 column:

where each number in parenthesis is the exponential value of base 2 at its own position. Consequently, we may obtain the state number at each time instant. For instance, at time instant 5, we have  $2^4 = 16$  states and at time 9 have  $2^5 = 32$  states.

Trellis structure determines the complexity of the trellis-based decoding for a linear block code. This can be expressed in terms of some quantities of the trellis such as the logarithms of the maximum numbers of states and branches at any time index. The trellis structure of block encoder is irregular in comparison to the trellis of a convolutional code

the decoding complexity is equivalent to finding the minimal trellis diagram of a given code. Among the many trellis representations of block code, a minimal trellis diagram of a code C of length n is the one that has the minimal state numbers than in any other trellis for C at the time index i, i = 0, l,..., n. In this thesis, the Massey construction method is used to construct the minimal trellis of the RM code because of its systematic property. Some basic knowledge related to minimal trellis construction are presented below[22].

- Left index L(X) of X: Given a nonzero vector  $X = (x_1, x_2, ..., x_n)$  over GF(q), L(X) denotes the smallest integer i such that  $x_i \neq 0$ .

- Row-reduced echelon matrix: Given a  $k \times n$  matrix  $G = [x_{i,j}]$  over GF(q), G is in row-reduced echelon form if the rows  $X_1, X_2, ..., X_k$  of G are such that  $L(X_1) < L(X_2) < ... < L(X_k)$ , and the k columns found at positions  $L(X_i)$ : i = 1, 2,..., k in G are all of weight one.

In what follows we discuss Massey construction of minimal trellis. Let linear code C(n,k) be constructed by row-reduced echelon generator matrix G[k,n]. The left indices of its rows is denoted as  $\gamma_1, \gamma_2, ..., \gamma_k$ . This implies that  $\gamma_1 < \gamma_2 < ... < \gamma_k$  and the k positions  $\gamma_1, \gamma_2, ..., \gamma_k$  form the information bits for code C.

The Massey trellis T = (V, B, L) for code C is constructed by identifying the vertices in  $V_i$  at time i: i = 0, 1, 2, ..., n. Let m be the largest integer such that  $\gamma_m \le i$ , then  $V_i$  is defined as

$$V_i = \{(c_{i+1}, ..., c_n) \cdot (c_1, ..., c_n) = (u_1, ..., u_m, 0, ..., 0)G\}$$

(2.12)

By convention,  $V_0 = \{0\}$  and  $V_n = \{\emptyset\}$  where  $\emptyset$  is the empty string.

The branch set of T is defined as follows in two cases:

• In the case  $i > \gamma_m$ , there is a branch  $b \in B_i$  from a vertex  $v \in V_{i-1}$  to a vertex  $v' \in V_i$  if and only if there exists a codeword  $(c_1, c_2, ..., c_n) \in C$ , such that

$$(c_i, c_{i+1}, ..., c_n) = v$$

$(c_{i+1}, ..., c_n) = v'$

$$(2.13)$$

the branch label is  $c_i$ . In this case, there is exactly one branch beginning at  $\nu$  for each vertex  $\nu \in V_{i-1}$ .

• In the case  $i = \gamma_m$ , there is a branch  $b \in B_i$  from a vertex  $v \in V_{i-1}$  to a vertex  $v' \in V_i$  if and only if there exists a pair of codeword  $c = (c_1, c_2, ..., c_n)$  and  $c' = (c_1', c_2', ..., c_n')$  in C such that

$$(c_i, c_{i+1}, ..., c_n) = v$$

$(c_{i+1}', ..., c_n') = v'$

(2.14)

and either c'=c or  $\beta(c'-c)$  equals the *m*-th row of G for some constant  $\beta \in GF(q)$ . The branch label is  $c_i'$ , and the number of out-going branch for each  $v \in V_{i-1}$  is q.

In this thesis, RM(32,26) code is used as constituent code. According to Section 2.2.1, the generator matrix G of RM(32,26) is constructed, and modified to be a row-reduced echelon form as follows.

| 000000000000000000000000000000000000000 |

|-----------------------------------------|

| 000000000000000000000000000000000000000 |

As indicated in  $G_{RM(32,26)}$ , the information bit can be directly obtained in the position of  $k_i$  in which the weight is equal to one.

The *RM*(32,26) trellis diagram is too complex with 638 vertices (states) and 1180 branches to draw in this size paper. However, we can follow the state profile at each time instant to get a simple illustrative drawing. Figure 4.7 in page 61 can be used as a reference.

## 2.4 Trellis-based MAP algorithm

Since the MAP algorithm for trellis codes was proposed by [14], there has been many papers published concerning the MAP and its sub-optimum variants. Following

[17], we discuss the MAP algorithm in detail in order to provide a guide for later modified algorithm and implementation in this thesis.

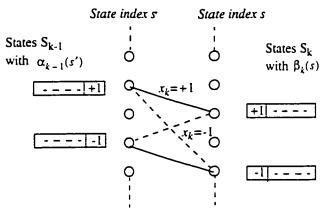

It is well known that codeword of a linear binary (N,K) block code can be represented as the paths through a trellis of depth n with at most  $2^{N-K}$  states[17,21]. Also due to the irregularity of the trellis of linear block code and the complexity of trellis of RM(32,26) code, one section of a trellis diagram is shown in Figure 2.5 to facilitate the description of the structure.

Figure 2.5 One section of trellis structure of block code

Let  $S_k$  and  $S_{k-1}$  denote the state set at times k and k-1; the trellis states at times k-1 and k are indexed by s' and s. The coded bit  $x_k$  at time k is the label of the branch linking the states at times k-1 and k. The soft-output of MAP algorithm conditioned on information sequence  $\hat{y}$  is

$$L(\hat{x}_k) = \log \frac{P(x_k = 1 | \hat{y})}{P(x_k = -1 | \hat{y})} = \log \frac{\sum_{\substack{(s, s) \\ (s, s)}} p(s', s, \hat{y})}{\sum_{\substack{(s, s) \\ (s, s)}} p(s', s, \hat{y})}$$

$$(2.16)$$

The sums in the numerator and denominator of  $p(s', s, \mathring{y})$  are taken over all existing transition from state s' to s labeled with the coded bit  $x_k = +1$  and  $x_k = -1$ , respectively. Under the memoryless channel assumption, the joint probability  $p(s', s, \mathring{y})$  can be written as

$$p(s', s, \mathring{y}) = p(s', \mathring{y}_{j < k}) \cdot p(s, \mathring{y}_{k} | s') \cdot p(\mathring{y}_{j > k} | s)$$

$$= p(s', \mathring{y}_{j < k}) \cdot P(s | s') \cdot p(\mathring{y}_{k} | (s', s)) \cdot p(\mathring{y}_{j > k} | s)$$

$$= \alpha_{k-1}(s') \cdot \gamma_{k}(s', s) \cdot \beta_{k}(s)$$

(2.17)

Here  $\mathfrak{F}_{j < k}$  denotes the part of the received sequence from bit 0 up to bit k-1, and  $\mathfrak{F}_{j > k}$  corresponds to the sequence part from bit k+1 up to bit n-1. The  $\alpha_k(s)$  and  $\beta_{k-1}(s')$ , namely forward recursion and backward recursion accordingly, of the MAP algorithm are

$$\alpha_k(s) = \sum_{s'} \gamma_k(s', s) \cdot \alpha_{k-1}(s')$$

(2.18)

$$\beta_{k-1}(s') = \sum_{s} \gamma_k(s', s) \cdot \beta_k(s)$$

(2.19)

In the above two equations, we assume that at time k=0 and k=n,  $\alpha_0(0)=1$  and  $\beta_n(0)=1$ . The branch transition probabilities  $\gamma_k(s',s)$  between s' and s for systematic block code with statistically independent information bits are given

$$\gamma_k(s', s) = P(s|s') \cdot p(y_k|s', s) = p(x_k; y_k)$$

(2.20)

with  $p(x_k; y_k)$  defined as

$$p(x_k; y_k) = \begin{cases} p(y_k | x_k) \cdot P(x_k) & 1 \le k \le K \\ p(y_k | x_k) & K+1 \le k \le N \end{cases}$$

(2.21)

Furthermore, the log-likelihood ratio associated with  $p(x_k; y_k)$  can be obtained by defining following equation.

$$L(x_k; y_k) = \begin{cases} L_c \cdot y_k + L(x_k) & 1 \le k \le K \\ L_c \cdot y_k & K + 1 \le k \le N \end{cases}$$

(2.22)

By omitting the common terms for all transition from time k-l to k, the branch transition probabilities can rewritten as

$$\gamma_{k}(s', s) = e^{(L(x_{k}; y_{k}) \cdot x_{k}/2)}

= \begin{cases} e^{[L_{c} \cdot y_{k} + L(x_{k})] \cdot x_{k}/2} & 1 \le k \le K \\ e^{L_{c} \cdot y_{k} \cdot x_{k}/2} & K + 1 \le k \le N \end{cases}$$

(2.23)

Finally, the soft-output of the trellis-based MAP algorithm for block code can be written as

$$L(\hat{x}_{k}) = L_{c} \cdot y_{k} + L(x_{k}) + \log \frac{x_{k} = 1}{\sum_{(S', S)} \alpha_{k-1}(s') \cdot \beta_{k}(s)}$$

$$= L_{c} \cdot y_{k} + L(x_{k}) + L_{e}(\hat{x}_{k})$$

$$= L_{c} \cdot y_{k} + L(x_{k}) + L_{e}(\hat{x}_{k})$$

(2.24)

The above Equation is the foundation of our design. We also look into the complexity of the computing process. Because it is computation-intensive, it is impractical to implement it using current techniques. Therefore, the simplified sub-optimal algorithm, called Max-Log-MAP, and its implementation are derived from the above Log-MAP algorithm.

## 2.5 Summary

On the basis of linear block turbo code, the Reed-Muller turbo code used in this thesis was discussed in detail. The construction of minimal trellis of RM code and trellis-based MAP decoding algorithm were presented. The PCCC turbo code scheme used in this thesis and iterative decoding approach as well as SISO decoder were explained in detail. Taking complexity of MAP algorithm into account, we will discuss the alternative decoding algorithms suitable for implementation in next chapter.

## Chapter 3

## Algorithms for implementation

#### 3.1 Introduction

In turbo decoding, two kinds of algorithms have been commonly used, the SOVA and the MAP algorithm[19].

For estimating the states or the outputs of a Markov process observed in a memoryless channel, the symbol-by-symbol maximum a posteriori (MAP) algorithm is optimal. However, MAP algorithm is likely to be considered too complex to implement in practice; basically because MAP decoding involves the non-linear function, and it requires a large number of memories and operations for exponentiation and multiplication. Log-MAP algorithm can be used to convert the multiplication into addition and to avoid exponential function, Log-MAP is equivalent to MAP and has the same performance as the MAP algorithm. The Log-MAP can be further simplified using Max-Log-MAP algorithm, which has been derived for simplifying the representation of probabilities and for reducing the computational complexity. It is sub-optimal compared to MAP but easy to implement without significant performance degradation [23-26]. In the additive white Gaussian noise (AWGN) channels, the Log-MAP is about 0.5 dB better than SOVA at low SNR region[65]. In this Chapter, we first discuss Max-Log-MAP and Log-MAP algorithms fol-

lowing [15,16,24], then a modified version of Max-Log-MAP with look-up table correction used in this thesis will be given.

## 3.2 Max-Log-MAP algorithm

In order to simplify the computation of Equation (2.24), to avoid the logarithmic operation and multiplication in the numerator and denominator, logarithmic function of forward recursion  $\alpha_k(s)$ , backward recursion  $\beta_{k-1}(s')$  and transition probabilities  $\gamma_k(s',s)$  are used.

First we give the notation and definitions used in following Equations: subscript k refers to the time instant k; s' and s represent state or node at time instant k-1 and k; S' and S represent the state set at time instant k-1 and k; K and N are turbo code information bit lengths and coded word lengths, respectively.

From Equation(2.23) we obtain

$$\log \gamma_k(s',s) = \frac{L(x_k, y_k) \cdot x_k}{2} = \begin{cases} \frac{[L_c \cdot y_k + L(x_k)] \cdot x_k}{2} & 1 \le k \le K \\ \frac{L_c \cdot y_k \cdot x_k}{2} & K+1 \le k \le N \end{cases}$$

(3.1)

In the logarithmic domain, the following approximation is used to simplify the computation of  $\alpha_k(s)$  and  $\beta_{k-1}(s')$ . That is

$$\log(e^{\delta_1} + e^{\delta_2} + \dots + e^{\delta_n}) \approx Max_{i \in \{1, 2\dots n\}} \delta_i$$

(3.2)

where  $Max_{i \in \{1, 2...n\}} \delta_i$  can be calculated by successively computing (n-1) maximum function over only two values.

Referring to Equation (3.2), we can obtain the logarithm of forward recursion

$$\log \alpha_k(s) = \log \sum_{S'} \gamma_k(s', s) \cdot \alpha_{k-1}(s')$$

$$= Max_S[\log \gamma_k(s', s) + \log \alpha_{k-1}(s')]$$

$$= Max_{S'} \left[ \frac{L(x_k, y_k) \cdot x_k}{2} + \log \alpha_{k-1}(s') \right]$$

(3.3)

with the initial condition  $\log \alpha_0(0) = 0$  at time k = 0.

Similarly, the logarithm of backward recursion is obtained as follow

$$\log \beta_{k-1}(s') = \sum_{S} \gamma_k(s', s) \cdot \beta_k(s)$$

$$= Max_S[\log \gamma_k(s', s) + \log \beta_k(s)]$$

$$= Max_S \left[ \frac{L(x_k, y_k) \cdot x_k}{2} + \log \beta_k(s) \right]$$

(3.4)

with the initial condition  $\log \beta_n(0) = 0$  at time k = n.

For the extrinsic information output, the approximate form is given as:

$$\sum_{(S',S)} \alpha_{k-1}(s') \cdot \beta_{k}(s)$$

$$L_{e}(x_{k}) = \log \frac{x_{k} = 1}{\sum_{(S',S)} \alpha_{k-1}(s') \cdot \beta_{k}(s)}$$

$$x_{k} = -1$$

$$= Max_{(S',S)} [\log \alpha_{k-1}(s') + \log \beta_{k}(s)]$$

$$x_{k} = 1$$

$$-Max_{(S',S)} [\log \alpha_{k-1}(s') + \log \beta_{k}(s)]$$

$$x_{k} = -1$$

(3.5)

Consequently, we obtain the logarithm of soft-output of MAP algorithm in the approximate form as follows:

$$L(\hat{x}_{k}) = L_{c} \cdot y_{k} + L(x_{k}) + L_{e}(\hat{x}_{k})$$

$$\sum_{(S', S)} \alpha_{k-1}(S') \cdot \beta_{k}(S)$$

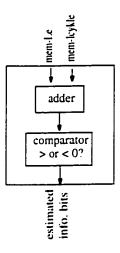

$$= L_{c} \cdot y_{k} + L(x_{k}) + \log \frac{x_{k} = 1}{\sum_{(S', S)} \alpha_{k-1}(S') \cdot \beta_{k}(S)}$$