#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand comer and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# Diagnosis and Yield Analysis of a Complex Interconnection Architecture

Bing Qiu

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfilment of the Requirements for the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

March 2003

©Bing Qiu, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your tile Votre référence

Our Sie Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-77688-3

#### **ABSTRACT**

## Diagnosis and Yield Analysis of a Complex Interconnection Architecture

## Bing Qiu

This thesis investigates problems associated with the integration of very large fault-tolerant networks. The focus of the research is on the diagnosis and yield analysis of a complex interconnection architecture. In this thesis, a closed form yield model that takes into account constraints of an architecture has been proposed. It applies to architectures that approximate global redundancy and for which the constraints translate into yield losses. The impact of the constraints on yield can be evaluated by calculating the probability of observing non-tolerable defect patterns and by subtracting these probabilities from yield of arrays with global redundancy. It has been shown that most of the yield losses come from a few patterns comprising small number of defects. According to the characteristics of the analyzed architecture and the nature of defect distributions, different yield models have been derived. With these models, the sensitivity of the yield of the analyzed architecture to variations of the defect density has been investigated. This thesis also proposes regression yield models that can be used to quickly predict the redundancy needed for given array and cell sizes as part of a design flow.

# Acknowledgements

This thesis owes its existence to the help, support, and inspiration of many people.

In the first place, I would like to express my sincere appreciation and gratitude to my Supervisors, Dr. Chunyan Wang and Dr. Yvon Savaria, for their support and encouragement throughout my graduate studies. I am also indebted to Dr. Claude Thibeault for his help and the fruitful discussions on my research.

The discussions and cooperations with all of my colleagues have contributed substantially to this research: Meng Lu, Normand Leclerc, Renault Tiennot, and Karl Fecteau. I also extend my appreciation to all for their assistance and support.

Finally, I owe special gratitude for the unconditional support, understanding and love that I received from my wife, He Zhang, and my parents during the past years.

# **Table of Contents**

| List of Figures                                                  | vii |

|------------------------------------------------------------------|-----|

| List of Tables                                                   | X   |

| List of Acronyms                                                 | xii |

| List of Primary Symbols                                          | xii |

| 1. Introduction                                                  | 1   |

| 1.1 Introduction                                                 |     |

| 1.2 Motivation and objective                                     | 4   |

| 1.3 Scope and organization of the thesis                         | 5   |

| 2. Analysis of a Complex Interconnection Architecture            |     |

| 2.1 Introduction to fault tolerance mechanism                    |     |

| 2.2 Complex interconnection architecture                         |     |

| 2.2.1 Overview of the fault-tolerant architecture                |     |

| 2.2.2 Configuration of the transmitter multiplexers of a cell    | 13  |

| 2.2.3 Configuration of the receiver multiplexers of a cell       | 14  |

| 2.3 Reconfiguration strategies of the fault-tolerant structure   |     |

| 2.3.1 Basic reconfiguration strategies                           | 16  |

| 2.3.2 Reconfiguration of cells in the fault-tolerant structure   |     |

| 2.3.3 Reconfiguration of bundles in the fault-tolerant structure |     |

| 2.4 Summary                                                      |     |

| 3. Yield Modeling of a Complex Interconnection Architecture      | 27  |

| 3.1 Introduction to yield analysis and yield models              | 27  |

| 3.1.1 Defects and faults                                         |     |

| 3.1.2 Review of basic yield models                               |     |

| 3.1.3 Yield modeling for circuits with redundant structures      |     |

| Appendix D Derivation of the regression yield model                               |              |

|-----------------------------------------------------------------------------------|--------------|

| Appendix C Analytical proof related to the second most significant                | 1 <i>7</i> 0 |

| Appendix B Thirteen kinds of non-tolerable patterns                               | 110          |

| Appendix A Terminology and replacement rules of the fault-tolerant structure1     |              |

| References                                                                        |              |

|                                                                                   |              |

| 5.2 Suggestion for future research                                                | 98           |

| 5.1 Summary of the work                                                           | 95           |

| 5. Conclusion                                                                     | 95           |

| 4.5 Summary                                                                       | .,,,         |

| 4.5 Summary                                                                       |              |

| 4.4 Yield model regression with clustered defects                                 |              |

| 4.3.2 Effects of clustered defects on the yield of forming logical arrays         |              |

| 4.3 Numerical result of the yield with clustered defects                          |              |

| 4.2.2 Yield modeling with all sub-circuits assumed statistically dependent        |              |

| 4.2.1 Yield modeling with identical sub-circuits assumed statistically dependent. |              |

| 4.2 Yield modeling for the architecture assuming clustered defects                |              |

| 4.1 Introduction to yield formulas when defects are clustered                     |              |

| 4. Analysis of the effects of clustered defects on yield                          |              |

|                                                                                   |              |

| 3.5 Summary                                                                       | .60          |

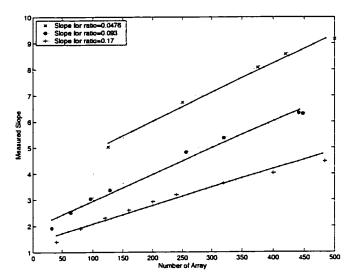

| 3.4 Yield model regression                                                        | 57           |

| 3.3 Defect density impact on forming a logical array                              | 56           |

| 3.2.2.2 Non-tolerable patterns with defective bundles and cells                   | 44           |

| 3.2.2.1 Non-tolerable patterns in the array with fault-free bundles               | 41           |

| 3.2.2 Non-tolerable patterns in an array of designated size                       | 41           |

| 3.2.1 Constraints-based yield model                                               | 33           |

| 3.2 Yield modeling for a complex interconnection architecture                     | 33           |

| Appendix E | Derivation of $Y_{cell}$ with Maxwell-Boltzman combinatorial statistics | 127 |

|------------|-------------------------------------------------------------------------|-----|

| Appendix F | Derivation of the formulas with Maxwell-Boltzman statistics             |     |

|            | and Bose-Einstein statistics                                            | 129 |

# **List of Figures**

| Figure 1.1  | A proposed architecture organized as a processing array of                      |      |

|-------------|---------------------------------------------------------------------------------|------|

|             | size 20 x20                                                                     | 4    |

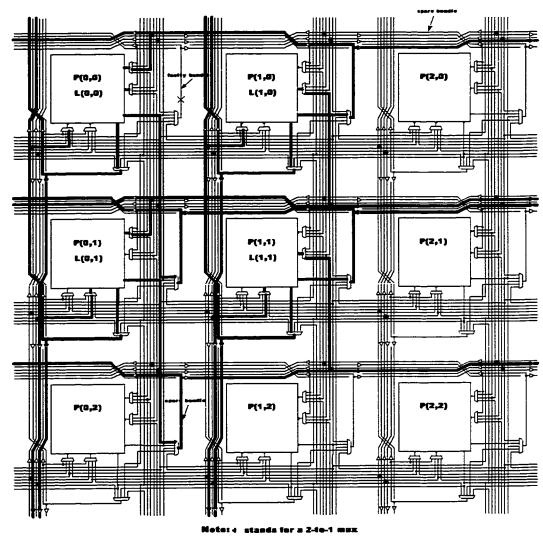

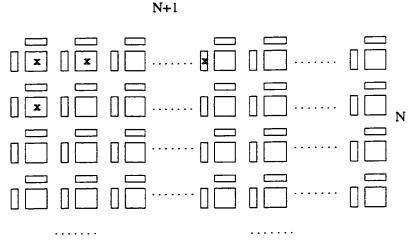

| Figure 2.1  | Processing array of size K x L based on the architecture in [27]-[29]           | 10   |

| Figure 2.2  | Interconnection structure of a physical array of size 3x3 based on the          |      |

|             | architecture in [27]-[29]                                                       | 12   |

| Figure 2.3  | Configuration of the transmitter multiplexers of cells                          | 13   |

| Figure 2.4  | Configuration of receiver multiplexers of cells in a 3x3 physical array         | 15   |

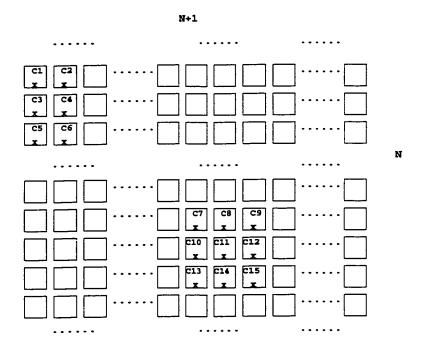

| Figure 2.5  | Example of using the cell-stealing strategy to construct a logical              |      |

|             | array of 2x3 out of a physical array of 3x3                                     | 17   |

| Figure 2.6  | Example of using the cell-shifting strategy to construct a logical array of     | 2x2  |

|             | out of a physical array of 3x2                                                  | 18   |

| Figure 2.7  | Example of using the column or row exclusion strategy to construct a logic      | ical |

|             | array of 2x2 from a physical array of 3x2                                       | 19   |

| Figure 2.8  | Using the cell-stealing strategy to construct a 3x2 logical array from          |      |

|             | 3x3 physical array based on the architecture in [27]-[29]                       | 20   |

| Figure 2.9  | Using the perfect replacement with cell-shifting strategy to build a $2x2 \log$ | ical |

|             | array from a 3x3 physical array                                                 | 21   |

| Figure 2.10 | Using the imperfect replacement with cell-shifting strategy to construct        |      |

|             | a 2x2 logical array from a 3x3 physical array                                   | 22   |

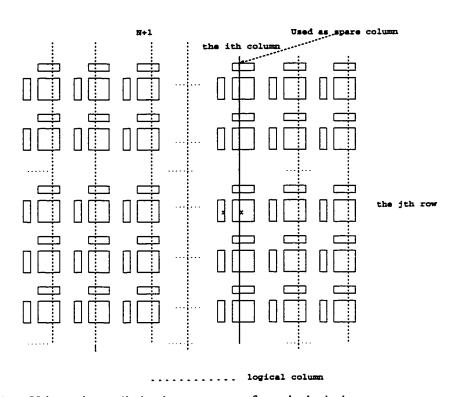

| Figure 2.11 | Intra-bus replacement in the fault-tolerant structure                           | 24   |

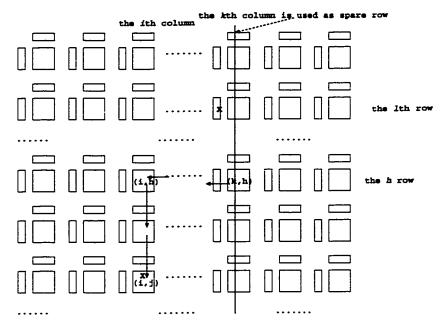

| Figure 2.12 | Inter-bus replacement in the fault-tolerant structure                           | 25   |

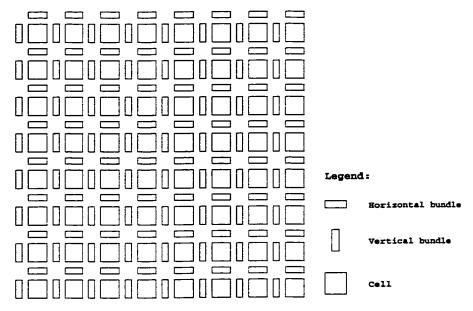

| Figure 3.1  | Simplified diagram of a 8 by 8 physical array based on the architecture         |      |

|             | in [27]-[29]                                                                    | 36   |

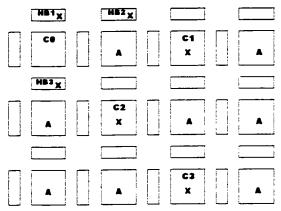

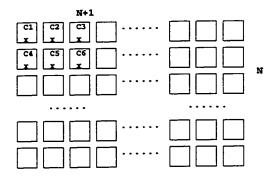

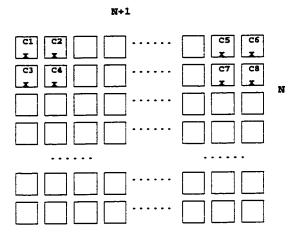

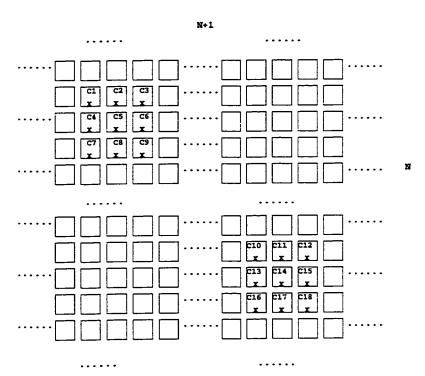

| Figure 3.2  | Pattern preventing the construction of a logical array size of 3 by 3           |      |

|             | out of a physical array of 4x3                                                  | 38   |

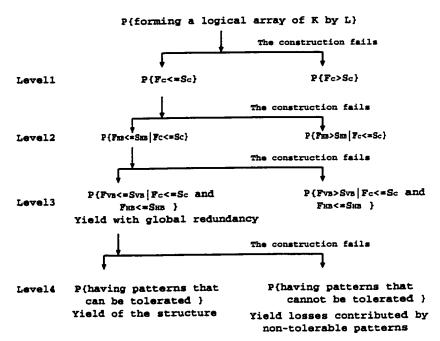

| Figure 3.3  | Flow chart of the probability of forming a logical array                        | 38   |

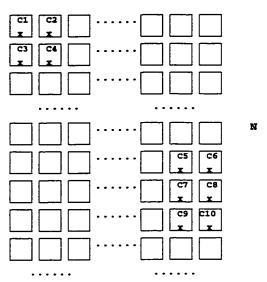

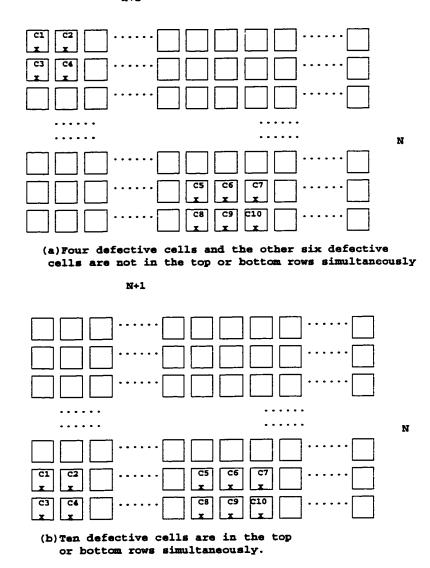

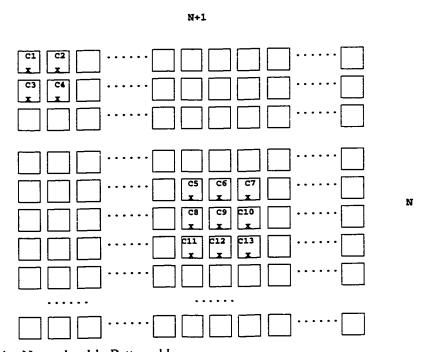

| Figure 3.4  | Non-tolerable pattern is composed of the least number of defective            |     |

|-------------|-------------------------------------------------------------------------------|-----|

|             | cells in an array without defective bundles                                   | .42 |

| Figure 3.5  | Six defective cells in a corner prevent the construction of a logical         |     |

|             | array of NxN                                                                  | .42 |

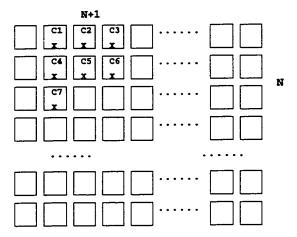

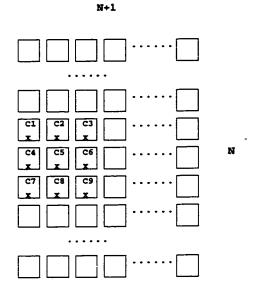

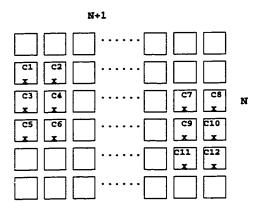

| Figure 3.6  | Non-tolerable Pattern 1 in a physical array of (N+1) x N                      | .45 |

| Figure 3.7  | Not allowed replacement for two defective vertical bundles                    | .47 |

| Figure 3.8  | Non-tolerable Pattern 2 in a physical array of (N+1) x N                      | .48 |

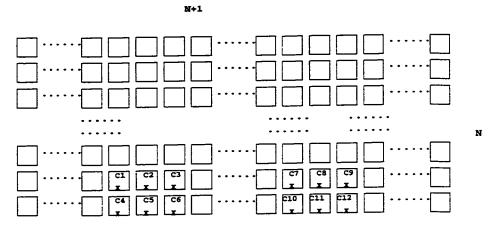

| Figure 3.9  | The first possibility of forming a logical array of NxN from a physical array | y   |

|             | of (N+1)xN with the existence of non-tolerable Pattern 2                      | .49 |

| Figure 3.10 | The second possibility of forming a logical array of NxN from a physical arr  | ay  |

|             | of (N+1)xN with the existence of non-tolerable Pattern 2                      | .50 |

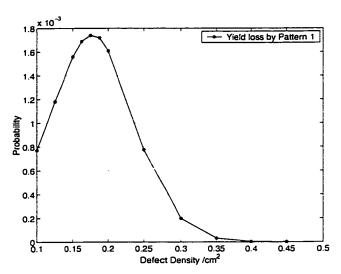

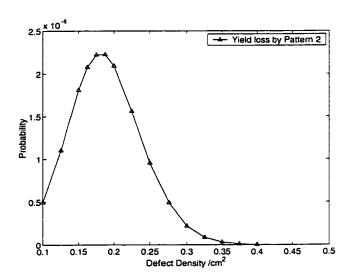

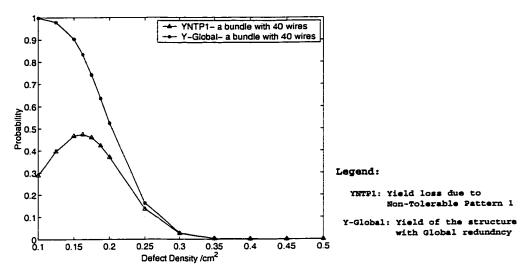

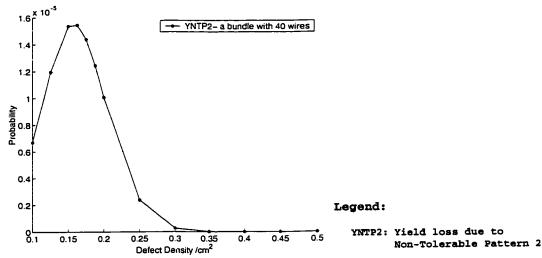

| Figure 3.11 | Yield loss contributed by the most significant non-tolerated pattern          | .53 |

| Figure 3.12 | Yield loss contributed by the second most significant non-tolerable pattern.  | .53 |

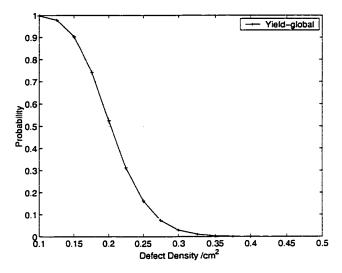

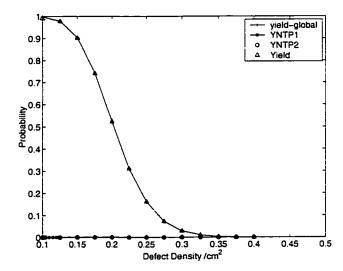

| Figure 3.13 | Yield of the structure with global redundancy                                 | .54 |

| Figure 3.14 | Comparison between Y <sub>loss</sub> and Y <sub>global</sub>                  | .54 |

|             | Yield loss by the first most significant non-tolerable pattern                |     |

|             | when a bundle comprises 40 wires                                              | .56 |

| Figure 3.16 | Yield loss by the second most significant non-tolerable pattern               |     |

|             | when a bundle comprises 40 wires                                              | .56 |

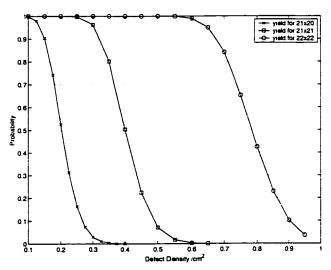

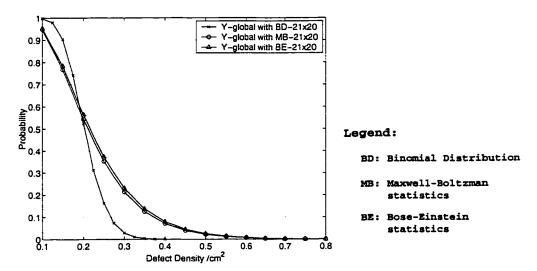

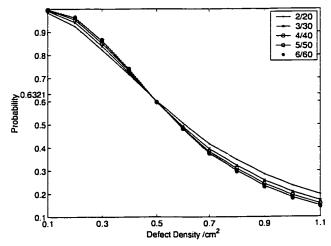

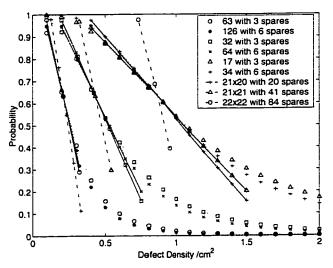

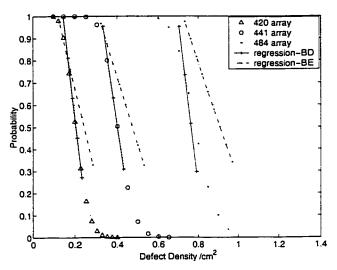

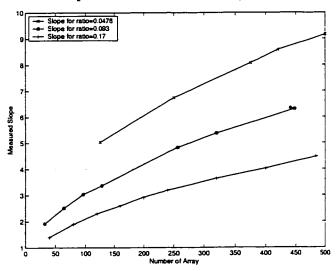

| Figure 3.17 | Yield of forming a logical array of 20x20 from physical arrays                |     |

|             | of 21x20, 21x21, and 22x22                                                    | .57 |

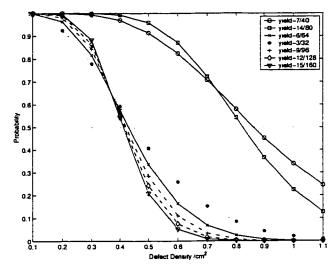

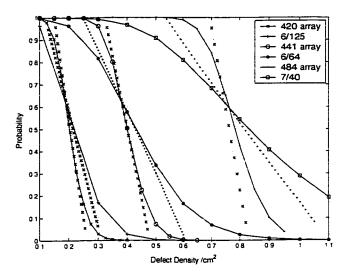

| Figure 3.18 | Cross points for arrays of different sizes with equivalent redundancy ratio . | .58 |

| Figure 3.19 | Comparison of the regression model and the complete yield model               | .60 |

| Figure 4.1  | Effect of clustered defects on a conventional chip yield(from [17])           | .63 |

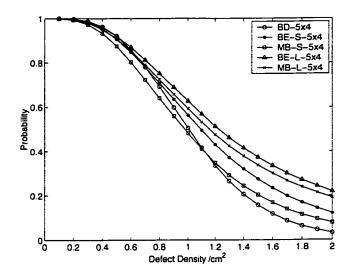

| Figure 4.2  | Effects of clustered defects on the yield of forming a logical array of       |     |

|             | 20x20 from a physical array of 21x20                                          | .79 |

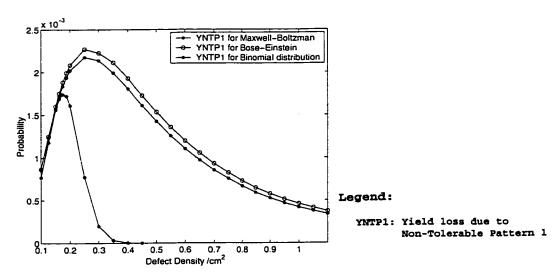

| Figure 4.3  | Effects of clustered defects on the yield loss contributed by the first       |     |

|             | most significant non-tolerable pattern in forming a logical array             |     |

|             | of 20 by 20 from a physical arrays of 21x20                                   | .80 |

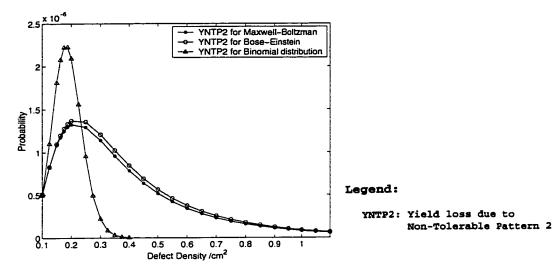

| Figure 4.4  | Effects of clustered defects on the yield loss contributed by the second most |     |

|             | significant non-tolerated pattern                                             | .81 |

| Figure 4.5  | Yield and yield losses due to two most significant non-tolerable patterns  |     |

|-------------|----------------------------------------------------------------------------|-----|

|             | at higher clustered defect density in forming a logical array of size      |     |

|             | 20x20 out of a physical array of size 21x20                                | .82 |

| Figure 4.6  | Yield loss contributed by the first most significant non-tolerant pattern  |     |

|             | in forming a logical array of 5x5 from a physical array of 6x5             | .84 |

| Figure 4.7  | Yield loss contributed by the second most significant non-tolerant pattern |     |

|             | in forming a logical array of 5x5 from a physical array of 6x5             | .84 |

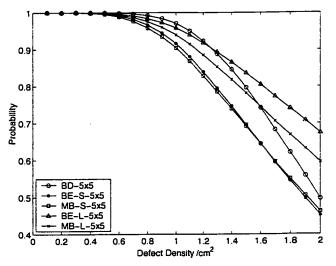

| Figure 4.8  | Yield of forming logical arrays size of 20x20 from physical array of       |     |

|             | 21x20, 21x21, and 22x22                                                    | .86 |

| Figure 4.9  | Comparison of the yields computed with different equations in              |     |

|             | constructing a logical array of 4x4 from a physical array of 5x4           | .88 |

| Figure 4.10 | Comparison of the yields calculated with different equations in            |     |

|             | constructing a logical array of 4x4 from a physical array of 5x5           | .88 |

| Figure 4.11 | Yield of arrays with equivalent redundancy ratio, computed with (4.27),    |     |

|             | (4.35), and (4.36) using Bose-Einstein statistics                          | .89 |

| Figure 4.12 | Comparison between the regression model and the yield model                |     |

|             | assuming Bose-Einstein distribution                                        | .91 |

| Figure 4.13 | Comparison of the yield predicted by regression model with the clustered   |     |

|             | defect distribution and the random defect distribution                     | .92 |

# **List of Tables**

| Table 3.1 | Yield of a bundle, a cell, and the reconfiguration logic within one cell. The      |

|-----------|------------------------------------------------------------------------------------|

|           | data comes from a WSI demonstration chip33                                         |

| Table 3.2 | Yield of a bundle, a cell and the reconfiguration logics within one cell. The      |

|           | data comes from the proposed WSI architecture33                                    |

| Table 3.3 | Yield losses contributed by thirteen kinds of significant non-tolerable patterns   |

|           | in the construction of a logical array of Nxn from a physical array of             |

|           | (N+1)xN43                                                                          |

| Table 3.4 | Numerical value of the pivot points of physical arrays of different sizes with     |

|           | redundancy ratio equal to 0.158                                                    |

| Table 4.1 | Computation time of one numerical point of the yield loss curves in forming        |

|           | a logical array of size 20x20 from a physical array of size 21x20, where a         |

|           | bundle comprises 40 wires with an area 11mm <sup>2</sup> and the area of a cell is |

|           | 25mm <sup>2</sup> 83                                                               |

| Table 4.2 | Numerical value of the approximate pivot points for arrays with redundancy         |

|           | ratio equal to 0.1. It is assumed that defects comply to Bose-Einstein             |

|           | distribution90                                                                     |

| Table 4.3 | Computation time for one numerical point of different yield curves in forming      |

|           | a logical array of 20x20 from a physical array of 21x21, where a bundle            |

|           | comprises 40 wires with an area 11mm <sup>2</sup> and the area of a cell is        |

|           | 25mm <sup>2</sup> 93                                                               |

# **List of Acronyms**

ASIC Application Specific Integrated Circuit

CMOS Complementary Metal Oxide Semiconductor

EE an Equivalent-area Element

IC Integration Circuit

JTAG Joint Test Action Group

LSI Large-Scale Integration

MSI Medium-Scale Integration

SoC System on Chip

SSI Small-Scale Integration

VLSI Very Large Scale Integration

WSI Wafer Scale Integration

## **List of Primary Symbols**

A the critical area of a circuit

α a clustering parameter

D the defect density of a chip

$G_{xy}$ ; the probability of all x defects being distributed over  $y_i$  EEs so that each of

these yi EEs has at least one defect

F<sub>c</sub> number of defective cells

F<sub>HB</sub> number of defective horizontal bundles

F<sub>VB</sub> number of defective vertical bundles

$i_{\rm m}$  the number of the defective EEs in the cells

j<sub>t</sub> the number of the defective EEs in the vertical bundles

k<sub>p</sub> the number of the defective EEs in the horizontal bundles

$\lambda$  the expected number of defects per chip

m the number of cells in a physical array of size K by L, i.e.,  $m=K\times L$

n<sub>c</sub> the total number of EEs in a cell

$n_{VB}$  the total number of EEs in a vertical bundle

n<sub>HB</sub> the total number of EEs in a horizontal bundle

N<sub>c</sub> number of cells in a column or a row

N<sub>HB</sub> number of horizontal bundles in a column or a row

N<sub>VB</sub> number of vertical bundles in a column or a row

NTC<sub>cell</sub> number of non-tolerable patterns when F<sub>C</sub> defective cells are distributed

over a complete array

$NTC_{HB}$  number of non-tolerable patterns when  $F_{HB}$  defective horizontal bundles

are distributed over a complete array

NTC<sub>VB</sub> number of non-tolerable patterns when F<sub>VB</sub> defective vertical bundles are

distributed over a complete array

Q<sub>c</sub> total number of cells

Q<sub>VB</sub> total number of vertical bundles

Q<sub>HB</sub> total number of horizontal bundles

$P_{xF_c}$  the probability of having all x defects distributed over  $F_c$  cells such that

each cell has at least one defect

$P_{vF_{vB}}$  the probability of having all y defects distributed over  $F_{VB}$  vertical bundles

such that each vertical bundle has at least one defect

$P_{zF_{IIB}}$  the probability of having all z defects distributed over  $F_{HB}$  horizontal

bundles such that each horizontal bundle has at least one defect

$P_{tx}$  the probability that x defects in the structure can be tolerated

r the redundancy ratio of a physical array of size K by L

S<sub>c</sub> number of spare cells

S<sub>VB</sub> number of spare vertical bundles

S<sub>HB</sub> number of spare horizontal bundles

$y_i(i=1,2,...,7)$  the total number of defective EEs in the i<sup>th</sup> item

y<sub>cell</sub> the yield of a cell

y<sub>HB</sub> the yield of a horizontal bundle

y<sub>VB</sub> the yield of a vertical bundle

Y<sub>chin</sub> the true yield of the structure

Y<sub>global</sub> the yield of the structure assuming global redundancy

Y<sub>loss</sub> the operability of having non-tolerable defect patterns in the structure

(Y<sub>NTP</sub>)<sub>i</sub> the yield loss due to the i<sup>th</sup> non-tolerable pattern of the structure

# Chapter 1 Introduction

## 1.1 Introduction

Since the implementation of the first integrated circuits (ICs) in the mid 1960s, the IC technologies have developed rapidly. Early small-scale integration (SSI) ICs contained several logic gates amounting to tens of transistors. Then, medium-scale integration (MSI) increased the range of integrated logic gates available to larger scale functions. In the era of large-scale integration (LSI), much complex logic functions, such as those of the first microprocessors, were packed into a single chip. The further improvement of CMOS process technologies led to the advent of very large scale integration (VLSI) in the 1980s. In this era, VLSI technologies could offer complete 64-bit microprocessors with cache memory circuits and floating-point arithmetic units on a single piece of silicon. More than a million transistors can be integrated in a chip with these technologies. Today, advanced VLSI technologies, particularly deep-submicron technologies, can integrate almost one billion transistors in a single chip. These state-of-the-art technologies make it possible to implement all aspects of a system design on a single chip, referred to System-on-Chip (SoC) circuits. SoC eliminates many off-chip driver circuits, the associated delay time and power consumption. Furthermore, the availability of rich on-chip wiring may allow a substantial increase in the data bandwidth between cores in the chip, thus improving the performance.

Implementing a system on a single chip implies that the integration density of a chip needs to increase greatly. Evidently there are two ways to achieve this target. One is to reduce the transistor size, and the other is to increase the area of a single chip. The former is the well-known feature size scaling technology, the dominant approach in the semiconductor industry. With the advent of deep submicron VLSI technologies, the feature size of a CMOS transistor has been scaled down to 0.10 µm from 1.0 µm of ten years ago. Different from the feature size scaling, enlarging the area of a single chip to increase the integration density of ICs is also very attractive to the semiconductor industry. A fascinating technology to enlarge the chip area is Wafer Scale Integration (WSI). This technology enables the fabrication of a single chip as large as the maximum wafer diameter in commercial manufacturing. Since Sack and his colleagues first attempted to implement an array comprising some simple logical circuits on a single wafer in 1964 [32], WSI technology has attracted the interest of the electronics industry and the academic community for decades. A large number of issues associated with WSI have been studied. The technological features to distinguish WSI from other integrated circuit arts are associated with the management of the special problems of large substrates, such as yield, interconnection, packaging and thermal dissipation. Among them, a very typical feature is using fault tolerance techniques to lower the impact of manufacturing defects and to increase the yield of WSI components [7].

Wafer scale integration emerges as a natural evolution from the device-oriented VLSI chip technologies to system-oriented wafer-level technologies. Due to the limitation of the VLSI technologies in the past years, the broad investigations of WSI issues have not led to mass commercial wafer-scale production. With the advent of deep submicron VLSI

technology, WSI is widely regarded as a technically feasible proposal for systems that possess enough regularity and reconfigurability in their architectures. WSI technology allows building a system with two orders of magnitude more active devices than VLSI circuits, and it eliminates all intermediate levels of packaging or bonding. Compared with systems implemented with VLSI circuit chips mounted on printed circuit boards, WSI systems provide much more potential benefits such as significant speed improvement and higher data communication bandwidth. Although WSI systems possess many attractive potential advantages, there exist a number of practical problems associated with WSI design and manufacturing. The problems can be classified as physical design problems and electrical design problems [43]. For instance, in the physical design problems, packaging is the most difficult problem facing WSI. A WSI package should provide the mechanical support and hermetic sealing with a cavity size large enough to accommodate an entire wafer. Moreover, a suitable packaging technology must take into account heat dissipation and thermal expansion. The latter problem represents serious challenges when packaging materials and the wafer material have differences in thermal expansion coefficients. Among the electrical design problems, power supply distribution, synchronization, signal integrity, extremely long interconnections, fault tolerance and the yield of a WSI system, all pose unique challenges to the implementation of WSI technology.

## 1.2 Motivation and objective

A system implemented with WSI can potentially provide multi-terabit switching and rich data communication bandwidth between cores in the system. These potential benefits

address special circuit needs for ever-increasing speed and bandwidth in telecommunication applications. For telecom routers, the demand for increased bandwidth to process large amount of data requires growing performances. Chip-based router architectures are already reaching their limits, and a superior technology is needed to alleviate this bottleneck. To meet this requirement, a highly parallel router architecture involving a large number of routing nodes was proposed by Richard S. Norman of Hyperchip Inc. [27]-[29], and the related circuit structures have been designed to enable WSI [1].

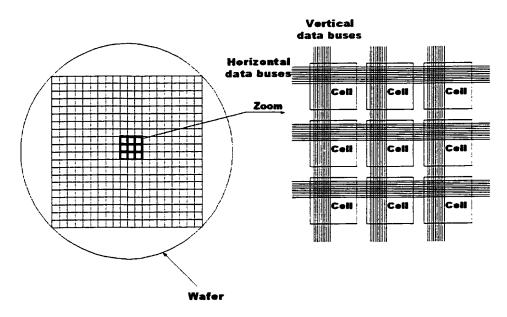

Figure 1.1 A proposed architecture organized as a processing array of size 20 x20.

The proposed architecture, as shown in Figure 1.1, contains complex vertical and horizontal interconnections running across a whole wafer. In a typical design, long wires are driven at more than 100 MHz, and as many as 400 cells could be organized as an array of size 20 by 20. When the architecture is implemented with WSI technology, it provides extreme-performance computing at low costs. However, the targeted unusual scale of

integration results in new problems that are not encountered in conventional ICs. In a nutshell, interconnection methods, electromagnetic compatibility, clocking and synchronization, power distribution, packaging, reconfiguration and yield analysis, testing, and thermal management need to be extensively studied.

The study in this thesis focuses on the yield analysis and modeling of the complex interconnection architecture that supports fault tolerance. Several authors have explored the design and analysis of fault-tolerant arrays [5][9][42]. Successful integration of these structures using large area ICs requires careful diagnosis and yield analysis [5][40]. Predicting the yield is necessary in order to define the number of redundant elements that must be added to the structure. Additionally, due to the interaction of sub-structures in this structure, the smaller defects may cause unusual constraints that cause the circuits unoperational even if fault tolerance schemes have been employed. As the structures involves these unusual constraints that are not taken into account in conventional reconfiguration strategies, existing yield models and reconfiguration strategies [4][16][17][18][20][38][39][46] cannot be applied directly. They must be revised and modified to take these constraints into account. Therefore, to determine the necessary redundancy for a given scale of integration, and to estimate the impact of varying defect densities, a yield model of this architecture needs to be developed.

## 1.3 Scope and organization of the thesis

In this thesis, a closed form yield model that takes into account constraints of the considered complex interconnection architecture is proposed. The impacts of the architectural constraints to yield are translated into yield losses. Yield losses are evaluated

by calculating the probability of observing non-tolerable defect patterns and by subtracting these probabilities from the yield of the arrays with global redundancy. Based on possible defect distributions in this architecture, corresponding yield models are developed. With these models, the sensitivity of the yield of the architecture to variations of the defect density is investigated. This thesis also proposes regression yield models that can be used to quickly predict when more redundancy is needed for given array and cell sizes.

This thesis is organized as follows. In chapter 2, the analysis of a complex interconnection architecture and the reconfiguration techniques used in the related circuit structure are presented. With the assumption of a random defect distribution, a yield model of the considered architecture that captures its specific constraints is presented in Chapter 3. A regression model that approximately predicts the yield of variable size arrays subject to changing defect density is proposed in this chapter as well. In Chapter 4, yield models of the architecture based on a clustered defect distribution are presented. Finally, in Chapter 5, the results of these investigations are summarized, the contributions are highlighted, and some directions for future study are suggested.

# Chapter 2 Analysis of a Complex Interconnection Architecture

#### 2.1 Introduction to fault tolerance mechanisms

Fault tolerance is the capability of a system to maintain its normal performance in an environment where faults occur. Applying fault tolerance techniques to the design of a large-area integrated circuit is required not only to enhance yield, but also to ensure reliability of a circuit. Especially for wafer-scale circuits, without fault tolerance, the yield of the circuits would be almost zero [6]. Therefore, to increase the yield of large-area circuits, on-chip fault tolerance is needed. Fault tolerance can be achieved by many techniques [2][11][13][14]. Among them, hardware redundancy and reconfiguration are of primary interest in this research.

The development of VLSI technology facilitates the physical replication of hardware units that provide the hardware redundancy in digital systems. Such redundancy is usually implemented by two approaches: the passive one and the active one. The passive approach uses the concept of fault masking to hide occurrence of faults and to prevent the faults from producing logical errors in a system. In a circuit with passive redundancy, the hardware is totally or partially triplicated or multiplicated to perform a majority vote to determine the output of the system. In other words, this approach achieves fault tolerance by masking the faults rather than detecting them. The active approach, however, aims at detecting the faults and reconfiguring the system in order to replace faulty modules with

spare modules. The major advantage of the active approach is that fault tolerance can be achieved with less redundant hardware in a system. Due to the need to implement fault detection and recovery mechanisms, the design of the system with active redundancy is more complicated. Moreover, the recovery process may disrupt the normal operation of a system.

When using active hardware redundancy in a system, a fault recovery mechanism is important. Fault recovery is part of a reconfiguration process that eliminates faulty units and restores the system to an operational state. Reconfiguration in VLSI systems has been broadly explored and investigated [25][43], particularly for a fault-tolerant array structure composed of a larger number of identical processing elements in a chip. Three specific types of reconfigurations can be identified: fabrication-time reconfiguration, compile-time reconfiguration and run-time reconfiguration. The key differences among them are the time when the reconfiguration is performed and whether the reconfiguration is permanent, as illustrated in the following.

- (1) Fabrication-time reconfiguration is performed in a foundry, immediately after the fabrication of a processing array. So the reconfiguration can be done only once.

- (2)Compile-time reconfiguration is performed in the field after an array has been operational for some period of time, and configuration is changeable.

- (3)Run-time reconfiguration is used to achieve fault tolerance during the normal operation of a processing array. The configuration can be changed as needed.

Besides these differences, these reconfiguration processes are similar. Firstly, faulty processing elements are identified by test vectors. Then, a reconfiguration algorithm is used to determine an interconnection pattern that is to be used to connect fault-free

elements. Finally, a fully functional array is formed. Recovery techniques used to implement desired connections include physical repair techniques and electronic switch techniques. With the former, the interconnections of the array are physically altered by cutting or adding interconnections. This reconfiguration action is usually irreversible. Whereas, with the latter, the reconfiguration is reversible.

In general, run-time reconfiguration is the most difficult process, and fabrication-time reconfiguration may be the easiest. However, fabrication-time reconfiguration is not suitable for field applications, due to its permanent reconfiguration decisions. Compared with these two kinds of reconfigurations, the compile-time reconfiguration provides a good compromise in many cases. This reconfiguration is reversible and the design is not too complex, which makes it widely used in fault-tolerant arrays.

In the next section, a complex interconnection architecture using a compile-time reconfiguration technique is analyzed and discussed.

## 2.2 Complex interconnection architecture

In this sub-section, a complex interconnection architecture with fault tolerance schemes is investigated in order to undertake its subsequent yield analysis study. This architecture is a highly parallel processing array architecture that is proposed by Richard S.Norman of Hyperchip Inc. [27]-[29]. To make the related circuit structure of this architecture implementable with WSI, the new constraints that are encountered in this unusual scale of integration described in Chapter 1 are studied in our WSI project. Among these studies, Zhongfang Jing concentrated on the study of the signal integrity [49], Claude Thibeault

[50] proposed a basic implementation of the fault-tolerant structure, Meng Lu and others [47] implemented a demonstration chip to verify the concept of fault tolerance.

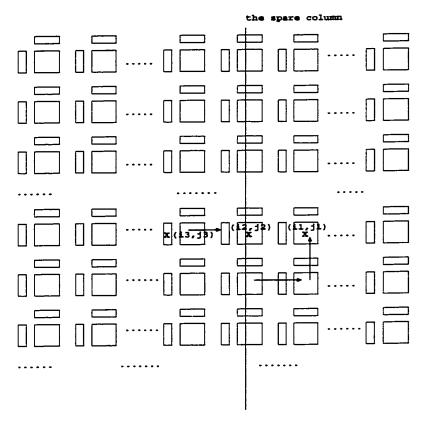

Figure 2.1 Processing array of size  $K \times L$  based on the architecture [27]-[29].

The architecture aims at implementing high speed computation for large data processing problems. To increase its bandwidth and realize a high throughput, a unique parallel interconnection structure is proposed. With this interconnection structure, each processing element, referring to a cell in this thesis, owns two communication bundles in each of horizontal and vertical directions. A cell can communicate with the other cells in the same row or column through its bundles as shown in Figure 2.1. Consequently, the considered architecture will possess a large number of horizontal and vertical interconnections when it comprises hundreds of cells. In addition, since wires are unidirectional and the structure must be completely regular, the number of the receivers and transmitters of a cell is doubled. For example, a physical array of size  $K \times L$  based on this architecture has total 2K bundles in a row and 2L bundles in a column, and each cell

has (K+L-2) receivers and 2 transmitters. Because each bundle contains multiple wires, the number of interconnection wires across the array becomes very large. When the related circuit structure is implemented with WSI, fault tolerance is essential to attain an acceptable yield.

#### 2.1.1 Overview of the fault-tolerant architecture

The purpose of fault tolerance in the architecture [27]-[29] is to enable forming a target array of N by M out of a physical array of K by L, with  $N \le K$  and  $M \le L$ . A key point in the fault tolerance design is to minimize critical areas, also called chip-killing areas. Therefore, a reconfiguration logic connecting cells and bundles should be designed in such way that none of the faults in those cells and bundles is critical to the construction of the target arrays. Several different topologies of reconfiguration logic were taken into consideration. Generally, with more connections available for reconfiguration, arrays with increased robustness can be designed. But it should be noted that the larger number of the connections, the larger the area overhead and possibly lower the performance. Finally, the reconfiguration logic in this architecture was selected on the basis of an engineering trade-off.

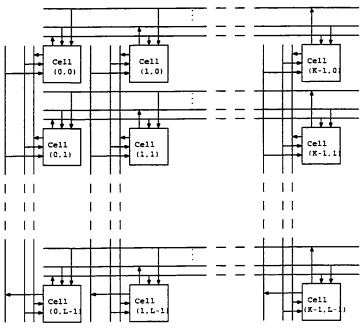

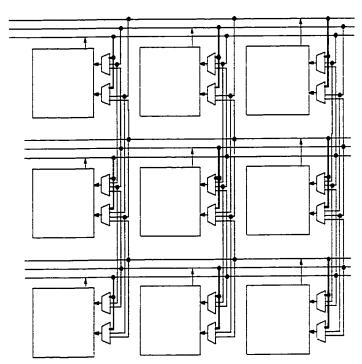

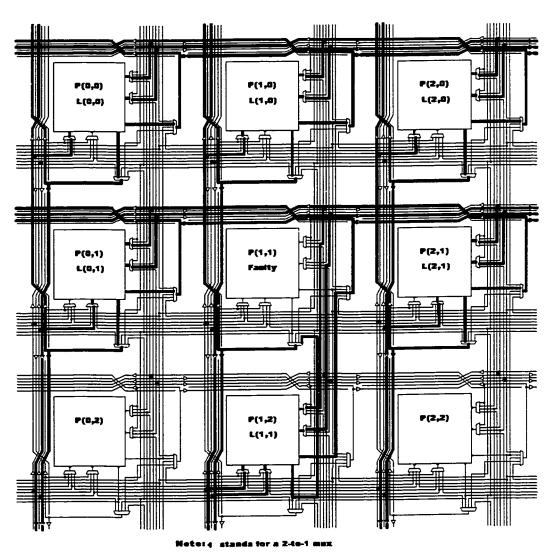

An in-depth discussion of the fault-tolerant structure is beyond the scope of this thesis. We only describe the basic framework of the structure. In order to minimize the interference between long interconnection lines, a transposed line structure is designed for the interconnections of the array. Figure 2.2 presents the interconnection structure of such array of size 3x3. In addition, the compile-time reconfiguration with the electronic switching technique is used to reconfigure the system and to achieve fault tolerance when defects are present. In order to reduce the complexity of the reconfiguration logic, fault

detection can be implemented by a host computer. The obtained fault map is stored in an external storage. Thus, the reconfiguration circuits are limited to the links that carry reconfiguration signals to multiplexers. The setup of these multiplexers is implemented through a fault-tolerant scan chain across each cell [47], which is based on a boundary scan architecture (JTAG IEEE1149.1) [30].

Figure 2.2 Interconnection structure of a physical array of size 3x3 based on the architecture [27]-[29].

#### 2.2.2 Configuration of the transmitter multiplexers of a cell

The configuration of the transmitter multiplexers of a cell should be designed to make the cell not critical to the building of a target array, i.e., the cell can be replaced in case of fault. According to this rule, the configuration of the multiplexers is designed to enable 5 cells, the cell in question and its four nearest neighbors, to send their signals through these multiplexers. The configuration is shown in Figure 2.3. When a cell is defective, a good neighboring cell can replace it by using its natural bundles through the corresponding multiplexers. Moreover, when its multiplexers are defective, the cell can also send its signals through the multiplexers of one of its neighboring cells.

Figure 2.3 Configuration of the transmitter multiplexers of cells. In this diagram, only the multiplexers in the vertical direction are illustrated. Similar multiplexers are used in the horizontal direction.

In addition, it is clearly shown in Figure 2.4 that the configuration of a transmitter multiplexer makes a bundle replaceable. Through the multiplexers, a cell may use the

bundles originally owned by one of its four nearest neighboring when its natural bundles are defective. Similar to that, when a defective cell is replaced with a good neighboring cell, this good cell can send its signals through the bundles originally owned by the defective cell. For other cells receiving these signals, the defects in the cell are not perceptible. This provides a perfect replacement for defective cells. However, to implement this scheme, the configuration of the receiver multiplexers of a cell needs to possess the corresponding fault tolerance capability.

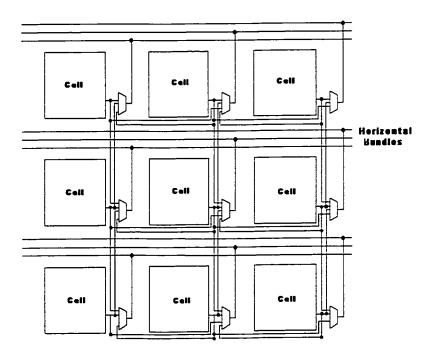

### 2.2.3 Configuration of the receiver multiplexers of a cell

In a  $K \times L$  physical array that is used to form a logical array of N by M, each cell has (L+K-2) receivers to receive signals from (K-1) horizontal bundles and (L-1) vertical bundles. The physical array comprises (K-N) spare horizontal bundles and (L-M) spare vertical bundles. If no defect is present in the array, each cell can broadcast to the others in a physical row through its horizontal bundle. If a horizontal bundle is defective, the cell originally owning this bundle may send its signals through a spare horizontal bundle of one of its nearest neighboring cells. Other cells in the physical row must be capable of receiving the signals from the spare bundle. Therefore, in the horizontal direction, the configuration of the receiver multiplexers of each cell must be designed in such way that a cell can receive signals through bundles in its natural row and those in its nearest neighboring rows. The same is required in the vertical direction. A possible configuration of the receiver multiplexers of a cell is illustrated in Figure 2.4. In this figure, a physical array of 3x3 is taken as an example. From the figure, it is clear that each cell can communicate with other cells through bundles in its natural row or its two nearest rows. It can be noted that specific connections shown with thick lines, proposed by Meng Lu [47],

make it possible for the cells to receive signals from their natural bundles. This connections make bundle replacements more flexible. As a result, a defective bundle in a row can be replaced by a good spare bundle either in one of its two nearest rows, or within the same row. The former is called inter-bus replacement and the latter is called intra-bus replacement. The same is true for a bundle in a column.

Figure 2.4 Configuration of the receiver multiplexers of cells in a 3x3 physical array. In this diagram, only the multiplexers in the vertical direction are illustrated. Similar multiplexers are also used in the horizontal direction.

With these multiplexers, a reconfiguration strategy is needed to implement the reconfiguration of the architecture when defects are present.

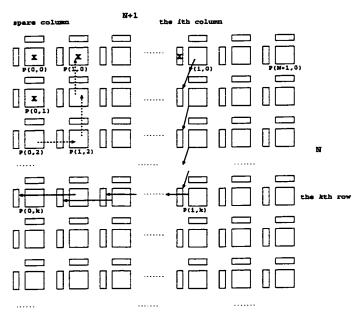

# 2.3 Reconfiguration strategies of the fault-tolerant structure

In this sub-section, because the yield of forming a target array relies heavily on the adopted strategies, the reconfiguration strategies used in the fault-tolerant structure are presented and analyzed. Two commonly used concepts in the theoretical analysis of the reconfiguration of processing arrays are first explained. These two concepts are physical array and logical array [21]. A physical array is an array that maps directly on the physical implementation and whose cells may be contaminated by manufacturing defects. A cell of a physical array is denoted by P(x,y), where x and y indicate the column and row position of the cell in the physical array, respectively. A logical array represents the desired array structure specified by the intended application as seen from external system parts. A cell in a logical array is denoted by L(x,y), where x and y indicate the logical column and row position of the cell in the desired array. In order to maximize the probability of a desired logical array being mapped to a physical array, reconfiguration strategies are needed.

### 2.3.1 Basic reconfiguration strategies

Using a reconfiguration strategy to map a logical array into a physical array aims at isolating, confining and overcoming defects in a physical array. The applications of reconfiguration strategies depend on constraints related to an architecture [8][9]. Because of the features of the fault-tolerant structure described in section 2.2, several basic reconfiguration strategies can be used. They are cell-stealing and cell-shifting, bundle-stealing and bundle-shifting, column or row exclusion strategy [25]. Some examples are presented below to illustrate applications of these strategies.

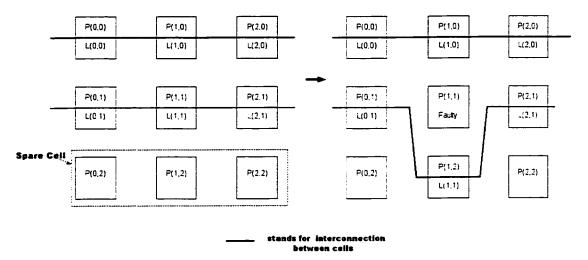

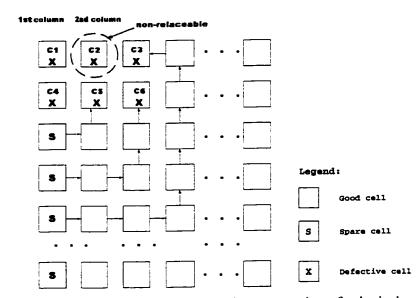

Figure 2.5 Example of using the cell-stealing strategy to construct a logical array of 2x3 out of a physical array of 3x3.

The cell-stealing strategy forms a logical array by replacing a defective cell with one of its nearest neighbors spare cells. Figure 2.5 shows such an example in which a logical array of 2x3 is formed out of a physical array of 3x3. Evidently a logical array of 2x3 can be directly constructed from the physical array of 3x3 if there is no defect in all cells. For instance, the logical cells L(i,j) (i=0,1 and j=0,1) of the logical array can be mapped directly into the physical cells P(i,j) (i=0,1 and j=0,1). When the physical cell P(1,1) is defective, a good spare cell in other row needs to be reconfigured to build a logical array. In this case, a good spare physical cell P(1,2) is stolen from the second row to form the logical array. Finally, the logical array is constructed by replacing the defective cell P(1,1) with the spare good cell P(1,2).

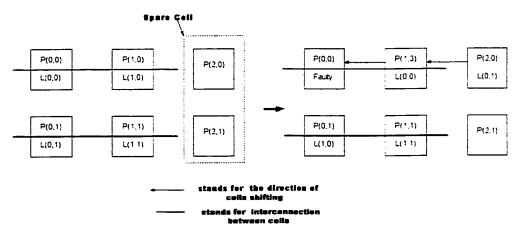

The cell-shifting strategy is to form a logical array by replacing a defective cell with a good spare cell that is not in its nearest neighboring position. Figure 2.6 shows the procedure of using the cell-shifting strategy to form a logical array of 2x2 from a physical

array of 3x2. When the cell P(0,0) is defective, the good spare cell P(2,0) is used to replace the defective one by shifting a cell one position at a time. Then, the logical array is obtained with L(0,0) being mapped to P(1,0) and L(1,0) to P(2,0).

Figure 2.6 Example of using the cell-shifting strategy to construct a logical array of 2x2 out of a physical array of 3x2.

Similar to the cell-stealing strategy, the bundle-stealing strategy is to construct a logical array by replacing one defective bundle with one good spare bundle that is in a nearest neighbor position. Also the bundle-shifting strategy replaces a defective bundle with a good spare bundle that is not in its nearest neighbor position. Similar to the operation of cells, this replacement needs to be operated one position at a time as well.

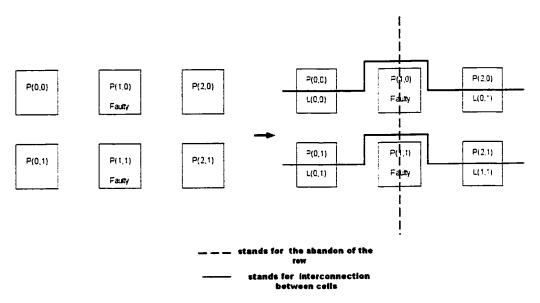

The column or row exclusion strategy consists in eliminating a suitable set of columns or rows containing defective cells from a physical array to form a desired logical array. In this case, a number of good cells can be eliminated by the reconfiguration process. The set to be excluded should be carefully chosen to lower the cost. It is also a common practice to use good cells in the eliminated columns or rows as a pool of spare cells exploited through a cell shifting strategy. Figure 2.7 shows that a logical array of 2x2 is constructed from a physical array of 3x2 by excluding a column containing defective cells. In this case, the

position of spare cells is not specified. Because there are two defective cells in the second column, this column is excluded. Then, the logical 2x2 array is built with the physical cells in the first column and the third column.

Figure 2.7 Example of using the column or row exclusion strategy to construct a logical array of 2x2 from a physical array of 3x2.

#### 2.3.2 Reconfiguration of the cells in the fault-tolerant structure

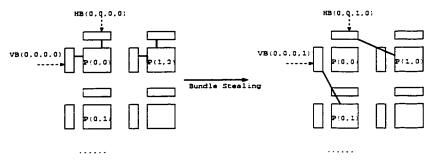

In the fault-tolerant structure shown in the section 2.2, a cell can communicate with other cells in the same physical row or column through its natural bundles and other bundles of its four nearest neighbors as well. Accordingly, the cell-stealing and cell-shifting strategies can be accomplished by controlling the multiplexers of receivers and transmitters if the corresponding bundles are not defective.

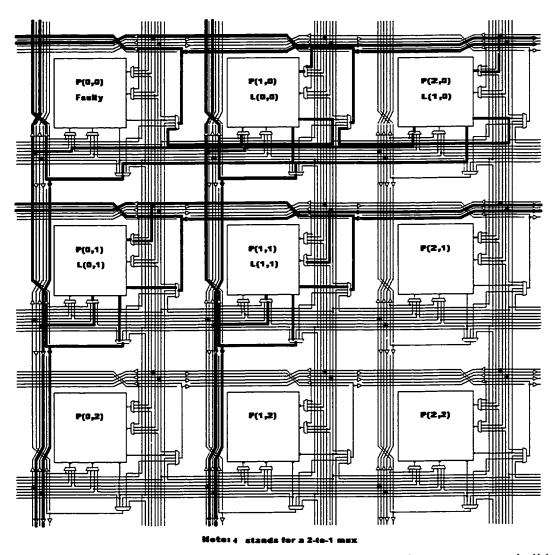

Without loss of generality, Figure 2.8 shows an example of forming a logical array of 3x2 from a physical array of 3x3 with the cell-stealing strategy in the fault-tolerant structure. In this case, it is assumed that all spare cells are in the third row and bundles are

not defective. When the cell P(1,1) is defective, the good spare cell P(1,2) needs to be used to replace the defective one. Through reconfiguring the transmitter multiplexers of the cell P(1,1), its horizontal and vertical bundles can be used as the data channels of cell P(1,2). The cell P(1,2) can also receive signals from cells P(1,0) and P(0,1) by reconfiguring the multiplexers of its receivers. After reconfiguration, the targeted logical array is formed with logical cell P(1,1) being mapped into the physical cell P(1,2).

Figure 2.8 Using the cell-stealing strategy to construct a 3x2 logical array from 3x3 physical array based on the architecture in [27]-[29]. The thick lines illustrate the final reconfiguration.

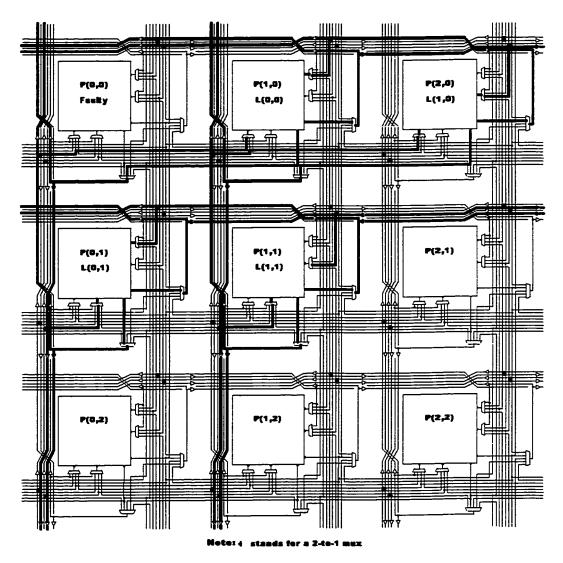

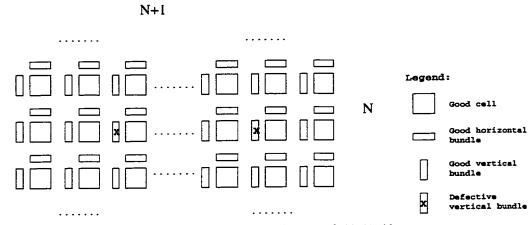

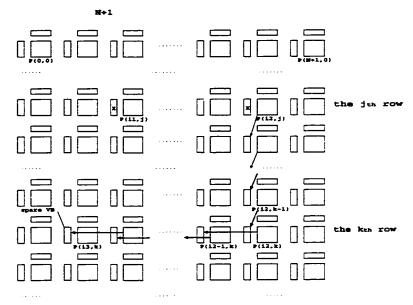

The use of the cell-shifting strategy is shown in Figure 2.9 and Figure 2.10 with two example of building a 2x2 logical array from a 3x3 physical array. In these examples, it is assumed that no bundle is defective and the spare cells are in the third column and the third row. There are two possible approaches to realize this reconfiguration.

Figure 2.9 Using the perfect replacement with the cell-shifting strategy to build a 2x2 logical array from 3x3 physical array.

The first is using the natural bundles of defective cells as shown in Figure 2.9. Because two bundles of the defective cell P(0,0) are finally owned by cell P(1,0), the defective cell

P(0,0) is perfectly replaced by left shifting the spare cell P(2,0). The perfect replacement can only be accomplished under the condition of the corresponding bundles being defect-free.

Figure 2.10 Using the imperfect replacement with cell-shifting strategy to construct a 2x2 logical array from a 3x3 physical array.

The second is that the bundles of defective cells are not be used. Figure 2.10 shows how this cell-shifting strategy can form a logical array of 2x2 out of a physical array of 3x3. In this case, the natural horizontal bundles of the defective cell P(0,0) are not used

when the good spare cell P(2,0) is left shifted. Because the spare cell and the defective cell are in the same physical row, the spare cell can communicate with the others in the same physical row with its original bundles.

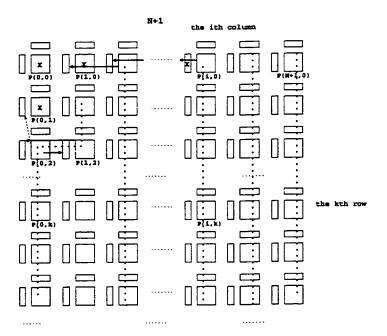

### 2.3.3 Reconfiguration of the bundles in the fault-tolerant structure

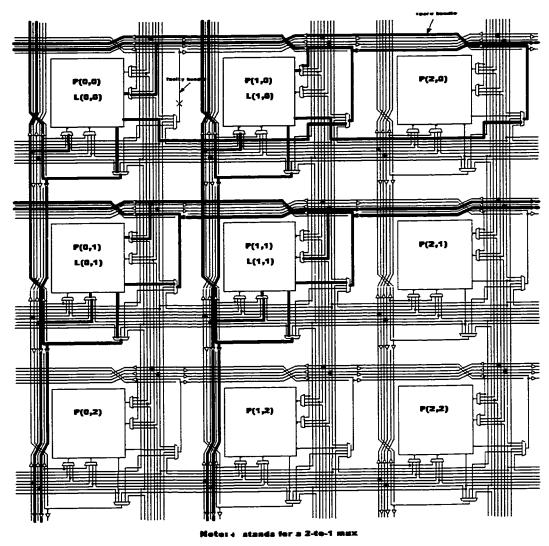

The process of reconfiguring bundles in this structure is similar to that of cells. However, two kinds of bundle replacement methods somewhat different from cell replacement methods exist. They are intra-bus replacement and inter-bus replacement. The former replaces a defective bundle with a spare one in the same physical row and the latter operates in a different physical row. The operation of the intra-bus replacement is shown in Figure 2.11. In this case, the defective bundle is originally owned by the physical cell P(0,0) and the spare bundle is originally owned by the spare cell P(2,0). After reconfiguration, the cell P(0,0) owns the bundles originally belonging to the cell P(1,0), and the cell P(1,0) owns the spare bundle. Then, an intra-bus replacement operation is accomplished.

Figure 2.11 Intra-bus replacement in the fault-tolerant structure.

Figure 2.12 shows the inter-bus replacement operation. In this case, the bundle replacement is operated between three different physical rows. Through shifting the bundles one position at a time, the cell P(0,0) uses the bundle in the second row and the cell P(0,1) uses the bundle in the third row. Finally, a logical array of size of 2x2 is constructed.

Figure 2.12 Inter-bus replacement in the fault-tolerant structure.

# 2.4 Summary

In this chapter, some fault tolerance mechanisms and a fault-tolerant architecture with complex interconnections have been described. A detailed analysis of the fault-tolerant configuration of this architecture and the basic reconfiguration strategies have been presented as well.

The architecture is a highly parallel processing array architecture that involves a large number of routing nodes. To enhance the yield, the reconfiguration logic is designed to enable the replacement of a defective cell with any of its nearest neighbor cells, as well as the replacement of the inter-bus or intra-bus bundles. Also, the structure can repair defects by repeatedly shifting spare cells and bundles one position at a time when building a logical array. As a first approximation, the structure can provide a global redundancy.

# Chapter 3 Yield Modeling of a Complex Interconnection Architecture

# 3.1 Introduction to yield analysis and yield models

#### 3.1.1 Defects and faults

The profitability of IC manufacturing depends heavily on the fabrication yield, which is defined as the fraction of the manufactured circuits that are good. Due to various manufacturing defects, 100% yield is impossible. Manufacturing defects, referring primarily to failures appearing during a production process and affecting the yield, can be classified into gross defects and random defects [35]. Gross defects are caused by manufacturing imperfections that result from the process being completely out of acceptable bound. They destroy a whole wafer or large parts of a wafer having no operational chip. Gross defects can usually not be recovered through fault tolerance techniques. Random defects are due to localized imperfections that occur during processing. Examples of random defects include missing contact windows, misaligned gates, and missing devices. Random defects are characterized as spot defects that are localized and randomly distributed over the whole wafer.

Both types of defects can contribute to yield losses. However, gross defects can be minimized and almost eliminated in mature and well-controlled manufacturing lines [20]. Comparatively, it is much more difficult to control spot defects in production lines. Consequently, the yield losses due to spot defects are much higher than those due to gross

defects. This is especially true for large area integrated circuits, since the occurrence of gross defects is almost independent of the chip size and the expected number of spot defects increases with the chip area [20]. Therefore, spot defects are of greater significance when yield enhancement is taken into account. In this thesis, only spot defects are taken into consideration in the yield analysis.

Not all spot defects result in circuit faults. A fault in a digital circuit is a logical difference between the behavior of a good and a bad circuit. Whether or not a defect will cause a fault depends on its location, its size, the layout and the density of the circuit. Only those defects that actually affect the circuit operation are called faults and are the ones causing yield losses [40]. Thus, for the purpose of yield estimation, the distribution of faults rather than that of defects is of interest.

#### 3.1.2 Review of basic yield models

To model the yield for a circuit, some analytical probability functions that describe the expected spatial distribution of defects that cause faults are needed. From this point defects and faults will be used interchangeably to refer to defects that cause faults and impact on yield. Moreover, the yield models with respect to a certain defect distribution for the circuits that use fault tolerance techniques differ from those for the circuits that do not. In this sub-section, the yield models of a circuit without fault tolerance scheme is discussed.

The yield of a circuit without fault tolerance schemes can be evaluated with the probability of no defect occurring in the whole circuit area. If x denotes the number of defects in the circuit, the yield,  $Y_{circuit}$ , is given by

$$Y_{circuit} = P(x=0) (3.1)$$

Where, P(x) is a probability distribution function of defects.

The earliest probability distribution function used to predict the yield of ICs was derived from the random Poisson model. Using that model, the probability of a circuit having x defects is given as follows.

$$P(x) = \frac{e^{-\lambda} \lambda^x}{x!} \tag{3.2}$$

Here,  $\lambda$  is the expected number of defects in the circuit.

When there is no defect in a circuit, the yield is obtained by substituting x=0 into (3.2). Then, (3.1) becomes,

$$Y_{circuit} = e^{-\lambda} = e^{-DA} \tag{3.3}$$

Where, D is the defect density of the circuit and A is its critical area, with  $\lambda = DA$ .

For small area circuits, the Poisson model works reasonably well. However, when the sizes of circuits grow, using the Poisson model to predict yields becomes increasingly inappropriate, because it tends to underestimate the yield of larger circuits [19][24][37]. Several approaches have been proposed to modify the Poisson model to reflect clustered yields. Among them, B.T.Murphy [23] assumed the defect density D is a random variable and proposed the following yield equation.

$$Y_{circuit} = \int_0^\infty e^{-DA} f(D) dD \tag{3.4}$$

Here, f(D) is a normalized probability distribution function of the defect density D.

Based on (3.4), using the gamma distribution for f(D), Stapper [33] proposed the probability distribution function presented in (3.5). This is the well-known negative

Binomial distribution, which leads to a corresponding yield model, the negative Binomial model given in (3.6).

$$P(x) = \frac{\Gamma(x+\alpha)(\lambda/\alpha)^{x}}{x!\Gamma(\alpha)(1+\lambda)^{x+\alpha}}$$

(3.5)

$$Y_{circuit} = \left(1 + \frac{\lambda}{\alpha}\right)^{-\alpha} \tag{3.6}$$

where  $\alpha$  is referred to the clustering parameter, a property of the IC manufacturing process.

With (3.6), the Poisson model and the other yield models proposed in [41] can also be evaluated by selecting an appropriate clustering parameter  $\alpha$ . When  $\alpha$  is low, the defects tend to be more clustered [33]. Conversely, when  $\alpha$  is high, the shape of the gamma distribution approaches that of the Poisson distribution, and the defects tend to be randomly distributed.

In fact, because the random defect distribution does not reflect the phenomenon of clustering defects in ICs, it can lead to predicting low yields in many cases. Stapper and his colleagues [40] investigated yield modeling issues extensively throughout the 1980s. They came to the important conclusion that the yield of large chips such as microprocessors and application specific integrated circuits (ASICs) is not only a function of the chip area, but also is related to features of different manufacturing processes. The introduction of the defect clustering parameter in the negative Binomial model can reflect the chip-to-chip variations in defect densities.

The negative Binomial yield model is found to be satisfactory for the yield prediction of a circuit without fault tolerance schemes. However, if the circuit uses fault tolerance

schemes in the form of redundant components, the evaluation of its yield requires a more elaborate statistical model.

## 3.1.3 Yield modeling for circuits with redundant structures

A well-known method to tolerate faults and defects in an integrated circuit is adding redundancy in the circuit. Its yield can be evaluated by calculating the probability that it contains enough defect-free basic blocks for proper operation. To compute the probability, a detailed statistical model is needed. This model should provide information about the distribution of defects over partial areas of the circuit, and possible correlations among defects in different sub-areas. Several authors have explored and developed yield models for circuits with redundancy [17][18][26][34][44]. Developing an accurate yield model needs a great deal of insight regarding the structure of a circuit and the fault tolerance schemes used in this circuit.

A general yield formula was proposed based on the Poisson model (3.1), and its derivative, the compound Poisson model [17][26]. In this approach, it is assumed that a circuit is composed of N identical sub-circuits, called modules in the literature, including R spare modules. The circuit can function correctly when it contains at least N-R defect-free modules. Therefore, the yield equation of the circuit is derived by calculating the probability of M out of N modules being defect-free, where  $M \ge N - R$ . This expression assumes that defects in any module are distributed according to the Poisson distribution, and that modules are statistically independent of each other. In that case, the yield formula is given by

$$Y = \sum_{M=N-R}^{N} {N \choose M} (e^{-AD})^M (1 - e^{-AD})^{N-M}$$

(3.7)

Where,  $A(cm^2)$  is the area of a module and  $D(cm^{-2})$  is the defect density of a module.

This formula corresponds to an idealization. Indeed, in practice, circuits rarely consist entirely of identical modules. A more general case is that a circuit is composed of multiple types of modules, each with its own redundancy. In that case, the yield equation of the circuit composed of n types of modules can be derived. Let  $N_i$  denote the number of type i modules, out of which  $R_i$  are spares. In this case, the yield is given by the following equation.

$$Y = \sum_{M_{1} = N_{1} - R_{1}}^{N_{1}} \dots \sum_{M_{i} = N_{i} - R_{i}}^{N_{i}} \dots \sum_{M_{n} = N_{n} - R_{n}}^{N_{n}} {N_{1} \choose M_{1}} \left(e^{-A_{1}D_{1}}\right)^{M_{1}} \left(1 - e^{-A_{1}D_{1}}\right)^{N_{1} - M_{1}} \dots \left(\frac{N_{i}}{M_{i}}\right) \left(e^{-A_{i}D_{i}}\right)^{M_{i}} \left(1 - e^{-A_{i}D_{i}}\right)^{N_{i} - M_{i}} \dots \left(\frac{N_{n}}{M_{n}}\right) \left(e^{-A_{n}D_{n}}\right) \left(1 - e^{-A_{n}D_{n}}\right)^{N_{n} - M_{n}}$$

$$(3.8)$$

Here,  $M_i$  is the number of defect-free type i modules,  $A_i$  is the area of type i modules, and  $D_i$  is the defect density of type i modules.

Equations (3.7) and (3.8) show a general method to develop the yield model of a chip with redundancy. Although the Poisson distribution used in both equations does not match actual defect and fault data very well, it provides an easy way to calculate the yield with an approximation that indicates the yield trend. Moreover, these equations were deduced by using an ideal model that does not take into account the interaction of different modules even though such interaction often exists. For example, when a module is defective, it can affect other modules, and make a circuit dysfunctional. Therefore, even if there are available spare modules, specific combinations of defective modules can also make a circuit operate incorrectly. To model the yield for a complex interconnection architecture,

we need to take into account not only several kinds of modules in the structure, but also some specific combinations of them.

# 3.2 Yield modeling for a complex interconnection architecture

#### 3.2.1 Constraints-based yield model

The architecture proposed in [27]-[29] is mainly composed of four parts as described in Chapter 2: identical cells, vertical and horizontal interconnection bundles between cells, and reconfiguration logic. The reconfiguration of the structure is implemented through a scan chain across all cells, which is based on the boundary scan architecture (JTAG[27]). These parts and the scan chain have different effects on the yield of the structure, and the impact of these effects on the yield can be estimated respectively with a simple yield model (3.6). The results of the computation of the yield of those parts are illustrated in Table 3.1 and 3.2. In this numerical analysis, an array of 20x20 based on [27]-[29] is used, and the parameters used are obtained from the proposed WSI architecture and the fault-tolerant demonstration chip that is presented in [47]. In the demonstration chip, the scan chain was designed without fault tolerance. Consequently, the scan chain may become the only critical circuit in this chip, i.e., any fault of the scan chain cannot be tolerated.

Table 3.1 Yield of a bundle, a cell, and the reconfiguration logic belonging to one cell. The data is obtained from a WSI demonstration chip designed and fabricated as part of a Hyperchip R&D projects. In this chip, each bundle comprises 4 wires. Random defect density  $D_0=1963$  m<sup>-2</sup> and the clustering parameter  $\alpha=5$  were used from ITRS[12]. The yield of a 20x20 array, with an area  $1.04 \times 10^2$  cm<sup>2</sup>, without fault tolerance is  $2.94 \times 10^{-4}$ .

|                                  | Reconfiguation logic in a cell | Bundle                | Cell                   | Scan chain<br>within a cell |

|----------------------------------|--------------------------------|-----------------------|------------------------|-----------------------------|

| Critical Area (cm <sup>2</sup> ) | 1.1x10 <sup>-4</sup>           | 4.3x10 <sup>-3</sup>  | 2.5x10 <sup>-1</sup>   | 4.0x10 <sup>-4</sup>        |

| $D_0$ A                          | 2.16x10 <sup>-5</sup>          | 8.44x10 <sup>-4</sup> | 4.91x 10 <sup>-2</sup> | 7.85x10 <sup>-5</sup>       |

| Yield                            | 0.999978                       | 0.999156              | 0.952314               | 0.999922                    |

Table 3.2 Yield of a bundle, a cell, and the reconfiguration logic belonging to one cell. The data is obtained from the proposed WSI architecture in Hyperchip R&D projects. In this case, each bundle comprises 40 wires. Random defect density  $D_0=1963$  m<sup>-2</sup> and the clustering parameter  $\alpha=5$  were used from ITRS[12]. The yield of a 20x20 array with an area  $2.56 \times 10^2$  cm<sup>2</sup> is  $6.06 \times 10^{-4}$ .

|                                  | Reconfiguation logic in a cell | Bundle                | Cell                   | Scan chain<br>within a cell |

|----------------------------------|--------------------------------|-----------------------|------------------------|-----------------------------|

| Critical Area (cm <sup>2</sup> ) | 2.8x10 <sup>-2</sup>           | 9.6x10 <sup>-2</sup>  | 2.5x10 <sup>-1</sup>   | 1.4x10 <sup>-3</sup>        |

| $D_0$ A                          | 5.50x10 <sup>-3</sup>          | 1.88x10 <sup>-2</sup> | 4.91x 10 <sup>-2</sup> | 2.75x10 <sup>-4</sup>       |

| Yield                            | 0.994522                       | 0.981366              | 0.952314               | 0.999725                    |

From Table 3.1 and 3.2, it is seen that the yield of the reconfiguration logic of a cell is much higher than that of a cell or a bundle because of its relatively small area. Thus, the yield loss contributed by the reconfiguration logic is not significant. Furthermore, available design techniques can make potentially critical signals robust to the presence of defects [3][15][31]. Applying such techniques to the low complexity reconfiguration logic can make its yield much closer to 1 than computed in Table 3.1 and 3.2. The small

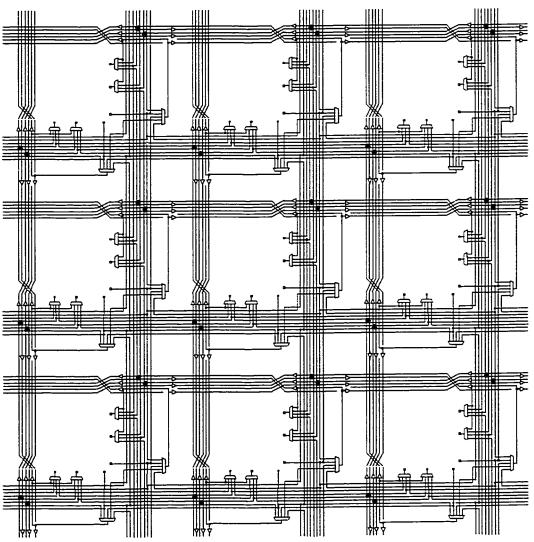

resulting yield reduction, due to defects in the simple robust reconfiguration logic described in Chapter 2, can be accounted for by a multiplying factor close to 1 that would derate the yield. Accordingly, in the yield analysis of this structure, the assumption of reconfiguration logic being defect-free is reasonable. From Table 3.1, it is clear, that the yield loss contributed by the scan chain in the demonstration chip is insignificant and the effect of the scan chain on the yield can also be expressed as a multiplying factor close to 1. But when a scan chain without fault tolerance schemes is used in the proposed WSI architecture, with each part of the scan chain within a cell assumed statistically independent, the yield of the scan chain across 400 cells is equal to 0.8958. When the scan chain is designed with fault tolerance [47], it is no longer critical to the structure and the yield loss contributed by the scan chain can be incorporated into that of cells. Form the above analysis, it is concluded that, in the yield modeling, cells, vertical bundles and horizontal bundles are the main concern. In addition, it is also implicitly assumed that existing robust methods of dealing with defects in critical signals are applied, such that normal spot-defects almost always lead to unusable cells or bundles, and do not invalidate the test and reconfiguration mechanisms. With the assumption of fault-free reconfiguration logic, a simplified diagram of the fault-tolerant structure is used to illustrate our model. Figure 3.1 shows a simplified diagram for a typical 8x8 array.

Figure 3.1 Simplified diagram of a 8 by 8 physical array based on the architecture in [27]-[29].

In this figure, a horizontal rectangle represents a horizontal bundle and a vertical rectangle represents a vertical bundle, while the squares represent cells. Each cell owns one bundle in the horizontal direction and another one in the vertical direction, and can communicate with the other cells in the same column or row through its bundles. To simplify the diagram, the connections between bundles and cells are not shown. The objective with this fault-tolerant architecture is to form a logical array sized N by M out of a physical array of size K by L with  $N \le K$  and  $M \le L$ . With the reconfiguration logic, a physical cell in the physical array can replace any of its nearest neighbors. When a cell broadcasts to other cells of a physical row, it can do so by using bundles from its natural row or from nearby spare bundles. The same is true for vertical bundles. It may appear that this architecture can only repair defects by shifting cells by one or a few positions, but by repeatedly shifting cells and bundles one position at a time, a spare at one corner of the array can be used to replace a defect at the other corner of the array, when building a

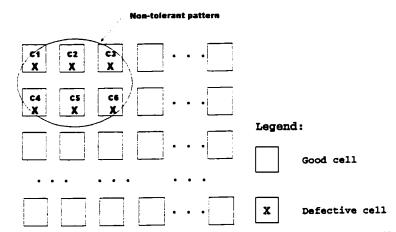

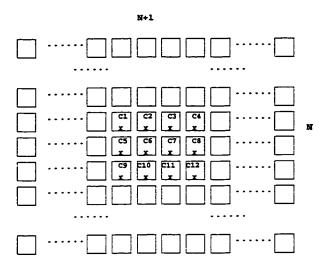

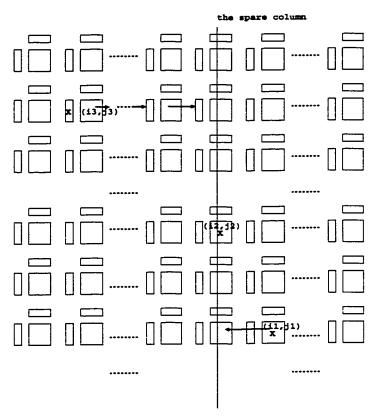

logical array that is arranged to use only good cells and bundles. As a first approximation, the structure provides global redundancy. It does so successfully when defects are sparse, which is the case when the probability of individual cell and bundle being defective is low. However, practical implementations are limited by the number of reconfiguration wires. Several different topologies of the reconfiguration multiplexers were considered. Generally, with more reconfiguration wires, we can design arrays with an increased robustness. In a configuration that is based on an engineering trade-off, the array has constraints. Some distributions of defective bundles and defective cells prevent construction of an adequate logical array. An example of this kind of patterns is illustrated in Figure 3.2. In this example, a logical array of 3 by 3 intends to be built from a physical 4 by 3 array. The physical array contains 3 spare cells, 3 spare vertical bundles and 3 spare horizontal bundles. However, when three cells (C1 to C3) and three horizontal bundles (HB1 to HB3) are defective as shown in Figure 3.2, the position of three defective horizontal bundles prevents the usage of the good cell, C0. Thus, only 8 good cells instead of 9 ones are available, and the logical array cannot be formed. Therefore, this kind of defective cells and bundles cannot be tolerated. In this thesis, this kind of distributions that cannot be tolerated are referred as non-tolerable patterns.

Figure 3.2 Pattern preventing the construction of a logical array size of 3 by 3 out of a physical array of 4x3. The symbol "X" stands for defective cell or bundle, and "A" for available cells

Figure 3.3 Flow chart of the probability of forming a logical array. F<sub>c</sub> is the number of defective cells, F<sub>HB</sub> is the number of defective horizontal bundle, F<sub>VB</sub> is the number of defective vertical bundle, S<sub>c</sub> is the number of spare cells, S<sub>VB</sub> is the number of spare vertical bundles, and S<sub>HB</sub> is the number of spare horizontal bundles.

Generally, there are several possibilities that prevent the construction of a logical array. According to the cause that prevents the construction of a logical array, they are classified as two major types. First, when there are not enough spares to replace the defects in the

structure, the construction fails. In other word, the structure must simultaneously contain enough spare cells, spare horizontal bundles and spare vertical bundles to tolerate the respective defects. Second, non-tolerable patterns occur in the structure. Figure 3.3 shows the probability of the events of forming a logical array. From this figure, it is known that the yield of the architecture can be evaluated with the probability of having tolerable patterns in the structure and it can be expressed as in (3.9).

$$Y_{chip} = Y_{global} - Y_{loss} (3.9)$$

where  $Y_{chip}$  is the true yield of the structure,  $Y_{global}$  is the yield of the structure with global redundancy, which would be observed if the structure had no constraint, and  $Y_{loss}$  is the probability to have non-tolerable defect patterns. In addition, the number of defective cells and bundles must be smaller than the respective number of spare cells and bundles.

Based on Equation (3.8), an analytical expression of  $Y_{\text{global}}$  is presented in (3.10). This expression assumes that defects in cells, vertical bundles and horizontal bundles are statistically independent, and that they comply with the binomial distribution.

$$Y_{global} = \sum_{F_{c}=0}^{S_{C}} \sum_{F_{vB}=0}^{S_{VB}} \sum_{F_{vB}=0}^{S_{HB}} \left( \frac{Q_{c}}{F_{c}} \right) \left( \frac{Q_{VB}}{F_{VB}} \right) \left( \frac{Q_{cHB}}{F_{vB}} \right) \left( \frac{Q_{c}-F_{c}}{F_{c}} \right) \left( \frac{Q_{vB}-F_{vB}}{F_{vB}} \right) \left( \frac{Q_{$$

In (3.10),  $y_{cell}$  is the yield of a cell,  $y_{HB}$  is the yield of a horizontal bundle, and  $y_{VB}$  is the yield of a vertical bundle.  $Q_c$  is the total number of cells,  $Q_{VB}$  is the total number of vertical bundles, and  $Q_{HB}$  is the total number of horizontal bundles.  $F_c$  is the number of defective cells,  $F_{HB}$  is the number of defective horizontal bundle, and  $F_{VB}$  is the number of defective vertical bundle.  $S_c$  is the number of spare cells,  $S_{VB}$  is the number of spare

vertical bundles, and  $S_{HB}$  is the number of spare horizontal bundles. In this case,  $y_{cell}$ ,  $y_{HB}$  and  $y_{VB}$  can be expressed by the negative Binomial yield model (3.6) or the Poisson yield model (3.3). Using the negative Binomial yield model, they are given as:

$$y_{cell} = \left(1 + \frac{D_c A_c}{\alpha}\right)^{-\alpha} \tag{3.11}$$

$$y_{VB} = \left(1 + \frac{D_{VB}A_{VB}}{\alpha}\right)^{-\alpha} \tag{3.12}$$

$$y_{HB} = \left(1 + \frac{D_{HB}A_{HB}}{\alpha}\right)^{-\alpha} \tag{3.13}$$

The equation of  $Y_{loss}$  is expressed as:

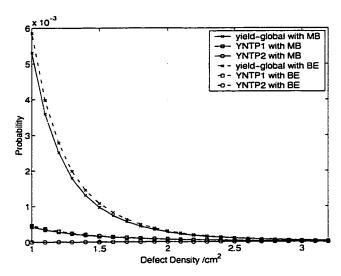

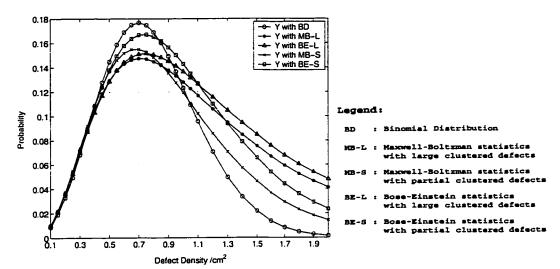

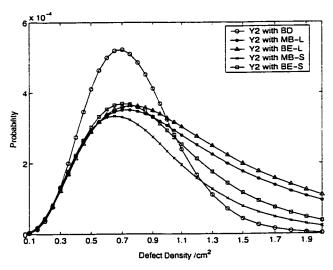

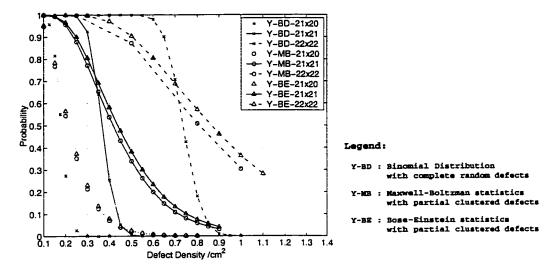

$$Y_{loss} = \sum_{i} (Y_{NTP})_{i} \tag{3.14}$$