**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

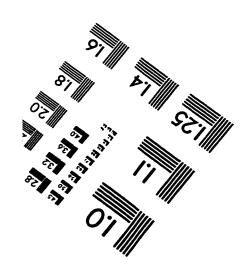

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

## A SINGLE STAGE FULL BRIDGE POWER FACTOR CORRECTED AC/DC CONVERTER

Nasser Ismail

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

November, 1996

©Nasser Ismail, 1996

Acquisitions and

of Canada

Bibliographic Services

395 Wellington Street

395 Wellington Street Ottawa ON K1A 0N4 Canada du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation

0-612-26004-6

#### **ABSTRACT**

## A Single Stage Full Bridge Power Factor Corrected

#### **AC/DC Converter**

#### Nasser Ismail

Conventional single phase AC/DC converters use a two stage power configuration to provide a regulated DC power supply at high input power factor. Elimination of one of these stages can reduce the cost, weight, size, complexity and increase the overall reliability of this converter. This thesis proposes a single stage power factor correction converter circuit. This proposed converter circuit uses the traditional non-power-factor corrected circuit configuration with only few additional components. These are: an additional winding on the high frequency transformer, a small high frequency inductor and three diodes. The topology allows the output voltage regulation and input current shaping with a single power processing stage and one control chip. In addition, it is shown that this converter can be designed to offer soft switching of the full bridge switches. The operating principles of the proposed converter are discussed and its performance characteristics under steady state conditions are examined. A design procedure is illustrated to select the components of the converter for a 500 W power supply operating at 50 kHz. Theoretical results are verified with simulation and experimental tests on a 500 W laboratory prototype.

#### **ACKNOWLEDGMENTS**

The author would like to express his deep gratitude to Professor Praveen Jain for his invaluable guidance, advice and financial support throughout all stages of this thesis.

The Experimental work reported in this thesis was performed at Nortel Technologies in Ottawa. The author would like to thank Mr. H. Soin and D. Bannard of Nortel for their invaluable help in conducting the experimental work.

The author also wishes to thank all his colleagues in the Power Electronics Laboratory at Concordia University, particularly Jose Espinoza, Manu Jain and Randy Lee for their help.

The financial support of the National Science and Engineering Research Council (NSERC) and Nortel Technologies is greatfuly acknowledged.

Finally, the author would like to thank all his friends and family members for their support and help.

## TABLE OF CONTENTS

| Page                                                                                                   |

|--------------------------------------------------------------------------------------------------------|

| List of Figuresix                                                                                      |

| List of Acronymsxiii                                                                                   |

| List of Principal Symbolsxiv                                                                           |

|                                                                                                        |

| CHAPTER 1. INTRODUCTION                                                                                |

| 1.1. General Introduction2                                                                             |

| 1.2. Literature Review3                                                                                |

| 1.3. Thesis Objectives and Scope6                                                                      |

|                                                                                                        |

| CHAPTER 2. CIRCUIT DESCRIPTION AND MODES OF OPERATION                                                  |

| 2.1. Introduction9                                                                                     |

| 2.2. Description of the Proposed Circuit9                                                              |

| 2.3. Principle of Operation11                                                                          |

| 2.4. Circuit Modes of Operation13                                                                      |

| 2.4.1. Mode 1, Interval [t <sub>1</sub> , t <sub>2</sub> ]: Q <sub>1</sub> , Q <sub>3</sub> Conduction |

| 2.4.2. Mode 2, Interval [t <sub>2</sub> , t <sub>3</sub> ]: Left Leg Transition16                      |

| 2.4.3. Mode 3, Interval [t <sub>3</sub> , t <sub>4</sub> ]: Primary and Secondary Free-wheeling18      |

| 2.4.4. Mode 4, Interval $[t_4, t_5]$ : $I_p$ is zero, $I_{aux}$ is charging $C_{dc}$ 20                |

| 2.4.5. Mode 5, Interval [t <sub>5</sub> , t <sub>6</sub> ]:Turning on Q <sub>2</sub> at zero current20 |

| 2.4.6. Mode 6, Interval [t <sub>6</sub> , t <sub>7</sub> ]: Power Cycle, Linear Current Rising22       |

| 2.4.7. Mode 7, Interval [t <sub>7</sub> , t <sub>8</sub> ]: Transition of the left leg, Q <sub>4</sub> Turn of | 24 |

|----------------------------------------------------------------------------------------------------------------|----|

| 2.4.8. Mode 8, Interval [t <sub>8</sub> , t <sub>9</sub> ]: Q <sub>1</sub> turn on                             | 25 |

| 2.4.9. Mode 9, Interval [t <sub>9</sub> , t <sub>10</sub> ]: Q <sub>2</sub> turn off                           | 26 |

| 2.5. Losses During Switching Operation                                                                         | 26 |

|                                                                                                                |    |

| CHAPTER 3. STEADY STATE ANALYSIS OF THE CIRCUIT FOR CONTI-                                                     | •  |

| NUOUS OUTPUT CURRENT                                                                                           |    |

| 3.1. Introduction                                                                                              | 30 |

| 3.2. States of Operation                                                                                       | 32 |

| 3.2.1. State one: Auxiliary Current Linearly Rising                                                            | 33 |

| 3.2.2. State two: Auxiliary Current Linearly decreasing                                                        | 36 |

| 3.2.3. State three: Auxiliary Current is Zero                                                                  | 39 |

| 3.3. Turns Ratio of the High Frequency Transformer                                                             | 39 |

| 3.4. Modes of Conduction and Value of the Auxiliary Inductor                                                   | 40 |

| 3.4.1. Value of the Auxiliary Inductor                                                                         | 40 |

| 3.4.2. Modes of Conduction of the Auxiliary Inductor                                                           | 42 |

| 3.5. DC Link Voltage                                                                                           | 45 |

| 3.6. Performance Characteristics                                                                               | 47 |

| 3.6.1. RMS Current Through the Switches                                                                        | 47 |

| 3.6.2. Input RMS Current                                                                                       | 50 |

| 3.6.3. DC Link Capacitor Current                                                                               | 52 |

| 3.6.4. Output Filter Capacitor RMS Current                                                                     | 54 |

| 3.6.5. Output Filter Inductor and Current Ripple                    | 56 |

|---------------------------------------------------------------------|----|

| 3.6.6. Output Voltage Ripple                                        | 57 |

| 3.6.7. Input Power Factor                                           | 57 |

| 3.6.8. Total Harmonic Distortion                                    | 57 |

| 3.7. Conclusions                                                    | 58 |

|                                                                     |    |

| CHAPTER 4. STEADY STATE ANALYSIS OF THE CIRCUIT FOR DIS-            |    |

| CONTINUOUS OUTPUT CURRENT                                           |    |

| 4.1 Introduction                                                    | 59 |

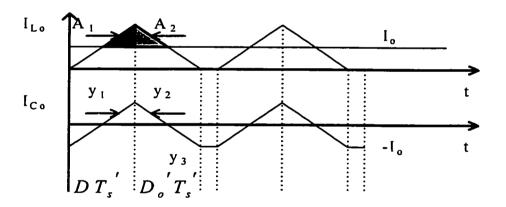

| 4.2 Summary of the Steady State Analysis for DACM and COCM          | 60 |

| 4.3 Steady State Analysis for DACM and DOCM                         | 61 |

| 4.4. Performance Characteristics of the converter for DACM and DOCM | 64 |

| 4.4.1. RMS Current Through the Switches                             | 64 |

| 4.4.2. DC Link Capacitor RMS Current                                | 67 |

| 4.4.3. Output Voltage Ripple                                        | 69 |

| 4.4.4. RMS Current Through the Output Filter Capacitor              | 70 |

| 4.5. Comparison of Performance Characteristics of COCM and DOCM     | 72 |

| 4.6. Conclusions                                                    | 77 |

|                                                                     |    |

| CHAPTER 5. DESIGN PROCEDURE AND GUIDELINES                          |    |

| 5.1 Introduction                                                    | 79 |

| 5.2 Design Procedure and Example                                    | 81 |

| 5.2.1 Design Specifications81                                          |

|------------------------------------------------------------------------|

| 5.2.2 DC Link Voltage Value82                                          |

| 5.2.3 The Turns Ratio of the High Frequency Transformer82              |

| 5.2.4 Switching Frequency Considerations                               |

| 5.2.5 The Auxiliary Inductor83                                         |

| 5.2.6 The Switch RMS Current83                                         |

| 5.2.7 Output Filter Inductor83                                         |

| 5.2.8 Input RMS Current84                                              |

| 5.2.9 Output Filter Capacitor84                                        |

| 5.2.10 DC Link Capacitor RMS Current85                                 |

| 5.3 Simulation and Experimental Results of The Designed Converter85    |

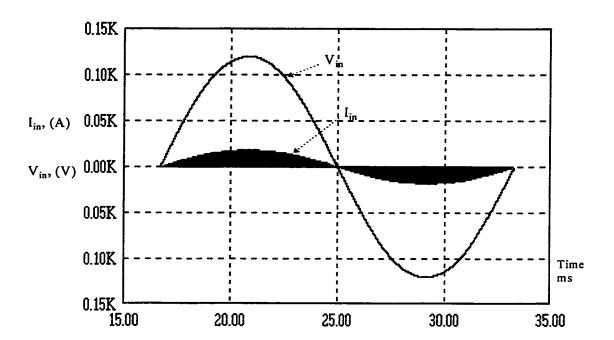

| 5.3.1 Simulated Input Current Waveform86                               |

| 5.3.2 Simulated Voltage at the Front - End Diode Rectifier Terminals88 |

| 5.3.3. Simulated DC Link Voltage                                       |

| 5.3.4. Experimental Results90                                          |

| 5.4 Conclusions91                                                      |

| CHAPTER 6. CONCLUSIONS                                                 |

| 6.1 Summary92                                                          |

| 6.2. Conclusions92                                                     |

| 6.3. Suggestions for Future Work93                                     |

|                                                                        |

| REFERENCES94                                                           |

## LIST OF FIGURES

| CHAPTER   | 1                                                                    | page |

|-----------|----------------------------------------------------------------------|------|

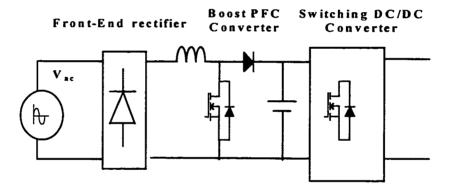

| Fig. 1.1  | Traditional Switch-Mode Power Supply (SMPS)                          | 2    |

| Fig. 1.2  | Input Voltage and Current Waveforms for the Traditional SMPS         | 2    |

| Fig. 1.3  | Two-Stage Power Factor Correction Circuit                            | 4    |

| Fig. 1.4  | Boost Converter in the Role of PFC Converter                         | 4    |

|           |                                                                      |      |

| CHAPTER   | 2                                                                    |      |

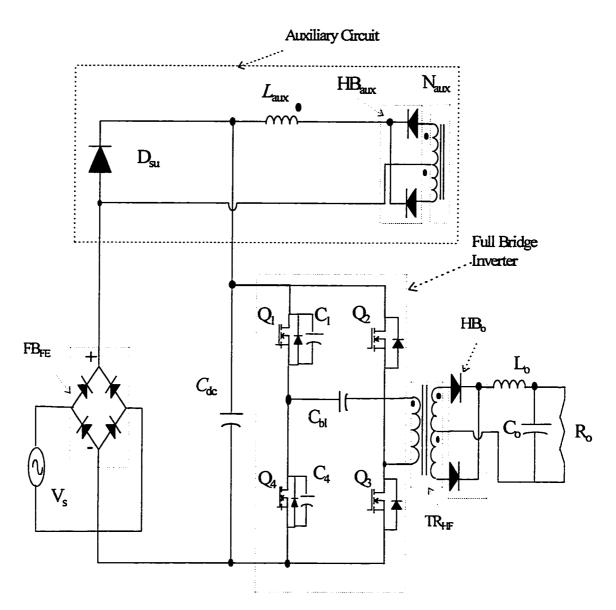

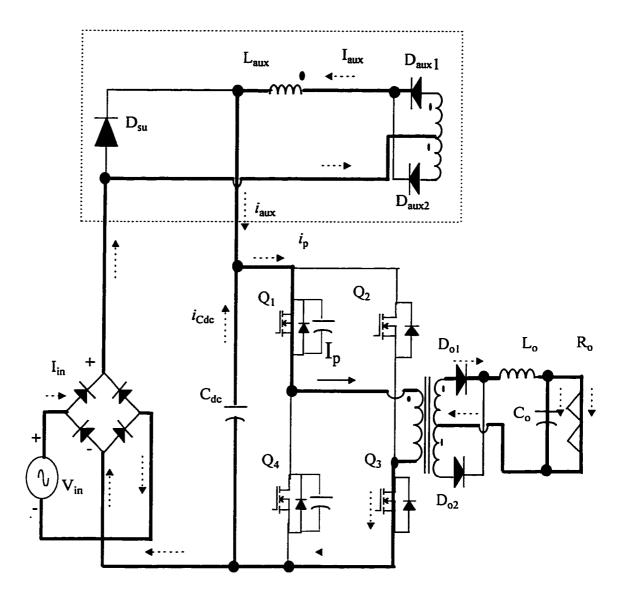

| Fig. 2.1. | Power circuit of the New Single Stage Full-Bridge Power Factor       |      |

|           | Corrected AC/DC Converter                                            | 12   |

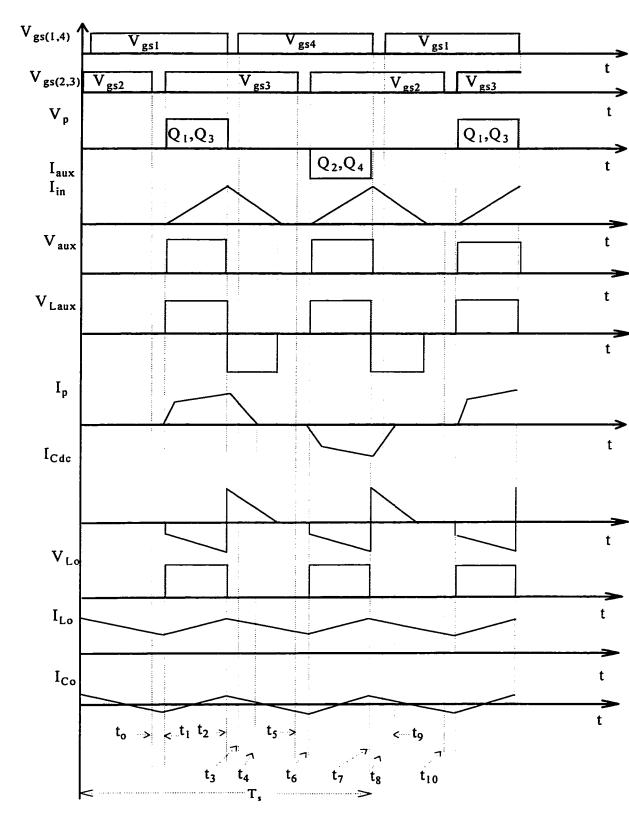

| Fig. 2.2  | Operating Waveforms of the Converter                                 | 14   |

| Fig. 2.3  | Mode I: Power Transfer Cycle: Q1 and Q3 are conducting               | 15   |

| Fig. 2.4  | Mode 2: Left Leg Transition                                          | 17   |

| Fig. 2.5  | Mode 3: Primary Free-Wheeling                                        | 19   |

| Fig. 2.6  | Mode 4: Zero Primary Current                                         | 21   |

| Fig. 2.7  | Mode 6 : Linear Current Ramping                                      | 23   |

| Fig. 2.8  | Mode 7 : Left Leg Transition                                         | 24   |

| Fig. 2.9  | Mode 8 : t=[t <sub>8</sub> ,t <sub>9</sub> ]- Q <sub>1</sub> turn on | 25   |

| Fig. 2.10 | Current Through the Auxiliary Inductor                               | 26   |

### **CHAPTER 3**

| Fig. 3.1  | Auxiliary Current Waveform                                               |

|-----------|--------------------------------------------------------------------------|

| Fig. 3.2  | State One Equivalent Circuit- On Time                                    |

| Fig. 3.3  | State one: a) Linear Rise of Auxiliary Current34                         |

| Fig. 3.4  | Power Transfer to the Load35                                             |

| Fig. 3.5  | Output Filter Inductor and Capacitor Currents                            |

| Fig. 3.6  | State Two Equivalent Simplified Circuit                                  |

| Fig. 3.7  | State Three: Zero Auxiliary Current                                      |

| Fig. 3.8  | Dc Link Capacitor Current41                                              |

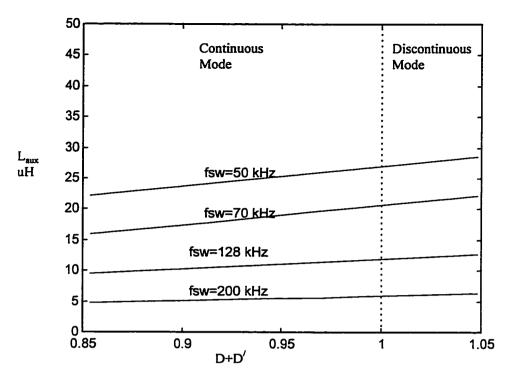

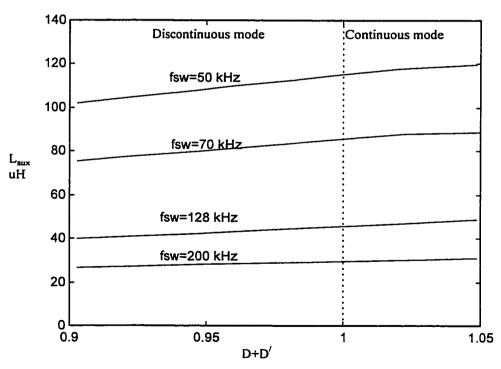

| Fig. 3.9  | The Value of the Auxiliary Inductor for Different Switching Frequencies  |

|           | and Input Voltage Levels42                                               |

| Fig. 3.10 | Boundary of CCM and DCM for $V_{in}$ =85-135 volts44                     |

| Fig. 3.11 | Boundary of CCM and DCM for $V_{in}$ =176-266 volts44                    |

| Fig. 3.12 | Current through the Auxiliary Inductor45                                 |

| Fig. 3.13 | Input Current and Auxiliary Voltage Waveforms50                          |

| Fig. 3.14 | Current through the Output Filter Components54                           |

|           |                                                                          |

| CHAPTER 4 | •                                                                        |

| Fig. 4.1  | Output Filter Current and Voltage Waveforms for Operation at the Edge of |

|           | COCM and DOCM62                                                          |

| Fig. 4.2  | DC Link Capacitor Current for DOCM67                                     |

| Fig. 4.3  | Current through the Output Filter Capacitor for DOCM70                   |

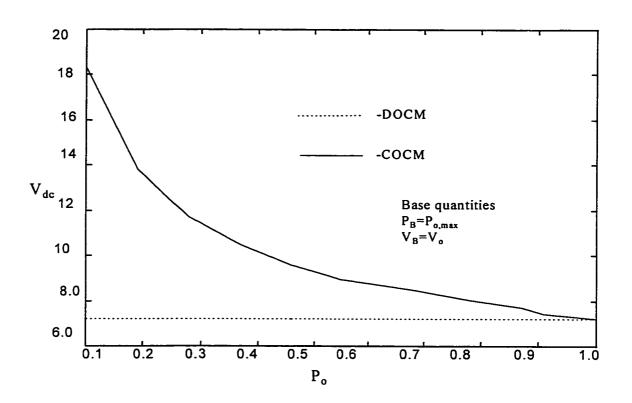

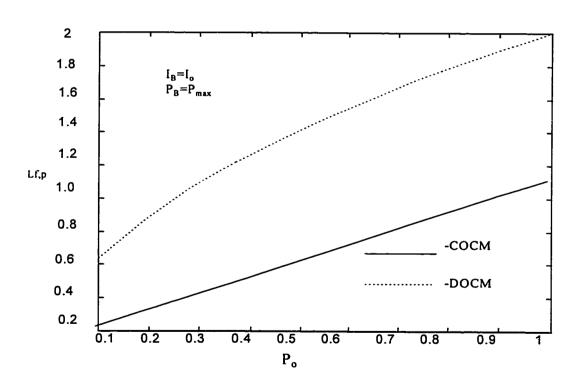

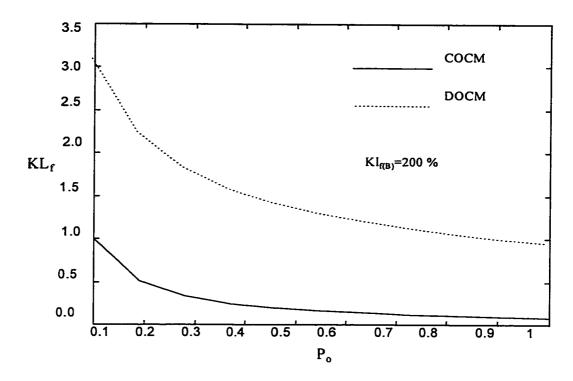

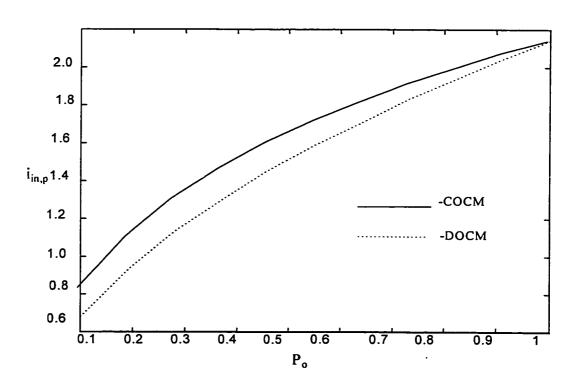

| Fig. 4.4  | Per Unit DC Link Voltage73                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------|

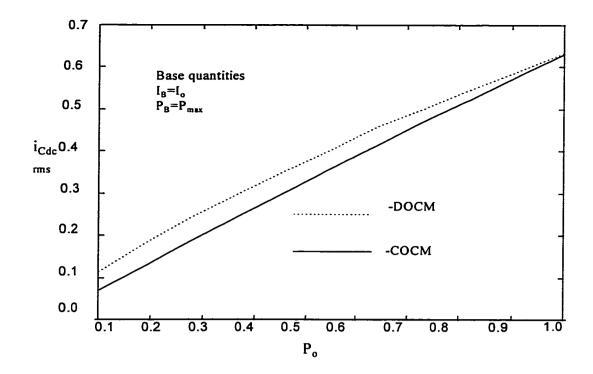

| Fig. 4.5  | Per Unit DC Link Capacitor RMS Current74                                                                 |

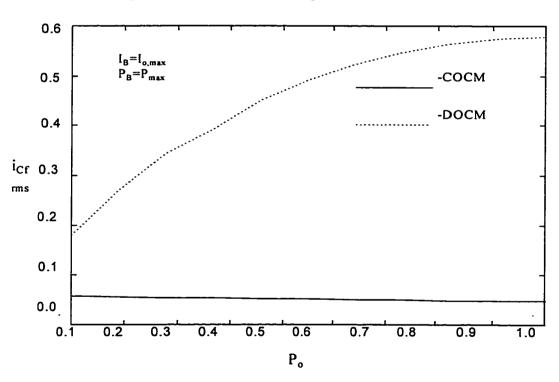

| Fig. 4.6  | Per Unit RMS Filter Capacitor Current74                                                                  |

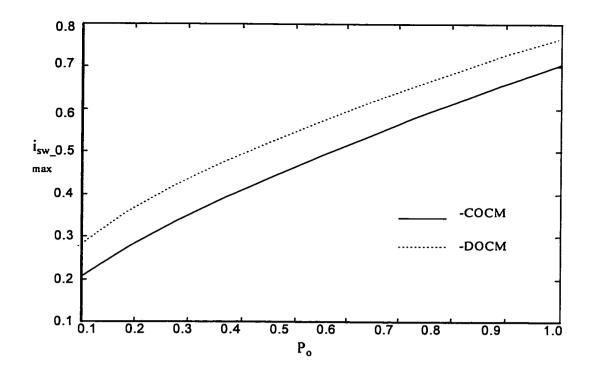

| Fig. 4.7  | Per Unit Switch RMS Current75                                                                            |

| Fig. 4.8  | Peak Output Inductor Current75                                                                           |

| Fig. 4.9  | Per Unit Ripple Factor of the Output Filter76                                                            |

| Fig. 4.10 | Per Unit Input Peak Current76                                                                            |

|           |                                                                                                          |

| CHAPTER 5 | 5                                                                                                        |

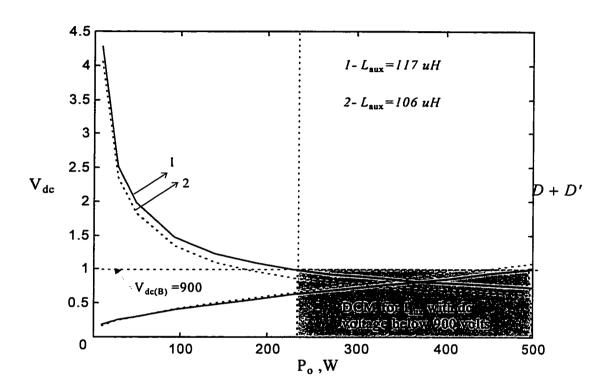

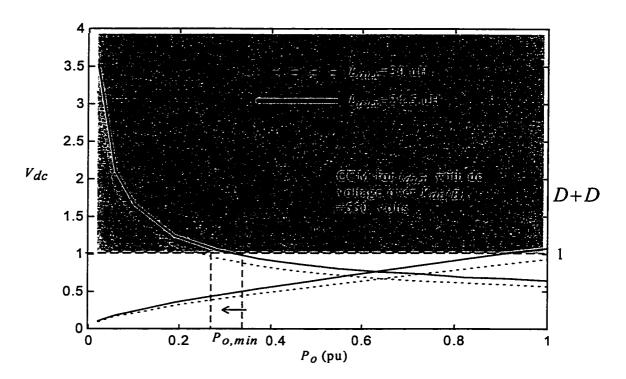

| Fig 5.1   | Influence of the Value of $L_{\rm aux}$ on $V_{\rm dc}$ and conduction mode of $I_{\rm aux}$             |

|           | for $V_{\text{s,rms}} = 176 - 266 \text{ volts}, f_{\text{sw}} = 50 \text{ kHz}79$                       |

| Fig 5.2   | Influence of the Value of $L_{\rm aux}$ on Vdc and Conduction mode of $I_{\rm aux}$                      |

|           | for $V_{\text{s,rms}} = 85-135 \text{ volts}, f_{\text{sw}} = 50 \text{ kHz}80$                          |

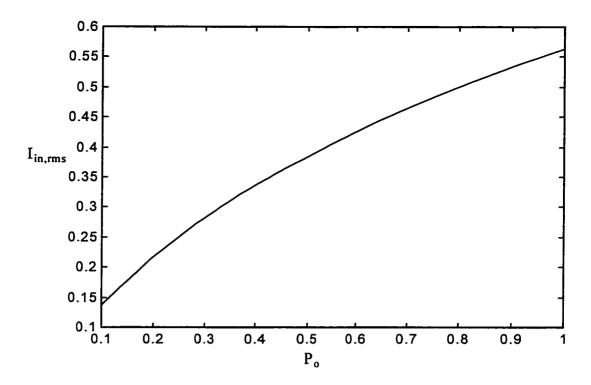

| Fig. 5.3  | Per Unit Input RMS Current for $V_{s,rms} = (85-135) \text{ V}85$                                        |

| Fig. 5.4  | Simulated Input Current and Voltage Waveforms for a 500 W Converter                                      |

|           | with $D_{\text{max}} = 0.45$ and $f_{\text{sw}} = 50 \text{ kHz}$ 86                                     |

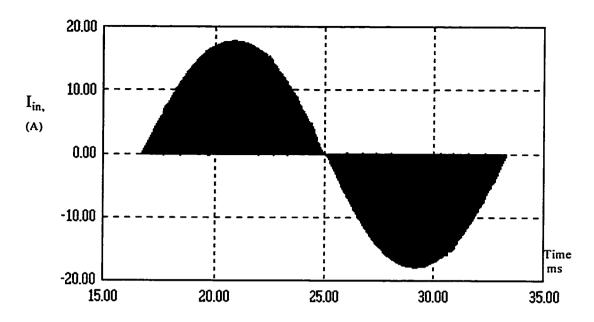

| Fig. 5.5  | Simulated Input Current Waveform for a 500 W Converter with $D_{\rm max}$                                |

|           | =0.45 and $f_{sw}$ = 50 kHz and $V_{s,rms}$ = 85 V87                                                     |

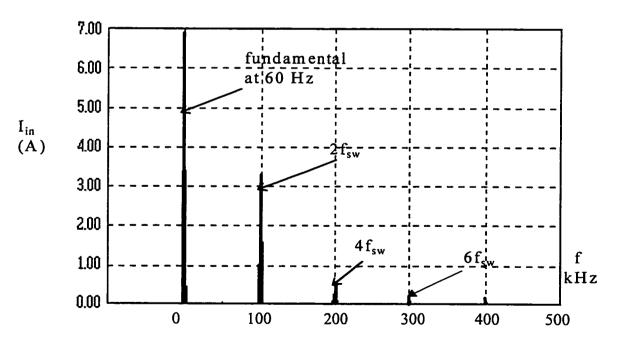

| Fig. 5.6  | Simulated Input Current Harmonic Spectrum for a 500 W Converter                                          |

|           | with $D_{\text{max}} = 0.45$ and $f_{\text{sw}} = 50$ kHz and $V_{\text{s,rms}} = 85$ V                  |

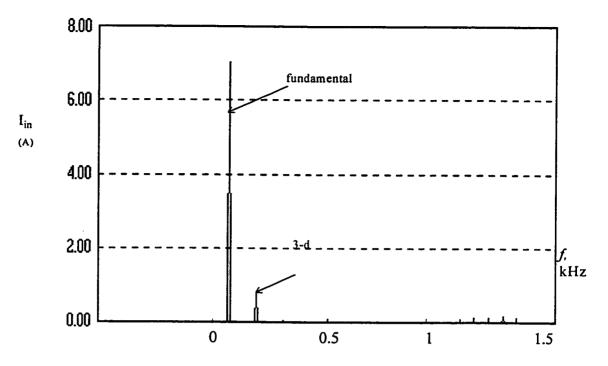

| Fig. 5.7  | Simulated Input Current (Low Frequency) Harmonic Spectrum for a                                          |

|           | 500W Converter with $D_{\text{max}} = 0.45$ and $f_{\text{sw}} = 50$ kHz and $V_{\text{s,rms}} = 85$ V89 |

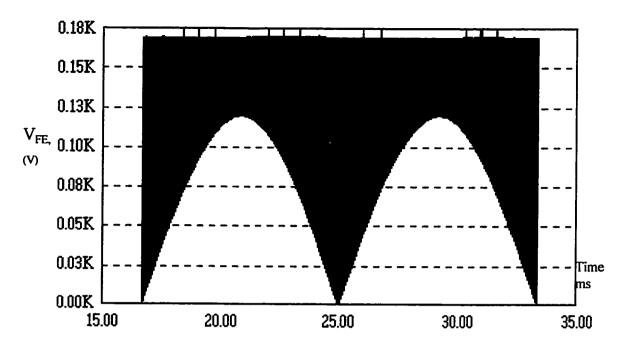

| Fig. 5.8  | Simulated Voltage across the Front - End Rectifier a 500 W Converter                    |

|-----------|-----------------------------------------------------------------------------------------|

|           | with $D_{\text{max}}$ = 0.45 and $f_{\text{sw}}$ = 50 kHz and $V_{\text{s,rms}}$ = 85 V |

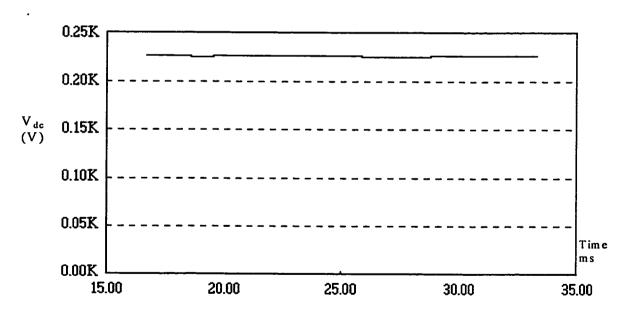

| Fig. 5.9  | Simulated DC link Capacitor Voltage Waveform for a 500 W Converter                      |

|           | with $D_{\text{max}} = 0.45$ and $f_{\text{sw}} = 50$ kHz and $V_{\text{s,rms}} = 85$ V |

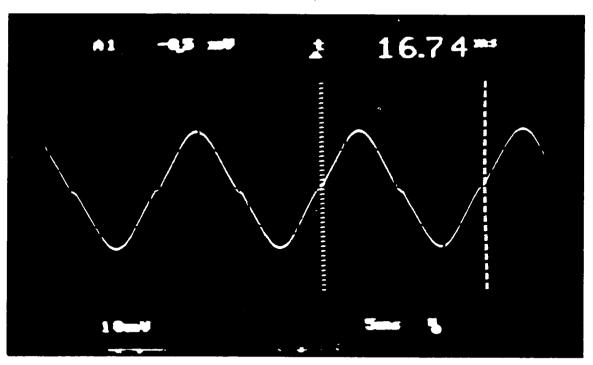

| Fig. 5.10 | Experimental Input Current Waveform Before Filtering for Operation at                   |

|           | 50 kHz and $V_{\text{s,rms}} = 85 \text{ V}$                                            |

| Fig. 5.11 | Experimental Input Current Waveform After Filtering for Operation at 50                 |

|           | kHz and Minimum Input Voltage9                                                          |

#### LIST OF ACRONYMS

AC Alternating Current

CACM Continuous Auxiliary Inductor Current Mode

COCM Continuous Output Inductor Current Mode

DACM Discontinuous Auxiliary Inductor Current Mode

DC Direct Current

DOCM Discontinuous Output Inductor Current Mode

FB Full Bridge DC/AC Converter

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

PFC Power Factor Correction

PWM Pulse Width Modulation

RMS Root Mean Square

SMPS Switch-Mode Power Supply

SS Single Stage

THD Total Harmonic Distortion

uF Micro Farad

uH Micro Henri

ZCS Zero Current Switching

ZVS Zero Voltage Switching

#### LIST OF PRINCIPAL SYMBOLS

C<sub>bl</sub> Dc Blocking Capacitor

$C_{dc}$  Dc Link Capacitor

C<sub>o</sub> Output Filter Capacitor

Duty Cycle - Charging Time of auxiliary and Output Inductors

D' Discharging Time of Auxiliary Inductor

$D_{\text{aux}}$ ,  $D_{\text{aux}}$  Diodes of the Auxiliary Diode Rectifier

$D_{\text{max}}$  Maximum Duty Cycle

$D_o$  Discharging Time of Output Inductor

$D_{01}$ ,  $D_{02}$  Diodes of the Output Diode Rectifier

$D_{su}$  Start-up Diode

$f_{\rm L}$  Line Frequency

$f_{sw}$  Switching Frequency

$f_{\rm sn}$  Number of Switching Periods in one line frequency period

*i*<sub>aux</sub> Auxiliary Inductor Current

*i*<sub>aux,n</sub> N-th Component of the Auxiliary Current

i<sub>Cdc</sub> DC Link Capacitor Current

$i_{Cdc\_ln}$  N-th Component of the DC Link Capacitor Current During On Time

i<sub>Cdc\_In</sub> N-th Component of the DC Link Capacitor Current During Off Time

$i_{Cdc_n}$  N-th Component of the Overall DC Link Capacitor Current

I<sub>Cdc.rms</sub> DC Link Capacitor RMS Current

| <i>i</i> <sub>Co_1</sub> | Output Filter Capacitor Current During Charging Time        |

|--------------------------|-------------------------------------------------------------|

| <i>i</i> <sub>Co_2</sub> | Output Filter Capacitor Current During Discharging Time     |

| $I_{\rm co,rms}$         | Output Filter Capacitor RMS Current                         |

| i <sub>in_ln</sub>       | N-th Component of the Input Current During On Time          |

| i <sub>in_2n</sub>       | N-th Component of the Input Current During Off Time         |

| i <sub>in_n</sub>        | N-th Component of the Overall Input Current                 |

| $I_{in,rms}$             | Input RMS Current                                           |

| $i_{Lo}$                 | Output Inductor Current                                     |

| $I_{Lo,p}$               | Peak Output Inductor Current                                |

| $i_{M}$                  | Magnetizing Current                                         |

| i <sub>o</sub>           | Instantaneous Output Current                                |

| $I_{ m o,avg}$           | Average Output Current                                      |

| $I_{p}$                  | Primary Current                                             |

| i <sub>sw</sub>          | Current through Full Bridge Switches                        |

| $I_{ m sw,rms}$          | RMS Switch Current                                          |

| $K_{ripple}$             | Ratio of Output Inductor Ripple to The Rated Output Current |

| $L_{\rm aux}$            | Auxiliary Inductor                                          |

| $L_{o}$                  | Output Filter Inductor                                      |

| $n_{ m aux}$             | Turns Ratio of Primary to Auxiliary Windings                |

| $n_{\rm s}$              | Turns Ratio of Primary to Secondary Windings                |

| $N_{ m aux}$             | Auxiliary Winding Number of Turns                           |

|                          |                                                             |

Primary Winding Number of Turns

$N_{\mathbf{p}}$

N<sub>s</sub> Secondary Winding Number of Turns

$P_{(B)}$  Base Power

P<sub>o</sub> Output Power

$P_{\text{o,disc}}$  Output Power For Discontinuous Output Inductor Current

$P_{\text{sw,loss}}$  Switching Losses

Q<sub>1-</sub>Q<sub>4</sub> Switches of The Full Bridge

R<sub>o</sub> Output Load Resistance

$t_{\rm on}$  On Time

$t_{\rm off}$  Off Time

$t_1$ - $t_{10}$  Switching Instants of The full Bridge switches

$T_{\rm L}$  Line Frequency Period

T<sub>s</sub> Switching Frequency Period

$T_s'$  Half Switching Frequency Period, or Auxiliary Current Waveform Period

V<sub>aux</sub> Auxiliary Added Voltage

$V_{(B)}$  Base Voltage

V<sub>dc</sub> DC Link Voltage

$V_{\text{laux}}$  Voltage Across the Auxiliary Inductor

V<sub>o</sub> Output Voltage

V<sub>p</sub> Primary Voltage

V<sub>s</sub> Peak Input Voltage

$V_{s,rms}$  RMS Input Voltage

V<sub>s.max</sub> Maximum Value of Line Voltage

$V_{\rm s,min}$  Minimum Value of Line Voltage

$V_{\rm sn}$  Value of Input Voltage at the n-th Switching Period

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 General Introduction

A desired feature in most of today's switch-mode power supplies (SMPS) is to improve power factor and thereby to comply with various national and international regulations on harmonic pollution of the utility (such as IEC 555-2, IEC 1000-3-2 and IEEE 519) in line operated electronic equipment [1]-[2].

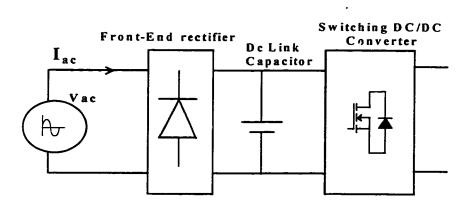

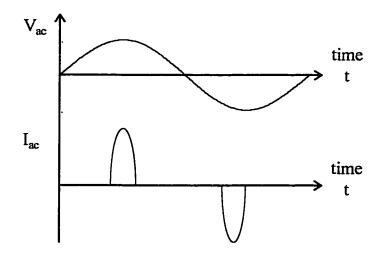

Power factor is defined as the ratio of the real power measured in Watts to the apparent power which is the product of the RMS current multiplied by the RMS voltage. However, it has been historically defined in terms of a phase-shift between the voltage and current waveforms. In a SMPS, shown in Fig. 1.1, which uses a front-end diode rectifier to provide a dc voltage across a bulky dc link capacitor, poor input power factor does not come from the phase-shift between the line voltage and current. Rather it is the discontinuous charging of the dc link filter capacitor, which results in a narrow pulse of high peak current as shown in Fig. 1.2. This leads to a low input power factor ( < 0.65) [3] and high total harmonic distortion.

High harmonic content of the input current causes a voltage distortion at the point of common coupling causing over-voltages. This is unacceptable especially if sensitive equipment such as mainframe computers and telecommunication equipment are connected to the same point of common coupling.

Traditionally their are two ways of shaping the input current waveform so that the overall off-the-line AC/DC converter is seen as a resistive load by the ac mains. The first is the passive approach in which a 60 Hz inductor connected to the ac mains is used, but this is not a practical solution, as it adds to the size and weight of the power supply, in a time when these parameters are minimized by the use of higher switching frequencies. The second is the active approach, where a DC/DC converter is used to shape the input current waveform.

Fig. 1.1 Traditional Switch-Mode Power Supply (SMPS)

Fig. 1.2 Input voltage and current waveforms for a traditional SMPS

#### 1.2 <u>Literature Review</u>

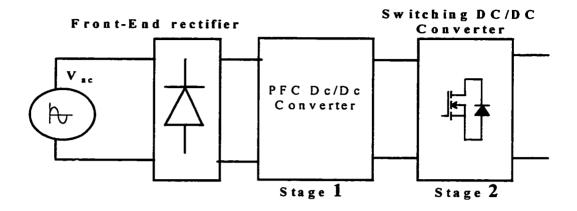

Active power factor correction techniques which are used to provide a sinusoidal input current for SMPS that use a front-end diode rectifier have been widely reported in the literature. The two stage technique which uses a separate DC/DC converter to perform the input current shaping is shown in Fig 1.3, [4]-[5]. This approach which is presented in Fig 1.4 is mostly used with a boost converter in the role of wave-shaper [6]-[7]. The boost converter has an output voltage across the DC capacitor, which is higher than the peak input voltage. When the switch is on, current rises and flow through the switch. When the switch is off, current falls and flow through the diode to the output. The input current is shaped to be sinusoidal if the rise and fall times are programmed to track a sine wave. The boost converter might operate in continuous mode for high power or in discontinuous mode for lower power applications [8]. Although the two-stage PFC approach has many advantages, it has some drawbacks. For instance, it has two power stages and two control circuits are therefore needed, it is inefficient and is not cost effective [9] as in the case of low power applications.

The drawbacks associated with two-stage PFC methods motivated several researchers to find other ways to provide both input current shaping and output voltage regulation. Thus, a new class of new single stage PFC (SS-PFC) topologies have been proposed [10]-[20].

The use of the boost converter topology to perform both functions of current shaping and output voltage regulation was reported in [6]-[7], and [11]-[13]. However

this approach has a main drawback: that is bandwidth of the output voltage regulation is limited to few Hertz [14].

Fig. 1.3 Two-Stage power factor correction circuit

Fig. 1.4. Boost converter in the role of PFC converter

The buck-boost derived topologies were proposed to perform PFC mainly because they emulate a natural resistor when operating in discontinuous conduction mode (DCM) [15]-[16]. They can also offer an output voltage less or higher than the input voltage [8].

Other topologies such as forward derived topologies were also presented in [11]-[12] and [17]-[20]. These topologies are appropriate for low power levels up to 250 watts.

A new family of isolated power factor corrected switching power supplies have been proposed in [21] and design considerations for these converters have been presented in [22]. In these topologies, the power factor correction cell is followed by a DC/DC converter cell, and both cells are operated in DCM. The voltage across the energy storage capacitor is independent of the load, but still increases with line voltage and decreasing ratio of input and output stage inductance. When the DC/DC cell is operated in continuous conduction mode (CCM), which is preferable for low output voltage, light load current applications. The negative effect is a load dependent variation of the energy storage capacitor voltage [23]-[24].

The use of magnetic amplifiers (magamps) for PFC has also been reported, where the magamp controls the rectified line current, while the fast output regulation is provided independently. This is done through pulse width modulation (PWM) of the active switch of the Cuk converter as shown in [25] or PWM of the bridge switches as shown in [14]. The use of magamps with DCM provide input current shaping with fast voltage regulation, while keeping constant the voltage on the energy storage capacitor regardless of load and line eliminating the increased voltage stress on the transistors and diodes.

A boost supply using resonant techniques might be used in series with the energy storage capacitor to provide high input power factor in a single stage configuration [26]. Other resonant SS-PFC circuits based on the half bridge converter [3] and forward converter topologies [20]. The Characteristics of full bridge parallel and series-parallel

converters operating in high power factor mode were presented in [27]. These converters offer a power factor up to 0.96. Unfortunately, the resonant converters use resonant techniques, with variable frequency operation which leads to higher circulating currents and variable frequency operation that complicates EMI filter design.

#### 1.3 Thesis Objectives and Scope

The objectives of this thesis are to propose and analyze a new single stage power factor corrected AC/DC converter which overcomes several of the drawbacks mentioned in the previous section. The scope of this thesis is limited to the analysis of the characteristics of the proposed converter topology under steady-state conditions. Emphasis is given on demonstrating the operating principle, modes of operation, and derives circuit equations.

The major contributions of this thesis are:

- (1) Proposing a new single stage power factor corrected AC/DC converter topology that features simple power and control circuitry.

- (2) Performing steady state analyses of the proposed converter in both continuous and discontinuous modes of operation.

- (3) Selection of a proper control technique to modulate the full bridge to provide close to zero switching losses.

- (4) Development of a design procedure to choose circuit components.

- (5) Experimental verification of the proof-of-concept of the proposed converter.

The contents of this thesis are organized as follows:

In Chapter 2, a general description of the new single-stage power factor corrected full-bridge converter is provided. The principle of operation is explained in details and the operation of the converter over a switching period is described in terms of nine operating modes. The issue of switching losses and requirements for soft switching are given in this chapter as well.

In Chapter 3, the steady state analysis of the proposed converter for continuous output current is performed. The steady state operation analysis is based on three different states of the auxiliary inductor current waveform. An alternative method to find the value of the auxiliary inductance necessary for proper operation of the circuit is proposed. The method also provides a way of finding the turns ratios of the high frequency transformer. The Dc link voltage depends on the duty cycle, load, output and auxiliary inductances. Performance characteristics of the converter such as RMS current through the switches, capacitors, RMS. input current, output voltage and current ripples and power factor are also presented.

In Chapter 4, the operation of the converter with discontinuous output inductor current mode (DOCM) is proposed. This mode of operation reduces the dc link voltage value to acceptable levels. The steady state analysis of the converter in this mode is provided. A comparison of performance characteristics for the converter operating in both COCM and DOCM is presented and results are illustrated in the form of graphs.

In Chapter 5, the design issues of the SS-FB-PFC converter are considered. The choice of operating switching frequency is explained and the auxiliary inductor is chosen.

The design procedure is presented and verified with simulated and experimental results.

In Chapter 6, the conclusions of this thesis are given and suggestions for future work are presented.

#### **CHAPTER 2**

# DESCRIPTION OF THE PROPOSED CONVERTER CIRCUIT AND MODES OF OPERATION

## 2.1 <u>Introduction</u>

This chapter provides a general description of the proposed single stage high power factor full bridge AC/DC converter topology. Details of the circuit and its operation principle are presented.

Description of the proposed circuit is given in section 2.2. In Section 2.3 the principle of operation is described. Modes of operation of the circuit are discussed in section 2.4. In Section 2.5 the issues and requirements for loss-less switching operation are discussed.

#### 2.2 Description of the Proposed Converter Circuit

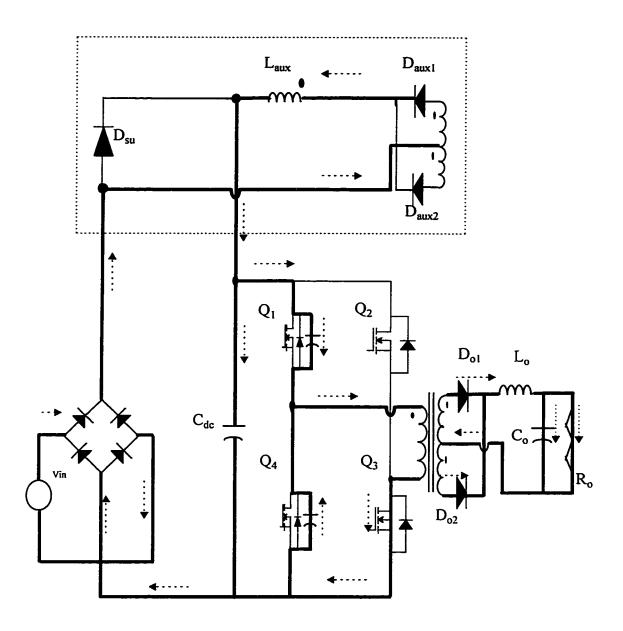

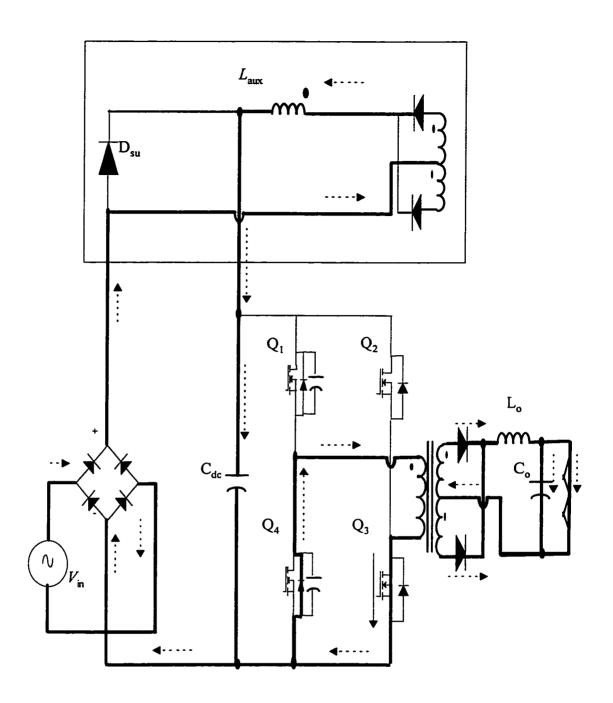

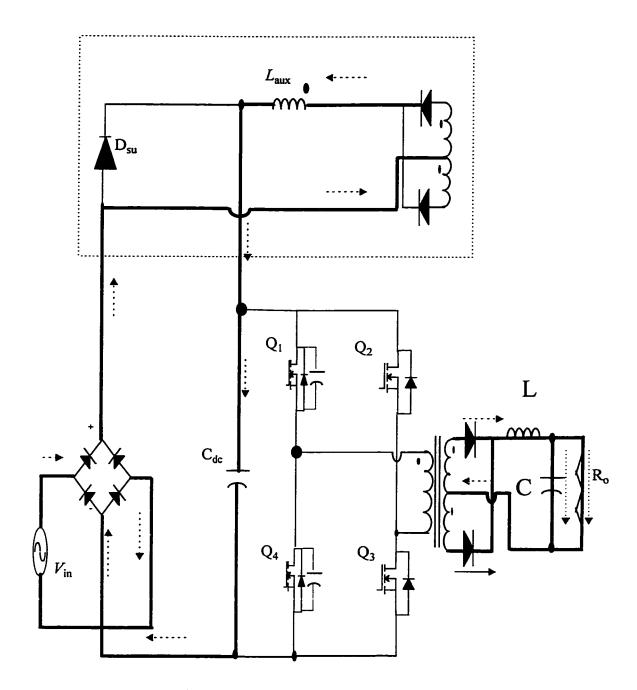

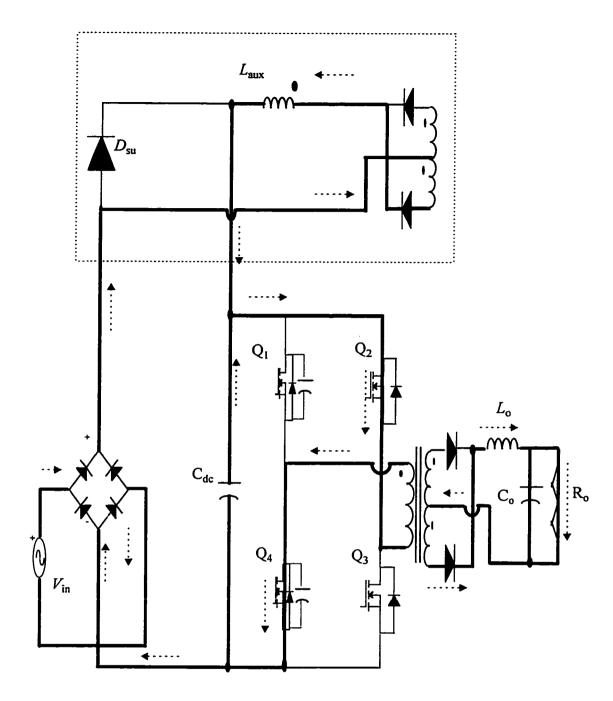

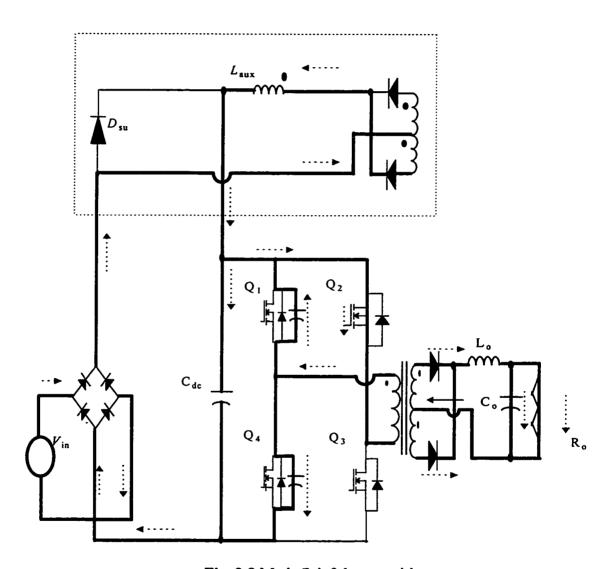

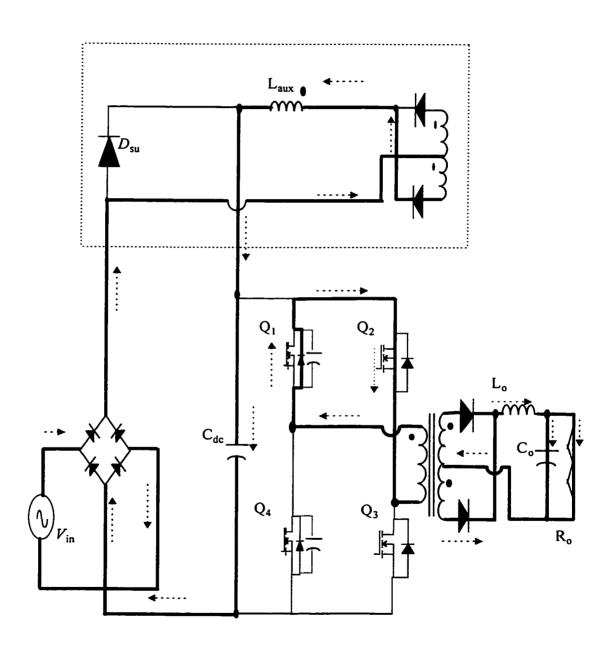

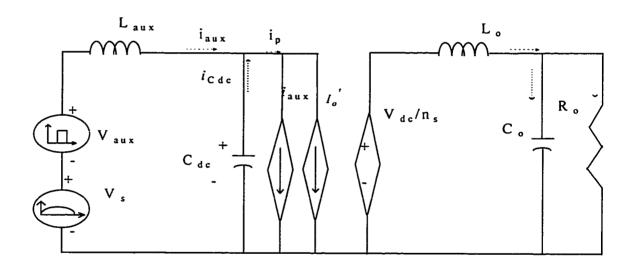

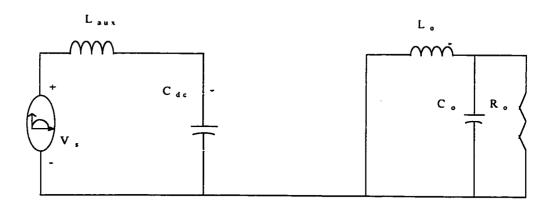

The proposed single-stage PFC full bridge AC/DC converter is shown in Fig. 2.1, which consists of:

- (a) Front-End Diode Rectifier (FB<sub>FE</sub>) which is used to convert the ac input voltage to an uncontrolled DC voltage across the DC link capacitor,

- (b) DC Link Capacitor ( $C_{dc}$ ) which provides the filtering action for the 120 Hz component and hold-up time,

- (c) Full Bridge DC/AC Inverter (FB) which consists of four MOSFET switches that have built-in anti-parallel diodes. Phase shift control is used to control the switching action of the full bridge switches.

- (d) DC Blocking Capacitor (C<sub>bl</sub>) which is used to block any net dc component that might saturate the high frequency transformer.

- (e) High Frequency Transformer ( $TR_{HF}$ ) which has three windings: The primary winding (with  $N_P$  turns) is connected to the FB legs, the secondary winding (with  $N_S$  turns) is connected to the Output Full-Wave Diode Rectifier ( $HB_o$ ), and the third auxiliary winding (with  $N_{aux}$  turns) is connected to the Auxiliary Full-Wave Diode Rectifier ( $HB_{aux}$ ).

- Auxiliary Circuit which includes the Auxiliary Transformer Winding (with  $N_{aux}$  turns),  $HB_{aux}$  and Auxiliary Inductor ( $L_{aux}$ ). This auxiliary circuit is the key to the proper operation of the proposed circuit as a power factor correction circuit. A proper design of  $L_{aux}$  will cause the input current to be discontinuous and follow a sinusoidal shape, as the net positive voltage applied across this inductor during the conduction of any diagonal pair of the FB switches is necessarily the rectified ac mains voltage.

- (g) Output Filter which consists of Output Filter Capacitor ( $C_0$ ) and Inductor ( $L_0$ ) which might operate in continuous conduction mode (COCM), or in discontinuous current mode (DOCM) to reduce the dc link voltage to acceptable levels.

#### 2.3 Principle of Operation

The sinusoidal mains voltage is rectified through the front end bridge diode rectifier. A voltage from the auxiliary transformer winding which is rectified using half bridge diode rectifier is added to the rectified voltage. This forces the input current to follow a sinusoidal shape and flow in discontinuous manner. The full bridge phase shifted PWM converter topology provides a good choice to control the converter. Its control features are similar to regular PWM converter.

Four MOSFET switches ( $Q_1 - Q_4$ ) and a high frequency power transformer are used to form the full bridge. The capacitor  $C_{bl}$  is used to block any net dc voltage from appearing across the transformer primary and saturating it. A center-tapped secondary is used with ultra-fast rectifiers at the output. The gate drives of both legs,  $Q_1$ ,  $Q_4$  or  $Q_2$ ,  $Q_3$  are complementary with duty cycle close to 50%. However a known delay is introduced between turn-off of one switch and the turn-on of the other switch of the same leg to avoid simultaneous conduction of any two switches from the same leg. This delay also allows the capacitor across the switch to discharge to zero so that the switch is turned on at zero voltage.

The output voltage regulation is achieved by phase modulation, that is by adjusting the amount of time the right and left legs of the full bridge are in phase or out of phase with each other. When both legs are in phase, no power is transferred to the load. If they are out of phase full power is transferred or delivered. When  $Q_1$ ,  $Q_3$  are conducting, positive voltage is applied to the primary and when  $Q_2$ ,  $Q_4$  are conducting, negative

voltage is applied to it. During other periods the primary voltage is zero and energy stored in the output filter inductor free-wheels through the secondary.

Fig. 2.1 Power circuit of the New Single Stage Full-Bridge Power Factor Corrected AC/DC Converter

#### 2.4 <u>Circuit Modes of Operation</u>

The analysis of circuit operation and its topological modes are presented in this section. To be able to perform this analysis, the operating waveforms are presented in Fig. 2.2.

These waveforms show the gating signals of the FB switches. The amount of phase shift between the left and right legs is adjusted to keep the output voltage constant with changing line and load. Pulse duration of each switch is slightly less than 50 % of the switching period due to the time delay introduced between the gating signals of any two switches from the same leg. The effective duty cycle is defined as the time during which a diagonal pair conducts  $(Q_1, Q_3 \text{ or } Q_2, Q_4)$ . This duty cycle is maximum for minimum line voltage and maximum load. Also the current through the primary winding of the high frequency transformer and voltage across it are shown in this figure.

The operation of the circuit over a cycle of switching frequency could be explained in terms of the following topological modes of operation

### 2.4.1 MODE 1, Interval [t1, t2]: Q<sub>1</sub>, Q<sub>3</sub> Conduction

The circuit representing this topological mode of operation is shown in Fig 2.3. During this mode: At time  $t = t_1$ ,  $Q_3$  is turned on and power is transferred to the secondary winding as the diagonal pair of switches  $Q_1$  and  $Q_3$  are both conducting. The dc link capacitor discharges during this mode as the current flows in the negative direction, and the output inductor current reaches peak value at  $t = t_2$ .

Fig. 2.2 Operating Waveforms of the converter

Fig. 2.3 Mode I, Power Transfer Cycle:  $Q_1$  and  $Q_3$  are conducting

Conducting Elements:  $Q_1$ ,  $Q_3$ ,  $D_{o1}$ ,  $D_{aux1}$

Final Conditions:

$$i_p = \frac{I_o}{n_s} + i_{aux} \tag{2.1}$$

$$\begin{aligned}

v_{ds1} &= v_{ds3} = 0 \\

v_{ds2} &= v_{ds4} = V_p

\end{aligned}$$

(2.2)

The primary current is the sum of the reflected load current and the auxiliary current. Auxiliary current is linearly rising until it reaches its peak value. At the end of this interval switch  $Q_1$  is turned off at zero voltage.

#### 2.4.2 MODE 2, Interval $t = [t_2, t_3]$ : Left leg Transition

Mode 2 is shown in Fig. 2.4. When  $Q_1$  is turned off, the primary current,  $i_p$ , starts discharging  $C_4$  and charging  $C_1$  in a linear fashion. At time  $t_3$ , the voltage across  $Q_4$  reaches zero while the voltage across  $Q_1$  reaches  $V_{dc}$ . If  $Q_4$  is turned on after  $t_3$ , then it will turn on at zero voltage, thus reducing the switching losses. The rate of discharge is defined by the MOSFET capacitance and the primary current in the circuit. Thus, at higher load currents it is easy to achieve ZVS. The magnetizing current is assumed to be constant and very small and could be neglected during this interval as any change would be a negligible second-order effect. This mode ends when  $D_4$  starts conducting after  $v_{ds4}$  had reduced to zero voltage.

Conducting elements:  $Q_3$ ,  $C_1$ ,  $C_4$ ,  $D_{01}$ ,  $D_{02}$ ,  $D_{aux1}$

Initial conditions:  $v_{ds1} = v_{ds3} = 0$

$$v_{\rm ds2} = v_{\rm ds4} = V_{\rm dc}$$

Final Conditions:

$$t_3 = \frac{(C_1 + C_4)V_{dc}}{i_p} \tag{2.3}$$

Fig. 2.4 Mode 2: left leg Transition

State Equations:

$$v_{ds1} = \frac{i_P}{(C_1 + C_4)}t\tag{2.4}$$

$$V_{ds4} = v_p = V_{dc} - v_{ds1} = V_{dc} - \frac{i_p}{(C_1 + C_4)}t$$

(2.5)

## 2.4.3 MODE 3, Interval $t = [t_3, t_4]$ : Primary and Secondary Free-wheeling

This mode starts with  $v_{ds4}$  going to zero and  $D_4$  turning on. During this mode, the primary current free-wheels through  $Q_3$  and  $D_4$ . All variables remain unchanged during this interval. Switch  $Q_4$  can be turned on at zero voltage at any time during this interval. Turning  $Q_4$  on will divert the current from  $D_4$  to  $Q_4$ . The voltage across the primary is zero. The load current also free-wheels through the shorted secondary winding. Fig. 2.5 demonstrates the events during this mode.

Conducting elements:  $Q_1$ ,  $D_2$ /  $Q_2$ ,  $D_{o1}$ ,  $D_{o2}$ ,  $D_{aux1}$

Initial conditions:

$$v_{\rm ds1} = v_{\rm ds2} = V_{\rm dc}$$

and  $v_{\rm ds3} = v_{\rm ds4} = 0$

Fig. 2.5 Mode 3: Primary freewheeling

# 2.4.4 MODE 4, Interval $t = [t_4, t_5]$ : Primary Current is zero, $I_{aux}$ is charging $C_{dc}$

This mode starts when no switch is conducting and primary voltage and current are zero. The auxiliary current will charge the dc link capacitor. Secondary is freewheeling. Mode 4 is shown in Fig 2.6

Conducting Elements:  $D_{ol}$ ,  $D_{o2}$ ,  $D_{auxl}$

$$v_{\rm ds1} = v_{\rm ds2} = V_{\rm dc}$$

$$v_{ds3} = v_{ds4} = V_p = 0$$

Final Conditions:  $v_{ds4} = 0$ ,  $v_{ds1} = V_{dc}$

# 2.4.5 Mode 5, Interval $t = [t_5, t_6]$ : Turning on $Q_2$ at zero current

At instant  $t = t_6$ ,  $Q_2$  is turned on at zero current as the current ramps slowly due to leakage and auxiliary inductance and the voltage across the drain to source of  $Q_2$  becomes zero.

Fig. 2.6 Mode 4: Zero primary current

## 2.4.6 Mode 6, Interval $t = [t_6, t_7]$ : Power Cycle, Linear Current Ramping

During this mode, the primary current  $(i_p)$  falls down linearly and goes negative. Once the current reverses direction, (assuming  $Q_4$  has been turned on by then) the circuit remains in this mode until the primary current can support the load current through  $D_{o1}$ . At this point,  $D_{o2}$  turns off,  $Q_4$  and  $Q_2$  conduct and the dc link voltage appears across the primary winding of the transformer. The circuit representing this mode is shown in Fig. 2.7

Conducting Elements: Q2, Q4, Do2, Daux2

$$v_{\rm ds1} = v_{\rm ds3} = V_{\rm dc}$$

$$v_{\rm ds2} = v_{\rm ds4} = V_{\rm p} = 0$$

Final equations:

$$i_L = \frac{-I_o}{n_s} + i_{aux} \tag{2.6}$$

$$V_p = -V_{dc}$$

Fig. 2.7 Mode 6: Linear Current Ramping

# 2.4.7 Mode 7, Interval $t = [t_7, t_8]$ : Transition of the left leg, $O_4$ turn off.

At instant  $t = t_7$ ,  $Q_4$  is turned off at zero voltage,  $C_1$  is discharged to zero volts and  $C_4$  is charged to  $V_{dc}$ . After this instant  $Q_1$  can be turned on at zero voltage. Fig. 2.8 shows the circuit during this mode of operation

Fig. 2.8 Mode 7, left leg transition

# 2.4.8 Mode 8, Interval $t = [t_8, t_9]$ : $Q_1$ turn on

At instant  $t = t_8$ ,  $Q_1$  is turned on at ZV as  $C_1$  was fully discharged.  $D_1$  and  $Q_2$  are conducting during this interval which is similar to mode 3. This mode is shown in Fig. 2.9.

**Fig. 2.9** Mode  $8 - t = [t_8, t_9]$

## 2.4.9 Mode 9, Interval $t = [t_9, t_{10}]$ : $Q_2$ turn off

At instant  $t = t_{10}$ , switch  $Q_2$  is turned off at zero current (ZC). This mode is similar to mode 4 with zero primary current and auxiliary current charging the dc bus capacitor. This mode ends when  $Q_2$  is turned off and a complete cycle of operation ends at this point.

#### 2.5 Losses During Switching Operation

As was seen from the analysis of various modes of operation presented in section 2.3, the left leg switches are switched with zero voltage and those of the right leg with zero current.

The peak auxiliary current plays an important role in zero voltage switching as when one of the left leg switches turns off, its capacitor starts charging and the capacitor of the other switch in the same leg starts discharging. If the voltage becomes zero before the switch is turned on, then we achieve zero voltage switching, if not switching will be with some losses.

The energy stored in the auxiliary and leakage inductors at the time when  $Q_1$  is turned off should be equal to or greater than the energy stored in the output capacitance of the switch.

$$\frac{1}{2} (C_{ds} + C_{sn}) V_{dc}^{2} \le \frac{1}{2} (L_{aux} + L_{leak}) i_{p}^{2}$$

(2.7)

As the leakage inductance is very small compared to the auxiliary inductance, it is ignored in later discussions. Also, as we consider the most severe conditions for

switching ( with maximum losses), which occur close to no load condition, the primary current will be equal to the auxiliary current.

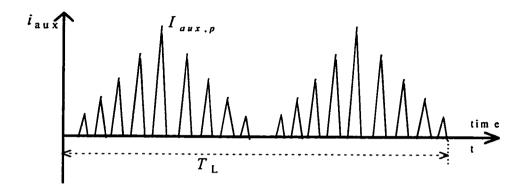

The auxiliary current is ac modulated, as shown in Fig. 2.10, so at the beginning of line frequency it has smaller values.

Fig. 2.10 Current through the auxiliary inductor

The instantaneous value of the auxiliary current in each n-th auxiliary current period

$$i_{aux,n} = I_{aux,p} Sin \left( \frac{nT_s}{T_L} 2\pi \right)$$

(2.8)

where  $V_{dc}$  is the dc link voltage which appears across the primary and any switch of the full bridge when it is off.

$T_L$  is the line frequency period.

$T_s$  is the a period of switching frequency, and  $\frac{T_s}{2} = T_s'$  is a period of the auxiliary current and equal to half a switching period.

The peak auxiliary current  $I_{aux,p}$  is written as:

$$I_{aux,p} = \frac{V_{s,max}}{L_{aux}} \frac{DT_s}{2} \tag{2.9}$$

Replacing  $(C_{ds} + C_{sn})$  by  $C_1$  and  $i_p$  by  $i_{aux}$  in (2.7) yields

$$\frac{1}{2}C_1V_{dc}^2 \le \frac{1}{2}(L_{aux} + L_{leak})i_{aux}^2$$

(2.10)

For known values of inductance, capacitance and dc link voltage, the minimum required current for fully discharging the capacitance is calculated as:

$$i_{aux,\min} \ge \sqrt{\frac{4C_1}{L_{mix}}V_{dc}^2} \tag{2.11}$$

When the instantaneous value of the auxiliary current  $(i_{aux,n})$  is less than  $i_{aux,min}$  for the whole line period, then switching losses exist and are expressed as:

$$P_{sw,loss} = \frac{1}{2} C_1 V_{dc}^2 f_{sw}$$

(2.12)

This is valid in case the auxiliary current is less than the minimum during the whole line frequency period, otherwise only a portion of these losses exist whenever  $i_{aux,n} < i_{aux,min}$ .

The value of the losses could be approximated by the following expression:

$$P_{sw,loss} = \frac{1}{2} C_1 V_{dc}^2 f_{sw} \frac{\left(\sin^{-1} \left(\frac{i_{aux,n}}{i_{aux,min}}\right)\right)}{\pi/2}$$

(2.13)

#### 2.6 Conclusions

This chapter presented the topological modes of operation of the proposed converter circuit. In each switching frequency period, nine distinctive modes were explained. It is noted that the left leg switches have ZV turn on and turn off, a small snubber capacitor is added to achieve ZVS at turn off if the parasitic capacitance value is not enough. Due to the presence of the auxiliary inductor, the right leg switches have a natural ZCS at both turn on and turn off.

The following conclusions about the switching losses are made: when operating at full load, the  $1/2CV^2$  losses negligible, but at light loads these losses tend to increase depending on the amount of peak energy stored in both the leakage and auxiliary inductors, whether it is enough to discharge the switch output capacitance before it turns on. This is the case for the left leg switches, but the right leg switches always have  $1/2CV^2$  losses.

#### CHAPTER 3

# STEADY STATE ANALYSIS OF THE CIRCUIT FOR CONTINUOUS OUTPUT CURRENT

#### 3.1 Introduction

In this chapter steady state analysis of the single stage power factor corrected converter described in chapter two is presented in detail. This analysis is important to predict steady state performance and to develop necessary equations for the proper choice of converter components.

The steady state analysis is carried out for continuous conduction mode of the output filter inductor (COCM) and the discontinuous conduction mode of the auxiliary inductor (DACM).

The steady state analysis of this converter is more complicated than that of the conventional converters due to the nature of current and voltage waveforms. Some of these waveforms have a switching frequency period ( $T_s = 1/f_{sw}$ ), while others have half switching frequency period ( $T_s/2$ ). This fact complicates the steady state analysis. For example, to obtain the value of the RMS current through the auxiliary inductor, the area under the  $I_{aux}$  curve in each cycle is found ( these waveforms repeat in shape, but differ in value or amplitude). Then all these areas are summed and averaged over the line frequency and the square root is taken for this sum.

In this chapter the circuit equations are derived and used to describe the proposed circuit. The schematic shown in Fig 2.1 represents the main power circuit. Simplified

equivalent circuits are used in the analysis as well. Section 3.2 presents the states (intervals) of operation. Section 3.3 shows how to find the turns ratio of the high frequency transformer. In Section 3.4 modes of conduction of the auxiliary current are discussed and its value is found. In Section 3.5 DC link voltage value is found as a function of duty ratio, output load and auxiliary inductance.

Performance characteristics of the converter such as RMS current through the switches, RMS input current, dc link capacitor current, output filter capacitor RMS current, input power factor, total harmonic distortion and the output current ripple are developed in Section 3.6.

## 3.2 States of Operation

The steady state analysis of the circuit is conducted using equivalent simplified circuits and using the following simplifying assumptions:

- (1) Magnetizing current is neglected due to the high value of magnetizing inductance.

- (2) The rectified line voltage  $|V_s|$  is constant during the switching period.

- (3) DC link voltage V<sub>dc</sub> is constant during a switching period.

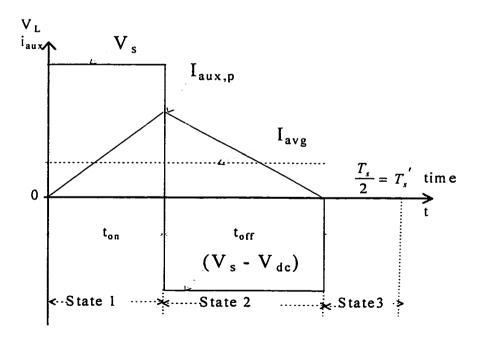

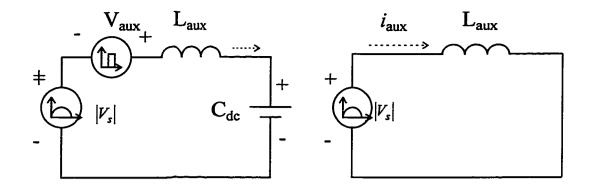

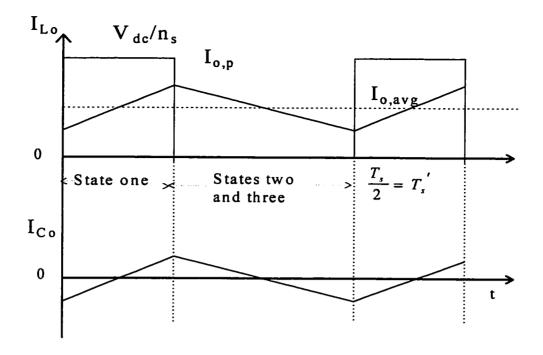

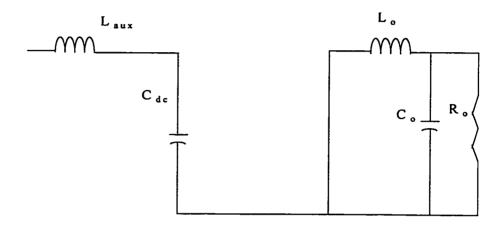

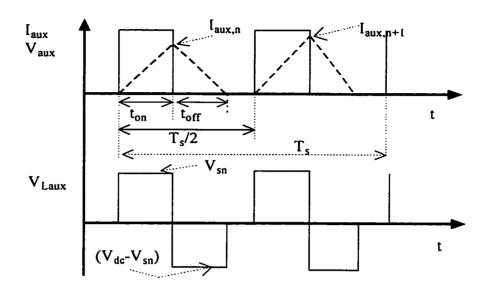

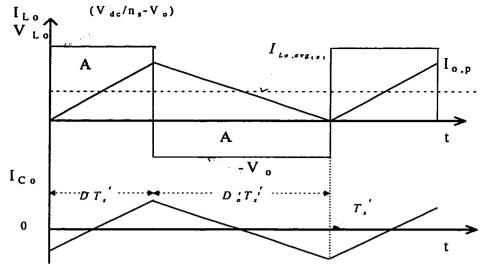

Circuit operation is better described in terms of the auxiliary current waveform during one cycle of operation, which is equal to half the switching period. The waveform is shown in Fig. 3.1.

Fig. 3.1 Auxiliary Current waveform

This waveform clearly shows three states or intervals of operation:

- (1) State One: The on-time interval: Linear Rise of the Auxiliary Current- ton

- (2) State Two: The off-time interval: Linear fall of the Auxiliary Current- toff

- (3) State Three: The dead-band interval: Auxiliary current is zero-  $T_s/2$ - $(t_{on}+t_{off})$

## 3.2.1 State One: Auxiliary Current linearly Rising

In this state current is rising as the net voltage across the inductor is positive. The circuit representing this state is shown in Fig. 3.2. During this interval the operation of the circuit is explained by the following events:

Fig. 3.2 State One Equivalent circuit- on time

a) Auxiliary current increases linearly with the net positive voltage applied across  $L_{aux}$  equal to  $|V_s|$  as shown in Fig. 3.3.

Fig. 3.3 State one a) Linear Rise of Auxiliary Current

$$V_{aux} = V_{dc} \frac{N_{aux}}{N_n} \tag{3.1}$$

Applying KVL to Fig. 3.3 yields

$$V_{Laux} = |V_s| + V_{aux} - V_{dc} \tag{3.2}$$

Assuming  $N_{aux} = N_{\rho}$

In a power transfer cycle, during first state  $V_{aux}$  equals  $V_{dc}$  and they cancel each other as they have different signs, this yields

$$V_{Laux} = |V_s| \tag{3.3}$$

and the auxiliary current is:

$$i_{aux} = \frac{|V_s|}{L_{aux}} \cdot t_{on} \tag{3.4}$$

b) Primary current is the sum of auxiliary current and load current reflected to the primary.

$$i_p = I_o' + i_{aux} \tag{3.5}$$

Also the primary current is the sum of the auxiliary inductor current and the dc link capacitor current:

$$i_p = i_{GL} + i_{ax} \tag{3.6}$$

By equating the two expression for the primary current (3.5) and (3.6)

$$i_{Cdc} + i_{\alpha\alpha} = I_o' + i_{\alpha\alpha} \tag{3.7}$$

By eliminating i<sub>aux</sub> from both sides, (3.7) becomes

$$i_{Cdc} = I_o' \tag{3.8}$$

This means that in this state the load draws the current from the dc link capacitor  $C_{dc}$  and discharges it.

c) Power is transferred to the load as a voltage is applied across the primary. This voltage is transferred to the secondary and then rectified. This mode is explained in Fig. 3.4 & 3.5

Fig. 3.4 State one c) Power transfer to the load

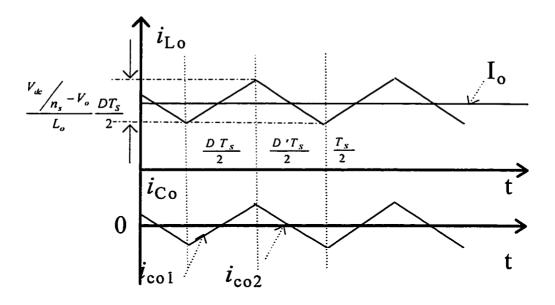

Fig. 3.5 Output filter inductor and capacitor currents

The duration of this period is the duty cycle

$$D = \frac{t_{on}}{T_{\star}'} \tag{3.9}$$

## 3.2.2 State Two: Auxiliary Current Linearly decreasing

In this state auxiliary current is decreasing (falling) as the net voltage across the auxiliary inductor is negative. The auxiliary voltage is zero and the following events take place:

a) The voltage across  $L_{\text{aux}}$  is negative dc voltage according to the following considerations

$$V_{Laux} = |V_s| + V_{aux} - V_{dc}$$

and  $V_{aux} = 0$

$$V_{Laux} = |V_s| - V_{dc} \tag{3.10}$$

The value of the dc link voltage which ensures the discontinuous operation for the auxiliary inductor could be found as follows.

The peak value of the auxiliary current is

$$I_{Laux,p} = \frac{V_s}{L_{aux}} t_{on} \tag{3.11}$$

Also it could be written as

$$I_{Laux,p} = \frac{V_{dc} - V_s}{L_{aux}} t_{off}$$

3.12)

The auxiliary current has to be discontinuous for proper operation of the circuit, so the following relationship has to be satisfied:

$$t_{on} + t_{off} \le T_s' \tag{3.13}$$

The time scale is normalized to simplify the presentation

$$D = \frac{t_{on}}{T_s'} \tag{3.14}$$

and

$$D' = \frac{t_{off}}{T_{-}} \tag{3.15}$$

Substituting (3.14) and (3.15) in (3.13) yields:

$$D + D' \le 1 \tag{3.16}$$

By equalizing (3.11) and (3.12) and substituting  $D' \le 1 - D$  in these equations, we have

$$\frac{V_s}{L_{aux}}DT_s' = \frac{(V_{dc} - V_s)}{L_{aux}}D'T_s'$$

(3.17)

And substituting (3.16) for D' in (3.17) yields

$$V_s D = (V_{dc} - V_s) D' \le (V_{dc} - V_s) (1 - D)$$

(3.18)

Equation (3.18) might be simplified and give the following expression

$$V_{dc} \ge \frac{V_s}{1 - D} \Rightarrow V_{dc} > V_s$$

(3.19)

Substituting (3.19) in (3.10) shows that the voltage across  $L_{aux}$  during this state is negative and current  $i_{aux}$  is decreasing.

2) The dc link capacitor is charged as the auxiliary current flows through it. Current in the secondary is freewheeling through the output diodes and load. At the end of this state auxiliary current becomes zero.

$$i_{\text{aux}} = i_{\text{Cdc}} \tag{3.20}$$

Fig. 3.6 shows the equivalent simplified circuit representing this state.

Fig. 3.6 State Two Equivalent Simplified Circuit

## 3.2.3 State Three: Auxiliary Current is zero $[T_s/2-(t_{on}+t_{off})]$

In this state the auxiliary current is zero as all the energy stored in the auxiliary inductor has been used to charge the dc link capacitor and the net dc voltage across the auxiliary inductor is also zero. The equivalent simplified circuit could be represented as shown in Fig. 3.7.

Fig. 3.7 State Three: Zero auxiliary current

During this state the output current is freewheeling through the output diodes and the load, auxiliary current is zero. This state continues until another power cycle starts.

## 3.3 Turns Ratio of the High Frequency Transformer

The turns ratio of the high frequency transformer is found using the value of minimum input voltage, maximum duty cycle and the rated output voltage.

For proper operation of the circuit the maximum pulse width  $(t_{on})$  should not exceed 90° which results in a maximum duty cycle of 50% (D =  $2t_{on}$ )

$$D = \frac{V_o}{V_{dr}} \frac{N_p}{N_s} = \frac{V_o}{V_{dr}} n_s$$

$$n_s = \frac{DV_{dc}}{V_o} \tag{3.22}$$

Also, the value of dc link voltage is found from (3.19) as

$$V_{dc} = \frac{V_s}{1 - D} \tag{3.23}$$

Using these equations the value of the turns ratio of the transformer is found Example:

$$D_{max} = 0.45$$

$$V_{s,min} = 248.902 \text{ V}$$

$$V_0 = 50 \text{ V}$$

The value of the dc link voltage is found from (3.23)

$$V_{dc} = \frac{Vs}{1 - D} = \frac{248.902}{1 - 0.45} = 452.55 \text{ V}$$

$$n_s = \frac{DV_{Cdc}}{V_o} = \frac{0.45 * 452.55}{50} = 4.07$$

we chose  $n_s = 4$  and the maximum duty cycle becomes:

$$D = \frac{V_o}{V_{GE}} n_s = \frac{50}{452.55} 4 = 0.442$$

## 3.4 Modes of Conduction and the Value of the Auxiliary Inductor

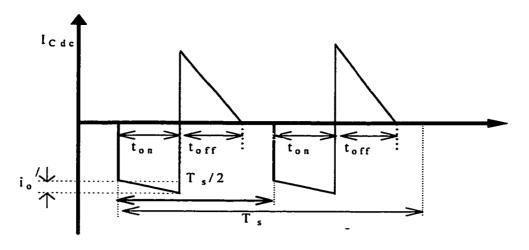

#### 3.4.1 Value of the Auxiliary Inductor

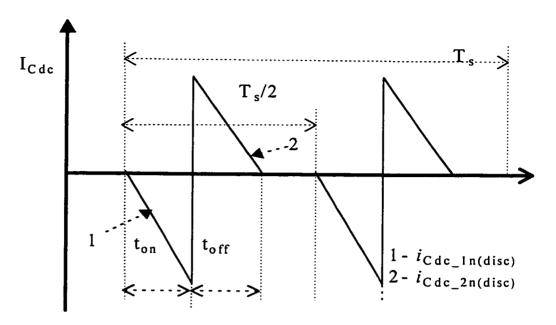

The dc link capacitor current waveform is shown in Fig. 3.8. This waveform is used to find the value of the auxiliary inductor.

Fig. 3.8 Dc link capacitor current

It is well known that in steady state the average current through the dc link capacitor is equal to zero. This fact is used to find the value of the auxiliary inductor.

$$i_{Cdc} = \frac{1}{T_L} \int_0^{T_L} i_{Cdc} \cdot dt = 0$$

$$= \frac{1}{T_L} \left( -\sum_{n=1}^{f_{sn}} \frac{DT_S}{2} \frac{V_o}{R_o} \frac{1}{n_s} + \sum_{n=1}^{f_{sn}} \frac{D'T_S}{4} \frac{V_{sn}}{L_{aux}} \frac{DT_s}{2} \right) = 0$$

(3.24)

Solving equation (3.24),  $L_{aux}$  is expressed as:

$$L_{aux} = \frac{R_o}{V_o^2} \frac{1}{T_L} \frac{\left(\frac{T_s}{2}D\right)^2}{2} \sum_{n=1}^{f_m} \frac{V_{sn}^2}{\left(1 - \frac{V_{sn}}{V_{dr}}\right)}$$

(3.25)

The value of the inductance as a function of input voltage and switching frequency is plotted in Fig. 3.9

The per unit inductor value could be expressed as:

$$L_{aux} = \frac{24.4\pi}{2\pi f_{sw} R_{o(Rated)}}$$

(3.25.a)

Fig. 3.9 The value of the auxiliary inductor for different switching frequencies and input voltage levels

### 3.4.2 Modes of Conduction of the Auxiliary Inductor

The auxiliary inductor is a key element in the operation of this circuit, it might even be considered the most important component. As any inductor it might operate in two modes of conduction:

I) Continuous Auxiliary Inductor Conduction Mode (CACM); when there is no time interval where the current passing through it drops to zero. With higher inductance values we operate in CACM.

II) Discontinuous Auxiliary Inductor Conduction Mode (DACM), when in some time intervals the current passing through it drops to zero. With lower inductance values we operate in DACM. There is a value of inductance, which gives an operation on the boundary between these two modes.

As was mentioned before, for the proper operation of the circuit we must operate in DACM all the time, independent of the line and load conditions. The inductor should be designed for extreme conditions of low line voltage and full load.

The boundary is drawn using calculations for different input voltage ranges and switching frequencies. It is observed that maximum load and low input voltage are the extreme conditions which define where this boundary occurs.

Fig. 3.10 shows the boundary between these two modes for input voltage range Vin = 85-135 volts.

Fig. 3.11 shows the boundary between these two modes for input voltage range Vin = 176-266 volts.

Fig. 3.10 Boundary of CCM and DCM for  $V_{in} = 85-135$  volts

Fig. 3.11 Boundary of CCM and DCM for  $V_{in} = 176-266$  volts

## 3.5 Dc Link Voltage

The waveforms of the auxiliary current and voltage during a switching period are shown in Fig. 3.12.

Fig. 3.12 Current through the auxiliary inductor

The peak current of the auxiliary inductor in each period, 'n', could be expressed

$$i_{aux,n} = \frac{V_{sn}}{L_{aux}} t_{on} \tag{3.26}$$

or as:

as:

$$i_{aux,n} = \frac{V_{dc} - V_{sn}}{L_{our}} \cdot t_{off} \tag{3.27}$$

where

$$t_{on} = \frac{DT_s}{2}$$

and  $t_{off} = \frac{D'T_s}{2}$

Where, V<sub>sn</sub> is the value of line voltage at the beginning of each power transfer cycle.

$$V_{sn} = V_s \sin \left( 2\pi \cdot \frac{n}{2T_L} \right)$$

(3.28)

Using equations (3.26) - (3.27) and the energy balance between the average input and output power, the value of the auxiliary inductor could be found. The input power in each half switching cycle could be found as:

$$P_{in,n} = \frac{1}{2L_{aux}} \cdot t_{on}^{2} \cdot \left( \frac{(V_{sn})^{2}}{1 - \frac{V_{sn}}{V_{dc}}} \right)$$

(3.29)

and the overall average power is found by the summation of all these average power components over a line frequency cycle ( $T_L = 1/f_L$ ), where  $t_{on}$  - is the power cycle duration and  $T_s$  - is the switching frequency.

The output power (averaged over a line frequency cycle) could be expressed as:

$$P_o = \frac{t_{on}^2}{2.T_L.L_{aux}} \sum_{n=1}^{f_{sn}} \left( \frac{V_{sn}^2}{1 - (V_{sn}/V_{dc})} \right)$$

(3.30)

$$D = \frac{V_o}{V_{dc}} \frac{N_p}{N_s} \tag{3.31}$$

where, D - is the duty cycle, or power transfer period. The value of dc link capacitor voltage and the required duty cycle can be found by solving the equations (3.30) and (3.31) numerically.  $V_{dc}$  is a function of load, duty cycle and output current.

#### 3.6 Performance Characteristics - Ratings Of The Components

#### 3.6.1 RMS Current Through The Switches

The current passing through any of the full bridge switches is the sum of three components:

#### 1. Reflected load current

$$i_{o}' = \frac{1}{n_{s}} \left[ \frac{V_{o}}{R_{o}} + \frac{V_{dc}/n_{s} - V_{o}}{L_{o}} t - \frac{V_{dc}/n_{s} - V_{o}}{L_{o}} DT_{s} \right]$$

(3.32)

This expression is valid for continuous current mode of the output filter inductor.

#### 2. Magnetizing current

$$i_{M} = \frac{V_{dc}}{L_{M}} t - \frac{V_{dc}}{L_{M}} \frac{DT_{S}}{4}$$

(3.33)

#### 3. Auxiliary current

$$i_{aux} = \frac{V_{sn}}{L_{aux}}t\tag{3.34}$$

The expression for the switch current is:

$$i_{sw} = i_o' + i_M + i_{aux} (3.35)$$

And its RMS value over a period of  $T_S/2$  is found by integrating the expression for  $i_{switch}^2$  from 0 to  $T_S/2$ . This is the RMS current for half a switching period and the RMS switch current is found by averaging all these particular areas over the line frequency period.

$$i_{sw}(t) = \frac{1}{n_s} \left[ \frac{V_o}{R} + \frac{V_{dc}/n_s - V_o}{L_o} t - \frac{V_{dc}/n_s - V_o}{L_o} \frac{DT_s}{4} \right] + \frac{V_{dc}}{L_M} t - \frac{V_{dc}}{L_M} \frac{DT_S}{4L_M} + \frac{V_S}{L_S} t \quad (3.36)$$

The following expression is used to find the RMS value of the switch current:

$$I_{sw,rms} = \sqrt{\frac{1}{T_L} \int_{0}^{T_L} i_{sw}^2(t) dt}$$

(3.37)

This expression is valid for the case when the current waveform has an analytical-continuous expression in the line frequency period. In the given topology the switch current consists of a discrete waveform which repeats itself over switching frequency period with a difference in amplitude between each cycle. So the RMS switch current is found by using a modified formula of (3.37)

$$I_{sw,rms} = \sqrt{\frac{1}{T_L} \sum_{n=1}^{f_{sn}} \int_{0}^{DT_s} i_{sw}^{2}(t) dt}$$

(3.38)

where

$f_{sn} = \frac{2T_L}{T_S}$ , number of auxiliary current periods in a line frequency period.

$$i_{sw}^{2}(t) = \left(\frac{1}{n_{s}} \frac{V_{dc}/n_{s} - V_{o}}{L_{o}} \left[ \frac{V_{o}}{R_{o}} \frac{L_{o}}{V_{dc}/n_{s} - V_{o}} + t - \frac{dT_{s}}{4} \right] + \frac{V_{dc}}{L_{M}} \left(t - \frac{DT_{S}}{4}\right) + \frac{V_{sn}}{L_{aux}} t \right)^{2}$$

(3.39)

We know that

$$V_o = \frac{V_{dc}}{n_s} D \tag{3.40}$$

Substituting the expression for the output voltage from (3.40) in (3.41) yields

$$i_{sw}^{2}(t) = \left(\frac{1}{n_{s}} \frac{V_{dc}/(1-D)}{L_{o}} \left[ \frac{V_{o}}{R} \frac{L_{o}}{V_{dc}/n_{s}} (1-D) + t - \frac{DT_{s}}{4} \right] + \frac{V_{dc}}{L_{M}} \left(t - \frac{DT_{S}}{4}\right) + \frac{V_{sn}}{L_{aux}} t \right)^{2} (3.41)$$

And by integrating (3.41) we obtain

$$\int_{0}^{DT_{s}} i_{sw}^{2}(t)dt = \int_{0}^{DT_{s}} \left( \frac{1}{n_{s}} \frac{V_{dc}/n_{s}(1-D)}{L_{o}} \left[ \frac{V_{o}}{R} \frac{L_{o}}{V_{dc}/n_{s}(1-D)} + t - \frac{DT_{s}}{4} \right] + \frac{V_{dc}}{L_{M}} \left( t - \frac{DT_{s}}{4} \right) + \frac{V_{sn}}{L_{s}} t \right)^{2} dt$$

$$= \frac{\left[\left(\frac{1}{n_{s}} \frac{V_{dc}/(1-D)}{I_{o}} \left[\frac{V_{o}}{R_{o}} \frac{L_{o}}{\left(\frac{V_{dc}}{n_{s}}(1-D)\right)} + t - \frac{DT_{s}}{4}\right] + \frac{V_{dc}}{L_{M}} \left(t - \frac{DT_{s}}{4}\right) + \frac{V_{sn}}{L_{aux}} t\right)\right]^{3}}{3\left(\frac{V_{sn}}{L_{aux}} + \frac{V_{dc}}{L_{M}} + \frac{V_{dc}(1-D)}{n_{s}^{2}L_{o}}\right)}$$

(3.42)

Expression (3.42) is substituted in (3.38) and the result is used to plot the value of the switch RMS current versus the output load as will be shown in later parts of this thesis.

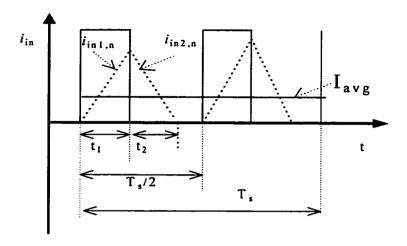

## 3.6.2 RMS Input Current

The waveform of the input current is shown on Fig. 3.13

Fig. 3.13 Input current and auxiliary voltage waveforms

The rms. value of the input current is expressed as

$$I_{im,rms} = \sqrt{\frac{1}{T_L}} \int_{0}^{T_L} i_{in}^{2}(t) dt = \sqrt{\frac{1}{T_L}} \sum_{1}^{f_{im}} \left( \int_{0}^{DT_L/2} i_{in1}^{2}(t) dt + \int_{0}^{DT_L/2} i_{in2}^{2}(t) dt \right)$$

(3.44)

The first increasing part of the input current  $i_{\text{in}\,\text{I}}$  is

$$i_{in1,n}(t) = \frac{V_{sn}}{L_{core}}t\tag{3.45}$$

and its square is

$$i_{inl,n}^{2}(t) = \frac{V_{sn}^{2}}{L_{max}^{2}}t^{2}$$

(3.46)

The corresponding area under this curve is found as

$$\int_{0}^{DT_{s}/2} dt = \int_{0}^{DT_{s}/2} \left(\frac{V_{sn}}{L_{aux}}t\right)^{2} dt = \left(\frac{V_{sn}}{L_{aux}}\right)^{2} \frac{t^{3}}{3} \Big|_{0}^{DT_{s}/2} = \left(\frac{V_{sn}}{L_{aux}}\right)^{2} \frac{\left(\frac{DT_{s}/2}{2}\right)^{3}}{3}$$

(3.47)

The second decreasing part of the input current iin2 is

$$i_{in2,n}(t) = \frac{V_{sn}}{L_{aux}} \frac{DT_S}{D'T_S} t = \frac{V_{sn}}{L_{aux}} \frac{D}{D'} t$$

(3.48)

The corresponding area under this curve is found as

$$\int_{0}^{D'T_{S}/2} i_{in2}(t)^{2} dt = \int_{0}^{D'T_{S}/2} \left( \frac{V_{sn}}{L_{aux}} \frac{D}{D'} t \right)^{2} dt = \left( \frac{V_{sn}}{L_{aux}} \frac{D}{D'} \right)^{2} \frac{t^{3}}{3} \Big|_{0}^{\Delta_{1}T_{S}/2} = \left( \frac{V_{sn}}{L_{aux}} \frac{D}{D'} \right)^{2} \frac{\left( \frac{D'T_{S}/2}{2} \right)^{3}}{3}$$

$$= \left(\frac{V_{sn}}{L_{max}}\right)^2 \left(\frac{V_{dc} - V_{sn}}{V_{sn}}\right)^2 \left(\frac{D^2 T_s}{2}\right)^3$$

(3.49)

where

$$D' = D \frac{V_{sn}}{V_{dc} - V_{sn}} \tag{3.50}$$

Using the following relationship (3.50) in (3.49) yields

$$\int_0^{D'T_{s/2}} i_{in2,n}^2(t) dt = \left(\frac{V_{sn}}{L_{aux}}\right)^2 \left(\frac{V_{dc}}{V_{dc} - V_{sn}}\right)^2 \frac{\left(\frac{DT_{s/2}}{2}\right)^3}{3}$$

(3.51)

and the expression for the overall RMS input current before filtering is obtained by substituting (3.47) and (3.51) in (3.44):

$$I_{in,rms} = \sqrt{\frac{1}{T_L}} \sum_{n=1}^{f_m} \int_{0}^{DT_S/2} i_{in,1}^2(t) dt + \int_{0}^{\Delta_1 T_S/2} i_{in2}^2 dt$$

(3.52)

Using these equations, the current RMS value is plotted in later chapters.

The expression for input current after filtering could be found by averaging the waveform of the current

$$I_{in,avg} = \frac{1}{T_{s/2}} \int_{0}^{T_{s/2}} i_{avg}(t)dt$$

$$= \frac{1}{T_{s/2}} \frac{\left(DT_{s}/2\right)^{2}}{2L_{aux}} \frac{V_{sn}}{1 - \left(V_{sn}/V_{dc}\right)}$$

(3.53)

and the RMS value of this current is found as:

$$I_{in,rms} = \sqrt{\frac{1}{T_L} \sum_{n=1}^{f_{sn}} \left( \frac{1}{T_S / 2} \frac{(DT_s / 2)^2}{2L_{aux}} \frac{V_{sn}}{1 - \frac{V_{sn}}{V_{dc}}} \right)^2}$$

(3.54)

#### 3.6.3 DC Link Capacitor Current

Based on the waveform of the current passing through the dc link capacitor, shown in Fig. 3.8, during the first period  $t_{on} = DT_s/2$  the expression for the current is:

$$i_{Cdc_{-}1n} = \frac{I_o}{n_s} + \frac{V_{dc}/n_s - V_o}{L_o n_s} t - \frac{V_{dc}/n_s - V_o}{L_o n_s} \frac{DT_S}{4}$$

(3.55)

During the second period  $t_{off} = D'T_s / 2$  the expression for the current is:

$$i_{Cdc_{2n}} = \frac{-V_{sn}}{L_{aux}} \frac{2DT_{S}}{2D'T_{S}} t + \frac{-V_{sn}}{L_{aux}} \frac{DT_{s}}{2} = \left(-\frac{V_{dc} - V_{sn}}{L_{aux}} t + \frac{V_{sn}}{L_{aux}} \frac{DT_{s}}{2}\right)$$

(3.56)

The RMS current is defined by the following formula:

$$I_{Cdc,ms} = \sqrt{\frac{1}{T_L} \int_{0}^{T_L} i_{Cdc_{-n}}^2 dt}$$

(3.57)

where,

$$i_{Cdc} {}_{n}^{2}(t) = i_{Cdc} {}_{1n}^{2}(t) + i_{Cdc} {}_{2n}^{2}(t)$$

(3.58)

First integrals of both dc capacitor currents in expressions (3.55) and (3.56) are found as:

$$\int_{0}^{DT_{s}/2} i_{Cdc_{-} \ln^{2}} dt = \int_{0}^{DT_{s}/2} \left( \frac{I_{o}}{n_{s}} + \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} t - \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} \frac{DT_{s}}{4} \right) dt$$

$$= \frac{1}{3 \left( \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} \right)} \left( \frac{I_{o}}{n_{s}} + \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} t - \frac{V_{Cdc}/n_{s} - V_{o}}{L_{o}n_{s}} \frac{DT_{s}}{4} \right)^{3} \Big|_{0}^{DT_{s}/2}$$

$$= \frac{1}{3 \left( \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} \right)} \left\{ \left( \frac{I_{o}}{n_{s}} + \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} \frac{DT_{s}}{4} \right)^{3} - \left( \frac{I_{o}}{n_{s}} - \frac{V_{dc}/n_{s} - V_{o}}{L_{o}n_{s}} \frac{DT_{s}}{4} \right)^{3} \right\}$$

$$(3.59)$$

and the area for the second current component is:

$$\int_{0}^{DT_{s}/2} i_{Cdc_{2}n}^{2} dt = \int_{0}^{DT_{s}/2} \left( -\frac{V_{dc} - V_{sn}}{L_{aux}} t + \frac{V_{sn}}{L_{aux}} \frac{DT_{S}}{2} \right)^{2} dt$$

$$= \frac{1}{3 \left( \frac{V_{sn} - V_{dc}}{L_{aux}} \right)} \left( -\frac{V_{dc} - V_{sn}}{L_{aux}} t + \frac{V_{sn}}{L_{aux}} \frac{DT_{S}}{2} \right)^{3} \Big|_{0}^{DT_{s}/2}$$

$$= \frac{1}{3 \left( \frac{V_{sn} - V_{dc}}{L} \right)} \left( \frac{V_{sn}}{L_{aux}} \frac{DT_{S}}{2} \right)^{3}$$

(3.60)

where

$$D' = D \frac{V_{dc}}{V_{dc} - V_{sn}}$$

(3.61)

The RMS current through the dc link capacitor is:

$$I_{Cdc,rms} = \sqrt{\frac{1}{T_L} \sum_{n=1}^{L_m} \int_{0}^{DT_s/2} i_{Cdc_{-1}n}^2(t)dt + \int_{0}^{DT_s/2} i_{Cdc_{-2}n}(t)^2 dt}$$

(3.62)

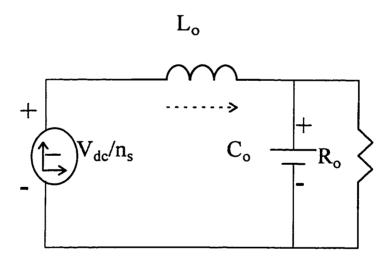

# 3.6.4 Output Filter Capacitor RMS Current

The RMS current through the output filter capacitor is a function of the allowed current ripple which is in turn a function of the inductor value. Fig 3.14 shows the theoretical waveforms of the current through the output filter components.

Fig. 3.14 Current through the output filter components

During the on time interval  $t = [0, DT_S/2]$  the expression for the output capacitor current is:

$$i_{C_{o_{-1}}} = \left(\frac{\frac{V_{dc}}{n_{s}} - V_{o}}{L_{o}} t - \frac{\frac{V_{dc}}{n_{s}} - V_{o}}{L_{o}} \frac{DT_{S}}{4}\right)$$

(3.63)

And the area under the square value of this current component is

$$\int_{0}^{DT_{c}/4} i_{Co_{-1}} = \int_{0}^{DT_{c}/4} \left( \frac{V_{dc}/n_{s} - V_{o}}{L_{o}} t - \frac{V_{dc}/n_{s} - V_{o}}{L_{o}} \frac{DT_{S}}{4} \right)^{2} dt$$

$$= \frac{1}{3} \left( \frac{\binom{V_{dc}}{n_{s}} - V_{o}}{L_{o}} t - \frac{\binom{V_{dc}}{n_{s}} - V_{o}}{L_{o}} \frac{DT_{S}}{4} \right)^{3} \cdot \frac{1}{\binom{V_{dc}}{n_{s}} - V_{o}}}{\frac{L_{o}}{L_{o}}} \right)^{3}$$

$$=\frac{2}{3}\left(\frac{\left(\frac{V_{dc}}{n_s}-V_o\right)}{L_o}\frac{DT_S}{4}\right)^3\frac{L_o}{\left(\frac{V_{dc}}{n_s}-V\right)_o}$$

(3.64)

During the remainder of the half switching period,  $t = [0, (1-D)T_S/4]$ , the expression for the output capacitor current is:

$$i_{C_{o_{-}2}} = \left(\frac{-V_o}{L_o}t + \frac{V_o(1-D)T_S}{L_o}\right)$$

(3.65)

and the area under the square value of this current component is

$$= \int_{0}^{(1-D)T_S/4} \left( \frac{-V_o}{L_o} t + \frac{V_o}{L_o} \frac{DT_S}{4} \right)^2 dt$$

$$= \frac{1}{3} \left( \frac{-V_o}{L_o} t + \frac{V_o}{L_o} \frac{(1-D)T_s}{4} \right)^3 \frac{1}{\frac{-V_o}{L_o}} \bigg|_{0}^{(1-D)T_s/4}$$

$$=\frac{1}{3} \left( \frac{-L_o}{V_o} \right) \left( \frac{V_o (1-D)T_s}{L_o 4} \right)^3$$

(3.66)

and the overall RMS current of the output filter capacitor is

$$I_{co,rms} = \sqrt{\frac{1}{T_L}} \left[ \int_{0}^{DT_L/4} i_{Co_{-1}}(t)dt + \int_{0}^{(1-D)T_L/4} i_{Co_{-2}}(t)dt \right]$$

(3.67)

#### 3.6.5 Output Filter Inductor And Current Ripple

The output voltage is expressed in terms of the dc link voltage and the duty cycle

$$V_o = \frac{V_{dc}}{n_c} D \tag{3.68}$$

The current ripple of the output filter inductor was shown in Fig. 3.5 and equals

$$\Delta i_{lo} = \frac{V_{dc} / n_s - V_o}{L_o} \frac{DT_S}{2} = \frac{\frac{V_{dc}}{n_s} - \frac{V_{dc}}{n_s} D}{L_o} \frac{DT_S}{2}$$

$$= \frac{V_{dc} / n_s (1 - D)}{L} \frac{DT_S}{2}$$

(3.69)

Also,

$$\Delta i_{L_o} = \frac{V_o(1-D)}{L_o} \frac{DT_S}{2}$$

(3.70)

and the ripple factor is defined as:

$$K_{ripple} = \frac{\Delta i_{L_o}}{I_o} = \frac{V_o(1-D)}{I_o L_o} \frac{T_S}{2} = \frac{V_o^2(1-D)}{P_o L_o} \frac{T_S}{2}$$

(3.71)

The value of the output filter inductor is found for a given ripple factor by solving (3.71)

$$L_o = \frac{V_o^2 (1 - D)}{P_o K_{rimple}} \frac{T_S}{2}$$

(3.72)

#### 3.6.6 Output Voltage Ripple