#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## A Bandwidth Efficient Turbo Coding Scheme for VDSL Systems

Sreekanth Marti

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

April 2003

© Sreekanth Marti, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our lile Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-77974-2

#### ABSTRACT

## A Bandwidth Efficient Turbo Coding Scheme for VDSL Systems

#### Sreekanth Marti

The two important issues presently under consideration by ANSI and ETSI for very high bit-rate digital subscriber lines (VDSL) are the last-mile problem and the home local area network (home-LAN) interference problem. The first issue concerns the maximum distance for which a VDSL system can operate reliably for a given data rate. The second issue is the interference due to home-LAN services associated with the twisted pair lines. The drawback of the existing FEC scheme (a 4D Wei-RS scheme) for the VDSL systems is that further improvement is not possible to achieve without a substantial increase in complexity and power penalty. Also, the VDSL systems employing the 4D Wei-RS scheme operates far below the channel capacity. On the other hand, several techniques have been proposed to solve the home-LAN interference problem using iterative-decoding techniques. However, these techniques are complex to implement. In order to provide solutions to these problems and to ensure a reliable transmission of data over longer loops while providing the end user with maximal bit rate, a good FEC scheme with a high coding gain is required.

In this thesis, the last-mile and home-LAN interference problems of VDSL systems are addressed using turbo codes. With regard to the last-mile problem, a bandwidth efficient turbo coding scheme is proposed in which, turbo codes are combined with bandwidth efficient modulation and the soft information is exchanged between

the decoder and demodulator in an iterative manner. The main objective of the proposed scheme is to provide a higher coding gain than that provided by the 4D Wei-RS scheme to result in an improved performance of the VDSL modems in terms of bit rate, loop length and transmitting power. The scheme is investigated for various values of transmitting power, signal frequencies and numbers of crosstalkers for a targeted BER of 10<sup>-5</sup>. The effects of various code parameters on the performance of VDSL modems are explored. In order to reduce the latency at the receiver end, a pipelined decoding scheme is proposed. Simulation results are presented and compared with that of the 4D Wei-RS scheme. The results show that the choice of turbo codes not only provides a significant coding gain over the standard FEC scheme but also efficiently maximizes the loop length and bit rate at a very low transmitting power in the presence of dominant far-end crosstalk (FEXT). In order to compare the hardware complexity, the proposed and 4D Wei-RS schemes are synthesized using SYNOPSYS with the target technology of Xillinx 4010-3. The Xilinx FPGA statistics of the proposed scheme is compared with that of the 4DWei-RS scheme.

To mitigate the effect of home-LAN interference, an iterative soft interference cancellation and decoding technique is proposed in which, the VDSL and home-LAN signals are jointly detected using a soft interference canceller and a soft-in soft-out demodulator combined with a set of turbo decoders. A symbol estimation algorithm based on the soft information of the coded data is developed to estimate the transmitted symbols. Simulations are carried out to evaluate the BER performance of the proposed technique. The data rates provided by the VDSL systems employing the proposed technique are evaluated. The results show that by employing the proposed technique in VDSL systems, the home-LAN interference can be successfully minimized thereby providing higher data rates and maximizing the loop length.

Dedicated to my uncle, aunty, and parents

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor Dr. M. O. Ahmad for providing the guidance and support that made this work possible. I am grateful for his extremely careful and thorough review of my thesis, and for his inspiration throughout the course of this work. I feel privileged for having the opportunity to work with him. I would also like to thank all my teachers who were of great support throughout my academic life.

I am heartily grateful to my parents, elder uncle and aunt for their love, support and sacrifices that they made in bringing me up. I would like to express my deepest gratitude for my grandmother, brother, aunts, uncles, cousins and my fiance Deepa who supported me with their love and understanding.

Finally, I would like to thank all my friends for their help and advice.

## TABLE OF CONTENTS

| LI | ST C | F TAB  | ELES                                                | N   |

|----|------|--------|-----------------------------------------------------|-----|

| LI | ST C | F FIG  | URES                                                | X   |

| LI | ST O | F ABB  | REVIATIONS AND SYMBOLS                              | xiv |

| 1  | Ger  | ieral  |                                                     | 1   |

|    | 1.1  | Basic  | Concepts of VDSL                                    | 2   |

|    |      | 1.1.1  | VDSL System Architecture                            | 3   |

|    |      | 1.1.2  | VDSL System Requirements                            | 5   |

|    | 1.2  | VDSL   | Issues                                              | 7   |

|    | 1.3  | Scope  | and Organization of the Thesis                      | 9   |

| 2  | VD   | SL Lin | ne Impairments and Impact of Coding in VDSL Systems | 12  |

|    | 2.1  | Introd | luction                                             | 12  |

|    | 2.2  | VDSL   | Channel Model                                       | 13  |

|    | 2.3  | VDSL   | Line Impairments                                    | 15  |

|    |      | 2.3.1  | Background Noise                                    | 16  |

|    |      | 2.3.2  | Crosstalk Noise                                     | 16  |

|    |      | 2.3.3  | Impulse Noise                                       | 19  |

|    |      | 2.3.4  | Radio Frequency Interference                        | 20  |

|    | 2.4  | Impac  | t of Coding                                         | 20  |

|    | 2.5  | Overv  | iew of the Existing Coding Scheme                   | 22  |

|    |      | 2.5.1  | Reed-Solomon Coding                                 | 25  |

|    |      | 2.5.2  | 16 State 4D Wei Coder                               | 26  |

|    | 2.6  | VDSL   | Line Codes                                          | 30  |

|    |      | 2.6.1  | CAP/QAM                                             | 30  |

|    |      | 2.6.2  | DMT                                                 | 31  |

|    |      | 2.6.3  | Comparison of QAM and DMT                           | 32  |

|   | 2.7  | Concl  | usion                                                  | 33 |

|---|------|--------|--------------------------------------------------------|----|

| 3 | A E  | Bandwi | dth Efficient Turbo Coding Scheme for VDSL             | 35 |

|   | 3.1  | Introd | luction                                                | 35 |

|   | 3.2  | Basic  | Concepts of Turbo Codes                                | 36 |

|   |      | 3.2.1  | Turbo Encoder                                          | 36 |

|   |      | 3.2.2  | Turbo Decoder                                          | 38 |

|   | 3.3  | Bit In | terleaved Turbo Coded Modulation                       | 39 |

|   |      | 3.3.1  | Demodulation and Bit LLR Computation                   | 42 |

|   |      | 3.3.2  | Binary Turbo Decoder                                   | 44 |

|   |      | 3.3.3  | Design Criteria for Constituent Codes                  | 48 |

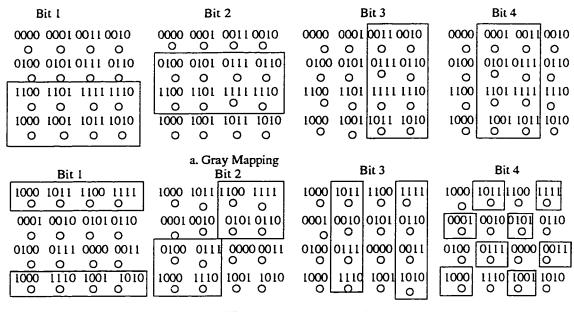

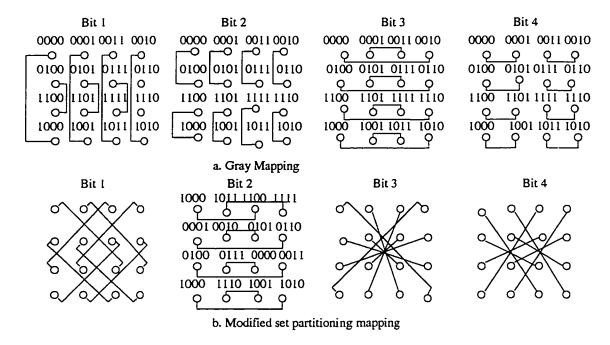

|   |      | 3.3.4  | Signal Mapping                                         | 51 |

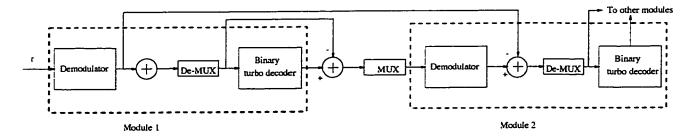

|   | 3.4  | Pipe I | Lined Decoding Scheme                                  | 53 |

|   | 3.5  | Comp   | lexity Analysis                                        | 54 |

|   |      | 3.5.1  | Arithmetic Complexity                                  | 55 |

|   |      | 3.5.2  | Hardware Complexity                                    | 55 |

|   | 3.6  | Simula | ation Results                                          | 60 |

|   |      | 3.6.1  | Performance of Bit Interleaved Coded Modulation Scheme | 60 |

|   |      | 3.6.2  | Performance Comparison between different Codes         | 66 |

|   | 3.7  | Conclu | ısion                                                  | 67 |

| 1 | Peri | formar | ace Evaluation of VDSL Employing BICM Scheme           | 69 |

|   | 4.1  | Introd | uction                                                 | 69 |

|   | 4.2  | Effect | of Transmitting Frequency                              | 70 |

|   | 4.3  |        | of Transmitting Power                                  |    |

|   | 4.4  |        | of Numbers of Crosstalkers                             | 75 |

|   | 4.5  |        | able Loop Length                                       | 76 |

|   | 46   |        | ision                                                  |    |

| 5 | An    | Iterative Soft Interference Cancellation and Decoding technique |     |

|---|-------|-----------------------------------------------------------------|-----|

|   | to I  | Vitigate the Effect of Home-LAN on VDSL                         | 84  |

|   | 5.1   | Introduction                                                    | 84  |

|   | 5.2   | System Model                                                    | 86  |

|   | 5.3   | Iterative Turbo Multiuser Receiver Structure                    | 88  |

|   | 5.4   | Soft Interference Cancellation via Multiuser Detection          | 90  |

|   | 5.5   | Simulation Results                                              | 93  |

|   | 5.6   | Conclusion                                                      | 96  |

| 6 | Cor   | iclusion and Future Work                                        | 98  |

|   | 6.1   | Contributions and Concluding Remarks                            | 98  |

|   | 6.2   | Scope for Further Investigation                                 | 101 |

| A | ppen  | $\mathbf{dix}$                                                  | 102 |

| R | efere | nces [                                                          | 107 |

## LIST OF TABLES

| 2.1 | Parameters for a simplified cable model                                      | 13 |

|-----|------------------------------------------------------------------------------|----|

| 3.1 | Best rate 1/3 rate turbo codes                                               | 51 |

| 3.2 | Decoder complexity.                                                          | 55 |

| 3.3 | Number of clock cycles required for metric computation                       | 58 |

| 3.4 | Range of parameters                                                          | 58 |

| 3.5 | Maximum storage requirements                                                 | 58 |

| 3.6 | Xilinx FPGA statistics                                                       | 59 |

| 3.7 | Performance comparison between the codes for a targeted BER of               |    |

|     | $10^{-5}$ for various code memories                                          | 62 |

| 3.8 | Performance comparison between the codes for a targeted BER of               |    |

|     | $10^{-5}$ for various interleaver sizes                                      | 62 |

| 3.9 | Required SNR for various codes for a targeted BER of 10 <sup>-5</sup>        | 67 |

| 4.1 | Comparison of data rates for various codes at $f=14~\mathrm{MHz}$ and Trans- |    |

|     | mitting Power=10 dBm                                                         | 71 |

| 4.2 | Comprison of data rates for various codes for number of cross-talkers=40.    | 78 |

| 4.3 | Realizable loop lengths with various codes for a data rate of 40 Mbps.       | 80 |

## LIST OF FIGURES

| 1.1  | Block diagram of a typical DSL transceiver                           | 4  |

|------|----------------------------------------------------------------------|----|

| 1.2  | FTTE architecture [3]                                                | ۷  |

| 1.3  | FTTC architecture [3]                                                | 4  |

| 1.4  | VDSL spectrum                                                        | ۶  |

| 2.1  | Attenuation as a function of frequency of two 26 AWG (0.4 mm) lines  |    |

|      | and two 24 AWG (0.5 mm) lines                                        | 14 |

| 2.2  | Illustration of near-end crosstalk (NEXT)                            | 17 |

| 2.3  | Next coupling with 6 dB noise margin                                 | 18 |

| 2.4  | Illustration of far-end crosstalk                                    | 19 |

| 2.5  | FEXT coupling loss with 6 dB noise margin for $N=49$                 | 19 |

| 2.6  | Spectral efficiency as a function of loop length                     | 21 |

| 2.7  | Signal-to-self-FEXT plus white noise ratio for 24-gauge twisted-pair |    |

|      | loop                                                                 | 23 |

| 2.8  | Signal-to-self-FEXT plus white noise ratio for 24-gauge twisted-pair |    |

|      | loop as a function of loop length.                                   | 24 |

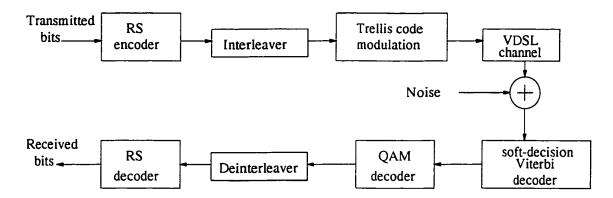

| 2.9  | 4D Wei-RS coding scheme                                              | 24 |

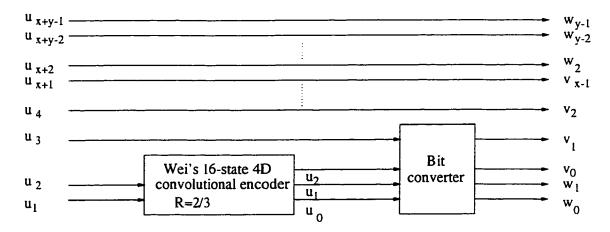

| 2.10 | Wei's 4D 16 State encoder                                            | 27 |

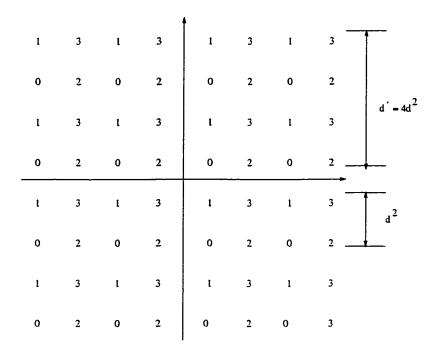

| 2.11 | 2-dimensional subsets for Wei's code                                 | 28 |

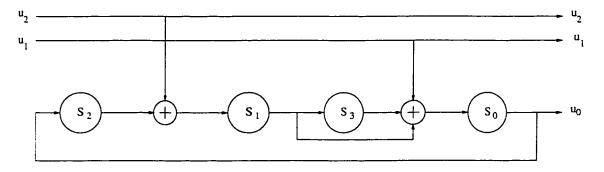

| 2.12 | Wei's 16-state 4D convolutional encoder                              | 28 |

| 2.13 | Decoding Wei's code                                                  | 29 |

| 2.14 | BER Performance of 4D Wei-RS scheme                                  | 30 |

| 2.15 | QAM transmitter block diagram                                        | 31 |

| 2.16 | DMT Transmitter/Receiver pair Block Diagram                          | 32 |

| 3.1  | Turbo encoder.                                                       | 37 |

| 3.2  | Turbo decoder.                                                               | 38 |

|------|------------------------------------------------------------------------------|----|

| 3.3  | BICM encoder                                                                 | 41 |

| 3.4  | VDSL crosstalk channel model                                                 | 41 |

| 3.5  | BICM decoder                                                                 | 41 |

| 3.6  | Subset partitions of 16 QAM for two mapping schemes                          | 52 |

| 3.7  | Signal constellation after the feedback                                      | 53 |

| 3.8  | Pipe-lined decoding scheme                                                   | 54 |

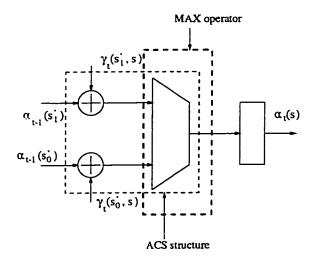

| 3.9  | Architecture of ACS unit.                                                    | 57 |

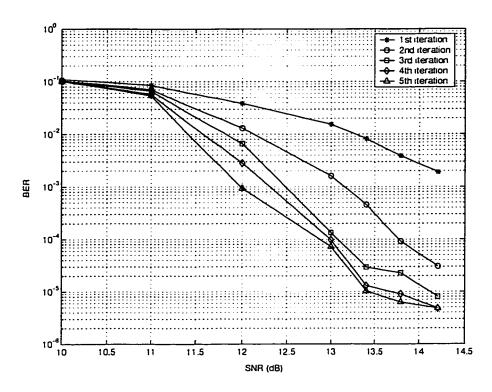

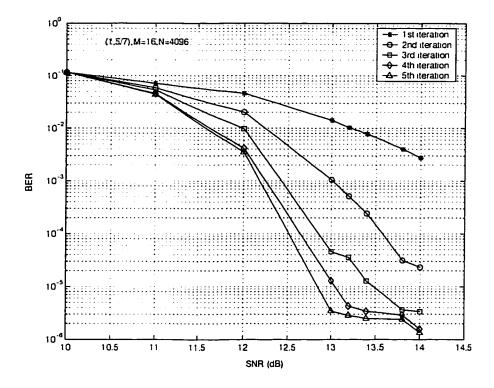

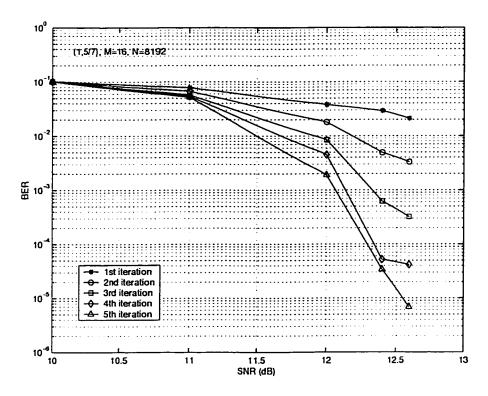

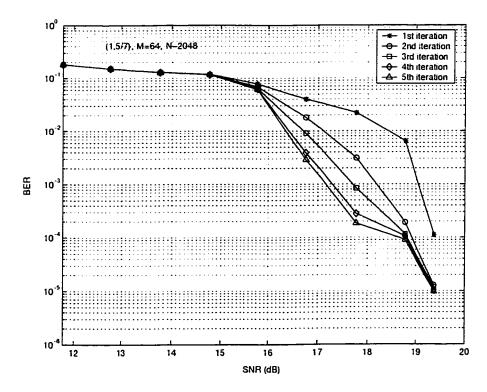

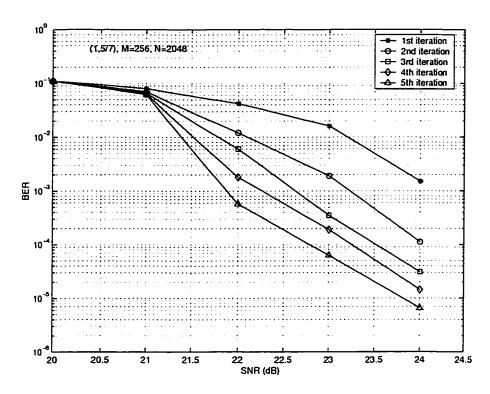

| 3.10 | Performance of BICM with encoder generator (5,7), $v=2.\ldots$               | 63 |

| 3.11 | Performance of BICM with encoder generator (17,15), $v=3.\ldots$             | 63 |

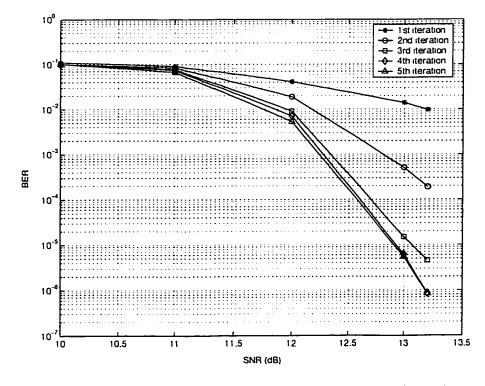

| 3.12 | Performance of BICM with encoder generator (27,31), $v=4.\ldots$             | 64 |

| 3.13 | Performance of BICM with encoder generator (7,5) , $N=4096$                  | 64 |

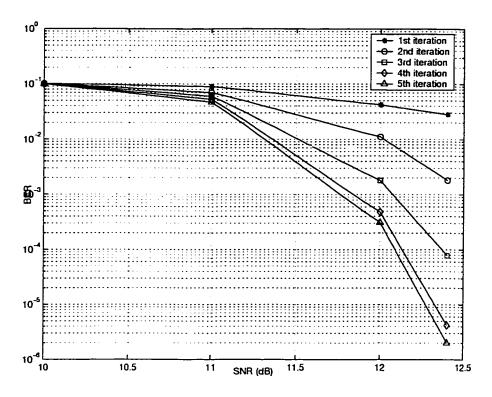

| 3.14 | Performance of BICM with encoder generator (7,5) , N=8192                    | 65 |

| 3.15 | Performance of BICM with encoder generator (7,5) , M=64                      | 65 |

| 3.16 | Performance of BICM with encoder generator (7,5) , $M=256$                   | 66 |

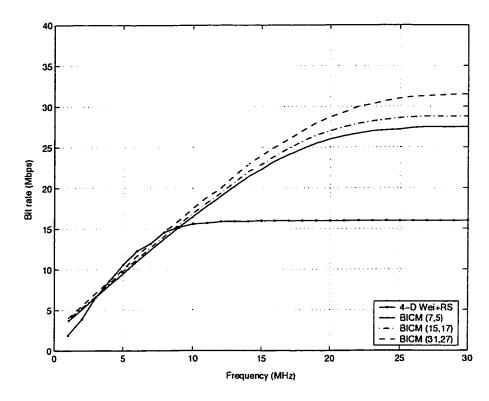

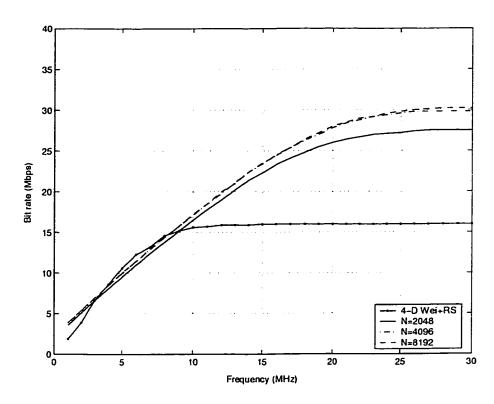

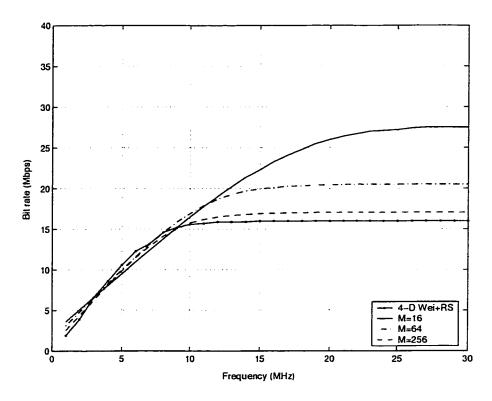

| 4.1  | Effect of Frequency as a function of code memory for BICM                    | 72 |

| 4.2  | Effect of Frequency as a function of interleaver length for BICM             | 73 |

| 4.3  | Effect of Frequency as a function of modulation for BICM                     | 74 |

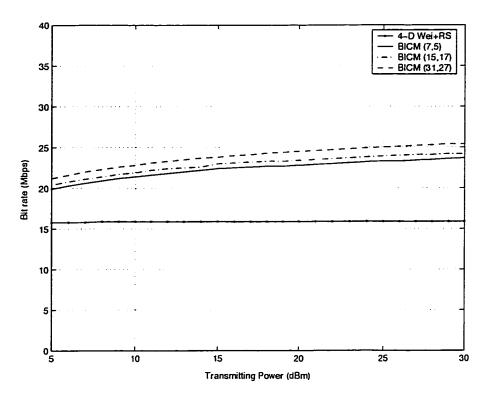

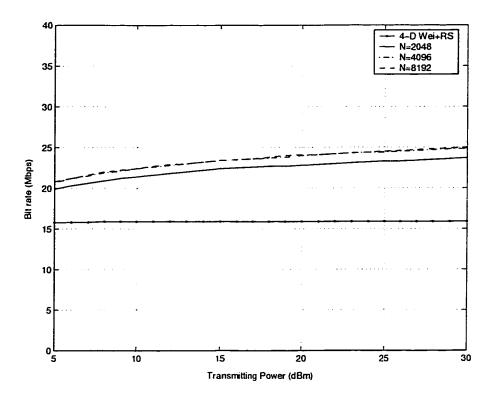

| 4.4  | Effect of Transmitting Power for various code memories for BICM              | 75 |

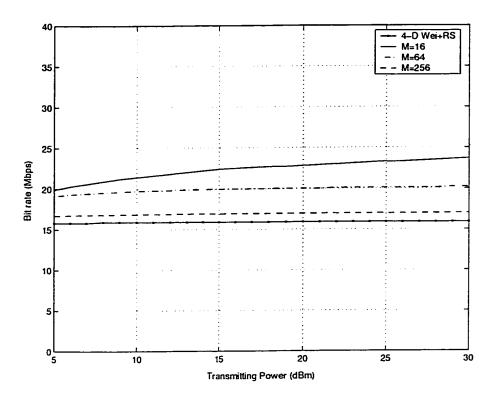

| 4.5  | Effect of Transmitting Power for various interleaver lengths for BICM.       | 76 |

| 4.6  | Effect of Transmitting Power for various modulation levels for BICM.         | 77 |

| 4.7  | Comparison of power for various codes at $f=14~\mathrm{MHz}$ for a data rate |    |

|      | of 22 Mbps                                                                   | 77 |

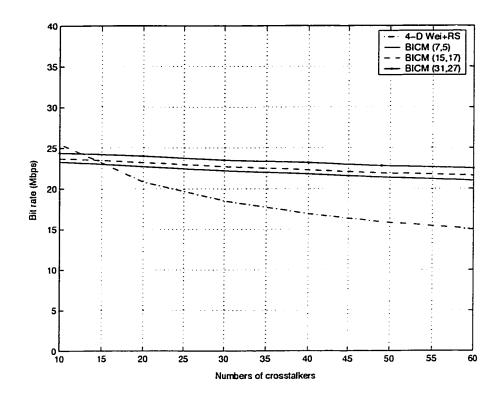

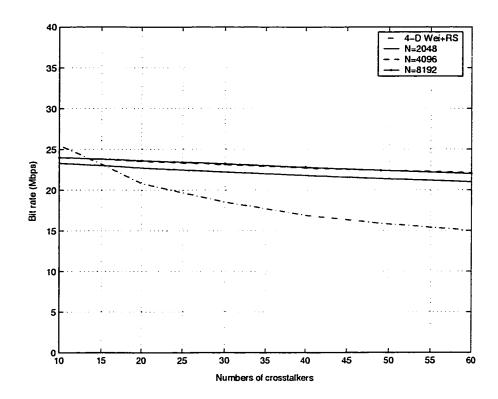

| 4.8  | Effect of numbers of cross talkers for various code memories                 | 78 |

| 4.9  | Effect of numbers of cross-talkers for various interleaver sizes             | 79 |

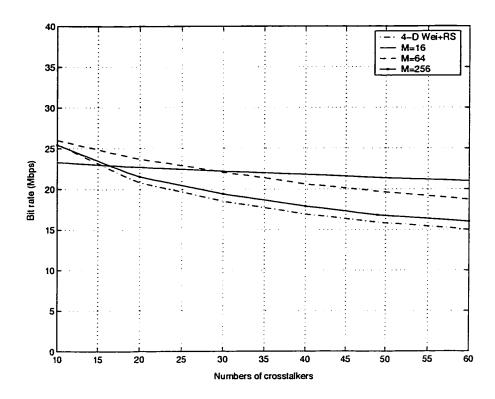

| 4.10 | Effect of numbers of cross-talkers for various levels of modulation          | 80 |

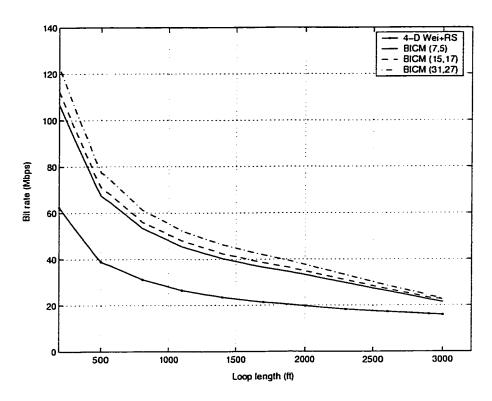

| 4.11 | Bit rate as a function of loop length for various code memories              | 81 |

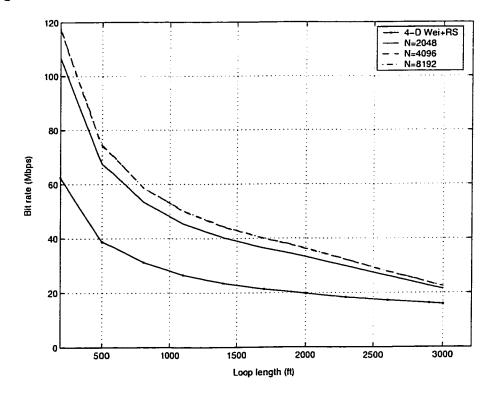

| 4.12 | Bit rate as a function of loop length for various interleaver sizes          | 81 |

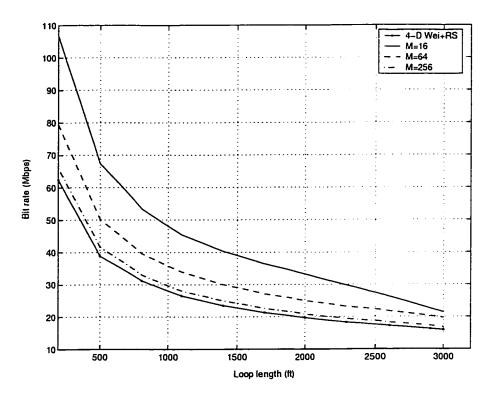

| 4.13 | Bit rate as a function of loop length for various modulation levels | 82 |

|------|---------------------------------------------------------------------|----|

| 5.1  | Example for soft cancellation                                       | 85 |

| 5.2  | Crosstalk system model [12]                                         | 87 |

| 5.3  | Interference model                                                  | 88 |

| 5.4  | Turbo iterative multiuser receiver with SIC                         | 90 |

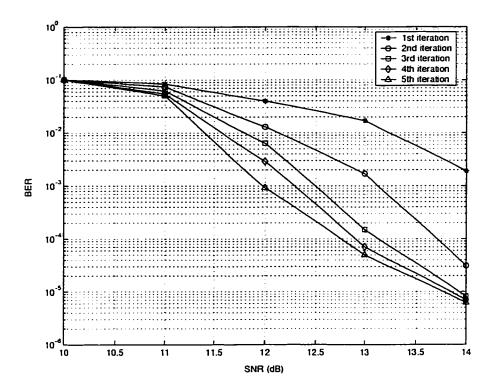

| 5.5  | BER performance of the iterative decoder                            | 94 |

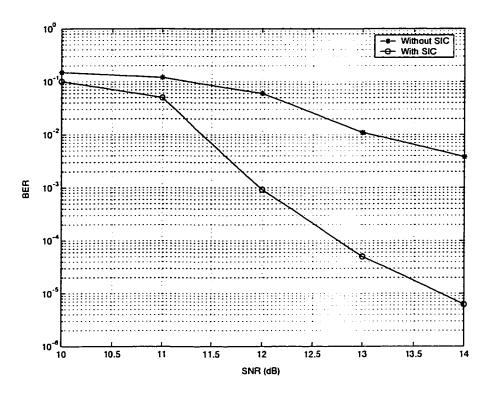

| 5.6  | Performance comparison of the proposed receiver with and without    |    |

|      | SIC                                                                 | 95 |

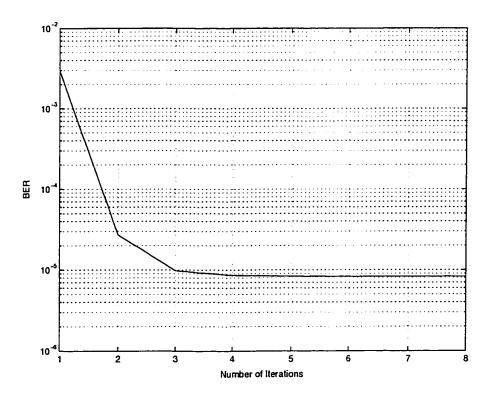

| 5.7  | Convergence curve for the soft interference cancellation technique  | 95 |

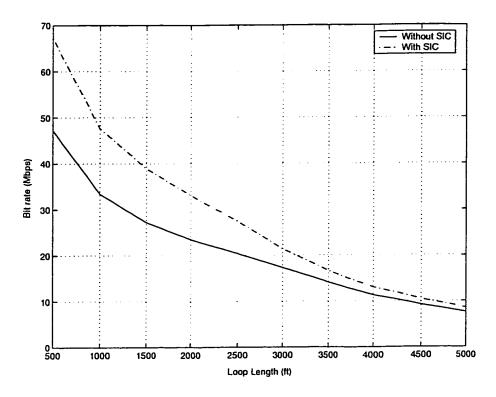

| 5.8  | Achievable data rates with and without SIC.                         | 96 |

## LIST OF ABBREVIATIONS

ACS Add Compare Select

ADC Analog To Digital Converter

ADSL Asymmetrical Digital Subscriber Lines

ATM Asynchronous Transfer Mode

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BER Bit Error Rate

BICM Bit Interleaved Coded Modulation

CC Code Complexity

CLB Control Logic Block

CO Central Office

DAC Digital To Analog Converter

De-MUX Demultiplexer

DFT Discrete Fourier Transform

DMT Discrete Multi-tone Modulation

DSL Digital Subscriber Line

FDM Frequency Division Multiplexing

FEC Forward Error Correction

FEQ Frequency Domain Equalizer

FEXT Far End Crosstalk

FPGA Field Programmable Gate Array

FTTC Fiber To The Curb

FTTE Fiber To The Exchange

HDSL High Bit Rate Digital Subscriber Lines

HDTV High Definition Television

home-LAN Home Local Area Network

IDFT Inverse Discrete Fourier Transform

IOB Input Output Buffer

ISDN Integrate Digital Services Network

ISI Inter Symbol Interference

Lex Local Exchange

LLR Log Likelihood Ratio

MAI Multiple Access Interference

MAP Maximum A Posteriori

MSP Modified Set Partitioning Mapping

MUX Multiplexer

NEXT Near End Crosstalk

ONU Optical Network Unit

POTS Plain Old Telephone Set

PSD Power Spectral Density

PSTN Public Switched Telephone Network

QAM Quadrature Amplitude Modulation

RF Radio Frequency

RFI Radio Frequency Interface

RS Reed Solomon

RSC Recursive Systematic Convolution

SDH Synchronous Digital Hierarchy

SHDSL Single pair High Bit Rate Digital Subscriber Lines

SIC Soft Interference Canceller

SISO Soft-in Soft-out

SNR Signal To Noise Ratio

SONET Synchronous Optical Network

SOVA Soft Output Viterbi Algorithm

TCM Trellis Coded Modulation

TDM Time Division Multiplexing

VDSL Very High Bit Rate Digital Subscriber Lines

### LIST OF SYMBOLS

c Coded bits

d Length of the twisted pair cable

$d_{free,eff}$  Effective free distance of code word

f Frequency of operation

$f_i$  Crosstalk coupling function

$g_0(D)$  Feedback polynomial

$g_I(D)$  Feedforward polynomial

h VDSL channel gain

$k_1, k_2$  Cable parameters

p(r|x) Probability density function

r Received noisy symbol

$S_t$  State of the encoder

v Code memory

x Transmitted symbols

z Weight of the code sequence

B Bandwidth of noise

$B_{free,eff}$  Error coefficient related to the code effective free distance

C Channel capacity of twisted pair loop

E Statistical expectation operator

G(D) Generator matrix

H(f) Twisted pair channel transfer function

M Level of modulation

K Number of interferers

N<sub>0</sub> Additive white Gaussian noise

$N_F(f)$  FEXT coupling loss

$N_N(f)$  NEXT coupling loss

P Signal power

*Pr(b)* Probability of symbol

Q(f) Transmit power spectrum density

R Receiver input impedance

S(f) Received signal power spectrum density

State of the Trellis

v Average voltage of noise

W White noise power spectral density

$\alpha_t(s',s)$  Term associated with forward recursion

$\beta_t(s',s)$  Term associated with backward recursion

$\gamma_i(s,s)$  State transition probability

$\sigma^2$  Total power of white noise

$\Lambda(c_i)$  Log-likelihood ratio

$\lambda(c_i)$  Soft metric corresponding to a bit

$\chi$  Signal space of symbols

Decision

## Chapter 1

## General

There exist many possible solutions to the problems of overloading the *public switched* telephone network (PSTN) with packetized data and broadband services. Some involve building entirely new systems based on wireless and satellite networks. But, a more realistic and cost-effective solution would be to maximize the reuse of existing analog local loops, or to include provision for providing some backward compatibility with the existing voice telephony equipment of analog hand set.

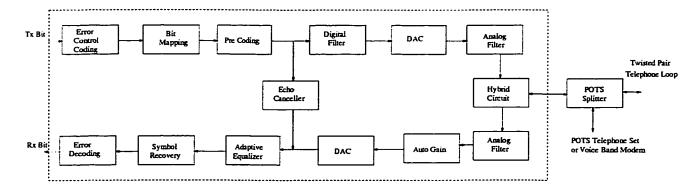

Only copper-based solutions satisfy these criteria. Digital subscriber line (DSL) is a copper-based solution which was created to foster a total digitization of the PSTN end-to-end, from the user device to user device. Also, the drawbacks of the voice-band modem can be overcome with the DSL technology [1]-[4]. Through a process of bypassing the plain old telephone set (POTS) interface at a local central office (CO), a DSL can utilize the full potential of a copper telephone subscriber loop to deliver a transmission throughput of up to a few hundred times that of a voice-band modem. Figure 1.1 shows the general structure of a DSL transceiver [5]. The transceiver set consists of an analog part and a digital part. The analog part consists of analog transmit and receive filters, a digital to analog converter (DAC), an automatic gain device, and an analog to digital converter (ADC). The digital part has three major functions: modulation/demodulation, coding/decoding, and

Figure 1.1: Block diagram of a typical DSL transceiver.

bit packing/unpacking.

Integrated services digital network (ISDN) was the first DSL service. New DSL technologies which are more interesting and promising are commonly listed as xDSL, where x represents a number or letter designation. The xDSL technologies in the chronological order can be listed as digital subscriber lines, high bit rate digital subscriber lines (HDSL/HDSL2), asymmetrical digital subscriber lines (ADSL), single pair high bit rate digital subscriber lines (SHDSL), and very high bit rate digital subscriber lines (VDSL). The latest member of the xDSL family, the VDSL is capable of providing a data rate of 13 Mbps to 52 Mbps upstream, and 1.5 Mbps to 6 Mbps downstream depending on the actual loop length. The applications supported by VDSL include all that ADSL was intended for, plus high definition TV (HDTV) digital television services.

## 1.1 Basic Concepts of VDSL

VDSL is the latest transmission technology for providing a high speed digital service on the twisted pair phone lines with a range of speeds depending on the actual line length [3]. The basic intention of the VDSL technology is to create a serviceindependent transmission platform at a much higher transmission throughput than that provided by the ADSL technology. Therefore VDSL can be considered as a high speed version of ADSL. The potential of a higher transmission throughput can be achieved by expanding the signal bandwidth to the region of 10 to 30 MHz. At such a high frequency, a usable channel can be realized only on short twisted-pair telephone loops. Because of this short range, it is no longer possible to provide the service simply from the central office. Hybrid structures are required to provide the VDSL service to the customers living in direct proximity of a central office.

To operate successfully, the VDSL equipment should overcome the line attenuation, crosstalk, radio-frequency (RF) ingress and other interferences. Of particular importance is the operation on the existing unshielded twisted-pair lines. VDSL modems must also sustain specified data rates over specified distances, suppress RF emissions, and must be compatible with the frequency spectra of other services that may be present in the same cable bundle such as ADSL, ISDN, and HDSL. The high throughput VDSL is easier to be made compatible with synchronous optical network (SONET) and asynchronous transfer mode (ATM) based services. VDSL can also be used to interconnect business customers within a concentrated area through leased telephone lines for high-speed intranet use.

## 1.1.1 VDSL System Architecture

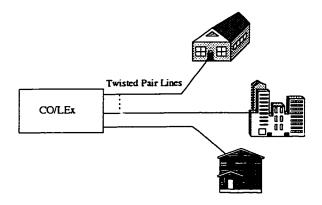

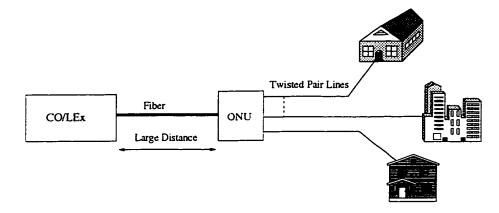

For a public telephone networks, there are two architectures in general [6]. In densely populated areas, many customers are within a few kilo feet of the CO or local exchange (LEx). In such cases, VDSL can be deployed directly from the CO or LEx. This configuration is known as fiber-to-the-exchange (FTTE) and is shown in Figure 1.2. When fiber extends deeper into the network, VDSL can be deployed from the optical network unit (ONU) in a configuration known as fiber-to-the-cabinet (FTTC). The FTTC architecture is shown in Figure 1.3. The transmission directions from the CO, LEx or ONU to the customer premise is called downstream. The direction from the customer to the CO, LEx or ONU is called upstream. In this thesis, we concentrate on the FTTC architecture as it is most commonly employed.

Figure 1.2: FTTE architecture [3].

Figure 1.3: FTTC architecture [3].

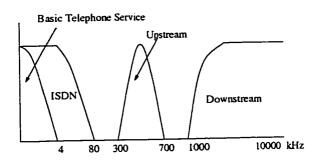

The allowable frequency band for VDSL signals start from 300 KHz to 30 MHz as shown in Figure 1.4. The first limit is for long range systems and the second limit is for short range systems. The VDSL channel is separated from the bands used for narrow band services like POTS and ISDN basic rate access (ISDN-BA), thus enabling the service providers to overlay VDSL on the existing services. The ADSL frequency band, however, overlaps with the VDSL signals. Hence, in some circumstances, it may be prudent to place the start of the VDSL band above 1.1 MHz. Normal practice is to locate the downstream channel above the upstream one.

Figure 1.4: VDSL spectrum.

## 1.1.2 VDSL System Requirements

The standards ANSI T1E1.4 and ETSI TM6 have established consistent sets of VDSL system requirements to find a common VDSL solution [7]. In the following paragraphs, these requirements are briefly described.

## a) Data Rates and Ratios

VDSL should consider both symmetric and asymmetric transmissions between the CO and the customer. The downstream speed range from about 13 Mbps to 55 Mbps, depending on the distance. The upstream data rate start at 1.5 Mbps and end at about 26 Mbps. Downstream data rates derive from the sub multiples of the SONET and synchronous digital hierarchy (SDH) canonical speed of 155.52 Mbps. Each rate has a corresponding target range. However, the overall transmission data rate depends on a number of factors such as the loop length, wire gauge, type of the cable, presence of bridged taps, and the crosstalk coupled interference. Also, line attenuation tends to increase as the line length increases. Hence, line attenuation must be taken into account during the design stages of a VDSL system.

#### b) Transmit Power and Power Spectral Density

The transmit power spectral density (PSD) describes how the power of a information bearing signal is distributed in frequency when the signal is applied to the channel at the transmitter output. A transmit PSD mask specifies the maximum allowable transmit PSD, which is by definition a function of frequency. The maximum allowable transmit power specified by both ANSI and ETSI is 11.5 dBm for a VDSL system. Both the groups have defined the masks specifying the maximum allowable transmit PSD, and require modems to be capable of reducing their transmit PSD to -80 dBm/Hz [7]. The PSD may be independently selected for the downstream and upstream directions of transmission. Regardless of mask option, the total transmitted power should not exceed 11.5 dBm. As mentioned previously, VDSL modems are deployed from the ONU which is typically located in a small curbside cabinet with no temperature control mechanisms. Thus, VDSL power consumption must be less than 1.5 Watts per transceiver, including line drivers.

#### c) Spectral Compatibility

If a VDSL system has to be viable, it must be spectrally compatible with other DSL services that may reside in the same cable. The DSL service most vulnerable to interference from VDSL is ADSL. VDSL can harm the performance of ADSL and the vice-versa can also occur. In FTTC architecture, VDSL can be detrimental to ADSL performance, since VDSL signals can couple into ADSL signals as Near-End-Crosstalk (NEXT) or Far-end -crosstalk (FEXT). The effect of VDSL on ADSL performance is quantified in [8]. Simulations in [8] show that if the downstream VDSL transmission is below 1.104 MHz, it adversely affects the ADSL performance in the FTTC configuration. For example, when a 300 meter VDSL line injects FEXT into the ADSL line, the range for a fixed bit rate of 6 Mbps decreases from 3.75 km to only 2.75 km, and for a fixed range of 3.75 km, the bit rate decreases from 6 Mbps to 3.5 Mbps. To avoid such a substantial degradation in the ADSL performance,

the VDSL must be restricted from transmitting at -60 dBm/Hz either upstream or downstream in the band below 1.104 MHz when the ADSL loops reside in the same binder.

#### 1.2 VDSL Issues

At present, there is no complete standard, defining VDSL; however, the issue of standards is under consideration by both ANSI as well as ETSI. The most important VDSL question concerns the maximum distance for which a VDSL system can operate reliably for a given data rate i.e. the last-mile problem. This is a difficult question, since the real line characteristics at high frequency of operation of a VDSL system are not easy to measure, and the items such as short bridged taps or unterminated extension lines in homes may have detrimental effects on the VDSL in certain configurations. The disadvantage of the VDSL system compared to other DSL systems is its short copper loops that make the distribution area shrink to a few dozen customers. To make the VDSL systems more economical and to increase the distribution area, the design of such a system has to focus on increasing the length of the copper line without a loss in the bandwidth efficiency. In order to increase the loop length, the bit rate has to be compromised. To ensure a reliable transmission of data over longer loops and also to provide the end user with a maximal bit rate at a very low bit error rate (BER), a good forward error correction (FEC) scheme with a high coding gain is required. The FEC scheme for the VDSL systems that is under consideration in T1.413 proposal is a concatenated coding scheme consisting of an inner Trellis code (4-D Wei's code [9]) and an outer Reed-Solomon (RS) code [10]. There are two problems with this approach. First, the system operates far below the channel capacity. Second, the power penalty is more for multi-dimensional constellations. Though the 4D Wei-RS scheme has a high spectral efficiency of 6.12

bits/s/Hz, it requires a high signal-to-noise ratio (SNR) of 27 dB to reach the targeted BER. In order to maintain this high SNR, the bit rate available to the end customer has to be drastically reduced or the transmitting power has to be increased. Increasing the transmitting power increases the crosstalk which is detrimental to the VDSL performance in terms of bit rate and loop length. On the other hand, if the bit rate has to be kept constant, the loop length must be decreased drastically in order to maintain the targeted BER. Due to the concatenation of 4D Wei code and RS code, error propagation occurs between the two decoders thereby degrading the BER performance. Hence, a coding scheme which can achieve the targeted BER at a lower SNR than the 4D Wei-RS scheme can successfully address the last-mile problem.

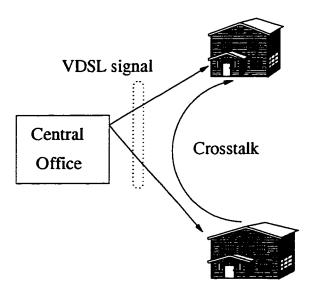

The second issue is interference due to the existing services associated with the twisted pair lines while providing enough bandwidth to support the required highdata rates [11]-[12]. The proposal to use the existing telephone wiring in homes for computer networking (home local area network (home-LAN)) avoids laying of additional wires in the same premise [11]. Due to the spectral crowding of home-LAN on the twisted pair lines, a severe performance loss in the VDSL services occur. To provide a better infrastructure for the internet services, it is desirable for both the VDSL and home-LAN systems to co-exist on the same twisted pair lines. This can be made possible by advanced receiver architectures and multiuser detection techniques [12]. Cioffi and Zeng proposed a crosstalk cancellation technique in [13], in which the crosstalk is estimated in some frequency bands and cancelled in others. But the authors considered NEXT as a major crosstalk which is not the case in general. Several authors proposed multiuser detection techniques to identify and cancel the crosstalk via iterative decoding [14] and [15]. In [15], a linear soft interference canceller has been proposed to reduce the interference with a small loss of VDSL signal bandwidth. These previously presented receivers for multi-user detection are complex to implement. The complexity involved in the multi-user detection can

be reduced if iterative-decoding methods are used [12]. Hence, a low complex soft interference canceller coupled with a good coding scheme is necessary to mitigate the home-LAN interference on VDSL.

From the above discussion, we conclude that a good coding scheme is required to provide a solution for the VDSL issues. The introduction of turbo codes in 1993 by Berrou is perhaps one of the most important contributions in the coding theory in this decade [16]. The performance of this coding scheme approaches close to the Shannon limit. Hence, it is worth addressing the two VDSL issues discussed above using turbo codes.

## 1.3 Scope and Organization of the Thesis

The objective of this thesis is to address the last-mile problem and the home-LAN interference problems of VDSL systems. Regarding the first problem, we propose a bandwidth efficient turbo coding scheme that is more suitable for VDSL modems. The objective of this scheme is to provide a higher coding gain than that provided by the standard 4D Wei-RS scheme, to result in an improved performance in terms of the bit rate, loop length and transmitting power. Also, due to the large volume of data in VDSL applications, the use of turbo codes can avoid the problem of fixed length code word. Some design criteria are presented for constructing good constituent codes for VDSL systems. A mapping method which can maximize the inter-signal Euclidean distance is proposed. The interleaver size, the number of decoder iterations, the code complexity and the level of modulation are the important parameters in determining the coding gain provided by the turbo codes. Hence, the effect of these parameters on the performance of the VDSL modems is explored. The proposed scheme is investigated for different signal frequencies, values of transmitting power, numbers of crosstalkers and loop lengths. Also, since the VDSL systems are delay sensitive, a pipe-lined decoding scheme is proposed to reduce the latency

generated due the iterations in the decoder. To compare the hardware complexity, the proposed and 4D Wei-RS schemes are synthesized using Xilinx Synthesizer. The Xilinx FPGA statistics of the proposed scheme is compared with that of the 4D Wei-RS scheme. A simulation study on the implementation of the proposed scheme is carried out to evaluate the achievable bit rates and loop lengths of the VDSL modems. The results are compared with that of the standard 4D Wei-RS scheme.

To mitigate the effect of home-LAN on VDSL, an iterative soft interference cancellation and decoding technique is proposed. The VDSL and home-LAN signals are jointly detected using a soft interference canceller and a soft-in soft-out demodulator combined with a set of turbo decoders. The soft interference canceller uses the a priori probabilities to perform the soft interference cancellation. The turbo decoder produces a posteriori probabilities which are fed back to the soft interference canceller as a priori probabilities.

The thesis is organized as follows. In Chapter 2, VDSL line impairments are discussed along with the need for a good coding scheme to improve the VDSL performance in terms of bit rate, loop length and transmitting frequency. A brief overview of the existing 4D Wei-RS scheme is provided. Two line codes, quadrature amplitude modulation (QAM) and discrete multi-tone modulation (DMT), that are presently under consideration by ANSI and ETSI for VDSL systems are presented and a comparison is provided.

In Chapter 3, the proposed turbo coding scheme for the VDSL systems is presented. Complexity analysis is carried out to compare the proposed scheme with 4D Wei-RS scheme. To compare the hardware complexity, the proposed and the 4D Wei-RS scheme are synthesized using Xilinx Synthesizer. The mapping method used in the proposed scheme is discussed. To reduce the delay generated in the decoder, a pipe-lined decoding scheme is presented. Simulation results are discussed to evaluate the BER performance of the proposed scheme and the results compared with that of the 4D Wei-RS scheme.

In Chapter 4, the performance of the VDSL systems employing the proposed scheme is discussed. The effect of transmitting power, transmitting frequency and the the numbers of cross talkers are discussed. The channel capacity and bit rates provided by the VDSL systems employing the proposed scheme are evaluated. Results are compared with that of the 4D Wei-RS scheme.

In Chapter 5, an iterative soft interference cancellation and decoding technique is presented to mitigate the effect of home-LAN on VDSL. Simulation results are discussed to evaluate the performance of this technique.

Chapter 6 concludes the thesis by summarizing and highlighting the significant results of this investigation.

## Chapter 2

# VDSL Line Impairments and Impact of Coding in VDSL Systems

### 2.1 Introduction

For a VDSL system, the strength of the received signal is determined by the strength of the signal from the corresponding transmitter and the attenuation of the telephone subscriber loop [17]-[19]. Also, channel capacity of a telephone subscriber loop is determined by the transmit signal level, channel attenuation, and the receiver front end noise. Hence, to design an efficient VDSL system, an analysis has to be performed on the VDSL channel and the transceiver front end noise models.

In this chapter, a VDSL channel model is presented and the channel attenuation characteristics are discussed. Various VDSL line impairments are presented along with their models. Using the VDSL channel model and the front end noise models, the SNR of a VDSL signal at the receiver front end is analyzed. Based on the analysis impact of a good coding scheme on the VDSL systems is explained. We also discuss the existing FEC scheme for the VDSL systems and its disadvantages. Finally, two different line codes QAM and DMT that are under consideration by ANSI and ETSI to be employed in a VDSL system are presented and a comparison

| Gauge | $k_1 (\times 10^{-3})$ | $k_2 (\times 10^{-8})$ |

|-------|------------------------|------------------------|

| 22    | 3.0                    | 0.035                  |

| 24    | 3.8                    | -0.541                 |

| 26    | 4.8                    | -1.709                 |

Table 2.1: Parameters for a simplified cable model.

is drawn out.

### 2.2 VDSL Channel Model

The twisted pair channel model has been investigated and modeled in [1] and [19]. Since VDSL operates in a high frequency range (f > 1 MHz), the simplified high frequency twisted pair channel transfer function can be formulated as

$$H(d, f) = e^{-d(k_1\sqrt{f} + k_2 f)},$$

(2.1)

where d is the length of the twisted pair cable in miles, f the frequency of operation in Hz, and  $k_1$  and  $k_2$  the proportional constants which are shown in Table 2.1.

The received signal power spectrum density, S(f), is determined by the transmit power spectrum density, Q(f), and the twisted pair loop channel transfer function, H(f), as shown in the following expression

$$S(f) = Q(f) |H(f)|^{2}$$

$$= Q(f)e^{-2d(k_{1}\sqrt{f}+k_{2}f)}$$

(2.2)

Let us examine the signal attenuation (insertion loss) that can occur in a VDSL channel. In general, signal attenuation increases with an increase in the frequency. The rate at which the attenuation increases is a function of line length and wire gauge as shown below

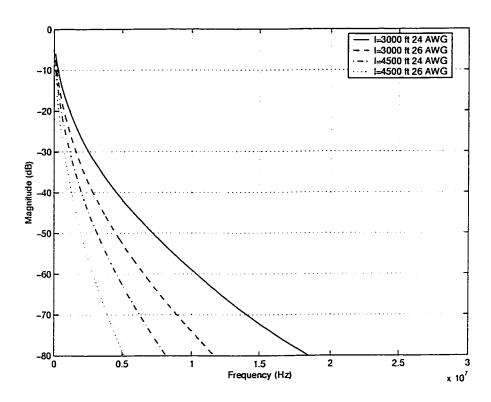

Figure 2.1: Attenuation as a function of frequency of two 26 AWG (0.4 mm) lines and two 24 AWG (0.5 mm) lines.

$$|H(f)|^2 = e^{-2d(k_1\sqrt{f} + k_2 f)}$$

(2.3)

Figure 2.1 illustrates the signal attenuation as a function of frequency for four different twisted pair loops: 3000 ft and 4500 ft of 26 AWG (or 0.4 mm) line, 3000 ft and 4500 ft of 24 AWG (or 0.5 mm) lines. The attenuation curves are smooth because the loops are terminated in the appropriate characteristic impedance at both ends. Comparison of the four curves show the relationship between the signal attenuation, line length, and wire gauge. Signals on longer wires composed of smaller diameter wires are attenuated very rapidly with an increase in the frequency, whereas shorter lines made of larger diameter wires cause a more gentle increase in the attenuation with an increase in the frequency. A single line terminated in an appropriate impedance at both ends is preferred for VDSL transmission since in this case, the attenuation is smooth with frequency. However, many twisted pair lines do not exhibit such smooth attenuation because of bridged tap configurations in which an unused twisted pair line is connected in shunt to the main cable pair.

## 2.3 VDSL Line Impairments

Besides the limitation of a transceiver hardware noise floor, the other types of noises that effect the performance of a VDSL system are background noise, crosstalk noise, impulse noise, and radio frequency interference (RFI). The severity of a noise is usually measured from its power level or its power density level. The noise power is usually expressed in dBm [5] and is defined as

$$P = 10 \times \log_{10} \frac{v^2}{R \times p_m} = 10 \times \log_{10} \frac{v^2}{100 \times 0.001},$$

(2.4)

where, v is the average voltage of noise,  $R = 100\Omega$  the receiver input impedance, and  $P_m = 0.001$  the reference of 1 milli-Watt. The noise power density usually expressed

in units of dBm/Hz is defined as

$$PSD = 10 \times \log_{10} \frac{v^2}{R \times P_m \times B} = 10 \times \log_{10} \frac{v^2}{0.1 \times B},$$

(2.5)

where B is the bandwidth of noise in hertz.

#### 2.3.1 Background Noise

Background noise in the telephone subscriber loop can be caused by a combination of the radio noise and the noise generated by electrical and electronic devices. The probability density of the background noise is very close to the Gaussian distribution. Therefore, background noise can be modelled as a Gaussian noise. Based on the results from the Bellcore noise survey, the background noise level in the twisted pair telephone loop has been assumed to be -140 dBm/Hz [20].

#### 2.3.2 Crosstalk Noise

Due to the capacitive and inductive coupling of the binder groups, there is a crosstalk between each twisted pair even though the pairs are well insulated. As a result, a local receiver can detect signals transmitted on the other lines, thus increasing the noise power and degrading the received signal quality on that line. For VDSL systems crosstalk could become a limiting factor to the achievable throughput. There are two different types of crosstalks that can occur in a VDSL loop: Near End Crosstalk (NEXT) and Far End Crosstalk (FEXT) [21]. To adjust the interference level when the number of interferers differ from 49, we use a de-rating factor of  $6 \times \log_{10}(n)$ . This is called as 6-dB noise margin.

#### 2.3.2.1 Near End Crosstalk

NEXT as shown in Figure 2.2 occurs when a local receiver detects signals transmitted on the other lines by one or more local transmitters. The level of NEXT detected

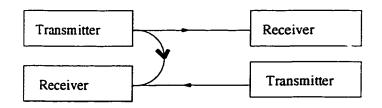

Figure 2.2: Illustration of near-end crosstalk (NEXT).

at a local receiver is primarily dependent on the number of interferers, proximity to the line of interest, relative power, spectral shapes of the interfering signals, and the frequency band over which NEXT occurs.

In general, NEXT coupling between adjacent lines in a cable is worse than NEXT between lines spaced further apart. Also, NEXT worsens if the transmit power on the interfering lines are increased. The simplified Unger NEXT model generalized for K disturbers [5] is given by

$$N_N = \left(\frac{K}{49}\right)^{0.6} \frac{1}{1.134 \times 10^{13}} f^{\frac{3}{2}} \tag{2.6}$$

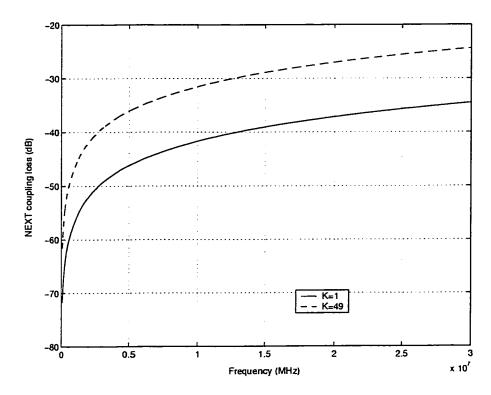

Figure 2.3 shows the NEXT coupling loss for 1 and 49 disturbers with a 6 dB noise margin. From the figure we can observe that, the loss difference between 1 disturber and 49 disturbers is about 10 dB. However, NEXT can be eliminated by employing the frequency division multiplexing (FDM) approach in which one directional transmission is adopted among all the telephone subscriber loops. Hence, in this work the effect of NEXT is neglected.

#### 2.3.2.2 Far End Crosstalk

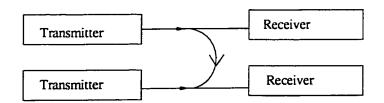

FEXT, as shown in Figure 2.4, occurs when a local receiver detects signals transmitted in its frequency band by one or more remote transmitters. As in the case of NEXT, the level of FEXT is dependent on the number of interferers, proximity to the line of interest, relative power, spectral shapes of the interfering signals, and the frequency band over which FEXT occurs. A simplified Unger FEXT model

Figure 2.3: Next coupling with 6 dB noise margin.

generalized to K disturbers [5] can be expressed as

$$N_F = \left(\frac{K}{49}\right)^{0.6} k df^2 |H(f)|^2 \tag{2.7}$$

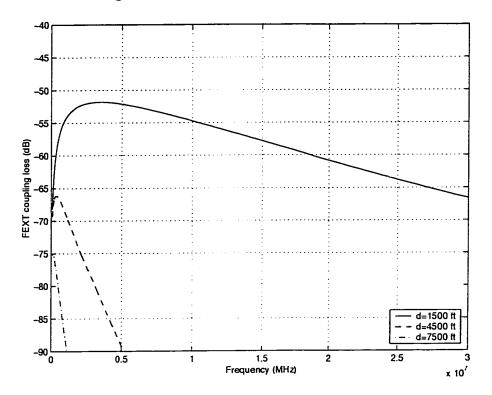

where,  $k = 8 \times 10^{-20}$ , d the loop length in feet, f the frequency in Hz, and H(f) is the transfer function of the loop. Figure 2.5 shows the FEXT coupling loss due to 49 disturbers for 1500 ft, 4500 ft, and 7500 ft loop lengths. From the graph, it is observed that FEXT decreases with an increase in the loop length. But, this is not the case with NEXT which is independent of line length. This is because, as the loop length increases, FEXT signals gradually attenuates. For this reason, FEXT is a minor impairment in longer loops. As VDSL employs smaller loops, the effect of FEXT is severe. On longer loops, the line attenuation is severe enough to counteract the  $f^2$  contribution to the FEXT coupling expression. Thus, the coupling curves decrease rapidly beyond some frequency.

Figure 2.4: Illustration of far-end crosstalk.

Figure 2.5: FEXT coupling loss with 6 dB noise margin for N=49.

## 2.3.3 Impulse Noise

Impulse noise is a short-duration, high-power burst of energy that can temporarily overwhelm information bearing signals. Impulse noise can be caused by electronic, electro-mechanical devices, and lightning [22]. To mitigate the impulse noise, a well-designed FEC scheme can be used with data interleaving. The interleaver rearranges the order of the coded bytes so that any impulse noise that corrupts a set of bytes, when de-interleaved are spread out in time. Also, the interaleaver reduces the time over which a single impulse harms the signal.

## 2.3.4 Radio Frequency Interference

Radio frequency interference noise appears at the receivers when over-the-air signals in overlapping frequency bands couple into phone lines. Overhead distribution cables and wires within homes, are particularly susceptible to interference from AM radio signals. AM interferers appear in the VDSL frequency spectrum as high-level noise spikes in the band between 525 kHz and 1.61 MHz [6]. However, radio frequency interference can be successfully eliminated by relying on the QAM based adaptive equalization techniques [23].

## 2.4 Impact of Coding

In this section, we discuss the need of a good coding scheme to improve the VDSL performance in terms of bit rate, loop length and transmitting power.

The disadvantage of the VDSL system compared to other DSL systems is its short copper loops that make the distribution area shrink to a few dozen customers. To make the VDSL systems more economical and to increase the distribution area, the design of such a system has to focus on increasing the length of the copper line without a loss in the bandwidth efficiency. To explain the impact of coding, we assume that FEXT and background noise are the major line impairments. The FEXT noise power spectral density is determined by the transmit power spectral density and the FEXT coupling transfer function as

$$N_F = Q(f) |H(f)|^2 k df^2$$

(2.8)

By including the background noise power density, the received SNR becomes

$$\frac{S(f)}{N_F(f) + W} = \frac{1}{kdf^2 + \frac{\sigma^2}{P}e^{2d(k_1\sqrt{f} + k_2f)}},$$

(2.9)

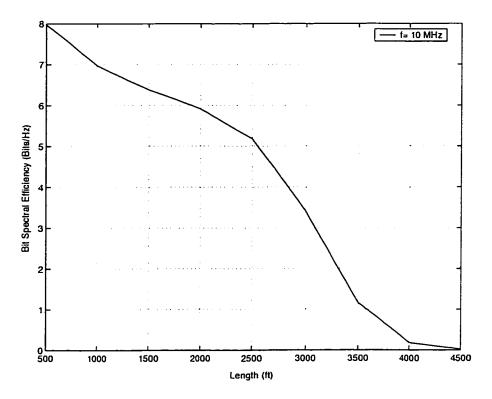

Figure 2.6: Spectral efficiency as a function of loop length.

where W is the white noise power density with total power  $\sigma^2$ , and P the total power of the transmit signal. As discussed in Section 1.1.2.2, the maximum allowable transmit signal PSD is -80 dBm/Hz. Hence, we set the value of P at an acceptable level of -70 dBm/Hz. The differential channel capacity for a VDSL system can be expressed as

$$\frac{dC}{dB} = \log_2\left(1 + \frac{S(f)}{N_F(f) + W}\right) = \log_2\left(1 + \frac{1}{kdf^2 + \frac{\sigma^2}{P}e^{2d(k_1\sqrt{f} + k_2f)}}\right)$$

(2.10)

From Figure 2.6, we can observe the trade off between the spectral efficiency of a VDSL system and loop length. Due to this, the user located near the CO receives high bit-rate data, whereas the user far from the CO receives the data with low bit rate.

In order to explain the necessity for a coding scheme to improve the VDSL performance, we examine the SNR of the received VDSL signal at the receiver.

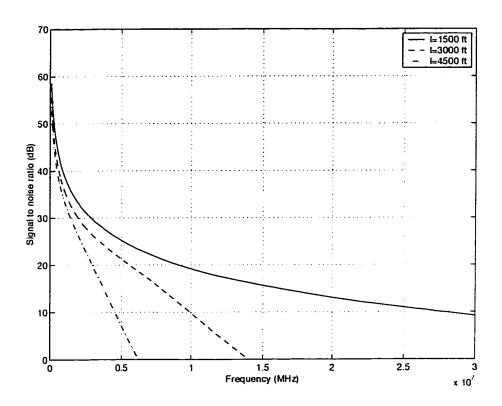

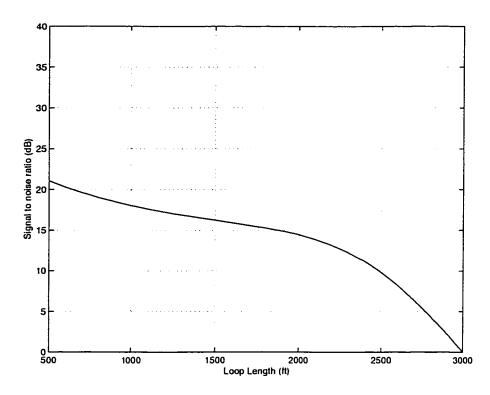

Figure 2.7 shows the SNR as a function of frequency under the FEXT plus white noise condition for a 24-gauge twisted-pair loop with background noise level -140 dBm/Hz. From this graph we can see the compromise between the parameters SNR, loop length, and frequency of operation. For a fixed frequency of operation, if the targeted BER can be achieved for a lower SNR, the loop length can be increased. On the other hand, for a fixed loop length, if the targeted BER can be achieved for a lower SNR, the frequency of operation can be increased thereby increasing the bit rate and reducing the line attenuation (refer to Figure 2.1). Figure 2.8 shows the SNR as a function of loop length for a frequency of operation of 14 MHz. From this figure we can conclude that, the lower the SNR, the longer the loop length that can be realized. Due to the trade off between the SNR and the bit rate in VDSL loops, user located near the CO receives high bit rate data, whereas user located far from the CO receives the data with low bit rate. From Figure 2.8, we can observe that, the received SNR decreases as the loop length increases because the signal attenuates more with an increase in the loop length. As the signal attenuation increases, the BER performance of the VDSL system degrades. Hence, if VDSL systems can achieve the targeted BER for a lower SNR, the loop length can be increased. These requirements suggest the necessity of employing a bandwidth and power-efficient coding scheme in the VDSL loops to provide the end user with a maximal bit rate.

## 2.5 Overview of the Existing Coding Scheme

In this section a brief overview of the existing coding scheme for the VDSL systems is presented. The xisting coding scheme for the VDSL systems employs a 4D Wei-RS code as an inner code and Reed-Solomon code as an outer code as shown in Fig 2.9.

Figure 2.7: Signal-to-self-FEXT plus white noise ratio for 24-gauge twisted-pair loop.

Figure 2.8: Signal-to-self-FEXT plus white noise ratio for 24-gauge twisted-pair loop as a function of loop length.

Figure 2.9: 4D Wei-RS coding scheme.

### 2.5.1 Reed-Solomon Coding

Reed-Solomon (RS) codes are cyclic block codes that perform forward error control by using redundancy bits. The data is partitioned into symbols of m bits and each symbol is processed as one unit by encoder and decoder. RS codes are described as (n,k) block codes, where n is the coded data block length and k is the uncoded data block length. The extra (n-k) symbols are called the parity check symbols. The RS code satisfies:  $n \leq 2^m - 1$  and  $n - k \geq 2t$ , where t is the number of correctable symbol errors. Under the assumption that errors are independently distributed the symbol error rate can be estimated by

$$P_e = \sum_{i=t+1}^{n} \binom{n-1}{i-1} P^i (1-P)^{n-i}, \qquad (2.11)$$

where P is the symbol error probability. In a VDSL system, the number of data symbols and the size of the code word vary depending on the VDSL data frame structure. The VDSL RS codes operate in Galois Field GF( $2^8$ ). A popular RS code used in VDSL is RS(255,223) with 8 bit symbols. For this code each codeword contains 255 bytes, of which 223 bytes are data symbols and 32 bytes are redundant parity symbols [10].

The interleaver is used to rearrange the coded data such that the location of errors look random and is distributed over many code words rather than a few code words. A periodic interleaver of depth m reads m code words of length n each and arrange them in a block with m rows and n columns. Then this block is read column wise. In the deinterleaver the bits are rearranged back to its original order. When an erroneous decision is made in the Trellis decoder it takes some sub symbols to reach the correct the trellis path again. This makes the interleaving useful in trellis coded modulation (TCM) systems where error bursts occur.

### 2.5.2 16 State 4D Wei Coder

Trellis-coded modulation is an optional coding and modulation scheme for VDSL to either meet the performance requirement for longer loops or increase the transmission throughput under a certain performance margin. In VDSL, TCM uses Wei's 16 state four-dimensional (4D) convolutional encoder. This code has a theoretical coding gain of 4.5 dB. Figure 2.12 shows the trellis encoder structure in VDSL. Fig. shows the Wei's 16-state 4D convolutional encoding circuit [9].

The trellis encoder takes a set of bits  $u = \{u_1, u_2, ...\}$  as its input. Because of the 4-dimensional nature of the encoder, each word u is encoded into two binary symbols v and w, which are modulated into two constellation points. The encoding process can be summarized as

- 1) Encode  $(u_1, u_2)$  using Wei's 16-state 4D rate 2/3 convolutional encoder to produce  $(u_0, u_1, u_2)$ , in which  $(u_1, u_2)$  are unchanged and  $u_0 = S_0$ .

- 2)  $(u_0, u_1, u_2)$  is used to select one of the eight 4D subset.

- 3) The subset is mapped to two indices that determine the least significant bits (LSBs) of u and w. The mapping method is

$$v_{o} = u_{3}$$

$$v_{1} = u_{1} \oplus u_{3}$$

$$w_{0} = u_{2} \oplus u_{3}$$

$$w_{1} = u_{0} \oplus u_{1} \oplus u_{2} \oplus u_{3}$$

$$(2.12)$$

4) The remaining bits of u and v are directly mapped to the most significant bits (MSBs) of v and w.

The subset in the Wei's code is the union of two Cartesian products of two 2D subsets. Figure 2.11 shows the 2D subsets used by Wei's 4D code. The numbers in the figure represent the 2D subset indices, which are in fact the decimal values of two LSBs of v and w.

Figure 2.10: Wei's 4D 16 State encoder.

TCM decoder reads a pair of constellation points and takes them as its input. Soft-decision Viterbi decoding is used to decode the 4D code. The output of the decoder is an estimated sequence of received constellation points. After that, QAM decoder converts the constellation points into a set of bits.

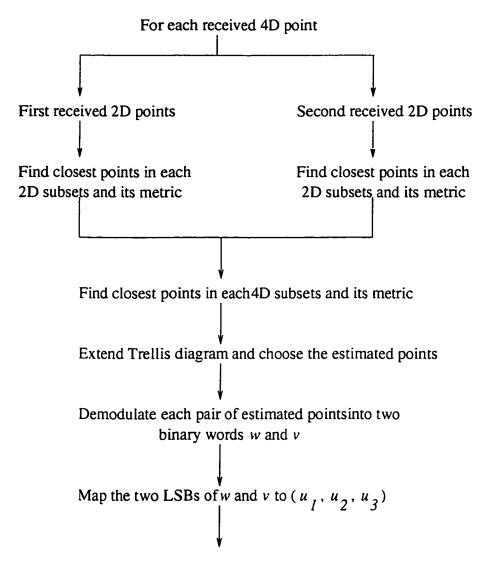

Figure 2.13 shows the viterbi decoding process. The metric used in the decoding is the Euclidean distance. The 4D metric can be obtained by adding the two 2D subset metrics for the pair of 2D subsets corresponding to that 4D subset.

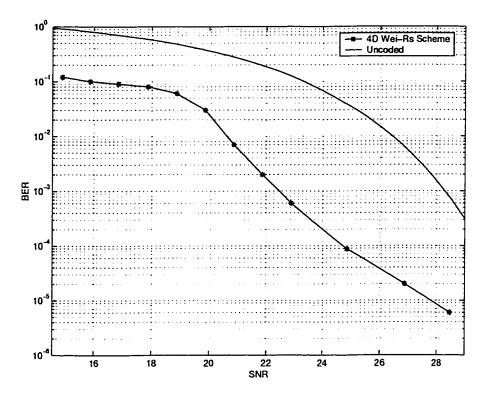

Figure 2.14 shows the BER performance of the 4D Wei-RS scheme. The asymptotic coding gain of this code is approximately 4-4.5 dB. The drawback of this scheme is that it requires a SNR higher than 27 dB to reach the targeted BER of 10<sup>-5</sup>, though it provides a high spectral efficiency of 6.12 bits/s/Hz. In order to maintain this high SNR, the bit rate available to the end user has to be drastically reduced. On the other hand, if a coding scheme can be devised to provide a high coding gain at the expense of some loss in the spectral efficiency, most of the transmitting power can be utilized to achieve high signal frequency in order to provide a high data rate.

Figure 2.11: 2-dimensional subsets for Wei's code.

Figure 2.12: Wei's 16-state 4D convolutional encoder.

Directly map the remaining bits of w and v to the MSBs of u

Figure 2.13: Decoding Wei's code.

Figure 2.14: BER Performance of 4D Wei-RS scheme.

## 2.6 VDSL Line Codes

In this section, we briefly discuss two line codes, QAM and DMT, which are under consideration to be employed in a VDSL system, and make a comparison to determine which one can best realize the VDSL's potential.

## 2.6.1 CAP/QAM

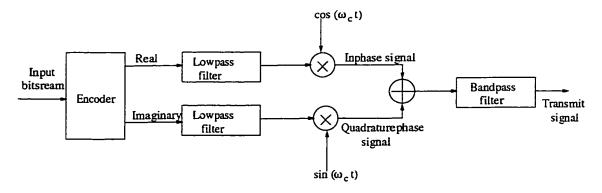

The CAP/QAM proposal is associated with the frequency division multiplexing (FDM) for the upstream and downstream channels. Figure 2.15 [6] shows the general structure of a QAM VDSL transmitter. A bit stream is encoded into symbols by mapping consecutive sets of b bits, where b is generally less than 8, into constellation points. These constellation points are then modulated, filtered, and transmitted within some predetermined channel bandwidth.

Figure 2.15: QAM transmitter block diagram.

### 2.6.2 DMT

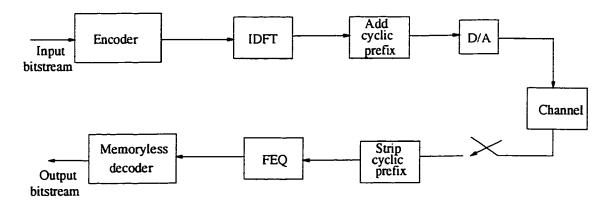

DMT is a multi-carrier modulation technique in which channel is partitioned into a set of orthogonal, independent sub-channels, each of which supports a distinct carrier. Figure 2.16 [6] shows the general transceiver structure of a DMT system. The source bits are encoded into a set of QAM sub symbols, each of which represents a number of bits determined by the SNR. The set of sub symbols is then input as a block to a complex-to-real inverse discrete Fourier transform (IDFT). Following the IDFT, a cyclic prefix is prepended to the output samples to mitigate inter-symbol interference (ISI). The resulting time domain samples are converted from digital to analog format and applied to the channel. At the receiver, after analog-to-digital conversion, the cyclic prefix is stripped, and the noisy samples are transformed back to the frequency domain by a discrete Fourier transform (DFT). Each output value is then scaled by a single complex number to compensate for the magnitude and phase of its sub-channel's frequency response and further processed by a frequency-domain equalizer (FEQ). After the FEQ, a memory less detector decodes the sub symbols. The DMT proposal deals with the time division multiplexing (TDM).

Figure 2.16: DMT Transmitter/Receiver pair Block Diagram.

## 2.6.3 Comparison of QAM and DMT

Here, a comparison of QAM and DMT techniques is presented in order to determine which technology can best realize VDSL's potential [24], [25].

The QAM approach rely on time-domain processing of signals thus taking into account the serial and analog nature of the signal on the wire. On the other hand, the DMT approach focuses on frequency-domain processing of the signal. It requires a time-to-frequency and serial-to-parallel data stream conversion at each end of the line.

Another important consideration is power. A area of a QAM chip will be about  $14mm^2$  and the power consumption will be about 110 mW. Whereas, the area of a DMT chip will be about  $50mm^2$  in area with power consumption of 138 mW.

Considering the ingress and egress problems, adaptive equalization algorithms in QAM can cope with incoming narrow band disturbers the to mitigate ingress, and programmable notch filters can be employed to mitigate egress. The same approach used for QAM is also used for DMT to address ingress and egress problems. But spurious, transient ingress interference, such as RFI is a more significant problem for DMT. This is because, in this case, the noise frequency has to be detected, communicated between transmitter and receiver and then compensated by the DSP

circuitry. During the detection and compensation time, the data traffic being processed must be thrown away. On the other hand, QAM-based solutions rely on adaptive equalization techniques where no detection and communication between transmitter and receiver is needed.

In summary, QAM technology fits well with the VDSL requirements and the POTS environment.

## 2.7 Conclusion

In this chapter, VDSL line impairments and the necessity of a good coding scheme to improve the VDSL performance have been discussed. A VDSL channel model has been presented and is shown that the signals on longer wires composed of smaller diameter are attenuated rapidly, and shorter wires made of larger diameter cause a more gentle increase in the attenuation. The NEXT and FEXT models have been analyzed. The analysis has shown that the FEXT is more detrimental to VDSL compared to NEXT.

To explain the disadvantage of the present VDSL systems, the trade offs between the spectral efficiency and loop length of a VDSL system have been observed. In order to determine the impact of coding, the trade off between the received SNR, loop length, and transmitting frequency has been analyzed and concluded that, if the targeted BER can be achieved for a lower SNR, either the loop length or the transmitting frequency can be increased. The analysis has shown the necessity of a higher coding gain for the FEC scheme in the VDSL systems to provide the end user with a maximal bit rate.

The existing FEC (a concatenated 4D Wei-RS) scheme for VDSL systems and its disadvantages have been discussed. The drawback of this scheme is that, it is very complex to implement, and requires a high SNR of 22 dB to achieve the targeted BER of 10<sup>-5</sup>. Hence, a good FEC scheme that can achieve the targeted BER for a

lower SNR and is less complex than that of the 4D Wei-RS scheme is required.

Finally, the two line codes, QAM and DMT, that are under consideration by ANSI and ETSI to be implemented in a VDSL system have been discussed and concluded that the QAM has a better advantage than the DMT and can be successfully implemented in a VDSL system.

## Chapter 3

# A Bandwidth Efficient Turbo Coding Scheme for VDSL

## 3.1 Introduction

The most important VDSL question concerns the maximum distance for which a VDSL system can operate reliably for a given data rate i.e. the last-mile problem. In order to provide a solution to the last-mile problem, the design of the VDSL system has to focus on increasing the length of the copper line without a loss in the bandwidth efficiency. As discussed in Chapter 2, to ensure a reliable transmission of data over longer loops and also to provide the end user with a maximal BER, a good FEC scheme with a high coding gain is required. Since a VDSL has generally to deal with huge multimedia applications, the FEC scheme should be less complex in order to reduce the decoding delay, and also it should be bandwidth efficient. The introduction of turbo codes in 1993 by Berrou is perhaps one of the most important contributions in the coding theory in this decade [16]. The performance of this coding scheme approaches close to the Shannon limit. However, conventional turbo codes are low-rate codes. Turbo codes can be combined with bandwidth efficient modulation to develop power efficient coding techniques without sacrificing

the bandwidth efficiency. There are various approaches that have been used to increase the spectral efficiency of the turbo codes [26]-[31].

This Chapter is organized as follows. In Section 3.2, the basic concepts of turbo codes are explained. In Section 3.3, a bandwidth-efficient turbo coding scheme that is more suitable for VDSL modems is proposed [32]. The objective of the proposed scheme is to provide a higher coding gain than that of the 4D Wei-RS scheme resulting in an improved performance in terms of bit rate, loop length and transmitting power. Some design criterion is presented for constructing good turbo codes for VDSL systems are presented. In Section 3.4, a pipe-lined decoding scheme is proposed in order to reduce the decoding delay at the receiver end. In Section 3.5, an analysis is carried out to compare the complexity of the proposed scheme with that of the existing scheme. To compare the hardware complexity, the proposed and the 4D Wei-RS scheme are synthesized using Xilinx synthesizer. The FPGA statistics of the proposed schemes compared with that of the 4D Wei-RS scheme. In Section 3.6, simulation results are presented to evaluate the performance of the proposed scheme and results are compared with that of the 4D Wei-RS scheme.

## 3.2 Basic Concepts of Turbo Codes

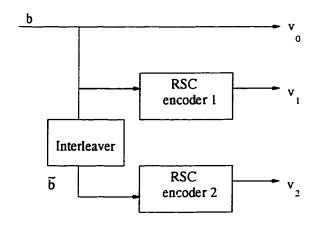

The turbo codes originally proposed consists of two parallel recursive systematic convolutional (RSC) encoders separated by an interleaver and uses an iterative soft input soft output (SISO) decoder. In this section, we will explain the general idea of turbo codes.

### 3.2.1 Turbo Encoder

A turbo encoder as shown in Figure 3.1, is formed by two RSC encoders with memory v (so that the number of states is  $2^v$ ), linked through an interleaver of length N. The role of the interleaver is to maximize the minimum Weight of the turbo code word

Figure 3.1: Turbo encoder.

at the output of the constituent encoders. The codeword is formed by adding the parity check bits generated by the first and second encoders to the input information bit. The Weight of the corresponding code word is given by  $d = w + z_1 + z_2$ , where w is the Weight of the information sequence, and  $z_1$  and  $z_2$  are the Weights of the first and second parity check sequences respectively. The effective free distance  $d_{free,eff}$  of the codeword [33] is given by

$$d_{free,eff} = 2 + 2z_{min}, \tag{3.1}$$

where  $z_{min}$  is the minimum free distance of the codeword. For a RSC code with a rate of 1/n and memory of v, the upper bound for  $z_{min}$  [33] is given by

$$z_{min} \le (n-1)(2^{v}+2) \tag{3.2}$$

The component codes and their rates are not necessarily the same. If the code rates of the two component encoders are denoted by  $R_1$  and  $R_2$ , the overall turbo code rate R can be determined by  $\frac{1}{R} = \frac{1}{R_1} + \frac{1}{R_2} - 1$  [34]. The overall code rate can be increased by suitably puncturing the original code. These punctured codes have a simpler Trellis structure than those of the corresponding non-punctured codes.

Figure 3.2: Turbo decoder.

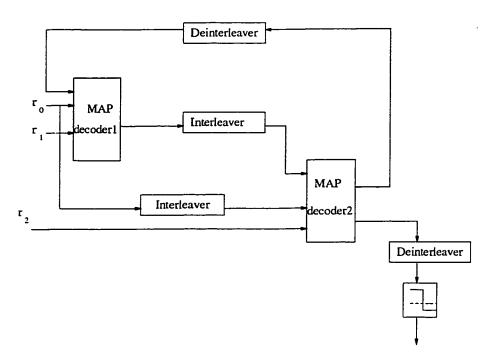

### 3.2.2 Turbo Decoder

A simple suboptimal iterative algorithm, where two soft-in soft-out (SISO) decoders are used in an iterative manner, is used in the decoder as shown in Figure 3.2. The  $maximum\ a\ posterioiri\ (MAP)$  criterion is used to provide a soft output. The LOG-MAP algorithm minimizes the bit error probability by computing the log-liklehood ratio (LLR) of the bit  $b\ [16]$ , [35], which is conditioned on the received sequence r, as given by

$$\Lambda(b_t) = log \frac{Pr(b_t = 1|r)}{Pr(b_t = 0|r)}$$

(3.3)

The first MAP decoder produces an estimate of the *a priori* probabilities for the information sequence for the second MAP decoder. This decoder also produces a soft output which is used to improve the estimate of the *a priori* probabilities for the information sequence at the input of the first MAP decoder. After a certain number of iterations, the soft outputs of both the MAP decoders stop to provide

further improvements in the performance. Finally, the last stage of decoding makes the hard decision after deinterleaving.

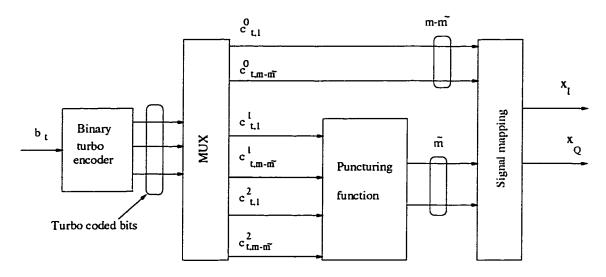

## 3.3 Bit Interleaved Turbo Coded Modulation

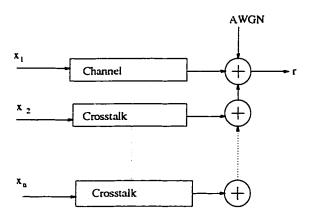

In this bit interleaved coded modulation (BICM) design, a single binary turbo code of rate 1/R is used. The RSC component code has a rate of  $1/n_0$ . The information bit b is first encoded by the turbo encoder to form the code bits given by  $c = \{c^0, c^1, c^2\}$ , where  $c^0$  is the first coded bit, which is equal to the information bit b,  $c^1$  is the second coded bit from the first RSC encoder and  $c^2$  is the third coded bit from the second RSC encoder. The encoder outputs are suitably multiplexed and punctured to obtain  $\tilde{m}$  parity symbols and m- $\tilde{m}$  information symbols as shown in Figure 3.3. These encoded symbols are mapped into an M-QAM signal set consisting of 2<sup>m</sup> points. A set  $\{c_i^j\}$  (i=1,...,m;j=0,1,2) of m bits is mapped into a complex signal symbol x to be transmitted over the channel. Each symbol x is represented by a set of real-valued symbols  $\{x_I, x_Q\}$ . The spectral efficiency of this scheme is (m- $\tilde{m}$ ) bits/s/Hz. The conventional turbo decoder [29] for this approach treats the demodulation and the decoding process as two separate entities, thereby degrading the performance with respect to the coding gain. The performance loss can be avoided by treating the demodulation and decoding processes as two separate stages of a single process. This is done through the so called "turbo principle", in which the "soft" information is exchanged between the demodulation and decoding operations in an iterative manner. To implement this joint demodulation and decoding of the VDSL signal, some assumptions are made with respect to the signal itself. A VDSL signal can be expressed as

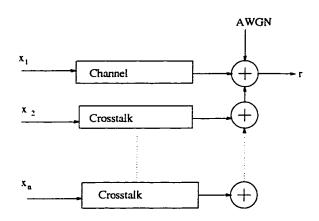

$$r = h.x + \sum_{i=2}^{n} f_i.\eta_i + N_0, \tag{3.4}$$

where r is the received symbol, x is transmitted symbol, h the VDSL channel gain,  $\eta_i$  the *i*th crosstalk signal,  $f_i$  the corresponding crosstalk coupling function and  $N_0$  the

additive white Gaussian noise (refer to Figure 3.4). Clearly y is the scaled version of x contaminated by a multiple access interference (MAI) and the channel noise, since we estimate each signal separately. Assuming that no knowledge of other signals is available, we can treat MAI as an extra "noise" source. As the MAI is independent of the channel noise, we can combine the MAI and the channel noise together and model the combined noise by another Gaussian distribution with its variance given by

$$\sigma_N^2 = \sigma_{MAI}^2 + \sigma_{AWGN}^2 \tag{3.5}$$

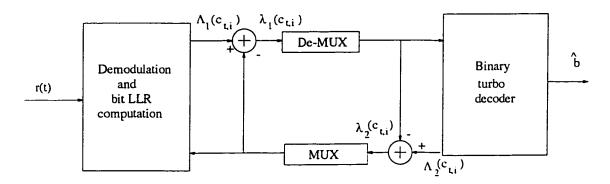

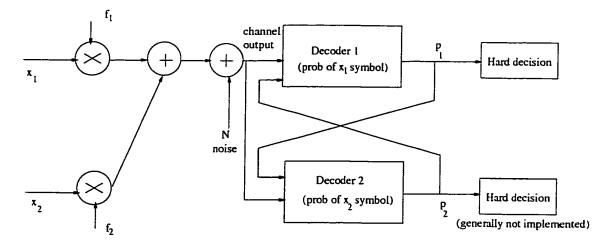

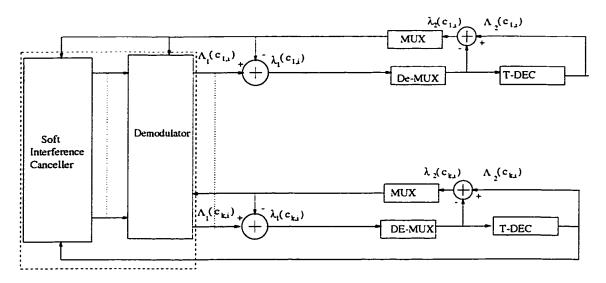

Figure 3.5 shows the proposed turbo structure for a joint demodulation and decoding process. Before giving the detailed analysis of this structure, we will briefly describe its operation. The received noisy symbols  $\{r\}$  are demapped and the log-likelihood ratio associated with each received bit is calculated. The log-likelihood ratio consists of a priori and extrinsic information. As the a priori information is not available to the demodulator during the first iteration, an equally likelihood assumption is made on the received symbols. The extrinsic information obtained from the demodulation stage is then demultiplexed and sent as a priori information to the binary turbo decoder. In turn, the binary turbo decoder computes the a posterioiri LLR of each code bit and then excludes the influence of its a priori information to obtain the extrinsic information of the decoding stage. This extrinsic information from the decoding stage is again suitably multiplexed and fed back to the demodulator as a priori information for the next iteration to improve the estimate of the received symbols. The operations carried out by the demodulator and decoder are repeated in an iterative manner. After the final iteration, the decoding stage makes hard decisions on its a posteriori LLR of the information bits. The receiver is thus expected to provide an improved performance by this iterative scheme as compared with the scheme in which the demodulation and decoding operations are two separate and distinct operations.

Figure 3.3: BICM encoder.

Figure 3.4: VDSL crosstalk channel model.

Figure 3.5: BICM decoder.

## 3.3.1 Demodulation and Bit LLR Computation

The log-likelihood ratio associated with each bit [14] can be calculated as

$$\Lambda_1(c_i^j) = log \frac{P(c_i^j = 1|r)}{P(c_i^j = 0|r)}$$

$$= log \frac{p(r|c_i^j = 1)}{p(r|c_i^j = 0)} + log \frac{P(c_i^j = 1)}{P(c_i^j = 0)}$$

$$= \lambda_1(c_i^j) + \lambda_2^p(c_i^j), \quad i = 1, ..., m$$

(3.6)

where,  $\lambda_1(c_i^j)$  denotes the soft metric corresponding to  $c_i^j$  delivered by the demodulation stage, and  $\lambda_2^p(c_i^j)$  is the *a priori* LLR delivered from the decoding stage in the previous iteration. The soft metric,  $\lambda_1(c_i^j)$ , is the extrinsic information delivered by the demodulation stage which is then deinterleaved and demultiplexed and sent to the channel decoder for further processing. For the first iteration, all the bits are assumed to be equally probable, and hence, this term is set to zero and it can be evaluated as

$$\lambda_1(c_i^j) = log \frac{p(r|c_i^j = 1)}{p(r|c_i^j = 0)}$$

$$= log \frac{p(r, c_i^j = 1)P(c_i^j = 0)}{p(r, c_i^j = 0)P(c_i^j = 1)}$$

(3.7)

By expressing the numerator and denominator of the operand used in (3.7) as summations of all m-bit M symbols, we can rewrite the equation as

$$\lambda_1(c_i^j) = log \frac{\sum_{x \in \chi(c_i^j = 1)} p(r, x) P(c_i^j = 0)}{\sum_{x \in \chi(c_i^j = 0)} p(r, x) P(c_i^j = 1)}$$

$$= log \frac{\sum_{x \in \chi(c_i'=1)} p(r|x) P(x) P(c_i^j = 0)}{\sum_{x \in \chi(c_i'=0)} p(r|x) P(x) P(c_i^j = 1)},$$

(3.8)

where,  $\chi$  represents the signal space of M symbols. Depending on the specific bit  $c_i$ , the signal space is divided into two sets,  $\chi(c_i^j = 1)$  and  $\chi(c_i^j = 0)$ . From the one-to-one correspondence between x and  $\{c_i^j\}$ , P(x) in the above equation can be replaced by  $\prod_{i=1}^m P(c_i^j)$ . Therefore, (3.8) can be rewritten as

$$\lambda_1(c_i^j) = \log \frac{\sum_{x \in \chi(c_i^j = 1)} p(r|x) \prod_{k \neq i}^m P(c_k^j = 1)}{\sum_{x \in \chi(c_i^j = 0)} p(r|x) \prod_{k \neq i}^m P(c_k^j = 0)},$$

(3.9)

where the conditional probability density function, p(r|x), is the likelihood function for the signal transmitted, and it is calculated as

$$p(r|x) = p(r_I, r_O|x_I, x_O)$$

$$=\frac{1}{\sqrt{2\pi}\sigma_N}exp\left[-\frac{|r-x|^2}{2\sigma_N^2}\right]$$

$$= \frac{1}{\sqrt{2\pi}\sigma_N} exp\left[-\frac{(r_I - x_I)^2 - (r_Q - x_Q)^2}{2\sigma_N^2}\right],$$

(3.10)